# SERVICE MANUAL Z-49 Video Display Terminal

NOTE: This is a PRELIMINARY manual. This publication has not been through our normal testing phase; therefore, it may contain technical inaccuracies. You will receive a final version of the manual after our normal evaluation cycle is completed.

585-45

860-38

HEATH

The purpose of this page is to make sure that all service bulletins are entered in this manual. When a service bulletin is received, annotate the manual and list the information in the record below.

### **Record of Service Bulletins**

| DATE<br>OF<br>ISSUE | CHANGED<br>PAGE(S) | PURPOSE OF SERVICE<br>BULLETIN | INITIALS            |

|---------------------|--------------------|--------------------------------|---------------------|

|                     |                    |                                |                     |

|                     |                    |                                |                     |

|                     |                    |                                |                     |

|                     |                    |                                |                     |

|                     |                    |                                |                     |

|                     |                    |                                |                     |

|                     |                    |                                |                     |

|                     | OF                 | OF PAGE(S)                     | OF PAGE(S) BULLETIN |

#### LIMITED RIGHTS LEGEND

Contractor is Zenith Data Systems Corporation of St. Joseph, Michigan 49085. The entire document is subject to Limited Rights data provisions.

PRELIMINARY GO

D

Copyright ©1984 Zenith Data Systems Corporation, all rights reserved. Printed in the United States of America

Zenith Data Systems Corporation St. Joseph, Michigan 49085

# Contents

| Record of Service Bulletins   | ii           |

|-------------------------------|--------------|

| Figures                       | viii         |

| Tables                        | ix           |

| Abbreviations                 | xi           |

|                               |              |

| Specifications                | xiii         |

| Video Display                 |              |

| Cursor                        |              |

| Communications                | xiv          |

| Editing and Erasing Functions |              |

| Printer Functions             |              |

| Environment                   | <b>xv</b>    |

| Power                         | xv           |

| Dimensions                    | xvi          |

| Keyboard                      | xvi          |

| Environment                   | <b>xv</b> ii |

| Dimensions                    | xvii         |

|                               |              |

| Introduction                  | xix          |

| The SMZ-49 Manual             | <b>xx</b>    |

| List of Tools                 |              |

| Test Equipment                | xxi          |

| List of Supplies              | xxii         |

|                               |              |

|                               | stallation   |

| Introduction                  |              |

| Video Display                 |              |

| Keyboard                      |              |

| Keyboard Indicators           |              |

| Keyboard Tilt Adjustment      |              |

| Voltage Selection             |              |

| Connections                   |              |

| Interfacing                   |              |

| DTE Device                    |              |

| Self-Check Tests              |              |

| POWER ON Indicator            | 1.11         |

|                               |              |

|                               | peration     |

| Introduction                  |              |

| Alphabetic Keys               |              |

| Nonalphabetic Keys            |              |

| Control Format Keys           |              |

| Keypad Keys                   |              |

| Special Purpose Keys          | 2.5          |

| Entering the Setup Mode       | 2.8          |

### Contents

| Main Menu Selection     | . 2.8 |

|-------------------------|-------|

| ON/OFF Line             |       |

| Primary Port Parameters | . 2.9 |

| Baud Rate               | . 2.9 |

| Duplex Mode             | 2.10  |

| Handshaking             | 2.10  |

| RTS/CTS Busy            | 2.11  |

| DTR/DSR Busy            | 2.12  |

| Stop Bits               | 2.12  |

| Parity                  | 2.13  |

| Aux Port Parameters     | 2.13  |

| Baud Rate               | 2.13  |

| Auto Print              | 2.14  |

| Blind Print             |       |

| Handshaking             |       |

| End With Form Feed      |       |

| DTR/DSR Busy            |       |

| Stop Bits               |       |

| Parity                  |       |

|                         |       |

| Display Parameters      |       |

| Wrap                    |       |

| Auto LF on CR           |       |

| Auto CR on LF           |       |

| Screen Saver            |       |

| Status Line             |       |

| Columns                 |       |

| Scroll                  |       |

| Hold Screen             |       |

| Cursor Parameters       |       |

| Cursor                  |       |

| Blink                   |       |

| Shape                   |       |

| Keyboard Parameters     |       |

| Key Click               |       |

| Keypad Shift            |       |

| Keypad Alt              |       |

| Auto Repeat             |       |

| Margin Bell             |       |

|                         |       |

|                         |       |

| Set Tabs                |       |

| Monitor Mode            | 2.25  |

| Mode ANSI/Zenith         Misc         Char Font         Line Frequency         Change Answer Back Message         One Pass Self Test         Continuous Self Test         Restore         Save         Programmable Keys         Function Type         Change User Function | 2.26<br>2.26<br>2.26<br>2.27<br>2.27<br>2.27<br>2.27<br>2.28<br>2.28<br>2.28<br>2.28 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Chapter 3                                                                                                                                                                                                                                                                   | Theory of Operation                                                                  |

|                                                                                                                                                                                                                                                                             |                                                                                      |

| Theory of Operation                                                                                                                                                                                                                                                         |                                                                                      |

|                                                                                                                                                                                                                                                                             |                                                                                      |

| Chapter 4                                                                                                                                                                                                                                                                   | <b>Detailed Circuit Description</b>                                                  |

| Introduction                                                                                                                                                                                                                                                                |                                                                                      |

| Keyboard Assembly                                                                                                                                                                                                                                                           |                                                                                      |

| Terminal Logic Board (TLB)                                                                                                                                                                                                                                                  |                                                                                      |

| Video Circuit Board                                                                                                                                                                                                                                                         |                                                                                      |

|                                                                                                                                                                                                                                                                             |                                                                                      |

|                                                                                                                                                                                                                                                                             |                                                                                      |

| Horizontal Circuits                                                                                                                                                                                                                                                         |                                                                                      |

| Power Supply                                                                                                                                                                                                                                                                |                                                                                      |

|                                                                                                                                                                                                                                                                             |                                                                                      |

| Chapter 5                                                                                                                                                                                                                                                                   | Disassembly                                                                          |

| Introduction                                                                                                                                                                                                                                                                |                                                                                      |

| Cabinet Top                                                                                                                                                                                                                                                                 |                                                                                      |

| Terminal Logic Board                                                                                                                                                                                                                                                        |                                                                                      |

| Video Circuit Board                                                                                                                                                                                                                                                         |                                                                                      |

| Power Supply                                                                                                                                                                                                                                                                |                                                                                      |

| Cathode Ray Tube                                                                                                                                                                                                                                                            |                                                                                      |

| Chapter 6                                                                                                                                                                                                                                                                   | Service Instructions                                                                 |

|                                                                                                                                                                                                                                                                             |                                                                                      |

| Safety Servicing Guidelines                                                                                                                                                                                                                                                 |                                                                                      |

| Warnings                                                                                                                                                                                                                                                                    |                                                                                      |

| Cautions                                                                                                                                                                                                                                                                    |                                                                                      |

| Cleaning Procedures                                                                                                                                                                                                                                                         |                                                                                      |

| -                                                                                                                                                                                                                                                                           |                                                                                      |

PRELIMINARY GOPY

{

Marginet

| VI |

|----|

|    |

|    |

### Contents

| Adjustments                             | .4 |

|-----------------------------------------|----|

| Horizontal Phase Control 6              | .5 |

| Brightness Control                      |    |

| Vertical Size Control                   | .5 |

| Horizontal Width Control 6              |    |

| Focus Control                           |    |

| Yoke Adjustments                        | .7 |

| Inspection                              | .8 |

| Testing and Troubleshooting 6           | .8 |

| General Troubleshooting                 | .8 |

| Power Supply Troubleshooting 6.         | 10 |

| Terminal Logic Board Troubleshooting 6. |    |

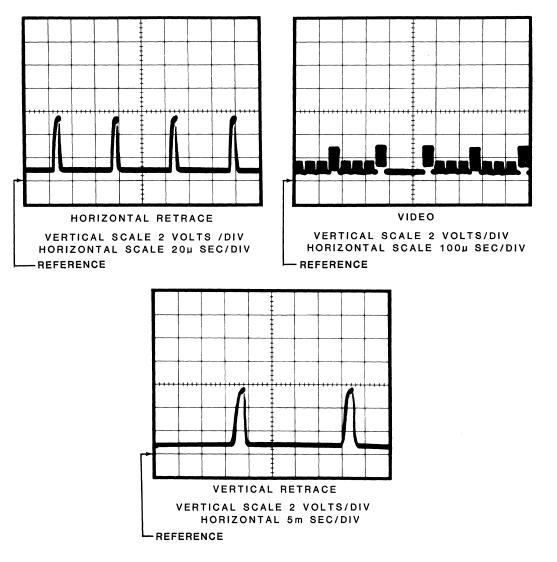

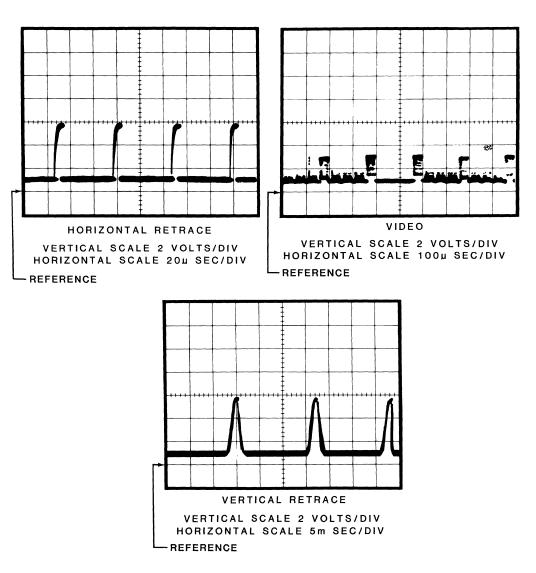

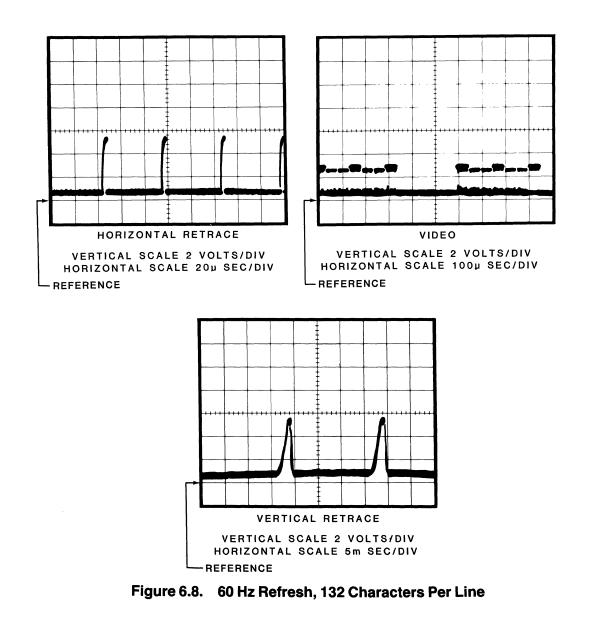

| Terminal Logic Board Waveforms 6.       |    |

| Video Driver Board Troubleshooting 6.   |    |

| Video Driver Board Waveforms 6.         |    |

| Transistor Voltage Measurements 6.2     |    |

| Picture Tube Voltage Measurements       |    |

| Keyboard Troubleshooting 6.3            | 23 |

#### Chapter 7

#### Reassembly

| Cathode Ray Tube Installation     | 7.1 |

|-----------------------------------|-----|

| Power Supply Installation         | 7.4 |

| Video Circuit Board Installation  | 7.6 |

| Terminal Logic Board Installation | 7.7 |

| Cabinet Top Installation          | 7.8 |

#### Chapter 8

| Chapter 8                    | Parts List |

|------------------------------|------------|

| Introduction                 | 8.1        |

| Video Display Unit           | 8.2        |

| Terminal Logic Board         | 8.3        |

| CRT Monitor/Video Driver     | 8.8        |

| Keyboard Unit                | 8.12       |

| Keyboard Assembly            | 8.13       |

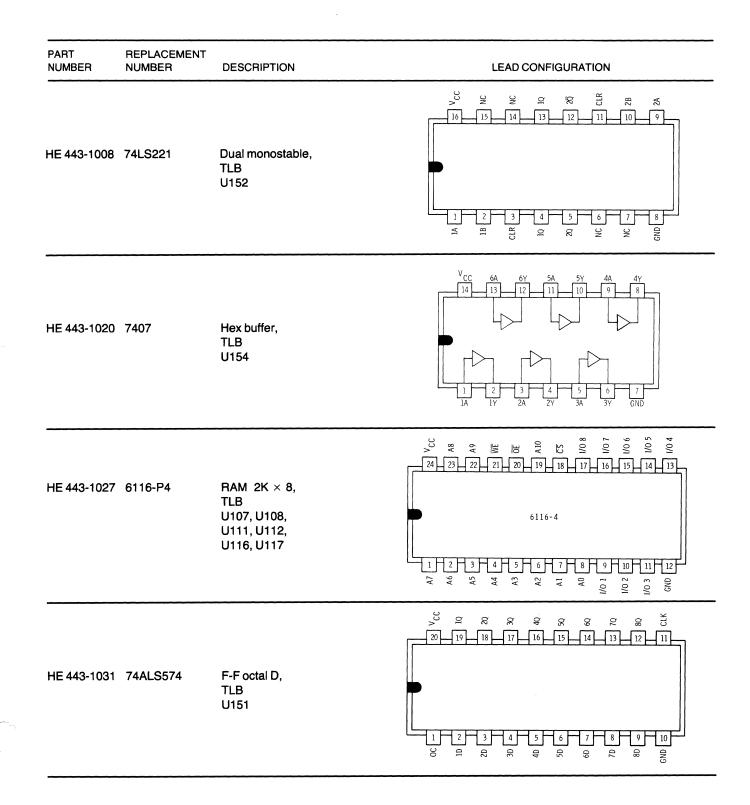

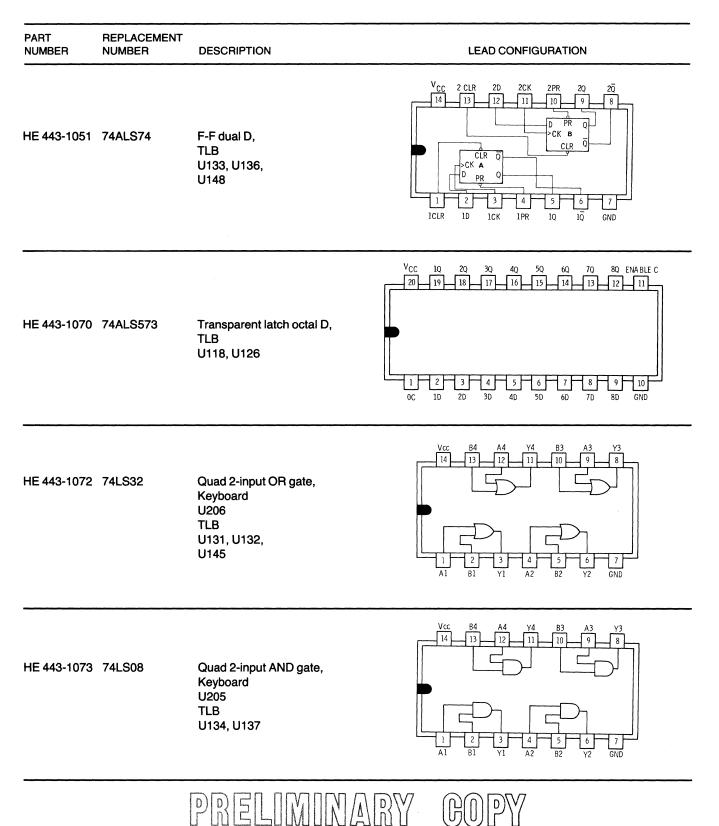

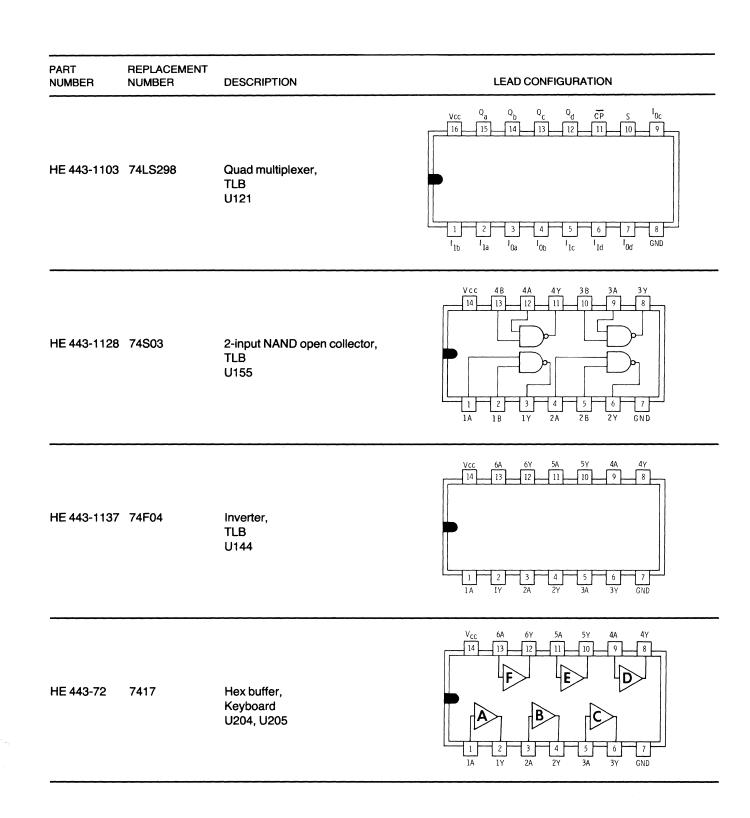

| Semiconductor Identification | 8.15       |

| PAL Equation                 | 8.27       |

#### Chapter 9

#### **Data Sheets**

| Introduction | 9.1 |

|--------------|-----|

| Appendix A       | Foreign | Keyboards |

|------------------|---------|-----------|

| United Kingdom   |         | A.1       |

| Danish/Norwegian |         | A.2       |

| French           |         | A.3       |

| German           |         | A.4       |

### Contents

| Italian                            |          | . A.5 |

|------------------------------------|----------|-------|

| Spanish                            |          | . A.6 |

| Śwedish                            |          |       |

|                                    |          |       |

| Appendix B Programming             | j Inform | ation |

| Zenith                             |          | . B.1 |

| Summary of Zenith Escape Sequences |          | . B.2 |

| Cursor Functions                   |          | . B.3 |

| Editing and Erasing                |          | . B.4 |

| Configuration                      |          | . B.5 |

| Modes of Operation                 |          | . B.6 |

| Additional Functions               |          | . B.7 |

| Print Functions                    |          | . B.8 |

| ANSI                               |          | B.10  |

| Summary of ANSI Escape Sequences   |          | B.11  |

| Cursor Functions                   |          | B.12  |

| Screen Functions                   |          | B.13  |

| Editing and Erasing                |          | B.14  |

| Configuration                      |          | B.15  |

| Modes of Operation                 |          | B.17  |

| Additional Functions               |          | B.19  |

| Print Functions                    |          | B.20  |

| Software Handshake                 |          | B.23  |

| Fill Character Requirements        |          | B.24  |

| •                                  |          |       |

#### Schematics

(and

Fold-ins

Z-49 Terminal Logic Board Schematic Z-49 Video Circuit Board Schematic Z-49 Keyboard Schematic

# Figures

| 1.1  | Rear Panel View                                     |

|------|-----------------------------------------------------|

| 1.2  | LED Indicators 1.4                                  |

| 1.3  | Tilt Adjustment                                     |

| 1.4  | Voltage Adjustment                                  |

| 2.1  | Alphabetic Keys 2.1                                 |

| 2.2  | Nonalphabetic Keys 2.2                              |

| 2.3  | Control Format Keys 2.3                             |

| 2.4  | Keypad Keys                                         |

| 2.5  | Special Purpose Keys 2.5                            |

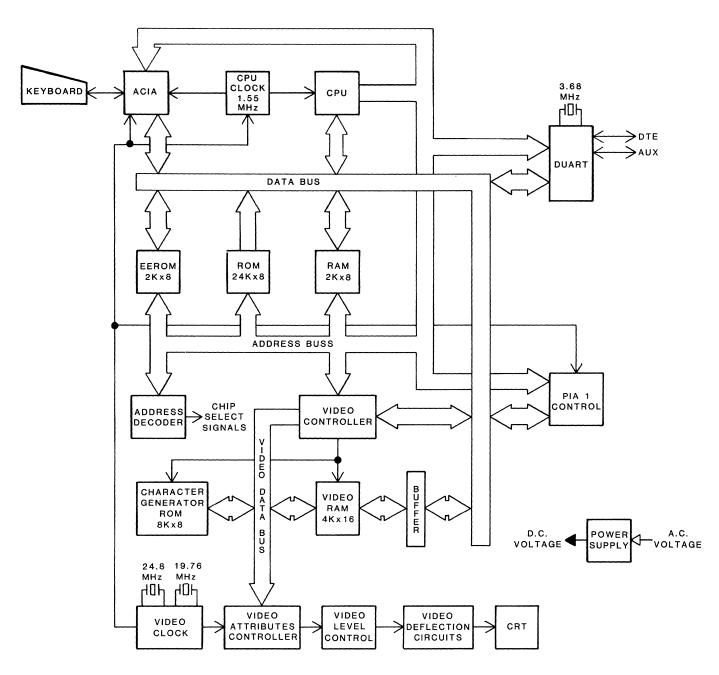

| 3.1  | Block Diagram                                       |

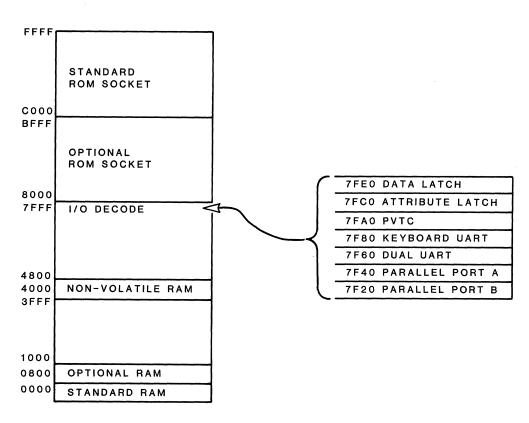

| 4.1  | Z-49 Memory Map                                     |

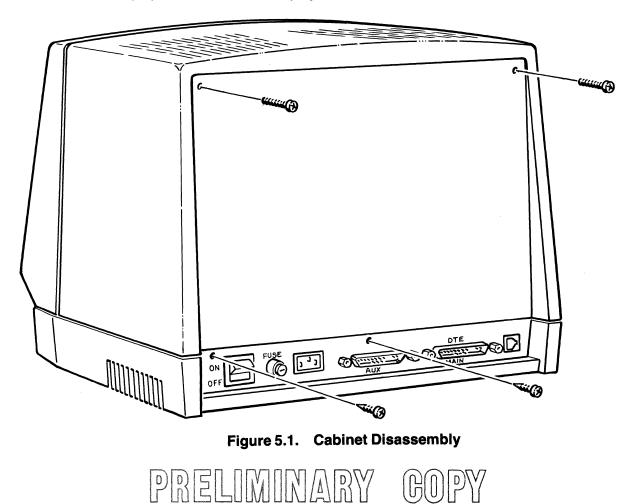

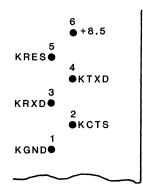

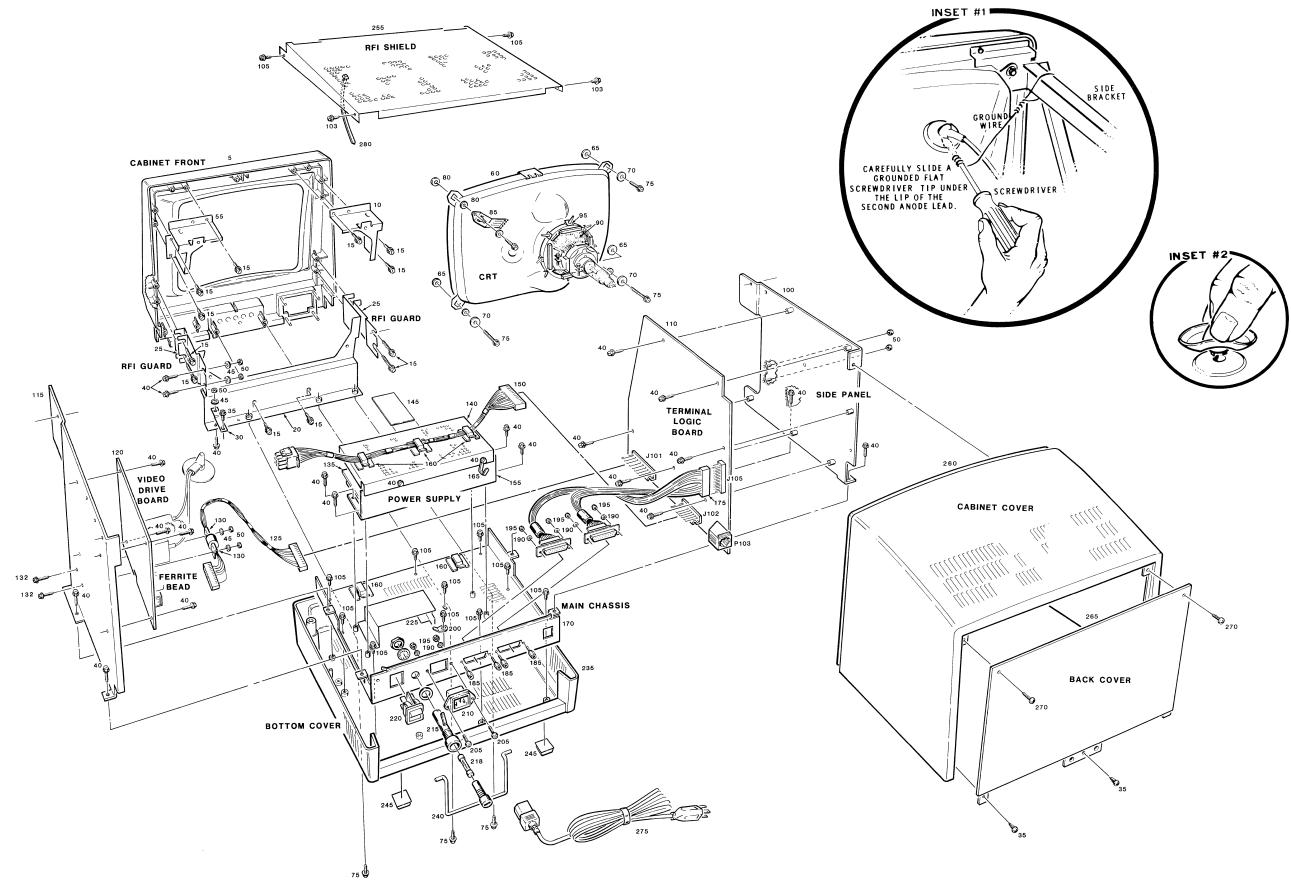

| 5.1  | Cabinet Disassembly                                 |

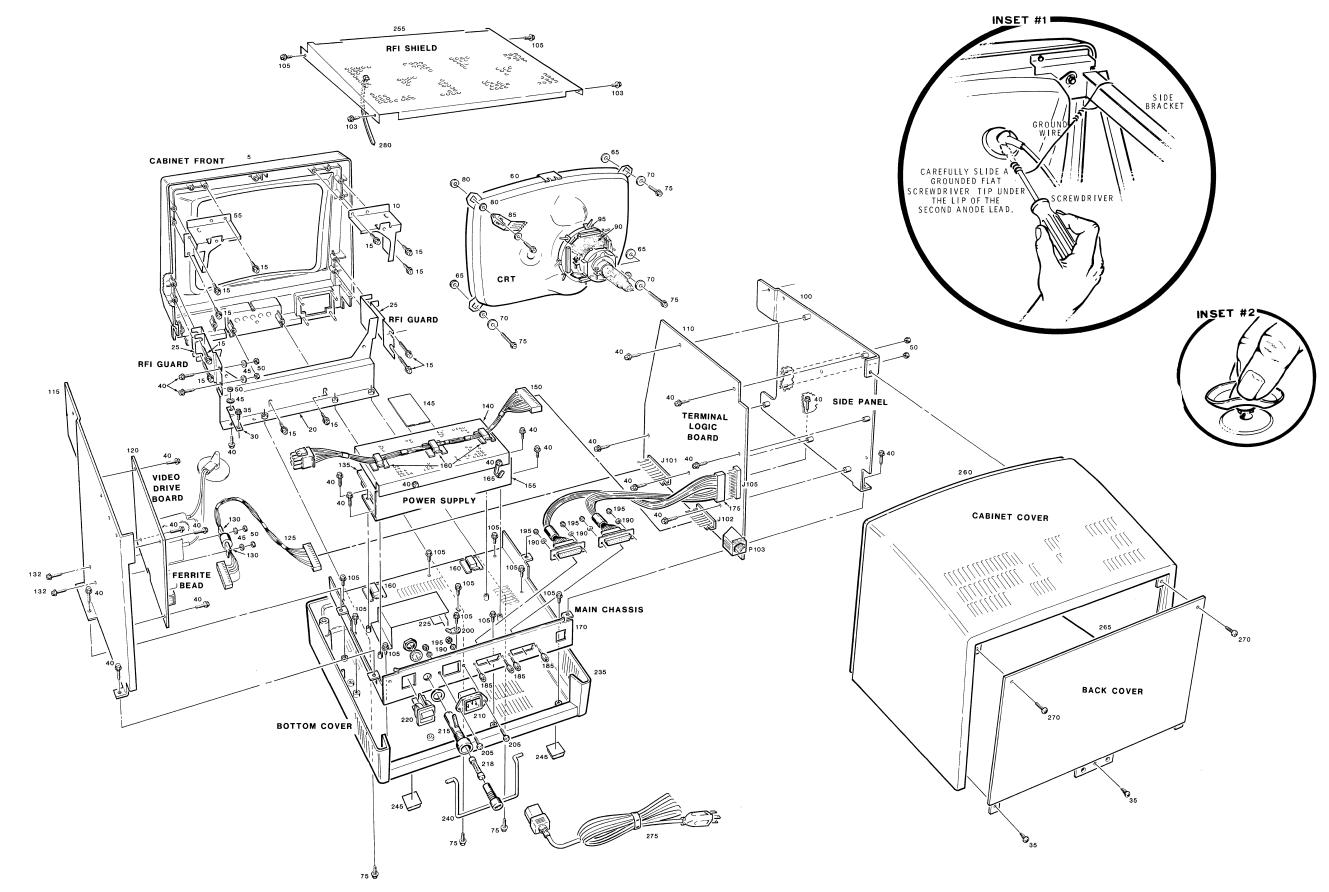

| 5.2  | Disassembly                                         |

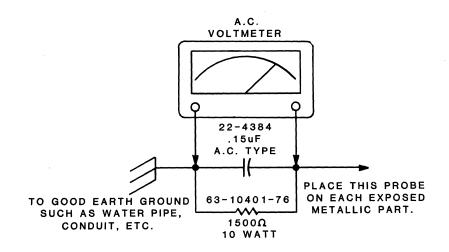

| 6.1  | AC Leakage Test 6.2                                 |

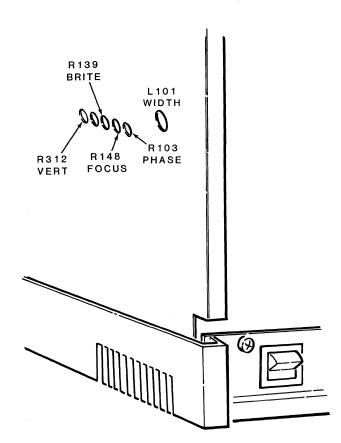

| 6.2  | Service Adjustments                                 |

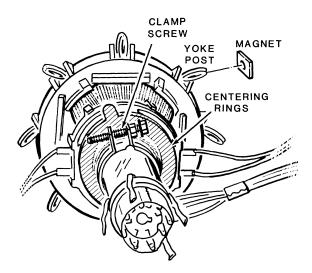

| 6.3  | Yoke Adjustment                                     |

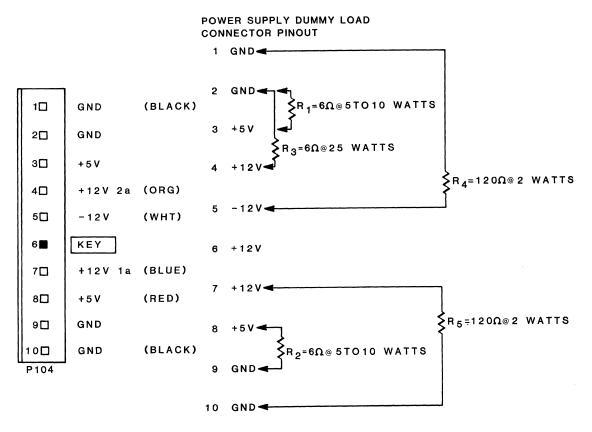

| 6.4  | Power Supply Testing                                |

| 6.5  | Video Interconnect                                  |

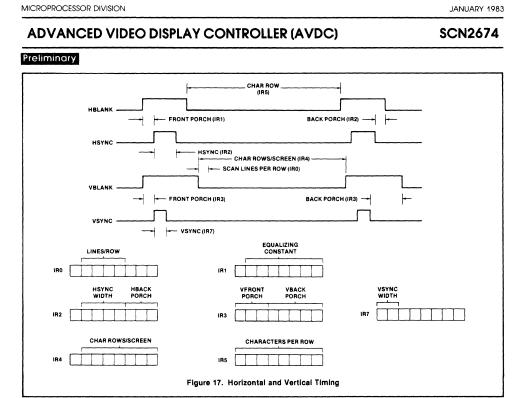

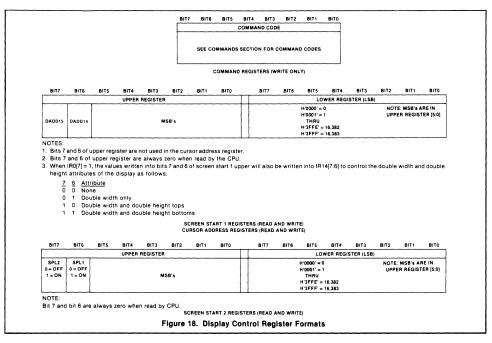

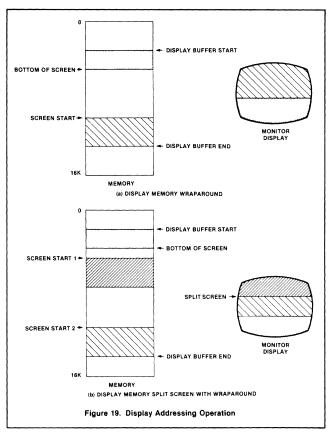

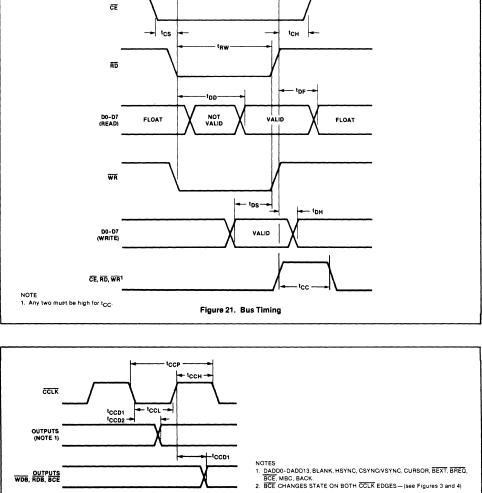

| 6.6  | 60Hz Refresh, 80 Characters Per Line                |

| 6.7  | 50Hz Refresh, 80 Characters Per Line                |

| 6.8  | 60Hz Refresh, 132 Characters Per Line               |

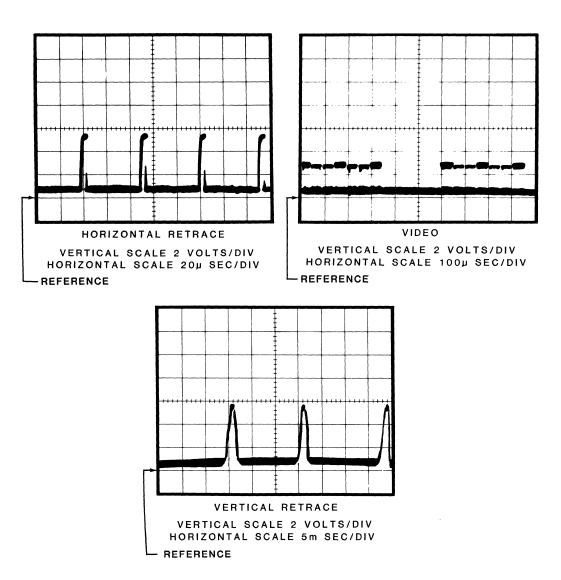

| 6.9  | 50Hz Refresh, 132 Characters Per Line               |

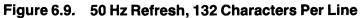

| 6.10 | Vertical Circuit Waveforms 6.19                     |

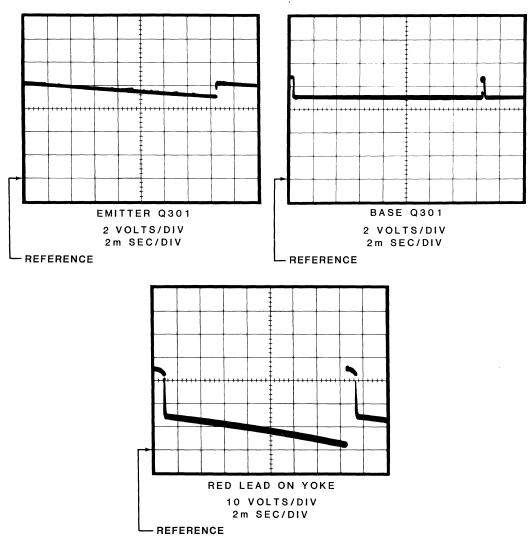

|      | Low Voltage Horizontal Circuit Waveforms            |

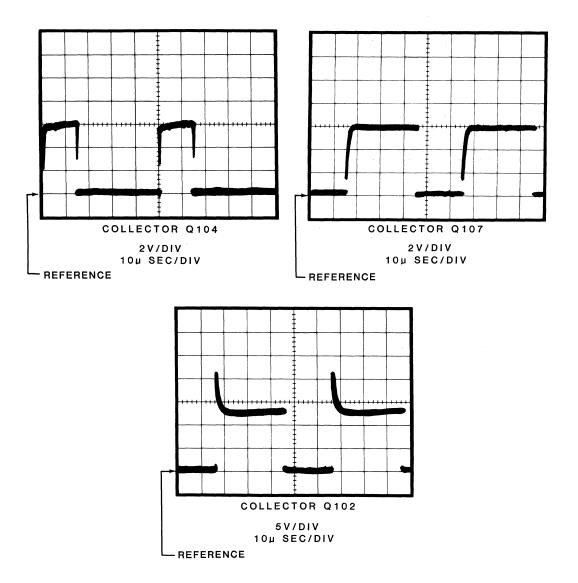

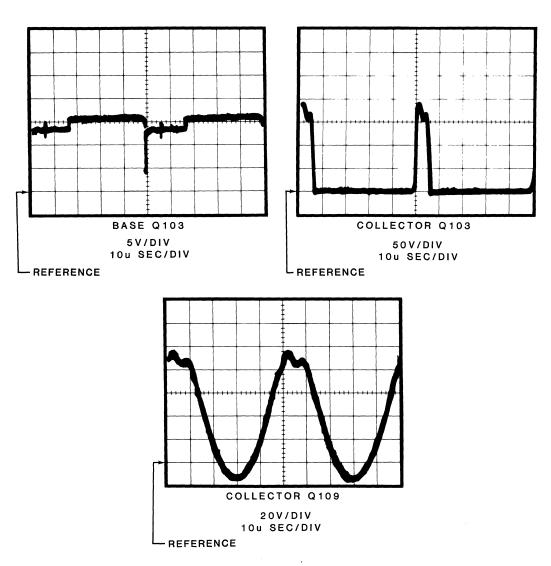

|      | High Voltage Horizontal Circuit Waveforms           |

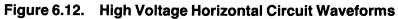

|      | Picture Tube Socket Pinout                          |

|      | Terminal Logic Board to Keyboard Pinout (P103) 6.23 |

| 7.1  | Reassembly                                          |

| 7.2  | Cabinet Reassembly                                  |

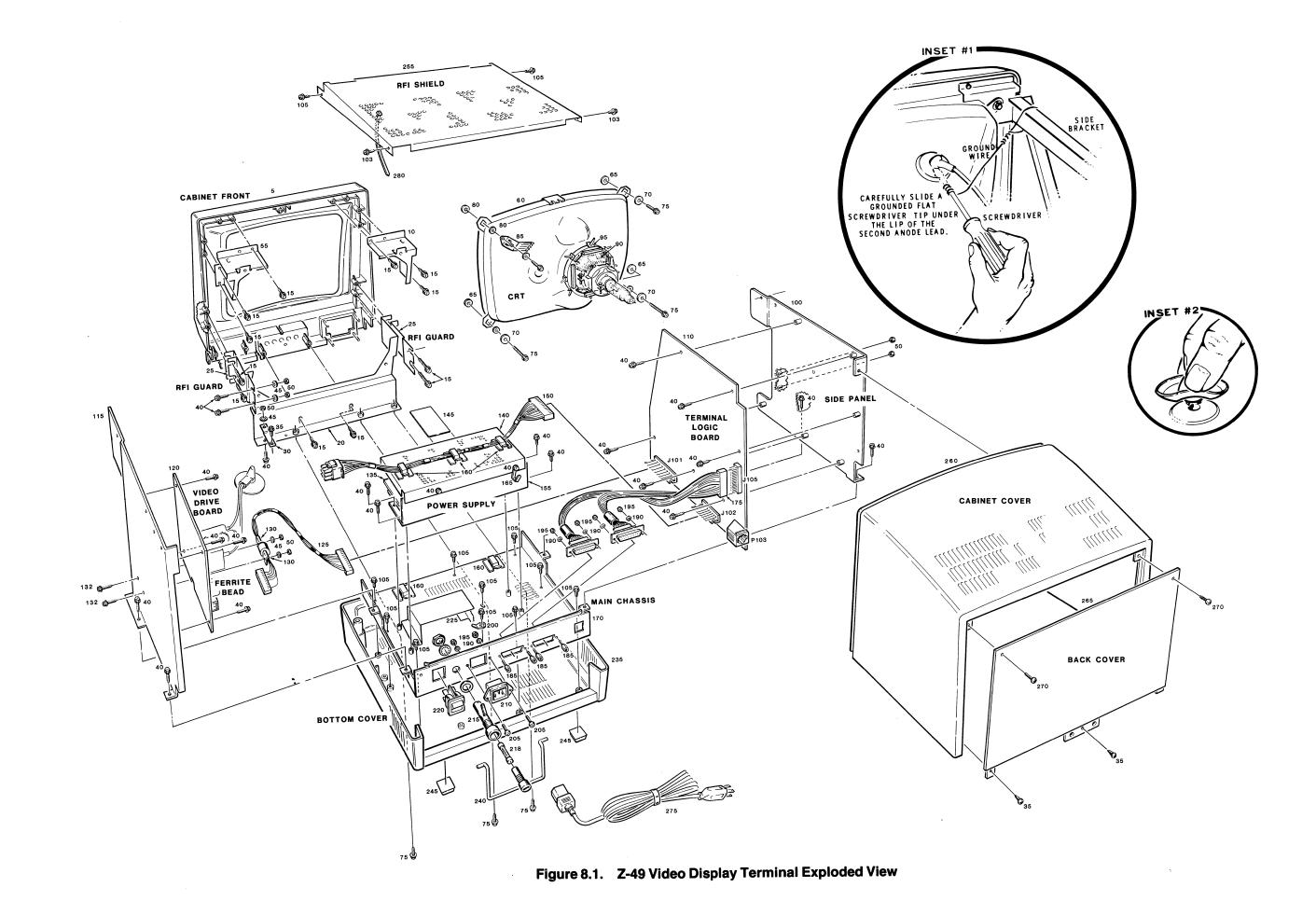

| 8.1  | Z-49 Video Display Terminal Exploded View           |

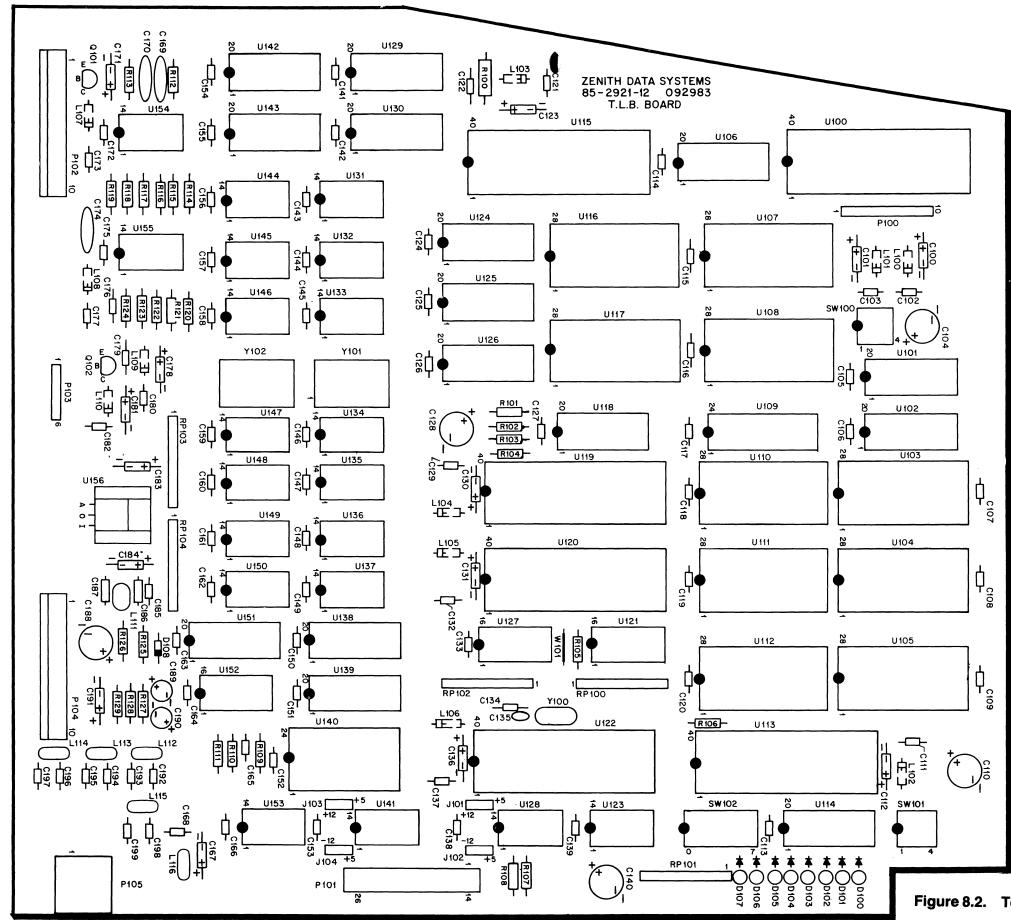

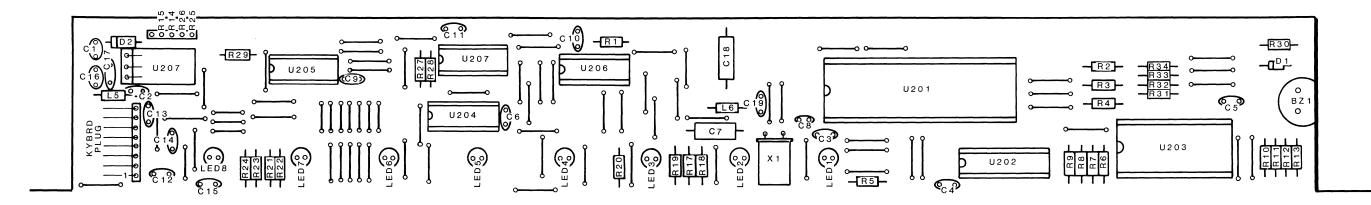

| 8.2  | Terminal Logic Board Component View                 |

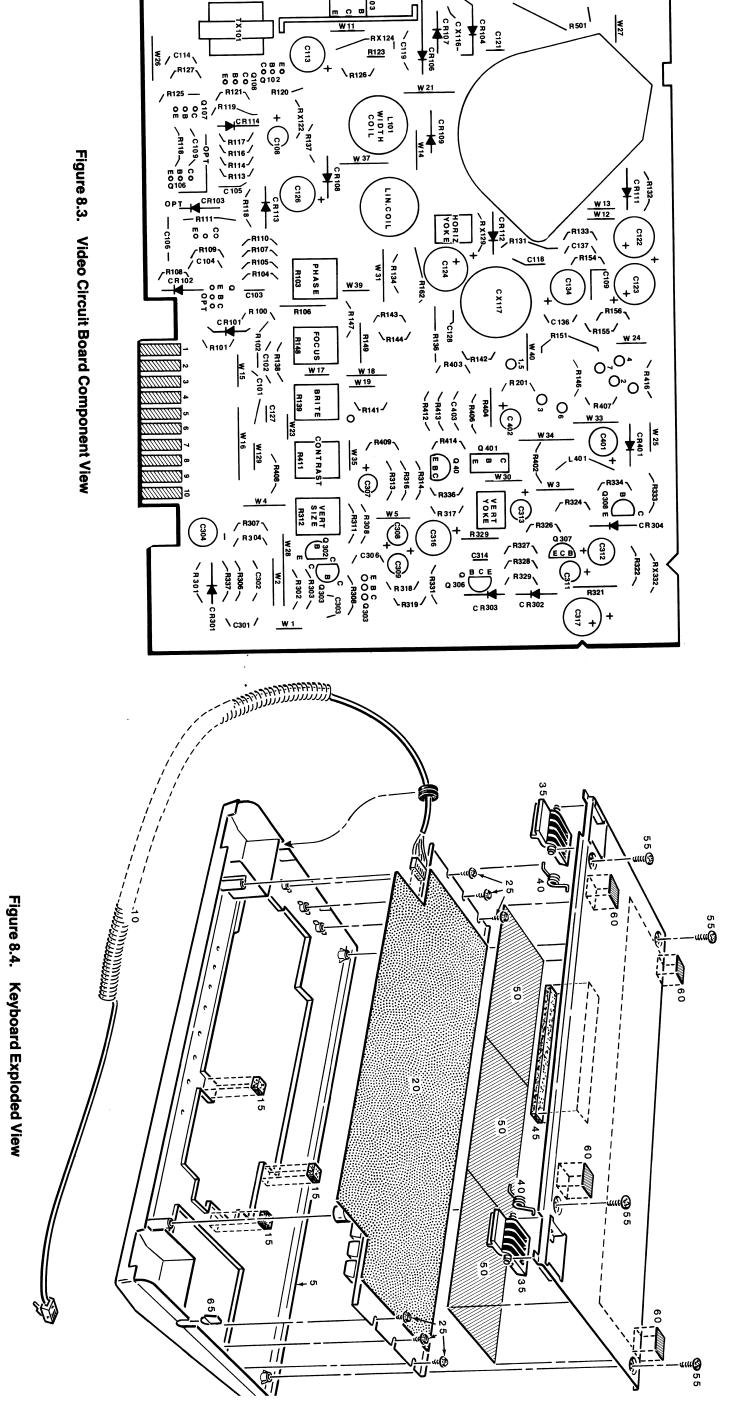

| 8.3  | Video Circuit Board Component View                  |

| 8.4  | Keyboard Exploded View                              |

| 8.5  | Keyboard Component View                             |

| B.1  | United Kingdom Keyboard A.1                         |

| B.2  | Danish/Norwegian Keyboard A.2                       |

| B.3  | French Keyboard A.3                                 |

| B.4  | German Keyboard A.4                                 |

| B.5  | Italian Keyboard A.5                                |

| B.6  | Spanish Keyboard A.6                                |

| B.7  | Swedish Keyboard A.7                                |

PRELIMINARY GOPY

## Tables

(prospers)

| 1.1         | Primary Serial Connector (DTE)       | 1.9          |

|-------------|--------------------------------------|--------------|

| 1.2         | Aux Connector (Printer Port) 1       | .10          |

| 1.3         | Self-Check Tests 1                   | .11          |

| 4.1         | DTE Signal Names                     | 4.5          |

| 6.1         | General Troubleshooting              | 6.9          |

| 6.2         | Terminal Logic Board Troubleshooting | j.12         |

| 6.3         | Video Driver Board Troubleshooting   | i.18         |

| 6.4         | Transistor Voltage Measurements      | 5. <b>22</b> |

| 6.5         | Picture Tube Voltage Measurements    | 5.22         |

| <b>B</b> .1 | Fill Character Requirements B        | 3.25         |

# Abbreviations

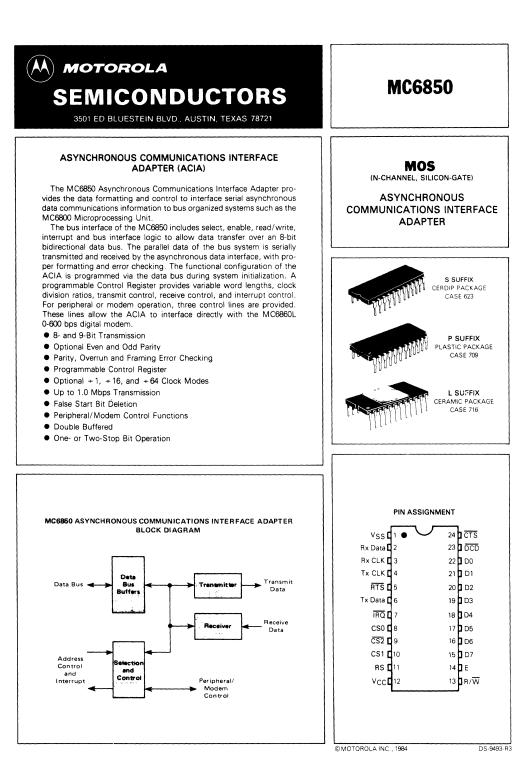

- ACIA Asynchronous Communication Interface Adapter

- ANSI American National Standards Institute

- AT Attribute

- ASCII American Standard Code for Information Interchange

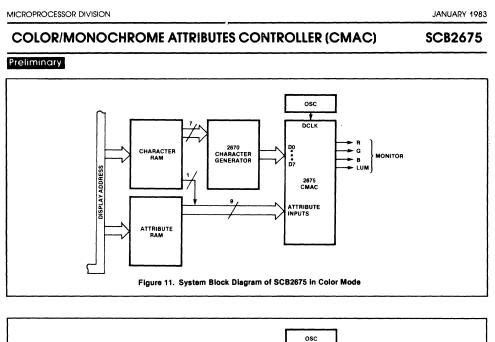

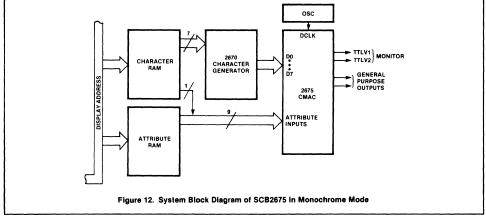

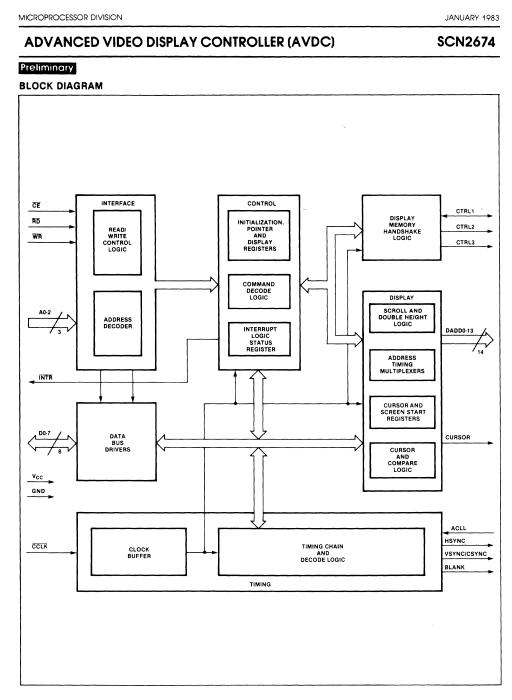

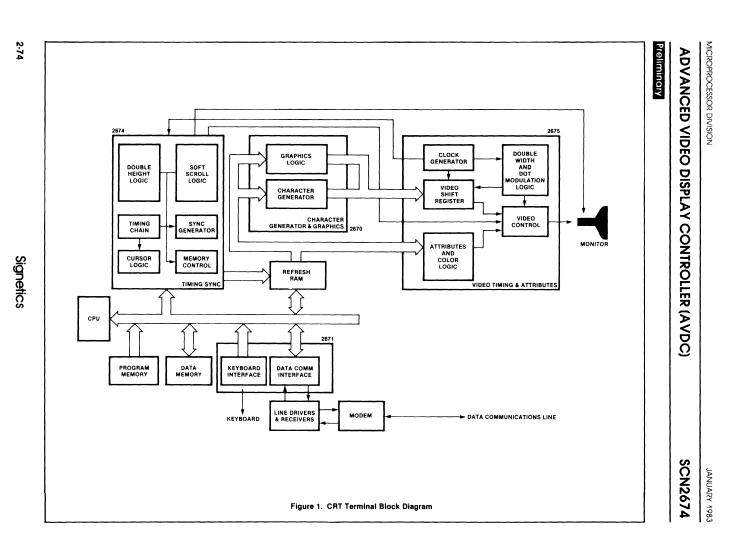

- AVDC Advanced Video Display Controller

- AUX Auxiliary

- CMAC Color/Monochrome Attributes Controller

- CRTC Cathode Ray Tube Controller

- CTS Clear to Send

- CPU Central Processing Unit

- CR Carriage Return

- CRT Cathode Ray Tube

- DIN German Industry Norm

- DOS Disk Operating System

- DSR Data Set Ready

- DTE Data Terminal Equipment

- DTR Data Terminal Ready

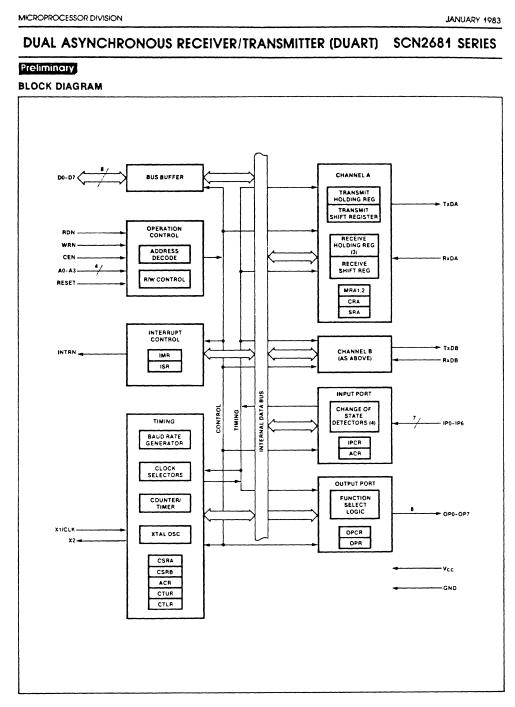

- DUART Dual Asynchronous Receiver/Transmitter

- EEROM Electrically Erasable Read Only Memory

- ESC Escape

- ESD Electrostatic Sensitive Device

- F-F Flip-Flop

- G0 User selected primary character set

- G1 User selected alternate character set

- IC Integrated Circuit

- LED Light-Emitting Diode

- LF Line Feed

- PAL Programmable Array Logic

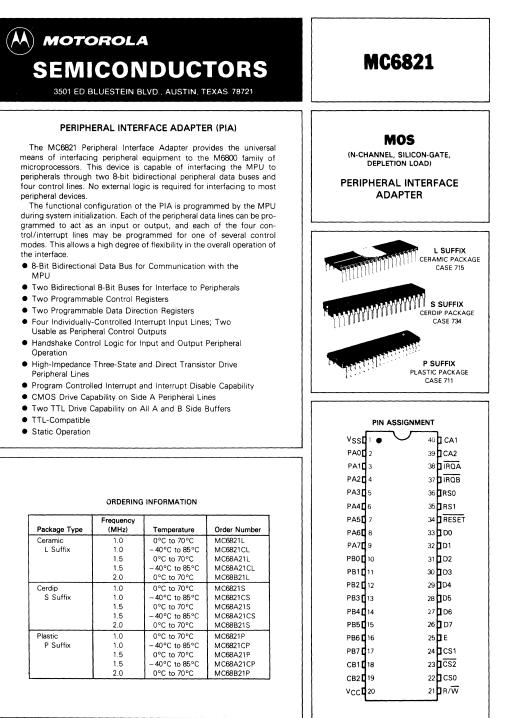

- PIA Peripheral Interface Adapter

- PVTC Programmable Video Timing Controller

- RAM Random Access Memory

- RMS Root Mean Squared

- ROM Read Only Memory

- RTS Ready to Send

- RXD Receive Data

- SCS Select Character Set

- TLB Terminal Logic Board

- TXD Transmit Data

- VDC Voltage Direct Current

- XOFF Transmit Off

- XON Transmit On

# **Specifications**

### Video Display

| CRT:                             | 14"(35.5cm) diagonal, enhanced contrast, non-<br>glare video screen.<br>Z-49 screen: Chromogold <sup>™</sup> screen (amber).<br>Z-49G screen: P31 green phosphor.                                                                                                                                                                                 |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Display Format:                  | 25 rows of 80 characters or<br>25 rows of 132 characters.                                                                                                                                                                                                                                                                                         |

| Display Size:                    | 6.75"(171mm) high $	imes$ 9.25"(235mm) wide.                                                                                                                                                                                                                                                                                                      |

| Character Type:                  | 10 $	imes$ 12 character cell for 80-column display.<br>8 $	imes$ 12 character cell for 132-column display.                                                                                                                                                                                                                                        |

| Character Size:<br>(approximate) | .255"(6mm) high $\times$ .12"(3mm) wide for 80-column display255"(6mm) high $\times$ .07"(1.8mm) wide for 132-column display.                                                                                                                                                                                                                     |

| Character Set:                   | <ul> <li>Normal: 128 characters; 95 printing ASCII, upper<br/>and lower case, numerics and punctuation,<br/>33 Zenith graphic characters.</li> <li>Alternate: 128 characters; 32 graphic representa-<br/>tion of non-printing ASCII 7 foreign character<br/>sets, 32 special Greek characters, and 32<br/>graphic characters (VT-100).</li> </ul> |

| Special Display<br>Features:     | Double-high double-wide characters per line,<br>Double-wide characters, smooth scroll, and<br>screen saver.                                                                                                                                                                                                                                       |

| Video Attributes:                | Normal or reverse character, normal or under-<br>lined character, variable intensity character and<br>background, normal or blinking display.                                                                                                                                                                                                     |

Chromogold is a trademark of Zenith Data Systems

### Specifications

| Refresh Rate:                 | 50 or 60 Hz.                                                                                                                                                                                                                     |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Status Line:                  | 25th line user programmable or indicates the ter-<br>minal's status of: ON or OFF Line, Insert Mode,<br>CAPS Locked, Printer Enabled.                                                                                            |

| Cursor                        |                                                                                                                                                                                                                                  |

| Туре:                         | Underline or reverse (solid) video block.                                                                                                                                                                                        |

| Attributes:                   | On, Off, or blinking.                                                                                                                                                                                                            |

| Addressing:                   | Direct or relative.                                                                                                                                                                                                              |

| Communications                |                                                                                                                                                                                                                                  |

| Туре:                         | EIA RS-232C                                                                                                                                                                                                                      |

| Baud Rates:                   | 50, 75, 110, 134.5, 150, 200, 300, 600, 1050, 1200, 1800, 2000, 2400, 4800, 7200, 9600, and 19200 baud. Different receive and transmit baud rates on the primary port, the same receive and transmit baud rates on the aux port. |

| Mode:                         | Half or full duplex on the primary port, full duplex on the aux port.                                                                                                                                                            |

| Code:                         | ASCII conforming to ANSI X3.4-1977.                                                                                                                                                                                              |

| Format:                       | Serial asynchronous.                                                                                                                                                                                                             |

| Word Length:                  | 7 data bits, 1 parity bit.                                                                                                                                                                                                       |

| Stop Bits:                    | 1 or 2.                                                                                                                                                                                                                          |

| Data Transmission<br>Control: | Hardware and software (Auto XON and XOFF).                                                                                                                                                                                       |

| Parity:                       | Even, odd, mark, space, or none.                                                                                                                                                                                                 |

### **Editing and Erasing Functions**

-

| Editing:           | Insert or delete character. Insert or delete line.                                                                                    |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Erasing:           | Erase page, erase line, erase to end of line, erase<br>to beginning of line, erase to beginning of page,<br>and erase to end of page. |

| Printer Functions  |                                                                                                                                       |

| Blind Mode:        | Turns print controller on and off (echo from DTE port).                                                                               |

| Auto Print:        | Prints a display line after the cursor is moved off<br>the line, using a form feed, line feed, vertical tab,<br>or wraparound.        |

| Print Cursor Line: | Prints displayed line with cursor.                                                                                                    |

| Print Screen:      | Prints the full screen or defined scrolling region.                                                                                   |

| Environment        |                                                                                                                                       |

| Operation:         | Temperature: 32 to 105 degrees Fahrenheit<br>(0 to 40 degrees Celsius).<br>Humidity: 10-90% (relative) noncondensing.                 |

| Storage:           | Temperature: - 40 to 150 degrees Fahrenheit<br>(- 40 to 66 degrees Celsius).<br>Humidity: 0-95% (relative) noncondensing.             |

| Power              |                                                                                                                                       |

| Voltage Range:     | 105-127 VAC or 210-254 VAC.                                                                                                           |

| Frequency:         | 50 or 60 Hz.                                                                                                                          |

### Specifications

| Fuse:        | Video Display: 3 Ampere, slow-blow for 120 VAC<br>operation;<br>1.5 Ampere, slow-blow for 240<br>VAC operation.                                                                                                                                                                 |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | Power Supply: 2 Ampere, 250 VAC.                                                                                                                                                                                                                                                |

| Consumption: | 73 Watts.                                                                                                                                                                                                                                                                       |

| Dimensions   |                                                                                                                                                                                                                                                                                 |

| Monitor:     | 13.625" high $\times$ 15.5" wide $\times$ 14.25" deep (34.6 cm $\times$ 39.4 cm $\times$ 36.2 cm).                                                                                                                                                                              |

| Weight:      | Monitor 22.8 pounds (10.37 kg).                                                                                                                                                                                                                                                 |

| Keyboard     |                                                                                                                                                                                                                                                                                 |

| Unit:        | 92-key, detached, low-profile, sculptured keys<br>keyboard unit conforming to European DIN er-<br>gonomic standards with a 6-foot(182 cm) coiled<br>cord.                                                                                                                       |

| Layout:      | Split: 74-key QWERTY layout with 5 programma-<br>ble special function keys, 8 indicators (LEDs), and<br>an 18-key keypad with 14 numeric and 4 special<br>programmable function keys.                                                                                           |

| Indicators:  | Visual: POWER ON, KEYBOARD LOCKED, OFF<br>LINE, CAPS LOCK, L1, L2, L3, and L4.<br>Audible: Power on; beep.<br>Print finished; beep.<br>Margin bell; beep.<br>Each key entry; click.<br>Brightness high and low limits; beep.<br>Save function; beep.<br>Restore function; beep. |

PRELIMINARY GOPY

| Cursor Controls: | Up, down, left, right, backspace, tab, back tab,<br>home, carriage return (CR), line feed (LF) and<br>brightness.       |

|------------------|-------------------------------------------------------------------------------------------------------------------------|

| Environment      |                                                                                                                         |

| Operation:       | Temperature: 32 to 105 degrees Fahrenheit<br>(0 to 40 degrees Celsius).<br>Humidity: 10-90% (relative) noncondensing.   |

| Storage:         | Temperature: -40 to 150 degrees Fahrenheit<br>(-40 to 66 degrees Celsius).<br>Humidity: 0-95% (relative) noncondensing. |

| Dimensions       |                                                                                                                         |

| Keyboard:        | 1.35" high $	imes$ 18.25" wide $	imes$ 8" deep (3.33 cm $	imes$ 46.33 cm $	imes$ 18.4 cm).                              |

| Weight:          | Keyboard 3.8 pounds (1.73 kg).                                                                                          |

# Introduction

The Zenith Data Systems Z-49 Terminal represents a truly state-of-the-art design capable of satisfying both business and personal needs. The many features include:

- Built-in power-up self check.

- Terminal emulation modes for both Zenith and ANSI (VT-100<sup>®</sup>/VT-102 compatible).

- Printing capabilities.

- Programmable character attributes and scrolling regions.

- Advanced keyboard features: automatic key repeat, status indicators, user defined function keys, and full cursor control keys.

- A height adjustable, detached, low-profile keyboard with sculptured keys and a six-foot coiled cable.

- All features are accessible through the keyboard, and a nonvolatile memory stores the settings.

- A professional 14-inch, non-glare screen with 24 rows of either 80 or 132 characters and a terminal 25th status line.

- Special attributes including double-high double-wide characters, double-wide characters, bold intensity, reverse video, blinking, underline capabilities and keyboard display brightness control.

- Character support for the following languages:

DANISH

FRENCH

GERMAN

VT-100 is a registered trademark of Digital Equipment Corporation

ITALIAN

NORWEGIAN

SPANISH

SWEDISH

UNITED KINGDOM

USA

SPECIAL GREEK CHARACTERS

The built-in flexibility and ease of operation make the terminal one of the most versatile units available today. The terminal can serve as a remote unit of a powerful and expandable business automation package.

#### The SMZ-49 Manual

This manual is divided into the following sections:

**Installation** — Describes the hardware and provides information for configuration, interfacing, and power on.

**Operation** — Describes the keys, functions, and modes of the terminal.

**Theory of Operation** — Briefly describes the hardware theory of operation of the terminal.

**Circuit Description** — Provides detailed description of hardware circuitry.

**Disassembly** — Provides disassembly sequence and instructions to board level.

**Service Procedures** — Provides information on cleaning, inspection, testing, and troubleshooting to board level.

Assembly — Provides reassembly instructions.

**Parts List** — Provides exploded views with part numbers, board component views, reference designator index to part numbers and semiconductor identification.

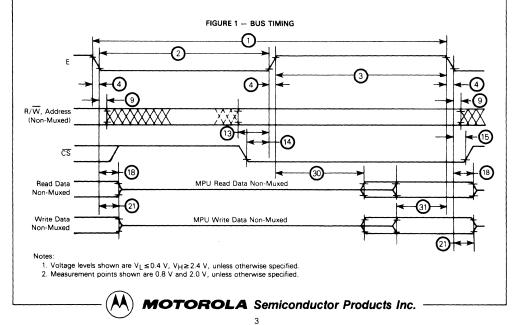

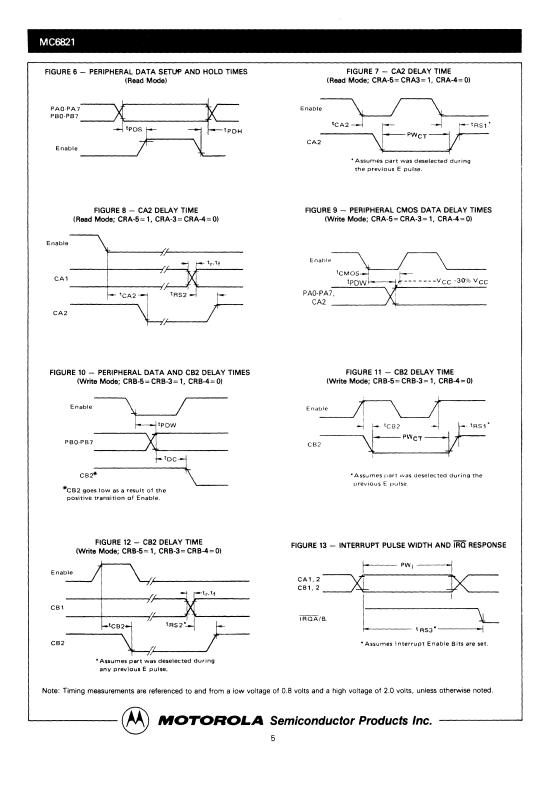

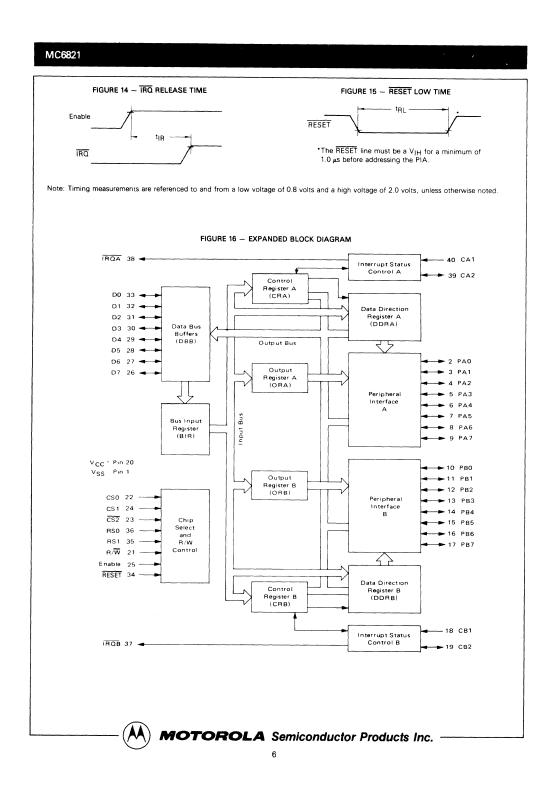

Data Sheets — Provides data for multifunctional integrated circuits.

**Schematics** — Provides a reference for circuit descriptions, testing, and troubleshooting.

Appendix A — Provides foreign keyboard information.

Appendix B — Provides escape sequence information.

#### **List of Tools**

1/4" nut driver

- 4" straight slot screwdriver

- 4" #1 Phillips screwdriver

- 4" #2 Phillips screwdriver

- 6" diagonal cutters

#### **Test Equipment**

The following is a list of recommended test equipment for this unit. Equivalent test equipment may be substituted.

- Oscilloscope DC to 100 MHz, dual trace, triggered sweep. Tektronics Model 465B.

- Logic Probe DC to 20 MHz. Capable of detecting 10 ns single pulses, and indicating logic one, logic zeroes, and high impedance states. Heath Model IT-7410.

- Digital Voltmeter High impedance input, zero to 1000 volts, zero to one megohm. Heath Model SM-2215.

#### Introduction

- Variable Power Supply Zero to 120 VAC RMS, 3 amperes. Heath Model IM-5210.

- Low Capacitance Oscilloscope Probe Input capacitance adjustable • from 15 pf to 50 pf, 4 ns rise time. Heath Model PKW-105.

- Video Monitor RGB color and monochrome composite wide band • monitor. Zenith Model ZVM-135.

- High Voltage Probe Zero to 40 kV. Heath Model IM5210. ۲

HE 421-6

### **List of Supplies**

| DESCRIPTION        | PART NUMBER |  |

|--------------------|-------------|--|

| Heat sink compound | 205-00303   |  |

| Cable ties         | HE 354-5    |  |

Cable ties Fuse 3AG slow blow

PRELIMINARY GO

# Chapter 1 Installation

### Introduction

The Zenith Data Systems terminal has two main components: a video display and a detached keyboard. The two are connected to each other with a 6-foot coiled cord. In addition to this documenation and the above components, a *Programmer's Quick Reference Guide* and an RS-232C cable are included.

**NOTE:** If you use a printer, you must use a null modem cable, part number HE 134-1454. Verify that the printer is configurable with the null modem cable.

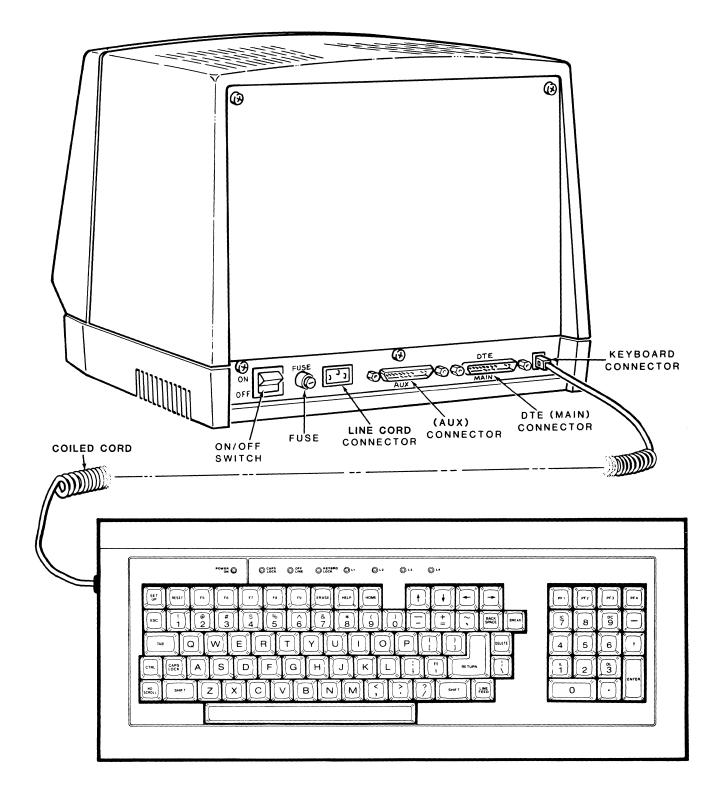

Refer to Figure 1.1 for a description of the plugs (connectors) on the video display and keyboard.

Installation

### **Video Display**

Refer to Figure 1.1.

The following is a rear view description of the video display. Be sure the video display power ON/OFF switch is in the OFF position and the line cord is unplugged from the AC power source. Turn the video display until the back is visible.

Power ON/OFF Switch — Turns the terminal ON or OFF.

WARNING: Be sure power is OFF when replacing the fuse.

FUSE — Provides circuit protection due to component failure and line voltage surges.

CAUTION: Replace only with a properly rated fuse.

Line Cord Connector — Connects power to the terminal.

Connector (AUX) — Connector for printer.

DTE Connector (MAIN) — Connector for computer or modem.

Keyboard Connector — Connector for keyboard cable.

### Keyboard

Refer to Figure 1.1.

The following is a description of the keyboard unit.

Keyboard cable --- Connects the keyboard to the video display.

Keyboard — The keyboard consists of 92 keys, a connector, eight visual indicators (LEDs), and is available in eight different languages.

Installation

Figure 1.1. Rear Panel View

Installation

### **Keyboard Indicators**

Refer to Figure 1.2.

POWER ON — lights when power is on and the keyboard is properly connected.

CAPS LOCK — Lights when the CAPS LOCK function is on.

OFF LINE — Lights when the terminal is off line with the host computer.

KEYBRD LOCK — Lights when the keyboard unit is locked or the terminal is printing. The keyboard must be enabled to operate.

L1 through L4 — Lights when instructed, by a user program.

Figure 1.2. LED Indicators

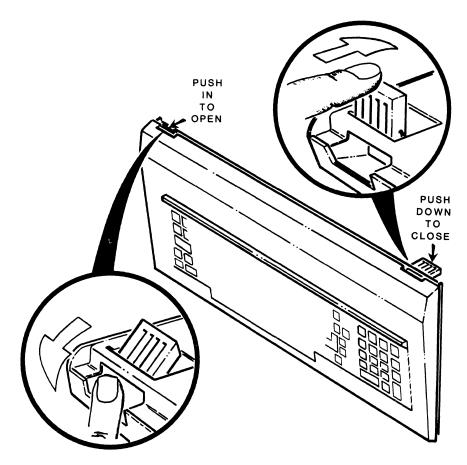

### **Keyboard Tilt Adjustment**

Refer to Figure 1.3.

You can raise the tilt of the keyboard by pressing the two tabs located in back of the unit.

Figure 1.3. Tilt Adjustment

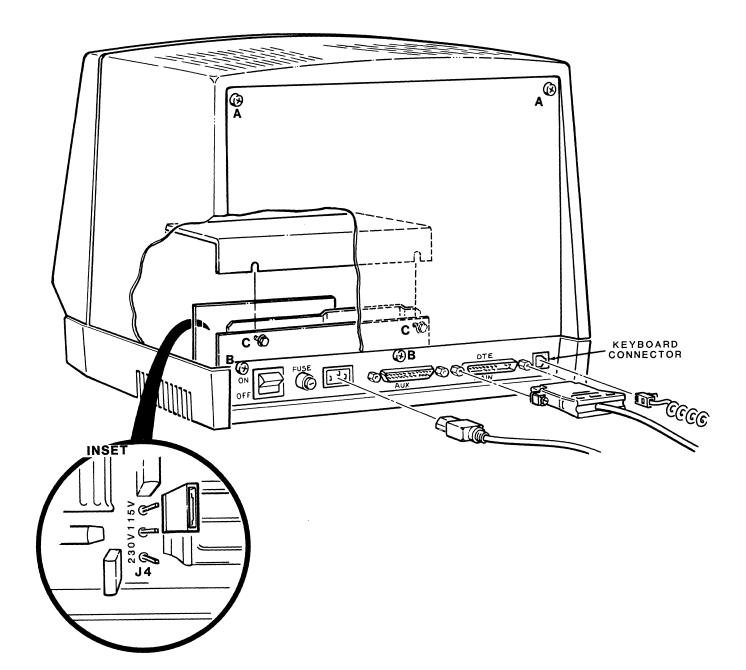

### **Voltage Selection**

Before connecting the terminal, make sure it is rated for the voltage available in your area. The terminal is wired for 120 VAC. To change the voltage rating to 240 VAC, refer to Figure 1.4 and perform the following six steps:

**WARNING:** This power supply contains lethal DC voltages. The line cord must be unplugged before proceeding with the following steps.

- 1. Place the terminal on a selected work surface so that the back is accessible.

- 2. Remove the two screws at point A and two screws at point B; then remove the back cover.

- 3. Remove two 6-32  $\times$  .375 screws (C) and the cover from the power supply.

- 4. Figure 1.4 (inset) depicts the jumper used to select either 115 VAC or 230 VAC operating voltage. Pull the jumper straight up and connect the jumper to the pins corresponding to the correct operating voltage.

- 5. Replace the power supply cover and the two screws that were removed in step 3.

- 6. Replace the back panel and the four screws that were removed in step 2.

### Connections

To install and connect the terminal, refer to Figure 1.4 and complete the following procedure:

- Place the video display on a solid work surface and turn it until the back is facing you.

- Locate the coiled keyboard cable. Connect it to the keyboard connector on the back of the video display.

**CAUTION:** The coiled cable assembly resembles a conventional telephone cord. DO NOT attempt to connect the end to a telephone plug or keyboard damage could result.

• Connect the line cord to the line cord connector.

### Interfacing

The terminal is designed to be used as an input/output (I/O) device for a computer system. The terminal may be connected directly or through telephone lines (via a modem) to any computer. The following discussion covers some of the considerations for proper installation with a computer.

**CAUTION:** A shielded cable must be used. A shielded cable is required for the terminal by FCC regulations.

### **DTE Device**

Refer to Figure 1.4.

On the back panel of the terminal, there are two standard connectors, marked AUX and DTE (MAIN). The DTE (MAIN) connects to the host computer or modem and AUX to the printer.

Table 1.1 provides information on the DTE connector, and Table 1.2 provides information on the AUX connector.

**NOTE:** The computer or modem used with the terminal must meet RS-232C standards or improper operation may result.

| PIN<br># | SIGNAL<br>NAME | INPUT/OUTPUT<br>I/O | SIGNAL<br>FUNCTION  |  |

|----------|----------------|---------------------|---------------------|--|

| 1        | GND            | _                   | Protective Ground   |  |

| 2        | TXD            | 0                   | Transmitted Data    |  |

| 3        | RXD            | 1                   | Received Data       |  |

| 4        | RTS            | 0                   | Request to Send     |  |

| 5        | CTS            | 1                   | Clear to Send       |  |

| 6        | DSR            | 1                   | Data Set Ready      |  |

| 7        | GND            | -                   | Signal Ground       |  |

| 8        | CD             | 1                   | Carrier Detect      |  |

| 11       | SS             | 0                   | Reserved            |  |

| 12       | SI             | 1                   | Reserved            |  |

| 20       | DTR            | 0                   | Data Terminal Ready |  |

| 22       | RI             | 1                   | Reseved             |  |

Table 1.1. Primary Serial Connector (DTE)

| PIN<br># | SIGNAL<br>NAME | INPUT/OUTPUT<br>I/O | SIGNAL<br>FUNCTION  |  |

|----------|----------------|---------------------|---------------------|--|

| 1        | GND            | _                   | Protective Ground   |  |

| 2        | TXD            | 0                   | Transmitted Data    |  |

| 3        | RXD            | 1                   | Received Data       |  |

| 6        | DSR            | I                   | Data Set Ready      |  |

| 7        | GND            | -                   | Signal Ground       |  |

| 20       | DTR            | 0                   | Data Terminal Ready |  |

#### Table 1.2. Aux Connector (Printer Port)

When connecting the terminal directly to a computer, connect the RS-232C cable into the DTE connector and the other end into the computer's DCE connector (refer to the computer hardware manual for the proper connector).

When connecting the terminal to a modem, connect the RS-232C cable into the DTE connector and the other end into the modem's (DCE) connector (refer to the modem hardware manual for the proper connector).

When you connect the terminal to a printer, you must use a null modem cable (HE 134-1454). Plug the printer cable into the AUX connector. The baud rate setting in AUX port parameters applies to both transmit and receive. Configure the terminal to the desired printer baud rate.

Make sure the power switch is OFF, then plug the power source into an AC outlet (wall plug).

Rotate the video display, so that the screen is facing you.

Press the power switch to ON.

### **Self-Check Tests**

As soon as you turn on the terminal, a series of internal self-check tests are performed to verify proper operation. If no faults are found, a beep will sound. If a problem is detected, an error message may be printed on the video display. Table 1.3 lists the tests performed and the corresponding error messages. Refer to Chapter 6, "Service Instructions," for further information and instructions.

Table 1.3. Self-Check Tests

| TEST                | ERROR MESSAGE  |

|---------------------|----------------|

| ROM                 | ROM Checksum   |

| RAM                 | RAM Fault      |

| CRT Controller      | CRTC Error     |

| Keyboard            | Keyboard       |

| Nonvolatile RAM     | NVRAM Checksum |

| CPU Interrupt       | CPUFIRQ ERROR  |

| Communications Port | DUART Error    |

### **POWER ON Indicator**

PRELIMINARY

When you turn the terminal ON, the POWER ON indicator (LED) should light. If the POWER ON indicator is not lit, either the keyboard is not connected to the terminal correctly or the terminal is not connected to an acceptable power source.

After 10 to 30 seconds a cursor should appear in the upper left corner of the screen. The 25th line also may display one or more messages: CAPS Lock, OFF Line, or ON Line.

# Chapter 2 Operation

### Introduction

The Z-49 Terminal uses the latest in solid-state technology for setting up and maintaining vital communication functions. You can enter these functions quickly and easily through the keyboard. This section covers the keyboard keys and setting up the features and functions of the terminal.

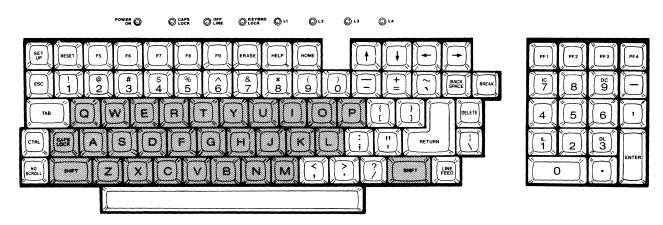

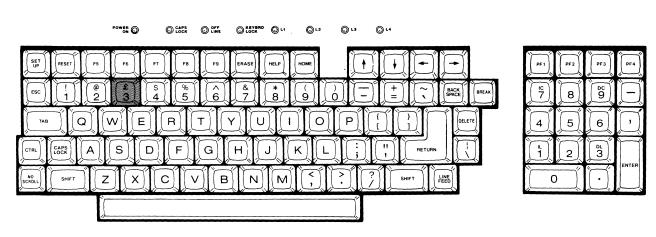

### **Alphabetic Keys**

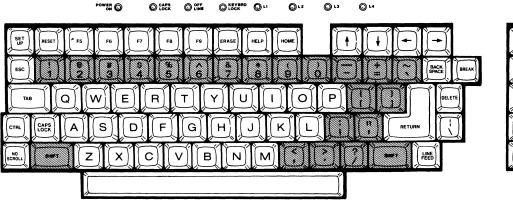

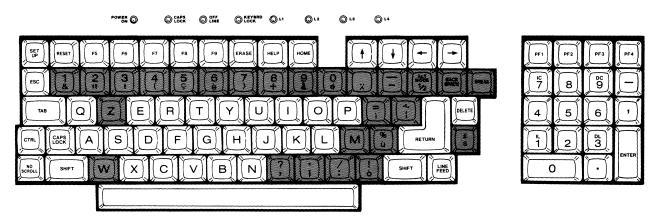

Refer to Figure 2.1.

The terminal's keyboard has the standard 26 letters of the alphabet arranged the same as a normal typewriter (QWERTY). The F and J keys are recessed to help determine the home row position. These keys will function in either upper or lower case. Press the SHIFT key or CAPS LOCK key to use upper case.

The CAPS LOCK key will light a keyboard indicator (CAPS LOCK) when enabled. If the status indicator line on the video display is on, a CAPS LOCK message will be displayed. The CAPS LOCK key affects only the alphabetic keys.

Figure 2.1. Alphabetic Keys

Page 2.2

Operation

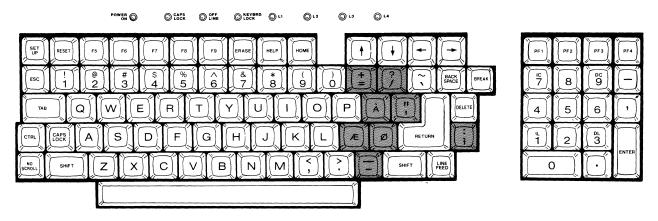

### **Nonalphabetic Keys**

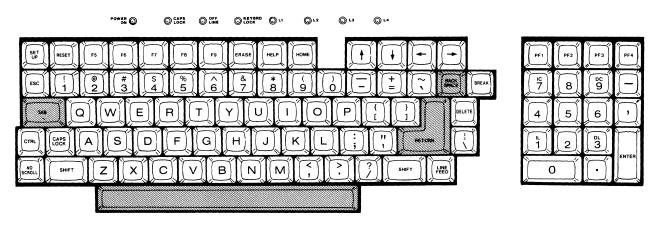

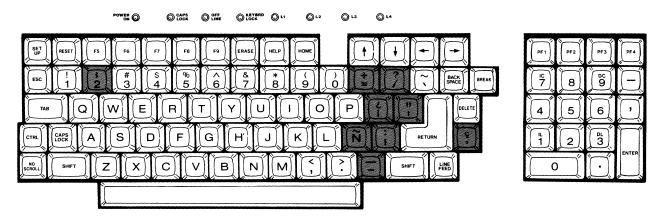

Refer to Figure 2.2.

Nonalphabetic keys include the numbers 0 through 9, punctuation marks, and special characters. The lower marking on each key is generated when the SHIFT keys are not held down. The upper marking will be generated when either SHIFT key is held down. The CAPS LOCK key will not shift these keys.

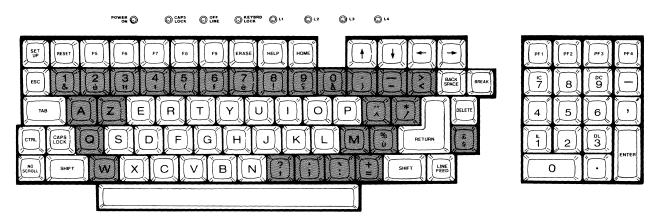

# **Control Format Keys**

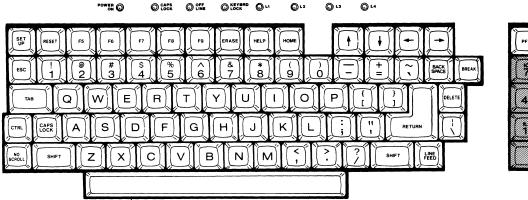

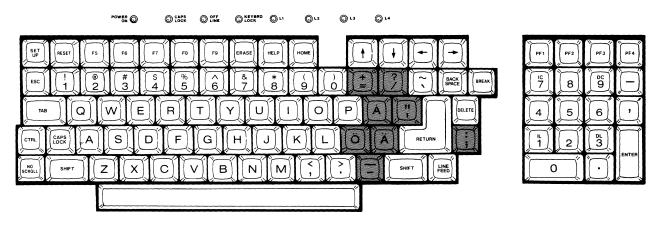

Refer to Figure 2.3.

**NOTE:** The following discussions describe the most common function for each key. However, software may direct any key to cause some other function to take place. Any key that has a special function is usually described in the documentation for that program.

**Space Bar** — Functions the same as a typewriter. A blank character can be entered by pressing the space bar.

**BACK SPACE** — Functions the same as a typewriter. Pressing the BACK SPACE key moves the cursor one space to the left.

**TAB** — Positions the cursor to the next tab column as set by software or in the Setup mode. If you press either SHIFT key and the TAB key simultaneously, the cursor will move to the previous tab column.

**RETURN** — Returns the cursor to the first character on the left side of the display, not necessarily advancing to the next line.

Figure 2.3. Control Format Keys

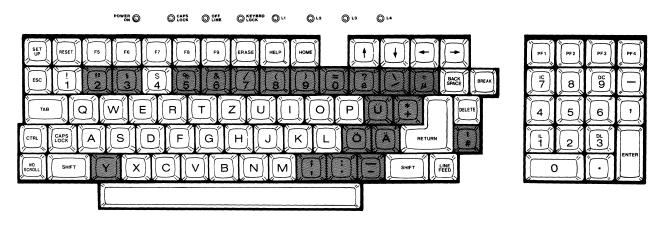

# **Keypad Keys**

Refer to Figure 2.4 for the following discussion of the keypad.

**Calculator Style Keypad** — The group of keys, located to the right of the main keyboard, is organized somewhat like a calculator and includes: numbers 0 through 9; a period for the entry of decimal points; a comma for data entry; a dash for the entry of negative numbers; and an ENTER key for signaling the computer that the entry has been completed.

The 5 key has a raised dimple to indicate the "home" position of the calculator keypad.

**Four Keys**: 1, 3, 7, and 9 are used for special insertion and deletion applications using the shifted mode. Key 1 (IL) is used to insert a line. Key 3 (DL) is used to delete a line. Key 7 (IC) is used to insert a character, and key 9 (DC) is used to delete a character.

Figure 2.4. Keypad Keys

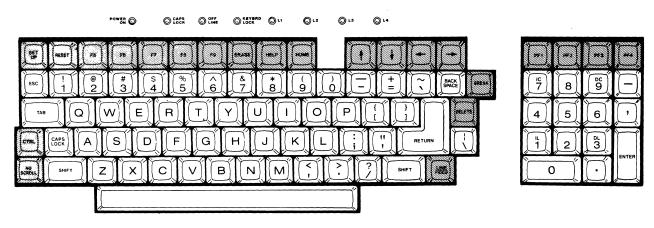

# **Special Purpose Keys**

Refer to Figure 2.5 for the following discussion of keyboard functions.

The following keys are used for special purposes and are nonrepeating. Instructions that tell you how to use them will appear with the software programs.

**PF1 through PF4 and F5 through F9** — Special function keys used for special purposes by software, or may be user-defined.

**RESET** — This key is used with the right-hand SHIFT key to "hardware reset" the terminal.

**ERASE** — This key erases the screen from the cursor to the bottom of the screen. The ERASE key and either SHIFT key are used to erase the entire screen.

**HELP** — Used by software programs to provide special "prompts" or "helps."

Figure 2.5. Special Purpose Keys

HOME,  $\uparrow$  (up arrow),  $\downarrow$  (down arrow),  $\leftarrow$  (left arrow),  $\rightarrow$  (right arrow) and LINE FEED are cursor control keys. These keys are used by some programs to control cursor movement and screen presentation.

**BREAK** — This key generates a 233.3 millisecond signal to interrupt (modem) communications. The BREAK key and either SHIFT key generate a 3.5 second signal for modem disconnect.

**DELETE** — Deletes one character to the left, or sometimes in software duplicates the BACK SPACE.

#### NO SCROLL -

Hold Screen enabled:

- Pressing the NO SCROLL key displays the next line of data.

- Pressing the NO SCROLL and either SHIFT key displays the next full page (24 lines).

Hold Screen disabled.

- Hardware and none-handshaking options disabled.

- Pressing the NO SCROLL key generates XON or XOFF commands.

**NOTE:** The following keys are used in a combination with other keys to perform a function.

**ESC** — The ESC (ESCAPE) key generates a control code for escape sequences.

EXAMPLE: ESCrA

In the above example, press and release the **ESC** key, press and release the lower case **r** key, and press and release the capital **A** key.

**CTRL** — Pressing the CTRL (CONTROL) key and another key at the same time performs a special function. Refer to Appendix B for more information.

Pressing the CTRL and ENTER will enter and exit auto print. Exiting or entering the Setup mode will terminate current printing.

PRELIMINARY GO

The CTRL and BREAK keys pressed at the same time generate a programmed answer-back message.

**SHIFT** — Pressing the SHIFT and ENTER keys will transmit the entire contents of the screen to the printer. Entering the Setup mode will terminate printing.

**SET UP** — Used to enter or exit the Setup mode. When printing, entering the Setup mode will terminate printing.

The terminal's functions are programmed in the Setup mode. To enter the Setup mode, press the **SET UP** key. The terminal will display the Main menu and be "off line".

**NOTE:** The terminal cannot communicate with the host computer until you exit the Main menu. The SET UP key sends an XOFF when entered and an XON when exited.

**NOTE:** Many of the setup procedures can be programmed by using software escape sequences. For more information about escape sequences, see Appendix B.

Brightness is controlled by pressing the **SET UP** key and then pressing either the up arrow ( $\uparrow$ ) key to increase contrast or the down arrow ( $\downarrow$ ) key to decrease contrast. A beep will sound whenever the high and low limits of brightness are reached.

The Main menu is shown in reverse, bold, and normal video on the bottom four lines of the screen (lines 22 through 25).

The selections displayed are: ON or OFF line, Primary port, Aux port, Display, Cursor, Keyboard, Set tabs, Monitor ON or OFF, Mode ANSI or ZENITH, Misc, Restore, Save, and Programmable keys.

Each function selected will display its status (current value). You may temporarily change or store the current value as explained in this section.

The cursor keys and auto repeat will be inoperative when you are in the Main menu, except for selected keys at selected times.

PRELIMINANY

# **Entering the Setup Mode**

To enter the Main menu, press the **SET UP** key. The bottom four lines will indicate a display similar to this Main menu.

A ON lineD DisplayG Set tabsJ MiscPF1PF4F7B Primary portE CursorH Monitor ONR RestorePF2F5F8C Aux portF KeyboardI Mode ANSIS SavePF3F6F9MAINMENU(Press SETUP to exit)Programmable keysF0

# **Main Menu Selection**

To select a function or feature, press the corresponding key.

Each function or feature is associated with an alphabetical key. You can temporarily change the current value of the function by pressing the alphabetical key as many times as necessary until you obtain the desired configuration, and then exiting the Main menu, or a new submenu (feature) can be displayed by pressing the appropriate alphabetical key. To exit the Main menu, press the **SET UP** key.

To store a new current value, press the **CTRL** key and the **S** (SAVE) key while in the Main menu. The screen will display the message saving and a beep will sound. When saving disappears, a beep sounds, the screen will display the Main menu, and the new current value will be stored. To exit the Main menu, press the **SET UP** key.

**NOTE:** Entering and exiting the Setup mode will cancel the current print option without a termination character. When printing is resumed, the printer will start printing from the previous postion unless a termination character is sent.

## **ON/OFF Line**

The terminal is an input/output device for a computer whenever it is on-line.

When the terminal is off-line, it is controlled only through the keyboard, and no information can be received from or transmitted to the host computer.

When the OFF Line mode is selected, OFF LINE will be displayed on the terminal status line of the screen and the OFF LINE indicator will be lit. When the terminal is ON Line, the OFF LINE indicator will not be lit and the status line will display ON LINE.

You can change ON/OFF Line from the Main menu by pressing the A key. The ON/OFF Line selection will be effective upon exiting the Main menu.

## **Primary Port Parameters**

To change the Primary port parameters in the Main menu, press the **B** key. The bottom four lines will indicate a display similar to:

A Rcv baud 9600

D Handshake SOFTWARE

G Stop bits 1

B Xmt baud 9600

E RTS/CTS busy LOW

H Parity EVEN

C Duplex

FULL

F DTR/DSR busy LOW

PRIMARY PORT PARAMETERS

(Press SET UP to return to main menu)

#### **Baud Rate**

The terminal can use a variety of baud rates to communicate with the host computer. These rates are: 50, 75, 110, 134.5, 150, 200, 300, 600, 1050, 1200, 1800, 2000, 2400, 4800, 7200, 9600, and 19200 baud. The display shows a current value of 9600 baud.

The primary port can receive and transmit data at different baud rates.

• The receive baud rate can be changed by pressing the A key.

- The transmit baud rate can be changed by pressing the B key.

- Pressing the up arrow ( ↑ ) key increases both the receive and transmit baud rates.

- Pressing the down arrow (  $\downarrow$  ) key decreases both baud rates.

Press the desired key(s) as many times as necessary until the desired baud rate(s) is displayed. The new baud rate will become effective when you exit the Main menu.

## **Duplex Mode**

The terminal can communicate with the host computer in either the FULL or HALF Duplex mode.

- FULL duplex is simultaneous communication between the terminal and the host which displays the data returned from the computer.

- HALF duplex is one-way communication between the terminal and the computer, but not at the same time. The terminal will display the data from the keyboard.

You can change the Duplex mode between FULL and HALF Duplex by pressing the C key. The new Duplex mode will become effective when exiting the Main menu.

#### Handshaking

The terminal uses four methods of handshaking: Software, Hardware, Both, or None.

In the Software handshake mode, the terminal will automatically generate the XON or XOFF codes.

Hardware handshaking is performed through the use of four control lines via the DTE (MAIN) connector. The four lines are: CTS (Clear to Send), RTS (Request to Send), DSR (Data Set Ready), and DTR (Data Terminal Ready).

Both handshaking is a combination of hardware and software handshaking.

The None option disables handshaking between the terminal and host computer.

You can change the Handshaking mode by pressing the D key until the desired mode is displayed. The new Handshaking will become effective when exiting the Main menu.

#### **RTS/CTS Busy**

The RTS/CTS function uses two methods of communication.

- Hardware handshaking must be enabled.

- RTS (Request to Send) is a signal from the terminal to the host computer.

- CTS (Clear to Send) is a signal from the host computer to the terminal (ignored).

The two signals are RTS/CTS busy LOW, and RTS/CTS busy HIGH. Normal RS-232 operation is RTS/CTS busy LOW.

If you change the above functions, the terminal can respond to either busy LOW or busy HIGH signals.

You can change this function by pressing the E key until the desired method of communication is displayed. RTS/CTS busy will become effective when exiting the Main menu.

## DTR/DSR Busy

The DTR/DSR function uses two methods of communication.

- Hardware handshaking must be enabled.

- DTR (Data Terminal Ready) is a signal from the terminal to the host computer.

- DSR (Data Set Ready) is a signal from the host computer to the terminal (ignored).

The two signals are DTR/DSR busy LOW, and DTR/DSR busy HIGH. Normal operation per RS-232 is DTR/DSR busy LOW.

If you change the above functions, the terminal can respond to either busy LOW or busy HIGH signals.

You can change this function by pressing the F key until the desired method of communication is displayed. The new DTR/DSR busy will become effective when exiting the Main menu.

#### **Stop Bits**

The terminal operating in the Zenith or ANSI modes uses one stop bit at all baud rates. When operating at 110 baud, some systems require two stop bits.

You can change stop bits by pressing the G key until the desired Stop bit option is displayed. The new Stop bits will become effective when exiting the Main menu.

## Parity

The available parity options are: ODD, EVEN, MARK, SPACE, and NONE. MARK and SPACE are used in modem communications. The data word with and without parity is outlined as below.

- Seven bits with parity; parity being EVEN, ODD, MARK, or SPACE. The eighth bit will be set according to the parity selected.

- Seven bits with no parity; the eighth bit will be forced to zero (no parity checking will be performed).

You can change the parity option by pressing the H key until the desired option is displayed. Parity will become effective when exiting the Main menu.

**NOTE:** The terminal has parity sensing capabilities. If the data received is the wrong polarity, the VT-100 graphic character for 61 HEX is displayed.

## **Aux Port Parameters**

To change the Aux port parameters, in the Main menu press the **C** key. The bottom four lines will indicate a display similar to:

A R/T baud 9600D Handshake SOFTWAREG Stop bits 1B Auto Print OFFE End With Form Feed OFF H ParityEVENC Blind Print OFFF DTR/DSR Busy LOWI ExtentENTIRE SCREENAUX PORT PARAMETERS(Press SETUP to return to main menu)

#### **Baud Rate**

The terminal can use a variety of baud rates to communicate with the printer. These rates are: 50, 75, 110, 134.5, 150, 200, 300, 600, 1050, 1200, 1800, 2000, 2400, 4800, 7200, 9600, and 19200 baud. The display shows a current value of 9600 baud.

The receive and transmit baud rates can only be increased or decreased at the same time.

- You can increase the receive and transmit baud rates by pressing the A key or up arrow (↑).

- You can decrease the receive and transmit baud rates by pressing the down arrow (↓).

Press the desired key(s) as many times as necessary until the desired baud rate is displayed.

The new baud rates will become effective when exiting the Main menu.

#### Auto Print

Auto print prints a display line after the cursor moves to the next line via a line termination character (LF, CR, or VT).

- Prints during WRAP with a line termination character of CR or LF.

- Double-high/double-wide lines are converted to single-wide lines when printed.

- Double-wide characters are converted to single-wide characters followed by a space when printed.

- Exiting the Setup mode will terminate printing of the current line only.

- After Restore, the Auto print status remains until any type of reset is initiated.

- The terminal will automatically generate the proper GO character set to the printer.

The Auto print mode can be turned on or off by pressing the B key.

#### **Blind Print**

Blind print enables the print controller. The terminal transmits received characters to the printer without displaying them.

- The terminal does not insert or delete spaces, provide line delimiters, or select character sets.

- Blind print has a higher priority than Auto print.

- During this operation, a print page can be initiated from the keyboard by pressing the SHIFT and ENTER keys simultaneously.

- A beep will sound after the print page is printed.

- Exiting the Setup mode will terminate printing.

- The terminal will automatically change the character set and then reset the character set to the original value, if the print page is initiated.

- After Restore, the Blind print status remains until any type of reset is initiated.

The Blind print mode can be turned ON or OFF by pressing the C key.

#### Handshaking

The two methods of handshaking are Software or Both.

In the Software handshake mode, the terminal will look for the XON or XOFF codes from the printer.

- The XOFF code tells the terminal that data transmission to the printer should cease.

- The XON code tells the terminal that data transmission to the printer can be resumed.

Both handshaking is a combination of hardware and software handshaking.

NOTE: Software handshaking always is on.

Hardware handshaking is performed through the use of two control lines via the AUX connector.

The two lines are: DSR (Data Set Ready) and DTR (Data Terminal Ready).

You can change the Handshaking mode by pressing the D key until the desired mode is displayed. The new Handshaking mode will become effective when you exit the Main menu.

#### **End With Form Feed**

Screen print always ends with a line feed; also, it can end with a form feed. This option can be set to ON by pressing the E key.

#### **DTR/DSR Busy**

The DTR/DSR function uses two methods of communication.

- Both handshaking must be enabled.

- DTR (Data Terminal Ready) is a signal from the terminal to the printer.

- DSR (Data Set Ready) is a signal from the printer to the terminal.

The two signals are DTR/DSR busy LOW and DTR/DSR busy HIGH. Normal operation per RS-232 is DTR/DSR busy LOW.

You can change this feature by pressing the F key until the desired method of communication is displayed.

## **Stop Bits**

The terminal operating in the Zenith or ANSI modes uses one Stop bit at all baud rates. When operating at 110 baud some systems require two stop bits.

You can change Stop bits by pressing the G key until the desired Stop bit option is displayed. The new Stop bits will become effective when you exit the Main menu.

## Parity

The available parity options are: ODD, EVEN, MARK, SPACE, and NONE. MARK and SPACE are used in modem communications. The data word with and without parity is outlined as below.

- Seven bits with parity; parity being EVEN, ODD, MARK, or SPACE. The eighth bit will be set according to the parity selected.

- Seven bits with no parity; the eighth bit will be forced to zero (no parity checking will be performed).

You can change the parity option by pressing the H key until the desired option is displayed. Parity will become effective when you exit the Main menu.

#### Extent

Extent is an option between printing the entire screen or the defined scrolling region.

The desired option can be selected by pressing the I key.

## **Display Parameters**

To change Display parameters, in the Main menu press the **D** key. The bottom four lines will indicate a display similar to:

A WrapOFFD Screen saverOFFG ScrollJUMPB Auto LF on CR OFFE Status LineONH Hold ScreenOFFC Auto CR on LFOFFF Columns80DISPLAY PARAMETERS(Press SETUP to return to main menu)

#### Wrap

The Wrap (wraparound) is a feature that allows you to continue to enter data after reaching the end of a line, without a loss, by generating a CR or LF.

- Depending on the terminal's configuration, a line may be 80 or 132 characters.

- When Wrap is on, the next character you enter after you reach the end of a line, will start the next line.

- If the line is at the bottom of the screen, the screen will be scrolled (moved) up one line.

- When Wrap is off, the character at the end of the line will be overprinted.

You can turn the Wrap function on or off by pressing the A key. The Wrap function will become effective when exiting the Main menu.

#### Auto LF on CR

When Auto (Automatic) LF (Line Feed) on CR (Carriage Return) is ON, a line feed is generated whenever a carriage return is received.

You can turn the Auto LF on CR ON or OFF by pressing the B key. Auto LF on CR will become effective when exiting the Main menu.

PRELIMINARY

#### Auto CR on LF

When Auto (Automatic) CR (Carriage Return) on LF (Line Feed) is ON, a carriage return is generated whenever a line feed is received.

You can turn the Auto CR on LF ON or OFF by pressing the C key. Auto CR on LF will become effective when exiting the Main menu.

#### **Screen Saver**

The screen will be automatically "blanked out" if no key is pressed or no data is received by the terminal for 15 consecutive minutes. This function increases the life of the screen.

The screen can be restored by pressing any key, or reception of data from the host computer, or auxiliary port via the serial channels.

You can turn the Screen saver function ON or OFF by pressing the D key. The selection will become effective immediately.

#### Status Line

The terminal Status Line (25th) on the CRT displays the following information after you exit from the Main menu: CAPS LOCK if the CAPS LOCK is enabled, OFF LINE if the terminal is in the Off-Line mode or ON LINE if the terminal is On-Line, Printer if the printer line is enabled, and INSERT MODE if the terminal is in the Insert mode.

You can turn the Status Line ON or OFF by pressing the E key. The terminal Status Line is not displayed until exiting the Main menu.

#### Columns

PRELIMINARY

This function allows you to select between 80- or 132-character Columns (characters per line).

You can select the desired number of Columns by pressing the F key. The selection will become effective immediately.

**NOTE:** When you change the number of Columns, the display is cleared and the data previously displayed is lost.

#### Scroll

The terminal is capable of scrolling the screen up in two modes, JUMP and SMOOTH Scroll.

- JUMP Scroll moves one character line up at a time.

- SMOOTH Scroll improves readability from rapidly received data by scrolling part of a character line up, instead of a whole line.

You can select the Scroll function desired by pressing the G key. The Scroll selection will become effective when exiting the Main menu.

**NOTE:** Screen flicker may occur when you select SMOOTH Scroll.

#### **Hold Screen**

The Hold Screen function operates in the Zenith mode only.

- When you enable the Hold Screen function, pressing the NO SCROLL key displays a new line of received information.

- You can display an entire new page of received information by pressing the NO SCROLL key and either SHIFT key at the same time.

- When the Hold Screen function is OFF, the NO SCROLL key generates a software handshake. Refer to Appendix B for more information.

You can turn the Hold Screen function ON or OFF by pressing the H key. The new Hold Screen selection will become effective when exiting the Main menu.

## **Cursor Parameters**

To change the Cursor parameters, in the Main menu press the **E** key. The cursor will be disabled while in the Main menu. The bottom four lines will indicate a display similar to:

A Cursor ON B Blink ON C Shape UNDERLINE CURSOR PARAMETERS

(Press SETUP to return to main menu)

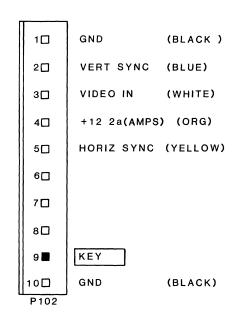

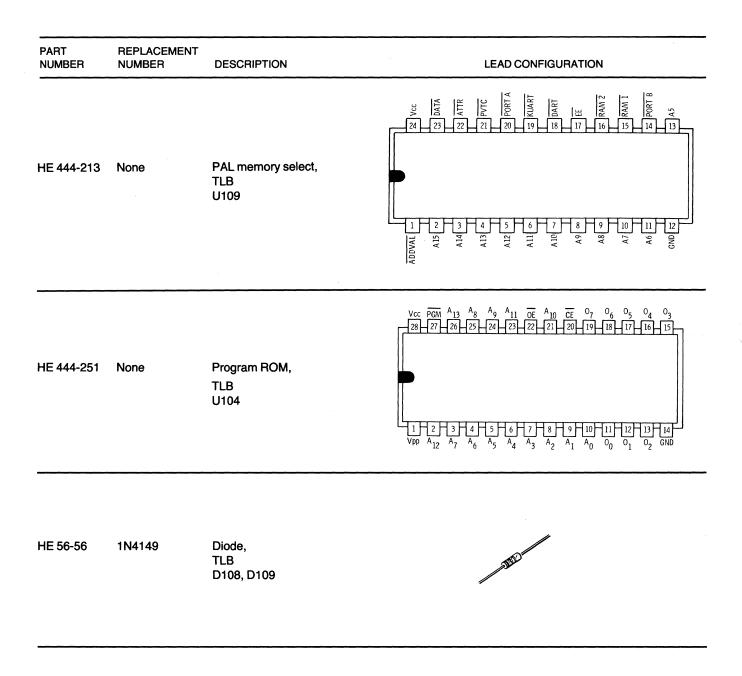

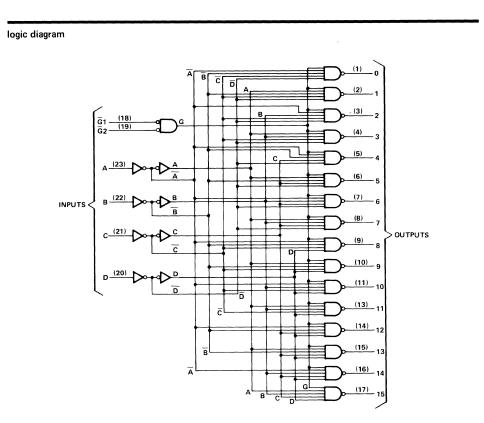

#### Cursor