# SST-1(a.k.a. Voodoo Graphics<sup>TM</sup>)

# HIGH PERFORMANCE GRAPHICS ENGINE FOR 3D GAME ACCELERATION

Revision 1.61 December 1, 1999 Copyright © 1995 3Dfx Interactive, Inc. All Rights Reserved

# **3dfx Interactive, Inc.** 4435 Fortran Drive

San Jose, CA 95134 Phone: (408) 935-4400 Fax: (408) 262-8602 www.3dfx.com

# **Proprietary Information**

## **Copyright Notice:**

[English translations from legalese in brackets]

©1996-1999, 3Dfx Interactive, Inc. All rights reserved

#### This document may be reproduced in written, electronic or any other form of expression only in its entirety.

[If you want to give someone a copy, you are hereby bound to give him or her a complete copy.]

#### This document may not be reproduced in any manner whatsoever for profit.

[If you want to copy this document, you must not charge for the copies other than a modest amount sufficient to cover the cost of the copy.]

#### **No Warranty**

THESE SPECIFICATIONS ARE PROVIDED BY 3DFX "AS IS" WITHOUT ANY REPRESENTATION OR WARRANTY, EXPRESS OR IMPLIED, INCLUDING ANY WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, NONINFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS, OR ARISING FROM THE COURSE OF DEALING BETWEEN THE PARTIES OR USAGE OF TRADE. IN NO EVENT SHALL 3DFX BE LIABLE FOR ANY DAMAGES WHATSOEVER INCLUDING, WITHOUT LIMITATION, DIRECT OR INDIRECT DAMAGES, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OF OR INABILITY TO USE THE SPECIFICATIONS, EVEN IF 3DFX HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

[You're getting it for free. We believe the information provided to be accurate. Beyond that, you're on your own.]

| CO           | PYRIGHT NOTICE:                                                                                                                                                                                                                       | 2  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| No           | WARRANTY                                                                                                                                                                                                                              | 2  |

|              | GENERAL DESCRIPTION                                                                                                                                                                                                                   |    |

| 1.           | GENERAL DESCRIPTION                                                                                                                                                                                                                   | 0  |

| 2.           | PERFORMANCE                                                                                                                                                                                                                           | 7  |

| •            |                                                                                                                                                                                                                                       | 0  |

| 3.           | ARCHITECTURAL AND FUNCTIONAL OVERVIEW                                                                                                                                                                                                 |    |

| 3.1          | System Level Diagrams                                                                                                                                                                                                                 |    |

| 3.2          | ARCHITECTURAL OVERVIEW                                                                                                                                                                                                                |    |

| 3.3          | FUNCTIONAL OVERVIEW                                                                                                                                                                                                                   | 13 |

| 4.           | SST-1 ADDRESS SPACE                                                                                                                                                                                                                   |    |

| 5.           | MEMORY MAPPED REGISTER SET                                                                                                                                                                                                            | 18 |

| 5.1          | status Register                                                                                                                                                                                                                       | 24 |

| 5.2          | VERTEX AND FVERTEX REGISTERS                                                                                                                                                                                                          |    |

| 5.3          | STARTR, STARTG, STARTB, STARTA, FSTARTR, FSTARTG, FSTARTB, AND FSTARTA REGISTERS                                                                                                                                                      |    |

| 5.4          | STARTZ AND FSTARTZ REGISTERS                                                                                                                                                                                                          |    |

| 5.5          | STARTS, STARTT, FSTARTS, AND FSTARTT REGISTERS                                                                                                                                                                                        |    |

| 5.6          | STARTW AND FSTARTW REGISTERS                                                                                                                                                                                                          |    |

| 5.7          | DRDX, DGDX, DBDX, DADX, FDRDX, FDGDX, FDBDX, AND FDADX REGISTERS                                                                                                                                                                      |    |

| 5.8          | DZDX AND FDZDX REGISTERS                                                                                                                                                                                                              |    |

| 5.9          | DSDX, DTDX, FDSDX, AND FDTDX REGISTERS                                                                                                                                                                                                |    |

| 5.10         | DWDX AND FDWDX REGISTERS                                                                                                                                                                                                              |    |

| 5.11         | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, _, |    |

| 5.12         |                                                                                                                                                                                                                                       |    |

| 5.13         |                                                                                                                                                                                                                                       |    |

| 5.14         |                                                                                                                                                                                                                                       |    |

| 5.15         |                                                                                                                                                                                                                                       |    |

| 5.           | 15.1 Caveats                                                                                                                                                                                                                          |    |

| 5.16         |                                                                                                                                                                                                                                       |    |

| 5.17         |                                                                                                                                                                                                                                       |    |

| 5.18         |                                                                                                                                                                                                                                       |    |

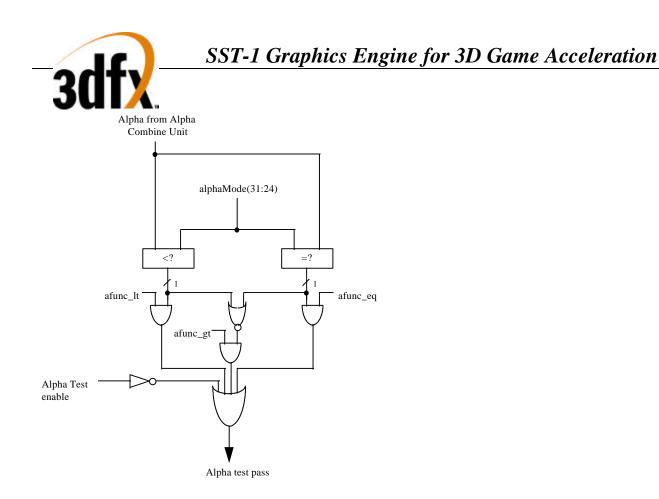

|              | 18.1 Alpha function                                                                                                                                                                                                                   |    |

|              | 18.2 Alpha Blending                                                                                                                                                                                                                   |    |

| 0.17         | FBZMODE REGISTER                                                                                                                                                                                                                      |    |

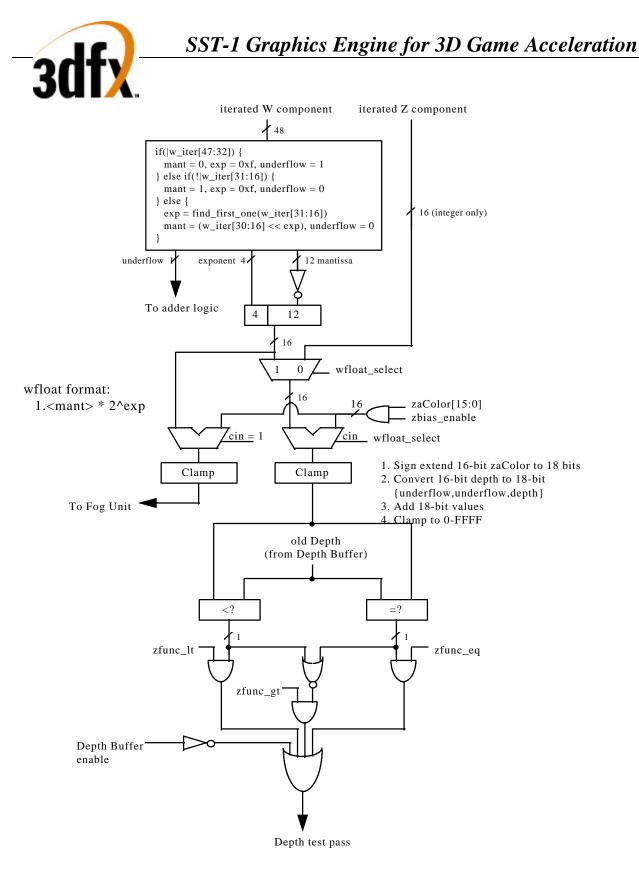

|              | 19.1 Depth-buffering function                                                                                                                                                                                                         |    |

| 5.20         |                                                                                                                                                                                                                                       |    |

|              | 20.1 Linear Frame Buffer Writes                                                                                                                                                                                                       |    |

|              | 20.2 Linear Frame Buffer Reads                                                                                                                                                                                                        |    |

| 5.21         |                                                                                                                                                                                                                                       |    |

| 5.22<br>5.23 |                                                                                                                                                                                                                                       |    |

| 5.23         |                                                                                                                                                                                                                                       |    |

| 5.24         |                                                                                                                                                                                                                                       |    |

| 5.25         |                                                                                                                                                                                                                                       |    |

| 5.20         |                                                                                                                                                                                                                                       |    |

| 5.21         |                                                                                                                                                                                                                                       |    |

| 5.28                         | STIPPLE REGISTER                                                                                                  | 56                         |

|------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------|

| 5.29                         | COLORO REGISTER                                                                                                   | 56                         |

| 5.30                         | COLOR1 REGISTER                                                                                                   |                            |

| 5.31                         | FBIPIXELSIN REGISTER                                                                                              |                            |

| 5.32                         | FBICHROMAFAIL REGISTER                                                                                            |                            |

| 5.33                         | FBIZFUNCFAIL REGISTER                                                                                             |                            |

| 5.34                         | FBIAFUNCFAIL REGISTER                                                                                             |                            |

| 5.35                         | FBIPIXELSOUT REGISTER                                                                                             |                            |

| 5.36                         | FOGTABLE REGISTER                                                                                                 |                            |

| 5.37                         | VRETRACE REGISTER                                                                                                 |                            |

| 5.38                         | HSYNC REGISTER                                                                                                    |                            |

| 5.39                         | vSync Register                                                                                                    |                            |

| 5.40                         | BACKPORCH REGISTER                                                                                                |                            |

| 5.41                         | VIDEODIMENSIONS REGISTER                                                                                          |                            |

| 5.42                         | FBIINITO REGISTER                                                                                                 |                            |

| 5.43                         | FBIINIT1 REGISTER                                                                                                 |                            |

| 5.44                         | FBIINIT2 REGISTER                                                                                                 |                            |

| 5.45                         | FBIINIT3 REGISTER                                                                                                 |                            |

| 5.46                         | FBIINIT4 REGISTER                                                                                                 |                            |

| 5.47                         | CLUTDATA REGISTER                                                                                                 |                            |

| 5.48                         | DACDATA REGISTER                                                                                                  |                            |

| 5.49                         | MAXRGBDELTA REGISTER                                                                                              |                            |

| 5.50                         | TEXTUREMODE REGISTER                                                                                              |                            |

| 5.51                         | TLOD REGISTER                                                                                                     |                            |

| 5.52                         | TDETAIL REGISTER                                                                                                  |                            |

| 5.53                         | TEXBASEADDR, TEXBASEADDR1, TEXBASEADDR2, AND TEXBASEADDR38 REGISTERS                                              |                            |

| 5.54                         | TREXINITO REGISTER                                                                                                |                            |

| 5.55                         | TREXINIT1 REGISTER                                                                                                |                            |

| 5.56                         | NCCTABLEO AND NCCTABLE1/PALETTE REGISTERS                                                                         |                            |

| 5.56                         |                                                                                                                   |                            |

| 5.56                         | 5.2 8-Bit Palette (not revision 0 TMU)                                                                            | 70                         |

| < D                          | CI CONFIGURATION REGISTER SET                                                                                     | = -                        |

| 6. P                         |                                                                                                                   |                            |

| 6.1                          | VENDOR_ID REGISTER                                                                                                | 72                         |

| 6.2                          | DEVICE_ID REGISTER                                                                                                | 72                         |

| 6.3                          | COMMAND REGISTER                                                                                                  | 72                         |

| 6.4                          | STATUS REGISTER                                                                                                   | 73                         |

| 6.5                          | REVISION_ID REGISTER                                                                                              | 73                         |

| 6.6                          | CLASS_CODE REGISTER                                                                                               | 73                         |

| 6.7                          | CACHE_LINE_SIZE REGISTER                                                                                          | 73                         |

| 6.8                          | LATENCY_TIMER REGISTER                                                                                            | 74                         |

| 6.9                          | HEADER_TYPE REGISTER                                                                                              | 74                         |

| 6.10                         |                                                                                                                   | 74                         |

|                              | BIST REGISTER                                                                                                     | /+                         |

| 6.11                         | BIST REGISTER                                                                                                     |                            |

| 6.11<br>6.12                 |                                                                                                                   | 74                         |

|                              | MEMBASEADDR REGISTER                                                                                              | 74<br>74                   |

| 6.12                         | MEMBASEADDR REGISTER                                                                                              | 74<br>74<br>74             |

| 6.12<br>6.13                 | MEMBASEADDR REGISTER<br>INTERRUPT_LINE REGISTER<br>INTERRUPT_PIN REGISTER                                         | 74<br>74<br>74<br>75       |

| 6.12<br>6.13<br>6.14         | MEMBASEADDR REGISTER                                                                                              | 74<br>74<br>75<br>75<br>75 |

| 6.12<br>6.13<br>6.14<br>6.15 | MEMBASEADDR REGISTER<br>INTERRUPT_LINE REGISTER<br>INTERRUPT_PIN REGISTER<br>MIN_GNT REGISTER<br>MAX_LAT REGISTER | 74<br>74<br>75<br>75<br>75 |

| 6.18        |                                         |  |

|-------------|-----------------------------------------|--|

| 6.19        |                                         |  |

| 6.20        |                                         |  |

| 6.21        | FASTFILL COMMAND                        |  |

| 6.22        | SWAPBUFF COMMAND                        |  |

| <b>7.</b> ] | LINEAR FRAME BUFFER ACCESS              |  |

| 7.1         | LINEAR FRAME BUFFER WRITES              |  |

| 7.2         | LINEAR FRAME BUFFER READS               |  |

| 8.          | TEXTURE MEMORY ACCESS                   |  |

| 9.          | PROGRAMMING CAVEATS                     |  |

| 9.1         | I/O Accesses                            |  |

| 9.2         | Memory Accesses                         |  |

| 9.3         | DETERMINING SST IDLE CONDITION          |  |

| 9.4         | TRIANGLE SUBPIXEL CORRECTION            |  |

| 9.5         | LOADING THE INTERNAL COLOR LOOKUP TABLE |  |

| 10.         | VIDEO TIMING                            |  |

| 11.         | SCANLINE INTERLEAVING                   |  |

| 12.         | SST-1 REVISION 2.0 CHANGES              |  |

| 13.         | REVISION HISTORY                        |  |

## 1. General Description

The SST-1 Graphics Engine from 3Dfx Interactive is the first video subsystem that enables personal computers and low cost video game platforms to host true 3D entertainment applications. Optimized for real-time texture-mapped 3D games and educational titles, SST-1 provides acceleration for advanced 3D features including true-perspective texture mapping with trilinear mipmapping and lighting, detail and projected texture mapping, texture antialiasing, and high precision sub-pixel correction. In addition, SST-1 supports general purpose 3D pixel processing functions including polygonal-based Gouraud shading, depth-buffering, alpha blending, and dithering.

## Features

- Triangle raster engine

- Linearly interpolated Gouraud-shaded rendering

- Perspective-corrected (divide-per-pixel) texture-mapped rendering with iterated RGB modulation/addition

- Detail and Projected Texture mapping

- Linearly interpolated 16-bit Z-buffer rendering

- Perspective-corrected 16-bit floating point W-buffer rendering (patent pending)

- Texture filtering: point-sampling, bilinear, and trilinear filtering with mipmapping

- Texture formats: 8-bit RGB(3-3-2), 8-bit intensity, 8-bit alpha, 8-bit narrow channel YIQ(4-2-2), 8-bit alpha-intensity(4-4), 16-bit RGB(5-6-5), 16-bit ARGB (1-5-5-5), 16-bit ARGB (4-4-4-4), 16-bit ARGB (8-3-3-2), 16-bit narrow channel AYIQ (8-4-2-2), 16-bit alpha-intensity (8-8)

- Texture decompression: 8-bit "narrow channel" YIQ (patent pending)

- Transparency with dedicated color mask

- Source/Destination pixel alpha blending

- Sub-pixel correction to .4 x .4 resolution

- 24-bit color dithering to native 16-bit RGB buffer using 4x4 or 2x2 ordered dither matrix

- Gamma-correction color lookup table

- Advanced memory architecture utilizing 1+ GByte/sec bandwidth

- 2-4 MBytes of EDO DRAM frame buffer memory

- 1-4 MBytes of EDO DRAM texture memory

- Resolution Support:

| Frame Buffer<br>Memory | Double Buffered,<br>no Depth-Buffering | Triple Buffered,<br>no Depth-Buffering | Double Buffered,<br>16-bit Depth-Buffering |

|------------------------|----------------------------------------|----------------------------------------|--------------------------------------------|

| 2 MBytes               | 800x600x16                             | 640x480x16                             | 640x480x16                                 |

| 4 MBytes               | 800x600x16                             | 800x600x16                             | 800x600x16                                 |

- Direct memory-mapped access to frame buffer and texture memories via linear address mapping

- PCI Bus 2.1 compliant

## Benefits

- Real-time, true-perspective, texture-mapped rendering with lighting support at low cost

- Eases software porting, as SST-1 only accelerates the inner rasterization loop

- Lowest cost solution designed expressly for use in the entertainment markets

- Patent pending techniques result in reduced texture memory requirements

## 2. Performance

The following tables show the estimated performance of SST-1. Performance is calculated assuming that the PCI Bus master is supplying data at its peak bandwidth. Thus, the performance levels are the maximum sustainable rates of SST-1, not necessarily the system performance. If a particular operation is CPU limited or a particular PCI bus master is not supplying data at its peak rate, then the effective system performance level will decrease. All numbers are represented in 16-bit MPixels/sec unless otherwise specified with the optional memory FIFO is disabled, and are measured assuming 640x480 resolution @ 60 Hz with a 50 MHz graphics clock frequency driving 50-ns Extended-Data-Out (EDO) DRAMs.

| Flat shaded triangles (no fogging, alpha-blending, Z-buffering, or sub-<br>pixel correction) | Ktriangles/sec |

|----------------------------------------------------------------------------------------------|----------------|

| 10-pixel, right-angled, horizontally oriented                                                | 1911           |

| 25-pixel, right-angled, horizontally oriented                                                | 1096           |

| 50-pixel, right-angled, horizontally oriented                                                | 644            |

| 1000-pixel, right-angled, horizontally oriented                                              | 42             |

| Gouraud shaded, sub-pixel corrected triangles with fogging, alpha-<br>blending and Z-buffering | Ktriangles/sec |

|------------------------------------------------------------------------------------------------|----------------|

| 10-pixel, right-angled, randomly oriented                                                      | 1231           |

| 25-pixel, right-angled, randomly oriented                                                      | 968            |

| 50-pixel, right-angled, randomly oriented                                                      | 550            |

| 1000-pixel, right-angled, randomly oriented                                                    | 37             |

| Bilinear filtered, Mipmapped, fogged, texture-mapped Gouraud shaded, sub-pixel corrected triangles (no alpha-blending or Z-buffering) | Ktriangles/sec |

|---------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 10-pixel, right-angled, randomly oriented                                                                                             | 828            |

| 25-pixel, right-angled, randomly oriented                                                                                             | 823            |

| 50-pixel, right-angled, randomly oriented                                                                                             | 655            |

| 1000-pixel, right-angled, randomly oriented                                                                                           | 43             |

| Bilinear filtered, Mipmapped, fogged, texture-mapped Gouraud<br>shaded, sub-pixel corrected triangles with alpha-blending and Z-<br>buffering | Ktriangles/sec |

|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 10-pixel, right-angled, randomly oriented                                                                                                     | 826            |

| 25-pixel, right-angled, randomly oriented                                                                                                     | 807            |

| 50-pixel, right-angled, randomly oriented                                                                                                     | 549            |

| 1000-pixel, right-angled, randomly oriented                                                                                                   | 37             |

| Screen Clears                       | msec |

|-------------------------------------|------|

| RGB Buffer                          | 3.45 |

| Depth Buffer                        | 3.45 |

| RBG and Depth Buffer simultaneously | 3.45 |

## 3. Architectural and Functional Overview

## 3.1 System Level Diagrams

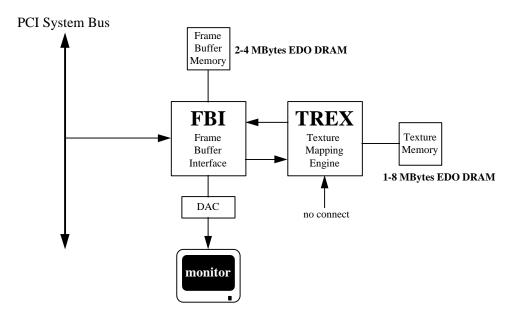

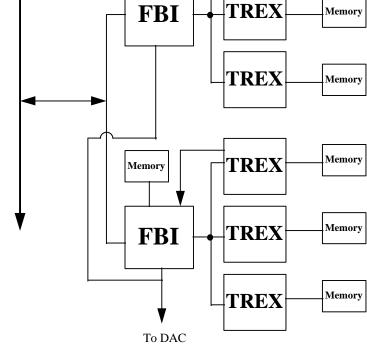

In its entry level configuration, a SST-1 graphics solution consists of two rendering ASICS: TREX and FBI. FBI ("Frame Buffer Interface") serves as a PCI slave device, and all communication from the host CPU to the SST-1 graphics subsystem is performed through FBI. FBI implements basic 3D primitives including Gouraud shading, alpha blending, depth-buffering, and dithering. FBI also includes logic for the programmable fog table, and incorporates logic to handle all linear frame buffer accesses. Additionally, FBI includes a video display controller which controls output to the display monitor. TREX ("Texture Raster Engine") implements all texture mapping capabilities of the SST-1 graphics subsystem. TREX includes logic to support true-perspective texture mapping (dividing by W every pixel), level-of-detail (LOD) mipmapping, and bilinear filtering. Additionally, TREX implements advanced texture mapping techniques such as detail texture mapping, projected texture mapping, and trilinear texture filtering. Both FBI and TREX support various memory types including standard, Extended-Data-Out (EDO), and Synchronous DRAM to provide a wide range of price/performance options. Note in the single TREX SST-1 solution, the advanced texture mapping techniques of detail texture mapping, projected texture mapping, and trilinear texture filtering are two-pass operations. There is no performance penalty, however, for point-sampled or bilinear filtered texture mapping with mipmapping with the single TREX solution. The diagram below illustrates a base-level SST-1 graphics solution.

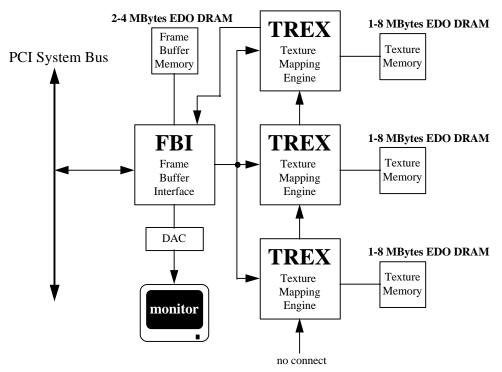

TREX includes a dedicated expansion bus which allows multiple TREX ASICs to be chained together. By chaining together multiple TREX ASICs, the performance of advanced texture mapping features such as detailed texture mapping, projected texture mapping, and trilinear filtering can be doubled. A two TREX SST-1 graphics solution allows single pass, full-speed, detail texture mapping, projected texture mapping, or trilinear filtering. The diagram below illustrates a two TREX graphics solution.

Three TREX ASICs can also be chained together to provide single-pass, full-speed rendering of all supported advanced texture mapping features including projected texture mapping. The diagram below illustrates the three TREX SST-1 graphics architecture:

The chart below provides performance characterization of advanced texture mapping rendering functionaltity for various SST-1 configurations.

| Texture Mapping<br>Functionality                                   |               | TREX<br>Performance |            |

|--------------------------------------------------------------------|---------------|---------------------|------------|

| Tunctionanty                                                       | One TREX      | Two TREX            | Three TREX |

| Point-sampled with mipmapping                                      | One-Pass      | One-Pass            | One-Pass   |

| Bilinear filtering with mipmapping                                 | One-Pass      | One-Pass            | One-Pass   |

| Bilinear filtering with mipmapping and projected textures          | Two-Pass      | One-Pass            | One-Pass   |

| Bilinear filtering with mipmapping<br>and detail textures          | Two-Pass      | One-Pass            | One-Pass   |

| Bilinear filtering with mipmapping, projected and detail textures  | Not supported | Two-Pass            | One-Pass   |

| Trilinear filtering with mipmapping                                | Two-Pass      | One-Pass            | One-Pass   |

| Trilinear filtering with mipmapping and projected textures         | Not supported | Two-Pass            | One-Pass   |

| Trilinear filtering with mipmapping and detail textures            | Not supported | Two-Pass            | One-Pass   |

| Trilinear filtering with mipmapping, projected and detail textures | Not supported | Two-Pass            | Two-Pass   |

For the highest possible rendering performance, multiple FBI/TREX subsystems can be chained together utilizing scan-line interleaving to effectively double the rendering rate of a single FBI/TREX subsystem. The figure below illustrates this high-performance SST-1 architecture:

Memory

TREX

### 3.2 Architectural Overview

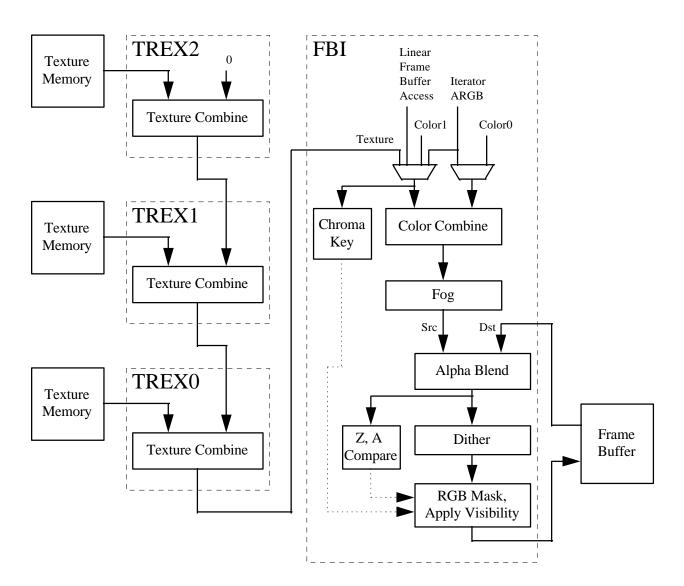

The diagram below illustrates the abstract rendering engine of the SST-1 graphics subsystem. The rendering engine is structured as a pipeline through which each pixel drawn to the screen must pass. The individual stages of the pixel pipeline modify pixels or make decisions about them.

#### 3.3 Functional Overview

<u>Bus Support</u>: SST-1 implements the PCI bus protocol, and conforms to PCI bus specification 2.1. SST-1 is a slave only device, and supports zero-wait-state and burst transfers.

<u>PCI Bus Write Posting</u>: SST-1 uses an asynchronous FIFO 64 entries deep which allows sufficient write posting capabilities for high performance. The FIFO is asynchronous to the graphics engine, thus allowing the memory interface to operate at maximum frequency regardless of the frequency of the PCI bus. Zero-wait-state writes are supported for maximum bus bandwidth.

<u>Memory FIFO</u>: SST-1 can optionally use off-screen frame bufffer memory to increase the effective depth of the PCI Bus FIFO. The depth of this memory FIFO is programmable, and when used as an addition to the regular 64 entry host FIFO, allows up to 65536 host writes to be queued without stalling the PCI interface.

<u>Memory Architecture</u>: SST-1(FBI) contains a 64-bit wide interleaved datapath to RGB and alpha/depth-buffer memory with support for up to 50 MHz EDO DRAMs. For Gouraud-shaded or textured-mapped polygons with depth buffering enabled, one pixel is written per clock. This results in a 50 Mpixels/sec peak fill rate with an EDO DRAM configuration. For screen/depth-buffer clears, two pixels are written per clock, resulting in a 100 Mpixels/sec fill rate. 2 MBytes of memory is required to support 640x480x16 resolution with 16-bit depth buffering. Additionally, non-depth-buffered modes are supported with the 2 MByte RGB/depth-buffer configuration, including 640x480x16 triple-buffered and 800x600x16 double-buffered. 800x600x16 double-buffered with depth-buffering is supported with 4 MBytes of RGB/depth-buffer memory. The minimum amount of RGB/depth-buffer memory is 2 MBytes, with a maximum of 4 MBytes supported.

For storing texture bitmaps, SST-1(TREX) also contains a separate 64-bit wide datapath to texture memory. TREX provides support for EDO DRAM memory to be used as texture memory. The texture memory datapath is fully interleaved, which allows an individual bank to access data irrespective of the address used to access data in other banks. This interleaved architecture allows SST-1 to perform bilinear texture filtering with no performance penalty relative to point sampling. Another advantage of the interleaved architecture is that it imposes no additional memory cost, since texels are not duplicated in texture memory. The minimum amount of texture memory required is 1 MByte, with a maximum of 8 MBytes of texture memory supported.

<u>Host Bus Addressing Schemes</u>: SST-1 occupies 16 Mbytes of memory mapped address space. SST-1 does not utilize I/O mapped address space. The register space of SST-1 occupies 4 Mbytes of address space, the linear frame buffer access port occupies 4 Mbytes of address space, and the texture memory access port occupies the last 8 Mbytes of address space.

<u>Linear Frame Buffer and Texture Access</u>: SST-1 supports linear frame buffer and texture memory accesses for software ease and regular porting. Multiple color formats are supported for linear frame buffer writes, and all pixels written may optionally be passed through the normal SST-1 pixel pipeline for fogging, lighting, alpha blending, dithering, etc. of linear frame buffer writes. All texture maps are downloaded to local SST-1 texture memory through the texture memory access address space.

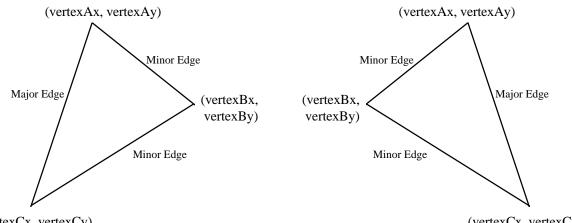

<u>*Triangle-based Rendering*</u>: SST-1 supports a triangle drawing primitive -- spans (both horizontal and vertical) and lines are rendered as special case triangles. Complex primitives such as quadrilaterals must be decomposed into triangles before they can be rendered by SST-1.

<u>Gouraud-shaded Rendering</u>: SST-1 supports Gouraud shading by providing RGBA iterators with rounding and clamping. The host provides starting RGBA and  $\Delta$ RGBA information, and SST-1 automatically iterates RGBA values across the defined span or trapezoid.

<u>Texture-mapped Rendering</u>: SST-1 supports texture mapping for trapezoids and spans. The host provides starting texture S/W, T/W, 1/W, and their slopes  $\Delta$ (S/W),  $\Delta$ (T/W), and  $\Delta$ (1/W) information. SST-1 automatically performs proper iteration and perspective correction necessary for true-perspective texture mapping. During each iteration of span/trapezoid walking, a division is performed by 1/W to correct for perspective distortion. Texture image dimensions must be powers of 2 and less than or equal to 256. Rectilinear and square texture bitmaps are supported.

<u>Texture-mapped Rendering with Lighting</u>: Texture-mapped rendering can be combined with Gouraud shading to introduce lighting effects during the texture mapping process. The host provides the starting Gouraud shading RGBA and slope  $\Delta$ RGBA information, as well as the starting texture S/W, T/W, 1/W, and slope  $\Delta$ (S/W),  $\Delta$ (T/W), and  $\Delta$ (1/W) information. SST-1 automatically performs the proper iteration and calculations required to implement the lighting models and texture lookups. A texel is either modulated (multiplied by), added, or blended to the Gouraud shaded color. The selection of color modulation or addition is programmable.

<u>Texture Mapping Anti-aliasing</u>: SST-1 allows for anti-aliasing of texture-mapped rendering with support for texture filtering and mipmapping. SST-1 supports point-sampled, bilinear, and trilinear texture filters. While point-sampled and bilinear are single pass operations, single TREX SST-1 graphics solutions require two-passes for trilinear texture filtering. Multiple TREX SST-1 graphics solutions support trilinear texture filtering as a single-pass operation. Note that regardless of the number of TREX ASICs in a given SST-1 graphics solution, there is no performance difference between point-sampled and bilinear filtered texture-mapped rendering.

In addition to supporting texture filtering, SST-1 also supports texture mipmapping. SST-1 automatically determines the mipmap level based on the mipmap equation, and selects the proper texture image to be accessed. When performing point-sampled or bilinear filtered texture mapping, dithering of the mipmap levels can optionally be used to remove mipmap "banding" during rendering. Using dithered mipmapping with bilinear filtering results in images almost indistinguishable from full trilinear filtered images.

<u>Texture-space Decompression</u>: Texture data compression is accomplished using a patent-pending "narrow channel" YIQ compression scheme. 8-bit YIQ format is supported. The compression is based on an algorithm which compresses 24-bit RGB to a 8-bit YIQ format with little loss in precision. This YIQ compression algorithm is especially suited to texture mapping, as textures typically contain very similar color components. The algorithm is performed by the host CPU, and YIQ compressed textures are passed to SST-1 The advantages of using compressed textures are increased effective texture storage space and lower bandwidth requirements to perform texture filtering.

<u>Depth-Buffered Rendering</u>: SST-1 supports hardware accelerated depth-buffered rendering with no performance penalty when enabled. With 2 MBytes of frame buffer memory, 640x480x16 resolution, double buffered with a 16-bit Z-buffer is supported. To eliminate many of the Z-aliasing problems typically found on 16-bit Z-buffer graphics solutions, SST-1 allows the (1/W) parameter to be used as the depth component for hardware-accelerated depth-buffered rendering. When the (1/W) parameter is used for depth-buffering, a16-bit floating point format is supported. A 16-bit floating point (1/W)-buffer provides much greater precision and dynamic range than a standard 16-bit Z-buffer, and reduces many of the Z-aliasing problems found on 16-bit Z-buffer systems. An additional benefit of using the (1/W) component for depth-buffering is that the host CPU no longer needs to setup the Z component for a given polygon -- the (1/W) component must be setup to perform perspective-corrected texture mapping anyway, and using this parameter for depth-buffering eliminates the need for a separate Z parameter.

Whether to use an integer-Z or floating-point-(1/W) is software programmable. If hardware-accelerated depthbuffering is not required, additional memory may be used to increase screen resolution. With 2 MBytes of frame buffer memory, 800x600x16, double buffered resolutions may be used if hardware-accelerated depth-buffering is not required.

<u>Pixel Blending Operations</u>: SST-1 supports alpha blending functions which allow incoming source pixels to be blended with current destination pixels with no performance penalty when enabled. An alpha channel (i.e. destination alpha) stored in offscreen memory is only supported when depth-buffering is disabled. [TO BE COMPLETED]. The alpha blending function is as follows:

$\mathsf{Dnew} \Leftarrow (S \cdot \alpha) + (\mathsf{Dold} \cdot \beta)$  where

Dnew The new destination pixel being written into the frame buffer

S The new source pixel being generated

Dold The old (current) destination pixel about to be modified

α The source pixel alpha function.

β The destination pixel alpha function.

<u>Special Effects</u>: TO BE COMPLETED (e.g. translucent billboards, spotlights, diffuse lighted texture, translucent cellophane [translucent filter]).

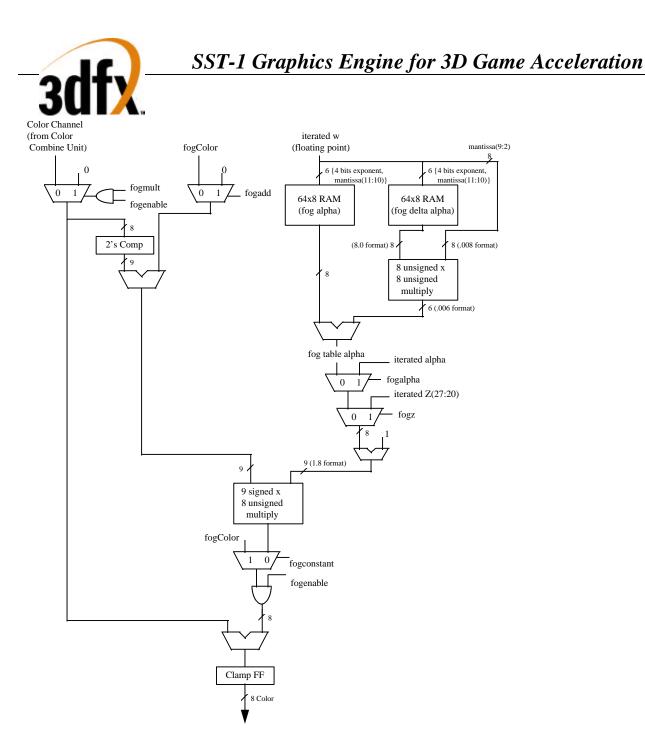

<u>FOG</u>: SST-1 supports a 64-entry lookup table to support atmospheric effects such as fog and haze. When enabled, a 6-bit floating point representation of (1/W) is used to index into the 64-entry lookup table. The output of the lookup table is an "alpha" value which represents the level of blending to be performed between the static fog/haze color and the incoming pixel color. Low order bits of the floating point (1/W) are used to blend between multiple entries of the lookup table to reduce fog "banding." The fog lookup table is loaded by the host CPU, so various fog equations, colors, and effects are supported.

<u>Color Modes</u>: SST-1 supports 16-bit RGB buffer displays only. The host may transfer 24-bit pixels to SST-1, and color dithering is utilized to convert the input pixels to native 16-bit format with no performance penalty.

<u>Chroma-Key Operation</u>: SST-1 supports a chroma-key operation used for transparent object effects. When enabled, an outgoing pixel is compared with the chroma-key register. If a match is detected, the outgoing pixel is invalidated in the pixel pipeline, and the frame buffer is not updated.

<u>Color Dithering Operations</u>: All operations internal to SST-1 operate in native 24-bit pixel mode. However, color dithering from 24-bit pixels to 16-bit pixels is provided on the back end of the pixel pipeline. Using the color dithering option, the host can pass 24-bit pixels to SST-1, which converts the 24-bit incoming pixels to 16-bit pixels which are then stored in the 16-bit RGB buffer. The 16-bit color dithering allows for the generation of photorealistic images without the additional cost of a true color frame buffer storage area.

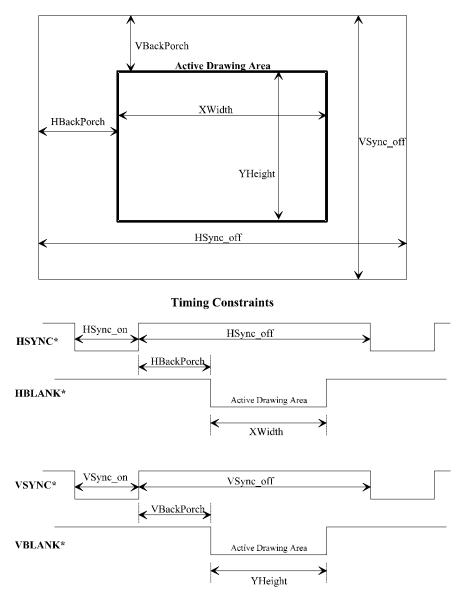

<u>*Programmable Video Timing*</u>: SST-1 uses a programmable video timing controller which allows for very flexible video timing. Any monitor type may be used with SST-1, with 76+ Hz vertical refresh rates supported at 800x600 resolution, and 100+ Hz vertical refresh rates supported at 640x480 resolution.

<u>*Gamma Correction*</u>: SST-1 uses a programmable color lookup table to allow for programmable gamma correction. The 16-bit dithered color data from the frame buffer is used an an index into the gamma-correction color table -- the 24-bit output of the gamma-correction color table is then fed to the monitor.

*External DAC Support*: SST-1 is compatible with industry standard RAMDACs and DACs. The DAC interface is identical to that provided by popular graphics accelerators such as the S3 864 and the Tseng Labs W32p.

## 4. <u>SST-1 Address Space</u>

SST-1 requires 16 Mbytes of memory mapped address space. SST-1 does not utilize I/O mapped memory. The memory mapped address space is shown below:

| Address           | Description                                 |  |  |

|-------------------|---------------------------------------------|--|--|

| 0x000000-0x3fffff | SST-1 memory mapped register set (4 MBytes) |  |  |

| 0x400000-0x7fffff | SST-1 linear frame buffer access (4 MBytes) |  |  |

| 0x800000-0xffffff | SST-1 texture memory access (8 MBytes)      |  |  |

The physical memory address for SST-1 accesses is calculated by adding the SST-1 address offset (0-16 MBytes) to the SST-1 base address register. The SST-1 base address register, **memBaseAddr**, is located in PCI configuration space. **memBaseAddr** is setup by the PCI System BIOS during system poweron and initialization and should not be modified by software. See section 5 for more information on the memory mapped register set, section 6 for more information on the PCI configuration space, section 8 for more information on linear frame buffer access, and section 9 for more information on texture memory access.

## 5. Memory Mapped Register Set

A 4 Mbyte (22-bit) SST-1 memory mapped register address is divided into the following fields:

| Wrap | Chip | Register | Byte |

|------|------|----------|------|

| 8    | 4    | 8        | 2    |

The **wrap** field aliases multiple 14-bit register maps. The **wrap** field is useful for processors such as the Digital Alpha AXP which contains large writebuffers which collapse multiple writes to the same address into a single write (an undesirable effect when programming SST-1). By writing to different **wraps**, software can guarantee that writes are not collapsed in the write buffer. Note that SST-1 functionality is identical regardless of which **wrap** is accessed. The **chip** field selects one or more of the SST-1 chips (FBI and/or TREX) to be accessed. Each bit in the **chip** field selects one chip for writing, with FBI controlled by the lsb of the **chip** field, and TREX#2 controlled by the msb of the **chip** field. Note the **chip** field value of 0x0 selects all chips. The following table shows the **chip** field mappings:

| Chip Field | SST-1 Chip Accessed         |

|------------|-----------------------------|

| 0000       | FBI + all TREX chips        |

| 0001       | FBI                         |

| 0010       | TREX #0                     |

| 0011       | FBI + TREX #0               |

| 0100       | TREX #1                     |

| 0101       | FBI + TREX #1               |

| 0110       | TREX #0 + TREX #1           |

| 0111       | FBI + TREX #0 + TREX #1     |

| 1000       | TREX #2                     |

| 1001       | FBI + TREX #2               |

| 1010       | TREX #0 + TREX #2           |

| 1011       | FBI + TREX #0 + TREX #2     |

| 1100       | TREX #1 + TREX #2           |

| 1101       | FBI + TREX #1 + TREX #2     |

| 1110       | TREX #0 + TREX #1 + TREX #2 |

| 1111       | FBI + all TREX chips        |

Note that TREX #0 is always connected to FBI in the system level diagrams of section 3, and TREX #1 is attached to TREX #0, etc. By utilizing the different **chip** fields, software can precisely control the data presented to individual chips which compose the SST-1 graphics subsystem. Note that for reads, the **chip** field is ignored, and read data is always read from FBI. The **register** field selects the register to be accessed from the table below. All accesses to the memory mapped registers must be 32-bit accesses. No byte (8-bit) or halfword (16-bit) accesses are allowed to the memory mapped registers, so the **byte** (2-bit) field of all memory mapped register accesses must be 0x0. As a result, to modify individual bits of a 32-bit register, the entire 32-bit word must be written with valid bits in all positions.

The table below shows the SST-1 register set. The register set shown below is the address map when triangle registers address aliasing (remapping) is disabled(**fbiinit3**(0)=0). When The **chip** column illustrates which registers are stored in which chips. For the registers which are stored in TREX, the % symbol specifies that the register is unconditionally written to TREX regardless of the chip address. Similarly, the \* symbol specifies that the register is only written to a given TREX if specified in the chip address. The **R/W** column illustrates the

read/write status of individual registers. Reading from a register which is "write only" returns undefined data. Also, reading from a register that is TREX specific returns undefined data.. Reads from all other memory mapped registers only contain valid data in the bits stored by the registers, and undefined/reserved bits in a given register must be masked by software. The **sync** column indicates whether the graphics processor must wait for the current command to finish before loading a particular register from the FIFO. A "yes" in the **sync** column means the graphics processor will flush the data pipeline before loading the register -- this will result in a small performance degradation when compared to those registers which do not need synchronization. The **FIFO** column indicates whether a write to a particular register will be pushed into the PCI bus FIFO. Care must be taken when writing to those registers not pushed into the FIFO in order to prevent race conditions between FIFOed and non-FIFOed registers. Also note that reads are not pushed into the PCI bus FIFO, and reading FIFOed registers will return the current value of the register, irrespective of pending writes to the register present in the FIFO.

| Register Name | Address    | Bits | Chip                  | R/W | Sync? Description<br>/Fifo? |                                                  |  |

|---------------|------------|------|-----------------------|-----|-----------------------------|--------------------------------------------------|--|

| status        | 0x000(0)   | 31:0 | FBI                   | R/W | No / Yes                    | SST-1 Status                                     |  |

| reserved      | 0x004(4)   | n/a  | n/a                   | n/a | n/a                         |                                                  |  |

| vertexAx      | 0x008(8)   | 15:0 | FBI+TREX <sup>%</sup> | W   | No / Yes                    | Vertex A x-coordinate location (12.4 format)     |  |

| vertexAy      | 0x00c(12)  | 15:0 | FBI+TREX <sup>%</sup> | W   | No / Yes                    | Vertex A y-coordinate location (12.4 format)     |  |

| vertexBx      | 0x010(16)  | 15:0 | FBI+TREX <sup>%</sup> | W   | No / Yes                    | Vertex B x-coordinate location (12.4 format)     |  |

| vertexBy      | 0x014(20)  | 15:0 | FBI+TREX <sup>%</sup> | W   | No / Yes                    | Vertex B y-coordinate location (12.4 format)     |  |

| vertexCx      | 0x018(24)  | 15:0 | FBI+TREX <sup>%</sup> | W   | No / Yes                    | Vertex C x-coordinate location (12.4 format)     |  |

| vertexCy      | 0x01c(28)  | 15:0 | FBI+TREX <sup>%</sup> | W   | No / Yes                    | Vertex C y-coordinate location (12.4 format)     |  |

| startR        | 0x020(32)  | 23:0 | FBI                   | W   | No / Yes                    | Starting Red parameter (12.12 format)            |  |

| startG        | 0x024(36)  | 23:0 | FBI                   | W   | No / Yes                    | Starting Green parameter (12.12 format)          |  |

| startB        | 0x028(40)  | 23:0 | FBI                   | W   | No / Yes                    | Starting Blue parameter (12.12 format)           |  |

| startZ        | 0x02c(44)  | 31:0 | FBI                   | W   | No / Yes                    | Starting Z parameter (20.12 format)              |  |

| startA        | 0x030(48)  | 23:0 | FBI                   | W   | No / Yes                    | Starting Alpha parameter (12.12 format)          |  |

| startS        | 0x034(52)  | 31:0 | TREX*                 | W   | No / Yes                    | Starting S/W parameter (14.18 format)            |  |

| startT        | 0x038(56)  | 31:0 | TREX*                 | W   | No / Yes                    | Starting T/W parameter (14.18 format)            |  |

| startW        | 0x03c(60)  | 31:0 | FBI+TREX*             | W   | No / Yes                    | Starting 1/W parameter (2.30 format)             |  |

| dRdX          | 0x040(64)  | 23:0 | FBI                   | W   | No / Yes                    | Change in Red with respect to X (12.12 format)   |  |

| dGdX          | 0x044(68)  | 23:0 | FBI                   | W   | No / Yes                    | Change in Green with respect to X (12.12 format) |  |

| dBdX          | 0x048(72)  | 23:0 | FBI                   | W   | No / Yes                    | Change in Blue with respect to X (12.12 format)  |  |

| dZdX          | 0x04c(76)  | 31:0 | FBI                   | W   | No / Yes                    | Change in Z with respect to X (20.12 format)     |  |

| dAdX          | 0x050(80)  | 23:0 | FBI                   | W   | No / Yes                    | Change in Alpha with respect to X (12.12 format) |  |

| dSdX          | 0x054(84)  | 31:0 | TREX*                 | W   | No / Yes                    | Change in S/W with respect to X (14.18 format)   |  |

| dTdX          | 0x058(88)  | 31:0 | TREX*                 | W   | No / Yes                    | Change in T/W with respect to X (14.18 format)   |  |

| dWdX          | 0x05c(92)  | 31:0 | FBI+TREX*             | W   | No / Yes                    | Change in 1/W with respect to X (2.30 format)    |  |

| dRdY          | 0x060(96)  | 23:0 | FBI                   | W   | No / Yes                    | Change in Red with respect to Y (12.12 format)   |  |

| dGdY          | 0x064(100) | 23:0 | FBI                   | W   | No / Yes                    | Change in Green with respect to Y (12.12 format) |  |

| dBdY          | 0x068(104) | 23:0 | FBI                   | W   | No / Yes                    | Change in Blue with respect to Y (12.12 format)  |  |

| dZdY          | 0x06c(108) | 31:0 | FBI                   | W   | No / Yes                    | Change in Z with respect to Y (20.12 format)     |  |

| dAdY          | 0x070(112) | 23:0 | FBI                   | W   | No / Yes                    | Change in Alpha with respect to Y (12.12 format) |  |

| dSdY          | 0x074(116) | 31:0 | TREX <sup>*</sup>     | W   | No / Yes                    | Change in S/W with respect to Y (14.18 format)   |  |

| dTdY          | 0x078(120) | 31:0 | TREX*                 | W   | No / Yes                    | Change in T/W with respect to Y (14.18 format)   |  |

| dWdY          | 0x07c(124) | 31:0 | FBI+TREX*             | W   | No / Yes                    | Change in 1/W with respect to Y (2.30 format)    |  |

| triangleCMD   | 0x080(128) | 31   | FBI+TREX <sup>%</sup> | W   | No / Yes                    | Execute TRIANGLE command (floating point)        |  |

| -             |            |      |                       | W   |                             | Execute TRIANGLE command (noaling point)         |  |

| reserved      | 0x084(132) | n/a  | n/a                   | W   | n/a                         |                                                  |  |

| <b>VUI</b>    | <b>/ </b>                |      |                       |      |                        |                                                                         |

|---------------|--------------------------|------|-----------------------|------|------------------------|-------------------------------------------------------------------------|

| fvertexAx     | 0x088(136)               | 31:0 | FBI+TREX%             | W    | No / Yes               | Vertex A x-coordinate location (floating point)                         |

| fvertexAy     | 0x08c(140)               | 31:0 | FBI+TREX%             | W    | No / Yes               | Vertex A y-coordinate location (floating point)                         |

| fvertexBx     | 0x090(144)               | 31:0 | FBI+TREX <sup>%</sup> | W    | No / Yes               | Vertex B x-coordinate location (floating point)                         |

| fvertexBy     | 0x094(148)               | 31:0 | FBI+TREX <sup>%</sup> | W    | No / Yes               | Vertex B y-coordinate location (floating point)                         |

| fvertexCx     | 0x098(152)               | 31:0 | FBI+TREX%             | W    | No / Yes               | Vertex C x-coordinate location (floating point)                         |

| fvertexCy     | 0x09c(156)               | 31:0 | FBI+TREX <sup>%</sup> | W    | No / Yes               | Vertex C y-coordinate location (floating point)                         |

| for the st    | 0.0.0(1(0))              | 21.0 | EDI                   | 337  | NL / X                 |                                                                         |

| fstartR       | 0x0a0(160)               | 31:0 | FBI                   | W    | No / Yes               | Starting Red parameter (floating point)                                 |

| fstartG       | 0x0a4(164)               | 31:0 | FBI                   | W    | No / Yes               | Starting Green parameter (floating point)                               |

| fstartB       | 0x0a8(168)               | 31:0 | FBI                   | W    | No / Yes               | Starting Blue parameter (floating point)                                |

| fstartZ       | 0x0ac(172)               | 31:0 | FBI                   | W    | No / Yes               | Starting Z parameter (floating point)                                   |

| fstartA       | 0x0b0(176)               | 31:0 | FBI                   | W    | No / Yes               | Starting Alpha parameter (floating point)                               |

| fstartS       | 0x0b4(180)               | 31:0 | TREX*                 | W    | No / Yes               | Starting S/W parameter (floating point)                                 |

| fstartT       | 0x0b8(184)               | 31:0 | TREX*                 | W    | No / Yes               | Starting T/W parameter (floating point)                                 |

| fstartW       | 0x0bc(188)               | 31:0 | FBI+TREX*             | W    | No / Yes               | Starting 1/W parameter (floating point)                                 |

| fdRdX         | 0x0c0(192)               | 31:0 | FBI                   | W    | No / Yes               | Change in Red with respect to X (floating point)                        |

| fdGdX         | 0x0c4(196)               | 31:0 | FBI                   | W    | No / Yes               | Change in Green with respect to X (floating                             |

|               |                          |      |                       |      |                        | point)                                                                  |

| fdBdX         | 0x0c8(200)               | 31:0 | FBI                   | W    | No / Yes               | Change in Blue with respect to X (floating point)                       |

| fdZdX         | 0x0cc(204)               | 31:0 | FBI                   | W    | No / Yes               | Change in Z with respect to X (floating point)                          |

| fdAdX         | 0x0d0(208)               | 31:0 | FBI                   | W    | No / Yes               | Change in Alpha with respect to X (floating                             |

| C1C 177       | 0.014/212                | 21.0 | TDEM                  | ** * | NT ( <b>T</b> 7        | point)                                                                  |

| fdSdX         | 0x0d4(212)               | 31:0 | TREX*                 | W    | No / Yes               | Change in S/W with respect to X (floating point)                        |

| fdTdX         | 0x0d8(216)               | 31:0 | TREX*                 | W    | No / Yes               | Change in T/W with respect to X (floating point)                        |

| fdWdX         | 0x0dc(220)               | 31:0 | FBI+TREX*             | W    | No / Yes               | Change in 1/W with respect to X (floating point)                        |

| fdRdY         | 0x0e0(224)               | 31:0 | FBI                   | W    | No / Yes               | Change in Red with respect to Y (floating point)                        |

| fdGdY         | 0x0e4(228)               | 31:0 | FBI                   | W    | No / Yes               | Change in Green with respect to Y (floating point)                      |

| fdBdY         | 0x0e8(232)               | 31:0 | FBI                   | W    | No / Yes               | Change in Blue with respect to Y (floating point)                       |

| fdZdY         | 0x0ec(236)               | 31:0 | FBI                   | W    | No / Yes               | Change in Z with respect to Y (floating point)                          |

| fdAdY         | 0x0f0(240)               | 31:0 | FBI                   | W    | No / Yes               | Change in Alpha with respect to Y (floating point)                      |

| fdSdY         | 0x0f4(244)               | 31:0 | TREX*                 | W    | No / Yes               | Change in S/W with respect to Y (floating point)                        |

| fdTdY         | 0x0f8(248)               | 31:0 | TREX*                 | W    | No / Yes               | Change in T/W with respect to Y (floating point)                        |

| fdWdY         | 0x0fc(252)               | 31:0 | FBI+TREX*             | W    | No / Yes               | Change in 1/W with respect to Y (floating point)                        |

|               | 0.100/25(0)              | 01   |                       | ***  | NT ( 17                |                                                                         |

| ftriangleCMD  | 0x100(256)               | 31   | FBI+TREX%             | W    | No / Yes               | Execute TRIANGLE command (floating point)                               |

| fbzColorPath  | 0x104(260)               | 27:0 | FBI+TREX <sup>%</sup> | R/W  | No / Yes               | FBI Color Path Control                                                  |

| fogMode       | 0x108(264)               | 5:0  | FBI                   | R/W  | No / Yes               | Fog Mode Control                                                        |

| alphaMode     | 0x10c(268)               | 31:0 | FBI                   | R/W  | No / Yes               | Alpha Mode Control                                                      |

| fbzMode       | 0x110(272)               | 20:0 | FBI                   | R/W  | Yes / Yes              | RGB Buffer and Depth-Buffer Control                                     |

| lfbMode       | 0x114(276)               | 16:0 | FBI                   | R/W  | Yes / Yes              | Linear Frame Buffer Mode Control<br>Left and Right of Clipping Register |

| clipLeftRight | 0x118(280)<br>0x11a(284) | 31:0 | FBI                   | R/W  | Yes / Yes<br>Yes / Yes | Top and Bottom of Clipping Register                                     |

| clipLowYHighY | 0x11c(284)               | 31:0 | FBI                   | R/W  | Tes / Tes              |                                                                         |

| nopCMD        | 0x120(288)               | 0    | FBI+TREX <sup>%</sup> | W    | Yes / Yes              | Execute NOP command                                                     |

| fastfillCMD   | 0x124(292)               | n/a  | FBI                   | W    | Yes / Yes              | Execute FASTFILL command                                                |

| swapbufferCMD | 0x128(296)               | 8:0  | FBI                   | W    | Yes / Yes              | Execute SWAPBUFFER command                                              |

| fogColor      | 0x12c(300)               | 23:0 | FBI                   | W    | Yes / Yes              | Fog Color Value                                                         |

| zaColor       | 0x130(304)               | 31:0 | FBI                   | W    | Yes / Yes              | Constant Alpha/Depth Value                                              |

| chromaKey     | 0x134(308)               | 23:0 | FBI                   | W    | Yes / Yes              | Chroma Key Compare Value                                                |

|                 | - T - T    |      |       |     |            |                                                  |

|-----------------|------------|------|-------|-----|------------|--------------------------------------------------|

| reserved        | 0x138(312) | n/a  | n/a   | n/a | n/a        |                                                  |

| reserved        | 0x13c(316) | n/a  | n/a   | n/a | n/a        |                                                  |

|                 |            |      |       |     |            |                                                  |

| stipple         | 0x140(320) | 31:0 | FBI   | R/W | Yes / Yes  | Rendering Stipple Value                          |

| color0          | 0x144(324) | 31:0 | FBI   | R/W | Yes / Yes  | Constant Color #0                                |

| color1          | 0x148(328) | 31:0 | FBI   | R/W | Yes / Yes  | Constant Color #1                                |

| fbiPixelsIn     | 0x14c(332) | 23:0 | FBI   | R   | n/a        | Pixel Counter (Number pixels processed)          |

| fbiChromaFail   | 0x150(336) | 23:0 | FBI   | R   | n/a        | Pixel Counter (Number pixels failed Chroma test) |

| fbiZfuncFail    | 0x154(340) | 23:0 | FBI   | R   | n/a        | Pixel Counter (Number pixels failed Z test)      |

| fbiAfuncFail    | 0x158(344) | 23:0 | FBI   | R   | n/a        | Pixel Counter (Number pixels failed Alpha test)  |

| fbiPixelsOut    | 0x15c(348) | 23:0 | FBI   | R   | n/a        | Pixel Counter (Number pixels drawn)              |

|                 |            |      |       |     |            |                                                  |

| fogTable        | 0x160(352) | 31:0 | FBI   | W   | Yes / Yes  | Fog Table                                        |

| 6               | to         |      |       |     |            |                                                  |

|                 | 0x1dc(476) |      |       |     |            |                                                  |

|                 | , , ,      |      |       |     |            |                                                  |

| reserved        | 0x1e0(480) | n/a  | n/a   | n/a | n/a        |                                                  |

|                 | to         |      |       |     |            |                                                  |

|                 | 0x1fc(508) |      |       |     |            |                                                  |

|                 |            |      |       |     |            |                                                  |

| fbiInit4        | 0x200(512) | 12:0 | FBI   | R/W | (n/a) / No | FBI Hardware Initialization (register 4)         |

| vRetrace        | 0x204(516) | 11:0 | FBI   | R   | (n/a) / No | Vertical Retrace Counter                         |

| backPorch       | 0x208(520) | 23:0 | FBI   | R/W | (n/a) / No | Video Backporch Timing Generator                 |

| videoDimensions | 0x20c(524) | 25:0 | FBI   | R/W | (n/a) / No | Video Screen Dimensions                          |

| fbiInit0        | 0x210(528) | 31:0 | FBI   | R/W | (n/a) / No | FBI Hardware Initialization (register 0)         |

| fbiInit1        | 0x214(532) | 31:0 | FBI   | R/W | (n/a) / No | FBI Hardware Initialization (register 1)         |

| fbiInit2        | 0x218(536) | 31:0 | FBI   | R/W | (n/a) / No | FBI Hardware Initialization (register 2)         |

| fbiInit3        | 0x21c(540) | 31:0 | FBI   | R/W | (n/a) / No | FBI Hardware Initialization (register 3)         |

|                 | , , ,      |      |       |     | ì.         |                                                  |

| hSync           | 0x220(544) | 25:0 | FBI   | W   | (n/a) / No | Horizontal Sync Timing Generator                 |

| vSync           | 0x224(548) | 27:0 | FBI   | W   | (n/a) / No | Vertical Sync Timing Generator                   |

| clutData        | 0x228(552) | 29:0 | FBI   | W   | (n/a) / No | Internal Color Lookup Table Initialization       |

| dacData         | 0x22c(556) | 31:0 | FBI   | W   | (n/a) / No | External DAC Initialization                      |

| maxRgbDelta     | 0x230(560) | 23:0 | FBI   | W   | (n/a) / No | Max. RGB difference for Video Filtering          |

| reserved        | 0x234(564) | n/a  | n/a   | n/a | n/a        |                                                  |

|                 | to         |      |       |     |            |                                                  |

|                 | 0x2fc(764) |      |       |     |            |                                                  |

|                 |            |      |       |     |            |                                                  |

| textureMode     | 0x300(768) | 30:0 | TREX* | W   | No / Yes   | Texture Mode Control                             |

| tLOD            | 0x304(772) | 23:0 | TREX* | W   | No / Yes   | Texture LOD Settings                             |

| tDetail         | 0x308(776) | 16:0 | TREX* | W   | No / Yes   | Texture LOD Settings                             |

| texBaseAddr     | 0x30c(780) | 18:0 | TREX* | W   | No / Yes   | Texture Base Address                             |

| texBaseAddr_1   | 0x310(784) | 18:0 | TREX* | W   | No / Yes   | Texture Base Address (supplemental LOD 1)        |

| texBaseAddr_2   | 0x314(788) | 18:0 | TREX* | W   | No / Yes   | Texture Base Address (supplemental LOD 2)        |

| texBaseAddr_3_8 | 0x318(792) | 18:0 | TREX* | W   | No / Yes   | Texture Base Address (supplemental LOD 3-8)      |

| trexInit0       | 0x31c(796) | 31:0 | TREX* | W   | Yes / Yes  | TREX Hardware Initialization (register 0)        |

| trexInit1       | 0x320(800) | 31:0 | TREX* | W   | Yes / Yes  | TREX Hardware Initialization (register 1         |

|                 | Ì          |      |       |     | 1          |                                                  |

| nccTable0       | 0x324(804) | 31:0 | TREX* | W   | Yes / Yes  | Narrow Channel Compression Table 0 (12           |

|                 | to         | or   |       |     |            | entries)                                         |

|                 | 0x350(848) | 26:0 |       |     |            |                                                  |

|                 |            |      |       |     |            |                                                  |

|                 |            |      |       |     |            |                                                  |

|           | - N         |      |       |     |           |                                        |

|-----------|-------------|------|-------|-----|-----------|----------------------------------------|

| nccTable1 | 0x354(852)  | 31:0 | TREX* | W   | Yes / Yes | Narrow Channel Compression Table 1 (12 |

|           | to          | or   |       |     |           | entries)                               |

|           | 0x380(896)  | 26:0 |       |     |           |                                        |

|           |             |      |       |     |           |                                        |

| reserved  | 0x384(900)  | n/a  | n/a   | n/a | n/a       |                                        |

|           | to          |      |       |     |           |                                        |

|           | 0x3fc(1020) |      |       |     |           |                                        |

When **fbiinit3**(0)=1, the triangle parameter registers can be aliased to a different address mapping to improve PCI bus throughput. When **fbiinit3**(0)=1 and the upper bit of the **wrap** field in the pci address is 0x1 (**pci\_ad**[21]=1), the following table shows the addresses for the triangle parameter registers. Note that enabling triangle parameter remapping (**fbiinit3**(0)=1) has no affect any registers not specified in the table below.

| Register Name | Address    | Bits | Chip                  | R/W | Sync?<br>/Fifo? | Description                                      |

|---------------|------------|------|-----------------------|-----|-----------------|--------------------------------------------------|

| status        | 0x000(0)   | 31:0 | FBI                   | R/W | No / Yes        | SST-1 Status                                     |

| reserved      | 0x004(4)   | n/a  | n/a                   | n/a | n/a             |                                                  |

| vertexAx      | 0x008(8)   | 15:0 | FBI+TREX%             | W   | No / Yes        | Vertex A x-coordinate location (12.4 format)     |

| vertexAy      | 0x00c(12)  | 15:0 | FBI+TREX%             | W   | No / Yes        | Vertex A y-coordinate location (12.4 format)     |

| vertexBx      | 0x010(16)  | 15:0 | FBI+TREX%             | W   | No / Yes        | Vertex B x-coordinate location (12.4 format)     |

| vertexBy      | 0x014(20)  | 15:0 | FBI+TREX <sup>%</sup> | W   | No / Yes        | Vertex B y-coordinate location (12.4 format)     |

| vertexCx      | 0x018(24)  | 15:0 | FBI+TREX%             | W   | No / Yes        | Vertex C x-coordinate location (12.4 format)     |

| vertexCy      | 0x01c(28)  | 15:0 | FBI+TREX <sup>%</sup> | W   | No / Yes        | Vertex C y-coordinate location (12.4 format)     |

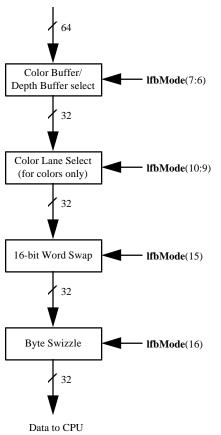

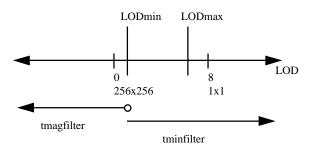

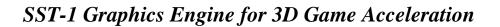

|               |            |      |                       |     |                 |                                                  |