### KL5C80A12

### 1. General Description

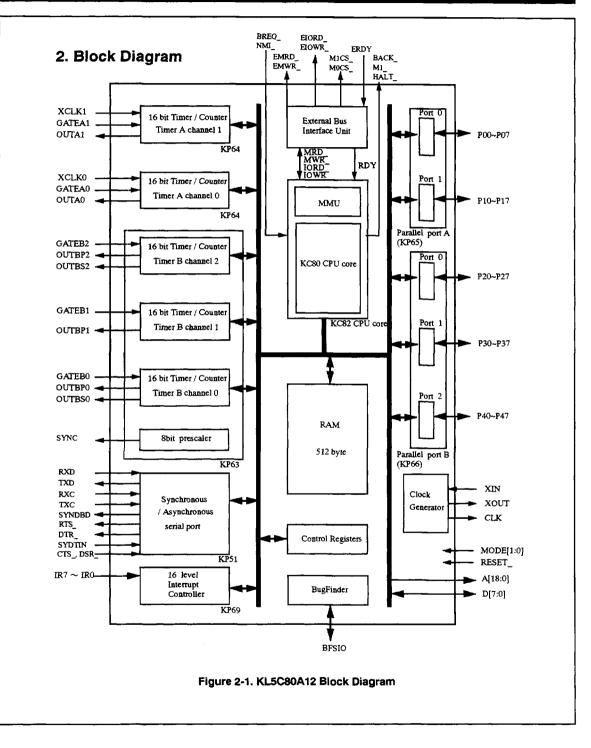

KL5C80A12CFP is a 8-bit high speed microcontroller developed with the state-of-the-art 0.8µm CMOS process. KL5C80A12CFP is compatible. In this data sheet. As CPU core it uses KC82, which is binary compatible with Zilog's Z80, and contains MMU to expand address space. The KC82 is a next generation 8-bit CPU core which executes instructions about four times faster than the Z80 (10MHz) and offers higher performance than typical 16-bit CPUs. In addition to the CPU core, KL5C80A12 contains a 512-byte high speed RAM, an interrupt controller, five16-bit high performance timer/counters, a synchronous/synchronous serial communication interface (USART)and 40 parallel ports, providing all requirements for high performance and compact system. It has also low power dissipation and is suitable for application to portable devices.

### Features

- 1) Binary compatible with the Z80 CPU,4 times faster than Z80 at the same clock rate

- 2) Built-in MMU which expands address space to 512KB

- 3) High speed USART (Universal Synchronous Asynchronous Receiver Transmitter)

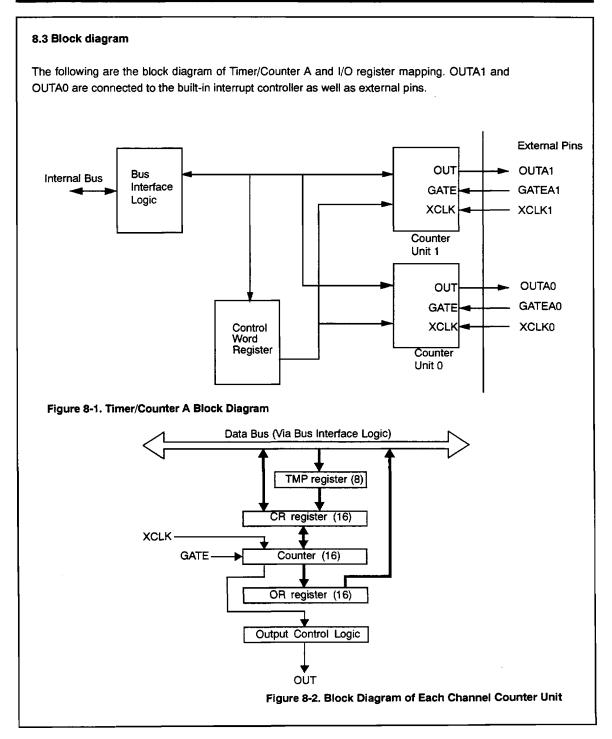

- 4) Two high performance 16-bit timer/counters

- 5) Three high performance 16-bit timer/counters with 8-bit prescaler

- 6) Eight internal interrupts and eight external interrupts (flexible priority), one non-maskable interrupt

- 7) 40 parallel ports

- 8) On-chip 512-byte high speed RAM

- 9) On-chip external memory chip select circuit

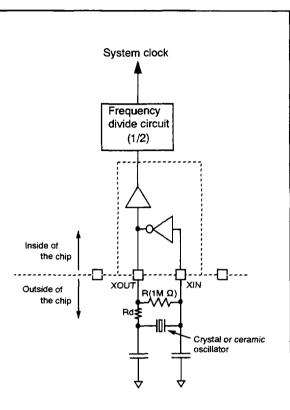

- 10) On-chip crystal oscillator buffer

- 11) Maximum operating frequency 10MHz

- 12) Low power dissipation

### KL5C80A12

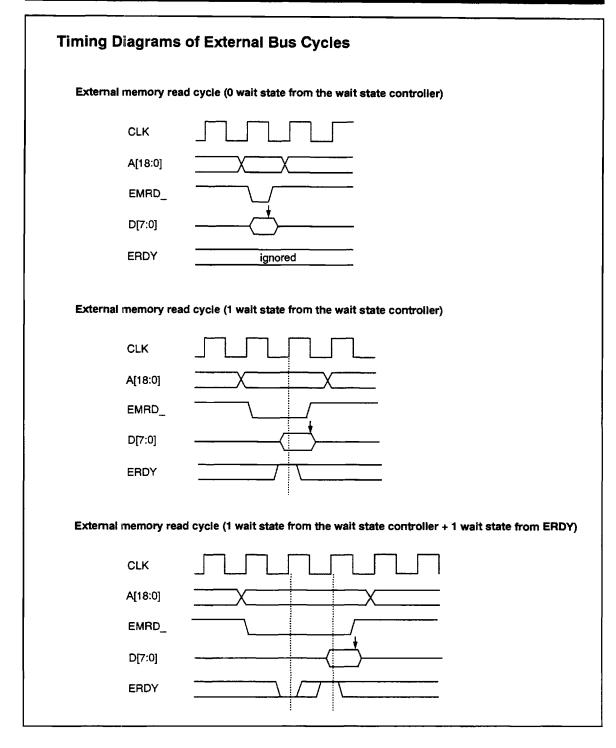

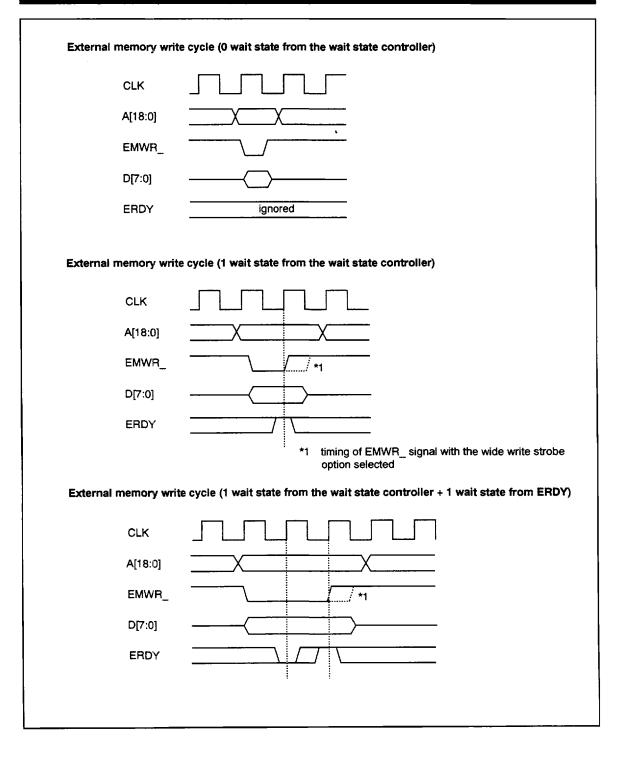

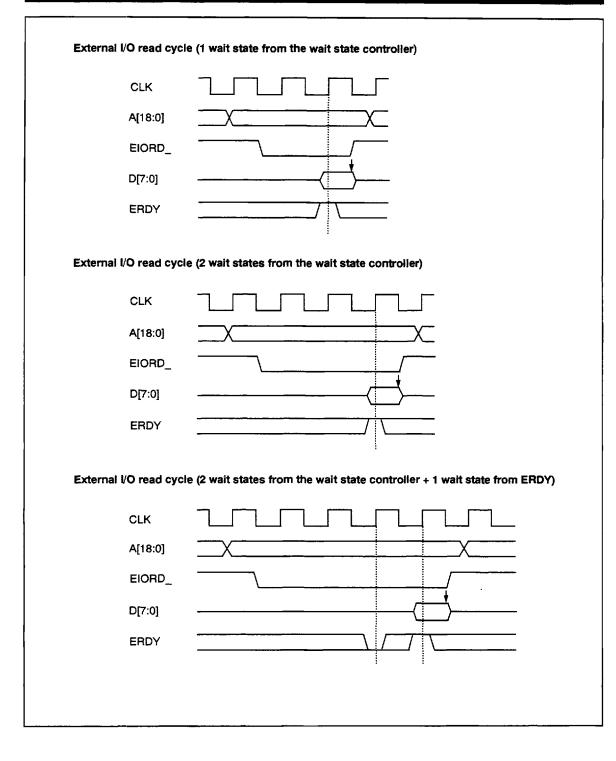

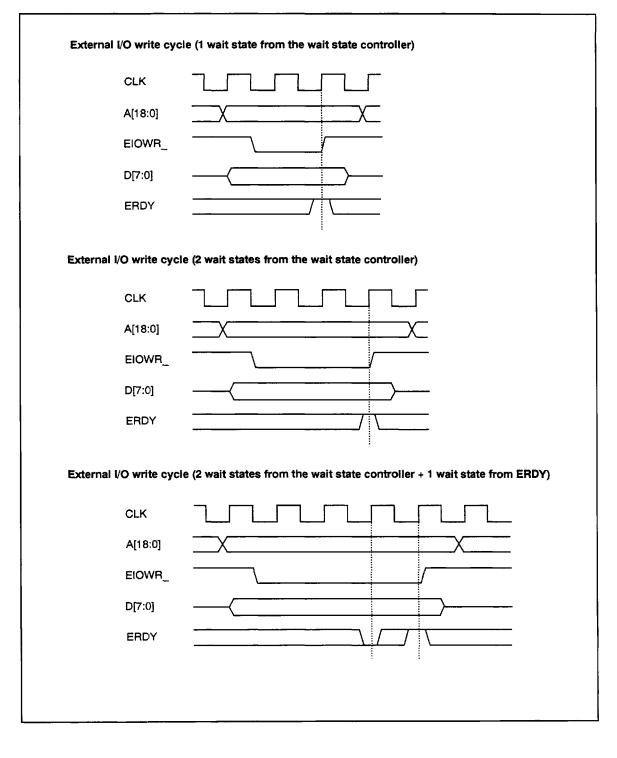

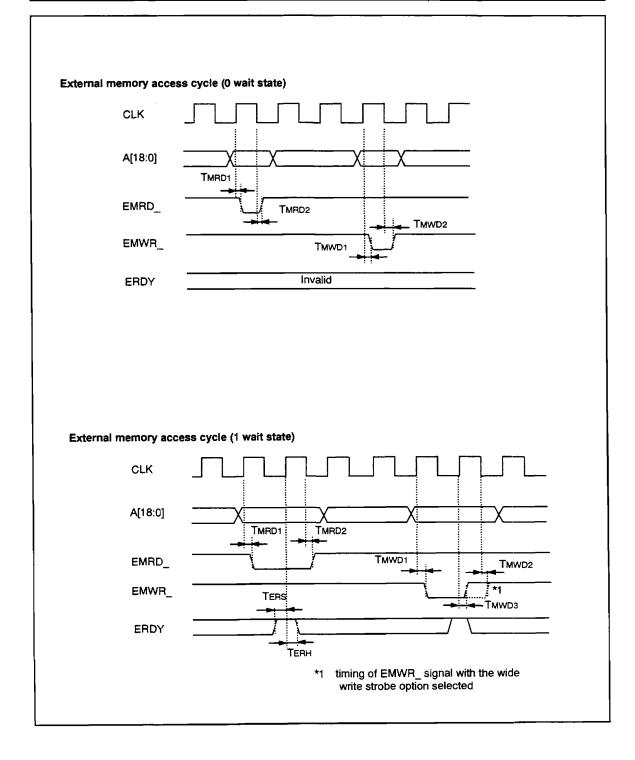

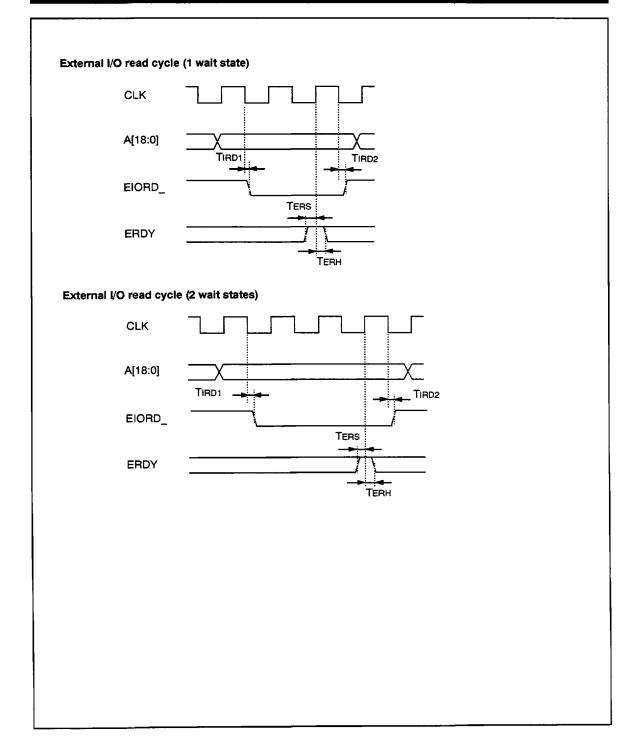

The KL5C8012's CPU core (KC82) uses synchronous system bus. Its internal I/Os and high speed RAMs include a bus interface suitable for the KC82's synchronous bus so that they are connected directly. When connecting I/O and memory to KL5C8012, it is required to convert KC82's synchronous bus signals to asynchronous bus signals which can be input to ordinary memories. For this purpose KL5C8012 contains a circuit (external bus interface unit), which outputs Read/Write signals (EMRD, EMWR, EIORD, EIOWR) appropriate for external asynchronous buses. Unlike Read/Write signals of internal bus cycle on the synchronous bus, these Read/Write signals of external bus cycle are strobe signals which can be directly connected to external memories. In this Manual the KC82's synchronous bus is referred to as internal bus cycle and the external asynchronous bus converted by the external bus interface unit as external bus cycle.

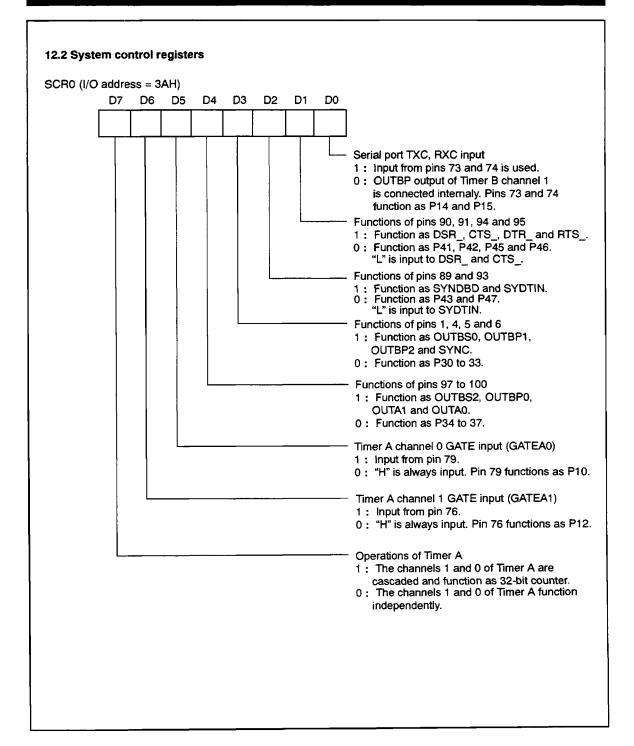

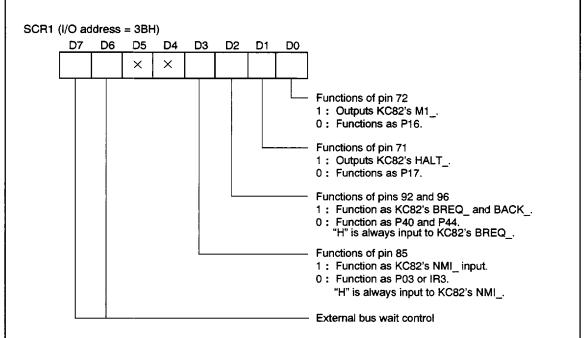

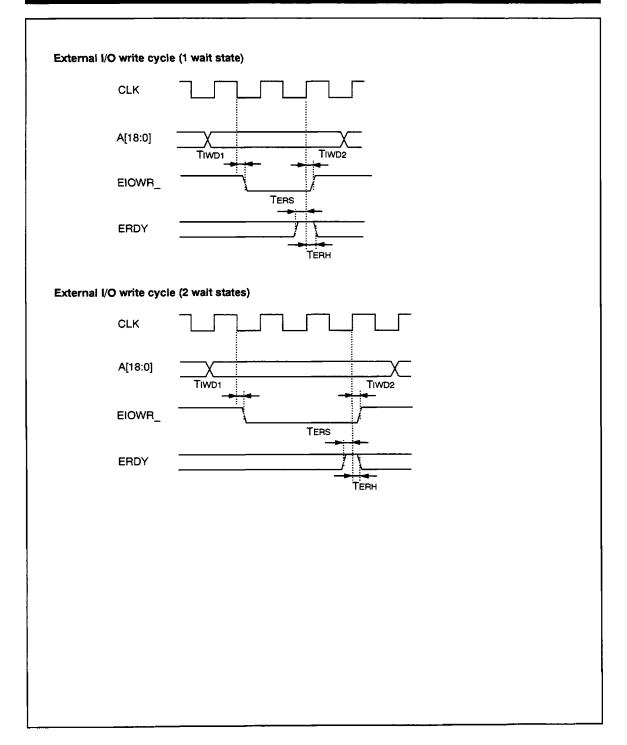

All bus cycles in the figures of the chapter "KC82 CPU" are shown in terms of internal bus cycle, that is, the operations of KC82 in that chapter are described as bus cycles inside KL5C8012 are described. Therefore, a wait state may be inserted by the external wait input or wait state controller when accessing external memories or I/Os in the same operations as shown in that chapter. Refer to the chapter "External Bus Interface Unit" for more information on external bus cycle. The external bus interface unit contains a wait state controller to enable an efficient connection with external memories. When accessing external memory or I/ O, this controller automatically inserts wait states according to two bits of SCR1 (System Control Register 1), and generates various external accesses such as external memory access (0 wait state), external memory access (1 wait state), external I/O access (1 wait state), and external I/O access (2 wait states). The controller is designed to connect two kinds of memories with different access time efficiently, such as high speed SRAM and EPROM, by controlling 1MB internal physical memory divided in two. Internal memory access is always executed in the internal memory cycle (Owait state) regardless of the SCR1 setting. It should be noted that a external wait signal (ERDY) is ignored in the external memory access (0 wait state).

In addition to SCR0 and SCR1, two external inputs (MODE[1:0]) are provided to set the mode. When MODE[1] = 0 and MODE[0] = 1 are selected and a Bug Finder adapter is connected to the external pin BFSIO, our simple debugging tool (Bug Finder) is started just after reset. If RAM is connected in place of external ROM, a program can be downloaded from a personal computer to the RAM and debugging operation can be performed on this RAM just like an ICE.

### KL5C80A12

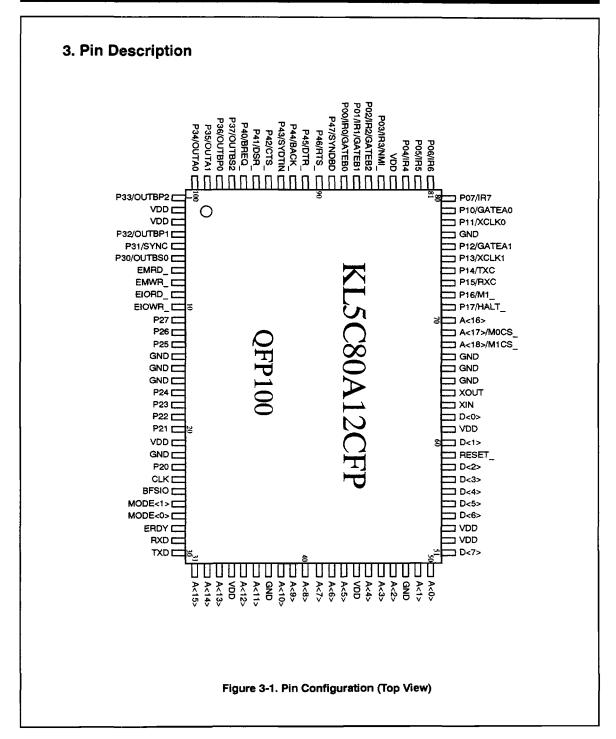

The KL5C8012 pins are divided into two groups, dedicated pins and multiplexed pins. Please see the Table 3-1 for the dedicated pins. The pins in the Table 3-2 are multiplexed with parallel port pins in the Table 3-3. For more information on multiplexing refer to the Pin Configuration. All input/output pins and 3-state output pins (A[15:0], EMRD\_, EMWR\_, EIORD\_, and EIOWR\_) and some input pins are provided with internal pull-up resistors.

| pin name    | 1/0                       | description                                                                                                             |

|-------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------|

| GND         | power                     | supply Connect 0V.                                                                                                      |

| VDD         | power                     | supply Connect 5V.                                                                                                      |

| EMRD_       | 0                         | External memory read signal. This signal is obtained by converting the KC80'                                            |

|             |                           | internal bus signal MRD_ for external bus by the external bus interface unit                                            |

| EMWR_       | 0                         | External memory write signal. This signal is obtained by converting th                                                  |

|             |                           | KC80's internal bus signal MWR_ for external bus by the external bus inter                                              |

|             |                           | face unit.                                                                                                              |

| EIORD_      | 0                         | External I/O device read signal. This signal is obtained by converting th                                               |

|             |                           | KC80's internal bus signal IORD_ for external bus by the external bus inter                                             |

|             |                           | face unit.                                                                                                              |

| EIOWR_      | 0                         | External I/O device write signal. This signal is obtained by converting th                                              |

|             |                           | KC80's internal bus signal IOWR_ for external bus by the external bus inter                                             |

|             | -                         | face unit.                                                                                                              |

| CLK         | 0                         | Outputs the internal clock generated by crystal oscillator to external circuit.                                         |

| BFSIO       | I/O                       | Dedicated port for Bug Finder debugging tool. Leave open when the Bu                                                    |

|             |                           | Finder is not used.                                                                                                     |

| MODE[1:0]   | 1                         | Input for setting the mode. Sets the KL5C8012's operation mode.                                                         |

| ERDY        | 1                         | External wait request input.                                                                                            |

| A[16:0]     | 0                         | Address output. CPU's A[16:0] are connected.                                                                            |

| D[7:0]      | 1/0                       | External data bus.                                                                                                      |

| RESET_      |                           | Reset input. The circuit is reset when this signal goes "L".                                                            |

| XIN         | For crystal<br>oscillator | Connects an external crystal oscillator to the built-in clock generator. Use                                            |

|             | Coomator                  | clock of twice the system clock frequency. Input a clock of twice the system                                            |

| XOUT        | Ear an intel              | clock frequency when a crystal oscillator is not used.                                                                  |

| X001        | For crystal<br>oscillator | Connects an external crystal oscillator to the built-in clock generator. Use clock of twice the system clock frequency. |

| A[17]/M0CS_ | 0                         | CPU address output A[17] or external ROM chip select output (address                                                    |

| A[17]/MOCS_ | 0                         | 00000H ~ 1FFFFH).                                                                                                       |

| A[18]/M1CS_ | 0                         | CPU address output A[18] or external RAM/ROM chip select output (address                                                |

|             |                           | = E0000H ~ FFDFFH).                                                                                                     |

| RXD         |                           | Receive data input of USART. Serial receive data is input. Receive data                                                 |

|             | <sup>.</sup>              | sampled at the rising edge of RXC according to the set baud rate.                                                       |

### **Table 3-1. Dedicated Pins**

## KL5C80A12

| pin name | 1/0 | description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXD      | 0   | Transmit data output of USART. Transmit data is output serially. Transmit data is output in synchronization with the falling edge of TXC according to the serial rate. If a send break command (sbrk= '1') is entered, the TXD output forced to be masked in "L" state (break state). The break state continues und a break clear command (sbrk= '1') is entered, and in the meantime the receive buffer, TXRDYPIN and TXEMPTY outputs function according to the initial set character length at the same timing as ordinary characters are sent. Whe CTS_= "L" and send is enabled (txen= '1'), transmit data can be output. CTS_= "H" or send is disabled (txen= '0') during data transfer, it is placed is marking state when there is no data to be sent. |

| pin name      | 1/0 | description                                                                   |

|---------------|-----|-------------------------------------------------------------------------------|

| IR7~0         | 1   | External interrupt input levels 7 to 0. For more information see Chapter 6.   |

| XCLK1         | 1   | External counter clock input to the Counter A channel 1. For more information |

|               |     | see Chapter 8.                                                                |

| XCLK0         | 1   | External counter clock input to the Counter A channel 0. For more information |

|               |     | see Chapter 8.                                                                |

| GATEA1        | 1   | GATE input to the Counter A channel 1. For more information see Chapter 8.    |

| GATEA0        | I   | GATE input to the Counter A channel 0. For more information see Chapter 8.    |

| GATEB2        | 1   | GATE input to the Counter B channel 2. For more information see Chapter 9.    |

| GATEB1        | I   | GATE input to the Counter B channel 1. For more information see Chapter 9.    |

| GATEB0        | 1   | GATE input to the Counter B channel 0. For more information see Chapter 9.    |

| OUTA1         | 0   | OUT output of the Counter A channel 1. For more information see Chapter 8.    |

| OUTA0         | 0   | OUT output of the Counter A channel 0. For more information see Chapter 8.    |

| OUTBS2        | 0   | Strobe output of the Counter B channel 2. For more information see Chapter 9  |

| OUTBS0        | 0   | Strobe output of the Counter B channel 0. For more information see Chapter 9  |

| OUTBP2        | 0   | Pulse output of the Counter B channel 2. For more information see Chapter 9.  |

| OUTBP1        | 0   | Pulse output of the Counter B channel 1. For more information see Chapter 9.  |

| <b>OUTBP0</b> | 0   | Pulse output of the Counter B channel 0. For more information see Chapter 9   |

| SYNC          | 0   | Synchronous output of the Counter B's prescaler. For more information se      |

|               |     | Chapter 9.                                                                    |

| HALT          | 0   | HALT signal output.                                                           |

|               |     | Active Low. This signal indicates the CPU executes HALT instruction and is i  |

|               |     | HALT status. The CPU resumes from the HALT status by receiving active NMI     |

|               |     | INT_ or reset. During HALT status, the CPU contiguously executes NO           |

|               |     | instructions.                                                                 |

#### Table 3-2. Pins Multiplexed with Parallel Ports

| pin name | 1/0 | description                                                                     |

|----------|-----|---------------------------------------------------------------------------------|

| M1_      | 0   | M1 cycle output.                                                                |

|          |     | Active Low. This signal indicates current machine cycle is opcode fetc          |

|          |     | cycle of current executing instruction. (During execution of two-byt            |

|          |     | instruction, "L" is output continuously.)                                       |

| BACK_    | 0   | Bus Acknowledge output.                                                         |

|          |     | This signal indicates that the CUP released the bus for external bus maste      |

| BREQ_    | 1   | Bus request input. Active Low.                                                  |

|          |     | When this signal goes active, the address bus and data bus go to hig            |

|          |     | impedance state after completion of current instruction execution. This sig     |

|          |     | nal has higher priority than NMI_ and INT                                       |

| NMI_     | 1   | Non-Maskable interrupt input. Falling edge trigger.                             |

|          |     | This input accepts the non-maskable interrupt. The priority of this input       |

|          |     | higher than maskable interrupt but lower than BREQ As soon as current           |

|          |     | instructions execution is completed, it jumps to 0066H and executes the         |

|          |     | interrupt service routine regardless of the status of interrupt enable flag.    |

| RXC      | 1   | Receiver clock input of USART. This clock input controls the baud rate          |

|          |     | when data is read or received from the RXD input.                               |

| тхс      | 1   | Transmitter clock input of USART. This clock input controls the baud rate       |

|          |     | when data is sent from the TXD output.                                          |

| SYNDBD   | 0   | Sync detect/break detect signal output of USART.                                |

|          |     | This signal goes "L" after reset, but it has different functions depending of   |

|          |     | modes. If it is programmed to the internal sync detect of the sync mode,        |

|          |     | goes "H" when a sync character is received and detected after issuing a         |

|          |     | Enter Hunt command. It is set to "H" at the center of final bit of the syr      |

|          |     | character (at the center of final bit of the second sync character in the t     |

|          |     | sync mode, or at the center of parity bit when parity is enabled). Then it      |

|          |     | reset to "L" by status read. If it is programmed to the external sync deter     |

|          |     | of the sync mode, it goes "H" when SYDTIN= "H" is detected at RXC= "H           |

|          |     | As with the internal sync detect, it is reset to "L" by status read. In the asy |

|          |     | chronous mode, it is used as the output pin to indicate that a break sign       |

|          |     | is detected. When "L" of more than two character data blocks (start bit, pa     |

|          |     | ity bit and stop bit) is received from the RXD pin, it is regarded as a brea    |

|          |     | signal and this signal goes "H". When "H" is received from the RXD pin,         |

|          |     | goes "L".                                                                       |

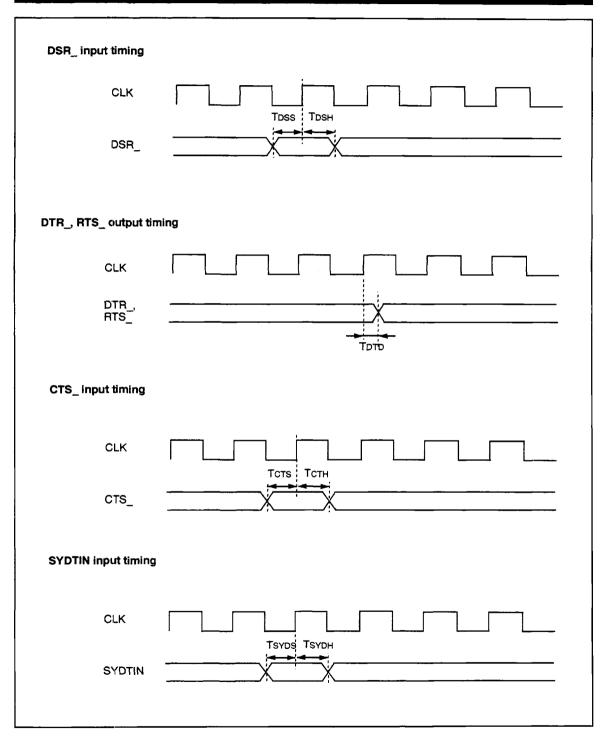

| RTS_     | 0   | Request-to-send signal output of USART.                                         |

|          |     | It is usually used to output a request-to-send signal to a modem, but can it    |

|          | 1   | used as general-purpose output port.                                            |

## KL5C80A12

| pin name | 1/0 | description                                                                          |

|----------|-----|--------------------------------------------------------------------------------------|

| DTR_     | 0   | Data terminal ready signal output of USART. It is usually used to output a data      |

|          |     | terminal ready signal to a modem, but can be used as general-purpose output port.    |

| SYDTIN   | ł   | External sync detect signal input of USART. When it is programmed to the exter-      |

|          |     | nal sync detect of the sync mode and "H" is input to this pin during RXC= "H",       |

|          |     | the USART exits the Enter Hunt mode and starts sampling of receive data at the       |

|          |     | rising edge of the next RXC. If an Enter Hunt command was not executed, it           |

|          |     | does not receive data. "H" input must be longer than one cycle of RXC. This pin      |

|          |     | does not function in the internal sync detect mode.                                  |

| CTS_     | I   | Clear-to-send signal input of USART. A transmission request signal to USART          |

|          |     | is input. transmission is being requested while it is "L". It is usually used as     |

|          |     | clear-to-send signal to the modem. If transmission is enabled (txen= '1'; the bit    |

|          |     | 0 of command register is set to '1') and there is data to be sent, data is sent from |

|          |     | the TXD when this input is "L". When this input goes "H", all data in the buffer is  |

|          |     | sent and then the TXD goes into the marking state.                                   |

| DSR_     | I I | Data set ready signal input. It is usually used as data set ready signal to check    |

|          |     | the status of modem ("L" = modem enabled to send, "H" = disabled to send), but       |

|          |     | can be used as general-purpose input port.                                           |

### Table 3-3. Parallel Port Pins

| pin name | 1/0 | description                                                                |

|----------|-----|----------------------------------------------------------------------------|

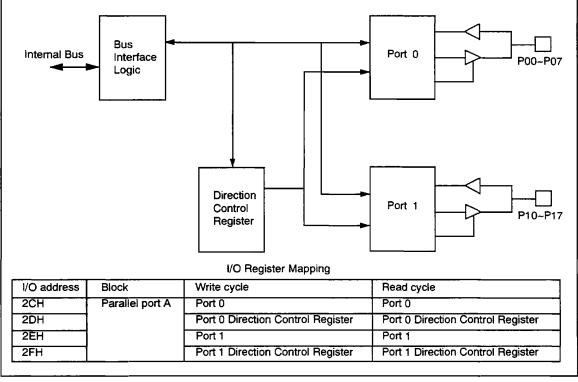

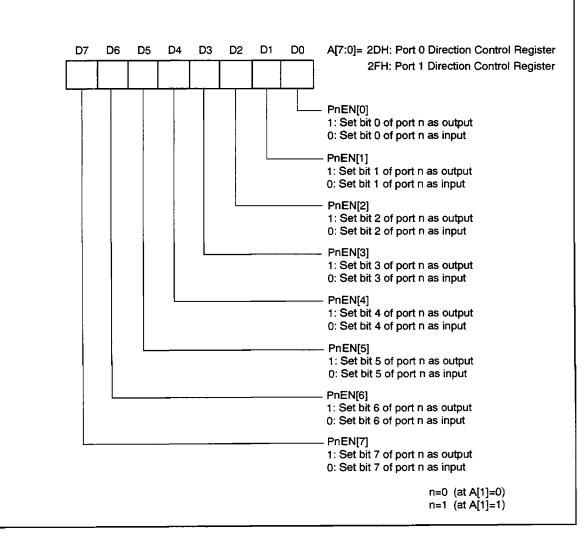

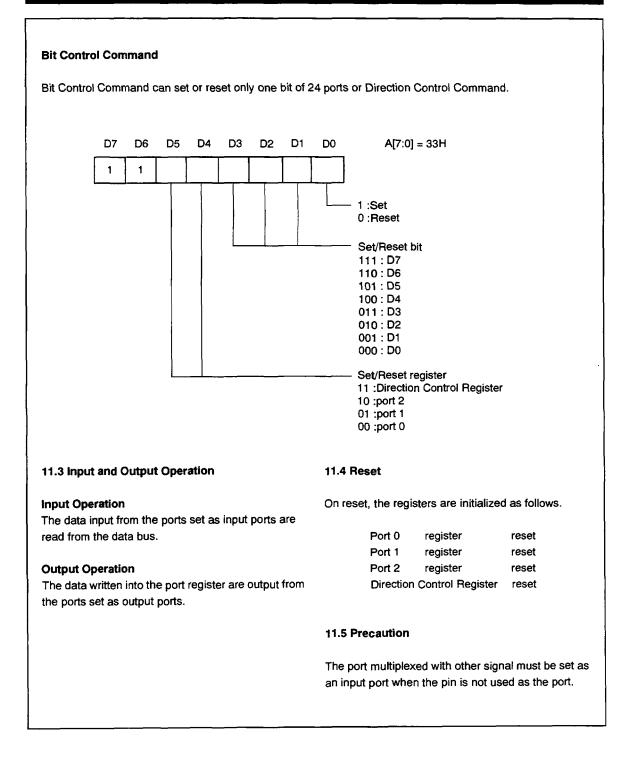

| P00~P07  | I/O | P0 port of the parallel port block A. For more information see Chapter 10. |

| P10~P17  | I/O | P1 port of the parallel port block A. For more information see Chapter 10. |

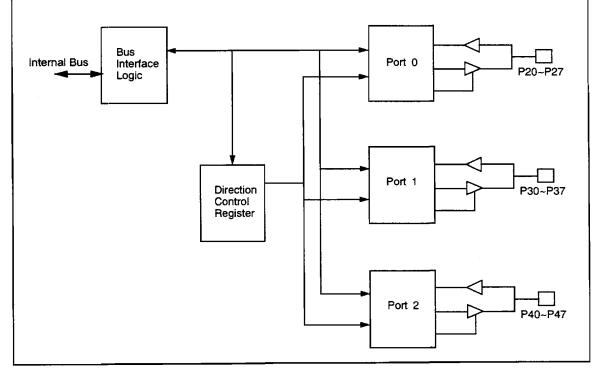

| P20~P27  | 1/0 | P0 port of the parallel port block B. For more information see Chapter 10. |

| P30~P37  | I/O | P1 port of the parallel port block B. For more information see Chapter 10. |

| P40~P47  | I/O | P2 port of the parallel port block B. For more information see Chapter 10. |

### KL5C80A12

### 4. External Bus Interface Unit

#### 4. 1 General description

The80A12 external bus interface unit includes a wait state controller, and converts internal bus cycles to external bus cycles inserting specified number of wait states. The number of wait states is specified by bits 6 and 7 of SCR1 (System Control Register 1). This unit works only at the access of external I/O and external memory. The Read/Write signal of external bus stays "H" at the access of internal I/Os and the internal high speed RAM.

external bus wait control

|    | external memory (00000 - 7FFFF) |         | external memory (80000 -FFDFF) |  | external I/O |         |    |     |             |

|----|---------------------------------|---------|--------------------------------|--|--------------|---------|----|-----|-------------|

| 00 | 1 w                             | ait sta | te                             |  | 1 w          | ait sta | te | 2 % | vait states |

| 01 | 1                               | "       | *                              |  | 1            | "       | *  | 2   | "           |

| 10 | 1                               | "       |                                |  | 0            | "       |    | 1   | "           |

| 11 | 0                               |         |                                |  | 0            | "       |    | 1   | 11          |

\* wide write strobe option

The KL5C80A12's CPU core (KC82) uses synchronous system bus. Its internal I/Os and high speed RAMs include a bus interface suitable for the KC82's synchronous bus so that they are connected directly. When connecting I/O and memory to KL5C80A12, the external bus interface unit converts KC82's synchronous bus Read/Write signals (MRD\_, MWR\_, IORD, IOWR) to external asynchronous bus Read/ Write signals (EMRD\_, EMWR\_, EIORD\_, EIOWR\_) described later. The external bus interface unit includes a wait state controller, and converts internal bus cycles to external bus cycles inserting specified number of wait states. The number of wait states is specified by bit 6 and 7 of SCR1. The external bus interface unit adds a wait request from the built-in wait state controller to an external wait request input

from ERDY, and send them to the CPU.

This controller is designed to connect two kinds of memories with different access time efficiently, such as high speed SRAM and EPROM, by controlling 1MB internal physical memory divided in two. Internal memory access is always executed in the internal memory cycle (0 wait status) regardless of the SCR1 setting. It should be noted that a external wait signal (ERDY) is ignored in the external memory access (0 wait status).

### KL5C80A12

### 5. KC82 CPU

### 5.1 General description

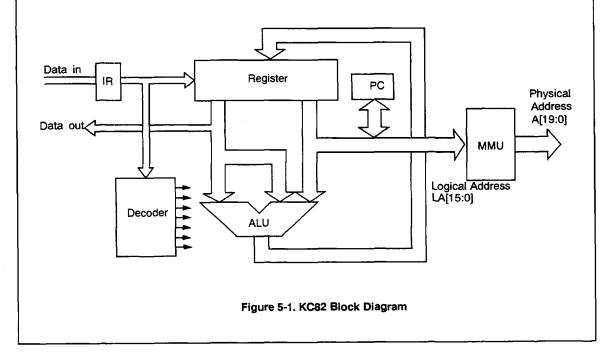

KC 82 is the CPU core which is object compatible with Zilog's Z80 CPU with MMU that extends the address space up to 1M byte. But its internal circuit is totally different. KC82 has RISC like architecture, 16 bit internal data path and synchronous bus, and offers higher performance than typical 16 bit CPU.

### Feature

KC82 has the following features:

1)KC82 executes instructions 4 times faster than Zilog Z80 CPU at the same clock rate.

| ex: instruction | Z80       | KC82    |

|-----------------|-----------|---------|

| LD r, r'        | 4 clocks  | 1 clock |

| ADD HL, ss      | 11 clocks | 1 clock |

2)With interface macro cell, it can be used with the Z80 peripheral and ordinary RAMs.

3) 158 instructions and fully compatible with the Z80 CPU at object code level.

### 5.2 Block Diagram

The following figures 5-1 has the block diagram of the KC82.

| signal name | I/O | description                                                                |

|-------------|-----|----------------------------------------------------------------------------|

| MRD         | 0   | Memory read. Active Low.                                                   |

|             |     | This signal goes active while reading data from memory.                    |

| MWR_        | 0   | Memory write. Active Low.                                                  |

|             |     | This signal goes active while writing data to memory.                      |

| IORD        | 0   | I/O read. Active Low.                                                      |

|             |     | This signal goes active for minimum of two clock cycles while reading      |

|             |     | data from I/O device.                                                      |

| IOWR_       | 0   | I/O write. Active Low.                                                     |

|             |     | This signal goes active for minimum of two clock cycles while writing      |

|             |     | data to I/O device.                                                        |

| WAIT_       | 1   | Wait input. Active Low.                                                    |

| _           |     | This signal is to notify the CPU that the peripherals or memory is not     |

|             |     | ready for data transfer. While this signal stays active, the CPU is        |

|             |     | placed in the wait state. This input is connected to the external pin.     |

|             |     | ERDY through the wait state controller in the external bus interface       |

|             |     | unit.                                                                      |

| INT_        | 1   | Maskable interrupt input. Active Low.                                      |

|             |     | This input accepts the interrupt from peripherals. If the interrupt enable |

|             |     | flag of the CPU is set, and BREQ_ is inactive, the CPU completes the       |

|             |     | execution of the current instruction, and starts interrupt service. This   |

|             |     | input is connected to the INT_ output of the interrupt controller.         |

| IACK_       | 0   | Interrupt Acknowledge output. Active Low.                                  |

|             |     | This signal indicates that the CPU acknowledges the interrupt              |

|             |     | requesting interrupt vector or instruction from the I/O device. It stays   |

|             |     | active at minimum of two clock cycles. This output is connected to the     |

|             |     | interrupt controller. The CPU reads the interrupt vector synchronously     |

|             |     | with this signal.                                                          |

| EOI_        | 0   | End of interrupt signal output. Active Low.                                |

|             | }   | This signal goes active at refetch of RETI instruction (code ED 4D)        |

|             |     | This output is connected to the interrupt controller.                      |

| LA [15:0]   | 0   | Logical Address output.                                                    |

|             | 1   | It outputs the physical address A[19:0] expanded by the MMU in KC82.       |

### KL5C80A12

### 5.4 Register architecture 5.4.1 Special purpose registers Program Counter (PC)

Program Counter holds the address of the next instruction. The next instruction is fetched from memory address Program Counter indicates.

#### Stack Pointer (SP)

Stack Pointer holds the current top address of stack area in RAM.

#### Index registers (IX, IY)

Index registers hold base address for indexed addressing. There are two index registers. The one is IX, and the other IY.

#### Interrupt page address register (I)

Interrupt page address register holds indirect upper 8 bit address for indirect jump in Mode 2.

#### Memory refresh register (R)

This register automatically increments by one on instruction fetch. Bit D7 of this register will not change by increments on D6-D0.

#### Accumulator (A, A'), and Flag register (F, F')

There are two 8 bit accumulators (A, A') and two flag registers. Accumulator holds the result of arithmetic and logical operation. Flag register holds status of 8 bit or 16 bit operation. The instruction, EX AF, AF' exchanges A, F and A', F'.

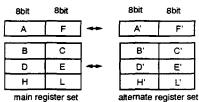

#### 5.4.2 General purpose registers

There are two sets of general purpose registers. Each of them can be used as an 8 bit register independently (B, C, D, E, H, L or B', C', D', E', H', L'). Paired registers (BC, DE, HL, BC', DE' and HL') can be used as a 16 bit register. The instruction, EXX exchanges B,C, D, E, H, L and B',C', D', E', H', L'.

| 800 | 800 |

|-----|-----|

| A'  | F'  |

| B'  | C,  |

| D'  | E,  |

| H,  | Ľ   |

|     |     |

|   | 16bit |   |

|---|-------|---|

|   | IX    |   |

|   | ΙY    |   |

| 1 |       | R |

|   | SP    |   |

|   | PC    |   |

Special purpose registers

#### Figure 5-3. KC82 register architecture.

### KL5C80A12

### 5.5 Flags

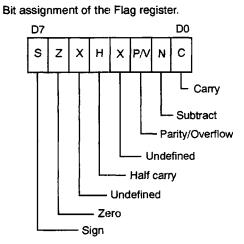

#### Figure 5-4. Flag register

The function of each bit in the Flag register is defined as below.

#### Carry flag (C)

Carry flag is set by carry produced by Accumulator from the MSB at execution of add instructions, subtract instructions, shift and rotate instructions, etc.

#### Zero flag (Z)

Zero flag is set if the operation result is zero, when add instructions, subtract instructions, logical instructions including INC, DEC, DAA instructions. This also occurs on block I/O instructions, rotate and shift instructions, string search instructions, bit test instructions and data detection of block search instructions.

#### Sign flag (S)

Sign flag is set when the result of sign number operations is negative.

#### Parity/Overflow flag (P/V)

Parity/Overflow flag has two functions. It indicates the parity on logical operations, and also the overflow on arithmetic operations. The overflow means that the

content of Accumulator is less than -128 in 2's complement, or larger than 127. It is also set by block search instructions, block I/O instructions, LD A, R instruction and LD A, I instruction.

#### Half carry flag (H)

Half carry flag is set when the carry or borrow from lower 4 bits is produced.

#### Subtract flag (N)

Subtract flag is set on subtract instructions. KC82 checks if the previous instruction is addition or subtraction with this flag on DAA instruction.

### KL5C80A12

#### 5.6 Functional description and timing

In this section, functional description and timing are described. Note that the address bus in the timing diagrams is the logical address, LA[15:0], to describe easily. The logical address LA[15:0] is converted to the physical address by MMU.

All bus cycles are described using the internal bus. See the chapter 4 for more information of the external bus.

#### 5.6.1 Basic operation (Instruction cycle)

Basic operation of the KC82 can be divided into the following 5 cycles.

1)Opcode fetch cycle - Fetches opcode of an instruction from memory.

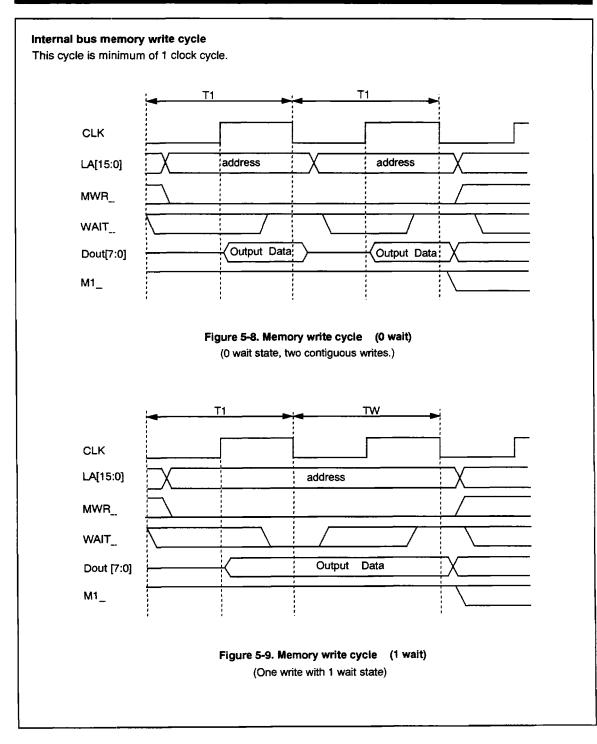

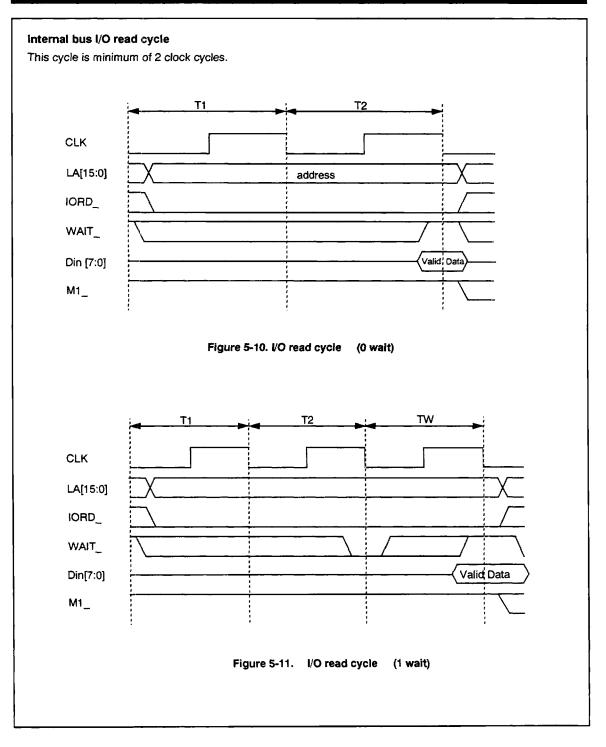

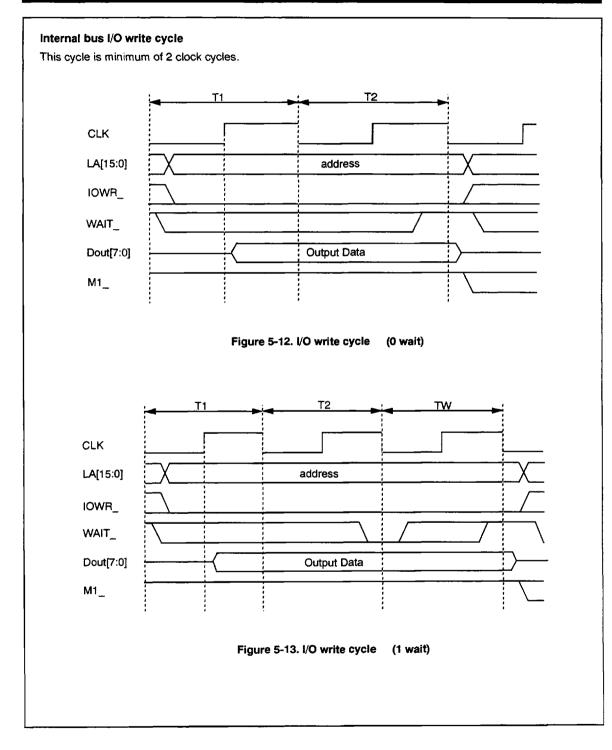

2)Memory read cycle - reads data from memory3)Memory write cycle - writes data to memory.4)I/O read cycle - reads data from I/O device

5)I/O write cycle - writes data to I/O device

Follows are the description of the each machine cycles.

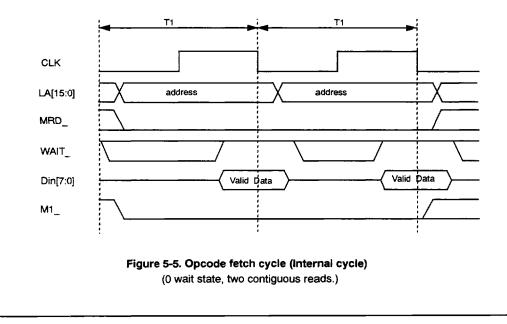

#### Opcode fetch cycle

As shown figure 5-5, KC82 fetches one byte of an instruction in a clock cycle unless there is a wait. During this cycle, MRD\_ and M1\_ go active. The difference between memory read cycle is whether if M1\_ goes active or not. This cycle is minimum of one clock cycle and appears at the end of the instruction execution sequence.

### KL5C80A12

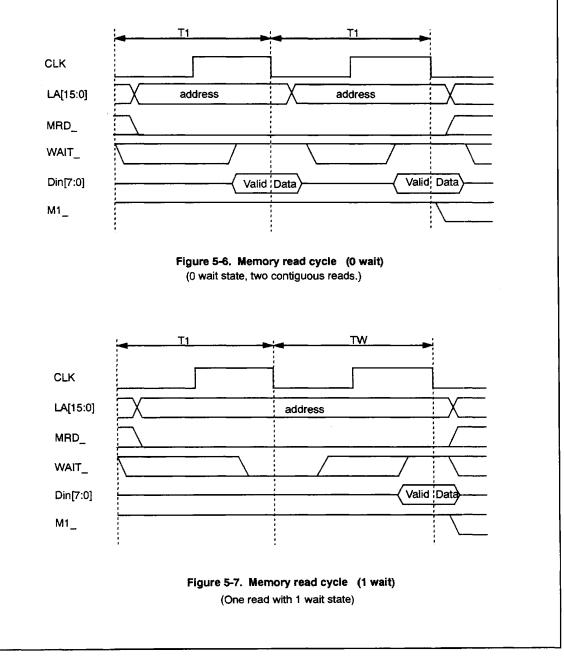

### Internal bus memory read cycle

The difference between opcode fetch cycle is whether if M1\_ goes active or not. This cycle is minimum of 1 clock cycle.

### KL5C80A12

#### Instruction Prefetch cycle

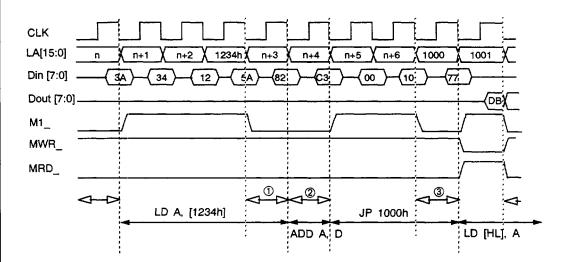

The KC82 has the prefetch cycle at the end of instruction execution cycle all the time. Figure5-15 shows that KC82 executes the instruction sequence indicated in Figure5-14 as an example.

✓ (referred as "arrow" hereinafter) in the Figure 5-15 denotes the prefetch cycle. The arrow ① part prefetches the instruction at n+3 (ADD A,D), the arrow ② part is for prefetching instruction at n+4 (opcode of JP instruction, C3h), the arrow ③ part is for prefetching 77h at 1000h (LD [HL], A instruction). As shown, these cycles appear at the end of execution of current instruction.

| address | mnemonic      | code     |

|---------|---------------|----------|

| n       | LD A, [1234h] | 3A 34 12 |

| n+3     | ADD A, D      | 82       |

| n+4     | JP 1000h      | C3 00 10 |

| 1000h   | LD [HL], A    | 77       |

| 1234h   | •             | 5A       |

Figure 5-14. Source code for Figure 5-15

Figure 5-15. Prefetch cycle ( <------> denotes the prefetch cycle. Assumes memory location 1000h has 77h, memory location 1234h has 5Ah, and D register has 81H.)

### KL5C80A12

## Special case for prefetch. (Discard of the prefetched instruction)

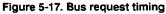

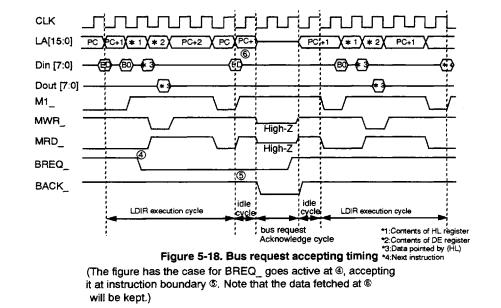

For example, under normal condition, the prefetched instruction, at address 1000h, data 77h at ③ in Figure 5-15 on execution of the instruction, JP 1000h is held and execute correctly. However, on interrupt the prefetched instruction will be discarded and refetch on return from an interrupt service routine. On interrupt recognition, PC is decremented by one before saved onto stack. On RETI or RETN instruction the PC will be loaded with the address of the discarded instruction. Figure 5-19 has the timing diagram for the case of receiving interrupt in mode 1 when executing LDIR instruction. In the figure, the data "EDh" prefetched at 6, is discarded and then go to interrupt service. On return, the CPU resume from the prefetch of this "EDh". For the bus request cycle, the data "EDh" prefetched at 6 prior to the bus request will be kept, and on bus release the CPU starts to prefetch from the next address to the "EDh" as shown in the Figure 5-18.

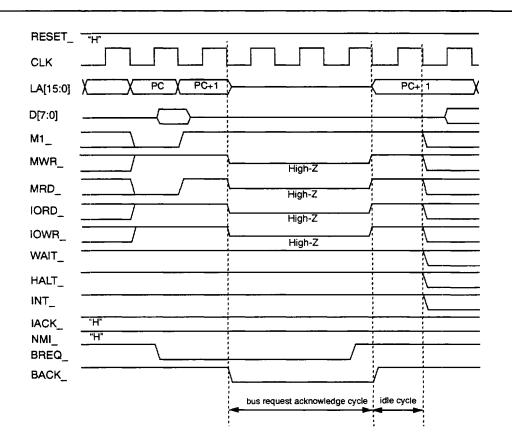

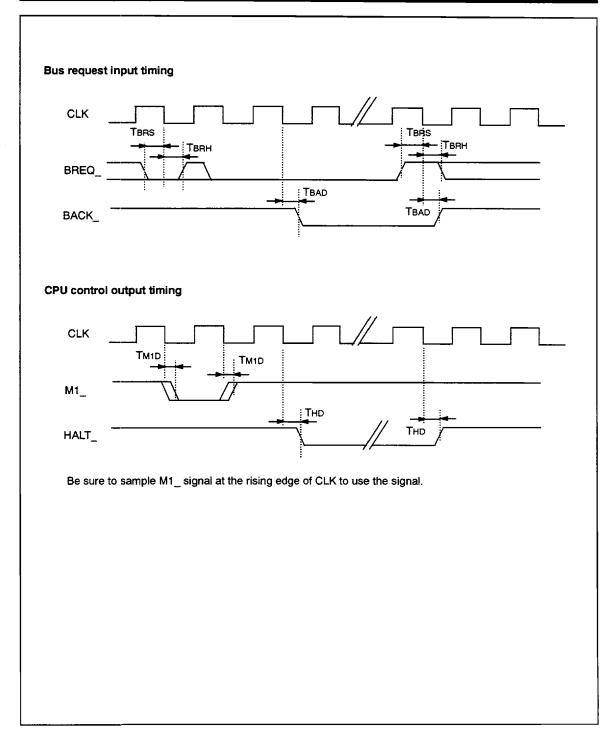

## 5.6.2 Bus release (Bus request/acknowledge cycle)

Under normal operation, the CPU holds the control of address bus, control bus (MRD\_, MWR\_, IORD\_ and IOWR\_). However, if there is an external bus request (BREQ\_="L"), address bus goes to high-impedance state, all the interrupts are disabled, BACK\_ turns to "L", and the CPU releases the bus control to the external device. By using this feature, data transfer without CPU intervention can be done. Figure 5-17 shows basic timing for the bus request cycle. This cycle continues while BREQ\_ stays "L".

Note that bus request is accepted only at the end of instructions except the instructions which have iteration, such as block transfer instructions, block search instructions and iterating IN/OUT instructions. In a special case, for the block move instructions the acceptance of a bus request occurs on every iteration of an execution cycle, not the end of the instruction. As shown in the Figure 5-18, BREQ\_ is asserted at point ④ during the execution, the bus is released at the last execution cycle of an instruction ⑤.

#### 5.6.3 Interrupt and timing

The KC82 can handle the following two kinds of interrupts.

1)maskable interrupt on INT\_

2)Non-maskable interrupt on NMI\_

2) has the higher priority over 1). If both request made simultaneously, 2) will be accepted over 1).

#### Maskable interrupt

The El instruction enables interrupts, and the DI instruction disables interrupts. The control of interrupt is implemented using two flip-flops (IFF1 and IFF2). Figure 5-16 has the state table for these flip-flops.

| events                    | IFF1 | IFF2 |                          |

|---------------------------|------|------|--------------------------|

| reset                     | 0    | 0    |                          |

| DI instruction            | 0    | 0    |                          |

| El instruction            | 1    | 1    |                          |

| INT accepted              | 0    | 0    |                          |

| NMI accepted              | 0    | -    |                          |

| RETN instruction accepted | IFF2 | -    | IFF2 is copied into IFF1 |

| LD A, I instruction       |      | -    | IFF2 is copied into P/V  |

| LD A, R instruction       |      | -    | IFF2 is copied into P/V  |

### Figure 5-16. State diagram for IFF1 and IFF2

("-" denotes remain unchanged.)

The maskable interrupt will be accepted if all of the following conditions are met:

1)Both IFF1 and IFF2 are set. (The El instruction and RETN instructions change the status of these flags after the execution of the following instruction. So if there are El instruction followed by DI instruction, the interrupt request will not be accepted.)

### KL5C80A12

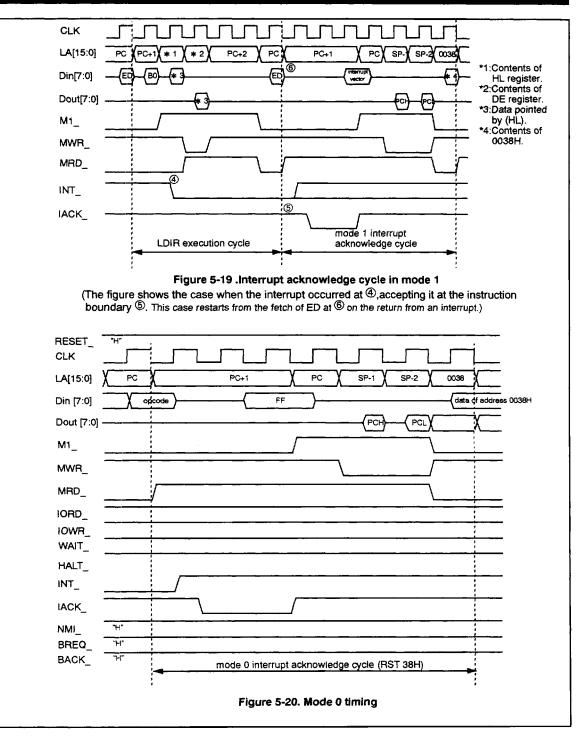

1)Mode 0

2)BREQ\_ is inactive ("H"). (When BREQ\_ goes inactive, interrupt will be accepted after execution of an instruction.)

3)No NMI\_ falling edge has been detected.

The KC82 has the dedicated signal, IACK\_ for the external devices to acknowledged that the interrupt has been accepted, while the Z80 CPU signals using M1\_ and IORQ\_ combination for that purpose.

#### Maskable Interrupt modes

The KC82 has the following three different interrupt handling modes, and interrupt sequence is different by each modes. The following descriptions are the operations in each mode. Use the mode 2 usually. This is the default mode and set to this on reset automatically.

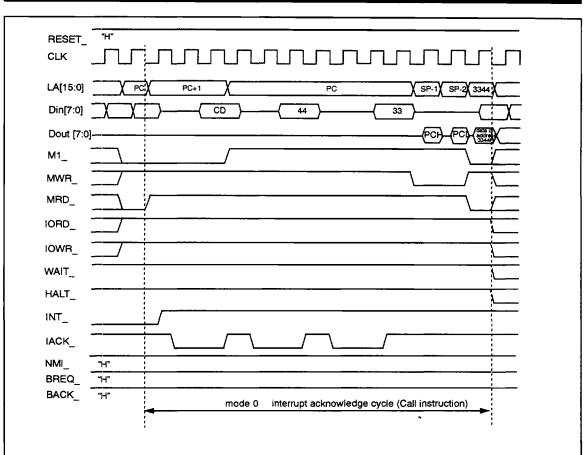

Also, executing "IM 0" instruction sets the CPU to this mode. In this mode, the CPU executes the instruction read during interrupt acknowledge cycle.

Usually the instruction to be used in this mode is RST instructions, or CALL instruction.

Figure 5-20 and 5-21 show each timing for RST and CALL instructions. For the all interrupt modes, if  $INT_{_}$  goes active during execution of a mode change instruction (IM 0~2), the new mode become effective right after these instructions.

### KL5C80A12

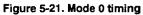

#### 2)Mode 1

The "IM 1 instruction" sets the CPU in this mode. In this mode, the CPU saves the contents the PC (Program Counter) onto the stack, ignores the data read during the interrupt acknowledge cycle, and executes "RST 38H" instruction internally. Figure 5-22 has the timing for Mode 1 interrupt.

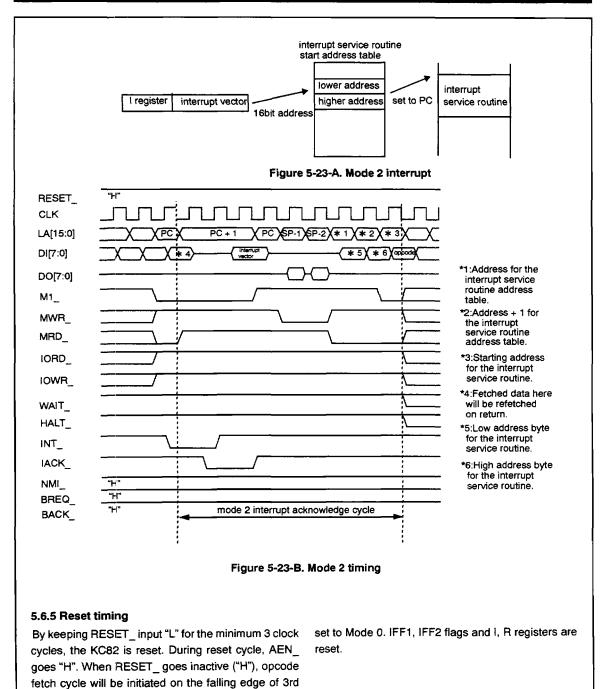

#### 3)Mode 2

The "IM 2 instruction sets" the CPU to this mode. In this mode, as shown in the Figure 5-23-A, the 8-bit wide vector with 0 in LSB read during the interrupt acknowledge cycle as a lower byte, and the content of the I register as a upper byte form up a pointer which points an entry in a table of address for the interrupt service routines. After forming up the 16-bit address, the CPU fetches the table location and gets the start address, saves the return address onto the stack, then jumps to the service routine. Figure 5-23-B has the timing diagram for Mode 2 interrupt acknowledge cycle.

#### Timing on interrupt acceptance

The Figure 5-19 show the interrupt acknowledge timing. In this figure, an interrupt is accepted during block move instruction. ④ shows that when an interrupt request occurs, the interrupt will not be accepted until the prefetch cycle of the last instruction, ⑤. In this case, the data "EDh" fetched at ⑥ will not be kept by the CPU, and it will be refetched on the return from an interrupt.

#### Non-maskable interrupt

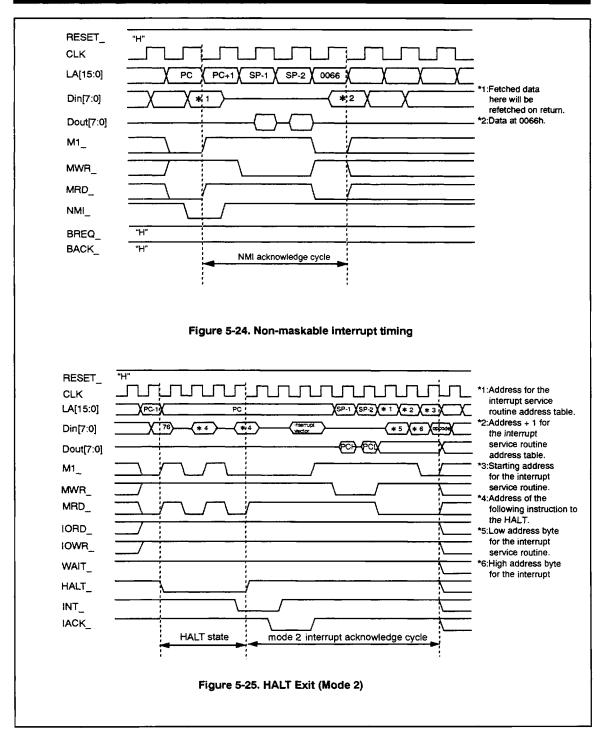

Non-maskable interrupt is an interrupt which can not be masked by software. The falling edge of the signal NMI\_ is latched internally, and checked on the clock falling edge of the last cycle of every instruction. Non--maskable interrupt takes place if BREQ\_ is inactive. If BREQ\_ goes inactive, NMI\_ will be accepted after execution of an instruction.

When a non-maskable interrupt is accepted, the CPU saves the contents of the PC onto the stack, and jumps to 0066h. Return from non-maskable service is done by "RETN" instruction. Figure 5-24 shows the timing for NMI\_acknowledge cycle.

### KL5C80A12

#### Enable/disable of interrupts

Enable/disable of an interrupt is controlled by two flip-flops - IFF1 and IFF2. Refer to Figure 5-16 on the state diagram for these flip-flops. As shown, maskable interrupt will be accepted when both IFF1 and IFF2 set to 1. After reset and execution of DI instruction maskable interrupt is disabled, because both of these flip-flops are reset. An interrupt can be accepted while both IFF1 and IFF2 are set to 1 by execution of an El instruction. The reason there are two flip-flops is to memorize the status of El/DI condition with IFF2 on acceptance a Non-maskable interrupt. For example, if both IFF1 and IFF2 are '1' (maskable interrupt is enabled) on acceptance a non-maskable interrupt, in a non-maskable interrupt acknowledge cycle IFF1 is cleared to 0 and maskable interrupts are disabled. At this stage, IFF2 still holds "1" and the content of IFF2 is copied back into IFF1 on RETN instruction so that maskable interrupts could be enabled automatically again.

### KL5C80A12

#### 5.6.4 Halt enter and exit

By executing the HALT instruction, the CPU enters into HALT cycle. In this cycle, the CPU continues to execute NOP instruction internally. The CPU exits from this cycle by either reset, or interrupts (Nonmaskable interrupt or interrupt with IFF set). Figure 5-25 shows timing for the case of acceptance an interrupt in mode 2 during HALT cycle. Then the CPU exits from the HALT cycle. HALT cycle made up with two separate bus cycles; the first cycle is idle cycle and the second cycle is opcode fetch cycle. The address lines holds the next address to the HALT instruction during this cycle. The instruction fetched during the second opcode fetch cycle will not be read by the KC82. The INT input is sampled on the falling CLK edge of the second cycle, and forces HALT back to "H".

### KL5C80A12

clock, and starts from 0000h. The interrupt mode is

### KL5C80A12

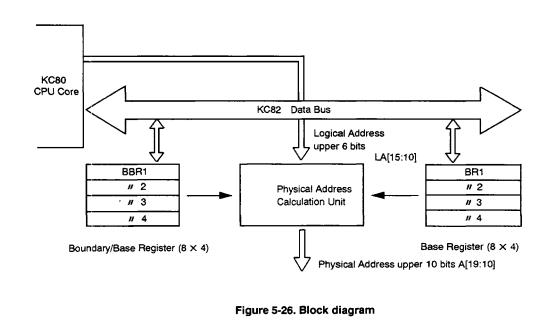

### 5.7 MMU

### 5.7.1 General description

The MMU block is the circuit which converts the KC82 16 bit logical address, LA[15:0], to 20 bit physical address, A[19:0]. However, the MMU converts addresses only in case of memory access. It does not affect addresses in case of I/O access. The MMU is consisted of the following registers and a physical address calculation unit. The operation of the physical address calculation unit is described in the later section.

| Name                 |             | Number of Bits | Read / Write |

|----------------------|-------------|----------------|--------------|

| Boundary/Base Regist | er 1 (BBR1) | 8bit           | R/W          |

| "                    | 2 (BBR2)    | "              | R/W          |

| "                    | 3 (BBR3)    | 11             | R/W          |

| "                    | 4 (BBR4)    | 8bit*          | R/W          |

| Base Register        | 1 (BR1)     | 8bit           | R/W          |

| "                    | 2 (BR2)     | "              | R/W          |

| "                    | 3 (BR3)     | "              | R/W          |

| , II                 | 4 (BR4)     | , II           | Read Only    |

### Table 5-1. Register Architecture

\*Upper 2 bit is Read Only

### KL5C80A12

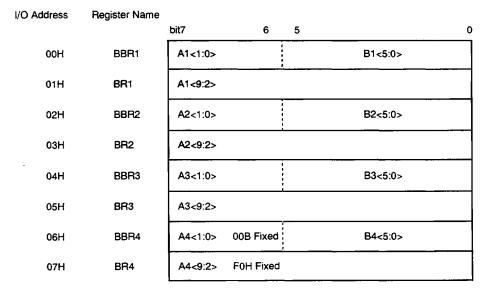

#### 5.7.2 Description of registers

Eight 8 bit registers are included in the MMU block. These 8 registers hold four 10 bit data and four 6 bit data which are necessary for the MMU block.

#### Boundary/base registers (BBR1 ~ BBR4)

The upper 2 bits of these registers (A1<1:0>  $\sim$  A4<1:0>) are used to hold base addresses in the physical address space with the 8 bits of base registers. The lower 6 bits are logical boundary addresses (B1<5:0>  $\sim$  B4<5:0>). They are used as the boundary addresses to divide the logical space into five regions. The upper 2 bits of BBR4 are fixed, and the contents don't change when data is written on it.

### Base registers(BR1 ~ BR4)

These registers compose 10 bit physical address bases (A1<9:0>  $\sim$  A4<9:0>) with the upper 2 bits of boundary/base resisters. They are used to hold base addresses in the physical address space. The content of BR4 is fixed to F0H.

## Logical boundary address and physical address base

The MMU block divides the logical address space into five regions, and each region is mapped to the physical address space. The MMU block needs five logical boundary addresses (B0 ~ B4) and five physical address bases (A0 ~ A4). The content of A0 is fixed to 000H, and that of B0 is fixed to 00H. The other data are assigned in boundary/base registers and base registers as shown in Figure 5-27.

### KL5C80A12

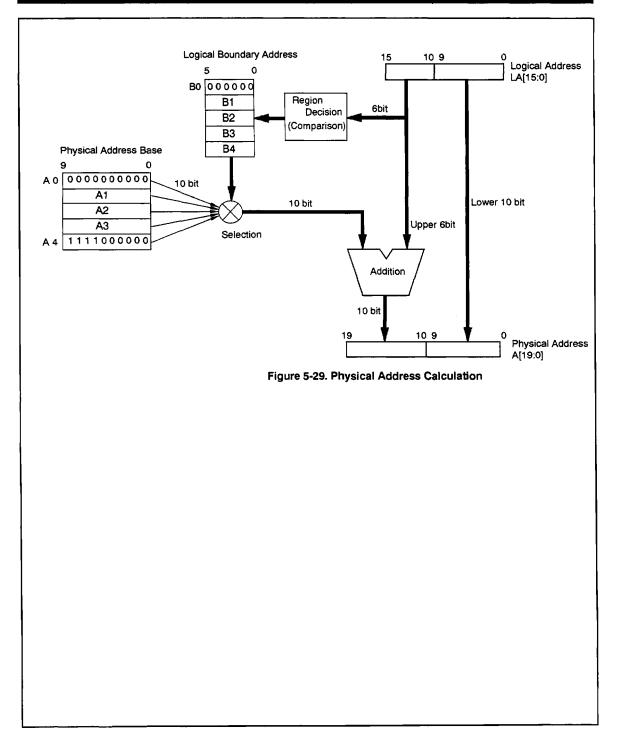

#### 5.7.3 Calculation of physical address by MMU

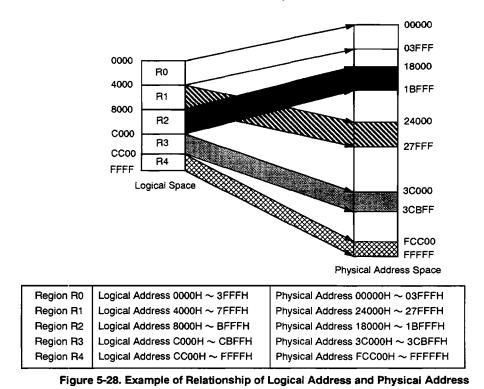

The logical address space is divided into five regions (R0 ~ R4) as shown in Figure 5-28. The five regions are decided with logical boundary address (B0<5:0> ~ B4<5:0>). The lower limit address of Rn region is (Bn+1)\*400H, and the higher limit address of Rn region is (B(n+1)+1)\*400H-1. (The R0's lower limit address is always 00000H and the R4's higher limit address is always FFFFFH.) These regions in the physical space are created by adding the physical address base (10 bits) of divided each region and the upper 6 bits of logical address. (See Figure 5-29.) The division of logical space is decided by comparison of the upper 6 bits of logical address and the logical boundary address (B0 ~ B4). Setting of 1K byte unit is possible. The lowest value of the R1 region's lower limit address is 0400H and the content of A0 is fixed to 000H. Therefore, the lowest 1K byte of logical

space (0000H ~ 03FFH), which is belong to R0 region, is always mapped to 00000H ~ 003FFH in the physical space.

An example is shown in Figure 5-28. For example, bit data are set as following;

$\begin{array}{rcl} B0 &=& 00H \mbox{ (Fixed)} \\ B1 &=& 0FH \\ B2 &=& 1FH \\ B3 &=& 2FH \\ B4 &=& 32H \\ A0 &=& 000H \mbox{ (Fixed)} \\ A1 &=& 080H \\ A2 &=& 040H \\ A3 &=& 0C0H \\ A4 &=& 3C0H \mbox{ (Fixed)} \end{array}$

The relationship of five logical regions and physical regions is followed.

### KL5C80A12

#### 5.7.4 MMU mechanism

(1) Memory space

The MMU converts the address when the CPU accesses memory space. This is divided into following cases.

1.Instruction fetch

2.Read or write to memory space by instruction

- 3.Instruction fetch to interrupt restart address

- 4.Start address table in mode 2 interrupt

- (2) I/O space

When the CPU accesses I/O space, the MMU does not convert the address and outputs the logical address. In this case, 0H is put on upper 4 bits of the address.

(3) DMA controller

When a DMA controller (KP37 etc.) is on the chip, the MMU does not convert the address which the DMA outputs. In case of KP37, a special register is necessary for each channel to assign the upper 4 bits of the physical address.

#### 5.7.5 Reset

The registers are initialized when they are reset as following.

| <b>B</b> 0 | = | 00H (Fixed)  |

|------------|---|--------------|

| <b>B</b> 1 | = | ЗFH          |

| <b>B</b> 2 | Ξ | 3FH          |

| B3         | = | 3FH          |

| <b>B</b> 4 | = | 3FH          |

| A0         | = | 000H (Fixed) |

| A1         | = | 000H         |

| A2         | = | 000H         |

| AЗ         | = | 000H         |

| A4         | = | 3C0H (Fixed) |

|            |   |              |

When they are reset, there is only R0 region in the logical address space. 64K byte of the logical address space is mapped to the lowest 64K byte in the physical address space.

#### 5.7.6 Precautions on the use of the MMU

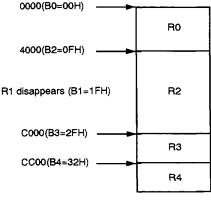

(1)When the logical boundary address is set as B0 < B1 < B2 < B3 < B4, all regions are valid. When the logical boundary addresses are set in opposite order or equally, the region whose region number is bigger is valid. The region whose region number is smaller is disappears. For example, if B1 >= B2 is set, R1 region disappears.

Figure 5-30. Example when  $B1 \ge B2$

## KL5C80A12

(2)When data is written in MMU registers (boundary/ base registers, base registers), the set value is valid from the next bus cycle of I/O write cycle in which data is written in MMU registers.

(3)There is no hardware restriction for the use of each region(R0 ~ R4). However, the following assignments are recommended.

- R0: resident program region (common program, interrupt vector, etc.)

- R1: program bank window

- R2: data bank window 1 (source)

- R3: data bank window 2 (destination)

- R4: resident data region (stack etc.)

(4)This MMU circuit occupies the following I/O addresses. Note that these I/O addresses cannot be assigned for user's I/O.

#### Table 5-2 I/O. Mapping MMU circuit uses.

| I/O Address    | Register Name         |

|----------------|-----------------------|

| 00H            | BBR1                  |

| 01H            | BR1                   |

| 02H            | BBR2                  |

| 03H            | BR2                   |

| 04H            | BBR3                  |

| 05H            | BR3                   |

| 06H            | BBR4                  |

| 07H            | BR4                   |

| $08H \sim 0FH$ | Reserved For Kawasaki |

|                | Steel corp.           |

(5)The logical boundary address of R1 is decided by the R1 logical boundary address (B1). Because the lower limit address of the R1 region is (B1+1)\*400H, the lowest value of the R1 region lower limit address is 0400H. On the other hand, the lower limit address of the R0 region is 0000H. Therefore, the lowest 1K byte of logical address is always belong to the R0 region. This lowest 1K byte is always mapped to the fixed location, 0000H ~ 003FFH.

(6)Set a value under 3FH to B1  $\sim$  B4. 3FH to B1  $\sim$  B4 is an invalid value and the corresponding region disappears.

## KL5C80A12

## 6. Interrupt Controller

## 6.1 General description

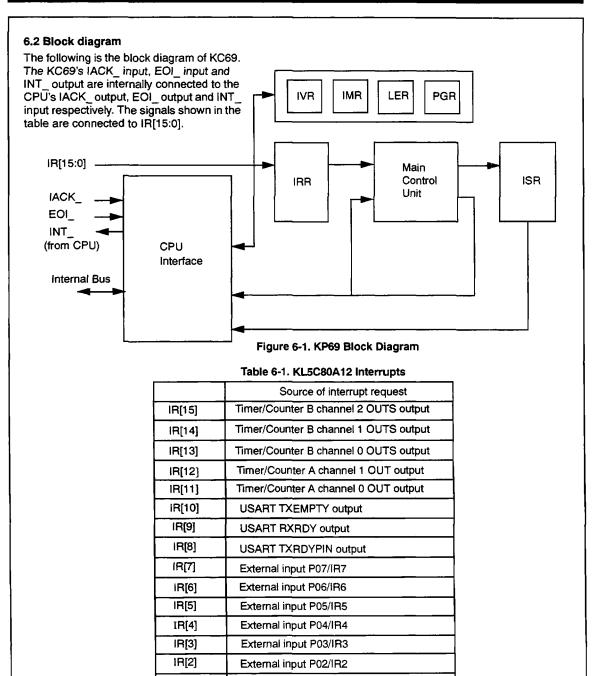

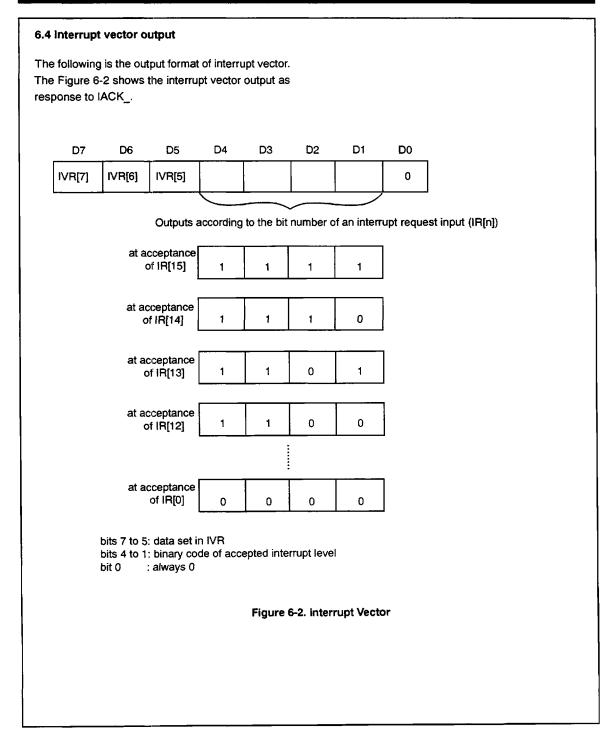

The KL5C8080A1212 includes a KP69 macro cell as interrupt controller. The KP69 is a small-sized interrupt controller developed exclusively for microcontroller based on our CPUs (KC80 or KC82). The KP69 can support 16 levels of interrupt request inputs for the KC80 or KC82's Mode 2 interrupt. Each interrupt request can be set to the HIGH or LOW priority group, and within each group a higher number of interrupt request input level has higher priority. The edge/level operation and mask condition of each interrupt request input, higher 3 bits of interrupt vector can be programmed.

When the KP69 receives an interrupt request, it determines its mask condition and priority and sends the INT\_ signal to the CPU. When the IACK\_signal returns from the CPU, it sends a programmed interrupt vector to the data bus. It also recognizes the end of interrupt service routine with EOI\_= "L" from the CPU. This EOI\_ signal goes low while executing the RETI instruction. Therefore, if the RETI instruction is placed at the end of interrupt service routine, the KC69 automatically recognizes the RETI instruction and the end of interrupt service routine. The KC69 has also an illegal interrupt detection capability.

## Features

- · Support KC80/KC82 mode 2 interrupt.

- The priorities of 16 level interrupt request inputs can be programmed.

- · Each interrupt request maskable.

- · Nested interrupt operation possible.

- · The edge/level mode of interrupt request input can be selected.

- · Illegal interrupt detection capability

- Automatically detects the execution of the CPU's RETI instruction and the end of interrupt service routine.

## KL5C80A12

External input P01/IR1

External input P00/IR0

IR[1]

IR[0]

## KL5C80A12

#### 6.3 Register architecture and I/O mapping

KP69 contains the following registers.

| I/O address | Block                | Write cycle | Read cycle |

|-------------|----------------------|-------------|------------|

| 34H         | Interrupt controller | LERL/PGRL   | ISRL       |

| 35H         |                      | LERH/PGRH   | ISRH       |

| 36H         |                      | IMRL        | IMRL       |

| 37H         |                      |             | IMRH       |

## Table 6-2. I/O Mapping

## IRR (Interrupt Request Register)

(not readable, not writable)

The corresponding bits are set when an interrupt request is generated. When the interrupt request is accepted in the level mode, this register is reset by disappearance of the request. When the interrupt request is accepted in the edge mode, it is reset by the start of interrupt service. The edge detection circuits of all interrupt levels are reset right after the reset.

## ISR (In Service Register)

(read only)

When the IACK\_ signal is returned, the bits corresponding to the accepted interrupt request are set. They are reset at the end of request service. All bits are reset right after the reset. Each 8 bits can be read.

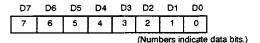

#### D1 D0 D7 D6 D5 D4 D3 D2 ISR[11] ISR[10] ISR[9] ISR[8] ISRH ISR[15] ISR[14] ISR[13] ISR[12] D1 D0 D7 D6 D5 D4 D3 D2 ISR[5] ISR[1] ISR[0] ISR[4] **ISR[3] ISR**[2] ISRL ISR[7] **ISR[6]** ISR[n] description 0 Out of service 1 In service D0 D3 D2 D1 D5 D4 D7 D6 IVR[5] IVR IVR[7] IVR[6]

#### IVR (Interrupt Vector Register) (write only)

This register specifies higher 3 bits of interrupt vector of the KC82 Mode 2 interrupt. Writable registers change when data is written into this register.

## KL5C80A12

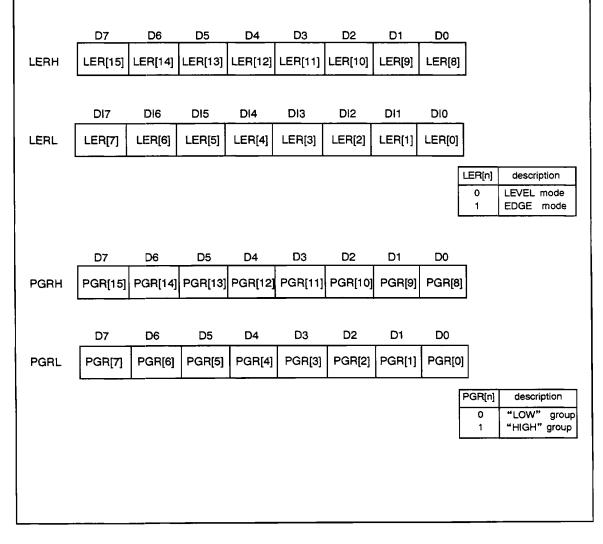

## LER (Level / Edge Register)

(write only)

This register controls the level/edge mode of each interrupt request input (hereinafter referred to as "IR input"). The mode can be set for each IR input. All bits are set to the level mode right after the reset. Be sure to write data to this register before setting IVR. This register is write only.

Note: To use an interrupt of timer/counter, the corresponding IR input should be set to the edge mode.

## PGR (Priority Group Register) (write only)

This register controls priority groups of IR inputs. The priority group can be set for each IR input. There are two kinds of priority groups; "HIGH" and "LOW". All bits are set to LOW right after the reset. Be sure to write data to this register after setting IVR. This register is write only.

## KL5C80A12

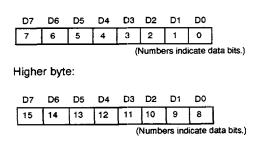

## IMR (Interrupt Mask Register) (readable, writable) This register mask IR inputs. The mask state can be set for each IR input. All bits are set to "1" right after the reset. Be sure to write data to this register after setting IVR. This register is write/read enable. D7 D6 D0 D5 D4 D3 D2 D1 IMRH IMR[15] IMR[14] IMR[13] IMR[12] IMR[11] IMR[10] IMR[9] IMR[8] D7 D6 D5 D4 D3 D2 D1 D0 IMR[6] IMR[5] IMR[4] IMR[3] IMR[2] IMR[1] IMR[0] IMRL IMR[7] IMR[n] description 0 non-masked state 1 masked state

## KL5C80A12

## KL5C80A12

## 6.5 Priorities of interrupt requests

The priorities of interrupt request inputs are set in descending order of bit numbers right after the reset. The priorities can be changed in terms of priority group. There are two kinds of priority groups ("LOW" and "HIGH") and

the priority group can beset for each IR. The IRs of "HIGH" group have higher priority over those of "LOW" group. Within each group, an IR with higher bit number has higher priority. The following is an example of IR priorities.

| Interrupt request input | Group |

|-------------------------|-------|

| IR[15]                  | LOW   |

| IR[14]                  | LOW   |

| IR[13]                  | LOW   |

| IR[12]                  | HIGH  |

| IR[11]                  | LOW   |

| IR[10]                  | HIGH  |

| IR[9]                   | LOW   |

| IR[8]                   | HIGH  |

| IR[7]                   | HIGH  |

| IR[6]                   | LOW   |

| I <b>R</b> [5]          | LOW   |

| IR[4]                   | HIGH  |

| IR[3]                   | LOW   |

| IR[2]                   | HIGH  |

| IR[1]                   | HIGH  |

| IR[0]                   | HIGH  |

|                         |       |

⇒

| Interrupt request input | Group | Priority |

|-------------------------|-------|----------|

| IR[12]                  | HIGH  | Highest  |

| IR[10]                  | HIGH  | t I      |

| IR[8]                   | HIGH  | ↓        |

| IR[7]                   | HIGH  | ↓        |

| IR[4]                   | HIGH  | ↓        |

| IR[2]                   | HIGH  | Ļ        |

| IR[1]                   | HIGH  | Ļ        |

| IR[0]                   | HIGH  | ↓ ↓      |

| IR[15]                  | LOW   | Ļ        |

| IR[14]                  | LOW   | Ļ        |

| IR[13]                  | LOW   | ↓<br>    |

| IR[11]                  | LOW   | Ļ        |

| IR[9]                   | LOW   | 4        |

| IR[6]                   | LOW   | Ļ        |

| IR[5]                   | LOW   | Ļ        |

| IR[3]                   | LOW   | Lowest   |

Figure 6-3. Interrupt Request Priority

## KL5C80A12

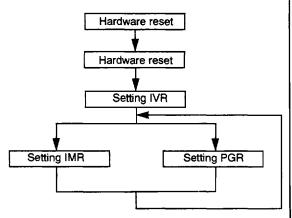

## 6.6 Register setting sequence

I/O addresses are assigned to the internal registers of KC69 as shown in Table 6-2. So initialization of registers after clearing the reset is performed in the following order: LER, IVR and IMR (or PGR). It should be noted that only IMR or PGR can be set after setting IVR.

Figure 6-4. Register Setting Sequence

## 6.7 Readout of registers

Of the KP69 registers, ISR and IMR are always readable. Readout of ISR is required to determine an illegal interrupt.

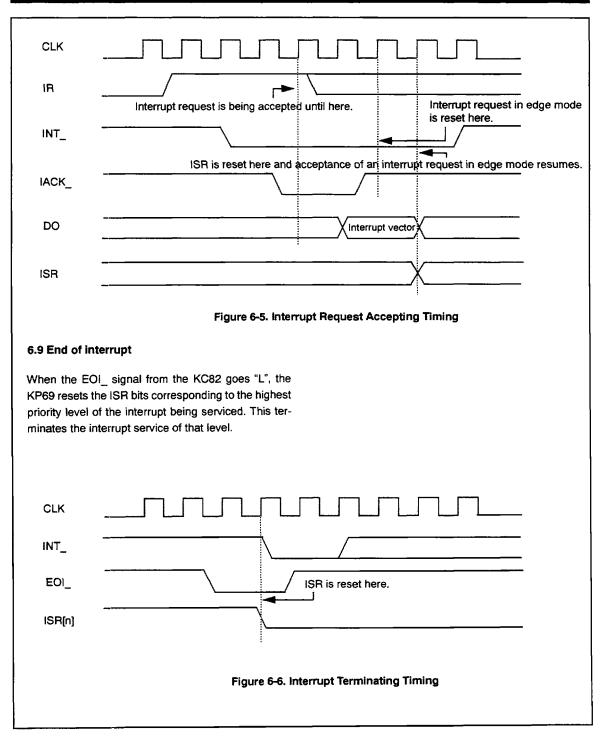

## 6.8 Acceptance of interrupt request

There are two modes (level and edge) for the acceptance of interrupt request and they are set by LER.

## Level mode

In level mode, "H" level of IR input is recognized as interrupt request.

## Edge mode

In edge mode, the rising edge of IR input is recognized as interrupt request. In this case, the interrupt request is held until accepted.

## **Operation sequence**

The following is the operations when an interrupt request is generated at IR[n] pin.

When IR input goes "H" to generate an interrupt request, the corresponding bits of IRR are set. This interrupt request becomes an INT\_signal through the mask conditions determined by IMR and the priority decision by ISR and PGR. The KC82 receives the signal and makes the IACK\_signal "L". When the KP69 receives this IACK\_signal, it outputs an interrupt vector corresponding to the IR[n] where the interrupt request has been generated to set the corresponding bit of ISR and (in edge mode) reset the corresponding bits of IRR. Then the CPU enters the interrupt service routine. When ISR is set, acceptance of an interrupt request in edge mode is enabled.

## KL5C80A12

## KL5C80A12

## 6.10 Nested interrupt operation

The KP69 compares the interrupt level of a new interrupt request with that of the interrupt request being serviced in terms of the predetermined priority. When the interrupt level of a new interrupt request has higher priority than that of the interrupt request being serviced, the KP69 accepts a new interrupt request, otherwise the KP69 rejects it or keeps it wait. This implements a nested interrupt operation. The state of nested interrupts can be obtained by reading ISR.

## 6.11 Illegal interrupt operation

An illegal interrupt indicates the following state: when an interrupt request input set to the level mode made INT signal "L" and the KC82 returned IACK as response, the interrupt request has already disappeared and there is no higher interrupt request input than the interrupt request being serviced with the highest priority. In this state the KP69 does not set ISR and outputs an interrupt vector corresponding to IR[0], entering an illegal interrupt operation state which lasts until the EOI from the KC82. ISR is not reset by this EOI . Any interrupt request (legal or illegal) would not be accepted in the illegal interrupt operation state. Therefore, during the IR[0] interrupt service it is necessary to distinguish a normal interrupt request or an illegal interrupt request based on ISR[0]. When the KP69 goes to an illegal interrupt request state during the IR[0] interrupt service, the readout of ISR gives ISR[0]=0. This indicates that ISR[0]=1 represents a legal interrupt request and ISR[0]=0 represents an illegal interrupt request.

## 6.12 Reset

When the RESET\_ goes "L", the following operations are performed.

- (1) IMR is set to "FFFFH". (All levels in masked state)

- (2) IRR, ISR, LER and PGR are reset to "0000H".

- (3) Illegal interrupt operation state is disabled.

(4) IVR is placed in non-set state. (Initialization is required.)

## 6.13 Precautions

- (1) Be sure to use Mode 2 for CPU interrupt mode.

- (2) Be sure to place RETI instruction (source code: ED 4D) at the end of interrupt service routine.

- (3) To use an interrupt of timer/counter, the corresponding IR input should be set to the edge mode.

## KL5C80A12

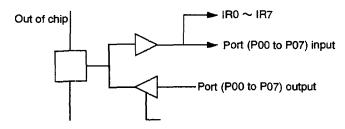

#### 6.14 Advanced Applications

The external outputs IR7 to IR0 are always connected to the input buffer of pins 80 to 83 and 85 to 88. When the ports are set to the input direction, the conditions of interrupt request on IR7 to IR0 can be checked by readout of the ports. This is very useful for checking the presence of nested interrupt requests. When the ports are set to the output direction, an external interrupt can be generated through the output ports by software. Read the following precautions about how to use these pins.

Figure 6-7. Structure of Pins 80 to 83 and 85 to 88

## Precautions:

- when placing an external input to IR7 to IR0 Set the parallel ports to the input direction.

- (2) when setting the parallel ports to the output direction

The values to be output from the parallel ports are input to IR7 to IR0. Mask the corresponding external request level when not using IR7 to IR0.

## KL5C80A12

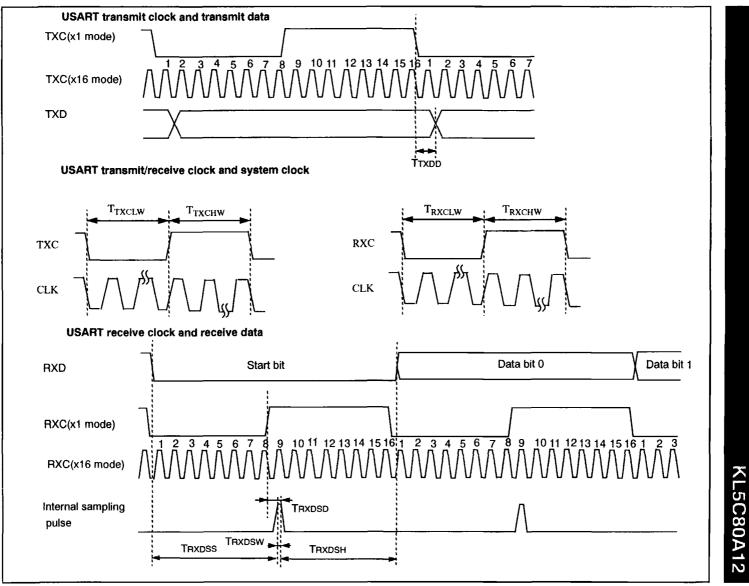

## 7. USART

## 7.1 General description

The USART in the chip is KP51 macro cell. KP51 is a programmable serial communication macro cell. Once initialized, it transmits and receives data according to the mode. This macro cell is compatible with popular 8251, but much faster than it.

## Synchronous mode and asynchronous mode

KP51 provides the following two modes.

- (1) Synchronous (sync) mode

- character length: 5 to 8 bits

- · number of synchronous characters: 1 to 2 characters

- parity bit odd/even/non parity bit, internal synchronization detection/external synchronization detection

- (2) Asynchronous (async) mode

- character length: 5 to 8 bits

- stop bit length: 1, 1.5, or 2 bits

- parity bit odd/even/non parity bit

- baud rate: x 1, x 6, x 64

## Error detection during data reception

The following errors can be detected as status information while receiving data.

- · parity error (when parity is enabled)

- overrun error

- framing error (async mode only)

## Sending and detecting a break signal

## Transmit enable and receive enable flags

When the transmit enable flag is set to '1', it is enabled to send data. When it is set to '0', transmit data stored in the buffer is sent and the transmit data pin goes '1' (marking state).

When the receive enable flag is set to '0', in async mode all receive operations (reception of data and change of flag) are disabled, and in sync mode the reception of data is not disabled and RXRDY and an overrun flag are reset. When it is set to '1', normal operations are performed.

## Enter hunt feature

When detecting sync characters in sync mode, an enter hunt command enables sync characters to be detected at each bit boundary.

## KL5C80A12

## 7.2 KP51 internal pin description

| pin name | I/O | description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXRDYPIN | 0   | Transmitter ready signal output<br>When transmit data can be written and transmit is enable<br>(CTS_="H" and txen= '1'), it goes "H". When transmit data is wri-<br>ten, it goes "L" and data transfer starts if in transmit enable state<br>As the KP51 has double internal buffer structure, this signal goe<br>"H" to inform that a next transmit data can be written when dat<br>transfer starts.<br>This signal differs from the bit 0 of status register (TXRDY) in th<br>following points.<br>Status register bit 0 - "H" when write of transmit data is enabled<br>TXRDYPIN signal - "H" when transmit data can be written an<br>transmit is enabled (CTS_= "L" and txen= "1" |

| TXEMPTY  | 0   | Transmitter empty output<br>It outputs "H" when there is no data to be sent. When transmit dat<br>is written, it outputs "L".<br>This signal remains "H" in transmit disable state (CTS_= "H" an<br>txen= '0'). In sync mode, when data is written and transmitted, an<br>there is no data to be sent, it keeps automatically outputting syn<br>characters. Even at this time TXEMPTY outputs "H".                                                                                                                                                                                                                                                                                    |

| RXRDY    | 0   | Receiver ready signal output<br>It outputs "H" when one character data is received and readout of<br>data is enabled. It is reset to "L" when data is read out. The execu-<br>tion of a receive disable command (rxen= '0': setting the comman<br>register bit 2 to '0') also resets this signal to "L". In sync mode it<br>reset to "L" by issuing the enter hunter command (setting the com-<br>mand register bit 7 to '1').                                                                                                                                                                                                                                                        |

Refer to Chapter 3 for the KP51's external I/O pins (CTS\_, RXC,DSR\_, RXD, TXD, TXC, DTR\_, RTS\_, SYN-DBD, SYDTIN).

## KL5C80A12

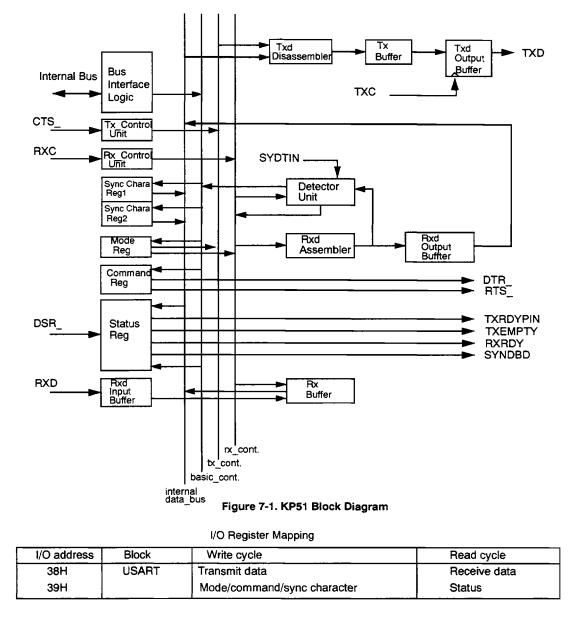

## 7.3 Block diagram

The following is the KP51 block diagram. The KP51 internal pins (TXRDYPIN, TXEMPTY, RXRDY) are connected to the interrupt controller.

## KL5C80A12

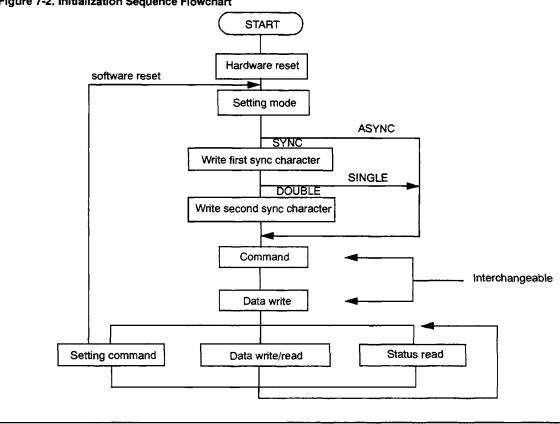

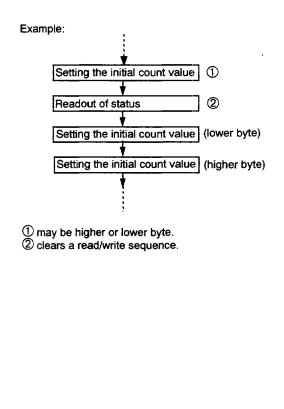

#### 7.4 Initialization

To start transmitting or receiving data, the setting mode and command entry should be made after reset as shown in Figure 7-2.

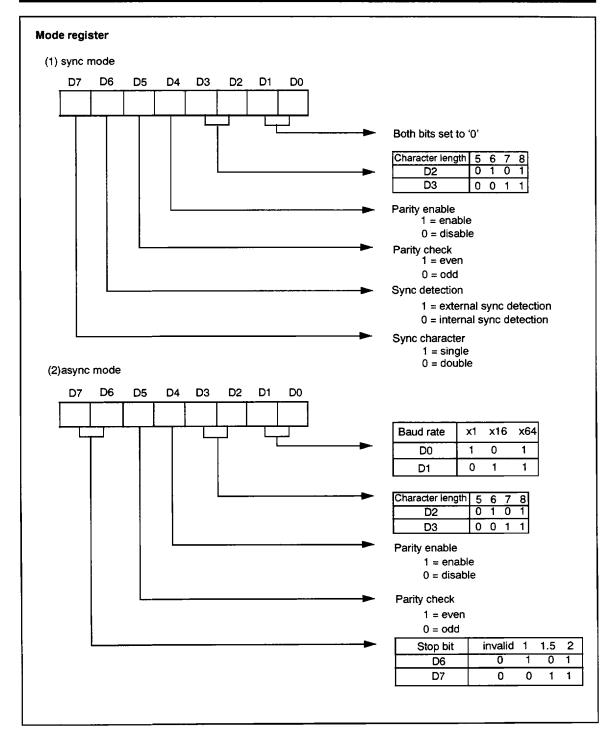

#### Setting mode

When writing to I/O address 39H is made after reset, data is written to the mode register. The KP51 always waits for mode set state after reset (external RESET input or software reset command entry).

In this state, the sync or async mode is selected, and baud rate, character length and others are set. Set the mode according to the format described in the following pages.

#### Setting sync characters

When the sync mode is selected, the KP51 then waits for the sync character. Write one sync character for single mode or two sync characters for double(bisync) mode. When the async mode is selected, the KP51 automatically skips this step and proceeds to the next command waiting state.

#### Setting command

When the mode and sync character are set, all data writes at I/O address = 39H are regarded as a command.

The command enables data transmission. About commands, refer to P.7-6.

#### Figure 7-2. Initialization Sequence Flowchart

## KL5C80A12

## KL5C80A12

## KL5C80A12

## 7.5 Operation modes

The operations in each mode are described below.

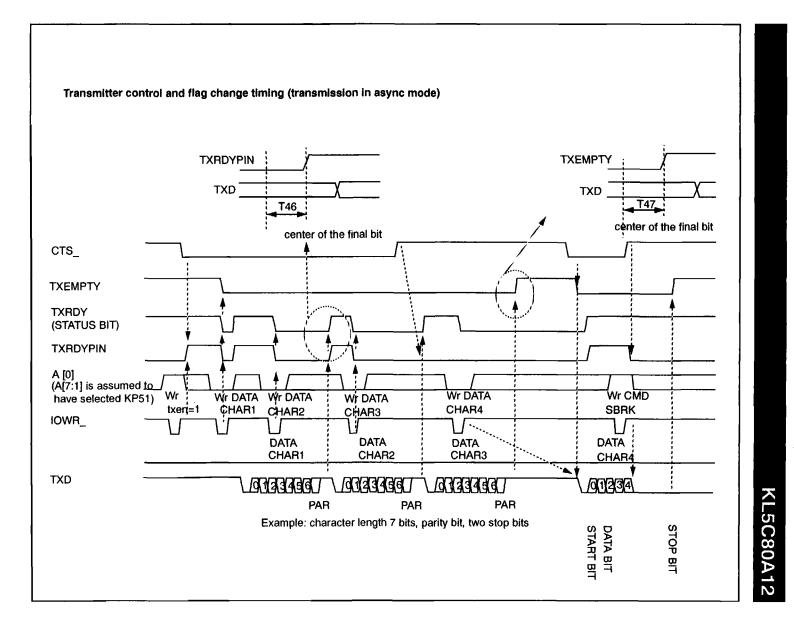

## Data transmission in async mode

When data is written from the CPU, character data is disassembled to the transmit format with start bit, parity bit and stop bit based on the conditions specified by the mode register.

When a transmission break command (sbrk= '1') is issued, TXD outputs "L".

When a transmission break command (sbrk='1') is not issued and transmit is enabled ( $CTS_="L"$  or txen='1'), data is transmitted. Before transmission the TXD signal remains "H" (marking state) until transmit data is written. When there is no data to be sent after transmitting 1 character, it returns to the marking state.

Transmit data is sent in synchronization with the rising edge of the TXC signal at 1, 1/16 or 1/64 times of the TXC according to the set baud rate.

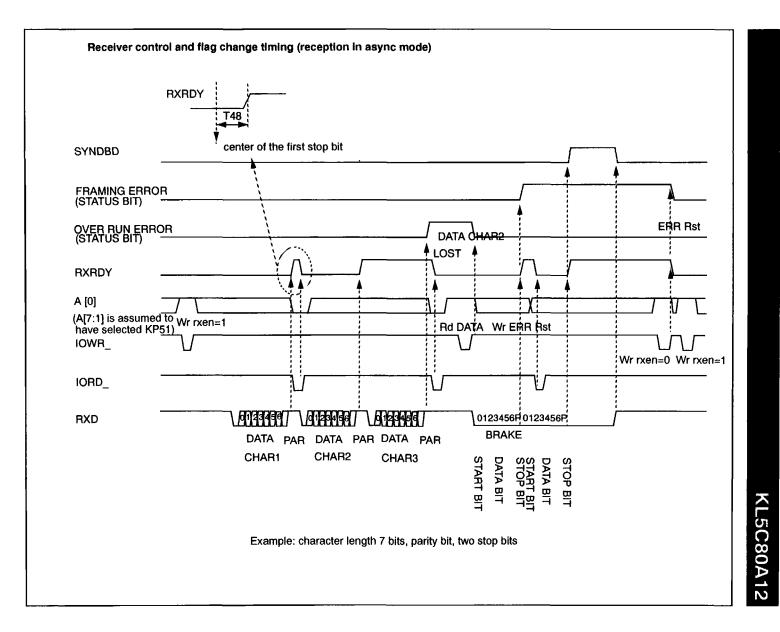

## Data reception in async mode

When the KP51 detects RXD input "H" at receive enable state (rxen= '1'), it waits until the RXD goes "L". When the RXD goes "L", a start bit becomes effective. If the KP51 samples a "L" in the center of a bit, it identifies it as start bit and starts receiving data. It detects a parity error, framing error and overrun error during data reception. Each of these errors can be checked by the readout of status register described later. These errors do not affect the receive operation itself.

Framing error is recognized not by the number of stop bits, but by the first stop bit being "L".

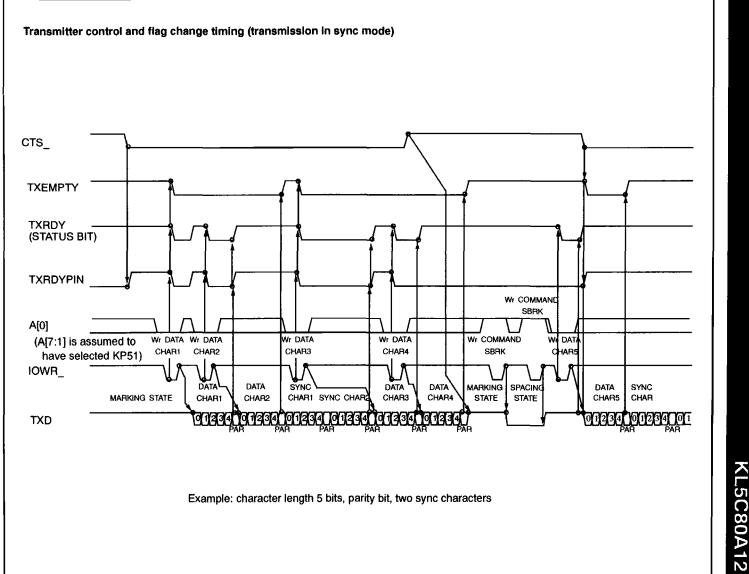

## Data transmission in sync mode

Even at transmit enable state (CTS\_= "L" and txen= '1') the TXD signal remains "H" (marking state) until a first data is written. When there is data to be sent, data is transmitted in synchronization with the rising edge of TXC. Next transmit data should be provided before there is no data to be sent (TXEMPTY goes "H"). When data is provided late, sync characters are automatically sent repeatedly.

When transmitting sync characters, the TXEMPTY signal is "H" until the next data is provided, and it goes "L" when data is provided.

Sync characters are not sent unless the first transmit data is written.

## Data reception in sync mode

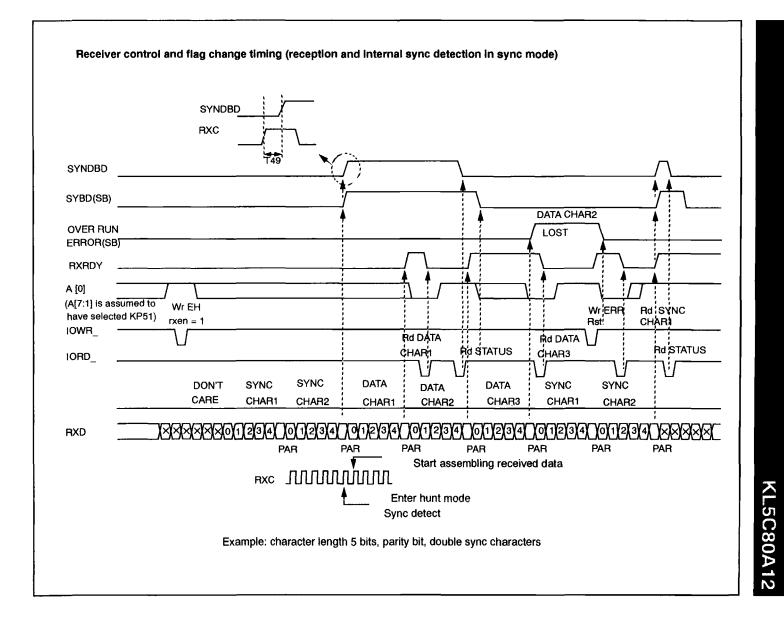

There are two kinds of sync detection; internal sync detection and external sync detection. In sync mode, an enter hunt command should be issued (bit 7 of the command register set to '1') before start receiving data. The enter hunt command enables async character to be detected.

In internal sync detection, a sync character is searched for a match at each rising edge of RXC. In bi-sync mode, the second sync character is also compared after the first sync character match (two contiguous sync characters should be received).

When the detection of sync characters is completed, SYNDBD pin goes "H" and the KP51 exits the hunt mode. The SYNDBD pin is usually set in the center of the final bit of data. But if data contains a parity bit, it is set in the center of the parity bit.

The detection of sync characters is performed at each specified character boundary even after the end of the hunt mode.

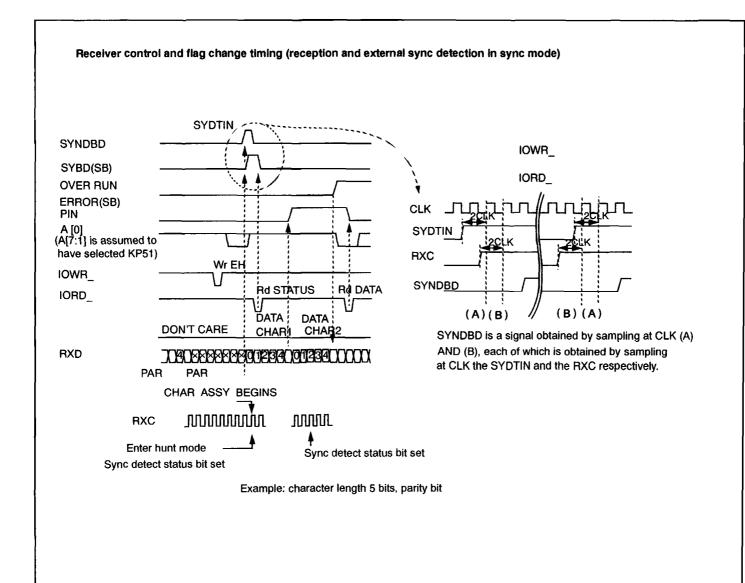

In external sync detection, it is recognized as completion of sync detection that the SYDTIN pin is "H" for more than one cycle of RXC, and then the KP51 exits the hunt mode. At this time the SYNDBD pin is set to "H" as in internal sync detection.

In this external sync detection, the internal sync detection is not performed.

In sync mode, data reception is performed regardless of whether transmit is enabled or disabled. As in async mode, detection of parity error is performed except in the hunt mode.

## KL5C80A12

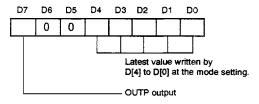

## 7.6 Status register

D7 D6

This 8-bit register stores the status information on data transmission and reception. Readout of this register allows you to make polling operation.

D5 D4 D3

D2 D1 D0

The following is the bit assignment of the status register. It should be noted that the set conditions may be different from those of external pins in some status.

| D1 R<br>D2 T)<br>D3 PE<br>D4 OI | Parity Error<br>It goes '1' when a parity error is detected in received data.<br>It changes regardless of whether receive is enabled (Command Register bit 2 (rxen)= '1') or<br>disabled (rxen= '0').<br>In sync mode, it does not function in the hunt mode.<br>It is cleared to '0' by Error Clear command (Command Register bit4 (er)= '1').<br>E<br>Overrun Error<br>It is set to '1' when readout of data is delayed after its reception and the next data has already been<br>received in receive enable state (rxen= '1').<br>It is cleared to '0' by an Error Clear command or Receive Disable command.                                                                                                                                                                                                                                                                                                            |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

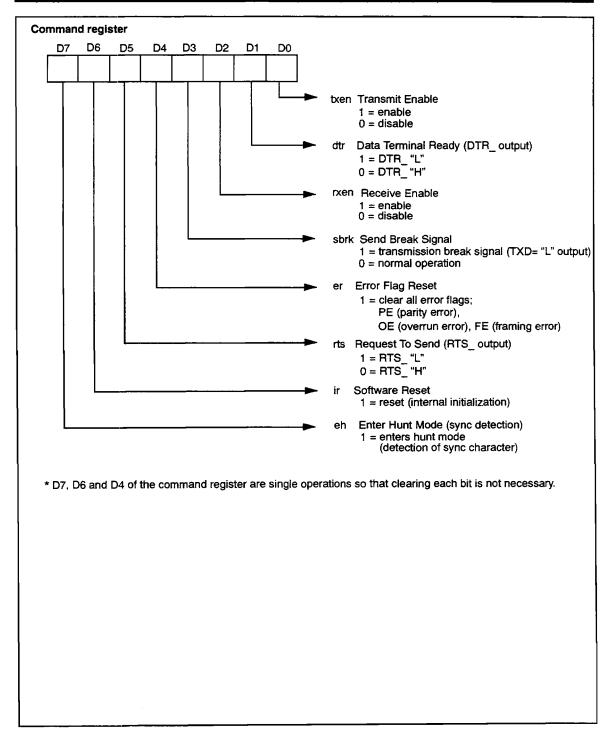

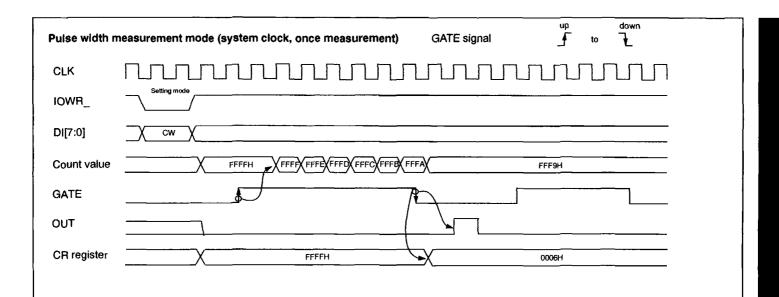

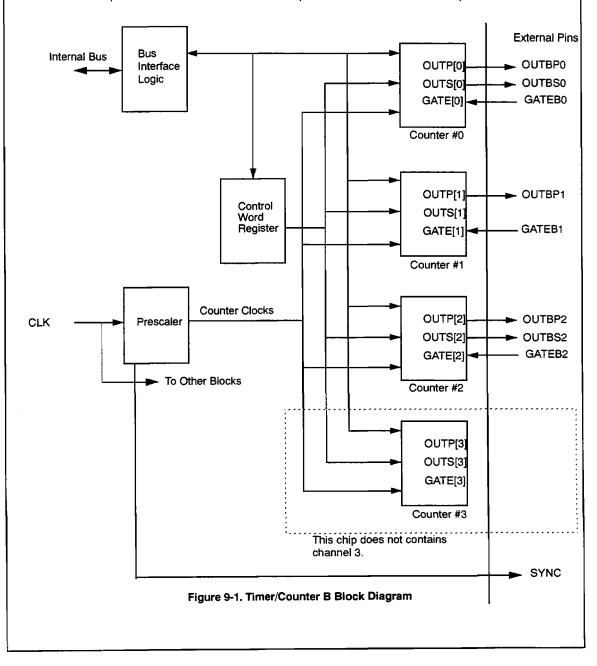

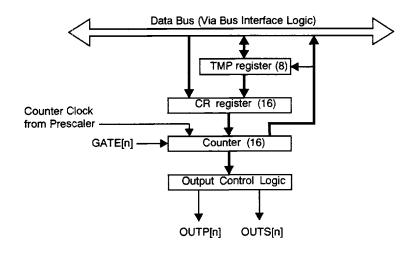

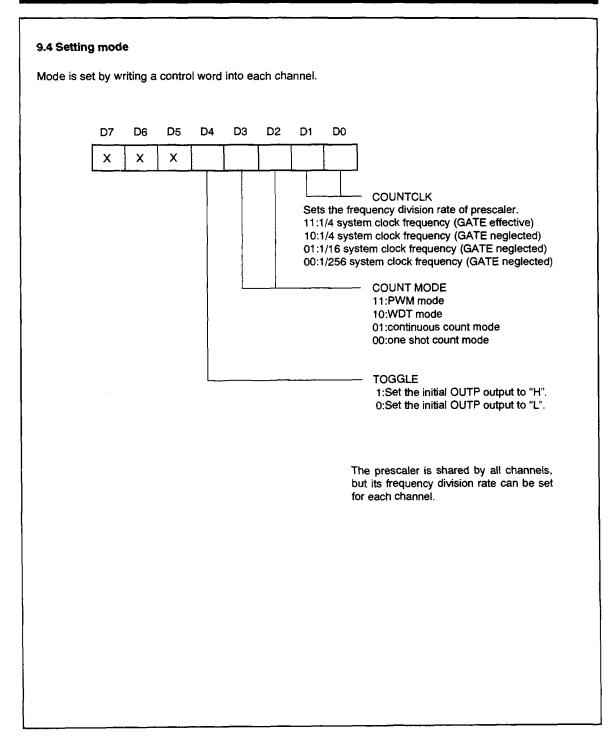

| D1 R<br>D2 T)<br>D3 PE<br>D4 OI | TXRDYPIN = "H" when the internal Data Buffer is empty, CTS_= "L" and<br>Command Register bit 0 (txen)= '1'<br>XRDY<br>The same function as the RXRDY pin.<br>KEMPTY<br>The same function as the TXEMPTY pin.<br>Parity Error<br>It goes '1' when a parity error is detected in received data.<br>It changes regardless of whether receive is enabled (Command Register bit 2 (rxen)= '1') or<br>disabled (rxen= '0').<br>In sync mode, it does not function in the hunt mode.<br>It is cleared to '0' by Error Clear command (Command Register bit4 (er)= '1').<br>E<br>Overrun Error<br>It is set to '1' when readout of data is delayed after its reception and the next data has already beer<br>received in receive enable state (rxen= '1').<br>It is cleared to '0' by an Error Clear command or Receive Disable command.<br>E<br>Framing Error<br>It is set to '1' when '0' is detected at stop bits in async mode. |