# **1984 MOS Products Catalog**

V

Copyright© 1984 American Microsystems, Inc. (All rights reserved) Trade Marks Registered®

Information furnished by AMI in this publication is believed to be accurate. Devices sold by AMI are covered by the warranty and patent indemnification provisions appearing in its Terms of Sale only. AMI makes no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. AMI makes no warranty of merchantability or fitness for any purposes. AMI reserves the right to discontinue production and change specifications and prices at any time and without notice.

Advanced Product Description means that this product has not been produced in volume, the specifications are preliminary and subject to change, and device characterization has not been done. Therefore, prior to programming or designing this product into a system, it is necessary to check with AMI for current information.

**Preliminary** means that this product is in limited production, the specifications are preliminary and subject to change. Therefore, prior to programming or designing this product into a system, it is necessary to check with AMI for current information.

These products are intended for use in normal commercial applications. Applications requiring extended temperature range, unusual environmental requirements, or high reliability applications, such as military, medical life-support or life-sustaining equipment are specifically **not** recommended without additional processing by AMI for such application.

### Introduction

American Microsystems, Inc. (AMI) headquartered in Santa Clara, California is the semiconductor industry leader in the design and manufacture of custom MOS/VLSI (metal-oxide-silicon very-large-scale-integrated) circuits. It manufactures special circuits for the leading computer manufacturers, telecommunications companies, automobile manufacturers and consumer product companies worldwide. AMI is a wholly owned subsidiary of Gould, Inc.

Along with being the leading designer of custom VLSI, AMI is a major alternate source for the S6800 8-bit microprocessor family and the only alternate source for the S9900 16-bit family of microprocessors. AMI is also an alternate source for the 4-bit 7500 and the 8-bit 7800 series of single chip microcomputers. The company provides the market with selected low power CMOS Static RAMs, and 8K, 16K, 32K, 64K and 128K ROMs for all JEDEC pinouts or as EPROM replacements.

The most experienced designer of systems-oriented MOS/VLSI communication circuits, AMI provides components for station equipment, PABX and Central Office Switching systems, data communications and advanced signal processing applications.

AMI is a leading innovator in combining digital and analog circuitry on a single silicon chip, and is a recognized leader in switched capacitor filter technology.

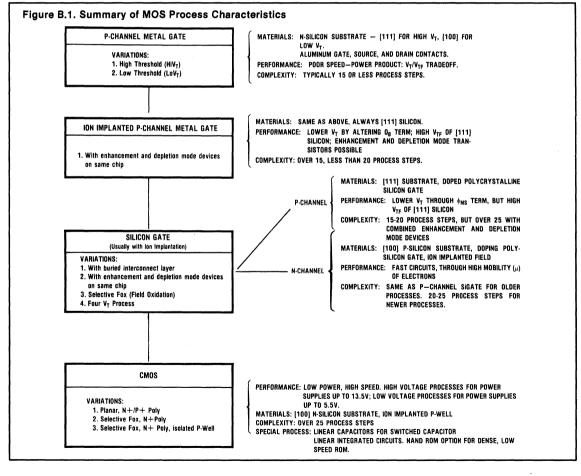

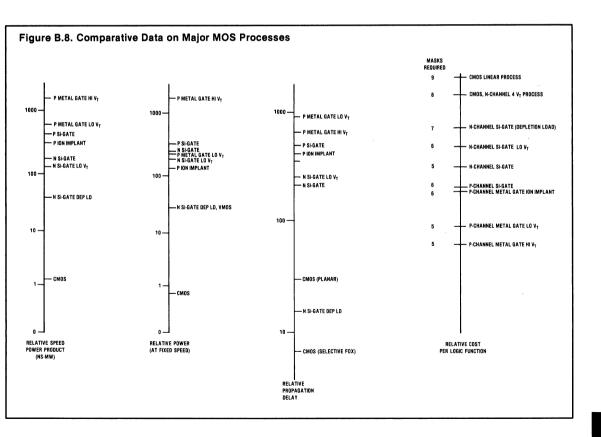

Processing technologies range from the mature PMOS metal gate, to silicon gate N-Channel to the advanced, small geometry, high performance silicon gate CMOS. Over 25 variations are available.

Headquartered in Santa Clara, California, AMI has design centers in Santa Clara; Pocatello, Idaho; and Swindon, England. Wafer fabricating plants are in Santa Clara and Pocatello, and assembly facilities are in Seoul, Korea and the Philippines. A joint venture company in Graz, Austria will include complete design and manufacturing facilities.

Field sales offices are located throughout the United States, in Europe and in the Far East. Their listing, plus those of domestic and international representatives and distributors appear on pages B.31 through B.34 of this publication.

.

.

•

.

AM

A Subsidiary of Gould Inc.

### Numerical Index

| Device          | Page         |

|-----------------|--------------|

| S10110          | 4.47         |

| S10131          | 4.51         |

| S10430          | 4.53         |

| S1602           | 6.35         |

| S23128A         | 5.45         |

| S23128B         | 5.45         |

| S2333           | 5.21         |

| S2350           | 6.43         |

| S2364A          | 5.32         |

| S2364B          | 5.49         |

| S23256B         | 5.49         |

| S23256C         | 5.49         |

| S25089          | 3.61         |

| S2550A          | 3.3          |

| S2559A          | 3.10         |

| S2559B          | 3.10         |

| S2559C          | 3.10         |

| S2559D          | 3.10         |

| S2559E          | 3.21         |

| S2559F          | 3.21         |

| S2559G          | 3.21         |

| S2559H          | 3.21         |

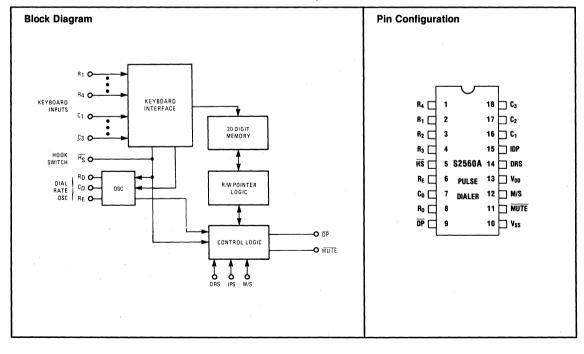

| S2560A          | 3.28         |

| S2560G          | 3.35         |

| S2561A          | 3.37         |

| S2561C          | 3.37         |

| S25610          | 3.67         |

| S25610E         | 3.75         |

| S2563           | 3.45         |

| S2567           | 4.60         |

| S2569           | 3.46         |

| S2569A          | 3.46         |

| S2369B          | 3.53         |

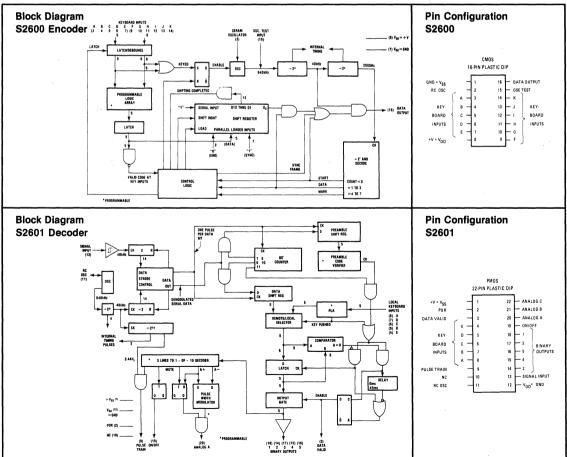

| S2600           | 4.30         |

| S2601           | 4.30         |

| S2602<br>S2603  | 4.33<br>4.33 |

| S2604           |              |

| S2605           | 4.36<br>4.36 |

| 00000           | 4.62         |

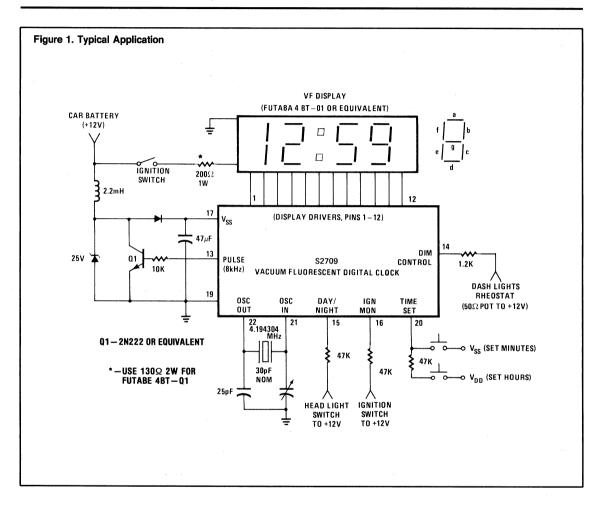

| S2688<br>S2709A | 4.02         |

| S2709A          | 4.42         |

| 0.07.40         | 4.42         |

| S2743<br>S2747  | 4.42         |

| S2748           | 4.45         |

| 00000           | 4.45         |

| RTDS28212       | 3.90         |

| SSPP28211       | 3.92         |

| S28211          | 3.93         |

| S28212          | 3.95         |

| S28214          | 3.99         |

|                 | 5.00         |

| Device   | Page  |

|----------|-------|

| S28215   | 3.118 |

| S28216   | 3.122 |

| S2859    | 3.23  |

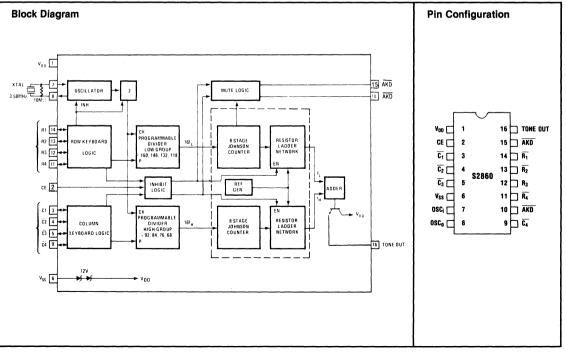

| S2860    | 3.25  |

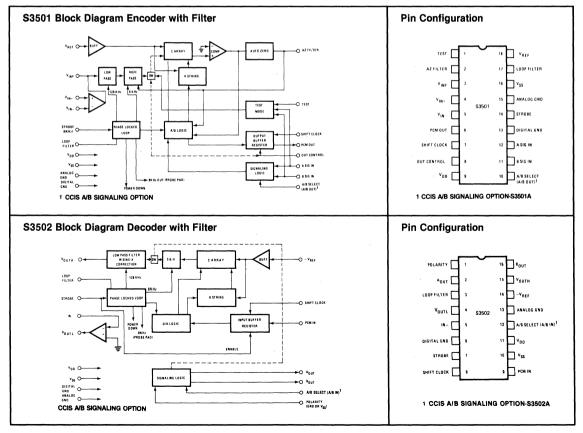

| S3501    | 3.86  |

| S3502    | 3.86  |

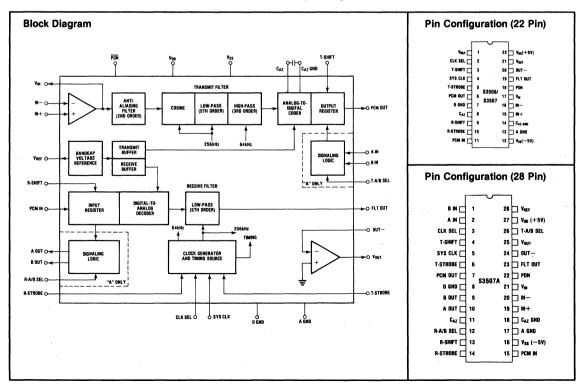

| S3506    | 3.88  |

| S3507    |       |

| S3507A   | 3.88  |

| S3522    | 3.125 |

| S35212   | 3.131 |

| S3525A   | 3.133 |

| S3525B   | 3.133 |

| S3526    | 3.140 |

| S3530    | 3.156 |

| S3610    | 4.3   |

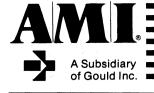

| S3620    | 4.10  |

| S4003    |       |

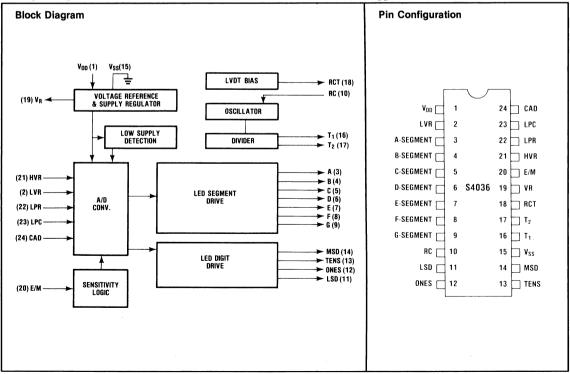

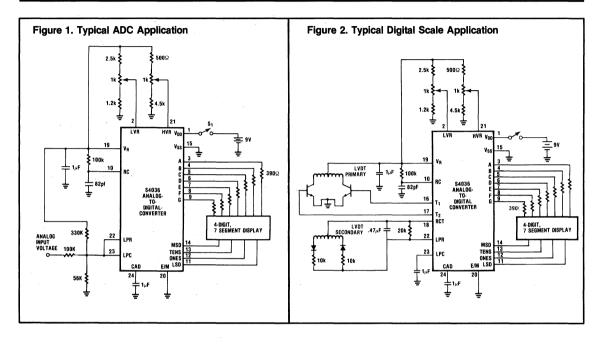

| S4036    | 4.75  |

| S4521    | 4.27  |

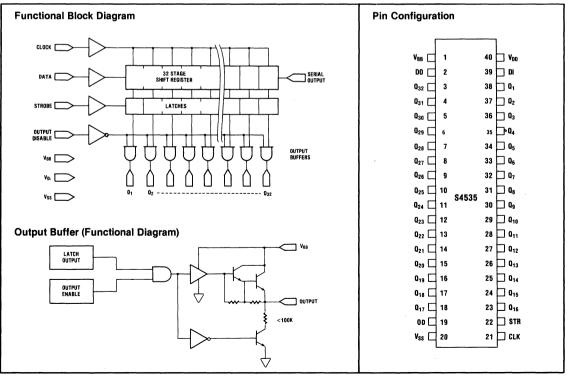

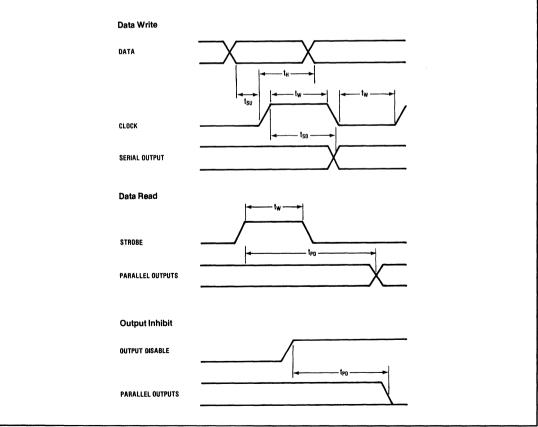

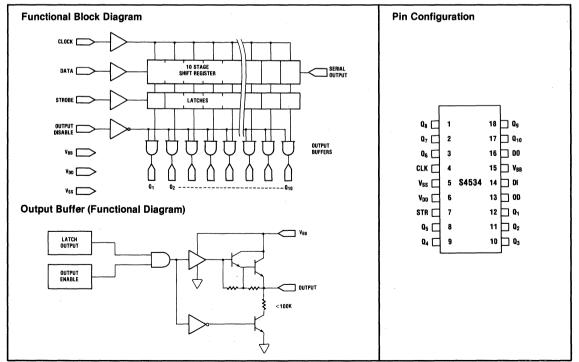

| S4534    | 4.24  |

| S4535    | 4.21  |

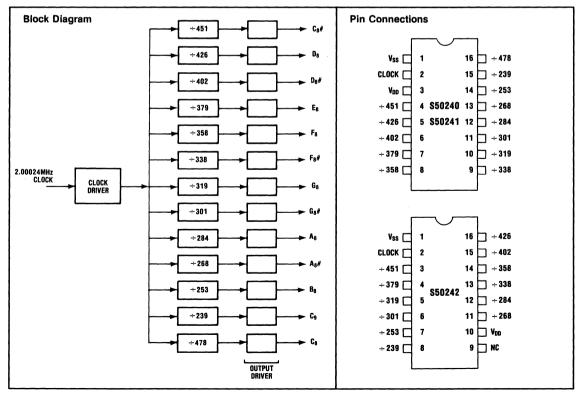

| S50240   | 4.65  |

| S50241   | 4.65  |

| S50242   | 4.65  |

| S5101    | 5.45  |

| S5101L-1 | 5.45  |

| S6501    | 5.45  |

| S6501L   | 5.45  |

| S6501L-1 | 5.45  |

| S6514    | 5.45  |

| S6516    | 5.45  |

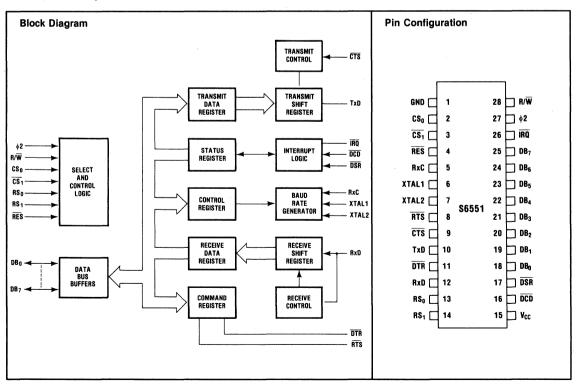

| S6551    | 6.46  |

| S6551A   | 6.46  |

| S6800    | 6.31  |

| S68A00   | 6.31  |

| S68B00   | 6.31  |

| S6801    | 6.91  |

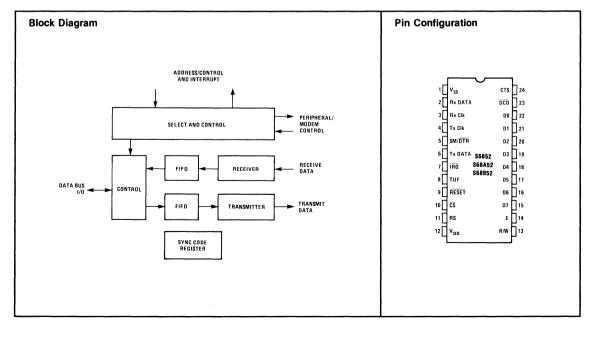

| S6802    | 6.12  |

| S68A02   | 6.12  |

| S68B02   | 6.12  |

| S6303    |       |

| S6303N/R | 6.21  |

| S68045   |       |

| S6805    |       |

| S6808    |       |

| S68A08   |       |

| S68B08   |       |

| S6809    |       |

| S68A09   |       |

| S68B09   | 6.32  |

|          |       |

| S6809(E)       6.33         S68A09(E)       6.33         S68B09(E)       6.33         S6810       6.79         S6810       6.79         S6810       6.79         S6811       6.54         S6821       6.54         S6821       6.54         S6821       6.54         S6821       6.54         S6821       6.54         S6821       6.54         S68232       5.18         S68B332       5.18         S68B332       5.18         S68B34       5.29         S68B364       5.29         S68B364       5.29         S68B364       5.29         S68B364       5.29         S68B40       6.60         S6840       6.60         S6840       6.60         S6845       6.70         S6852       6.73         S6854       6.76         S6854       6.76         S6854       6.76         S6854       6.76         S680B       5.39         S9900       7.31         S9901       7.27      S9902.4       <                                                                                                   | Device    | Page |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------|

| S68B09(E)         6.33           S6810         6.79           S68A10         6.79           S68B10         6.79           S68B10         6.79           S68E1         6.54           S68A21         6.54           S68B21         6.54           S68B21         6.54           S68B21         6.54           S68B21         5.18           S68A32         5.18           S68A32         5.18           S68A32         5.18           S68A32         5.18           S68A34         5.29           S68B364         5.29           S68B40         6.60           S68A40         6.60           S68A40         6.60           S68B40         6.60           S68B40         6.60           S68A50         6.70           S68A52         6.73           S68A52         6.73           S68A52         6.73           S68B54         6.76           S68B54         6.76           S68B54         6.76           S68B54         5.24           S9580B         5.39           S9901<                        | S6809(E)  | 6.33 |

| S6810         6.79           S68A10         6.79           S68B10         6.79           S6821         6.54           S6821         6.54           S68A32         5.15           S68A332         5.18           S68B332         5.18           S68B332         5.18           S68B34         5.29           S68B40         6.60           S68B50         6.70           S68B50         6.70           S68B52         6.73           S68B52         6.73           S68B54         6.76           S9808A         5.24           S9580B         5.39           S9901         7.27           S9901         7.27           S9904         7.38           S9902.4         7.27           S9904         7.10           S7501                              | S68A09(E) | 6.33 |

| S68A10         6.79           S68B10         6.79           S6821         6.54           S68A21         6.54           S68B32         5.15           S68B32         5.18           S68B32         5.29           S68B364         5.29           S68B40         6.60           S68B40         6.60           S68B40         6.60           S68B40         6.60           S68B50         6.70           S68E50         6.70           S68E52         6.73           S68E52         6.73           S68E52         6.73           S68E54         6.76           S9908A         5.24           S9900         7.31           S9901         7.27           S9901         7.27           S9904         7.10           S7500         8.31           S7501         8.51           S7502                                 | S68B09(E) |      |

| S68B10         6.79           S6821         6.54           S68A21         6.54           S68A21         6.54           S68A21         6.54           S68A21         6.54           S68A21         6.54           S68A316         5.15           S68A322         5.18           S68B332         5.18           S68B332         5.18           S68B332         5.18           S68B332         5.18           S68B34         5.29           S68B364         5.29           S68B364         5.29           S68B364         6.60           S68A40         6.60           S68B40         6.60           S68B40         6.60           S68B50         6.70           S68B50         6.70           S68B52         6.73           S68B52         6.73           S68B54         6.76           S9508A         5.24           S9508A         5.24           S9808         5.39           S9901.4         7.27           S980A         7.10           S7501         8.51           S7                        | S6810     |      |

| S6821         6.54           S6821         6.54           S68B21         6.54           S68B21         6.54           S68B21         5.15           S68A316         5.15           S68B32         5.18           S68B32         5.18           S68B32         5.18           S68B346         5.29           S68B364         5.29           S68B40         6.60           S68A40         6.60           S68A40         6.60           S68A50         6.70           S68B50         6.70           S68A52         6.73           S68A52         6.73           S68A52         6.73           S68A54         6.76           S68A54         6.76           S6854         6.76           S9508A         5.24           S9508A         5.24           S9508A         5.39           S9900         7.31           S9901-4         7.27           S980A         7.10           S7500         8.31           S7501         8.51           S7502         8.11           S7508                               | S68A10    |      |

| S68A21         6.54           S68A316         5.15           S68A316         5.15           S68A332         5.18           S68B32         5.18           S68B32         5.18           S68A32         5.18           S68B364         5.29           S68B364         5.29           S68B40         6.60           S68A40         6.60           S68A40         6.60           S68A40         6.60           S68A40         6.60           S68A40         6.60           S68A50         6.70           S68A52         6.73           S68A52         6.73           S68A52         6.73           S68A54         6.76           S68B54         6.76           S68B54         6.76           S68B54         6.76           S9808         5.39           S9900         7.31           S9901-4         7.27           S9901-4         7.27           S9902-4         7.28           S7500         8.31           S7501         8.51           S7502         8.11           S7506                        |           |      |

| S68B21         6.54           S68A316         5.15           S68A332         5.18           S68B332         5.18           S68B332         5.18           S68B34         5.29           S68B364         5.29           S68B40         6.60           S68B40         6.70           S68B50         6.70           S68B52         6.73           S68B52         6.73           S68B54         6.76           S68B54         6.76           S9808A         5.24           S9580B         5.39           S9901         7.27           S9901         7.27           S9901         7.27           S9902         7.38           S9902         7.38           S9902         7.38           S9904         7.10           S7500         8.31           S7501         8.51           S7502                               |           |      |

| S68A316         5.15           S68A322         5.18           S68B332         5.18           S68B332         5.18           S68B364         5.29           S68B364         5.29           S68B40         6.60           S6840         6.60           S68450         6.70           S6850         6.70           S6852         6.73           S6854         6.76           S6854         6.76           S6880B         5.39           S9900         7.31           S9901         7.27           S9808         5.39           S9901-4         7.27           S9902         7.38           S9902         7.38           S9902         7.38           S9902         8.31           S7501         8.51           S7502         8.11           S7503 <td< td=""><td></td><td></td></td<>     |           |      |

| S68A332         5.18           S68B332         5.18           S68B332         5.18           S68B364         5.29           S68B364         5.29           S68B364         5.29           S68B364         5.29           S68B364         5.29           S68B364         6.60           S68B40         6.60           S68B40         6.60           S68B40         6.60           S68B40         6.60           S68B40         6.60           S68B50         6.70           S68B50         6.70           S68B52         6.73           S68B52         6.73           S68B54         6.76           S9508A         5.24           S9508A         5.24           S9808         5.39           S9900         7.31           S9901.4         7.27           S980A         7.10           S7500         8.31           S7501         8.51           S7502         8.11           S7503         8.11           S7506         8.23           S7507         8.23           S7508 </td <td></td> <td></td> |           |      |

| S68B332         5.18           S68B364         5.29           S68B364         5.29           S68B364         5.29           S68B364         5.29           S68B364         6.60           S68A40         6.60           S68A40         6.60           S6840         6.60           S6840         6.60           S6840         6.60           S6845         6.70           S6850         6.70           S6852         6.73           S68452         6.73           S6854         6.76           S6854         6.76           S6854         6.76           S9808         5.39           S9900         7.31           S9901-4         7.27           S9901-4         7.27           S9902-4         7.28           S7500         8.31           S7501         8.51           S7502         8.11           S7503         8.11           S7506         8.23           S7508         8.23           S7508         8.23           S7508         8.23           S7509                                     |           |      |

| S68A364         5.29           S68B364         5.29           S6840         6.60           S68A40         6.60           S68A40         6.60           S68A40         6.60           S68A40         6.60           S68A40         6.60           S68A40         6.60           S68A50         6.70           S68A50         6.70           S68A52         6.73           S68A52         6.73           S68A52         6.73           S68A54         6.76           S68A54         6.76           S68A54         6.76           S68B54         6.76           S68B54         6.76           S9808         5.39           S9900         7.31           S9901-4         7.27           S9901-4         7.27           S9902-4         7.28           S7500         8.31           S7501         8.51           S7502         8.11           S7503         8.11           S7506         8.23           S7508         8.23           S7508         8.23           S7508                                |           |      |

| S68B364         5.29           S6840         6.60           S68A40         6.60           S68A40         6.60           S68B40         6.60           S68B40         6.60           S68B40         6.60           S68B40         6.60           S68B50         6.70           S68B50         6.73           S68B52         6.73           S68B52         6.73           S68B54         6.76           S68B54         6.76           S68B54         6.76           S68B54         6.76           S9808A         5.24           S9580B         5.39           S9901         7.27           S9901         7.27           S9902         7.38           S9902         7.38           S9902         7.38           S9904         7.10           S7501         8.51           S7502         8.11           S7503         8.11           S7506         8.23           S7508         8.23           S7509         8.23           S7508         8.23           S7508 <t< td=""><td></td><td></td></t<>      |           |      |

| S6840         6.60           S68A40         6.60           S68B40         6.60           S68B40         6.60           S68B40         6.60           S68A50         6.70           S68A50         6.70           S68A52         6.73           S68A52         6.73           S68A52         6.73           S68A52         6.73           S68B54         6.76           S68B54         6.76           S68B54         6.76           S9508A         5.24           S9508A         5.24           S9901         7.27           S9901.4         7.27           S9902.4         7.27           S9902.4         7.27           S9902.8         8.31           S7501         8.51           S7502         8.11           S7503         8.11           S7506         8.23           S7508         8.23           S7509         8.30           S7508         8.23           S7509         8.23           S7508         8.23           S7509         8.23           S7509                                   | ••••      |      |

| S68A40         6.60           S68B40         6.60           S68B40         6.60           S6850         6.70           S6850         6.70           S6850         6.70           S6852         6.73           S6852         6.73           S6852         6.73           S6854         6.76           S6854         6.76           S9508A         5.24           S9508A         5.24           S9508A         5.24           S9901         7.27           S9902         7.38           S9902.4         7.27           S980A         7.10           S7500         8.31           S7501         8.51           S7503         8.11           S7506         8.13           S7508         8.23           S7519         8.30 <td></td> <td></td>                 |           |      |

| S68B40         6.60           S6846         6.67           S6850         6.70           S68A50         6.70           S68A50         6.70           S68A50         6.73           S68A52         6.73           S68A52         6.73           S68A52         6.73           S68454         6.76           S68A54         6.76           S68B54         6.76           S9508A         5.24           S9508A         5.24           S9508A         5.39           S9900         7.31           S9901         7.27           S9902         7.38           S9902.4         7.27           S980A         7.10           S7501         8.51           S7502         8.11           S7503         8.11           S7506         8.23           S7508         8.23           S7508         8.23           S7509         8.30           S7508         8.23           S7508         8.23           S7508         8.23           S7509         8.30           S7506         9                                 |           |      |

| S6846         6.67           S6850         6.70           S68450         6.70           S68450         6.70           S68450         6.70           S6852         6.73           S68452         6.73           S68452         6.73           S68452         6.73           S68454         6.76           S68454         6.76           S68454         6.76           S9808A         5.24           S9580B         5.39           S9900         7.31           S9901-4         7.27           S9901-4         7.27           S9902         7.38           S9902         7.38           S9902         7.38           S9902         7.38           S9902         7.38           S9902         7.38           S7500         8.31           S7501         8.51           S7502         8.11           S7503         8.11           S7506         8.23           S7508         8.23           S7509         8.30           S7508         8.23           S7519         8                                 |           |      |

| S6850         6.70           S68450         6.70           S68450         6.70           S6852         6.73           S68452         6.73           S68452         6.73           S68452         6.73           S68454         6.76           S68854         6.76           S68854         6.76           S68854         6.76           S68854         5.24           S9580B         5.39           S9900         7.31           S9901         7.27           S9901         7.27           S9902         7.38           S9902         7.38           S9902.4         7.27           S980A         7.10           S7501         8.31           S7502         8.11           S7503         8.11           S7506         8.23           S7508         8.23           S7509         8.30           S7508         8.23           S7519         8.30           S78C06         9.31                                                                                                                      |           |      |

| S68A50         6.70           S68B50         6.73           S68D52         6.73           S68D52         6.73           S68D52         6.73           S68D52         6.73           S68D52         6.73           S68D54         6.76           S68D54         6.76           S68D54         6.76           S68D54         6.76           S9808A         5.24           S9500B         5.39           S9900         7.31           S9901         7.27           S9901         7.27           S9902.4         7.27           S9980A         7.10           S7500         8.31           S7501         8.51           S7502         8.11           S7503         8.11           S7506         8.23           S7508         8.23           S7509         8.30           S7508         8.23           S7509         8.30           S7508         8.23           S7509         8.30           S7508         9.31                                                                                       |           |      |

| S68B50         6.70           S6852         6.73           S68A52         6.73           S68B52         6.73           S68B52         6.73           S68B52         6.73           S68B52         6.73           S68B54         6.76           S68B54         6.76           S9508A         5.24           S9508A         5.24           S9901         7.27           S9901-4         7.27           S9902         7.38           S9902-4         7.27           S9900         8.31           S7501         8.51           S7502         8.11           S7503         8.11           S7506         8.23           S7508         8.23           S7509         8.30           S7509         8.30           S7508         8.23           S7508         8.23           S7506         9.31                                                                                                                                                                                                             |           |      |

| S6852         6.73           S68A52         6.73           S68B52         6.73           S68B52         6.73           S68B54         6.76           S68A54         6.76           S68B54         6.76           S9508A         5.24           S9508A         5.39           S9900         7.31           S9901         7.27           S9902         7.38           S9902.4         7.27           S980A         7.10           S7500         8.31           S7501         8.51           S7502         8.11           S7506         8.23           S7508         8.23           S7509         8.30           S7508         8.23           S7509         8.30           S7508         8.23           S7508         8.23           S7509         8.30           S7508         9.31                                                                                                                                                                                                                 |           |      |

| S68A52         6.73           S68B52         6.73           S68B52         6.73           S6854         6.76           S68A54         6.76           S68B54         6.76           S9508A         5.24           S9508A         5.39           S9900         7.31           S9901         7.27           S9901.4         7.27           S9902.4         7.27           S980A         7.10           S7500         8.31           S7501         8.51           S7502         8.11           S7506         8.11           S7507         8.23           S7508         8.23           S7509         8.30           S7508         8.23           S7509         8.30           S7508         9.31                                                                                                                                                                                                                                                                                                       |           |      |

| S68B52         6.73           S6854         6.76           S68A54         6.76           S68B54         6.76           S68B54         6.76           S9508A         5.24           S9508A         5.23           S9900         7.31           S9901         7.27           S9901.4         7.27           S9902.4         7.38           S7500         8.31           S7502         8.11           S7503         8.11           S7506         8.12           S7508         8.23           S7509         8.30           S7508         8.23           S7519         8.30                                                                                                                                                                                                                                                                                                                                                                                                                            |           |      |

| S68A54         6.76           S68B54         6.76           S9508A         5.24           S9580B         5.39           S9900         7.31           S9901         7.27           S9902.4         7.27           S9980A         7.10           S7500         8.31           S7501         8.51           S7503         8.11           S7506         8.17           S7508         8.23           S7509         8.30           S7508         8.23           S7519         8.31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |      |

| S68A54         6.76           S68B54         6.76           S9508A         5.24           S9580B         5.39           S9900         7.31           S9901         7.27           S9902.4         7.27           S9980A         7.10           S7500         8.31           S7501         8.51           S7503         8.11           S7506         8.17           S7508         8.23           S7509         8.30           S7508         8.23           S7519         8.31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | S6854     | 6.76 |

| S9508A         5.24           S9580B         5.39           S9900         7.31           S9901         7.27           S9901.4         7.27           S9902.4         7.38           S7501         8.31           S7502         8.11           S7506         8.11           S7507         8.23           S7508         8.23           S7509         8.30           S7508         8.23           S7509         8.30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | S68A54    |      |

| S9580B         5.39           S9900         7.31           S9901         7.27           S9901.4         7.27           S9902         7.38           S9904         7.10           S7500         8.31           S7502         8.11           S7503         8.11           S7506         8.23           S7508         8.23           S7519         8.30           S78C06         9.31                                                                                                                                                                                                                       | S68B54    | 6.76 |

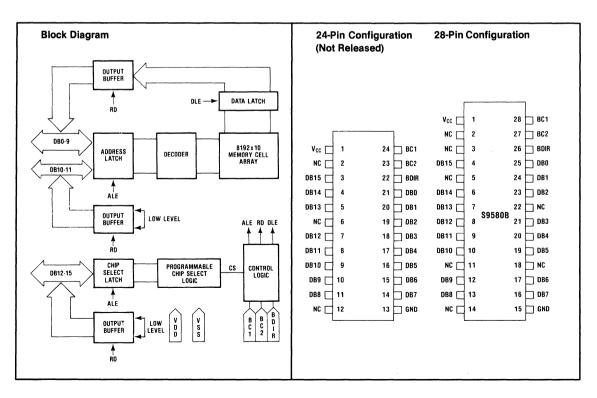

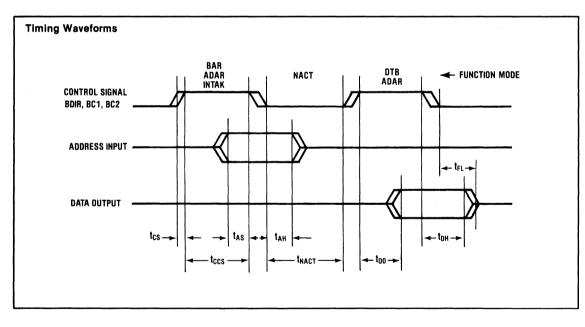

| S9900         7.31           S9901         7.27           S9901-4         7.27           S9902         7.38           S9902.         7.38           S9902.         7.38           S9902.         7.31           S9902.         7.38           S9902.         7.38           S9902.         7.38           S9902.         7.38           S9902.         7.31           S7500         8.31           S7501         8.51           S7502         8.11           S7503         8.11           S7506         8.17           S7507         8.23           S7508         8.23           S7519         8.30           S78C06         9.31                                                                                                                                                                                                                                                                                                                                                                 | S9508A    | 5.24 |

| S9901         7.27           S9901-4         7.27           S9902         7.38           S9902-4         7.27           S9980A         7.10           S7500         8.31           S7501         8.51           S7502         8.11           S7506         8.17           S7507         8.23           S7508         8.23           S7519         8.30           S78C06         9.31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | S9580B    | 5.39 |

| S9901-4         7.27           S9902         7.38           S9902.4         7.27           S9980A         7.10           S7500         8.31           S7501         8.51           S7502         8.11           S7506         8.11           S7506         8.17           S7507         8.23           S7508         8.23           S7519         8.30           S78C06         9.31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | S9900     |      |

| S9902         7.38           S9902-4         7.27           S9980A         7.10           S7500         8.31           S7501         8.51           S7502         8.11           S7506         8.17           S7507         8.23           S7508         8.23           S7519         8.30           S78C06         9.31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | S9901     | 7.27 |

| S9902-4         7.27           S9980A         7.10           S7500         8.31           S7501         8.51           S7502         8.11           S7506         8.11           S7507         8.23           S7508         8.23           S7509         8.30           S7508         8.30           S78C06         9.31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | S9901-4   | 7.27 |

| S9980A         7.10           S7500         8.31           S7501         8.51           S7502         8.11           S7503         8.11           S7506         8.17           S7507         8.23           S7508         8.23           S7509         8.30           S7508         9.31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           |      |

| S7500         8.31           S7501         8.51           S7502         8.11           S7503         8.11           S7506         8.17           S7507         8.23           S7508         8.23           S7519         8.30           S78C06         9.31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |      |

| S7501         8.51           S7502         8.11           S7503         8.11           S7506         8.17           S7507         8.23           S7508         8.23           S7519         8.30           S78C06         9.31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           |      |

| S7502         8.11           S7503         8.11           S7506         8.17           S7507         8.23           S7508         8.23           S7519         8.30           S78C06         9.31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |      |

| S7503         8.11           S7506         8.17           S7507         8.23           S7508         8.23           S7519         8.30           S78C06         9.31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |      |

| S7506         8.17           S7507         8.23           S7508         8.23           S7519         8.30           S78C06         9.31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |      |

| S7507         8.23           S7508         8.23           S7519         8.30           S78C06         9.31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |      |

| S7508         8.23           S7519         8.30           S78C06         9.31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |      |

| S7519 8.30<br>S78C06 9.31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |      |

| S78C06 9.31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |      |

| 5/5/7 9.51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0/011     | 9.01 |

### **Functional Index**

| Device                                                                                                                                                                                                                                                                                              | Page                                                                                                                                                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Communications Produ                                                                                                                                                                                                                                                                                | cts                                                                                                                                                                                                                              |

| Communications Produ<br>Station Products<br>S2550A<br>S2559A<br>S2559B<br>S2559C<br>S2559C<br>S2559C<br>S2559C<br>S2559C<br>S2559C<br>S2559G<br>S2559G<br>S2559G<br>S2559G<br>S2559G<br>S2559G<br>S2559G<br>S2560A<br>S2560A<br>S2560A<br>S2560A<br>S2560A<br>S2560A<br>S2561/C<br>S2561A<br>S2561A | 3.3         3.10         3.10         3.10         3.10         3.10         3.21         3.21         3.21         3.21         3.21         3.21         3.23         3.28         3.28         3.37         3.37         3.37 |

| S2561C<br>S2563<br>S2569<br>S2569A<br>S2569B<br>S25089<br>S25610<br>S25610E<br>S25910<br>PCM Products<br>S3501<br>S3502<br>S3506<br>S3507<br>S3507A                                                                                                                                                 | 3.37<br>3.45<br>3.46<br>3.53<br>3.61<br>3.67<br>3.75<br>3.83<br>3.86<br>3.86<br>3.88<br>3.88<br>3.88<br>3.88                                                                                                                     |

| Signal Processors           RTDS28212           SSPP28211           S28211           S28212           S28214           S28215           S28216                                                                                                                                                      | 3.90<br>3.92<br>3.93<br>3.95<br>3.99<br>3.118<br>3.122                                                                                                                                                                           |

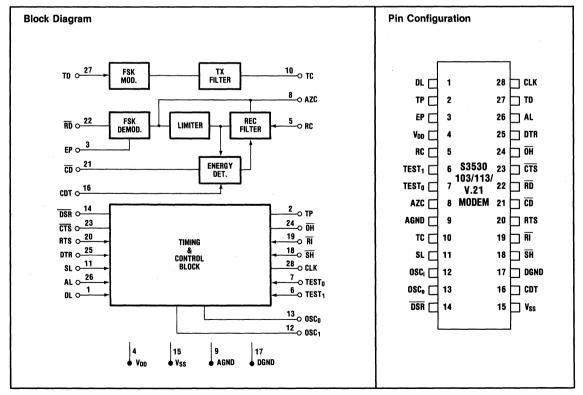

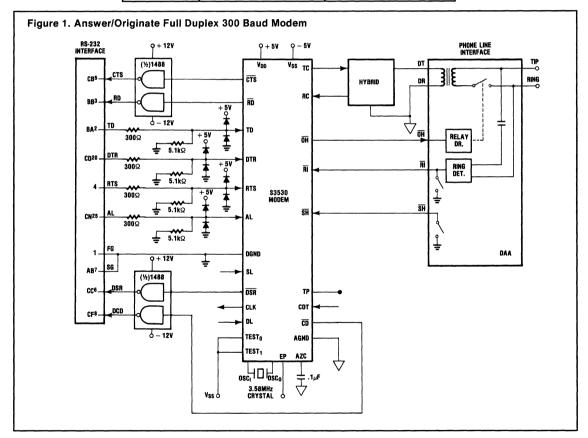

| Modems and Filters           S3522           S35212           S3525           S3525A           S3525B           S3526           S3528           S3528                                                                                                                                               | 3.125<br>3.131<br>3.133<br>3.133<br>3.133<br>3.140<br>3.140<br>3.147<br>3.156                                                                                                                                                    |

| Device                                                                                                   | Page                                                                                 |

|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Consumer Products                                                                                        |                                                                                      |

| Driver Circuits<br>S2809<br>S4535<br>S4534<br>S4521                                                      | 4.17<br>4.21<br>4.24<br>4.27                                                         |

| Speech Products                                                                                          |                                                                                      |

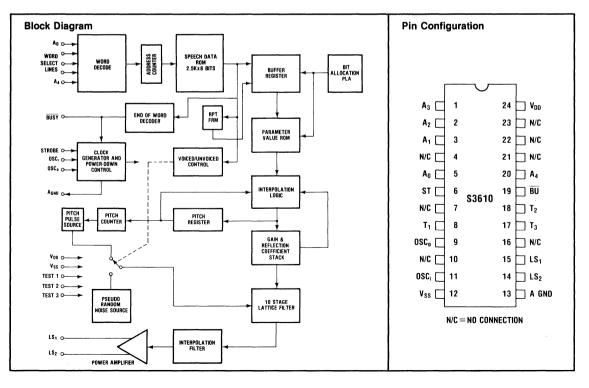

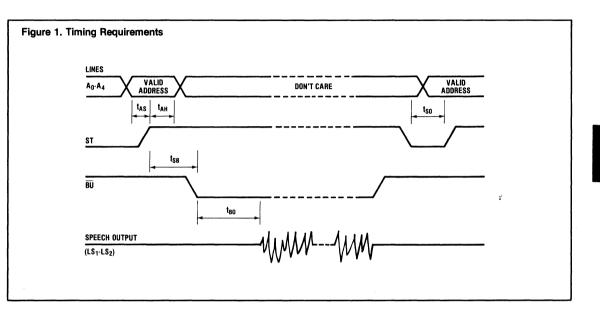

| S3610<br>S3620                                                                                           | 4.3<br>4.10                                                                          |

| Remote Control Circuits                                                                                  |                                                                                      |

| S2600<br>S2601<br>S2602<br>S2603<br>S2604<br>S2605<br>S2742<br>S2742<br>S2743<br>S2743<br>S2747<br>S2748 | 4.30<br>4.33<br>4.33<br>4.36<br>4.36<br>4.36<br>4.42<br>4.42<br>4.42<br>4.45<br>4.45 |

| S2748                                                                                                    | 4.43<br>4.52<br>4.54<br>4.60<br>4.62<br>4.65<br>4.65<br>4.65                         |

| S2709A                                                                                                   | 4.68<br>4.71                                                                         |

| A/D Converter and Digital                                                                                |                                                                                      |

| Scale Circuit<br>S4036                                                                                   | 4.75                                                                                 |

| Memory Products                                                                                          |                                                                                      |

| RAMs                                                                                                     |                                                                                      |

| S6810<br>S68A10<br>S68B10<br>S5101L<br>S5101L-1<br>S6501L<br>S6514<br>S6516                              | 6.79<br>6.79<br>6.79<br>5.2<br>5.2<br>5.2<br>5.2<br>5.2<br>5.2<br>5.3<br>5.7         |

| Davias             | Deee         |

|--------------------|--------------|

| Device             | Page         |

| ROMs               |              |

| S68A316            | 5.15         |

| S68A332<br>S68B332 | 5.18<br>5.18 |

| S2333              | 5.21         |

| S9508A             | 5.24         |

| S68A364            | 5.29         |

| S68B364            | 5.29         |

| S2364A             | 5.32         |

| S2364B<br>S9580B   | 5.32<br>5.39 |

| S9580B             | 5.39<br>5.45 |

| S23126A            | 5.49         |

| S23256C            | 5.49         |

| Microprocessors/   |              |

| Microcomputers     |              |

| S6800 Family       |              |

| S6800              | 6.3          |

| S68A00             | 6.3          |

| S68B00             | 6.3          |

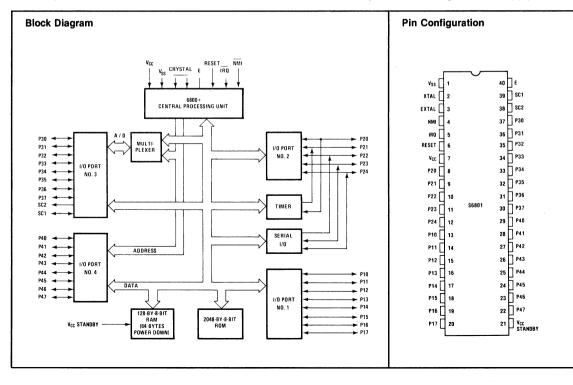

| S6801              | 6.9          |

| S6802<br>S68A02    | 6.12<br>6.12 |

| S68A02<br>S68B02   | 6.12         |

| S6808              | 6.12         |

| S68A08             | 6.12         |

| S68B08             | 6.12         |

| S6803              | 6.2          |

| S6803N/R           | 6.2          |

| S6805<br>S6809     | 6.14<br>6.32 |

| S6809<br>S68A09    | 6.32<br>6.32 |

| S68B09             | 6.32         |

| S6809(E)           | 6.33         |

| S68A09(E)          | 6.33         |

| S68B09(E)          | 6.33         |

| S1602              | 6.35         |

| S2350<br>S6551     | 6.43<br>6.46 |

| S6551              | 6.46         |

| S6821              | 6.52         |

| S68A21             | 6.52         |

| S68B21             | 6.52         |

| S6840              | 6.60         |

S68A40 ..... 6.60

S68B40 ..... 6.60

S68045 ..... 6.64

S6846 ..... 6.67

S6850 ..... 6.70

### **Functional Index**

| Device                 | Page  |

|------------------------|-------|

| Microprocessor/        |       |

| Microcomputers (Contin | iuea) |

| 6800 Family            |       |

| S68A50                 | 6.70  |

| S68B50                 | 6.70  |

| S6852                  | 6.73  |

| S68A52                 | 6.73  |

| S68B52                 | 6.73  |

| S6854                  | 6.76  |

| S68A54                 | 6.76  |

| S68B54                 | 6.76  |

| S6810                  | 6.79  |

| S68A10                 | 6.79  |

| S68B10                 | 6.79  |

| S6810-1                | 6.2   |

| Device<br>9900 Family                                                                  | Page                                                       |

|----------------------------------------------------------------------------------------|------------------------------------------------------------|

| S9900                                                                                  | 7.3<br>7.10<br>7.15<br>7.27<br>7.27<br>7.38<br>7.38        |

| 7500 Family                                                                            |                                                            |

| \$7500<br>\$7501<br>\$7502<br>\$7503<br>\$7506<br>\$7506<br>\$7507<br>\$7508<br>\$7508 | 8.3<br>8.5<br>8.11<br>8.11<br>8.17<br>8.23<br>8.23<br>8.30 |

| Device               | Page |

|----------------------|------|

| 7800 Family          |      |

| S78C06               | 9.3  |

| S7811                | 9.5  |

| Semi-Custom Products |      |

| Gate Arrays          | 1.5  |

| Standard Cells       | 1.17 |

|                      |      |

INDICES

### **Cross Reference Guide**

### **Communication Products**

### **Cross Reference by Manufacturer**

| Manufacturer | Part Number      | AMI Functional<br>Equivalent Part | Manufacturer | Part Number | AMI Functional<br>Equivalent Part |

|--------------|------------------|-----------------------------------|--------------|-------------|-----------------------------------|

| G.I.         | SPR 128          | 3630                              | Mostek       | MK 50982    | 2560A                             |

| G.I.         | ACF 7310,12,7410 | 3526                              | Mostek       | MK 50991    | 2560A                             |

| G.I.         | ACF 7323C        | 3525                              | Mostek       | MK 50992    | 2560A                             |

| G.I.         | ACF 7363C        | 3525                              | Mostek       | MK 5116     | 3501/3502, 3507                   |

| G.I.         | ACF 7383C        | 3525                              | Mostek       | MK 5151     | 3501/3502, 3507                   |

| G.I.         | AY5-9100         | 2560A                             | Mostek       | MK 5156     | 3503/3504, 3506                   |

| G.I.         | AY5-9151         | 2560A                             | Mostek       | MK 5170     | 2562/2563                         |

| G.I.         | AY5-9152         | 2560A                             | Mostek       | MK 5175     | 25610                             |

| G.I.         | AY5-9153         | 2560A                             | Mostek       | MK 5387     | 2559                              |

| G.I.         | AY5-9154         | 2560A                             | Mostek       | MK 5389     | 25089                             |

| G.I.         | AY5-9158         | 2560A                             | Motorola     | MC 14400    | 3507                              |

| G.I.         | AY5-9200         | 2562/2563                         | Motorola     | MC 14401    | 3507                              |

| G.I. ·       | AY3-9400         | 2559                              | Motorola     | MC 14402    | 3507                              |

| G.I.         | AY3-9401         | 2559                              | Motorola     | MC 14406    | 3501/3502                         |

| G.I.         | AY3-9410         | 2559                              | Motorola     | MC 14408    | 2560A                             |

| G.I.         | AY5-9800         | 3525                              | Motorola     | MC 14409    | 2560A                             |

| G.I.         | AY3-9900         | 3501/3502                         | National     | MM 5393     | 2560A                             |

| Hitachi      | HD 44211         | 3507                              | National     | MM 5395     | 2559                              |

| Hitachi      | HD 44231         | 3506                              | NEC          | μPD 7720    | 2811                              |

| Intel        | 2364             | 3630                              | Nitron       | NC 320      | 2560A                             |

| Intel        | 2910/2912        | 3501/2                            | OKI          | MSM 38128   | 3630                              |

| Intel        | 2913             | 3507                              | Phillips     | TDA 1077    | 2559                              |

| Intel        | 2914             | 3507                              | RCA          | CD 22859    | 2559                              |

| Intersil     | ICM 7206         | 2559                              | SSI          | SSI 201     | 3525                              |

| Mitel        | MT 4320          | 3525                              | Siliconix    | DF 320      | 2560A                             |

| Mitel        | ML 8204          | 2561A                             | Siliconix    | DF 321      | 2560A                             |

| Mitel        | ML 8205          | 2561A                             | Siliconix    | DF 322      | 2560A                             |

| Mitel        | MT 8865          | 3525                              | Siliconix    | DF 341      | 3501/3502                         |

| Mostek       | MK 5087          | 2559E                             | Siliconix    | DF 342      | 3501/3502                         |

| Mostek       | MK 5089          | 25089                             | Supertex     | CM 1310     | 3630                              |

| Mostek       | MK 50981         | 2560A                             |              |             |                                   |

## **Cross Reference Guide**

### **Communication Products**

### Cross Reference by Part Number

| Manufacturer | Part Number | AMI Functional<br>Equivalent Part |

|--------------|-------------|-----------------------------------|

| TDA 1077     | Phillips    | 2559                              |

| SPR 128      | G.I.        | 3630                              |

| CM 1310      | Supertex    | 3630                              |

| MC 14400     | Motorola    | 3507                              |

| MC 14401     | Motorola    | 3507                              |

| MC 14402     | Motorola    | 3507                              |

| MC 14406     | Motorola    | 3501/3502                         |

| MC 14408     | Motorola    | 2560A                             |

| MC 14409     | Motorola    | 2560A                             |

| SSI 201      | SSI         | 3525                              |

| CD 22859     | RCA         | 2559                              |

| 2364         | Intel       | 3630                              |

| 2910/2912    | Intel       | 3501/2                            |

| 2913         | Intel       | 3507                              |

| 2914         | Intel       | 3507                              |

| DF 320       | Siliconix   | 2560A                             |

| NC 320       | Nitron      | 2560A                             |

| DF 321       | Siliconix   | 2560A                             |

| DF 322       | Siliconix   | 2560A                             |

| DF 328       | Siliconix   | 2560A                             |

| DF 341       | Siliconix   | 3501/3502                         |

| DF 342       | Siliconix   | 3501/3502                         |

| MSM 38128    | ОКІ         | 3630                              |

| MT 4320      | Mitel       | 3525                              |

| HD 44211     | Hitachi     | 3507                              |

| HD 44231     | Hitachi     | 3506                              |

| MK 5087      | Mostek      | 2559E                             |

| MK 5089      | Mostek      | 25089                             |

| MK 50981     | Mostek      | 2560A                             |

| MK 50982     | Mostek      | 2560A                             |

| MK 50991     | Mostek      | 2560A                             |

| Manufacturer     | Part Number | AMI Functional<br>Equivalent Part |

|------------------|-------------|-----------------------------------|

| MK 50992         | Mostek      | 2560A                             |

| MK 5116          | Mostek      | 3501/3502, 3507                   |

| MK 5151          | Mostek      | 3501/3502, 3507                   |

| MK 5156          | Mostek      | 3503/3504, 3506                   |

| MK 5170          | Mostek      | 2562/2563                         |

| MK 5175          | Mostek      | 25610                             |

| MK 5387          | Mostek      | 2559                              |

| MK 5389          | Mostek      | 25089                             |

| MM 5393          | National    | 2560A                             |

| MM 5395          | National    | 2559                              |

| ICM 7206         | Intersil    | 2559                              |

| ACF 7310,12,7410 | G.I.        | 3526                              |

| ACF 7323C        | G.I.        | 3525                              |

| ACF 7363C        | G.I.        | 3525                              |

| ACF 7383C        | G.I.        | 3525                              |

| μPD 7720         | NEC         | 2811                              |

| ML 8204          | Mitel       | 2561A                             |

| ML 8205          | Mitel       | 2561A                             |

| MT 8865          | Mitel       | 3525                              |

| AY5 9100         | G.I.        | 2560A                             |

| AY5 9151         | G.I.        | 2560A                             |

| AY5 9152         | G.I.        | 2560A                             |

| AY5 9153         | G.1.        | 2560A                             |

| AY5 9154         | G.I.        | 2560A                             |

| AY5 9158         | G.I.        | 2560A                             |

| AY5 9200         | G.I.        | 2562/2563                         |

| AY3 9400         | G.I.        | 2559                              |

| AY3 9401         | G.I.        | 2559                              |

| AY3 9410         | G.I.        | 2559                              |

| AY5 9800         | G.I.        | 3525                              |

| AY3 9900         | G.I.        | 3501/3502                         |

## **Cross Reference Guide**

### **Memory Products**

| CMOS RAMs                     |                          |                          |                      |                      |  |  |  |

|-------------------------------|--------------------------|--------------------------|----------------------|----------------------|--|--|--|

| Vendor                        | 256 × 4                  | 1K×1                     | 1K×4                 | 4K × 1               |  |  |  |

| AMI                           | S5101                    |                          | S6514                |                      |  |  |  |

| FUJITSU                       |                          |                          | 6514/8414            | 8404                 |  |  |  |

| HARRIS<br>HITACHI<br>INTERSIL | 6561<br>435101<br>6551   | 6508<br>—<br>6508        | 6514<br>4334<br>6514 | 6504<br>4315<br>6504 |  |  |  |

| MOTOROLA<br>NATIONAL<br>NEC   | 145101<br>74C920<br>5101 | 146508<br>74C929<br>6508 | 6514<br>444/6514     | 146504<br>6504       |  |  |  |

| OKI<br>RCA                    | 573<br>5101              | 574<br>1821              | 5115<br>1825         | 5104                 |  |  |  |

| SSS<br>TOSHIBA                | 5101<br>5101             | 5102<br>5508             | 5514                 | <br>5504             |  |  |  |

|           |           |           | BYTE WI  | DE NMOS ROMs      |                               |          |          |

|-----------|-----------|-----------|----------|-------------------|-------------------------------|----------|----------|

| Vendor    | 2K × 8    | 4K × 8    | 4K × 8*  | 8K 	imes 8-24 Pin | $8 \mathrm{K} 	imes 8-28$ Pin | 16K × 8  | 32K × 8  |

| AMI       | S68A316   | S68A332   | S2333    | S68A364           | S2364A                        | S23128A  | S23256B  |

| AMD       | AM9218    | 9232      | 9233     | AM9264            | AM9265                        | AM92128  |          |

| NEC/EA    | µPD2316   | µPD2332A  | µPD2332B | µPD8364           | µPD2364                       | µPD23128 | µPD23256 |

| FAIRCHILD | F68316    | F3532     | F3533    | F3564             |                               |          |          |

| FUJITSU   |           |           |          |                   |                               |          |          |

| GI        | R03-9316  |           | R03-9333 | R03-9364          | R03-9365                      | SPR-128  |          |

| GTE       | 2316      | 2332      |          | 2364              |                               |          |          |

| MOS       |           |           |          | MPS2364           |                               |          |          |

| MOSTEK    | MK34000   |           |          | MK36000           | MK37000                       |          | MK38000  |

| MOTOROLA  | MCM68A316 | MCM68A332 |          | MCM68365          |                               |          | MCM65256 |

| SIGNETICS | 2616      | 2632      |          | 2664A             | 2664AM                        | 23128    | 23256    |

| SYNERTEK  | SY2316    | SY2332    | SY2333   | SY2364            | SY2365                        | SY23128  | SY23256  |

| OKI       | MSM2916   |           |          |                   |                               |          |          |

| ROCKWELL  | R2316     | R2332     |          | R2364A            | R2364B                        |          |          |

| SGS       | M2316     |           |          |                   |                               |          |          |

| TOSHIBA   | TSU2316   |           | TSU333-2 |                   |                               |          |          |

| NATIONAL  |           | MM52132   |          | MM52164           |                               |          |          |

| VTI       |           | VT2332    | VT2333   |                   | VT2365A                       | VT23129  | VT23256  |

\*Pin compatible with 2732 EPROM

## **Microprocessor Family**

|             |                                                                     | / | A FERRE |             | - jor       | 2. Series | REPLACES                                                                                 |

|-------------|---------------------------------------------------------------------|---|---------|-------------|-------------|-----------|------------------------------------------------------------------------------------------|

| DEVICE      | DESCRIPTION                                                         |   | /       | /           | °/*         |           | REPLACES                                                                                 |

| \$1602      | UART (UNIVERSAL ASYNCHRONOUS<br>Receiver/transmitter)               |   |         | P<br>C<br>D | P<br>C<br>D |           | S1883, MB8868A, AY-5-1013, AY-3-1015, TR1863,<br>TR1602, TMS6011, NATIONAL 5303, SMC2502 |

| \$2350      | USRT (UNIVERSAL SYNCHRONOUS<br>Receiver/transmitter)                |   |         | P<br>C<br>D | P<br>C<br>D |           |                                                                                          |

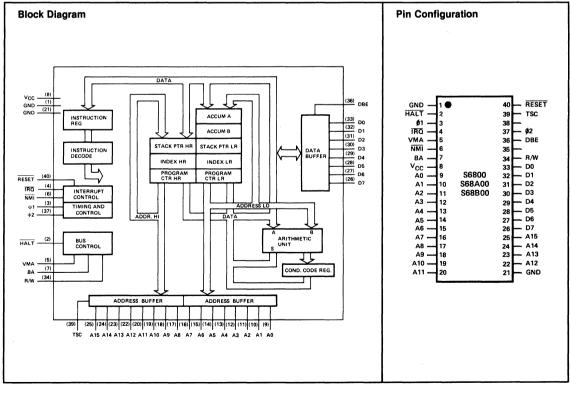

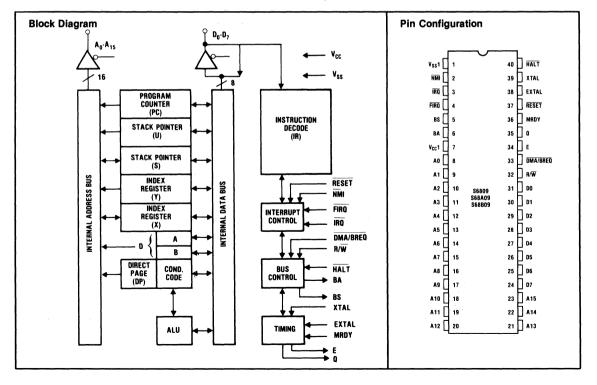

| S6800       | MPU (MICROPROCESSOR)                                                | x | x       | P<br>C<br>D | P<br>C<br>D |           | MC6800, HD46800D, F6800                                                                  |

| S6801       | 8-BIT MICROCOMPUTER 2K ROM,<br>128 Bytes Ram, Uart, Timer, 1/0      |   |         | P<br>C<br>D | C<br>D      | x         | MC6801, HD6801X                                                                          |

| S6802       | 8-BIT MICROPROCESSOR WITH CLOCK<br>AND 128 BYTES RAM                | X | X       | P<br>C      | P<br>C      |           | MC6802, HD46802, F6802                                                                   |

| \$6803      | S6801 WITHOUT ROM                                                   |   |         | P<br>C<br>D | C           |           | MC6803                                                                                   |

| S6803NR     | S6803 WITHOUT RAM                                                   |   |         | P<br>C<br>D | C           |           | MC6803NR                                                                                 |

| S6805       | 8-BIT MICROCOMPUTER WITH 1.1K BYTES<br>Rom, 64 Bytes RAM, Timer, Vo |   | _       | P<br>C<br>D | P<br>C<br>D | x         | MC6805P2, HD6805S                                                                        |

| S6808       | MICROPROCESSOR AND CLOCK                                            | x | x       | P<br>C      | P<br>C      |           | MC6808, HD46808, F6808                                                                   |

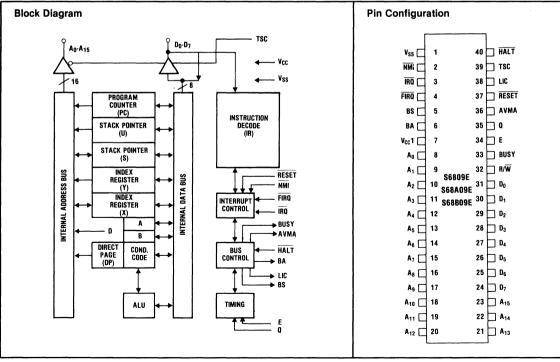

| S6809       | ENHANCED 8-BIT MPU                                                  | X | X       | P<br>C<br>D | P<br>C<br>D |           | MC6809, HD6809, F6809E                                                                   |

| S6809E      | ENHANCED 8-BIT MPU EXTERNAL<br>CLOCK INPUT                          |   |         | P<br>C<br>D | P<br>C<br>D |           | MC6809E, HD6809E, F6809E                                                                 |

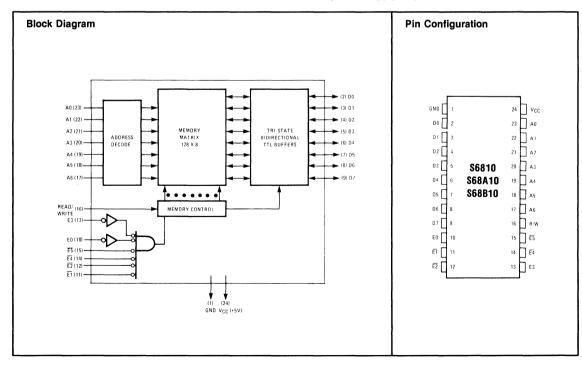

| S6810       | RAM (128x8)                                                         | x | x       | P<br>C<br>D | P<br>C<br>D |           | MC6810, HD46810, F6810                                                                   |