# MB86294/294S <CORAL\_LB> Graphics Controller Specifications

Revision 1.2 19th Apr, 2004

Copyright © FUJITSU LIMITED 2001 ALL RIGHTS RESERVED <Notes>

✓!\CAUTION

• The specifications in this manual are subject to change without notice. Contact our Sales Department before purchasing the product described in this manual.

• Information and circuit diagrams in this manual are only examples of device applications, they are not intended to be used in actual equipment. Also, Fujitsu accepts no responsibility for infringement of patents or other rights owned by third parties caused by use of the information and circuit diagrams.

• The contents of this manual must not be reprinted or duplicated without permission of Fujitsu.

• Fujitsu's semiconductor devices are intended for standard uses (such as office equipment (computers and OA equipment), industrial/communications/measuring equipment, and personal/home equipment). Customers using semiconductor devices for special applications (including aerospace, nuclear, military and medical applications) in which a failure or malfunction might endanger life or limb and which require extremely high reliability must contact our Sales Department first. If damage is caused by such use of our semiconductor devices without first consulting our Sales Department, Fujitsu will not assume any responsibility for the loss.

• Semiconductor devices fail with a known probability. Customers must use safety design (such as redundant design, fireproof design, over-current prevention design, and malfunction prevention design) so that failures will not cause accidents, injury or death).

• If the products described in this manual fall within the goods or technologies regulated by the Foreign Exchange and Foreign Trade Law, permission must be obtained before exporting the goods or technologies.

Burns There is a danger of burns because the IC surface is heated depending on the IC operating conditions. In this case, take safety measures.

# Update history

| Date       | Version | Page count | Change                        |

|------------|---------|------------|-------------------------------|

| 2003.1.31  | 1.0     | 303        | First release                 |

| 2003.10.27 | 1.1     | 303        | Refer Rev10vsRev11Diff_e file |

| 2004.4.19  | 1.2     | 303        | Refer Rev11vsRev12Diff_e file |

|            |         |            |                               |

|            |         |            |                               |

|            |         |            |                               |

|            |         |            |                               |

|            |         |            |                               |

|            |         |            |                               |

#### CONTENTS

| 1 | GENE  | RAL                                       | . 11        |

|---|-------|-------------------------------------------|-------------|

|   | 1.1   | PREFACE                                   | 11          |

|   | 1.2   | FEATURES                                  | . 12        |

|   | 1.3   | BLOCK DIAGRAM                             | . 13        |

|   | 1.4   | FUNCTIONAL OVERVIEW                       | . 14        |

|   | 1.4.1 | Host CPU interface                        | . 14        |

|   | 1.4.2 | External memory interface                 | . 16        |

|   | 1.4.3 | Display controller                        | . 17        |

|   | 1.4.4 | Video Capture                             | . 19        |

|   | 1.4.5 | Geometry processing                       | . 19        |

|   | 1.4.6 | 2D Drawing                                | . 20        |

|   | 1.4.7 | 3D Drawing                                | . 22        |

|   | 1.4.8 | Special effects                           | . 23        |

|   | 1.4.9 | Others                                    | . 26        |

| 2 | PINS  |                                           | . 27        |

|   | 2.1   | SIGNALS                                   | . 27        |

|   | 2.1.1 | Signal lines                              | . 27        |

|   | 2.2   | PIN ASSIGNMENT                            | . 28        |

|   | 2.2.1 | PBGA256 Pin assignment diagram (TOP_VIEW) | . <i>28</i> |

|   | 2.2.2 | PBGA256 Pin assignment table              | . <i>29</i> |

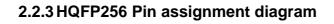

|   | 2.2.3 | HQFP256 Pin assignment diagram            | . 30        |

|   | 2.2.4 | HQFP256 Pin assignment table              | . 31        |

|   | 2.3   | PIN FUNCTION                              | . 35        |

|   | 2.3.1 | Host CPU interface                        | . 35        |

|   | 2.3.2 | Video output interface                    | . 37        |

|   | 2.3.3 | Video Capture interface                   | . 38        |

|   | 2.3.4 | Graphics memory interface                 | . 39        |

|   | 2.3.5 | Clock input                               | . 40        |

|   | 2.3.6 | Test pins                                 | . 41        |

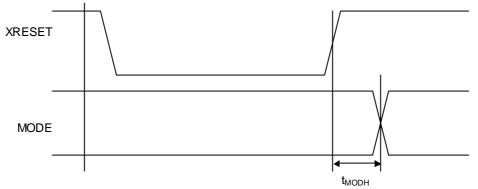

|   | 2.3.7 | Reset sequence                            | . 41        |

| 3 | PROC  | EDURE OF THE HARDWARE INITIALIZATION      | . 42        |

|   | 3.1   | HARDWARE RESET                            | . 42        |

|   | 3.2   | RE-RESET                                  | . 42        |

|   | 3.3   | SOFTWARE RESET                            | . 42        |

| 4 | HOST  | INTERFACE                                 | . 43        |

|   | 4.1          | OPERATION MODE                                      | . 43 |

|---|--------------|-----------------------------------------------------|------|

|   | 4.1.1        | Host CPU mode                                       | . 43 |

|   | <i>4.1.2</i> | Ready signal mode                                   | . 43 |

|   | 4.1.3        | BS signal mode                                      | . 44 |

|   | 4.1.4        | Endian                                              | . 44 |

|   | 4.2          | Access Mode                                         | . 45 |

|   | 4.2.1        | SRAM interface                                      | . 45 |

|   | 4.2.2        | FIFO interface (fixed transfer destination address) | . 45 |

|   | 4.3          | DMA TRANSFER                                        | . 46 |

|   | 4.3.1        | Data transfer unit                                  | . 46 |

|   | 4.3.2        | Address mode                                        | . 46 |

|   | 4.3.3        | Bus mode                                            | . 47 |

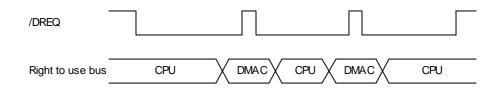

|   | 4.3.4        | DMA transfer request                                | . 47 |

|   | 4.3.5        | Ending DMA transfer                                 | . 47 |

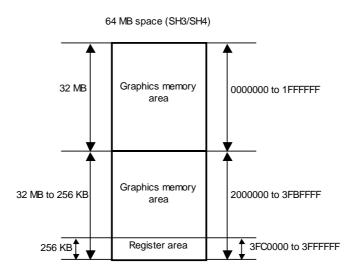

|   | 4.4          | TRANSFER OF LOCAL DISPLAY LIST                      | . 48 |

|   | 4.5          | INTERRUPT                                           | . 49 |

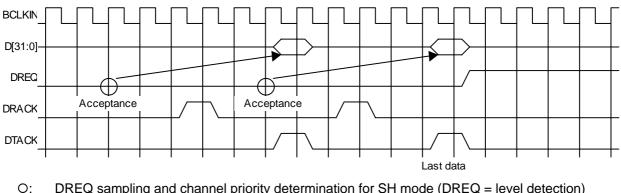

|   | 4.6          | SH3 MODE                                            | . 49 |

|   | 4.7          | WAIT                                                | . 49 |

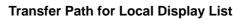

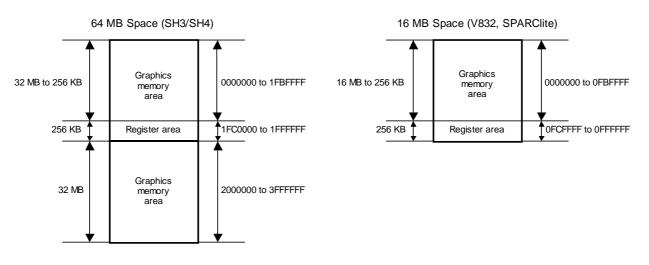

|   | 4.8          | MEMORY MAP                                          | . 50 |

| 5 | GRAF         | PHICS MEMORY                                        | . 52 |

|   | 5.1          | CONFIGURATION                                       | . 52 |

|   | 5.1.1        | Data type                                           | . 52 |

|   | <i>5.1.2</i> | Memory Mapping                                      |      |

|   | 5.1.3        | Data Format                                         |      |

|   | 5.2          | FRAME MANAGEMENT                                    | . 55 |

|   | <i>5.2.1</i> | Single Buffer                                       | . 55 |

|   | 5.2.2        | Double Buffer                                       | . 55 |

|   | 5.3          | MEMORY ACCESS                                       | . 55 |

|   | 5.3.1        | Memory Access by host CPU                           | . 55 |

|   | <i>5.3.2</i> | Priority of memory accessing                        | . 55 |

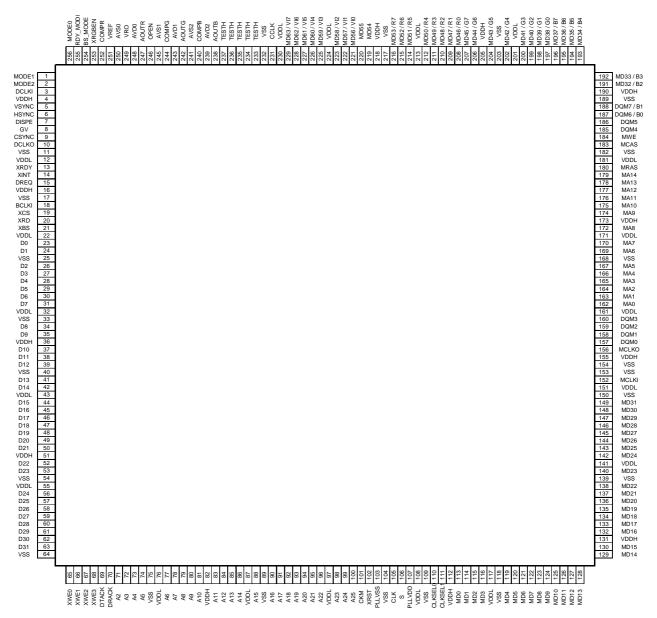

|   | 5.4          | CONNECTION WITH MEMORY                              | . 56 |

|   | 5.4.1        | Connection with memory                              | . 56 |

| 6 | DISPL        | AY CONTROLLER                                       | . 57 |

|   | 6.1          | Overview                                            | 57   |

|   | 6.2          | DISPLAY FUNCTION                                    |      |

|   | 6.2.1        | Layer configuration.                                |      |

|   | 6.2.1        | Overlay                                             |      |

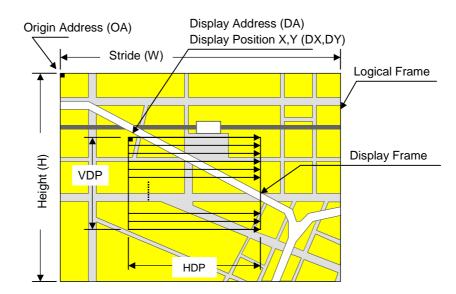

|   | 6.2.2        | Display parameters                                  |      |

|   |              |                                                     |      |

|   | 6.2.4        | Display position control                            |      |

|   | 6.3          | DISPLAY COLOR                                                                              | 64        |

|---|--------------|--------------------------------------------------------------------------------------------|-----------|

|   | 6.4          | CURSOR                                                                                     | 65        |

|   | 6.4.1        | Cursor display function                                                                    | <i>65</i> |

|   | <i>6.4.2</i> | Cursor control                                                                             | 65        |

|   | 6.5          | DISPLAY SCAN CONTROL                                                                       | 66        |

|   | 6.5.1        | Applicable display                                                                         | 66        |

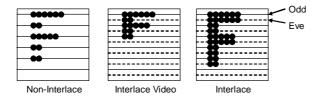

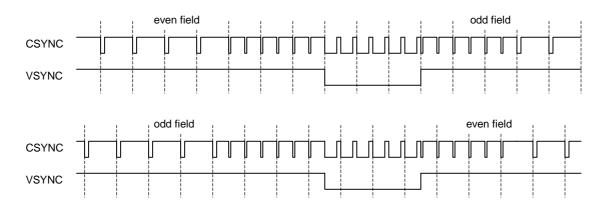

|   | 6.5.2        | Interlace display                                                                          | 67        |

|   | 6.6          | THE EXTERNAL SYNCHRONOUS SIGNAL                                                            | 68        |

|   | 6.7          | VIDEO INTERFACE, NTSC/PAL OUTPUT                                                           | 71        |

| 7 |              | D CAPTURE                                                                                  | 72        |

| ' |              |                                                                                            |           |

|   | 7.1          | FORMAT                                                                                     |           |

|   | 7.1.1        | Input Data Format                                                                          |           |

|   | 7.1.2        | Video Signal Capture                                                                       |           |

|   | 7.1.3        | Non-interlace Transformation                                                               |           |

|   | 7.2          | VIDEO BUFFER                                                                               |           |

|   | 7.2.1        | Data Format                                                                                |           |

|   | 7.2.2        | Synchronous Control                                                                        | 73        |

|   | 7.2.3        | Area Allocation                                                                            | 73        |

|   | 7.2.4        | Window Display                                                                             | 74        |

|   | 7.2.5        | Interlace Display                                                                          | 74        |

|   | 7.3          | SCALING                                                                                    | 75        |

|   | 7.3.1        | Video Reduction Function                                                                   | 75        |

|   | 7.3.2        | Vertical Interpolation                                                                     | 75        |

|   | 7.4          | ERROR HANDLING                                                                             | 75        |

|   | 7.4.1        | Error Detection Function                                                                   | 75        |

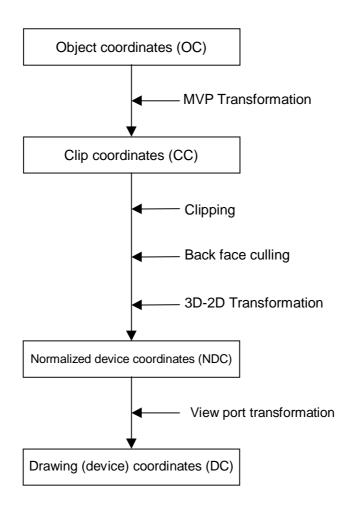

| 8 | GEON         | IETRY ENGINE                                                                               | 76        |

|   | 8.1          | GEOMETRY PIPELINE                                                                          | 76        |

|   | 8.1.1        | Processing flow                                                                            |           |

|   | 8.1.2        | Model-view-projection (MVP) transformation (OC $\rightarrow$ CC coordinate transformation) |           |

|   | 8.1.3        | $3D-2D$ transformation (CC $\rightarrow$ NDC coordinate transformation)                    |           |

|   | 8.1.4        | View port transformation (NDC $\rightarrow$ DC coordinate transformation)                  |           |

|   | 8.1.5        | View volume clipping                                                                       |           |

|   | 8.1.6        | Back face curling                                                                          |           |

|   | 8.2          |                                                                                            |           |

|   | <u>8.2.1</u> | Data format                                                                                |           |

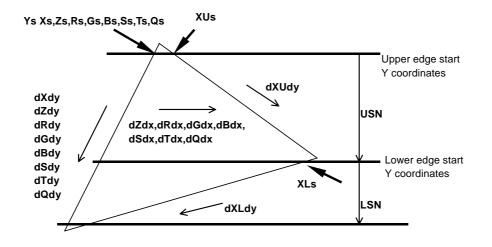

|   | 8.3          | SETUP ENGINE                                                                               |           |

|   | <i>8.3.1</i> | Setup processing                                                                           |           |

|   | 8.4          | Log Output of Device Coordinates                                                           |           |

|   | <i>8.4.1</i> | Log output mode                                                                            |           |

|   | 5. 1. 1      |                                                                                            |           |

|   | <i>8.4.2</i> | Log output destination address       | 82        |

|---|--------------|--------------------------------------|-----------|

| 9 | DRAV         | VING PROCESSING                      | 83        |

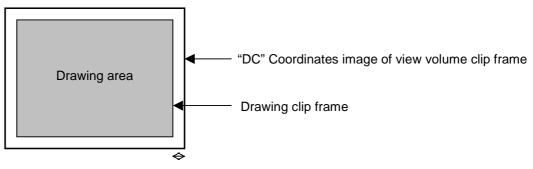

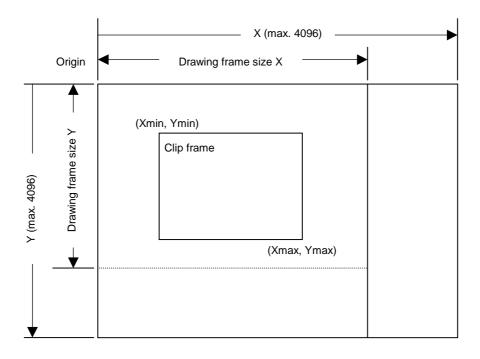

|   | 9.1          | COORDINATE SYSTEM                    | 83        |

|   | 9.1.1        | Drawing coordinates                  | 83        |

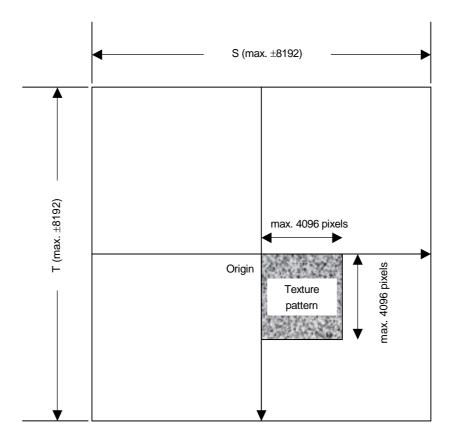

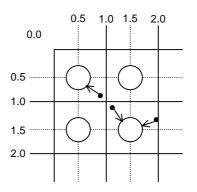

|   | <i>9.1.2</i> | Texture coordinates                  | 84        |

|   | <i>9.1.3</i> | Frame buffer                         | 85        |

|   | 9.2          | FIGURE DRAWING                       | 86        |

|   | <i>9.2.1</i> | Drawing primitives                   | 86        |

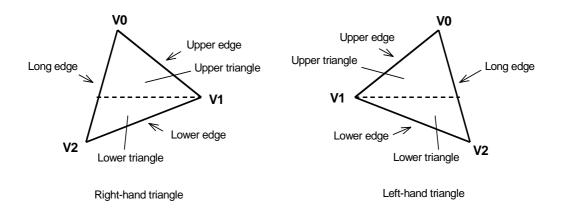

|   | <i>9.2.2</i> | Polygon drawing function             | 86        |

|   | <i>9.2.3</i> | Drawing parameters                   | 87        |

|   | <i>9.2.4</i> | Anti-aliasing function               | 88        |

|   | 9.3          | BIT MAP PROCESSING                   | 89        |

|   | <i>9.3.1</i> | BLT                                  | 89        |

|   | <i>9.3.2</i> | Pattern data format                  | 89        |

|   | 9.4          | Texture Mapping                      |           |

|   | <i>9.4.1</i> | Texture size                         | 90        |

|   | <i>9.4.2</i> | Texture color                        |           |

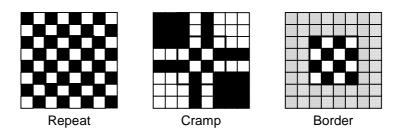

|   | <i>9.4.3</i> | Texture lapping                      |           |

|   | <i>9.4.4</i> | Filtering                            |           |

|   | <i>9.4.5</i> | Perspective correction               |           |

|   | <i>9.4.6</i> | Texture blending                     |           |

|   | <i>9.4.7</i> | Bi-linear high-speed mode            |           |

|   | 9.5          | Rendering                            |           |

|   | <i>9.5.1</i> | Tiling                               |           |

|   | <i>9.5.2</i> | Alpha blending                       |           |

|   | <i>9.5.3</i> | Logic operation                      |           |

|   | 9.5.4        | Hidden plane management              |           |

|   | 9.6          | DRAWING ATTRIBUTES                   |           |

|   | <i>9.6.1</i> | Line drawing attributes              |           |

|   | <i>9.6.2</i> | Triangle drawing attributes          |           |

|   | <i>9.6.3</i> | Texture attributes                   | <i>98</i> |

|   | <i>9.6.4</i> | BLT attributes                       |           |

|   | <i>9.6.5</i> | Character pattern drawing attributes |           |

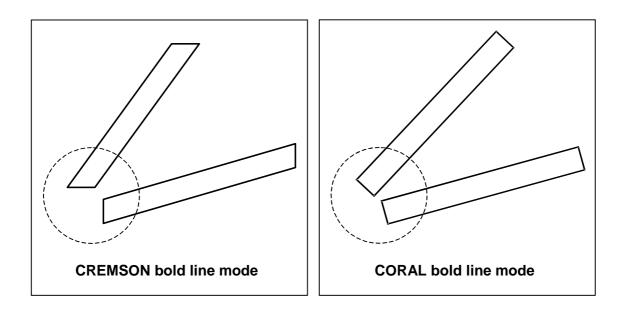

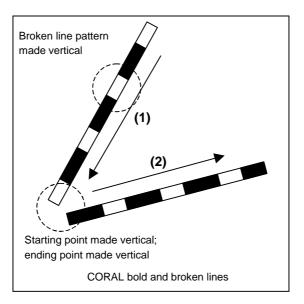

|   | 9.7          | BOLD LINE                            | 100       |

|   | <i>9.7.1</i> | Starting and ending points           | 100       |

|   | <i>9.7.2</i> | Broken line pattern                  | 101       |

|   | <i>9.7.3</i> | Edging                               | 102       |

|   | 9.7.4        | Interpolation of bold line joint     | 103       |

|   | 9.8          | Shadowing                            | 104       |

|    | <i>9.8.1</i>   | Shadowing                                | 104        |

|----|----------------|------------------------------------------|------------|

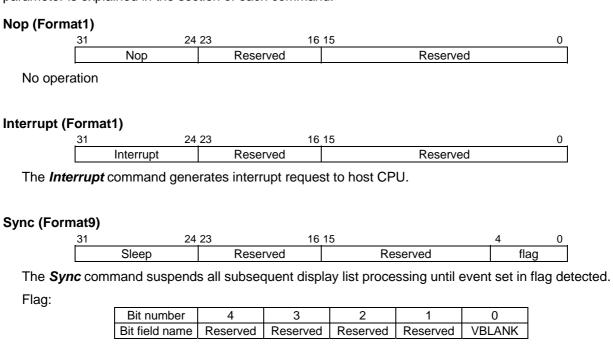

| 10 | DISPLA         | Y LIST                                   | 105        |

| 1  | 0.1 C          | VERVIEW                                  | 105        |

|    | 10.1.1         | Header format                            | 106        |

|    | 10.1.2         | Parameter format                         | 106        |

| 1  | 0.2 G          | GEOMETRY COMMANDS                        | 107        |

|    | 10.2.1         | Geometry command list                    | 107        |

|    | 10.2.2         | Explanation of geometry commands         | 110        |

| 1  | 0.3 R          | ENDERING COMMAND                         | 121        |

|    | 10.3.1         | Command list                             | 121        |

|    | 10.3.2         | Details of rendering commands            | 126        |

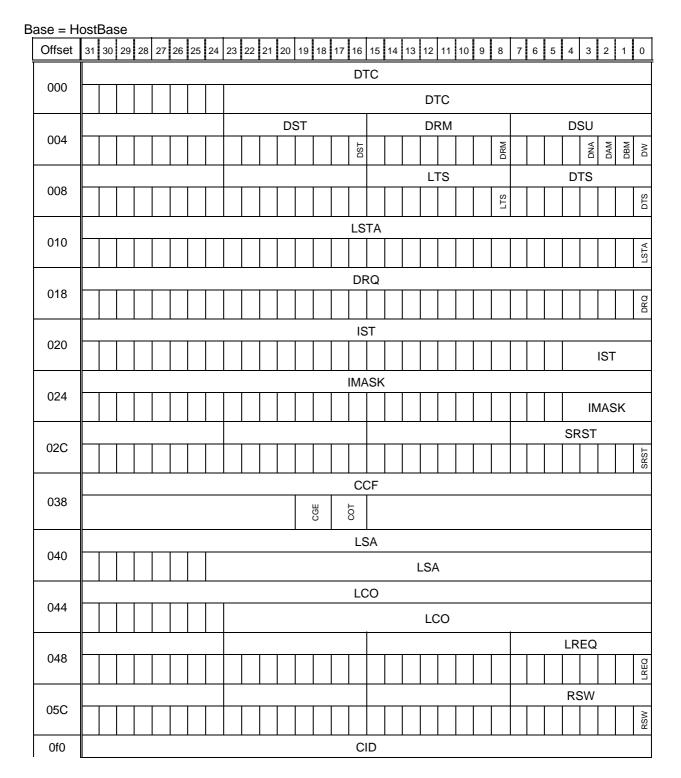

| 11 | REGIST         | 'ER                                      | 136        |

| 1  | 1.1 R          | EGISTER LIST                             | 136        |

|    | 11.1.1         | Host interface register list             | 136        |

|    | 11.1.2         | Graphics memory interface register list  | <i>138</i> |

|    | 11.1.3         | Display controller register list         | 139        |

|    | 11.1.4         | Video Capture register list              | 144        |

|    | 11.1.5         | Drawing engine register list             | 145        |

|    | 11.1.6         | Geometry engine register list            | 151        |

| 1  | 1.2 E          | XPLANATION OF REGISTER                   | 152        |

|    | <i>11.2.1</i>  | Host interface registers                 | 153        |

|    | <i>11.2.2</i>  | Graphics memory interface registers      | 160        |

|    | <i>11.2.3</i>  | Display control register                 | <i>163</i> |

|    | 11.2.4         | Video Capture Registers                  | 211        |

|    | 11.2.5         | Drawing control registers                | 218        |

|    | 11.2.6         | Drawing mode registers                   | 221        |

|    | <i>11.2.7</i>  | Triangle drawing registers               | 240        |

|    | 11.2.8         | Line drawing registers                   | 243        |

|    | <i>11.2.9</i>  | Pixel drawing registers                  | 244        |

|    | 11.2.10        | Rectangle drawing registers              | 244        |

|    | <i>11.2.11</i> | Blt registers                            | 245        |

|    | 11.2.12        | High-speed 2D line drawing registers     | 246        |

|    | 11.2.13        | High-speed 2D triangle drawing registers | 247        |

|    | 11.2.14        | Geometry control register                | 248        |

|    | 11.2.15        | Geometry mode registers                  | 250        |

|    | 11.2.16        | Display list FIFO registers              | 257        |

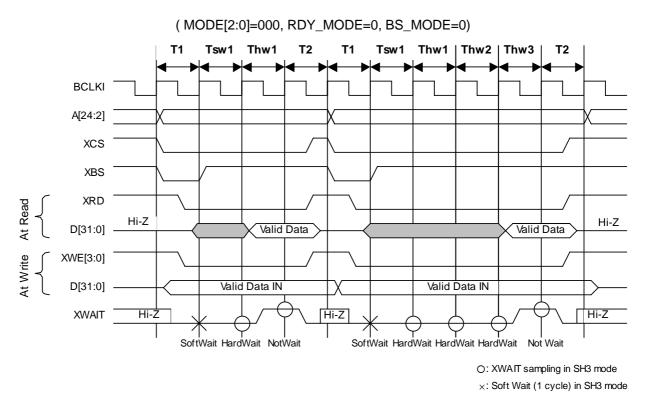

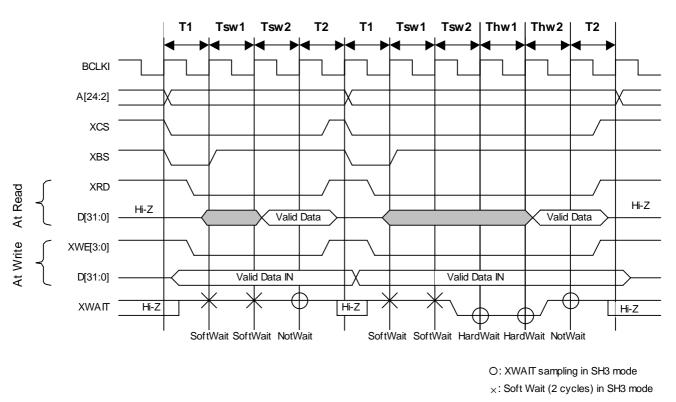

| 12 | TIMING         | DIAGRAM                                  | 258        |

| 1  | 2.1 H          | IOST INTERFACE                           | 258        |

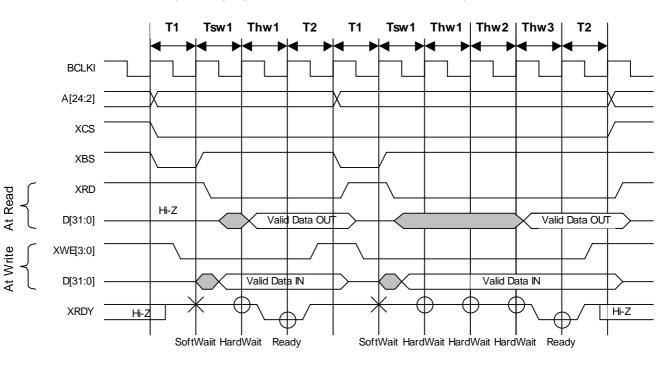

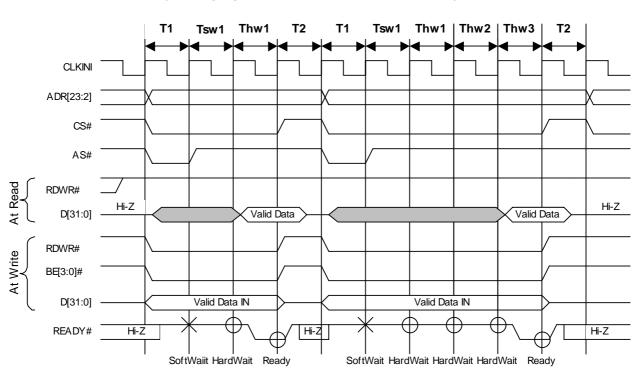

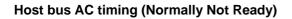

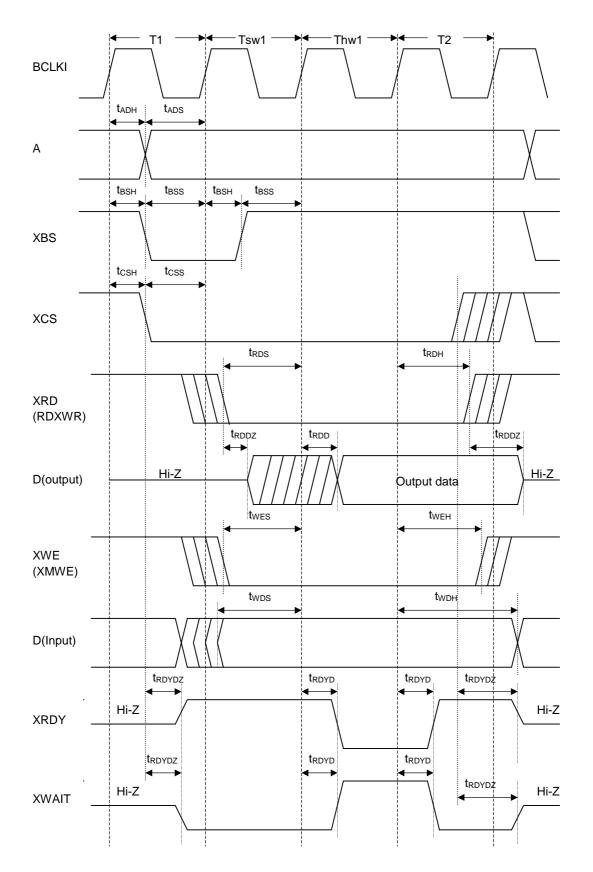

|    | 12.1.1 | CPU read/write timing diagram in SH3 mode (Normally Not Ready Mode)  | 258 |

|----|--------|----------------------------------------------------------------------|-----|

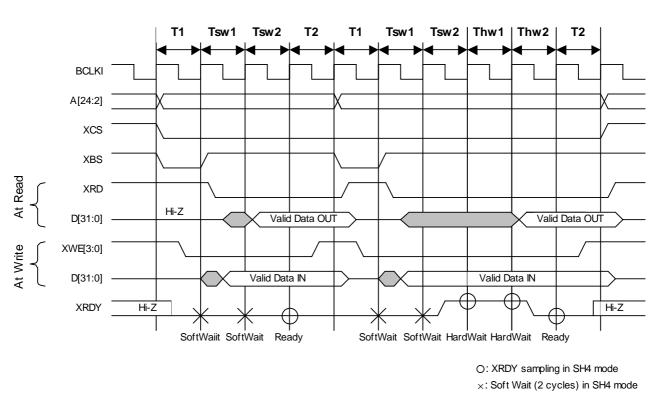

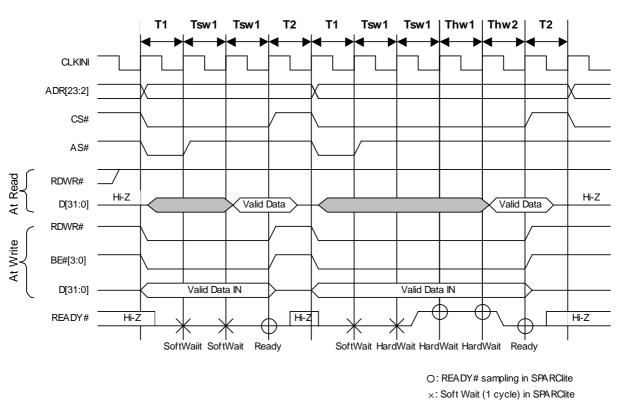

|    | 12.1.2 | CPU read/write timing diagram in SH3 mode (Normally Ready Mode)      | 259 |

|    | 12.1.3 | CPU read/write timing diagram in SH4 mode (Normally Not Ready Mode)  | 260 |

|    | 12.1.4 | CPU read/write timing diagram in SH4 mode (Normally Ready Mode)      | 261 |

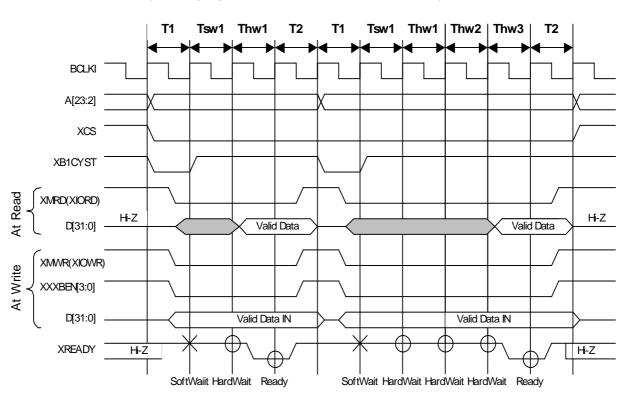

|    | 12.1.5 | CPU read/write timing diagram in V832 mode (Normally Not Ready Mode) | 262 |

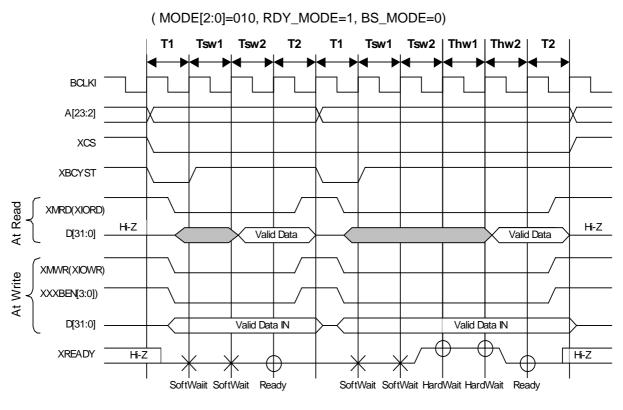

|    | 12.1.6 | CPU read/write timing diagram in V832 mode (Normally Ready Mode)     | 263 |

|    | 12.1.7 | CPU read/write timing diagram in SPARClite (Normally Not Ready Mode) | 264 |

|    | 12.1.8 | CPU read/write timing diagram in SPARClite (Normally Ready Mode)     | 265 |

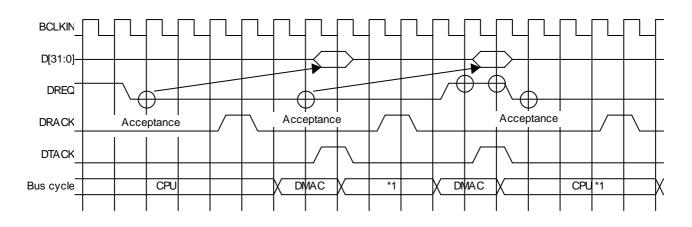

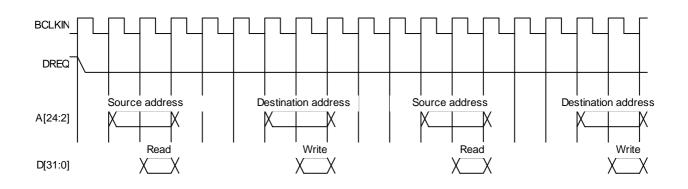

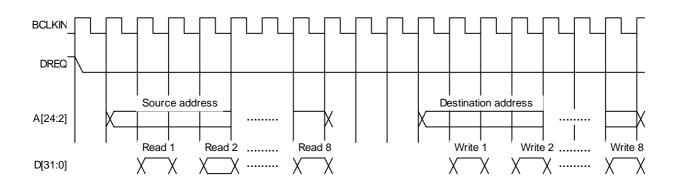

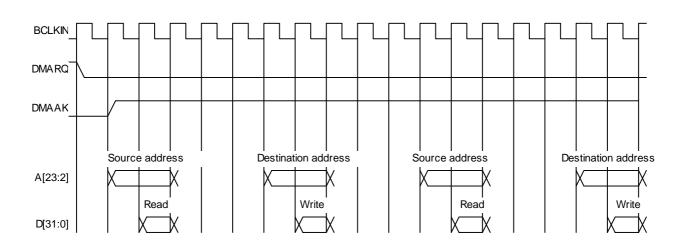

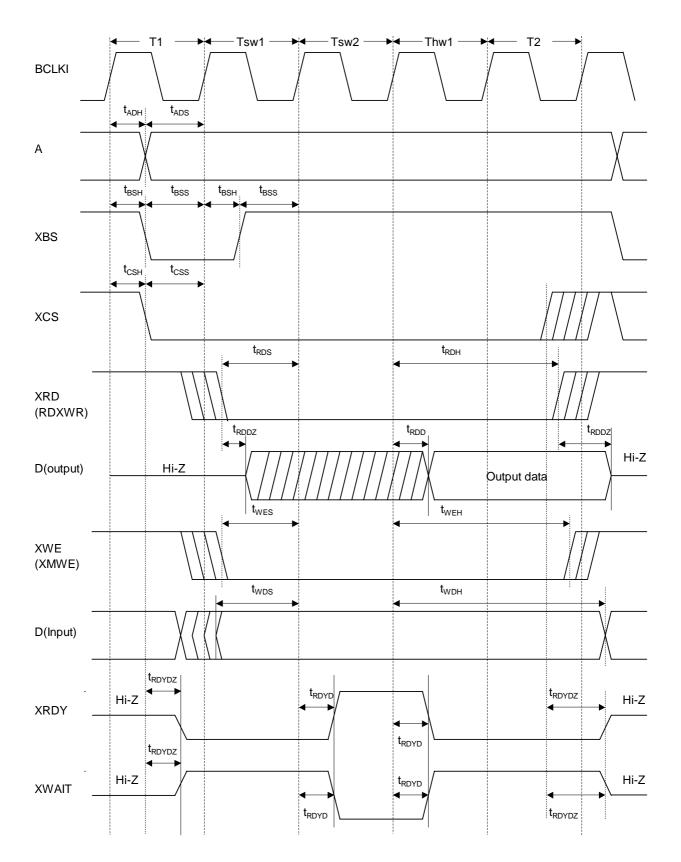

|    | 12.1.9 | SH4 single-address DMA write (transfer of 1 long word)               | 266 |

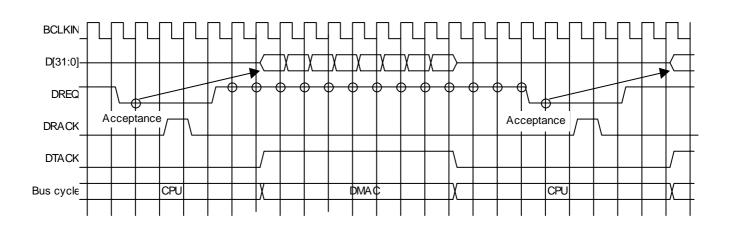

|    | 12.1.1 | 0 SH4 single-address DMA write (transfer of 8 long words)            | 267 |

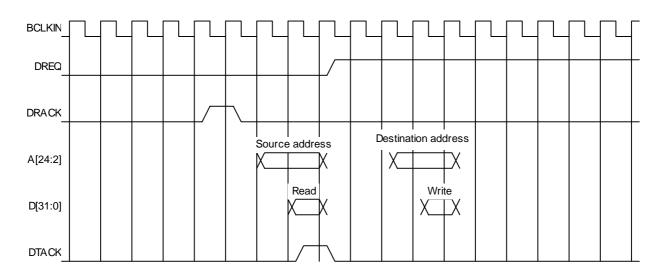

|    | 12.1.1 | 1 SH3/4 dual-address DMA (transfer of 1 long word)                   | 268 |

|    | 12.1.1 | 2 SH3/4 dual-address DMA (transfer of 8 long words)                  | 268 |

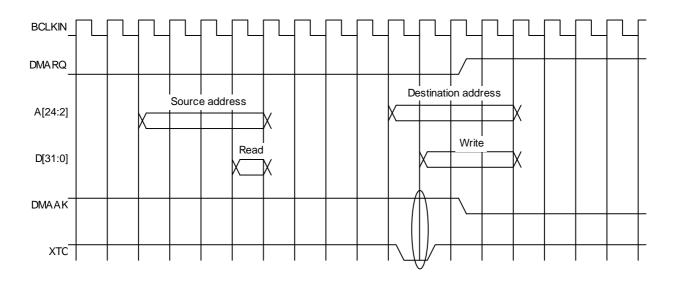

|    | 12.1.1 | 3 V832 DMA transfer                                                  | 269 |

|    | 12.1.1 | 4 SH4 single-address DMA transfer end timing                         | 270 |

|    | 12.1.1 | 5 SH3/4 dual-address DMA transfer end timing                         | 270 |

|    | 12.1.1 | 6 V832 DMA transfer end timing                                       | 271 |

|    | 12.1.1 | 7 SH4 dual DMA write without ACK                                     | 272 |

|    | 12.1.1 | 8 Dual-address DMA (without ACK) end timing                          | 273 |

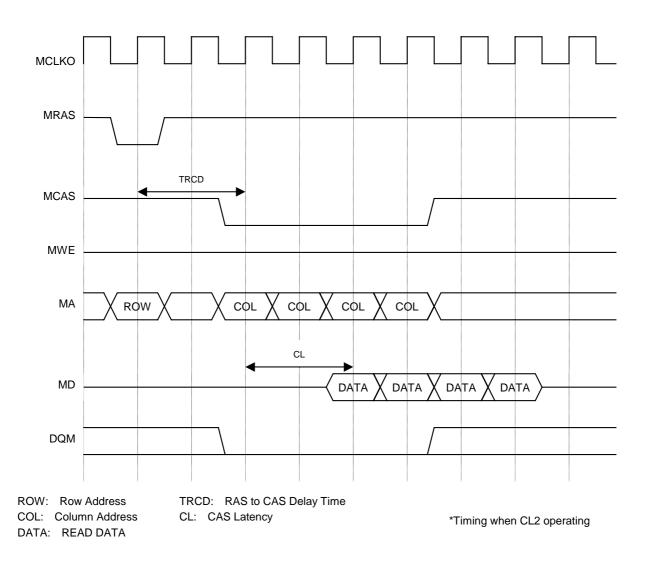

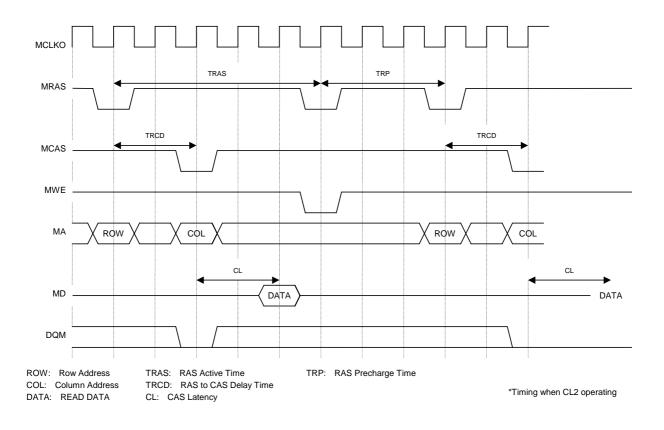

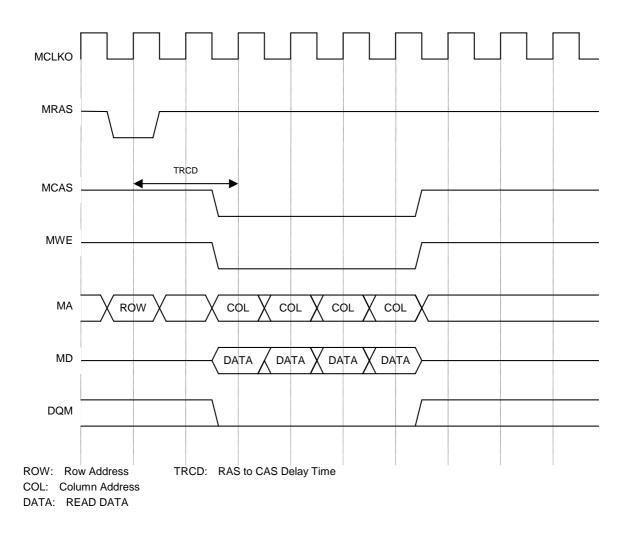

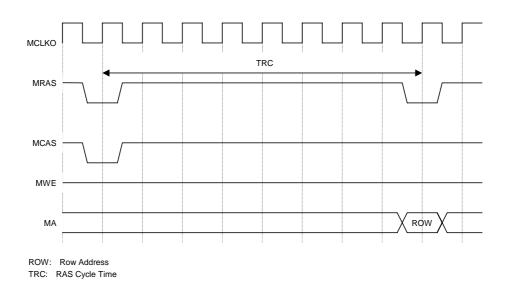

| 1  | 2.2    | GRAPHICS MEMORY INTERFACE                                            | 274 |

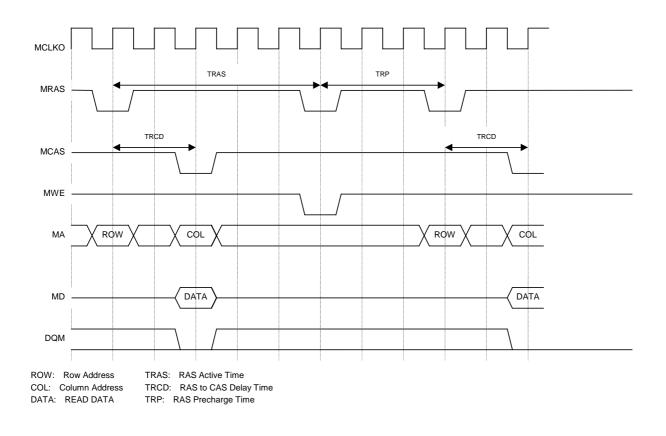

|    | 12.2.1 | Timing of read access to same row address                            | 274 |

|    | 12.2.2 | Timing of read access to different row addresses                     | 275 |

|    | 12.2.3 | Timing of write access to same row address                           | 276 |

|    | 12.2.4 | Timing of write access to different row addresses                    | 277 |

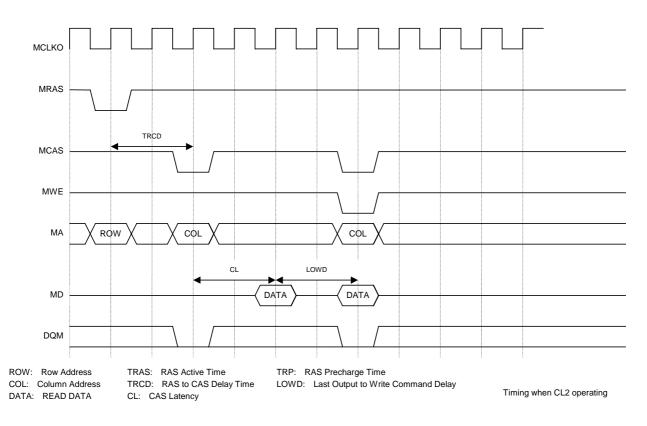

|    | 12.2.5 | Timing of read/write access to same row address                      | 278 |

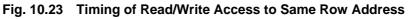

|    | 12.2.6 | Delay between ACTV commands                                          | 279 |

|    | 12.2.7 | Delay between Refresh command and next ACTV command                  | 279 |

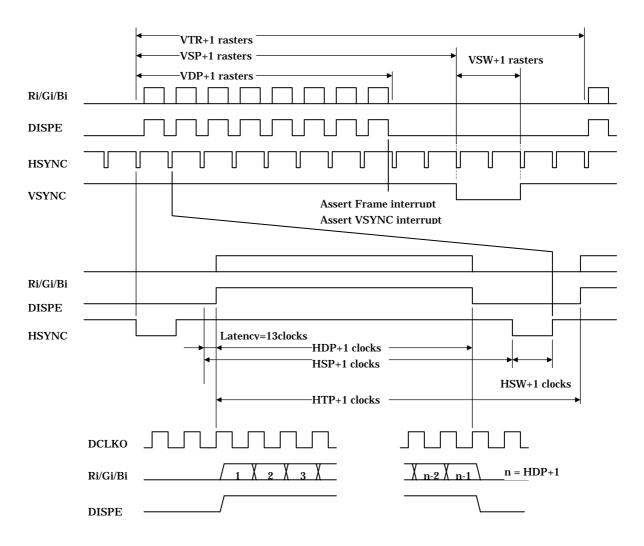

| 1  | 2.3    | DISPLAY TIMING                                                       | 280 |

|    | 12.3.1 | Non-interlace mode                                                   | 280 |

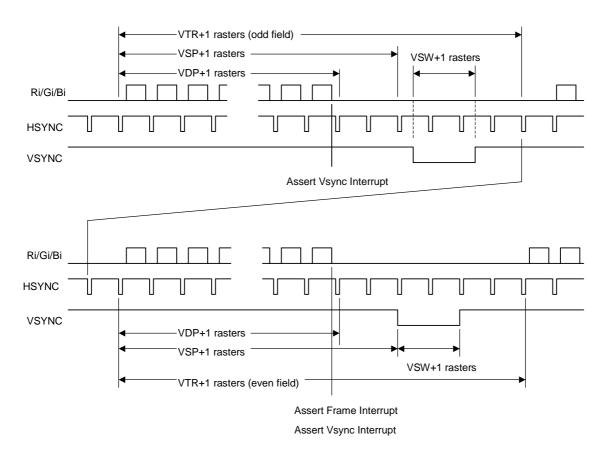

|    | 12.3.2 | Interlace video mode                                                 | 281 |

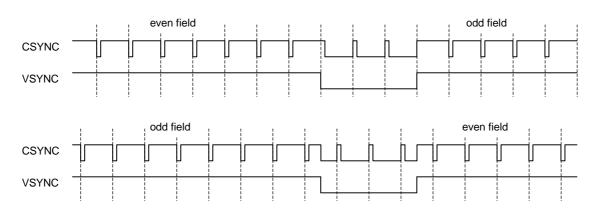

|    | 12.3.3 | Composite synchronous signal                                         | 282 |

| 1  | 2.4    | CPU CAUTIONS                                                         | 282 |

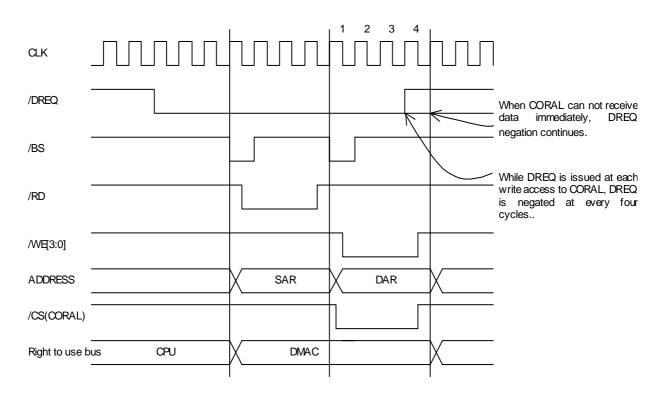

| 1  | 2.5    | SH3 MODE                                                             | 283 |

| 1  | 2.6    | SH4 Mode                                                             | 283 |

| 1  | 2.7    | V832 MODE                                                            | 284 |

| 1  | 2.8    | SPARCLITE                                                            | 284 |

| 1  | 2.9    | SUPPORTED DMA TRANSFER MODES                                         | 284 |

| 13 | ELEC   | TRICAL CHARACTERISTICS                                               | 285 |

| 1  | 3.1    | INTRODUCTION                                                         | 285 |

| 1  | 3.2    | MAXIMUM RATING                                                       | 285 |

| 13.3 F        | RECOMMENDED OPERATING CONDITIONS       |

|---------------|----------------------------------------|

| 13.3.1        | Recommended operating conditions       |

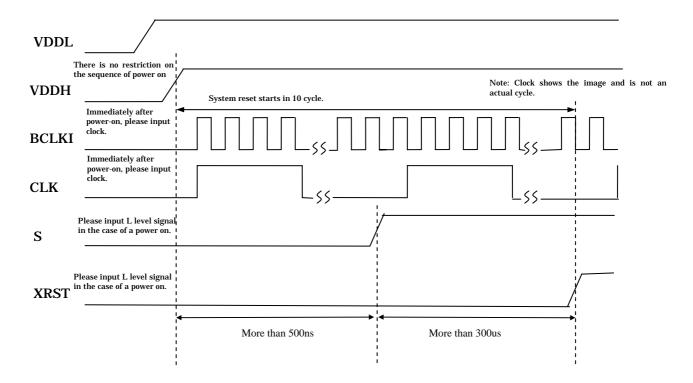

| <i>13.3.2</i> | Note at power-on                       |

| 13.4 C        | DC CHARACTERISTICS                     |

| 13.4.1        | DC Characteristics                     |

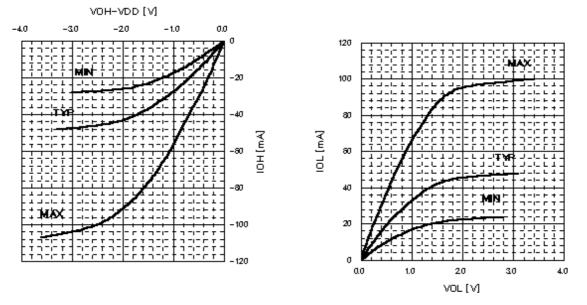

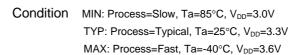

| <i>13.4.2</i> | V-I characteristics diagram            |

| 13.5 A        | C CHARACTERISTICS                      |

| 13.5.1        | Host interface                         |

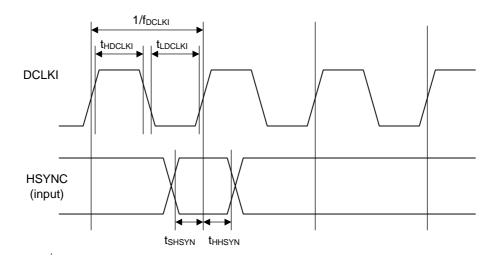

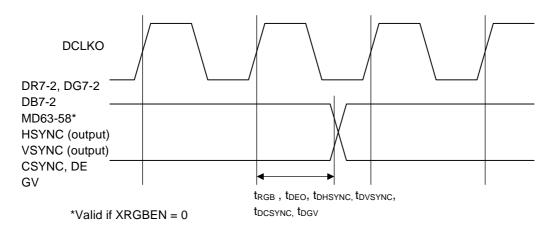

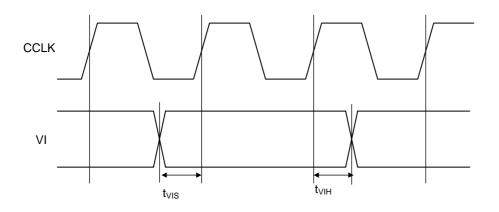

| <i>13.5.2</i> | Video interface                        |

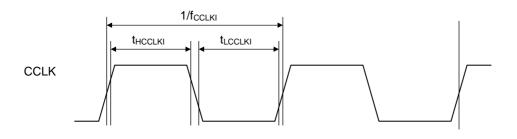

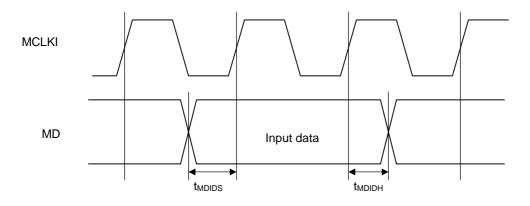

| 13.5.3        | Video Capture Interface                |

| 13.5.4        | Graphics memory interface              |

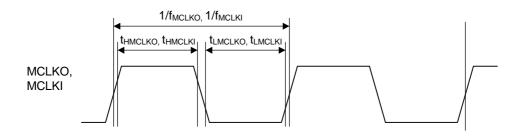

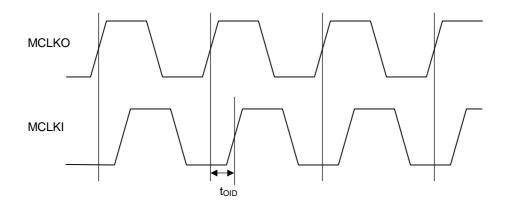

| 13.5.5        | PLL specifications                     |

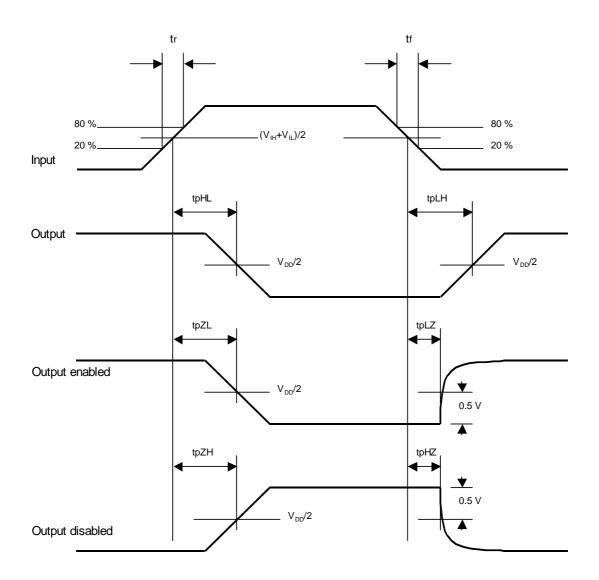

| 13.6 A        | C CHARACTERISTICS MEASURING CONDITIONS |

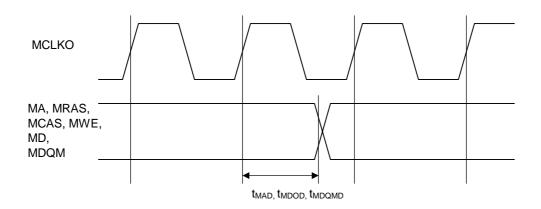

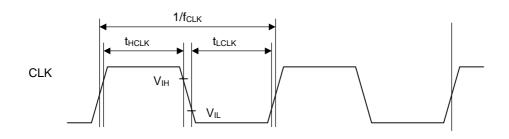

| 13.7 T        | IMING DIAGRAM         299              |

| 13.7.1        | Host interface                         |

| <i>13.7.2</i> | Video interface                        |

| 13.7.3        | Video Capture Interface                |

| 13.7.4        | Graphics memory interface              |

# 1 GENERAL

# 1.1 **Preface**

Coral graphics controller has some functions and optional efficiency and is planned to be serial-manufactured according to purposes.

The MB86294S is graphics controller LSI which is added the  $I^2C$  interface function to the MB86294.

For detail of the I<sup>2</sup>C interface function, please refer an another additional manual for MB86294S.

Note)

Purchase of Fujitsu  $I^2C$  components conveys a license under the Philips  $I^2C$  Patent Right to use these components in an  $I^2C$  system, provided that the system conforms to the  $I^2C$  Standard Specification as defined by Philips.

# **1.2 Features**

• Geometry engine

Geometry engine supports the geometry processing that is compatible with ORCHID (MB86292). Using the display list created by ORCHID enables drawing. \*\*(But Floating point setup command is deleted.)

Heavy processing of geometric operations such as coordinates conversions or clipping performed by this device can reduce the CPU loads dramatically.

• 2D and 3D Drawing

Coral has a drawing function that is compatible with the CREMSON (MB86290A). It can draw data using the display list created for CREMSON. \*\*(But Internal texture RAM is deleted.)

Coral also supports 3D rendering, such as texture mapping with perspective collection and Gouraud shading, alpha blending, and anti-aliasing for drawing smooth lines.

• Display controller

Coral has a display controller that is compatible with ORCHID.

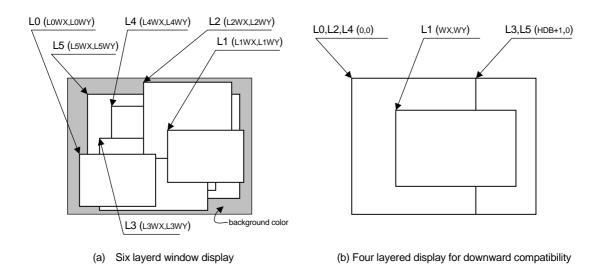

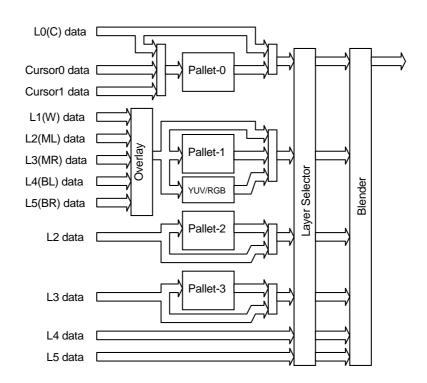

In addition to the traditional XGA ( $1024 \times 768$  pixels) display, 4-layer overlay, left/right split display, wrap-around scrolling, double buffers, and translucent display, function of 6-layer overlay, 4-siding for palette are expanded.

• Digital video capture

Digital video capture function can store digital video data such as TV in graphics memory; it can display rendered graphics and video graphics on the same screen.

Host CPU interface

Can be connected to SH3 and SH4 manufactured by Hitachi, to V832 microprocessor by NEC and to SPARClite (MB86833) by Fujitsu without external circuits.

• External memory interface

SDRAM and FCRAM can be connected.

Others

CMOS technology with 0.18-µm Package: BGA 256 pin, HQFP 256 pin Supply voltage: 1.8 V (internal operation) /3.3 V (I/O) Current consumption ( TYPICAL ) 1.8 V power supply : 500mA 3.3V power supply : 100mA

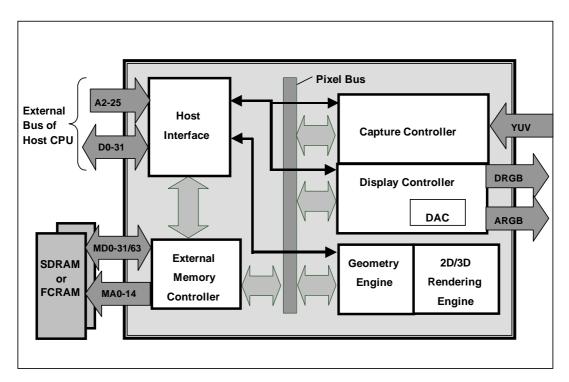

# 1.3 Block Diagram

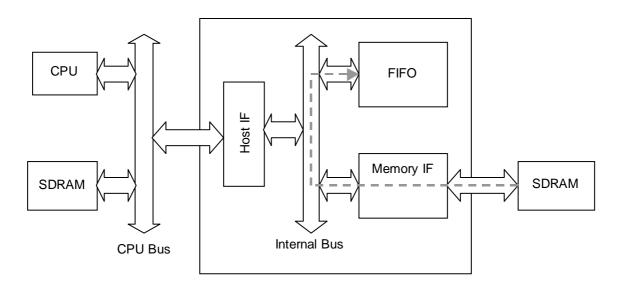

CORAL general block diagram is shown below:

Fig.1.1 CORAL Block Diagram

# **1.4 Functional Overview**

# 1.4.1 Host CPU interface

#### Supported CPU

Coral can be connected to SH3 and SH4 manufactured by HITACHI, V832 by NEC, SPARClite (MB86833) by Fujitsu.

#### **External Bus Clock**

Can be connected at max. 100 MHz (when using SH4 interface)

#### **Ready Mode**

Supports normal ready/not ready.

#### Endian

Supports little endian.

#### Access Mode

SRAM interface

FIFO interface (transfer destination address fixed)

#### DMA transfer

Supports 1-double word (32 bits) /8-double word (32 bytes) (only SH4) for transfer unit.

ACK used/unused mode can be selected as protocol (only for DAM in dual address mode)

Supports dual address/mode single address mode (only SH4).

Supports cycle steel/burst.

Supports local display list transfer.

#### Interrupt

Vertical (frame) synchronous detection

Field synchronous detection

External synchronous error detection

Drawing command error

Drawing command execution end

#### Switching internal operating frequency

Switch the operating frequency immediately after a reset (before rewriting MMR mode register of external memory interface).

Any operating frequency can be selected from the five combinations shown in Table 2-6.

| Clock for geometry engine | Clock for other than geometry engine |

|---------------------------|--------------------------------------|

| 166 MHz                   | 133 MHz                              |

| 166 MHz                   | 100 MHz                              |

| 133 MHz                   | 133 MHz                              |

| 133 MHz                   | 100 MHz                              |

| 100 MHz                   | 100 MHz                              |

#### Table 1-1 Frequency Setting Combinations

The following relationship is disabled: Clock for geometry engine < Clock for other than geometry engine

# 1.4.2 External memory interface

SDRAM or FCRAM can be connected.

64 bits or 32 bits can be selected for data bus.

Max. 133 MHz is available for operating frequency.

Connectable memory configuration is as shown below.

| Туре                       | Data bus width | Use count | Total capacity |

|----------------------------|----------------|-----------|----------------|

| FCRAM 16 Mbits (x16 Bits)  | 32 Bits        | 2         | 4 Mbytes       |

| FCRAM 16 Mbits (x16 Bits)  | 64 Bits        | 4         | 8 Mbytes       |

| SDRAM 64 Mbits (x32 Bits)  | 32 Bits        | 1         | 8 Mbytes       |

| SDRAM 64 Mbits (x32 Bits)  | 64 Bits        | 2         | 16 Mbytes      |

| SDRAM 64 Mbits (x16 Bits)  | 32 Bits        | 2         | 16 Mbytes      |

| SDRAM 64 Mbits (x16 Bits)  | 64 Bits        | 4         | 32 Mbytes      |

| SDRAM 128 Mbits (x32 Bits) | 32 Bits        | 1         | 16 Mbytes      |

| SDRAM 128 Mbits (x32 Bits) | 64 Bits        | 2         | 32 Mbytes      |

| SDRAM 128 Mbits (x16 Bits) | 32 Bits        | 2         | 32 Mbytes      |

| SDRAM 128 Mbits (x16 Bits) | 64 Bits        | 4         | 64 Mbytes      |

| SDRAM 256 Mbits (x16 Bits) | 32 Bits        | 2         | 64 Mbytes      |

#### **External Memory Configuration**

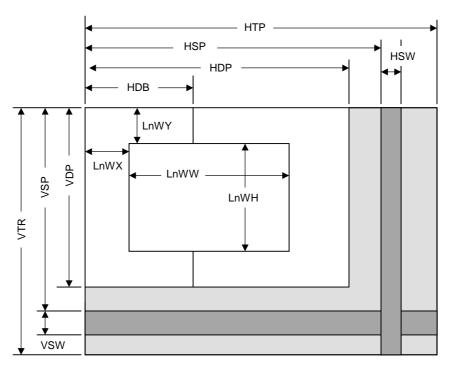

### 1.4.3 Display controller

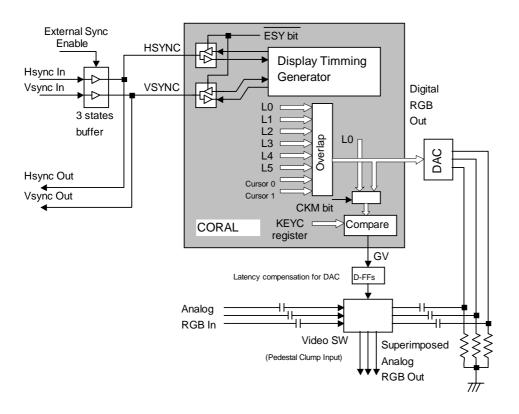

#### Video data output

Analog RGB video output is provided. And setting graphics memory bus to 32 bits, digital RGB video output is also provided.

#### Screen resolution

LCD panels with wide range of resolutions are supported by using a programmable timing generator as follows:

| Resolutions |

|-------------|

| 1024 × 768  |

| 1024 × 600  |

| 800 × 600   |

| 854 × 480   |

| 640 × 480   |

| 480 × 234   |

| 400 × 234   |

| 320 × 234   |

#### **Screen Resolutions**

#### Hardware cursor

Coral supports two hardware cursor functions. Each of these hardware cursors is specified as a  $64 \times 64$ -pixel area. Each pixel of these hardware cursors is 8 bits and uses the same look-up table as indirect color mode.

#### Double buffer method

Double buffer method in which drawing window and display window is switched in units of 1 frame enables the smooth animation.

Flipping (switching of display window area) is performed in synchronization with the vertical blanking period using program.

#### Scroll method

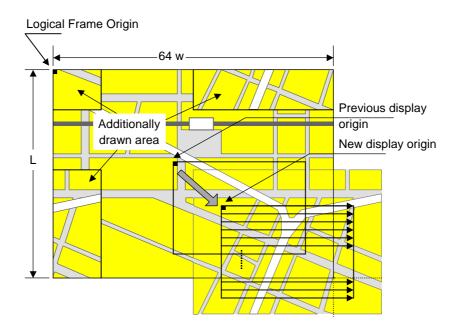

Independent setting of drawing and display windows and their starting position enables the smooth scrolling.

#### **Display colors**

- Supports indirect color mode which uses the look-up table (color palette) in 8 bits/pixels.

- Entry for look-up table (color palette) corresponds to color code for 8 bits, in other words, 256. Color data is each 6 bits of RGB. Consequently, 256 colors can be displayed out of 260,000 colors.

- Supports direct color mode which specifies RGB with 16 bits/pixels.

#### Overlay

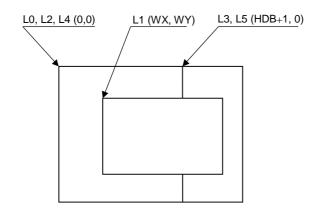

#### Compatibility mode

Up to four extra layers (C, W, M and B) can be displayed overlaid.

The overlay position for the hardware cursors is above/below the top layer (C).

The transparent mode or the blend mode can be selected for overlay.

The M- and B-layers can be split into separate windows.

Window display can be performed for the W-layer.

Two palettes are provided: C-layer and M-/B-layer.

The W-layer is used as the video input layer.

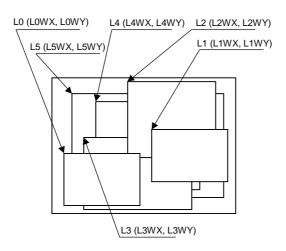

#### Window mode

- Up to six screens (L0 to 5) can be displayed overlaid.

- The overlay sequence of the L0- to L5-layers can be changed arbitrarily.

- The overlay position for the hardware cursors is above/below the L0-layer.

- The transparent mode or the blend mode can be selected for overlay.

- The L5-layer can be used as the blend coefficient plane (8 bits/pixel).

- Window display can be performed for all layers.

- Four palettes corresponded to L0 to 3 are provided.

- The L1-layer is used as the video input layer.

- Background color display is supported in window display for all layers.

# 1.4.4 Video Capture

The video capture function captures ITU RBT-656 format videos. Video data is stored in graphics memory once and then displayed on the screen in synchronization with the display scan.

Both NTSC and PAL video formats are supported.

# 1.4.5 Geometry processing

Coral has a geometry engine for performing the numerical operations required for graphics processing. The geometry engine uses the floating-point format for highly precise operations. It selects the required geometry processing according to the set drawing mode and primitive type and executes processing to the final drawing.

#### Primitives

Point, line, line strip, independent triangle, triangle strip, triangle fan, and arbitrary polygon are supported.

#### **MVP** Transformation

#### **MVP** Transformation

Setting a 4  $\times$  4 transformation matrix enables transformation of a 3D model view projection. Two-dimensional affine transformation is also possible.

#### Clipping

Clipping stops drawing of figures outside the window (field of view). Polygons (including concave shapes) can also be clipped.

#### Culling

Triangles on the back are not drawn.

#### **3D-2D Transformation**

This functions transforms 3D coordinates (normalization) into 2D coordinates in orthogonal or perspective projections.

#### View port transformation

This function transforms normalized 2D coordinates into drawing (device) coordinates.

#### **Primitive setup**

This function automatically performs a variety of slope computations, etc., based on transforming vertex data into coordinates and prepares for rendering (setup).

#### Log output of device coordinates

The view port conversion results are output to the local memory.

# 1.4.62D Drawing

#### 2D Primitives

Coral can perform 2D drawing for graphics memory (drawing plane) in direct color mode or indirect color mode.

Bold lines with width and broken lines can be drawn. With anti-aliasing smooth diagonal lines also can be drawn.

A triangle can be tiled in a single color or 2D pattern (tiling), or mapped with a texture pattern by specifying coordinates of the 2D pattern at each vertex (texture mapping). At texture mapping, drawing/non-drawing can be set in pixel units. Moreover, transparent processing can be performed using alpha blending. When drawing in single color or tiling without Gouraud shading or texture mapping, high-speed 2DLine and high-speed 2DTriangle can be used. Only vertex coordinates are set for these primitives. High-speed 2DTriangle is also used to draw polygons.

| Primitive type     | Description                                                    |

|--------------------|----------------------------------------------------------------|

| Point              | Plots point                                                    |

| Line               | Draws line                                                     |

| Bold line strip    | Draws continuous bold line                                     |

| (provisional name) | This primitive is used when interpolating the bold line joint. |

| Triangle           | Draws triangle                                                 |

| High-speed 2DLine  | Draws lines                                                    |

|                    | Compared to line, this reduces the host CPU processing load.   |

| Arbitrary polygon  | Draws arbitrary closed polygon containing concave shapes       |

|                    | consisting of vertices                                         |

#### **2D Primitives**

#### Arbitrary polygon drawing

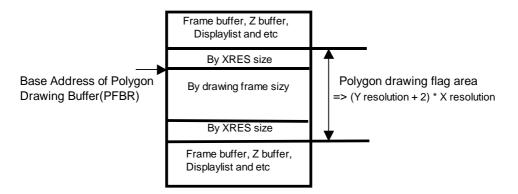

Using this function, arbitrary closed polygon containing concave shapes consisting of vertices can be drawn. (There is no restriction on the count of vertices, however, the polygon with its sides crossed are not supported.) In this case, as a work area for drawing, polygon drawing flag buffer is used on the graphics memory. In drawing polygon, draw triangle for polygon drawing flag buffer using high-speed 2DTriangle. Decide any vertex as a starting point to draw triangle along the periphery. It enables you to draw final polygon form in single color or with tiling/texture mapping in a drawing frame.

#### **BLT/Rectangle drawing**

This function draws a rectangle using logic operations. It is used to draw pattern and copy the image pattern within the drawing frame. It is also used for clearing drawing frame and Z buffer.

| Attribute              | Description                                                                                               |

|------------------------|-----------------------------------------------------------------------------------------------------------|

| Raster operation       | Selects two source logical operation mode                                                                 |

| Transparent processing | Performs BLT without drawing pixel consistent with the<br>transparent color.                              |

| Alpha blending         | The alpha map and source in the memory is subjected to alpha blending and then copied to the destination. |

#### **BLT Attributes**

#### Pattern (Text) drawing

This function draws a binary pattern (text) in a specified color.

# Attribute Description Enlarge Vertically 2 × 2 Horizontally × 2 Vertically and Horizontally × 2 Shrink Vertically 1/2 × 1/2 Horizontally 1/2 Vertically and Horizontally 1/2

#### Pattern (Text) Drawing Attributes

#### Drawing clipping

This function sets a rectangle frame in drawing frame to prohibit the drawing of the outside the frame.

# 1.4.73D Drawing

#### **3D Primitives**

This function draws 3D objects in drawing memory in the direct color mode.

| Primitive         | Description                                                                        |

|-------------------|------------------------------------------------------------------------------------|

| Point             | Plots 3D point                                                                     |

| Line              | Draws 3D line                                                                      |

| Triangle          | Draws 3D triangle                                                                  |

| Arbitrary polygon | Draws arbitrary closed polygon containing concave shapes<br>consisting of vertexes |

#### **3D Primitives**

#### 3D Drawing attributes

Texture mapping with bi-linear filtering/automatic perspective correction and Gouraud shading provides high-quality realistic 3D drawing. A built-in texture mapping unit performs fast pixel calculations. This unit also delivers color blending between the shading color and texture color.

#### Hidden plane management

Coral supports the Z buffer for hidden plane management.

# 1.4.8 Special effects

#### Anti-aliasing

Anti-aliasing manipulates line borders of polygons in sub-pixel units and blend the pre-drawing pixel color with color to make the jaggies be seen smooth. It is used as a functional option for 2D drawing (in direct color mode only).

#### Bold line and broken line drawing

This function draws lines of a specific width and a broken line.

#### Line Drawing Attributes

| Attribute   | Description                                    |

|-------------|------------------------------------------------|

| Line width  | Selectable from 1 to 32 pixels                 |

| Broken line | Set by 32 bit or 24 bit of broken line pattern |

- Supports the verticality of starting and ending points.

- Supports the verticality of broken line pattern.

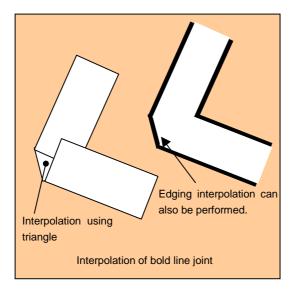

- Interpolation of bold line joint supports the following modes:

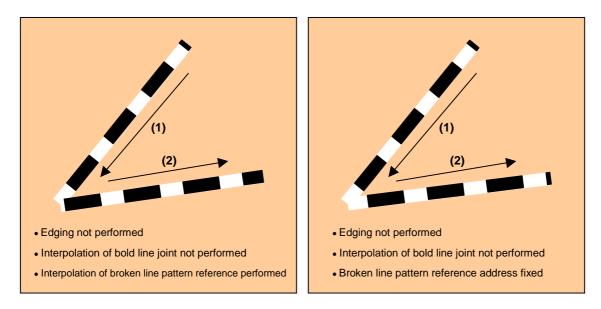

- (1) Broken line pattern reference address fix mode

- → The same broken line pattern is kept referencing for the period of some pixels starting from the joint and the starting point for the next line.

- (2) No interpolation

- Supports the equalization of the width of bold lines.

- Supports the bold line edging.

- Not support the Anti-aliasing of dashed line patterns.

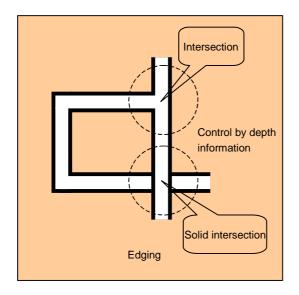

- For a part overlaid due to connection of bold lines, natural overlay can be represented by providing depth information. (Z value).

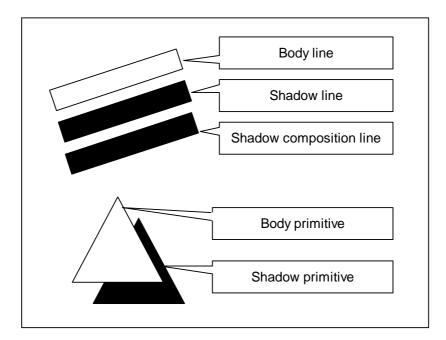

#### Shading

Supports the shading primitive.

Drawing is performed to the body primitive coordinates (X, Y) with an offset as a shade. At this drawing, the Z buffer is used in order to differentiate between the body and shade.

#### Alpha blending

Alpha blending blends two image colors to provide a transparent effect. CORAL supports two types of blending; blending two different colors at drawing, and blending overlay planes at display. Transparent color is not used for these blending options.

There are two ways of specifying alpha blending for drawing:

- (1) Set a transparent coefficient to the register; the transparent coefficient is applied for transparency processing of one plane.

- (2) Set a transparent coefficient for each vertex of the plane; as with Gouraud shading, the transparent coefficient is linear-interpolated to perform transparent processing in pixel units.

In addition to the above, the following settings can be performed at texture mapping. When the most significant bit of each texture cell is 1, drawing or transparency can be set. When the most significant bit of each texture cell is 0, non-drawing can be set.

| Туре            | Description                                                                                           |

|-----------------|-------------------------------------------------------------------------------------------------------|

| Drawing         | Transparent ratio set in particular register                                                          |

|                 | While one primitive (polygon, pattern, etc.), being drawn, registered transparent ratio applied       |

|                 | A transparent coefficient set for each vertex. A linear-interpolated transparent coefficient applied. |

|                 | This is possible only in direct color mode.                                                           |

| Overlay display | Blends top layer pixel color with lower layer pixel color                                             |

|                 | Transparent coefficient set in particular register                                                    |

|                 | Registered transparent coefficient applied during one frame scan                                      |

#### **Alpha Blending**

#### Gouraud Shading

Gouraud shading can be used in the direct color mode to provide 3D object real shading and color gradation.

#### **Gray Scale Gouraud Shading**

Gray scale gouraud shading can be used in the in-direct color(8bit/pixel) mode to draw a blend coefficient layer.

#### Texture mapping

Coral supports texture mapping to map an image pattern onto the surface of plane. The texture pattern can be laid out in the graphics memory. In this case, max.  $4096 \times 4096$  pixels can be used.

For drawing 8-bit color, only point sampling can be specified for texture interpolation; only de-curl can be specified for the blend mode.

| Function               | Description      |

|------------------------|------------------|

| Filtering              | Point sample     |

|                        | Bi-linear filter |

| Coordinates correction | Linear           |

|                        | Perspective      |

| Blend                  | De-curl          |

|                        | Modulate         |

|                        | Stencil          |

| Alpha blend            | Normal           |

|                        | Stencil          |

|                        | Stencil alpha    |

| Wrap                   | Repeat           |

|                        | Cramp            |

|                        | Border           |

#### Texture Mapping

### 1.4.9 Others

#### **Drawing color**

8-bit indirect color and 16-bit direct color are supported as a drawing input data.

#### Top-left rule non-applicable mode

In addition to the top-left rule applicable mode in which the triangle borders are compatible with CREMSON, the top-left rule non-applicable mode can be used. (In case of non-top-left polygon drawing, an object has to be in a geometry clipping area.)

Caution: Use perspective correct mode when use texture at the top-left rule non-applicable mode.

Top-left rule non-applicable primitives cannot use Geometry clip function.

Non-top-left-part's pixel quality is less than body. (using approximate calculation)

# 2 PINS

# 2.1 Signals

# 2.1.1 Signal lines

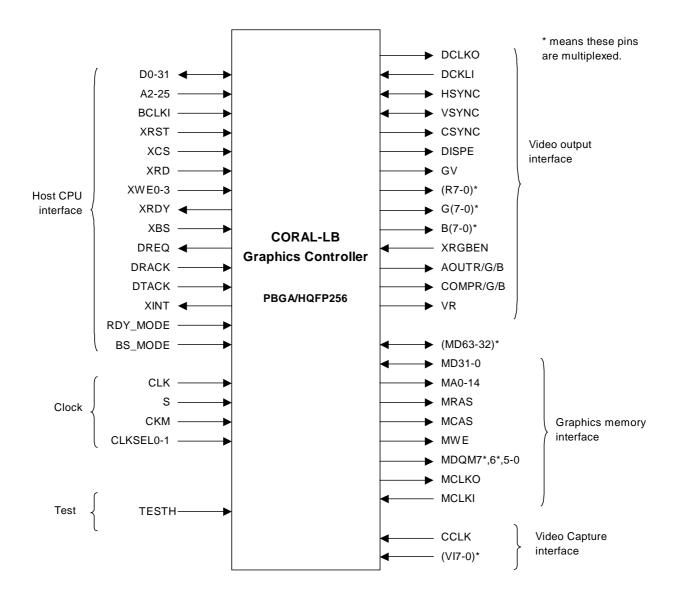

Fig. 2.1 CORAL Signal Lines

# 2.2 Pin Assignment

# 2.2.1 PBGA256 Pin assignment diagram (TOP\_VIEW)

|   |   | 1  | 2  | 3        | 4        | 5        | 6        | 7        | 8     | 9      | 10     | 11   | 12    | 13    | 14  | 15  | 16  | 17  | 18  | 19        | 20 |  |

|---|---|----|----|----------|----------|----------|----------|----------|-------|--------|--------|------|-------|-------|-----|-----|-----|-----|-----|-----------|----|--|

|   | _ |    |    |          |          |          |          |          |       |        |        |      |       |       |     |     |     |     |     |           |    |  |

| A |   | 1  | 76 | 75       | 74       | 73       | 72       | 71       | 70    | 69     | 68     | 67   | 66    | 65    | 64  | 63  | 62  | 61  | 60  | 59        | 58 |  |

| В |   | 2  | 77 | 144      | 143      | 142      | 141      | 140      | 139   | 138    | 137    | 136  | 135   | 134   | 133 | 132 | 131 | 130 | 129 | 128       | 57 |  |

| C |   | 3  | 78 | 145      | 204      | 203      | 202      | 201      | 200   | 199    | 198    | 197  | 196   | 195   | 194 | 193 | 192 | 191 | 190 | 127       | 56 |  |

| D |   | 4  | 79 | 146      | 205      | 256      | 255      | 254      | 253   | 252    | 251    | 250  | 249   | 248   | 247 | 246 | 245 | 244 | 189 | 126       | 55 |  |

| E |   | 5  | 80 | 147      | 206      |          |          |          |       |        |        |      |       |       |     |     |     | 243 | 188 | 125       | 54 |  |

| F |   | 6  | 81 | 148      | 207      |          |          |          |       |        |        |      |       |       |     |     |     | 242 | 187 | 124       | 53 |  |

| G |   | 7  | 82 | 149      | 208      |          |          |          |       |        |        |      |       |       |     |     |     | 241 | 186 | 123       | 52 |  |

| Η |   | 8  | 83 | 150      | 209      |          |          |          |       |        |        |      |       |       |     |     |     | 240 | 185 | 122       | 51 |  |

| J |   | 9  | 84 | 151      | 210      |          |          |          | T     | her    | mal    | Bal  | s     |       |     |     |     | 239 | 184 | 121       | 50 |  |

| K |   | 10 | 85 | 152      | 211      |          |          |          |       |        |        |      |       |       |     |     |     | 238 | 183 | 120       | 49 |  |

| L |   | 11 | 86 | 153      | 212      |          |          |          | In o  | rder 1 | to rec | luce | heat, |       |     |     |     | 237 | 182 | 119       | 48 |  |

| M |   | 12 | 87 | -        | 213      |          |          | p        | lease | conr   | nect t | hese | pins  | to Gì | ٧D  |     |     |     | 181 |           |    |  |

| N |   | 13 | 88 |          | 214      |          |          |          |       |        |        |      |       |       |     |     |     |     | 180 |           |    |  |

| Р |   | 14 | 89 |          | 215      |          |          |          |       |        |        |      |       |       |     |     |     | -   | 179 | 116       |    |  |

| R |   | 15 |    | 157      | _        |          |          |          |       |        |        |      |       |       |     |     |     |     | 178 |           |    |  |

| Т |   | 16 | 91 | 158      |          |          |          |          |       |        |        |      |       |       |     |     |     |     | 177 |           |    |  |

| U |   | 17 | 92 |          |          |          |          |          |       |        |        |      |       |       |     |     |     |     | 176 |           | 42 |  |

| V |   | 18 | 93 |          | 161      | -        |          |          |       |        |        |      |       | 170   |     |     |     |     | 175 |           | 41 |  |

| W |   | 19 | 94 | 95<br>22 | 96<br>22 | 97<br>24 | 98<br>25 | 99<br>26 | 100   | 101    | -      |      | 104   |       | 106 |     | 108 | 109 |     | 111<br>29 | 40 |  |

| Y |   | 20 | 21 | 22       | 23       | 24       | 25       | 26       | 27    | 28     | 29     | 30   | 31    | 32    | 33  | 34  | 35  | 36  | 37  | 38        | 39 |  |

|   |   |    |    |          |          |          |          |          |       |        |        |      |       |       |     |     |     |     |     |           |    |  |

Note: The MODE2 signal used for Orchid is changed as shown below. MODE2 signal for Orchid  $\rightarrow$  RDY\_MODE signal for Coral

# 2.2.2 PBGA256 Pin assignment table

| Pin No |        |    | Pin Name  | Pin No |   |    | Pin Name   | Pin No |   |    | Pin Name   | Pin No |   |    | Pin Name   |

|--------|--------|----|-----------|--------|---|----|------------|--------|---|----|------------|--------|---|----|------------|

| 1      | А      | 1  | OPEN      | 65     | Α | 13 | MD54       | 129    | В | 18 | MD35 / B5  | 193    | С | 15 | VDDL       |

| 2      | В      | 1  | VSYNC     | 66     | Α | 12 | MD57 / VI1 | 130    | В | 17 | MD40 / G2  | 194    | С |    |            |

| 3      | С      | 1  | GV        | 67     | Α | 11 | VDDL       | 131    | В | 16 |            | 195    | С | 13 | MD48 / R2  |

| 4      | D      | 1  | XINT      | 68     | Α | 10 | MD59 / VI3 | 132    | В | 15 | MD45 / G7  | 196    | С | 12 | MD52 / R6  |

| 5      | Е      | 1  | VDDH      | 69     | Α | 9  | MD60 / VI4 | 133    | В | 14 | MD49 / R3  | 197    | С | 11 | MD55       |

| 6      | F      | 1  | XRD       | 70     | Α | 8  | VDDL       | 134    | В | 13 | VDDL       | 198    | С | 10 | MD62 / VI6 |

| 7      | G      | 1  | D1        | 71     | Α | 7  | TESTH      | 135    | В | 12 | VDDH       | 199    | С | 9  | TESTH      |

| 8      | Н      | 1  | D3        | 72     | Α | 6  | TESTH      | 136    | В | 11 | MD56 / VI0 | 200    | С | 8  | AVD2       |

| 9      | J      | 1  | D6        | 73     | Α | 5  | AVS2       | 137    | В | 10 | MD61 / VI5 | 201    | С | 7  | AVD1       |

| 10     | Κ      | 1  | VDDL      | 74     | Α | 4  | COMPG      | 138    | В | 9  | CCLK       | 202    | С | 6  | AVD0       |

| 11     | L      | 1  | VSS       | 75     | Α | 3  | VRO        | 139    | В | 8  | TESTH      | 203    | С | 5  | VREF       |

| 12     | Μ      | 1  | D8        | 76     | Α | 2  | COMPR      | 140    | В | 7  | AOUTB      | 204    | С | 4  | RDY_MODE   |

| 13     | Ν      | 1  | D11       | 77     | В | 2  | MODE1      | 141    | В | 6  | AOUTG      | 205    | D | 4  | VSS        |

| 14     | Ρ      | 1  | D13       | 78     | С | 2  | MODE2      | 142    | В | 5  | AOUTR      | 206    | Ε | 4  | VDDH       |

| 15     | R      | 1  | D16       | 79     | D | 2  | DISPE      | 143    | В | 4  | AVS0       | 207    | F | 4  | VSS        |

| 16     | Т      | 1  | D20       | 80     | Е | 2  | DCLKO      | 144    | В | 3  | BS_MODE    | 208    | G | 4  | VDDL       |

| 17     | U      | 1  | D22       | 81     | F | 2  | DREQ       | 145    | С | 3  | MODE0      | 209    | Н | 4  | VSS        |

| 18     | V      | 1  | D25       | 82     | G | 2  | XCS        | 146    | D | 3  | DCLKI      | 210    | J | 4  | VDDL       |

| 19     | W      | 1  | D28       | 83     | Н | 2  | XBS        | 147    | Ε | 3  | HSYNC      | 211    | Κ |    | D7         |

| 20     | Υ      | 1  | VSS       | 84     | J | 2  | D2         | 148    | F | 3  | CSYNC      | 212    | L | 4  | D10        |

| 21     | Υ      | 2  | DTACK     | 85     | K | 2  | D5         | 149    | G | 3  | XRDY       | 213    | Μ | 4  | VDDL       |

| 22     | Υ      | 3  | A3        | 86     | L | 2  | D9         | 150    | Ĥ | 3  | BCLKI      | 214    | Ν | 4  | VSS        |

| 23     | Υ      | 4  | A7        | 87     | Μ | 2  | D12        | 151    | J | 3  | D0         | 215    | Ρ | 4  | D23        |

| 24     | Υ      | 5  | A9        | 88     | Ν | 2  | D15        | 152    | K | 3  | D4         | 216    | R | 4  | D19        |

| 25     | Υ      | 6  | A12       | 89     | Ρ | 2  | D17        | 153    | L | 3  | VDDH       | 217    | Т | 4  | D29        |

| 26     | Y      | 7  | A15       | 90     | R | 2  | D21        | 154    | М | 3  | D14        | 218    | U | 4  | VSS        |

| 27     | Y      | 8  | A17       | 91     | Т | 2  | VDDL       | 155    | Ν | 3  | D18        | 219    | U | 5  | XWE3       |

| 28     | Υ      | 9  | A20       | 92     | U | 2  | D26        | 156    | Ρ | 3  | VDDH       | 220    | Ū | 6  | A10        |

| 29     | Y      | 10 | A22       | 93     | V | 2  | D30        | 157    | R | 3  | D24        | 221    | U | 7  | VDDL       |

| 30     | Υ      | 11 | VDDL      | 94     | W | 2  | XWE0       | 158    | Т | 3  | D27        | 222    | Ū | 8  | VSS        |

| 31     |        | 12 | A23       | 95     | W | 3  | XWE1       | 159    | U | 3  | D31        | 223    | Ū |    | A14        |

| 32     |        | 13 | XRST      | 96     | W | 4  | A2         | 160    | V | 3  | VSS        | 224    |   | 10 |            |

| 33     |        | 14 | CLK       | 97     | W | 5  | A5         | 161    | V | 4  | XWE2       | 225    | Ū | 11 | CKM        |

| 34     |        | 15 | VSS       | 98     | Ŵ | 6  | A8         | 162    | V | 5  | DRACK      | 226    |   | 12 |            |

| 35     |        | 16 | MD0       | 99     | W | 7  | A11        | 163    | V | 6  | A4         | 227    |   | 13 |            |

| 36     |        | 17 | MD3       | 100    | W | 8  | A13        | 164    | V | 7  | A6         | 228    | Ū |    |            |

| 37     |        | 18 | MD6       | 101    | Ŵ | 9  | A16        | 165    | V | 8  | VDDH       | 229    | Ŭ |    |            |

| 38     | Υ      | 19 | MD9       | 102    | W | 10 | A19        | 166    | V | 9  | VDDL       | 230    | Ū | 16 | MD10       |

| 39     |        | 20 | VSS       | 103    | W | 11 | A24        | 167    | V | 10 |            | 231    | Ū | 17 |            |

| 40     | W      | 20 | MD17      | 104    | W | 12 | PLLVSS     | 168    | V | 11 | A25        | 232    | Ť | 17 | MD16       |

| 41     |        | 20 | MD20      | 105    | W | 13 | VDDL       | 169    | V | 12 |            | 233    | R | 17 | MD27       |

| 42     | U      | 20 | MD24      | 106    | W | 14 | CLKSEL0    | 170    | V | 13 | CLKSEL1    | 234    | Р | 17 | MD23       |

| 43     |        | 20 | MD26      | 107    | Ŵ | 15 | MD1        | 171    | v | 14 |            | 235    | Ň | 17 | VSS        |

| 44     |        | 20 | MD30      | 108    | W | 16 | MD4        | 172    | V | 15 |            | 236    | M |    | VSS        |

| 45     |        | 20 | MCLKI     | 109    | Ŵ | 17 | MD7        | 173    | V | 16 |            | 237    | L | 17 | DQM2       |

| 46     |        | 20 | VDDH      | 110    | W | 18 | MD11       | 174    | V | 17 | MD12       | 238    | K | 17 | MA3        |

| 47     |        | 20 | DQM1      | 111    | W | 19 | MD14       | 175    | V | 18 |            | 239    | J |    | VDDL       |

| 48     |        | 20 | DQM3      | 112    | V | 19 | MD15       | 176    | Ū |    |            | 240    | Ĥ |    | VSS        |

| 49     |        | 20 | VDDL      | 113    | Ū | 19 | MD19       | 177    | Ť | 18 |            | 241    |   | 17 | VDDL       |

| 50     | J      | 20 | MA0       | 114    | Т | 19 | MD22       | 178    | R | 18 | MD21       | 242    | F | 17 | MA11       |

| 51     |        | 20 | MA4       | 115    | R | 19 | MD25       | 179    | Ρ | 18 |            | 243    | Е | 17 | VSS        |

| 52     |        | 20 | MA6       | 116    | Ρ | 19 | MD29       | 180    | Ν | 18 |            | 244    | D | 17 | VSS        |

| 53     |        | 20 | VDDH      | 117    | N | 19 | MD31       | 181    | M | 18 |            | 245    |   | 16 |            |

| 54     |        | 20 | MA12      | 118    | Μ | 19 | VSS        | 182    | L | 18 | MCLKO      | 246    | D | 15 |            |

| 55     |        | 20 | MRAS      | 119    | L | 19 | DQM0       | 183    | ĸ | 18 |            | 247    |   | 14 |            |

| 56     |        | 20 | DQM4      | 120    | Κ |    | MA1        | 184    | J | 18 |            | 248    | D | 13 |            |

| 57     |        | 20 | DQM7 / B1 | 121    | J | 19 | MA5        | 185    | Ĥ | 18 |            | 249    |   | 12 |            |

| 58     |        | 20 | VSS       | 122    | Ĥ | 19 | MA8        | 186    | G | 18 | MA14       | 250    |   | 11 | MD58 / VI2 |

| 59     |        | 19 | MD38 / G0 | 123    | G | 19 | MA9        | 187    | F | 18 | MWE        | 251    | D | 10 |            |

| 60     |        | 18 | MD41 / G3 | 124    | F | 19 | MA13       | 188    | Ē | 18 |            | 252    | D | 9  | TESTH      |

| 61     |        | 17 | MD44 / G6 | 125    | Ē | 19 | MCAS       | 189    | D | 18 |            | 253    | D | 8  | VSS        |

| 62     |        | 16 | MD46 / R0 | 126    | D | 19 | DQM5       | 190    | C | 18 | MD33 / B3  | 254    | D | 7  | AVS1       |

| 63     |        | 15 | MD50 / R4 | 120    | C | 19 | VDDH       | 191    | č | 17 |            | 255    | D |    | COMPB      |

| 64     |        | 14 | MD53 / R7 | 128    | В |    | MD34 / B4  | 192    | č |    |            | 256    | D |    | XRGBEN     |

|        | $\sim$ | 17 | 11000/111 | 120    | 5 |    |            | 172    |   |    | 11000/01   | 200    |   |    |            |

Note: The MODE2 signal used for Orchid is changed as shown below. MODE2 signal for Orchid  $\rightarrow$  RDY\_MODE signal for Coral

# 2.2.4 HQFP256 Pin assignment table

| Pin No         | Pin Name   | Pin No     | Pin Name    | Pin No     | Pin Name         | Pin No | Pin Name               |

|----------------|------------|------------|-------------|------------|------------------|--------|------------------------|

| 1              | MODE1      | 65         | XWE0        | 129        | MD14             | 193    | MD34 / B4              |

| 2              | MODE2      | 66         | XWE1        | 130        | MD15             | 194    | MD35 / B5              |

| 3              | DCLKI      | 67         | XWE2        | 131        | VDDH             | 195    | MD36 / B6              |

| 4              | VDDH       | 68         | XWE3        | 132        | MD16             | 196    | MD37 / B7              |

| 5              | VSYNC      | 69         | DTACK       | 133        | MD17             | 197    | MD38 / G0              |

| 6              | HSYNC      | 70         | DRACK       | 134        | MD18             | 198    | MD39 / G1              |

| 7              | DISPE      | 71         | A2          | 135        | MD19             | 199    | MD40 / G2              |

| 8              | GV         | 72         | A3          | 136        | MD20             | 200    | MD41 / G3              |

| 9              | CSYNC      | 73         | A4          | 137        | MD21             | 201    | VDDL                   |

| 10             | DCLKO      | 74         | A5          | 138        | MD22             | 202    | MD42 / G4              |

| 11             | VSS        | 75         | VSS         | 139        | VSS              | 203    | VSS                    |

| 12             | VDDL       | 76         | VDDL        | 140        | MD23             | 204    | MD43 / G5              |

| 13             | XRDY       | 77         | A6          | 141        | VDDL             | 205    | VDDH                   |

| 14             | XINT       | 78         | A7          | 142        | MD24             | 206    | MD44 / G6              |

| 15             | DREQ       | 79         | A8          | 143        | MD25             | 207    | MD45 / G7              |

| 16             | VDDH       | 80         | A9          | 144        | MD26             | 208    | MD46 / R0              |

| 17             | VSS        | 81         | A10         | 145        | MD27             | 209    | MD47 / R1              |

| 18             | BCLKI      | 82         | VDDH        | 146        | MD28             | 210    | MD48 / R2              |

| 19             | XCS        | 83         | A11         | 147        | MD29             | 210    | MD49 / R3              |

| 20             | XRD        | 84         | A12         | 148        | MD20<br>MD30     | 211    | MD50 / R4              |

| 20             | XBS        | 85         | A13         | 149        | MD30<br>MD31     | 212    | VDDL                   |

| 21             | VDDL       | 86         | A14         | 149        | VSS              | 213    | MD51 / R5              |

| 22             | D0         | 87         | VDDL        | 150        | VDDL             | 214    | MD51 / R5<br>MD52 / R6 |

| 23             | D0         | 88         | A15         | 151        | MCLKI            | 213    | MD52 / R0<br>MD53 / R7 |

| 24             | VSS        | 89         | VSS         | 152        | VSS              | 210    | VSS                    |

| 25             | D2         | 90         | A16         | 154        | VSS              | 217    | VDDH                   |

| 20             | D2<br>D3   | 90         | A17         | 154        | VDDH             | 218    | MD54                   |

| 27             | D3         | 91         | A18         | 155        | MCLKO            | 219    | MD54<br>MD55           |

| 28             | D4<br>D5   | 92         | A19         | 157        | DQM0             | 220    | MD55 / VI0             |

| 30             |            | 93         |             |            |                  | 221    |                        |

| 30             | D6<br>D7   | 94         | A20<br>A21  | 158<br>159 | DQM1             |        | MD57 / VI1             |

|                |            |            |             |            | DQM2             | 223    | MD58 / VI2             |

| 32             | VDDL       | 96         | A22         | 160        | DQM3             | 224    | VDDL                   |

| 33             | VSS        | 97         | VDDL        | 161        | VDDL             | 225    | MD59 / VI3             |

| 34             | D8         | 98         | A23         | 162        | MA0              | 226    | MD60 / VI4             |

| 35             | D9         | 99         | A24         | 163        | MA1              | 227    | MD61 / VI5             |

| 36             | VDDH       | 100        | A25         | 164        | MA2              | 228    | MD62 / VI6             |

| 37             | D10        | 101        | CKM         | 165        | MA3              | 229    | MD63 / VI7             |

| 38             | D11        | 102        | XRST        | 166        | MA4              | 230    | VDDL                   |

| 39             | D12        | 103        | PLLVSS      | 167        | MA5              | 231    | CCLK                   |

| 40             | VSS        | 104        | VSS         | 168        | VSS              | 232    | VSS                    |

| 41             | D13        | 105        | CLK         | 169        | MA6              | 233    | TESTH                  |

| 42             | D14        | 106        | S           | 170        | MA7              | 234    | TESTH                  |

| 43             | VDDL       | 107        | PLLVDD      | 171        | VDDL             | 235    | TESTH                  |

| 44             | D15        | 108        | VDDL        | 172        | MA8              | 236    | TESTH                  |

| 45             | D16        | 109        | VSS         | 173        | VDDH             | 237    | TESTH                  |

| 46             | D17        | 110        | CLKSEL0     | 174        | MA9              | 238    | AOUTB                  |

| 47             | D18        | 111        | CLKSEL1     | 175        | MA10             | 239    | AVD2                   |

| 48             | D19        | 112        | VDDH        | 176        | MA11             | 240    | COMPB                  |

| 49             | D20        | 113        | MD0         | 177        | MA12             | 241    | AVS2                   |

| 50             | D21        | 114        | MD1         | 178        | MA13             | 242    | AOUTG                  |

| 51             | VDDH       | 115        | MD2         | 179        | MA14             | 243    | AVD1                   |

| 52             | D22        | 116        | MD3         | 180        | MRAS             | 244    | COMPG                  |

| 53             | D23        | 117        | VDDL        | 181        | VDDL             | 245    | AVS1                   |

| 54             | VSS        | 118        | VSS         | 182        | VSS              | 246    | OPEN                   |

| 55             | VDDL       | 119        | MD4         | 183        | MCAS             | 247    | AOUTR                  |

| 56             | D24        | 120        | MD5         | 184        | MWE              | 248    | AVD0                   |

| 57             | D25        | 121        | MD6         | 185        | DQM4             | 249    | VRO                    |

| 58             | D26        | 122        | MD7         | 186        | DQM5             | 250    | AVS0                   |

|                |            | 122        | MD8         | 187        | DQM6 / B0        | 250    | VREF                   |

|                | D27        |            |             | 107        |                  |        |                        |

| 59             | D27<br>D28 |            |             | 188        | DOM7 / B1        | 2.52   | ICOMPR                 |

| 59<br>60       | D28        | 124        | MD9         | 188<br>189 | DQM7 / B1<br>VSS | 252    | COMPR<br>XRGBEN        |

| 59<br>60<br>61 | D28<br>D29 | 124<br>125 | MD9<br>MD10 | 189        | VSS              | 253    | XRGBEN                 |

| 59<br>60       | D28        | 124        | MD9         |            |                  |        |                        |

#### FUJITSU LIMITED PRELIMINARY and CONFIDENTIAL

#### Notes

| V <sub>SS</sub> /PLLV <sub>SS</sub> | : | Ground                      |

|-------------------------------------|---|-----------------------------|

| V <sub>DDH</sub>                    | : | 3.3-V power supply          |

|                                     | : | 1.8-V power supply          |

|                                     | : | PLL power supply (1.8 V)    |

| OPEN                                | : | Do not connect anything.    |

| TESTH                               | : | Input a 3.3 V-power supply. |

| AVS                                 | : | Analog Ground               |

| AVD                                 | : | Analog power supply (3.3 V) |

- It is recommended that PLLV<sub>DD</sub> should be isolated on the PCB.

- It is recommended that AVD should be isolated on the PCB.

- Insert a bypass capacitor with good high frequency characteristics between the power supply and ground.

Place the capacitor as near as possible to the pin.

# 2.2.5 Pin treatment table

#### Table 1. Pin treatment table

#### (Host interface, Video output interface)

|                           | Pin Name              | Direction<br>*1 | Default Treatment                                                                                                       | Treatment of unused *2  | Comment                                                                                                                     |

|---------------------------|-----------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------|

|                           | MODE0-2               | I               | Connect to VDDH or GND according to the CPU mode.                                                                       | <=                      | See "4.1 Oepration Mode"                                                                                                    |

|                           | RDY_MODE              | I               | Connect to VDDH or GND according to the<br>Ready signal mode.                                                           | <=                      | See "4.1 Oepration Mode"                                                                                                    |

|                           | BS_MODE               | I               | Connect to VDDH or GND according to the<br>BS signal mode.                                                              | <=                      | See "4.1 Oepration Mode"                                                                                                    |

|                           | D0-31                 | 10              | Connect to CPU data bus                                                                                                 | <=                      |                                                                                                                             |

|                           | A2-A25                | I               | Connect to CPU address bus                                                                                              | <=                      | Connect A24 to XMWR in the V832 mode                                                                                        |

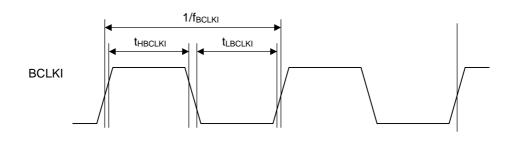

|                           | BCLKI                 | I               | Connect to CPU bus clock                                                                                                | <=                      | Max 100MHz. Input the clock when<br>power-on. See "12.2.2 Power on<br>Precaution"                                           |

|                           | XBS                   | I               | Connect to CPU bus cycle start<br>indicating signal                                                                     | VDD when BS_MODE=VDD    | This signal is 1 shot BCLKI pulse<br>that indicates the bus cycle start.<br>See "4.1 Oepration Mode".                       |

| Host Interface            | XCS                   | I               | Connect to chip select signal                                                                                           | <=                      |                                                                                                                             |

| nost interface            | XRD                   | I               | Connect to CPU read strobe signal                                                                                       | <=                      |                                                                                                                             |

|                           | XWE0-XWE4             | I               | Connect to CPU write byte enable signals                                                                                | <=                      | Connect byte enable signal in V832 mode                                                                                     |

|                           | XRDY                  | 0(T)            | Connect to CPU Ready (Wait) signal and<br>Pull Up/Down according to RDY_MODE                                            | <=                      | See "4.1 Operation Mode"                                                                                                    |

|                           | DREQ                  | 0               | Connect to CPU DREQ signal                                                                                              | OPEN                    | SH3/4,V832=Low Active, See "4.3<br>DMA Transfer"                                                                            |

|                           | DRACK/DMAAK           | I               | Connect to CPU DRACK signal                                                                                             | Connect to GND          | Connect to DMAAK signal in V832<br>Mode, SH3/4,V832=High Active,<br>See "4.3 DMA Transfer "                                 |

|                           | DTACK/XTC             | I               | Connect to CPU DTACK signal                                                                                             | SH3/4=GND,<br>V832=VDDH | Connect to XTC signal in V832<br>mode,<br>SH3/4=High Active, V832=Low<br>Active, See "4.3 DMA Transfer"                     |

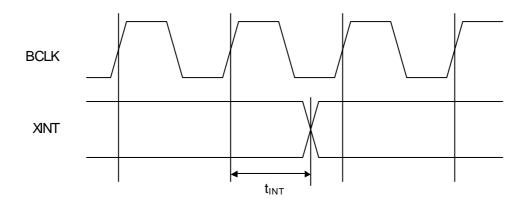

|                           | XINT                  | 0               | Connect to CPU interrupt signal                                                                                         | OPEN                    | SH3/4=Low Active,V832=High<br>Active                                                                                        |

|                           | DCLKO                 | 0               | Connect to dot clock                                                                                                    | <=                      | Selectable clock source, DCLKI or<br>output of internal PLL. See DCM<br>Register in "10.2.3 Display<br>Controller Register" |

|                           | DCLKI                 |                 | Connect to clock for dot clock                                                                                          | GND                     |                                                                                                                             |

|                           | HSYNC                 | 10              | Connect to HSYNC signal and Pull Up                                                                                     | <=                      |                                                                                                                             |

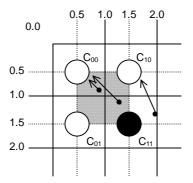

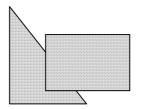

|                           | VSYNC                 | 10              | Connect to VSYNC signal and Pull Up                                                                                     | <=                      |                                                                                                                             |