Volume 3

inear Jata Acquisition · Communications · Linear · Data Acquisitio

MARRIS

Analog Data Book

Divinuications Linear DataAcquisition Communications Linea

### Harris Linear & Data Acquisition Products

Harris Semiconductor Analog Products represent the state of the art in precision and high speed performance. Capitalizing on the advanced linear processing technologies developed over the past 15 years, Harris Semiconductor Analog Products offer high quality and unmatched performance.

This data book describes Harris Semiconductor's complete line of Linear and Data Acquisition products, and includes a complete set of product specifications and data sheets, application notes and a separate section describing our quality and high reliability program.

All specifications in this data book are applicable only to packaged products. Specifications for dice are obtainable in Harris Semiconductor's Chip Data Book.

Please fill out the registration card at the back of this data book and return it to us so we may keep you informed of our latest new product developments over the next year.

If you need more information on these and other Harris products, please contact the nearest Harris sales office listed in the back of this data book.

Copyright (C) Harris Corporation 1982

(All rights reserved)

Printed in USA

Harris Semiconductor's products are sold by description only. Harris reserves the right to make changes in circuit design specifications and other information at any time without prior notice. Accordingly, the reader is cautioned to verify that data sheets and other information in this publication are current before placing orders. Information contained in application notes is intended solely for general guidance; use of the information for user's specific application is at user's risk. Reference to products of other manufacturers are solely for convenience of comparison and do not imply total equivalency of design, performance, or otherwise.

### Contents

# ~~~

### **General Information**

Alpha-Numeric Product Index Ordering Information I. C. Handling Procedures Harris Analog I. C. Technologies Cross Reference High Temperature Electronics Advanced Packaging Techniques

### **Operational Amplifiers, References and Comparators**

**CMOS** Analog Switches

**CMOS** Analog Multiplexers

**Data Conversion Products**

**Communications Products**

**Harris Hi-Rel Products**

**Analog Application Notes**

Chip Information

Harris Quality and Reliability Programs

Packaging

Harris Sales Locations

.

.

·

### Alpha-Numeric Product Index

|                               |                                                                                                       | Page         |

|-------------------------------|-------------------------------------------------------------------------------------------------------|--------------|

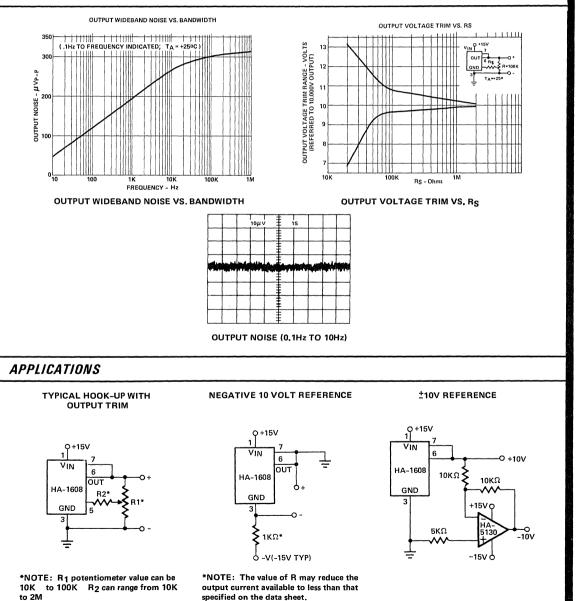

| HA-1608                       | +10V Adjustable Voltage Reference                                                                     | 2-3          |

| HA-2400/04/05                 | PRAM, Four Channel Operational Amplifiers                                                             | 2-6          |

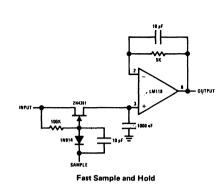

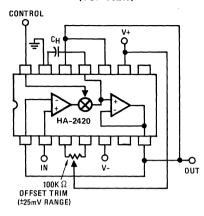

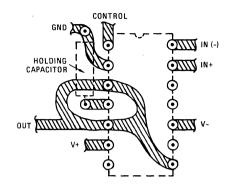

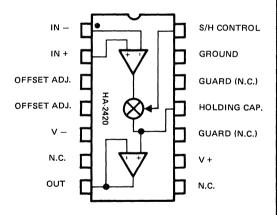

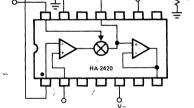

| HA-2420/25                    | Fast Sample and Hold Operational Amplifiers                                                           | 5-2          |

| HA-2500/02/05                 | Precision High Slew Rate Operational Amplifiers                                                       | 2-10         |

| HA-2510/12/15                 | High Slew Rate Operational Amplifers                                                                  | 2-14         |

| HA-2520/22/25                 | Uncompensated High Slew Rate Operational Amplifiers                                                   | 2-18         |

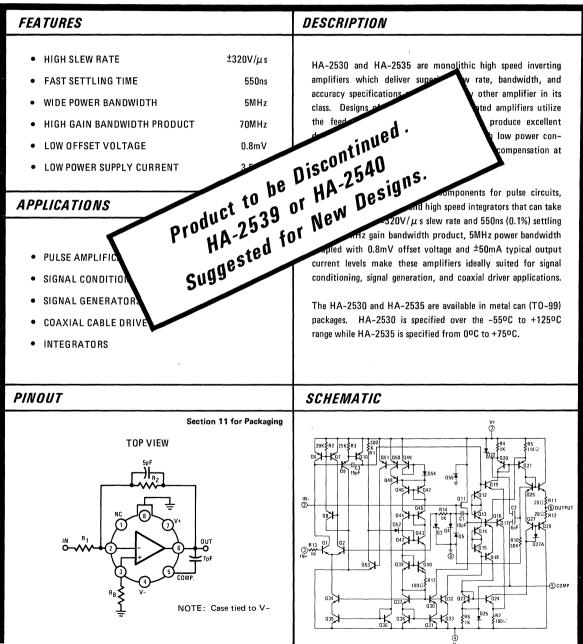

| HA-2530/35                    | High Slew Rate Wideband Inverting Operational Amplifiers                                              | 2-22         |

| HA-2539                       | Super High Slew Rate Wideband Operational Amplifiers                                                  | 2-26         |

| HA-2540                       | Ultra High Slew Rate Operational Amplifiers                                                           | 2-29         |

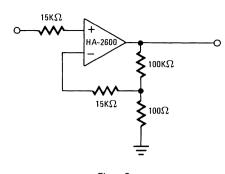

| HA-2600/02/05                 | Wideband, High Impedance Operational Amplifiers                                                       | 2-32         |

| HA-2620/22/25                 | Very Wideband, Uncompensated Operational Amplifiers                                                   | 2-36         |

| HA-2630/35                    | High Performance Current Booster                                                                      | 2-40         |

| HA-2640/45                    | High Voltage Operational Amplifiers                                                                   | 2-44         |

| HA-2650/55<br>HA-2720/25      | Dual High Performance Operational Amplifiers                                                          | 2-48         |

| HA-2720/25<br>HA-2730/35      | Wide Range Programmable Operational Amplifiers<br>Wide Range Dual Programmable Operational Amplifiers | 2-52         |

| HA-2730/35<br>HA-2740         | Quad Programmable Operational Amplifiers                                                              | 2-58<br>2-64 |

| HA-4156                       | High Performance Quad Operational Amplifiers                                                          | 2-64         |

| HA-4600/02/05                 | High Performance Quad Operational Amplifiers                                                          | 2-07         |

| HA-4620/22/25                 | Wideband, High Performance Quad Operational Amplifiers                                                | 2-78         |

| HA-4741                       | Quad Operational Amplifier                                                                            | 2-84         |

| HA-4900/02/05                 | Precision Quad Comparators                                                                            | 2-88         |

| HA-5062                       | Dual Low Power, JFET Input Operational Amplifier                                                      | 2-95         |

| HA-5064                       | Low Power, JFET Input Quad Operational Amplifier                                                      | 2-97         |

| HA-5082                       | Dual JFET Input Operational Amplifier                                                                 | 2-100        |

| HA-5084                       | JFET Input Quad Operational Amplifier                                                                 | 2-102        |

| HA-5100/05                    | Wideband, JFET Input Operational Amplifiers                                                           | 2-105        |

| HA-5110/15                    | Wideband, JFET Input, Uncompensated Operational Amplifiers                                            | 2-111        |

| HA-5130/35                    | Precision Operational Amplifiers                                                                      | 2-117        |

| HA-5160/62                    | Wideband, JFET Input, High Slew Rate, Uncompensated Operational Amplifiers                            | 2-124        |

| HA-5170                       | Precision JFET Input Operational Amplifier                                                            | 2-131        |

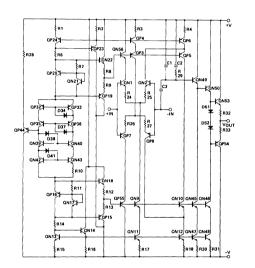

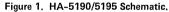

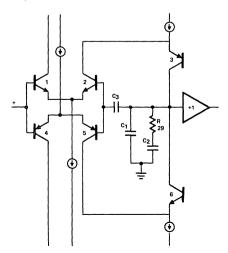

| HA-5190/95                    | Wideband, Fast Settling Operational Amplifiers                                                        | 2-133        |

| HA-8023                       | Triple Low Power Programmable Operational Amplifier                                                   | 2-140        |

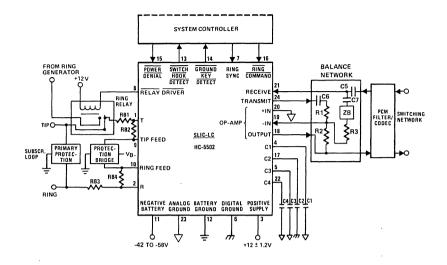

| HC-5502                       | SLIC-LC Subscriber Line Interface Circuit                                                             | 6-7          |

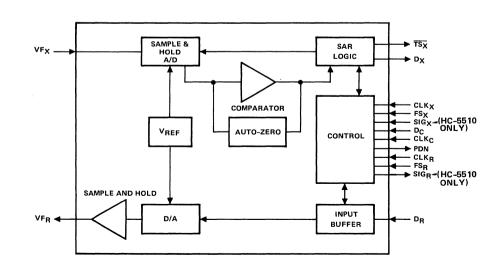

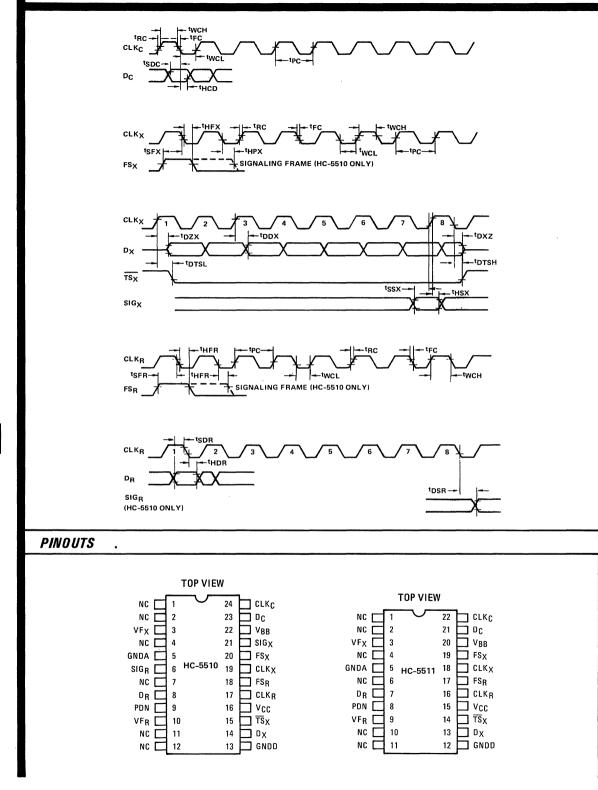

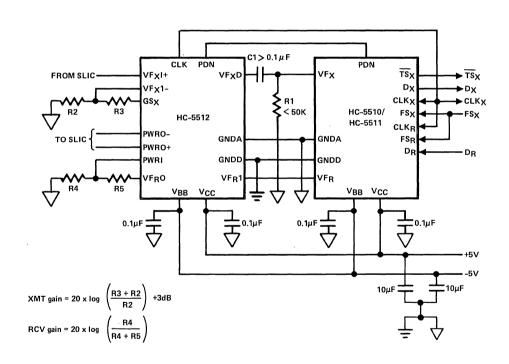

| HC-5510/5511<br>HC-5512/5512A | Monolithic CODECs                                                                                     | 6-12         |

| HC-5512/5512A                 | PCM Monolithic Filter<br>All Digital Continuously Variable Slope Delta Modulator (CVSD)               | 6-21         |

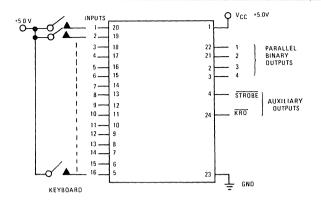

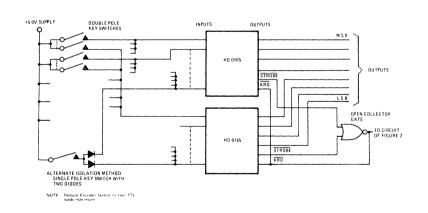

| HD-0165                       | Keyboard Encoder                                                                                      | 6-2          |

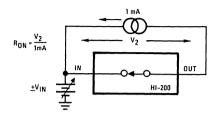

| HI-200                        | Dual SPST CMOS Analog Switch                                                                          | 5–2<br>3–4   |

| HI-201                        | Quad SPST CMOS Analog Switch                                                                          | 3-4<br>3-10  |

| HI-201HS                      | High Speed Quad SPST CMOS Analog Switch                                                               | 3-16         |

| HI-300                        | Dual SPST CMOS Analog Switch                                                                          | 3-19         |

| HI-301                        | SPDT CMOS Analog Switch                                                                               | 3-19         |

| HI-302                        | Dual DPST CMOS Analog Switch                                                                          | 3-19         |

| HI-303                        | Dual SPDT CMOS Analog Switch                                                                          | 3-19         |

| HI-304                        | Dual SPST CMOS Analog Switch                                                                          | 3-19         |

| HI-305                        | SPDT CMOS Analog Switch                                                                               | 3-19         |

| HI-306                        | Dual DPST CMOS Analog Switch                                                                          | 3-19         |

| HI-307                        | Dual SPDT CMOS Analog Switch                                                                          | 3-19         |

| HI-381                        | Dual SPST CMOS Analog Switch                                                                          | 3-24         |

| HI-384                        | Dual DPST CMOS Analog Switch                                                                          | 3-24         |

| HI-387                        | SPDT CMOS Analog Switch                                                                               | 3-24         |

| HI-390                        | Dual SPDT CMOS Analog Switch                                                                          | 3-24         |

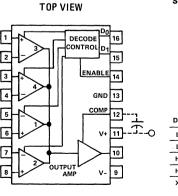

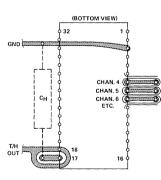

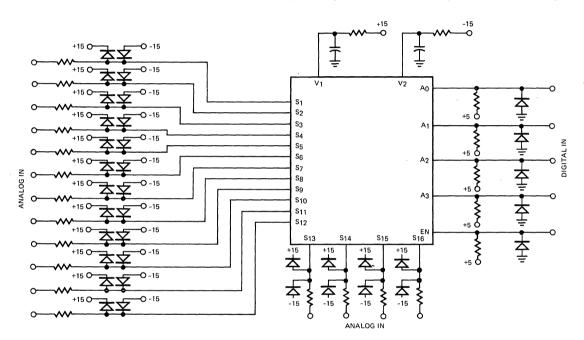

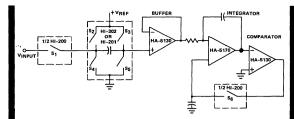

| HI-506/507                    | Single 16/Differential 8 Channel CMOS Analog Multiplexers                                             | 4-3          |

| HI-506A/507A                  | 16 Channel CMOS Analog Multiplexers with Overvoltage Protection                                       | 4-9          |

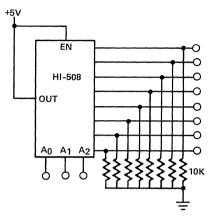

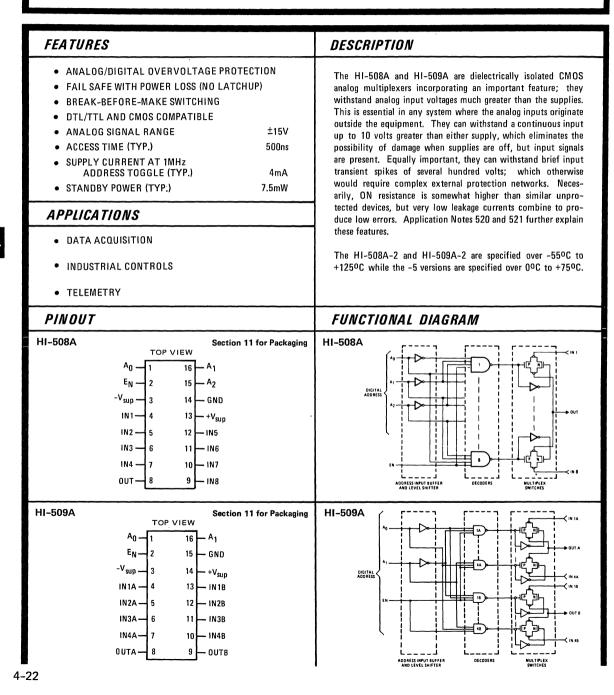

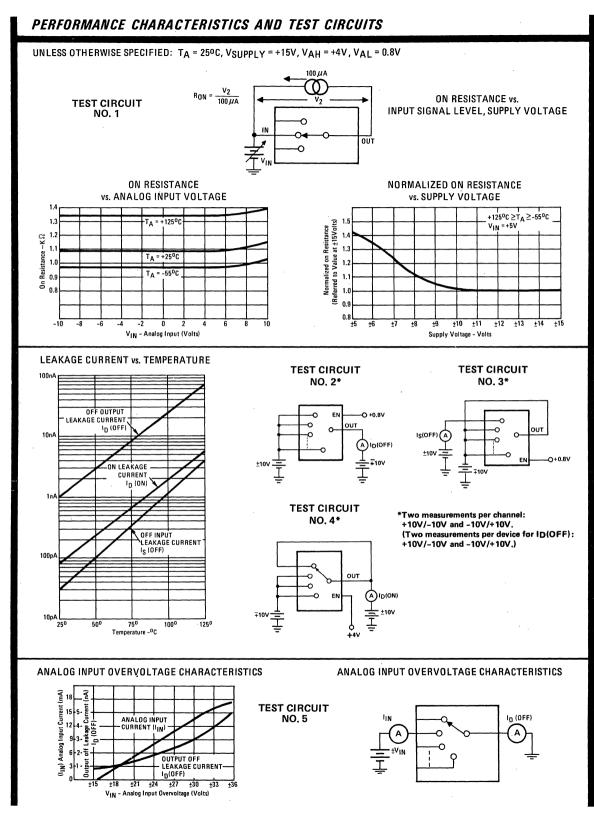

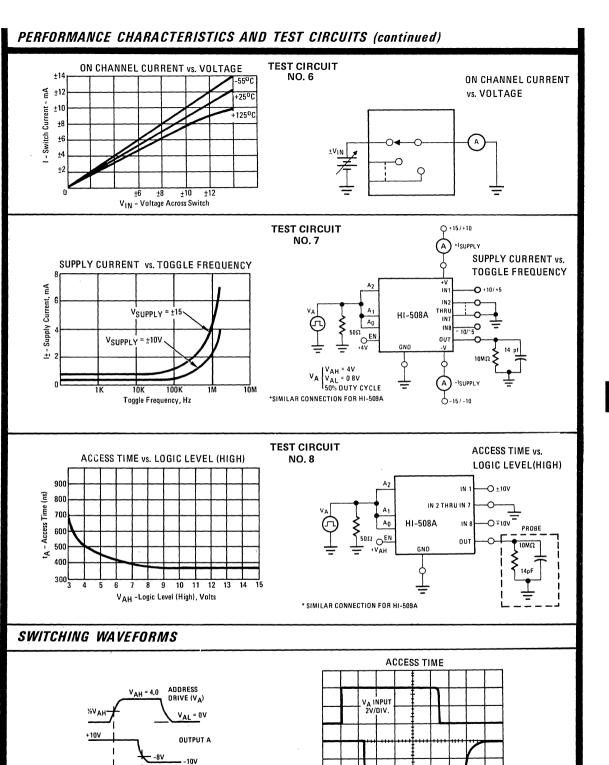

| HI-508/509                    | Single 8/Differential 4 Channel CMOS Analog Multiplexers                                              | 4-15         |

| HI-508A/509A<br>HI-516        | 8 Channel CMOS Analog Multiplexers with Overvoltage Protection                                        | 4-22         |

|                               | 16 Channel/Differential 8 Channel CMOS High Speed Analog Multiplexer                                  | 4-28<br>4-31 |

| HI-518<br>HI-524              | 8 Channel/Differential 4 Channel CMOS High Speed Analog Multiplexer<br>4 Channel Video Multiplexer    | 4-31         |

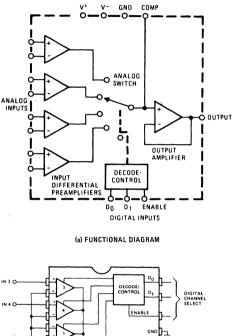

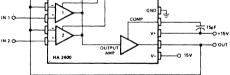

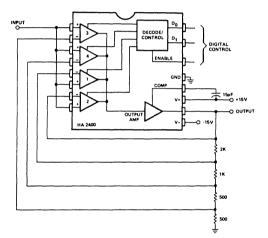

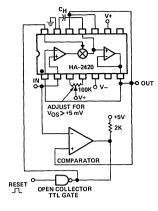

| HI-524<br>HI-539              | 4 Channel Video Multiplexer<br>Monolithic, Four Channel, Low Level, Differential Multiplexer          | 4-34<br>4-39 |

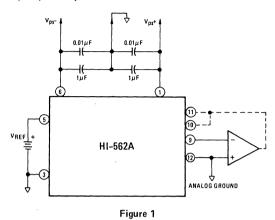

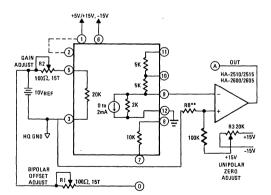

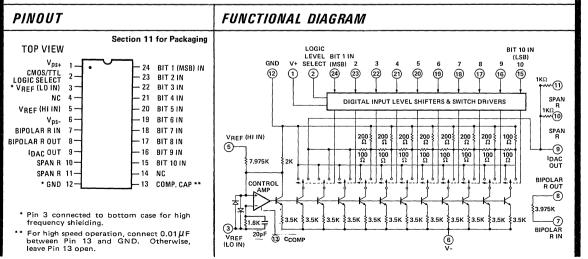

| HI-562A                       | 12 Bit High Speed Monolithic Digital-to-Analog Converter                                              | 5-12         |

|                               |                                                                                                       | 5 12         |

|                |                                                                     | -     |

|----------------|---------------------------------------------------------------------|-------|

| HI-1818A/1828A | Low Resistance 8 Channel CMOS Analog Multiplexer                    | 4-48  |

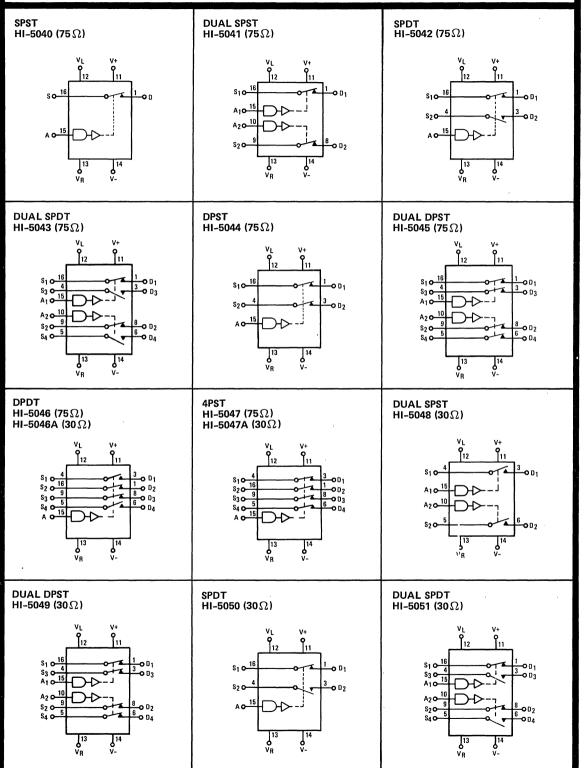

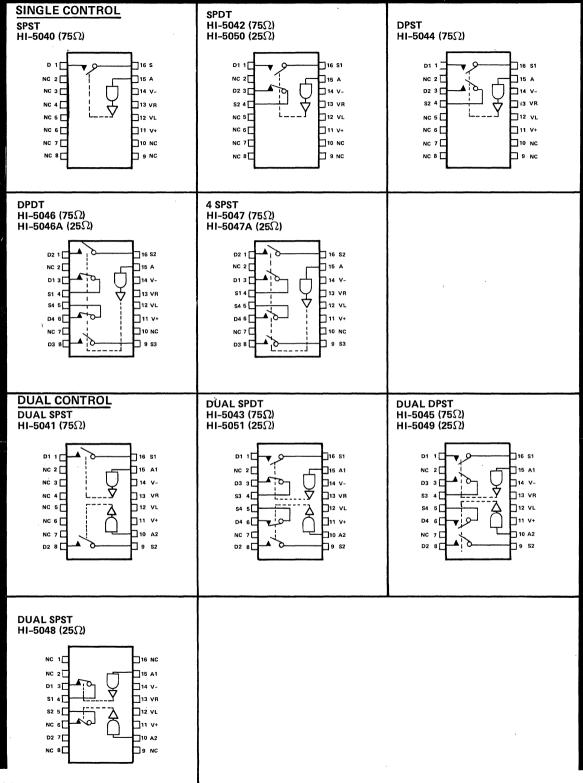

| H1-5040        | Low Resistance SPST Switch                                          | 3-29  |

| HI-5041        | Low Resistance Dual SPST Switch                                     | 3-29  |

| HI-5042        | Low Resistance SPDT Switch                                          | 3-29  |

| HI-5043        | Low Resistance Dual SPDT Switch                                     | 3-29  |

| HI-5044        | Low Resistance DPST Switch                                          | 3-29  |

| HI-5045        | Low Resistance Dual DPST Switch                                     | 3-29  |

| HI-5046        | Low Resistance DPDT Switch                                          | 3-29  |

| HI-5046A       | Low Resistance DPDT Switch                                          | 3-29  |

| HI-5047        | Low Resistance 4 PST Switch                                         | 3-29  |

| HI-5047A       | Low Resistance 4 PST Switch                                         | 3-29  |

| HI-5048        | Low Resistance Dual SPST Switch                                     | 3-29  |

| HI-5049        | Low Resistance Dual DPST Switch                                     | 3-29  |

| HI-5050        | Low Resistance SPDT Switch                                          | 3-29  |

| HI-5051        | Low Resistance Dual SPDT Switch                                     | 3-29  |

| HI-5610        | 10 Bit High Speed Monolithic Digital-to-Analog Converter            | 5-17  |

| HI-5618A/18B   | 8 Bit High Speed Digital-to-Analog Converters                       | 5-23  |

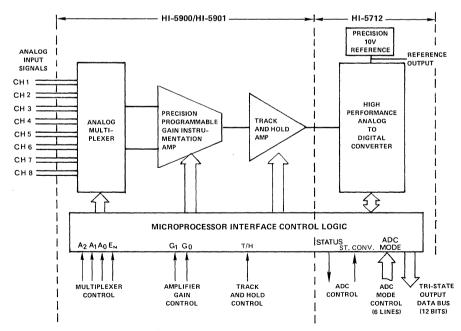

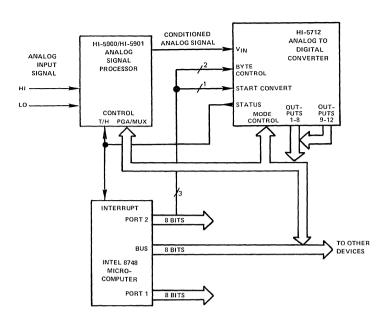

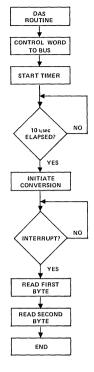

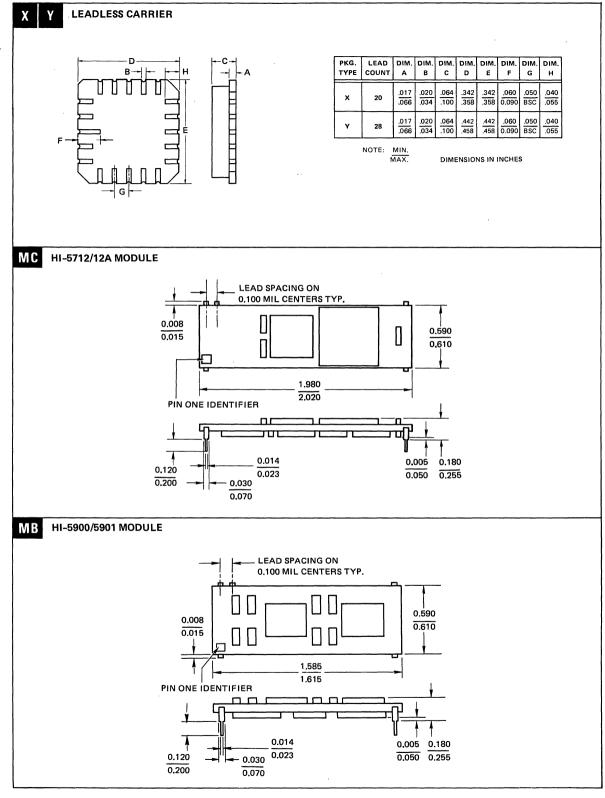

| HI-5712/12A    | High Performance 12 Bit Analog-to-Digital Converters                | 5-30  |

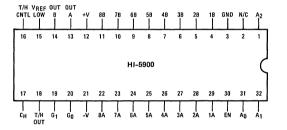

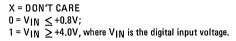

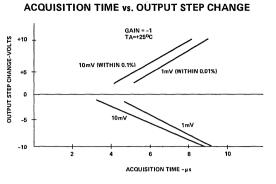

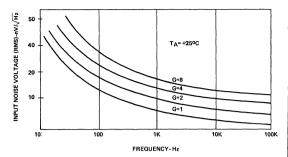

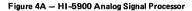

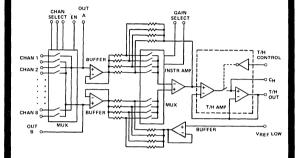

| HI-5900        | Analog Data Acquisition Signal Processor                            | 5-39  |

| HI-5901        | Analog Data Acquisition Signal Processor                            | 5-44  |

| HI-7541        | 12 Bit Multiplying Monolithic Digital-to-Analog Converter           | 5-50  |

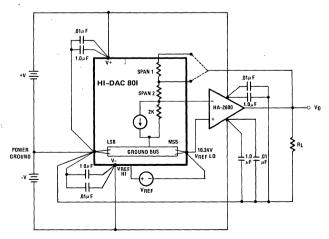

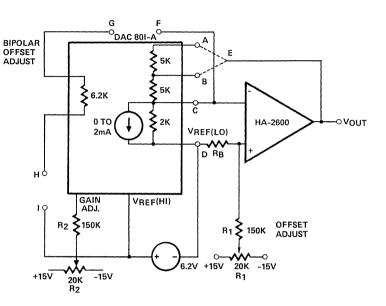

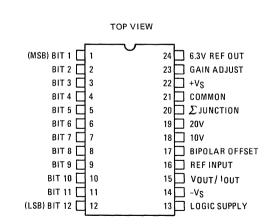

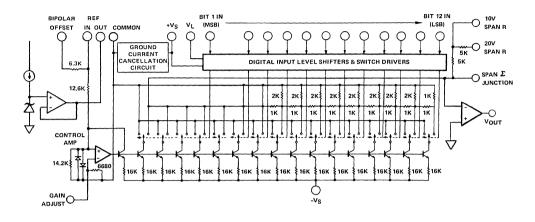

| HI-DAC801      | 12 Bit High Speed Monolithic Digital-to-Analog Converter            | 5-57  |

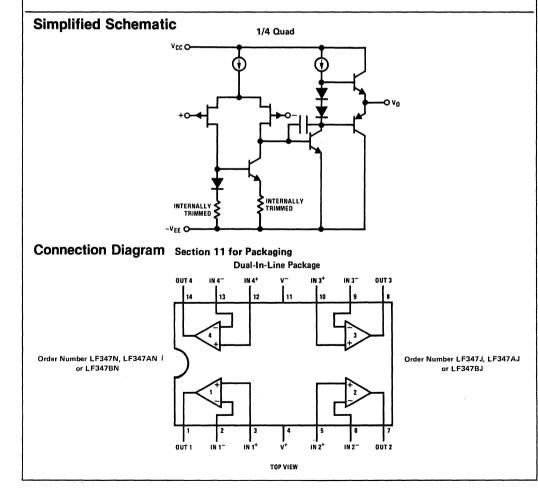

| LF347          | Wideband Quad JFET Input Operational Amplifiers                     | 2-179 |

| LF353          | Wideband Dual JFET Input Operational Amplifier                      | 2-187 |

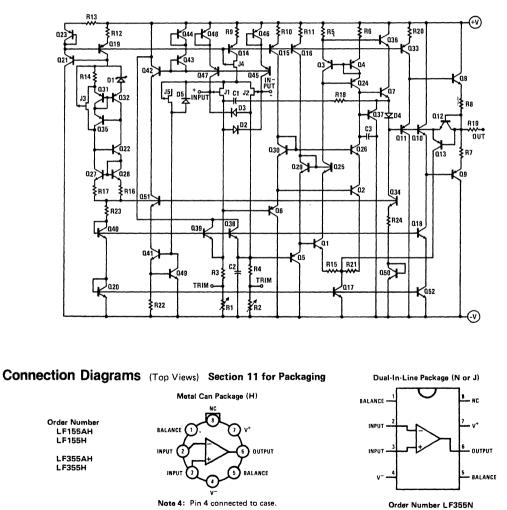

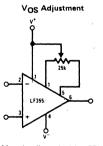

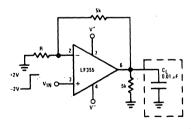

| LF355 Series   | Monolithic JFET Input Operational Amplifiers                        | 2-143 |

| LF356 Series   | Wideband Monolithic JFET Input Operational Amplifiers               | 2-156 |

| LF357 Series   | Decompensated Wideband Monolithic JFET Input Operational Amplifiers | 2-169 |

| LM108/308      | Operational Amplifiers                                              | 2-196 |

| LM108A/308A    | Operational Amplifiers                                              | 2-201 |

| LM118/318      | Operational Amplifiers                                              | 2-206 |

| LM118A/318A    | Operational Amplifiers                                              | 2-213 |

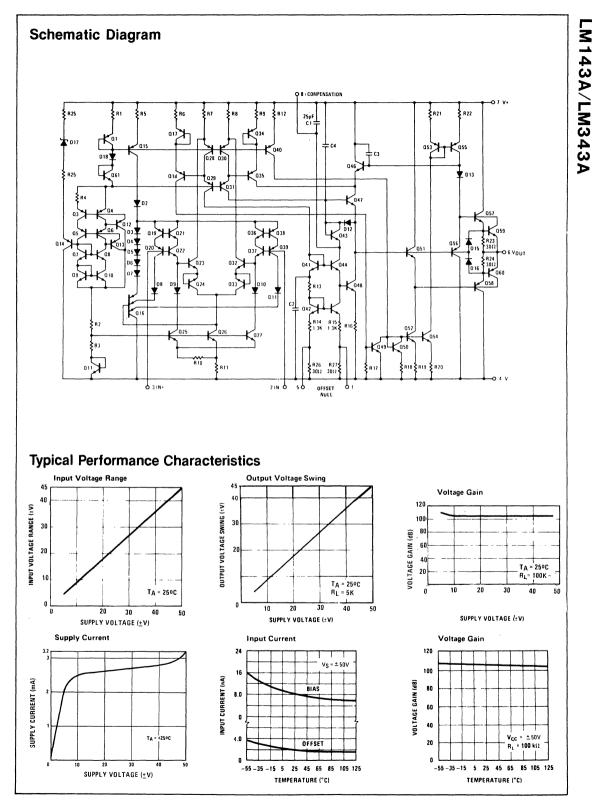

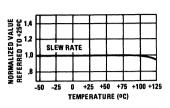

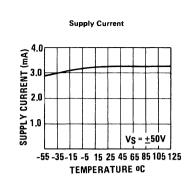

| LM143/343      | High Voltage Operational Amplifiers                                 | 2-220 |

| LM143A/343A    | High Voltage Operational Amplifiers                                 | 2-227 |

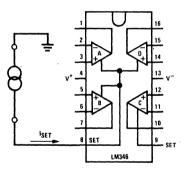

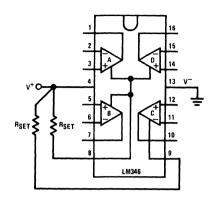

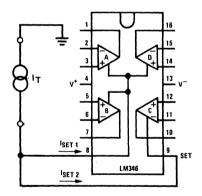

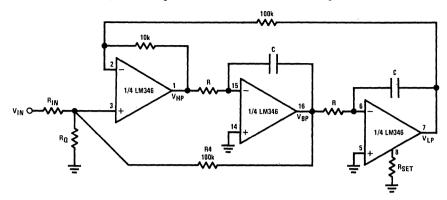

| LM146/346      | Programmable Quad Operational Amplifiers                            | 2-234 |

| LM148/348      | Quad 741 Operational Amplifiers                                     | 2-246 |

| LM148A/348A    | Quad 741 Operational Amplifiers                                     | 2-254 |

| LM1558A/1458A  | Dual Operational Amplifiers                                         | 2-262 |

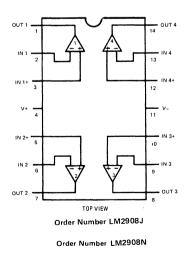

| LM2908         | Quad Operational Amplifiers                                         | 2-265 |

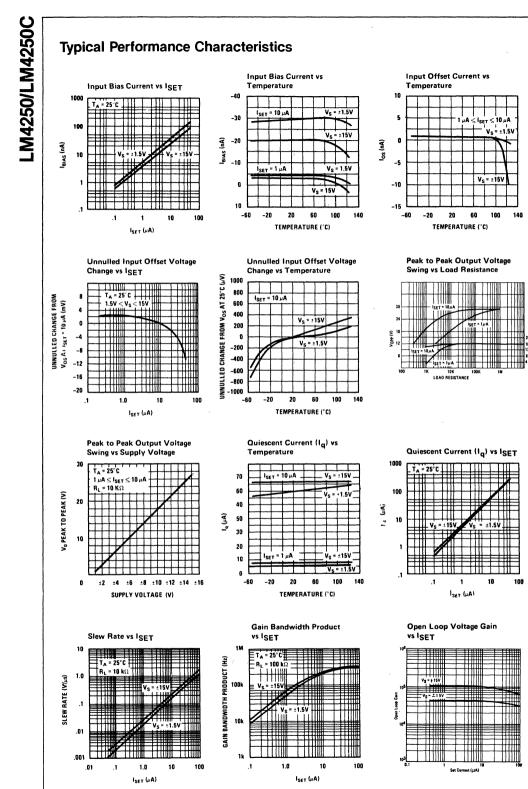

| LM4250/4250C   | Programmable Operational Amplifiers                                 | 2-267 |

| OP-07          | Ultra-Low Offset Voltage Operational Amplifier                      | 2-272 |

| 0, 01          | ona Low onset voltage Operational Amplitien                         | 2 212 |

Page

### Advance

| HA-5141/42/44<br>HA-5180/5180A<br>HA-5320<br>HC-5531<br>HI-565A<br>HI-5660<br>HI-5680<br>HI-5685<br>HI-5687<br>HI-5687 | $\mu$ Power Operational Amplifier, Single, Dual & Quad<br>Ultra Low IBIAS JFET Input Precision Operational Amplifier<br>High Speed Precision Monolithic Sample & Hold Amplifier<br>Automatic Line Balance Network<br>High Speed Monolithic Digital-to-Analog Converter with Reference<br>Fast, Complete 12 Bit A-to-D Converter with $\mu$ P Interface<br>High Speed Monolithic D-to-A Converter<br>12 Bit Low Cost Monolithic D-to-A Converter<br>High Performance Monolithic 12 Bit D-to-A Converter<br>Wide Temperature Range Monolithic 12 Bit D-to-A Converter | 2-275<br>2-277<br>5-62<br>6-28<br>5-63<br>5-64<br>5-65<br>5-66<br>5-66<br>5-68<br>5-72 |

|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

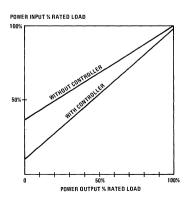

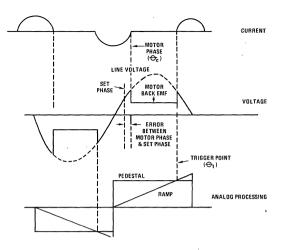

| HI-5687<br>HI-DAC16B/C<br>HV-1000/05/10                                                                                | Wide Temperature Range Monolithic 12 Bit D-to-A Converter<br>16 Bit D-to-A Converter<br>Induction Motor Energy Saver                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-70<br>5-72<br>6-30                                                                   |

|                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                        |

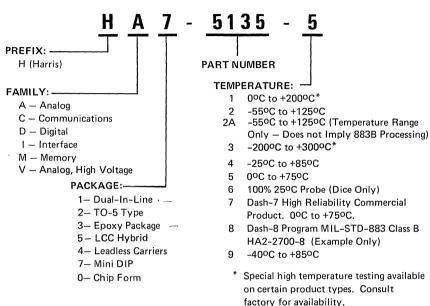

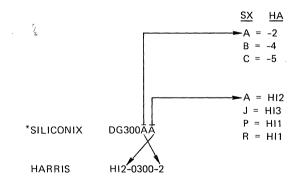

### **Ordering Information**

Harris proprietary Analog products are designated by "Harris Product Code". These products will always begin with the letter H and specific device numbers are isolated by hyphens. "Industry standards" are identified by their standardized part numbers and product. Examples of both product codes are shown below. When ordering, please refer to products by the full code identification.

### HARRIS PRODUCT CODE EXAMPLE

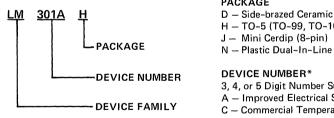

#### INDUSTRY STANDARDS PRODUCT CODE EXAMPLE

### PACKAGE

H - TO-5 (TO-99, TO-100, TO-8) J - Mini Cerdip (8-pin) N - Plastic Dual-In-Line Package

#### **DEVICE NUMBER\***

3, 4, or 5 Digit Number Suffix Indicators: A - Improved Electrical Specification

C - Commercial Temperature Range

#### DEVICE FAMILY

LF - Linear FET LM - Linear Monolithic

\* The first digit in the device number signifies the operating temperature range. A "1" denotes a Military temperature range device (~55°C to +125°C), A "3" denotes a Commercial temperature range device (0°C to +70°C).

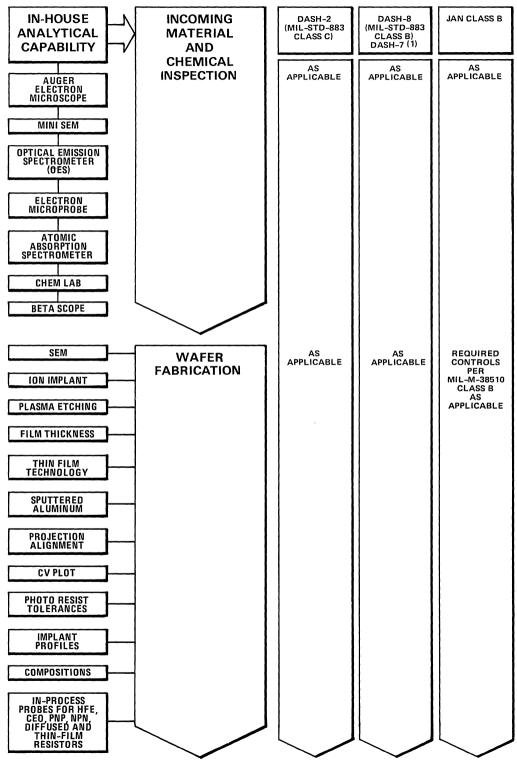

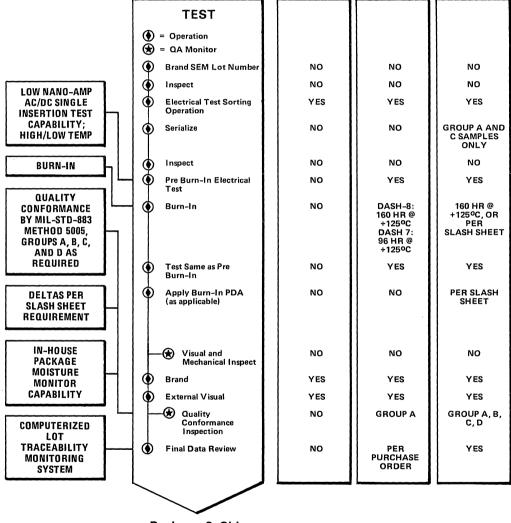

#### HARRIS DASH 8 PROGRAM

As a service to users of High Rel products Harris makes readily available via the high reliability DASH 8 program many products from our product lines. Parts screened to MIL-STD-883 Method 5004 Class B are simply branded with the post-script "-8" to the appropriate Harris part numbers, in effect, offering "off the shelf" delivery. For details concerning this special Harris program for High Rel users, see Section 10 of this Data Book.

### HARRIS DASH 7 PROGRAM

The Harris DASH 7 program extends the normal processing to include an added burn-in step for enhanced reliability. Details on DASH 7 are included in Section 10 of this Data Book.

### HARRIS ANALOG JAN PROGRAM

In March 1980, Harris received JAN certification for the Analog Wafer Fabrication and Assembly facilities. All Harris Analog JAN products are produced on the certified line in strict compliance with all MIL-M-38510 program requirements.

Many Harris Analog high performance ICs are now available for immediate delivery in JAN Class B form. Consult your local Harris representative for an up-to-date list of all Harris JANqualified devices. JAN from Harris offers the IC user high reliability, quality, and performance at a lower price and with faster delivery than similar products fabricated in accordance with non-standard source control drawings.

### SPECIAL ORDERS

For best availability and price, it is urged that standard "Product Code" devices be specified, which are available worldwide from authorized distributors. Where enhanced reliability is needed, note standard "Dash 8" screening described in this Data Book. Harris application engineers may be consulted for advice about suitability of a part for a given application.

If additional electrical parameter guarantees or reliability screening are absolutely required, a Request for Quotation and Source Control Drawing should be submitted through the local Harris Sales Office or Sales Representative. Since many electrical parameters may be economically assured through design analysis, characterization, or correlation with other parameters, additionally desired parameters should be labeled, "Vendor will guarantee, but not necessarily test".

Harris reserves the right to decline to quote, or to request modification to special screening requirements. Harris Analog I.C. processes produce circuits more rugged than similar ones. However, no semiconductor is immune from damage resulting from the sudden application of many thousands of volts of static electricity. While the phenomenon of catastrophic failure of devices containing MOS transistors or capacitors is well known, even bipolar circuits can be damaged by static discharge, with altered electrical properties and diminished reliability. None of the common I.C. internal protection networks operate quickly enough to positively prevent damage.

It is suggested that all semiconductors be handled, tested, and installed using standard "MOS handling techniques" of proper grounding of personnel and equipment. Parts and subassemblies should not be in contact with untreated plastic bags or wrapping material. High impedance I.C. inputs wired to a P.C. connector should have a path to ground on the card.

### HANDLING RULES

Since the introduction of integrated circuits with MOS structures and high quality junctions, a safe and effective means of handling these devices has been of primary importance. One method employed to protect gate oxide structures is to incorporate input protection diodes directly on the monolithic chip. However, there is no completely foolproof system of chip input protection in existance in the industry. In addition most compensation networks in linear circuits are located at high impedance nodes, where protection networks would disturb normal circuit operation. If static discharge occurs at sufficient magnitude (2kV or more), some damage or degradation will usually occur. It has been found that handling equipment and personnel can generate static potentials in excess of 10KV in a low humidity environment; thus it becomes necessary for additional measures to be implemented to eliminate or reduce static charge. It is evident, therefore, that proper handling procedures or rules should be adopted.

Elimination or reduction of static charge can be accomplished as follows:

- Use conductive work stations. Conductive plastic\* mats on work benches and floor, connected to ground through a 1-M ohm resistor, help eliminate static build-up and discharge. Do not use metallic surfaces.

- · Ground all handling equipment.

- Ground all handling personnel with a conductive bracelet through 1-M ohm to ground (the 1-M ohm resistor will prevent electroshock injury to personnel). Transient product personnel should wear grounding heel straps.

- Smocks, clothing, and especially shoes of certain insulating materials (notably nylon) should not be worn in areas where devices are handled. These materials, highly dielectric in nature, will hold, or aid, in the generation of a static change. Where they cannot be eliminated natural materials such as cotton etc. should be used to minimize charge generation capacity. Conductive smocks are also available as an alternative.

- Control relative humidity to as high a level as practical. 50% is generally considered sufficient (operations should cease if R. H. falls below 25%).

- Ionized airblowers reduce charge build-up in areas where grounding is not possible or practical.

- Devices should be in conductive carriers during all phases of transport. Leads may be shorted bytubular metallic carriers, conductive foam or foil.

- In automated handling equipment, the belts, chutes, or other surfaces should be of conducting non-metal material. If this is not possible, ionized air blowers or ionizing bars may be a good alternative.

\*Supplier 3M Company 'Static Control Table Mat 8210/8210R'' ''Static Control Floor Mat 8200/8200R''

### Harris Analog I. C. Technologies

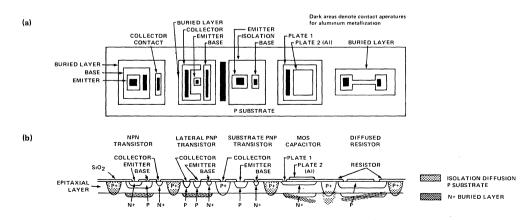

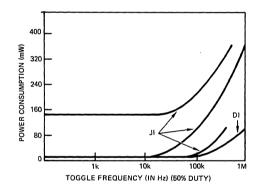

#### JUNCTION ISOLATION (J.I.)

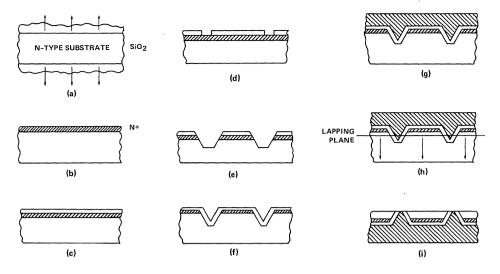

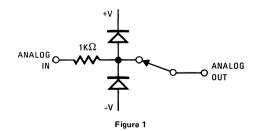

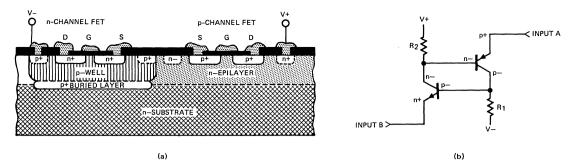

This is the most common integrated circuit proccess. Bipolar I.C.'s generally begin with a p-type wafer into which a buried layer pattern, if used, is first diffused. Then the n-type epitaxial layer is grown, and p-type isolation walls are diffused around each area which is to be electrically isolated from the other circuitry. These isolation walls must be diffused deeply into the wafer in order to contact the original p-substrate. In operation, the p-substrate and isolation walls are connected to the most negative circuit potential, so that each active area is surrounded on the sides and bottom by a reverse biased junction through which negligible current flows (Figure 1).

To complete the I.C., base and emitter diffusions are performed, the wafer is coated with aluminum and the conductor pattern is etched.

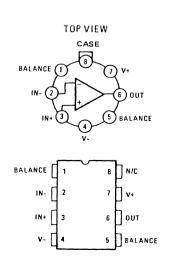

Representative Harris devices using this process are HA-4741, HA-5082, and HA-5084.

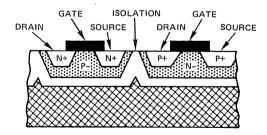

#### DIELECTRIC ISOLATION (D.I.)

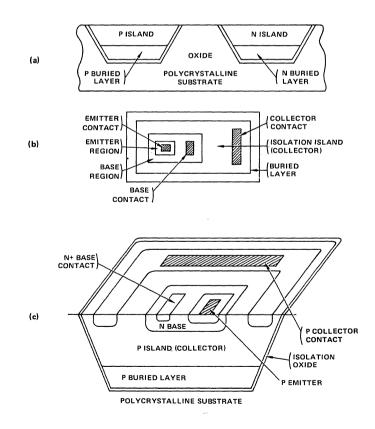

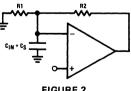

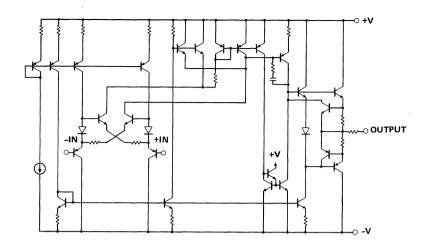

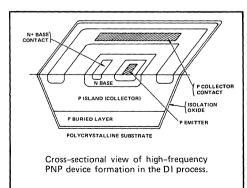

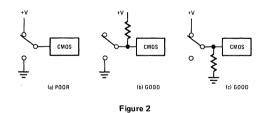

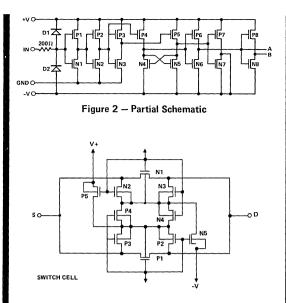

A somewhat different process has been proven particularly advantageous for fabricating high performance analog I.C.'s. This is dielectric isolation (D.I.), where each active area is surrounded on the sides and bottom by an insulating layer of silicon dioxide, and for mechanical strength imbedded in polycrystalline silicon. This process for bipolar I.C.'s begins with a wafer of n-type silicon. The side of the wafer which will eventually be the bottom is deeply etched to form the sidewall pattern, then silicon dioxide and polycrystalline silicon are grown to fill the etched "moats". The opposite side of the wafer is then polished until the insulating sidewalls appear at the wafer surface (Figure 2). Conventional diffusion and metallization processes follow to complete the I.C. D.I. for analog I.C.'s has a number of advantages:

Almost all op amp designs require at least one PNP transistor in the signal path. Typical J.I. op amps must use a lateral PNP which inherently has very low frequency response, limiting typical compensated bandwidth to 1MHz. The D.I. process makes it practical to build a vertical PNP with much higher bandwidth making possible compensated op amp bandwidths of 12MHz or higher (Figure 3). Also, transistor collector to substrate capacitance is 2/3 less using D.I., further enhancing high frequency performance.

- 2. Other devices such as optimally specified MOS or JFET transistors may be fabricated on the same chip. Isolated diffused and thin film resistors are also practical.

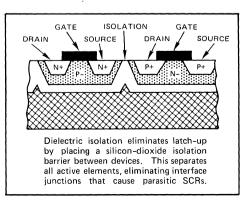

- 3. The isolation removes the possibility of parasitic SCR's which might create latchup under certain sequences of power and signal application.

- 4. Leakage currents to the substrate under high temperature conditions are greatly reduced. While the circuits in this data book were not specifically designed for operating temperatures greater than +125°C, many have shown superior performance. For I.C.'s requiring the ultimate in radiation resistance, Harris Semiconductor Programs Division should be consulted.

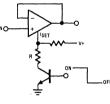

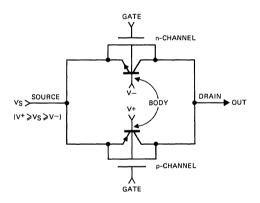

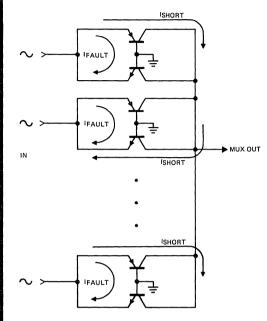

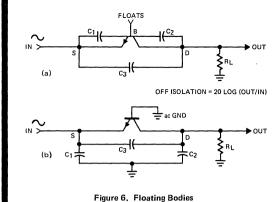

#### DIELECTRIC ISOLATED CMOS

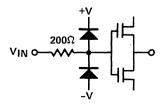

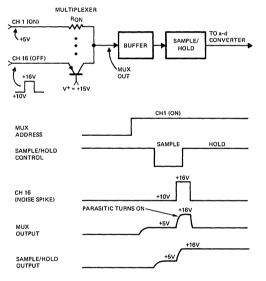

J.I. processed CMOS Analog I.C.'s, which are generally used in conjunction with several power supplies, are particularly prone to parasitic SCR latchup failures and failures due to input voltage spikes. The D.I. CMOS process, which is compared in detail in Harris Application Note 521, has proved to be the best solution.

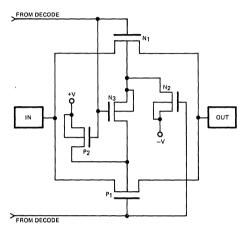

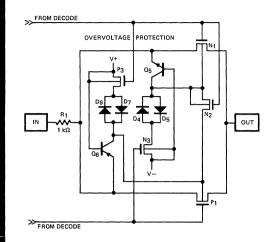

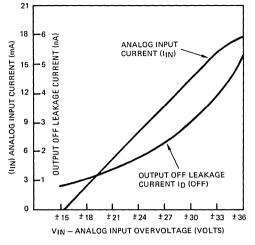

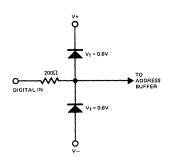

Since analog multiplexers are often used at the input of a data acquisition system, particular attention must be paid to the possibility of damaging input overvoltage conditions. Harris has provided an effective answer in the HI-506A through HI-509A multiplexers with built-in overvoltage protection.

Figure 1 – Structures of various components formed in the junction-isolation process. (a) Topological view. (b) Cross-sectional view.

Figure 2- Process steps for dielectric isolation. (a) Surface preparation, (b) N-buried layer diffusion, (c) masking oxide, (d) isolation pattern, (e) silicon etch, (f) dielectric oxide, (g) polycrystalline deposition, (h) backlap and polish, (i) finished slice.

Figure 3- The high-frequency process. (a) Cross-sectional view of P and N islands for PNP and NPN transistors. (b) Topological view showing relative placement of transistor regions. (c) Cross-sectional view of high-frequency PNP device formation in the D. I. process.

| MANU-<br>FACTURER | PART NUMBER                                                                                                                                                                                                                                     | HARRIS PIN-FOR-PIN<br>REPLACEMENT                                                                                                                              | HARRIS CLOSEST<br>REPLACEMENT                                | SUGGESTED FOR<br>NEW DESIGN                                                |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------|

| AMD               | AM118/318<br>AM715<br>AM1660                                                                                                                                                                                                                    | LM118/318                                                                                                                                                      | LM118A/318A                                                  | LM118A/318A<br>HA-2520/25<br>HA-2500/05<br>HA-2600/05                      |

|                   | AM6012                                                                                                                                                                                                                                          |                                                                                                                                                                | HI-562A                                                      | HI-562A                                                                    |

| ANALOG<br>DEVICES | AD505<br>AD507JH*<br>AD507SH<br>AD509JH*<br>AD509SH<br>AD518<br>AD562<br>AD565A<br>AD566A<br>AD574A<br>AD582<br>AD583KS<br>AD7501<br>AD7502<br>AD7503<br>AD7506TD*<br>AD7507TD*<br>AD7510<br>AD7511<br>AD7512<br>AD7513TH*<br>AD7541<br>ADDAC80 | HA2-2625-5<br>HA2-2620-2<br>HA2-2525-5<br>HA2-2520-2<br>LM318<br>HI-565A<br>HI-574A<br>HA1-2425-3<br>HI1-506-2<br>HI1-507-2<br>HI2-200-2<br>HI-7541<br>HI-5680 | HA-2530/35<br>HA-2510/15<br>HI-562A<br>HI-5660<br>HA-2420/25 | HI-5660<br>HI-1818A<br>HI-1828A<br>HI-1818A<br>HI-201<br>HI-201<br>HI-5043 |

| BURR<br>BROWN     | 3500/3510A<br>3500/3510R<br>3503J<br>3506J<br>3507J<br>3508J<br>3527AM<br>3553AM<br>MPC4D<br>MPC8S<br>MPC8D<br>MPC16S<br>DAC80                                                                                                                  | HA2-2505-5<br>HA2-2605-5<br><b>HA2-2525-5</b><br>HA2-2625-5<br>H11-509A-5<br>H11-508A-5<br>H11-507A-5<br>H11-506A-5<br>H1-5680                                 | HA2-5170-5                                                   | HA-2605<br>HA-2605<br>HA-2630/35                                           |

| DATEL             | AM-450-2<br>AM-452-2<br>AM-460-2<br>AM-462-1<br>AM-462-2<br>AM-464-2<br>AM-464-2<br>AM-490-2A<br>MX-808<br>MX-1606                                                                                                                              | HA2-2505-5<br>HA2-2525-5<br>HA2-2605-5<br>HA1-2625-5<br>HA2-2625-5<br>HA2-2645-5<br>HA2-2905-5<br>HP-508A-5<br>HI-506A-5                                       |                                                              |                                                                            |

\*"K" equivalent is either military or selected commercial

| (continued)                             |                        |                                   |                               |                             |

|-----------------------------------------|------------------------|-----------------------------------|-------------------------------|-----------------------------|

| MANU-<br>FACTURER                       | PART NUMBER            | HARRIS PIN-FOR-PIN<br>REPLACEMENT | HARRIS CLOSEST<br>REPLACEMENT | SUGGESTED FOR<br>NEW DESIGN |

| DATEL                                   | MXD-409                | HI-509A-5                         |                               |                             |

| (Continued)                             | MXD-807                | HI-507A-5                         |                               |                             |

|                                         | SHM-1C-1               | HA1-2425-5                        |                               |                             |

|                                         | DAC-681                | HI-562A                           |                               |                             |

| EXAR                                    | XR4212                 |                                   | HA-4741                       |                             |

| <u> </u>                                |                        |                                   |                               | LLA 2020/25                 |

| FAIRCHILD                               | μΑ702                  | }                                 | HA-2620/2625                  | HA-2620/25                  |

|                                         | μΑ709                  |                                   | HA-2020/2025                  |                             |

|                                         | μΑ714                  |                                   | HA-5150                       | HA-2520/25                  |

|                                         | μΑ715                  |                                   |                               |                             |

|                                         | μΑ727                  |                                   |                               | HA-5130                     |

|                                         | μΑ740                  |                                   | 114 2620/2625                 | HA-5170                     |

|                                         | μΑ741                  |                                   | HA-2620/2625                  | 114 0050/55                 |

|                                         | μΑ747                  |                                   |                               | HA-2650/55                  |

|                                         | μΑ748                  |                                   | 114 0510/15                   | HA-2620/25                  |

|                                         | μΑ772                  |                                   | HA-2510/15                    |                             |

|                                         | μΑ776                  |                                   | HA-2720/25                    | 114 0000/05                 |

|                                         | μΑ791                  |                                   |                               | HA-2630/35                  |

|                                         | SH3002<br>1558/1458    |                                   | HA-2650/55                    |                             |

| kina kana kana kana kana kana kana kana | 1556/1456              |                                   | HA-2050/55                    |                             |

| INTERSIL                                | IH201                  | HI-201                            |                               |                             |

|                                         | IH200                  | HI-201                            |                               |                             |

|                                         | 4250                   |                                   | HA-2720                       |                             |

|                                         | 4250C                  |                                   | HA-2725                       |                             |

|                                         | IH5040MDE              | H11-5040-2                        |                               |                             |

|                                         | IH5040CDE              | HI1-5040-5                        |                               |                             |

|                                         | IH5041MDE              | HI1-5041-2                        |                               |                             |

|                                         | IH5041CDE              | HI1-5041-5                        |                               |                             |

|                                         | IH5042MDE              | HI1-5042-2                        |                               |                             |

|                                         | IH5042CDE              | HI1-5042-5                        |                               |                             |

|                                         | IH5043MDE              | HI1-5043-2                        |                               |                             |

|                                         | IH5043CDE              | HI1-5043-5                        |                               |                             |

|                                         | IH5044MDE              | HI1-5044-2                        |                               |                             |

|                                         | IH5044CDE              | HI1-5044-5                        |                               |                             |

|                                         | IH5045MDE              | HI1-5045-2                        |                               |                             |

|                                         | IH5045CDE              | H11-5045-5                        |                               |                             |

|                                         | IH5046MDE              | HI1-5046-2                        |                               |                             |

|                                         | IH5046CDE              | HI1-5046-5                        |                               |                             |

|                                         | IH5047MDE              | HI1-5047-2                        |                               |                             |

|                                         | IH5047CDE              | H11-5047-5                        |                               |                             |

|                                         | IH5048MDE              | HI1-5048-2                        |                               |                             |

|                                         | IH5048CDE              | HI1-5048-5                        |                               |                             |

|                                         | IH5049MDE              | HI1-5049-2                        |                               |                             |

|                                         | IH5049CDE<br>IH5050MDE | HI1-5049-5<br>HI1-5050-2          |                               |                             |

|                                         |                        | HI1-5050-2<br>HI1-5050-5          |                               |                             |

|                                         | IH5050CDE              |                                   |                               |                             |

|                                         | IH5051MDE              | HI1-5051-2                        |                               |                             |

|                                         | IH5051CDE              | HI1-5051-5                        |                               | HA 2520/25                  |

|                                         | 8017                   |                                   |                               | HA-2520/25                  |

|                                         | 8021M                  |                                   | HA-2720                       |                             |

|                                         | 8021C                  | HA-8023                           | HA-2725                       |                             |

|                                         | 8023                   | HA-0023                           |                               |                             |

|                                         | IH5110/5111            | HI_7541                           |                               | HA-2420/25                  |

|                                         | AD7541                 | HI-7541                           |                               | L                           |

| MANU-<br>FACTURER       | PART NUMBER                                                                                                                                                                                                                                                                                                 | HARRIS PIN-FOR-PIN<br>REPLACEMENT                                                                            | HARRIS CLOSEST<br>REPLACEMENT                                                | SUGGESTED FOR<br>NEW DESIGN                                                                                                                                               |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTERSIL<br>(Continued) | IH5060<br>IH5070<br>HA-2500/02/05<br>HA-2510/12/15<br>HA-2520/22/25<br>HA-2600/02/05<br>HA-2620/22/25                                                                                                                                                                                                       | HA-2500/02/05<br>HA-2510/12/15<br>HA-2520/22/25<br>HA-2600/02/05<br>HA-2620/22/25                            | HI-506A<br>HI-507A                                                           |                                                                                                                                                                           |

| INTRONICS               | A-560<br>A-561<br>A-570                                                                                                                                                                                                                                                                                     | HA2-2525-5<br>HA2-2625-5<br>HA2-2535-5                                                                       |                                                                              |                                                                                                                                                                           |

| MOTOROLA                | MC1520/1420<br>MC1530/1531/<br>1430/31<br>MC1536/1436<br>MC1538/1438<br>MC1539/1439<br>MC1545/1445<br>MC1554/1454<br>MC1556/1456<br>MC1558/1458<br>MC3301/3401<br>MC3302<br>MC3403/3505<br>MC3412<br>MX4741                                                                                                 | LM1558/1458A<br>HI-565A                                                                                      | HA-2640/45<br>HA-2650/55<br>HA-4741<br>HA-4741                               | HA-2600/05<br>HA-2600/05<br>HA-2620/2635<br>HA-2620/2505<br>HA-2620/2635<br>HA-2620/2635<br>HA-2600/05<br>HA-4741<br>HA-4900<br>HA-2700/05                                |

| NATIONAL                | LF11508/13508<br>LF11509/13509<br>LF11201/12201/13201<br>LF155A/156A/157A<br>LF355A/356A/357A<br>LF198/398<br>LH0002<br>LH0003<br>LH0004<br>LH0005<br>LH0022/42/52<br>LH0023/43<br>LH0024<br>LH0032<br>LH0033/63<br>LH0052<br>LH0052<br>LH0062<br>LM102/302<br>LM108/208/308<br>LM108/208A/308A<br>LM10/310 | LF 155A/156A/157A<br>LF 355A/356A/357A<br>LF 342<br>HA-5180A<br>HA-5162<br>LM108/208/308<br>LM108A/208A/308A | HI-508A<br>HI-509A<br>HI-201<br>HA-5100-2<br>HA-5105-5<br>HA-2540<br>HA-2540 | HA-2420/25<br>HA-2630<br>HA-2520<br>HA-2640<br>HA-2620<br>HA-5180<br>HA-2420/25<br>HA-2530/35<br>HA-2630/35<br>HA-2630/05<br>HA-2700/04/05<br>HA-2700/04/05<br>HA-2500/05 |

|                         | 1                                                                                                                                                                                                                                                 | (continued)                                                                                                                                         | T                                                                                                                  | r                                                                       |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| MANU-<br>FACTURER       | PART NUMBER                                                                                                                                                                                                                                       | HARRIS PIN-FOR-PIN<br>REPLACEMENT                                                                                                                   | HARRIS CLOSEST<br>REPLACEMENT                                                                                      | SUGGESTED FOR<br>NEW DESIGN                                             |

| NATIONAL<br>(Continued) | LM112/212/312<br>LM118/318<br>LM124/324<br>LM139/339<br>LM143/343<br>LM144/344<br>LM148/248/348<br>LM149/349<br>LM4250/4250C<br>DAC1280                                                                                                           | LM118/318<br>LM143/343<br>LM148/248/348<br>LM4250/4250C<br>H1-5680                                                                                  | LM118A/318A<br>HA-4741<br>HA-2640/45<br>HA-4741                                                                    | HA-2700/04/05<br>HA-2510/15<br>HA-4900/05<br>LM143A/343A<br>LM148A/348A |

| PRECISION<br>MONO.      | MUX-08<br>MUX-09<br>OP-01<br>OP-07883AJ<br>OP-07AJ<br>OP-07883J<br>OP-07J<br>OP-07EP/CP/DP<br>SMP 10/11<br>MUX-88<br>OP-15A<br>OP-15E<br>OP-15F<br>OP-15F<br>OP-17A<br>OP-17E<br>OP-17F<br>REF-01A<br>REF-01E<br>SSS1558/1458<br>DAC-12<br>SSS562 | HI-508/508A<br>HI-509/509A<br>HA2-5130-8<br>HA2-5130-2/OP-07AJ<br>HA2-5135-8<br>HA2-5135-2/OP-07J<br>HA3-5135-5<br>HA-2420/25<br>HI-508A<br>HI-508A | HA-5170-2<br>HA-5170-5<br>HA-5170-5<br>HA-5110-2<br>HA-5110-5<br>HA-5115-5<br>HA-1608-2<br>HA-1608-5<br>HA-2650/55 | HA-2600/05<br>HA-2500/05<br>HI-562A                                     |

| RCA                     | CA3020<br>CA3078<br>CA3100<br>CA6078<br>CD4016                                                                                                                                                                                                    |                                                                                                                                                     | HA-5144                                                                                                            | HA-2630/35<br>HA-2720<br>HA-2520/25<br>HA-2720<br>HI-201                |

| RAYTHEON                | RM/RC1556A<br>RM/RC4131<br>RM/RC4136<br>RM4156<br>RC4156<br>HA1-4741-2<br>HA1-4741-5<br>RM/RC4531<br>RM/RC4558                                                                                                                                    | HA1-4156-2<br>HA1-4156-5<br>HA1-4741-2<br>HA1-4741-5                                                                                                | HA-2650/55                                                                                                         | HA-2600/05<br>HA-2600/05<br>HA-4741<br>LM348<br>HA-2500/05              |

| MANU-<br>FACTURER | PART NUMBER         | HARRIS PIN-FOR-PIN<br>REPLACEMENT | HARRIS CLOSEST<br>REPLACEMENT | SUGGESTED FOR<br>NEW DESIGN            |

|-------------------|---------------------|-----------------------------------|-------------------------------|----------------------------------------|

| SIGNETICS         | 5537<br>531<br>5556 |                                   |                               | HA-2420/25<br>HA-2510/15<br>HA-2600/05 |

|                   | 5539<br>5558        | HA-2539                           | HA-2650/55                    |                                        |

| SILICON           | SG741S              |                                   |                               | HA-2500                                |

| GENERAL           | SG741SG             |                                   |                               | HA-2505                                |

| SILICONIX         | DG181               |                                   |                               | HI-381, HI-5048                        |

|                   | DG182               |                                   |                               | HI-381, HI-5041                        |

|                   | DG184               |                                   |                               | HI-384, HI-5049<br>HI-384, HI-5045     |

|                   | DG185               | · · ·                             |                               | HI-384, HI-5045                        |

|                   | DG187               |                                   |                               | HI-387, HI-5050                        |

|                   | DG188<br>DG190      |                                   |                               | HI-390, HI-5051                        |

|                   | DG190               |                                   |                               | HI-390, HI-5043                        |

|                   | DG200AA             | H12-0200-2                        |                               | 11-550, 11-5045                        |

|                   | DG200AA<br>DG200BA  | H12-0200-2                        |                               |                                        |

|                   | DG200BA<br>DG200AP  | HI1-0200-2                        |                               |                                        |

|                   | DG200BP             | HI1-0200-4                        |                               |                                        |

|                   | DG200CJ             | H13-0200-5                        |                               |                                        |

|                   | DG201AP             | H11-0201-2                        |                               |                                        |

|                   | DG201BP             | HI1-0201-4                        |                               |                                        |

|                   | DG201CJ             | HI3-0201-5                        |                               | HI3-0201HS-J                           |

|                   | DG211CK             |                                   |                               | HI3-0201-5                             |

|                   | DG300AA             | H12-0300-2                        |                               |                                        |

|                   | DG300BA             | H12-0300-4                        |                               |                                        |

|                   | DG300AP             | HI1-0300-2                        |                               |                                        |

|                   | DG300BP             | HI1-0300-4                        |                               |                                        |

|                   | DG300CJ             | HI3-0300-5                        |                               |                                        |

|                   | DG301AA             | HI2-0301-2                        |                               |                                        |

|                   | DG301BA             | HI2-0301-4                        |                               |                                        |

|                   | DG301AP             | HI1-0301-2                        |                               |                                        |

|                   | DG301BP             | HI1-0301-4                        |                               |                                        |

|                   | DG301CJ             | HI3-0301-5                        |                               |                                        |

|                   | DG302AP             | HI1-0302-2                        |                               |                                        |

|                   | DG302BP             | HI1-0302-4                        |                               |                                        |

|                   | DG302CJ             | HI3-0302-5                        |                               |                                        |

|                   | DG303AP             | HI1-0303-2                        |                               |                                        |

|                   | DG303BP             | HI1-0303-4                        |                               |                                        |

|                   | DG303CJ             | HI3-0303-5                        |                               |                                        |

|                   | DG304AA<br>DG304BA  | HI2-0304-2<br>HI2-0304-4          |                               |                                        |

|                   | DG304BA<br>DG304AP  | H12-0304-4<br>H11-0304-2          |                               |                                        |

|                   | DG304AP<br>DG304BP  | HI1-0304-2<br>HI1-0304-4          |                               |                                        |

|                   | DG304CJ             | HI3-0304-5                        |                               |                                        |

|                   | DG305AA             | HI2-0305-2                        |                               |                                        |

|                   | DG305BA             | H12-0305-4                        |                               |                                        |

|                   | DG305AP             | HI1-0305-2                        |                               |                                        |

|                   | DG305BP             | HI1-0305-4                        |                               |                                        |

|                   | DG305CJ             | HI3-0305-5                        |                               |                                        |

|                   | DG306AP             | HI1-0306-2                        |                               |                                        |

|                   | DG306BP             | HI1-0306-4                        |                               |                                        |

|                   | DG306CJ             | HI3-0306-5                        |                               |                                        |

1

| MANU-<br>FACTURER | PART NUMBER | HARRIS PIN-FOR-PIN<br>REPLACEMENT | HARRIS CLOSEST<br>REPLACEMENT | SUGGESTED FOR<br>NEW DESIGN |

|-------------------|-------------|-----------------------------------|-------------------------------|-----------------------------|

| SILICONIX         | DG307AP     | HI1-0307-2                        |                               |                             |

| (Continued)       | DG307BP     | HI1-0307-4                        |                               |                             |

|                   | DG307CJ     | HI3-0307-5                        |                               |                             |

|                   | DG381AA     | HI2-0381-2                        |                               |                             |

|                   | DG381BA     | HI2-0381-4                        |                               |                             |

|                   | DG381AP     | HI1-0381-2                        |                               |                             |

|                   | DG381BP     | HI1-0381-4                        |                               |                             |

|                   | DG381CJ     | HI3-0381-5                        |                               |                             |

|                   | DG384AP     | HI1-0384-2                        |                               |                             |

|                   | DG384BP     | HI1-0384-4                        |                               |                             |

|                   | DG384CJ     | HI3-0384-5                        |                               |                             |

|                   | DG387AA     | H12-0387-2                        |                               |                             |

|                   | DG387BA     | H12-0387-4                        |                               |                             |

|                   | DG387AP     | HI1-0387-2                        |                               |                             |

|                   | DG387BP     | HI1-0387-4                        |                               |                             |

|                   | DG387CJ     | H13-0387-5                        |                               |                             |

|                   | DG390AP     | HI1-0390-2                        |                               |                             |

|                   | DG390BP     | HI1-0390-4                        |                               |                             |

|                   | DG390CJ     | H13-0390-5                        |                               |                             |

|                   | DG506AR     | HI1-0506-2                        |                               | HI1-0506A-2                 |

|                   | DG506BR     | HI1-0506-4                        |                               | HI1-0506A-4                 |

|                   | DG506CJ     | H13-0506-5                        |                               | H13-0506A-5                 |

|                   | DG507AR     | HI1-0507-2                        |                               | HI1-0507A-2                 |

|                   | DG507BR     | HI1-0507-4                        |                               | HI1-0507A-4                 |

|                   | DG507CJ     | HI3-0507-5                        |                               | H13-0507A-5                 |

|                   | DG508AP     | HI1-0508-2                        |                               | HI1-0508A-2                 |

|                   | DG508BP     | HI1-0508-4                        |                               | HI1-0508A-4                 |

|                   | DG508CJ     | HI3-0508-5                        |                               | HI3-0508A-5                 |

|                   | DG509AP     | HI1-0509-2                        | · · ·                         | HI1-0509A-2                 |

|                   | DG509BP     | HI1-0509-4                        |                               | HI1-0509A-4                 |

|                   | DG509CJ     | H13-0509-5                        |                               | HI3-0509A-5                 |

|                   | L140        |                                   |                               | HA-2720/25                  |

1-13

| MANU-<br>FACTURER     | PART NUMBER                                                                                                                                                       | HARRIS PIN-FOR-PIN<br>REPLACEMENT                                                                            | HARRIS CLOSEST<br>REPLACEMENT | SUGGESTED FOR<br>NEW DESIGN                                                                                                              |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| SOLITRON              | CM4016A<br>μc4000/4001C/<br>4002C<br>μc4250<br>μc4250c                                                                                                            | LM4250<br>LM4250C                                                                                            | HA-2720<br>HA-2725            | HI-201<br>HA-2605                                                                                                                        |

| SPRAGUE               | ULS/ULN2139<br>ULS/ULN2151<br>ULS/ULN2156<br>ULS/ULN2157<br>ULS/ULN2158<br>ULS/ULN2171<br>ULS/ULN2172<br>ULS/ULN2173<br>ULS/ULN2174<br>ULS/ULN2175<br>ULS/ULN2176 |                                                                                                              |                               | HA-2600/05<br>HA-2600/05<br>HA-2650/55<br>HA-2650/55<br>HA-2650/55<br>HA-2600/05<br>HA-2620/25<br>HA-2600/05<br>HA-2600/05<br>HA-2600/05 |

| TELEDYNE<br>PHILBRICK | 1321<br>1321-01<br>1322<br>1322-01<br>1332<br>1339<br>4551<br>4552<br>4856<br>1430                                                                                | HA2-2625-5<br>HA2-2620-2<br>HA2-2525-5<br>HA2-2520-2<br>HA2-2645-5<br>H11-507A-5<br>H11-506A-5<br>HA1-2425-5 |                               | HA-2625<br>HA-5195                                                                                                                       |

| ТІ                    | TL044<br>TL062<br>TL064<br>TL082<br>TL084<br>MC1558/1458                                                                                                          | HA-5062<br>HA-5064<br>HA-5082<br>HA-5084                                                                     | HA-2650/55                    | HA-4741                                                                                                                                  |

| TRANSITRON            | TOA7709<br>TOA8709                                                                                                                                                |                                                                                                              |                               | HA-2600<br>HA-2605                                                                                                                       |

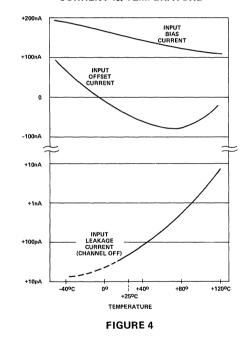

### **High Temperature Electronics**

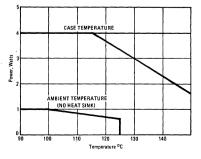

To serve the growing need for electronics that will operate in severe high temperature environments, Harris will offer integrated circuits that have been characterized over elevated temperatures and that have electrical characteristics guaranteed at 200°C.

Typical applications include:

- Well Logging

- Industrial Process Control

- Engine Control and Testing

- High Temperature Data Acquisition Systems

It is the intention of Harris Semiconductor to make available in the high temperature series (identified by the -1 suffix following the device part number) all the basic elements required for the designer to build a data acquisition system that will function to specified limits at 200°C.

The devices to be offered:

- Operational Amplifiers

- Analog Switches

- Analog Multiplexers

- 12 Bit Digital to Analog Converter

- Sample & Hold Amplifiers A/D Converters

All parts offered in the -1 series have had their electrical performance parameters characterized up to 250°C.

Production flow of -1 parts includes screening to MIL-STD-883B, 160 hours burn-in and final electrical test at 200°C.

Devices available Now:

- HA-2420-1

- Sample & Hold Amplifier Operational Amplifier

- HA-2600-1 Operational Amplifier

HA-2620-1 Operational Amplifier

- HI-200-1

- Analog Switch

- HI-201-1

- Analog Switch

Consult factory for price and availability information.

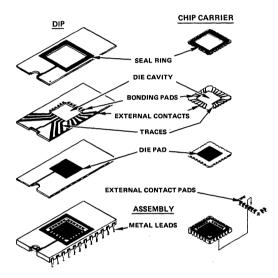

### **Advanced Packaging Techniques**

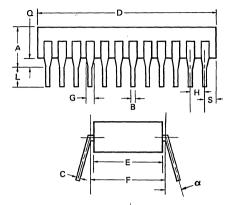

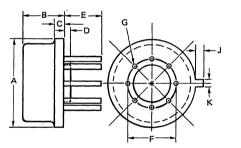

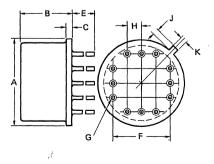

Harris Semiconductor is now offering Leadless Chip Carriers (LCC) as a packaging option on various Analog integrated circuits. An LCC is a square or rectangular package for an Integrated Circuit (IC) that is manufactured in the same manner as a conventional side-braze dual-in-line package (DIP). The LCC is essentially comprised of the cavity and seal ring section of a standard DIP. It offers the user a means of achieving high density system configurations while retaining the reliability benefits of hermetic IC packaging. Figure 1 provides a comparison of the construction of an LCC and a conventional side-braze DIP.

The LCC's two principle advantages over conventional side braze DIPs are packaging density and electrical performance. Packaging density is the number one advantage to an LCC over a side braze DIP. The size of a DIP is governed primarily by the number of leads required and not by the size of the IC. As pin count increases, more and more of the DIP package is used only to provide an electrical trace path to the external leads. The size of an LCC is dependant on the size of the die not on the number of leads. As pin count increases, overall size increases but at a much slower rate. Table 1 provides a comparison between the areas of 18, 28, and 48 lead LCCs to 18, 28, and 48 lead side braze DIPs. The chart indicates a 270% improvement in packaging area for the 18 lead LCC, and 542% improvement for the 48 lead LCC. Obviously, sizable savings in circuit board area can be achieved with this packaging option. The second major advantage of the LCC is in electrical performance. The package size and geometry also dictates trace length and uniformity. Figure 2 provides a comparison between the trace lengths for various LCCs and side braze DIPs. As pin

count goes up, trace lengths get longer, adding resistance and capacitance unequally around the package. As ICs get faster and more complex, these factors start to become a limiting factor on performance. LCCs minimize this effect by maintaining, as close as possible, uniform trace length so that the package is significantly smaller determinant of system performance.

The LCC also offers environmental advantages over "chip-and-wire" manufacturing techniques used in high density hybrid circuits. An IC can be fully tested, burned-in and processed to MIL-STD-883B in an LCC, thereby guaranteeing its performance.

FIGURE 1. Exploded view of Chip Carrier and DIP.

The IC is further protected by small hermetic package in which internal water vapor content can be carefully controlled during production.

In summary, Harris Semiconductor Leadless Chip Carriers use a proven technology to provide a reliable high density, high performance packaging option for today's systems.

A list of products available in LCC form is provided in the Packaging Section on page 11-6. Consult the factory or your Harris sales representative for pricing and availability.

| LEAD<br>COUNT | LONGEST TRACE DIP<br>LONGEST TRACE CC | LONGES<br>SHORTES | T TRACE |

|---------------|---------------------------------------|-------------------|---------|

|               | _                                     | <u>CC</u>         | DIP     |

| 18            | 2:1                                   | 1.5:1             | 6:1     |

| 24            | 4:1                                   | 1.5:1             | 3:1     |

| 40            | 5:1                                   | 1.5:1             | 6:1     |

| 54            | 6:1                                   | 1.5:1             | 7:1     |

FIGURE 2. Electrical Performance (Resistance and Speed)

| Т | Α | В | L | Е | L |  |

|---|---|---|---|---|---|--|

|   |   |   |   |   |   |  |

|         | LCC  | DIP  | DIP AREA<br>LCC AREA |

|---------|------|------|----------------------|

| 18 Lead | 0.10 | 0.22 | 270                  |

| 28 Lead | 0.20 | 0.84 | 420                  |

| 48 Lead | 0.31 | 1.68 | 542                  |

(All units in square inches)

1

1-16

5

### Operational Amplifiers and Comparators

#

|                         |                                                                                               | PAGE           |

|-------------------------|-----------------------------------------------------------------------------------------------|----------------|

| Linear Products – Para  | ametric Classification Reference                                                              | 2-1A           |

| Operational Amplifier   |                                                                                               | 2-2            |

| HA-1608                 | +10V Adjustable Voltage Reference                                                             | 2-3            |

| HA-2400/04/05           | PRAM Four Channel Programmable Amplifier                                                      | 2-6            |

| HA-2500/02/05           | Precision High Slew Rate Operational Amplifiers                                               | 2-10           |

| HA-2510/12/15           | High Slew Rate Operational Amplifiers                                                         | 2-14           |

| HA-2520/22/25           | Uncompensated High Slew Rate Operational Amplifiers                                           | 2-18           |

| HA-2530/2535            | High Slew Rate, Wideband Inverting Amplifier                                                  | 2-22           |

| HA-2539                 | Very High Slew Rate Wideband Operational Amplifiers                                           | 2-26           |

| HA-2540                 | Wideband, Fast Settling Operational Amplifiers                                                | 2-29           |

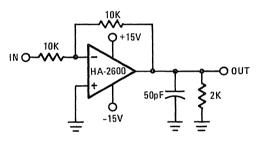

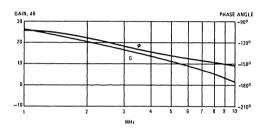

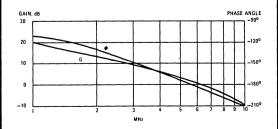

| HA-2600/02/05           | Wideband, High Impedance Operational Amplifiers                                               | 2-32           |

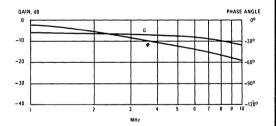

| HA-2620/22/25           | Very Wide Band Uncompensated Operational Amplifiers                                           | 2-36           |

| HA-2630/2635            | High Performance Current Booster                                                              | 2-40           |

| HA-2640/2645            | High Voltage Operational Amplifier                                                            | 2-44           |

| HA-2650/2655            | Dual High Performance Operational Amplifier                                                   | 2-48           |

| HA-2720/25              | Wide Range Programmable Operational Amplifier                                                 | 2-52           |

| HA-2730/35              | Wide Range Dual Programmable Operational Amplifiers                                           | 2-58           |

| HA-2740                 | Quad Programmable Operational Amplifier                                                       | 2-64           |

| HA-4156                 | High Performance Quad Operational Amplifier                                                   | 2-67           |

| HA-4600/02/05           | High Performance Quad Operational Amplifier                                                   | 2-71           |

| HA-4620/22/25           | Wideband, High Performance Quad Operational Amplifier                                         | 2-78           |

| HA-4741                 | Quad Operational Amplifier                                                                    | 2-84           |

| HA-4900/02/05           | Precision Quad Comparator                                                                     | 2-88           |

| HA-5062                 | Low Power JFET Input Dual Operational Amplifiers                                              | 2-95           |

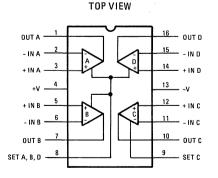

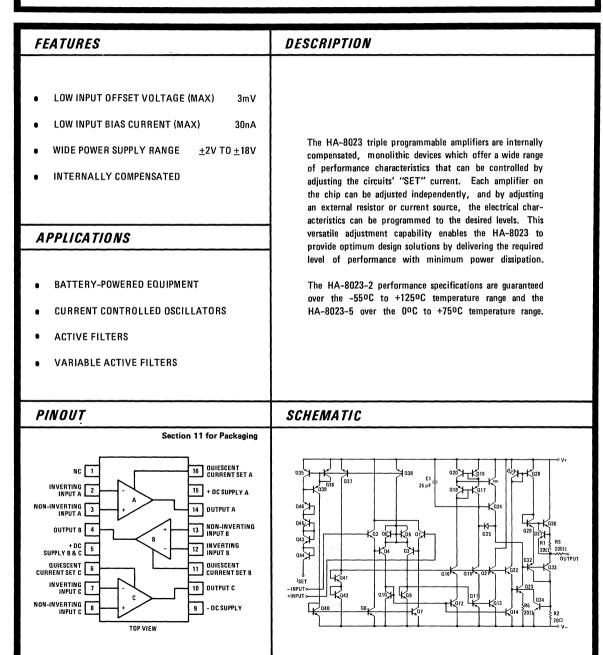

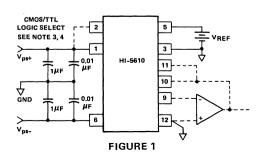

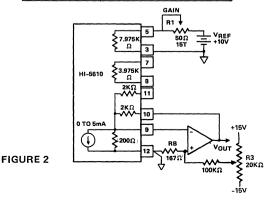

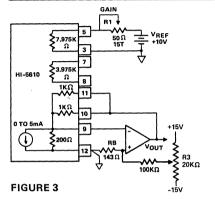

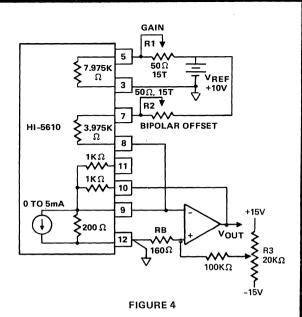

| HA-5064                 | Low Power, JFET Input Quad Operational Amplifiers                                             | 2-97           |