Western Microtechnology 10040 Bubb Road Cupertino, CA 95014 Phone (408) 725-1660 TWX 910-338-0013

# CMOS DIGITAL DATA BOOK

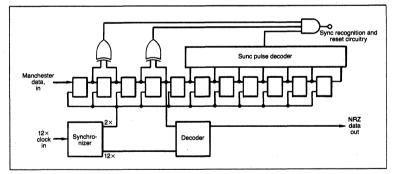

Part of the Harris Spectrum of Integrated Circuits

# **1984 Harris CMOS** Digital Data Book

Harris Semiconductor CMOS Digital Products Division's products represent state-of-the-art in density and high performance. The HARRIS expertise in CMOS design and processing offers the user the most reliable product available in a wide choice of formats, options, and package types. With continuing research and development and the introduction of new products, Harris will provide its customers with the most advanced CMOS technology.

This book describes Harris Semiconductor CMOS Digital Products Division's complete line of digital products and includes a complete set of product specifications and data sheets. Also included are sections on reliaiblity, programming, and packaging.

Please fill out the registration card at the back of this book and return it to us so we may keep you informed of our latest new product developments over the next year.

If you need more information on these and other HARRIS products, please contact the nearest HARRIS sales office listed in the back of this data book.

Harris Semiconductor's products are sold by description only. HARRIS reserves the right to make changes in circuit design, specifications and other information at any time without prior notice. Accordingly, the reader is cautioned to verify that data sheets and other information in this publication are current before placing orders. Information contained in application notes is intended soley for general guidance; use of the information for user's specific application is at user's risk. Reference to products of other manufacturers are solely for convenience of comparison and do not imply total equivalency of design, performance, or otherwise.

#### Copyright C Harris Corporation 1984

(All rights reserved)

Printed in USA

# 1984 Digital Data Book

| 1  | General Information                       |

|----|-------------------------------------------|

| 2  | CMOS Memory                               |

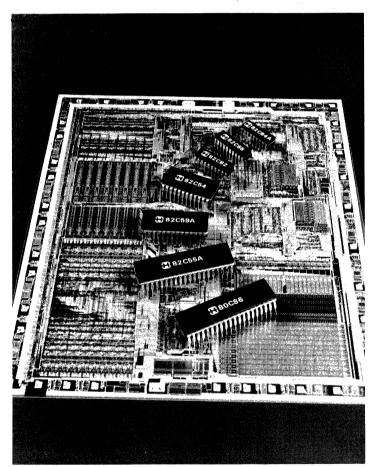

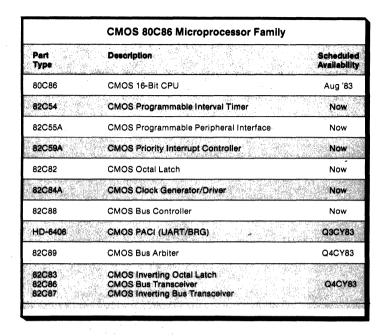

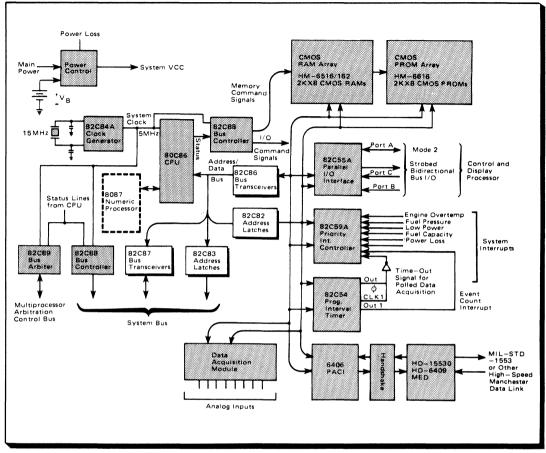

| 3  | CMOS 80C86 Family                         |

| 4  | CMOS 12-Bit Microprocessors & Peripherals |

| 5  | <b>CMOS</b> Data Communication            |

| 6  | Harris Reliability and Quality            |

| 7  | Hi-Reliability & Military Products        |

| 8  | Article Reprints                          |

| 9  | Custom – Semi-Custom CMOS IC Information  |

| 10 | Ordering and Packaging                    |

| 11 | DICE Information                          |

| 12 | Appendices                                |

CMOS

# Table of Contents

|            |                                                                                                                                                                                                                                                                                                                                                       | PAGE                                                                                 |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| SECTION 1  | GENERAL INFORMATION                                                                                                                                                                                                                                                                                                                                   | . *                                                                                  |

|            | Sector Capabilities<br>CMOS Alpha-Numeric Index<br>CMOS Devices by Families<br>Classification of Literature<br>Symbols and Abbrevations                                                                                                                                                                                                               | 1-2<br>1-3<br>1-4<br>1-6<br>1-6                                                      |

| SECTION 2  | CMOS MEMORY                                                                                                                                                                                                                                                                                                                                           |                                                                                      |

|            | CMOS Memory Product Index<br>Low Voltage Data Retention<br>Industry CMOS RAM Cross-Reference<br>1K CMOS RAM Data Sheets<br>4K CMOS RAM Data Sheets<br>16K CMOS RAM Data Sheets<br>CMOS RAM Module Data Sheets<br>CMOS PROM Data Sheets<br>Preview of CMOS PROM Products<br>Programming Format for Harris PROMs<br>Preview of Future CMOS HPL Circuits | 2-2<br>2-3<br>2-4<br>2-5<br>2-29<br>2-51<br>2-85<br>2-113<br>2-126<br>2-127<br>2-130 |

| SECTION 3  | CMOS 80C86 FAMILY                                                                                                                                                                                                                                                                                                                                     |                                                                                      |

|            | CMOS 80C86 Family Product Index<br>CMOS 80C86 Family Cross Reference<br>Harris 80C86 Family Data Sheets<br>Preview of Future Harris 80C86 Family Products                                                                                                                                                                                             | 3-2<br>3-3<br>3-4<br>3-96                                                            |

| SECTION 4  | CMOS 12 BIT MICROPROCESSORS AND PERIPHERALS                                                                                                                                                                                                                                                                                                           |                                                                                      |

|            | CMOS 12 Bit Microprocessor and Peripheral Product Index<br>CMOS Microprocessor Data Sheets<br>CMOS Peripheral Data Sheets                                                                                                                                                                                                                             | 4-2<br>4-3<br>4-59                                                                   |

| SECTION 5  | CMOS DATA COMMUNICATIONS                                                                                                                                                                                                                                                                                                                              |                                                                                      |

|            | CMOS Data Communications Product Index<br>CMOS Data Communications Data Sheets                                                                                                                                                                                                                                                                        | 5-2<br>5-3                                                                           |

| SECTION 6  | HARRIS RELIABILITY AND QUALITY                                                                                                                                                                                                                                                                                                                        |                                                                                      |

|            | Harris Reliability and Quality Table of Contents                                                                                                                                                                                                                                                                                                      | 6-1                                                                                  |

| SECTION 7  | HARRIS HI-REL AND MILITARY PRODUCTS                                                                                                                                                                                                                                                                                                                   |                                                                                      |

| SECTION 8  | Harris Hi-Rel and Military Products Table of Contents ARTICLE REPRINTS                                                                                                                                                                                                                                                                                | 7-1                                                                                  |

|            | Article Reprints Table of Contents                                                                                                                                                                                                                                                                                                                    | 8-2                                                                                  |

| SECTION 9  | CUSTOM – SEMI-CUSTOM CMOS IC INFORMATION                                                                                                                                                                                                                                                                                                              |                                                                                      |

|            | Custom – Semi-Custom CMOS IC Information Table of Contents                                                                                                                                                                                                                                                                                            | 9-1                                                                                  |

| SECTION 10 | ORDERING AND PACKAGING                                                                                                                                                                                                                                                                                                                                |                                                                                      |

|            | Ordering and Packaging Information                                                                                                                                                                                                                                                                                                                    | 10-1                                                                                 |

| SECTION 11 | DICE INFORMATION                                                                                                                                                                                                                                                                                                                                      |                                                                                      |

|            | Dice Information                                                                                                                                                                                                                                                                                                                                      | 11-1                                                                                 |

| SECTION 12 | APPENDICES                                                                                                                                                                                                                                                                                                                                            | 10.5                                                                                 |

|            | Sector Alpha-Numeric Product Index<br>Harris Sales Locations                                                                                                                                                                                                                                                                                          | 12-3<br>12-8                                                                         |

# CMOS

# General Information

| Sector Capabilities          | 1-2 |

|------------------------------|-----|

| CMOS Alpha-Numeric Index     | 1-3 |

| CMOS Devices by Families     | 1-4 |

| Classification of Literature | 1-6 |

| Symbols and Abbreviations    | 1-6 |

## Harris Semiconductor Sector Capabilities

Harris Semiconductor is one of the five management groups of Harris Corporation, a producer of high-technology communication and information processing systems sold in over 160 countries. Five main operations of Harris Semiconductor produce standard and custom semiconductor devices. These operations are:

#### ANALOG PRODUCTS DIVISION

Harris is a major force in analog integrated circuitry, offering a broad line of products including: analog-to-digital converters, digital-toanalog converters, switches, multiplexers, voltage references, operational amplifiers, telecommunications and speech processing products.

#### **BIPOLAR DIGITAL PRODUCTS DIVISION**

Harris introduced the industry's first bipolar programmable read only memory in 1970 and has continued as a leader in the field of bipolar PROMs. Harris offers a complete spectrum of bipolar PROMs from 256 bits to 64K bits. Also, offered is a new family of programmable logic products featuring on-chip testability.

#### CMOS DIGITAL PRODUCTS DIVISION

Harris is a pioneer in developing and producing digital CMOS products including: CMOS RAMs, CMOS PROMs, CMOS microprocessors, CMOS peripherals, CMOS data communications products, and this year introducing a full line of 80C86 microprocessors and peripherals.

#### CUSTOM INTEGRATED CIRCUITS DIVISION

Harris designs, develops and manufactures custom analog, digital bipolar, radiation-hardened, and CMOS circuits for specialized military and commercial applications.

#### MICROWAVE SEMICONDUCTOR, INC.

Harris Microwave Semiconductor, Inc. develops and manufactures gallium arsenide transistors, integrated circuits and microwave amplifiers.

# **CMOS** Alpha-Numeric Index

| PRODUCT             | DESCRIPTION                                           | PAGE<br>NO.  |

|---------------------|-------------------------------------------------------|--------------|

| HD-15530            | Manchester Encoder-Decoder                            | 5-3          |

| HD-15531            | Manchester Encoder-Decoder                            | 5-10         |

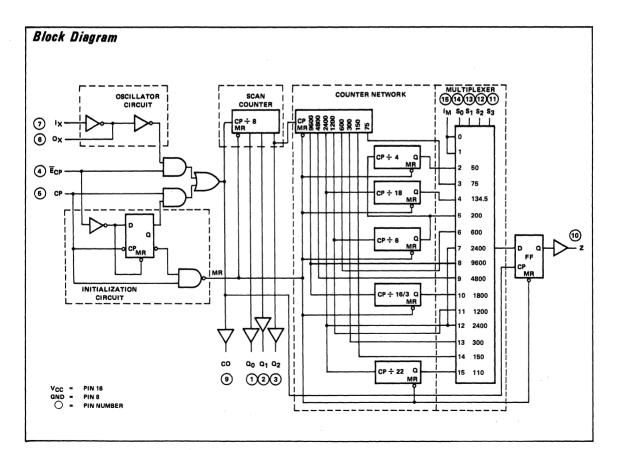

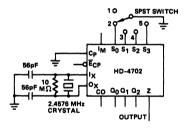

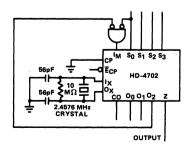

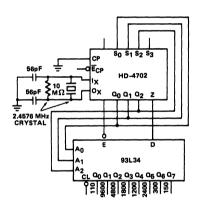

| HD-4702             | Programmable Bit Rate Generator                       | 5-56         |

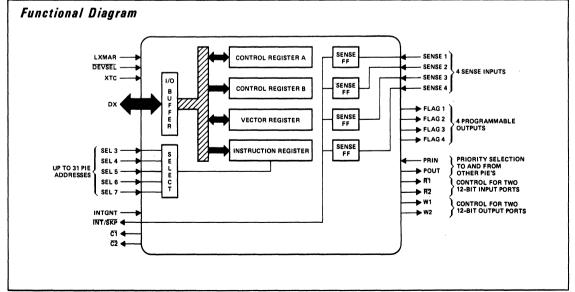

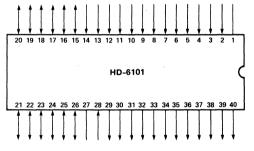

| HD-6101             | Parallel Interface Element                            | 4-51         |

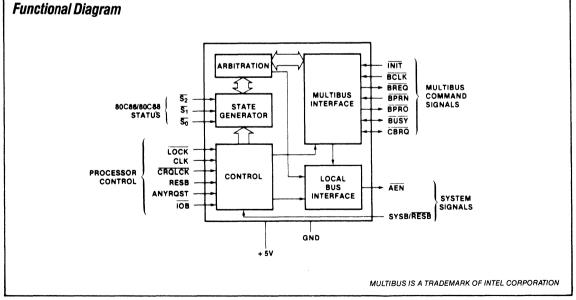

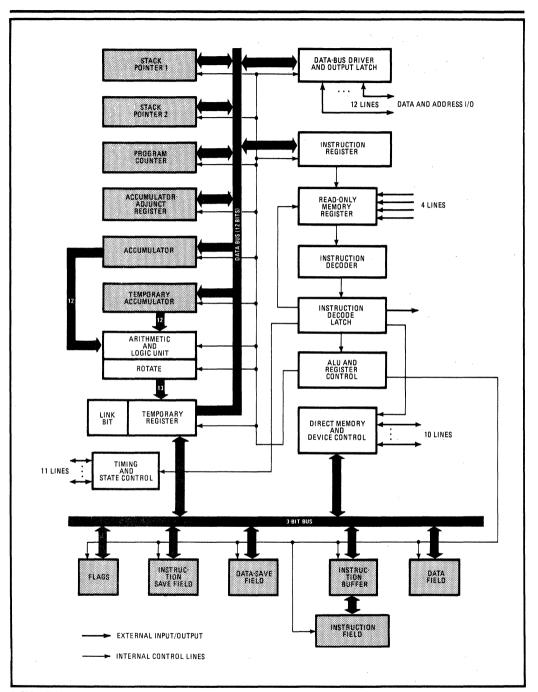

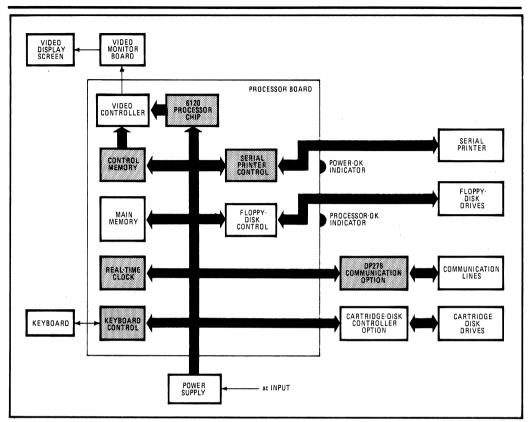

| HD6120              | 12 Bit High Performance Microprocessor                | 4–3          |

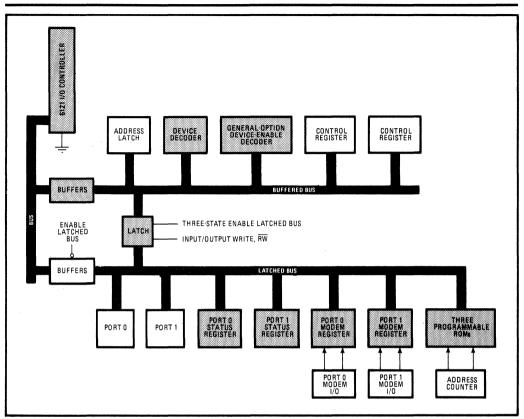

| HD-6121             | I/O Controller                                        | 4-22         |

| HD-6402             | LSI Universal Asynchronous Receiver Transmitter       | 5-51         |

| HD-6406             | Programmable Asynchronous Communication Interface     | 5-39         |

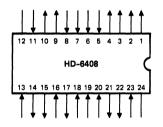

| HD-6408             | Asynchronous Manchester Adapter                       | 5-25         |

| HD-6409<br>HD-6431  | Manchester Encoder-Decoder<br>Hex Latching Bus Driver | 5-30<br>4-59 |

| HD-6432             | Hex Bi-directional Bus Driver                         | 4-59<br>4-62 |

| HD-6433             | Quad Bus Separator/Driver                             | 4-65         |

| HD-6434             | Octal Resettable Latch                                | 4-68         |

| HD-6436             | Octal Bus Buffer/Driver                               | 4-71         |

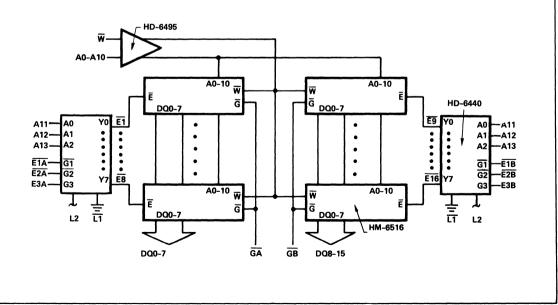

| HD-6440             | Latch Decoder/Driver                                  | 4-74         |

| HD-6495             | Hex Bus Driver                                        | 4-78         |

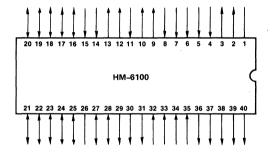

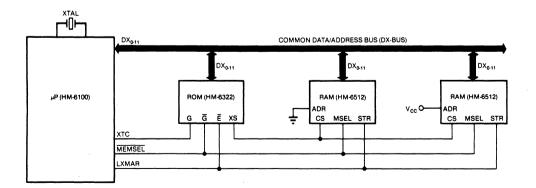

| HM-6100             | 12 Bit Static Microprocessor                          | 4-30         |

| HM-6504             | 4K X 1 Synchronous RAM                                | 2-29         |

| HM-6508             | 1K X 1 Synchronous RAM                                | 2-5          |

| HM-6514             | 1K X 4 Synchronous RAM                                | 2-40         |

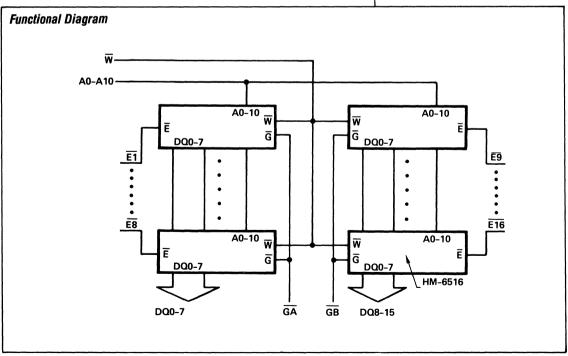

| HM-6516             | 2K X 8 Synchronous RAM                                | 2-51         |

| HM-65162            | 2K X 8 Asynchronous RAM                               | 2-57         |

| HM-65172            | 2K X 8 Asynchronous RAM                               | 2-70         |

| HM-6518             | 1K X 1 Synchronous RAM                                | 2-11         |

| HM-65262<br>HM-6551 | 16K X 1 Asynchronous RAM<br>256 X 4 Synchronous RAM   | 2-83         |

| HM-6561             | 256 X 4 Synchronous RAM<br>256 X 4 Synchronous RAM    | 2-17         |

| HM-6564             | 64K Synchronous RAM Module                            | 2-23<br>2-85 |

| HM-6616             | 2K X 8 Fuse Link PROM                                 | 2-05         |

| HM-6641             | 512 X 8 PROM                                          | 2-118        |

| HM-6664             | 8K X 8 Fuse Link PROM                                 | 2-126        |

| HM-92560            | 256K Synchronous RAM Module                           | 2-96         |

| HM-92570            | 256K Synchronous RAM Module                           | 2-104        |

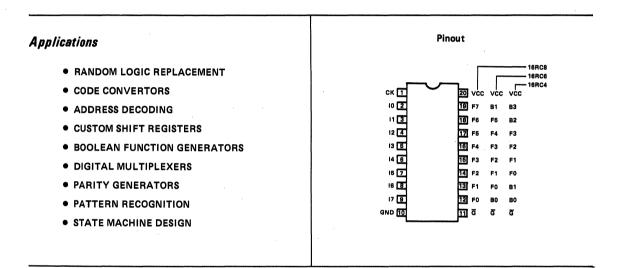

| HPL- 16LC8          | Programmable Logic                                    | 2-130        |

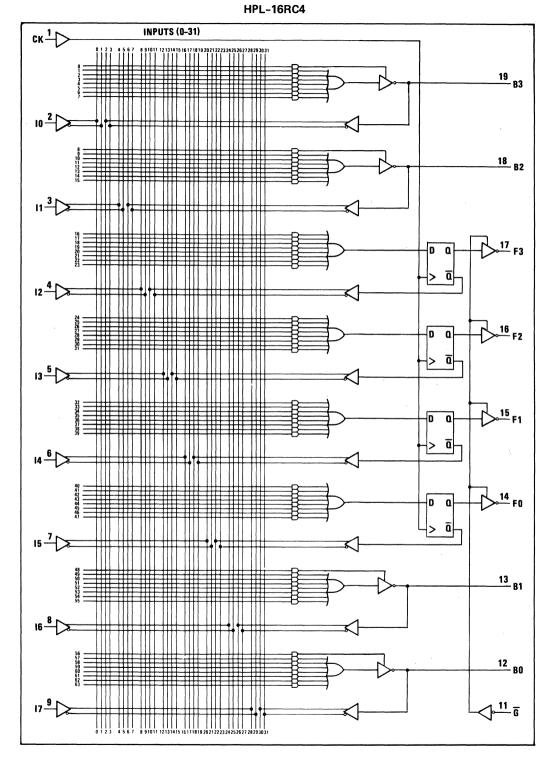

| HPL-16RC4           | Programmable Logic                                    | 2-132        |

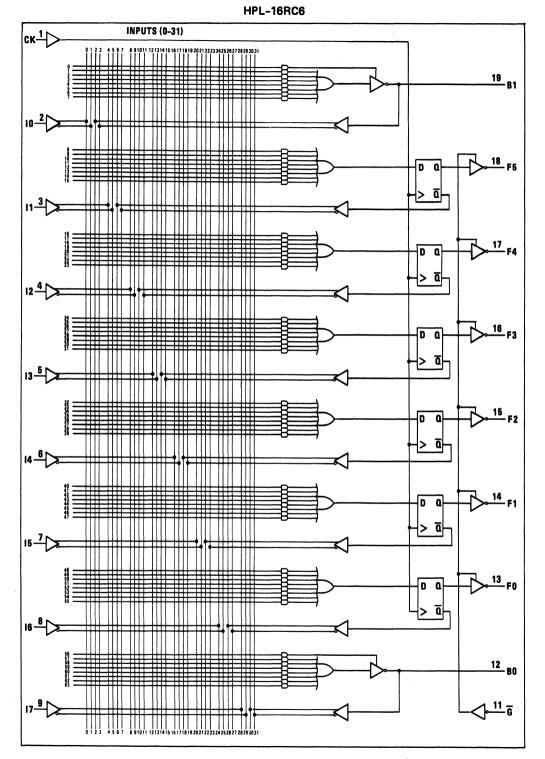

| HPL-16RC6           | Programmable Logic                                    | 2-132        |

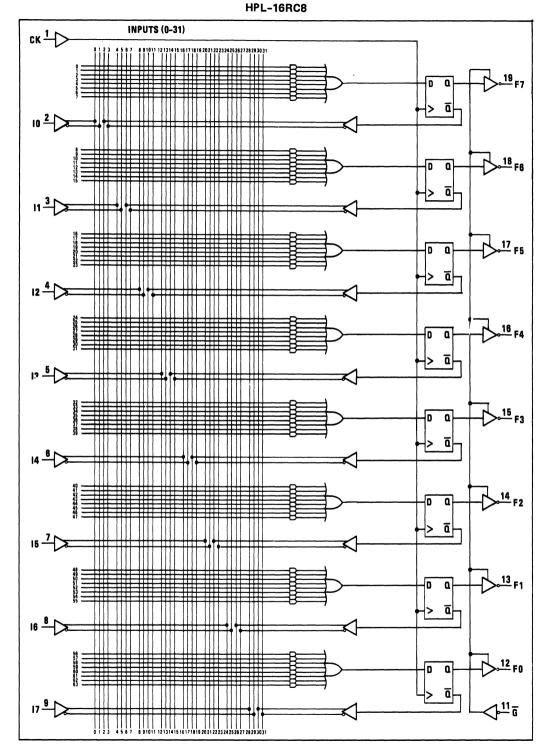

| HPL-16RC8           | Programmable Logic                                    | 2-132        |

| 80C86               | 16 Bit Microprocessor                                 | 3-4          |

| 80C88               | 8 Bit Microprocessor                                  | 3-96         |

| 82C37A              | High Performance Programmable DMA Controller          | 3-97         |

| 82C52               | Full Duplex UART                                      | 3-27         |

| 82C54               | Programmable Interval Timer                           | 3-28         |

| 82C55A              | Programmable Peripheral Interface                     | 3–43<br>3–62 |

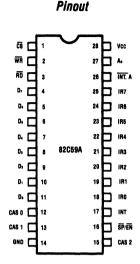

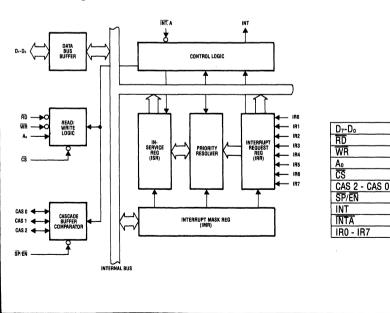

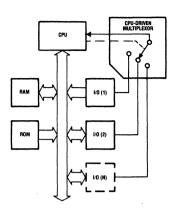

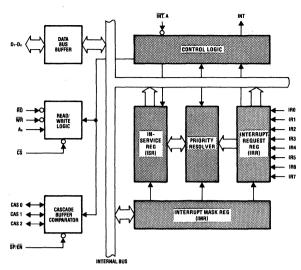

| 82C59A<br>82C82     | Priority Interrupt Controller<br>Octal Latch          | 3-62         |

| 82C83               | Octal Latching Inverting Bus Driver                   | 3-98         |

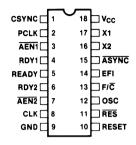

| 82C84A              | Clock Generator/Driver                                | 3-82         |

| 82C84B              | Clock Generator Driver                                | 3-99         |

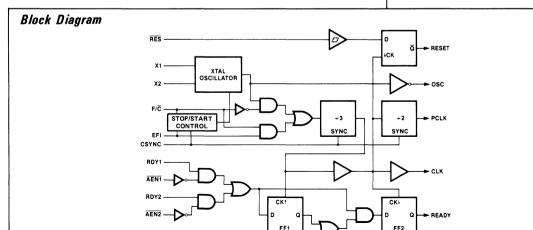

| 82C86               | Octal Bus Transceiver                                 | 3-100        |

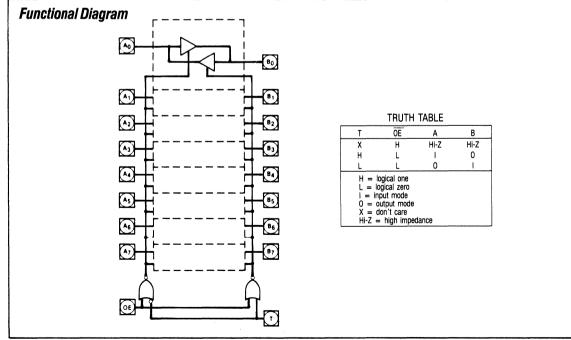

| 82C87               | Octal Bus Transceiver                                 | 3-101        |

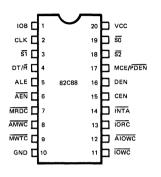

| 82C88               | Bus Controller                                        | 3-89         |

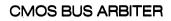

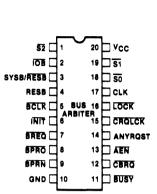

| 82C89               | Bus Arbiter                                           | 3-102        |

|                     |                                                       |              |

GENERAL INFORMATION

# **CMOS** Devices by Families

| CMOS Mid                                                                        | croprocessor and Support Circuits                                                                                                                                                                                                                         | PAGE                                                            |  |

|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--|

| 8/16 BIT MICROPROCESSORS                                                        |                                                                                                                                                                                                                                                           |                                                                 |  |

| 80C86<br>80C88                                                                  | 16 Bit CMOS Microprocessor<br>8 Bit CMOS Microprocessor                                                                                                                                                                                                   | 3–4<br>3–96                                                     |  |

| 80C86/88 PEF                                                                    | RIPHERAL CIRCUITS                                                                                                                                                                                                                                         |                                                                 |  |

| 82C37A<br>82C52<br>82C54<br>82C55A<br>82C55A<br>82C59A                          | CMOS DMA Controller<br>CMOS Serial Communication Interface<br>CMOS Programmable Interval Timer<br>CMOS Programmable Peripheral Interface<br>CMOS Priority Interrupt Controller                                                                            | 3-97<br>3-27<br>3-28<br>3-43<br>3-62                            |  |

| 80C86/88 BU                                                                     | S SUPPORT CIRCUITS                                                                                                                                                                                                                                        |                                                                 |  |

| 82C82<br>82C83<br>82C84A<br>82C84B<br>82C86<br>82C86<br>82C87<br>82C88<br>82C89 | CMOS Octal Latching Bus Driver<br>CMOS Octal Latching Inverting Bus Driver<br>CMOS Clock Generator Driver<br>CMOS Clock Generator Driver<br>CMOS Octal Bus Transceiver<br>CMOS Octal Inverting Bus Transceiver<br>CMOS Bus Controller<br>CMOS Bus Arbiter | 3-77<br>3-98<br>3-82<br>3-99<br>3-100<br>3-101<br>3-89<br>3-102 |  |

| 12 BIT MICRO                                                                    | DPROCESSORS                                                                                                                                                                                                                                               |                                                                 |  |

| HM-6100<br>HD-6120                                                              | CMOS 12 Bit Microprocessor<br>CMOS High Performance 12 Bit Microprocessor                                                                                                                                                                                 | 4-30<br>4-3                                                     |  |

| 12 BIT PERIP                                                                    | HERAL CONTROLLERS                                                                                                                                                                                                                                         |                                                                 |  |

| HD-6101<br>HD-6121                                                              | CMOS Parallel Interface Element (PIE)<br>CMOS I/O Controller (IOC)                                                                                                                                                                                        | 4–51<br>4–22                                                    |  |

| BUS SUPPOR                                                                      | T CIRCUITS                                                                                                                                                                                                                                                |                                                                 |  |

| HD-6431<br>HD-6432<br>HD-6433<br>HD-6434<br>HD-6436<br>HD-6440<br>HD-6495       | CMOS Hex Latching Bus Driver<br>CMOS Hex Bi-directional Bus Driver<br>CMOS Quad Bus Separator/Driver<br>CMOS Octal Bus Driver W/Reset<br>CMOS Octal Bus Buffer/Driver<br>CMOS Latched 3 to 8 Line Decoder/Driver<br>CMOS Hex Bus Driver                   | 4-59<br>4-62<br>4-65<br>4-68<br>4-71<br>4-74<br>4-78            |  |

| SERIAL COM                                                                      | MUNICATION CIRCUITS                                                                                                                                                                                                                                       |                                                                 |  |

| HD-4702<br>HD-6402<br>HD-6406<br>HD-6408<br>HD-6409<br>HD-15530<br>HD-15531     | CMOS Bit Rate Generator<br>CMOS UART<br>CMOS Prog. Async. Communication Interface<br>CMOS Async. Serial Manchester Adapter (ASMA)<br>CMOS Manchester Encoder-Decoder<br>CMOS Manchester Encoder-Decoder<br>CMOS Manchester Encoder-Decoder                | 5-56<br>5-51<br>5-39<br>5-25<br>5-30<br>5-3<br>5-10             |  |

# **CMOS Devices by Families**

(continued)

| CMOS Static RAMS                                              |                                                                                      | PAGE                                |

|---------------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------------|

| 1K - SYNCHRO                                                  | NOUS                                                                                 |                                     |

| HM-6508<br>HM-6518<br>HM-6551<br>HM-6561                      | 1K X 1<br>1K X 1<br>256 X 4<br>256 X 4                                               | 2-5<br>2-11<br>2-17<br>2-25         |

| 4K - SYNCHRO                                                  | DNOUS                                                                                |                                     |

| HM-6504<br>HM-6514                                            | 4K X 1<br>1K X 4                                                                     | 2-29<br>2-40                        |

| 16K-SYNCHRO                                                   | NOUS                                                                                 |                                     |

| HM-6516                                                       | 2K X 8                                                                               | 2-51                                |

| 16K- ASYNCHI                                                  | RONOUS                                                                               |                                     |

| HM-65162<br>HM-65172<br>HM-65262                              | 2K X 8<br>2K X 8<br>16K X 1                                                          | 2-57<br>2-70<br>2-83                |

| CMOS RAM MC                                                   | DULES                                                                                |                                     |

| HM-6564<br>HM-92560<br>HM-92570                               | 64K<br>256K<br>Buffered 256K                                                         | 2-85<br>2-96<br>2-104               |

| CMOS RADIAT                                                   | ION HARDENED RAMS                                                                    |                                     |

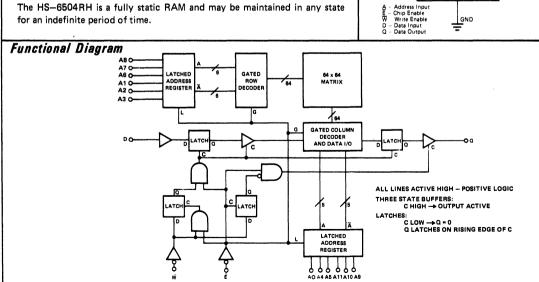

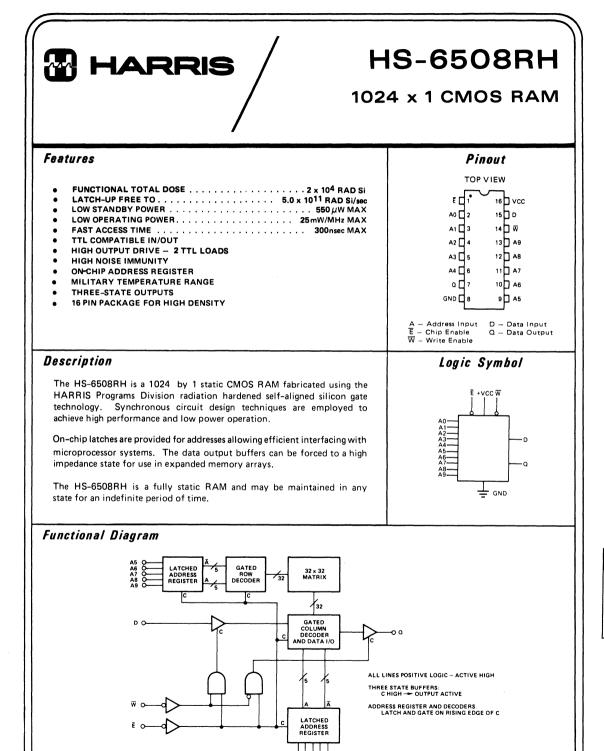

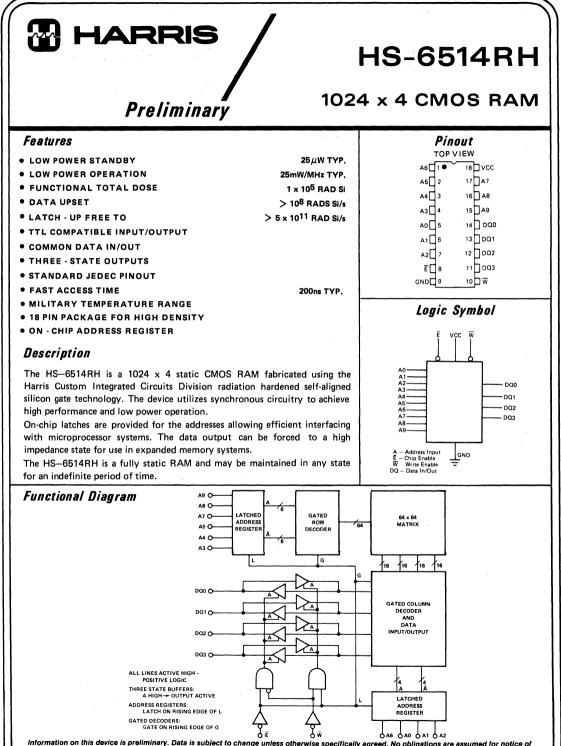

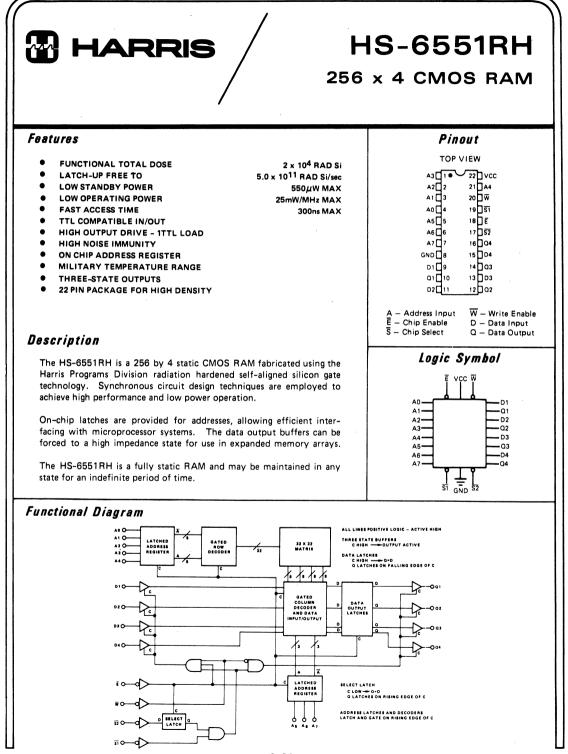

| HS-6504RH<br>HS-6508RH<br>HS-6514RH<br>HS-6551RH<br>HS-6564RH | 4K X 1<br>1K X 1<br>1K X 4<br>256 X 4<br>16K X 4 or 8K X 8                           | 9-18<br>9-19<br>9-20<br>9-21<br>9-2 |

| CMOS Fuse Link PROMS                                          |                                                                                      |                                     |

| HM-6641<br>HM-6616<br>HM-6664                                 | 512 X 8<br>2K X 8<br>8K X 8                                                          | 2-113<br>2-118<br>2-126             |

| CMOS Programmable Logic                                       |                                                                                      |                                     |

| HPL-16LC8<br>HPL-16RC4<br>HPL-16RC6<br>HPL-16RC8              | Programmable Logic<br>Programmable Logic<br>Programmable Logic<br>Programmable Logic | 2-130<br>2-132<br>2-132<br>2-132    |

## **Classification of Literature**

| CLASSIFICATION                               | PRODUCT STAGE                 | DISCLAIMERS                                                                                                                                       |

|----------------------------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Preview</b><br>DATA<br>SHEET              | Formative or<br>Design        | This document contains the design specifications<br>for product under development. Specifications<br>may be changed in any manner without notice. |

| <i>Advance<br/>Information</i><br>DATA SHEET | Sampling or<br>Pre-Production | This is advanced information, and specifications are subject to change without notice.                                                            |

| <b>Preliminary</b><br>DATA SHEET             | First Production              | Supplementary data may be published at a later date.                                                                                              |

|                                              |                               | Harris reserves the right to make changes at any-<br>time without notice, in order to improve design<br>and supply the best product possible.     |

## Symbols & Abbreviations

This data book utilizes a new set of specification nomenclature. This new format is an IEEE and JEDEC supported standard for semiconductor memories. It is intended to clarify the symbols, abbreviations and definitions, and to make all memory data shests consistent. We believe that, once acclimated, you will find this standardized format easy to read and use.

#### ELECTRICAL PARAMETER ABBREVIATIONS

All abbreviations use upper case letters with no subscripts. The initial symbol is one of these four characters:

- V (Voltage)

- I (Current)

- P (Power) C (Capacitance)

The second letter specifies input (I) or output (O), and the third letter indicates the high (H), low (L) or off (Z) state of the pin during measurements. Examples:

VIL – Input Low Voltage IOZ – Output Leakage Current

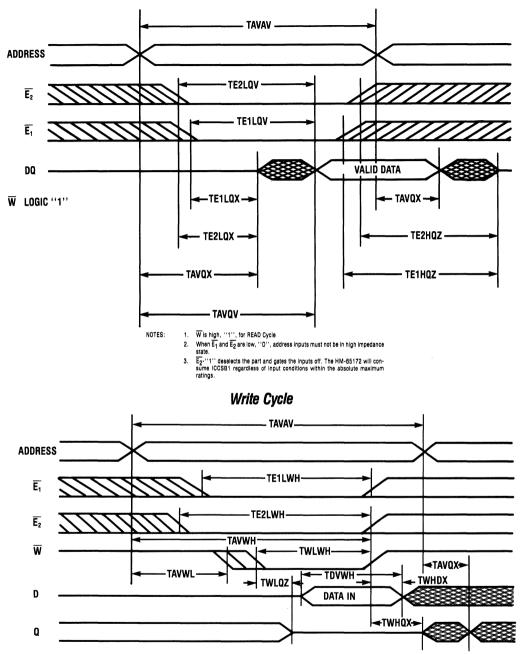

#### TIMING PARAMETER ABBREVIATIONS

All timing abbreviations use upper case characters with no subscripts. The initial character is always T and is followed by four descriptors. These characters specify two signal points arranged in a "from-to" sequence that define a timing interval. The two descriptors for each signal point specify the signal name and the signal transitions. Thus the format is:

| T X X X X<br>Signal name from which interval is defined<br>Transition direction for first signal<br>Signal name to which interval is defined<br>Transition direction for second signal |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal Definitions:                                                                                                                                                                    |

| A = Address                                                                                                                                                                            |

| D = Data In                                                                                                                                                                            |

| Q = Data Out                                                                                                                                                                           |

| W = Write Enable                                                                                                                                                                       |

| E = Chip Enable                                                                                                                                                                        |

| S = Chip Select                                                                                                                                                                        |

| EXAMPLE:        |                |   |

|-----------------|----------------|---|

| CHIP            | Ē              |   |

|                 | TWLEH          | _ |

| WRITE<br>ENABLE | <u>AIIIII.</u> | 7 |

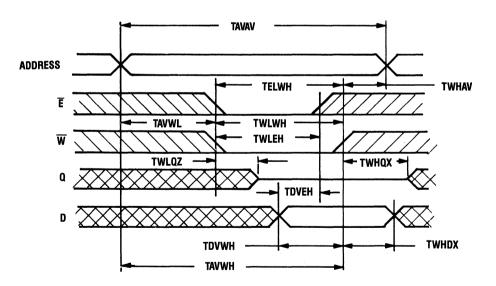

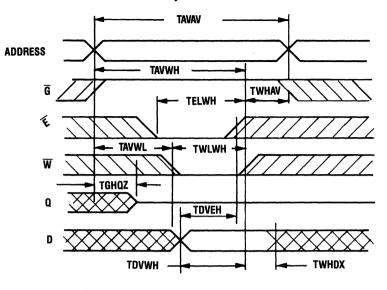

The example shows Write pulse setup time defined as TWLEH-Time from Write enable Low to chip Enable High.

#### TIMING LIMITS

The table of timing values shows either a minimum or a maximum limit for each parameter. Input requirements are specified from the external system point of view. Thus, address set-up time is shown as a minimum since the system must supply at least that much time (even though most devices do not require it). On the other hand, responses from the memory are specified from the device point of view. Thus, the access time is shown as a maximum since the device never provides data later than that time.

#### WAVEFORMS

| WAVEFORM<br>SYMBOL | INPUT                                  | OUTPUT                     |

|--------------------|----------------------------------------|----------------------------|

|                    | MUST BE<br>VALID                       | WILL BE<br>VALID           |

| M                  | CHANGE<br>FROM H TO L                  | WILL CHANGE<br>FROM H TO L |

| Π                  | CHANGE<br>FROM L TO H                  | WILL CHANGE<br>FROM L TO H |

| ***                | DON'T CARE:<br>ANY CHANGE<br>PERMITTED | CHANGING:<br>STATE UNKNOWN |

| $\rightarrow$      |                                        | HIGH                       |

Transition Definitions:

H = Transition to High

G = Output Enable

L = Transition to Low

- V = Transition to Valid X = Transition to Invalid or Don't Care

- Z = Transition to Off (High Impedance)

# **CMOS Memory**

| Product Index                        | 2-2 |

|--------------------------------------|-----|

| Low Voltage Data Retention           | 2-3 |

| Industry CMOS RAM<br>Cross-Reference | 2-4 |

| Product Information                  | 2-5 |

$\mathbb{Z}$

# CMOS Memory Product Index

|                           | 1 · · · · · · · · · · · · · · · · · · ·          | ,           |

|---------------------------|--------------------------------------------------|-------------|

|                           |                                                  | PAGE        |

| 1K CMOS RAM DA<br>HM-6508 |                                                  |             |

| HM-6508                   | 1K x 1 Synchronous RAM<br>1K x 1 Synchronous RAM | 2-5<br>2-11 |

| HM-6551                   | 256 x 4 Synchronous RAM                          | 2-17        |

| HM-6561                   | 256 x 4 Synchronous RAM                          | 2-17        |

|                           |                                                  | 2 20        |

| 4K CMOS RAM DA            |                                                  |             |

| HM-6504                   | 4K x 1 Synchronous RAM                           | 2-29        |

| HM-6514                   | 1K x 4 Synchronous RAM                           | 2-40        |

| 16K CMOS RAM D            | ATA SHEETS                                       |             |

| HM-6516                   | 2K x 8 Synchronous RAM                           | 2-51        |

| HM-65162                  | 2K x 8 Asynchronous RAM                          | 2-57        |

| HM-65172                  | 2K x 8 Asynchronous RAM                          | 2-70        |

|                           | JRE CMOS RAM PRODUCTS                            |             |

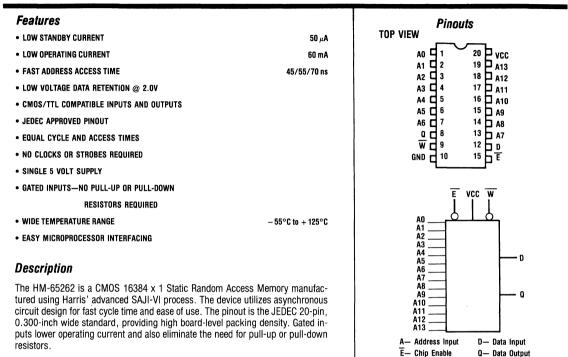

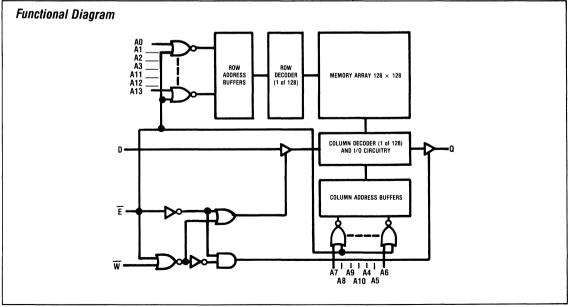

| HM-65262                  | 16K x 1 Asynchronous RAM                         | 2-83        |

| 1101-05202                | TOR X T Asynchronous NAM                         | 2-03        |

| CMOS RAM MODU             | LE DATA SHEETS                                   |             |

| HM-6564                   | 64K Synchronous RAM Module                       | 2-85        |

| HM-92560                  |                                                  | 2-96        |

| HM92570                   | 256K Synchronous RAM Module                      | 2-104       |

| CMOS PROM DATA            | SHEETS                                           |             |

| HM-6641                   | 512 x 8 Fuse Link PROM                           | 2-113       |

| HM-6616                   | 2K x 8 Fuse Link PROM                            | 2-118       |

|                           | URE CMOS PROM PRODUCTS                           |             |

| HM-6664                   |                                                  | 2-126       |

| 110-0004                  | SK X OT USE LINK FROM                            | 2-120       |

| PROGRAMMING F             | ORMAT FOR HARRIS PROMs                           | 2-128       |

| PREVIEW OF FUT            | URE CMOS HPL CIRCUITS                            |             |

| HPL-16LC8                 | Programmable Logic                               | 2-130       |

| HPL-16RC4                 | Programmable Logic                               | 2-132       |

| HPL-16RC6                 | Programmable Logic                               | 2-132       |

| HPL-16RC8                 | Programmable Logic                               | 2-132       |

|                           | - •                                              |             |

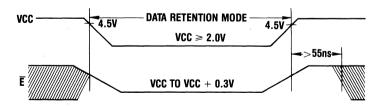

## Low Voltage Data Retention

## HARRIS CMOS/NMOS RAM Cross-Reference

|    | CMOS F           | EAMS<br>FEATURES | and  | FULLT | HITAC HI     | 101  | IWTER | MICROB | Anires. | MOTO  | NATIO HA       | NEC MAL | or           | ACA          | <sup>7</sup> OSkii | nues<br>nemos                   | Centerics    |

|----|------------------|------------------|------|-------|--------------|------|-------|--------|---------|-------|----------------|---------|--------------|--------------|--------------------|---------------------------------|--------------|

| 1K | 1K CMOS RAMs     |                  |      |       |              |      |       |        |         |       |                |         |              |              |                    |                                 | V//          |

| нм | I-6508 — 1K x 1  | 16 PIN<br>SYNCH  | 6508 | 8401  |              |      | 6508  | 6508   |         | 6508  | 6508<br>74C929 | 443     |              | 6508<br>1821 | 5508               | 2125<br>4015                    | ///          |

| нм | I-6518 – 1K x 1  | 18 PIN<br>SYNCH  | 6518 |       |              |      | 6518  | 6518   |         | 6518  | 6518<br>74C930 |         |              |              |                    |                                 |              |

| нм | –6561 – 256 x 4  | 22 PIN<br>SYNCH  |      |       |              |      | 6551  |        |         |       | 6551<br>74C920 |         |              | 1822         | 5101               | 2101                            | V//          |

| нм | -6561 — 256 x 4  | 18 PIN<br>SYNCH  |      |       |              |      | 6561  |        |         |       |                |         |              |              |                    | 2111                            | V/           |

| 41 | 4K CMOS RAMs     |                  |      |       |              |      |       |        |         |       |                |         |              |              |                    |                                 | V/           |

| нм | –6504 – 4K x 1   | 18 PIN<br>SYNCH  | 6504 | 8404  | 4315<br>6147 |      | 6504  | 6504   |         | 6504  | 6504           |         | 5104         |              | 5504               | 2141/47<br>315D<br>4104<br>4404 |              |

| нм | –6514 – 1K x 4   | 18 PIN<br>SYNCH  | 6514 | 8414  | 4334<br>6148 |      | 6514  | 6514   | 58981   | 6514  | 6514           | 444     | 5114<br>5115 | 5114         | 5514               | 2114<br>2148/49<br>4045<br>314A |              |

| 16 | K CMOS RAN       | /Is              |      |       |              |      |       |        |         |       |                |         |              |              |                    |                                 | V/           |

| HM | –6516 – 2K x 8   | 24 PIN<br>SYNCH  | 6516 |       |              |      |       |        |         |       | 6516           |         |              |              |                    |                                 | V/           |

| нм | -65162 — 2K x 8  | 24 PIN<br>ASYNCH |      | 8416  | 6116         | 6116 |       |        | 5117    | 65116 | 6116           | 446     | 5128         | 6116         | 5517               | 4802<br>2116<br>2016<br>4016    |              |

| нм | -65172 — 2K x 8  | 24 PIN<br>ASYNCH |      | 8418  | 6117         |      |       |        | 5116    |       |                | 449     |              |              | 5516               |                                 | V/           |

| нм | -65262 — 16K x 1 | 20 PIN<br>ASYNCH |      |       | 6167         | 6167 |       |        |         |       |                |         |              |              |                    | 2167<br>8167                    | $\mathbf{V}$ |

2-4

# HM-6508 1024 x 1 CMOS RAM

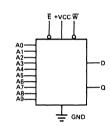

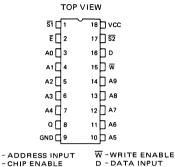

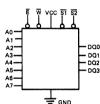

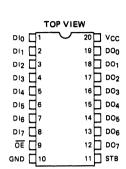

Pinout TOP VIEW

16 VCC

15 D D

14 D W

13 1 49

12 1 48

11 0 47

10 1 46

FLI

A2 🗖 4

A3 DE

A1 Пз

A4 Пe

۵

#### Features

- LOW STANDBY POWER .

- LOW OPERATING POWER .

- FAST ACCESS TIME . .

- DATA RETENTION VOLTAGE . TTL COMPATIBLE IN/OUT

- HIGH OUTPUT DRIVE 2 TTL LOADS .

- HIGH NOISE IMMUNITY .

- . ON CHIP ADDRESS REGISTER

- . MILITARY TEMPERATURE RANGE

- INDUSTRIAL TEMPERATURE RANGE

- . THREE-STATE OUTPUTS

- **16 PIN PACKAGE FOR HIGH DENSITY**

#### Description

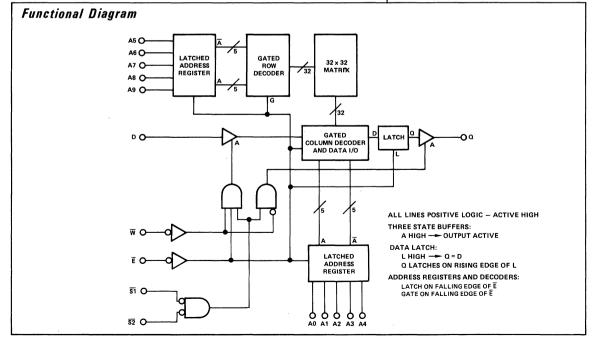

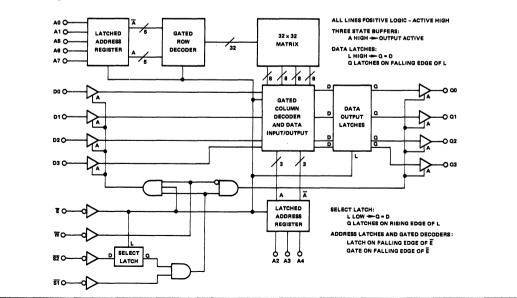

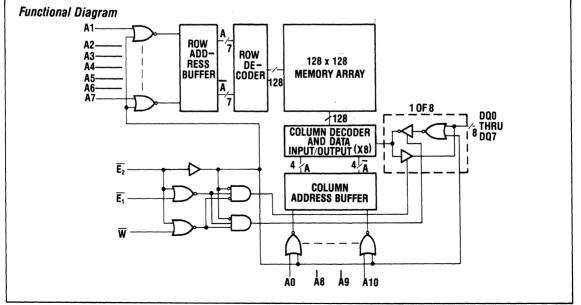

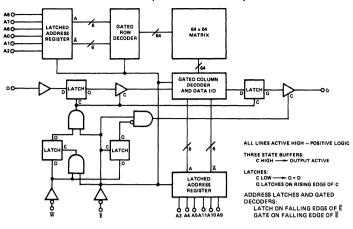

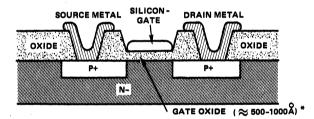

The HM-6508 is a 1024 by 1 static CMOS RAM fabricated using selfaligned silicon gate technology. Synchronous circuit design techniques are employed to achieve high performance and low power operation.

On chip latches are provided for address allowing efficient interfacing with microprocessor systems. The data output buffers can be forced to a high impedance state for use in expanded memory arrays.

The HM-6508 is a fully static RAM and may be maintained in any state for an indefinite period of time. Data retention supply voltage and supply current are guaranteed over temperature.

50 µW MAX 20mW/MHz MAX 180nsec MAX 2.0 VOLTS MIN

## Specifications HM-6508B-2/HM-6508B-9

| ABSOLUTE MAXIMUM RATIN          | GS                            | OPERATING RANGE                                           |                                   |

|---------------------------------|-------------------------------|-----------------------------------------------------------|-----------------------------------|

| Supply Voltage - (VCC -GND)     | -0.3V to +8.0V                | Operating Supply Voltage –VCC<br>Military (–2)            | 4.5V to 5.5V                      |

| Input or Output Voltage Applied | (GND -0.3V)<br>to (VCC +0.3V) | Industrial (-9)                                           | 4.5V to 5.5V                      |

| Storage Temperature             | -65°C to +150°C               | Operating Temperature<br>Military (-2)<br>Industrial (-9) | -55°C to +125°C<br>-40°C to +85°C |

#### ELECTRICAL CHARACTERISTICS

|        |                                    | TEMP. 8<br>OPERA<br>RAN |          | TEMP. = 25°C (1)<br>VCC = 5.0V |       | TEST                                 |

|--------|------------------------------------|-------------------------|----------|--------------------------------|-------|--------------------------------------|

| SYMBOL | PARAMETER                          | MIN                     | MAX      | TYPICAL                        | UNITS | CONDITIONS                           |

| ICCSB  | Standby Supply Current             |                         | 10       | 0.1                            | μΑ    | IO = 0<br>VI = VCC or GND            |

| ICCOP  | Operating Supply Current ②         |                         | 4        | 1.5                            | mA    | f = 1MHz, IO = 0<br>VI = VCC or GND  |

| ICCDR  | Data Retention Supply Current      |                         | 5        | 0.01                           | μΑ    | VCC = 2.0, IO = 0<br>VI = VCC or GND |

| VCCDR  | Data Retention Supply Voltage      | 2.0                     |          | 1.4                            | v     | Ē = VCC                              |

| П      | Input Leakage Current              | -1.0                    | +1.0     | 0.0                            | μΑ    | GND ≼ VI ≼ VC0                       |

| IOZ    | Output Leakage Current             | -1.0                    | +1.0     | 0.0                            | μΑ    | GND & VO & VC                        |

| VIL    | Input Low Voltage                  | -0.3                    | 0.8      | 2.0                            | v     |                                      |

| VIH    | Input High Voltage                 | VCC -2.0                | VCC +0.3 | 2.0                            | v     |                                      |

| VOL    | Output Low Voltage                 |                         | 0.4      | 0.2                            | v     | 10 = 3.2mA                           |

| voн    | Output High Voltage                | 2.4                     |          | 4.5                            | l v l | 10 = -0.4mA                          |

| CI     | Input Capacitance ③                |                         | 6        | 4                              | рF    | VI = VCC or GND<br>f = 1MHz          |

| со     | Output Capacitance ③               |                         | 10       | 6                              | рF    | VO = VCC or GND<br>f = 1MHz          |

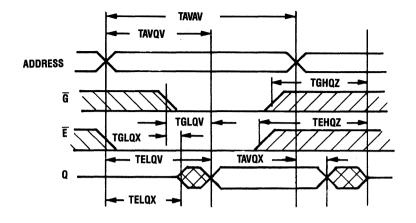

| TELQV  | Chip Enable Access Time            |                         | 180      | 100                            | ns    |                                      |

| TAVQV  | Address Access Time                |                         | 180      | 90                             | ns    | ā                                    |

| TELQX  | Chip Enable Output Enable Time     | 20                      | 120      | 40                             | ns    | 4                                    |

| TWLQZ  | Write Enable Output Disable Time   |                         | 120      | 40                             | ns    | ۹                                    |

| TEHQZ  | Chip Enable Output Disable Time    |                         | 120      | 40                             | ns    | 4                                    |

| TELEH  | Chip Enable Pulse Negative Width   | 180                     |          | 100                            | ns    | ବିଭିତ୍ତି ଭିତ୍ତି ଭିତି ଭିତି ଭିତି ଭିତି  |

| TEHEL  | Chip Enable Pulse Positive Width   | 100                     |          | 50                             | ns    | 4                                    |

| TAVEL  | Address Setup Time                 | 0                       |          | -10                            | ns    | 4                                    |

| TELAX  | Address Hold Time                  | 40                      |          | 20                             | ns    | <b>(()</b>                           |

| TDVWH  | Data Setup Time                    | 80                      |          | 40                             | ns    | <u>(4)</u>                           |

| TWHDX  | Data Hold Time                     | 0                       |          | 0                              | ns    | (4)                                  |

| TWLEH  | Chip Enable Write Pulse Setup Time | 100                     |          | 50                             | ns    | (4)                                  |

| TELWH  | Chip Enable Write Pulse Hold Time  | 100                     |          | 50                             | ns    | (4)                                  |

| TWLWH  | Write Enable Pulse Width           | 100                     |          | 50                             | ns    | (4)                                  |

| TELEL  | Read or Write Cycle Time           | 280                     |          | 150                            | ns    | (4)                                  |

NOTES: 1. All devices tested at worst case limits. Room temp., 5 volt data provided for information - not guaranteed.

Operating Supply Current (ICCOP) is proportional to Operating Frequency. Example: Typical ICCOP = 1.5mA/MHz.

Capacitance sampled and guaranteed - not 100% tested.

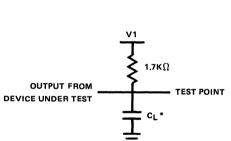

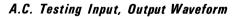

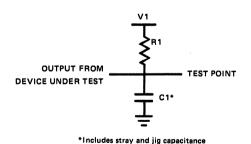

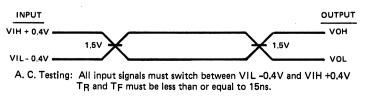

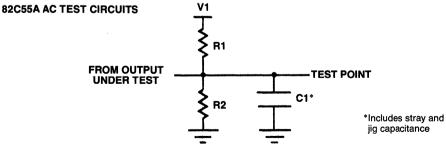

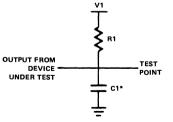

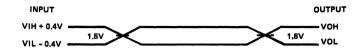

AC Test Conditions: Inputs – TRISE = TFALL = 20nsec; Outputs – CLOAD = 50pF. All timing measurements at 1.5V reference level.

D.C.

A.C.

| ABSOLUTE MAXIMUM RATIN          | IGS                           | OPERATING RANGE               |                 |

|---------------------------------|-------------------------------|-------------------------------|-----------------|

| Supply Voltage - (VCC - GND)    | -0.3V to +8.0V                | Operating Supply Voltage -VCC |                 |

|                                 |                               | Military (-2)                 | 4.5V to 5.5V    |

| Input or Output Voltage Applied | (GND -0.3V)<br>to (GND +0.3V) | Industrial (-9)               | 4.5V to 5.5V    |

|                                 |                               | Operating Temperature         |                 |

| Storage Temperature             | -65°C to +150°C               | Military (-2)                 | -55°C to +125°C |

|                                 |                               | Industrial (–9)               | -40°C to +85°C  |

CMOS MEMORY

Specifications HM-6508-2/HM-6508-9

#### **ELECTRICAL CHARACTERISTICS**

|                |                                                               | TEMP. & VCC =<br>OPERATING<br>RANGE |          |          |       | TEST                                                                                                           |

|----------------|---------------------------------------------------------------|-------------------------------------|----------|----------|-------|----------------------------------------------------------------------------------------------------------------|

| SYMBOL         | PARAMETER                                                     | MIN                                 | MAX      | TYPICAL  | UNITS | CONDITIONS                                                                                                     |

| ICCSB          | Standby Supply Current                                        |                                     | 10       | 0.1      | μΑ    | IO = 0<br>VI = VCC or GND                                                                                      |

| ICCOP          | Operating Supply Current ②                                    |                                     | 4        | 1.5      | mA    | f = 1MHz, IO = 0<br>VI = VCC or GND                                                                            |

| ICCDR          | Data Retention Supply Current                                 |                                     | 10       | 0.01     | μΑ    | VCC = 2.0, IO = 0<br><u>V</u> I = VCC or GND                                                                   |

| VCCDR          | Data Retention Supply Voltage                                 | 2.0                                 |          | 1.4      | v     | E = VCC                                                                                                        |

| - 11           | Input Leakage Current                                         | -1.0                                | +1.0     | 0.0      | μΑ    | GND                                                                                                            |

| ıoz            | Output Leakage Current                                        | -1.0                                | +1.0     | 0.0      | μΑ    | GND € VO € VCC                                                                                                 |

| VIL            | Input Low Voltage                                             | -0.3                                | 0.8      | 2.0      | v     |                                                                                                                |

| VIH            | Input High Voltage                                            | VCC -2.0                            | VCC +0.3 | 2.0      | v     |                                                                                                                |

| VOL            | Output Low Voltage                                            |                                     | 0.4      | 0.2      | v     | 10 = 3.2mA                                                                                                     |

| <b>VOH</b>     | Output High Voltage                                           | 2.4                                 |          | 4.5      | v     | 10 = -0.4mA                                                                                                    |

| CI             | Input Capacitance ③                                           |                                     | 6        | 4        | pF    | VI = VCC or GND<br>f = 1MHz                                                                                    |

| со             | Output Capacitance ③                                          |                                     | 10       | 6        | pF    | VO=VCC or GND<br>f = 1MHz                                                                                      |

| TELQV          | Chip Enable Access Time                                       |                                     | 250      | 110      | ns    | 4                                                                                                              |

| TAVQV          | Address Access Time                                           |                                     | 250      | 100      | ns    | 4                                                                                                              |

| TELOX          | Chip Enable Output Enable Time                                | 20                                  | 160      | 60       | ns    | 4                                                                                                              |

| TWLQZ          | Write Enable Output Disable Time                              |                                     | 160      | 60       | ns    | 4                                                                                                              |

| TEHQZ          | Chip Enable Output Disable Time                               |                                     | 160      | 60       | ns    | 4                                                                                                              |

| TELEH          | Chip Enable Pulse Negative Width                              | 250                                 |          | 110      | ns    | 4                                                                                                              |

| TEHEL          | Chip Enable Pulse Positive Width                              | 100                                 |          | 50       | ns    | (4)                                                                                                            |

| TAVEL          | Address Setup Time                                            | 0                                   |          | -10      | ns    | (4)                                                                                                            |

| TELAX          | Address Hold Time                                             | 50                                  |          | 30       | ns    | କାର କାରକାର କ |

| TDVWH          | Data Setup Time                                               | 110                                 |          | 50       | ns    | (4)                                                                                                            |

| TWHDX          | Data Hold Time                                                | 0                                   |          | 0        | ns    | 4                                                                                                              |

| TWLEH          | Chip Enable Write Pulse Setup Time                            | 130                                 |          | 60       | ns    | 4                                                                                                              |

| TELWH<br>TWLWH | Chip Enable Write Pulse Hold Time<br>Write Enable Pulse Width | 130<br>130                          |          | 60<br>60 | ns    | 4                                                                                                              |

|                |                                                               |                                     | 1 1      | i bU     | ns    | (4)                                                                                                            |

D.C.

A.C.

NOTES: 1. All devices tested at worst case limits. Room temp., 5 volt data provided for information - not guaranteed.

Operating Supply Current (ICCOP) is proportional to Operating Frequency. Example: Typical ICCOP = 1.5mA/MHz.

Capacitance sampled and guaranteed - not 100% tested.

AC Test Conditions: Inputs – TRISE = TFALL = 20nsec; Outputs – CLOAD = 50pF. All timing measurements at 1.5V reference level.

| ABSOLUTE MAXIMUM RATIN          | IGS                           | OPERATING RANGE                             |              |

|---------------------------------|-------------------------------|---------------------------------------------|--------------|

| Supply Voltage -(VCC -GND)      | -0.3V to +8.0V                | Operating Supply Voltage –VCC<br>Commercial | 4.5V to 5.5V |

| Input or Output Voltage Applied | (GND -0.3V)<br>to (VCC +0.3V) |                                             |              |

|                                 |                               | Operating Temperature                       |              |

| Storage Temperature             | -65°C to +150°C               | Commercial                                  | 0°C to +70°C |

|      |                |                                         | TEMP. 8<br>OPERA<br>RAM | TING     | TEMP. = 25°C (1)<br>VCC = 5.0V |          | TEST                                  |

|------|----------------|-----------------------------------------|-------------------------|----------|--------------------------------|----------|---------------------------------------|

|      | SYMBOL         | PARAMETER                               | MIN                     | МАХ      | TYPICAL                        | UNITS    | CONDITIONS                            |

|      | ICCSB          | Standby Supply Current                  |                         | 100      | 10                             | μA       | IO = 0<br>VI = VCC or GND             |

|      | ICCOP          | Operating Supply Current ②              |                         | 4        | 1.5                            | mA       | f = 1MHz, IO = 0<br>VI = VCC or GND   |

|      | ICCDR          | Data Retention Supply Current           |                         | 100      | 1,0                            | μΑ       | VCC = 2.0, IO = 0<br>VI = VCC or GND  |

| D.C. | VCCDR          | Data Retention Supply Voltage           | 2.0                     |          |                                | v        | Ē = VCC                               |

|      | 11             | Input Leakage Current                   | -1.0                    | +1.0     | 0.0                            | μΑ       | GND ≰ VI ≰ VCC                        |

|      | IOZ            | Output Leakage Current                  | -1.0                    | +1.0     | 0.0                            | μΑ       | GND ≪ VO ≪ VCC                        |

|      | VIL            | Input Low Voltage                       | -0.3                    | 0.8      | 2.0                            | v        |                                       |

|      | VIH            | Input High Voltage                      | VCC -2.0                | VCC +0.3 | 2.0                            | v        |                                       |

|      | VOL            | Output Low Voltage                      |                         | 0.4      | 0.2                            | v        | 10 = 1.6mA                            |

|      | <b>VOH</b>     | Output High Voltage                     | 2.4                     |          | 4.5                            | v        | 10 = -0.2mA                           |

|      | СІ             | Input Capacitance ③                     |                         | 6        | 4                              | рF       | VI = VCC or GND<br>f = 1MHz           |

|      | со             | Output Capacitance ③                    |                         | 10       | 6                              | pF       | VO = VCC or GND<br>f = 1MHz           |

|      | TELQV          | Chip Enable Access Time                 |                         | 300      | 160                            | ns       | 4                                     |

|      | TAVQV          | Address Access Time                     |                         | 310      | 160                            | ns       | 4                                     |

|      | TELQX          | Chip Enable Output Enable Time          | 20                      | 200      | 60                             | ns       | 4                                     |

|      | TWLQZ          | Write Enable Output Disable Time        |                         | 200      | 60                             | ns       | 4                                     |

|      | TEHOZ          | Chip Enable Output Disable Time         |                         | 200      | 60                             | ns       | (4)                                   |

|      | TELEH          | Chip Enable Pulse Negative Width        | 300                     |          | 160                            | ns       | (4)                                   |

| A.C. | TEHEL          | Chip Enable Pulse Positive Width        | 150                     |          | 90                             | ns       | (4)                                   |

| A.C. | TAVEL<br>TELAX | Address Setup Time<br>Address Hold Time | 10<br>70                |          | 0<br>40                        | ns       | 4                                     |

|      | TDVWH          | Data Setup Time                         | 130                     |          | 80                             | ns<br>ns |                                       |

|      | TWHDX          | Data Hold Time                          | 0                       |          | 0                              | ns       | ()<br>()                              |

|      | TWLEH          | Chip Enable Write Pulse Setup Time      | 160                     |          | 100                            | ns       | ୧୦୦୦୦୦୦୦୦୦୦୦୦୦୦୦୦୦୦୦୦୦୦୦୦୦୦୦୦୦୦୦୦୦୦୦୦ |

|      | TELWH          | Chip Enable Write Pulse Hold Time       | 160                     |          | 100                            | ns       | ă I                                   |

|      | TWLWH          | Write Enable Pulse Width                | 160                     |          | 100                            | ns       | ă                                     |

|      | TELEL          | Read or Write Cycle Time                | 450                     |          | 250                            | ns       | ĕ                                     |

|      | L              |                                         | L                       | ll       | L                              | I        |                                       |

NOTES: 1. All devices tested at worst case limits. Room temp., 5 volt data provided for information - not guaranteed.

2. Operating Supply Current (ICCOP) is proportional to Operating Frequency. Example: Typical ICCOP = 1.5mA/MHz.

3. Capacitance sampled and guaranteed - not 100% tested.

AC Test Conditions: Inputs – TRISE = TFALL = 20nsec; Outputs – CLOAD = 50pF. All timing measurements at 1.5V reference level.

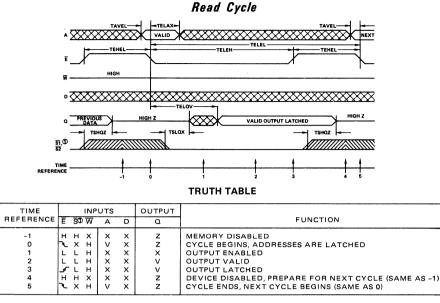

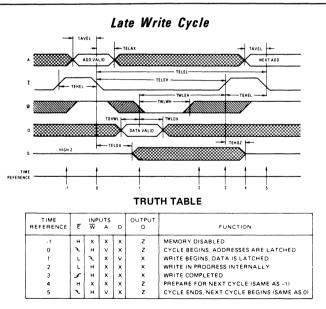

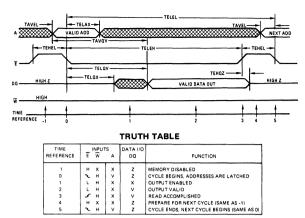

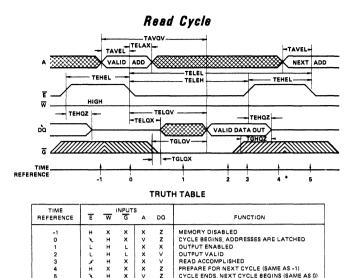

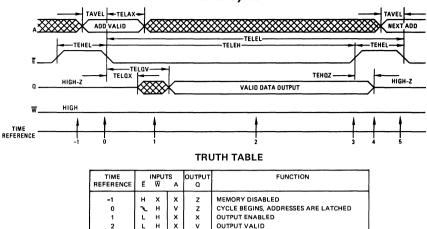

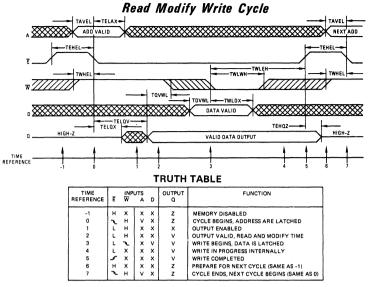

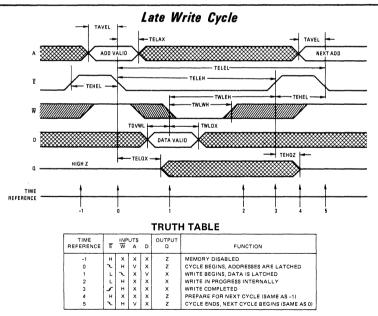

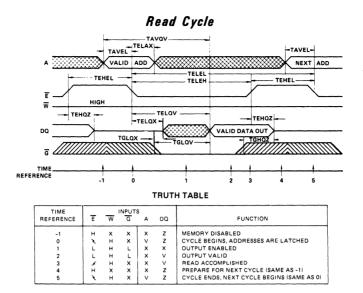

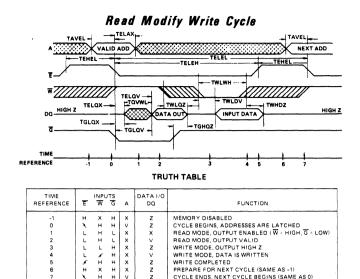

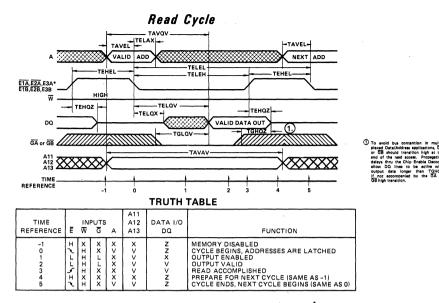

TRUTH TABLE

| TIME<br>REFERENCE                | Ē       | INP<br>W | UTS<br>A      | D               | OUTPUTS<br>Q               | FUNCTION                                                                                                                                                                          |

|----------------------------------|---------|----------|---------------|-----------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -1<br>0<br>1<br>2<br>3<br>4<br>5 | エイレントエイ | ΧΙΙΙΧΙ   | * > * * * * > | × × × × × × × × | z<br>z<br>x<br>v<br>z<br>z | MEMORY DISABLED<br>CYCLE BEGINS, ADDRESSES ARE LATCHED<br>OUTPUT ENABLED<br>READ ACCOMPLISHED<br>PREPARE FOR NEXT CYCLE (SAME AS -1)<br>CYCLE ENDS, NEXT CYCLE BEGINS (SAME AS 0) |

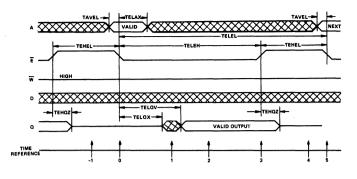

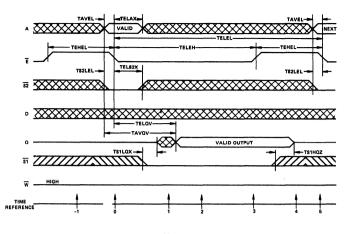

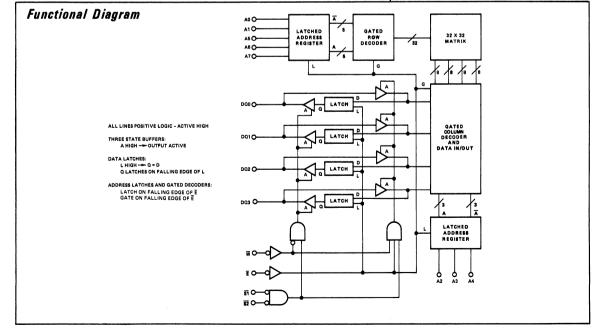

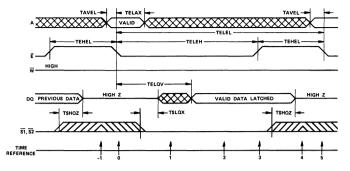

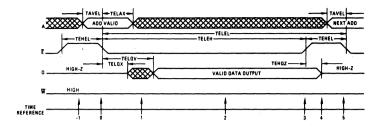

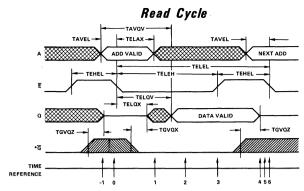

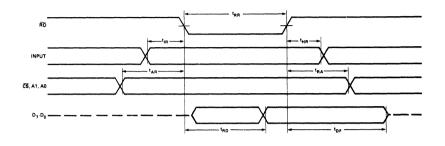

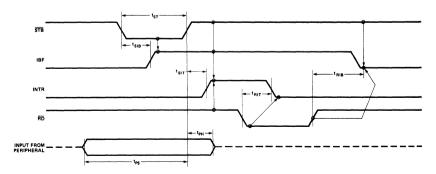

In the HM-6508 Read Cycle, the address information is latched into the on chip registers on the falling edge of  $\overline{E}$  (T = 0). Minimum address setup and hold time requirements must be met. After the required hold time, the addresses may change state without affecting device operation. During time (T = 1) the data output becomes enabled; however, the data is not valid until during time

(T = 2). W must remain high for the read cycle. After the output data has been read,  $\overline{E}$  may return high (T = 3). This will disable the chip and force the output buffer to a high impedance state. After the required  $\overline{E}$  high time (TEHEL) the RAM is ready for the next memory cycle (T = 4).

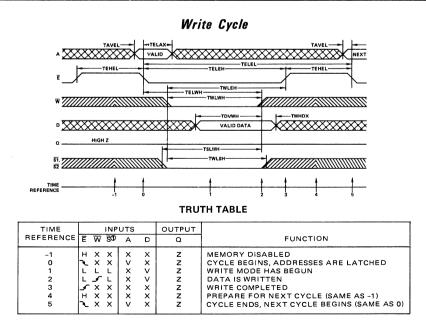

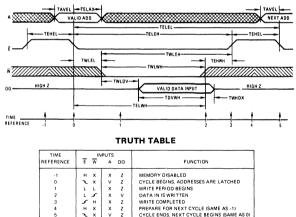

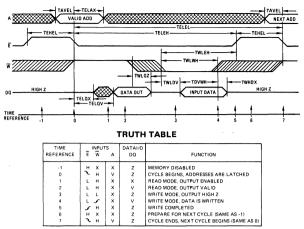

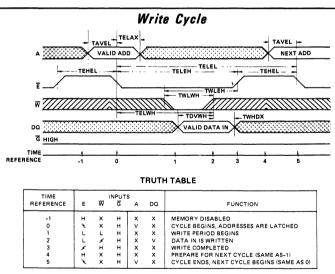

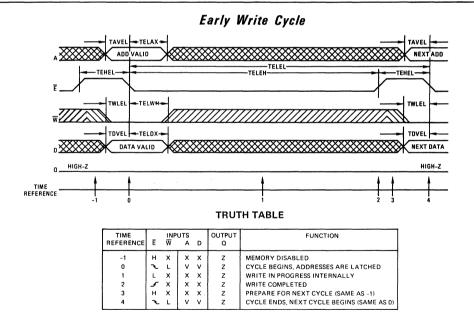

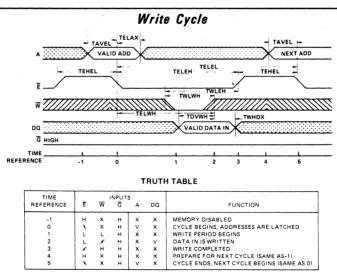

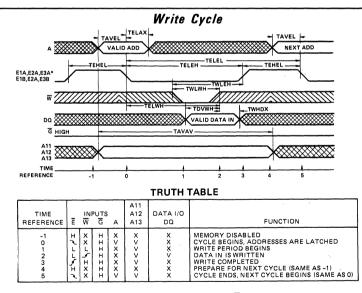

| TRUTH TABLE |

|-------------|

|-------------|

| TIME                             | Ē             |                              | UTS<br>A      | D   | OUTPUTS<br>Q                    | FUNCTION                                                                                                                                                                                                |

|----------------------------------|---------------|------------------------------|---------------|-----|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -1<br>0<br>1<br>2<br>3<br>4<br>5 | ד א ד א ד א ד | $\times \times \pi^{\prime}$ | * > * * * * > | *** | Z<br>Z<br>Z<br>Z<br>Z<br>Z<br>Z | MEMORY DISABLED<br>CYCLE BEGINS, ADDRESSES ARE LATCHED<br>WRITE PERIOD BEGINS<br>DATA IS WRITTEN<br>WRITE COMPLETED<br>PREPARE FOR NEXT CYCLE (SAME AS -1)<br>CYCLE ENDS, NEXT CYCLE BEGINS (SAME AS 0) |

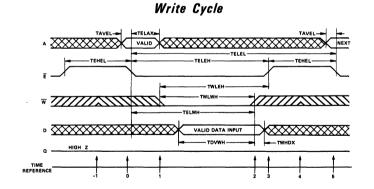

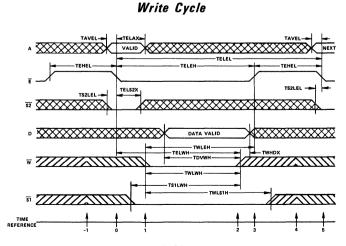

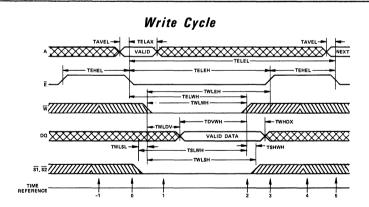

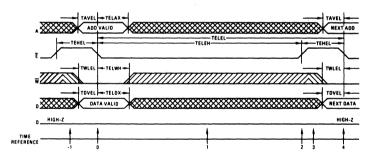

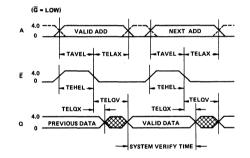

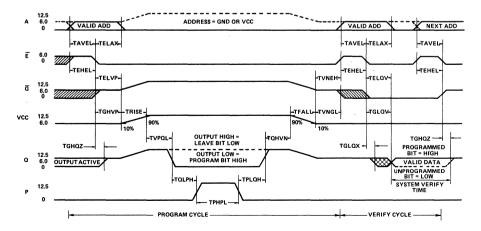

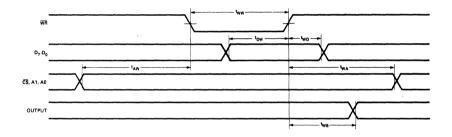

CMOS MEMORY The write cycle is initiated by the falling edge of  $\overline{E}$  which latches the address information into the on chip registers. The write portion of the cycle is defined as both  $\overline{E}$  and  $\overline{W}$  being low simultaneously.  $\overline{W}$  may go low anytime during the cycle provided that the write enable pulse setup time (TWLEH) is met. The write portion of the cycle is terminated by the first rising edge of either  $\overline{E}$  or  $\overline{W}$ . Data setup and hold times must be referenced to the terminating signal.

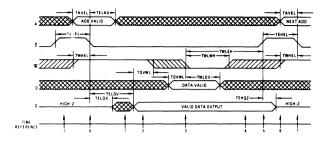

If a series of consecutive write cycles are to be performed, the  $\overline{W}$  line may remain low until all desired locations have been written. When this method is used, data setup and hold times must be referenced to the rising edge of  $\overline{E}$ . By positioning the  $\overline{W}$  pulse at different times within the  $\overline{E}$  low time (TELEH), various types of write cycles may be performed.

If the  $\overline{E}$  low time (TELEH) is greater than the  $\overline{W}$  pulse (TWLWH) plus an output enable time (TELOX), a combination read write cycle is executed. Data may be modified an indefinite number of times during any write cycle (TELEH). The data input and data output pins may be tied together for use with a common I/O data bus structure. When using the RAM in this method allow a minimum of one output disable time (TWLOZ) after  $\overline{W}$  goes low before applying input data to the bus. This will insure that the output buffers are not active.

# HM-6518 1024 x 1 CMOS BAM

Pinout

#### Features

- HM-6100 COMPATIBLE

- LOW STANDBY POWER

- LOW OPERATING POWER

- FAST ACCESS TIME

- DATA RETENTION VOLTAGE

- TTL COMPATIBLE IN/OUT

- HIGH OUTPUT DRIVE 2 TTL LOADS

- HIGH NOISE IMMUNITY

- ON CHIP ADDRESS REGISTER

- TWO CHIP SELECTS FOR EASY ARRAY EXPANSION

- THREE STATE OUTPUTS

- MILITARY TEMPERATURE RANGE

- INDUSTRIAL TEMPERATURE RANGE

#### Description

The HM-6518 is a 1024 by 1 static CMOS RAM fabricated using selfaligned silicon gate technology. Synchronous circuit design techniques are employed to achieve high performance and low power operation.

On chip latches are provided for address and data outputs allowing efficient interfacing with microprocessor systems. The data output buffers can be forced to a high impedance state for use in expanded memory arrays.

The HM-6518 is a fully static RAM and may be maintained in any state for an indefinite period of time. Data retention supply voltage and supply current are guaranteed over temperature.

50 µW MAX

180nsec MAX

20 mW/MHz MAX

2.0 VOLTS MIN

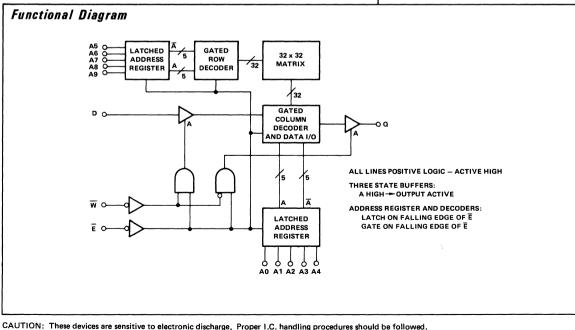

CAUTION: These devices are sensitive to electronic discharge. Proper I.C. handling procedures should be followed. 2 - 11

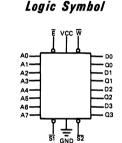

D - DATA INPUT Q - DATA OUTPUT

Logic Symbol

Ê

S - CHIP SELECT

## Specifications HM-6518B-2/HM-6518B-9

| ABSOLUTE MAXIMUM RATIN          | IGS                           | OPERATING RANGE                                           |                                   |

|---------------------------------|-------------------------------|-----------------------------------------------------------|-----------------------------------|

| Supply Voltage - (VCC -GND)     | -0.3V to +8.0V                | Operating Supply Voltage -VCC<br>Military (-2)            | 4.5V to 5.5V                      |

| Input or Output Voltage Applied | (GND -0.3V)<br>to (VCC +0.3V) | Industrial (–9)                                           | 4.5V to 5.5V                      |

| Storage Temperature             | -65°C to +150°C               | Operating Temperature<br>Military (-2)<br>Industrial (-9) | -55°C to +125°C<br>-40°C to +85°C |

#### **ELECTRICAL CHARACTERISTICS**

|                |                                                                        | OPERA      | & VCC =<br>ATING<br>NGE | TEMP. = 25°C ①<br>VCC = 5.0V |          | TEST                                 |

|----------------|------------------------------------------------------------------------|------------|-------------------------|------------------------------|----------|--------------------------------------|

| SYMBOL         | PARAMETER                                                              | MIN        | MAX                     | TYPICAL                      | UNITS    | CONDITIONS                           |

| ICCSB          | Standby Supply Current                                                 |            | 10                      | 0.1                          | μΑ       | IO = 0<br>VI = VCC or GND            |

| ICCOP          | Operating Supply Current ②                                             |            | 4                       | 1.5                          | mA       | f = 1MHz, IO = 0<br>VI = VCC or GND  |

| ICCDR          | Data Retention Supply Current                                          |            | 5                       | 0.01                         | μΑ       | VCC = 2.0, IO = 0<br>⊻I = VCC or GND |

| VCCDR          | Data Retention Supply Voltage                                          | 2.0        |                         | 1.4                          | v        | E = VCC                              |

| н              | Input Leakage Current                                                  | -1.0       | +1.0                    | 0.0                          | μΑ       | GND ≼ VI ≼ VCC                       |

| IOZ            | Output Leakage Current                                                 | -1.0       | +1.0                    | 0.0                          | μΑ       | GND ≼ VO ≼ VCC                       |

| VIL            | Input Low Voltage                                                      | -0.3       | 0.8                     | 2.0                          | v        |                                      |

| VIH            | Input High Voltage                                                     | VCC -2.0   | VCC +0.3                | 2.0                          | v        |                                      |

| VOL            | Output Low Voltage                                                     |            | 0.4                     | 0.2                          | v        | 10 = 3.2mA                           |

| VOH            | Output High Voltage                                                    | 2.4        |                         | 4.5                          | v        | 10 = -0.4mA                          |

| CI             | Input Capacitance ③                                                    |            | 6                       | 4                            | pF       | VI = VCC or GND<br>f = 1MHz          |

| со             | Output Capacitance ③                                                   |            | 10                      | 6                            | pF       | VO= VCC or GND<br>f = 1MHz           |