-total

HARRIS

1989

DIGITAL

# DIGITAL PRODUCT DATA BOOK MILITARY

MC 62

> MC \*•63

## Harris Semiconductor Military & Aerospace Products

This databook contains detailed technical information on the extensive line of military and aerospace digital products currently available from Harris Semiconductor. A sister publication describing analog military and aerospace ICs — "Analog Military Databook" — published in January 1989 is also available. Other high reliability products available under the brand names of GE, RCA and Intersil — now a part of the New Harris Semiconductor — can be found in the two-volume GE Solid State High-Reliability databook. Volume I contains information on CMOS ICs and Volume II covers Analog ICs and Discrete Devices.

Copyright © Harris Corporation 1989 (All Rights Reserved) Printed in U.S.A.

## Harris CMOS Digital Products

Harris Semiconductor is the eighth largest U.S. merchant semiconductor supplier and is a sector of Harris Corporation. Harris acquired the solid state division of General Electric (including RCA and Intersil semiconductor products) in December 1988. Harris is a pioneer in developing and producing digital CMOS products including: CMOS RAMs, CMOS PROMs, CMOS microprocessors, CMOS peripherals, CMOS data communications products and a full line of 80C286 and 80C86/88 microprocessors and peripherals.

This data book describes Harris Semiconductor's military line of CMOS digital products. It includes a complete set of data sheets for product specifications, application notes with design details for specific applications of Harris products, and a description of the Harris quality and high reliability program.

If you need more information on these and other Harris products, please contact the nearest Harris sales office listed in the back of this data book, or the Harris Semiconductor literature department.

Harris Semiconductor products are sold by description only. All specifications in this data book are applicable only to packaged products; specifications for dice are available upon request. Harris reserves the right to make changes in circuit design, specifications and other information at any time without prior notice. Accordingly, the reader is cautioned to verify that data sheets and other information in this publication are current before placing orders. Information contained in the application notes is intended solely for general guidance; use of the information for user's specific application is at user's risk. Reference to products of other manufacturers are solely for convenience of comparison and do not imply total equivalency of design, performance or otherwise. Finally, without the pior specific approval of an officer of Harris, the Harris products should not be used as critical components (i.e., failure of the Harris product is likely to cause failure of the system) in life support devices or systems (i.e., surgically implantable devices or life-sustaining machines).

# 1989 Military Data Book

DIGITA

# **General Information**

#### PAGE ALPHA NUMERIC PRODUCT INDEX 6-43 HD-15530/883 Manchester Encoder-Decoder ..... Manchester Encoder-Decoder ..... 6-56 HD-15531/883 Programmable Bit Rate Generator HD-4702/883 6-3 HD-6402/883 Universal Asynchronous Receiver Transmitter ..... 6-14 HD-6409/883 Manchester Encoder-Decoder ..... 6-27 4K x 1 Synchronous RAM ..... 3-52 HM-6504/883 HM-6508/883 1K x 1 Synchronous RAM ..... 3-4 HM-6514/883 1K x 4 Synchronous RAM 3-67 2K x 8 Synchronous RAM ..... HM-6516/883 3-82 HM-65162/883 2K x 8 Asynchronous BAM 3-91 1K x 1 Synchronous RAM HM-6518/883 3-16 HM-65262/883 16K x 1 Asynchronous RAM ..... 3 - 104HM-6551/883 256 x 4 Synchronous RAM ..... 3-28 256 x 4 Synchronous RAM ..... HM-6561/883 3 - 40HM-6564 64K Synchronous RAM Module ..... 3-140 HM-65642/883 8K x 8 Asynchronous RAM ..... 3-115 8K x 8 Asynchronous RAM ..... HM-65642C/883 3-129 HM-6617/883 2K x 8 Fuse Link PROM ..... 3-206 HM-6642/883 512 x 8 Fuse Link PROM ..... 3-194 HM-8808/08A 8K x 8 Asynchronous RAM Modules ..... 3-146 HM-8816H 16K x 8 Asynchronous RAM Module ..... 3-159 HM-8832 32K x 8 Asynchronous RAM Module ..... 3-165 HM-92560 256K Synchronous RAM Module ..... 3-172 HM-92570 256K Buffered Synchronous RAM Module ..... 3-178 HM-91M2 1M Bit Asynchronous RAM Module ..... 3-184 80C86/883 Static 16-Bit Microprocessor 4-62 Static 8/16-Bit Microprocessor 4-97 80C88/883 80C286/883 Static 16-Bit Microprocessor 4-3 82C284/883 Clock Generator and Ready Interface for 80C286 Processors ..... 5-153 82C288/883 Bus Controller for 80C286 Processors ..... 5-168 High Performance Programmable DMA Controller ..... 82C37A/883 5-3 5-4 82C52/883 Serial Controller Interface..... 82C54/883 Programmable Interval Timer ..... 5 - 1982C55A/883 Programmable Peripheral Interface ..... 5-38 Priority Interrupt Controller..... 82C59A/883 5-62 Octal Latching Bus Driver ..... 5-81 82C82/883 82C83H/883 Octal Latching Inverting Bus Driver 5-90 Clock Generator Driver 82C84A/883 5 - 9882C85/883 Static Clock Controller/Generator ..... 5 - 11082C86H/883 Octal Bus Tranceiver ..... 5 - 11182C87H/883 Octal Bus Tranceiver ..... 5-119 82C88/883 Bus Controller 5-127 Bus Arbiter ..... 82C89/883 5-138

1

GENERAL INFORMATION

# CMOS Devices by Families

| 8, | 16-BIT MICROPROCE  | SSORS                                                     | PAGE   |

|----|--------------------|-----------------------------------------------------------|--------|

|    | 80C286/883         | Static 16-Bit Microprocessor                              | 4-3    |

|    | 80C86/883          | Static 16-Bit Microprocessor                              | 4-62   |

|    | 80C88/883          | Static 8/16-Bit Microprocessor                            | 4-97   |

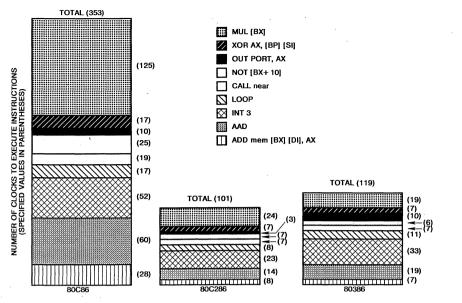

|    | App Note 111       | Harris 80C286 Performance Advantages Over the 80386       | 4-131  |

|    | App Note 112       | 80C286/80386 Hardware Comparison                          | 4-143  |

|    | App Note 120       | Interfacing the 80C286-16 with the 80287-10               | 4-147  |

| 8  | 0C86/88 PERIPHERAL | CIRCUITS                                                  |        |

|    | 82C37A/883         | High Performance Programmable DMA Controller              | 5-3    |

|    | 82C52/883          | Serial Controller Interface                               | 5-4    |

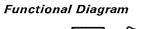

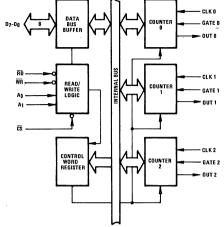

|    | 82C54/883          | Programmable Interval Timer                               | 5-19   |

|    | 82C55A/883         | Programmable Peripheral Interface                         | 5-38   |

|    | 82C59A/883         | Priority Interrupt Controller                             | 5-62   |

|    | App Note 109       | 82C59A Priority Interrupt Controller                      | 5-169  |

| 8  | 0C86/88 BUS SUPPOR | IT CIRCUITS                                               |        |

|    | 82C82/883          | Octal Latching Bus Driver                                 | 5-81   |

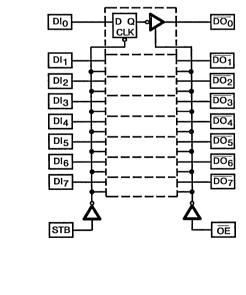

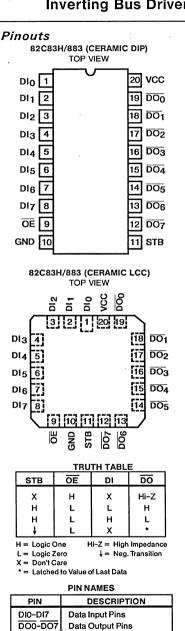

|    | 82C83H/883         | Octal Latching Inverting Bus Driver                       | 5-90   |

|    | 82C84A/883         | Clock Generator Driver                                    | 5-98   |

|    | 82C85/883          | Static Clock Controller/Generator                         | 5-110  |

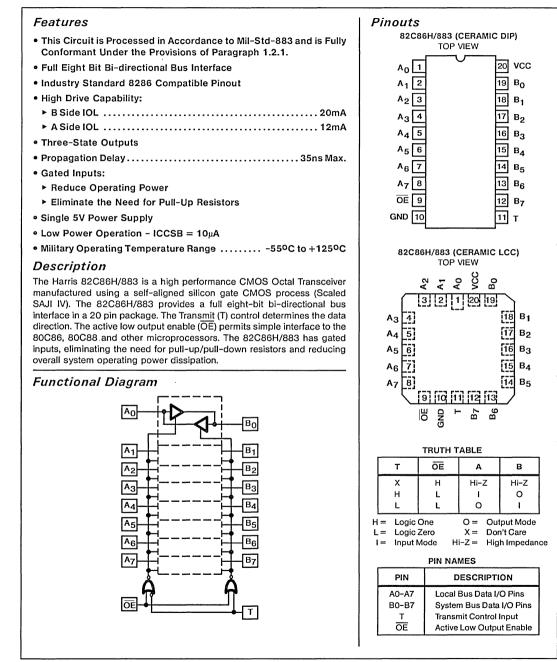

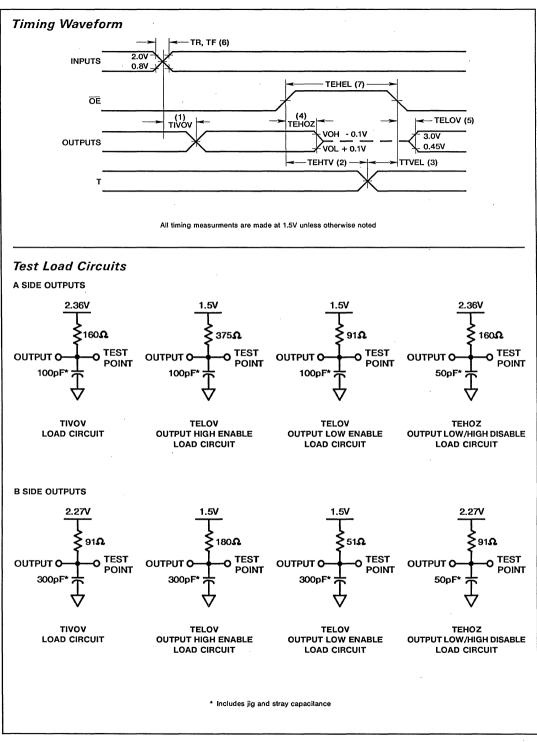

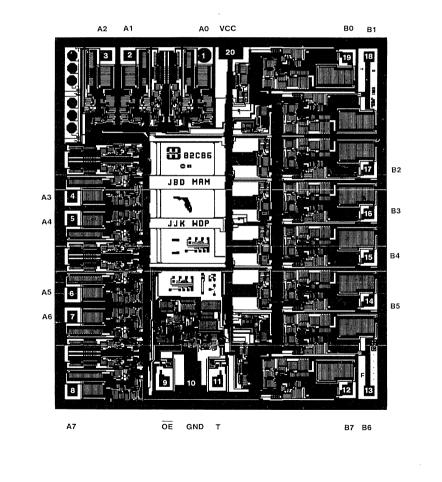

|    | 82C86H/883         | Octal Bus Tranceiver                                      | 5-111  |

|    | 82C87H/883         | Octal Bus Tranceiver                                      | 5-119  |

|    | 82C88/883          | Bus Controller                                            | 5-127  |

|    | 82C89/883          | Bus Arbiter                                               | 5-138  |

| 8  | 0C286 BUS SUPPORT  |                                                           |        |

| -  | 82C284/883         | Clock Generator and Ready Interface for 80C286 Processors | 5-153  |

|    | 82C288/883         | Bus Controller for 80C286 Processors                      | 5-168  |

| s  | ERIAL COMMUNICATIO |                                                           |        |

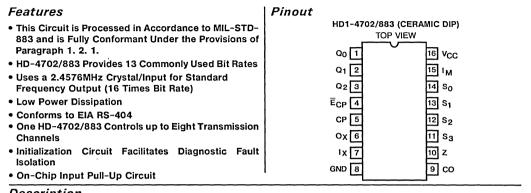

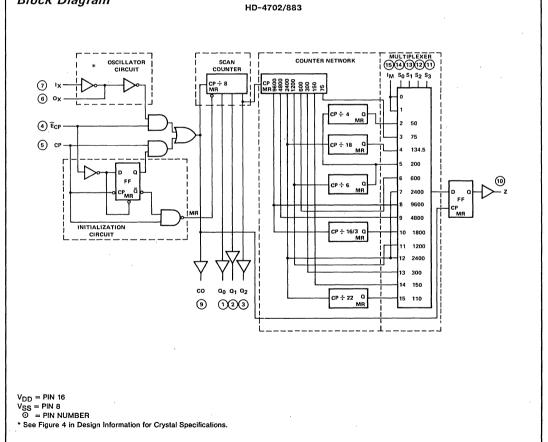

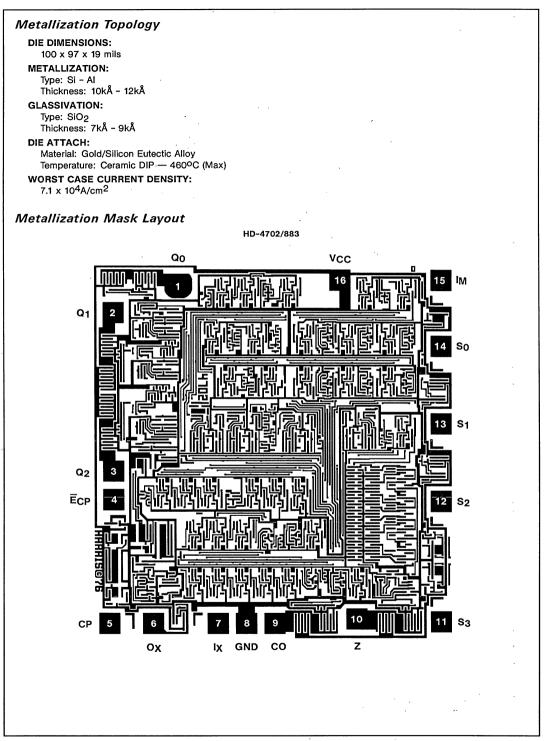

| -  | HD-4702/883        | Programmable Bit Rate Generator                           | 6-3    |

|    | HD-6402/883        | Universal Asynchronous Receiver Transmitter               | 6-14   |

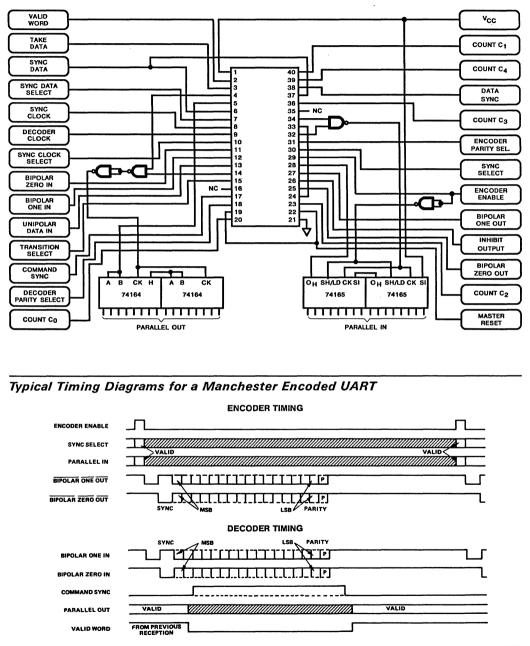

|    | HD-6409/883        | Manchester Encoder-Decoder                                | 6-27   |

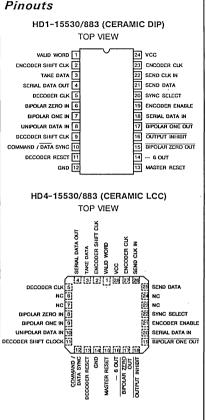

|    | HD-15530/883       | Manchester Encoder-Decoder                                | 6-43   |

|    | HD-15531/883       | Manchester Encoder-Decoder                                | 6-56   |

| С  | MOS STATIC RAMS    |                                                           | 0 00   |

|    | K — SYNCHRONOUS    |                                                           |        |

|    | HM-6508/883        | 1K x 1 Synchronous RAM                                    | 3-4    |

|    | HM-6518/883        | 1K x 1 Synchronous RAM                                    | 3-16   |

|    | HM-6551/883        | 256 x 4 Synchronous RAM                                   | 3-28   |

|    | HM-6561/883        | 256 x 4 Synchronous RAM                                   | 3-40   |

| 4  | K - SYNCHRONOUS    |                                                           | 0.10   |

| •  | HM-6504/883        | 4K x 1 Synchronous RAM                                    | 3-52   |

|    | HM-6514/883        | 1K x 4 Synchronous RAM                                    | 3-67   |

| 1  | 6K - SYNCHRONOUS   | •                                                         | 0.01   |

| •  | HM-6516/883        | 2K x 8 Synchronous RAM                                    | 3-82   |

| 1  | 6K - ASYNCHRONOU   |                                                           | 0 01   |

| •  | HM-65162/883       | 2K x 8 Asynchronous RAM                                   | 3-91   |

|    | HM-65262/883       | 16K x 1 Asynchronous RAM                                  | 3-104  |

| 6  | 4K - ASYNCHRONOU   |                                                           | • •• • |

| -  | HM-65642/883       | 8K x 8 Asynchronous RAM                                   | 3-115  |

|    | HM-65642C/883      | 8K x 8 Asynchronous RAM                                   | 3-129  |

| С  | MOS RAM MODULE     |                                                           | ••     |

|    | HM-6564            | 64K Synchronous RAM Module                                | 3-140  |

|    | HM-8808/08A        | 8K x 8 Asynchronous RAM Modules                           | 3-146  |

|    | HM-8816H           | 16K x 8 Asynchronous RAM Module                           | 3-159  |

|    | HM-8832            | 32K x 8 Asynchronous RAM Module                           | 3-165  |

|    | HM-92560           | 256K Synchronous RAM Module                               | 3-172  |

|    | HM-92570           | 256K Buffered Synchronous RAM Module                      | 3-178  |

|    | HM-91M2            | 1M Bit Asynchronous RAM Module                            | 3-184  |

| c  | MOS FUSE LINK PROM | •                                                         | 5 .64  |

|    | HM-6642/883        | 512 x 8 Fuse Link PROM                                    | 3-194  |

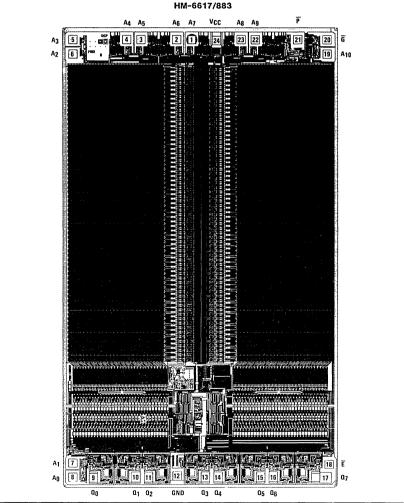

|    | HM-6617/883        | 2K x 8 Fuse Link PROM                                     | 3-206  |

|    |                    |                                                           |        |

# **Ordering Information**

Harris Semiconductor products are represented by an extensive network of factory sales personnel, sales representative, and authorized distributors throughout the world. Please contact your nearest sales office, representative, or distributor for product information, pricing, ordering, or delivery details. A complete list of sales offices is available by contacting the Harris Semiconductor literature department at (407) 724-3739. Headquarters are also listed at the end of this book.

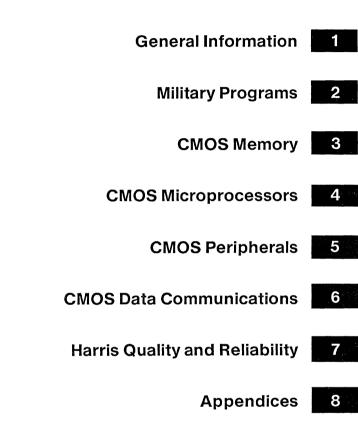

#### Product Code

Harris products are designated by a "Product Code". This code includes designators for the product family, device type, performance grade, temperature grade and package style. Examples of the product codes are shown below:

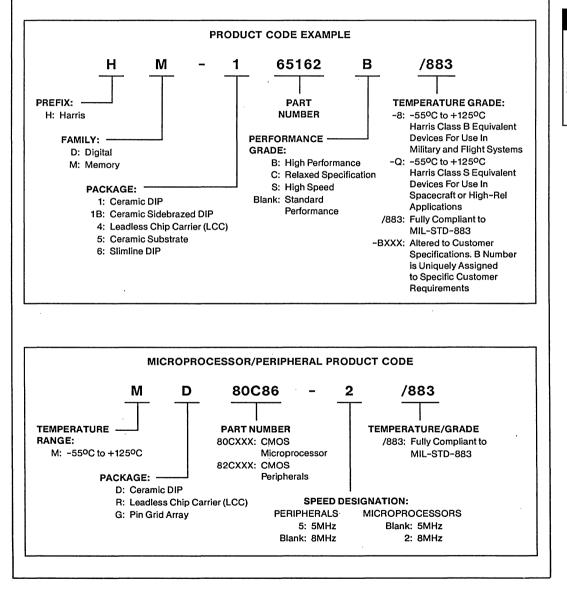

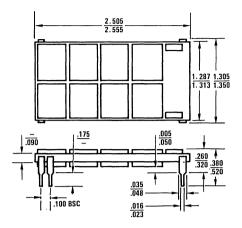

# Packaging Techniques

Harris Semiconductor offers Leadless Chip Carriers (LCC) as a packaging option on various Digital integrated circuits. An LCC is a square or rectangular package for an Integrated Circuit (IC) that is manufactured in the same manner as a conventional side-braze dual-in-line package (DIP). The LCC is comprised of the cavity and seal ring section of a standard DIP and offers the user a means of achieving high density system configurations while retaining the reliability benefits of hermetic IC Packaging. Figure 1 provides a comparison of the construction of an LCC and a conventional side-braze DIP.

FIGURE 1. EXPLODED VIEW OF CHIP CARRIER AND DIP

The LCC's two principle advantages over conventional side-braze DIPs are packaging density and electrical performance. Packaging density is the number one advantage to an LCC over a side-braze DIP. The size of a DIP is governed primarily by the number of leads required and not by the size of the IC. As pin count increases, more and more of the DIP package is used only to provide an electrical trace path to the external leads. The size of an LCC is dependent on the size of the die not on the number of leads. As pin count increases, overall size increases but at a much slower rate. Table 1 provides a comparison between the areas of 18, 28 and 48 lead LCCs to 18, 28 and 48 lead side-braze DIPs.

|               | IA          | DLC I.      |                          |

|---------------|-------------|-------------|--------------------------|

| LEAD<br>COUNT | LCC<br>AREA | DIP<br>AREA | DIP AREA vs.<br>LCC AREA |

| 18            | 0.10        | 0.22        | 220%                     |

| 28            | 0.20        | 0.84        | 420%                     |

| 48            | 0.31        | 168         | 542%                     |

(All Units in Square Inches)

The chart indicates a 220% improvement in packaging area for the 18 lead LCC, and 542% improvement for the 48 lead LCC. Obviously, sizeable savings in circuit board area can be achieved with this packaging option. The second major advantage of the LCC is in electrical performance. The package size and geometry also dictates trace length and uniformity. Figure 2 provides a comparison between the trace lengths for various LCCs and side-braze DIPs. As pin count goes up, trace lengths get longer, adding resistance and capacitance unequally around the package. As ICs get faster and more complex these factors start to become a limiting factor on performance. LCCs minimize this effect by maintaining, as close as possible, uniform trace length so that the package is a significantly smaller determinant of system performance.

| LEAD<br>COUNT | LONGEST TRACE DIP<br>LONGEST TRACE LCC | LONGES<br>SHORTES |     |

|---------------|----------------------------------------|-------------------|-----|

|               |                                        | LCC               | DIP |

| 18            | 2:1                                    | 1.5:1             | 6:1 |

| 24            | 4:1                                    | 1.5:1             | 3:1 |

| 40            | 5:1                                    | 1.5:1             | 6:1 |

| 54            | 6:1                                    | 1.5:1             | 7:1 |

The LCC also offers environmental advantages over "chip-and-wire" manufacturing techniques used in high density hybrid circuits. An IC can be fully tested, burned-in and processed in an LCC, thereby guaranteeing its performance.

The IC is further protected by a small hermetic package in which internal vapor content can be carefully controlled during production.

Harris Semiconductor Leadless Chip Carriers in both Ceramic and Epoxy provide reliable, high density, high performance packaging options for today's systems.

Consult the factory or your Harris sales representative for pricing and availability.

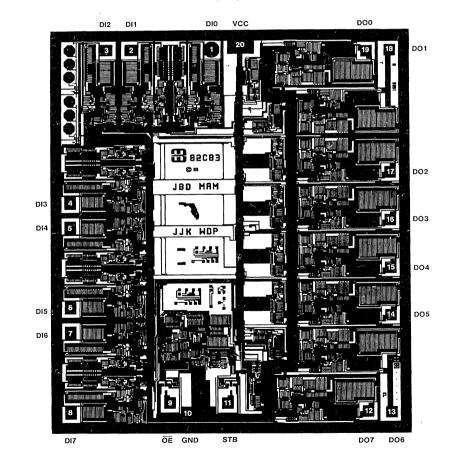

#### Self Aligned Junction Isolation (SAJI)

The most prevalent CMOS Technology was patented by Harris (#4,135,955) and has been in production at Harris since 1980. It incorporates self-aligned guard ring techniques and more recently planarization prior to first metal into the traditional complementary transistor structures.

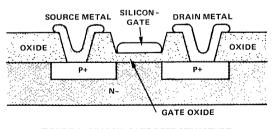

The process begins on 1–0–0 N– type silicon, although a process option is available with N epi over N++ starting material to eliminate circuit latch-up due to parasitic SCR action. A sequence of oxidation, photo resist delineation, Boron implant and diffusion create the P well for the N channel devices. A critical feature of the diffusion causes all of the silicon crystal defects to be annihilated, resulting in a defect free zone for the transistors to be fabricated.

Next, silicon nitride is deposited and etched to define the active NMOS and PMOS areas followed by implants which create the self aligned guard rings around the active devices. These guard rings provide electrical isolation between transistors and also raise the field thresholds of the parasitic MOS devices to allow leakage-free circuit operation. The self aligning of these guard rings allows a substantial reduction in circuit area.

Following is the local oxidation and the conventional formation of the poly gate MOS transistors. The electrical channel length of these all implanted devices is 1.5 micron.

The field oxide and metalization structure are based on a time proved reflowed glass process with one important improvement. Prior to metal deposition the surface is planarized and the walls of the contacts are sloped which creates a final topography with excellent interconnect step coverage. The aluminum interconnect is silicon doped to prevent contact spiking and improved reliability. The passivation, metalization and layout rules guarantee electromigration free operation at +125°C for over ten years.

The principal advantages of the process can be summarized as: • Low leakage operation

- Latch-up free option

- Good packing density

- Excellent step coverage

- Electromigration free designs

This process has been successfully applied to numerous designs including static RAMs, microprocessors, peripherals, and custom ROM circuits.

L7

A newer, higher performance process, named L7, builds on and enhances the basic CMOS technology. This 1.5 micron process has several advantages over the older 2.5 micron version. The epi over N++ starting material is standard with the epi thickness being scaled down in concert with the P well and device junctions. This brings even more latch-up immunity to all circuits on this technology.

Transistors achieve electrical channel lengths of  $1.0\mu$  typical with the N channel incorporating a double diffused LDD structure which eliminates susceptibility to hot electron damage. Of greatest impact is the use of a planarized double layer metal structure allowing greater layout freedom without introducing step coverage or electromigration concerns. The low stress oxinitride passivation provides moisture protection in plastic packages.

The L7 process with its added features has been successfully employed on numerous semicustom and standard cell designs as well as supplying production quantities of the 80C286 microprocessor.

FIGURE 3. SILICON-GATE PFET STRUCTURE CROSS-SECTION SHOWS THE HEAVILY DOPED SOURCE AND DRAIN REGION. THEY ARE SEPARATED BY THE NARROW GAP OVER WHICH LIES A THIN-GATE OXIDE AND GATE MATERIAL.

1-5

# IC Handling Procedures -

Harris Digital IC processes are designed to produce the most rugged products on the market. However, no semiconductor is immune from damage resulting from the sudden application of many thousands of volts of static electricity. While the phenomenon of catastrophic failure of devices containing MOS transistors or capacitors is well known, even bipolar circuits can be damaged by static discharge, with altered electrical properties and diminished reliability. None of the common IC internal protection networks operate quickly enough to positively prevent damage.

It is suggested that all semiconductors be handled, tested, and installed using standard "MOS handling techniques" of proper grounding of personnel and equipment. Parts and subassemblies should not be in contact with untreated plastic bags or wrapping material. High impedance IC inputs wired to a P.C. connector should have a path to ground on the card.

#### Handling Rules

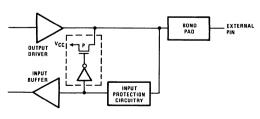

Since the introduction of integrated circuits with MOS structures and high quality junctions, a safe and effective means of handling these devices has been of primary importance. One method employed to protect gate oxide structures is to incorporate input protection diodes directly on the monolithic chip. However, there is no completely foolproof system of chip input protection in existence in the industry. In addition, most compensation networks in linear circuits are located at high impedance nodes, where protection networks would disturb normal circuit operation. If static discharge occurs at sufficient magnitude (2kV or more), some damage or degradation will usually occur. It has been found that handling equipment and personnel can generate static potentials in excess of 10kV in a low humidity environment. Thus it becomes necessary for additional measures to be implemented to eliminate or reduce static charge. It is evident, therefore, that proper handling procedures or rules should be adopted.

Elimination or reduction of static charge can be accomplished as follows:

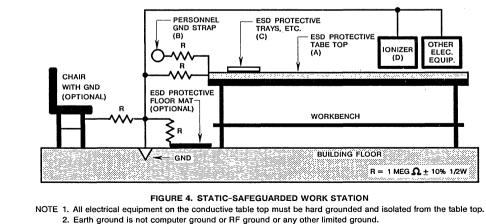

- Use static-free work stations. Static-dissipative mats on work benches and floor, connected to common point ground through a  $1M\Omega$  resistor, help eliminate static build-up and discharge. Do not use metallic surfaces.

- Ground all handling equipment.

- Ground all handling personnel with a conductive bracelet through 1MΩ to ground (the 1MΩ resistor will prevent electroshock injury to personnel). Transient product personnel should wear grounding heel straps when conductive flooring is present.

- Smocks and clothing of certain insulating materials (notably nylon) should not be worn in areas where devices are handled. These materials, highly dielectric in nature, will hold, or aid in the generation of a static charge. Where they cannot be eliminated, natural materials such as cotton should be used to minimize charge generation capacity. Conductive smocks are also available as an alternative.

- Control relative humidity to as high a level as practical. 50% is generally considered sufficient. (Operations should cease if R.H. falls below 25%).

- lonized air blowers reduce charge build-up in areas where grounding is not possible or practical.

- Devices should be in conductive static-shielded containers during all phases of transport. Leads may be shorted by tubular metallic carriers, conductive foam, or foil.

- In automated handling equipment, the belts, chutes, or other surfaces should be of conducting non-metal material. If this is not possible, ionized air blowers or ionizing bars may be a good alternative.

# ESD Handling Procedures

Harris has developed a static control program that enables employees to detect problems generated by static electricity whether on site, in transit, or in the field. Controlling the requirements, methods, materials, and training for static protection of our products is ongoing and updated with new developments in electrostatic prevention. Harris has responded with controls and procedures as part of daily operations to be followed in all areas.

The challenge is to insure all electrostatic control procedures are followed throughout the system — from manufacturing through end use. Unprotected integrated circuits can be destroyed or functionally altered by merely passing them through the electrostatic field of something as simple as styrofoam<sup>™</sup> or human contact.

#### Measures of Protection and Prevention

When handling static sensitive devices, three standard procedures must be followed:

- Prior to any handling of static-sensitive components, the individual must be properly grounded.

- 2. All static-sensitive components must be handled at static safeguarded work stations.

- 3. Containers and packing materials that are staticprotective must be used when transporting all static-sensitive components.

Special handling equipment (static-safeguarded work stations, conductive wrist straps, static-protected packaging, ionized air blowers) should be used to reduce damaging effects of electrostatic fields and charges.

Static-safeguarded work station is an area that is free from all damaging electricity, including people. To accomplish this, static on conductors and nonconductors must be controlled. Controlling electrically conductive items can be accomplished by bonding and grounding techniques. The human body is considered a conductor of electricity and is by far the greatest generator of static electricity. Personnel handling ICs must use conductive wrist straps to ground themselves. Simple body moves act like a variable capacitor, and can create static charges. In addition, conductive clothing is recommended for minimizing electrostatic build up.

Static protective packaging prevents electric field from influencing or damaging ICs. An effective staticprotective package exhibits three types of features:

- 1. Antistatic protection that prevents triboelectric or frictional charging,

- 2. Dielectric protection that insulates discharging, and

- 3. Shielding or Faraday cage protection that prevents transient field penetration.

Harris uses only packaging that exhibits all three features. Employees are required to adhere to the same static-protective packaging techiques during handling and shipment to assure device integrity is maintained.

**Ionized air blowers** aid in neutralizing charges on nonconductors such as synthetic clothing, plastics, and Styrofoam<sup>™</sup>. The blowers are placed at the work site and in close proximity to the IC handling area, since nonconductors do not lose or drain charges using normal grounding techniques.

By using wrist straps, static-protected work stations and static-protected containers, Harris product quality is maintained throughout the product cycle.

Styrofoam™ is a trademark of Dow Chemical Corporation

# Harris Product Specification Highlights

Harris Semiconductor is a leading supplier of high reliability integrated circuits to the military and aerospace community and takes pride in offering products tailored to the most demanding applications requirements. Our Manufacturing facilities are JAN-Certified to MIL-M-38510 and provide JAN-qualified and MIL-STD-883 compliant products as standard data book items. This Digital Military Products Data Book contains detailed information on high-reliability integrated circuits presently available from Harris Semiconductor.

The intent of the /883 data sheet is to provide to our customers a clear understanding of the testing being performed in conformance with MIL-STD-883 requirements. Additionally, it is our intent to provide the most effective and comprehensive testing feasible.

This data book is organized in 8 different sections, each being identified by the darkened tab index which is provided as a visual guide to the reader. Each section covers a specific topic or product line, such as CMOS Memories, CMOS Microprocessors and General Information. Section 7 emphasizes the Harris commitment to Quality and Reliability in all levels of production, test and documentation, and may be of special interest to military customers.

#### **Document Control**

Harris has established each of the /883 data sheets as an internally revision controlled document. Any product revision or modification must be approved and signed-off throughout the manufacturing and engineering sections. Harris has made every effort to ensure accuracy of the information in this data book through quality control methods. Harris reserves the right to make changes to the products contained in this data book to improve performance, reliability and producibility. Each data sheet will use the printed date as the revision control identification. Harris has also established a Data Sheet Registration Program to inform users of data sheet updates. Registration is done through the sign-up card attached to the back of this data book. Otherwise, contact Harris for the latest available specifications and performance data.

#### /883 Data Sheet Highlights

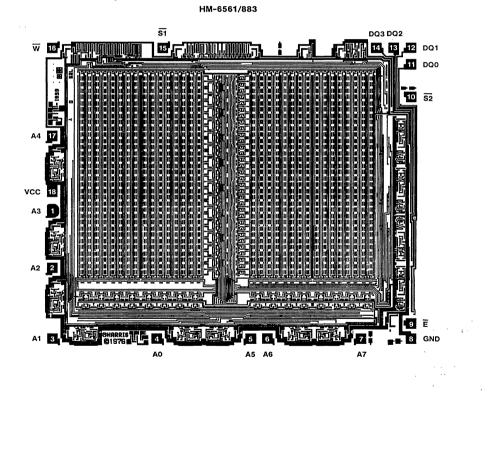

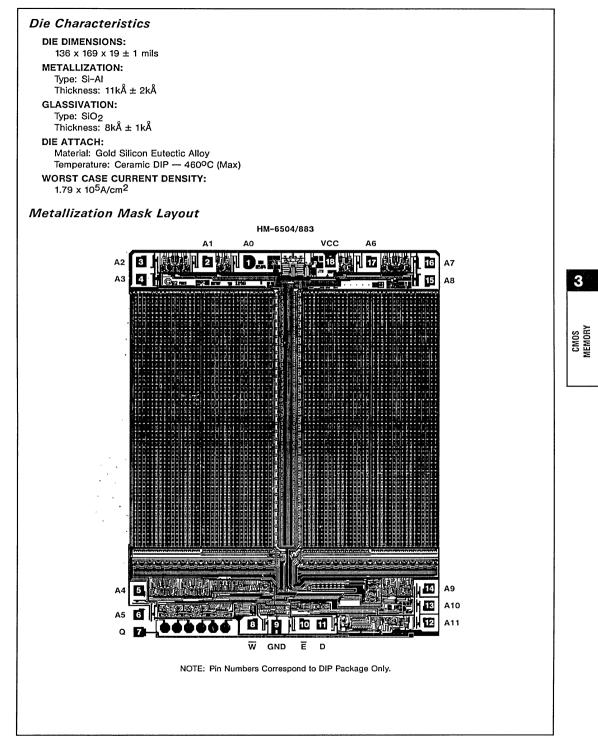

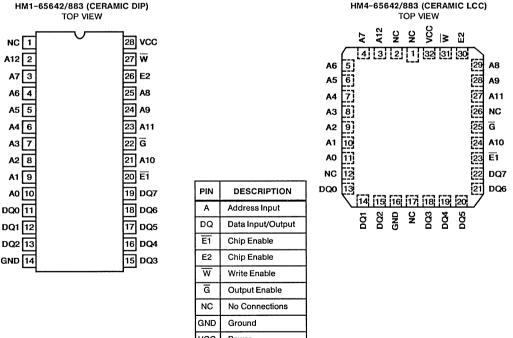

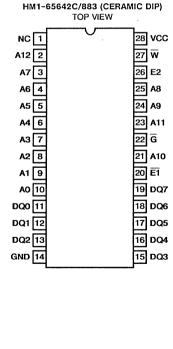

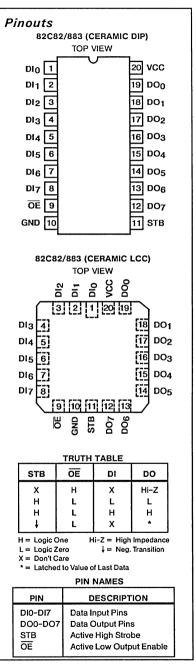

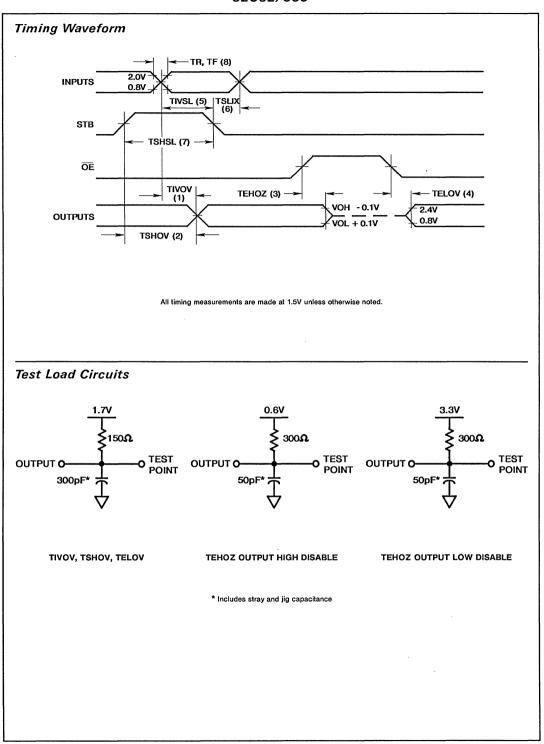

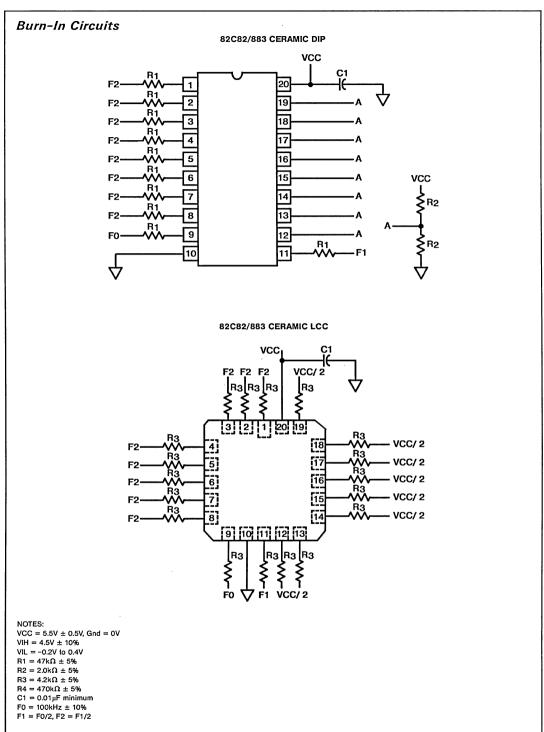

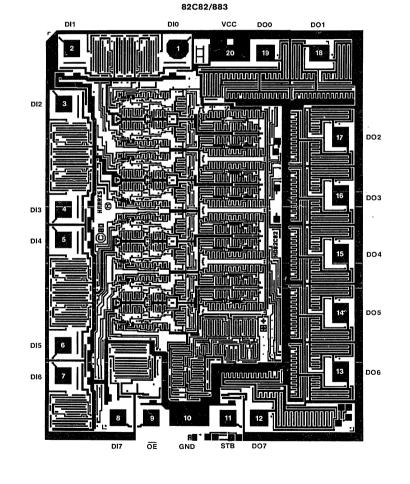

Each specific /883 data sheet documents the features, description, pinouts, tested electrical parameters, test circuits, burn-in circuits, die characteristics, packaging and design information. The following are notes and clarifications that will help in applying the information provided in the data sheet.

Absolute Maximum Ratings: These ratings are provided as maximum stress ratings and should be taken into consideration during system design to prevent conditions which may cause permanent damage to the device. Operation of the device at or above the "Absolute Maximum Ratings" is not intended, and extended exposure may affect the device reliability.

Reliability Information: Each /883 data sheet contains thermal information relating to the package and die. This information is intended to be used in system design for determining the expected device junction temperatures for overall system reliability calculations.

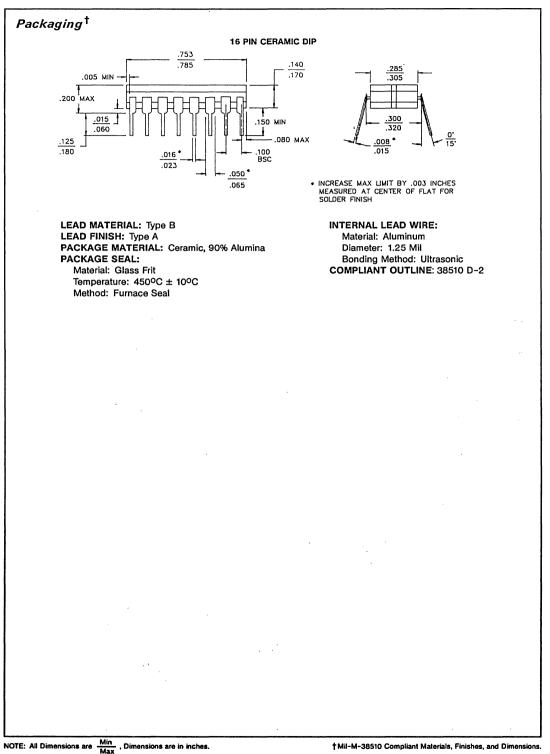

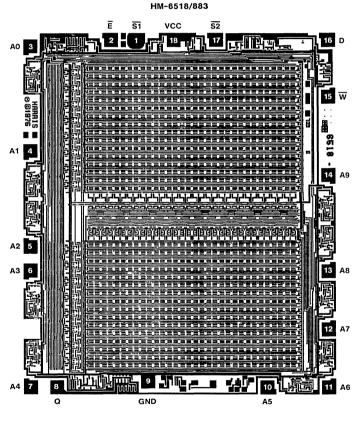

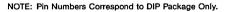

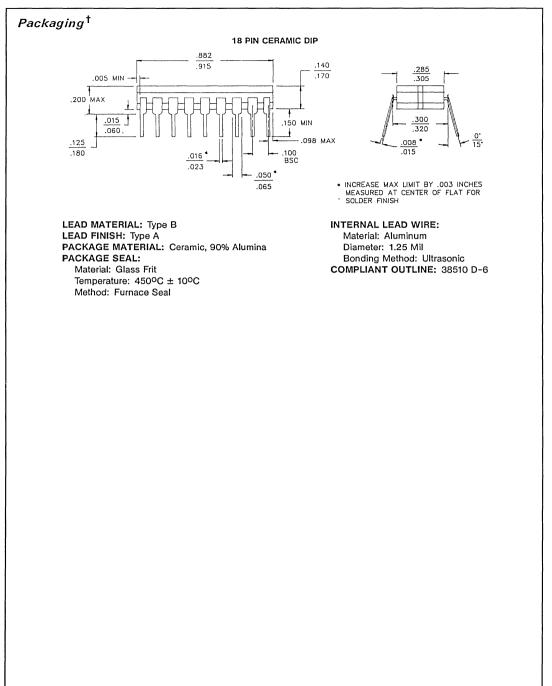

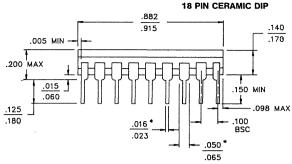

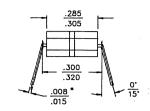

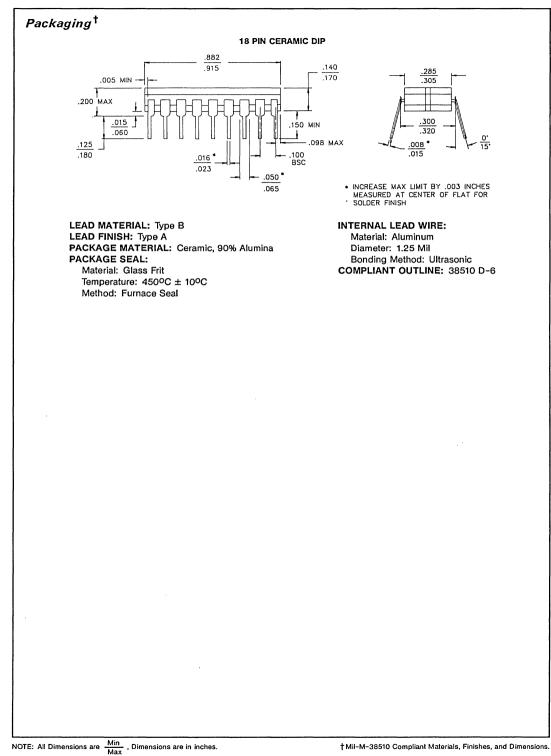

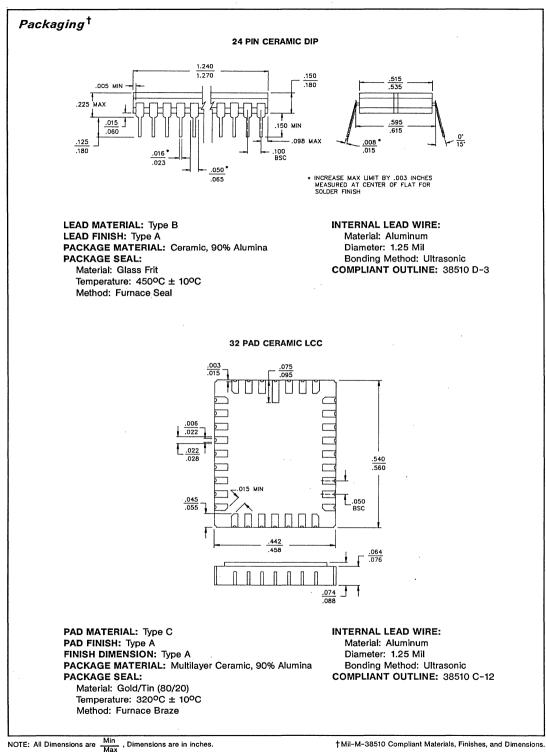

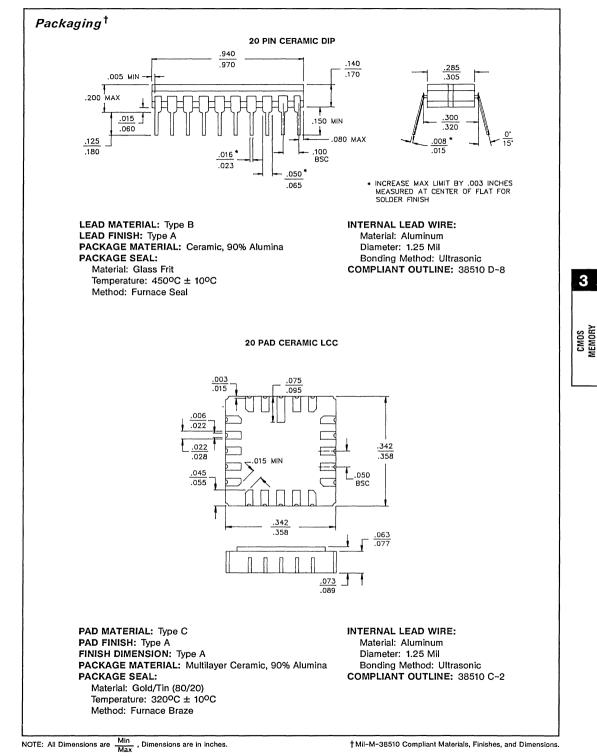

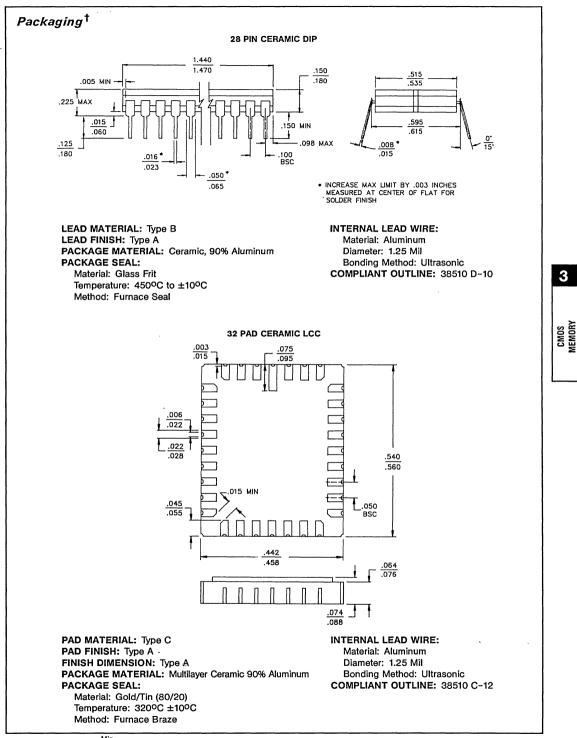

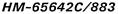

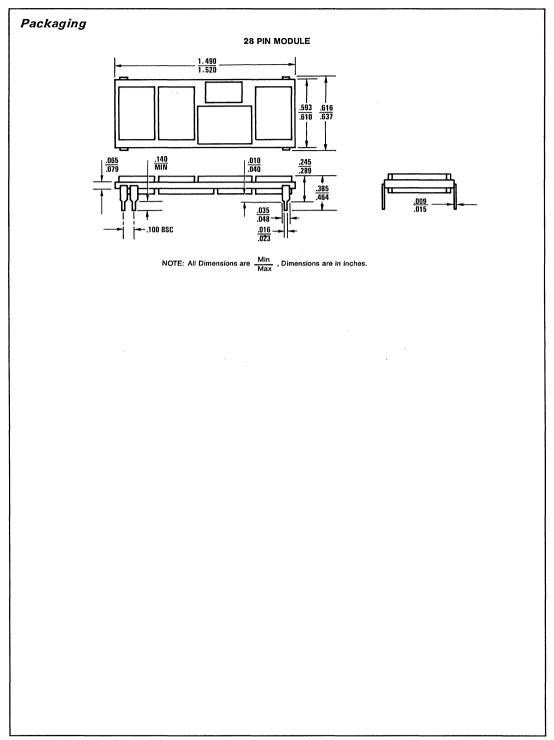

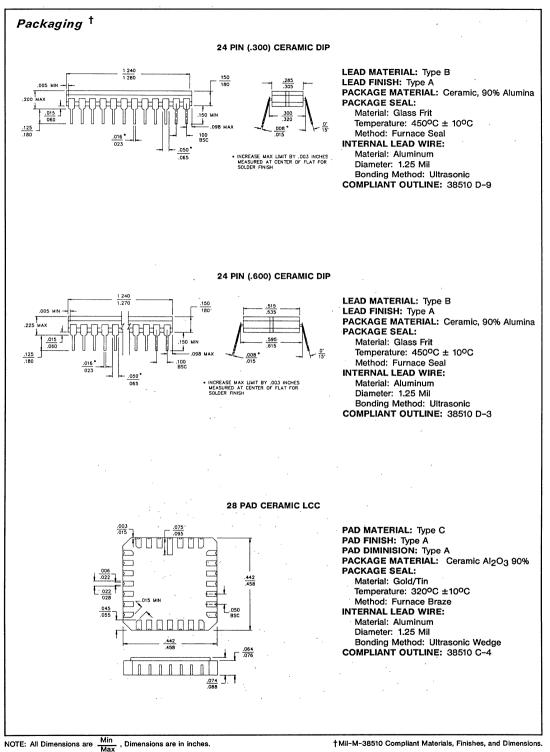

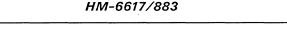

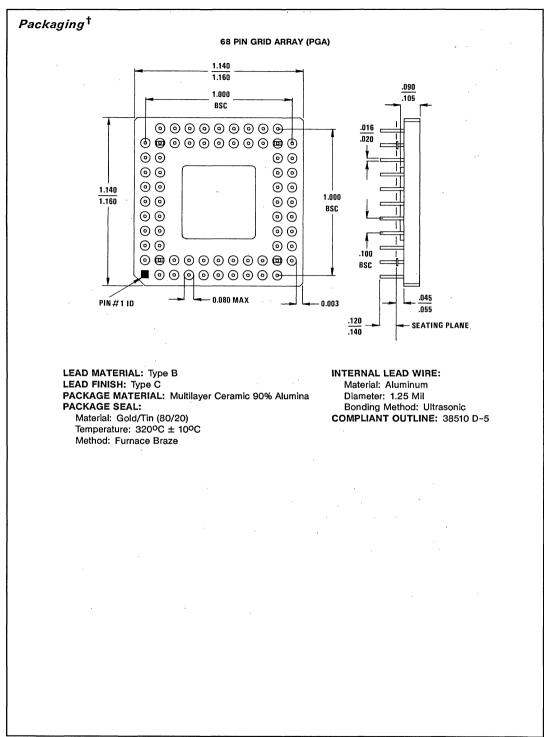

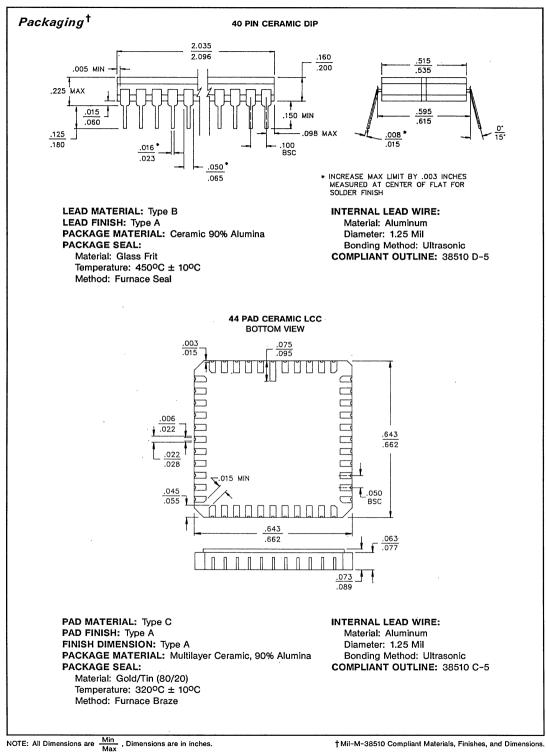

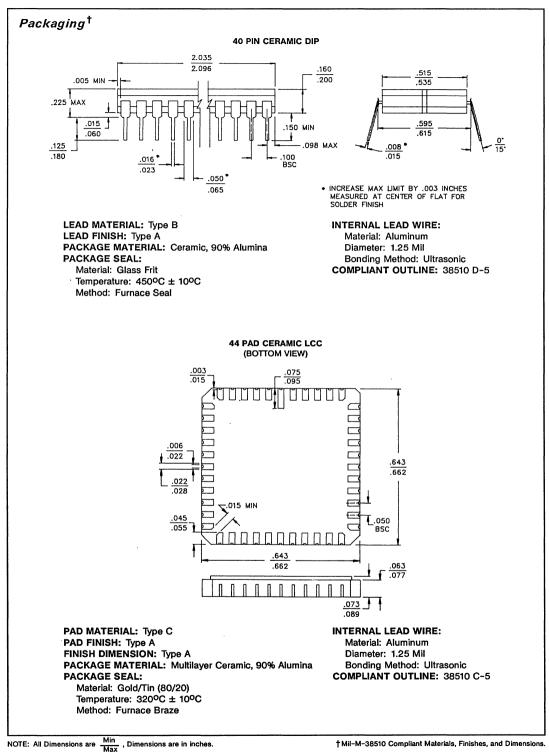

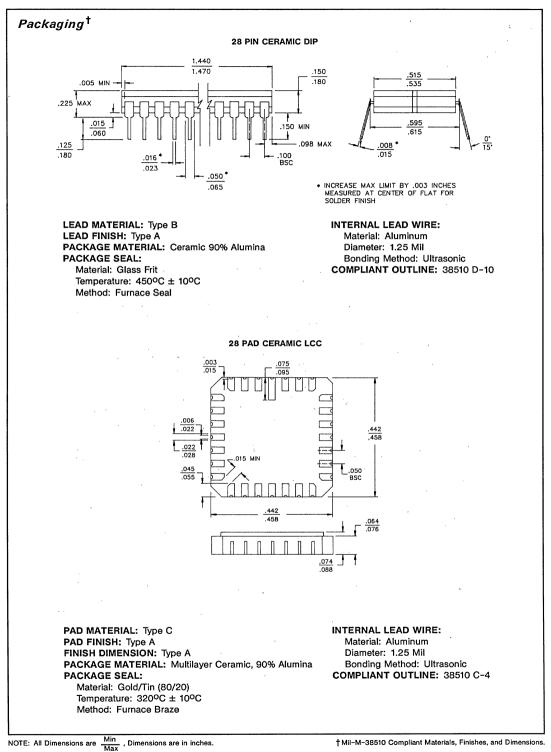

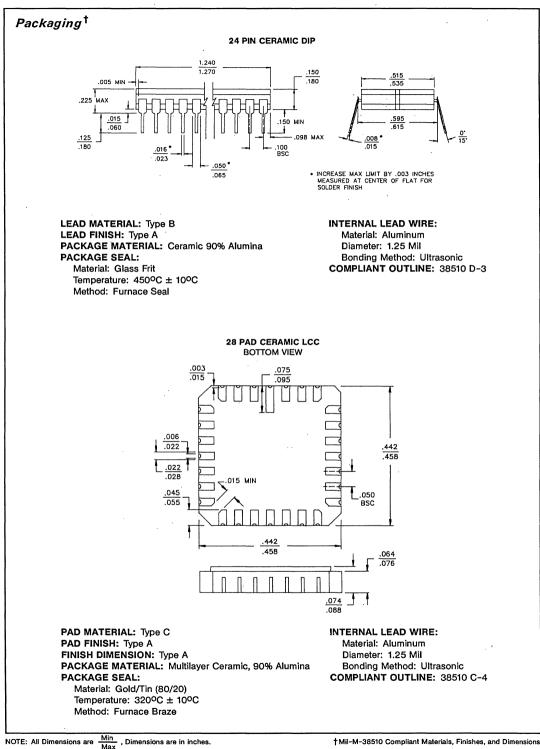

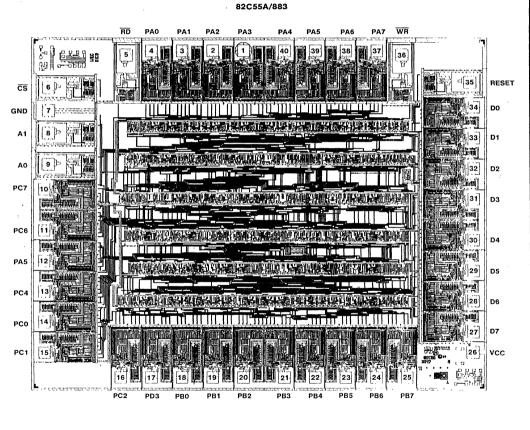

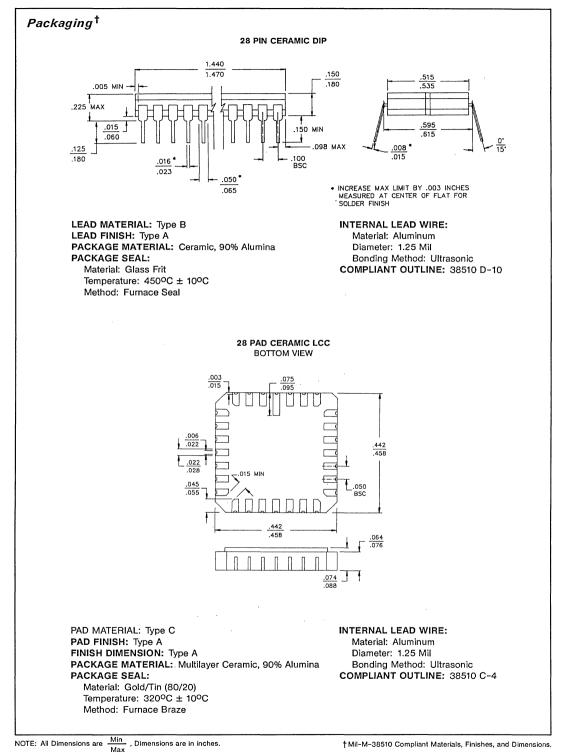

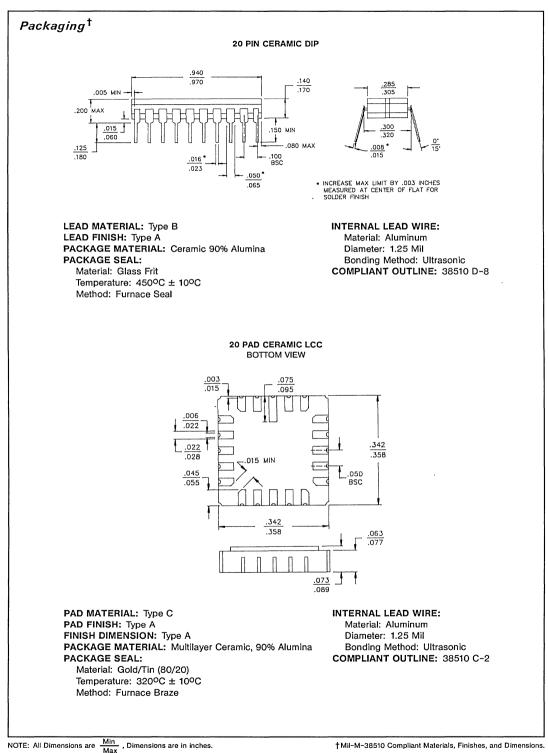

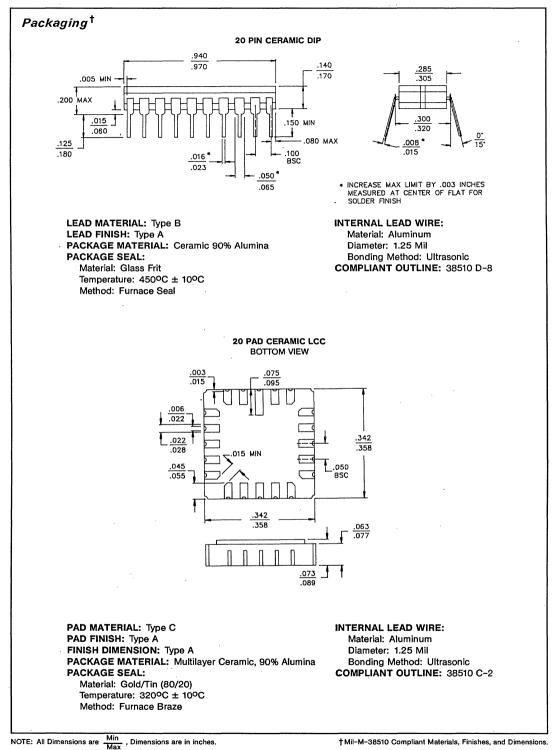

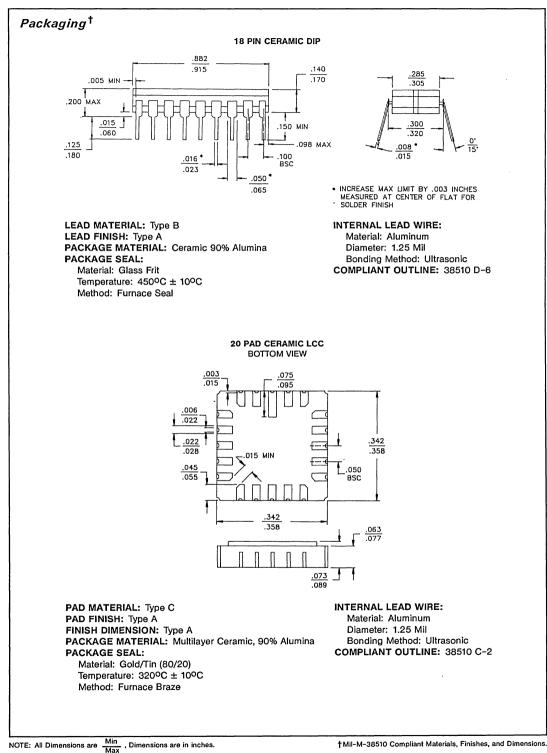

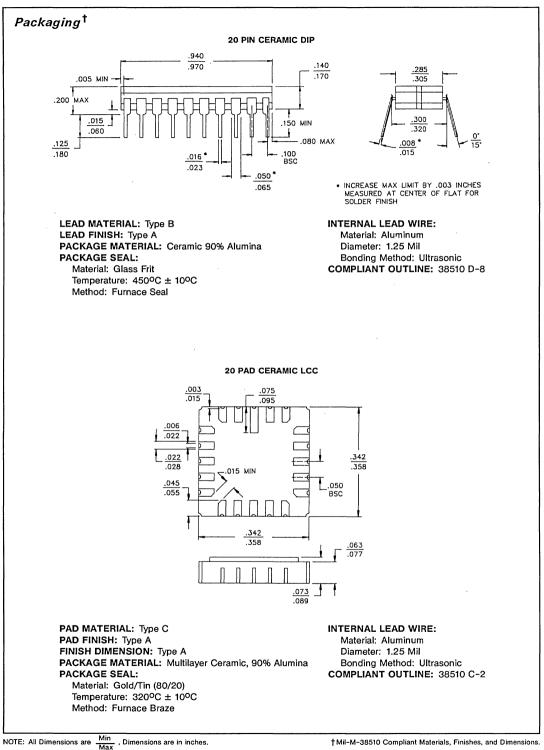

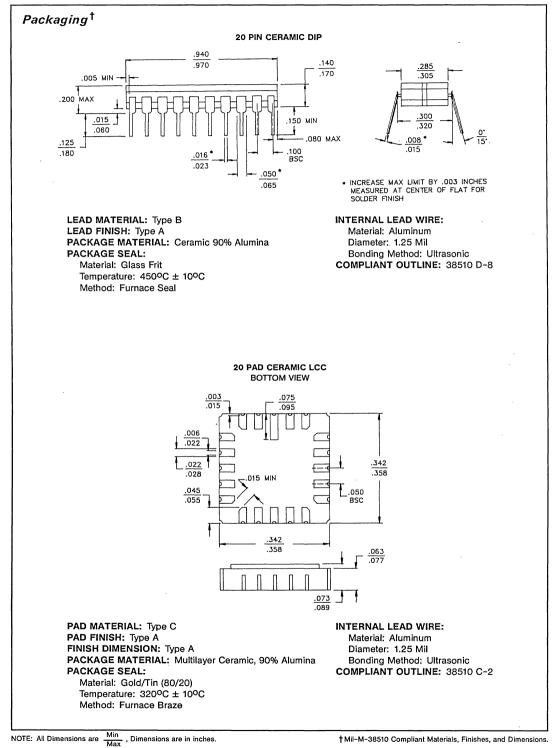

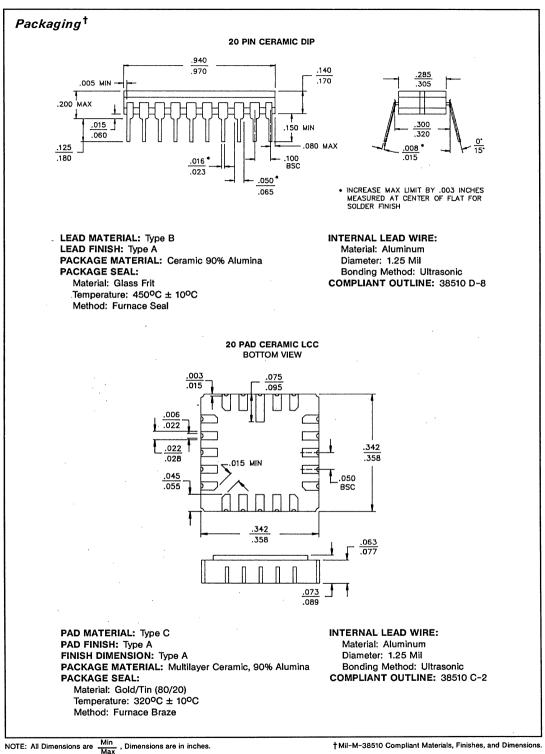

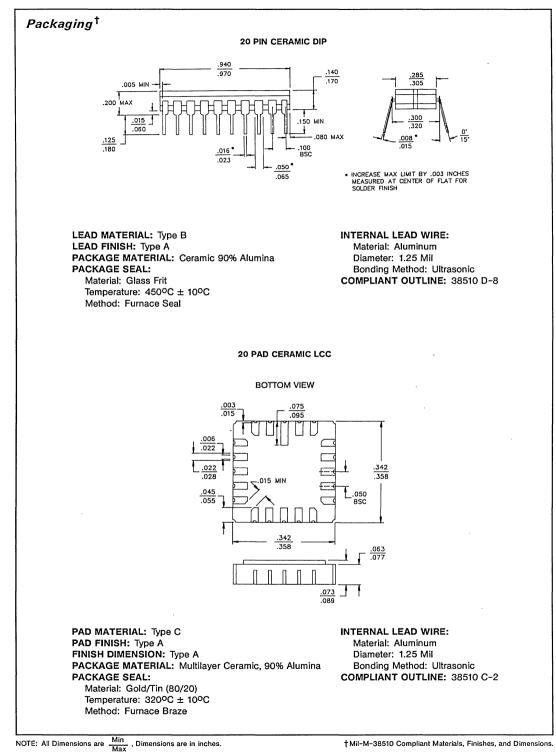

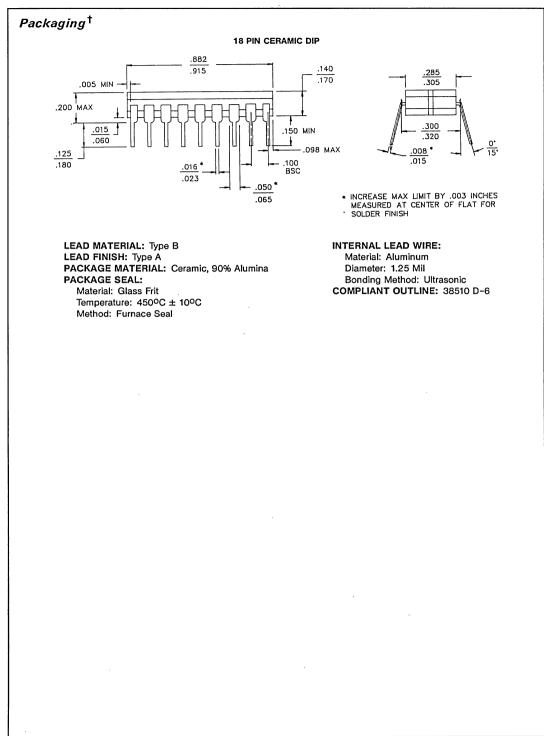

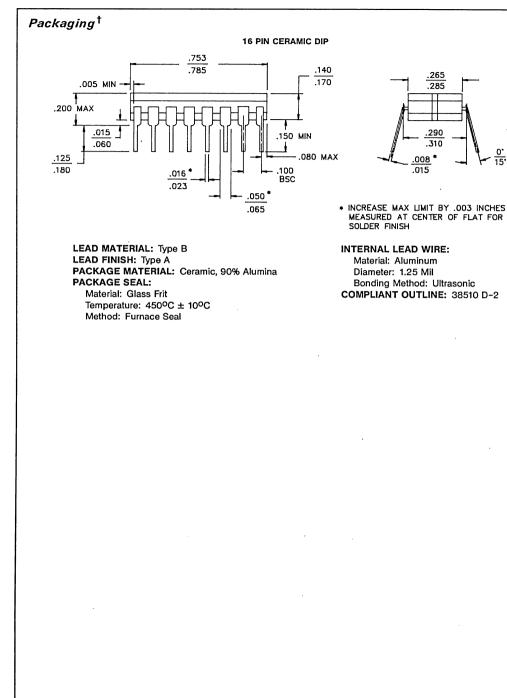

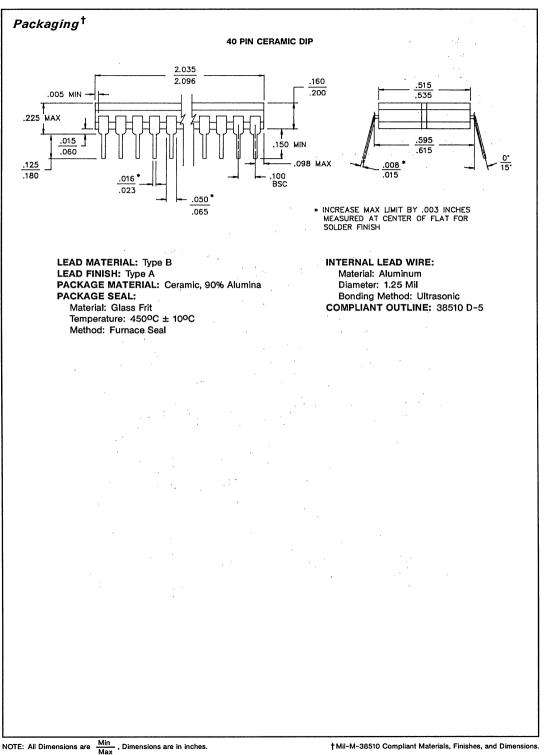

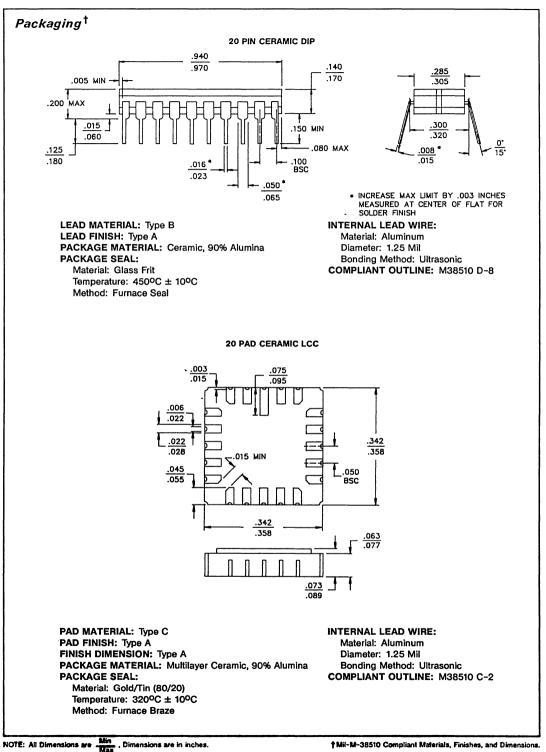

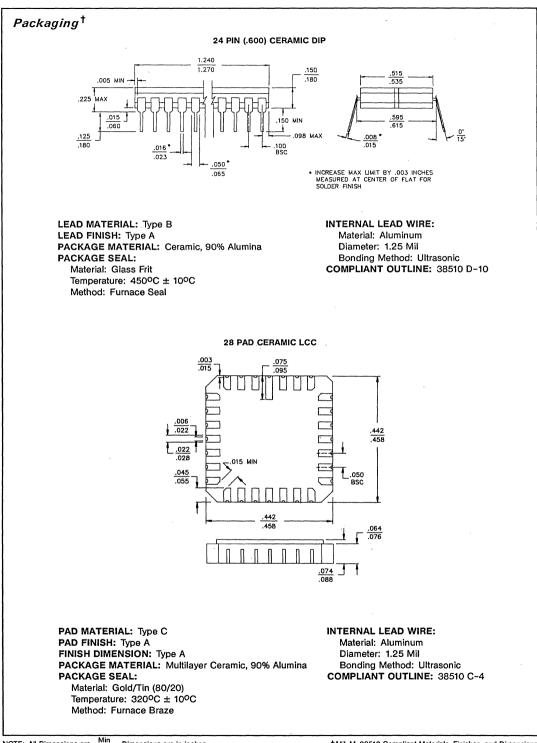

Packaging: Harris utilizes MIL-M-38510, Appendix C for packages used for /883 products. The mechanical dimensions and materials used are shown for each individual product to complete each data sheet as a self contained document.

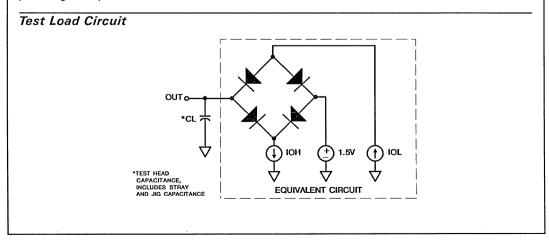

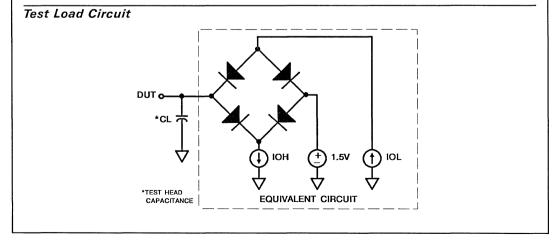

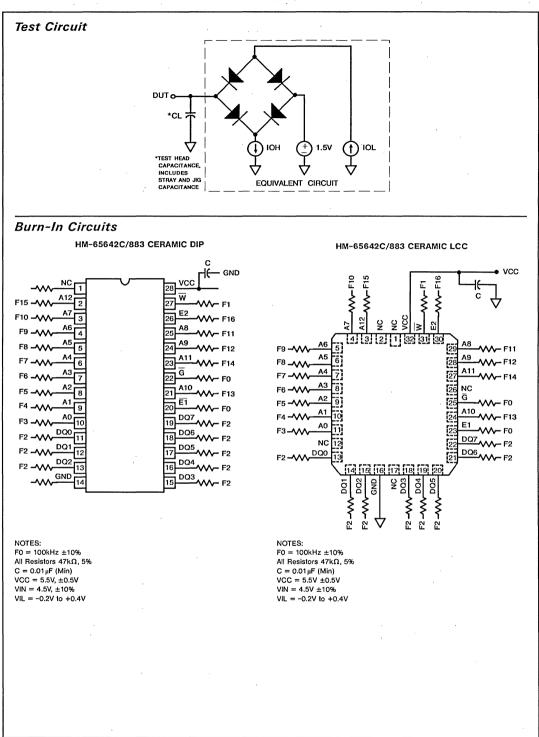

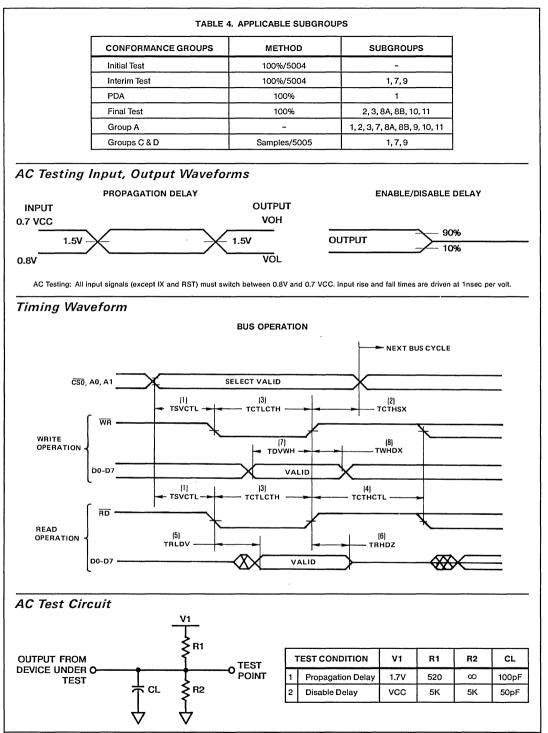

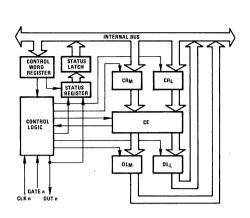

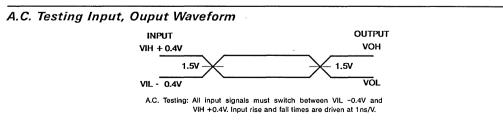

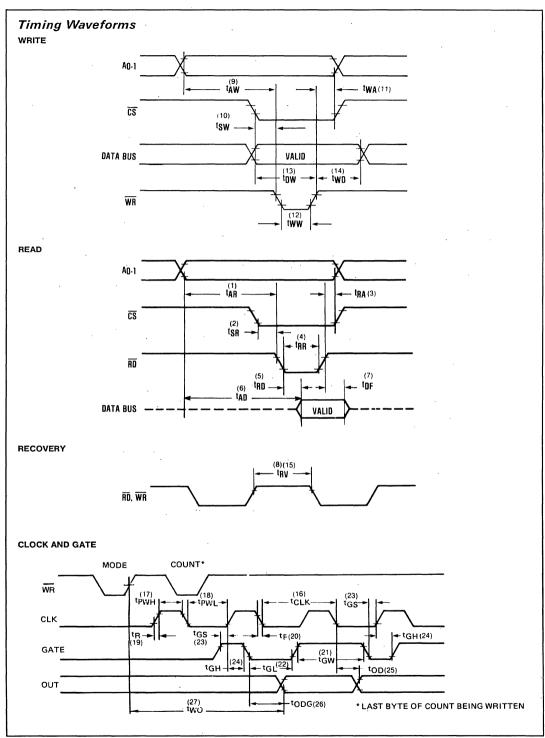

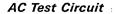

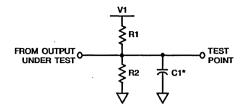

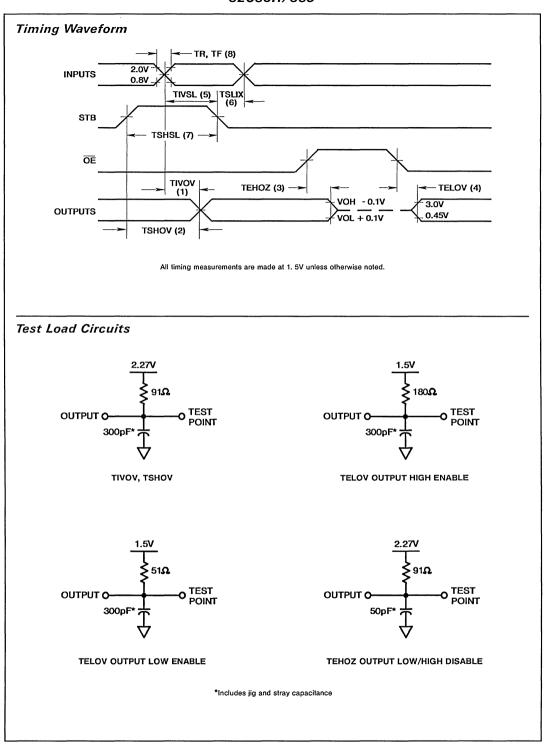

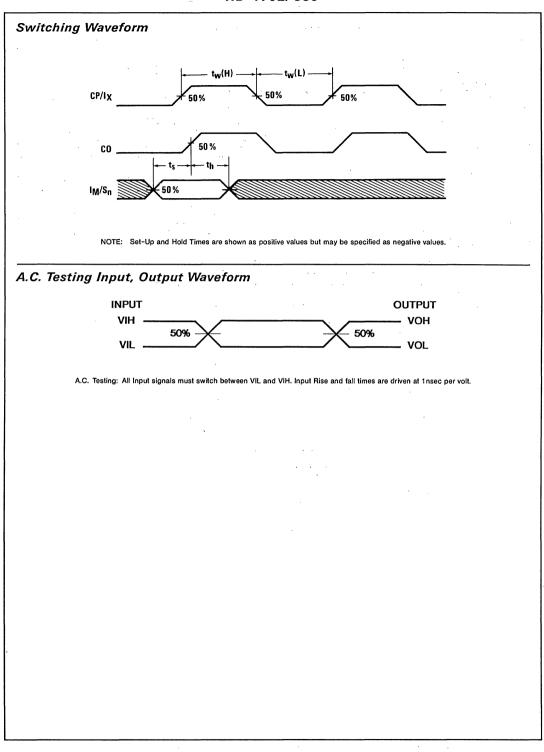

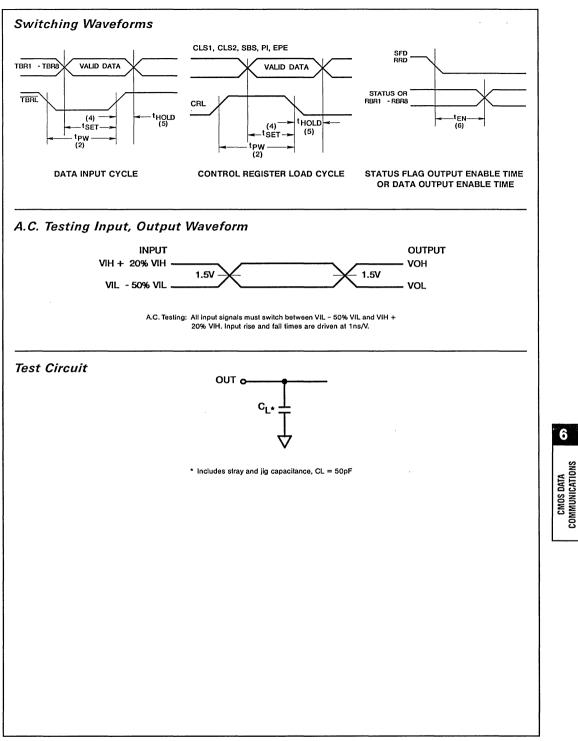

**D.C.** and **A.C.** Electrical Parameters: Tables 1 and 2 define the D.C. and A.C. Electrical Parameters that are 100% tested in production to guarantee compliance to MIL-STD-883. The subgroups used are defined in MIL-STD-883, Method 5005 and designated under the provisions of Paragraph 1.2.1a. Test Conditions and Test Circuits are provided for specific parameter testing.

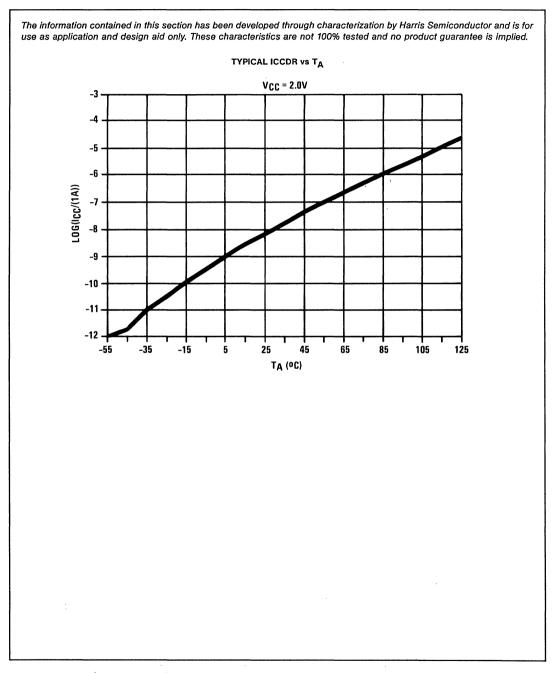

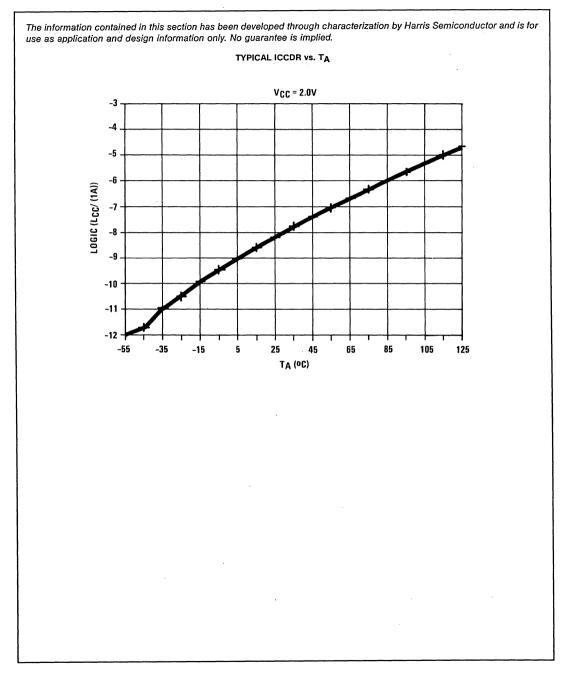

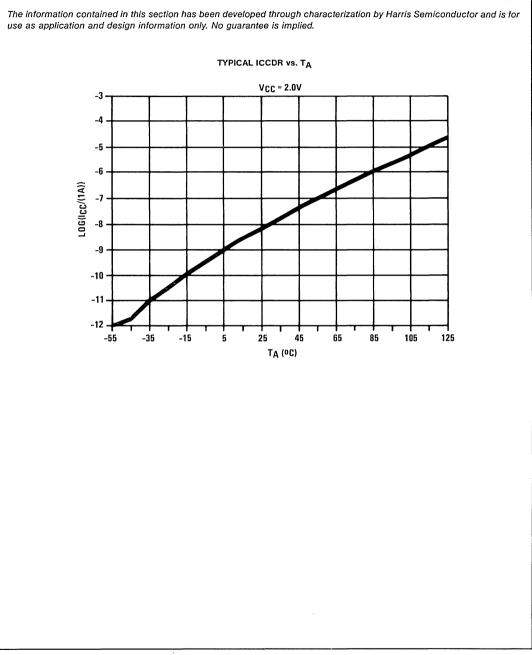

Table 3 provides additional device limits that are guaranteed by characterization of the device and are not directly tested in production. Characterization takes place at initial device design and after any major process or design changes. The characterization data is on file and available demonstrating the test limits established.

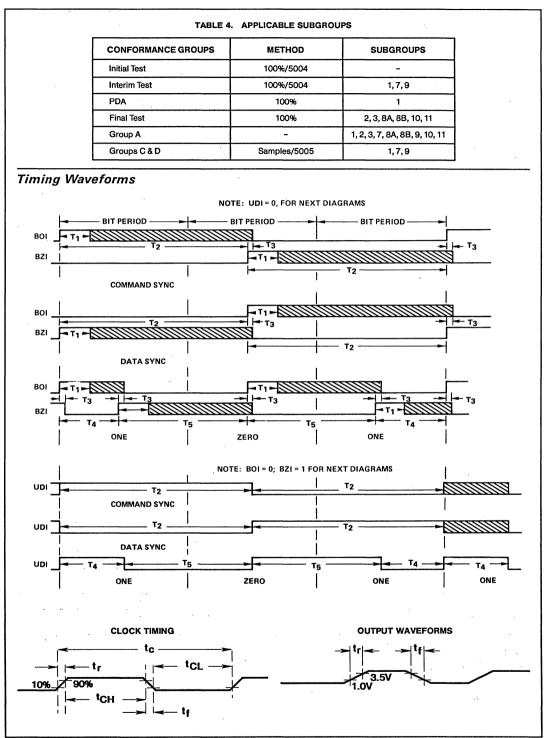

Table 4 provides a summary of the test requirements and the applicable MIL-STD-883 subgroups.

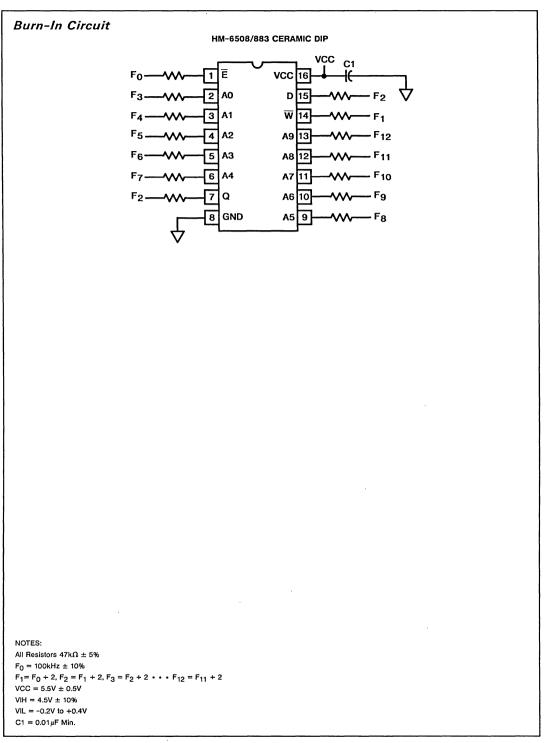

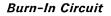

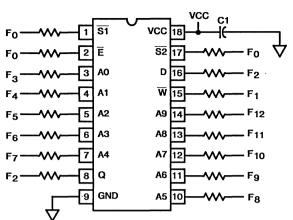

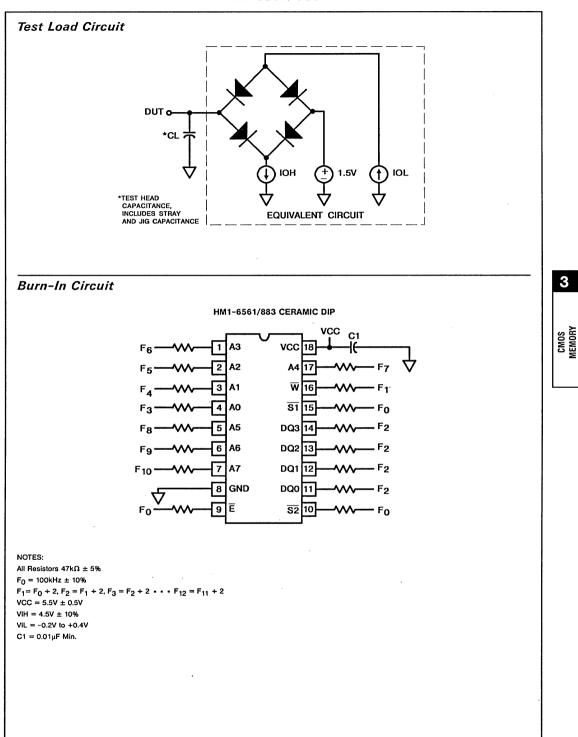

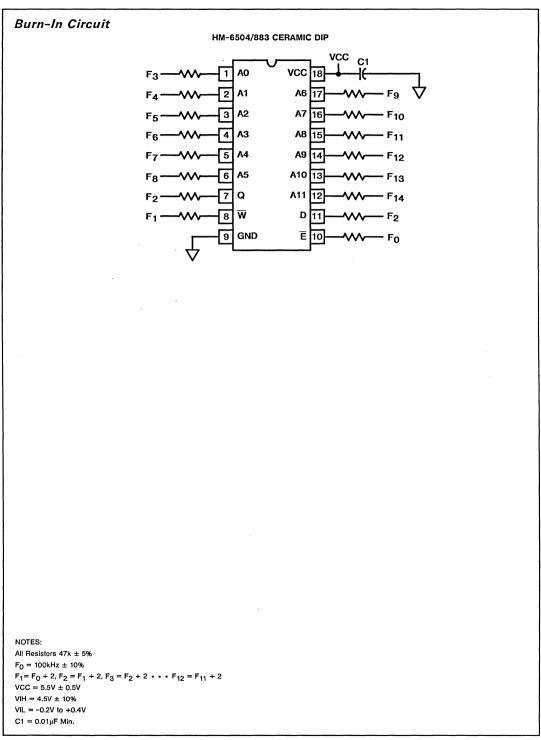

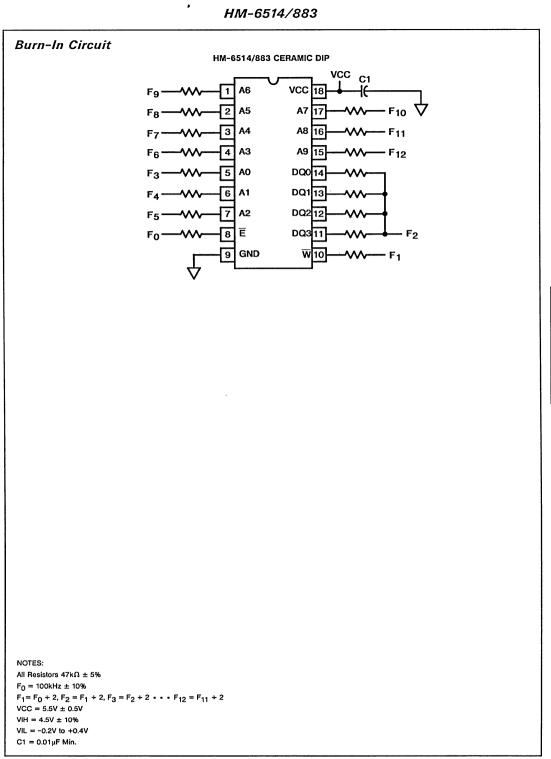

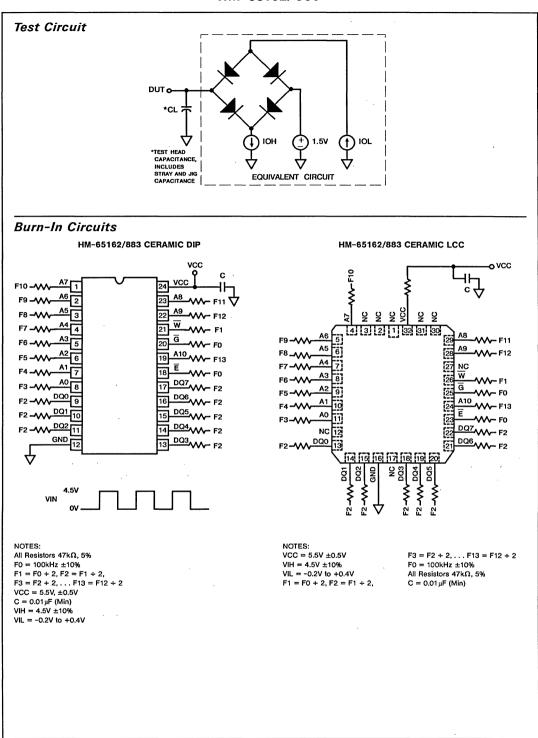

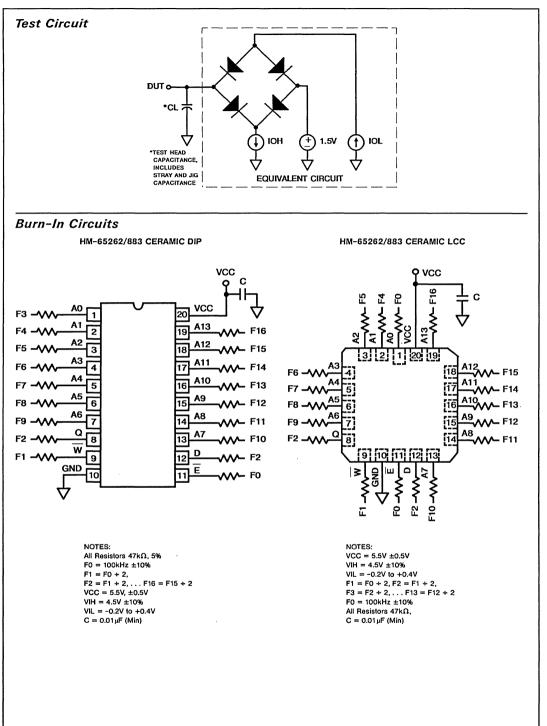

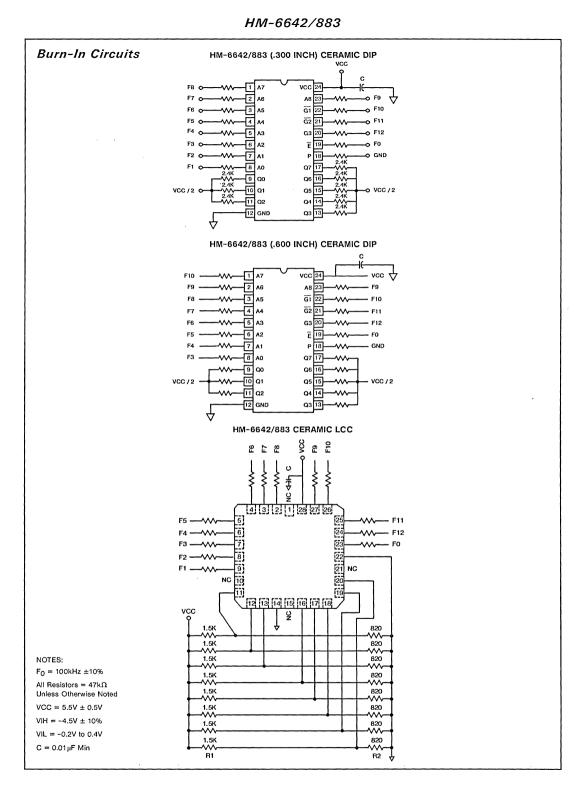

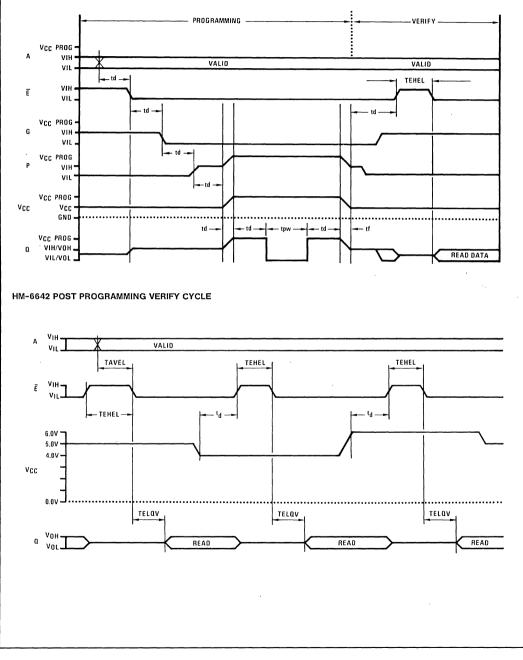

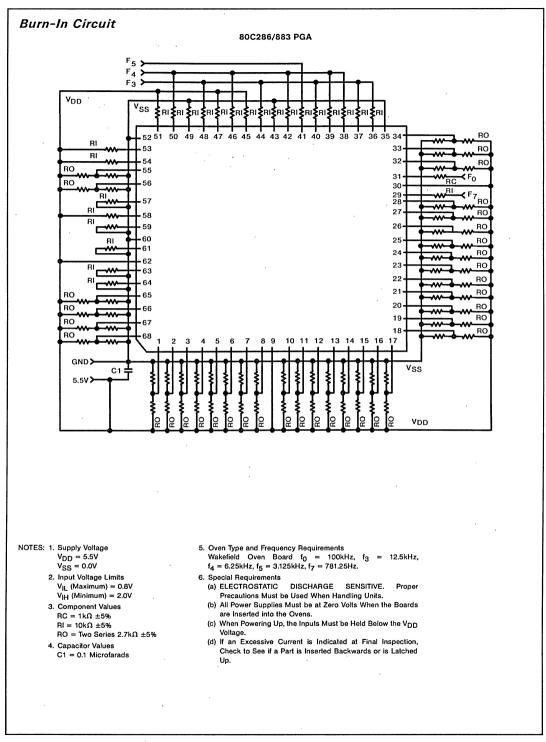

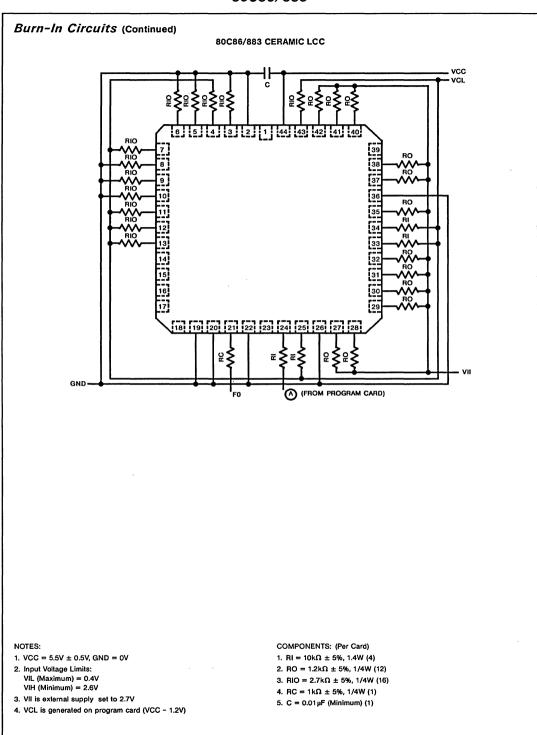

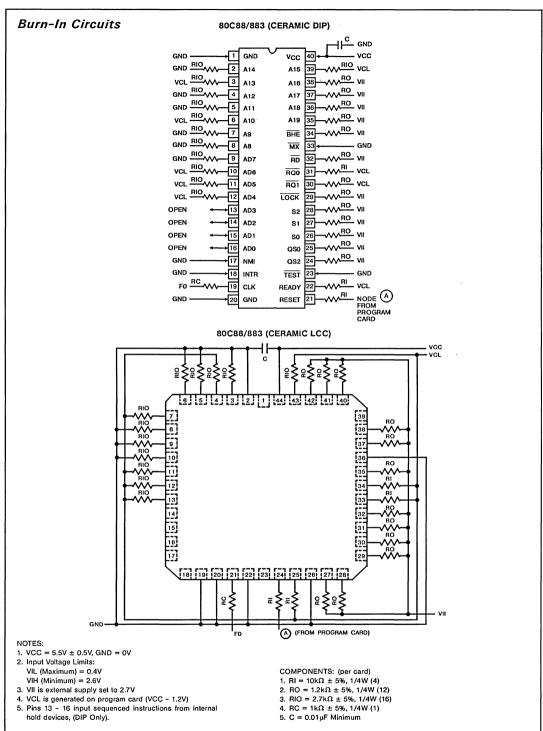

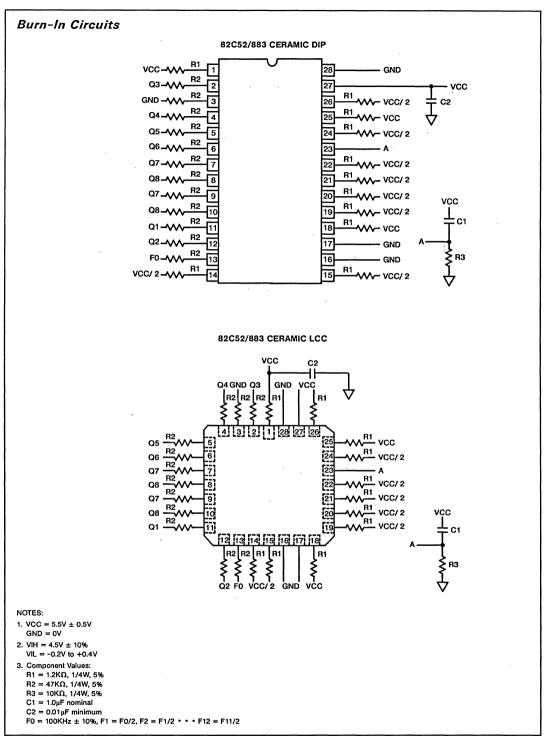

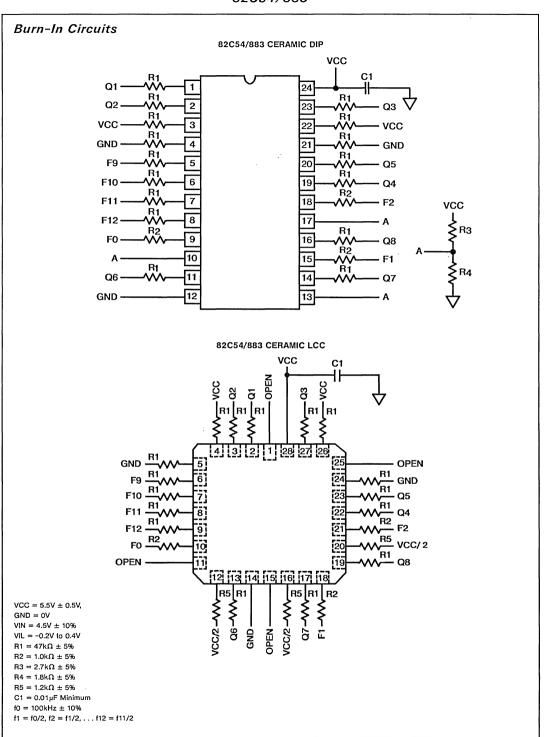

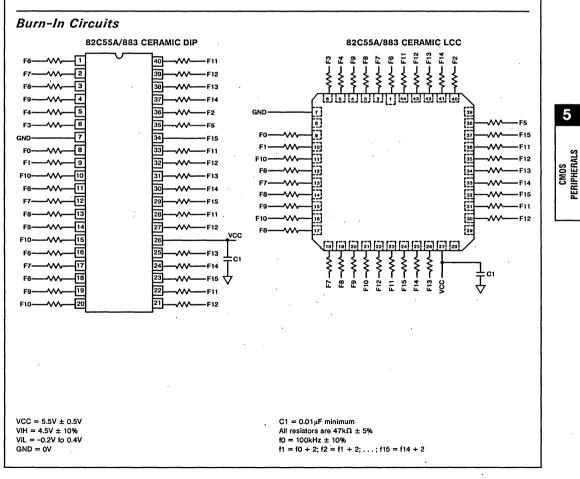

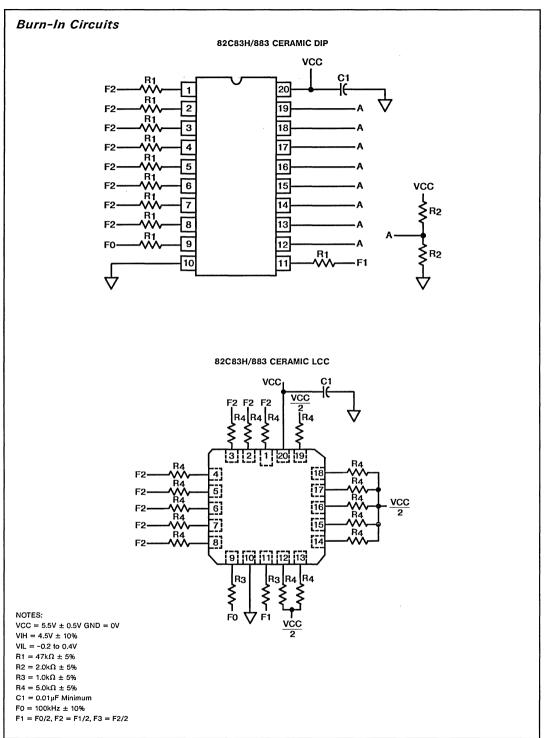

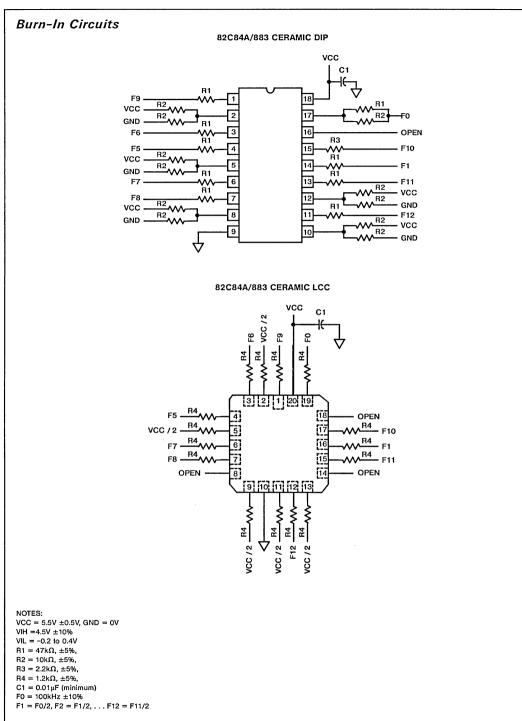

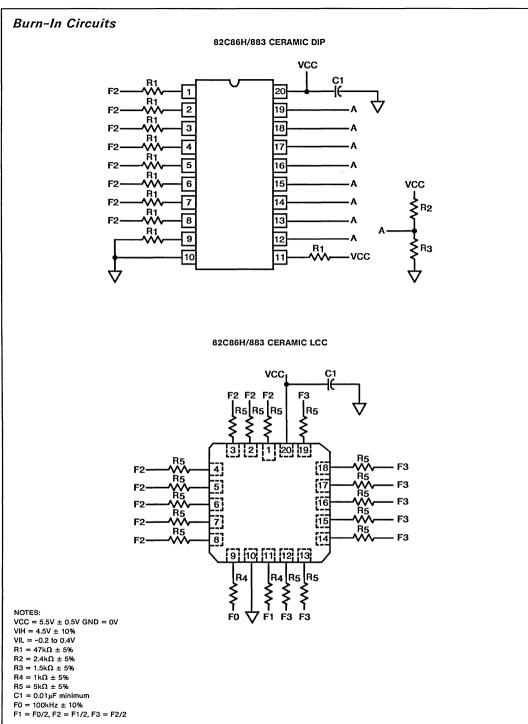

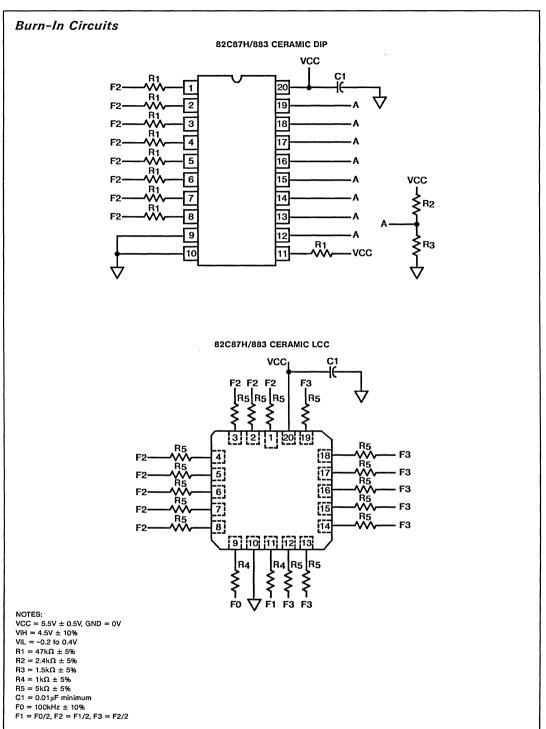

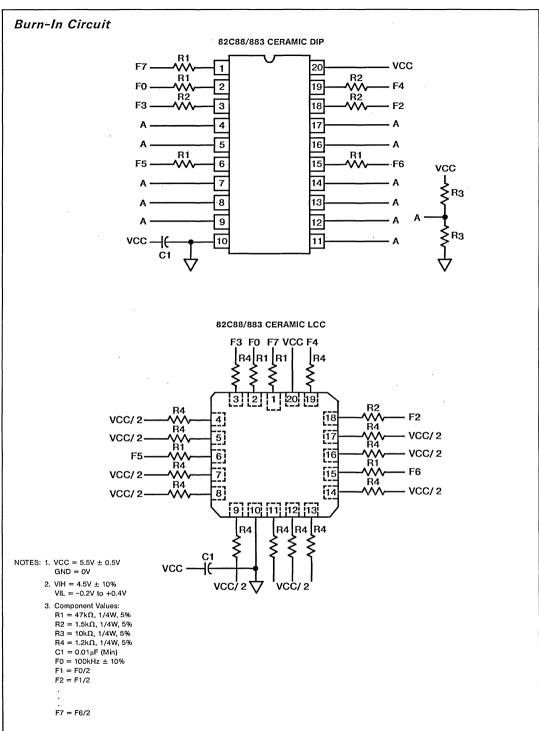

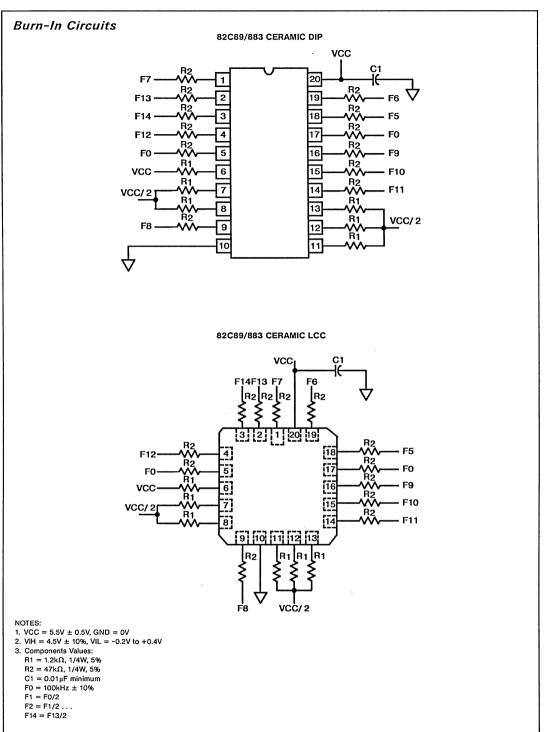

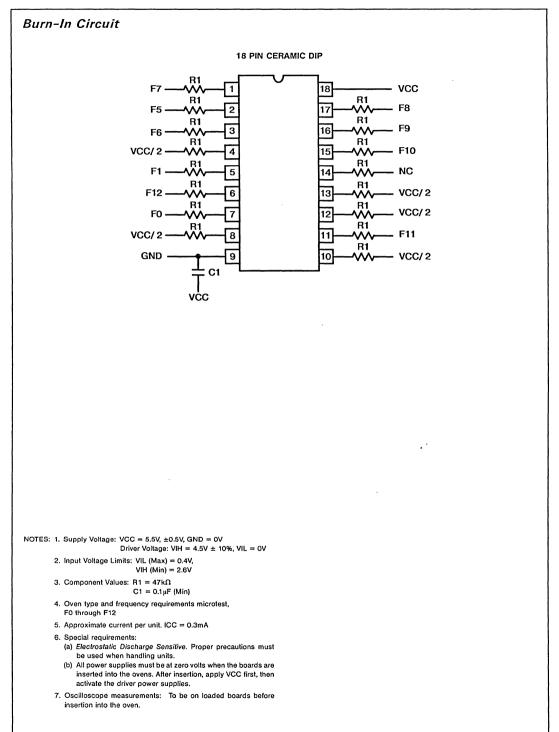

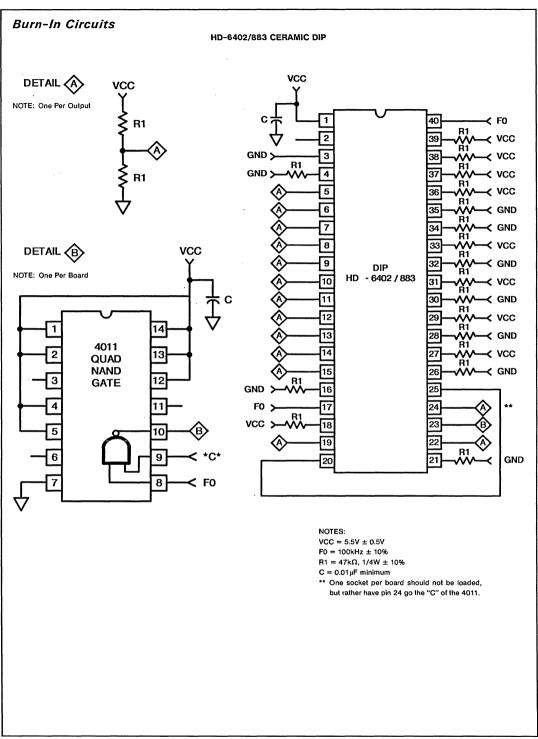

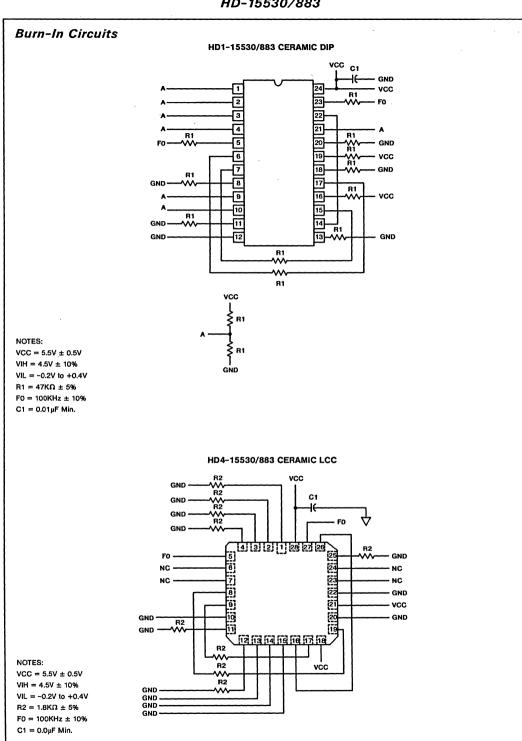

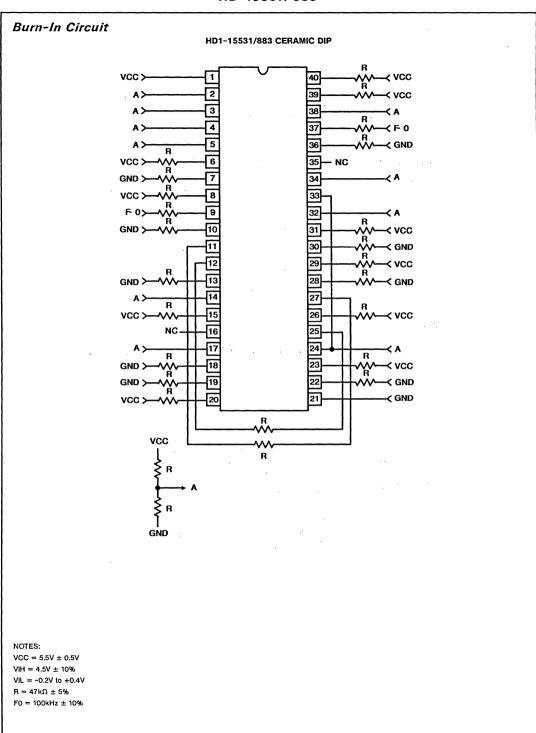

**Burn-in Circuits:** The Burn-in circuits defined in the individual data sheets are those used in the actual production process. Burn-in is conducted per MIL-STD-883, Method 1015.

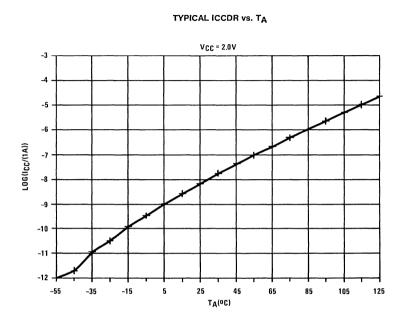

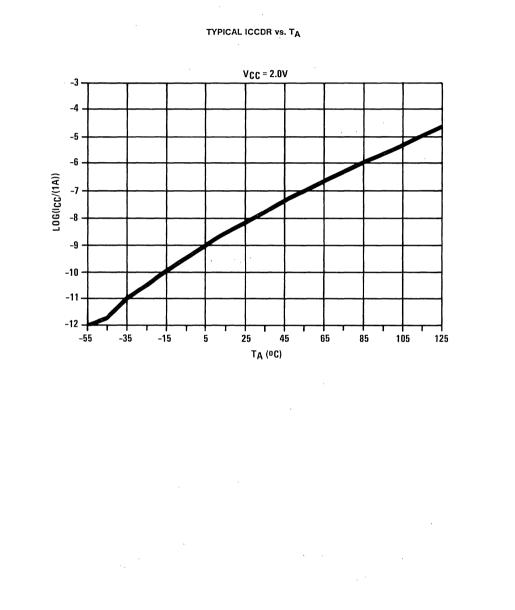

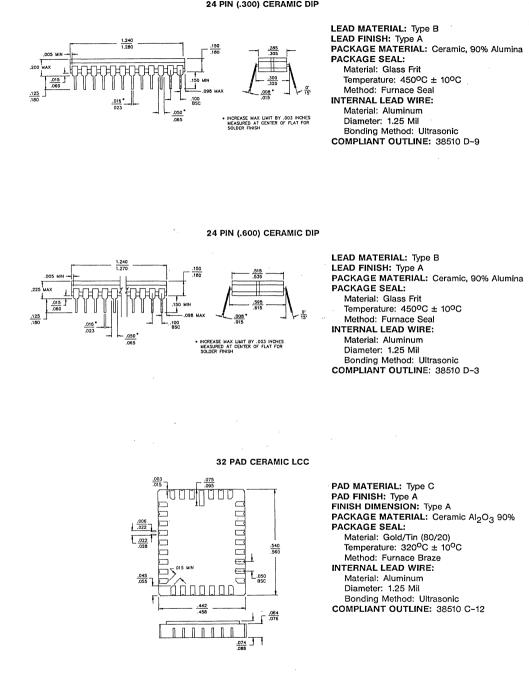

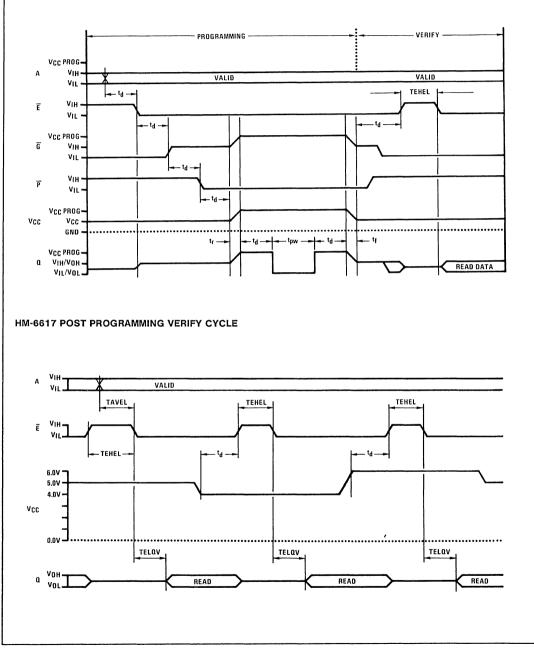

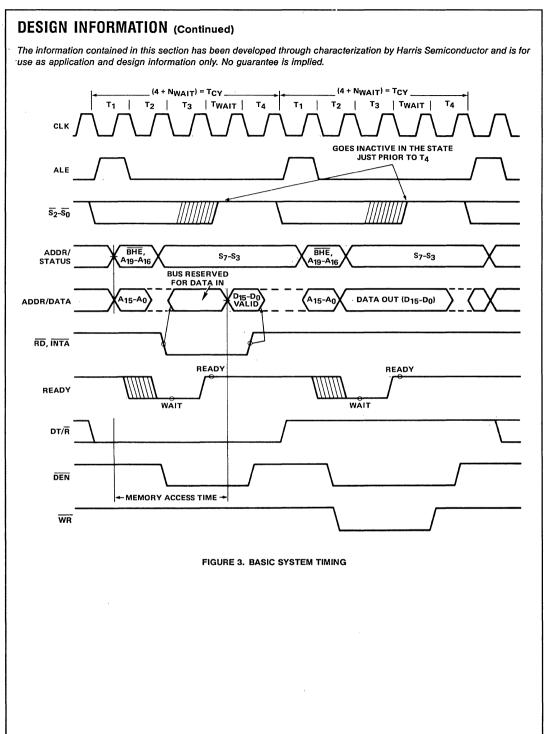

Design Information Sections: Harris provides an additional Design Information Section in many of the data sheets to assist in system application and design. This information may be in the form of applications circuits, typical device parameters, or additional device related user information such as programming information. While this information cannot be guaranteed, it is based on actual characterization of the product and is representative of the data sheet device.

\_\_\_\_

# High Reliability Products Information

Harris' High Reliability Products are all produced in accordance with military specifications and standards, primarily MIL-M-38510 (General Specifications for Microcircuits) and MIL-STD-883 (Test Methods and Procedures for Microelectronics).

MIL-M-38510 provides the ground rules for standardization in the manufacturing, testing and qualification of Integrated Circuits which are applicable to all qualified suppliers. MIL-M-38510 delineates two product assurance levels of screening, sampling, and documentation control requirements (Class S and Class B).

**Class S** is intended for use in manned space flight or extreme high reliability aerospace applications where replacement is extremely difficult or impossible.

**Class B** is intended for use in unmanned space flight, high reliability ground systems or commercial "hi-reliability use". These devices are the most frequently procured military ICs.

MIL-STD-883 contains test methods and procedures for various electrical, mechanical and environmental tests as well as requirements for screening, qualification and quality conformance inspection. Method 5004 of MIL-STD-883 lists the 100% screening tests which are required for each of the product assurance classes defined above.

Following the device screening, samples are removed from the production lot(s) for Quality Conformance Inspection testing. This testing is divided into four inspection groups: A, B, C and D, which are performed at prescribed intervals per MIL-M-38510 to assure the processes are in control and to ensure the continued quality level of the product being produced.

**Group A** electrical inspection involves dynamic, static, functional and switching tests at maximum, minimum and ambient operating temperatures. Sample sizes and specific tests performed depend upon the particular product assurance class chosen. Electrical test sampling is performed on all subgroups as defined in MIL-STD-883, Method 5005.

**Group B** inspection includes tests for marking permanency, internal visual and mechanical correctness, bond strength, and solderability. It is intended to provide assurance of the absence of lot-to-lot fabrication and manufacturing variances. Group B tests are again defined in test Method 5005.

**Group C** is oriented toward die integrity and consists of operating life testing as defined in MIL-STD-883, Method 5005.

**Group D** environmental testing is provided to verify die and package reliability. Among the Group D tests are lead integrity, hermeticity, temperature cycling, thermal and mechanical shock, and constant acceleration.

MIL-M-38510 requires that Group A and Group B inspection be performed on each lot, while Group C inspection must be done every 3 months and Group D every 6 months to be in compliance with MIL-M-38510 JAN requirements. To limit the amount of testing, MIL-M-38510 allows the multitude of microcircuits to be grouped by technology, commonly known as "generic families". Thus, one group C performed will cover all parts included in that generic family for three months. For Group D, which is package related, although there are some restrictions, one Group D performed on a 24-pin ceramic dual-in-line packaged part will cover all devices in the same package regardless of the technology group.

For MIL-STD-883 products, Groups A and B are required on each lot, Groups C and D are required every 52 weeks by generic die family and package fabricated and manufactured from the same plant as the die and package represented. 1

# General Test Philosophy -

The general philosophy for test set development is to supply test software that guarantees the high performance and quality of the products being designed and manufactured by Harris. The general final test set includes a guardbanded initial test program and a QA test program for the quality test step. Characterization software is an additional test program that parametrically measures and records the performance of the device under test. This test set is used to evaluate the performance of a product and to determine the acceptability of non-standard Source Control Drawings. BSPEC test programs are custom final test programs written to conform to customer specifications.

The general test development strategy is to develop software using a "shell" programming technique which creates standard test program flows, and reduces test development and execution times. Statistically derived guardbands are utilized in the "shell" programs to null out test system variability. High performance hardware interface designs are incorporated for maximized test effectiveness, and efficient fault graded vector sets are utilized for functional and AC testing.

The initial step in generating the test set is the test vector generation. The test vectors are the binary stimulus applied to the device under test to

functionally test the operation of the product. The vectors are developed against a behavioral model that is a software representation of the device functionality. The output of the behavioral model can be translated directly to ATE test vectors or prepared for CAD simulation.

The philosophy in the generation of test vectors is to develop efficient fault graded patterns with a goal of greater than 90% fault coverage. There is no intent to generate a worst case or best case noise vector set. The intent is to maximize fault coverage through efficient vector use. Generally only one vector set will be required to enable complete test coverage within a given test program. Exceptions to this would be vector generation to test certain identified critical AC speed paths or DC vectors for testing VIH/VIL parameters. These vector sets typically will not increase fault coverage and can not be substituted for fault graded vector sets.

The ultimate goal for testing all military /883, SMD and JAN products is data sheet compliancy, thoroughness, and quality of testing. By taking this approach to test set generation, Harris is capable of supplying high performance semiconductors of the highest quality to the marketplace.

**No. 52** February 1989

# Harris Digital

# ELECTROSTATIC DISCHARGE CONTROL A GUIDE TO HANDLING INTEGRATED CIRCUITS

This paper discusses methods and materials recommended for protection of ICs against ESD damage or degradation during manufacturing operations vulnerable to ESD exposure. Areas of concern include dice prep and handling, dice and package inspection, packing, shipping, receiving, testing, assembly and all operations where ICs are involved.

All integrated circuits are sensitive to electrostatic discharge (ESD) to some degree. Since the introduction of integrated circuits with MOS structures and high quality junctions, safe and effective means of handling these devices have been of primary importance.

If static discharge occurs at a sufficient magnitude, 2kV or greater, some damage or degradation will usually occur. It has been found that handling equipment and personnel can generate static potentials in excess of 10kV in a low humidity environment; thus it becomes necessary for additional measures to be implemented to eliminate or reduce static charge. Avoiding any damage or degradation by ESD when handling devices during the manufacturing flow is therefore essential.

#### ESD Protection and Prevention Measures

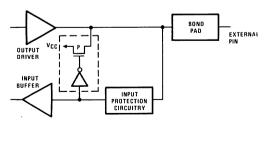

One method employed to protect gate oxide structures is to incorporate input protection diodes directly on the monolithic chip. However, there is no completely foolproof system of chip input protection in existence in the industry.

In areas where ICs are being handled, certain equipment should be utilized to reduce the damaging effects of ESD. Typically, equipment such as grounded work stations, conductive wrist straps, conductive floor mats, ionized air blowers and conductive packaging materials are included in the IC handling environment. Any time an individual intends to handle an IC, in any way, they must insure they have been grounded to eliminate circuit damage.

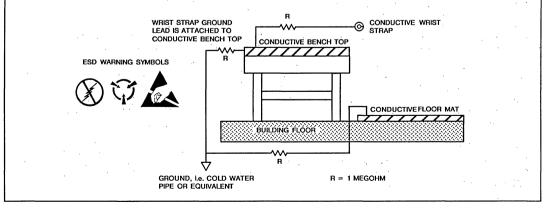

Grounding personnel can, practically, be performed by two methods. First, grounded wrist straps which are usually made of a conductive material, such as Velostat or metal. A resistor value of 1 megohm (1/2 watt) in series with the strap to ground completes a discharge path for ESD when the operator wears the strap in contact with the skin. Another method is to insure direct physical contact with a grounded, conductive work surface.

This consists of a conductive surface like Velostat, covering the work area. The surface is connected to a 1 megohm (1/2 watt) resistor in series with ground.

In addition to personnel grounding, areas where work is being performed with ICs, should be equipped with an ionized air blower. Ionized air blowers force positive and negative ions simultaneously over the work area so that any nonconductors that are near the work surface would have their static charge neutralized before it would cause device damage or degradation.

Relative humidity in the work area should be maintained as high as practical. When the work environment is less than 40% RH, a static build-up condition can exist on nonconductors allowing stored charges to remain near the ICs causing possible static electricity discharge to ICs.

Integrated circuits that are being shipped or transported require special handling and packaging materials to eliminate ESD damage. Dice or packaged devices should be in conductive carriers during all phases of transport and handling. Leads of packaged devices can be shorted by tubular metalic carriers, conductive foam or foil.

#### Do's and Don'ts for Integrated Circuit Handling <sup>Do's</sup>

Do keep paper, nonconductive plastic, plastic foams and films or cardboard off the static controlled conductive bench top. Placing devices, loaded sticks or loaded burn-in boards on top of any of these materials effectively insulates them from ground and defeats the purpose of the static controlled conductive surface.

Do keep hand creams and food away from static controlled conductive work surfaces. If spilled on the bench top, these materials will contaminate and increase the resistivity of the work area.

Do be especially careful when using soldering guns around conductive work surfaces. Solder spills and heat from the gun may melt and damage the conductive mat.

Do check the grounded wrist strap connections daily. Make certain they are snugly fitted before starting work with the product.

Do put on grounded wrist strap before touching any devices. This drains off any static build-up from the operator.

Do know the ESD caution symbols.

Do remove devices or loaded sticks from shielding bags only when grounded via wrist strap at grounded work station. This also applies when loading or removing devices from the antistatic sticks or the loading on or removing from the burn-in boards.

Copyright © Harris Corporation 1989

1

Do wear grounded wrist straps in direct contact with the bare skin – never over clothing.

Do use the same ESD control with empty burn-in boards as with loaded boards if boards contain permanently mounted ICs as part of driver circuits.

Do insure electrical test equipment and solder irons at an ESD control station are grounded and only uninsulated metal hand tools be used. Ordinary plastic solder suckers and other plastic assembly aids shall not be used.

Do use ionizing air blowers in static controlled areas when the use of plastic (nonconductive) materials cannot be avoided.

#### Don'ts

Don't allow anyone not grounded to touch devices, loaded sticks or loaded burn-in boards. To be grounded they must be standing on a conductive floor mat with conductive heel straps attached to footwear or must wear a grounded wrist strap.

Don't touch the devices by the pins or leads unless grounded since most ESD damage is done at these points.

Don't handle devices or loaded sticks during transport from work station to work station unless protected by shielding bags. These items must never be directly handled by anyone not grounded.

Don't use freon or chlorinated cleaners at a grounded work area.

Don't wax grounded static controlled conductive floor and bench top mats. This would allow build-up of an insulating layer and thus defeating the purpose of a conductive work surface.

Don't touch devices or loaded sticks or loaded burn-in boards with clothing or textiles even though grounded wrist strap is worn. This does not apply if conductive coats are worn.

Don't allow personnel to be attached to hard ground. There must always be 1 megohm series resistance (1/2 watt between the person and the ground).

Don't touch edge connectors of loaded burn-in boards or empty burn-in boards containing permanently mounted driver circuits when not grounded. This also applies to burn-in programming cards containing ICs.

Don't unload stick on a metal bench top allowing rapid discharge of charged devices.

Don't touch leads. Handle devices by their package even though grounded.

Don't allow plastic "snow or peanut" polystyrene foam or other high dielectric materials to come in contact with devices or loaded sticks or loaded burn-in boards.

Don't allow rubber/plastic floor mats in front of static controlled work benches.

Don't solvent-clean devices when loaded in antistatic sticks since this will remove antistatic inner coating from sticks.

Don't use antistatic sticks for more than one throughput process. Used sticks should not be reused unless recoated.

#### Recommended Maintenance Procedures

#### Daily:

Perform visual inspection of ground wires and terminals on floor mats, bench tops, and grounding receptacles to ensure that proper electrical connections via 1 megohm resistor (1/2 watt) exist.

Clean bench top mats with a soft cloth or paper towel dampened with a mild solution of detergent and water.

#### Weekly:

Damp mop conductive floor mats to remove any accumulated dirt layer which causes high resistivity.

#### Annually:

Replace nuclear elements for ionized air blowers.

Review ESD protection procedures and equipment for updating and adequacy.

#### Static Controlled Work Station

The figure below shows an example of a work bench properly equipped to control electro-static discharge. Note that the wrist strap is connected to a 1 megohm resistor. This resistor can be omitted in the setup if the wrist strap has a 1 megohm assembled on the cable attached.

# Military Programs

#### PAGE

| MILITARY GRADE PRODUCT OFFERINGS        | 2-3 |

|-----------------------------------------|-----|

| HARRIS/883/JAN/DESC PART NUMBER LISTING | 2-4 |

| MILITARY PRODUCT PROGRAM CONTROLS       | 2-7 |

| PROGRAMS SERVED BY HARRIS               | 2-8 |

2

.

Harris High Reliability Products are offered in the following Military grades:

#### JAN (Joint Army Navy)

Registered trademark of the U.S. Government indicating that a device is fully compliant to MIL-M-38510. The Defense Electronics Supply Center (DESC) maintains a continuing audit of manufacturing compliance. There are two product assurance classes available for M38510 products (Class S and B). Devices are defined and identified by their particular detail specification or "slash sheet" number issued by DESC (eg. M38510/29104BJX). The IC manufacturers who are qualified to supply products to a particular M38510 slash sheet are identified in the Qualified Products List (QPL) issued by DESC.

#### SMD (Standard Military Drawing)

The SMD evolved from the DESC drawing program which was viewed as a preliminary specification prior to JAN approval. SMDs were created to control the proliferation of non-standard Source Control Drawings. The Standard Military Drawing provides standardized MIL-STD-883 processing in conjunction with non-JAN devices as specified in paragraph 1.2.1 of MIL-STD-883. These devices are defined and identified by their Standard Military Drawing number issued by DESC (eg. 5962-8757701RA). The manufacturers qualified to supply a particular SMD device are listed in the back of the individual Standard Military Drawing.

#### Harris Class B Compliant

These devices are fully compliant to MIL-STD-883, Class B and are identified by the /883 suffix on the Harris part number. The parametric limits for an /883 data sheet are controlled by the manufacturer rather than a governmental agency, and therefore, there may be differences in the test methodology and actual limits for "similar" devices made by different manufacturers.

This manufacturer control of the /883 specifications allows the offering of 883-level products long before they might become available as MIL-M-38510 or SMD devices. In many cases, Harris actually specifies /883 devices with more stringent conditions than those appearing on the MIL-M-38510 slash sheet or SMD describing the same generic device. Harris recommends using our /883 data sheets as the baseline for new military or aerospace source control drawings.

#### • Harris Class B "Equivalent"

These devices are processed and tested in a manner equivalent to the MIL-STD-883 compliant devices. They may not be classified as compliant since government standards have not been established for processing these types of components (eg. Ram Modules). The Class B "Equivalent" products can be identified by the -8 suffix on the Harris part number.

#### Non-Standard Product Offerings

Harris understands the need for customer generated Source Control Drawings with non-standard parameter and/or screening requirements. A Customer Engineering Department is responsible for efficiently expediting the SCDs through a comprehensive review process. Our Customer Engineering Group compares the SCD to its closest equivalent product grade and works closely with the Product Engineer, Manufacturing Engineer, Design Engineer, or applicable individual to compare Harris' screening ability against the customer's non-standard requirement(s). For products processed to non-standard requirements, a unique part number suffix is assigned.

Harris shares the military's objective to utilize standards wherever possible. We recommend using our /883 data sheets as guidelines for generating new Source Control Drawings. In instances where an available military specification or Harris /883 data sheet is inappropriate, it is Harris' sincerest wish to work closely with the customer in establishing an acceptable procurement document. For this reason, the customer is requested to contact the nearest Harris Sales Office or Representative before finalizing the Source Control Drawing. Harris looks forward to working with the customer prior to implementation of the formal drawing so that both parties may create a mutually acceptable procurement document. 2

# Harris/883/JAN/DESC Part Number Listing —

| HARRIS PART #       | JAN PART # | SMD/DESC PART # | /883 PART #     |

|---------------------|------------|-----------------|-----------------|

| MICROPROCESSOR PROD | UCTS       |                 | ······          |

| MG80C286-12         |            |                 | MG80C286-12/883 |

| MG80C286-10         |            |                 | MG80C286-10/883 |

| MD82C284-12         |            |                 | MD82C284-12/883 |

| MD82C284-10         |            |                 | MD82C284-10/883 |

| MD82C288-12         | 1          |                 | MD82C288-12/883 |

| MD82C288-10         |            |                 | MD82C288-10/883 |

| MD80C86             |            | 8405201QA       | MD80C86/883     |

| MR80C86             | · .        | 8405201XA       | MR80C86/883     |

| MD80C86-2           |            |                 | MD80C86-2/883   |

| MR80C86-2           |            |                 | MR80C86-2/883   |

| MD80C88             |            |                 | MD80C88/883     |

| MR80C88             | ,          |                 | MR80C88/883     |

| MD80C88-2           |            |                 | MD80C88-2/883   |

| MR80C88-2           |            |                 | MR80C88-2/883   |

| MD82C37A            |            |                 | MD82C37A/883    |

| MR82C37A            | k.         |                 | MR82C37A/883    |

| MD82C37A-5          |            |                 | MD82C37A-5/883  |

| MR82C37A-5          |            |                 | MR82C37A-5/883  |

| MD82C52             | 1          | 8501501XA       | MD82C52/883     |

| MR82C52             |            | 85015013A       | MR82C52/883     |

| MD82C54             |            | 8406501JA       | MD82C54/883     |

| MR82C54             |            | 84065013A       | MR82C54/883     |

| MD82C55A            |            | 8406602QA       | MD82C55A/883    |

| MR82C55A            |            | 8406602XA       | MR82C55A/883    |

| MD82C55A-5          | н.<br>С    | 8406601QA       | MD82C55A-5/883  |

| MR82C55A-5          |            | 8406601XA       | MR82C55A-5/883  |

| MD82C59A            |            | 5962-8501602YA  | MD82C59A/883    |

| MR82C59A            |            | 5962-85016023A  | MR82C59A/883    |

| MD82C59A-5          |            | 5962-8501601YA  | MD82C59A-5/883  |

| MR82C59A-5          |            | 5962-85016013A  | MR82C59A-5/883  |

| MD82C82             |            | 8406701RA       | MD82C82/883     |

| MR82C82             |            | 84067012A       | MR82C82/883     |

| MD82C83H            |            | 8406702RA       | MD82C83H/883    |

| MR82C83H            |            | 84067022A       | MR82C83H/883    |

| MD82C84A            | i.         | 8406801VA       | MD82C84A/883    |

| MR82C84A            |            | 84068012A       | MR82C84A/883    |

| MD82C85             |            |                 | MD82C85/883     |

| MR82C85             |            |                 | MR82C85/883     |

| MD82C86H-5          |            | 5962-8757701RA  | MD82C86H-5/883  |

| MR82C86H-5          |            | 5962-87577012A  | MR82C86H-5/883  |

| MD82C87H-5          |            | 5962-8757702RA  | MD82C87H-5/883  |

| MR82C87H-5          |            | 5962-87577022A  | MR82C87H-5/883  |

| MD82C88             |            | 8406901RA       | MD82C88/883     |

| MR82C88             |            | 84069012A       | MR82C88/883     |

| MD82C89             |            | 5962-8552801RA  | MD82C89/883     |

| MR82C89             |            | 5962-85528012A  | MR82C89/883     |

# - Harris/883/JAN/DESC Part Number Listing —

| HARRIS PART #      | JAN PART #       | SMD/DESC PART # | /883 PART #                           |

|--------------------|------------------|-----------------|---------------------------------------|

| DATA COMMUNICATIO  | NPRODUCTS        |                 | · · · · · · · · · · · · · · · · · · · |

| HD1-6409           |                  |                 | HD1-6409/883                          |

| HD1-15530          |                  | 7802901JA       | HD1-15530/883                         |

| HD4-15530          |                  | 78029013A       | HD4-15530/883                         |

| HD1-15531          |                  |                 | HD1-15531/883                         |

| HD1-15531B         |                  |                 | HD1-15531B/883                        |

| HD1-4702           |                  |                 | HD1-4702/883                          |

| HD1-6402           |                  |                 | HD1-6402/883                          |

| CMOS MEMORY PROD   | UCTS             |                 |                                       |

| 1K CMOS STATIC RAM | S                |                 |                                       |

| HM1-6508           |                  |                 | HM1-6508/883                          |

| HM1-6508B          |                  |                 | HM1-6508B/883                         |

| HM1-6518           |                  |                 | HM1-6518/883                          |

| HM1-6518B          |                  |                 | HM1-6518B/883                         |

| HM1-6551           |                  |                 | HM1-6551/883                          |

| HM1-6551B          |                  |                 | HM1-6551B/883                         |

| HM1-6561           |                  |                 | HM1-6561/883                          |

| HM1-6561B          |                  |                 | HM1-6561B/883                         |

| 4K CMOS STATIC RAM | s                |                 |                                       |

| HM1-6504           |                  | 8102405VA       | HM1-6504/883                          |

| HM1-6504B          |                  | 8102403VA       | HM1-6504B/883                         |

| HM1-6504S          | M38510/24501BVA  |                 | HM1-6504S/883                         |

| HM1-6514           |                  | 8102406VA       | HM1-6514/883                          |

| HM1-6514B          |                  | 8102404VA       | HM1-6514B/883                         |

| HM1-6514S          | M38510/24502BVA  |                 | HM1-6514S/883                         |

| 16K CMOS SYNCHRON  | IOUS STATIC RAMS | ····            |                                       |

| HM1-6516           | M38510/29102BJA  |                 | HM1-6516/883                          |

| HM4-6516           | M38510/29102BXA  |                 | HM4-6516/883                          |

| HM1-6516B          |                  | 8403607JA       | HM1-6516B/883                         |

| HM4-6516B          |                  | 8403607ZA       | HM4-6516B/883                         |

| 16K CMOS ASYNCHRO  | NOUS STATIC RAMS |                 |                                       |

| HM1-65162          | M38510/29104BJA  |                 | HM1-65162/883                         |

| HM4-65162          | M38510/29104BXA  |                 | HM4-65162/883                         |

| HM1-65162B         | M38510/29110BJA  |                 | HM1-65162B/883                        |

| HM4-65162B         | M38510/29110BXA  |                 | HM4-65162B/883                        |

| HM1-65162C         |                  | 8403603JA       | HM1-65162C/883                        |

| HM4-65162C         |                  | 8403603ZA       | HM4-65162C/883                        |

| HM1-65262          | M38510/29103BRA  |                 | HM1-65262/883                         |

| HM4-65262          | M38510/29103BYA  |                 | HM4-65262/883                         |

| HM1-65262B         | M38510/29109BRA  |                 | HM1-65262B/883                        |

| HM4-65262B         | M38510/29109BYA  |                 | HM4-65262B/883                        |

2

MILITARY Programs

# Harris/883/JAN/DESC Part Number Listing —

| HARRIS PART #       | JAN PART #                  | SMD/DESC PART #                                                   | /883 PART #             |

|---------------------|-----------------------------|-------------------------------------------------------------------|-------------------------|

| CMOS MEMORY PRODU   | CTS (CONTINUED)             |                                                                   |                         |

| 64K CMOS STATIC RAM | 5                           |                                                                   |                         |

| HM1-65642           |                             |                                                                   | HM1-65642/883           |

| HM4-65642           |                             |                                                                   | HM4-65642/883           |

| HM1-65642B          | M38510/29205BXA             |                                                                   | HM1-65642B/883          |

| HM4-65642B          | M38510/29205BYA             |                                                                   | HM4-65642B/883          |

| HM1-65642C          |                             |                                                                   | HM1-65642C/883          |

| HM4-65642C          |                             |                                                                   | HM4-65642C/883          |

| CMOS FUSE LINK PROM | S                           | • · · · · · · · · · · · · · · · · · · ·                           |                         |

| HM1-6617            |                             |                                                                   | HM1-6617/883            |

| HM4-6617            |                             |                                                                   | HM4-6617/883            |

| HM6-6617            |                             |                                                                   | HM6-6617/883            |

| HM1-6617B           |                             |                                                                   | HM1-6617B/883           |

| HM4-6617B           |                             |                                                                   | HM4-6617B/883           |

| HM6-6617B           |                             |                                                                   | HM6-6617B/883           |

| HM1-6642            |                             |                                                                   | HM1-6642/883            |

| HM4-6642            |                             |                                                                   | HM4-6642/883            |

| HM6-6642            |                             |                                                                   | HM6-6642/883            |

| HM1-6642B           |                             |                                                                   | HM1-6642B/883           |

| HM4-6642B           |                             |                                                                   | HM4-6642/883            |

| HM6-6642B           |                             |                                                                   | HM6-6642B/883           |

| CMOS STATIC RAM MOI | DULES                       |                                                                   |                         |

| HM5-6564            |                             |                                                                   |                         |

| HM5-8808            |                             |                                                                   | · ·                     |

| HM5-8808B           |                             | odules are available for militar<br>ur high–rel DASH 8 program fi |                         |

| HM5-8808S           | burn-in and value added pro | ccessing (temperature cycling<br>arris sales office or representa | , SEM inspection, etc.) |

| HM5-8808A           |                             |                                                                   |                         |

| HM5-8808AB          |                             |                                                                   |                         |

| HM5-8808AS          |                             |                                                                   |                         |

| HM5-8816H           |                             |                                                                   |                         |

| HM5-8832            |                             |                                                                   |                         |

| HM5-8832B           |                             |                                                                   |                         |

| HM5-92560           |                             |                                                                   |                         |

| HM5-92570           |                             |                                                                   |                         |

# **Military Product Program Controls**

|          | REQUIREMENT               | 883<br>REFERENCE | JAN                      | DESC/SMD                       | /883                           | -8                              |

|----------|---------------------------|------------------|--------------------------|--------------------------------|--------------------------------|---------------------------------|

|          | Product<br>Assurance Plan | 1.2.1.B.21       | Per Ap                   | pendix A of MIL M              | Per Harris R&QA<br>Manual      |                                 |

|          | Facility<br>Certification | 1.2.1.B.28       | RADC/DESC                | Harris QC                      | Harris QC                      | Harris QC                       |

|          | Product<br>Certification  | 1.2.1.B.26       | RADC/DESC                | RADC/DESC                      | Harris QA                      | Not Required                    |

| S        | Detail<br>Specifications  | 1.2.1.A          | Slash Sheet              | sh Sheet DESC DWG/<br>SMD      |                                | Harris Catalog                  |

| CONTROLS | Qualifying<br>Activity    | 1.2.1.B.1        | RADC/DESC                | Harris                         | Harris                         | Harris                          |

| CON      | Qualification<br>Test GPC | 1.2.1.B.17       | Required                 | Per Governing<br>Military Spec | Per Governing<br>Military Spec | Per<br>Harris Spec              |

| SYSTEM   | Qualification<br>Test GPD | 1.2.1.B.17       | Required                 | Per Governing<br>Military Spec | Per Governing<br>Military Spec | Per<br>Harris Spec              |

| γs       | QPL Listing               |                  | MIL M38510               | None                           | None                           | None                            |

| N        | Change<br>Controls        | 1.2.1.B.25       | MIL M38510<br>para 3.4.2 | DoD 480                        | DoD 480                        | Harris Internal<br>ECN Controls |

|          | Change<br>Notification    | 1.2.1.B.25       | DESC DESC                |                                | Data Sheet<br>Registration     | Catalog                         |

|          | Traceability              | 1.2.1.B.27       | Wafer Lot                | 6 Week Seal                    | 6 Week Seal                    | 6 Week Seal                     |

|          | Deviations to<br>883      | 1.2.1            | Per<br>Slash Sheet       | Per DESC<br>DWG/SMD            | None                           | Per<br>Harris Spec              |

|          | Product<br>Construction   | 1.2.1.B.2-12     | Compliant                | Compliant                      | Compliant                      | May Be<br>Non-Compliant         |

| SN       | Fab                       |                  | USA Only                 | USĄ                            | USA                            | USA                             |

| 0        | Assembly                  |                  | USA Only                 | USA/Malaysia                   | USA/Malaysia                   | Malaysia                        |

| OCATIONS | Screening                 |                  | USA Only                 | USA/Malaysia                   | USA/Malaysia                   | Malaysia                        |

| ГОС      | Quality<br>Conformance    |                  | USA Only                 | USA                            | USA                            | Malaysia                        |

+ -8 is available in support of programs with part requirements dated prior to Dec. 31, 1984 in accordance with paragraph 1.2. of MIL-STD-883 or where 883 is not currently available.

. . .

2-7

### **Programs Served By Harris**

Tube-Launched, Optically Tracked, Wire-Guided Missile Angle Rate Bombing Set Advanced Medium Range Air-To-Air Missile Advanced Capability (MK-48 Torpedo) Position Location and Reporting System Joint Tactical Information Distribution System Target Acquisition System (MK-23) Miniature Vehicle Sensors **Driver's Thermal Viewer** Detecting and Ranging Set Fighting Vehicle System (Bradley) Helicopter (or Hughes) Night Vision System Advanced Optic Adjunct Advanced Light Weight Torpedo Ground Launched Cruise Missile Air Launched Cruise Missile Medium Range Air-To-Surface Missile Modular Universal Laser Equipment Low Altitude Navigation and Targeting Infrared Anti-Submarine Warfare Multiple Launch Rocket System Advanced Self Protection Jammer **Global Positioning System Distant Early Warning** High Speed Anti-Radar Missile **Rolling Airframe Missile** Medium Depth Mine Terminal Guidance Small Missile Time Division Multiple Access **Distributed Time Division Multiple Access** Long Range Search and Track Glide Bomb Unit **Divisional Air Defense**

Field Support Tracked Vehicle Integrated Solar Sensor Assembly Continuous Motion Gyro for ISSA Advanced Warning and Control System Forward Looking Infrared **Ring Laser Gyro Programs** Tail Warning System Space Telescope Mariner Series MK 46 NEARTIP **AV8B HARRIER** F14/A6E SMS Bearclaw CAINS II TAI/MK6 B1 F-16 Phalanx Stinger Locust Sidearm Rattler Pavetack Viking Skylab Shuttle Intelsat Spacelab Voyager Mark 50 Captor Maverick Phoenix

# DIGITAL

# **CMOS Memory**

| ൭ |  |

|---|--|

| G |  |

|                  |                                      | PAGE  |

|------------------|--------------------------------------|-------|

| LOW VOLTAGE DAT  | A RETENTION                          | 3-2   |

| INDUSTRY CMOS RA | M CROSS REFERENCE                    | 3-3   |

| 1K CMOS RAM DATA | SHEETS                               |       |

| HM-6508/883      | 1K x 1 Synchronous RAM               | 3-4   |

| HM-6518/883      | 1K x 1 Synchronous RAM               | 3-16  |

| HM-6551/883      | 256 x 4 Synchronous RAM              | 3-28  |

| HM-6561/883      | 256 x 4 Synchronous RAM              | 3-40  |

| 4K CMOS RAM DATA | SHEETS                               |       |

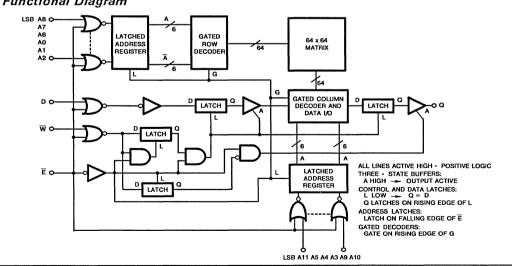

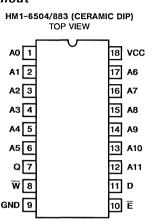

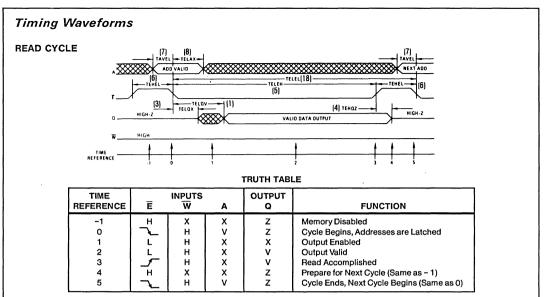

| HM-6504/883      | 4K x 1 Synchronous RAM               | 3-52  |

| HM-6514/883      | 1K x 4 Synchronous RAM               | 3-67  |

| 16K CMOS RAM DAT | A SHEETS                             |       |

| HM-6516/883      | 2K x 8 Synchronous RAM .             | 3-82  |

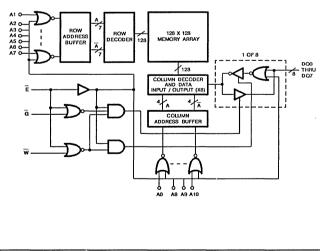

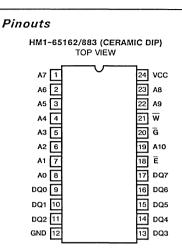

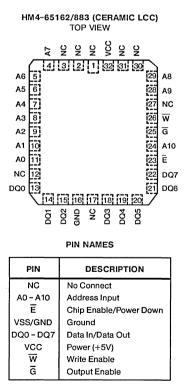

| HM-65162/883     | 2K x 8 Asynchronous RAM              | 3-91  |

| HM-65262/883     | 16K x 1 Asynchronous RAM             | 3-104 |

| 64K CMOS RAM DAT | ASHEETS                              |       |

| HM-65642/883     | 8K x 8 Asynchronous RAM              | 3-115 |

| HM-65642C/883    | 8K x 8 Asynchronous RAM              | 3-129 |

| CMOS RAM MODULE  | E DATA SHEETS                        |       |

| HM-6564          | 64K Synchronous RAM Module           | 3-140 |

| HM-8808/08A      | 8K x 8 Asynchronous RAM Modules      | 3-146 |

| HM-8816H         | 16K x 8 Asynchronous RAM Module      | 3-159 |

| HM-8832          | 32K x 8 Asynchronous RAM Module      | 3-165 |

| HM-92560         | 256K Synchronous RAM Module          | 3-172 |

| HM-92570         | 256K Buffered Synchronous RAM Module | 3-178 |

| HM-91M2          | 1M Bit Asynchronous RAM Module       | 3-184 |

| CMOS PROM DATA S | SHEETS                               |       |

| HM-6642/883      | 512 x 8 Fuse Link PROM               | 3-194 |

| HM-6617/883      | 2K x 8 Fuse Link PROM                | 3-206 |

CMOS Memory

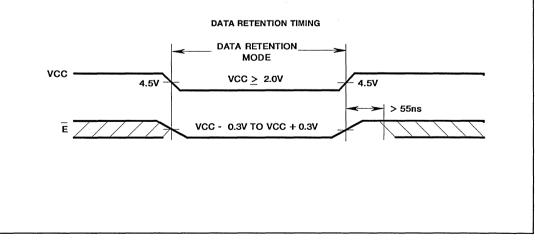

# Low Voltage Data Retention

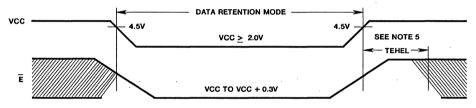

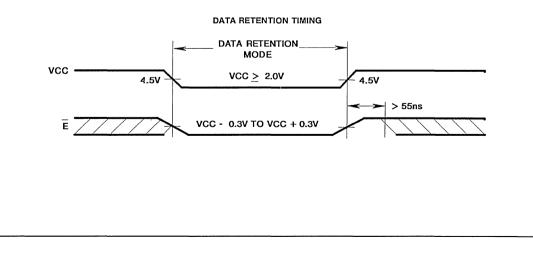

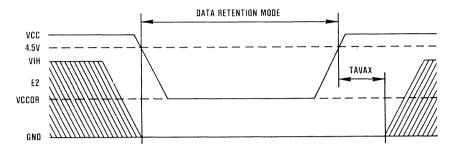

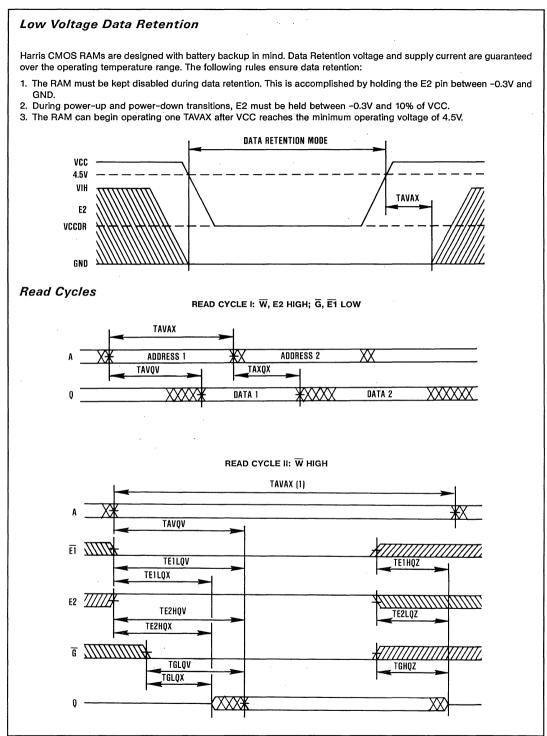

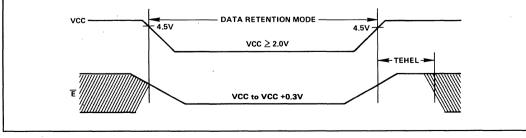

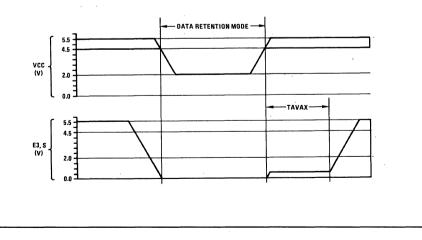

HARRIS CMOS RAMs are designed with battery backup in mind. Data retention voltage and supply current are guaranteed over temperature. The following rules insure data retendtion:

- 1. Chip Enable (E) must be held high during data retention; within VCC to VCC +0.3V

- 2. On RAMs which have selects or output enables (e.g.  $\overline{S}$ ,  $\overline{G}$ ), one of the selects or output enables should be held in the deselected state to keep the RAM outputs high impedance, minimizing power dissipation.

- ... 3. All other inputs should be held either high (at CMOS VCC) or at ground to minimize ICCDR.

- 4. Inputs which are to be held high (e.g. E) must be kept between VCC +0.3V and 70% of VCC during the power up and power down transitions.

- 5. The RAM can begin operation one TEHEL (for synchronous RAMs) and > 5ns (for asynchronous RAMs) after VCC reaches the minimum operating voltage (4.5 volts).

#### DATA RETENTION TIMING

#### HARRIS CMOS RAMs

# Industry CMOS RAM Cross Reference

| DESCRIPTION                                       | HARRIS                            | AMD            | EDI           | FUJI-<br>ITSU | HIT-<br>ACHI | IDT                    | MITSU-<br>BISHI | MOT-<br>OROLA | NAT-<br>IONAL  | NEC      | окі          | HARRIS/<br>RCA | SMOS         | TOSH-<br>IBA | NMOS,<br>OTHER                   |

|---------------------------------------------------|-----------------------------------|----------------|---------------|---------------|--------------|------------------------|-----------------|---------------|----------------|----------|--------------|----------------|--------------|--------------|----------------------------------|

| 1K CMOS RAMs                                      |                                   |                |               |               |              |                        |                 |               |                |          |              |                |              |              |                                  |

| 1k x 1, 16 Pin<br>Synchronous                     | HM-6508                           |                |               | 8401          |              |                        |                 | 6508          | 6508<br>74C929 | 443      |              | 6508<br>1821   |              | 5508         | 2125, 4015                       |

| 1K x 1, 18 Pin<br>Synchronous                     | HM-6518                           |                |               |               |              |                        |                 | 6518          | 6518<br>74C930 |          |              |                |              |              |                                  |

| 256 x 4, 22 Pin<br>Synchronous                    | HM-6551                           |                |               |               |              |                        |                 |               | 6551<br>74C920 |          |              | 1822<br>5101   |              | 5101         | 2101                             |

| 256 x 4, 18 Pin<br>Synchronous                    | HM-6561                           |                |               |               |              |                        |                 |               |                |          |              |                |              |              | 2111                             |

| 4K CMOS RAMs                                      | - <b>I</b>                        | 1              | L             |               | 1            |                        | 1               | L             | 1              | I        | 4            | .I             |              | L            | 1                                |

| 4K x 1, 18 Pin<br>Synchronous                     | HM-6504                           | 92144          |               | 8404          | 4315<br>6147 |                        |                 | 6504          | 6504           |          | 5104         |                | 6504         | 5504         | 2141, 2147<br>315D, 4104<br>4404 |

| 1K x 4, 18 Pin<br>Synchronous                     | HM-6514                           | 91L14<br>91L24 |               | 8414          | 4334<br>6148 |                        | 58981           | 6514          | 6514           | 444      | 5114<br>5115 | 5114           | 6514         | 5514         | 2114, 2148<br>2149, 4045<br>314A |

| 16K CMOS RAMs                                     | -l                                | I              | 1             | L             | 1            | L                      | I               | L             | L              | i        | L            | I              | L            | <b>1</b>     |                                  |

| 2K x 8, 24 Pin<br>Synchronous                     | HM-6516                           |                |               |               |              |                        |                 |               | 6516           |          |              |                |              |              |                                  |

| 2K x 8, 24 Pin<br>Asynchronous                    | HM-65162                          |                |               | 8416          | 6116         | 6116                   | 5117            | 65116         | 6116           | 446      | 5128         | 6116           | 2016         | 5517         | 4802, 2116<br>2016, 4016         |

| 16K x 1, 20 Pin<br>Asynchronous                   | HM-65262                          |                |               | 8167          | 6167         | 6167                   |                 | 1             |                |          |              |                | 2267<br>2367 |              | 2167, 8167<br>1400               |

| 64K CMOS RAMs                                     |                                   |                | d             |               | •            |                        |                 | L             | <b>.</b>       | <b>I</b> | <b></b>      |                |              | <b>4</b>     |                                  |

| 8K x 8, 28 Pin<br>Asynchronous                    | HM-65642<br>HM-8808A*<br>HM-8808* | 99C88          | 8808A<br>8808 | 8464          | 6264         | 7164<br>7M864<br>8M864 | 5164            | 6164          | 6164           | 4464     |              | 6264           | 2064<br>2264 | 5564<br>5565 |                                  |