## **Digital Signal Processing**

## 🗄 HARRIS

#### HARRIS SEMICONDUCTOR DSP PRODUCTS

This digital signal processing databook represents the full line of Harris Semiconductor DSP products for commercial and military applications and supersedes previously published DSP material under the Harris, GE, RCA or Intersil names. For a complete listing of all Harris Semiconductor products, please refer to the Product Selection Guide (SPG-201R; ordering information below).

For complete, current and detailed technical specifications on any Harris device please contact the nearest Harris sales, representative or distributor office; or direct literature requests to:

#### Harris Semiconductor Literature Department P.O. Box 883, MS CB1-28 Melbourne, FL 32901 (407) 724-3739 FAX 407-724-3937

For general information regarding Harris Semiconductor and its products, call 1-800-4-HARRIS

#### **U.S. HEADQUARTERS**

Harris Semiconductor 1301 Woody Burke Road Melbourne, Florida 32902 TEL: (407) 724-3000

#### SOUTH ASIA

Harris Semiconductor H.K. Ltd 13/F Fourseas Building 208-212 Nathan Road Tsimshatsui, Kowloon Hong Kong TEL: (852) 3-723-6339

#### **EUROPEAN HEADQUARTERS**

Harris Semiconductor Mercure Centre Rue de la Fusse 100 1130 Brussels, Belgium TEL: (32) 2-246-2111

#### NORTH ASIA

Harris K.K. Shinjuku NS Bldg. Box 6153 2-4-1 Nishi-Shinjuku Shinjuku-Ku, Tokyo 163 Japan TEL: 81-03-3345-8911

Copyright © Harris Corporation 1991 (All rights reserved) Printed in U.S.A., 1991

en en en en fan en en fan de fan de fan en fan en fan en fan de fan de fan de fan de fan en fan een en fan een De fan de fan een een een de fan de fan een de fan de f De fan de fan

Harris Semiconductor products are sold by description only. All specifications in this product guide are applicable only to packaged products; specifications for die are available upon request. Harris reserves the right to make changes in circuit design, specifications and other information at any time without prior notice. Accordingly, the reader is cautioned to verify that information in this publication is current before placing orders. Reference to products of other manufacturers are solely for convenience of comparison and do not imply total equivalency of design, performance, or otherwise.

and a straight for the straight of the straigh

HARRIS

and an original solution of an architecture and a solution of the solution and a solution of the solution

# DIGITAL SIGNAL PROCESSING

### FOR COMMERCIAL AND MILITARY APPLICATIONS

#### DIGITAL SIGNAL PROCESSING PRODUCT TECHNICAL ASSISTANCE

For technical assistance on the Harris products listed in this databook, please contact Field Applications Engineering staff available at one of the following Harris Sales Offices:

#### UNITED STATES

| CALIFORNIA    | Costa Mesa             |

|---------------|------------------------|

| FLORIDA       | Melbourne              |

| GEORGIA       | Norcross               |

| ILLINOIS      | Itasca708-250-0070     |

| MASSACHUSETTS | Burlington617-221-1850 |

| NEW JERSEY    | Mt. Laurel             |

| TEXAS         | Dallas                 |

| INTERNATIONAL              |                          |

|----------------------------|--------------------------|

| FRANCE                     | Paris                    |

| GERMANY                    | Munich                   |

| ITALY                      | Milano 39-2-262-22127    |

| JAPAN                      | Tokyo81-3-345-8911       |

| SWEDEN                     | Stockholm 46-8-623-5220  |

| . <b>U.K.</b><br>19-10-10- | Camberley 44-2-766-86886 |

For literature requests, please contact Harris at 407-724-3739.

. . . .

GENERAL INFORMATION

### **GENERAL INFORMATION**

#### ALPHA NUMERIC PRODUCT INDEX

|                              |                                                                | PAGE  |

|------------------------------|----------------------------------------------------------------|-------|

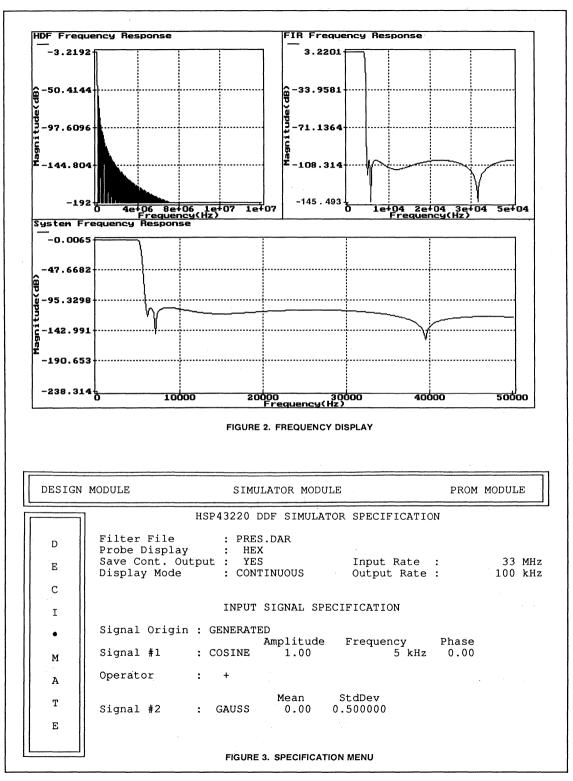

| DECI ● MATE™                 | Harris HSP43220 Decimating Digital Filter Development Software | 3-31  |

| HMA510                       | 16 x 16-Bit CMOS Parallel Multiplier Accumulator               | 2-29  |

| HMA510/883                   | 16 x 16-Bit CMOS Parallel Multiplier Accumulator               | 2-36  |

| HMU16/HMU17                  | 16 x 16-Bit CMOS Parallel Multipliers                          | 2-3   |

| HMU16/883                    | 16 x 16-Bit CMOS Parallel Multiplier                           | 2-13  |

| HMU17/883                    | 16 x 16-Bit CMOS Parallel Multiplier                           | 2-21  |

| HSP43168                     | Dual FIR Filter                                                | 3-102 |

| HSP43220                     | Decimating Digital Filter                                      | 3-3   |

| HSP43220/883                 | Decimating Digital Filter                                      | 3-23  |

| HSP43481                     | Digital Filter                                                 | 3-81  |

| HSP43481/883                 | Digital Filter                                                 | 3-96  |

| HSP43881                     | Digital Filter                                                 | 3-58  |

| HSP43881/883                 | Digital Filter                                                 | 3-73  |

| HSP43891                     | Digital Filter                                                 | 3-35  |

| HSP43891/883                 | Digital Filter                                                 | 3-50  |

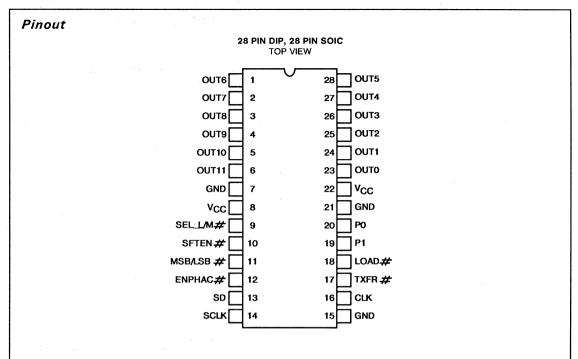

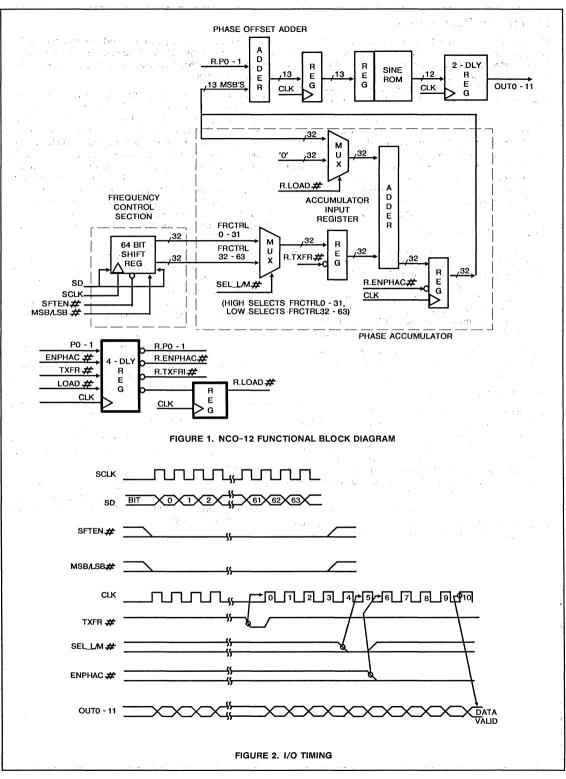

| HSP45102                     | 12 Bit Numerically Controlled Oscillator                       | 5-43  |

| HSP45106                     | 16 Bit Numerically Controlled Oscillator                       | 5-26  |

| HSP45106/883                 | 16 Bit Numerically Controlled Oscillator                       | 5-36  |

| HSP45116                     | Numerically Controlled Oscillator/Modulator                    | 5-3   |

| HSP45116/883                 | Numerically Controlled Oscillator/Modulator                    | 5-18  |

| HSP45240                     | Address Sequencer                                              | 6-3   |

| HSP45240/883                 | Address Sequencer                                              | 6-14  |

| HSP45256                     | Binary Correlator                                              | 6-33  |

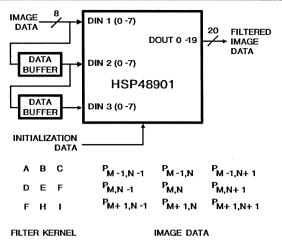

| HSP48901                     | 3 x 3 Image Filter                                             | 4-26  |

| HSP48908                     | Two Dimensional Convolver                                      | 4-3   |

| HSP48908/833                 | Two Dimensional Convolver                                      | 4-19  |

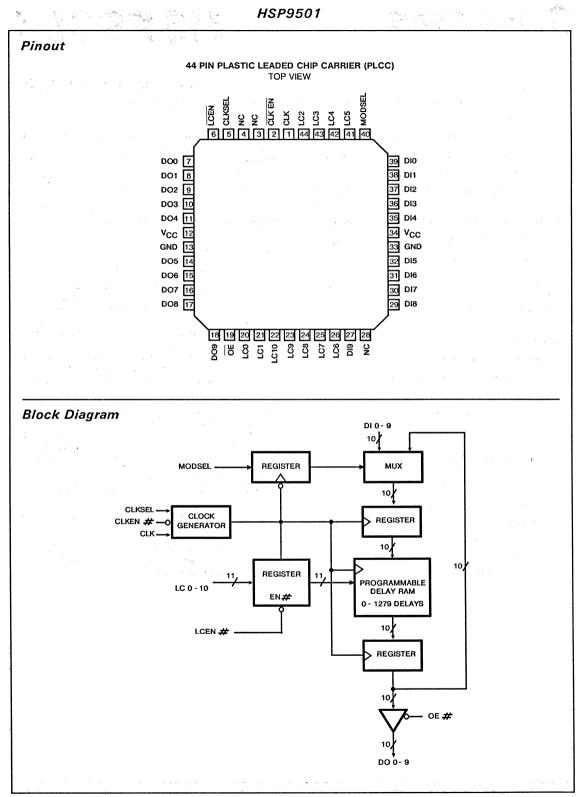

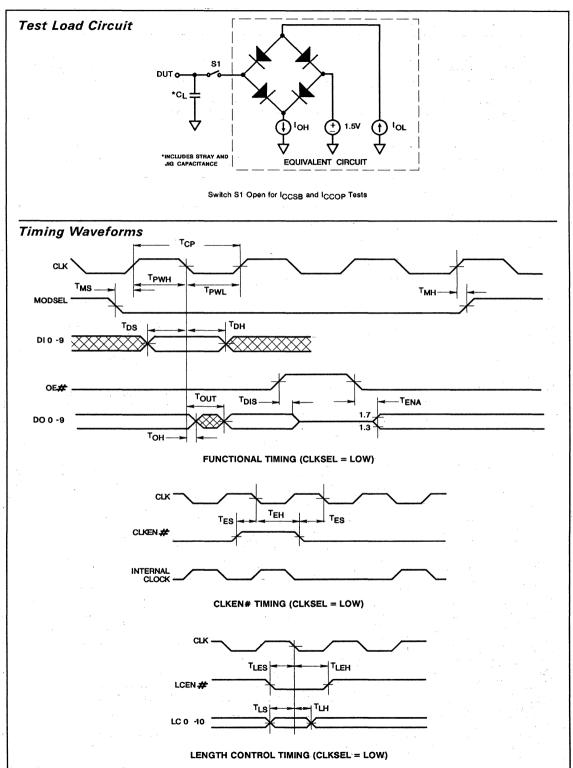

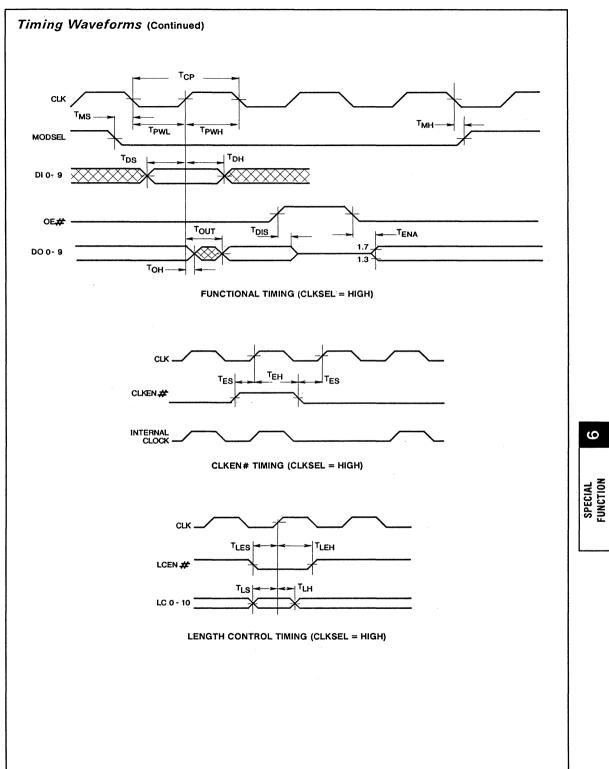

| HSP9501                      | Programmable Data Buffer                                       | 6-21  |

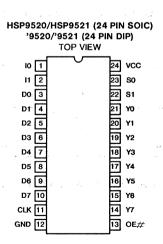

| HSP9520/9521<br>ISP9520/9521 | Multilevel Pipeline Register                                   | 6-28  |

DECI • MATE™ is a Trademark of Harris Corporation

#### **PRODUCT INDEX BY FAMILY**

| MULTIPLIERS                  |                                                                | PAGE  |

|------------------------------|----------------------------------------------------------------|-------|

| HMA510                       | 16 x 16-Bit CMOS Parallel Multiplier Accumulator               | 2-29  |

| HMA510/883                   | 16 x 16-Bit CMOS Parallel Multiplier Accumulator               | 2-36  |

| HMU16/HMU17                  | 16 x 16-Bit CMOS Parallel Multipliers                          | 2-3   |

| HMU16/883                    | 16 x 16-Bit CMOS Parallel Multiplier                           | 2-13  |

| HMU17/883                    | 16 x 16-Bit CMOS Parallel Multiplier                           | 2-21  |

| ONE DIMENSI                  | ONAL FILTERS                                                   |       |

| DECI • MATE                  | Harris HSP43220 Decimating Digital Filter Development Software | 3-31  |

| HSP43168                     | Dual FIR Filter                                                | 3-102 |

| HSP43220                     | Decimating Digital Filter                                      | 3-3   |

| HSP43220/883                 | Decimating Digital Filter                                      | 3-23  |

| HSP43481                     | Digital Filter                                                 | 3-81  |

| HSP43481/883                 | Digital Filter                                                 | 3-96  |

| HSP43881                     | Digital Filter                                                 | 3-58  |

| HSP43881/883                 | Digital Filter                                                 | 3-73  |

| HSP43891                     | Digital Filter                                                 | 3-35  |

| HSP43891/883                 | Digital Filter                                                 | 3-50  |

| TWO DIMENS                   | IONAL FILTERS                                                  |       |

| HSP48901                     | 3 x 3 Image Filter                                             | 4-26  |

| HSP48908                     | Two Dimensional Convolver                                      | 4-3   |

| HSP48908/833                 | Two Dimensional Convolver                                      | 4-19  |

| SIGNAL SYNT                  | HESIZERS                                                       |       |

| HSP45102                     | 12 Bit Numerically Controlled Oscillator                       | 5-43  |

| HSP45106                     | 16 Bit Numerically Controlled Oscillator                       | 5-26  |

| HSP45106/883                 | 16 Bit Numerically Controlled Oscillator                       | 5-36  |

| HSP45116                     | Numerically Controlled Oscillator/Modulator                    | 5-3   |

| HSP45116/883                 | Numerically Controlled Oscillator/Modulator                    | 5-18  |

| SPECIAL FUN                  | CTION                                                          | *     |

| HSP45240                     | Address Sequencer                                              | 6-3   |

| HSP45240/883                 | Address Sequencer                                              | 6-14  |

| HSP45256                     | Binary Correlator                                              | 6-33  |

| HSP9501                      | Programmable Data Buffer                                       | 6-21  |

| HSP9520/9521<br>ISP9520/9521 | Multilevel Pipeline Register                                   | 6-28  |

|                              |                                                                | 1.11  |

/883 Data Sheet Format - In the interests of conserving space, data sheets for /883 qualified products have been printed without the Pinouts, Pin Description, Waveforms, AC Test Load Circuit and Design Information sections. The information in these sections can be obtained from the corresponding portion of the commercial data sheet.

### **MULTIPLIERS**

#### PAGE

#### DATA SHEETS

| HMU16/HMU17 | 16 x 16-Bit CMOS Parallel Multipliers            | 2-3  |

|-------------|--------------------------------------------------|------|

| HMU16/883   | 16 x 16-Bit CMOS Parallel Multiplier             | 2-13 |

| HMU17/883   | 16 x 16-Bit CMOS Parallel Multiplier             | 2-21 |

| HMA510      | 16 x 16-Bit CMOS Parallel Multiplier Accumulator | 2-29 |

| HMA510/883  | 16 x 16-Bit CMOS Parallel Multiplier Accumulator | 2-36 |

2

na de la construcción de la constru En la construcción de la construcción

.

## HARRIS HMU16/HMU17

#### 16 x 16-Bit CMOS Parallel Multipliers

May 1991

#### Features

- 16 x 16-Bit Parallel Multiplier with Full 32-Bit Product

- High-Speed (35ns) Clocked Multiply Time

- Low Power Operation:

- ► ICCSB = 500µA Maximum

- ICCOP = 7.0mA Maximum @ 1MHz

- Supports Two's Complement, Unsigned Magnitude and Mixed Mode Multiplication

- HMU16 is Compatible with the AM29516, LMU16, IDT7216 and the CY7C516

- HMU17 is Compatible with the AM29517, LMU17, IDT7217 and the CY7C517

- TTL Compatible Inputs/Outputs

- Three-State Outputs

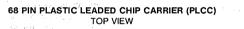

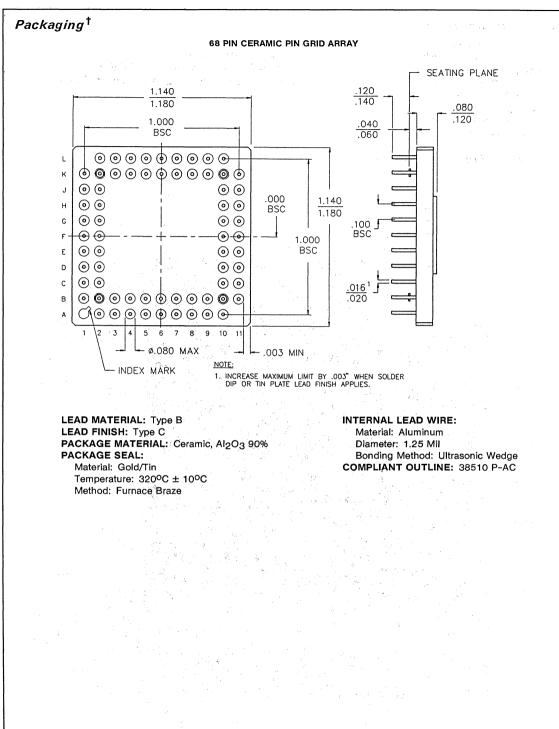

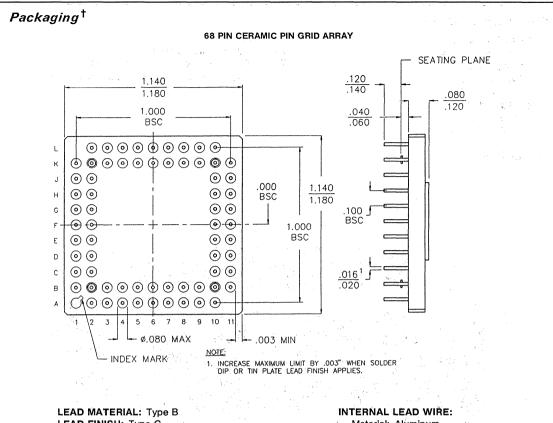

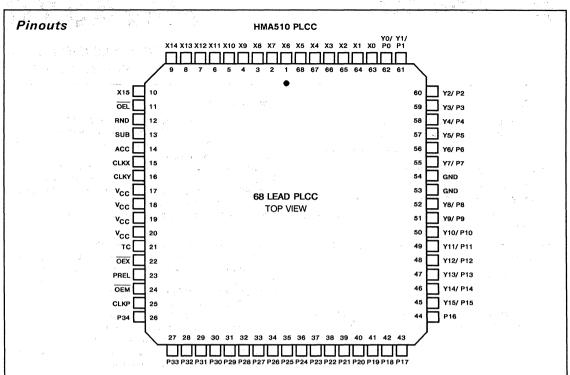

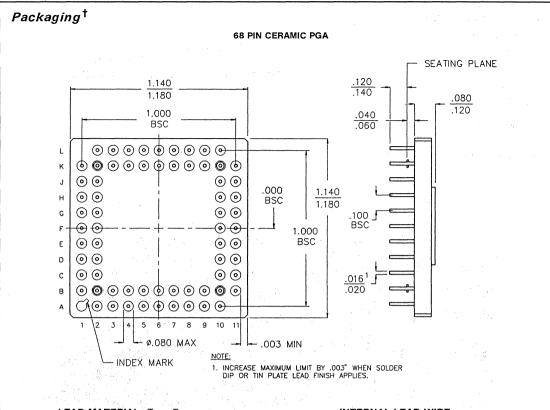

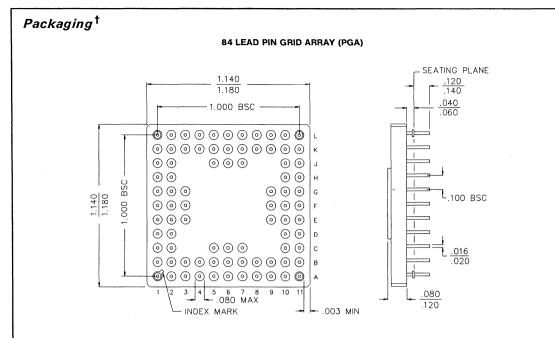

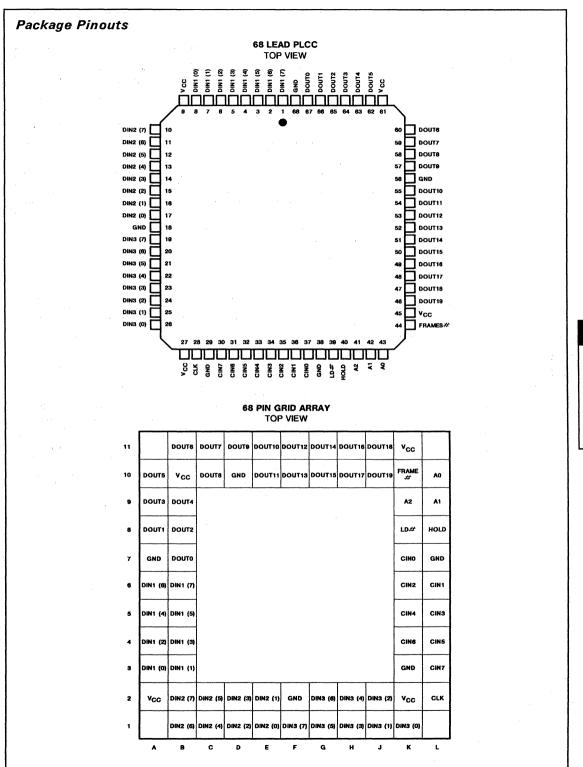

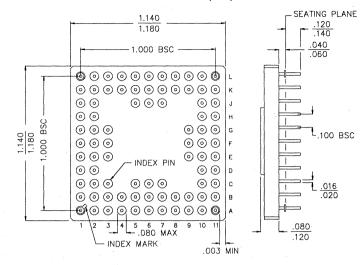

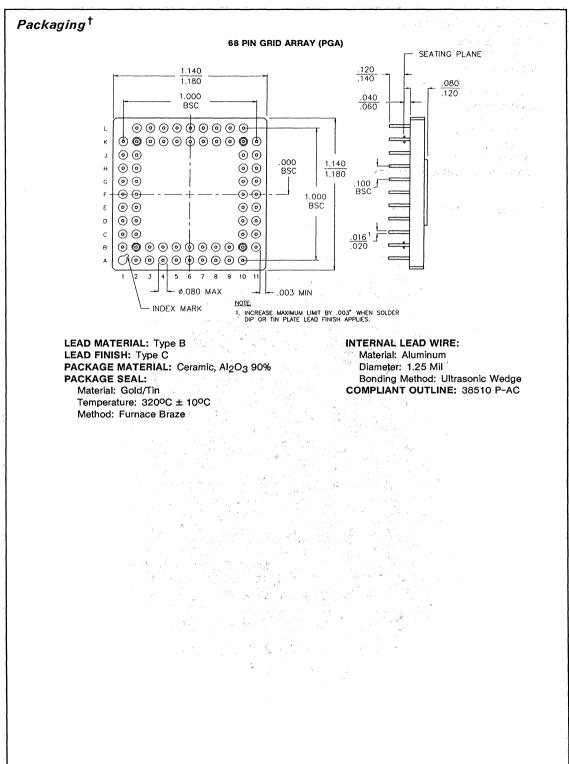

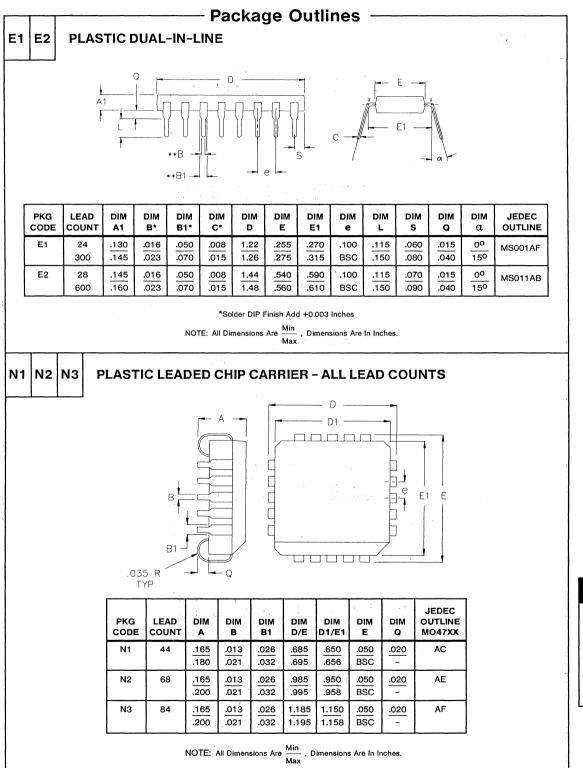

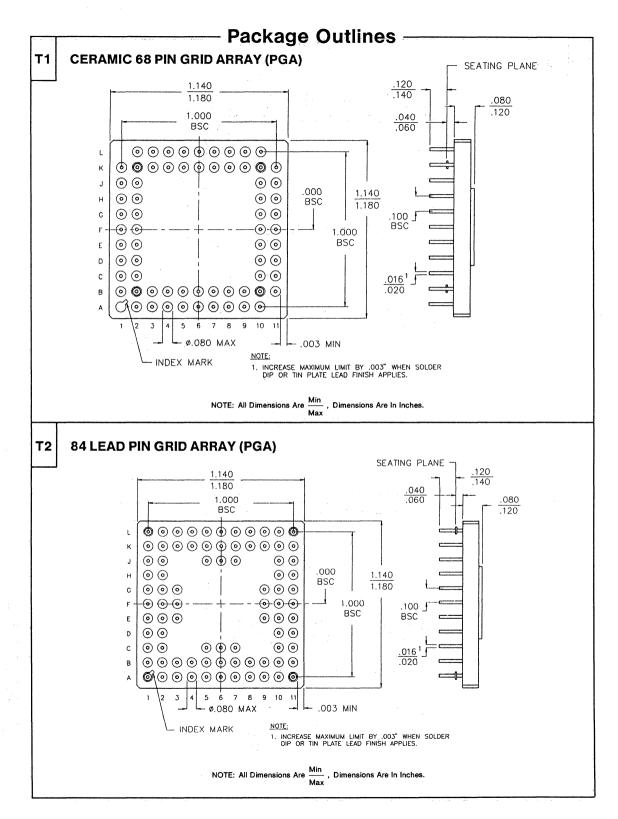

- Available in a Ceramic 68 Pin Grid Array (PGA) and 68 Pin Plastic Leaded Chip Carrier (PLCC)

#### Applications

- Fast Fourier Transform Analysis

- Digital Filtering

- Graphic Display Systems

- Image Processing

- Radar and Sonar

- Speech Synthesis and Recognition

#### Description

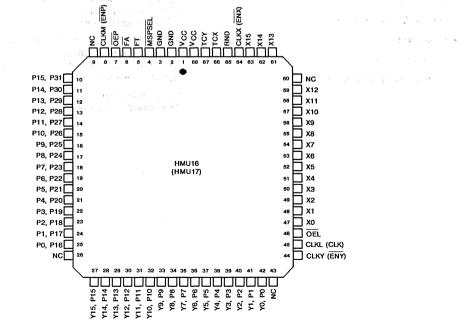

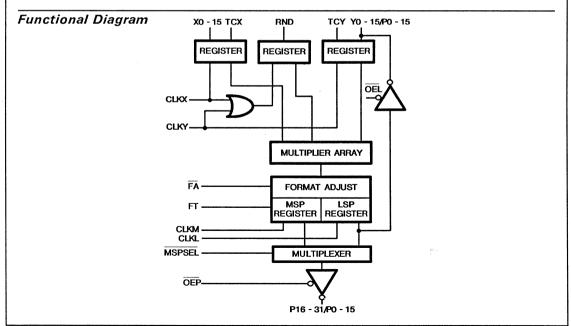

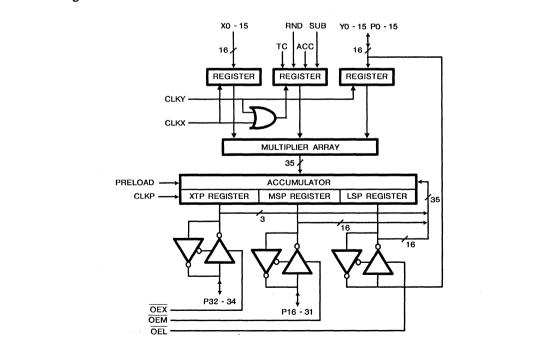

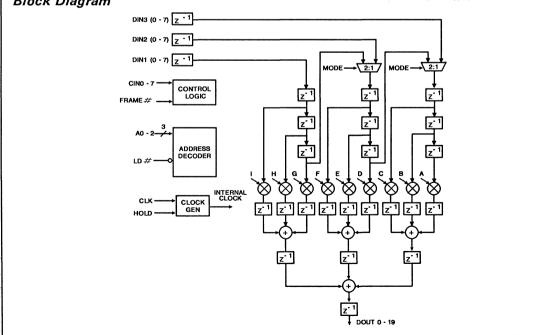

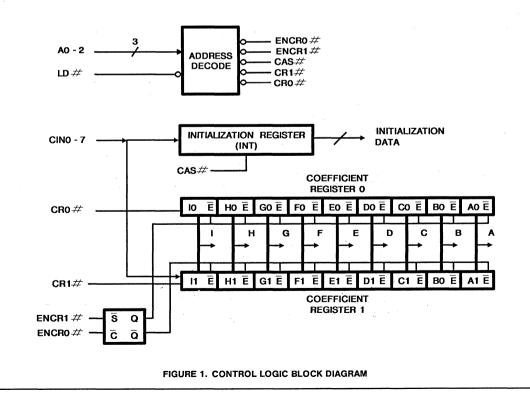

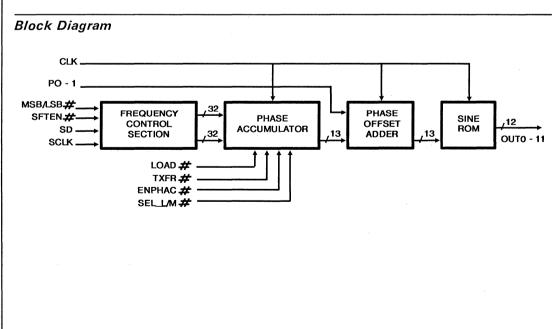

The HMU16/HMU17 are high speed, low power CMOS 16 x 16-bit multipliers ideal for fast, real time digital signal processing applications.

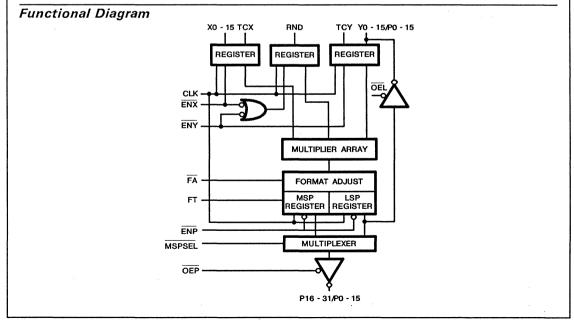

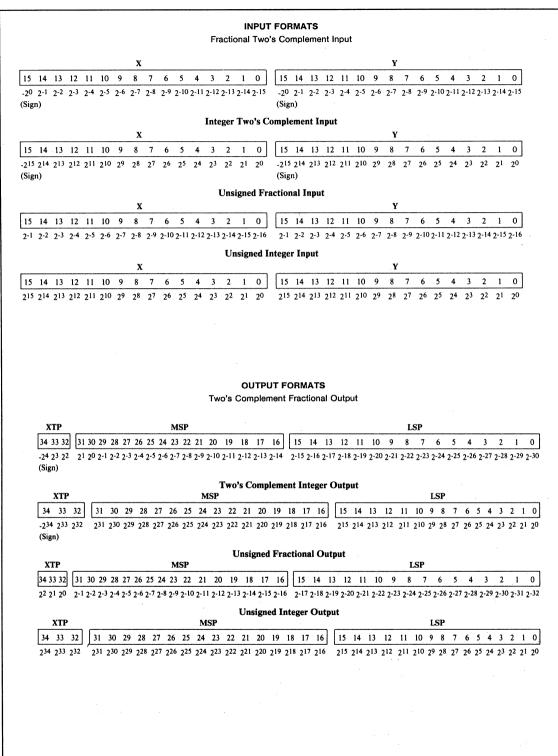

The X and Y operands along with their mode controls (TCX and TCY) have 17-bit input registers. The mode controls independently specify the operands as either two's complement or unsigned magnitude format, thereby allowing mixed mode multiplication operations.

Two 16-bit output registers are provided to hold the most and least significant halves of the result (MSP and LSP). For asynchronous output these registers may be made transparent through the use of the feedthrough control (FT).

Additional inputs are provided for format adjustment and rounding. The format adjust control (FA) allows the user to select either a left shifted 31-bit product or a full 32-bit product, whereas the round control (RND) provides the capability of rounding the most significant portion of the result.

The HMU16 has independent clocks (CLKX, CLKY, CLKL, CLKM) associated with each of these registers to maximize throughput and simplify bus interfacing. The HMU17 has only a single clock input (CLK), but makes use of three register enables (ENX, ENY and ENP). The ENX and ENY inputs control the X and Y input registers, while ENP controls both the MSP and LSP output registers. This configuration facilitates the use of the HMU17 for microprogrammed systems.

The two halves of the product may be routed to a single 16-bit three-state output port via a multiplexer, and in addition, the LSP is connected to the Y-input port through a separate three-state buffer.

All outputs of the HMU16/HMU17 multipliers also offer threestate control for multiplexing results onto multi-use busses.

#### HMU16/HMU17

20

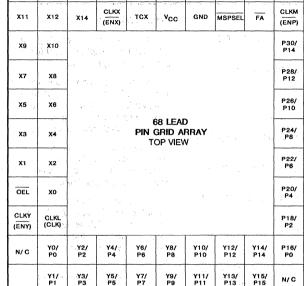

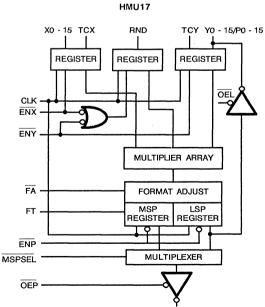

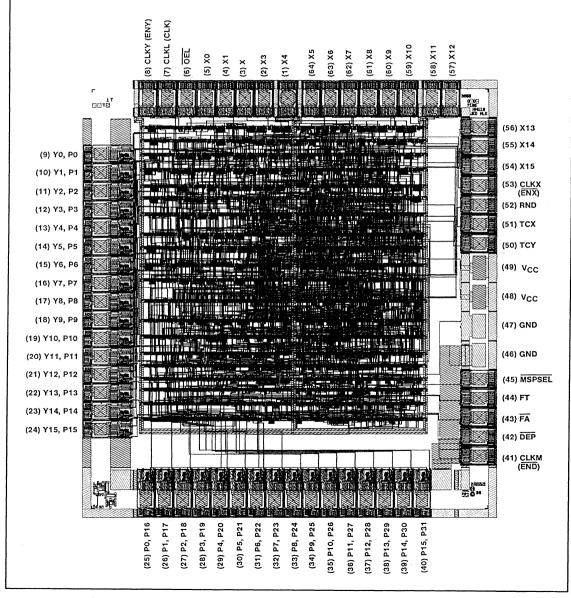

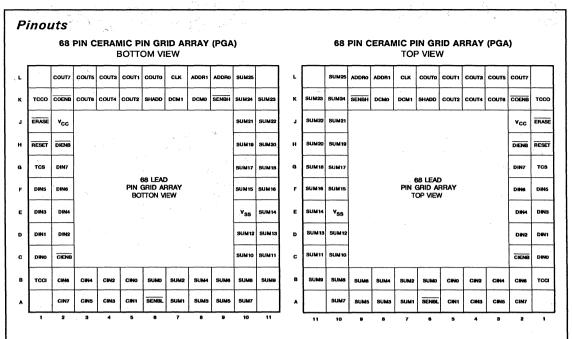

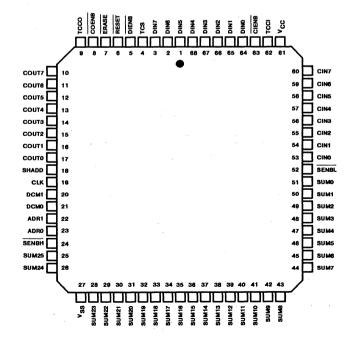

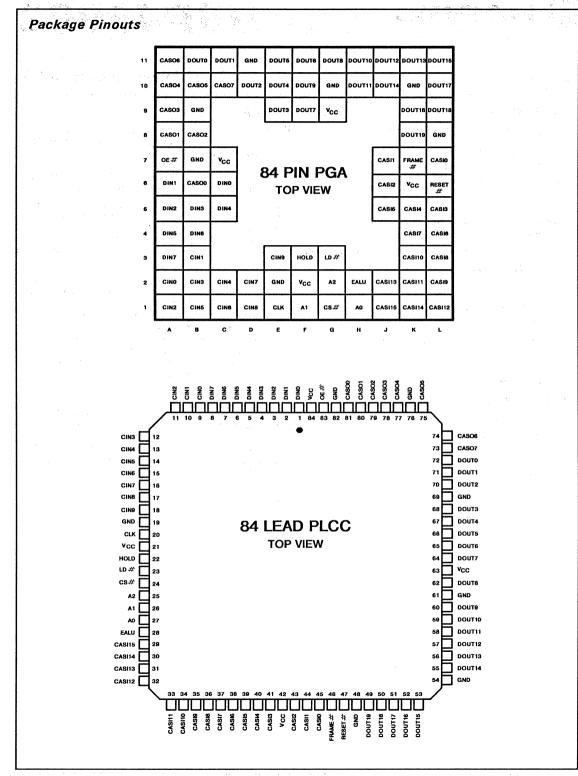

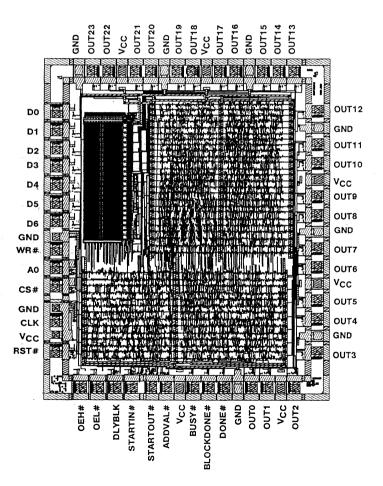

### Package Pinouts

8

X13

N/C

1.12

X15

RND

CERAMIC 68 PIN GRID ARRAY (PGA) TOP VIEW

тсү

GND

vcc

FT

OEP

N/C

P31/

P15

P29/

P13

P27/

P11

P25/

P9

P23/

P7

P21/

P5

P19/ P3

P17/

P1

| ĝ.  | 25 | έs.  | )<br>I |           |    |

|-----|----|------|--------|-----------|----|

| 949 | *; | ł.J  | <br>   | e<br>.+ 1 | Na |

|     |    | S 16 | ~      |           |    |

| ç, |  | 555 |  |

|----|--|-----|--|

|    |  |     |  |

т н т н т

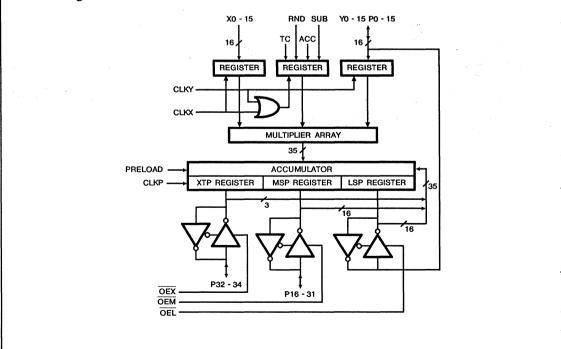

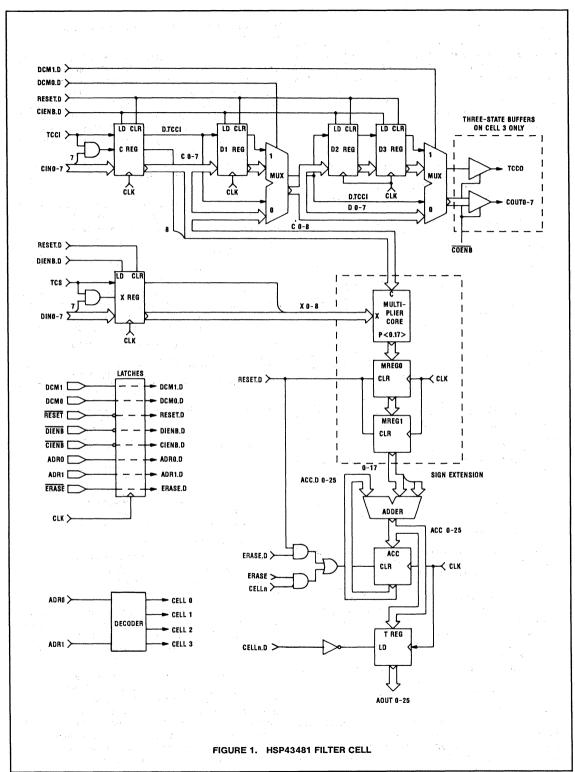

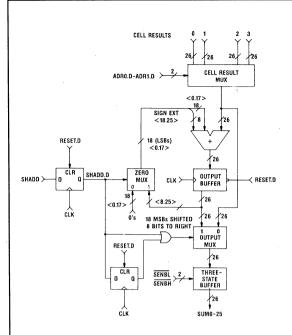

#### Functional Block Diagram

HMU16 X0 - 15 TCX RND TCY Y0 - 15/P0 - 15 REGISTER REGISTER REGISTER OEL 9 CLKX-CLKY-MULTIPLIER ARRAY FA FORMAT ADJUST MSP REGISTER LSP REGISTER FT -CLKM CLKL MSPSEL MULTIPLEXER OEP -P16 - 31/P0 - 15

P16 - 31/P0 - 15

N N

MULTIPLIERS

#### Pin Description

| SYMBOL             | PLCC<br>PIN NUMBER   | TYPE                  | DESCRIPTION                                                                                                                                                                                                                                                                                                        |

|--------------------|----------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| v <sub>cc</sub>    | 1,68                 | ,                     | $V_{CC}.$ The +5V power supply pins. A 0.1 $\mu\text{F}$ capacitor between the $V_{CC}$ and GND pin is recommended.                                                                                                                                                                                                |

| GND                | 2,3                  |                       | GND. The device ground.                                                                                                                                                                                                                                                                                            |

| X0-X15             | 47-59, 61-63         | I                     | X-Input Data. These 16 data inputs provide the multiplicand which may be in two's complement or unsigned magnitude format.                                                                                                                                                                                         |

| Y0-Y15/<br>P0-P15  | 27-42                | k <b>I/O</b><br>2     | Y-Input/LSP Output Data. This 16-Bit port is used to provide the multiplier which<br>may be in two's complement or unsigned magnitude format. It may also be used for<br>output of the Least Significant Product (LSP).                                                                                            |

| P16-P31/<br>P0-P15 | 10-25                | 0                     | Output Data. This 16-Bit port may provide either the MSP (P16-31) or the LSP (P0-15).                                                                                                                                                                                                                              |

| ТСҮ, ТСХ           | 66, 67               | ( <b>I</b>            | Two's Complement Control. Input data is interpreted as two's complement when this<br>control is HIGH. A LOW indicates the data is to be interpreted as unsigned<br>magnitude format.                                                                                                                               |

| FT                 | 5                    | Ι.                    | Feedthrough Control. When this control is HIGH, both the MSP and LSP registers ar transparent. When LOW, the registers are latched by their associated clock signals.                                                                                                                                              |

| FA                 | 6                    | <b>I</b>              | Format Adjust Control. A full 32-bit product is selected when this control line<br>is HIGH. A LOW on this control line selects a left shifted 31-bit product with the sign<br>bit replicated in the LSP. This control is normally HIGH except for certain two's<br>complement integer and fractional applications. |

| RND                | 65                   | l                     | Round Control. When this control is HIGH, a one is added to the Most Significant Bit<br>(MSB) of the LSP. This position is dependent on the FA control; FA = HIGH indicates<br>RND adds to the 2–15 bit (P15), and FA = LOW indicates RND adds to the 2 <sup>-16</sup><br>bit (P14).                               |

| MSPSEL             | 4                    | l                     | Output Multiplexer Control. When this control is LOW, the MSP is available for output at the dedicated output port, and the LSP is available at the Y-input/LSP output port. When MSPSEL is HIGH, the LSP is available at both ports and the MSP is not available for output.                                      |

| OEL                | 46                   | 1                     | Y-In/P0-15 Output Port Three-state Control. When $\overline{\text{OEL}}$ is HIGH, the output drivers are in the high impedance state. This state is required for Y-data input. When $\overline{\text{OEL}}$ is LOW, the port is enabled for LSP output.                                                            |

| OEP                | 7                    | l                     | P16-31/P0-15 Output Port Three-state Control. A LOW on this control line enables the output port. When OEP is HIGH, the output drivers are in the high impedance state.                                                                                                                                            |

| The following      | Pin Descriptions a   | oply to the HM        | U16 only.                                                                                                                                                                                                                                                                                                          |

| CLKX               | 64                   |                       | X-Register Clock. The rising edge of this clock loads the X-data input register along with the TCX and RND registers.                                                                                                                                                                                              |

| CLKY               | 44                   | <b>I</b> <sup>i</sup> | Y-Register Clock. The rising edge of this clock loads the Y-data input register along with the TCY and RND registers.                                                                                                                                                                                              |

| CLKM               | 8                    | I.,                   | MSP Register Clock. The rising edge of CLKM loads the most significant product (MSP) register.                                                                                                                                                                                                                     |

| CLKL               | 45                   |                       | LSP Register Clock. The rising edge of CLKL loads the least significant product (LSP) register.                                                                                                                                                                                                                    |

| The following      | J Pin Descriptions a | pply to the HM        | U17 only.                                                                                                                                                                                                                                                                                                          |

| CLK                | 45                   | 1                     | Clock. The rising edge of this clock will load all enabled registers.                                                                                                                                                                                                                                              |

| ENX                | 64                   | I .                   | X-Register Enable. When ENX is LOW, the X-register is enabled; X-input data and TCX will be latched at the rising edge of CLK. When ENX is high, the X-register is in a hold mode.                                                                                                                                 |

| ENY                | 44                   | 1                     | Y-Register Enable. $\overline{\text{ENY}}$ enables the Y-register. (See $\overline{\text{ENX}}$ ).                                                                                                                                                                                                                 |

| ENP                | 8                    | I                     | Product Register Enable. $\overline{ENP}$ enables the product register. Both the MSP and LSP sections are enabled by $\overline{ENP}$ . (See $\overline{ENX}$ ).                                                                                                                                                   |

#### Functional Description

The HMU16/HMU17 are high speed 16 X 16-bit multipliers designed to perform very fast multiplication of two 16-bit binary numbers. The two 16-bit operands (X and Y) may be independently specified as either two's complement or unsigned magnitude format by the two's complement controls (TCX and TCY). When either of these control lines is LOW, the respective operand is treated as an unsigned 16-bit value; and when it is HIGH, the operand is treated as a signed value represented in two's complement format. The operands along with their respective controls are latched at the rising edge of the associated clock signal. The HMU16 accomplishes this through the use of independent clock inputs for each of the input registers (CLKX and CLKY), while the HMU17 utilizes a single clock signal (CLK) along with the X and Y register enable inputs (ENX and ENY).

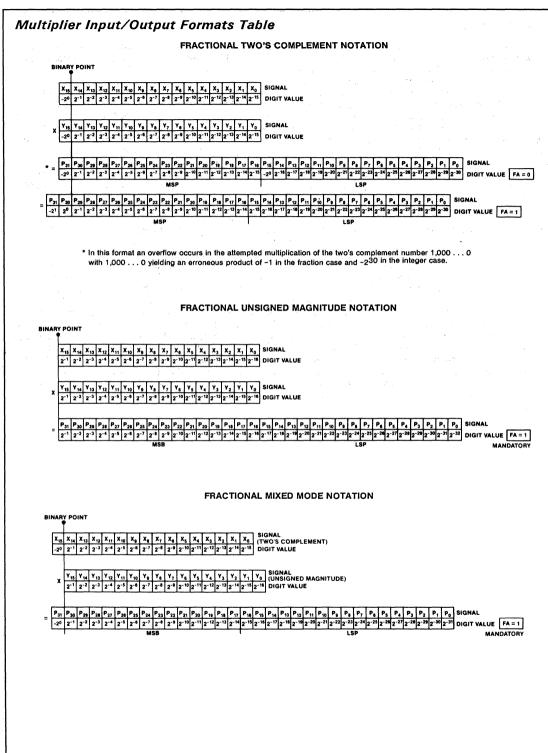

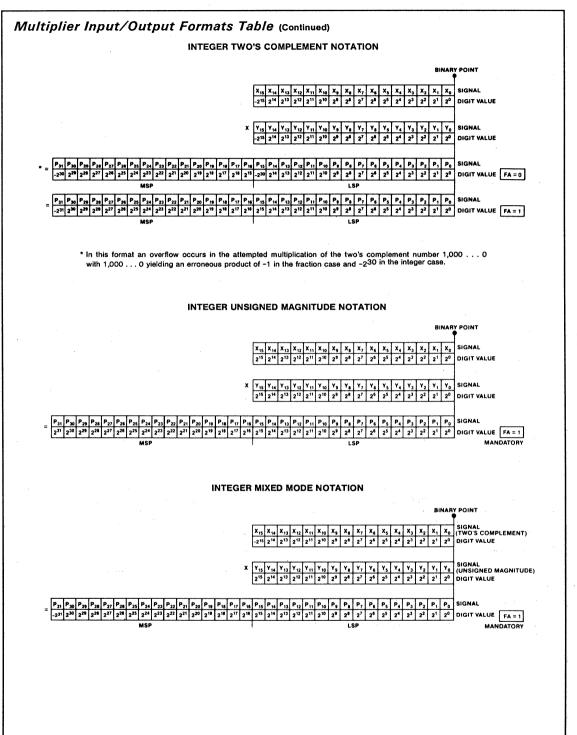

Input controls are also provided for rounding and format adjustment of the 32-bit product. The Round input (RND) is provided to accomodate rounding of the most significant portion of the product by adding one to the Most Significant Bit (MSB) of the LSP register. The position of the MSB is dependent on the state of the Format Adjust Control (See Pin Descriptions and Multiplier Input/Output Format Tables). The Round input is latched into the RND register whenever either of the input registers is clocked. The Format Adjust control (FA) allows the product output to be formatted. When the FA control is HIGH, a full 32-bit product is output; and when FA is LOW, a left-shifted 31-bit product is output with the sign bit replicated in bit position 15 of the LSP. The FA control must be HIGH for unsigned magnitude, and mixed mode multiplication

operations. It may be LOW for certain two's complement integer and fractional operations only (See Multiplier Input/ Output Formats Table).

The HMU16/HMU17 multipliers are equipped with two 16-bit output registers (MSP and LSP) which are provided to hold the most and least significant portions of the resultant product respectively. The HMU16 uses independent clocks (CLKM and CLKL) for latching the two output registers, while the HMU17 uses a single clock input (CLK) along with the Product Latch Enable (ENP). The MSP and LSP registers may also be made transparent for asynchronous output through the use of the Feedthrough control (FT).

There are two output configurations which may be selected when using the HMU16/HMU17 multipliers. The first configuration allows the simultaneous access of the most and least significant halves of the product. When the MSPSEL input is LOW, the Most Significant Product will be available at the dedicated output port (P16-31/P0-15). The Least Significant Product is simultaneously available at the bi-directional port shared with the Y-inputs (Y0-15/P0-15) through the use of the LSP output enable (OEL). The other output configuration involves multiplexing the MSP and LSP registers onto the dedicated output port through the use of the MSPSEL control. When the MSPSEL control is LOW, the Most Significant Product will be available at the dedicated output port; and when MSPSEL is HIGH, the Least Significant Product will be available at this port. This configuration allows access of the entire 32-bit product by a 16-bit wide system bus.

#### HMU16/HMU17

S

MULTIPLIERS

#### Absolute Maximum Ratings

| Supply Voltage                                                                                                                                                                            |                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Input, Output or I/O Voltage Applied                                                                                                                                                      |                                  |

| Storage Temperature Range                                                                                                                                                                 |                                  |

| Gate Count                                                                                                                                                                                | 4500 Gates                       |

| θ <sub>ja</sub>                                                                                                                                                                           | 43.2°C/W (PLCC), 42.69°C/W (PGA) |

| θ <mark>ίς</mark>                                                                                                                                                                         | 15.1°C/W (PLCC), 10.0°C/W (PGA)  |

| Maximum Package Power Dissipation at 70°C                                                                                                                                                 |                                  |

| Junction Temperature                                                                                                                                                                      |                                  |

| Lead Temperature (Soldering, Ten Seconds)                                                                                                                                                 | +300°C                           |

| CAUTION: Stresses above those listed in the "Absolute Maximum Ratings" may cause perman<br>and operation at these or any other conditions above those indicated in the operations section |                                  |

#### **Operating Conditions**

| Operating Voltage Range     | $\pm 4.75$ // to $\pm 5.25$ // |

|-----------------------------|--------------------------------|

| Operating voltage hange     | 14.750 10 15.250               |

| Operating Temperature Range | $0^{\circ}C$ to +70^{\circ}C   |

| SYMBOL | PARAMETER                      | MIN | МАХ | UNITS | TEST CONDITIONS                                                     |

|--------|--------------------------------|-----|-----|-------|---------------------------------------------------------------------|

| VIH    | Logical One Input Voltage      | 2.0 | -   | v     | V <sub>CC</sub> = 5.25V                                             |

| VIL    | Logical Zero Input Voltage     | -   | 0.8 | Ý     | V <sub>CC</sub> = 4.75V                                             |

| VOH    | Output High Voltage            | 2.6 |     | v     | -I <sub>OH</sub> = -400μA, V <sub>CC</sub> = 4.75V                  |

| VOL    | Output Low Voltage             |     | 0.4 | v     | $I_{OL} = +4.0$ mA, $V_{CC} = 4.75$ V                               |

| l      | Input Leakage Current          | -10 | 10  | μA    | $V_{I} = V_{CC} \text{ or GND}, V_{CC} = 5.25 V$                    |

| ю      | Output or I/O Leakage Current  | -10 | 10  | μA    | $V_{O} = V_{CC}$ or GND, $V_{CC} = 5.25V$                           |

| ICCSB  | Standby Power Supply Current   | -   | 500 | μA    | $V_I = V_{CC}$ or GND, $V_{CC} = 5.25V$<br>Outputs Open             |

| ICCOP  | Operating Power Supply Current |     | 7.0 | mA    | $V_I = V_{CC} \text{ or GND}, V_{CC} = 5.25V$<br>f = 1 MHz (Note 1) |

#### **D.C. Electrical Specifications** ( $V_{CC} = 5.0V + 5\%$ , $T_A = 0^{\circ}C$ to $+70^{\circ}C$ )

#### Capacitance $(T_A = +25^{\circ}C, Note 2)$

| SYMBOL          | PARAMETER          | TYPICAL | UNITS | TEST CONDITIONS                                  |

|-----------------|--------------------|---------|-------|--------------------------------------------------|

| C <sub>IN</sub> | Input Capacitance  | 15      | pF    | Frequency = 1MHz.<br>All measurements referenced |

| COUT            | Output Capacitance | 10      | pF    | to device Ground.                                |

| CI/O            | I/O Capacitance    | 10      | pF    |                                                  |

#### NOTES:

Operating Supply Current is proportional to frequency, Typical rating is 5mA/MHz.

2. Not tested, but characterized at initial design and at major process/ design changes.

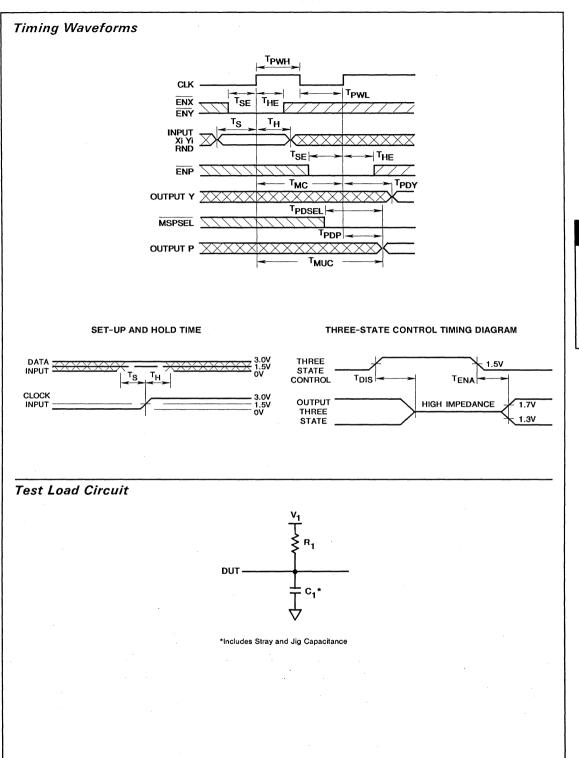

|                  |                                                                | HMU16/H | MU17-35 | HMU16/H | MU17-45 |       | TEST             |  |

|------------------|----------------------------------------------------------------|---------|---------|---------|---------|-------|------------------|--|

| SYMBOL           | PARAMETER                                                      | MIN     | МАХ     | MIN     | МАХ     | UNITS | CONDITIONS       |  |

| тмис             | Unclocked Multiply Time                                        | -       | 55      | -       | 70      | ns    |                  |  |

| тмс              | Clocked Multiply Time                                          | -       | 35      | -       | 45      | ns    |                  |  |

| TS               | X, Y, RND Setup Time                                           | 15      | -       | 18      | -       | ns    |                  |  |

| тн               | X, Y, RND Hold Time                                            | 2       | -       | 2       | -       | ns    |                  |  |

| Трун             | Clock Pulse Width High                                         | 10      | -       | 15      | -       | ns    |                  |  |

| TPWL             | Clock Pulse Width Low                                          | 10      | -       | 15      | -       | ns    |                  |  |

| TPDSEL           | MSPSEL to Product Out                                          | -       | 22      | -       | 25      | ns    |                  |  |

| T <sub>PDP</sub> | Output Clock to P                                              | -       | 22      | -       | 25      | ns    |                  |  |

| TPDY             | Output Clock to Y                                              | -       | 22      | -       | 25      | ns    |                  |  |

| TENA             | 3-State Enable Time                                            | -       | 22      | -       | 25      | ns    | Note 1           |  |

| TDIS             | 3-State Disable Time                                           | -       | 22      | -       | 25      | ns    |                  |  |

| TSE              | Clock Enable Setup Time<br>(HMU17 only)                        | 15      | -       | 15      | -       | ns    |                  |  |

| THE              | Clock Enable Hold Time<br>(HMU17 only)                         | 2       | -       | 2       | -       | ns    |                  |  |

| THCL             | Clock Low Hold Time CLKXY<br>Relative to CLKML<br>(HMU16 only) | 0       | -       | 0       | -       | ns    | Note 2           |  |

| т <sub>R</sub>   | Output Rise Time                                               | -       | 8       | -       | 8       | ns    | From 0.8V to 2.0 |  |

| TF               | Output Fall Time                                               | -       | 8       | -       | 8       | ns    | From 2.0V to 0.8 |  |

#### Specifications HMU16/HMU17

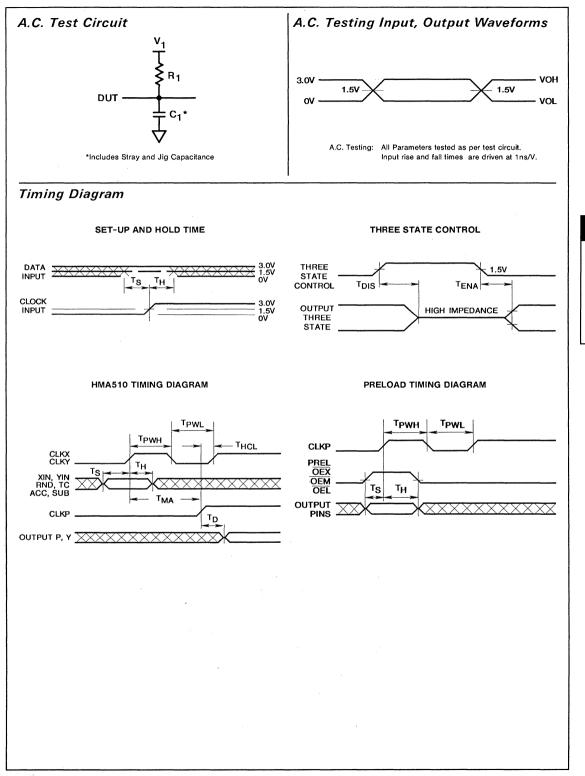

A.C. Electrical Specifications ( $V_{CC} = 5.0V + 5\%$ ,  $T_{\Delta} = 0^{\circ}C$  to +70°C. Note 3)

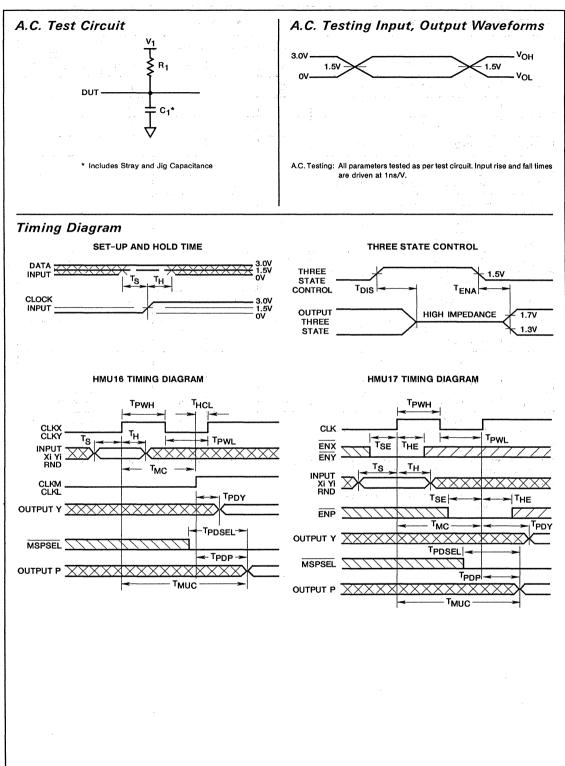

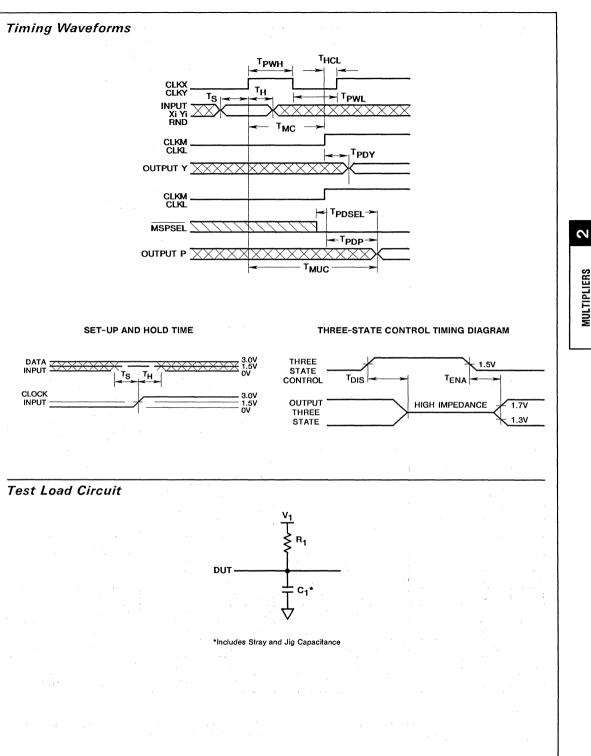

NOTES:

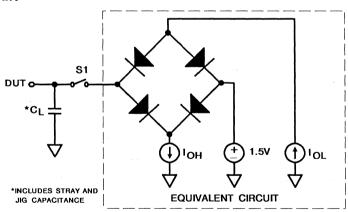

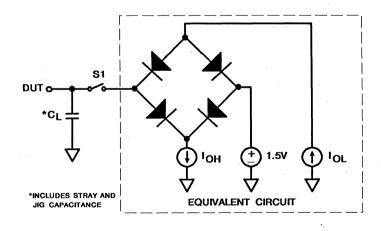

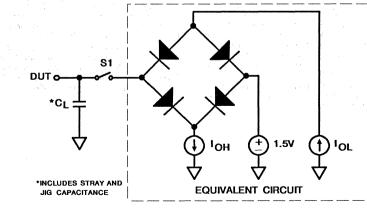

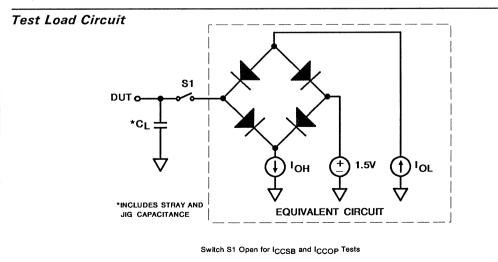

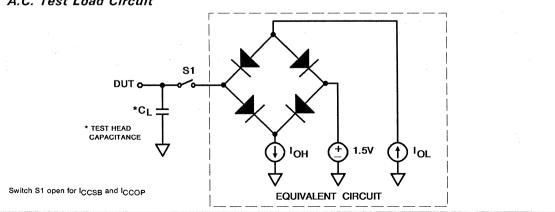

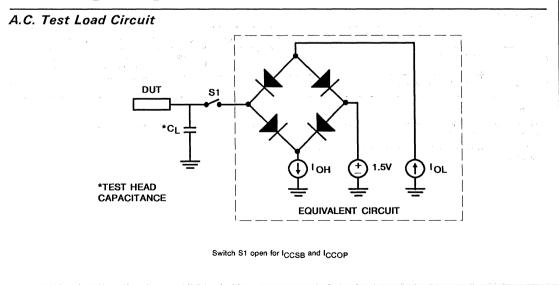

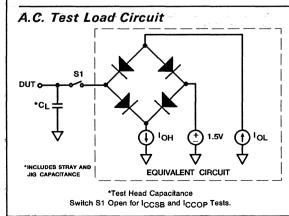

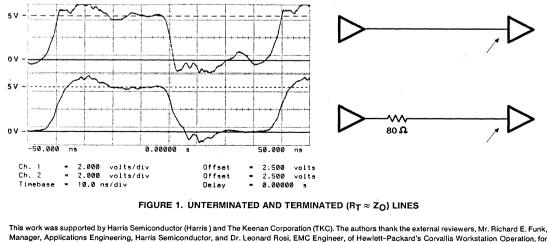

1. Transition is measured at ±200mV from steady state voltage with loading specified in Figure 1, V1 = 1.5V, R1 = 500 $\Omega$  and C1 = 40pF

To ensure the correct product is entered in the output registers, new data may not be entered into the input registers before the output registers have been clocked.

3. For A.C. Test load, Refer to Figure 1, with V\_1 = 2.4V, R\_1 = 500 \Omega and C\_1 = 40 pF

2

*HMU16/HMU17*

## HMU16/883

#### May 1991

#### Features

- This Circuit is Processed in Accordance to Mil-Std-883 and is Fully Conformant Under the Provisions of Paragraph 1.2.1.

- 16 x 16-Bit Parallel Multiplier with Full 32-Bit Product

- High-Speed (45ns) Clocked Multiply Time

- Low Power CMOS Operation:

- ► ICCSB = 500µA Maximum

- ICCOP = 7.0mA Maximum @ 1MHz

- HMU16 is compatible with the AM29516, LMU16, IDT7216, and the CY7C516

- Supports Two's Complement, Unsigned Magnitude and Mixed Mode Multiplication

- TTL Compatible Inputs/Outputs

- Three-State Outputs

- Available in a 68 Lead Pin Grid Array Package

#### 16 x 16-Bit CMOS Parallel Multiplier

#### Description

The HMU16 is a high speed, low power CMOS 16 x 16-bit parallel multiplier ideal for fast, real time digital signal processing applications. The 16-bit X and Y operands may be independently specified as either two's complement or unsigned magnitude format, thereby allowing mixed mode multiplication operations.

Additional inputs are provided to accommodate format adjustment and rounding of the 32-bit product. The Format Adjust control allows the user to select a 31-bit product with the sign bit replicated in the LSP. The Round control provides for rounding the most significant portion of the result by adding one to the most significant bit of the LSP.

Two 16-bit output registers (MSP and LSP) are provided to hold the most and least significant portions of the result, respectively. These registers may be made transparent for asynchronous operation through the use of the feedthrough control (FT). The two halves of the product may be routed to a single 16-bit three-state output port via the output multiplexer control, and in addition, the LSP is connected to the Y-input port through a separate three-state buffer.

The HMU16 utilizes independent clock signals (CLKX, CLKY, CLKL, CLKM) to latch the input operands and output product registers. This configuration maximizes throughput and simplifies bus interfacing. All outputs of the HMU16 also offer three-state control for multiplexing onto multi-use system busses.

Copyright © Harris Corporation 1991

3

MULTIPLIERS

| Absolute |  |  |

|----------|--|--|

|          |  |  |

| Supply Voltage+8.0V                                               |

|-------------------------------------------------------------------|

| Input or Output Voltage Applied GND-0.5V to V <sub>CC</sub> +0.5V |

| Storage Temperature Range65°C to +150°C                           |

| Junction Temperature                                              |

| Lead Temperature (Soldering 10 sec)                               |

| ESD ClassificationClass 1                                         |

|                                                                   |

#### **Reliability Information**

| Thermal Resistance<br>Ceramic PGA Package | <sup>θ</sup> ja<br>42.69°C/W | <sup>θ</sup> jc<br>10.0⁰C/W |

|-------------------------------------------|------------------------------|-----------------------------|

| Maximum Package Power Dissipation at      | +125°C                       |                             |

| Ceramic PGA Package                       |                              | 1.17 Watt                   |

| Gate Count                                |                              | 4500 Gates                  |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### **Operating Conditions**

#### TABLE 1. HMU16/883 D.C. ELECTRICAL PERFORMANCE CHARACTERISTICS

Device Guaranteed and 100% Tested

| and a second |        | en e                                            | [                    |                                                           | LIM | ITS | [          |

|----------------------------------------------------------------------------------------------------------------|--------|-------------------------------------------------------------------------------------|----------------------|-----------------------------------------------------------|-----|-----|------------|

| PARAMETER                                                                                                      | SYMBOL | CONDITIONS                                                                          | GROUP A<br>SUBGROUPS | TEMPERATURE                                               | MIN | MAX | UNITS      |

| Logical One Input<br>Voltage                                                                                   | VIH    | V <sub>CC</sub> = 5.5V                                                              | 1, 2, 3              | -55 <sup>0</sup> C ≤ T <sub>A</sub> ≤ +125 <sup>0</sup> C | 2.2 |     | V          |

| Logical Zero Input<br>Voltage                                                                                  | VIL    | $V_{CC} = 4.5V$                                                                     | 1, 2, 3              | $-55^{\circ}C \le T_{A} \le +125^{\circ}C$                | -   | 0.8 | v          |

| Output HIGH Voltage                                                                                            | VOH    | I <sub>OH</sub> = -400μA<br>V <sub>CC</sub> = 4.5V (Note 1)                         | 1, 2, 3              | -55°C ≤ T <sub>A</sub> ≤ +125°C                           | 2.6 |     | . <b>V</b> |

| Output LOW Voltage                                                                                             | VOL    | I <sub>OL</sub> = +4.0mA<br>V <sub>CC</sub> = 4.5V (Note 1)                         | 1, 2, 3              | -55°C ≤ T <sub>A</sub> ≤ +125°C                           | -   | 0.4 | ۷          |

| Input Leakage Current                                                                                          | 4      | $V_{IN} = V_{CC}$ or GND<br>$V_{CC} = 5.5V$                                         | 1, 2, 3              | -55°C ≤ T <sub>A</sub> ≤ +125°C                           | -10 | +10 | μA         |

| Output or I/O Leakage<br>Current                                                                               | 10     | $V_{OUT} = V_{CC} \text{ or GND}$<br>$V_{CC} = 5.5V$                                | 1, 2, 3              | -55°C ≤ T <sub>A</sub> ≤ +125°C                           | -10 | +10 | μΑ         |

| Standby Power Supply<br>Current                                                                                | ICCSB  | $V_{IN} = V_{CC} \text{ or GND},$<br>$V_{CC} = 5.5V, Outputs$<br>Open               | 1, 2, 3              | -55°C ≤ T <sub>A</sub> ≤ +125°C                           | -   | 500 | μА         |

| Operating Power<br>Supply Current                                                                              | ICCOP  | f = 1.0MHz,<br>$V_{IN} = V_{CC} \text{ or GND}$<br>$V_{CC} = 5.5V \text{ (Note 2)}$ | 1, 2, 3              | -55°C ≤ T <sub>A</sub> ≤ +125°C                           | -   | 7.0 | mA         |

| Functional Test                                                                                                | FT     | (Note 3)                                                                            | 7,8                  | -55°C ≤ T <sub>A</sub> ≤ +125°C                           | -   | -   |            |

#### NOTES:

1. Interchanging of force and sense conditions is permitted.

2. Operating Supply Current is proportional to frequency, typical rating is 5mA/MHz.

3. Tested as follows: f = 1MHz, V<sub>IH</sub> (Clock Inputs) = 3.0, V<sub>IH</sub> (All other inputs) = 2.6, V<sub>IL</sub> = 0.4, V<sub>OH</sub>  $\geq$  1.5V, and V<sub>OL</sub>  $\leq$  1.5V.

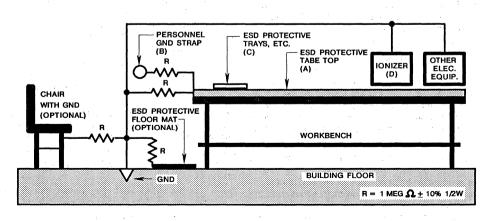

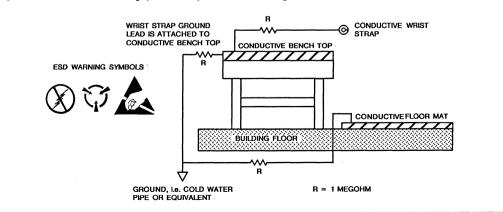

CAUTION: These devices are sensitive to electrostatic discharge. Proper IC handling procedures should be followed.

#### TABLE 2. HMU16/883 A.C. ELECTRICAL PERFORMANCE CHARACTERISTICS

Device Guaranteed and 100% Tested

|                                                   |                 | (NOTE 1)   | GROUP A               |                                            | -4  | 15  | -6  | 50  |       |

|---------------------------------------------------|-----------------|------------|-----------------------|--------------------------------------------|-----|-----|-----|-----|-------|

| PARAMETER                                         | SYMBOL          | CONDITIONS | SUBGROUPS             | TEMPERATURE                                | MIN | МАХ | MIN | мах | UNITS |

| Unclocked Multiply<br>Time                        | тмис            |            | 9, 10, 11             | -55°C ≤ T <sub>A</sub> ≤ +125°C            |     | 70  | -   | 90  | ns    |

| Clocked Multiply Time                             | т <sub>мс</sub> |            | <sup></sup> 9, 10, 11 | $-55^{\circ}C \le T_{A} \le +125^{\circ}C$ | -   | 45  | -   | 60  | ns    |

| X, Y, RND Setup Time                              | т <sub>S</sub>  |            | 9, 10, 11             | $-55^{\circ}C \le T_{A} \le +125^{\circ}C$ | 18  | -   | 20  | -   | ns    |

| Clock HIGH Pulse<br>Width                         | Трун            |            | 9, 10, 11             | -55°C ≤ T <sub>A</sub> ≤ +125°C            | 15  | -   | 20  | -   | ns    |

| Clock LOW Pulse<br>Width                          | TPWL            |            | 9, 10, 11             | -55°C ≤ T <sub>A</sub> ≤ +125°C            | 15  | -   | 20  | -   | ns    |

| MSPSEL to Product<br>Out                          | TPDSEL          |            | 9, 10, 11             | $-55^{\circ}C \le T_{A} \le +125^{\circ}C$ | -   | 25  | -   | 30  | ns    |

| Output Clock to P                                 | TPDP            |            | 9, 10, 11             | $-55^{\circ}C \le T_{A} \le +125^{\circ}C$ | -   | 25  | -   | 30  | ns    |

| Output Clock to Y                                 | TPDY            | ·.         | 9, 10, 11             | $-55^{\circ}C \le T_{A} \le +125^{\circ}C$ | -   | 25  | -   | 30  | ns    |

| 3-State Enable Time                               | TENA            | (Note 2)   | 9, 10, 11             | $-55^{\circ}C \le T_{A} \le +125^{\circ}C$ | -   | 25  | -   | 30  | ns    |

| Clock Low Hold Time<br>CLKXY Relative to<br>CLKML | THCL            | (Note 3)   | 9, 10, 11             | -55°C ≤ T <sub>A</sub> ≤ +125°C            | 0   | -   | 0   | -   | ns    |

3 MULTIPLIERS

#### NOTES:

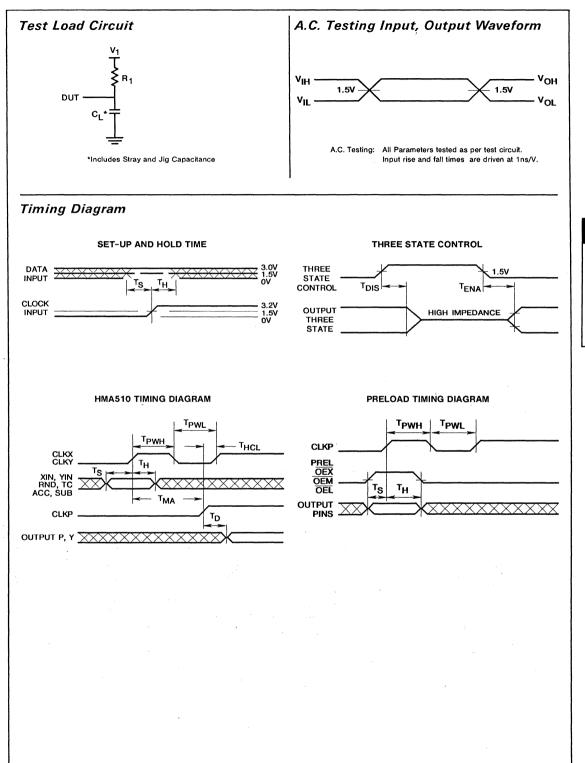

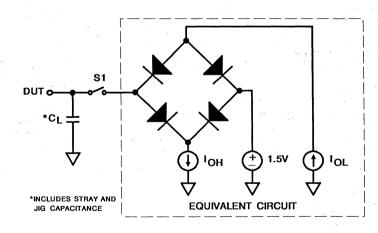

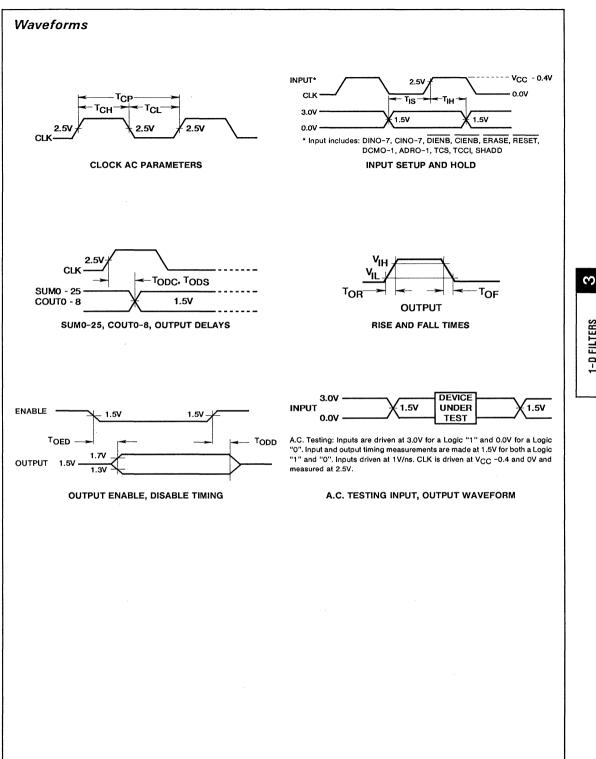

1. AC Testing as follows: Input levels 0V and 3.0V, Timing reference levels = 1.5V, Input rise and fall times driven at 1ns/V, Output load per test load circuit, with V<sub>1</sub> = 2.4V, R<sub>1</sub> =  $500\Omega$  and C<sub>L</sub> = 40pF.

2. Transition is measured at  $\pm$  200 mV from steady state voltage, Output loading per test load circuit, with V<sub>1</sub> = 1.5V, R<sub>1</sub> = 500 $\Omega$  and C<sub>1</sub> = 40pF.

To ensure the correct product is entered in the output registers, new data may not be entered into the input registers before the output registers have been clocked.

|                      |                 |                                       |            |                                            |     | 45  | -6  | 60  |       |

|----------------------|-----------------|---------------------------------------|------------|--------------------------------------------|-----|-----|-----|-----|-------|

| PARAMETER            | SYMBOL          | CONDITIONS                            | NOTES      | TEMPERATURE                                | MIN | МАХ | MIN | MAX | UNITS |

| Input Capacitance    | C <sub>IN</sub> | V <sub>CC</sub> = Open, f = 1MHz      | <u>,</u> 1 | T <sub>A</sub> = +25 <sup>o</sup> C        | -   | 15  | ·   | 15  | pF    |

| Output Capacitance   | COUT            | All Measurements<br>are referenced to | 1          | $T_{A} = +25^{\circ}C$                     |     | 10  | -   | 10  | pF    |

| I/O Capacitance      | CI/O            | device GND.                           | 1          | T <sub>A</sub> = +25 <sup>o</sup> C        | -   | 10  | -   | 10  | pF    |

| X, Y, RND Hold Time  | тн              |                                       | 1, 2       | $-55^{\circ}C \le T_{A} \le +125^{\circ}C$ | 3   | -   | 3   | -   | ns    |

| 3-State Disable Time | TDIS            |                                       | 1, 2, 3    | $-55^{\circ}C \le T_{A} \le +125^{\circ}C$ | -   | 25  | -   | 30  | ns    |

| Output Rise Time     | TR              | From 0.8V to 2.0V                     | 1, 2, 4    | $-55^{\circ}C \le T_{A} \le +125^{\circ}C$ | -   | 10  | -   | 10  | ns    |

| Output Fall Time     | TF              | From 2.0V to 0.8V                     | 1, 2, 4    | -55°C ≤ T <sub>A</sub> ≤ +125°C            | -   | 10  |     | 10  | ns    |

#### TABLE 3. HMU16/883 ELECTRICAL PERFORMANCE CHARACTERISTICS

NOTES: 1. The parameters listed in table 3 are controlled via design or process parameters and are not directly tested. These parameters are characterized upon initial design and after major process and/or design changes.

2. Guaranteed, but not 100% tested.

3. Transition is measured at  $\pm 200 mV$  from steady state voltage, Output loading per test load circuit, with V\_1 = 1.5V, R\_1 = 500\Omega and C\_L = 40 pF.

4. Loading is as specified in the test load circuit, with V\_1 = 2.4V, R\_1 = 500\Omega and  $C_L$  = 40pF.

#### TABLE 4. APPLICABLE SUBGROUPS

| CONFORMANCE GROUPS | METHOD       | SUBGROUPS                     |

|--------------------|--------------|-------------------------------|

| Initial Test       | 100%/5004    | -                             |

| Interim Test       | 100%/5004    | -                             |

| PDA                | 100%         | 1                             |

| Final Test         | 100%         | 2, 3, 8A, 8B, 10, 11          |

| Group A            | -            | 1, 2, 3, 7, 8A, 8B, 9, 10, 11 |

| Groups C & D       | Samples/5005 | 1,7,9                         |

CAUTION: These devices are sensitive to electrostatic discharge. Proper IC handling procedures should be followed.

MULTIPLIERS

HMU16/883

#### Burn-In Circuit

| 11 |      | N/ C      | X13       | X15       | RND       | тсү                           | v <sub>cc</sub> | GND         | FT          | OEP         | ,           |

|----|------|-----------|-----------|-----------|-----------|-------------------------------|-----------------|-------------|-------------|-------------|-------------|

| 10 | X11  | X12       | X14       | CLKX      | тсх       | v <sub>cc</sub>               | GND             | MSPSEL      | FA          | CLKM        | N/C         |

| 9  | X9   | X10       | ·. ,      |           |           |                               |                 | -           |             | P30/<br>P14 | P31/<br>P15 |

| 8  | X7   | X8        |           |           |           |                               |                 |             |             | P28/<br>P12 | P29/<br>P13 |

| 7  | X5   | X6        |           |           |           |                               |                 |             |             | P26/<br>P10 | P27/<br>P11 |

| 6  | ХЗ   | X4 .      |           |           | PIN 0     | 38 leai<br>Grid Ái<br>Op viev | RRAY            |             |             | P24/<br>P8  | P25/<br>P9  |

| 5  | X1   | X2        | -         |           |           |                               |                 |             |             | P22/<br>P6  | P23/<br>P7  |

| 4  | OEL  | X0        | 4.9       |           |           |                               |                 |             |             | P20/<br>P4  | P21/<br>P5  |

| 3  | CLKY | CLKL      |           |           |           |                               |                 |             |             | P18/<br>P2  | P19/<br>P3  |

| 2  | N/ C | Y0/<br>P0 | Y2/<br>P2 | Y4/<br>P4 | Y6/<br>P6 | Y8/<br>P8                     | Y10/<br>P10     | Y12/<br>P12 | Y14/<br>P14 | P16/<br>P0  | P17/<br>P1  |

| 1  |      | Y1/<br>P1 | Y3/<br>P3 | Y5/<br>P5 | Y7/<br>P7 | Y9/<br>P9                     | Y11/<br>P11     | Y13/<br>P13 | Y15/<br>P15 | N/C         |             |

|    | A    | 8         | C         | D.        | E         | F                             | G               | н           | , <b>1</b>  | ĸ           | L           |

| PGA<br>PIN | PIN<br>NAME | BURN-IN<br>SIGNAL | PGA<br>PIN | PIN<br>NAME | BURN-IN<br>SIGNAL  | PGA<br>PIN | PIN<br>NAME | BURN-IN<br>SIGNAL  | PGA<br>PIN      | PIN<br>NAME | BURN-IN<br>SIGNAL |

|------------|-------------|-------------------|------------|-------------|--------------------|------------|-------------|--------------------|-----------------|-------------|-------------------|

| B6         | X4          | F6                | F1         | Y9/P9       | F11                | K7         | P10/P26     | V <sub>CC</sub> /2 | E11             | RND         | F1 <sup>°</sup>   |

| A6         | ХЗ          | F5                | G2         | Y10/P10     | F12                | L7         | P11/P27     | V <sub>CC</sub> /2 | D10             | CLKX        | FO                |

| B5         | X2          | F4                | G1         | Y11/P11     | F13                | К8         | P12/P28     | V <sub>CC</sub> /2 | D11             | X15         | F3                |

| A5         | X1          | F3                | H2         | Y12/P12     | F14                | L8         | P13/P29     | V <sub>CC</sub> /2 | C10             | X14         | F2                |

| В4         | хо          | F2                | H1         | Y13/P13     | F15                | К9         | P14/P30     | V <sub>CC</sub> /2 | C11             | X13         | F15               |

| A4         | OEL         | Vcc               | J2         | Y14/P14     | F4                 | L9         | P15/P31     | V <sub>CC</sub> /2 | B10             | X12         | F14               |

| B3         | CLKL        | F0                | J1         | Y15/P15     | F5                 | K10        | CLKM        | F0                 | A10             | X11         | F13               |

| A3         | CLKY        | FO                | К2         | P0/P16      | V <sub>CC</sub> /2 | K11        | OEP         | F1                 | В9              | X10         | F12               |

| B2         | Y0/P0       | F2                | L2         | P1/P17      | V <sub>CC</sub> /2 | J10        | FA          | F14                | A9              | хэ          | F11               |

| B1         | Y1/P1       | F3                | КЗ         | P2/P18      | V <sub>CC</sub> /2 | J11        | FT          | F15                | B8              | X8          | F10               |

| C2         | Y2/P2       | F4                | L3         | P3/P19      | V <sub>CC</sub> /2 | H10        | MSPSEL      | F14                | A8              | X7          | F9                |

| C1         | Y3/P3       | F5                | К4         | P4/P20      | V <sub>CC</sub> /2 | H11        | GND         | GND                | B7 <sup>-</sup> | X6          | F8                |

| D2         | Y4/P4       | F6                | L4         | P5/P21      | V <sub>CC</sub> /2 | G10        | GND         | GND                | A7              | X5          | F7                |

| D1         | Y5/P5       | F7                | К5         | P6/P22      | V <sub>CC</sub> /2 | G11        | Vcc         | VCC                | A2              | N.C.        | NONE              |

| E2         | Y6/P6       | F8                | L5         | P7/P23      | V <sub>CC</sub> /2 | F10        | Vcc         | VCC                | К1              | N.C.        | NONE              |

| E1         | Y7/P7       | F9                | K6         | P8/P24      | V <sub>CC</sub> /2 | F11        | TCY         | F15                | L10             | N.C.        | NONE              |

| F2         | Y8/P8       | F10               | L6         | P9/P25      | V <sub>CC</sub> /2 | E10        | тсх         | F15                | B11             | N.C.        | NONE              |

NOTES:

1.  $V_{CC}$  = 5.0V +0.5V/-0.0V with 0.1µF decoupling capacitor to GND.

3. 47k $\Omega$  load resistors used on all pins except V\_{CC} and GND (Pin-Grid identifiers F10, G10, G11 and H11).

#### DIE DIMENSIONS:

179 x 169 x 19 ±1 mils

METALLIZATION: Type: Si-Al or Si-Al-Cu Thickness: 8kÅ

#### GLASSIVATION: Type: Nitrox

Thickness: 10kÅ

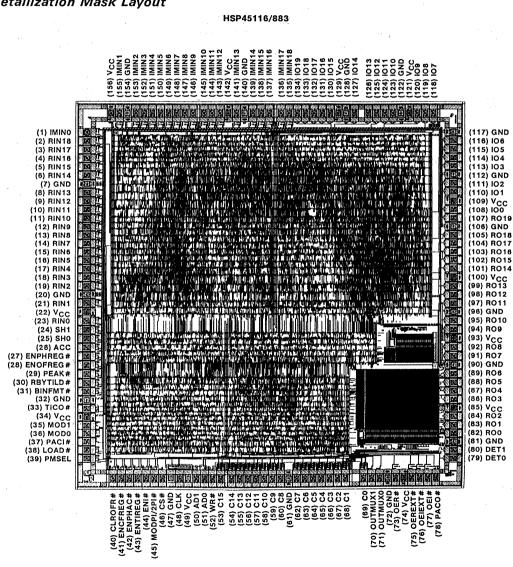

#### Metallization Mask Layout

DIE ATTACH: Material: Si-Au Eutectic Alloy Temperature: Ceramic PGA — 420°C (Max) WORST CASE CURRENT DENSITY: 1.2 x 10<sup>5</sup>A/cm<sup>2</sup>

HMU16/883

MULTIPLIERS

2

#### HMU16/883

## HMU17/883

May 1991

#### Features

- This Circuit is Processed in Accordance to Mil-Std-883 and is Fully Conformant Under the Provisions of Paragraph 1.2.1.

- 16 x 16-Bit Parallel Multiplier with Full 32-Bit Product

- High-Speed (45ns) Clocked Multiply Time

- Low Power CMOS Operation:

- ► ICCSB = 500µA Maximum

- ICCOP = 7.0mA Maximum @ 1MHz

- HMU17 is compatible with the AM29517, LMU17, IDT7217, and the CY7C517

- Supports Two's Complement, Unsigned Magnitude and Mixed Mode Multiplication

- TTL Compatible Inputs/Outputs

- Three-State Outputs

- Available in a 68 Lead Pin Grid Array Package

#### 16 x 16-Bit CMOS Parallel Multiplier

#### Description

The HMU17 is a high speed, low power CMOS 16 x 16-bit parallel multiplier ideal for fast, real time digital signal processing applications. The 16-bit X and Y operands may be independently specified as either two's complement or unsigned magnitude format, thereby allowing mixed mode multiplication operations.

Additional inputs are provided to accommodate format adjustment and rounding of the 32-bit product. The Format Adjust control allows the user the option of selecting a 31-bit product with the sign bit replicated LSP. The Round control is provided to accommodate rounding of the most significant portion of the result. This is accomplished by adding one to the most significant bit of the LSP.

Two 16-bit output registers (MSP and LSP) are provided to hold the most and least significant portions of the result, respectively. These registers may be made transparent for asynchronous operation through the use of the feedthrough control (FT). The two halves of the product may be routed to a single 16-bit three-state output port via the output multiplexer control, and in addition, the LSP is connected to the Y-input port through a separate three-state buffer.

The HMU17 utilizes a single clock signal (CLK) along with three register enables (ENX, ENY, and ENP) to latch the input operands and the output product registers. The ENX and ENY inputs enable the X and Y input registers, while ENP enables both the LSP and MSP output registers. This configuration facilitates the use of the HMU17 for micro-programmed systems.

All outputs of the HMU17 also offer three-state control for multiplexing onto multi-use system busses.

2

MULTIPLIERS

#### **Absolute Maximum Ratings**

| Supply Voltage                       | +8.0V             |

|--------------------------------------|-------------------|

| Input or Output Voltage Applied GND- | 0.5V to VCC +0.5V |

| Storage Temperature Range            | -65°C to +150°C   |

| Junction Temperature                 | +175°C            |

| Lead Temperature (Soldering 10 sec)  | 300°C             |

| ESD Classification                   | Class 1           |

#### **Reliability Information**

| Thermal Resistance                   | θja                         | θjc        |

|--------------------------------------|-----------------------------|------------|

| Ceramic PGA Package                  | 42.69°C/W                   | 10.0°C/W   |

| Maximum Package Power Dissipation at | t +125°C                    |            |

| Ceramic PGA Package                  |                             | 1.17 Watt  |

| Gate Count                           | • • • • • • • • • • • • • • | 4500 Gates |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### **Operating Conditions**

| Operating Voltage Range                   | / |

|-------------------------------------------|---|

| Operating Temperature Range55°C to +125°C | 2 |

#### TABLE 1. HMU16/883 D.C. ELECTRICAL PERFORMANCE CHARACTERISTICS

Device Guaranteed and 100% Tested

| $\gamma = -2^{10}$ , $\zeta$      | . t.   | ×                                                                                    | GROUP A   |                                            | LIM        | ITS |       |

|-----------------------------------|--------|--------------------------------------------------------------------------------------|-----------|--------------------------------------------|------------|-----|-------|

| PARAMETER                         | SYMBOL | CONDITIONS                                                                           | SUBGROUPS | TEMPERATURE                                | MIN        | МАХ | UNITS |

| Logical One Input<br>Voltage      | ViH    | V <sub>CC</sub> = 5.5V                                                               | 1, 2, 3   | -55°C ≤ T <sub>A</sub> ≤ +125°C            | 2.2        | -   | v     |

| Logical Zero Input<br>Voltage     | VIL    | $V_{CC} = 4.5V$                                                                      | 1, 2, 3   | -55°C ≤T <sub>A</sub> ≤ +125°C             |            | 0.8 | V     |

| Output HIGH Voltage               | VOH    | I <sub>OH</sub> = -400μA<br>V <sub>CC</sub> = 4.5V (Note 1)                          | 1, 2, 3   | -55°C ≤ T <sub>A</sub> ≤ +125°C            | 2.6        | -   | v     |

| Output LOW Voltage                | VOL    | I <sub>OL</sub> = +4.0mA<br>V <sub>CC</sub> = 4.5V (Note 1)                          | 1, 2, 3   | $-55^{\circ}C \le T_{A} \le +125^{\circ}C$ | <b></b> `. | 0.4 | V     |

| Input Leakage Current             | ų      | $V_{IN} = V_{CC} \text{ or GND}$<br>$V_{CC} = 5.5V$                                  | 1, 2, 3   | -55°C ≤ T <sub>A</sub> ≤ +125°C            | -10        | +10 | μA    |

| Output or I/O Leakage<br>Current  | 10     | $V_{OUT} = V_{CC} \text{ or } GND$<br>$V_{CC} = 5.5V$                                | 1, 2, 3   | $-55^{\circ}C \le T_{A} \le +125^{\circ}C$ | -10        | +10 | μA    |

| Standby Power Supply<br>Current   | ICCSB  | $V_{IN} = V_{CC} \text{ or GND},$<br>$V_{CC} = 5.5V, Outputs$<br>Open                | 1, 2, 3   | -55°C ≤T <sub>A</sub> ≤ +125°C             | -          | 500 | μΑ    |

| Operating Power<br>Supply Current | ICCOP  | f = 1.0MHz,<br>$V_{IN} = V_{CC} \text{ or } GND$<br>$V_{CC} = 5.5V \text{ (Note 2)}$ | 1, 2, 3   | -55°C ≤T <sub>A</sub> ≤ +125°C             | ·          | 7.0 | mA    |

| Functional Test                   | FT     | (Note 3)                                                                             | 7,8       | $-55^{\circ}C \le T_{A} \le +125^{\circ}C$ | -          | -   |       |

#### NOTES:

1. Interchanging of force and sense conditions is permitted.

2. Operating Supply Current is proportional to frequency, typical rating is 5mA/MHz.

3. Tested as follows: f = 1MHz, V<sub>IH</sub> (Clock Inputs) = 3.0, V<sub>IH</sub> (All other inputs) = 2.6, V<sub>IL</sub> = 0.4, V<sub>OH</sub>  $\geq$  1.5V, and V<sub>OL</sub>  $\leq$  1.5V.

CAUTION: These devices are sensitive to electrostatic discharge. Proper IC handling procedures should be followed.

#### TABLE 2. HMU17/883 A.C. ELECTRICAL PERFORMANCE CHARACTERISTICS

Device Guaranteed and 100% Tested

|                            |                | (NOTE 1)   | GROUP A   |                                                         | -4  | 45  | -6  | 30  |       |

|----------------------------|----------------|------------|-----------|---------------------------------------------------------|-----|-----|-----|-----|-------|

| PARAMETER                  | SYMBOL         | CONDITIONS | SUBGROUPS | TEMPERATURE                                             | MIN | мах | MIN | мах | UNITS |

| Unclocked Multiply<br>Time | тмис           |            | 9, 10, 11 | $-55^{\circ}C \le T_{A} \le +125^{\circ}C$              | -   | 70  | -   | 90  | ns    |

| Clocked Multiply Time      | тмс            |            | 9, 10, 11 | $-55^{\circ}C \le T_{A} \le +125^{\circ}C$              | -   | 45  | -   | 60  | ns    |

| X, Y, RND Setup Time       | т <sub>S</sub> |            | 9, 10, 11 | $-55^{\circ}C \le T_{A} \le +125^{\circ}C$              | 18  | -   | 20  | -   | ns    |

| Clock HIGH Pulse<br>Width  | TPWH           |            | 9, 10, 11 | -55°C ≤ T <sub>A</sub> ≤ +125°C                         | 15  | -   | 20  | -   | ns    |

| Clock LOW Pulse<br>Width   | TPWL           |            | 9, 10, 11 | -55 <sup>0</sup> C ≤T <sub>A</sub> ≤+125 <sup>ŏ</sup> C | 15  |     | 20  | -   | ns    |

| MSPSEL to Product<br>Out   | TPDSEL         |            | 9, 10, 11 | -55°C ≤ T <sub>A</sub> ≤ +125°C                         | -   | 25  | -   | 30  | ns    |

| Output Clock to P          | TPDP           |            | 9, 10, 11 | $-55^{\circ}C \le T_{A} \le +125^{\circ}C$              | -   | 25  | -   | 30  | ns    |

| Output Clock to Y          | TPDY           |            | 9, 10, 11 | -55°C ≤ T <sub>A</sub> ≤ +125°C                         | -   | 25  | -   | 30  | ns    |

| 3-State Enable Time        | TENA           | (Note 2)   | 9, 10, 11 | $-55^{\circ}C \le T_{A} \le +125^{\circ}C$              | -   | 25  | -   | 30  | ns    |

| Clock Enable Setup         | TSE            |            | 9, 10, 11 | -55°C < T <sub>A</sub> < +125°C                         | 15  | -   | 15  | -   | ns    |

NOTES:

1. AC Testing as follows: Input levels 0V and 3.0V, Timing reference 2. Transition is measured at ± 200mV from steady state voltage, Output levels = 1.5V, Input rise and fall times driven at 1ns/V, Output load per test load circuit, with V<sub>1</sub> = 2.4V, R<sub>1</sub> = 500 $\Omega$  and C<sub>L</sub> = 40pF.

loading per test load circuit, with  $V_1 = 1.5V$ ,  $R_1 = 500\Omega$  and  $C_L = 40pF$ .

2

| n en ser en | and the second | and the second second                 |         | -45                                        |     | · - ( |            |     |       |

|-------------------------------------------------|----------------|---------------------------------------|---------|--------------------------------------------|-----|-------|------------|-----|-------|

| PARAMETER                                       | SYMBOL         | CONDITIONS                            | NOTES   | TEMPERATURE                                | MIN | MAX   | MIN        | MAX | UNITS |

| Input Capacitance                               | CIN            | V <sub>CC</sub> = Open, f = 1MHz      | 1       | T <sub>A</sub> = +25 <sup>o</sup> C        | _   | 15    |            | 15  | pF    |

| Output Capacitance                              | COUT           | All Measurements<br>are referenced to | 1 5     | T <sub>A</sub> = +25°C                     |     | .10   | -          | 10  | pF    |

| I/O Capacitance                                 | CI/O           | device GND.                           | 1       | T <sub>A</sub> = +25 <sup>o</sup> C        | -   | 10    | -          | 10  | pF    |

| X, Y, RND Hold Time                             | Тн             |                                       | 1,2     | -55°C ≤ T <sub>A</sub> ≤ +125°C            | 3   | -     | 3          | - ' | ns    |

| 3-State Disable Time                            | TDIS           | -                                     | 1, 2, 3 | $-55^{\circ}C \le T_{A} \le +125^{\circ}C$ | -   | 25    | -          | 30  | , ns  |

| Clock Enable<br>Hold Time                       | THE            |                                       | 1, 2, 3 | -55°C ≤ T <sub>A</sub> ≤ +125°C            | 3   | -     | 3          | -   | ns    |

| Output Rise Time                                | TR             | From 0.8V to 2.0V                     | 1, 2, 4 | -55°C ≤ T <sub>A</sub> ≤ +125°C            |     | 10    | <i>1</i> - | 10  | ns    |

| Output Fall Time                                | TF             | From 2.0V to 0.8V                     | 1, 2, 4 | $-55^{\circ}C \le T_{A} \le +125^{\circ}C$ | -   | 10    | -          | 10  | ns    |

#### TABLE 3. HMU17/883 ELECTRICAL PERFORMANCE CHARACTERISTICS

NOTES:

The parameters listed in Table 3 are controlled via design or process parameters and are not directly tested. These parameters are characterized upon initial design and after major process and/or design changes. 3. Transition is measured at ±200mV from steady state voltage, Output loading per test load circuit, with V<sub>1</sub> = 1.5V, R<sub>1</sub> = 500 $\Omega$  and C<sub>L</sub> = 40pF.

4. Loading is as specified in the test load circuit, with V  $_1$  = 2.4V, R  $_1$  = 500  $\Omega$  and C  $_L$  = 40pF.

2. Guaranteed, but not 100% tested.

#### TABLE 4. APPLICABLE SUBGROUPS

| CONFORMANCE GROUPS | METHOD       | SUBGROUPS                     |

|--------------------|--------------|-------------------------------|

| Initial Test       | 100%/5004    | -                             |

| Interim Test       | 100%/5004    | -                             |

| PDA                | 100%         | 1                             |

| Final Test         | 100%         | 2, 3, 8A, 8B, 10, 11          |

| Group A            | -            | 1, 2, 3, 7, 8A, 8B, 9, 10, 11 |

| Groups C & D       | Samples/5005 | 1,7,9                         |

2

MULTIPLIERS

HMU17/883

| Burn-In Circuit | 1  |     |             |           | 1         | 1         | 1                             |                 | T           |             | 1           | ·           |

|-----------------|----|-----|-------------|-----------|-----------|-----------|-------------------------------|-----------------|-------------|-------------|-------------|-------------|

|                 | 11 |     | N/C         | X13       | X15       | RND       | тсү                           | v <sub>cc</sub> | GND         | FT          | OEP         |             |

|                 | 10 | X11 | X12         | X14       | ENX       | тсх       | vcc                           | GND             | MSPSEL      | FA          | ENP         | N/C         |

|                 | 9  | X9  | X10         |           |           |           |                               | ,               |             |             | P30/<br>P14 | P31/<br>P15 |

|                 | 8  | X7  | : <b>X8</b> |           |           |           |                               |                 |             |             | P28/<br>P12 | P29/<br>P13 |

|                 | 7  | X5  | X6          |           |           |           |                               |                 |             |             | P26/<br>P10 | P27/<br>P11 |

|                 | 6  | X3  | X4          |           | - a-      | PIN       | 68 Leai<br>Grid Ai<br>Op Viev | RRAY            |             |             | P24/<br>P8  | P25/<br>P9  |

|                 | 5  | X1  | X2          |           |           |           |                               |                 |             |             | P22/<br>P6  | P23/<br>P7  |

|                 | 4  | OEL | xo          |           |           |           |                               |                 |             |             | P20/<br>P4  | P21/<br>P5  |

|                 | 3  | ENY | CLK         |           |           |           |                               |                 |             |             | P18/<br>P2  | P19/<br>P3  |

| · .             | 2  | N/C | Y0/<br>P0   | Y2/<br>P2 | Y4/<br>P4 | Y6/<br>P6 | Y8/<br>P8                     | Y10/<br>P10     | Y12/<br>P12 | Y14/<br>P14 | P16/<br>P0  | P17/<br>P1  |

|                 | 1  |     | Y1/<br>P1   | Y3/<br>P3 | Y5/<br>P5 | Y7/<br>P7 | Y9/<br>P9                     | Y11/<br>P11     | Y13/<br>P13 | Y15/<br>P15 | N/C         |             |

|                 | 1  | A   | в           | C         | D         | E         | F                             | G               | ́н.         | J           | к           | L           |

| PGA<br>PIN | PIN<br>NAME | BURN-IN<br>SIGNAL | PGA<br>PIN | PIN<br>NAME | BURN-IN<br>SIGNAL  | PGA<br>PIN | PIN<br>NAME | BURN-IN<br>SIGNAL  | PGA<br>PIN | PIN<br>NAME | BURN-IN<br>SIGNAL |

|------------|-------------|-------------------|------------|-------------|--------------------|------------|-------------|--------------------|------------|-------------|-------------------|

| B6         | X4          | F6                | F1         | Y9/P9       | F11                | К7         | P10/P26     | V <sub>CC</sub> /2 | E11        | RND         | F1                |

| A6         | ХЗ          | F5                | G2         | Y10/P10     | F12                | L7         | P11/P27     | V <sub>CC</sub> /2 | D10        | ENX         | FO                |

| B5         | X2          | F4                | G1         | Y11/P11     | F13                | K8         | P12/P28     | V <sub>CC</sub> /2 | D11        | X15         | F3                |

| A5         | X1          | F3                | H2         | Y12/P12     | F14                | L8         | P13/P29     | V <sub>CC</sub> /2 | C10        | X14         | F2                |

| B4         | xo          | F2                | H1         | Y13/P13     | F15                | К9         | P14/P30     | V <sub>CC</sub> /2 | C11        | X13         | F15               |

| A4         | OEL         | Vcc               | J2         | Y14/P14     | F4                 | L9         | P15/P31     | V <sub>CC</sub> /2 | B10        | X12         | F14               |

| B3         | CLK         | FO                | J1         | Y15/P15     | F5                 | K10        | ENP         | FO                 | A10        | X11         | F13               |

| A3         | ENY         | FO                | К2         | P0/P16      | V <sub>CC</sub> /2 | K11        | OEP         | F1                 | B9         | X10         | F12               |

| B2         | Y0/P0       | F2                | L2         | P1/P17      | V <sub>CC</sub> /2 | J10        | FA          | F14                | A9         | хэ          | F11               |

| B1         | Y1/P1       | F3                | кз         | P2/P18      | V <sub>CC</sub> /2 | J11        | FT          | F15                | B8         | X8          | F10               |

| C2         | Y2/P2       | F4                | L3         | P3/P19      | V <sub>CC</sub> /2 | H10        | MSPSEL      | F14                | A8         | X7          | F9                |

| C1         | Y3/P3       | F5                | К4         | P4/P20      | V <sub>CC</sub> /2 | H11        | GND         | GND                | B7         | X6          | F8                |

| D2         | Y4/P4       | F6                | L4         | P5/P21      | V <sub>CC</sub> /2 | G10        | GND         | GND                | A7         | X5          | F7                |

| D1         | Y5/P5       | F7                | К5         | P6/P22      | V <sub>CC</sub> /2 | G11        | Vcc         | Vcc                | A2         | N.C.        | NONE              |

| E2         | Y6/P6       | F8                | L5         | P7/P23      | V <sub>CC</sub> /2 | F10        | Vcc         | Vcc                | K1         | N.C.        | NONE              |

| E1         | Y7/P7       | F9                | K6         | P8/P24      | V <sub>CC</sub> /2 | F11        | тсү         | F15                | L10        | N.C.        | NONE              |

| F2         | Y8/P8       | F10               | L6         | P9/P25      | V <sub>CC</sub> /2 | E10        | тсх         | F15                | B11        | N.C.        | NONE              |

NOTES:

1.  $V_{CC} = 5.0V + 0.5V - 0.0V$  with  $0.1 \mu F$  decoupling capacitor to GND.

3. 47k  $\!\Omega$  load resistors used on all pins except V\_{CC} and GND (Pin-Grid identifiers F10, G10, G11 and H11).

2. F0 = 100kHz, F1 = F0/2, F2 = F1/2, .....

DIE ATTACH:

Material: Si-Au Eutectic Alloy

Temperature: Ceramic PGA - 420°C (Max)

WORST CASE CURRENT DENSITY: 1.2 x 10<sup>5</sup>A/cm<sup>2</sup>

#### **Die Characteristics**

#### **DIE DIMENSIONS:**

179 x 169 x 19 ±1 mils

METALLIZATION: Type: Si-Al or Si-Al-Cu

Thickness: 8kÅ

#### GLASSIVATION: Type: Nitrox

Thickness: 10kÅ

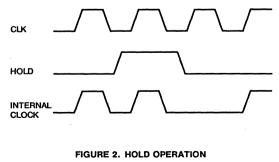

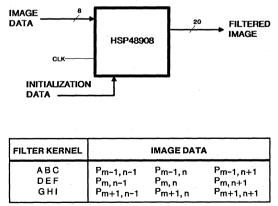

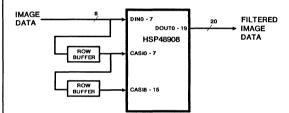

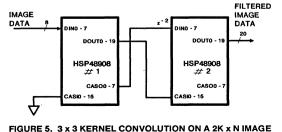

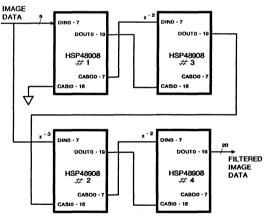

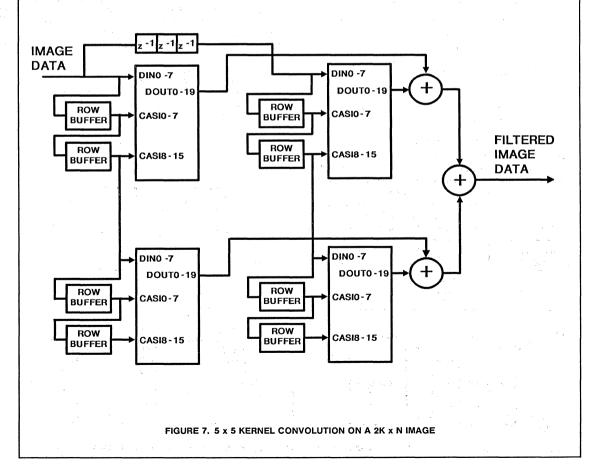

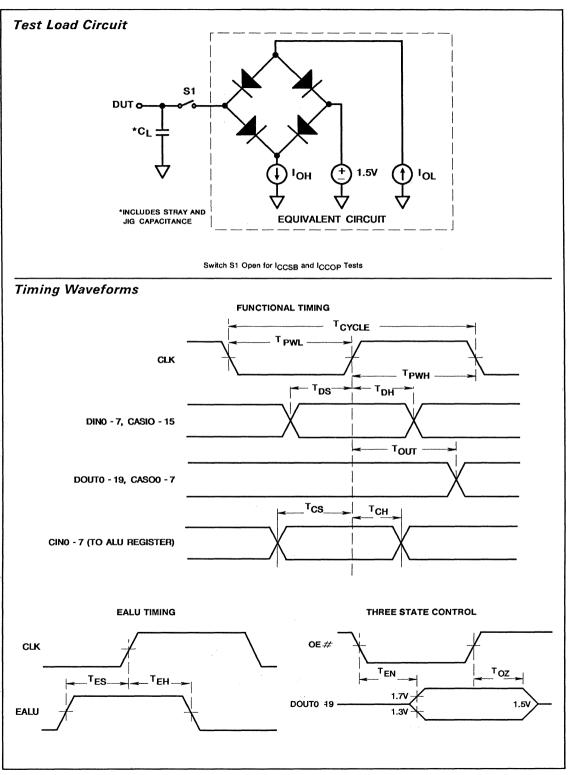

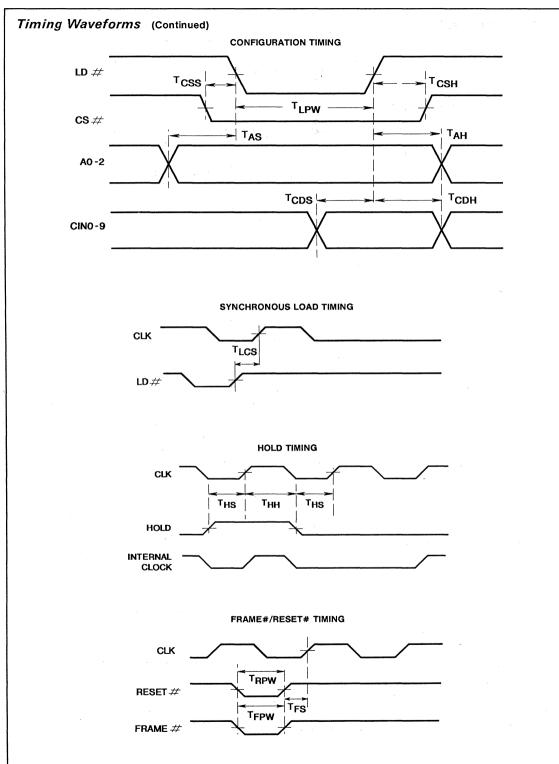

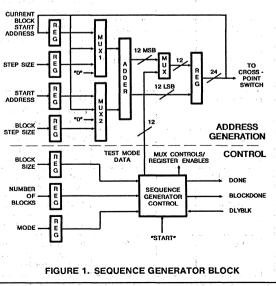

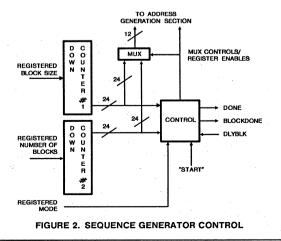

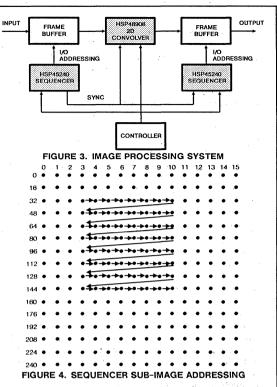

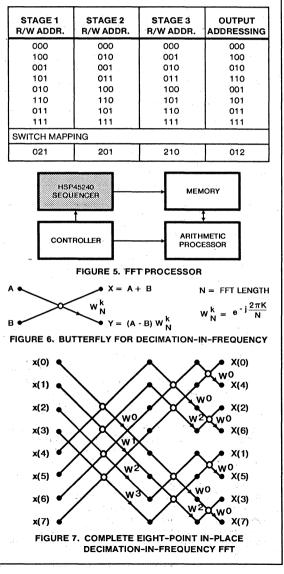

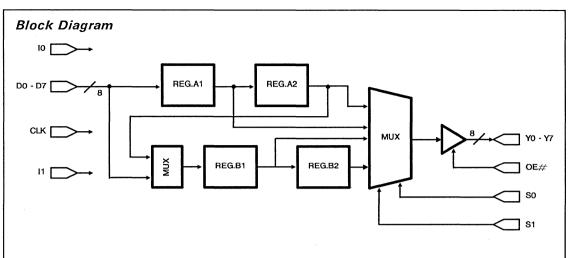

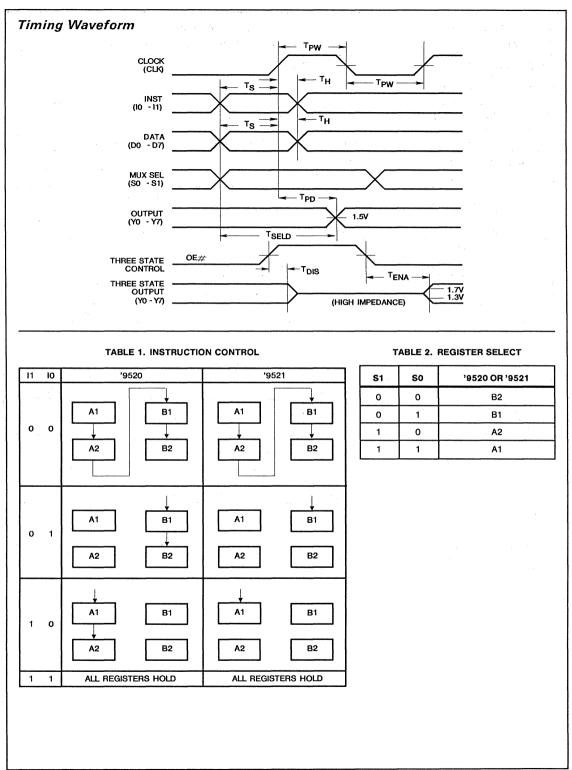

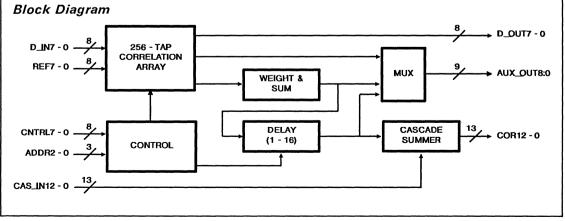

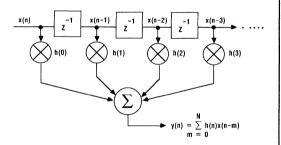

#### Metallization Mask Layout