# **MOS DATA BOOK**

MCRON TECHNOLOGY, INC.

| DYNAMIC RAMs                   |   |

|--------------------------------|---|

| DYNAMIC RAM MODULES            | 2 |

| MULTIPORT DYNAMIC RAMs (VRAMs) | 3 |

| STATIC RAMs                    | 4 |

| CACHE DATA RAMs                | 5 |

| FIFO MEMORIES                  | 6 |

| MILITARY PRODUCTS              | 7 |

| PACKAGE INFORMATION            | 8 |

| SALES INFORMATION              | Q |

# MOS DATA BOOK

2805 East Columbia Road Boise, Idaho 83706 Telephone: (208) 386-3900 TWX - (910)-970-5973 FAX - (208)343-2536

12/88

Micron Technology, Inc. reserves the right to change products or specifications without notice TM Trademark of Micron Technology, Inc.

#### **IMPORTANT NOTICE**

Micron Technology, Inc. reserves the right to change products or specifications without notice. Customers are advised to obtain the latest versions of product specifications, which should be considered in evaluating a product's appropriateness for a particular use. There is no assurance that Micron's semiconductors are appropriate for any application by a customer.

MICRON TECHNOLOGY, INC. MAKES NO WARRANTIES EXPRESSED OR IMPLIED OTHER THAN COMPLIANCE WITH MICRON'S SPECIFICATION SHEET FOR THE COMPONENT AT THE TIME OF DELIVERY. ANY CLAIM AGAINST MICRON MUST BE MADE WITHIN NINETY (90) DAYS FROM THE DATE OF SHIPMENT FROM MICRON, AND MICRON HAS NO LIABILITY THEREAFTER. ANY MICRON LIABILITY IS LIMITED TO REPLACEMENT OF DEFECTIVE ITEMS OR RETURN OF AMOUNTS PAID FOR DEFECTIVE ITEMS (AT THE BUYER'S ELECTION).

MICRON'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COM-PONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF MICRON TECHNOLOGY, INC. AS USED HEREIN:

A. LIFE SUPPORT DEVICES OR SYSTEMS ARE DEVICES OR SYSTEMS WHICH (1) ARE INTENDED FOR SURGICAL IMPLANT INTO THE BODY, OR (2) SUPPORT OR SUSTAIN LIFE AND WHOSE FAILURE TO PERFORM WHEN PROPERLY USED IN ACCORDANCE WITH INSTRUCTIONS FOR USE PROVIDED IN THE LABELING CAN BE REASONABLY EXPECTED TO RESULT IN A SIGNIFICANT INJURY TO THE USER.

B. CRITICAL COMPONENT IS ANY COMPONENT OF A LIFE SUPPORT DEVICE OR SYSTEM WHOSE FAILURE TO PERFORM CAN BE REASONABLY EXPECTED TO CAUSE THE FAILURE OF THE LIFE SUPPORT DEVICE OR SYSTEM OR TO AFFECT ITS SAFETY OR EFFECTIVENESS.

The MOS Data Book has been organized into nine sections and includes complete detailed specifications on our growing, high performance CMOS and NMOS product line.

Sections 1 through 7 cover individual product families. Each section contains a product selection guide followed by data sheets. Three different types of data sheets are used: Advance Information, which contains initial descriptions of products still under development; Preliminary Information, which contains initial device characterization limits which are subject to change upon full characterization of production devices; and Final Information, which contains minimum and maximum limits specified over the complete power supply and temperature range for production devices.

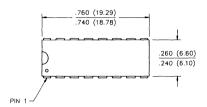

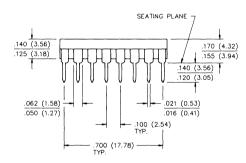

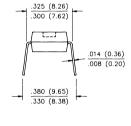

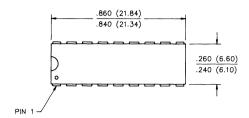

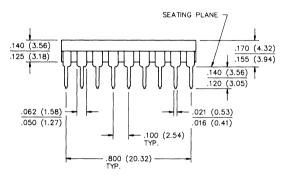

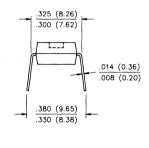

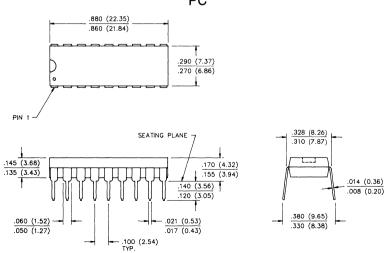

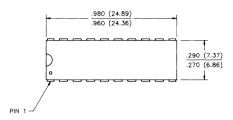

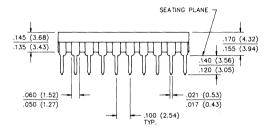

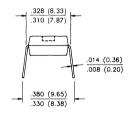

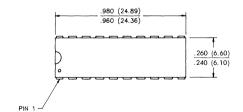

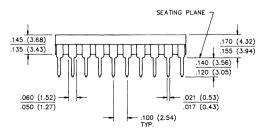

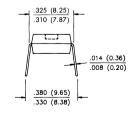

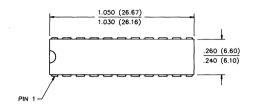

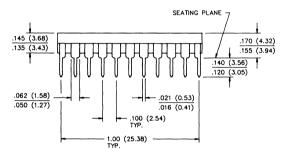

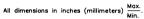

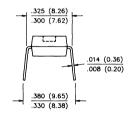

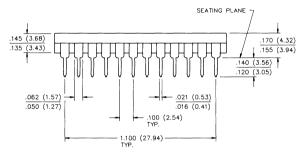

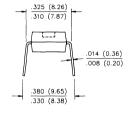

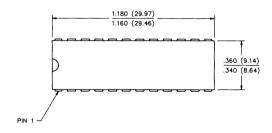

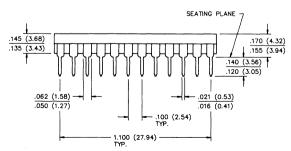

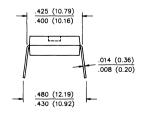

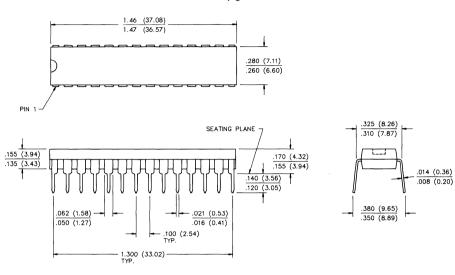

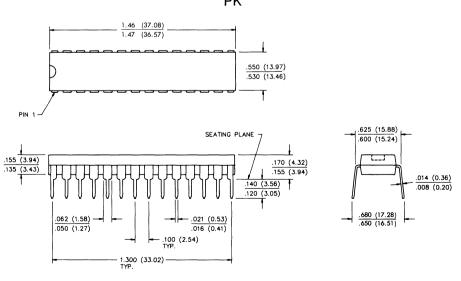

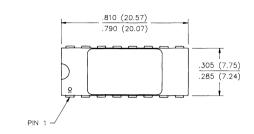

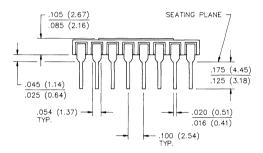

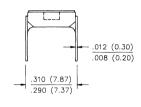

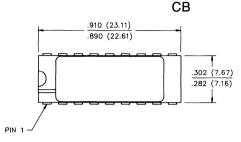

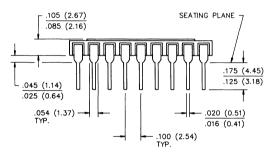

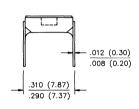

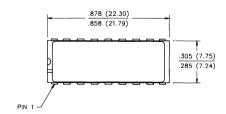

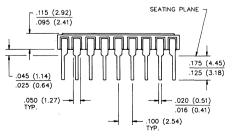

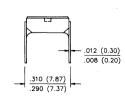

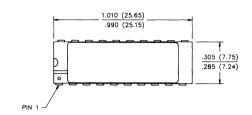

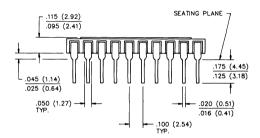

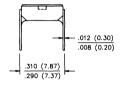

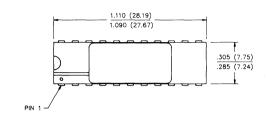

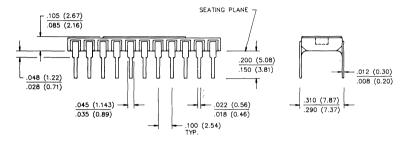

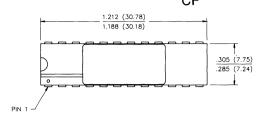

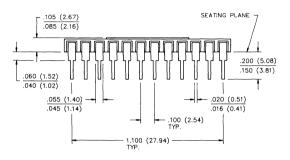

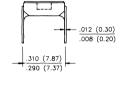

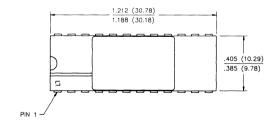

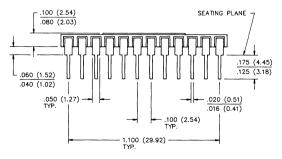

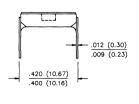

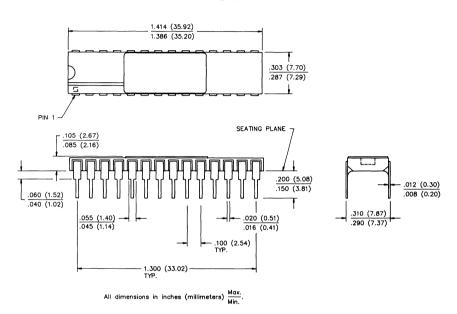

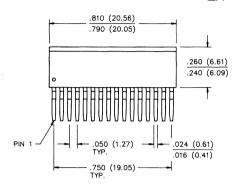

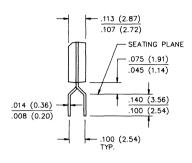

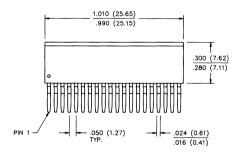

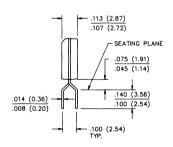

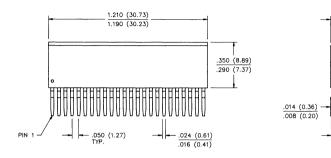

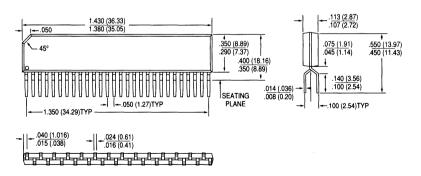

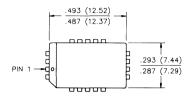

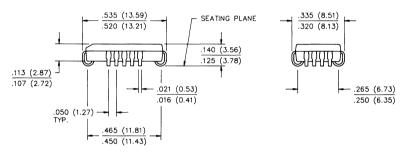

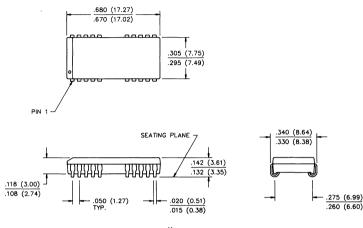

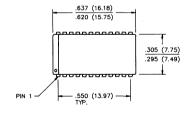

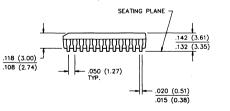

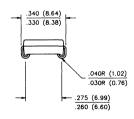

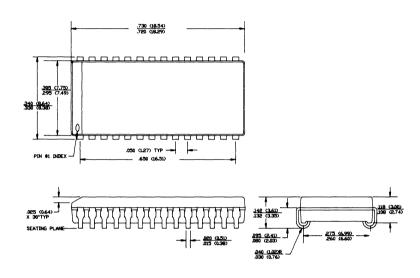

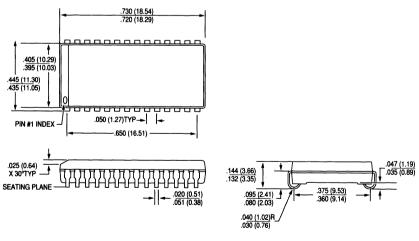

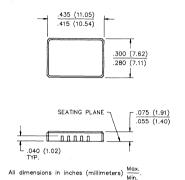

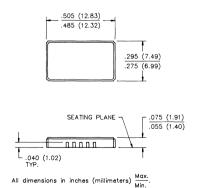

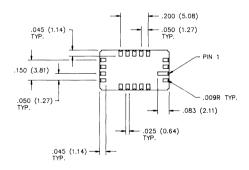

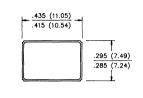

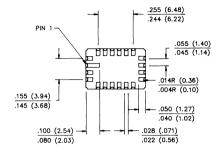

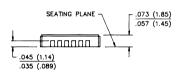

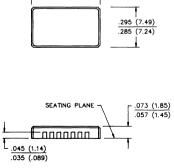

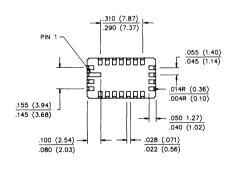

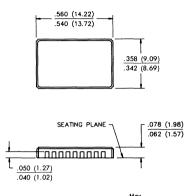

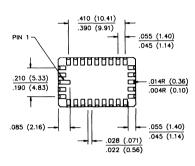

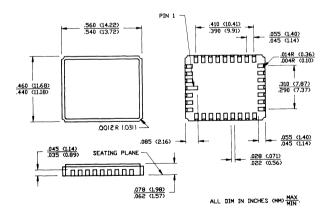

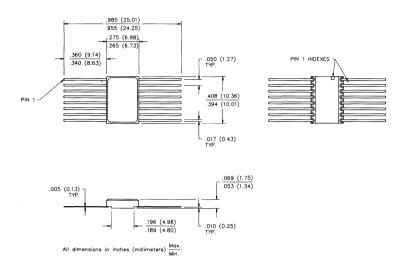

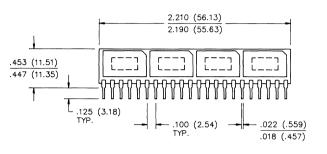

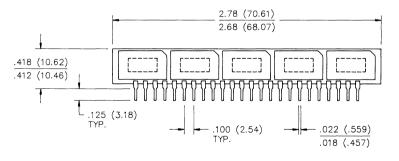

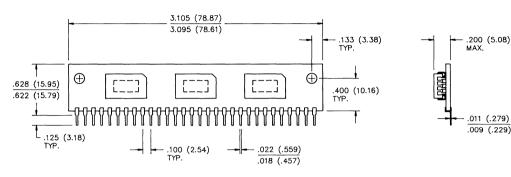

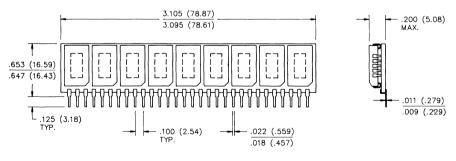

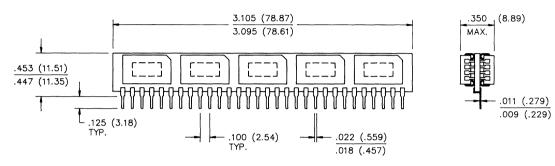

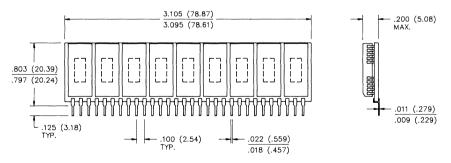

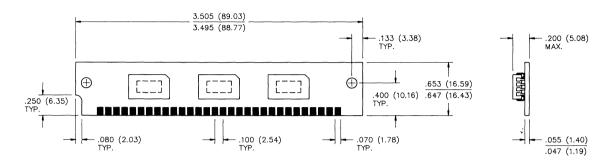

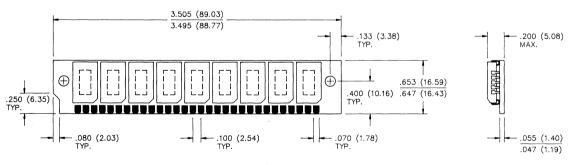

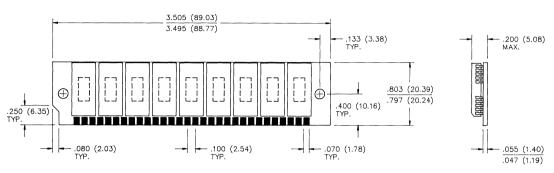

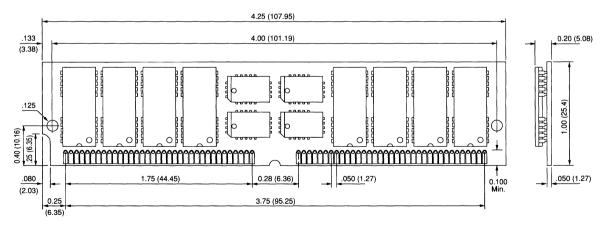

Section 8 contains detailed mechanical data on each package used by Micron.

Section 9 contains sales information, with a list of sales representatives and distributors by geographical location for the North American Continent, Europe and Asia.

Additional or updated information on any Micron product is available from:

MICRON TECHNOLOGY, INC.

**Marketing Department**

2805 East Columbia Road

Boise, Idaho 83706

Telephone: (208) 386-3900

TWX - (910) 970-5973

FAX - (208) 343-2536

## MICRON

| DYNAMIC RAMS            |                 | ]                      | PAGE    |

|-------------------------|-----------------|------------------------|---------|

| Product Selection Guide |                 |                        | 1-1     |

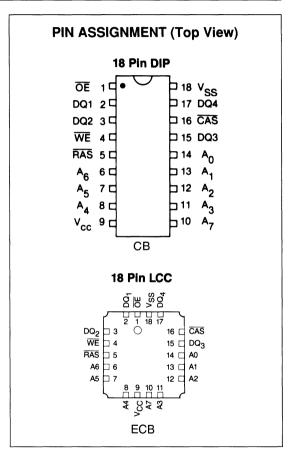

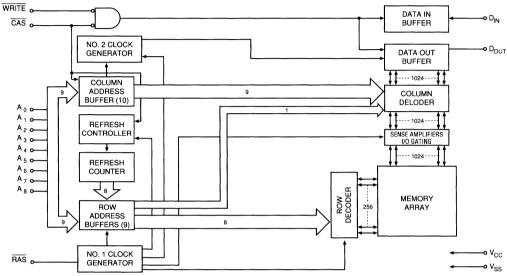

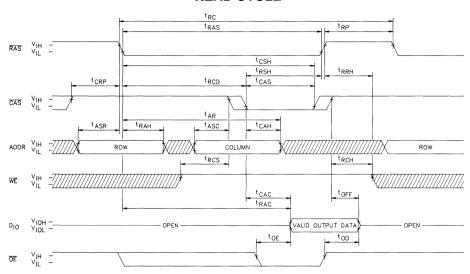

| MT4264                  | 64K X 1         | Page mode              | 1-3     |

| MT4067                  |                 | Page mode              |         |

| MT1259                  | 256K X 1        | Page mode              | 1-23    |

| MT4C4256                | 256K X 4        | Fast page mode         |         |

| MT4C4258                | 256K X 4        | Static column mode     |         |

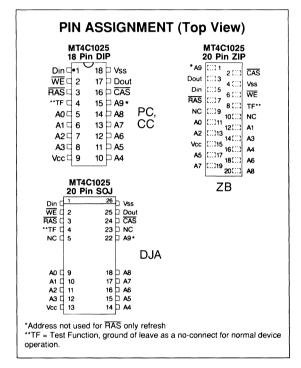

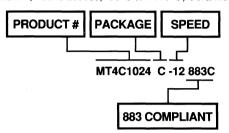

| MT4C1024                | 1MEG X 1        | Fast page mode         | 1-57    |

| MT4C1025                | 1MEG X 1        | Nibble mode            |         |

| MT4C1026                | 1MEG X 1        | Static column mode     | 1-81    |

| MT4C4001                | 1MEG X 4        | Fast page mode         | 1-93    |

| MT4C4003                | 1MEG X 4        | Static column mode     | 1-105   |

| MT4C1004                |                 | Fast page mode         | 1-117   |

| MT4C1005                |                 | Nibble mode            |         |

| MT4C1006                | 4MEG X 1        | Static column mode     | 1-141   |

| DYNAMIC RAM MODU        | ULES            |                        |         |

|                         |                 |                        |         |

| MT8068                  | 64K X 8         | Page mode              |         |

| MT9068                  |                 | Page mode              |         |

| MT4259                  |                 | Page mode              | . 2-23  |

| MT85259                 |                 | Page mode              |         |

| MT8259                  |                 | Page mode, low profile | . 2-43  |

| MT8259                  |                 | Page mode              |         |

| MT9259                  |                 | Page mode, low profile | . 2-63  |

| MT9259                  |                 | Page mode              |         |

| MT8C3656                |                 | Page mode              |         |

| MT8C8024                |                 | Fast page mode         |         |

| MT8C8025                |                 | Nibble mode            |         |

| MT8C8026                |                 | Static column mode     |         |

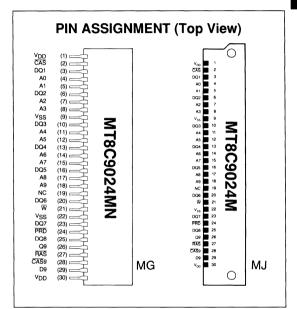

| MT8C9024                |                 | Fast page mode         |         |

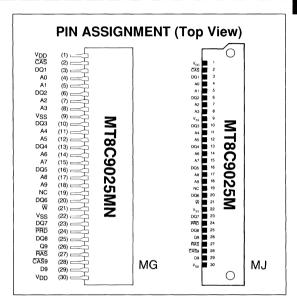

| MT8C9025                |                 | Nibble mode            |         |

| MT8C9026                | 1MEG X 9        | Static column mode     | . 2-149 |

| MUTIPORT DYNAMIC        | RAMS (VIDEO     | RAMS)                  |         |

| Product Selection Guide |                 |                        | . 3-1   |

| MT42C406464K X 4 DR     | AM, 256 X 4 SAM |                        | . 3-3   |

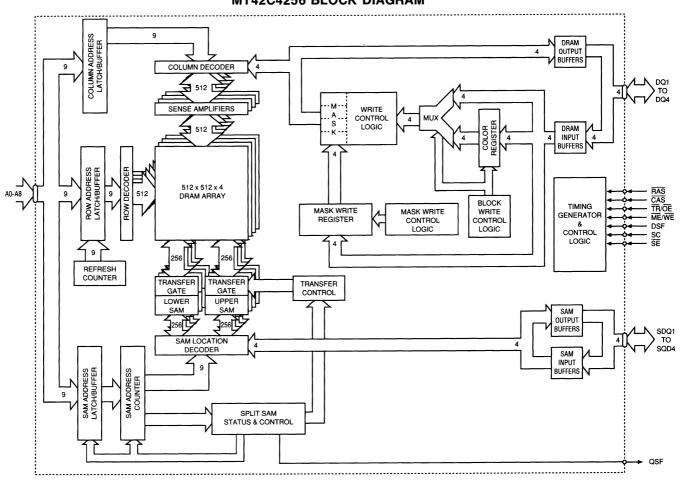

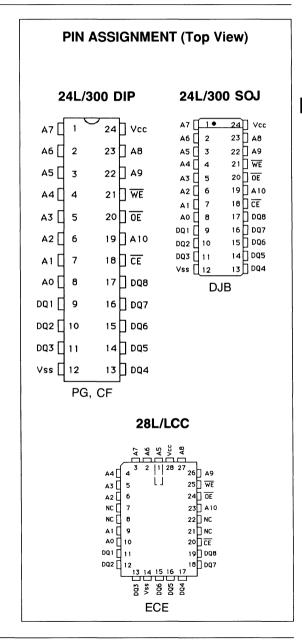

| MT42C4256256K X 4 DR    | AM, 512 X 4 SAM |                        | . 3-29  |

| S | TATIC RAMS              |                     | I             | PAGE  |

|---|-------------------------|---------------------|---------------|-------|

|   | Product Selection Guide |                     |               | 4-1   |

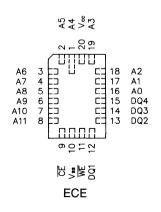

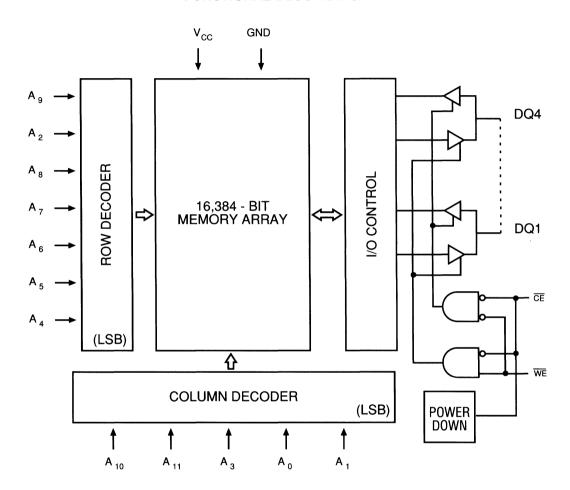

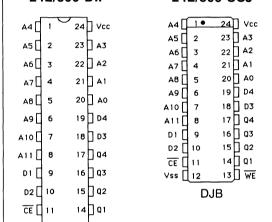

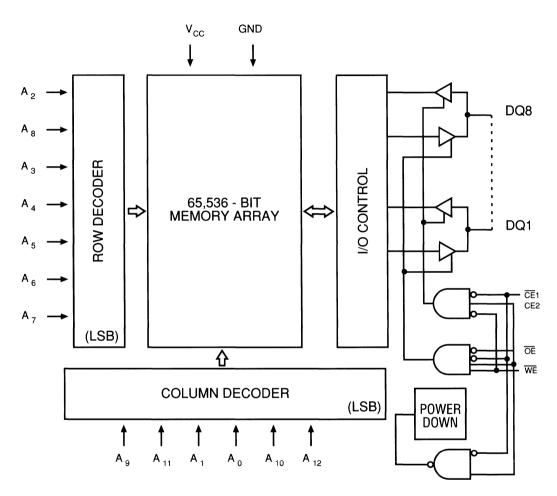

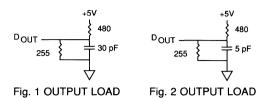

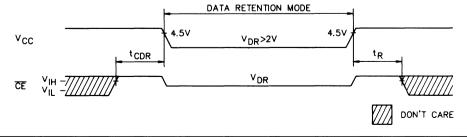

|   | MT5C1608                | 2K X 8              |               | 4-3   |

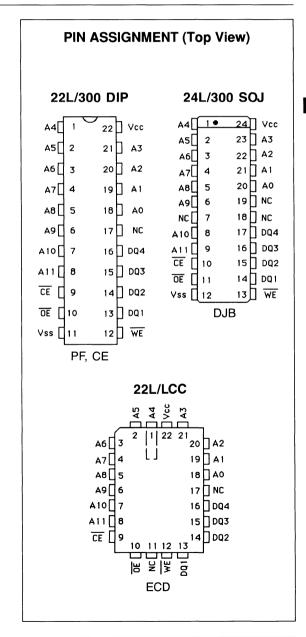

|   | MT5C1604                | 4K X 4              |               | 4-11  |

|   | MT5C1605                | 4K X 4              | OE            | 4-19  |

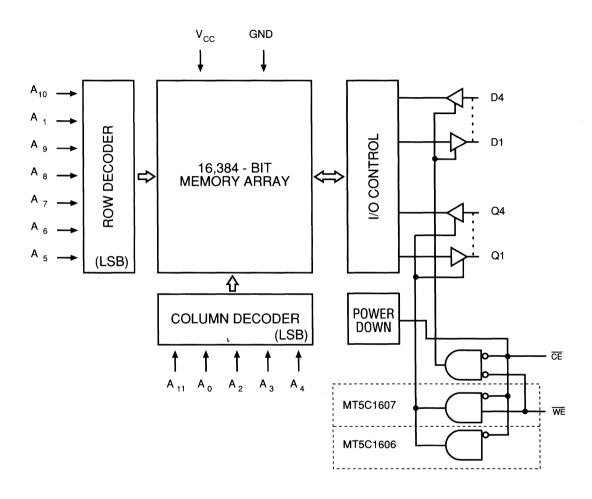

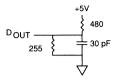

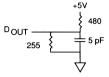

|   | MT5C1606                | 4K X 4              | SI/O, OT      | 4-27  |

|   | MT5C1607                | 4K X 4              | SI/O, HZ      | 4-27  |

|   | MT5C6416                | 4K X 16             |               | 4-35  |

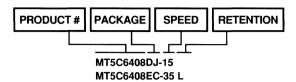

|   | MT5C6408                | 8K X 8              |               | 4-37  |

|   | MT5C1601                | 16K-X 1             |               | 4-45  |

|   | MT5C6404                | 16K X 4             |               | 4-53  |

|   | MT5C6405                | 16K X 4             | OE            | 4-61  |

|   | MT5C6405T               | 16K X 4             | CACHE TAG     | 4-69  |

|   | MT5C6406                | 16K X 4             | SI/O, OT      | 4-77  |

|   | MT5C6407                | 16K X 4             | SI/O, HZ      | 4-77  |

|   | MT5C2568                | 32K X 8             |               | 4-85  |

|   | MT5C6401                | 64K X 1             |               | 4-93  |

|   | MT5C2564                | 64K X 4             |               | 4-101 |

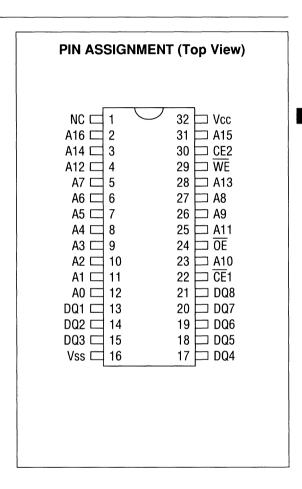

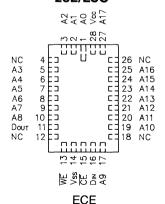

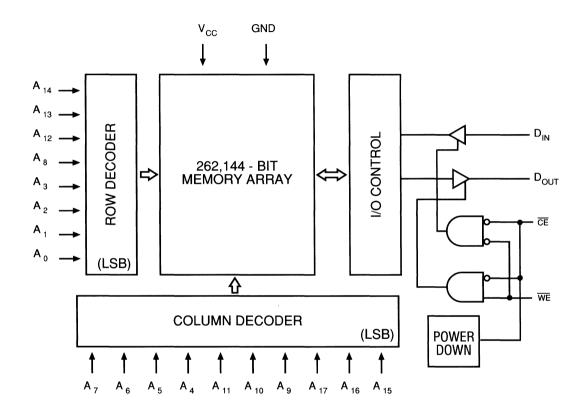

|   | MT5C2565                | 64K X 4             | OE            | 4-109 |

|   | MT5C1008                | 128K X 8            |               | 4-117 |

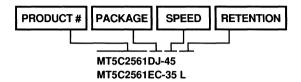

|   | MT5C2561                |                     |               | 4-119 |

|   | MT5C1005                | 256K X 4            |               | 4-127 |

|   | MT5C1001                | 1MEG X 1            |               | 4-129 |

|   | OE                      | With Output Enable  |               |       |

|   | SI/OSeparate Data       | Inputs and Outputs  |               |       |

|   | OTOutputs Track I       |                     |               |       |

|   | HZHigh Impedince Ou     | utputs During write |               |       |

| C | CACHE DATA STATIC I     |                     |               |       |

|   | Product Selection Guide | ,                   |               | 5-1   |

|   |                         |                     | or 8K Y 16/18 |       |

## MICHON

| FIFO MEMORIES (FIRST-IN FIRST-OUT) PA |              |             |        |

|---------------------------------------|--------------|-------------|--------|

| Product Selection Guide               |              |             | 6-1    |

| MT52C80065                            | 512 X 8      | MB, VF      | 6-3    |

| MT52C90055                            |              | E           |        |

| MT52C90065                            | 512 X 9      | MB          | 6-7    |

| MT52C90075                            | 512 X 9      | VF          | 6-9    |

| MT52C1605                             | 512 X 16     | E, MB, VF   | 6-11   |

| MT52C16075                            | 512 X 16/8   | E, MB, VF   | 6-13   |

| MT52C8011                             | 1K X 8       | MB,VF       | 6-15   |

| MT52C9010                             |              | E           | 6-17   |

| MT52C9011                             | 1K X 9       | MB          | 6-19   |

| MT52C9012                             | 1K X 9       | VF          | 6-21   |

| MT52C1610                             |              | E, MB, VF   |        |

| MT52C1612                             |              | E, MB, VF   |        |

| MT52C8021                             |              | MB, VF      |        |

| MT52C9020                             |              | E           | . 6-29 |

| MT52C9021                             |              | MB          |        |

| MT52C9022                             |              | VF          |        |

| MT52C1620                             | 2K X 16      | E, MB, VF   |        |

| MT52C1622                             | •            | E, MB,VF    |        |

| MT52C8041                             |              | E, MB, VF   |        |

| MT52C9040                             |              | E           |        |

| MT52C9041                             |              | MB          |        |

| MT52C9042                             | 4K X 9       | VF          | . 6-45 |

| E                                     | gister Logic |             |        |

| Comments                              |              |             | . 7-1  |

| Product Selection Guide               |              |             | . 7-3  |

| DRAM                                  |              |             |        |

| MT4264                                | 64K X 1      | M, SMD      | . 7-5  |

| MT4067                                |              | M, SMD      |        |

| MT1259                                |              | M, SMD, JAN |        |

| MT4C4256                              |              | M, SMD, JAN |        |

| MT4C10241                             |              | M, SMD, JAN |        |

| MILITARY PRODUCTS (Continued)         |                        | PAGE           |

|---------------------------------------|------------------------|----------------|

| VRAM                                  |                        |                |

| MT42C406464K X 4                      | M, SMD                 | . 7-65         |

| SRAM                                  |                        |                |

| MT5C16082K X 8                        | M, SMD                 | . <i>7-</i> 95 |

| MT5C64088K X 8                        | M, SMD, JAN            |                |

| MT5C160116K X 1                       | M, SMD, JAN            | . 7-111        |

| MT5C640416K X 4                       | M, SMD, JAN            |                |

| MT5C256832K X 8                       | M, SMD, JAN, R+, VHSIC |                |

| MT5C640164K X 1                       | M                      | . 7-135        |

| MT5C256464K X 4                       | M, SMD, JAN, R+, VHSIC | . 7-143        |

| MT5C2561256K X 1                      | M, SMD, JAN            | . 7-151        |

| M                                     |                        |                |

| PACKAGE INFORMATION                   |                        |                |

| Index                                 |                        | . 8-1          |

| SALES INFORMATION                     |                        |                |

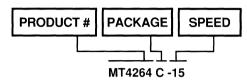

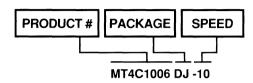

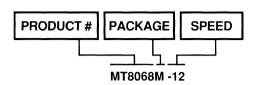

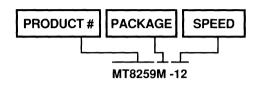

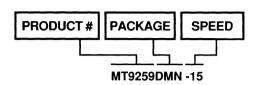

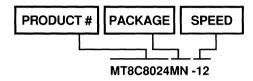

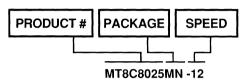

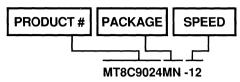

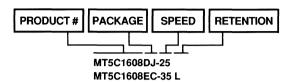

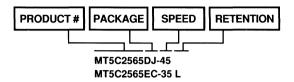

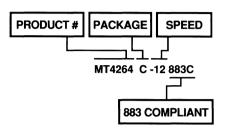

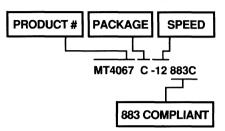

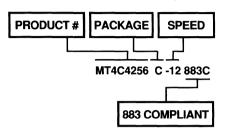

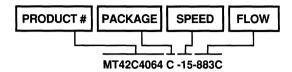

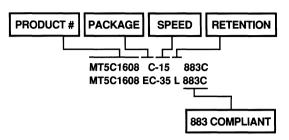

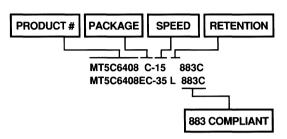

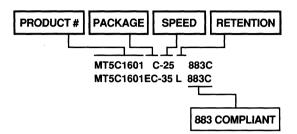

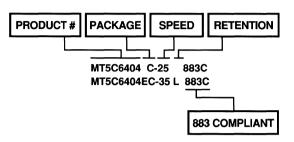

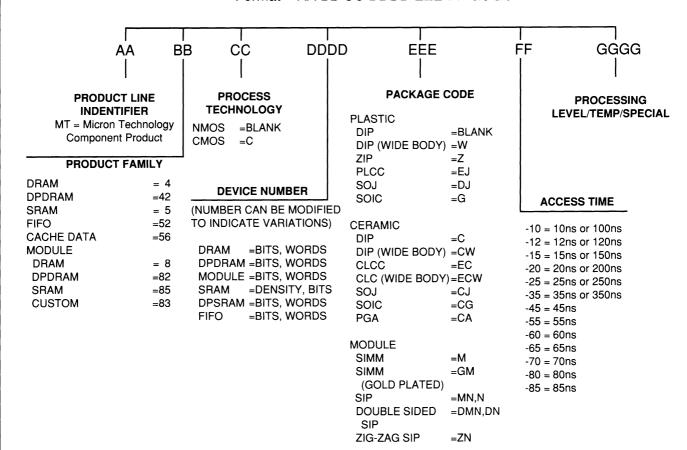

| Product Numbering System              |                        | . 9-1          |

| Sales Representatives and             |                        |                |

| Distributers by geographical location |                        | . 9-3          |

## MICRON

| Part #         1259         DRAM         1-23           1259 883C         DRAM         7-29           4067         DRAM         1-13           4067 883C         DRAM         7-17           4264         DRAM         1-3           4264 883C         DRAM         1-3           4264 883C         DRAM         1-117           4C1004         DRAM         1-117           4C1005         DRAM         1-117           4C1006         DRAM         1-129           4C1004         DRAM         1-141           4C1024         DRAM         1-157           4C1024 883C         DRAM         1-57           4C1024 883C         DRAM         1-69           4C1025         DRAM         1-69           4C1026         DRAM         1-793           4C4001         DRAM         1-193           4C4001         DRAM         1-105           4C4256         DRAM         1-13           4C4256         DRAM         1-33           4C4256         DRAM         1-41           4C24256         VRAM         3-3           42C4064         VRAM         3-3 </th <th>NUMERICAL INDEX</th> <th></th> <th>F</th> <th>AGE</th> | NUMERICAL INDEX |      | F                                       | AGE   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|-----------------------------------------|-------|

| 1259 883C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Part #          |      |                                         |       |

| 1-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1259            | DRAM |                                         | 1-23  |

| 1-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1259 883C       | DRAM |                                         | 7-29  |

| 4264 883C       DRAM       7-5         4C1004       DRAM       1-117         4C1005       DRAM       1-1129         4C1006       DRAM       1-129         4C1006       DRAM       1-141         4C1024       DRAM       1-57         4C1024       DRAM       7-53         4C1025       DRAM       1-69         4C1026       DRAM       1-81         4C4001       DRAM       1-93         4C4003       DRAM       1-105         4C4256       DRAM       1-105         4C4256       DRAM       1-33         4C4256       DRAM       1-45         4C4064       VRAM       3-3         42C4064       VRAM       3-3         42C4064       VRAM       3-3         42C4064       VRAM       3-29         5C1001       SRAM       4-129         5C1008       SRAM       4-129         5C1008       SRAM       4-125         5C1601       SRAM       4-15         5C1605       SRAM       4-17         5C1606       SRAM       4-27         5C1608       SRAM       4-27 <td>4067</td> <td>DRAM</td> <td></td> <td></td>                                                                                                         | 4067            | DRAM |                                         |       |

| 4264 883C       DRAM       7-5         4C1004       DRAM       1-117         4C1005       DRAM       1-129         4C1006       DRAM       1-141         4C1024       DRAM       1-57         4C1024 883C       DRAM       7-53         4C1025       DRAM       1-69         4C1026       DRAM       1-81         4C4001       DRAM       1-181         4C4003       DRAM       1-105         4C4256       DRAM       1-33         4C4256       DRAM       7-41         4C4258       DRAM       7-41         4C4258       DRAM       7-45         42C4064       VRAM       3-3         42C4064 883C       VRAM       3-29         5C1001       SRAM       4-129         5C1005       SRAM       4-127         5C1006       SRAM       4-125         5C1601       SRAM       4-45         5C1604       SRAM       4-11         5C1606       SRAM       4-11         5C1608       SRAM       4-27         5C1609       SRAM       4-27         5C1608       SRAM       4-27 <td>4067 883C</td> <td>DRAM</td> <td></td> <td>7-17</td>                                                                                       | 4067 883C       | DRAM |                                         | 7-17  |

| 4C1004       DRAM       1-117         4C1005       DRAM       1-129         4C1006       DRAM       1-141         4C1024       DRAM       1-57         4C1024 883C       DRAM       7-53         4C1025       DRAM       1-69         4C1026       DRAM       1-81         4C4001       DRAM       1-93         4C4003       DRAM       1-105         4C4256       DRAM       1-33         4C4256       DRAM       7-41         4C4258       DRAM       1-45         42C4064       VRAM       3-3         42C4064 883C       VRAM       3-29         5C1001       SRAM       4-129         5C1005       SRAM       4-125         5C1006       SRAM       4-125         5C1601       SRAM       4-125         5C1604       SRAM       4-19         5C1605       SRAM       4-19         5C1606       SRAM       4-19         5C1607       SRAM       4-19         5C1608       SRAM       4-19         5C1608       SRAM       4-27         5C1608       SRAM       4-27                                                                                                                                                  | 4264            | DRAM |                                         | 1-3   |

| 4C1005       DRAM       1-129         4C1006       DRAM       1-141         4C1024       DRAM       1-57         4C1024 883C       DRAM       7-53         4C1025       DRAM       1-69         4C1026       DRAM       1-81         4C4001       DRAM       1-93         4C4003       DRAM       1-105         4C4256       DRAM       1-33         4C4256 883C       DRAM       7-41         4C4258       DRAM       1-45         42C4064       VRAM       3-3         42C4064 883C       VRAM       3-29         5C1001       SRAM       4-129         5C1005       SRAM       4-129         5C1006       SRAM       4-125         5C1601       SRAM       4-15         5C1604       SRAM       4-11         5C1605       SRAM       4-11         5C1606       SRAM       4-17         5C1607       SRAM       4-17         5C1608       SRAM       4-27         5C1608       SRAM       4-27         5C1608       SRAM       4-27         5C1608       SRAM       4-17 <td>4264 883C</td> <td>DRAM</td> <td></td> <td>7-5</td>                                                                                       | 4264 883C       | DRAM |                                         | 7-5   |

| 4C1006       DRAM       1-141         4C1024       DRAM       1-57         4C1024 883C       DRAM       7-53         4C1025       DRAM       1-69         4C1026       DRAM       1-93         4C4001       DRAM       1-93         4C4003       DRAM       1-105         4C4256       DRAM       7-41         4C4258       DRAM       7-41         4C4258       DRAM       3-3         42C4064       VRAM       3-3         42C4064 883C       VRAM       7-65         42C4256       VRAM       3-29         5C1001       SRAM       4-129         5C1005       SRAM       4-127         5C1008       SRAM       4-125         5C1601       SRAM       4-15         5C1604       SRAM       4-11         5C1605       SRAM       4-11         5C1606       SRAM       4-19         5C1608       SRAM       4-27         5C1608       SRAM       4-27         5C1608       SRAM       4-3         5C1608       SRAM       4-3         5C2561       SRAM       4-11     <                                                                                                                                                 | 4C1004          | DRAM |                                         | 1-117 |

| 4C1024       DRAM       1-57         4C1025       DRAM       7-53         4C1025       DRAM       1-69         4C1026       DRAM       1-81         4C4001       DRAM       1-93         4C4003       DRAM       1-105         4C4256       BRAM       1-33         4C4256 883C       DRAM       7-41         4C4258       DRAM       1-45         4C4064       VRAM       3-3         4C4064 883C       VRAM       7-65         4C24256       VRAM       3-29         5C1001       SRAM       4-129         5C1005       SRAM       4-125         5C1008       SRAM       4-125         5C1601       SRAM       4-15         5C1604       SRAM       4-11         5C1605       SRAM       4-11         5C1606       SRAM       4-27         5C1608       SRAM       4-27         5C1608       SRAM       4-3         5C1608       SRAM       4-3         5C1608       SRAM       4-17         5C2561       SRAM       4-11         5C2564       SRAM       4-101 </td <td>4C1005</td> <td>DRAM</td> <td></td> <td>1-129</td>                                                                                            | 4C1005          | DRAM |                                         | 1-129 |

| 4C1024 883C       DRAM       7-53         4C1025       DRAM       1-69         4C1026       DRAM       1-81         4C4001       DRAM       1-93         4C4003       DRAM       1-105         4C4256       DRAM       1-33         4C4256 883C       DRAM       7-41         4C4258       DRAM       1-45         42C4064       VRAM       3-3         42C4064 883C       VRAM       7-65         42C4256       VRAM       3-29         5C1001       SRAM       4-129         5C1005       SRAM       4-125         5C1008       SRAM       4-125         5C1601       SRAM       4-45         5C1604       SRAM       4-11         5C1605       SRAM       4-11         5C1606       SRAM       4-27         5C1608       SRAM       4-27         5C1608       SRAM       4-3         5C1608       SRAM       4-3         5C1608       SRAM       4-11         5C2561       SRAM       4-11         5C2564       SRAM       4-101         5C2565       SRAM       4-101 <td>4C1006</td> <td>DRAM</td> <td></td> <td>1-141</td>                                                                                         | 4C1006          | DRAM |                                         | 1-141 |

| 4C1025       DRAM       1-69         4C1026       DRAM       1-81         4C4001       DRAM       1-93         4C4003       DRAM       1-105         4C4256       DRAM       1-33         4C4256 883C       DRAM       7-41         4C4258       DRAM       1-45         42C4064       VRAM       3-3         42C4064 883C       VRAM       3-29         5C1001       SRAM       4-129         5C1005       SRAM       4-125         5C1005       SRAM       4-125         5C1601       SRAM       4-45         5C1601 883C       SRAM       7-111         5C1605       SRAM       4-11         5C1606       SRAM       4-19         5C1607       SRAM       4-27         5C1608       SRAM       4-3         5C1608       SRAM       4-3         5C2561       SRAM       7-95         5C2561       SRAM       4-117         5C2564       SRAM       7-151         5C2564       SRAM       7-143         5C2565       SRAM       7-143         5C2565       SRAM       4-109<                                                                                                                                            |                 |      |                                         | 1-57  |

| 4C1025       DRAM       1-69         4C1026       DRAM       1-81         4C4001       DRAM       1-93         4C4003       DRAM       1-105         4C4256       DRAM       1-33         4C4256 883C       DRAM       7-41         4C4258       DRAM       1-45         42C4064       VRAM       3-3         42C4064 883C       VRAM       3-29         5C1001       SRAM       4-129         5C1005       SRAM       4-125         5C1005       SRAM       4-125         5C1601       SRAM       4-45         5C1601 883C       SRAM       7-111         5C1605       SRAM       4-11         5C1606       SRAM       4-19         5C1607       SRAM       4-27         5C1608       SRAM       4-3         5C1608       SRAM       4-3         5C2561       SRAM       7-95         5C2561       SRAM       4-117         5C2564       SRAM       7-151         5C2564       SRAM       7-143         5C2565       SRAM       7-143         5C2565       SRAM       4-109<                                                                                                                                            | 4C1024 883C     | DRAM |                                         | 7-53  |

| 4C4001       DRAM       1-93         4C4003       DRAM       1-105         4C4256       DRAM       1-33         4C4256 883C       DRAM       7-41         4C4258       DRAM       1-45         42C4064       VRAM       3-3         42C4064 883C       VRAM       7-65         42C4256       VRAM       3-29         5C1001       SRAM       4-129         5C1005       SRAM       4-127         5C1008       SRAM       4-125         5C1601       SRAM       4-45         5C1601       SRAM       4-11         5C1605       SRAM       4-11         5C1606       SRAM       4-19         5C1607       SRAM       4-27         5C1608       SRAM       4-27         5C1608       SRAM       4-3         5C2561       SRAM       4-117         5C2564       SRAM       7-151         5C2564       SRAM       7-143         5C2565       SRAM       4-109                                                                                                                                                                                                                                                                 |                 |      |                                         |       |

| 4C4001       DRAM       1-93         4C4003       DRAM       1-105         4C4256       DRAM       1-33         4C4256 883C       DRAM       7-41         4C4258       DRAM       1-45         42C4064       VRAM       3-3         42C4064 883C       VRAM       7-65         42C4256       VRAM       3-29         5C1001       SRAM       4-129         5C1005       SRAM       4-127         5C1008       SRAM       4-125         5C1601       SRAM       4-45         5C1601       SRAM       4-11         5C1605       SRAM       4-11         5C1606       SRAM       4-19         5C1607       SRAM       4-27         5C1608       SRAM       4-27         5C1608       SRAM       4-3         5C2561       SRAM       4-117         5C2564       SRAM       7-151         5C2564       SRAM       7-143         5C2565       SRAM       4-109                                                                                                                                                                                                                                                                 | 4C1026          | DRAM |                                         | 1-81  |

| 4C4003       DRAM       1-105         4C4256       DRAM       1-33         4C4256 883C       DRAM       7-41         4C4258       DRAM       1-45         42C4064       VRAM       3-3         42C4064 883C       VRAM       7-65         42C4256       VRAM       3-29         5C1001       SRAM       4-129         5C1005       SRAM       4-127         5C1008       SRAM       4-125         5C1601       SRAM       4-45         5C1601 883C       SRAM       7-111         5C1604       SRAM       4-11         5C1605       SRAM       4-19         5C1606       SRAM       4-27         5C1608       SRAM       4-27         5C1608       SRAM       4-3         5C1608       SRAM       4-3         5C1608       SRAM       7-95         5C2561       SRAM       7-151         5C2564       SRAM       4-101         5C2565       SRAM       4-109                                                                                                                                                                                                                                                             | 4C4001          | DRAM |                                         | 1-93  |

| 4C4256       DRAM       1-33         4C4256 883C       DRAM       7-41         4C4258       DRAM       1-45         42C4064       VRAM       3-3         42C4064 883C       VRAM       7-65         42C4256       VRAM       3-29         5C1001       SRAM       4-129         5C1005       SRAM       4-127         5C1008       SRAM       4-125         5C1601       SRAM       4-45         5C1601       SRAM       7-111         5C1604       SRAM       4-11         5C1605       SRAM       4-19         5C1606       SRAM       4-27         5C1608       SRAM       4-27         5C1608       SRAM       4-3         5C1608       SRAM       4-3         5C2561       SRAM       7-95         5C2564       SRAM       7-151         5C2564       SRAM       4-101         5C2565       SRAM       4-109                                                                                                                                                                                                                                                                                                        |                 |      |                                         | 1-105 |

| 4C4256 883C       DRAM       7-41         4C4258       DRAM       1-45         42C4064       VRAM       3-3         42C4064 883C       VRAM       7-65         42C4256       VRAM       3-29         5C1001       SRAM       4-129         5C1005       SRAM       4-127         5C1008       SRAM       4-125         5C1601       SRAM       4-45         5C1601       SRAM       7-111         5C1604       SRAM       4-11         5C1605       SRAM       4-11         5C1606       SRAM       4-19         5C1607       SRAM       4-27         5C1608       SRAM       4-3         5C1608       SRAM       4-3         5C1608       SRAM       4-11         5C2561       SRAM       7-95         5C2564       SRAM       7-151         5C2564       SRAM       4-101         5C2565       SRAM       4-109                                                                                                                                                                                                                                                                                                        |                 |      |                                         | 1-33  |

| 4C4258       DRAM       1-45         42C4064       VRAM       3-3         42C4064 883C       VRAM       7-65         42C4256       VRAM       3-29         5C1001       SRAM       4-129         5C1005       SRAM       4-127         5C1008       SRAM       4-125         5C1601       SRAM       4-45         5C1601 883C       SRAM       7-111         5C1604       SRAM       4-11         5C1605       SRAM       4-19         5C1606       SRAM       4-27         5C1607       SRAM       4-27         5C1608       SRAM       4-3         5C1608       SRAM       4-3         5C2561       SRAM       7-95         5C2564       SRAM       7-151         5C2564       SRAM       4-101         5C2565       SRAM       4-109                                                                                                                                                                                                                                                                                                                                                                                  |                 |      |                                         | 7-41  |

| 42C4064       VRAM       3-3         42C4064 883C       VRAM       7-65         42C4256       VRAM       3-29         5C1001       SRAM       4-129         5C1005       SRAM       4-127         5C1008       SRAM       4-125         5C1601       SRAM       4-45         5C1601 883C       SRAM       7-111         5C1604       SRAM       4-11         5C1605       SRAM       4-19         5C1606       SRAM       4-27         5C1607       SRAM       4-27         5C1608       SRAM       4-3         5C1608 883C       SRAM       4-3         5C2561       SRAM       7-151         5C2564       SRAM       7-151         5C2564       SRAM       7-143         5C2565       SRAM       4-109                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |      |                                         |       |

| 42C4064 883C       VRAM       7-65         42C4256       VRAM       3-29         5C1001       SRAM       4-129         5C1005       SRAM       4-127         5C1008       SRAM       4-125         5C1601       SRAM       4-45         5C1601 883C       SRAM       7-111         5C1604       SRAM       4-11         5C1605       SRAM       4-19         5C1606       SRAM       4-27         5C1607       SRAM       4-27         5C1608       SRAM       4-3         5C1608 883C       SRAM       7-95         5C2561       SRAM       7-151         5C2564       SRAM       7-151         5C2564       SRAM       4-101         5C2565       SRAM       7-143         5C2565       SRAM       4-109                                                                                                                                                                                                                                                                                                                                                                                                               |                 |      |                                         |       |

| 42C4256       VRAM       3-29         5C1001       SRAM       4-129         5C1005       SRAM       4-127         5C1008       SRAM       4-125         5C1601       SRAM       4-45         5C1601 883C       SRAM       7-111         5C1604       SRAM       4-11         5C1605       SRAM       4-19         5C1606       SRAM       4-27         5C1607       SRAM       4-27         5C1608       SRAM       4-3         5C1608 883C       SRAM       7-95         5C2561       SRAM       4-117         5C2564       SRAM       7-151         5C2564 883C       SRAM       4-101         5C2565       SRAM       7-143         5C2565       SRAM       4-109                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |      |                                         |       |

| 5C1001       SRAM       4-129         5C1005       SRAM       4-127         5C1008       SRAM       4-125         5C1601       SRAM       4-45         5C1601 883C       SRAM       7-111         5C1604       SRAM       4-11         5C1605       SRAM       4-19         5C1606       SRAM       4-27         5C1607       SRAM       4-27         5C1608       SRAM       4-3         5C1608 883C       SRAM       4-3         5C2561       SRAM       7-95         5C2561       SRAM       7-151         5C2564       SRAM       4-101         5C2565       SRAM       7-143         5C2565       SRAM       4-109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                 |      |                                         |       |

| 5C1005       SRAM       4-127         5C1008       SRAM       4-125         5C1601       SRAM       4-45         5C1601 883C       SRAM       7-111         5C1604       SRAM       4-11         5C1605       SRAM       4-19         5C1606       SRAM       4-27         5C1607       SRAM       4-27         5C1608       SRAM       4-3         5C1608 883C       SRAM       7-95         5C2561       SRAM       4-117         5C2564       SRAM       7-151         5C2564       SRAM       4-101         5C2565       SRAM       7-143         5C2565       SRAM       4-109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |      |                                         |       |

| 5C1008       SRAM       4-125         5C1601       SRAM       4-45         5C1601 883C       SRAM       7-111         5C1604       SRAM       4-11         5C1605       SRAM       4-19         5C1606       SRAM       4-27         5C1607       SRAM       4-27         5C1608       SRAM       4-3         5C1608 883C       SRAM       7-95         5C2561       SRAM       4-117         5C2564 883C       SRAM       7-151         5C2564       SRAM       4-101         5C2565       SRAM       7-143         5C2565       SRAM       4-109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |      |                                         |       |

| 5C1601       SRAM       4-45         5C1601 883C       SRAM       7-111         5C1604       SRAM       4-11         5C1605       SRAM       4-19         5C1606       SRAM       4-27         5C1607       SRAM       4-27         5C1608       SRAM       4-3         5C1608 883C       SRAM       7-95         5C2561       SRAM       4-117         5C2564 883C       SRAM       7-151         5C2564       SRAM       4-101         5C2565       SRAM       7-143         5C2565       SRAM       4-109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                 |      |                                         |       |

| 5C1601 883C       SRAM       7-111         5C1604       SRAM       4-11         5C1605       SRAM       4-19         5C1606       SRAM       4-27         5C1607       SRAM       4-27         5C1608       SRAM       4-3         5C1608 883C       SRAM       7-95         5C2561       SRAM       4-117         5C2564       SRAM       7-151         5C2564       SRAM       4-101         5C2565       SRAM       7-143         5C2565       SRAM       4-109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |      |                                         |       |

| 5C1604       SRAM       4-11         5C1605       SRAM       4-19         5C1606       SRAM       4-27         5C1607       SRAM       4-27         5C1608       SRAM       4-3         5C1608 883C       SRAM       7-95         5C2561       SRAM       4-117         5C2561 883C       SRAM       7-151         5C2564       SRAM       4-101         5C2564 883C       SRAM       7-143         5C2565       SRAM       4-109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 |      |                                         |       |

| 5C1605       SRAM       4-19         5C1606       SRAM       4-27         5C1607       SRAM       4-27         5C1608       SRAM       4-3         5C1608 883C       SRAM       7-95         5C2561       SRAM       4-117         5C2561 883C       SRAM       7-151         5C2564       SRAM       4-101         5C2564 883C       SRAM       7-143         5C2565       SRAM       4-109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                 |      |                                         |       |

| 5C1606       SRAM       4-27         5C1607       SRAM       4-27         5C1608       SRAM       4-3         5C1608 883C       SRAM       7-95         5C2561       SRAM       4-117         5C2561 883C       SRAM       7-151         5C2564       SRAM       4-101         5C2564 883C       SRAM       7-143         5C2565       SRAM       4-109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                 |      |                                         |       |

| 5C1607       SRAM       4-27         5C1608       SRAM       4-3         5C1608 883C       SRAM       7-95         5C2561       SRAM       4-117         5C2561 883C       SRAM       7-151         5C2564       SRAM       4-101         5C2564 883C       SRAM       7-143         5C2565       SRAM       4-109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |      |                                         |       |

| 5C1608       SRAM       4-3         5C1608 883C       SRAM       7-95         5C2561       SRAM       4-117         5C2561 883C       SRAM       7-151         5C2564       SRAM       4-101         5C2564 883C       SRAM       7-143         5C2565       SRAM       4-109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |      |                                         |       |

| 5C1608 883C       SRAM       7-95         5C2561       SRAM       4-117         5C2561 883C       SRAM       7-151         5C2564       SRAM       4-101         5C2564 883C       SRAM       7-143         5C2565       SRAM       4-109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |      |                                         |       |

| 5C2561       SRAM       4-117         5C2561 883C       SRAM       7-151         5C2564       SRAM       4-101         5C2564 883C       SRAM       7-143         5C2565       SRAM       4-109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 |      |                                         |       |

| 5C2561 883C       SRAM       7-151         5C2564       SRAM       4-101         5C2564 883C       SRAM       7-143         5C2565       SRAM       4-109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |      | *************************************** |       |

| 5C2564       SRAM       4-101         5C2564 883C       SRAM       7-143         5C2565       SRAM       4-109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 |      |                                         |       |

| 5C2564 883C       SRAM       7-143         5C2565       SRAM       4-109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |      |                                         |       |

| 5C2565 SRAM 4-109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 |      |                                         |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 |      |                                         |       |

| N / N/O 3N A IVI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                 |      |                                         |       |

| <b>NUMERICAL INI</b> | DEX (Continued) | I | PAGE  |

|----------------------|-----------------|---|-------|

| Part #               |                 |   |       |

| 5C2568 883C          | SRAM            |   | 7-129 |

|                      | SRAM            |   |       |

| 5C6401 883C          | SRAM            |   |       |

| 5C6404               | SRAM            |   | 4-53  |

|                      | SRAM            |   | 7-119 |

| 5C6405               | SRAM            |   | 4-61  |

|                      | SRAM            |   |       |

| 5C6406               | SRAM            |   |       |

| 5C6407               | SRAM            |   | 4-77  |

| 5C6408               | SRAM            |   |       |

| 5C6408 883C          | SRAM            |   | 7-103 |

|                      | SRAM            |   |       |

|                      | FIFO            |   |       |

| 52C1607              | FIFO            |   | 6-13  |

|                      | FIFO            |   |       |

|                      | FIFO            |   | 6-25  |

|                      | FIFO            |   |       |

| 52C1622              | FIFO            |   |       |

|                      | FIFO            |   | 6-3   |

|                      | FIFO            |   |       |

|                      | FIFO            |   | 6-27  |

|                      | FIFO            |   | 6-39  |

|                      | FIFO            |   |       |

|                      | FIFO            |   | 6-7   |

|                      | FIFO            |   |       |

|                      | FIFO            |   | 6-17  |

|                      | FIFO            |   | 6-19  |

|                      | FIFO            |   |       |

|                      | FIFO            |   | 6-29  |

|                      | FIFO            |   |       |

|                      | FIFO            |   | 6-33  |

|                      | FIFO            |   | 6-41  |

|                      | FIFO            |   |       |

|                      | FIFO            |   |       |

|                      | CACHE SRAM      |   |       |

|                      | DRAM MODULE     |   |       |

|                      | DRAM MODULE     |   |       |

|                      | DRAM MODULE     |   | 0.50  |

### MICRON

| NUMERICAL II<br>Part # | NDEX (Continued) | I | PAGE  |

|------------------------|------------------|---|-------|

| 85259                  | DRAM MODULE      |   | 2-33  |

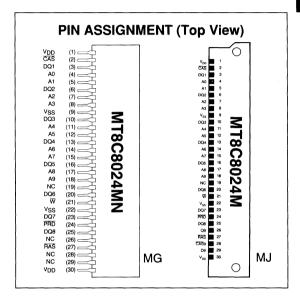

| 8C3656                 | DRAM MODULE      |   |       |

| 8C8024                 | DRAM MODULE      |   | 2-93  |

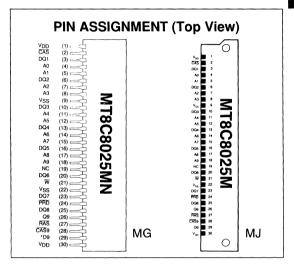

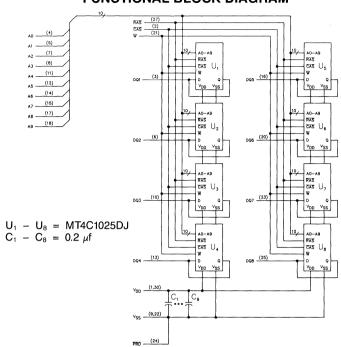

| 8C8025                 | DRAM MODULE      |   | 2-103 |

| 8C8026                 | DRAM MODULE      |   | 2-115 |

| 8C9024                 | DRAM MODULE      |   | 2-127 |

| 8C9025                 | DRAM MODULE      |   | 2-137 |

| 8C9026                 | DRAM MODULE      |   | 2-149 |

| 9068                   | DRAM MODULE      |   | 2-13  |

| 9259                   | DRAM MODULE      |   | 2-63  |

| 0250                   | DRAMACDITE       |   | 0.70  |

| DYNAMIC RAMs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| DYNAMIC RAM MODULES SEGRECARIOS SON SEGRECARIOS SEGRECARIOS SON SEGRECARIOS SE | 2   |

| MULTIPORT DYNAMIC RAMS (VRAMS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3   |

| STATIC RANS EXCENDED AND ADDRESS OF THE PROPERTY OF THE PROPER | 4   |

| CACHE DATA RAMS DESIGNATION OF THE REPRESENTATION OF THE PROPERTY OF THE PROPE | 5   |

| то и в по по в в в по в в в в                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6   |

| MILITARY PRODUCTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7   |

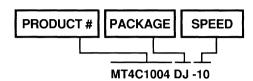

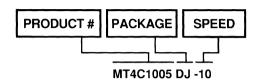

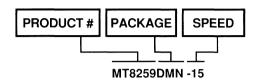

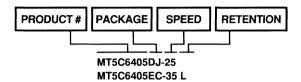

| PACKAGE INFORMATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8   |