## MCA3 ETL Series Design Manual

|  | • |  |  |

|--|---|--|--|

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

| 3  | Macrocell Array Description                 |

|----|---------------------------------------------|

| 4  | DC (Functional) Logic Design Considerations |

| 5  | AC Performance Guidelines                   |

| 6  | Using CAD Tools for Design Development      |

| 7  | Packaging                                   |

| 8  | Design for Testability                      |

| 9  | The Macrocell Library and Specification     |

| 10 | Appendices                                  |

| 11 | Index                                       |

|    |                                             |

Features of the MCA3 ETL Macrocell Array Family

Introduction

# MCA3 ETL SERIES THIRD GENERATION BIPOLAR MACROCELL ARRAYS

Preliminary

September 1991

### **ORIGINATED BY:**

Jerry Prioste

ASIC BIPOLAR PRODUCTS MANAGER

Jon Houghten

ASIC BIPOLAR SYSTEM DESIGN APPLICATIONS ENGINEER

Copyright MOTOROLA INC., 1991 "All Rights Reserved"

Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patient rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application. Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and (A) are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

MECL, MOSAIC II, MOSAIC III, and OACS are trademarks of Motorola. NetEd, SymEd, EXPAND and QuickSim are trademarks of Mentor Graphics Corp. Tri-state is a trademark of National Semiconductor Corp.

### **Summary of Change Information**

The following list represents information which has been added or changed since Version 1.41 of the Preliminary issue of the MCA3 ETL Series Design Manual.

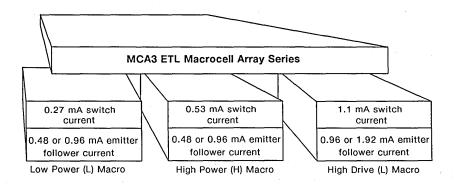

- 1. Revised Section 2.4 and Figure 2-2 to include High Drive (L) Macros in description of speed/power programmability macro selection.

- 2. Included 160 QFP Pad to Pin Cross-Reference Table in Section 4.

- 3. Revised frequency specification and related information on pages 5-23 thru 5-25.

- 4. Included Notes in Pad to Pin Cross-Reference Tables (Section 4) and the 'Fix Placement of I/O Macros/Pins' paragraph (Section 6.3.4) clarifying prefacing actual pin numbers for both the 64 and 160 QFP packages for data entry into the **FIX** file.

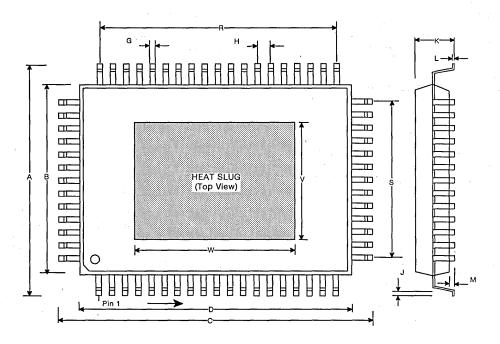

- 5. Included 160 QFP Packaging Information in Section 7.

NOTE: This manual is preliminary and therefore subject to change without notice in order to provide the user with a more accurate specification of the functionality and performance of the product.

### **Acknowledgments:**

The authors would like to acknowledge the MCA3 ETL Array Design Group for their effort and assistance in preparing this manual.

### **TABLE OF CONTENTS**

| Section 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                              |

| 1.1 Arrays Covered in This Manual 1.2 About the Manual 1.3 What is an ETL Macrocell Array?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1-1<br>1-1<br>1-1                                                                                            |

| Section 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                              |

| Features of the MCA3 ETL Macrocell Array Family                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2-1                                                                                                          |

| 2.1 MOSAIC III Technology 2.2 Internal Architecture 2.3 I/O Structure 2.4 Speed/Power Programmability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-2                                                                                                          |

| Section 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                              |

| Macrocell Array Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3-1                                                                                                          |

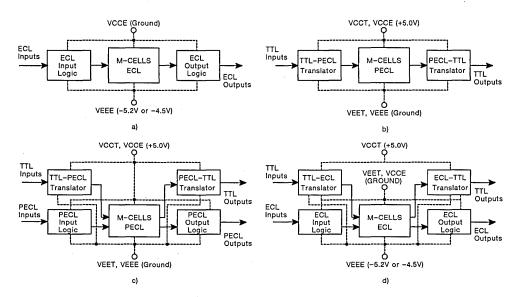

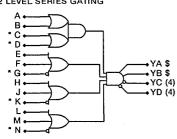

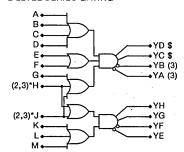

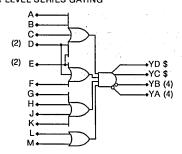

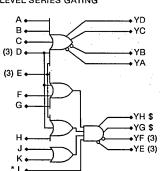

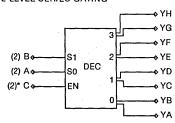

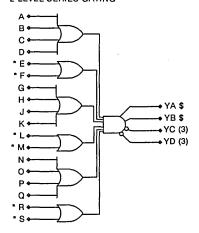

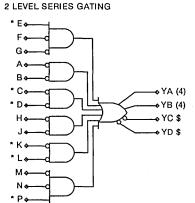

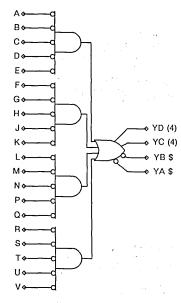

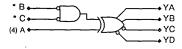

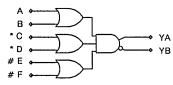

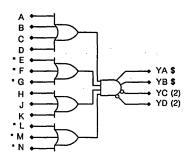

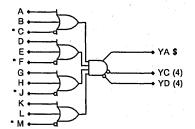

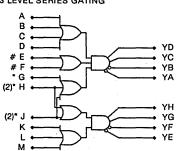

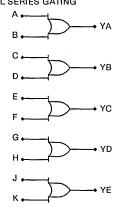

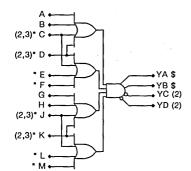

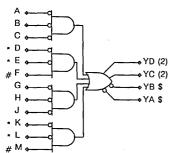

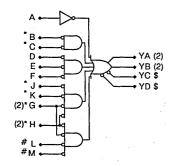

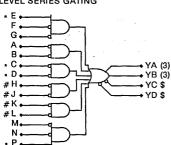

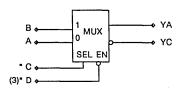

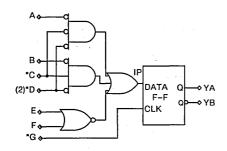

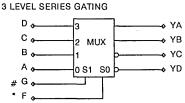

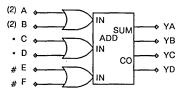

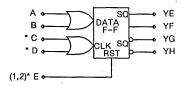

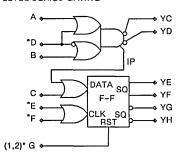

| 3.1 Operational Modes and Allowed I/O 3.1.1 Standard ECL I/O (a) 3.1.2 TTL I/O (b) 3.1.3 PECL/TTL I/O (c) 3.1.4 ECL/TTL I/O (d) 3.1.5 Bidirectional I/O 3.2 Series-Terminated ECL (STECL) 3.3 Series Gating 3.4 Internal Cell Architecture 3.5 Using the Thermal Diode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3-1<br>3-1<br>3-1<br>3-1<br>3-2<br>3-2<br>3-2<br>3-2                                                         |

| Section 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                              |

| DC (Functional) Logic Design Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4-1                                                                                                          |

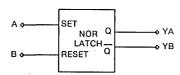

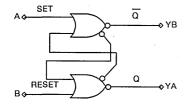

| UPPER and LOWER Level Inputs RESET and SET Input Considerations for Flip-flop and Latch Macros 4.1 I/O Connection Rules 4.1.1 I/O Pin Assignments 4.1.2 Input Configurations 4.1.3 Current Source Inputs 4.1.4 Output Configurations 4.2 Internal Connection Rules 4.2.1 Restrictions on Using Three-Level Series Gated Macros 4.2.2 Rules for 'M' and 'J' Inputs and Outputs 4.2.3 Rules for 'R' or 'N' Outputs 4.2.4 Unused Inputs and Outputs 4.2.5 Maximum Fanout of Macro Outputs 4.2.6 Wired-OR Rules 4.2.7 Twin Outputs 4.2.8 Designing Latches With Gates 4.2.9 Quad Buffer Rules 4.2.10 Using High Drive Macros 4.3 Macrocell Array Floorplans, Reference Tables, and Placement Restrictions 4.3.1 Thermal Diode Placement Restrictions 4.3.2 Macro T90 Placement Restrictions | 4-1<br>4-2<br>4-2<br>4-2<br>4-3<br>4-5<br>4-5<br>4-5<br>4-5<br>4-5<br>4-7<br>4-7<br>4-7<br>4-8<br>4-8<br>4-8 |

| 4.3.3 Edge or Level Sensitive Signal Placement Rules and Recommendations 4.3.4 I/O Macro Placement Restrictions for U-Cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4–9                                                                                                          |

### **TABLE OF CONTENTS** [continued]

| Section 4 DC (Functional) Logic Design Considerations [continued]                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.5 Differential Receivers                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Section 5                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| AC Performance Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5.1 Input/Output Delay Calculations 5–1 5.1.1 I/O Capacitance 5–1 5.1.2 External Degradation Due to Input Capacitance 5–1 5.1.3 Propagation Delay Degradation of the Input Due to Rise/Fall Time and Voltage Skew at the I/O Pin 5–1 5.1.4 Delay From an Input Pad to a Macrocell 5–2 5.1.5 Delay Due to the Package and Bonding 5–2 5.1.6 Simultaneous Switching Limit 5–2                                                                                             |

| 5.1.7 Simultaneous Switching Delay       5-3         5.1.8 Simultaneous Switching Noise       5-4         5.1.9 Output Delays       5-4         5.1.10 Output Edge Rates       5-5         5.1.11 SLOWDOWN Capacitor Delay       5-5         5.2 Between Internal Macros       5-5                                                                                                                                                                                      |

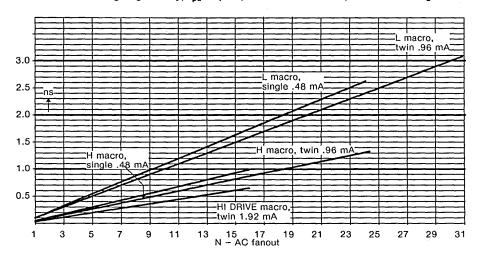

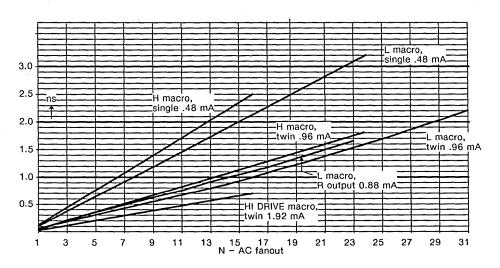

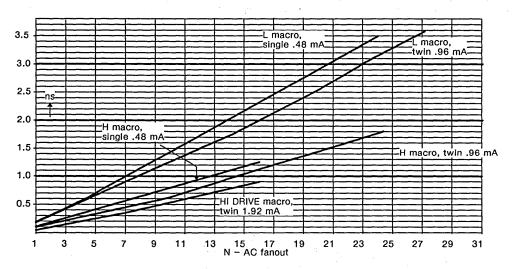

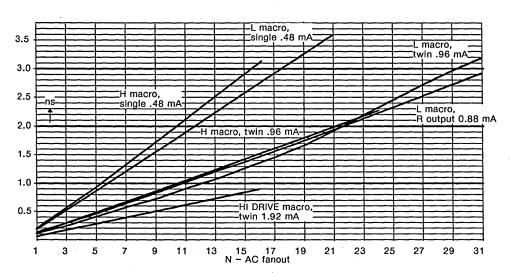

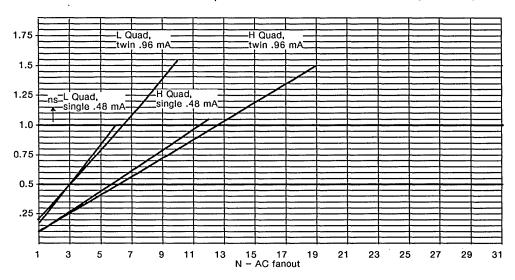

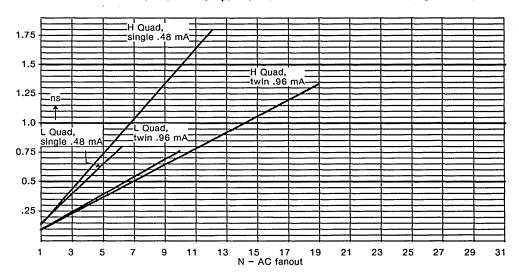

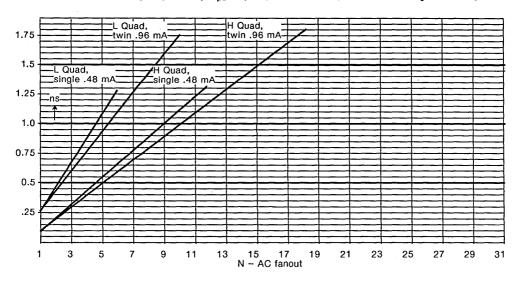

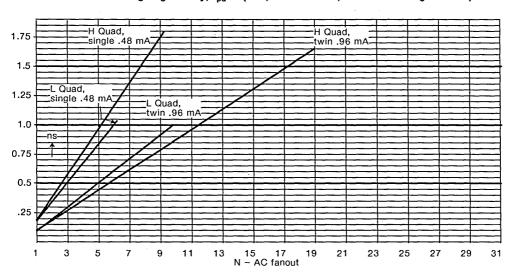

| 5.2.1 Metal and Fanout Degradation 5–5 5.2.2 Metal/Fanout Delay Equations 5–5 5.2.3 Estimating Metal Lengths Before Place and Route 5–10 5.2.4 Metal/Fanout Delay Curves 5–11 5.2.5 Twin Outputs Driving a Single Net 5–15 5.2.6 Twin Outputs Driving Separate Nets 5–15 5.2.7 Quad Buffer Outputs Driving Separate Nets 5–15                                                                                                                                           |

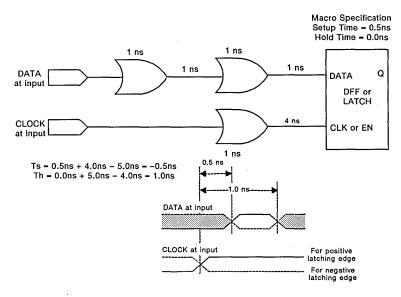

| 5.2.8 Wired-OR Delays       5-15         5.3 Delay Skew Considerations       5-16         5.3.1 Minimum Propagation Delays Due to Process Variation       5-16         5.3.2 Electrical Adjacency       5-16         5.3.3 On-Chip Propagation Delay Skew       5-16         5.3.4 Setup and Hold Time Calculations       5-17         5.3.5 Propagation Delay Skew Between Two Chips       5-21         5.3.6 Clock Distribution and Clock Pulse Generation       5-21 |

| 5-3.7 Pulse Width Shrinkage Due to Rise/Fall Delay Skew 5-23 5.3.8 Pulse Width Shrinkage Due to Narrow Pulses 5-23 5.3.9 Minimum Pulse Width Specifications 5-23 5.4 High Frequency Specifications 5-23 5.4.1 MCA3 ETL Maximum Recommended Operating Frequencies 5-23 5.4.2 High Frequency Input Macros 5-24 5.4.3 High Frequency Outputs 5-25                                                                                                                          |

| 5.4.4 Bit Rate Versus Frequency       5-25         5.4.5 On-chip Operation Above 650 MHz       5-25         5.4.6 High Frequency Design Considerations       5-25         5.5 Differential Calculations       5-26         5.5.1 Differential Macro Delay       5-26         5.5.2 Differential Net Delay       5-26         5.5.3 Differential Pulse Shrinkage Calculations       5-26                                                                                 |

| Section 6                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Using CAD Tools for Design Development                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 6.1 Motorola CAD System Overview 6- Logic Simulation 6- 6.2 MCA3 Option Development Procedure 6- 6.3 MCA3_DELAY (DECAL) Delay Calculation Limitations and Errors 6-                                                                                                                                                                                                                                                                                                     |

### TABLE OF CONTENTS [continued]

| Section 6                                                                                                                                                                    | Using CAD Tools for Design                                                                                                                                                           | Development                                                       | [continued]  |      |                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--------------|------|-------------------------------------------------------------|

| 6.4.1 SUPERNI<br>6.4.2 SPATTER<br>6.4.3 SCOMM/<br>6.4.4 FIX File<br>6.5 CAD Layout<br>6.5.1 Wired-O<br>6.5.2 Via Place                                                       | of Files Required by the WAT File                                                                                                                                                    |                                                                   |              |      | 6-5<br>6-6<br>6-7<br>6-11<br>6-11                           |

| Section 7                                                                                                                                                                    |                                                                                                                                                                                      |                                                                   |              |      |                                                             |

| Packaging                                                                                                                                                                    |                                                                                                                                                                                      |                                                                   |              |      | 7–1                                                         |

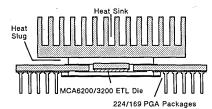

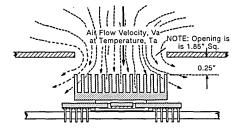

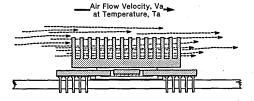

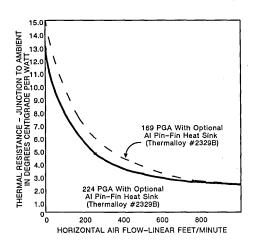

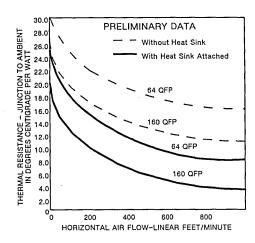

| 7.2 Heat Sinks a                                                                                                                                                             | aracteristics Using Heat Sink<br>and Cooling Considerations<br>aracteristics                                                                                                         |                                                                   |              |      | 7-2                                                         |

| Section 8                                                                                                                                                                    |                                                                                                                                                                                      |                                                                   |              |      |                                                             |

| Design for Testab                                                                                                                                                            | oility                                                                                                                                                                               |                                                                   |              |      | 8–1                                                         |

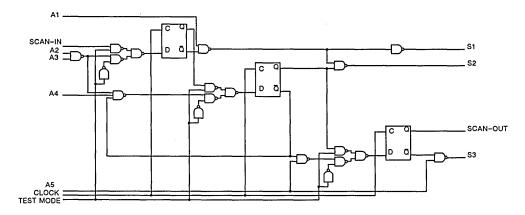

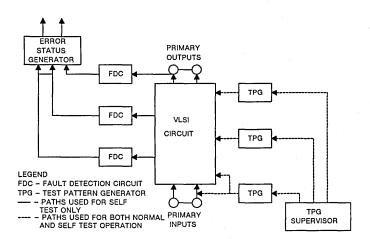

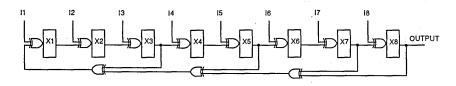

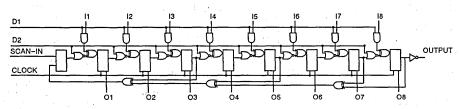

| 8.2 Design For<br>8.2.1 Test Poir<br>8.2.2 Partition<br>8.2.3 Scan Des<br>8.2.4 Self Test                                                                                    | f Testability Testability Approaches ints ing sign delines For Testability                                                                                                           |                                                                   |              |      | 8–1<br>8–1<br>8–2<br>8–5                                    |

| Section 9                                                                                                                                                                    |                                                                                                                                                                                      |                                                                   |              |      |                                                             |

| The Macrocell Lil                                                                                                                                                            | orary and Specification                                                                                                                                                              |                                                                   |              |      | 9-1                                                         |

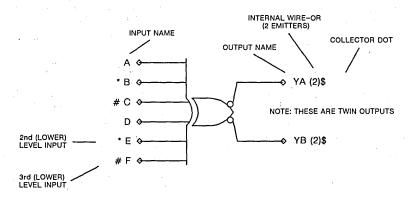

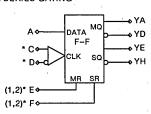

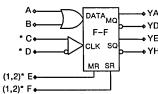

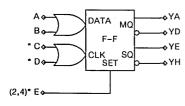

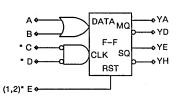

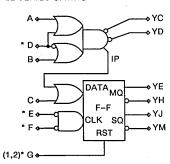

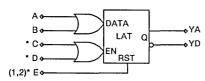

| 9.2 How to Rea<br>9.2.1 Input an<br>9.2.2 DC Inpu<br>9.2.3 AC Inpu<br>9.2.4 AC Inpu<br>9.2.5 Upper at<br>9.2.6 RESET a<br>9.3 Propagation<br>9.4 Minimum P<br>9.5 Min RESET, | rray Logic Type Classification of the Macro Symbols d Output Signal Names t Loading – Internal and I/C t Loading – Internal and I/C t Loading – Ouput Macroce and Lower Level Inputs | Macrocells  Did Macrocells  Is for Flip-flop on  Times  very Time | and Latch Ma | cros | 9-1<br>9-2<br>9-2<br>9-2<br>9-3<br>9-3<br>9-3<br>9-4<br>9-4 |

| Section 10                                                                                                                                                                   |                                                                                                                                                                                      |                                                                   |              |      |                                                             |

| Appendices                                                                                                                                                                   |                                                                                                                                                                                      |                                                                   |              |      | 10-1                                                        |

| 10.2 DC Electric<br>10.2.1 ECL an<br>10.2.2 PECL (                                                                                                                           | les Reference Gulde cal Characteristics d TTL Characteristics Characteristics on Conditions and Limits                                                                               |                                                                   |              |      | 10-9<br>10-11                                               |

### TABLE OF CONTENTS [continued]

| Section 10 | Appendices | [continued] |

|------------|------------|-------------|

|------------|------------|-------------|

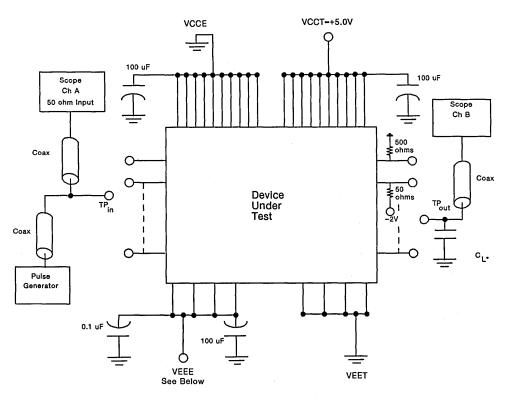

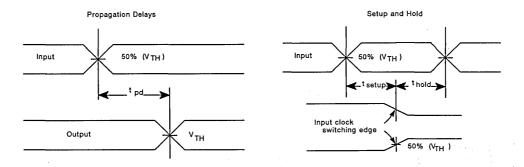

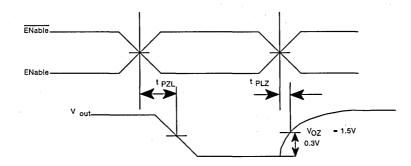

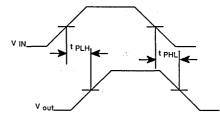

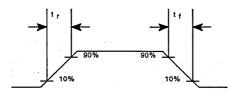

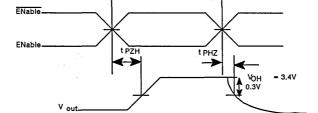

| 10.3 | Switching Circuit and Waveforms                      | 10-13 |

|------|------------------------------------------------------|-------|

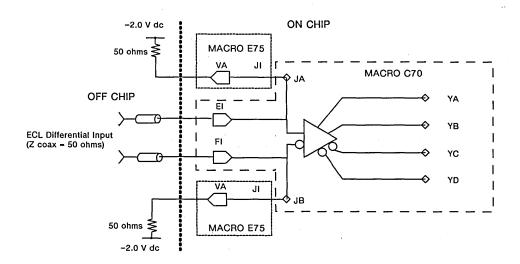

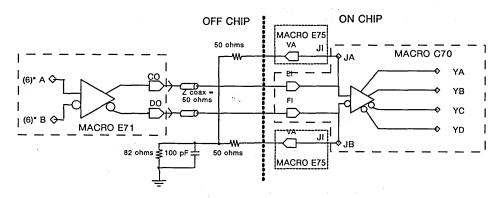

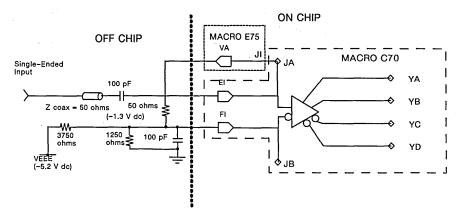

| 10.4 | Examples for Bringing High Frequency Signals On Chip | 10-15 |

| 10.5 | AC Switching Parameters and Waveforms                | 10-17 |

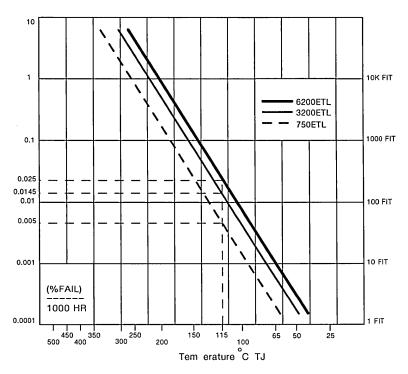

|      | Product Reliability                                  |       |

| 10.7 | Electrostatic Discharge (ESD)                        | 10-20 |

Index

### LIST OF FIGURES

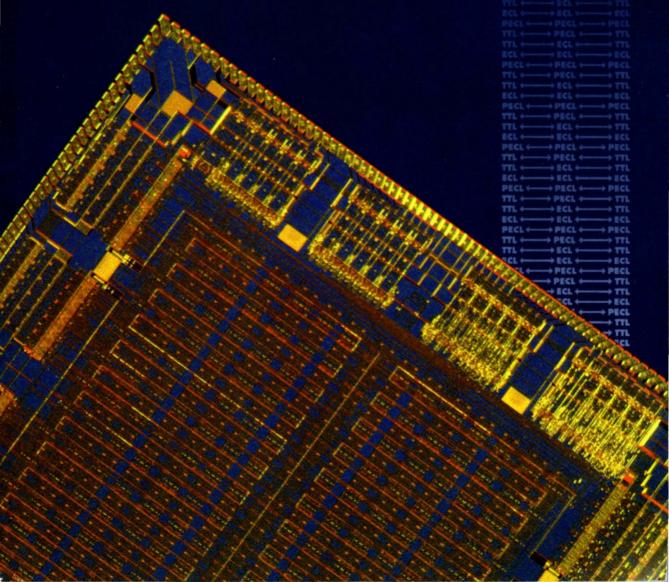

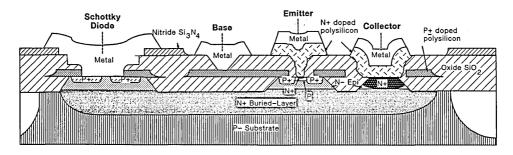

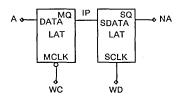

| 2-1.                                                                                                 | MOSAIC III Schottky-Transistor Cross-Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-1                                                                                       |

|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| 2-2.                                                                                                 | Speed/Power Programmability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-2                                                                                       |

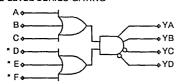

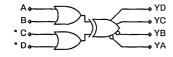

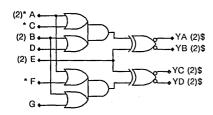

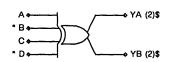

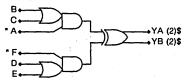

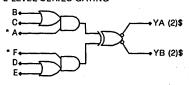

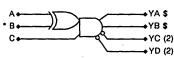

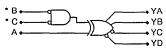

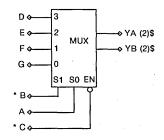

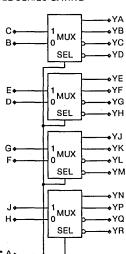

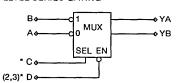

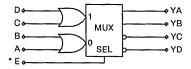

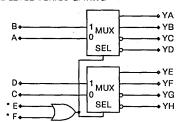

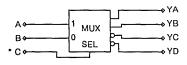

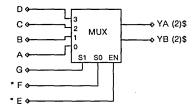

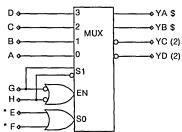

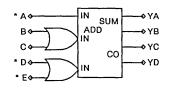

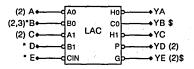

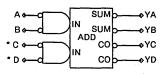

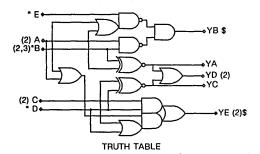

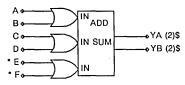

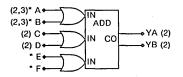

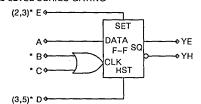

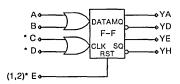

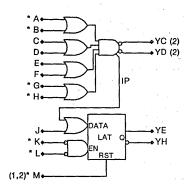

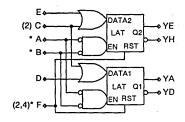

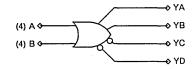

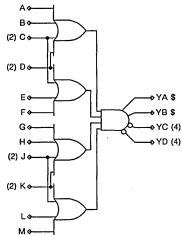

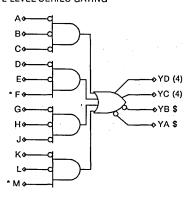

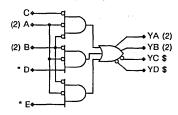

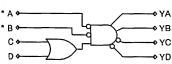

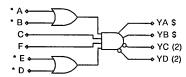

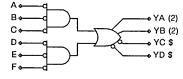

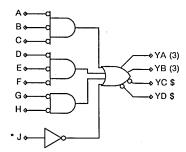

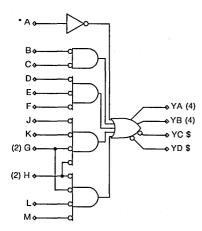

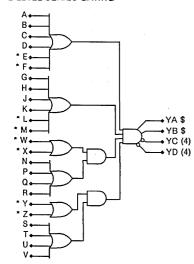

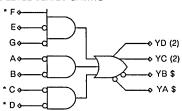

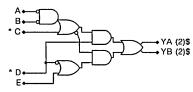

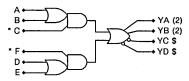

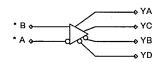

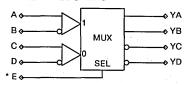

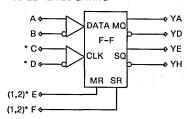

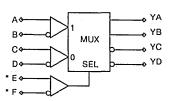

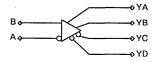

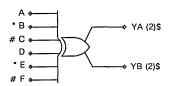

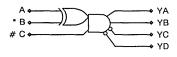

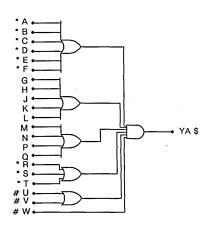

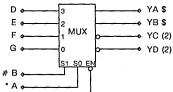

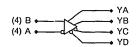

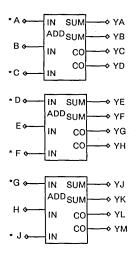

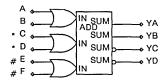

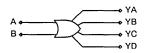

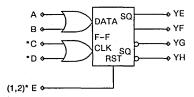

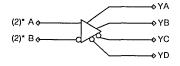

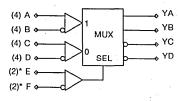

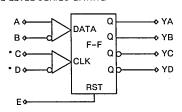

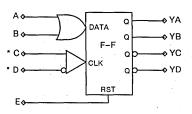

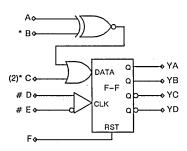

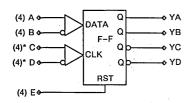

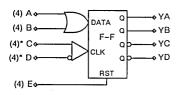

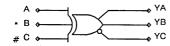

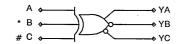

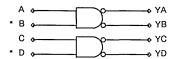

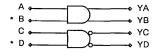

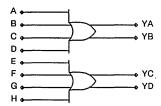

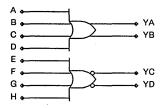

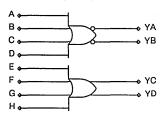

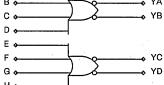

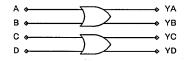

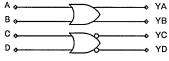

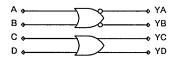

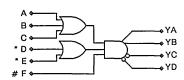

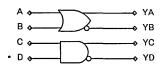

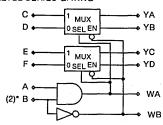

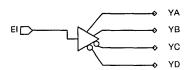

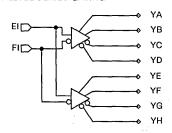

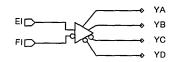

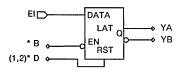

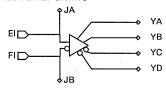

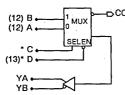

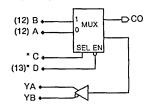

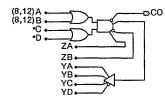

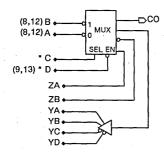

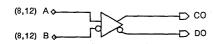

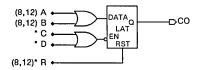

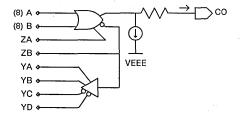

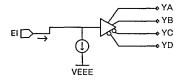

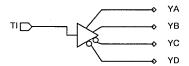

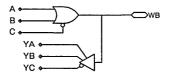

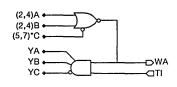

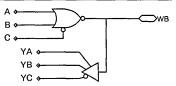

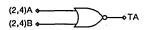

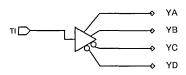

| 3-1.                                                                                                 | MCA3 ETL Array Signal Interface. a) ECL Signal b) TTL signal c) PECL/TTL Signal d)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                           |

|                                                                                                      | L/TTL Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3-1                                                                                       |

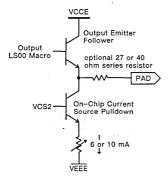

| 3-2.                                                                                                 | STECL Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3-2                                                                                       |

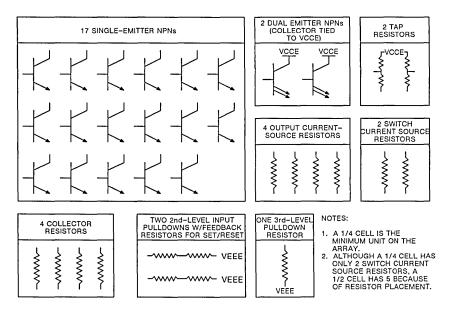

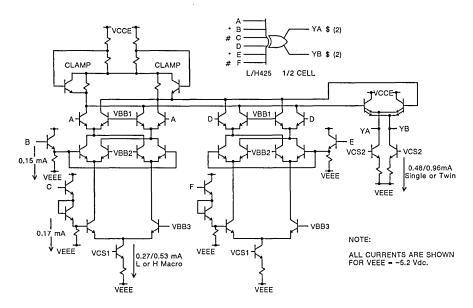

| 3-3.                                                                                                 | Internal Cell Architecture – 1/4 Cell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-3                                                                                       |

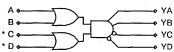

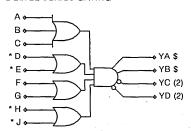

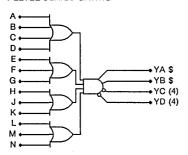

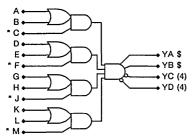

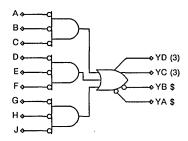

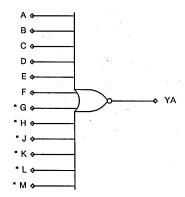

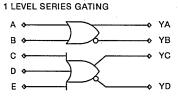

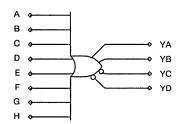

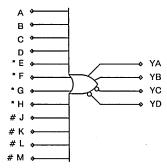

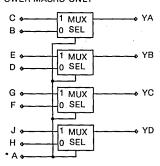

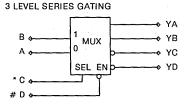

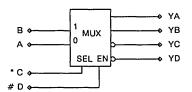

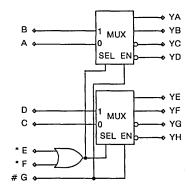

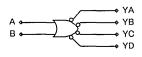

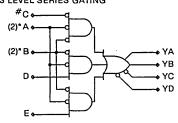

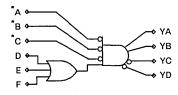

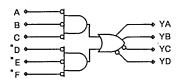

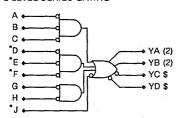

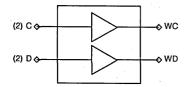

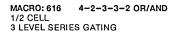

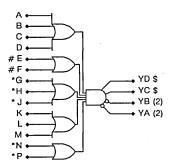

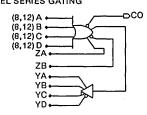

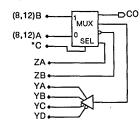

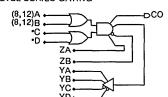

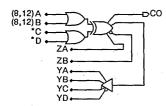

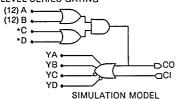

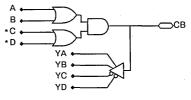

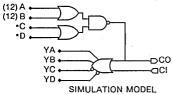

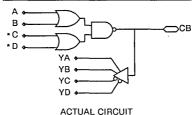

| 3-4.                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3-3                                                                                       |

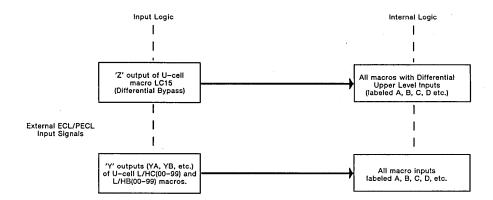

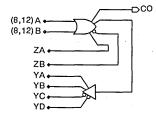

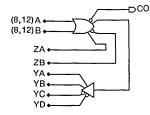

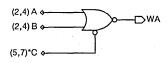

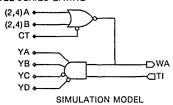

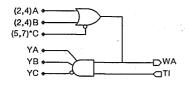

| 4-1.                                                                                                 | Allowed ECL/PECL Input Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-1                                                                                       |

| 4-2.                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4-2                                                                                       |

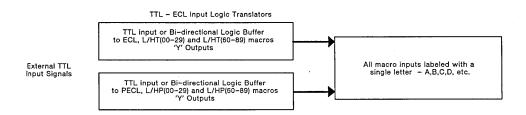

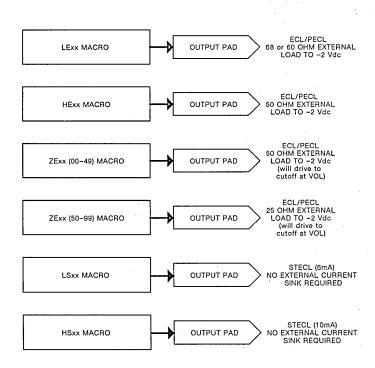

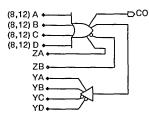

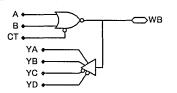

| 4-3.                                                                                                 | Allowed ECL/PECL Output Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-3                                                                                       |

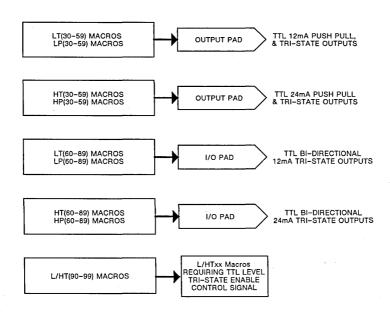

| 4-4.                                                                                                 | Allowed TTL Output Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-4                                                                                       |

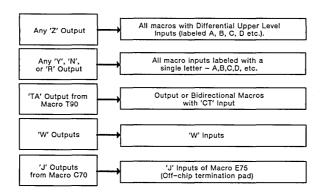

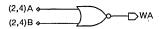

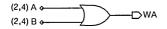

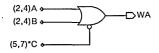

| 4-5.                                                                                                 | Allowed Internal Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                           |

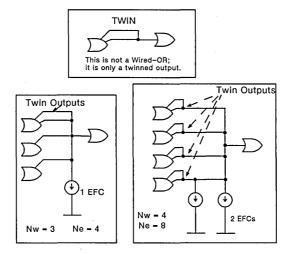

| 4-6.                                                                                                 | Wired-OR Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4-7                                                                                       |

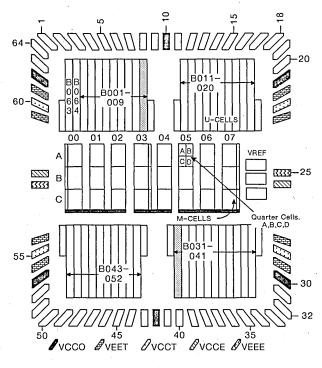

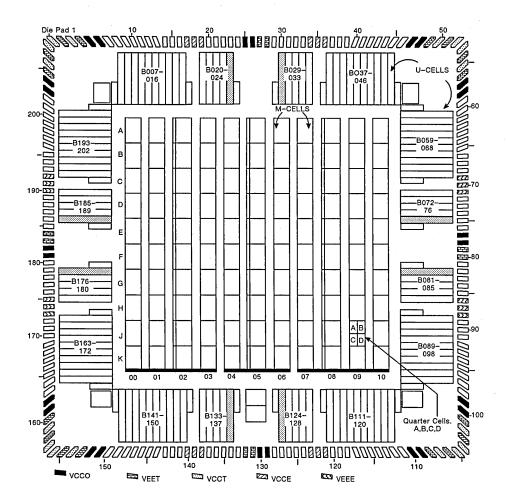

| 4-7.                                                                                                 | MCA750ETL Floorplan – 64 QFP (Wirebond)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4-10                                                                                      |

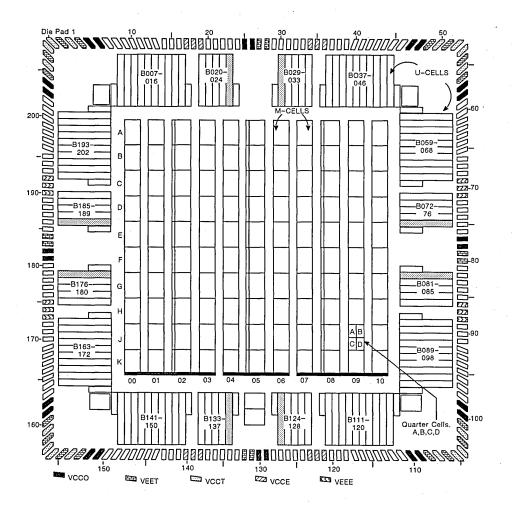

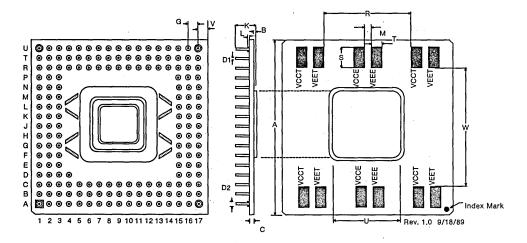

| 4-8.                                                                                                 | MCA3200ETL Floorplan - 160 QFP (Wirebond)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4-12                                                                                      |

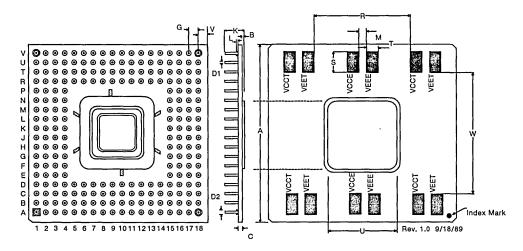

| 4-9.                                                                                                 | MCA3200ETL Floorplan - 169 PGA (Wirebond)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4-14                                                                                      |

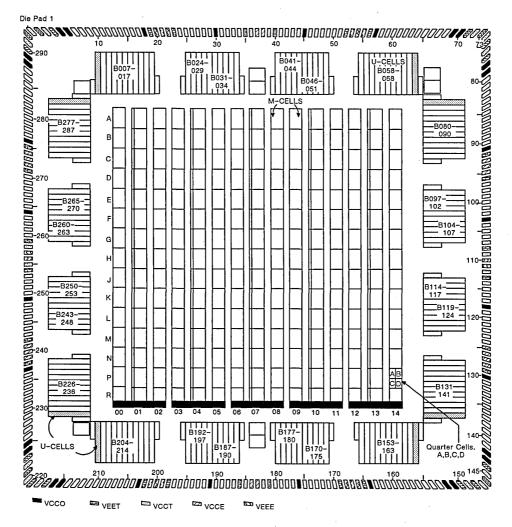

| 4-10.                                                                                                | MCA3200ETL Floorplan - 169 PGA (Wirebond)  MCA6200ETL Floorplan - 224 PGA (Wirebond)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4-16                                                                                      |

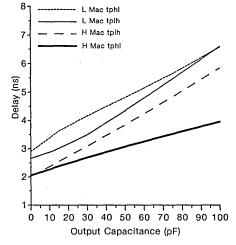

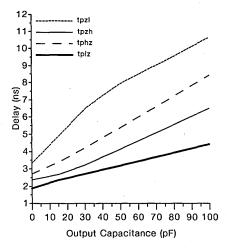

| 5-1.                                                                                                 | TTL OR/NOR Output Delay versus Output Capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5-4                                                                                       |

| 5-2.                                                                                                 | Tri-State Enable to Output Delay versus Output Capacitance (L Macro)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5-4                                                                                       |

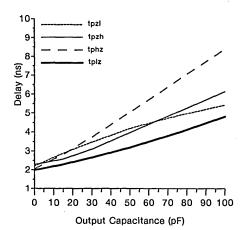

| 5-3.                                                                                                 | Tri-State Enable to Output Delay versus Output Capacitance (H Macro)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5-5                                                                                       |

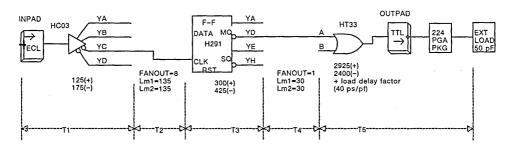

| 5-4.                                                                                                 | Path Delay Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5-9                                                                                       |

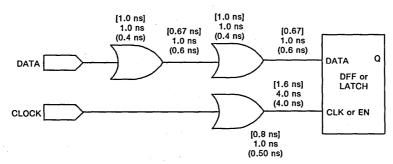

| 5-5.                                                                                                 | Setup and Hold Time Example – No Skew                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5-19                                                                                      |

| 5-6.                                                                                                 | Setup and Hold Time Example – With Skew                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5-20                                                                                      |

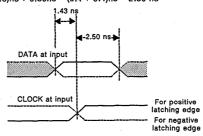

| 5-7.                                                                                                 | Clock Distribution Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5-22                                                                                      |

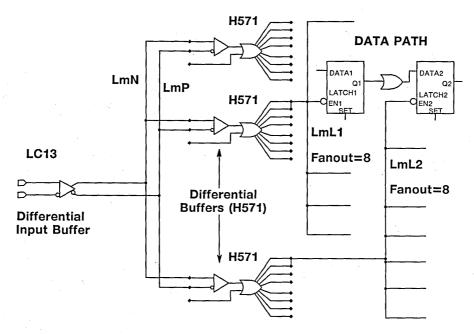

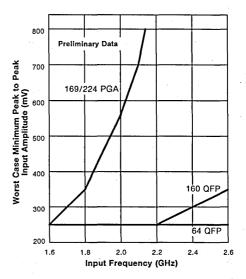

| 5-8.                                                                                                 | Recommended Minimum Differential Input Signal Amplitude for Single-Stage Input Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                           |

| (Ma                                                                                                  | acro LC70)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5-24                                                                                      |

| 5-9.                                                                                                 | Recommended Minimum Differential Input Signal Amplitude for Two-Stage Input Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5-24                                                                                      |

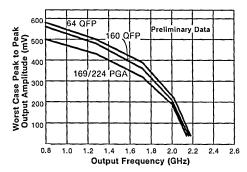

|                                                                                                      | . Worst-case Output Amplitude for Macro HE70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-25                                                                                      |

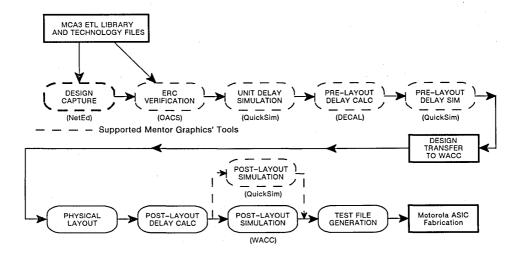

| 6-1.                                                                                                 | Typical MCA3 ETL OACS Originated Design Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6-1                                                                                       |

| 6-2.                                                                                                 | Example SUPERNET File                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6–6                                                                                       |

| 6-3.                                                                                                 | Sample FIX File                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6-10                                                                                      |

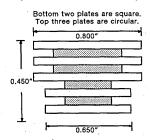

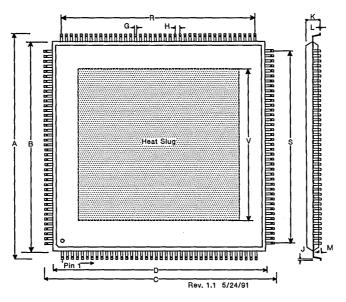

| 7-1.                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                           |

| 7-2.                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                           |

| 7-3.                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7-2                                                                                       |

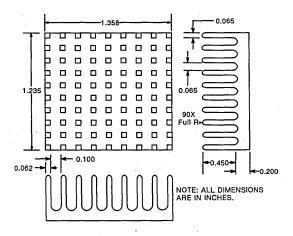

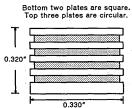

|                                                                                                      | Aluminum Pin-Fin Heat Sink for 224/169 PGA Packages (Thermalloy Part No. 2329B)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                           |

| 7-5.                                                                                                 | Aluminum Circular Fin Heat Sink for 64 QFP Package (Motorola H00809A001)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7-2                                                                                       |

|                                                                                                      | Aluminum Circular Fin Heat Sink for 160 QFP Package (Preliminary Drawing)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7-2                                                                                       |

| 7-7.                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7-3                                                                                       |

| 7-8.                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                           |

| 7-9.                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                           |

| 7-10                                                                                                 | . MCA3200ETL 160 QFP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                           |

|                                                                                                      | 14010000FF 400 DO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7-5                                                                                       |

| 7-12                                                                                                 | . MCA3200ETL 169 PGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7-6                                                                                       |

|                                                                                                      | . MCA3200ETL 169 PGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7-6<br>7-7                                                                                |

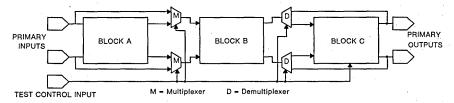

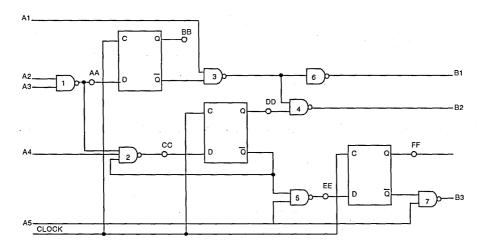

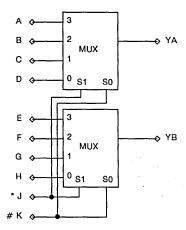

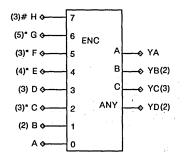

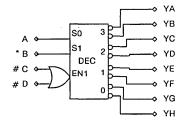

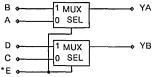

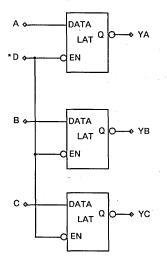

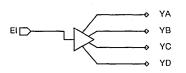

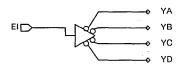

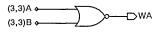

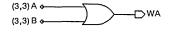

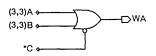

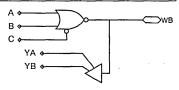

|                                                                                                      | . MCA3200ETL 169 PGA . MCA6200ETL 224 PGA . Network Partitioned Into Three Subnetworks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7-6<br>7-7<br>8-2                                                                         |

| 8-2.                                                                                                 | . MCA3200ETL 169 PGA . MCA6200ETL 224 PGA Network Partitioned Into Three Subnetworks Direct Access For Testability Improvement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7-6<br>7-7<br>8-2<br>8-2                                                                  |

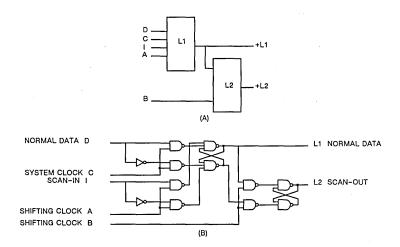

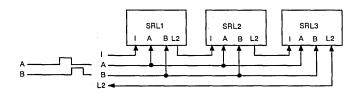

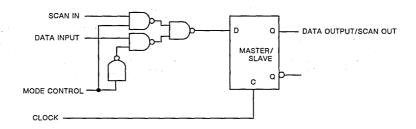

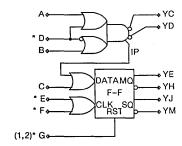

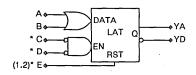

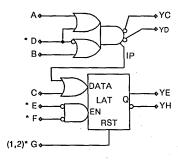

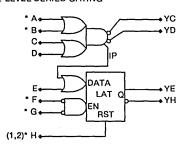

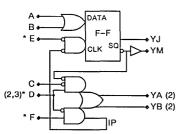

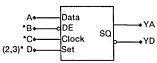

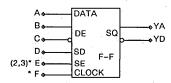

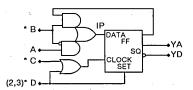

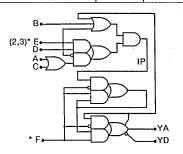

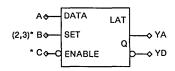

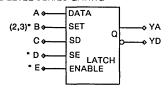

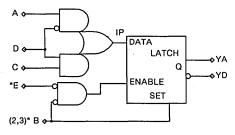

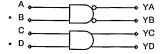

| 8-2.<br>8-3.                                                                                         | . MCA3200ETL 169 PGA . MCA6200ETL 224 PGA Network Partitioned Into Three Subnetworks Direct Access For Testability Improvement Shift Register Latch, (A) Symbolic Representation, (B) NAND Gate Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7-6<br>7-7<br>8-2<br>8-2<br>8-3                                                           |