1988 Standard Products Data Book

Microelectronics Division

# NCR STANDARD PRODUCTS DATABOOK APRIL 1988

While the information herein presented has been checked for both accuracy and reliability, NCR Corporation assumes no responsibility for either its use or for the infringement of any patents or other rights of third parties, which would result from its use. The publication and dissemination of the enclosed information offers no license, by implication or otherwise, under any patent or patent rights owned by NCR.

Copyright © 1988 by NCR Corporation, Dayton, Ohio, U.S.A. All Rights Reserved. Printed in U.S.A.

# **INDEX**

| OVERVIEW                | PAGE 1   |

|-------------------------|----------|

|                         |          |

|                         |          |

| SCSI PRODUCTS           | PAGE 21  |

|                         |          |

|                         |          |

| GRAPHICS PRODUCTS       | PAGE 257 |

|                         |          |

|                         |          |

| COMMUNICATIONS PRODUCTS | PAGE 277 |

|                         |          |

MEMORY PRODUCTS PAGE 431

MILITARY PRODUCTS PAGE 473

# **OVERVIEW**

| NCR: a History of Quality, Service and Support     |    |

|----------------------------------------------------|----|

| Strategy and Goals                                 | :  |

| NCR Quality                                        | •  |

| NCR Plants/Product Lines                           | 1  |

| NCR Microelectronics Division Regional Territories | 12 |

| NCR Sales Reps and Design Centers                  | 1: |

# NCR: A HISTORY OF QUALITY, SERVICE AND SUPPORT

The NCR Corporation was founded over 100 years ago with the invention of the cash register. Since then, its been one innovation after another. For example, as an early pioneer in electronic component technology, NCR performed advanced vacuum tube research as early as 1938. Later, in 1959, NCR produced the first commercial all solid-state computer.

Today, NCR Corporation is a multi-billion dollar manufacturer of diversified business and technology products including computer systems, retail and banking terminals, and semiconductors.

NCR established the microelectronics division in 1971 to design and manufacture advanced integrated circuits for internal use. In 1981, NCR Microelectronics became an autonomous division and began selling its services to the merchant market.

Just three years later in 1984, NCR achieved independent recognition as the industry's leading supplier of standard cell products—the fastest growing segment of the exploding ASIC market. This achievement not only made NCR one of the world's fastest growing ASIC suppliers, but assured its customers an early lead in getting their ASIC-based products to market.

In 1987, NCR introduced a technology breakthrough—the Design Advisor™. This first-of-its-kind application of artificial intelligence, assists design engineers by providing 1000 years of engineering knowledge. This product introduction, announced at New York City's Hayden Planetarium in unison with the Design Automation Conference (DAC), received very significant trade press and analyst coverage.

Today, NCR's Microelectronics Division consists of two modern manufacturing facilities located in Fort Collins and Colorado Springs, Colorado. In early 1988, the Miamisburg, Ohio, microelectronics center's operations were relocated in these two facilities.

These independent, but closely coupled plants, offer customers a new level of security of supply.

# Fort Collins, Colorado

The Fort Collins facility is headquarters for NCR's commercial/industrial Application Specific Integrated Circuits (ASIC), Digital Signal Processing (DSP), Software Development, and Customer Owned Tooling (COT) business units. The Fort Collins ASIC business unit conducts a great deal of research and development in gate arrays, standard cell libraries, and "supercells," as well as customer owned tooling. The recently formed software development business unit is dedicated to providing leading edge software products.

The Fort Collins facility also houses volume wafer fabrication and test facilities and a complete small-volume/fast-turn assembly capability for popular plastic and ceramic devices

# Colorado Springs, Colorado

Colorado Springs is home for NCR's logic product, Military ASIC, and Automotive ASIC business units.

The logic products group supplies a variety of microprocessors, logic support devices, and special function chips. The military products group is dedicated to supplying both standard ICs and ASIC devices screened to military requirements. It offers a comprehensive quality system based on the MIL-Q-9858A. Devices can be screened and qualified to MIL-STD-883C, Method 5004/5005 and 5010 on a stand-alone basis. The automotive ASIC group supplies both standard and ASIC devices to the special requirements of the automotive industry.

The Colorado Springs facility is the site of NCR's newest advanced wafer fab. Currently, this fab is running geometies down to  $1.5\mu m$  with  $1.0\mu m$  in prototype development.

This Standard Products Databook highlights NCR's standard product offering. The complementary ASIC Databook (May 1988) includes ASIC product information for all applications.

If you desire a copy of the ASIC Databook, please contact the sales office in your area (see page 13) or call NCR's hotline: 1-800-334-5454.

3

# STRATEGY AND GOALS

## **SCSI Products**

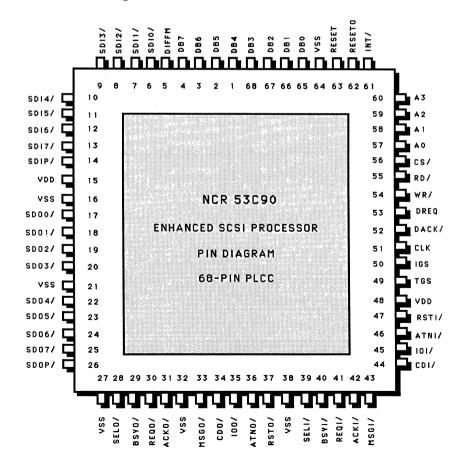

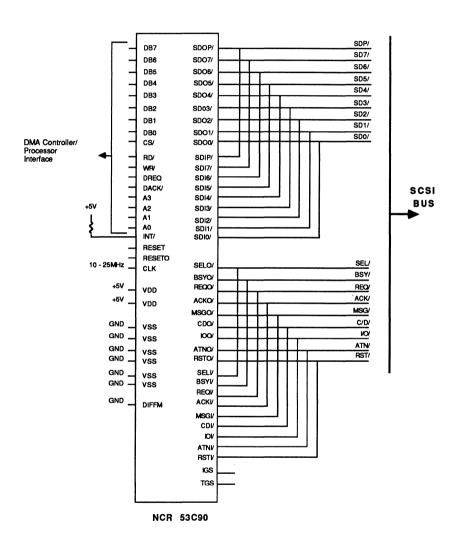

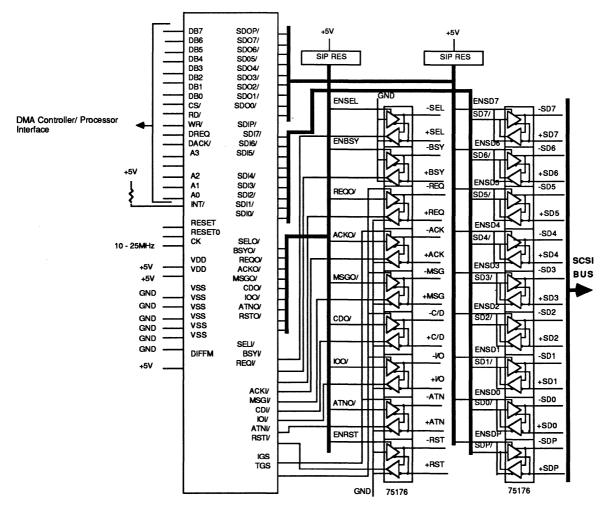

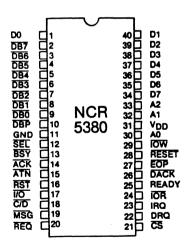

NCR is creating high value products for its customers in the SCSI Controller area. As the SCSI leader, NCR offers the broadest line of SCSI products ranging from the low cost 5380 family of chips to the high performance 53C90. SCSI products are designed using the semi-custom modular approach while maintaining sensitivity to the industry trend toward higher integration. An emphasis is placed on software compatibility with the 5380 and the 53C90 to provide customers a migration path to higher performance products. NCR's high volume marketing approach allows for an optimum price/performance ratio giving customers high value products.

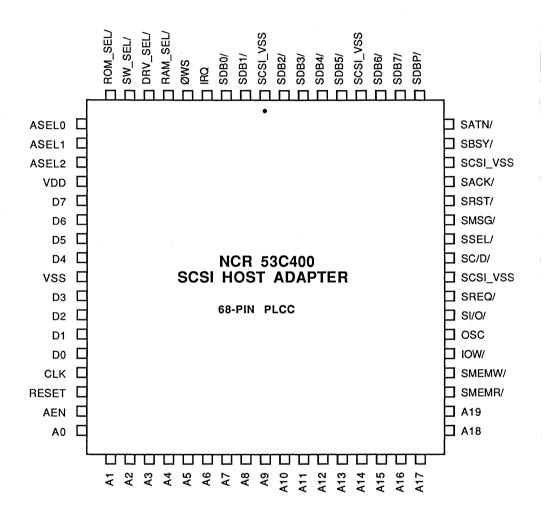

Some of NCR's newest developments in the SCSI area include the 53C90 - a high performance SCSI processor which features sequenced commands and high speed synchronous data transfers, the 53C80-40 - a CMOS part pin compatible with the 5380 that also features a faster REQ-ACK SCSI handshake, and the 53C400 - a single chip host adapter chip compatible with the IBM PC/XT/AT Bus and the PS/2 Model 30 which also features two 128 byte buffers to provide speed matching.

NCR's SCSI Products group is continuing to provide customers with high perfromance, low cost quality products by using the latest process technology, Computer Aided Design tools, and quality assurance programs. NCR maintains a high degree of customer satisfaction by filling the market needs with performance products quickly and effectively.

# **Graphics Products**

As users become more comfortable with personal computers, there will be an increase in demand for color monitors. Likewise, computer manufacturers will demand high performance color/graphics controllers for these monitors. NCR's graphics products provide a solution now. Our graphics products provide easy-to-use, highly integrated and cost effective solutions for the needs of the PC market.

NCR's foremost strategy is to provide industry standard solutions to the marketplace which preserve compatibility, while providing leadership, performance, features and integration. With this strategy, NCR has

become a popular source of CRT controllers for both monochrome and color display systems.

NCR Microelectronics will compete only at the chip level in the marketplace. This allows us to concentrate on the production of CRT controller chips rather than the production of PC board-based display systems. With this strategy, NCR can provide the best product, service and commitment to our customers' needs.

Providing timely and current solutions for the needs of the display systems market is our strategy for the future. This will continue to maintain NCR's position as an industry leader.

## **Communication Products**

The Communications Business Unit develops semiconductor circuits for use in local area networks and digital telephony. NCR develops local area digital communication network circuits, these circuits are for networks usually less than 50,000 meters and connecting up to 1024 nodes. Local area network speeds range from 1200 bits per second to greater than 100 MB/S. These circuits support 802 Standards, PC Networks, Factory Automation Networks, Office Automation Networks, CAE and CAD Networks and Backbone Networks.

Digital telephony circuits include Digital Telecom as well as Integrated Services Digital Networks (ISDN). These circuits support digital applications on existing twisted pair wiring circuits as well as fiber optic networks. They include ISDN interfaces, PBX's, and central office applications.

# **NCR Memory Products**

NCR Memory products group has moved from Miamisburg, Ohio to Fort Collins, Colorado and is a part of the Customer Owned Tooling (COT) group.

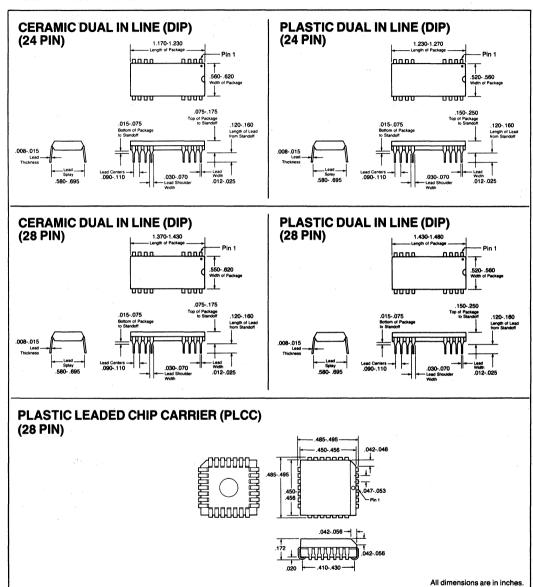

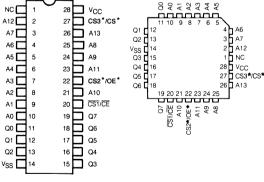

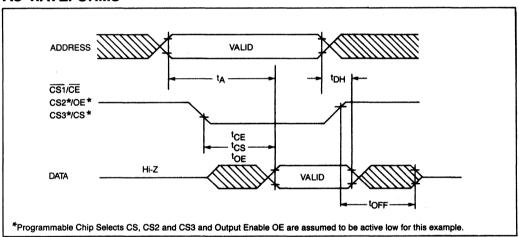

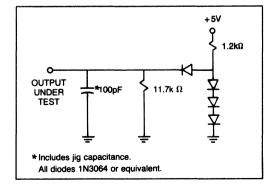

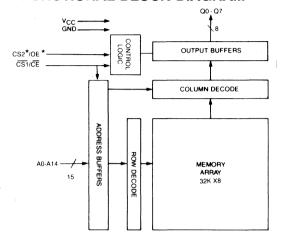

NCR offers a full line of high performance CMOS and NMOS read-only memories (ROM) with a variety of pinouts, access times, and packages (DIP, PLCC, Fpp). NCR's strong manufacturing capability allows for fast turn around of both prototype and production quantities. NCR provides the customer service levels and the engineering support required of a major supplier of ROM's in today's market.

# **NCR Military Products**

6

NCR Microelectronics Military group, now located in Colorado Springs, Colorado, is dedicated to providing both standard and ASIC products to the military market.

It offers a comprehensive quality system based on the MIL-Q-9858A. Devices can be screened and

qualified to MIL-STD-883C, Method 5004/5005 and 5010 on a stand-alone basis.

The NCR Microelectronics Military group is expanding its capabilities and expects several new standard and ASIC products to be included in its offerings this year.

04/88

# **NCR QUALITY**

# NCR Microelectronics Division — A History of Quality

The NCR Corporation was founded over 100 years ago with the invention of the cash register. Since then it has been one innovation after the other. Today NCR Corporation is a multi-billion dollar manufacturer of diversified business and technology products including computer systems, peripherals, retail and banking terminals and semiconductors.

NCR established its first microelectronics laboratory in 1963 to stay abreast of the emerging semiconductor technology. The laboratory was expanded in 1966, and by 1968 NCR's first production MOS circuits were produced. NCR created the Microelectronics Division in 1971 with the opening of its first manufacturing plant located in Miamisburg, Ohio to manufacture advanced integrated circuits for internal use. NCR expanded its Microelectronics operation in 1975 with a second production facility in Colorado Springs, Colorado and in 1979 added a third facility in Fort Collins, Colorado.

In 1981 NCR Microelectronics became an autonomous division and began selling its products to the merchant market. And by 1984 the division had become the market leader in the standard cell sector of the semicustom application specific ICs (ASIC) market serving customers with commercial, industrial, automotive and military applications.

In addition to standard cell devices NCR Microelectronics also manufactures an extensive line of state-of-the-art VLSI devices including gate arrays, peripheral ICs, logic devices, digital signal processing devices, microprocessors, and memories.

# A Commitment to Quality

"NCR Corporation is totally committed to maintaining a reputation for excellence second to none in the markets we serve. We intend to maintain this reputation by providing only defect-free products and error-free services."

Charles E. Exley Jr.

Chairman of the Board and President

NCR Corporation

Mr. Exley's statement, from our highest level of management, exemplifies the commitment to quality, reliability and customer satisfaction NCR has held for over 100 years.

The NCR goal in all products is to exceed the customer's quality and reliability requirements by building quality in. Of course, we test each device extensively, but testing alone cannot insure long-term reliability.

Each of NCR Microelectronics standard products, cell libraries and processes has been extensively characterized and qualified. Our quality assurance engineers work closely with standard product, standard cell and gate array IC designers, as well as, computer-aided design software engineers and process engineers to assure that long-term product quality is an integral part of every NCR standard or ASIC device.

At NCR we have learned that not only must each and every element of the design and manufacturing process be fully validated, but that they must also be validated as an entire system—from processing to workstation simulations. For example, in the design process, strict design rules with carefully controlled margining requirements are used to insure products meet or exceed customer quality and reliability requirements. In the fabrication and assembly operation, Statistical Process Control (SPC) is the key to maintaining a high level of confidence.

Of course each ASIC device receives full screening, testing and qualification prior to shipment, but without built-in quality attributes, long term reliability could not be ensured. And at NCR quality is not measured in percent of failed devices received by our customers, but rather the reliability of the devices over the long haul.

Additionally, NCR supports a program of continuous quality improvement. This includes working closely with customers to help insure that applications are consistent with the intended use of the product. When problems are encountered, NCR maintains a closed loop corrective action system to insure that problems are resolved and corrected in a timely manner.

All of this attention to quality and reliability has paid off—for NCR and our customers. As a result of our exceedingly high standards, NCR Microelectronics has an AQL level much better than the industry average.

# Quality is a System

Behind NCR's reputation for excellence in quality and reliability is a comprehensive quality system based upon MIL-Q-9858A. This system provides detailed documentation of our design and manufacturing processes as well as for the handling, testing and inspections of the raw material and work-in-process. It also documents manufacturing operation controls, final acceptance and delivery. Here are some of the key elements of that system.

#### Defect Prevention

NCR Microelectronics is committed to the philosophy that defect prevention is the most effective means of assuring the quality of all products and services. As a result of this commitment, defect prevention is practiced throughout every phase of the operation.

Quality is designed into our products through the use of documented design rules and procedures. Comprehensive design reviews are conducted to ensure the product design conforms to specifications. Processing is accomplished under documented controlled conditions thereby providing the highest quality throughout the fabrication process. Extensive characterization and reliability verification testing can be performed to help ensure that products are defect-free and perform reliably over an extended period of time.

## Closed Loop Corrective Action

A Closed Loop Corrective Action (CLCA) system is in place at NCR Microelectronics to ensure that problems are resolved in a timely manner. The basic elements of the system include:

- ... Problem identification

- ... Investigation and determination of cause

- ...Corrective action to eliminate the problem and prevent its recurrence

- ... Verification that the corrective action has eliminated the problem

## • Configuration Control

Configuration control procedures ensure that product designs are fully documented and production changes are implemented in a controlled manner. With

this procedure, customers are assured of complete configuration accountability of the end item. Engineering documentation is handled under strict change control procedure utilizing request for change and engineering change notice procedures. Engineering changes are documented using part number and revision letter control. Change implementation is monitored, tracked and recorded to ensure that changes are incorporated into production as scheduled. Configuration accountability records are maintained to allow complete design traceability of the completed end item.

## • Calibration of Equipment

The procedures used by NCR for calibrating manufacturing and testing equipment are based upon MIL-C-45662, Calibration System Requirements. These procedures are designed to ensure that all measurements are accurate and reliable. Calibration of NCR's manufacturing and testing equipment is performed in accordance with the manufacturer's recommendations or those proven by the National Bureau of Standards. Calibrations are performed in-house or by a certified laboratory depending upon the type and complexity of the equipment. NCR's calibration system includes machine labeling and record documentation system designed to ensure that calibrations are performed on schedule.

## • Supplier Quality Management

NCR is committed to doing business with selected suppliers who have demonstrated their ability to constantly deliver defect-free products as scheduled. Suppliers are selected by NCR based upon evaluation and audits of their quality systems and their capabilities for meeting the specified quality requirements. NCR's supplier evaluation criteria include:

- ... Commitment to quality

- ... Proven ability to produce defect-free product

- ... Well documented processes that are under strict con-

- ... Use of statistics to evaluate process capabilities

- ... Engineering expertise and design maturity

- ... Engineering change control procedures

- ... Test documentation, inspection records, certification of performance, quality reports on a regular basis

- ...Corrective action system with ability to resolve problems in a timely manner

- ... Continuous quality improvement program

- ... Flow down procedures for second source suppliers

#### Statistical Process Control

NCR uses Statistical Process Control (SPC) as one of the key elements in their systems to build in quality and reliability. For example, within wafer fabrication, critical process parameters are charted to monitor the on-going statistical performance of the process. The targeted performance standard of each monitored process is continually raised resulting in ever improving performance. Numerous other process parameters are monitored throughout the manufacturing, qualification and support process to assure conformance to documented requirements.

#### Wafer Fabrication

After the device is approved for production, stringent process and assembly controls are used to build in quality and reliability. Within wafer fabrication, over 150 critical process parameters are monitored to assure performance of the process. The following quality assurance functions are just some of the functions performed during wafer fabrication:

- ... After Develop Inspections (ADIs) performed at each masking level

- ... After Etch Inspection (AEIs) performed at each masking level

- ... All critical process operations implemented on statistical process control (SPC) chart

- ...In-process QC audits and final QC wafer lot acceptance gate

- ... CV sampling performed for every lot

- ... Profile testing of critical parameters

- ...100% die probe

- ...QC lot acceptance for assembly

## **Quality and Reliability Testing Procedures**

NCR offers complete quality assurance services to provide the optimum high reliability solution to meet your system requirements. At NCR, end items are thoroughly tested to ensure conformance to specified requirements. For military and high reliability applications, NCR supports the stringent MIL-STD-883C, Method 5004/5005 and Method 5010 screening and quality conformance inspection test methods and on a stand-alone basis. These testing procedures are

designed to insure that the quality and reliability of the completed device conforms with the applicable procurement document. Additionally, NCR can support customer requirements for special screening and qualification testing procedures.

Methods 5004 and 5005 are companion test methods establishing total lot screening and quality conformance inspection procedures for microcircuits. Method 5010 is a relatively new all inclusive screening and qualification procedure for custom and semicustom microcircuits with low production volume requirements.

Using Method 5010 as an example, the testing and evaluation procedure involves four major areas:

- ...Element Evaluation—This series of tests involve the materials for device assembly, i.e. wafers, die and packages.

- ...Process Control—These tests are performed to ensure the integrity of the die attachment and wire bonding process.

- ...100% Device Screening—This series of rigorous tests are performed on assembled devices to ensure the quality and reliability levels specified by the device specification has been achieved.

- ...Quality Conformance Inspection—This group of tests establishes qualification and quality conformance inspection procedures for initial device qualification, requalification and retention of qualification. These quality conformance tests consist of Group A, B, C and D.

- Group A—Electrical tests performed on an inspection lot that has already passed 100% screening.

- Group B—Environmental tests designed to test the integrity of the fabrication and assembly processes.

- Group C—Die related test conducted on a three month periodic basis, as required.

- Group D—Package related tests conducted on a six month periodic basis, as required.

# High Rel ASIC

These products are available in commercial, industrial, automotive and military temperature ranges and a variety of screening procedures including MIL-STD-883C Method 5004/5005 and Method 5010, on a stand alone basis.

NCR's ASIC CMOS product family is comprised of both standard cells and gate arrays all screened for operation in the automotive temperature ranges and military temperature range. Standard cells are offered in  $2\mu m$  double-level-metal (DLM) and  $3\mu m$  single-level-metal (SLM). Gate arrays are provided in 25m double-level-metal with complexity ranging from 600 to 8,500 usable gates.

NCR's automotive products group is based in Colorado Springs, Colorado. This plant is NCR's newest microelectronics factory and features an automotive design center, 1.5-micron fabrication capability, testing, and qualification. The automotive products group supplies full custom, cell based and gate array products to the automotive and high-temp industrial markets.

The Miamisburg plant is home to the Microelectronics Division's Military Products Unit. The plant offers a military applications design center, on-site fabrication, and back-end screening, testing and qualification to a variety of Mil standards. The Military Products Group is dedicated to supplying both standard and ASIC devices screened to military requirements.

NCR's CMOS devices, using our semicustom design approach, have the characteristics essential to military and automotive systems including high reliability in rugged environments, low power consumption, and high immunity to noise and power supply variations.

# A Commitment to Customer Satisfaction

NCR's commitment to quality, reliability and customer satisfaction is an integral part of corporate policy and philosophy. And it's been that way since 1884 when NCR's founder, John H. Patterson, set the standards that NCR follows today.

Patterson's premise was simple. Build each product the best it could be built and provide a level of service to customers which exceeds their expectations. Patterson knew that if each employee believed and lived that premise, success for his newly founded company would be assured. Today, as then, everyone at NCR is committed to continue its successful growth in the markets we serve by striving to provide defect-free products and error-free services to each of our customers.

Every NCR employee is motivated to ensure our customer's satisfaction in our products and services. It's this commitment to customer service that forms the underlying foundation on which our Quality Assurance Program is based. At NCR we feel this is a fundamental part of quality. Testing for quality is an important function, but we believe that the long-term reliability cannot be tested-in. Reliability begins and ends with people. People committed to product and service excellence.

At NCR, when we say, "We Take Customer Satisfaction Personally," - we mean it.

# NCR PLANTS/PRODUCT LINES

## FORT COLLINS

Commercial ASIC Products

Digital Signal Processing Products

Customer Owned Tooling/Memory Products

Telecommunications Products

Software Development

2001 Danfield Court Fort Collins, CO 80525 (303) 226-9500

## **COLORADO SPRINGS**

SCSI Products Graphics Products Military ASIC Products Automotive ASIC Products Distribution Internal Marketing

1635 Aeroplaza Drive Colorado Springs, CO 80916 (303) 596-5611 or (800) 525-2252

**NCR Microelectronics Division Regional Territories**

#### NORTHEASTERN AREA SALES OFFICE

NCR Microelectronics Division 400 W. Cummings Park Suite 2750

Woburn, MA 01801 Phone: (617) 933-0778

#### SOUTHEASTERN OFFICE

NCR Microelectronics Division 700 Old Roswell Lakes Pkwy.

Suite 250

Roswell, GA 30076 Phone: (404) 587-3736

#### NORTH CENTRAL OFFICE

NCR Microelectronics Division 33 West Higgins Road South Barrington, IL 60010 Phone: (312) 426-4600

#### SOUTH CENTRAL OFFICE

NCR Microelectronics Division 400 Chisholm Place, Suite 100 Plano, TX 75075

Phone: (214) 578-9113

## NORTHWESTERN AREA SALES OFFICE

NCR Microelectronics Division

3130 De la Cruz Blvd.

Suite 209

Santa Clara, CA 95054-2410 Phone: (408) 727-6575

#### SOUTHWESTERN REGIONAL SALES OFFICE

NCR Microelectronics Division 1940 Century Park East

Los Angeles, CA 90067 Phone: (213) 556-5231

15

# NCR SALES REPS AND DESIGN CENTERS

Cross Referenced by State/International Area February 15, 1988

#### ALABAMA

Electronic Manufacturers Agents 309 Jordan Lane Huntsville, AL 35805 205-830-4030

#### ARIZONA

Sun State Technical, Inc. Suite 115 2323 East Magnolia Phoenix, AZ 85034 602-220-0595

#### ARKANSAS

ION Associates, Inc. 1504 109th Street Grand Prairie, TX 75050 214-647-8225

#### CALIFORNIA

## (North)

Quorum Technical Sales Building 12 4701 Patrick Henry Drive Santa Clara, CA 95054 408-980-0812

#### (South)

Leading Concept Technologies, Inc. 3900 Birch Street, Suite 104 Newport Beach, CA 92660 714-851-0654

# (San Diego and Imperial Counties)

Earle Associates, Inc. Suite 200 7585 Ronson Road San Diego, CA 92111 619-278-5441

#### **COLORADO**

Electrodyne Suite 110 2620 South Parker Road Aurora, CO 80014 303-695-8903

#### CONNECTICUT

John E. Boeing Co., Inc. 139 Billerica Road Chelmsford, MA 01824-3501 617-256-5800

# DELAWARE

**OPEN**

#### DISTRICT OF COLUMBIA OPEN

OFEN

#### FLORIDA

Delmac Sales, Inc. 1701 West Hillsboro Boulevard Suite 304 Deerfield, FL 33441 305-427-7788

Delmac Sales, Inc. 1963 Corporate Square Drive Suite 106 Longwood, FL 32750 305-831-0040

Delmac Sales, Inc. 1170 Woodlawn Street Clearwater, FL 34616 813-443-2622

#### **GEORGIA**

Electronic Manufacturers Agents 620 Colonial Park Drive Roswell, GA 30075 404-992-7240

#### IDAHO

Electrodyne Suite 120 825 East 4800 South Street Salt Lake City, UT 84107 801-264-8050

#### ILLINOIS

(South of I-74)

Dy-Tronix, Inc. 3407 Bridgeland Drive Bridgeton, MO 63044 314-291-4777

#### ILLINOIS (Continued)

(North of I-74)

Eagle Technical Sales

1805-B Hicks Road

Rolling Meadows, IL 60008

#### (Rock Island County)

312-991-0700

Aldridge Associates, Inc. 7138 Shady Oak Road Eden Prairie, MN 55344-3517 612-944-8433

#### INDIANA

Bailey's Electronics Sales 87 Bali Hai Carmel, IN 46032 317-846-5578

#### **IOWA**

Aldridge Associates, Inc. 7138 Shady Oak Road Eden Prairie, MN 55344-3517

#### **KANSAS**

Dy-Tronix, Inc. Suite 322 1999 Amidon Wichita, KS 67203-2124 316-838-0884

Dy-Tronix, Inc. Suite 106 5001 College Boulevard Leawood, KS 66211 913-339-6333

#### **KENTUCKY**

(W of I-75)

Bailey's Electronics Sales 87 Bali Hai Carmel, IN 46032 317-846-5578

## (E of I-75)

Arthur Baier Company 7480 Kingswood Drive Westchester, OH 45069 513-779-2395

#### LOUISIANA

ION Associates, Inc. 1504 109th Street Grand Prairie, TX 75050 214-647-8225

#### MAINE

John E. Boeing Co., Inc. 139 Billerica Road Chelmsford, MA 01824-3501 617-256-5800

# MARYLAND

**OPEN**

#### MASSACHUSETTS

John E. Boeing Co., Inc. 139 Billerica Road Chelmsford, MA 01824-3501 617-256-5800

#### MICHIGAN

Rathsburg Associates, Inc. 17600 Northland Park Court Suite 100, P.O. Box 5037 Southfield, MI 48086-5037 313-559-9700

## MINNESOTA

Aldridge Associates, Inc. 7138 Shady Oak Road Eden Prairie, MN 55344-3517

## MISSISSIPPI

Electronic Manufacturers Agents 309 Jordan Lane Huntsville, AL 35805 205-830-4030

#### MISSOURI

Dy-Tronix, Inc. 3407 Bridgeland Drive Bridgeton, MO 63044 314-291-4777

#### **MONTANA**

Electrodyne Suite 120 825 East 4800 South Street Salt Lake City, UT 84107 801-264-8065

#### NEBRASKA

Dy-Tronix, Inc. Suite 322 1999 Amidon Wichita, KS 67203-2124 316-838-0884

#### NEVADA

#### (All, excluding)

Quorum Technical Sales 4701 Patrick Henry Drive, Bldg. 12 Santa Clara, CA 95054 408-980-0812

#### (Clark County)

Sun State Technical, Inc. Suite 115 2323 East Magnolia Phoenix, AZ 85034 602-220-0595

#### NEW HAMPSHIRE

John E. Boeing Co., Inc. 139 Billerica Road Chelmsford, MA 01824-3501 617-256-5800

#### **NEW JERSEY**

### (North)

Comtronic Associates, Inc. 555 Braod Hollow Road Melville, NY 11747 516-249-0505

#### (South)

TCA, Inc. 1570 McDaniel Drive West Chester, PA 19380 215-692-6853

#### NEW MEXICO

Nelco Electronix 4801 General Bradley, N.E. Albuquerque, NM 87111 505-293-1399

#### **NEW YORK**

#### (All except L.I.)

Ontec Electronic Marketing 167 Flanders Street Rochester, NY 14619 716-464-8636

#### **NEW YORK (Continued)**

Ontec Electronic Marketing 16 Gabriella Road P.O. Box 525 Wappinger Falls, NY 12590 914-462-7374

#### (Long Island)

Comtronic Associates, Inc. 555 Broad Hollow Road Melville, NY 11747 516-249-0505

#### NORTH CAROLINA

Electronics Manufacturers Agents Suite 204 6604 Six Forks Road Raleigh, NC 27609 919-846-6888

#### NORTH DAKOTA

Aldridge Associates, Inc. 7138 Shady Oak Road Eden Prairie, MN 55344-3517

#### оню

Arthur Baier Company Suite 106 6690 Beta Drive Cleveland, OH 44143 216-461-6161

Arthur Baier Company 4940 Profit Way Dayton, OH 45414 513-276-4128

Arthur Baier Company 7395 Mapleleaf Boulevard Worthington, OH 43085 614-764-1144

Arthur Baier Company 7480 Kingswood Drive Westchester, OH 45069 513-779-2395

#### **OKLAHOMA**

ION Associates, Inc. 1504 109th Street Grand Prairie, TX 75050 214-647-8225

#### OREGON

Westerberg & Associates 7165 SW Fir Loop Portland, OR 97224 503-620-1931

#### **PENNSYVLANIA**

(West)

Arthur Baier Company Suite 106 6690 Beta Drive Cleveland, OH 44143 216-461-6161

#### (East)

TCA, Inc. 1570 McDaniel Drive West Chester, PA 19380 215-692-6853

#### RHODE ISLAND

John E. Boeing Co., Inc. 139 Billerica Road Chelmsford, MA 01824-3501 617-256-5800

#### SOUTH CAROLINA

Electronics Manufacturers Agents 309 Jordan Lane Huntsville, AL 35805 205-830-1947

#### SOUTH DAKOTA

Aldridge Associates, Inc. 7138 Shady Oak Road Eden Prairie, MN 55344-3517 612-944-8433

#### **TENNESSEE**

East (Eastern Time Zone)

Electronic Manufacturers Agents 620 Colonial Park Drive Roswell, GA 30075 404-992-7240

#### West (Central Time Zone)

Electronic Manufacturers Agents 309 Jordan Lane Huntsville, AL 35805 205-830-4030

#### **TEXAS**

(All, excluding) ION Associates, Inc. 1504 109th Street Grand Prairie, TX 75050 214-647-8225

ION Associates, Inc. Suite #100, Bldg. A 12731 Research Boulevard Austin, TX 78759 512-331-7251

ION Associates, Inc. 14347-A Torrey Chase Boulevard Houston, TX 77014-1696 713-537-7717

#### (El Paso County)

Nelco Electronix 4801 General Bradley, N.E. Albuquerque, NM 87111 505-293-1399

#### UTAH

Electrodyne Suite 120 825 E. 4800 South Street Salt Lake City, UT 84107 801-264-8050

#### VERMONT

John E. Boeing Co., Inc. 139 Billerica Road Chelmsford, MA 01824-3501 617-256-5800

#### VIRGINIA

**OPEN**

#### WASHINGTON

Westerberg & Associates 12505 Bell-Red Road, Suite 112 Bellevue, WA 98005 206-453-8881

#### WEST VIRGINIA

Arthur Baier Company Suite 106 6690 Beta Drive Cleveland, OH 44143 513-461-6161

#### WISCONSIN

Eagle Technical Sales 1805-B Hicks Road Rolling Meadows, IL 60008 312-991-0700

#### WYOMING

Electrodyne Suite 110 2620 South Parker Road Aurora, CO 80014-1660 303-695-8903

#### CANADA, excluding

Cantec Representative, Inc. 1573 Laperriere Avenue Kttawa, Ontario, CANADA K1Z 7T3 613-725-3704

Cantec Representatives, Inc. 8 Strathearn Avenue - Unit #18 Brampton, Ontario, CANADA L6T 4L8 416-791-5922

Cantec Representatives, Inc. 3639 Sources Road, Suite 116 Dollard des Ormeaux Quebec, CANADA H9B 2K4 514-683-6131

(Alberta & Br. Columbia) OPEN

## CUIDAD, MEXICO (only)

Nelco Electronix 4801 General Bradley, N.E. Albuquerque, NM 87111 505/293-1399

# UNITED KINGDOM AND CENTRAL EUROPE

Manhattan Skyline, Ltd. Manhattan House, Bridge Road Maidenhead, Berkshire England, S16 8DB 44-628/75851

# UNITED KINGDOM AND CENTRAL EUROPE (Continued)

Manhattan Skyline Halbleiter und Computerperipherie Vertriebs GmbH Weisbadener Str. 5/5a D-6204 Taunusstein-Hahn West Germany 49-6128/23044

#### ITALY

Skylab s.r.l. Electronic Components Piazza Carbonari 12 20125 Milano Italy 011/39-2-688-3806

#### FRANCE

Futur IDS 26, Rue de Versailles 78150 Le Chesnay France 011/39-63-2626

#### JAPAN

Japan Macnics Corporation 516 Imaimanami-Cho Kawasaki City, Kanagawa 211 Japan 011/81-44-711-0022

#### HONG KONG

Printed Circuits Int'l (HK), Ltd. 3rd Floor, Kin Yip Factory Bldg. 9 Cheung Yee Street Cheung Sha Wan Kowloon, Hong Kong 011/85-3743-1366

#### KOREA

Dongah Trading Corporation 7F, Dongah Building 14--2 Yoido-Dong, Youngdeungpo-GU C.P.O. Box 1815 Seoul, Korea 011/82-2-784-8312

## SINGAPORE

Datasource Electronics Private Ltd. 1296 Toa Payoh Lor 1 #04-01 Siong Hoe Int'l Building Singapore 1231 011/65-258-2752 or 5066

## **TAIWAN**

20

Prospect Technology Corporation 5, Lane 55, Long-Chiang Road Taipei, Taiwan 011/886-2-721-9533

# AUSTRAILIA, NEW ZEALAND

Energy Control Pty Ltd. 26 Boron Street Sumner Park Qld. 4074 P.O. Box 6502, Goodna Qld. 4300 Brisbane, Australia 011/61-7-376-2955

NCR Overview

04/88

# SCSI PRODUCTS

| 53C90 Enhanced SCSI Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 23  |

| ESP Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 25  |

| User-Accessible Register and Counters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 29  |

| Sequencer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 35  |

| Miscellaneous Blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 36  |

| Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 37  |

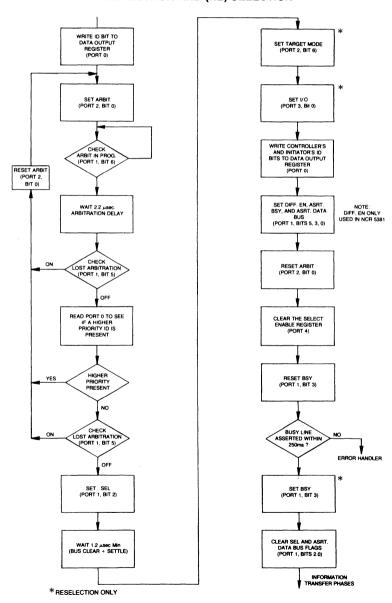

| Sequence Steps and Flow Charts.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 45  |

| Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 58  |

| Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| Appendices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 72  |

| 5380/C80 SCSI Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | , _ |

| General Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 75  |

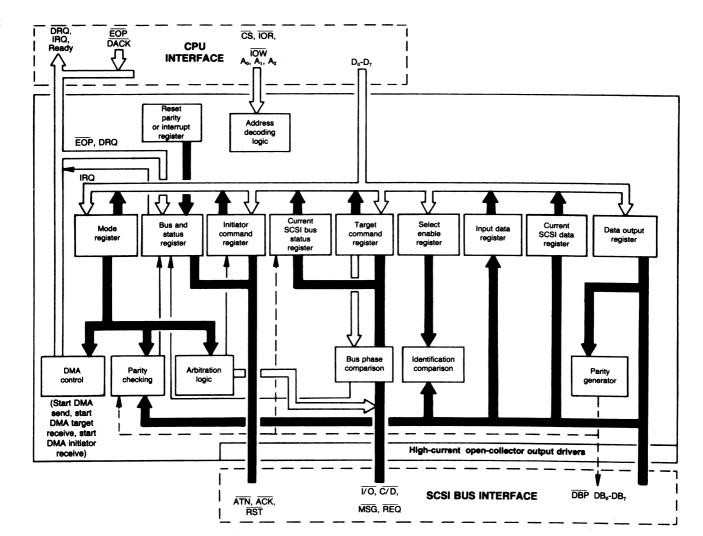

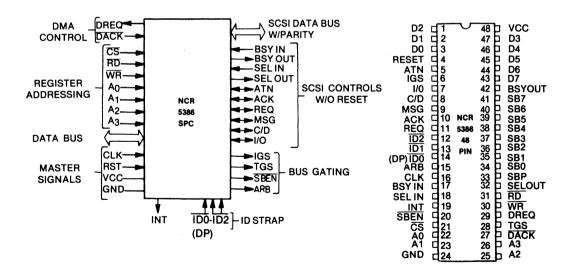

| Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 76  |

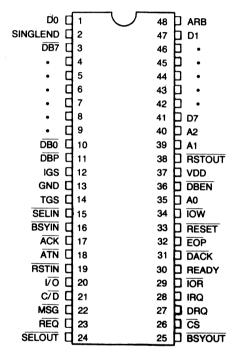

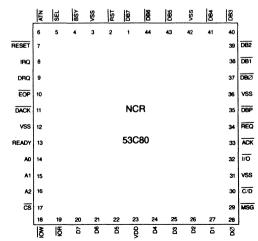

| Pin Description.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 77  |

| Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 79  |

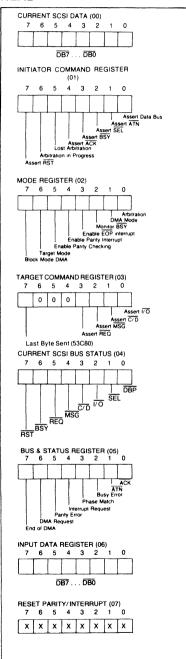

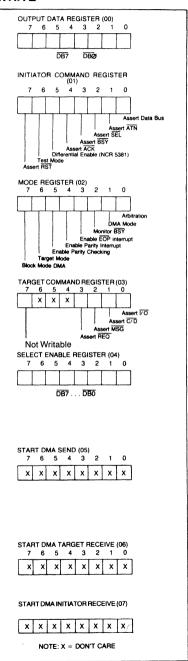

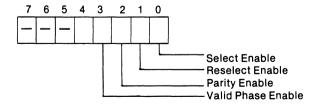

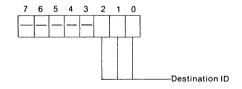

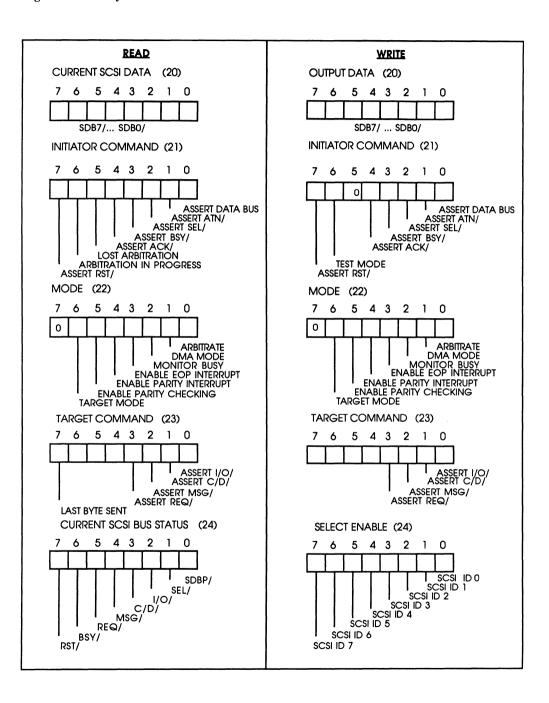

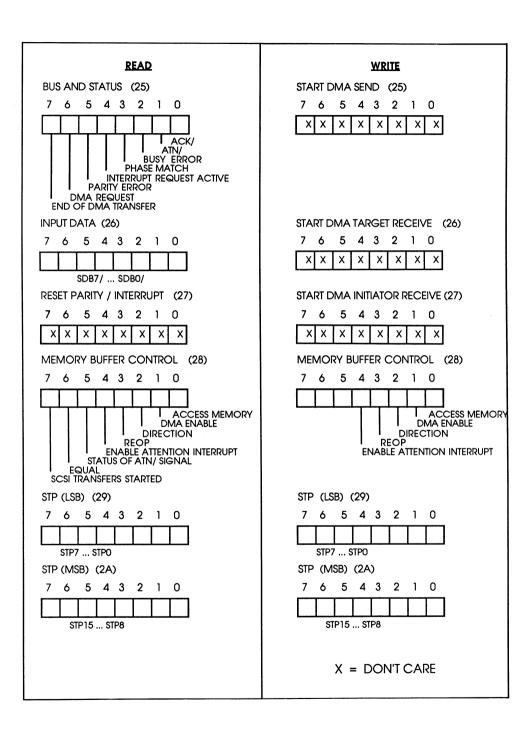

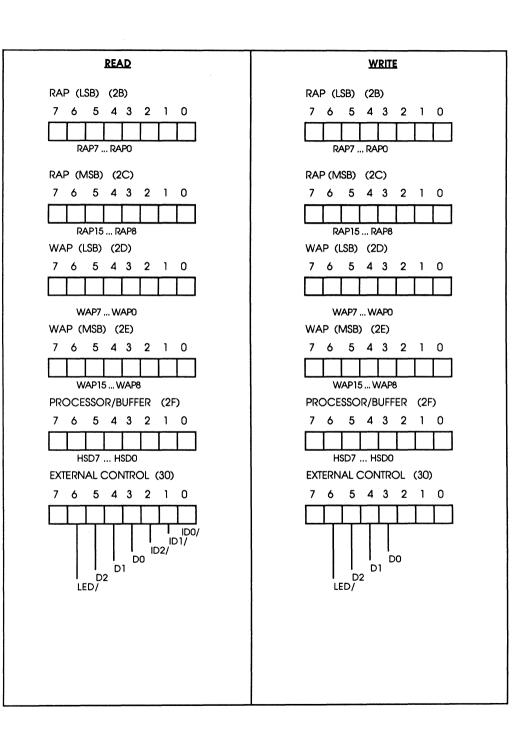

| Internal Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 80  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

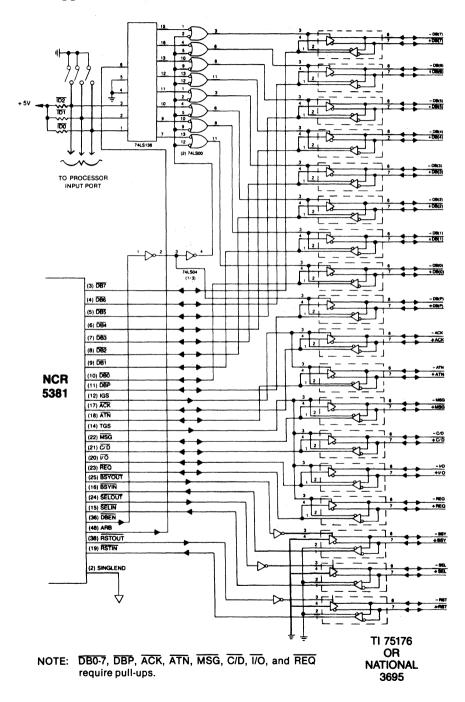

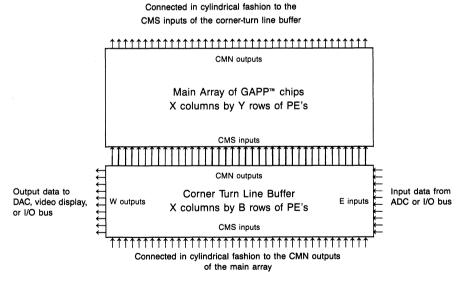

| On-Chip SCSI Hardware Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 86  |