## TMS34020 Software Development Board

# User's Guide

1991

**Computer Video Products**

TMS34020 Software Development Board

1991

-

User's Guide

### Installing the Board

- Step 1: Insert the Installation Disk into drive A.

- Step 2: Change to drive A and enter SURVEY.

- Step 3: If SURVEY detects a conflict, see the user's guide for instructions. If it doesn't, remove the diskette, turn your PC off, and install the SDB20 in your computer. Be sure to discharge any static electricity before touching the SDB20—ground yourself by touching the PC's power supply (usually a large silver or black box in the rear of the computer case).

Step 4: Connect the VGA passthrough cable to your VGA board. Connect your monitor cable to your SDB20 and turn on your PC.

- Step 5: Insert the Installation Disk into drive A.

- Step 6: Change to drive A and enter TIGASET.

Step 7: Select the Installation TIGA option and follow the instructions on the screen.

### **Quick Installation**

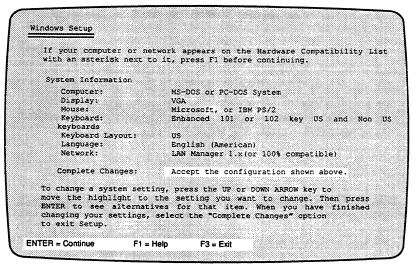

#### Installing the Windows Driver

If a TIGA Windows driver is supplied with your Microsoft Windows package, install it using the standard Windows set up. If the TIGA Windows driver is not supplied, install the driver that came with the board by following the steps below.

Step 1: Make sure the TIGA communications are running by rebooting your PC (if you had *tigaset*, edit your autoexec.bat file) or by running *TIGAAUTO*.

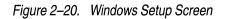

Step 2: Change directories to your Windows directory and enter SETUP.

Step 3: At the System Information screen, choose Display.

Step 4: You are presented with a list of drivers. Go to the bottom of the list and choose Other.

|       | we asked to change the type of Display to be installe<br>a Display from the following list:    |

|-------|------------------------------------------------------------------------------------------------|

|       |                                                                                                |

|       | 8514/a                                                                                         |

|       | CGA<br>Compag Portable Plasma                                                                  |

|       | EGA<br>Hercules Monochrome                                                                     |

|       | Olivetti/ATAT Monochrome or PVC Display                                                        |

| (To : | see more of the list, press the <-> arrow key)                                                 |

|       | is the UP or DOWN ARROW key to move the highlight to the you want to select. Then press ENTER. |

| If y  | you want to return to the System Information screen without                                    |

Step 5: Enter your TIGA directory path followed by \win30 (i.e., <TIGA DIRECTORY>\WIN30). The TIGA Windows driver is presented in 3 variations. Choose the appropriate driver for your system.

## TMS34020 Software Development Board User's Guide

2558670-9721 revision B July 1991

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to or to discontinue any semiconductor product or service identified in this publication without notice. TI advises its customers to obtain the latest version of the relevant information to verify, before placing orders, that the information being relied upon is current.

TI warrants performance of its semiconductor products to current specifications in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Unless mandated by government requirements, specific testing of all parameters of each device is not necessarily performed.

TI assumes no liability for TI applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Texas Instruments products are not intended for use in life-support appliances, devices, or systems. Use of a TI product in such applications without the written consent of the appropriate TI officer is prohibited.

| BYTE ANNUAL | PRODUCT | AWARDS |

|-------------|---------|--------|

|-------------|---------|--------|

| 1989<br>BUTTE<br>AWARD<br>OF<br>EXCELLENCE                                                                                                  | Presented To<br>Texas Instruments<br>For<br>TIGA-340             |  |

|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--|

| his BYTE Award of Excellence<br>recognizes this product<br>as one that bridges to<br>the future and truly advances<br>the state of the art. | Frederic S. Langa, Editor In Chief                               |  |

|                                                                                                                                             | J. Burt Totaro<br>J. Burt Totaro, Publisher/Group Vice President |  |

|                                                                                                                                             |                                                                  |  |

*Byte* editors chose TIGA as one of 1989's ten most technologically advanced products. The magazine concluded that TIGA is well on its way to becoming the standard for high-resolution graphics applications development.

### Preface

## **Read This First**

### How to Use This Manual

This document contains the following chapters:

| Chapter 1  | Introduction<br>Provides an overview of the key features for the TMS34020 Software Develop-<br>ment Board (SDB20).                                    |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 2  | <b>Installing SDB20 Hardware and Software</b><br>Identifies hardware and software system requirements; provides step-by-step installation procedures. |

| Chapter 3  | <b>Theory of Operation</b><br>Gives a functional description of the SDB20.                                                                            |

| Appendix A | Physical Specifications<br>Provides detailed technical information about the SDB20.                                                                   |

| Appendix B | <b>Troubleshooting</b><br>Outlines troubleshooting procedures; gives customer support information.                                                    |

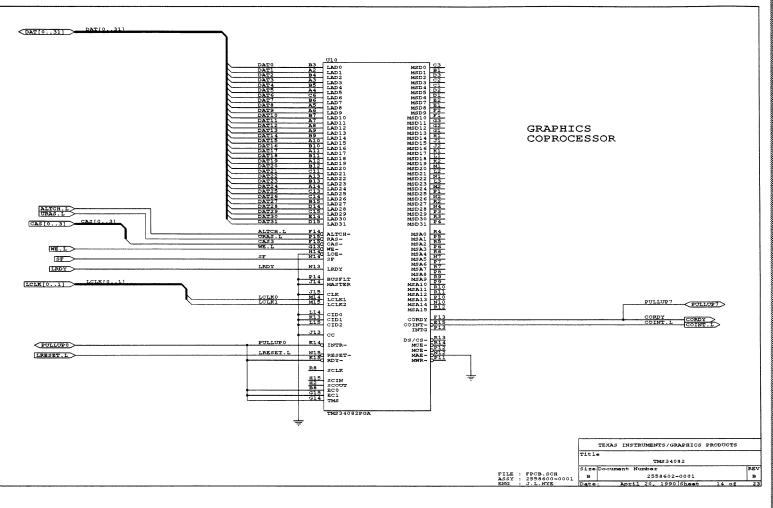

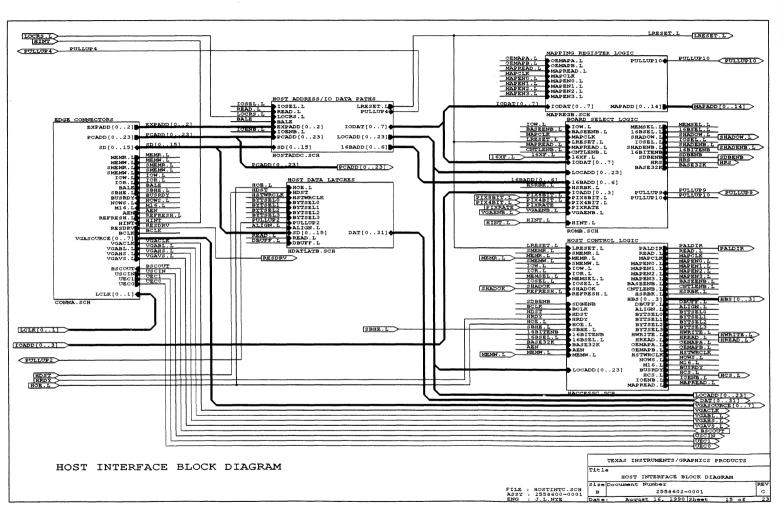

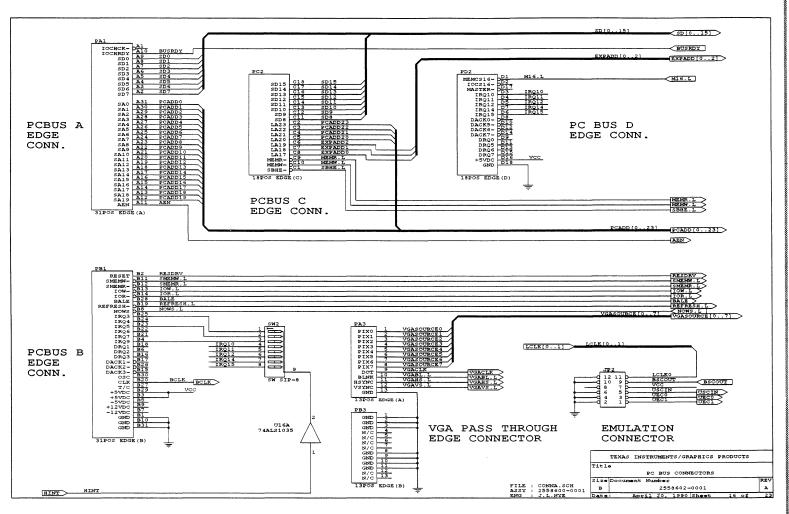

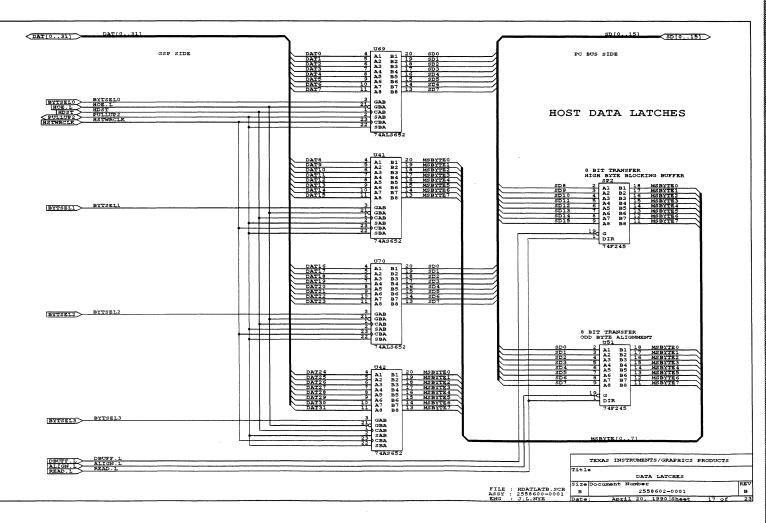

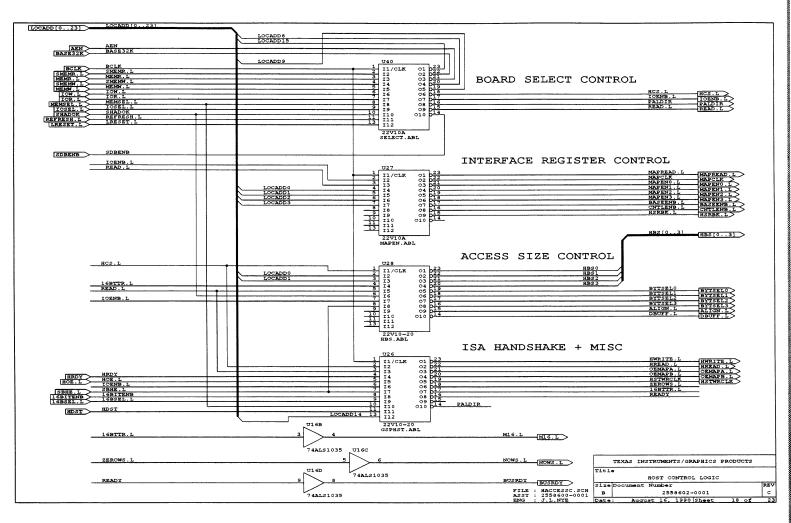

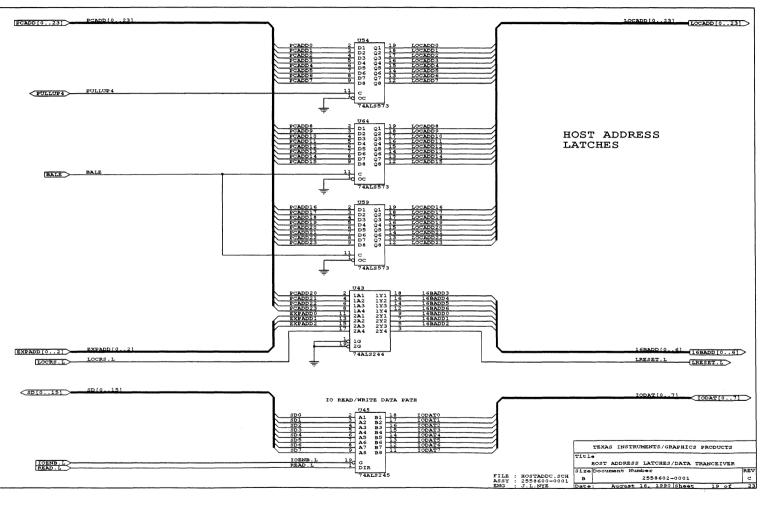

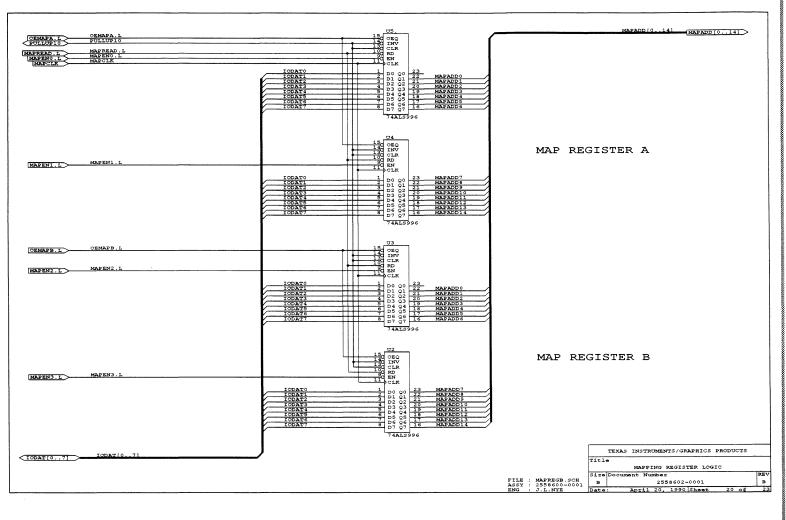

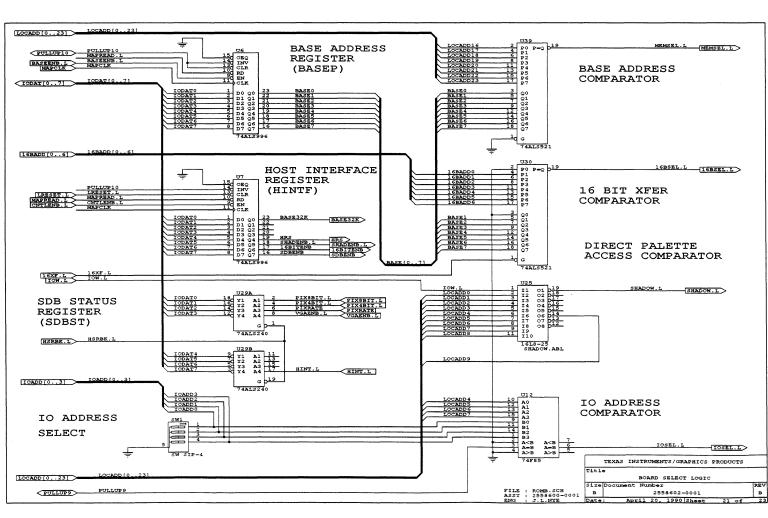

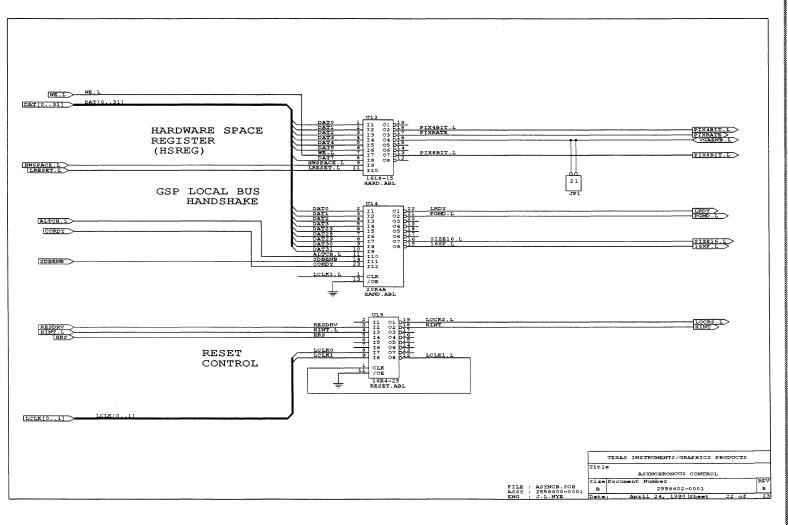

| Appendix C | Schematics<br>Contains the schematics for the SDB20.                                                                                                  |

Appendix D Glossary

### **Related Documentation**

The following TMS34020 documents are available from Texas Instruments. To obtain a copy of any of these TI documents, please call the Texas Instruments Customer Response Center (CRC) at (800) 336-5236, or if you are outside of the U.S. and Canada, call (214) 995-6611. When ordering, please identify the book by its title and its literature number.

- □ The *TMS340 Family Code-Generation Tools User's Guide*, literature number SPVU020, describes the C compiler, assembler, linker, archiver, and auxiliary tools that are available for developing TMS34010 or TMS34020 code.

- □ The *TMS340 Family C Source Debugger User's Guide*, literature number SPVU021, tells how to use the TMS340 Family C Source Debugger with the TMS34010 TIGA Development Board (TDB10), the TMS34020 Software Development Board (SDB20), and the TMS34020 Emulator.

- The TMS340 Family Graphics Library User's Guide, literature number SPVU027, describes the graphics operations library that is available for a TMS340-based graphics system.

- The TIGA Interface User's Guide, literature number SPVU015, describes the Texas Instruments Graphics Architecture (TIGA), a software interface that standardizes communication between application software and TMS340-based hardware for IBM-compatible PCs.

- □ The *TMS34020 User's Guide*, literature number SPVU019, describes the TMS34020, which is the second-generation graphics processor in the TMS340 family of computer video products.

- □ The TMS34082 SRAM Module Technical Reference, literature number SCGU002, describes the TMS34082 SRAM module, which extends the capabilities of the SDB20 by providing a platform for developing custom, floating-point routines that use external instructions.

- □ The *TMS34082 Designer's Handbook*, literature number SCGU004, discusses the hardware aspects of the TMS34082, such as pin functions, architecture, stack operation, and interface. It also contains the TMS34082 internal and external instructions sets.

- Pixel Perspectives, literature number SPVN05x, is a newsletter published by the Computer Video Products Group of Texas Instruments Incorporated. It describes new products, discusses support for existing products, and identifies new documentation releases.

### Style and Symbol Conventions

This document uses the following conventions.

Program listings, program examples, interactive displays, filenames, and symbol names are shown in a special font. Some examples use a bold version to identify code, commands, or portions of an example that you enter.

Here is an example of a system prompt and a command that you might enter:

A: tigaset

- □ CTRL/V, ^V, and CTRL V are synonymous and mean to press the keyboard CTRL (CNTL on some keyboards) and the V keys together.

- CR>, <RETURN>, <ENTER>, ENTER, and are synonymous and mean to press the keyboard ENTER or RETURN keys.

- SP> and synonymous and mean to press the keyboard space bar.

- <ESC> and <u>ESC</u> are synonymous and mean to press the keyboard ESC key.

### Information About Cautions and Warnings

This book contains cautions and warnings. The information in a caution or a warning is provided for your protection. Please read each caution and warning carefully.

This is what a warning looks like.

A warning describes a situation that could potentially cause harm to you.

### Trademarks

*Anvil 1000* and *Anvil 5000* are trademarks of Manufacturing Consulting Services, Inc. *AutoCAD Release 10, AutoShade, AutoSketch* are registered trademarks of Autodesk, Inc. *Bt478* is a trademark of Brooktree Corp.

CADKEY 3 V3.5, CADKEY Render, DataCAD, and DataCAD Velocity are trademarks of CADKEY, INC.

*DesignCAD 2D* and *DesignCAD 3D* are trademarks of American Small Business Computing. DGIS and GSS\*CGI are trademarks of Graphic Software Systems, Inc.

Drawbase is a trademark of CADworks, Incorporated.

GEM Artline, GEM Presentation Team, and Digital Research Draw Plus are trademarks of Digital Research, Inc.

Generic CADD is a trademark of Generic Software.

GSPOT I, II, and III are trademarks of Pixelab, Inc.

HALO is a trademark of Media Cybernetics, Inc.

HOOPS is a trademark of Ithaca Software.

*IBM PC, IBM PC/AT*, and *IBM PC/XT* are trademarks of International Business Machines. *Intel, i286,* and *i386* are trademarks of Intel Corp.

*Lotus, Lotus 1-2-3 Release 2.01* and *Release 2.2,* and *Symphony* are trademarks of Lotus. *MasterCAM* is a trademark of CNC Software.

*MS-DOS, Presentation Manager,* and *Windows 3.0* are trademarks of Microsoft Corp. *Microstation* is a trademark of Intergraph Corporation.

*MultiSync* and *MultiSync Graphics* are trademarks of NEC Home Electronics (U.S.A) Inc. *OrCAD/SDT III, OrCAD PCB II,* and *OrCAD VST* are trademarks of OrCAD L.P.

PAL is a registered trademark of Advanced Micro Devices, Inc.

Panacea is a trademark of Panacea, Inc.

RoboCAD 2.2 is a trademark of Robo Systems International, Inc.

SDB20 and TIGA are trademarks of Texas Instruments Incorporated.

Ventura Publisher/GEM is a registered trademark of Ventura Software, Inc.

X Window System is a trademark of the Massachusetts Institute of Technology. *Xoftware* is a trademark of AGE.

## Contents

| 1 |       | <i>des an o</i> ve<br>An Ove<br>The TIC<br>The TN | 1-1verview of the key features for the TMS34020 software development board (SDB20).erview of the SDB201-2GA Software Interface1-4IS34020 Graphics Processor1-5IS34082 Graphics Floating-Point Processor1-6 |

|---|-------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 |       | ies hard                                          | B20 Hardware and Software         2-1           Iware and software system requirements; provides step-by-step installation proce-                                                                          |

|   | 2.1   | 2.1.1                                             | Requirements       2-2         Hardware and Software Requirements       2-2         Oabling       2-2                                                                                                      |

|   | 2.2   | 2.1.2<br>Installir<br>2.2.1                       | Cabling         2-2           ng the SDB20         2-3           Determining Your System Configuration         2-3                                                                                         |

|   |       | 2.2.2<br>2.2.3                                    | Preparing the SDB20 for Installation                                                                                                                                                                       |

|   | 2.3   | 2.3.1                                             | ag and Running TIGA Setup Utilities                                                                                                                                                                        |

|   | 2.4   | 2.3.2<br>Sotting                                  | Installing TIGA Software2-12Up a Dual Monitor System2-23                                                                                                                                                   |

|   | 2.4   | -                                                 | nizing Monitor Timing                                                                                                                                                                                      |

|   | 2.6   |                                                   | oftware Drivers                                                                                                                                                                                            |

|   |       | 2.6.1                                             | TIGA Video Drivers                                                                                                                                                                                         |

|   |       | 2.6.2                                             | Installing the TIGA Windows Driver 2-29                                                                                                                                                                    |

| 3 |       |                                                   | eration                                                                                                                                                                                                    |

|   | Gives |                                                   | onal description of the SDB20.                                                                                                                                                                             |

|   | 3.1   |                                                   | terface                                                                                                                                                                                                    |

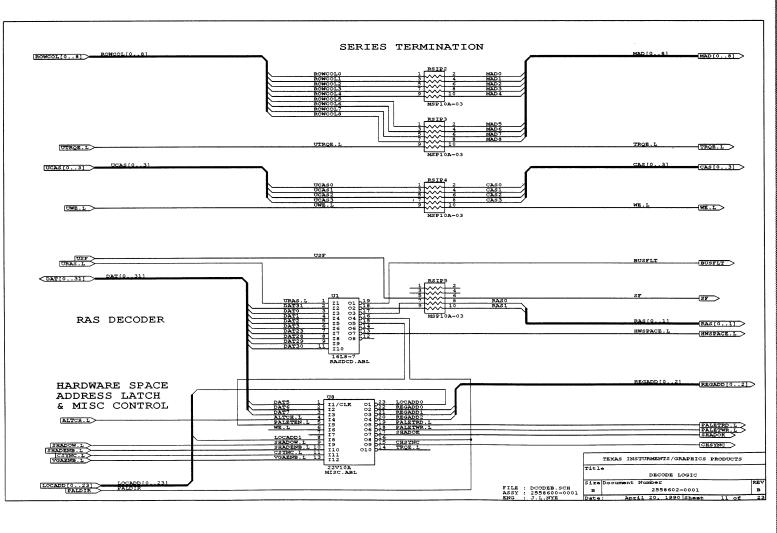

|   |       | 3.1.1                                             | Host I/O Decoding                                                                                                                                                                                          |

|   |       | 3.1.2                                             | SDB20 Host Communication Registers                                                                                                                                                                         |

|   |       | 3.1.3                                             | Address Conversion Principles                                                                                                                                                                              |

|   |       | 3.1.4                                             | Host Interface Control PALs                                                                                                                                                                                |

|   |       | 3.1.5                                             | Host 8-Bit I/O Write Cycle                                                                                                                                                                                 |

|   |       | 3.1.6                                             | Host 8-Bit Memory Read Cycle                                                                                                                                                                               |

|   |       | 3.1.7                                             | Host 16-Bit Memory Write Cycle    3-32                                                                                                                                                                     |

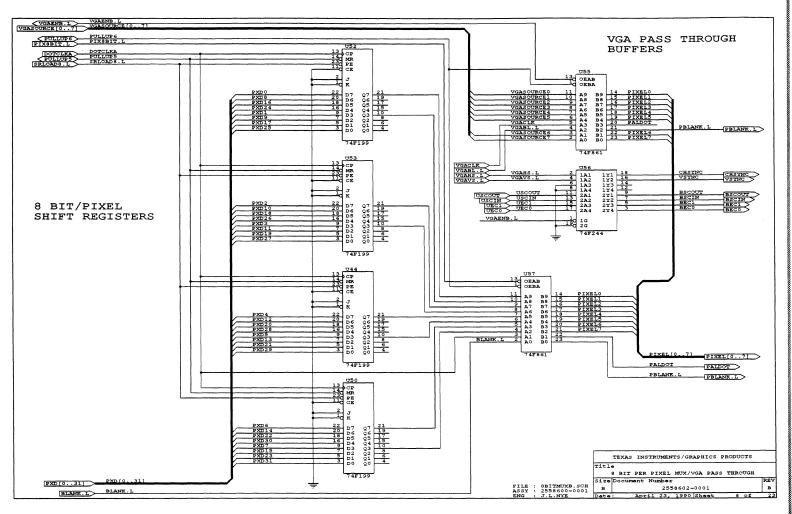

|   |       | 3.1.8<br>3.1.9<br>3.1.10            | VGA Passthrough3-34VGA Passthrough Cycle3-40Resetting the SDB203-42CDD20 Interment Control2-40                                    |

|---|-------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

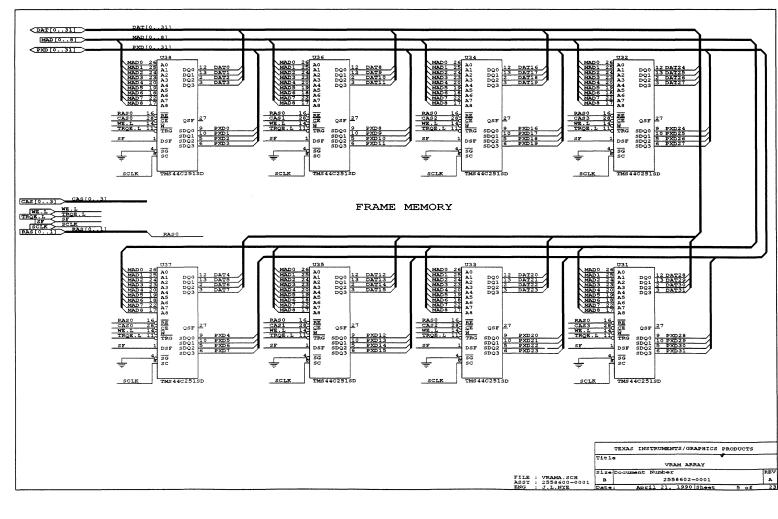

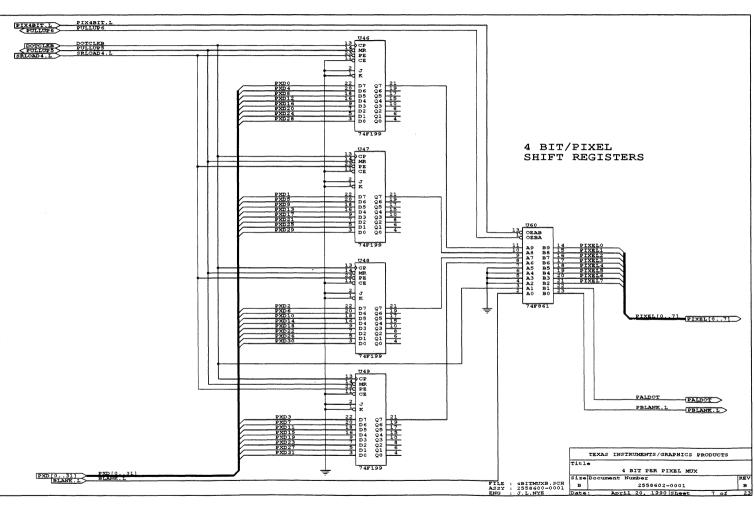

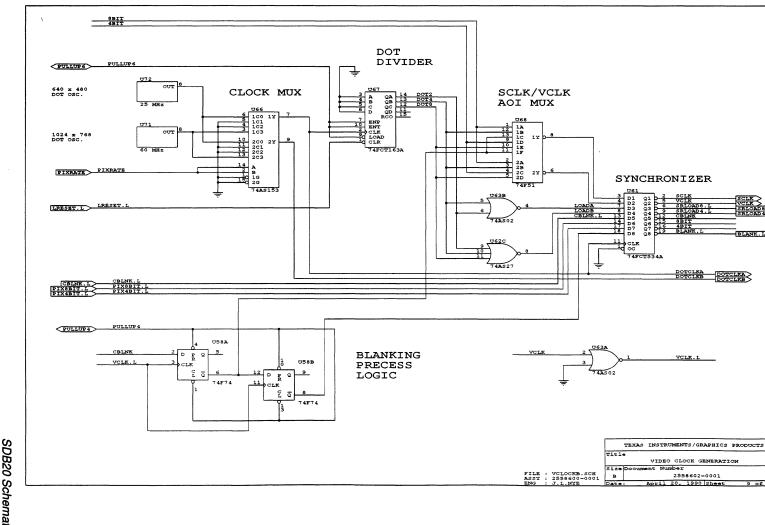

|   | 3.2   | 3.1.11<br>The Fra<br>3.2.1<br>3.2.2 | SDB20 Interrupt Control3-43ame Buffer/Program Memory Interface3-45TMS34020 Memory Mapping3-45The TMS34020-to-Memory Interface3-46 |

|   |       | 3.2.3<br>3.2.4<br>3.2.5             | The RASDCD PAL, U13-48TMS34020-to-VRAM Interface3-51TMS34020-to-DRAM Memory Interface3-52                                         |

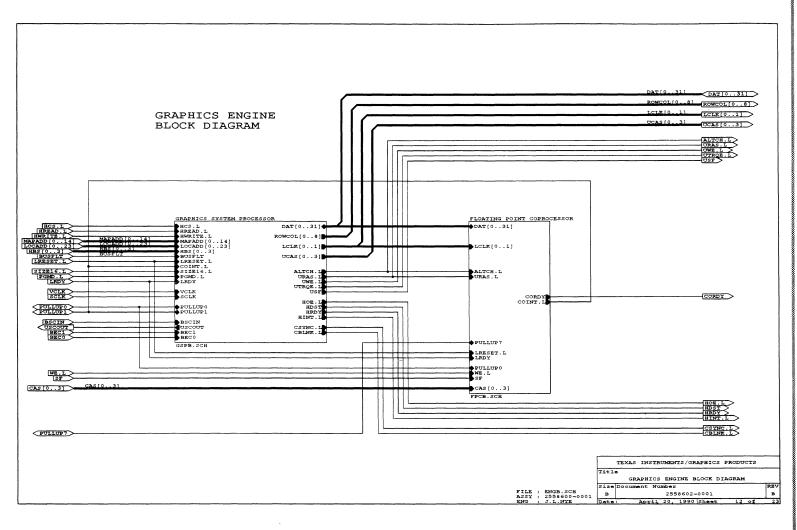

|   | 3.3   |                                     | IS34082 Floating-Point Coprocessor                                                                                                |

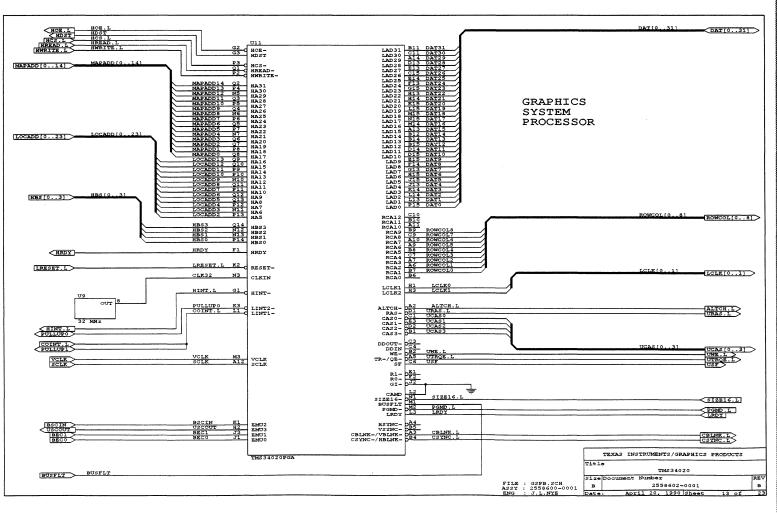

|   | 0.0   | 3.3.1                               | How the TMS34082 Communicates With the TMS34020                                                                                   |

|   |       | 3.3.2                               | The HAND PAL, U14                                                                                                                 |

|   |       | 3.3.3                               | Installing the TMS34082                                                                                                           |

|   |       | 3.3.4                               | The TMS34082 SRAM Module                                                                                                          |

|   |       | 3.3.5                               | The TMS34082 Bus Architecture                                                                                                     |

|   |       | 3.3.6                               | The TMS34082 Bus Architecture With the SRAM Module Installed                                                                      |

|   |       | 3.3.7                               | For Additional Information                                                                                                        |

|   | 3.4   | Backen                              | nd Section                                                                                                                        |

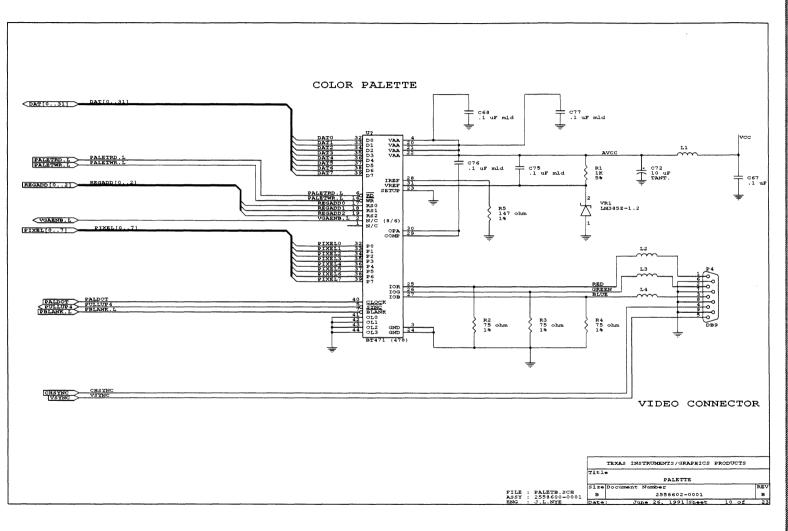

|   |       | 3.4.1                               | The Frame Buffer-to-Color Palette Interface                                                                                       |

|   |       | 3.4.2                               | The MISC PAL, U8                                                                                                                  |

|   |       | 3.4.3                               | The Bt478 Color Palette                                                                                                           |

|   |       | 3.4.4                               | The SDB20 Video Output Connector, P4                                                                                              |

|   | 3.5   | The TM                              | IS34020-to-XDS500 Interface                                                                                                       |

| A |       | -                                   | fications                                                                                                                         |

|   | A.1   | SDB20                               | Hardware Specifications                                                                                                           |

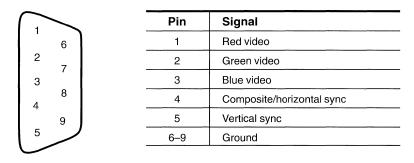

|   | A.2   | Video (                             | Dutput Connector Pinouts A-3                                                                                                      |

|   | A.3   |                                     | Fiming A-4                                                                                                                        |

|   | A.4   | SDB20                               | Input/Ouptut Registers                                                                                                            |

|   | A.5   | SDB20                               | Hardware Interrupt Settings A-6                                                                                                   |

| В |       | es troub                            | ting Guide                                                                                                                        |

|   | B.1   |                                     | rror MessagesB-2                                                                                                                  |

|   | B.2   | Custon                              | ner SupportB-6                                                                                                                    |

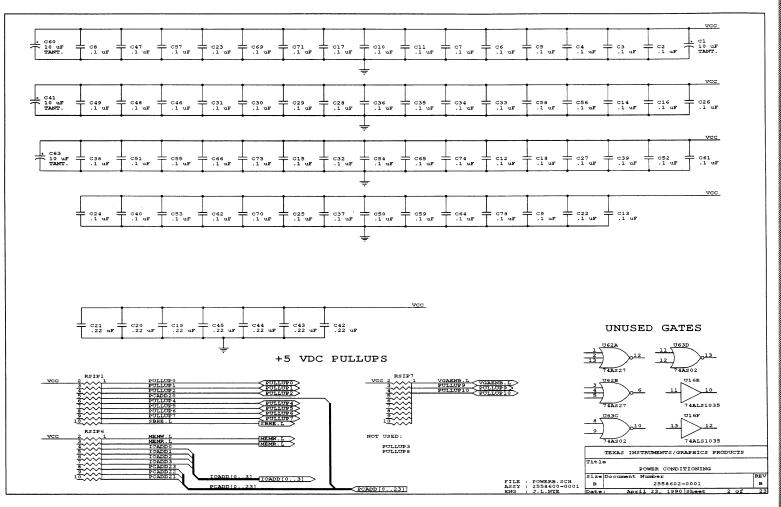

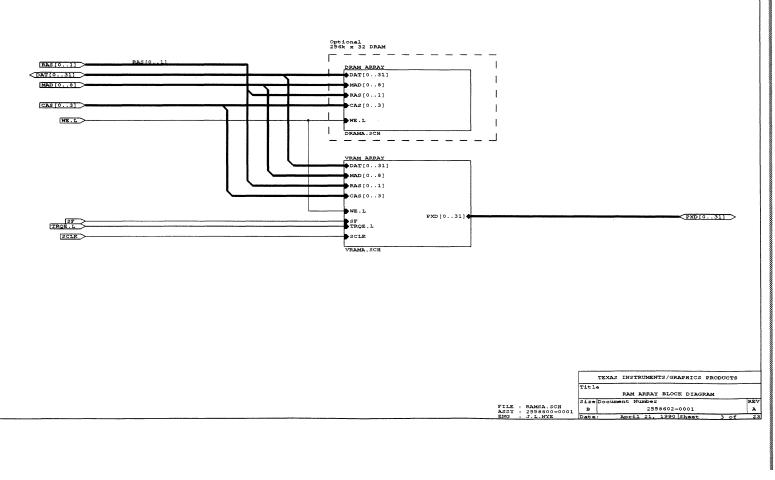

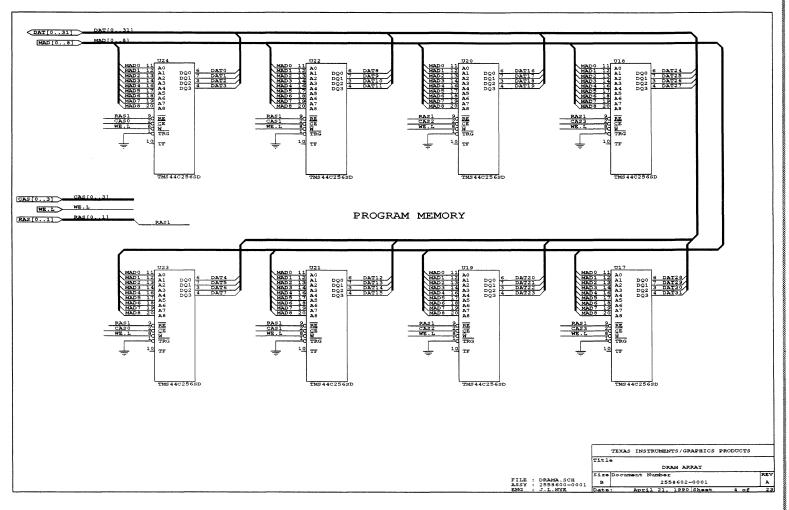

| С |       |                                     | chematics for the SDB20.                                                                                                          |

| D | Gloss | sary                                | D-1                                                                                                                               |

# Figures

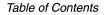

| 1–1.  | Software Development Board Block Diagram 1-3                              |

|-------|---------------------------------------------------------------------------|

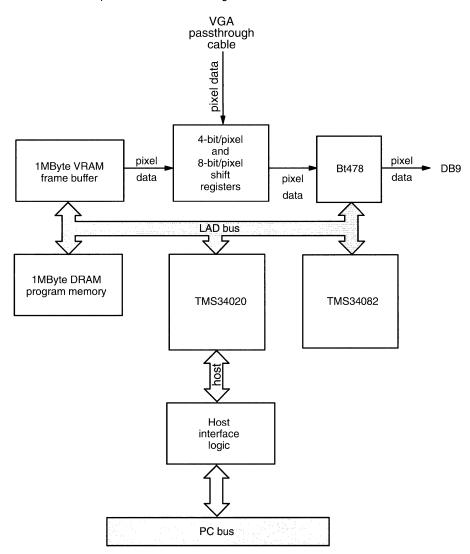

| 1–2.  | Graphics Processing Shared Between TMS340 and Host Processors 1-4         |

| 2–1.  | Removing the PC Cover                                                     |

| 2–2.  | Removing the PC Mounting Bracket 2-8                                      |

| 2–3.  | Installing the SDB20 2-9                                                  |

| 2–4.  | Connecting the VGA Passthrough Cable 2-10                                 |

| 2–5.  | Connecting the 9-Pin Monitor Cable 2-10                                   |

| 2–6.  | The TIGA Setup Utility Screen — Main Menu 2-13                            |

| 2–7.  | TIGA Installation Screen — Host I/O Base Address 2-14                     |

| 2–8.  | TIGA Installation Screen Host Memory Segment Base Address 2-15            |

| 2–9.  | TIGA Installation Screen — Data Transfer Size 2-16                        |

| 2–10. | TIGA Installation Screen — Default Directory 2-17                         |

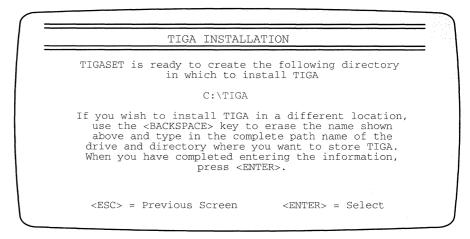

| 2–11. | TIGA Installation Screen — TIGA Environment 2-17                          |

| 2–12. | TIGA Installation Screen — Monitor Configuration 2-18                     |

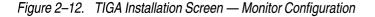

| 2–13. | TIGA Installation Screen — Defined Monitors 2-19                          |

| 2–14. | TIGA Installation Screen — Determining the Monitor Color 2-19             |

| 2–15. | TIGA Installation Screen — Correcting the Monochrome Display Problem 2-20 |

| 2–16. | Typical Change TIGA Display Mode Screen         2-21                      |

| 2–17. | TIGA Information Screen for the SDB20    2-22                             |

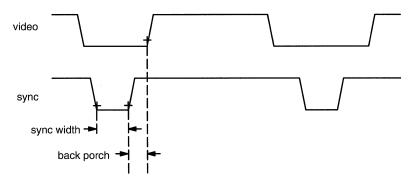

| 2–18. | Typical Video Timing Diagram    2-24                                      |

| 2–19. | Typical Change Monitor Option Window    2-26                              |

| 2–20. | Windows Setup Screen    2-30                                              |

| 2–21. | Windows Setup Screen — Display    2-31                                    |

| 2–22. | Windows Setup Screen—Display Driver    2-32                               |

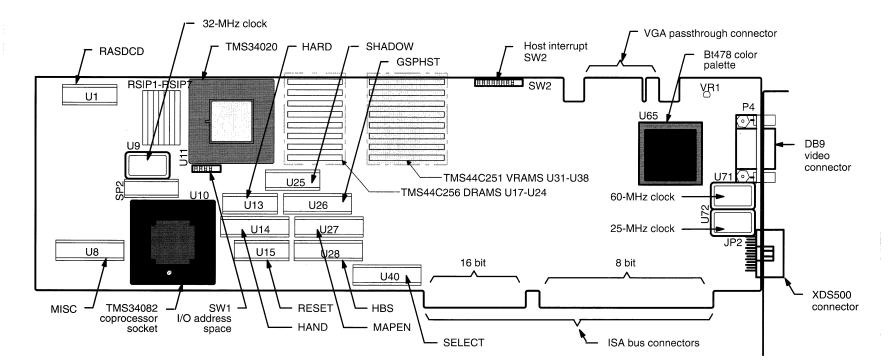

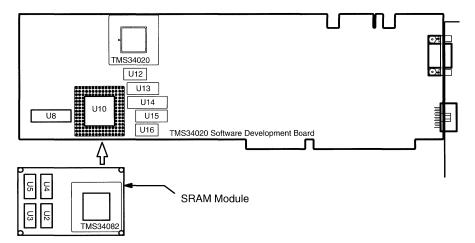

| 3–1.  | The SDB20 Software Development Board 3-3                                  |

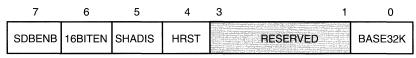

| 3–2.  | The HINTF Register                                                        |

| 3–3.  | The SDB20 Status Register 3-9                                             |

| 3–4.  | Hardware Space Control Register (HSREG) 3-10                              |

| 3–5.  | ABEL Source File for the HARD PAL, U13                                    |

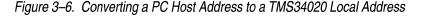

| 3–6.  | Converting a PC Host Address to a TMS34020 Local Address                  |

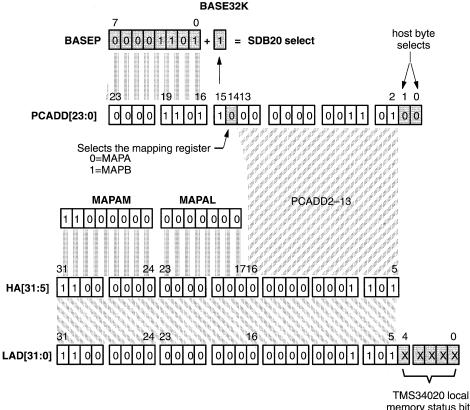

| 3–7.  | Converting a TMS34020 Local Address to a Host PC Address |

|-------|----------------------------------------------------------|

| 3–8.  | ABEL Source File for the GSPHST PAL, U26                 |

| 3–9.  | ABEL Source File for the HBS PAL, U28                    |

| 3–10. | ABEL Source File for the SELECT PAL, U40                 |

| 3–11. | ABEL Source File for the MAPEN PAL, U27                  |

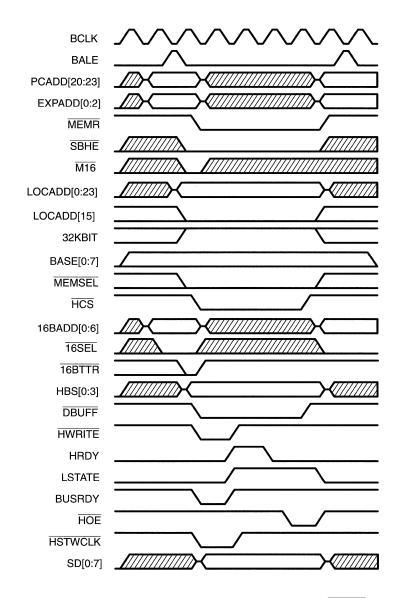

| 3–12. | Host-to-SDB20 I/O Write Cycle                            |

| 3–13. | Host-to-SDB20 8-Bit Memory Read Cycle 3-30               |

| 3–14. | Host-to-SDB20 16-Bit Memory Write Cycle 3-32             |

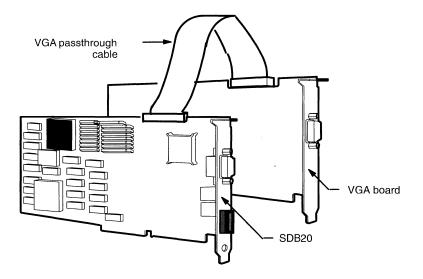

| 3–15. | VGA Passthrough Cable Connection 3-35                    |

| 3–16. | ABEL Source File for the SHADOW Device, U25              |

| 3–17. | ABEL Source File for the MISC PAL, U8                    |

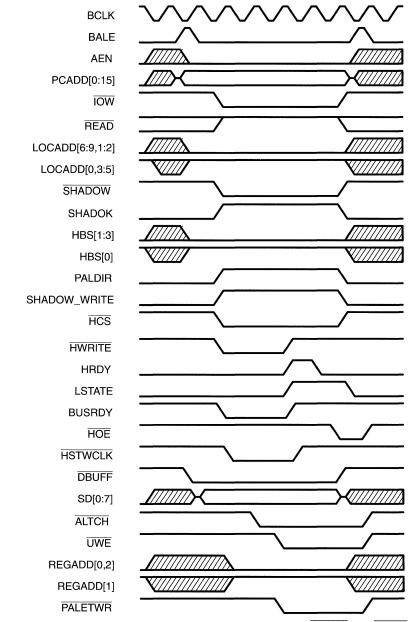

| 3–18. | VGA Passthrough Cycle 3-40                               |

| 3–19. | The ABEL Source File for the RASDCD PAL, U1              |

| 3–20. | ABEL Source File for the HAND PAL, U14                   |

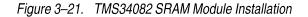

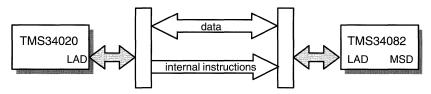

| 3–21. | TMS34082 SRAM Module Installation                        |

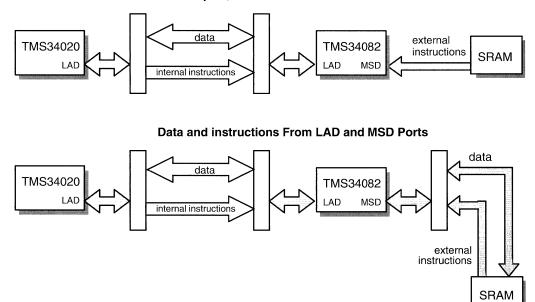

| 3–22. | The TMS34082 Bus Architecture in Standard SDB20 3-56     |

| 3–23. | The TMS34082 Bus Architecture Using the SRAM Module      |

| B–1.  | SDB20 Installation Option Window                         |

## Tables

| 2–1.  | Hardware Requirements 2-2                          |

|-------|----------------------------------------------------|

| 2–2.  | SW1 I/O Space Settings 2-5                         |

| 2–3.  | SW2 Interrupt Settings                             |

| 2–4.  | TIGA Video Drivers                                 |

| 3–1.  | The SDB20 Communication Registers 3-4              |

| 3–2.  | SDB20 Communication Register Memory Map 3-5        |

| 3–3.  | The MAPA and MAPB Mapping Registers                |

| 3–4.  | SDBST Bit Field Descriptions 3-9                   |

| 3–5.  | Host and Data Latch Byte Select 3-21               |

| 3–6.  | The TMS34020 Local Memory Map 3-45                 |

| 3–7.  | Local Memory Addresses-to-RCA Bus Connections 3-47 |

| 3–8.  | DRAM and VRAM Bank Selection 3-48                  |

| 3–9.  | RASDCD PAL Signal Selection 3-48                   |

| 3–10. | TMS44C251 Functional Truth Table 3-52              |

| A–1.  | SDB20 Hardware Specifications A-2                  |

| A–2.  | Video Output Connector Pinouts A-3                 |

| A–3.  | $1024 \times 768$ Noninterlaced Video Timing A-4   |

| A–4.  | 640 × 480 Noninterlaced Video Timing A-4           |

| A–5.  | ISA I/O Address Locations A-5                      |

| A6.   | SDB20 Hardware Interrupt Settings A-6              |

|       |                                                    |

### **Chapter 1**

### Introduction

The TMS34020 Software Development Board (SDB20) is a high-performance ISA bus-compatible graphics card that features the TMS34020 graphics processor.

This software development tool is designed for developing application software that is compatible with the TMS34020 graphics processor. This module demonstrates the simplicity of designing hardware by using the TMS34020 to develop a high-performance bit-mapped graphics display.

The SDB20 package includes the board, this manual, a high-density floppy disk containing demonstration and utility software, and the TMS340 Family C Source Debugger.

Instructions for installation of the board and the demonstration software are contained in Section 2.2, *Installing the SDB20*.

#### Note: TMS34020 Assembly Language Model

It is assumed that persons using the SDB20 have a knowledge of the TMS34020 graphics processor assembly language. The instruction set is explained in the *TMS340 Family Code Generation Tools* package and in the *TMS34020 User's Guide*.

Topics covered in this introductory chapter include:

| Section |                                         | Page |  |

|---------|-----------------------------------------|------|--|

| 1.1     | An Overview of the SDB20                | 1-2  |  |

| 1.2     | TIGA Software Interface                 | 1-4  |  |

| 1.3     | The TMS34020 Graphics Processor         | 1-5  |  |

| 1.4     | The TMS34082 Floating-Point Coprocessor | 1-6  |  |

### 1.1 An Overview of the SDB20

The TMS34020 SDB consists of a 32-bit TMS34020 graphics processor with the following features:

- A powerful 32-MHz TMS34020 graphics processor

- □ TIGA 2.05 compatibility

- □ An optional TMS34082 floating-point coprocessor

- □ An optional TMS34082 SRAM module

- A 32-bit local data bus

- Configurable PC bus transfer width (8- or 16-bit)

- ❑ Variable display resolutions:

- 1024 H × 768 V noninterlaced

- 640 H × 480 V noninterlaced

- Selectable screen resolution as follows:

- 1024 × 768 pixels, 256 colors/gray levels

- 1024 × 768 pixels, 16 colors/gray levels

- 640 × 480 pixels, 256 colors/gray levels

- 640 × 480 pixels, 16 colors/gray levels

- **VGA** passthrough

- □ 1 MByte zero wait-state video RAM (VRAM)

- 1 MByte zero wait-state dynamic RAM (DRAM)

- □ Supports TMS34020 emulation

- **G** Supports selectable PC bus interrupts

- □ Software-configurable base address, extended 16 MByte range

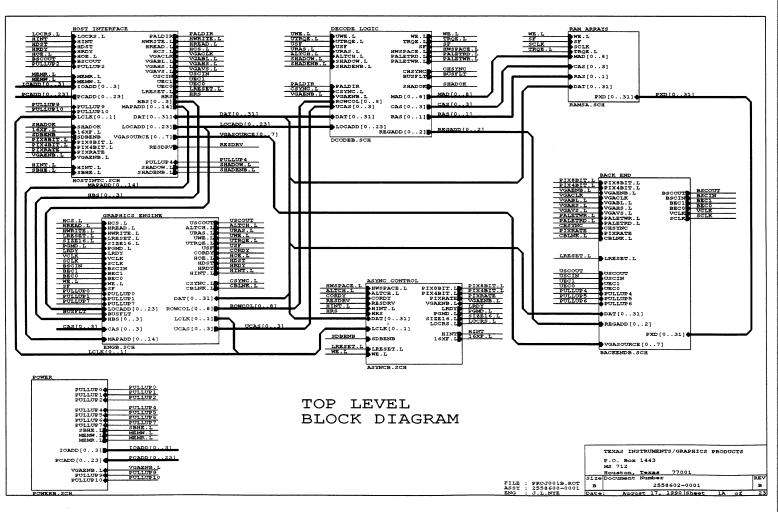

Figure 1–1 is a simplified block diagram that outlines the principle blocks and data paths within the SDB20. These are discussed in detail in Chapter 3, *Theory of Operation*.

Figure 1–1. Software Development Board Block Diagram

### 1.2 The TIGA Software Interface

The Texas Instruments Graphics Architecture (TIGA) is a software interface standard for the TMS340 family of graphics processors. Figure 1–2 shows the relationship between the TMS340 and host processors.

The TIGA software interface provides:

- A standard communication protocol between the host processor and the TMS340 processor.

- The ability to divide tasks between the TMS340 processor and the 80x86 host so that the graphics-intensive functions can run in parallel, thus improving system efficiency.

- The ability to customize TIGA to take advantage of any added feature available on the target TMS340-based board.

- The ability to develop portable applications and application drivers for the diverse range of TMS340-based systems.

### 1.3 The TMS34020 Graphics Processor

The TMS34020 is the second generation of the TMS340 family of graphics processors. It combines the best features of a general-purpose processor and a graphics controller.

The instruction set for the TMS34020 provides a full complement of generalpurpose instructions (e.g., jumps and calls) and supports pixel drawing, window, and Boolean operations. The TMS34020 architecture supports a variety of pixel sizes, frame buffer sizes, and screen sizes.

On-chip functions have been carefully selected so that no function ties the TMS34020 to a particular display resolution. This enhances the portability of graphics standards, such as MIT's X, CGI/CGM, PHIGS, and Microsoft's Windows and Presentation Manager.

### 1.4 The TMS34082 Graphics Floating-Point Processor

The TMS34082 Graphics Floating-Point Processor is designed to interface directly with the TMS34020. This allows the TMS34020 to perform computationintensive functions many times faster than a software implementation.

The TMS34082 performs single- and double-precision floating-point operations, conforming to the IEEE 754 standard. It also performs complex 2- and 3-dimensional operations such as  $3\times3$  convolution,  $4\times4$  matrix, and cubic spline operations.

### **Chapter 2**

## Installing SDB20 Hardware and Software

This chapter illustrates the installation requirements and procedure for using the SDB20. The SDB20 is a full-size printed circuit board that can be placed in either an 8- or 16-bit slot of a standard ISA bus. The board is software selectable for either 8- or 16-bit memory transfers; it is limited to 8-bit I/O transfers.

The SDB20 can be used effectively in a single monitor system because of the onboard VGA passthrough feature, which allows interactive switching between the high-resolution graphics generated by the TMS34020 and those generated by VGA.

The topics discussed in this chapter include:

| Sect | ion                                   | Page |

|------|---------------------------------------|------|

| 2.1  | System Requirements                   | 2-2  |

| 2.2  | Installing the SDB20                  | 2-3  |

| 2.3  | Installing and Running TIGA Utilities | 2-12 |

| 2.4  | Setting Up a Dual Monitor System      | 2-23 |

| 2.5  | Customize Monitor Timing              | 2-24 |

| 2.6  | TIGA Software Drivers                 | 2-28 |

|      |                                       |      |

### 2.1 System Requirements

### 2.1.1 Hardware and Software Requirements

In addition to the items that were shipped with the SDB20, you will need the items listed in Table 2–1.

### Table 2–1. Hardware Requirements

| Requirement             | Description                                                                                                    |

|-------------------------|----------------------------------------------------------------------------------------------------------------|

| SDB20 requirements      | Approximately 2 amps @ +5 V (10 watts)                                                                         |

| Host PC                 | An IBM PC/AT, IBM PC/XT, or 100% compatible PC EISA system with a hard-disk system and a floppy-disk drive.    |

| Display                 | Color (RGB)                                                                                                    |

| Slot                    | One 8-bit or 16-bit slot                                                                                       |

| Graphics card           | A VGA-compatible graphics display card. This card is needed only if you are using the VGA passthrough feature. |

| Miscellaneous materials | A small Phillips or flat-blade screwdriver, depending upon the type of screws used in your PC.                 |

| Operating system        | MS-DOS or PC-DOS (version 3.0 or higher).                                                                      |

### 2.1.2 Cabling

The TMS34020 SDB20 provides a DB9 video output connector (P4). Its pinout is shown in Section A.2, *Video Output Connector Pinouts*. Some monitors may require a 9-pin to 15-pin connector adapter. If so, see your PC operator's manual for video connector pinouts and see Section A.2, *Video Output Connector Pinouts* of this manual.

### 2.2 Installing the SDB20

This section contains all the information for installing the SDB20. The only tool required for installation is a Phillips or small flat-blade screwdriver for removing the PC cover, removing the slot mounting bracket, and installing the SDB20.

The installation process consists of the following steps:

- **Step 1:** Determining your system configuration (subsection 2.2.1).

- **Step 2:** Preparing the SDB20 for installation (subsection 2.2.2).

- **Step 3:** SDB20 installation (subsection 2.2.3).

### 2.2.1 Determining Your System Configuration

The SDB20 can be installed in an 8-bit or 16-bit slot. Your choice should be based on the following considerations:

- 1) If you have a 16-bit VGA or EGA board installed, install the SDB20 into 16-bit slot.

- 2) If you have an 8-bit VGA or EGA board installed, install the SDB20 into either an 8-bit or 16-bit slot.

- If you have a CGA or MDA board installed, install the SDB20 into either an 8-bit or 16-bit slot.

Accompanying the SDB20 is a diskette labeled *SDB20 Installation Diskette*. On this diskette are two utility programs that you need for installing the SDB20.

- □ The first utility is named *survey*, it checks for conflicts between the SDB20 I/O address and interrupt settings and the other boards that are installed in your PC.

- The second utility is named *tigaset*. This utility has many uses; for the purposes of this installation, it installs the TIGA software and sets up the TIGA environment.

Some peripheral hardware installed in your PC may conflict with the SDB20 bus assignments. To avoid potential problems, do the following to survey your PC environment:

Step 1: Insert the Installation Diskette into your floppy drive A.

Step 2: Execute the *survey* program by entering A: survey

After a short pause, the utility displays a message similar to this:

Ready for SDB20 at I/O Address 230 using Interrupt IRQ15. This is the default setting for the I/O address. This is the default setting for the interrupt.

The default location for the I/O address is 0x230; the default setting for the interrupt is IRQ15.

If there is a potential conflict, the message will indicate the steps that you must take to resolve the problem. See subsection 2.2.2.1, *How to Reconfigure Your SDB20*, for details.

### 2.2.2 Preparing the SDB20 for Installation

Once the PC environment is determined, be sure that the SDB20's SW1 I/O register and SW2 interrupt switches are set correctly to identify the following information:

- Switch **SW1** identifies the **I/O address space** that the SDB20 will use for communicating with the PC.

- Switch **SW2** identifies **the interrupt** that the SDB20 will use for host interrupt requests.

### 2.2.2.1 How to Reconfigure Your SDB20

Your SDB20 communicates with the host computer by means of 16 consecutive, 8-bit wide I/O address locations and a hardware interrupt. Your SDB20 is factory preconfigured to respond at address 230h and hardware interrupt 15.

If these locations are occupied by another add-in peripheral, such as a local area network (LAN) card, an address conflict occurs because two hardware components cannot occupy the same address location. The *survey* utility detects potential conflicts and warns you that relocation is necessary. To resolve the conflict, relocate either your SDB20 or the offending hardware to a new location.

### Note:

If you are reconfiguring an existing TIGA environment, go to subsection 2.2.3, *Procedures for Installing the SDB20 Into Your PC*, on page 2-6, for instructions on installing the SDB20. After installing the board, go to Section 2.3, *Installing and Running TIGA Setup Utilities*, for instructions on running *tigaset*. Choose the Modify Existing TIGA Settings option, then choose the Update TIGA option.

The I/O address and host interrupt can be changed from the factory preset by setting SW1 and SW2 to an alternative location. The following steps show how this is done:

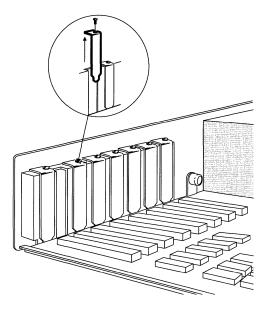

Do not touch the SDB20 before discharging any static electricity from your body. You could possibly damage SDB20 circuitry. Ground yourself by touching the PC's power supply (usually a large silver or black box in the rear of the computer case).

With the SDB20 board removed from your PC, locate the switch that you wish to change. The right side of each switch is labeled with an arrow: the arrow indicates the ON position. A switch in the ON position programs a 0 for that address bit.

□ To reconfigure the address range from 230h to another address, set SW1 to an alternate address listed in Table 2–2.

Table 2–2. SW1 I/O Space Settings

|                  | SW1-4 | SW1-3 | SW1-2 | SW1-1 | Addreess |

|------------------|-------|-------|-------|-------|----------|

|                  | ON    | ON    | ON    | ON    | 0200     |

|                  | ON    | ON    | ON    | OFF   | 0210     |

|                  | ON    | ON    | OFF   | ON    | 0220     |

| default settings | ON    | ON    | OFF   | OFF   | 0230     |

|                  | ON    | OFF   | ON    | ON    | 0240     |

|                  | ON    | OFF   | ON    | OFF   | 0250     |

|                  | ON    | OFF   | OFF   | ON    | 0260     |

|                  | ON    | OFF   | OFF   | OFF   | 0270     |

|                  | OFF   | ON    | ON    | ON    | 0280     |

|                  | OFF   | ON    | ON    | OFF   | 0290     |

|                  | OFF   | ON    | OFF   | ON    | 02A0     |

|                  | OFF   | ON    | OFF   | OFF   | 02B0     |

|                  | OFF   | OFF   | ON    | ON    | 02C0     |

|                  | OFF   | OFF   | ON    | OFF   | 02D0     |

|                  | OFF   | OFF   | OFF   | ON    | 02E0     |

|                  | OFF   | OFF   | OFF   | OFF   | 02F0     |

To **reconfigure the host interrupt** from IRQ15 to another interrupt location, set SW2 to an alternate location listed in Table 2–3.

SW2 Multiple Settings Only 1 switch element in SW2 should be set at a time. Multiple switch settings can cause unreliable operation or possible damage to your PC system.

### Table 2–3. SW2 Interrupt Settings

| Switches | Interrupt Line | Use       |

|----------|----------------|-----------|

| SW2-1    | IRQ3           | available |

| SW2–2    | IRQ5           | available |

| SW2–3    | IRQ9           | available |

| SW2-4    | IRQ10          | available |

| SW2–5    | IRQ11          | available |

| SW2–6    | IRQ12          | available |

| SW2-7    | IRQ14          | reserved  |

| SW2-8    | IRQ15          | available |

### 2.2.3 Procedures for Installing the SDB20 Into Your PC

To install the SDB20, do the following:

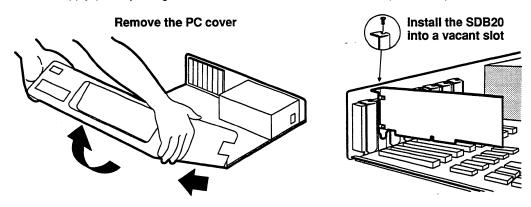

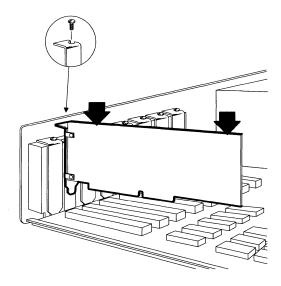

**Step 1:** Remove the cover from your PC by following the instructions contained in your PC's operator manual. Typically, this entails removing the screws from the back of your PC and sliding the cover off as shown in Figure 2–1.

Figure 2–1. Removing the PC Cover

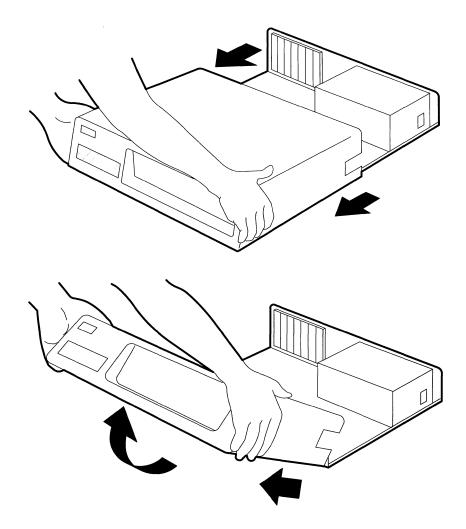

- **Step 2:** Remove the mounting bracket from an unused 8-bit or 16-bit slot (see Figure 2–2) and save the screw for reinstallation.

- □ If you are using only one display monitor with your system, find an open slot. You may want to relocate the VGA board to a different bus slot to accommodate this configuration.

- □ If you are using two monitors on your system, one for the SDB20 and the other for a primary display, refer to Section 2.4, *Setting Up a Dual Monitor System.*

**Step 3:** Touch the PC's power supply case (usually a large silver or black box in the rear of the computer case) to discharge any static electricity on your body.

Do not touch the SDB20 before discharging any static electricity from your body. You could possibly damage SDB20 circuitry. Ground yourself by touching the PC's power supply (usually a large silver or black box in the rear of the computer case).

- Step 4: Remove the SDB20 from its protective bag.

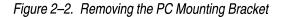

- **Step 5:** Install the SDB20 in the selected slot (see Figure 2–3); press firmly and evenly on the top edge of the card so that it seats all the way into the slot connectors.

### Figure 2–3. Installing the SDB20

Do not force the SDB20 into the slot. Avoid touching any board component while installing the board.

- Step 6: Tighten down the mounting bracket with the screw saved in Step 2.

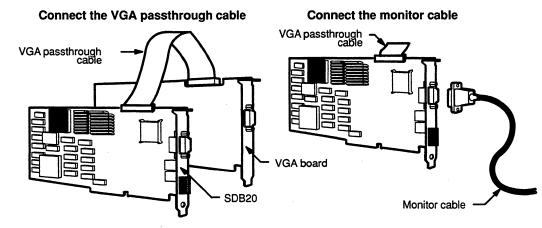

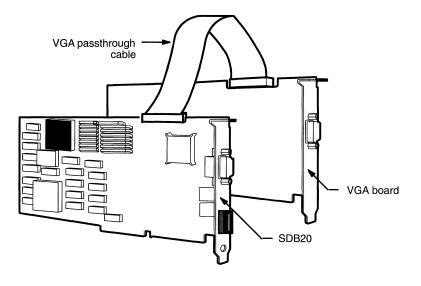

- **Step 7:** Connect a VGA passthrough cable to your feature connector as shown in Figure 2–4.

### Figure 2–4. Connecting the VGA Passthrough Cable

### Note:

Some monitors may require a 9-pin to 15-pin connector adapter. See your monitor specifications for video connector pinouts and see Section A.2, *Video Connector Pinouts*.

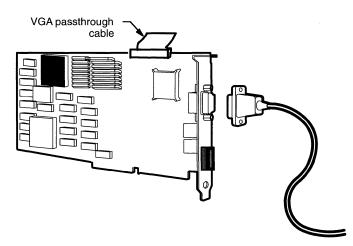

**Step 8:** Connect the monitor cable to the 9-pin connector on the side of the SDB20 as shown in Figure 2–5.

Figure 2–5. Connecting the 9-Pin Monitor Cable

Step 9: Replace the PC cover.

**Step 10:** Write down your monitor's manufacturer and model number in the box below. The SDB20 setup utility requires this information.

| Manufacturer | Model Number |

|--------------|--------------|

|              |              |

|              |              |

Step 11: Turn on power to the PC.

### 2.3 Installing and Running TIGA Setup Utilities

### 2.3.1 Before Running tigaset

The *tigaset* utility requires 450 kilobytes of free memory and 1 MByte of fixed disk space to run. Make sure that you have this amount of memory available, or

- 1) TIGA will be configured incorrectly.

- 2) The system will lock up.

The *tigaset* utility writes data back to the installation diskette during the installation process. To maintain the integrity of the original installation diskette, copy the installation diskette onto a formatted diskette that is not write-protected, and use the copy for installation.

The screen diagrams contained in this user's guide are representative of the screens that you will see when using the *tigaset* utility. The exact information on the screen may vary, depending on the board model that you are using and its memory population.

The installation diskette contains a file called *read.me*. It provides the latest information about TIGA installation and operation.

### 2.3.2 Installing TIGA Software

The SDB20 setup utility, *tigaset*, configures the SDB20 hardware and sets up the TIGA environment. Follow the simple instructions displayed on your screen and go through the following steps:

**Step 1:** Insert the *Installation Diskette* into your floppy drive A.

Step 2: Enter A: and press ENTER .

**Step 3:** Enter tigaset and press **ENTER**.

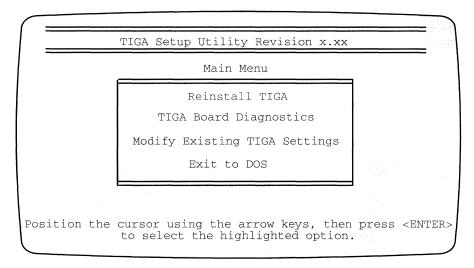

This invokes the *tigaset* utility. It displays a menu similar to that shown in Figure 2–6.

### Note:

If this is a first-time installation, you will see a subset of the options shown in Figure 2–6.

Figure 2–6. The TIGA Setup Utility Screen — Main Menu

#### Note:

Pressing **Esci** aborts the screen that you are working in and returns the main menu.

An explanation of the main menu options follows:

- (Re) Install TIGA presents a series of instructions and options for installing TIGA. For a first-time installation, the screen shows Install TIGA.

- Selects the host I/O base address setting.

- Selects the host memory segment base address.

- Selects the data transfer size: 8 bits or 16 bits.

- Copy TIGA files into the TIGA directory.

- Select TIGA system settings.

- TIGA Board Diagnostics provides you with a set of diagnostic tools to help you locate a suspected hardware failure.

- Modify Existing TIGA Settings allows you to:

- Change TIGA system settings.

- Update TIGA.

- Exit to DOS exits *tigaset* and returns to DOS.

Step 4: Use the arrow keys to select (Re)Install TIGA.

The screen shown in Figure 2–7 prompts for the host I/O base address set by the SDB20's SW1. The highlight and check mark identify the current I/O base address: the factory preconfigured default is  $0 \times 230$ . See subsection 2.2.2.1, *How to Reconfigure Your SDB20*, on page 2-4, for details about reconfiguring SW1.

Figure 2–7. TIGA Installation Screen — Host I/O Base Address

| TIGA Board Installation                                                                          |                    |

|--------------------------------------------------------------------------------------------------|--------------------|

| the HOST IO BASE ADDRESSes for<br>lighted was either used on a pre<br>or it is the default value | evious installatio |

| Select an IO Base Address                                                                        |                    |

| 0x210<br>0x220                                                                                   |                    |

| • • • • • • • • • • • • • • • • • • •                                                            |                    |

| 0x240<br>0x250                                                                                   |                    |

|                                                                                                  |                    |

Step 5: Do one of the following:

- 1) If you agree with the current selection, press 1.

- If you want to select another option, use the or keys to make your selection and press .

#### Note:

The TIGA Board NOT AT THIS ADDRESS message will appear if you attempt to select an I/O base address different from that where the SDB20 is installed. Choose another address or use the address selected by *tigaset*.

The screen shown in Figure 2–8 prompts for an SDB20 host memory segment base address where all memory-access cycles will be directed. The highlight and check mark identify the current host memory base address: the default is D000 to D7FF.

Figure 2–8. TIGA Installation Screen — Host Memory Segment Base Address

|                                                                                    | TIGA Board Installation                                                                                                      |                  |

|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------|

| The one hi                                                                         | the HOST SEGMENT BASE ADDRESSes for<br>ghlighted was either used on a previ<br>a HOST memory area the program feel           | ous installation |

|                                                                                    | Select a Host Segment Base Address                                                                                           |                  |

|                                                                                    | <ul> <li>✓ C800 to CFFF</li> <li>✓ D000 to D7FF</li> <li>D800 to DFFF</li> <li>E000 to E7FF</li> <li>E800 to EFFF</li> </ul> |                  |

| <e< td=""><td>SC&gt; = Previous Screen <enter> = Se</enter></td><td>lect</td></e<> | SC> = Previous Screen <enter> = Se</enter>                                                                                   | lect             |

Step 6: Do one of the following:

- 1) If you agree with the current selection, press  $\blacksquare$ .

- 2) If you want to select another option, use the 💽 or 💽 key to make your selection and press 🖃 .

VGA BIOS is typically located at C000–C7FF, and some PCs load shadow RAM at E000–EFFF. To avoid address conflict, determine your system's available addresses prior to selecting a different host memory segment address.

The screen shown in Figure 2–9 prompts for a data transfer width: 8-bit or 16-bit. The highlight and check mark identify the current data transfer size.

Figure 2–9. TIGA Installation Screen — Data Transfer Size

|                | TIGA Board Installation                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| If the TIGA bo | transfers data at either 8 or 16 bits.<br>ard is installed in an 8 bit slot, selec<br>ard is installed in a 16 bit slot, selec | and a second of a second of the second of th |

|                | Select TIGA Board bit transfer width                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                | 8<br>16                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                | SC> = Previous Screen <enter> = Select</enter>                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

Step 7: Do one of the following:

- □ If the SDB20 is installed in an 8-bit slot, press □ . This will allow 8-bit transfers only.

#### Note:

For proper operation, the transfer size selected for the SDB20 must be the same size as that of the system's EGA/VGA card, as well as any other memory-mapped device sharing the same 128K host memory page.

The screen shown in Figure 2–10 prompts for a directory where the TIGA software should be installed.

Figure 2–10. TIGA Installation Screen — Default Directory

If you wish to install TIGA in a different location, follow the instructions on the screen to change the destination.

**Step 8:** Press if you agree with the default location C: \TIGA.

The software now asks for permission to append your *AUTOEXEC.BAT* file. NO TAG shows your choices.

| The following commands must be run to set up the TIGA environmen<br>They are normally installed into the AUTOEXEC.BAT file.<br>PATH C:\TIGA; %PATH%<br>SET TIGA=-mC:\TIGA -lC:\TIGA -i0x60<br>TIGACD<br>Where should this information be placed?<br>C:\TIGA\TIGAAUTO.BAT<br>C:\AUTOEXEC.BAT |     | TIGA INSTALLATION                                  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------------------------|--|

| TIGACD<br>Where should this information be placed?<br>C:\TIGA\TIGAAUTO.BAT                                                                                                                                                                                                                  | The | y are normally installed into the AUTOEXEC.BAT fil |  |

| C:\TIGA\TIGAAUTO.BAT                                                                                                                                                                                                                                                                        |     |                                                    |  |

|                                                                                                                                                                                                                                                                                             |     | C:\TIGA\TIGAAUTO.BAT                               |  |

These instructions execute a series of commands to your PC when you power up or reboot your system.

If you decide not to modify your *AUTOEXEC.BAT* file, *tigaset* will place these commands into a file called *tigaauto.bat*, which is located in your TIGA directory. You must manually input these lines into your *AUTOEXEC.BAT* file after the installation is completed.

Next, *tigaset* asks whether you are using a single monitor or dual monitor setup (Figure 2–12).

| Monitor Configuration                              | Selection |  |

|----------------------------------------------------|-----------|--|

| Install as Single Monito<br>Install as Dual Monito | or system |  |

| Install as Dual Monito                             | rsystem   |  |

If you have separate monitors attached to the VGA and the TIGA board and you do not want VGA passthrough images to show on your secondary monitor, select the dual monitor option. Otherwise, choose the single monitor option.

# Note:

The VGA passthrough cable must be connected between your VGA and the TIGA board if you are using a single monitor.

- **Step 9:** Use the arrow keys and press it to select one of the following options:

- □ Install as Single Monitor system if you do want VGA passthrough images to show on your TIGA board's monitor.

- Install as Dual Monitor system if you are using separate monitors attached to your VGA and the TIGA board, and you do not want VGA passthrough images to show on your TIGA board's monitor.

You will be presented with a list of monitors (Figure 2–13).

# Figure 2–13. TIGA Installation Screen — Defined Monitors

**Step 10:** Select the model number of the monitor that you are using. If the monitor you are using is not on this list, press it accept the default selection.

Note:

See Section 2.5, *Customizing Monitor Timing*, for instructions on how to customize your monitor timing.

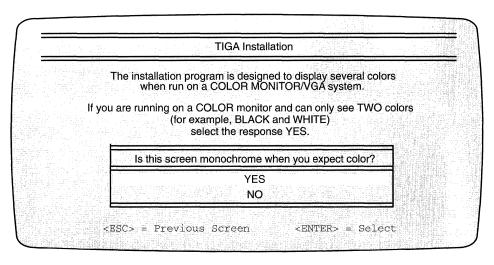

Figure 2–14. TIGA Installation Screen — Determining the Monitor Color

Some VGA boards require that the monitor be connected to the VGA board at boot-up. If the monitor is not connected, the system may boot the VGA in the monochrome mode. This problem may occur in single monitor systems. Step 11 and Step 12 help you to determine whether this condition exists and provide a suggested remedy.

- **Step 11:** Use the arrow keys and press it to select one of the following options:

- ❑ YES if the screen in Figure 2–15 is monochrome and you are expecting the screen to be in color.

- □ NO if you are working on a monochrome system or your screen is already in color.

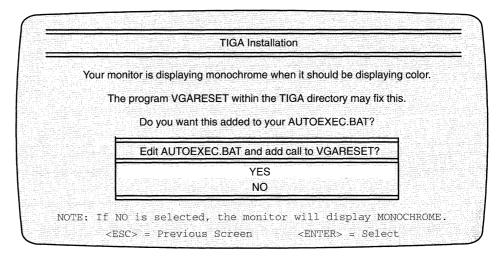

Figure 2–15. TIGA Installation Screen — Correcting the Monochrome Display Problem

- **Step 12:** Select one of the following to remedy the monochrome display problem:

- □ YES adds the VGARESET line to your AUTOEXEC.BAT file.

- NO means that you will have to execute VGARESET to return your VGA to the color mode each time that you reboot your PC.

The *tigaset* utility presents you with a review menu.

- □ If you need to change any setting, return to the main menu and make your change.

- □ If not, select Use Settings and proceed to the screen shown in Figure 2–16.

This screen displays the number of colors, display pages, and resolutions supported by the TIGA board. A check mark identifies the current display mode. You can also access this screen from the DOS command line by entering ti-gamode at the prompt, and pressing  $\boxed{-}$ .

Figure 2–16. Typical Change TIGA Display Mode Screen

| Availa | ble video mode         | es: 15, De:                           | fault Mode | : 1024x768, | 256 colors         | s, 1 Pag      |

|--------|------------------------|---------------------------------------|------------|-------------|--------------------|---------------|

|        | Resolution             | Colors                                | Pages      | Pixel Size  | Туре               |               |

|        | ✓ 1024x 768            | 256                                   | 1          | 8           | Palette            |               |

|        | 1024x 768<br>640 x 480 | 16<br>256                             | 1          | 4           | Palette<br>Palette |               |

|        | 640 x 480              | 256<br>16                             | 1          | o<br>4      | Palette            |               |

|        | 1024x 768              | 16                                    | 2          | 4           | Palette            |               |

|        | 640 x 480              | 256                                   | 2          | 8           | Palette            | a na si sa si |

|        | 640 x 480              | 16                                    | 2          | 4           | Palette            |               |

|        |                        | · · · · · · · · · · · · · · · · · · · |            |             |                    |               |

Step 13: Do one of the following:

- Use the arrow keys to select the desired display mode; press

.

The *tigaset* utility presents you with the SDB20 information screen (Figure 2–17). It lists configuration parameters: processor type, memory population, I/O address, and hardware interrupt.

Figure 2–17. TIGA Information Screen for the SDB20

| Processor: | TMS34020        | Speed:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 32MHz  |

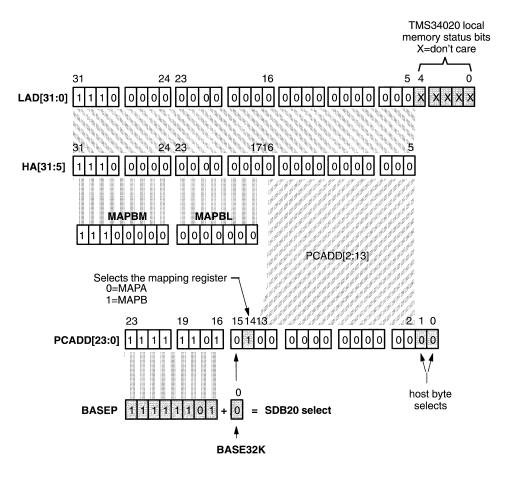

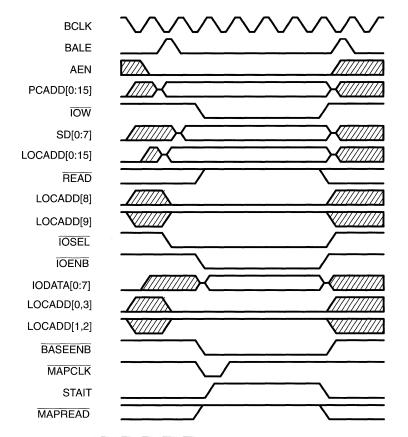

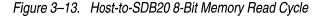

|------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|