# Memory Management Applications Handbook

**Contributors**

VLSI Logic Applications Engineering VLSI Marketing Department

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes in the devices or the device specifications identified in this publication without notice. TI advises its customers to obtain the latest version of device specifications to verify, before placing orders, that the information being relied upon by the customer is current.

TI warrants performance of its semiconductor products to current specifications in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems such testing necessary to support this warranty. Unless mandated by government requirements, specific testing of all parameters of each device is not necessarily performed.

In the absence of written agreement to the contrary, TI assumes no liability for TI applications assistance, customer's product design, or infringement of patents or copyrights of third parties by or arising from use of semiconductor devices described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor devices might be or are used.

Copyright © 1987, Texas Instruments Incorporated

## **Contents**

| Sectio | n e e e e e e e e e e e e e e e e e e e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Page                                                                                                                                                                                                          |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1-1                                                                                                                                                                                                           |

| 2      | Memory Timing Controllers 2.1 Introduction 2.2 Memory Timing Controller Using the 'ALS2967 and 'ALS2968 2.2.1 Functional Description 2.2.2 Typical Implementation 2.2.3 Timing Controller Details 2.2.4 Summary 2.2.5 ABEL <sup>TM</sup> and CUPL <sup>TM</sup> Files 2.3 Memory Timing Controller Using the 'ALS6301 and 'ALS6302 2.3.1 Functional Description 2.3.2 Typical Implementation 2.3.3 Timing Controller Details 2.3.4 Refresh Timer Details 2.3.5 Programmable Logic Designs 2.3.6 Summary 2.3.7 ABEL <sup>TM</sup> Files 2.3.8 CUPL <sup>TM</sup> Files 2.4 THCT4502B/MC68000L8 Interface 2.4.1 Introduction 2.4.2 ALE-to-Clock Relationship 2.4.3 DRAM Refresh Time 2.4.4 DRAM Precharge Time 2.4.5 Row Address Setup and Hold Time 2.4.6 Data Valid to Write Enable Setup Time 2.4.7 Read Access Time from CAS 2.4.8 Other Considerations 2.4.9 Summary 2.5 Programmer Manufacturer Addresses 2.5.1 Programmer Manufacturer Addresses | 2-1<br>2-1<br>2-1<br>2-1<br>2-4<br>2-5<br>2-8<br>2-14<br>2-17<br>2-18<br>2-21<br>2-22<br>2-23<br>2-23<br>2-34<br>2-36<br>2-37<br>2-37<br>2-38<br>2-39<br>2-39<br>2-39<br>2-39<br>2-39<br>2-39<br>2-39<br>2-39 |

| 3      | Cache Memory Systems  3.1 Introduction  3.2 Memory Systems with Cache  3.3 Cache Memory Systems Using 'ACT2151 and 'ACT2152  3.3.1 Set-Associative Cache Address Matching  3.3.2 Cycle Time Improvement  3.3.3 Cache Memory Configuration  3.3.4 Summary  3.4 Article Reprints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3-1<br>3-2<br>3-3<br>3-3<br>3-3<br>3-5<br>3-8<br>3-8                                                                                                                                                          |

ABEL is a trademark of DATA I/O CUPL is a trademark of Personal CAD Systems, Inc.

| Secti | on                                                                | Page |

|-------|-------------------------------------------------------------------|------|

| 4     | Error Detection and Correction (EDAC)                             | 4-1  |

|       | 4.1 Use of an Error Detection and Correction (EDAC) Device        | 4-1  |

|       | 4.1.1 Introduction                                                | 4-1  |

|       | 4.1.2 Error Types and Sources in Dynamic Memories                 | 4-1  |

|       | 4.1.3 Solutions to Boost System Reliability                       | 4-1  |

|       | 4.1.4 EDAC Operation                                              | 4-2  |

|       | 4.1.5 Texas Instruments EDAC Family                               | 4-5  |

|       | 4.1.6 Summary                                                     | 4-7  |

|       | 4.2 Error Detection and Correction Using 'ALS632B, 'ALS633,       |      |

|       | 'ALS634A, and 'ALS635                                             | 4-8  |

|       | 4.2.1 Introduction                                                | 4-8  |

|       | 4.2.2 Operational Description                                     | 4-10 |

| 5     | First-In First-Out Memories (FIFO)                                | 5-1  |

|       | 5.1 High-Speed Bus Coupling Considerations—FIFO Memory Buffers    | 5-1  |

|       | 5.1.1 Introduction                                                | 5-1  |

|       | 5.1.2 Toggle Fall-Through Architecture                            | 5-1  |

|       | 5.1.3 Zero Fall-Through Architecture                              | 5-2  |

|       | 5.1.4 Buffering Design Considerations                             | 5-3  |

|       | 5.1.5 Synchronization Design Considerations                       | 5-4  |

|       | 5.1.6 Summary                                                     | 5-5  |

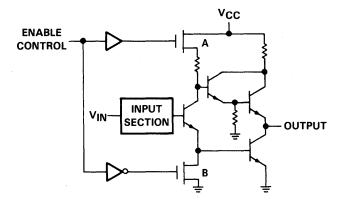

| 6     | BiCMOS                                                            | 6-1  |

|       | 6.1 BiCMOS Memory Drivers Boost Performance                       | 6-1  |

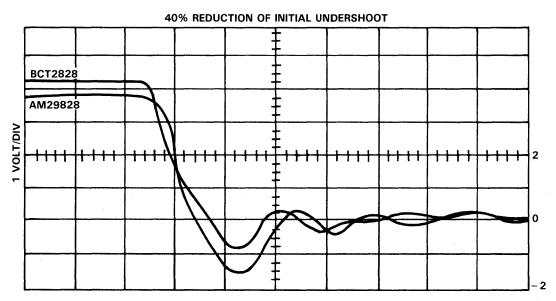

|       | 6.1.1 Reducing Undershoot Problems                                | 6-1  |

|       | 6.1.2 BiCMOS Drivers Match MOS Memory Needs                       | 6-2  |

|       | 6.1.3 BiCMOS Lowers Power by 50% or More                          | 6-2  |

|       | 6.1.4 Less Undershoot Means Higher Reliability                    | 6-3  |

|       | 6.1.5 How Do I Get More Information                               | 6-3  |

|       | 6.2 BiCMOS Bus Interface                                          | 6-4  |

|       | 6.2.1 Abstract                                                    | 6-4  |

|       | 6.2.2 Introduction                                                | 6-4  |

|       | 6.2.3 Reduction of Supply Current Demand Without                  |      |

|       | Sacrificing Performance                                           | 6-4  |

|       | 6.2.4 Combinational Bipolar and CMOS Optimal Process Solution     |      |

|       | 6.2.5 Variety of Functional Options in Two Package Configurations | 6-8  |

|       | 6.2.6 Summary                                                     | 6-8  |

# List of Illustrations

| Figure | Title                                                   | Page |

|--------|---------------------------------------------------------|------|

| 2-1    | 'ALS2967, 'ALS2968 Functional Block Diagram             | 2-2  |

| 2-2    | 'ALS2967, 'ALS2968 Timing Controller Interface          | 2-4  |

| 2-3    | 8086 Access Cycle                                       | 2-5  |

| 2-4    | Refresh/Access Cycle                                    | 2-6  |

| 2-5    | 'ALS2967, 'ALS2968 Memory Timing Controller Flow Chart  | 2-7  |

| 2-6    | Refresh/Memory Timing Controller                        | 2-8  |

| 2-7    | 'ALS6301, 'ALS6302 Functional Block Diagram             | 2-15 |

| 2-8    | 'ALS6301, 'ALS6302 Timing Controller Interface          | 2-17 |

| 2-9    | 68000 Access Cycle                                      | 2-18 |

| 2-10   | Refresh/Access Cycle                                    | 2-19 |

| 2-11   | 'ALS6301, 'ALS6302 Memory Timing Controller Flow Chart  | 2-20 |

| 2-12   | Refresh/Memory Timing Controller                        | 2-21 |

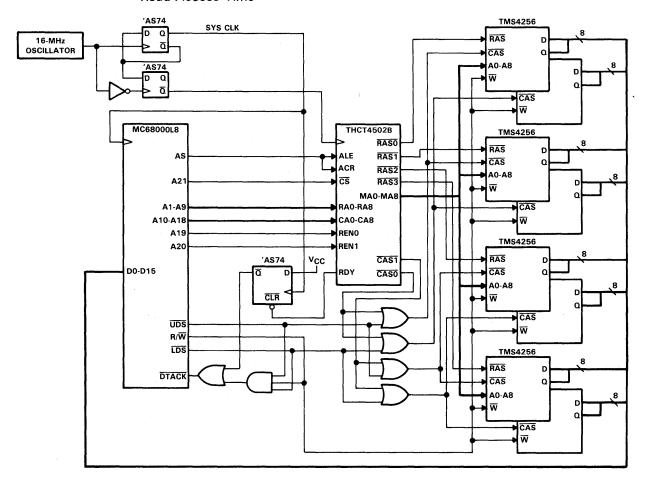

| 2-13   | THCT4502B/MC68000L8 Interface Block Diagram             | 2-34 |

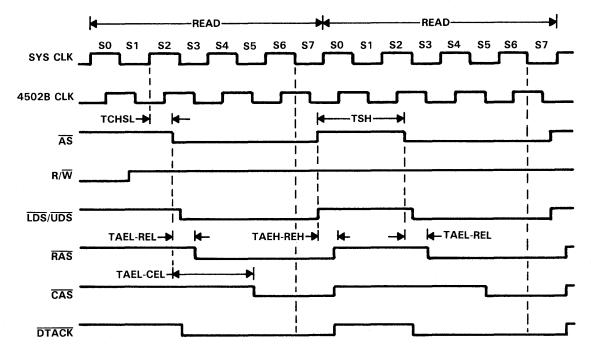

| 2-14   | THCT4502B/MC68000L8 Read Cycle Timing Diagram           | 2-35 |

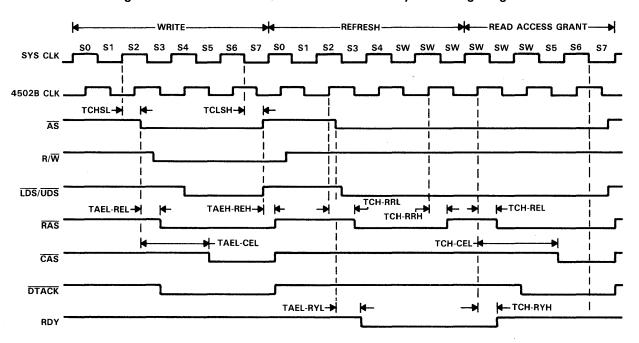

| 2-15   | THCT4502B/MC68000L8 Write Access, Refresh,              |      |

|        | and Read Access Timing Diagram                          | 2-35 |

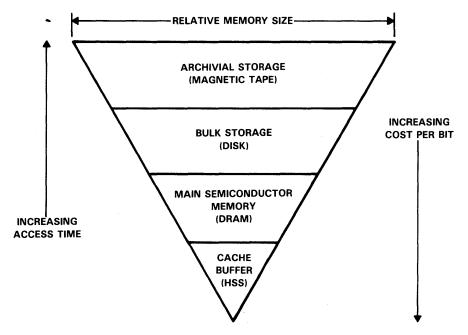

| 3-1    | Memory Size vs Access Time and Cost Per Bit             | 3-1  |

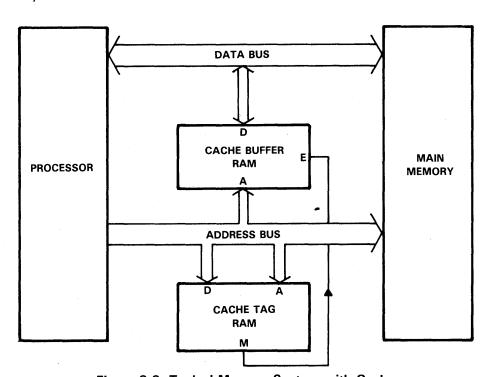

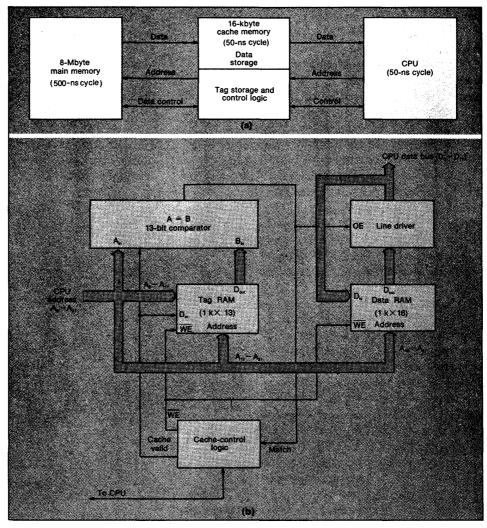

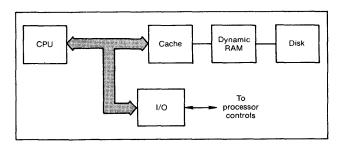

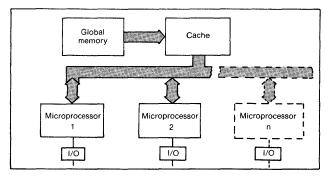

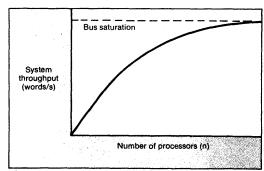

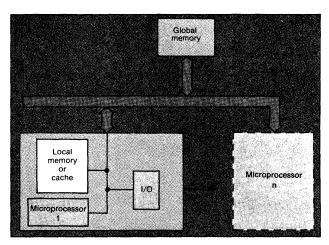

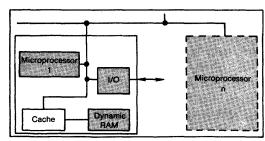

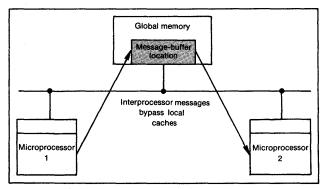

| 3-2    | Typical Memory System with Cache                        | 3-2  |

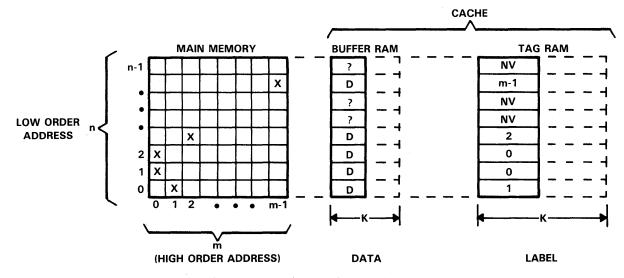

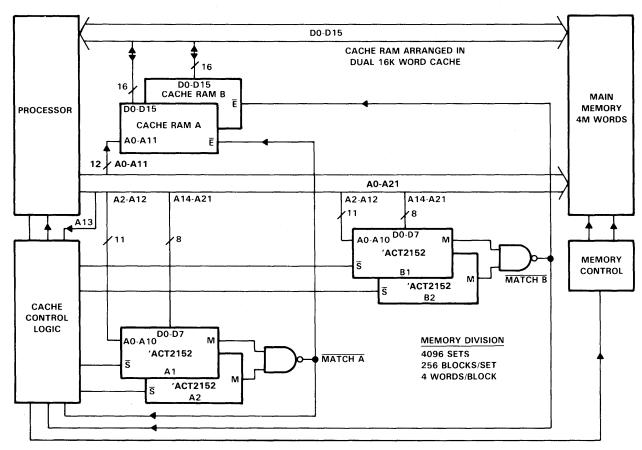

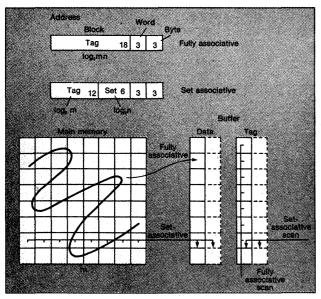

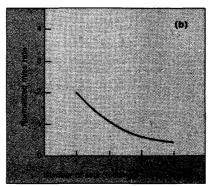

| 3-3    | Set-Associative Cache Address Matching                  | 3-3  |

| 3-4    | Cache Memory Configuration (Block Size = 1)             | 3-5  |

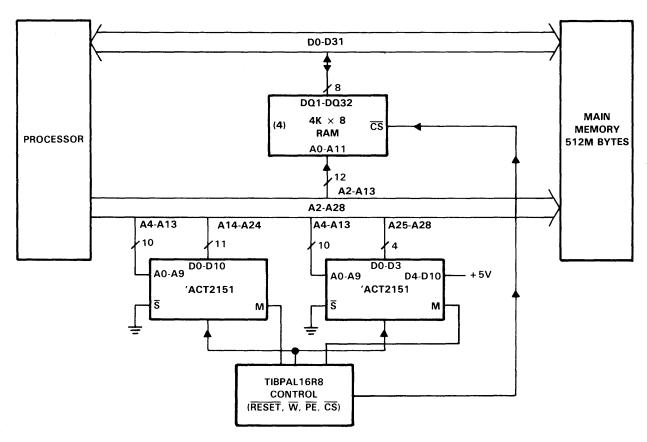

| 3-5    | Cache Memory Configuration (Block Size = 4)             | 3-6  |

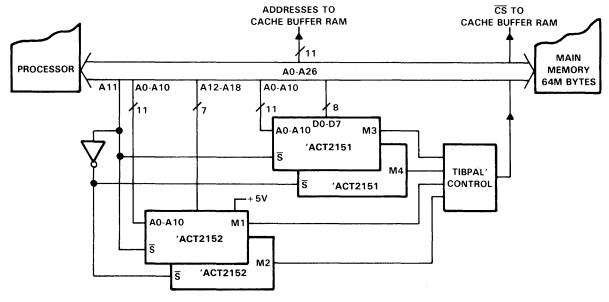

| 3-6    | Cache Memory Configuration, Dual Cache (K = 2)          | 3-7  |

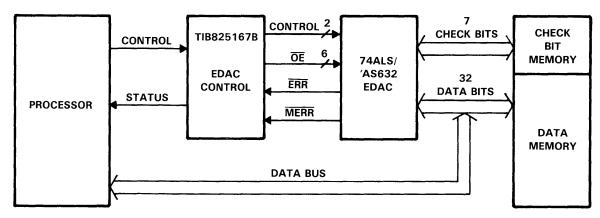

| 4-1    | Typical 'AS632 System                                   | 4-3  |

| 4-2    | Memory Management System Using Scrubbing                | 4-5  |

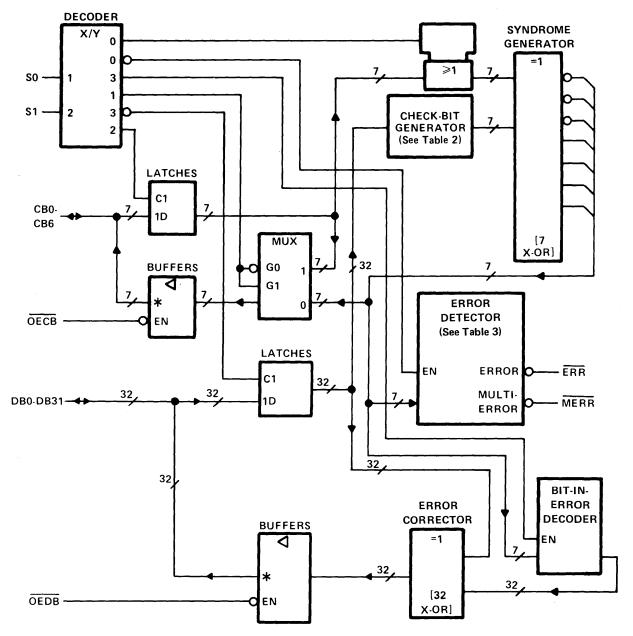

| 4-3    | 'AS632 Logic Diagram                                    | 4-6  |

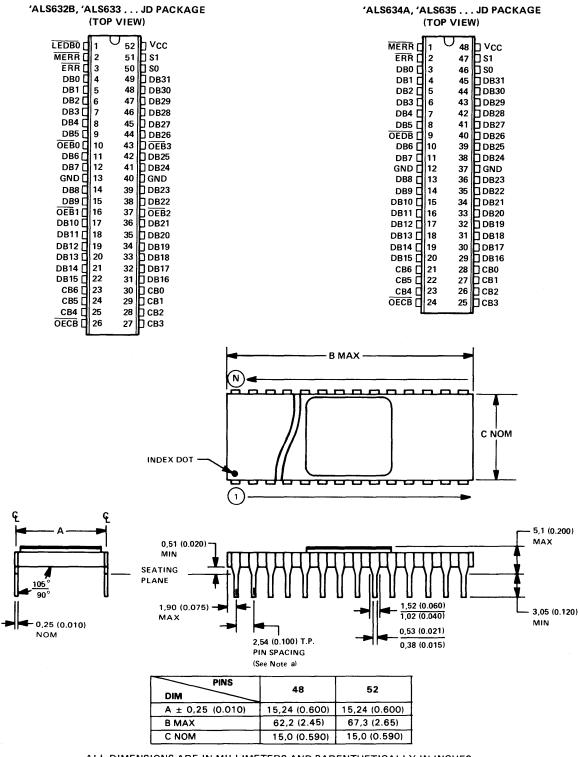

| 4-4    | Mechanical Data                                         | 4-9  |

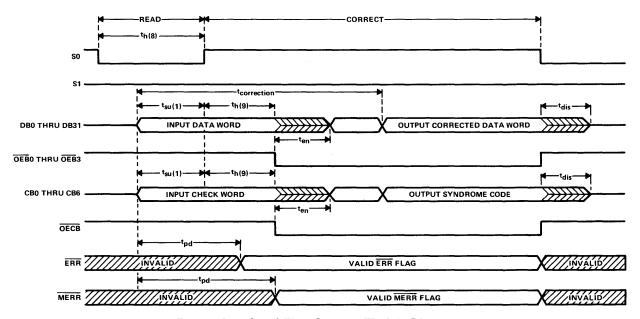

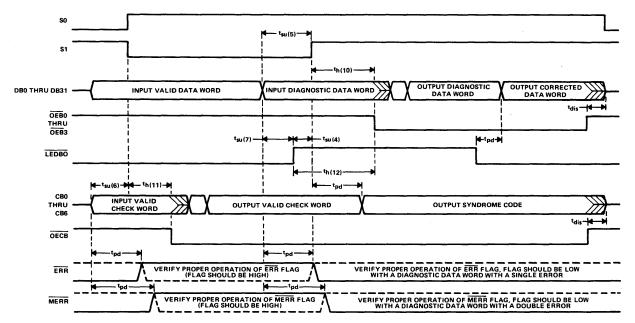

| 4-5    | Read-Flag-Correct Timing Diagram                        | 4-10 |

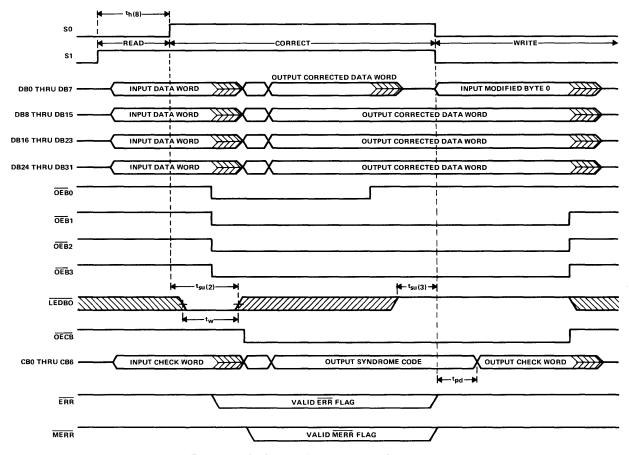

| 4-6    | Read-Modify-Write Operation                             | 4-12 |

| 4-7    | Diagnostic Mode Timing Diagram                          | 4-13 |

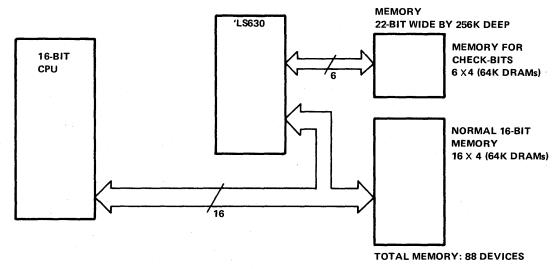

| 4-8    | 16-Bit System Using Conventional 16-Bit EDAC            | 4-13 |

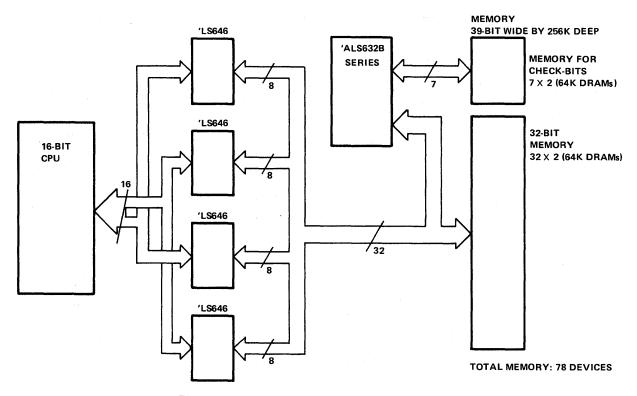

| 4-9    | 16-Bit System Using 32-Bit EDAC                         | 4-14 |

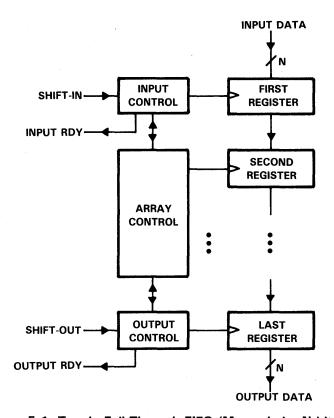

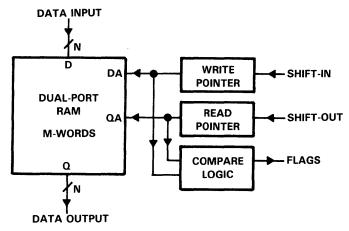

| 5-1    | Toggle Fall-Through FIFO (M Words by N Bits)            | 5-2  |

| 5-2    | Zero Fall-Through FIFO (M Words by N Bits)              | 5-3  |

| 5-3    | Buffering Application                                   | 5-3  |

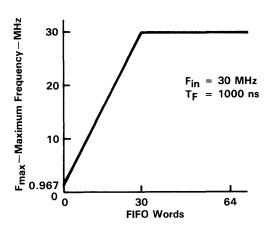

| 5-4    | Throughput Curve for 64-Word, 30-MHz FIFO               | 5-5  |

| 6-1    | Effect of On-Chip Series Output Resistors               |      |

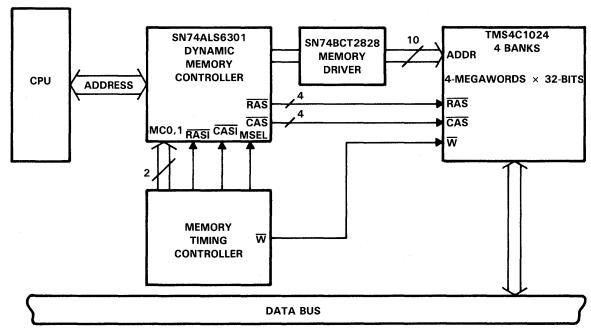

| 6-2    | 4M-Word X 32-Bit Memory System                          | 6-2  |

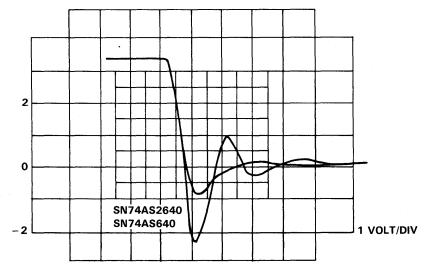

| 6-3    | Initial Undershoot Comparison of SN74BCT2828 vs AM29828 | 6-3  |

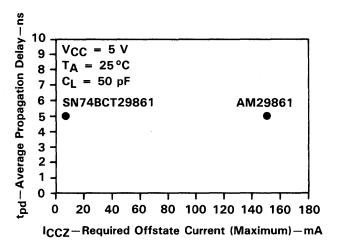

| 6-4    | SN74BCT29861 and AM29861 Required Off-State Current vs  | ۰.   |

| C E    | Average Propagation Delay                               | 6-5  |

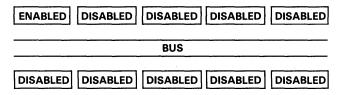

| 6-5    | Bus Network                                             | 6-6  |

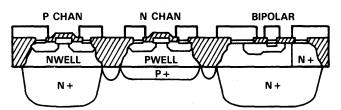

| 6-6    | BiCMOS Process                                          | 6-6  |

| 6-7    | BiCMOS Three-State Gate Schematic                       | 6-7  |

# List of Tables

| Table | Title                                                     | Page |

|-------|-----------------------------------------------------------|------|

| 2-1   | 'ALS2967, 'ALS2968 Mode Control Function Table            | 2-3  |

| 2-2   | 'ALS6301, 'ALS6302 Mode Control Function Table            | 2-16 |

| 2-3   | Refresh Clock Frequency Input Pin Strap Configuration     | 2-36 |

| 4-1   | Chip Densities vs Soft Error Rates                        | 4-1  |

| 4-2   | System MTBF Increases with an EDAC                        | 4-2  |

| 4-3   | Hamming Code Parity Algorithm                             | 4-2  |

| 4-4   | SN74AS632 Syndrome Decoding                               | 4-4  |

| 4-5   | Texas Instruments Error Detection and Correction Devices  | 4-7  |

| 4-6   | Pin Function for 'ALS632B, 'ALS633, 'ALS634A, and 'ALS635 | 4-8  |

| 5-1   | FIFO Applications                                         | 5-1  |

| 6-1   | SN74BCT29861/AM29861 ICC Comparison                       | 6-5  |

## 1 Introduction

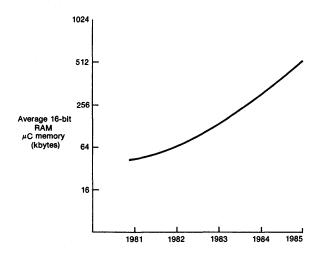

Texas Instruments (TI) is pleased to make available this collection of application reports and application briefs on several of our new single-chip memory management products. Designed to help you attain your systems goals, these products can help you achieve minimal memory access times for maximum system throughput. While there may be other alternatives available, few can provide speed enhancement while reducing both design effort and component cost. Many of the new memory management products from TI accelerate the performance of VME, VERSAbus®, MULTIBUS®, and PC Bus architectures even further.

Single chip solutions to complex functions such as cache tag control, DRAM address multiplexing and refresh, and soft error correction are all part of the TI memory management family of products. This family offers many benefits such as greater ease of use, improved system performance, and a reduction in cost over discrete logic options.

This document contains information on each of the new memory management products from TI. For example, the cache tag application report details how you can store frequently accessed data and instructions in a few high speed SRAMs and then "tag" them by using the TI family of CMOS cache controllers to achieve high speed system throughput.

High-performance DRAM controllers are discussed in "Memory Timing Controllers Using the "ALS2967/"ALS2968 & "ALS6301/"ALS6302." The TI SN74ALS6301 DRAM controller incorporates address multiplexing and refresh circuitry in a single chip. The wide address capability and IMPACT<sup>TM</sup> speed performance of the SN74ALS6301 allow it to support the newer 1M-bit DRAM chips.

Maintaining data integrity in larger memory arrays can be accomplished using error detection and correction circuits. The application report on the TI SN74AS632 32-bit Error Detection and Correction (EDAC) circuit describes how the 'AS632 can detect both hard and soft errors in memory arrays and guarantee system reliability by correcting these errors while avoiding processor wait states.

Every memory management function from TI uses a "universal architecture" design to allow for easy compatibility with any microprocessor, keeping design effort to a minimum. These single-chip solutions are designed to be especially easy to use with Motorola VME and VERSAbus® architectures as well as Intel MULTIBUS®, and PC Bus based systems.

IMPACT is a trademark of Texas Instruments VERSAbus is a registered trademark of Motorola MULTIBUS is a registered trademark of Intel Corporation

## 2 Memory Timing Controllers

#### 2.1 Introduction

As processor and memory speeds increase, so do dynamic memory controller requirements. Typical processor speeds today range from 8 to 10 MHz. This increase in processor speed has created a need for faster memories, as well as faster memory timing controllers. The 'ALS2967, 'ALS2968, 'ALS6301, and 'ALS6302 are Memory Timing Controllers that are designed to meet the need of high performance memory systems.

In addition to offering better system performance, a faster memory controller typically allows the designer to use slower-rated dynamic random access memories (DRAMs). This results in significant cost savings because of the large number of DRAMs required. In other words, a faster dynamic memory controller can reduce overall dynamic memory costs.

The 'ALS2967, 'ALS2968, 'ALS6301, and 'ALS6302 feature address multiplexing, memory bank selection, and an address latch for systems which multiplex both data and address on the same bus. A row counter is provided for normal refresh operations. Column and bank counters are available for systems which use memory scrubbing.

This Section describes the functional operation of the 'ALS2967, 'ALS2968, 'ALS6301, and 'ALS6302 and shows how they can be interfaced to a typical processor. For illustration purposes, a simple timing controller generated from programmable logic is used to interface both the 'ALS2967 and the 'ALS6301 to the microprocessor. The 'ALS2967 is interfaced with an Intel 8086 and the 'ALS6301 is interfaced with a Motorola 68000.

This Section also presents a circuit configuration which interfaces the MC68000 to DRAM memory using the THCT4502B dynamic RAM Controller. The memory array is organized as 4 banks of 256K memory (TMS4256/4257) providing a 1M byte deep system architecture.

#### 2.2 Memory Timing Controllers Using the SN54/74ALS2967, SN54/74ALS2968

#### 2.2.1 Functional Description

The 'ALS2967 and 'ALS2968 are capable of controlling 16K, 64K, and 256K DRAMs. The two devices typically operate in a read/write or a refresh mode. During normal read/write operations, the row and column addresses are multiplexed to the DRAM, and the corresponding  $\overline{RAS}$  and  $\overline{CAS}$  signals are activated to strobe the addresses into memory. In the refresh mode, the two counters cycle through the refresh addresses. If memory scrubbing is not being implemented, only the row counter is used. When memory scrubbing is being performed, both the row and column counters are used to perform read-modify-write cycles using an error detection and correction circuit such as the 'ALS632A. In this mode, all  $\overline{RAS}$  outputs will be active (low) while only one  $\overline{CAS}$  output is active at a time.

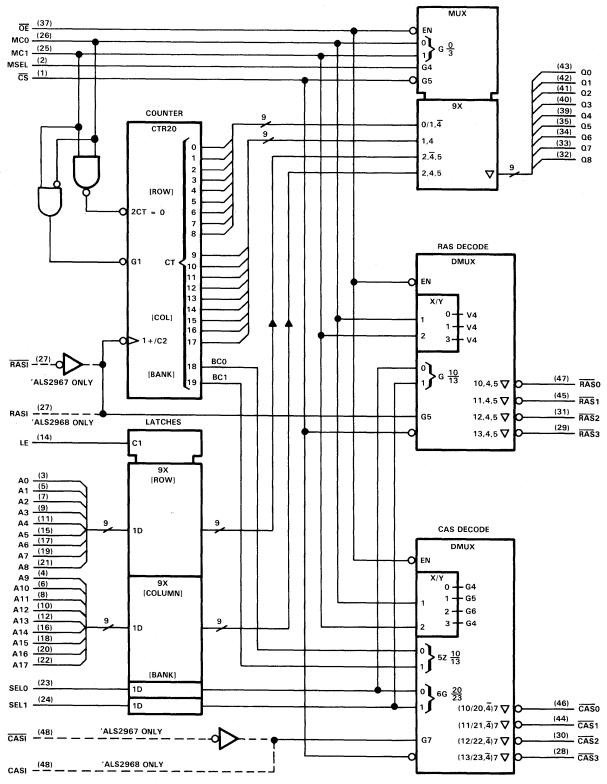

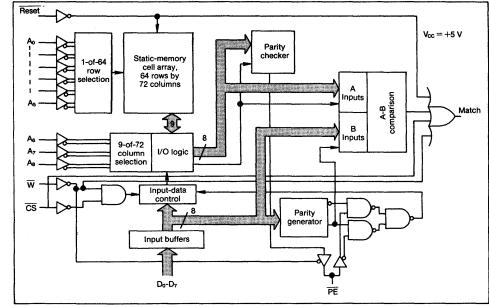

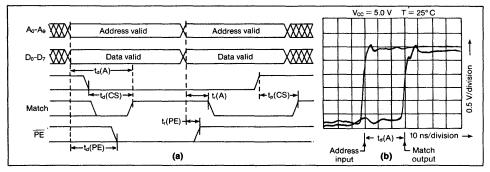

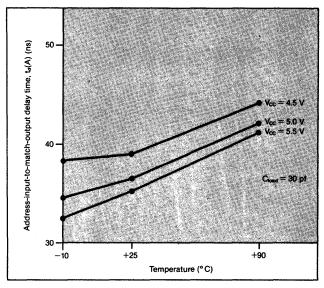

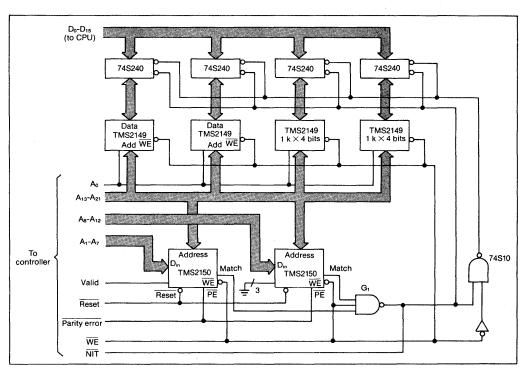

Two device types are offered to help simplify interfacing with the system dynamic timing controller. The 'ALS2967 offers active-low row address strobe input (RASI) and column address strobe input (CASI) signals, while the 'ALS2968 offers active-high RASI and CASI inputs. Figure 2-1 is a functional block diagram of the two devices.

Figure 2-1. 'ALS2967, 'ALS2968 Functional Block Diagram

Table 2-1 describes the four operating modes of the 'ALS2967 and 'ALS2968 as controlled by inputs MCO and MC1. During normal read/write operations, the row and column addresses are multiplexed to the DRAM. When MSEL is high, the column address is selected; when MSEL is low, the row address is selected. The corresponding RASn and CASn output signals strobe the addresses into the selected memory bank or banks. A single 'ALS2967 or 'ALS2968 can control as many as four banks of 256K memory. Additional banks of memory can be controlled by using additional 'ALS2967 or 'ALS2968 devices and decoding each chip select (CS) input.

Table 2-1. 'ALS2967, 'ALS2968 Mode-Control Function Table

| SIGNAL |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MC1    | мсо        | MODE SELECTED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| L      | L          | Refresh without Scrubbing. Refresh cycles are performed using the row counter to generate the addresses. In this mode, all four RAS outputs are active while the four CAS outputs remain high.                                                                                                                                                                                                                                                                                                                                   |

| L      | Н          | Refresh with Scrubbing/Initialize. Refresh cycles are performed using both the row and column counters to generate the addresses. MSEL selects the row or the column counter. All four RAS outputs go low in response to RASI ('ALS2967) or RASI ('ALS2968), while only one CASn output goes low in response to CASI ('ALS2967) or CASI ('ALS2968). The bank counter keeps track of which CAS output goes active. This mode can also be used during system power-up so that the memory can be written with a known data pattern. |

| Н      | <b>L</b> . | Read/Write. This mode is used to perform read/write cycles. Both the row and column addresses are multiplexed to the address output lines using MSEL. SELO and SEL1 are decoded to determine which RASn and CASn outputs will be active.                                                                                                                                                                                                                                                                                         |

| Н      | Н          | Clear Refresh Counters. This mode clears the three refresh counters (row, column, and bank) on the inactive transition of RASI ('ALS2967) or RASI ('ALS2968), putting them at the beginning of the refresh sequence. In this mode, all four RAS outputs are driven low after the active edge of RASI ('ALS2967) or RASI ('ALS2968) so that DRAM wake-up cycles can also be performed.                                                                                                                                            |

In systems where addresses and data are both multiplexed onto a single bus, the 'ALS2967 and 'ALS2968 use latches (row, column and bank) to hold the address information. The 20 input latches are transparent when the latch enable input (LE) is high; the input data is latched whenever LE goes low. For systems in which the processor has separate address and data buses, LE may be tied high.

The two 9-bit counters in the 'ALS2967 and 'ALS2968 support 128, 256, and 512 line refresh operations. Transparent, burst, synchronous, or asynchronous refresh modes are all possible as determined by the memory timing controller. The refresh counters are advanced on the low-to-high transition of  $\overline{RASI}$  on the 'ALS2967, and on the high-to-low transition of RASI on the 'ALS2968. This is true in either refresh mode. In the clear refresh counter mode, the refresh counters (row, column, and bank) can be reset to zero on the low-to-high transition of  $\overline{RASI}$  on the 'ALS2967 or on the high-to-low transition of RASI on the 'ALS2968.

#### 2.2.2 Typical Implementation

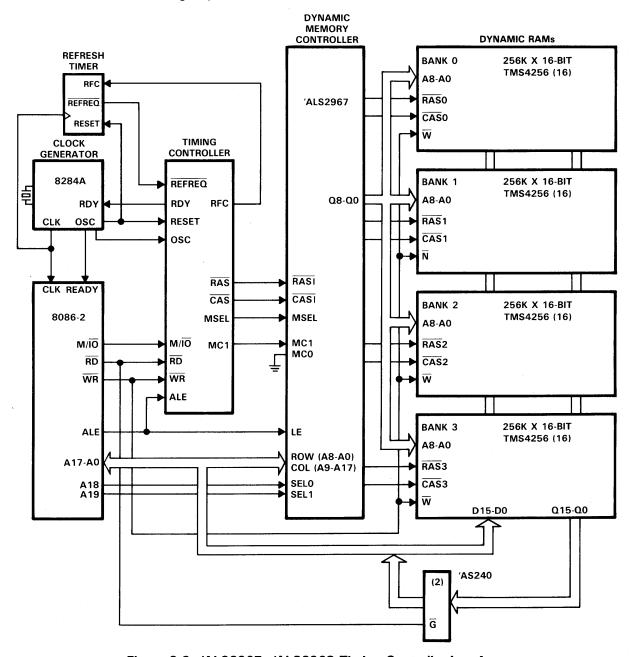

Figure 2-2 shows a system interface using the 'ALS2967 between an Intel 8086 and four banks of 256K DRAMs. Addresses A18 and A19 are used to select one of the four memory banks. Since members of the 8086 processor family multiplex both data and addresses onto the same data bus, input latches on the 'ALS2967 must be used to store the row, column, and bank information. The ALE signal from the 8086 can be directly connected to the latch enable (LE) input on the 'ALS2967.

The RASI, CASI, MSEL and mode control (MCO, MC1) inputs on the 'ALS2967 must be generated by the memory timing controller. The memory timing controller functions as an arbitrator between refresh cycles and 8086 access cycles. It also guarantees that timing requirements of the DRAM will be met.

Figure 2-2. 'ALS2967, 'ALS2968 Timing Controller Interface

#### 2.2.3 Timing Controller Details

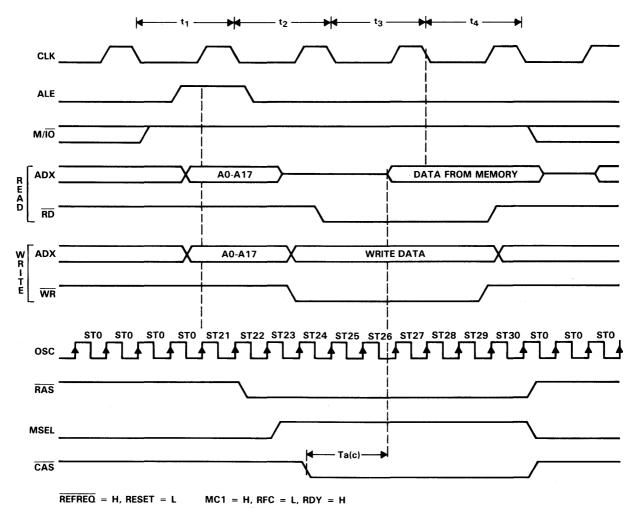

Figure 2-3 is a timing diagram for a typical 8086 access cycle. The 'ALS2967 control signals required to execute the access cycle are also shown. Control signals for the 'ALS2967 are referenced from the OSC output of the 8284A clock generator. The timing controller in this example is generated from a state machine referenced from the OSC output of the 8284A. In critical timing situations, it may be necessary to tightly control the phase relationship of the system clock to the OSC signal. This can be accomplished by using a phase lock loop or similar method to generate the OSC signal.

Figure 2-3. 8086 Access Cycle

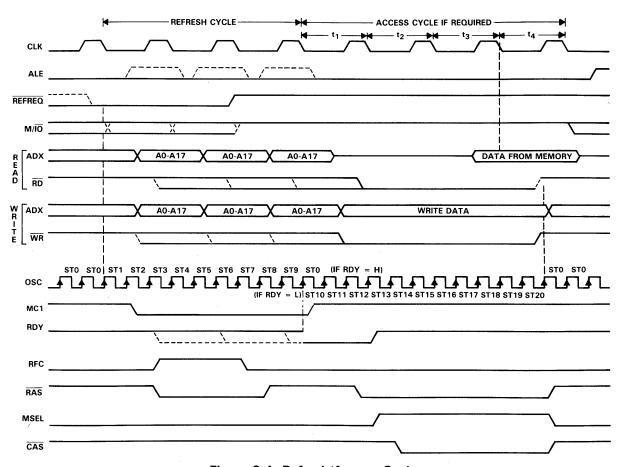

In this example, refresh requests ( $\overline{REFREQ}$ ) are generated every 122 clock cycles. The timing controller will perform the refresh cycle ( $\overline{RAS}$  only) immediately if the processor is not in the middle of an access cycle. If the controller is in the middle of an access cycle, the refresh cycle will be delayed until the access cycle is complete. If the controller is asked to perform an access cycle during a refresh, the controller will place the processor in a wait state (RDY low) until the refresh is complete. Figure 2-4 shows the timing diagram for a refresh/access cycle as explained above. To implement memory scrubbing, the controller must execute a read/write cycle during the refresh cycle and then place the 'ALS2967 in the memory scrubbing mode (This example executes  $\overline{RAS}$  only refresh).

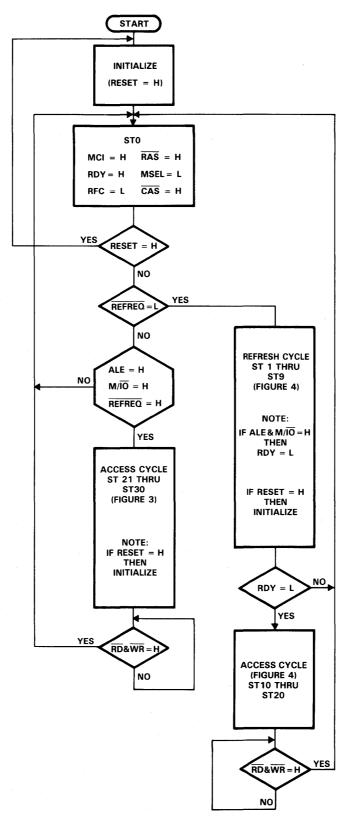

Figure 2-5 is a flow chart for the timing controller. ABEL<sup>TM</sup> and CUPL<sup>TM</sup> software was used to generate fuse maps from the present state of the inputs and present condition of the state machine. These fuse maps were then used in programming the field programmable logic devices. The files used to generate the fuse maps have been included for reference at the end of this application note.

Figure 2-4. Refresh/Access Cycle

Figure 2-5. 'ALS2967, 'ALS2968 Memory Timing Controller Flow Chart

Figure 2-6 shows the actual circuit implementation of the refresh and memory timing controller. The refresh timer signals the controller whenever it is time to execute a refresh cycle. As required by memory, every row (256 on the TMS4256 DRAM) must be addressed every 4 ms. This implies that one row should be refreshed at least once every 15.6  $\mu$ s. With an 8-MHz system clock, the refresh timer should use approximately a division factor of 122. This results in a refresh request every 15.3  $\mu$ s. The refresh complete input (RFC) is used to signal the refresh timer that the refresh has been completed. It is important that the timer not stop so that the 4-ms memory requirement is maintained.

Figure 2-6. Refresh/Memory Timing Controller

The TIBPAL16R8 circuit shown in Figure 2-6 is used to generate the refresh request signal every 122 clock cycles. The refresh request signal (active low) will remain active (low) until a refresh complete (RFC) signal is received from the timing controller. During a system reset, the refresh request output is set to a high-logic level. When using different clock rates or memory sizes, the division circuit in the refresh timer should be adjusted accordingly.

The TIB82S167B field programmable sequencer shown in Figure 2-6 is configured as a state machine to execute the flow chart shown in Figure 2-5. In cases with different system timings, the CUPL<sup>TM</sup> file can be modified to fit the processor requirements. In addition, a slight modification to the file will allow an 'ALS2968 to be used instead of an 'ALS2967.

A preprogrammed sample of the refresh and timing controllers shown in Figure 2-6 can be obtained by calling PAL/PROM Applications, 214/995-2980.

#### 2.2.4 Summary

The 'ALS2967 and 'ALS2968, coupled with programmable logic, offer the system designer a solution to high-speed dynamic memory requirements. Programmable logic allows the designer to tailor the timing controller to a selected processor and memory. In many cases, the generation of a high-speed timing controller from programmable logic will allow the designer to use slower DRAMs without affecting system speed. This results in lower total system cost because of the large number of memory devices used.

#### 2.2.5 ABEL<sup>TM</sup> and CUPL<sup>TM</sup> Files

## 2.2.5.1 ABEL<sup>TM</sup> File

```

module RF TIMER

title 'REFRESH TIMER

R. K. BREUNINGER TEXAS INSTRUMENTS, DALLAS, 08/12/86'

RFT

'P16R8';

DEVICE

"input declarations

" SYSTEM CLOCK (8086)

CLK

pin 1;

pin 2;

RESETS WHEN HIGH

RESET

REFRESH COMPLETE

RFC

pin 3;

" MUST BE TIED LOW

pin 11;

0E

"output declarations

" COUNTER STATES

Q0,Q1,Q2

pin 12,13,14;

pin 15,16,17,18; " COUNTER STATES

Q3,Q4,Q5,Q6

REFRESH REQUEST - ACTIVE LOW

REFREQ_

pin 19;

"intermediate variables

CNT_REF = Q0 & !Q1 & !Q2 & Q3 & Q4 & Q5 & Q6;

= RESET # CNT_REF;

SCLR

count

= [Q6,Q5,Q4,Q3,Q2,Q1,Q0];

C,H,L

= .C., 1, 0;

equations

REFREQ_ := RFC # !CNT_REF & REFREQ_ # RESET;

:= (!Q0 ) & !SCLR;

Q1

:= ( Q1 $ Q0) & !SCLR;

:= ( Q2 $ Q1 & Q0) & !SCLR;

02

:= ( Q3 $ (Q2 & Q1 & Q0)) & !SCLR;

Q3

:= ( Q4 $ (Q3 & Q2 & Q1 & Q0)) & !SCLR;

04

:= ( Q5 $ (Q4 & Q3 & Q2 & Q1 & Q0)) & !SCLR;

Q5

:= !(!Q5 & !Q6 # !Q4 & !Q6 # !Q3 & !Q6

Q6

# !Q0 & !Q6 # !Q2 & !Q6 # !Q1 & !Q6 # SCLR);

([OE,RESET,CLK,RFC] -> [count,REFREQ_])

test_vectors

[0, 1, C, 0] \rightarrow [0, H]

];

@CONST cnt = 1; @REPEAT 121 { [ 0, 0 , C , 0 ] -> [ cnt ,

];

@CONST cnt = cnt + 1;

];

];

@CONST cnt = 1; @REPEAT 20

@CONST cnt = cnt + 1;}

[0, 0, C, 1] \rightarrow [21,

Н

];

[0, 0, C, 0] \rightarrow [22,

Н

];

Н

[0, 0, C, 0] \rightarrow [23,

];

[0, 0, C, 0] \rightarrow [24,

];

```

end RF\_TIMER

#### 2.2.5.2 CUPLTM Source File

```

MTC-S167:

Partno

Name

MTC-S167:

Date

08/13/86;

Revision

03;

BREUNINGER;

Designer

Company

TEXAS INSTRUMENTS;

Assembly

None;

Location

DALLAS, TEXAS;

DYNAMIC TIMING CONTROLER

(FOR ALS2967)

/*************

/* Allowable Target Device Types: TIB82S167B

/***********************

/** Inputs **/

/* OSCILLATOR (8284A)

pin 1 = OSC;

/* REFRESH REQUEST

/* RESET - INITIALIZES WHEN HIGH

pin 2 = REFREQ;

pin 3 = RESET;

/* MEMORY I/O

pin 4 = MIO;

/* READ

pin 5 = RD;

/* WRITE

pin 6 = WR;

/* ADDRESS LATCH ENABLE

pin 7 = ALE;

/* PIN 16 MUST BE TIED LOW

pin 16 = GND;

/** Outputs **/

/* MODE CONTROL

/* MULTIPLEXER SELECT

pin 9 = MC1;

pin 10 = MSEL;

/* COLUMN ADDRESS STROBE

pin 11 = CAS;

/* ROW ADDRESS STOBE

pin 13 = RAS;

/* READY

pin 14 = RDY;

pin 15 = RFC;

/* REFRESH COMPLETE

/** Internal Node Group -

State bits declared as nodes

node [P4_,P3_,P2_,P1_,P0_];

/** Declarations and Intermediate Variable Definitions

Field State = [P4_,P3_,P2_,P1_,P0_];

$define ST0 'b'00000

$define ST1 'b'00001

$define ST2 'b'00010

$define ST3 'b'00011

$define ST4 'b'00100

$define ST5 'b'00101

$define ST6 'b'00110

$define ST7 'b'00111

$define ST8 'b'01000

$define ST9 'b'01001

$define ST10 'b'01010

$define ST11 'b'01011

$define ST12 'b'01100

```

```

$define ST13 'b'01101

$define ST14 'b'01110

$define ST15 'b'01111

$define ST16 'b'10000

$define ST17 'b'10001

$define ST18 'b'10010

$define ST19 'b'10011

$define ST20 'b'10100

$define ST21 'b'10101

$define ST22 'b'10110

$define ST23 'b'10111

$define ST24 'b'11000

$define ST25 'b'11001

$define ST26 'b'11010

$define ST27 'b'11011

$define ST28 'b'11100

$define ST29 'b'11101

$define ST30 'b'11110

$define ST31 'b'11111

/** Logic Equations **/

Sequence State

NEXT STO OUT [MC1_, RDY,!RFC, RAS,!MSEL, CAS];

{Present STO IF RESET

IF !RESET & !REFREQ NEXT ST1;

IF !RESET & REFREQ & ALE & MIO NEXT ST21;

NEXT STO;

DEFAULT

/** REFRESH CYCLE **/

Present ST1 IF ALE & MIO&!RESET NEXT ST2 OUT [!MC1_,!RDY];

NEXT ST2 OUT [!MC1_];

IF !RESET

Present ST2 IF ALE & MIO&!RESET NEXT ST3 OUT [!RDY, RFC,!RAS];

IF !RESET

NEXT ST3 OUT [ RFC,!RAS];

Present ST3 IF ALE & MIO&!RESET NEXT ST4 OUT [!RDY];

NEXT ST4;

IF !RESET

Present ST4 IF ALE & MIO&!RESET NEXT ST5 OUT [!RDY];

IF !RESET

NEXT ST5;

Present ST5 IF ALE & MIO&!RESET NEXT ST6 OUT [!RDY];

IF !RESET

NEXT ST6;

ALE & MIO&!RESET NEXT ST7 OUT [!RDY,!RFC];

Present ST6 IF

NEXT ST7 OUT [!RFC];

IF !RESET

Present ST7 IF ALE & MIO&!RESET NEXT ST8 OUT [!RDY, RAS];

IF !RESET

NEXT ST8 OUT [ RAS];

Present ST8 IF ALE & MIO&!RESET NEXT ST9 OUT [!RDY];

IF !RESET

NEXT ST9;

NEXT STO OUT [ MC1_, RDY,!RFC, RAS,!MSEL, CAS];

Present ST9 IF RDY & !RESET

NEXT STIO OUT [ MCI_];

IF !RDY & !RESET

```

```

/** ACCESS IMMEDIATELY AFTER REFRESH WHEN REQUESTED **/

NEXT ST11;

Present ST10 IF !RESET

Present ST11 IF !RESET

NEXT ST12 OUT [!RAS];

NEXT ST13 OUT [ RDY, MSEL];

Present ST12 IF !RESET

Present ST13 IF !RESET

NEXT ST14 OUT [!CAS];

Present ST14 IF IRESET

NEXT ST15;

Present ST15 IF !RESET

NEXT ST16;

Present ST16 IF !RESET

NEXT ST17;

NEXT ST18;

Present ST17 IF !RESET

Present ST18 IF !RESET

NEXT ST19;

Present ST19 IF !RESET

NEXT ST20;

Present ST20 IF RD & WR & !RESET NEXT ST0 OUT [ MC1_, RDY,!RFC, RAS,!MSEL, CAS];

IF !RESET

NEXT ST20;

/** ACCESS TIMING CYCLE **/

NEXT ST22 OUT [!RAS];

Present ST21 IF !RESET

NEXT ST23 OUT [ MSEL];

Present ST22 IF !RESET

Present ST23 IF !RESET

NEXT ST24 OUT [!CAS];

NEXT ST25;

Present ST24 IF !RESET

NEXT ST26;

Present ST25 IF !RESET

NEXT ST27:

Present ST26 IF !RESET

Present ST27 IF !RESET

NEXT ST28;

NEXT ST29;

Present ST28 IF !RESET

Present ST29 IF !RESET

NEXT ST30;

Present ST30 IF RD & WR & !RESET NEXT ST0 OUT [ MC1_, RDY,!RFC, RAS,!MSEL, CAS];

IF !RESET

NEXT ST30;}

APPEND MC1_.s = RESET;

APPEND RDY.s = RESET;

APPEND RFC.r = RESET;

APPEND RAS.s = RESET;

APPEND MSEL.r= RESET;

APPEND CAS.s = RESET;

APPEND P1_.r = RESET;

APPEND P2_.r = RESET;

APPEND PO .r = RESET;

APPEND P4_.r = RESET;

APPEND P3_.r = RESET;

```

#### 2.2.5.3 CUPLTM Simulation File

/\*ST19\*/ 0

/\*ST20\*/ 0

/\*ST20\*/ 0

С

С

0

0

0

Χ

Χ

Χ

Χ

$X \quad X \quad X$

1

Х

0 0

1

Н

Н

Н

Н

Н

L

L

L

L

Н

Н

Н

Н

L

L

L

```

Partno

MTC-S167:

Name

MTC-S167:

08/13/86;

Date

Revision

03;

Designer

BREUNINGER:

TEXAS INSTRUMENTS;

Company

Assembly

None;

DALLAS, TEXAS;

Location

DYNAMIC TIMING CONTROLLER SIMULATION FILE

(FOR ALS2967)

/* Allowable Target Device Types: TIB82S167B

ORDER:

GND, 73, OSC, 73, RESET, 76, REFREQ, 74, MIO, 73, RD, 72, WR, 72, ALE, 75,

MC1_,%4,MSEL,%3,CAS,%3,RAS,%3,RDY,%3,RFC;

VECTORS:

$msg"REFRESH WITH ACCESS FOLLOWING";

$msg"

----- INPUT -----

-----: OUTPUT -----";

GND OSC RESET REFREQ MIO RD WR ALE MCI MSEL CAS RAS RDY RFC";

$msg"

$msg"

/*RESET*/ 0

С

Н

Х

X X X

Н

L

/* STO*/ 0

C

0

0

Х

X \quad X \quad X

Н

L

Н

Н

Н

L

/* ST1*/ 0

С

0

Χ

0

X X 0

L

Н

Н

L

L

Н

/* ST2*/

С

0

0

Χ

0

ХХ

0

L

L

Н

L

Н

Н

C

/* ST3*/

0

0

Х

0

Х

Х

0

L

L

L

Н

Н

/* ST4*/

0

C

0

Х

1

X X

1

L

L

Н

L

L

Н

С

/* ST5*/

0

0

Х

Χ

X \quad X \quad X

L

Н

L

Н

/* ST6*/

С

Х

Χ

X X X

0

0

L

L

н

L

L

L

/* ST7*/

С

Х

Х

X X X

0

0

Н

Н

L

L

L

L

/* ST8*/

С

Χ

Х

0

0

Х

Х

Х

Н

L

Н

L

L

/* ST9*/

0

С

0

Х

Х

Χ

Х

Х

Н

Н

L

Н

L

L

/*ST10*/

0

C

0

1

Х

Χ

Х

Χ

L

Н

L

H

Н

L

С

Χ

/*ST11*/

0

Х

х х

Х

L

0

Н

Н

L

L

/*ST12*/

С

Х

Χ

х х

Χ

0

0

Н

Н

Н

L

Н

L

/*ST13*/

С

X.

Х

ХХ

Х

0

0

Н

Н

L

L

Н

L

/*ST14*/ 0

С

0

Х

Х

Х

Х

Х

Н

Н

L

L

L

C

/*ST15*/ 0

0

Х

Х

ХХ

Х

Н

Н

L

L

Н

L

/*ST16*/ 0

C

0

Х

Х

X X

Х

Н

Н

L

L

L

/*ST17*/ 0

C

0

Χ

Х

X X X

Н

Н

L

L

Н

L

/*ST18*/ 0

С

0

Х

Х

X X X

Н

Н

L

L

Н

L

```

```

$msq"

$msg"REFRESH WITHOUT ACCESS FOLLOWING";

----- INPUT -----

OUTPUT -

$msg"

GND OSC RESET REFREQ MIO RD WR ALE

RDY RFC":

$msg"

MC1 MSEL CAS RAS

/*RESET*/ 0

Х

Χ

С

1

Х

Х

Х

Н

L

Н

Н

н

L

/* STO*/

0

С

0

0

X

Х

Х

Х

H

L

H

Н

Н

L

/* ST1*/

0

С

0

Х

0

Х

Х

0

L

L

Н

Н

Н

L

ST2*/

0

C

0

Х

0

Х

Х

0

L

L

Н

L

Н

Н

ST3*/

0

C

0

Х

0

Х

Х

0

L

L

Н

L

Н

Н

ST4*

0

C

0

Х

0

Х

Х

0

L

L

Н

L

Н

Н

ST5*

0

C

0

Х

0

Х

Х

0

L

L

Н

L

H

н

/* ST6*/

С

0

Х

0

Х

Χ

0

L

0

L

L

Н

L

Н

C

ST7*/

0

0

Х

0

Х

Х

0

L

L

Н

Н

Н

L

C

Х

Х

Х

ST8*/

0

0

0

0

L

L

Н

Н

Н

L

ST9*/

0

C

0

Х

0

Х

Х

0

Н

Н

Н

Н

L

L

$msq"

$msg"ACCESS TIMING CYCLE ";

OUTPUT ----";

$msg"

----- INPUT

$msg"

GND OSC RESET REFREQ MIO RD WR ALE

MC1 MSEL

CAS RAS

RDY RFC";

/*RESET*/ 0

C

Х

Х

Х

Х

Х

Н

L

Н

Н

Н

L

1

C

Х

Х

/* STO*/

0

1

1

1

Н

Н

Н

L

0

Н

L

C

/*ST21*/

0

0

Х

Х

Х

Х

Х

H

L

Н

L

Н

L

C

Х

/*ST22*

0

Х

Х

Χ

Х

Н

Н

Н

L

H

L

0

Χ

C

Х

Х

Х

Х

L

0

H

Н

L

Н

/*ST23*/

0

L

Х

С

Х

Х

L

/*ST24*/

0

0

Х

Х

Н

Н

L

L

Н

C

0

Х

Х

Х

Х

Х

/*ST25*/

Н

Н

L

L

Н

L

C

Х

Х

Х

Х

Х

Н

Н

Н

/*ST26*/

0

0

L

L

L

C

Х

Х

Х

Х

Х

/*ST27*/

0

0

Н

Н

L

L

Н

L

/*ST28*/

C

Х

Х

Х

0

0

Х

Х

Н

H

L

L

Н

L

/*ST29*/

0

C

0

Х

Х

Х

Х

Х

Н

H

L

L

Н

L

/*ST30*/

n

C

0

Х

Х

0

0

Х

H

Н

L

L

Н

L

/*ST30*/

C

0

Х

Х

1

Х

H

Н

Н

Н

L

n

1

L

```

#### 2.3 Memory Timing Controllers Using the SN54/74ALS6301, SN54/74ALS6302

#### 2.3.1 Functional Description

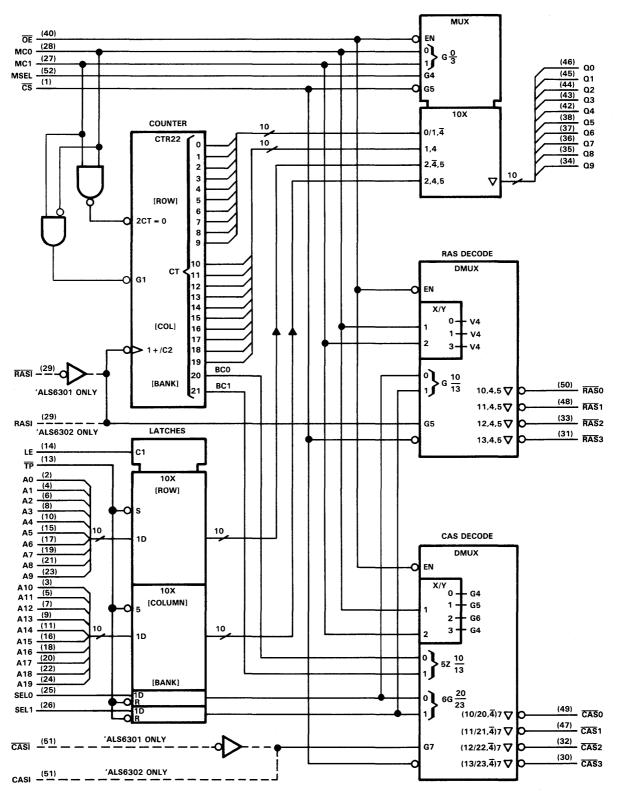

The 'ALS6301 and 'ALS6302 are capable of controlling any DRAM up to 1M. The two devices typically operate in a read/write or a refresh mode. During normal read/write operations, the row and column addresses are multiplexed to the DRAM, and the corresponding  $\overline{RAS}$  and  $\overline{CAS}$  signals are activated to strobe the addresses into memory. In the refresh mode, the two counters cycle through the refresh addresses. If memory scrubbing is not being implemented, only the row counter is used. When memory scrubbing is being performed, both the row and column counters are used to perform read-modify-write cycles using an error detection and correction circuit such as the 'ALS632A. In this mode, all  $\overline{RAS}$  outputs will be active (low) while only one  $\overline{CAS}$  output is active at a time.

Two device types are offered to help simplify interfacing with the system dynamic timing controller. The 'ALS6301 offers active-low row address strobe input (RASI) and column address strobe input (CASI) signals, while the 'ALS6302 offers active-high RASI and CASI inputs. Figure 2-7 is a functional block diagram of the two devices.

Figure 2-7. 'ALS6301, 'ALS6302 Functional Block Diagram

Table 2-2 describes the four operating modes of the 'ALS6301 and 'ALS6302 as controlled by inputs MCO and MC1. During normal read/write operations, the row and column addresses are multiplexed to the DRAM. When MSEL is high, the column address is selected; when MSEL is low, the row address is selected. The corresponding RASn and CASn output signals strobe the addresses into the selected memory bank or banks. A single 'ALS6301 or 'ALS6302 can control as many as four banks of 1M memory. Additional banks of memory can be controlled by using additional 'ALS6301 or 'ALS6302 devices and decoding each chip select (CS) input.

Table 2-2. 'ALS6301, 'ALS6302 Mode-Control Function Table

| SIGNAL |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MC1    | MC0 | MODE SELECTED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| L      | L   | Refresh without Scrubbing. Refresh cycles are performed using the row counter to generate the addresses. In this mode, all four RAS outputs are active while the four CAS outputs remain high.                                                                                                                                                                                                                                                                                                                                   |

| L      | Н   | Refresh with Scrubbing/Initialize. Refresh cycles are performed using both the row and column counters to generate the addresses. MSEL selects the row or the column counter. All four RAS outputs go low in response to RASI ('ALS6301) or RASI ('ALS6302), while only one CASn output goes low in response to CASI ('ALS6301) or CASI ('ALS6302). The bank counter keeps track of which CAS output goes active. This mode can also be used during system power-up so that the memory can be written with a known data pattern. |

| Н      | L   | Read/Write. This mode is used to perform read/write cycles. Both the row and column addresses are multiplexed to the address output lines using MSEL. SELO and SEL1 are decoded to determine which RASn and CASn outputs will be active.                                                                                                                                                                                                                                                                                         |

| Н      | н   | Clear Refresh Counters. This mode clears the three refresh counters (row, column, and bank) on the inactive transition of RASI ('ALS6301) or RASI ('ALS6302), putting them at the beginning of the refresh sequence. In this mode, all four RASI outputs are driven low after the active edge of RASI ('ALS6301) or RASI ('ALS6302) so that DRAM wake-up cycles can also be performed.                                                                                                                                           |

In systems where addresses and data are both multiplexed onto a single bus, the 'ALS6301 and 'ALS6302 use latches (row, column and bank) to hold the address information. The 22 input latches are transparent when the latch enable input (LE) is high; the input data is latched whenever LE goes low. For systems in which the processor has separate address and data buses, LE may be tied high.

The two 10-bit counters in the 'ALS6301 and 'ALS6302 support 128, 256, and 512 line refresh operations. Transparent, burst, synchronous, or asynchronous refresh modes are all possible as determined by the memory timing controller. The refresh counters are advanced on the low-to-high transition of RASI on the 'ALS6301, and on the high-to-low transition of RASI on the 'ALS6302. This is true in either refresh mode. In the clear refresh counter mode, the refresh counters (row, column, and bank) can be reset to zero on the low-to-high transition of RASI on the 'ALS6301 or on the high-to-low transition of RASI on the 'ALS6302.

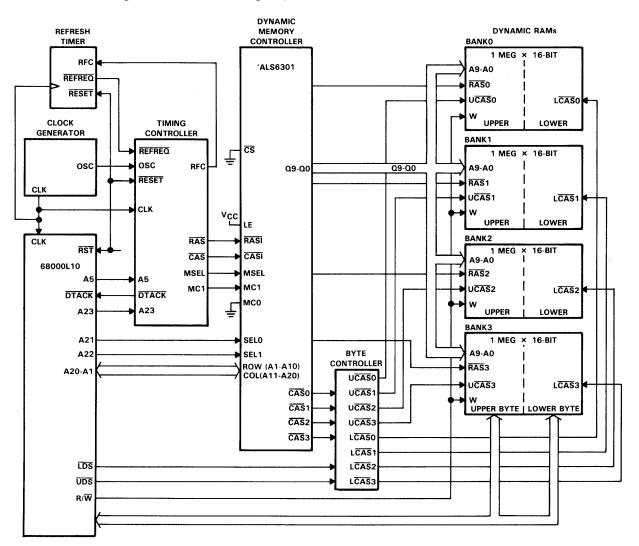

#### 2.3.2 Typical Implementation

Figure 2-8 shows a system interface using the 'ALS6301 between a Motorola 68000L10 and four banks of 1M DRAMs. Addresses A21 and A22 are used to select one of the four memory banks. Since members of the 68000 processor family have separate address and data busses, the input latches on the 'ALS6301 are left transparent by tying the latch enable (LE) input high. The  $\overline{\text{CAS0}}$  thru  $\overline{\text{CAS3}}$  outputs of the 'ALS6301 are fed into the byte controller along with processor signals  $\overline{\text{LDS}}$  and  $\overline{\text{UDS}}$ . The byte controller made from programmable logic allows the processor to determine whether upper, lower or both bytes are accessed.

The RASI, CASI, MSEL and mode control (MCO, MC1) inputs on the 'ALS6301 must be generated by the memory timing controller. The memory timing controller functions as an arbitrator between refresh cycles and 68000L10 access cycles. It also guarantees that timing requirements of the DRAM will be met.

Figure 2-8. 'ALS6301, 'ALS6302 Timing Controller Interface

#### 2.3.3 Timing Controller Details

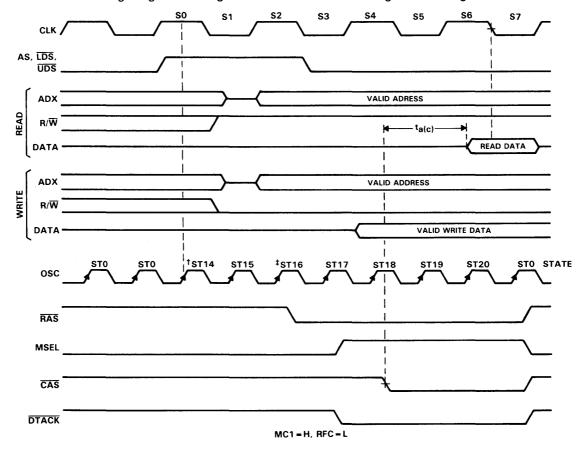

Figure 2-9 is a timing diagram for a typical 68000L10 access cycle. The 'ALS6301 control signals required to execute the access cycle are also shown. Control signals for the 'ALS6301 are referenced from the OSC output of the 8284A clock generator. OSC runs at 2 times the speed of the system clock, that is CLK = 10 MHz and OSC = 20 MHz. By running the timing controller at a higher speed than the system clock, the system performance is improved. A programmable logic sequencer, the TIB82S167B, was programmed for use as the timing controller.

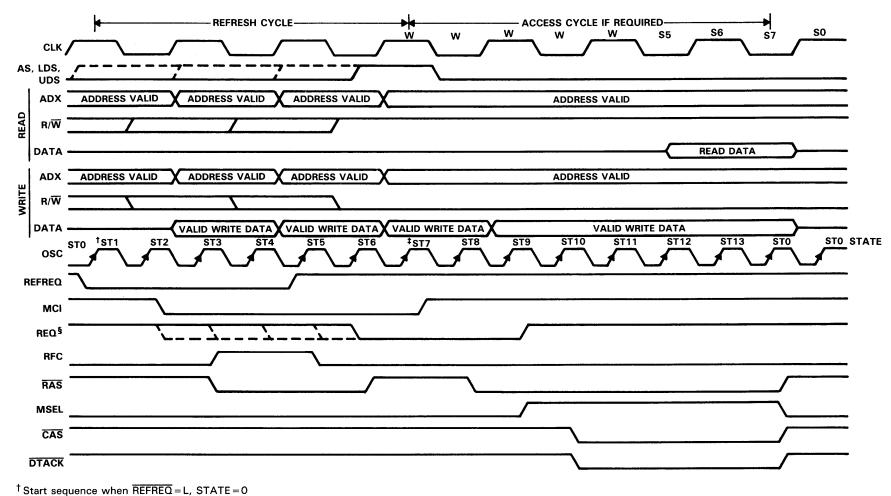

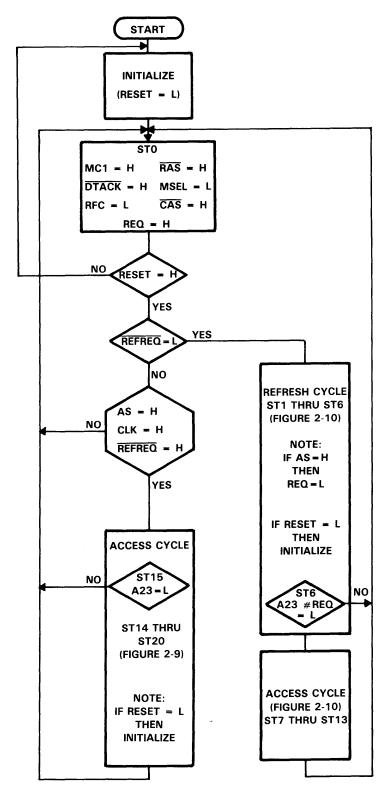

In this example, refresh requests (REFREQ) are generated every 155 clock cycles. The timing controller will perform the refresh cycle (RAS only) immediately if the processor is not in the middle of an access cycle. If the controller is in the middle of an access cycle, the refresh cycle will be delayed until the access cycle is complete. If the controller is asked to perform an access cycle during a refresh, the access cycle will begin immediately after the refresh cycle is completed. Address bit A23 indicates whether the access requested is a memory access (A23 = L) or an I/O access (A23 = H). The timing controller will perform an access cycle only if Address bit A23 is low. Figure 2-10 is a timing diagram of the refresh/access cycle as explained above. To implement memory scrubbing, the controller must execute a read/write cycle during the refresh cycle and then place the 'ALS6301 in the memory scrubbing mode. (This example executes a RAS only refresh.) The flowchart in Figure 2-11 outlines the required functionality of the timing controller. This flowchart was used along with the timing diagrams in Figures 2-9 and 2-10 to design the timing controller.

<sup>†</sup>Start sequence when AS=H, CLK=H, REFREQ=H, STATE=0

Figure 2-9. 68000 Access Cycle

<sup>&</sup>lt;sup>‡</sup>Return to STO if A23 is high

Figure 2-10. Refresh/Access Cycle

<sup>‡</sup>Return to STATE 0 if REQ = H or A23 = H

<sup>§</sup> REQ is internal status register used to store an access request during a refresh cycle. (If AS = H during refresh cycle ST1-ST5)

Figure 2-11. 'ALS6301, 'ALS6302 Memory Timing Controller Flow Chart

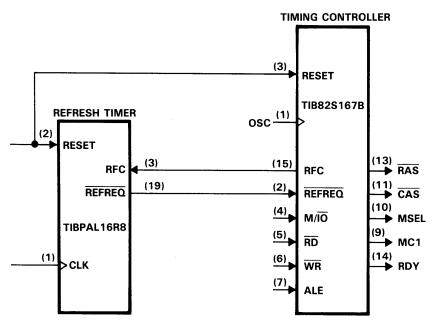

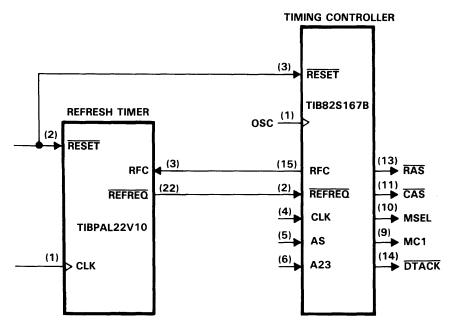

#### 2.3.4 Refresh Timer Details

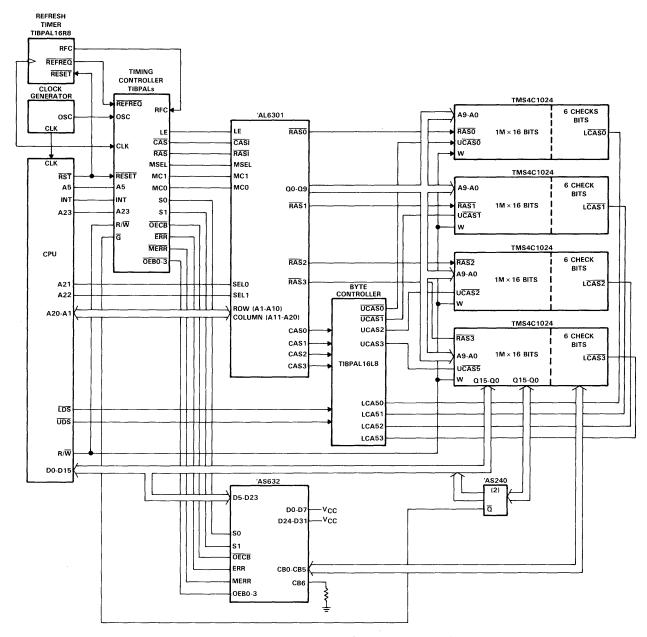

Figure 2-12 shows the actual circuit implementation of the refresh and memory timing controller. The refresh timer signals the controller whenever it is time to execute a refresh cycle. As required by memory, every row (512 on the TMS4C1025 DRAM) must be addressed every 8 ms. This implies that one row should be refreshed at least once every 15.6 ms. With a 10-MHz system clock, the refresh timer should use approximately a division factor of 155. This results in a refresh request every 15.3 ms. The refresh complete input (RFC) is used to signal the refresh timer that the refresh has been completed. It is important that the timer not stop so that the 8 ms memory requirement is maintained.

The TIBPAL22V10 circuit shown in Figure 2-12 is used to generate the refresh request signal every 155 clock cycles. The refresh request signal (active low) will remain active (low) until a refresh complete (RFC) signal is received from the timing controller. During a system reset, the refresh request output is set to a high logic level. When using different clock rates or memory sizes, the division circuit in the refresh timer should be adjusted accordingly.

Figure 2-12. Refresh/Memory Timing Controller

#### 2.3.5 Programmable Logic Designs

As mentioned previously, the timing controller, byte controller, and the refresh timer used in this example are created using programmable logic. ABEL<sup>TM</sup> and CUPL<sup>TM</sup> software packages have been used to reduce equations and generate the fuse maps needed to program these devices. The files used to generate the fuse maps have been included for reference at the end of this application report. Test vectors are included with the device files so software simulation can be performed on the computer. If the proper instruction is provided, the software will attach the test vectors to the end of the fuse map. This allows programming equipment to run a functional test on each device immediately after programming. To help familiarize the reader with these software tools, the timing controller design was done in both ABEL<sup>TM</sup> and CUPL<sup>TM</sup>.

The TIB82S167B field programmable sequencer shown in Figure 2-12 is configured as a state machine to execute the flow chart shown in Figure 2-11. As shown in the flowchart, the timing controller is initialized by taking the reset input low. From the initialization state, state 0, the timing controller can perform either an access or a refresh cycle depending on the signals AS, CLK, and REFREQ. If an access is requested (AS = H) during a refresh cycle, an internal status register, REQ, will flag the request and as soon as the refresh cycle is completed, an access cycle will be started. At the start of an access cycle, the timing controller checks the state of the A23 address bit. If A23 is high, indicating an I/O access, the timing controller terminates the access cycle and returns to state 0.

As seen in Figures 2-9, 2-10, and 2-11, a state, STO-ST30, has been assigned to each clock cycle. The appended ABEL<sup>TM</sup> and CUPL<sup>TM</sup> files can be easily understood by comparing the state equations to the states shown in these figures. Since the only difference between the 'ALS6301 and the 'ALS6302 is that the RASI and the CASI inputs are active-high instead of active-low, a slight modification to the timing controller software file will allow an 'ALS6302 to be used instead of an 'ALS6301. The TIBPAL22V10 refresh timer and the TIBPAL16L8 byte controller designs are straight forward and easily achieved as can be seen in the appended files.

In applications with different systems timings, the ABEL<sup>TM</sup> and CUPL<sup>TM</sup> files can be modified to fit the processor requirements. A preprogrammed sample of the timing controller, refresh timer and byte controller can be obtained by calling LSI/PAL/PROM Applications, 214/995-2980. If a basic understanding of programmable logic is needed, see the Texas Instruments Field Programmable Logic Applications note.

#### 2.3.6 Summary

The 'ALS6301 and 'ALS6302, coupled with programmable logic, offer the system designer a solution to high speed dynamic memory requirements. Programmable logic allows the designer to tailor the timing controller to a selected processor and memory. In many cases, the generation of a high speed timing controller from programmable logic will allow the designer to use slower DRAMs without affecting system speed. This results in lower total system cost because of the large number of memory devices used.

#### 2.3.7 ABEL<sup>TM</sup> Files

#### module DMC S167

module DMC\_S167 flag '-KY','-R2' "leave unused OR terms connected title 'DYNAMIC MEMORY CONTROLLER FOR THE ALS6301 APPLICATION Loren Schiele Texas Instruments, August 15, 1986'

DMC device 'F82S167';

```

" Input pin assignments

```

```

OSC

pin

1;

" OSCILLATOR

REFREQ

pin

" REFRESH REQUEST

2;

RESET

" RESET - INITIALIZES WHEN LOW

pin

3;

CLK

pin

4;

" OSC DIVIDED BY 2

AS

pin

5:

" ADDRESS STROBE

A23

" MOST SIGNIFICANT ADDRESS BIT

pin

6:

GND

" PIN 16 MUST BE TIED LOW

pin

16;

```

#### " Output pin and node assignments

```

MC I

pin

9;

MC1 R

node 25;

" MODE CONTROL

MSEL

pin

10;

MSEL R

node 26;

" MULTIPLEXER SELECT

CAS

pin

11;

CAS R

node 27:

" COLUMN ADDRESS STROBE

RAS_R

RAS

pin

13;

node 28;

" ROW ADDRESS STROBE

" DATA ACKNOWLEDGE

DTACK

pin 14;

DTACK_R node 29;

RFC

pin 15;

RFC_R

node 30;

" REFRESH COMPLETE

```

#### " Internal status and counter nodes

```

P<sub>0</sub>

node 36; P0 R

node 42;

" INTERNAL COUNTER REGISTER

PI

node 35;

P1 R

node 41;

" INTERNAL COUNTER REGISTER

P2

node 34:

P2_R

node 40:

" INTERNAL COUNTER REGISTER

P3

node 33:

P3 R

node 39;

" INTERNAL COUNTER REGISTER

P4

" INTERNAL COUNTER REGISTER

node 32:

P4 R

node 38:

" REFRESH REQUEST STATUS REGISTER

REQ

node 31; REQ R

node 37;

```

" Define Set and Reset inputs to output and status flip-flops

```

MC1_ = [MC1,MC1_R];

MSEL_ = [MSEL,MSEL_R];

CAS_ = [CAS,CAS_R];

RAS_ = [RAS,RAS_R];

DTACK_ = [DTACK,DTACK_R];

RFC_ = [RFC,RFC_R];

REQ_ = [REQ,REQ_R];

```

- "'high' and 'low' are used to set or reset the output and status "registers. Example: MCl\_ := high & RESET; will cause pin 9 to

- " go high on the next clock edge if input pin 3 is high.

```

high = [ 1, 0];

low = [ 0, 1];

Count = [P4,P3,P2,P1,P0]; " STATE REGISTER SET DEFINED

Cnt = [P4,P3,P2,P1,P0]; " STATE REGISTER SET DEFINED

H,L,clk,X = 1, 0, .C., .X.;

```

@page

```

" NEXT

state_diagram Count

State 0:

case

" STATE

!REFREQ

& RESET

: 1;

REFREO

& AS & CLK & RESET :14:

REFREQ

& (!AS # !CLK)

: 0;

endcase;

" REFRESH TIMING CYCLE

State 1:

MC1_ := low & RESET;

REQ_ := low & (AS & RESET);

case

RESET==1

: 2; endcase;

State 2:

RFC_ := high & RESET;

RAS_ := low & RESET;

:= low & (AS & RESET);

REQ_

RESET==1

case

: 3: endcase:

REQ_ := low & (AS & RESET);

State 3:

case

RESET==1

: 4; endcase;

State 4:

RFC_ := low & RESET;

REQ_ := low & (AS & RESET);

RESET==1

case

: 5; endcase;

State 5:

RAS_ := high;

REQ_ := low & (AS & RESET);

case

RESET == 1

: 6; endcase;

" DETERMINE IF ACCESS HAS BEEN REQUESTED

State 6:

REQ_ := high & A23;

MC1_ := high & RESET;

case

REQ # A23

: 0;

!A23 & !REQ & RESET

: 7;

endcase;

" ACCESS AFTER REFRESH

State 7:

RAS_ := low & RESET;

case

RESET==1

: 8; endcase;

REQ_ := high & RESET;

State 8:

MSEL_ := high & RESET;

case

RESET==1

: 9: endcase:

State 9:

CAS_ := low & RESET;

DTACK := low & RESET;

RESET==1

case

:10; endcase;

State 10:

case

RESET==1

:11; endcase;

State II:

RESET==1

case

:12; endcase;

State 12:

case

RESET==1

:13; endcase;

State 13:

RAS_ := high;

MSEL_ := low;

CAS_ := high;

DTACK := high;

case

RESET==1

: 0; endcase;

@page

```

```

" ACCESS TIMING CYCLE

State 14:

RESET==1

case

:15; endcase;

RAS_ := low & !A23 & RESET;

State 15:

case A23 == 1

: 0:

!A23 & RESET

:16:

endcase;

State 16:

MSEL_ := high & RESET;

DTACK_:= low & RESET;

case

RESET==1

:17; endcase;

State 17:

CAS_ := low & RESET;

RESET==1

case

:18; endcase;

State 18:

case

RESET==1

:19; endcase;

State 19:

case

RESET==1

:20; endcase;

RAS_ := high;

MSEL_ := low;

State 20:

CAS_ := high;

DTACK_:= high;

: 0; endcase;

case

RESET==1

equations

enable MC1 = 1; "always enabled, pin 19 is preset

" INITIALIZATION WHEN RESET IS LOW

[ MC1,RAS,DTACK,REQ,CAS]

:= !RESET:

[PO_R,PI_R,P2_R,P3_R,P4_R,MSEL_R,RFC_R] := !RESET;

test vectors ' REFRESH WITH ACCESS FOLLOWING'

([GND,OSC,RESET,REFREQ,CLK,AS,A23] -> [MC1,MSEL,CAS,RAS,DTACK,RFC,REQ,Cnt])

[0,clk, 0, X,X,X,X]->[H, L,H,H, H,L,H,0];

0 , X , X, X ] -> [ H , L , H , H , H , L , H , 1 ];

X , X , 1, X ] -> [ L , L , H , H , H , L , L , 2 ];

[ 0 ,clk,

1

[ 0 ,clk, 1

0 .clk, 1

X , X , X , X ] \rightarrow [ L , L , H , L , H

, H , L , 3 ];

0 ,clk, 1

X , X , X , X ] \rightarrow [ L , L , H , L , H

, H , L , 4 ];

X , X , X , X ] \rightarrow [L , L , H , L , H

[ 0 ,clk, 1

, L , L , 5 ];

0 ,clk, 1

X , X , X , X , X ] \rightarrow [ L , L , H , H , H

, L , L , 6 ];

[ 0 ,clk, 1

X , X , X , 0 ] \rightarrow [ H , L , H , H

, L , L , 7 ];

[ 0 ,clk, 1

X , X , X , X , X ] \rightarrow [ H , L , H , L , H

, L , L , 8 ];

[ 0 ,clk, 1 ,

X , X , X , X ] \rightarrow [ H , H , H , L , H

, L , H , 9 ];

[ 0 ,clk, 1 ,

X , X , X , X ] \rightarrow [ H , H , L , L , L

, L , H ,10 ];

[ 0 ,clk, 1 ,

X , X , X , X , X ] \rightarrow [ H , H , L , L , L

, L , H , [1 ];

[ 0 ,clk, 1 ,

X , X , X , X ] \rightarrow [ H , H , L , L

, L , H ,12 ];

[ 0 ,clk, 1 ,

X , X , X , X ] \rightarrow [ H , H , L , L , L

, L , H ,13 ];

[ 0 ,clk, 1 ,

X , X , X , X ] \rightarrow [ H , L , H , H , L , H , O ];

[ 0 ,clk, 1 ,

1 , 0 , 0, X ] -> [ H , L , H , H , L , H , O ];

[ 0 ,clk,

1

1 , 0 , 1, X ] -> [ H , L , H , H , L , H , O ];

[ 0 ,clk,

1

1 , 1 , 0, X ] -> [ H , L , H , H , H , L , H , O ];

test_vectors ' REFRESH WITHOUT ACCESS FOLLOWING'

([GND,OSC,RESET,REFREQ,CLK,AS,A23] -> [MC1,MSEL,CAS,RAS,DTACK,RFC,REQ,Cnt])

[0,clk, 0 , X , X , X , X ] -> [ H , L , H , H , L , H , O ];

0 , X , X, X ] -> [ H , L , H , H , H , L , H , 1 ];

[ 0 ,clk, 1

[ 0 ,clk, 1

X , X , 0 , X ] \rightarrow [ L , L , H , H , H , L , H , 2 ];

X , X , 0, X ] -> [ L , L , H , L , H

X , X , 0, X ] -> [ L , L , H , L , H

X , X , 0, X ] -> [ L , L , H , L , H

X , X , 0, X ] -> [ L , L , H , L , H

[ 0 ,clk, 1

, H , H , 3 ];

[ 0 ,clk, 1

, H , H , 4 ];

[ 0 ,clk, 1

, L , H , 5 ];

[ 0 ,clk, 1 ,

X , X , X , X ] \rightarrow [ L , L , H , H , H

, L , H , 6 ];

[ 0 ,clk, 1 ,

X , X , 0, X ] -> [ H , L , H , H , L , H , O ];

[0,clk, 1, 0, X, 0, X] -> [H, L, H, H, H, L, H, 1];

```

@page

```

test_vectors ' REFRESH WITH ACCESS REQUEST BUT DATA NOT IN DRAM (A23=H) '

([GND,OSC,RESET,REFREQ,CLK,AS,A23] -> [MC1,MSEL,CAS,RAS,DTACK,RFC,REQ,Cnt])

[0,c]k,0

X , X , X , X ] \rightarrow [ H , L , H , H ,

[ 0 ,clk,

, X , X, X ] -> [ H , L , H , H , H , L , H , 1 ];

[ 0 ,clk,

1

X , X , I , X ] \rightarrow [L , L , H , H ,

Н

, L , L , 2 ];

[ 0 ,clk,

X , X , 0 , X ] \rightarrow [ L , L , H , L ,

1

Н

, H , L , 3 ];

[ 0 ,clk,

X , X , 0 , X ] \rightarrow [ L , L , H , L , H

1

, H , L , 4 ];

[ 0 ,clk,

X , X , 0 , X ] \rightarrow [ L , L , H , L , H

, L , L , 5 ];

[ 0 ,clk,

1

X , X , 0 , X ] \rightarrow [ L , L , H , H , H

, L , L , 6 ];

[ 0 ,clk.

1

Х

, X , 0, 1 ] -> [ H , L , H , H , H , L , H , 0 ];

[ 0 ,clk,

1

, 0 , 0, X ] -> [ H , L , H , H , H , L , H , O ];

test_vectors ' ACCESS TIMING CYCLE '

([GND,OSC,RESET,REFREQ,CLK,AS,A23] -> [MC1,MSEL,CAS,RAS,DTACK,RFC,REQ,Cnt])

[ 0 ,clk, 0

X , X , X, X ] -> [ H , L , H , H , H , L , H , O ];

[ 0 ,clk,

1

,1,1,X]->[H, L,H,H, H,L,H,14];

X , X , X, X ] -> [ H , L , H , H , H , L , H , 15 ];

[ 0 ,clk,

[ 0 ,clk,

X , X , X , 0 ] \rightarrow [H , L , H , L ,

Н

, L , H , 16 ];

[ 0 ,clk,

X , X , X , X ] \rightarrow [ H , H , H , L ,

1

L

, L , H ,17 ];

[ 0 .clk.

X , X , X , X ] \rightarrow [ H , H , L , L

1

, L , H ,18 ];

[ 0 ,clk,

X , X , X , X ] \rightarrow [ H , H , L , L , L

1

, L , H ,19 ];

[ 0 ,clk,

1

X , X , X , X ] \rightarrow [ H , H , L , L

, L , H ,20 ];

[ 0 ,clk,

Χ

, X , X, X ] -> [ H , L , H , H , H

, L , H , 0 ];

[ 0 ,clk,

1

, 0, 0, X ] \rightarrow [H, L, H, H, H]

, L , H , O ];

test_vectors ' ACCESS TIMING CYCLE BUT DATA NOT IN DRAM (A23=H) '

([GND,OSC,RESET,REFREQ,CLK,AS,A23] -> [MC1,MSEL,CAS,RAS,DTACK,RFC,REQ,Cnt])

[ 0 ,clk, 0

X , X , X, X ] -> [ H , L , H , H , L , H , O ];

[ 0 ,clk, 1

1 , 1 , 1, X ] -> [ H , L , H , H , H , L , H , 14 ];

[ 0 ,clk,

X , X , X , X ] \rightarrow [ H , L , H , H ,

1

, L , H ,15 ];

[ 0 ,clk,

Χ

, X , X, 1 ] -> [ H , L , H , H , H , L , H , O ];

1

, 0 , 0, X ] -> [ H , L , H , H , H , L , H , O ];

test_vectors ' RESET DURING ACCESS TIMING CYCLE '

([GND,OSC,RESET,REFREQ,CLK,AS,A23] -> [MC1,MSEL,CAS,RAS,DTACK,RFC,REQ,Cnt])

[0,c]k,0

X , X , X, X ] -> [ H , L , H , H , L , H , O ];

1 , 1 , 1, X ] -> [ H , L , H , H , H , L , H , 14 ];

[ 0 ,clk,

1

[ 0 ,clk,

X , X , X, X ] -> [ H , L , H , H , L , H , 15 ];

[ 0 ,clk,

X , X , X , 0 ] \rightarrow [ H , L , H , L ,

1

Н

, L , H ,16 ];

X , X , X , X ] \rightarrow [ H , H , H , L , L

[ 0 .clk.

1

, L , H ,17 ];

[ 0 ,clk,

1

X , X , X , X , X ] \rightarrow [ H , H , L , L , L

, L , H ,18 ];

X, X, X, X] \rightarrow [H, L, H, H, H

[ 0 ,clk.

0

, L , H , O ];

[ 0 ,clk,

X , X , X, X ] -> [ H , L , H , H , L , H , O ];

end DMC_S167

```

```

module TIMER154

```

```

module TIMER154 flag '-r2','-f'

title

'REFRESH TIMER

LOREN SCHIELE TEXAS INSTRUMENTS, DALLAS, 08/15/86'

T154 DEVICE

'P22V10';

"input declarations

CLK

pin 1;

SYSTEM CLOCK

RESET

pin 2;

RESETS WHEN LOW

RFC

pin 3:

REFRESH COMPLETE

"output declarations

Q0,Q1,Q2,Q3

pin 14,15,16,17;

COUNTER STATES

Q4,Q5,Q6,Q7

pin 18,19,20,21;

COUNTER STATES

REFREQ_

pin 22;

REFRESH REQUEST - ACTIVE LOW

"intermediate variables

CNT_154_ = !Q0 & Q1 & !Q2 & Q3 & Q4 & !Q5 & !Q6 & Q7;

SCLR

= !RESET # CNT_154_;

count

= [Q7,Q6,Q5,Q4,Q3,Q2,Q1,Q0];

C,H,L,X

= .C., 1, 0, .X.;

equations

REFREQ_ := RFC # !CNT_154_ & REFREQ_ # !RESET;

Q0

:= (!Q0 ) & !SCLR;

Q1

:= ( Q1 $ Q0) & !SCLR;

:= ( Q2 $ Q1 & Q0) & !SCLR;

Q2

Q3

:= ( Q3 $ (Q2 & Q1 & Q0)) & !SCLR;

Q4

:= ( Q4 $ (Q3 & Q2 & Q1 & Q0)) & !SCLR;

:= ( Q5 $ (Q4 & Q3 & Q2 & Q1 & Q0)) & !SCLR;

Q5

:= ( Q6 $ (Q5 & Q4 & Q3 & Q2 & Q1 & Q0)) & !SCLR;

Q6

:= ( Q7 $ (Q6 & Q5 & Q4 & Q3 & Q2 & Q1 & Q0)) & !SCLR;

Q7

([RESET,CLK,RFC] -> [count,REFREQ_])

test vectors

[ 0 , C , 0 ] \rightarrow [ 0 ,

];

@CONST cnt = 1:

@REPEAT 154 {

[ 1 , C , 0 ] -> [ cnt ,

];

@CONST cnt = cnt + 1;

[1, C, 0] \rightarrow [0,

L

];

@CONST cnt = 1:

@REPEAT 20 {

[ 1 , C , 0 ] -> [ cnt ,

L

];

\emptyset CONST cnt = cnt + 1;

[

1, C, 1 \rightarrow [21]

];

[

1 , C , 0 ] \rightarrow [ 22 ,

Н

1:

, C , X ] -> [ 23

1

Н

];

0 , C , X ] \rightarrow [ 0 ,

];

end TIMER154

```

#### 2.3.8 CUPLTM Files

#### DYNAMIC MEMORY CONTROLLER

```

DMC-S167:

Partno

Name

DMC-S167;

Date

08/15/86;

Revision

01;

Designer

SCHIELE;

Company

TEXAS INSTRUMENTS;

Assembly

None:

DALLAS, TEXAS;

Location

DYNAMIC MEMORY CONTROLLER

/*

FOR ALS6301

/* Allowable Target Device Types: TIB82S167B

/** Inputs **/

pin 1 = OSC;

/* OSCILLATOR

/* REFRESH REQUEST

pin 2 = REFREQ;

/* RESET - INITIALIZES WHEN LOW

pin 3 = RESET;

/* OSC DIVIDED BY 2

pin 4 = CLK;

/* ADDRESS STROBE

pin 5 = AS;

/* MOST SIGNIFICANT ADDRESS BIT

pin 6 = A23_;

/* PIN 16 MUST BE TIED LOW

pin 16 = GND;

/** Outputs **/

/* MODE CONTROL

pin 9 = MC1_;

pin 10 = MSEL;

/* MULTIPLEXER SELECT

COLUMN ADDRESS STROBE

pin 11 = CAS;

pin 13 = RAS;

/*

ROW ADDRESS STOBE

/* DATA ACKNOWLEDGE

pin 14 = DTACK;

/* REFRESH COMPLETE

pin 15 = RFC;

/** Internal Node Group - State bits declared as nodes

node [REQ,P4_,P3_,P2_,P1_,P0_];

/** Declarations and Intermediate Variable Definitions

Field State = [P4_,P3_,P2_,P1_,P0_];

$define ST0 'b'00000

$define ST1 'b'00001

$define ST2 'b'00010

$define ST3 'b'00011

$define ST4 'b'00100

$define ST5 'b'00101

$define ST6 'b'00110

$define ST7 'b'00111

$define ST8 'b'01000

$define ST9 'b'01001

$define ST10 'b'01010

$define ST11 'b'01011

$define ST12 'b'01100

$define ST13 'b'01101

$define ST14 'b'01110

$define ST15 'b'01111

$define ST16 'b'10000

$define ST17 'b'10001

$define ST18 'b'10010

$define ST19 'b'10011

$define ST20 'b'10100

```

```

/** Logic Equations **/

Sequence State

{Present STO IF RESET & !REFREQ

NEXT ST1:

IF RESET & REFREQ & AS & CLK NEXT ST14;

DEFAULT

NEXT STO;

/* REFRESH TIMING CYCLE */

Present ST1 IF AS & RESET NEXT ST2 OUT [!MC1_,!REQ];

IF

NEXT ST2 OUT [!MC1 ];

RESET

Present ST2 IF

AS & RESET

NEXT ST3 OUT [ RFC,!RAS,!REQ];

IF

RESET

NEXT ST3 OUT [ RFC,!RAS];

NEXT ST4 OUT [!REQ];

Present ST3 IF

AS & RESET

NEXT ST4:

IF

RESET

Present ST4 IF

AS & RESET

NEXT ST5 OUT [!RFC,!REQ];

NEXT ST5 OUT [!RFC];

IF

RESET

Present ST5 IF

AS & RESET

NEXT ST6 OUT [ RAS,!REQ];

IF RESET

NEXT ST6 OUT [ RAS];

/** DETERMINE IF ACCESS HAS BEEN REQUESTED **/

Present ST6 IF A23_ # REQ NEXT ST0 OUT [ MC1_,REQ];

IF !A23_ & RESET & !REQ NEXT ST7 OUT [ MC1_];

/** ACCESS AFTER REFRESH **/

Present ST7 IF

RESET

NEXT ST8 OUT [!RAS];

Present ST8 IF

RESET

NEXT ST9 OUT [ REQ, MSEL];

Present ST9 IF

RESET

NEXT ST10 OUT [!CAS,!DTACK];

Present ST10 IF

RESET

NEXT ST11;

Present ST11 IF

RESET

NEXT ST12;

Present ST12 IF

RESET

NEXT ST13;

Present ST13

NEXT STO OUT [ RAS,!MSEL, CAS, DTACK];

/** ACCESS TIMING CYCLE **/

Present ST14 IF RESET

NEXT ST15;

Present ST15 IF A23_

NEXT STO;

IF !A23 & RESET NEXT ST16 OUT [!RAS];

Present ST16 IF

RESET

NEXT ST17 OUT [ MSEL,!DTACK];

Present ST17 IF

RESET

NEXT ST18 OUT [!CAS];

Present ST18 IF

NEXT ST19;

RESET

Present ST19 IF

RESET

NEXT ST20:

Present ST20

NEXT STO OUT [ RAS,!MSEL, CAS, DTACK];}

APPEND MC1 .s = !RESET; APPEND REQ.s = !RESET; APPEND RFC.r = !RESET;

APPEND RAS.s = !RESET; APPEND MSEL.r = !RESET; APPEND CAS.s = !RESET;

APPEND DTACK.s = !RESET; APPEND PO .r = !RESET; APPEND P1 .r = !RESET;

APPEND P2_.r = !RESET; APPEND P3_.r = !RESET; APPEND P4_.r = !RESET;

```

## DYNAMIC MEMORY SIMULATION

```

DMC-S167;

Partno

Name

DMC-S167;

Date

08/15/86;

Revision

01;

Designer

SCHIELE;

Company

TEXAS INSTRUMENTS;

Assembly

None:

DALLAS, TEXAS:

Location

DYNAMIC TIMING CONTROLLER

/*

SIMULATION FILE

FOR ALS6301

/**************

/* Allowable Target Device Types: TIB82S167B

ORDER: GND, %3, OSC, %3, RESET, %6, REFREQ, %4, CLK, %3, AS, %2, A23_, %6,

MC1_,%4,MSEL,%3,CAS,%3,RAS,%4,DTACK,%4,RFC,%4,REQ;

VECTORS:

$msq" REFRESH WITH ACCESS FOLLOWING":

$msg"

----- OUTPUT ----- ACCESS";

$msg"

----- INPUT -----

$msg"

GND OSC RESET REFREQ CLK AS A23

MC1 MSEL CAS RAS DTACK RFC REQ";

$msg"

/*RESET*/ 0

С

Н

Н

X X

Н

L

/* STO*/ 0

С

Х

Х

Х

Н

1

0

н

н

L

Н

н

L

/* ST1*/ 0

С

Х

1

Х

1

Х

L

Н

Н

Н

L

L

1

/* ST2*/

0