The Engineering Staff of TEXAS INSTRUMENTS INCORPORATED

Semiconductor Group

# The MOS Memory Data Book

for Design Engineers

1980

TEXAS INSTRUMENTS

Texas Instruments, Inc. MOS Memory Division, M/S 6965 P.O. Box 1443 Houston, Texas 77001

# The MOS Memory Data Book

# for

# **Design Engineers**

1980

TEXAS INSTRUMENTS

Printed in U.S.A.

# IMPORTANT NOTICE

Texas Instruments reserves the right to make changes at any time in order to improve design and to supply the best product possible.

TI cannot assume any responsibility for any circuits shown or represent that they are free from patent infringement.

Information contained herein supersedes previously published data on these devices from TI.

# ISBN 0-89512-105-0

Library of Congress Catalog Number: 79-93268

Copyright © 1980

Texas Instruments Incorporated

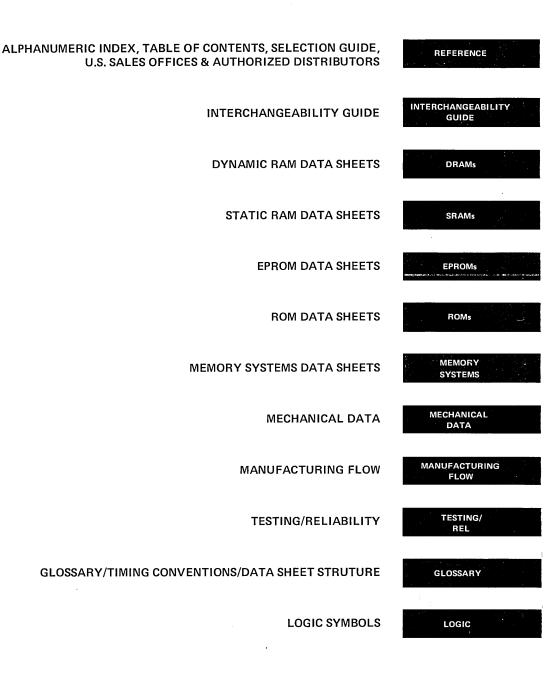

REFERENCE

# ALPHANUMERIC INDEX, TABLE OF CONTENTS, SELECTION GUIDE, U.S. SALES OFFICES & AUTHORIZED DISTRIBUTORS

# ALPHANUMERIC INDEX TO DATA SHEETS

| Page          | Page        |

|---------------|-------------|

| TMM 10000 151 | TMS 2708-35 |

| TMM 20000     | TMS 27L08   |

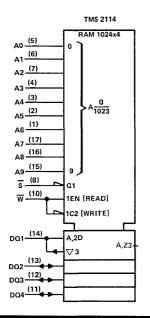

| TMS 2114      | TMS 2716    |

| TMS 2114L     | TMS 2758    |

| TMS 2147      | TMS 4008    |

| TMS 21L47     | TMS 4016    |

| TMS 2508      | TMS 4044    |

| TMS 2516      | TMS 40L44   |

| TMS 2516-35   | TMS 4108    |

| TMS 2532      | TMS 4116 38 |

| TMS 25L32     | TMS 4164    |

| TMS 2564      | TMS 4732    |

| TMS 2708      | TMS 4764    |

.

# TABLE OF CONTENTS

# Page

| Selection Guide<br>Sales Offices and Dis<br>Interchangeability G<br>Alternate Vene<br>Second Source<br>Dynamic | to Data Sheet<br>stributors<br>iuide<br>dor Part Numb<br>es<br>c RAMs |                                                     | · · · · · · · · · · · · · · · · · · ·   | · · · · · · · · · · · · · · · · · · · | 1<br>9<br>11<br>15<br>20<br>20 |

|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------|-----------------------------------------|---------------------------------------|--------------------------------|

| Static R<br>EPROM                                                                                              |                                                                       |                                                     |                                         |                                       | 20<br>21                       |

| Dynamic Random-A                                                                                               |                                                                       |                                                     |                                         |                                       |                                |

| TMS 4108                                                                                                       | 8192-Bit (                                                            |                                                     | · · · · · · · · · · · · · · · · · · ·   |                                       | 25                             |

| TMS 4108                                                                                                       | 16384-Bit                                                             |                                                     |                                         |                                       | 38                             |

| TMS 4110<br>TMS 4164                                                                                           | 65536-Bit                                                             |                                                     |                                         |                                       | 51                             |

|                                                                                                                |                                                                       |                                                     |                                         |                                       | •••                            |

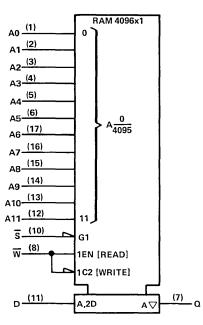

| Static Random-Acce<br>TMS 4044                                                                                 | 4096-Bit (4                                                           | K v 1)                                              |                                         |                                       | 65                             |

| TMS 4044<br>TMS 40L44                                                                                          |                                                                       | K x 1) - Low Power                                  |                                         |                                       | 65<br>65                       |

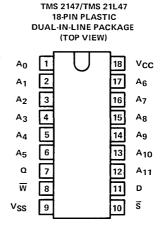

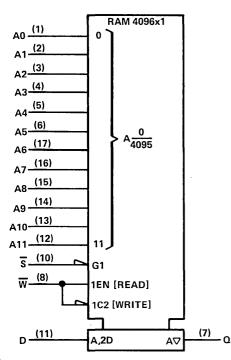

| TMS 2147                                                                                                       | -                                                                     | K x 1) - High Speed                                 |                                         |                                       | 71                             |

| TMS 2147<br>TMS 21L47                                                                                          |                                                                       | K x 1) · High Speed /Low Power                      |                                         |                                       | 71                             |

| TMS 21147                                                                                                      | 4096-Bit (                                                            |                                                     |                                         |                                       | 79                             |

| TMS 2114                                                                                                       | -                                                                     | K x 4) - Low Power                                  |                                         |                                       | 79                             |

| TMS 4016                                                                                                       | •                                                                     | 2K x 8)                                             |                                         |                                       | 85                             |

| TMS 4008                                                                                                       | 8192-Bit (                                                            |                                                     |                                         |                                       | 90                             |

|                                                                                                                |                                                                       |                                                     |                                         |                                       |                                |

| Erasable Programma                                                                                             | -                                                                     |                                                     |                                         |                                       | ~~                             |

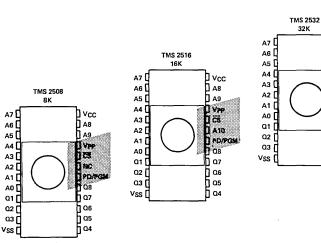

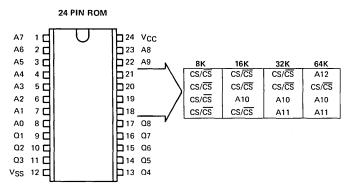

| EPROM Comp                                                                                                     | •                                                                     |                                                     |                                         |                                       | 93                             |

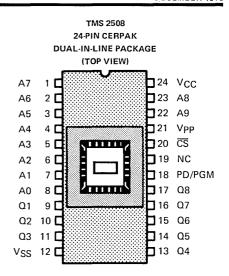

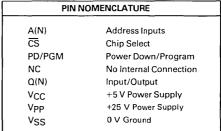

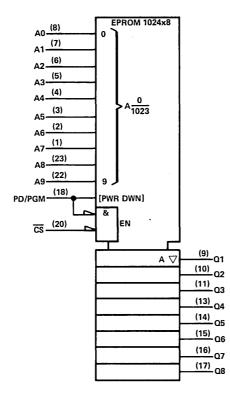

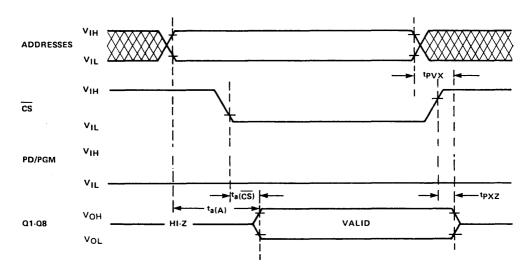

| TMS 2508                                                                                                       | 5 V                                                                   |                                                     |                                         |                                       | 95                             |

| TMS 2516                                                                                                       | 5 V                                                                   |                                                     |                                         |                                       | 03                             |

| TMS 2516-35                                                                                                    | 5 V                                                                   | 16384-Bit (2K x 8) - 350 ns                         |                                         |                                       | 03                             |

| TMS 2532                                                                                                       | 5 V                                                                   |                                                     |                                         |                                       | 11                             |

| TMS 25L32                                                                                                      | 5 V                                                                   | • •                                                 | •••••                                   |                                       | 11                             |

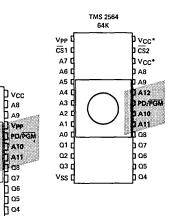

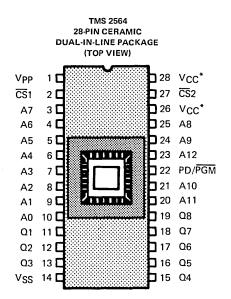

| TMS 2564                                                                                                       | 5 V                                                                   |                                                     | • • • • • • • • • • • • • • • • • • • • |                                       | 19                             |

| TMS 2758                                                                                                       | 5 V                                                                   |                                                     | •••••                                   |                                       | 27                             |

| TMS 2708                                                                                                       | 3-Supply                                                              |                                                     | •••••                                   |                                       | 29                             |

| TMS 2708-35                                                                                                    | 3-Supply                                                              |                                                     |                                         |                                       | 29                             |

| TMS 27L08                                                                                                      | 3-Supply                                                              | 8192-Bit (1K x 8) - Low Power .                     |                                         |                                       | 29                             |

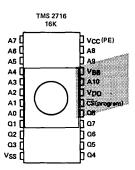

| TMS 2716                                                                                                       | 3-Supply                                                              | 16384-Bit (2K x 8)                                  |                                         | 13                                    | 37                             |

| Read-Only Memories                                                                                             | s                                                                     |                                                     |                                         |                                       |                                |

| TMS 4732                                                                                                       | 5 V                                                                   | 32768-Bit (4K x 8)                                  |                                         | 14                                    | 47                             |

| TMS 4764                                                                                                       | 5 V                                                                   | 65536-Bit (8K x 8)                                  |                                         | 14                                    | 47                             |

|                                                                                                                |                                                                       | mory for LSI-II Computers<br>mory for PDP Computers |                                         |                                       | 51<br>53                       |

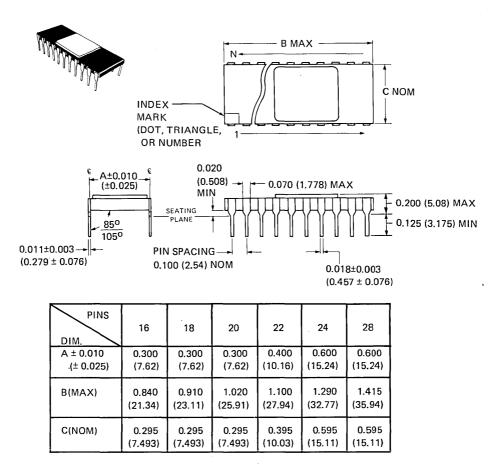

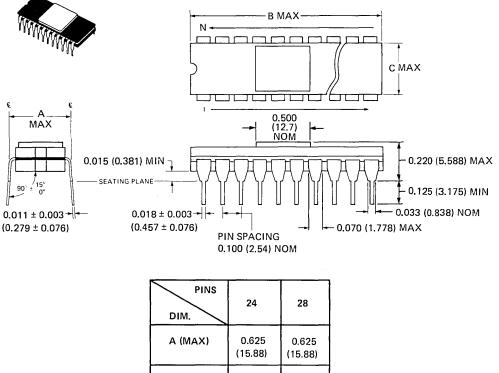

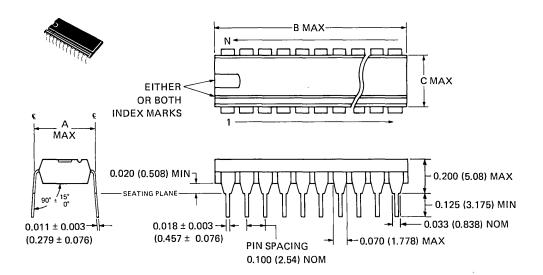

| Mechanical Data                                                                                                |                                                                       |                                                     |                                         | 11                                    | 57                             |

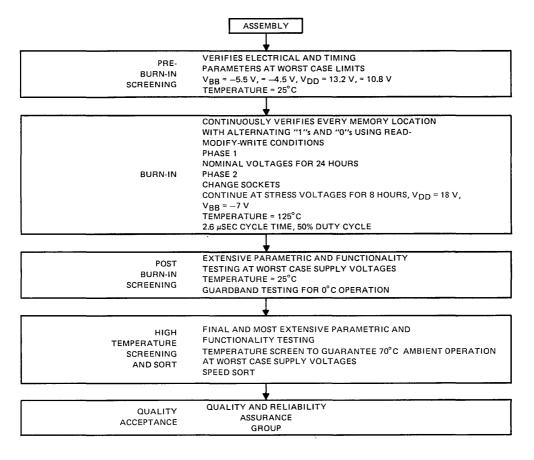

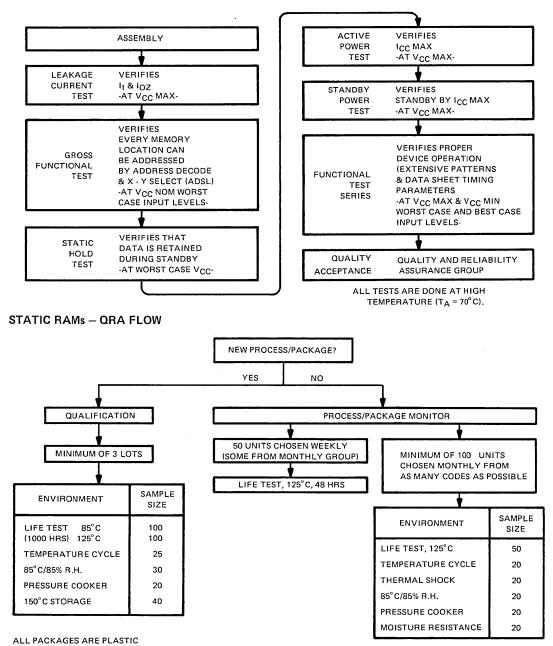

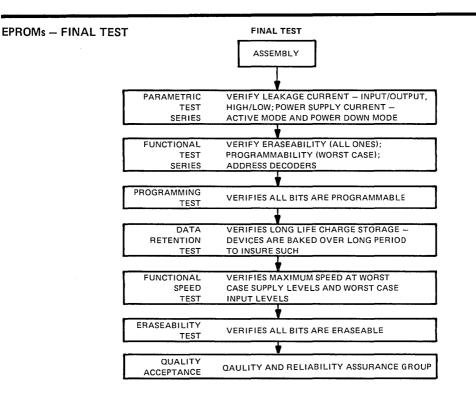

| Manufacturing Flow                                                                                             |                                                                       | • • • • • • • • • • • • • • • • • • • •             |                                         |                                       | 63                             |

| Hermetic Flow                                                                                                  |                                                                       |                                                     |                                         |                                       | 63                             |

| Plastic Flow                                                                                                   |                                                                       |                                                     |                                         |                                       | 63<br>64                       |

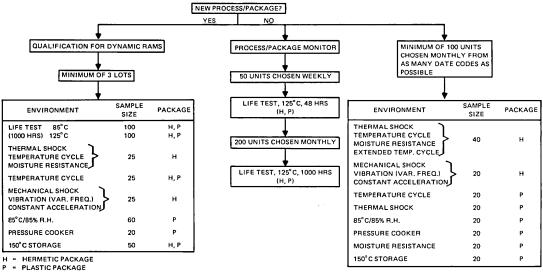

| Testing/Reliability                                                                                            |                                                                       |                                                     |                                         |                                       | 64<br>67                       |

| Glossary/Timing Cor                                                                                            |                                                                       |                                                     |                                         |                                       | 73                             |

| , ,                                                                                                            |                                                                       |                                                     |                                         |                                       | 83                             |

|                                                                                                                |                                                                       |                                                     |                                         |                                       |                                |

# RAMS, ROMS, EPROMS SELECTION GUIDE

| WORDS |                                                                        | BITS PER W                    | ORD                                                                                              |

|-------|------------------------------------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------|

| WUNDS | 1                                                                      | 4                             | 8                                                                                                |

| 1К    |                                                                        | (4K)<br>TMS 2114<br>TMS 2114L | EPROMs (8K)<br>TMS 2508<br>TMS 2708<br>TMS 2708-35<br>TMS 27L08<br>TMS 2758<br>SRAMs<br>TMS 4008 |

| 2К    |                                                                        |                               | (16K)<br><u>SRAMs</u> <u>EPROMs</u><br>TMS 4016 TMS 2516<br>TMS 2516-35<br>TMS 2716              |

| 4К    | (4K)<br><u>SRAMs</u><br>TMS 2147<br>TMS 21L47<br>TMS 4044<br>TMS 40L44 |                               | (32K)<br><u>ROMs</u> <u>EPROMs</u><br>TMS 4732 TMS 2532<br>TMS 25L32                             |

| 8К    | (8K)<br><u>DRAMs</u><br>TMS 4108                                       |                               | (64K)<br><u>ROMs</u><br>TMS 4764 TMS 2564                                                        |

| 16K   | (16K)<br><u>DRAMs</u><br>TMS 4116                                      | (Numbers in parentheses       | indicate overall complexity)                                                                     |

| 64K   | (64K)<br><u>DRAMs</u><br>TMS 4164                                      |                               |                                                                                                  |

. . .

9

# **TI Sales Offices**

ALABAMA: Huntsville, 4717 University Dr., Suite 101, Huntsville, AL 35805, (205) 837-7530.

ARIZONA: Phoenix, P.O. Box 35160, 8102 N. 23rd Ave., Suite A, Phoenix, AZ 85069, (602) 249-1313.

CALIFORNIA: Costa Mesa, 3186J Airway, Costa Mesa, CA 92626, (714) 540-7311; El Segundo, B31 S. Douglas S1. El Segundo, CA90253, (213) 973-2571 San Diego, 4333 View Ridge Ave, Suite B. San Diego, CA 92123, (714) 278-9600, Sunnyvie, CN Box 90054, 776 Palomar Ave., Sunnyvale, CA 94085, (408) 732-1840

COLORADO: Denver, 9725 E. Hampden St., Suite 301, Denver, CO 80231, (303) 751-1780.

CONNECTICUT: Hamden, 2405 Whitney Ave., Hamden, CT 06518, (203) 281-0074.

FLORIDA: Clearwater, 2280 U.S. Hwy. 19 N. Suite 232, Clearwater, FL 33515, (813) 725-1861, FL Lauderdate, 4600 W. Commercial Biud, H.: Lauderdate, FL 33319, (305) 733-3300, Winter Part, 1850 Lee Rd., Suite 115, Winter Park, FL 32789, (305) 644-3535.

GEORGIA: Atlanta, 3300 Northeast Expy., Suite 9, Atlanta, GA 30341, (404) 452-4600.

ILLINOIS: Arlington Heights, 515 W. Algonquin, Arlington Heights, IL 60005, (312) 640-3000.

INDIANA: Ft. Wayne, 2020 Inwood Dr., Ft. Wayne, IN 46805, (219) 424-5174: Indianapolis, 5726 Professional Cir., Suite 103, Indianapolis, IN 46241, (317) 248-8555. IOWA: Cedar Rapids, 411 Burdette Ave., #1026, Cedar Rapids, IA 52404, (319) 346-1100.

MASSACHUSETTS: Waltham, 504 Totten Pond Rd., Waltham, MA 02154, (617) 890-7400.

MICHIGAN: Southfield, Central Park Plaza, 26211 Central Park Blvd., Suite 215, Southfield, MI 48076. (313) 353-0830.

MINNESOTA: Edina, 7625 Parklawn, Edina, MN 55435, (612) 830-1600.

MISSOURI: Kansas City, 8080 Ward Pkwy. Kansas City, MO 64114, (816) 523-2500; St. Louis, 2368 Schuetz Rd., St. Louis, MO 63141, (314) 432-3333.

NEW JERSEY: Clark, 1245 Westfield Ave., Clark, NJ 07066, (201) 574-9800.

NEW MEXICO: Albuquerque, 5907 Alice N.E., Suite E, Albuquerque, NM 87110, (505) 265-8491.

NEW YORK: East Syracuse, 6700 Old Collamer Rd., East Syracuse, NY 13057, (315) 463-9291; Endicott, 112 Nanticoke Ave. P. D. Box 618, Endicott, NY 13760, (607) 754-3900, Melville, 1 Huntington Quadrangle, Suite 1C01, Melville, NY 11746, (516) 293-2560; Poughkeepsie, 201 South Ave., Poughkeepsie, NY 12601, (914) 473-2900; Rochester, 1210 Jefferson Rd., Rochester, NY 14623, (716) 451-1800.

NORTH CAROLINA: Charlotte, 1 Woodlawn Green, Woodlawn Rd., Charlotte, NC 28210, (704) 527-0930; Raleigh, 4130 C.2 Camelot Dr., Raleigh, NC 27609, (919) 787-9376. OHIO: Beachwood, 23408 Commerce Park Rd., Beachwood, OH 44122, (216) 464-6100. Dayton; Kingsley Bidg., 4124 Linden Ave., Dayton, OH 45432, (513) 258-3877.

OKLAHOMA: Tulsa, 3105 E. Skelly Dr., Suite 110, Tulsa, OK 74128, (918) 749-9548.

OREGON: Beaverton, 10700 S.W. Beaverton Hwy., Suite 565, Beaverton, OR 97005, (503) 643-6759.

PENNSYLVANIA: Ft. Washington, 575 Virginia Dr., Ft. Washington, PA 19034, (215) 643-6450.

TENNESSEE: Johnson City, P.O. Drawer 1255, Erwin Hwy., Johnson City, TN 37601, (615) 282-1100

TEXAS: Dallas, 13531 N. Central Expressway, Suite 2700, Dallas, TX 75243, (214) 238-6531; Houston, 9000 Southwest Frwy., Suite 400, Houston, TX 77036, (713) 776-6511.

UTAH: Salt Lake City, 3672 West 2100 South, Salt Lake City UT 84120. (801) 973-6310.

VIRGINIA: Arlington, Crystal Square 4, 1745 Jefferson Davis Hwy, Suite 600, Arlington, VA 22202, (703) 553-2200; Richmond, 3930 Beulah Rd., Richmond, VA 23234, (804) 275-6148.

WASHINGTON: Bellevue, 700 112th N.E., Suite 10, Bellevue, WA 98004, (206) 455-3480.

CANADA: St. Laurent, 945 McCaffery St., St. Laurent H4T1N3, Ouebec, Canada, (514) 341-3232; Richmond Hill, 280 Centre St. E., Richmond Hill L4C181, Ontario, Canada, (145) 884-9181. D

# **TI Distributors**

### ALABAMA: Huntsville, Hall-Mark (205)837-8700

ARIZONA: Phoenix, Kierulff Electronics (602) 243-4101; R V Weatherford (602) 272-7144; Tempe, Marshall Industries (602) 968-6181

(602) 968-6181

CALIFORNIA: Anaheim, R. V. Weatherford (714) 634-9600

Canaga Park, Marshail Industries (213) 999-5001

Chaisworh, JACO (213) 998-2200. Costa Mesa, 11 Supply (714) 975-3391. El Monte, Marshail Industries (213) 680-0141. El Segundo, 15 Supply (213) 27-261. Benedate, 873.

Viene, Marshail Industries (714) 565-6300. Data Allo, Los Angeles, Kieruit Electronics (213) 725-0325. RPS (213) 748-1271.

Mountain View, Time Electronics (145) 968-6322. Primona, R. V. Weather ford (714) 623-1261. San Diego, Arrow Electronics (714) 565-4800. Kieruit Electronics (141) 278-2112. Marshail Industries (714) 278-6350. RV. Weatherford (605) 455-851. Sunmysile, Arrow Electronics (141) 728-112. Marshail Industries (744) 737-471.

Keruit Gletronics (714) 7278-2112. Marshail Industries (744) 737-471.

Kanaga Parkan, R. V. Weatherford (605) 455-851. Sunmysile, Arrow Electronics (714) 728-1712. Marshail Industries (714) 680, 739-3011. Marshail Industries (714) 673-741.

Kanaga Parkan, R. V. Weatherford (741) 727-5751.

Keruit Beteronics (744) 773-5711.

COLORADO: Denver, Arrow Electronics (303) 758-2100, Diplomat/Denver, (303) 427-5544, Kierulff Electronics (303) 371-6500, Englewood, R. V. Weatherford (303) 770-9762

CONNECTICUT: Hamden, Arrow Electronics (203) 248-3801. TI Supply (203) 281-4669. Drange, Milgray/Connecticut (203) 795-0714. Wallingford, Wilshire Electronics (203) 265-3822

FLORIDA: Clearwater, Diplomat/Southland (813) 443-4514 FL. Lauderdale, Arrow Electronics (305) 776-7790 Diplomatri, Lauderdale (305) 971-760- All-Mar/Mamu (305) 971-9280, Orlando, Hall-Mar/Mindo (305) 855-4020, Palm Bay, Arrow Electronics (305) 725-1480, Diplomat/Fionda (305) 725-4520, SL. Petersburg, Kerulift Electronics (813) 576-1966. Winter Park, Milgray Electronics (305) 647-5747

GEORGIA: Doraville, Arrow Electronics (404) 455-4054, Norcross, Wilshire Electronics (404) 923-5750

ILLINDIS: Arlington Heights, TI Supply (312) 640-2964. Benzonville, Hall-Mark/Chicago (312) 860-3800. Elk Grove Village, Kierulff Electronics (312) 640-0200. Chicago, Newark Electronics (312) 638-4411. Schaumburg, Arrow Electronics (312) 893-9420

INDIANA: Ft. Wayne, Ft. Wayne Electronics (219) 423-3422. Indianapolis, Graham Electronics (317) 634-8202 IOWA: Cedar Rapids, Deeco (319) 365-7551

KANSAS: Lenexa, Component Specialties (913) 492-3555. Shawnee Mission, Hall-Mark/Kansas City (913) 888-4747

MARYLAND: Baltimore, Arrow Electronics (202) 737-1700 (301) 247-5200, Hali-Mark/Balimore (301) 756-9300, Columbia, Diplomat/Maryland (301) 951-1256, Gaithersburg, Cramer / Washington (301) 488-6400 Migray/Washington (301) 488-6400

MASSACHUSETTS: Billerica, Kieruilf Electronics (617) 667-8331 Burlington, Wilshire Electronics (617) 272-8200 Newton, Cramer/Newton (617) 969-7700 Waltham, TI Supply (617) 890-0510. Woburn, Arrow Electronics (617) 933-8130

MICHIGAN: Ann Arbor, Arrow Electronics (313) 971-8220. Oak Park, Newark Electronics (313) 967-0600. Grand Rapids, Newark Electronics (616) 241-6681

MINNESOTA: Edina, Arrow Electronics (612) 830-1800. Plymouth, Marshall Industrials (612) 559-2211

MISSOURI: Earth City, Hall-Mark/St. Louis (314) 291-5350. Kansas City, Component Specialties (913) 492-3555. LCOMP-Kansas City (816) 221-2400. St. Louis, LCOMP-St. Louis (314) 291-6200

NEW HAMPSHIRE: Manchester, Arrow Electronics (603) 668-6968

NEW JERSEY: Camden, General Radio Supply (609) 964-8560. Cherry Hill, Milgray/Delaware Valley (609) 424-1300. Clark, Ti Supply (201) 382-6400. Clitton, Wishwre Electronos: (201) 340-1900. Fairfield, Kieruitt Electronics (201) 575-6750. Moorstewn, Arrow Electronics (609) 235-1900. Saddlebrook, Arrow Electronics (201) 797-5800

NEW MEXICO: Albuquerque, Arrow Electronics (505) 243-4566. International Electronics (505) 262-2011. United Components (505) 345-9981

NEW YORX: Endwell, Wilshire Electronics (607) 754-1570. Farmingdale, Arrow Electronics (516) 694-6800, Freeport, Migray Electronics (516) 656-6000, N J (800) 665-3986. Hauppauge, Arrow Electronics (516) 231-1000, JACO (516) 273-5500, Liverpool, Cramer/Syracuse (316) 652-1000. New York, Wilshire Electronics (212) 682-8707, Rochester, Cramer/Rochester (716) 275-0300, Rochester (Aalo Suppl) (716) 454-7800, Wilshire Electronics (716) 235-7620. Woodbury, Dujolmai/Long Island (516) 921-7280. NORTH CAROLINA: Kernersville, Arrow Electronics (919) 966-2039. Raleigh, Hall-Mark (919) 832-4465

OHIO: Cleveland, TI Supply (216) 464-2435, Columbus, Hall-Mark/Ohio (614) 846-1682, Dayton, ESCO Electronics (513) 256-1133, Marshall Industries (513) 236-8088, Kettering, Arrow Electronics (513) 253-9176, Reading, Arrow Electronics (513) 761-5432, Solon, Arrow Electronics (216) 248-3990

OKLAHOMA: Tulsa, Component Speciallies (918) 664-2820; Hall-Mark/Tulsa (918) 835-8458; TI Supply (918) 749-9543

OREGON: Beaverton, Almac/Stroum Electronics (503) 641-9070 Milwaukie, United Components (503) 653-5940

PENNSYLVANIA: Huntington Valley, Hall-Mark/Philadelphia (215) 355-7300. Pittsburgh, Arrow Electronics (412) 351-4000

TEXAS: Austin. Component Specialities (512) 837-8922. Hall-Mark/Austin (512) 837-2814. Dallas, Component Specalities (214) 357-6511. Hall/Mark/Dallas (214) 234-7400. International Electronics. (214) 233-9923. Ti Supply (214) 238-6821. El Paso, International Electronics (915) 778. 9761. Houston, Component Specialities (713) 771-7237. Hail-Mark/Mouston (713) 7716-6511.

UTAH: Salt Lake City, Diplomat/Altaland (801) 486-4134. Kierulff Electronics (801) 973-6913

WASHINGTON: Redmond, United Components (206) 885 1985. Seattle, Almac/Stroum Electronics (206) 763-2300, Krenulf Electronics (206) 575-4420. Tukwila, Arrow Electronics (206) 575-0907

WISCONSIN: Dak Creek, Arrow Electronics (414) 764-6600. Hall-Mark/Milwaukee (414) 761-3000. Waukesha, Kierulff Electronics (414) 784-8160

CANADA: Calgary, Cam Gard Supply (403) 287-0520. Downsview, CESCO Electronics (416) 661-0220. Edmonton, Cam Gard Supply (403) 426-1805. Halitaz, Cam Gard Supply (92) 154-856. Kamioops, Cam Gard Supply (604) 372-3338. Moncton, Cam Gard Supply (506) 855-2200. Montreal, CESCO Electronics (514) 735-5511. Future Electronics (514) 731-7441. Ottawa, CESCO Electronics (613) 729-5118 Future Electronics (613) 802-6813. Queber City, CESCO Electronics (148) 667-4231. Regina, Cam Gard Supply (306) 525-1317. Saskatoon, Cam Gard Supply (306) 525-1317. Saskatoon, Cam Gard Supply (306) 637 Supply (604) 291-1441. Future Electronics (604) 438-5545. Winnipeg, Cam Gard Supply (204) 786-8481. S

TEXAS INSTRUMENTS

. . . . . 2 . .

# INTERCHANGEABILITY GUIDE

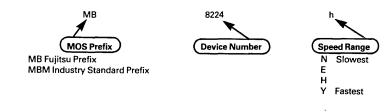

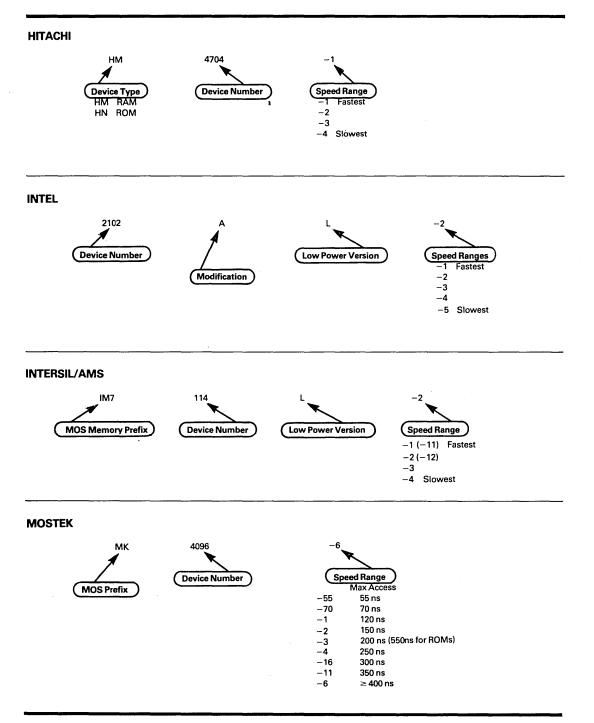

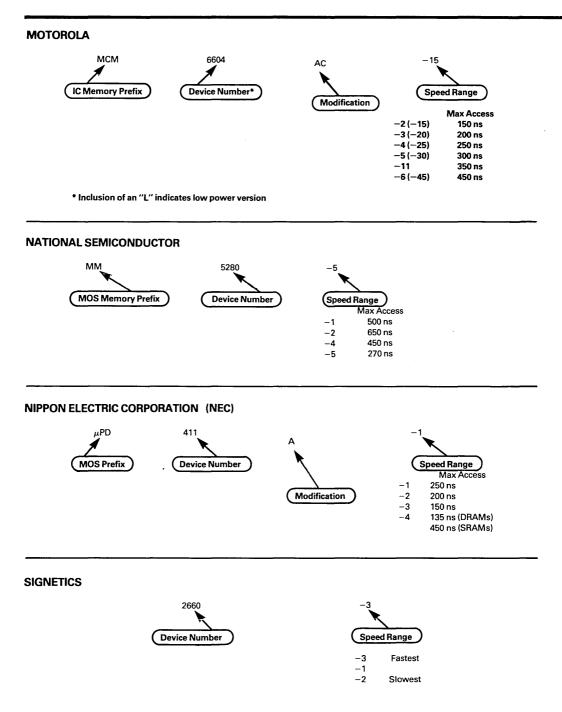

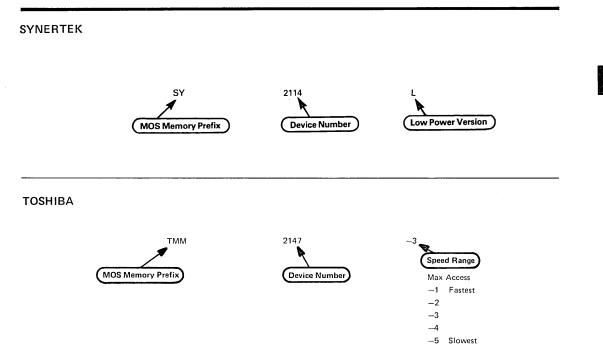

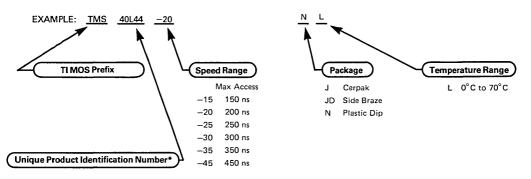

# PART I - ALTERNATE VENDOR PART NUMBERING (EXAMPLES)

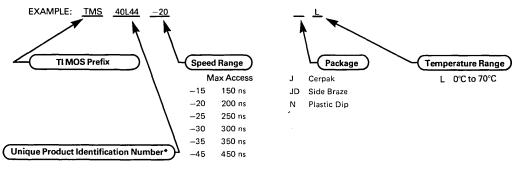

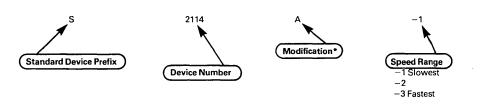

### **TEXAS INSTRUMENTS (TI)**

\* L indicates low power

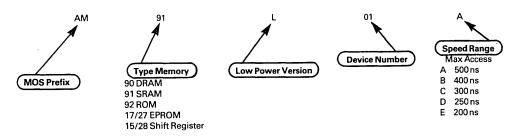

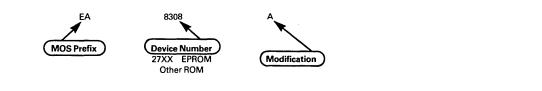

## ADVANCED MICRO DEVICES (AMD)

\*Can also be "L", usually indicates lower power and/or improved speed

# **ELECTRONIC ARRAYS, INC (EA)**

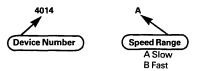

# EMM/SEMI

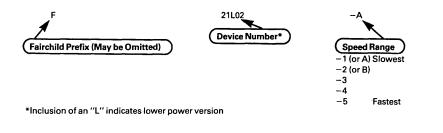

### FAIRCHILD

FUJITSU

# TEXAS INSTRUMENTS INCORPORATED POST OFFICE BOX 225012 • DALLAS, TEXAS 75265

# PART II - SECOND SOURCES\*

• Based on available published data. (Official second sourcing agreements not necessarily implied.) All devices listed operate over the 0°C to 70°C temperature range.

# **DYNAMIC RAMS**

|         |                                 | VENDOR    | PART NUMBER            |

|---------|---------------------------------|-----------|------------------------|

| 8K X 1  | Left Array (0), Right Array (1) | TI        | TMS 4108-20 NL0 or NL1 |

|         | Second Sources                  | Mostek    | MK 4108-40 or 41       |

| 16K X 1 |                                 | TI        | TMS 4116               |

|         | Second Sources                  | Fairchild | F 16K                  |

|         |                                 | Fujitsu   | MB 8116                |

|         |                                 | Hitachi   | HM 4716                |

|         |                                 | Intel     | 2117                   |

|         |                                 | Intersil  | IM 7116                |

|         |                                 | ITT       | 4116                   |

|         |                                 | Mostek    | MK 4116                |

|         |                                 | Motorola  | MCM 4116               |

|         |                                 | National  | MM 5290                |

|         |                                 | NEC       | μPD 416                |

|         |                                 | Toshiba   | TMM 416                |

| 64K X 1 | 5 V                             | TI        | TMS 4164               |

|         | Second Sources                  | Motorola  | MCM 6664               |

# STATIC RAMS

|        |                     | VENDOR      | PART NUMBER         |

|--------|---------------------|-------------|---------------------|

| 4K X 1 | Max Access ≥ 150 ns | ТІ          | TMS 4044/TMS 40L44  |

|        | Second Sources      | Intersil    | IM 7141/IM 7141L    |

|        |                     | National SC | MM 5257/MM 5257L    |

| 1K X 4 | Max Access ≥ 150 ns | ті          | TMS 2114/TMS 2114L  |

|        | Second Sources      | AMD         | AM 9114/AM 91L14    |

|        |                     | AMI         | S2114/S2114L/S2114A |

|        |                     | EMM/SEMI    | 2114                |

|        |                     | Fujitsu     | MB 8114             |

|        |                     | Hitachi     | HM 472114           |

|        |                     | Intel       | 2114/2114L          |

|        |                     | Intersil    | IM 7114/IM 7114L    |

|        |                     | National SC | MM 2114/MM 2114L    |

|        |                     | NEC         | μPD 2114L           |

|        |                     | Synertek    | SY 2114/SY 2114L    |

| 4K X 1 | Max Access ≥ 55 ns  | ТІ          | TMS 2147/TMS 21L47  |

|        | Second Sources      | AMD         | AM 9147             |

|        |                     | AMI         | S2147               |

|        |                     | Fujitsu     | MBM 2147            |

|        |                     | Hitachi     | HM 6147/HM 6147L    |

|        |                     | Intel       | 2147/2147L          |

|        |                     | Mostek      | MK 2147             |

|        |                     | Motorola    | MCM 2147            |

|        |                     | National SC | MM 2147             |

|        |                     | NEC         | μPD 4104            |

|        |                     | Toshiba     | TMM 2147            |

# STATIC RAMS (continued)

|        |                     | VENDOR              | PART NUMBER |

|--------|---------------------|---------------------|-------------|

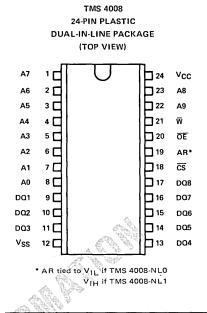

| 1K X 8 | Max Access 450 ns   | ті                  | TMS 4008    |

|        | Second Sources      | Anticipated in 1980 |             |

| 2K X 8 | Max Access ≥ 150 ns | ті                  | TMS 4016    |

|        | Second Sources      | Toshiba             | TC 5516P    |

# EPROMS

|          |                                       | VENDOR              | PART NUMBER        |

|----------|---------------------------------------|---------------------|--------------------|

| 1K X 8   | Max Access 350 ns/450 ns              | ті                  | TMS 2708/TMS 27L08 |

| 3 Supply | Second Sources                        | AMD                 | AM 2708            |

|          |                                       | EA                  | EA 2708            |

|          |                                       | Fairchild           | 2708               |

|          |                                       | Fujitsu             | MB 8518H           |

|          |                                       | Hitachi             | HN 462708          |

|          | · · · · · · · · · · · · · · · · · · · | Intel               | 2708/2708L         |

|          |                                       | Motorola            | MCM 2708           |

|          |                                       | National SC         | MM 2708            |

|          |                                       | Signetics           | 2708               |

| 1K X 8   | Max Access ≥ 250 ns                   | TI                  | TMS 2508           |

| 5 V      | Second Sources                        | Anticipated in 1980 |                    |

| 1K X 8   | Max Access 450 ns                     | ті                  | TMS 2758           |

| 5 V      | Second Sources                        | Intel               | 2758               |

| 2K X 8   | Max Access 450 ns                     | TI                  | TMS 2716           |

| 3 Supply | Second Sources                        | Motorola            |                    |

| 2K X 8   | Max Access 350 ns/450 ns              | ті                  | TMS 2516           |

| 5 V      | Second Sources                        | AMD                 | 2716               |

|          |                                       | AMI                 | S4716              |

|          |                                       | Fujitsu             | MBM 2716           |

|          |                                       | Hitachi             | HN 462716          |

|          |                                       | Intel               | 2716               |

|          |                                       | Mostek              | MK 2716            |

|          |                                       | Motorola            | MCM 2716A          |

|          |                                       | National            | MM 2716            |

|          |                                       | NEC                 | μPD 2716           |

|          |                                       | Signetics           | 2716               |

|          |                                       | Synertek            | SY 2716            |

|          |                                       | Toshiba             | TMM 323            |

| 4K X 8   | Max Access 450 ns                     | TI                  | TMS 2532/TMS 25L32 |

| 5 V      | Second Sources                        | Hitachi             | HN 462732          |

|          |                                       | Motorola            | MCM 2532           |

| 8K X 8   | Max Access 450 ns                     | TI                  | TMS 2564           |

| 5 V      | Second Sources                        | Anticipated in 1980 |                    |

# DYNAMIC RAM DATA SHEETS

DRAMs

) ,

VBB

D

w

RAS

A0

A2

A1

VDD

1

21

3

4 1

5

6

7

8

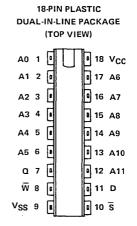

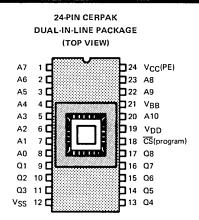

**16-PIN PLASTIC**

DUAL-IN-LINE PACKAGE (TOP VIEW)

16

15

13 A6

12 A3

11 44

10 A5

q

Vss

CAS

Vcc

o

AUGUST 1979

• 8,192 X 1 Organization

MOS

LSI

- 10% Tolerance on All Supplies

- All Inputs Including Clocks TTL-Compatible

- Unlatched Three-State Fully TTL-Compatible Output

- 3 Performance Ranges:

|             | ACCESS  | ACCESS  | READ   | READ,              |

|-------------|---------|---------|--------|--------------------|

|             | TIME    | TIME    | OR     | MODIFY-            |

|             | ROW     | COLUMN  | WRITE  | WRITE <sup>†</sup> |

|             | ADDRESS | ADDRESS | CYCLE  | CYCLE              |

|             | (MAX)   | (MAX)   | (MIN)  | (MIN)              |

| TMS 4108-15 | 150 ns  | 100 ns  | 375 ns | 375 ns             |

| TMS 4108-20 | 200 ns  | 135 ns  | 375 ns | 375 ns             |

| TMS 4108-25 | 250 ns  | 165 ns  | 410 ns | 515 ns             |

|             |         |         |        |                    |

- Page-Mode Operation for Faster Access Time

- Common I/O Capability with "Early Write" Feature

- Low-Power Dissipation

Operating . . . 462 mW (max)

- Standby . . . 20 mW (max)

- 1-T Cell Design, N-Channel Silicon-Gate Technology

- PIN NOMENCLATURE A0-A6 Address Inputs w Write Enable CAS Column address strobe -5-V power supply VBB D Data input Vcc +5-V power supply α Data output VDD +12-V power supply RAS Row address strobe VSS 0 V ground

Copyright © 1979 by Texas Instruments Incorporated

o 16-Pin 300-Mil (7,62 mm) Package Configuration

# description

The TMS 4108 series is composed of monolithic high-speed Dynamic 8,192-bit MOS random-access memories organized as 8,192 one-bit words and employing single-transistor storage cells and N-channel silicon-gate technology.

All input and outputs are compatible with Series 74 TTL circuits including clocks, Row Address Strobe ( $\overline{RAS}$  or R), and Column Address Strobe ( $\overline{CAS}$  or C). All address lines (A0 through A6) and the data input (D) are latched on chip to simplify system design. Data out (Q) is unlatched to allow greater system flexibility.

Typical power dissipation is less than 350 milliwatts active and 6 milliwatts during standby (V<sub>CC</sub> is not required during standby operation). To retain data, only 10 milliwatts average power is required which includes the power consumed to refresh the contents of the memory.

There are two array-select versions of the TMS 4108, each offered in the three speed ranges indicated above and in plastic (NL suffix) packaging only. The left-array version is indicated by "0" following the type number (e.g., TMS 4108-15 NL0), and the right-array version is indicated by "1" (e.g., TMS 4108-25 NL1). Each 8K X 1 version is in a 16-pin dual-in-line package rated for operation from  $0^{\circ}$ C to  $70^{\circ}$ C.

### operation

### address (A0 through A6)

Thirteen address bits are required to decode 1 of 8,192 storage cell locations. Seven row-address bits are set up on pins A0 through A6 and latched onto the chip by the row-address strobe ( $\overline{RAS}$ ). Then the seven column-address bits are set up on pins A0 through A6 and latched onto the chip by the column-address strobe ( $\overline{CAS}$ ). If the type number is followed by a "0", then column address input A0 must always be at V<sub>IL</sub>; if it is followed by a "1", column address A0 must always be at V<sub>IH</sub>. All addresses must be stable on or before the falling edges of  $\overline{RAS}$  and  $\overline{CAS}$ .  $\overline{RAS}$  is similar to a chip enable in that it activates the sense amplifiers as well as the row decoder.  $\overline{CAS}$  is used as a chip select activating the column decoder and the input and output buffers.

<sup>†</sup>The term "read-write cycle" is sometimes used as an alternative title to "read-modify-write cycle".

### write enable (W)

The read or write mode is selected through the write enable  $(\overline{W})$  input. A logic high on the  $\overline{W}$  input selects the read mode, and a logic low selects the write mode. The write enable terminal can be driven from standard TTL circuits without a pull-up resistor. The data input is disabled when the read mode is selected. When  $\overline{W}$  goes low prior to  $\overline{CAS}$ , data-out will remain in the high-impedance state for the entire cycle permitting common I/O operation.

### data-in (D)

Data is written during a write or read-modify write cycle. The latter falling edge of  $\overline{CAS}$  or  $\overline{W}$  strobes data into the on-chip data latch. This latch can be driven from standard TTL circuits without a pull-up resistor. In an early write cycle  $\overline{W}$  is brought low prior to  $\overline{CAS}$ , and the data is strobed in by  $\overline{CAS}$  with setup and hold times referenced to this signal. In a delayed write or read-modify write cycle,  $\overline{CAS}$  will already be low, thus the data will be strobed in by  $\overline{W}$  with setup and hold times referenced to this signal.

### data-out (Q)

The three-state output buffer provides direct TTL compatibility (no pull-up resistor required) with a fan-out of two Series 74 TTL loads. Data-out is the same polarity as data-in. The output is in the high-impedance (floating) state until  $\overrightarrow{CAS}$  is brought low. In a read cycle the output goes active after the enable time interval  $t_a(C)$  that begins with the negative transition of  $\overrightarrow{CAS}$  as long as  $t_a(R)$  is satisfied. The output becomes valid after the access time has elapsed and remains valid while  $\overrightarrow{CAS}$  is low;  $\overrightarrow{CAS}$  going high returns it to a high-impedance state. In an early write cycle, the output is always in the high-impedance state. In a delayed write or read-modify-write cycle, the output will follow the sequence for the read cycle.

### refresh

A refresh operation must be performed at least every two milliseconds to retain data. Since the output buffer is in the high-impedance state unless  $\overline{CAS}$  is applied, the  $\overline{RAS}$ -only refresh sequence avoids any output during refresh. Strobing each of the 128 row addresses (A0 through A6) with  $\overline{RAS}$  causes all bits in each row to be refreshed.  $\overline{CAS}$  remains high (inactive) for this refresh sequence, thus conserving power.

### page mode

Page-mode operation allows effectively faster memory access by keeping the same row address and strobing successive column addresses onto the chip. Thus, the time required to set up and strobe sequential row addresses on the same page is eliminated. To extend beyond the 64 column locations on a single RAM, the row address and RAS is applied to multiple 8K RAMs. CAS is decoded to select the proper RAM.

### power-up

V<sub>BB</sub> must be applied to the device either before or at the same time as the other supplies and removed last. Failure to observe this precaution will cause dissipation in excess of the absolute maximum ratings due to internal forward bias conditions. This also applies to system use, where failure of the V<sub>BB</sub> supply must immediately shut down the other supplies. After power up, eight memory cycles must be performed to achieve proper device operation.

### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)\*

| Voltage on any pin (see Note 1)   |      |      |     |    |    |   |   |   |  |  |  |   |  |  |  |    | -0.5 t  | o 20 V |

|-----------------------------------|------|------|-----|----|----|---|---|---|--|--|--|---|--|--|--|----|---------|--------|

| Voltage on VCC, VDD supplies v    | vith | resp | ect | to | ٧s | s |   |   |  |  |  |   |  |  |  |    | . —1 t  | o 15 V |

| Short circuit output current      |      |      |     |    |    |   |   |   |  |  |  |   |  |  |  |    |         | 50 mA  |

| Power dissipation                 |      |      |     |    |    |   |   |   |  |  |  |   |  |  |  |    |         | . 1W   |

| Operating free-air temperature ra | inge |      |     |    |    |   |   |   |  |  |  |   |  |  |  |    | 0°C to  | o 70°C |

| Storage temperature range         |      |      | •   | ·  | •  | • | • | • |  |  |  | • |  |  |  | -( | 65°C to | 150°C  |

NOTE 1: Under absolute maximum ratings, voltage values are with respect to the most-negative supply voltage, V<sub>BB</sub> (substrate), unless otherwise noted. Throughout the remainder of this data sheet, voltage values are with respect to V<sub>SS</sub>.

\*Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the "Recommended Operating Conditions" section of this specification is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### recommended operating conditions

| PARAMETER                          | · · · · · · · · · · · · · · · · · · · | MIN  | NOM | MAX  | UNIT |

|------------------------------------|---------------------------------------|------|-----|------|------|

| Supply voltage, VBB                |                                       | -4.5 | -5  | -5.5 | v    |

| Supply voltage, V <sub>CC</sub>    |                                       | 4.5  | 5   | 5.5  | V    |

| Supply voltage, VDD                |                                       | 10.8 | 12  | 13.2 | V    |

| Supply voltage, VSS                | · · · · · · · · · · · · · · · · · · · |      | 0   |      | V    |

| High level input voltors. Mus      | All inputs except RAS, CAS, WRITE     | 2.4  |     | 7    |      |

| High-level input voltage, VIH      | RAS, CAS, WRITE                       | 2.7  |     | 7    | V    |

| Low-level input voltage, VIL       |                                       | -11  | 0   | 0.8  | V    |

| Refresh time, trefresh             |                                       |      |     | 2    | ms   |

| Operating free-air temperature, TA |                                       | 0    |     | 70   | °C   |

<sup>†</sup>The algebraic convention where the more negative limit is designated as minimum is used in this data sheet for logic voltage levels and time intervals.

# electrical characteristics over full ranges of recommended operating conditions (unless otherwise noted)

|       | PARAMETERS                | TEST CONDITIONS                                                    | MIN | TYPT | MAX | UNIT |

|-------|---------------------------|--------------------------------------------------------------------|-----|------|-----|------|

| Vон   | High-level output voltage | I <sub>OH</sub> = -5 mA                                            | 2.4 |      |     | V    |

| VOL   | Low-level output voltage  | I <sub>OL</sub> = 4.2 mA                                           |     |      | 0.4 | V    |

| 4     | Input current (leakage)   | $V_I = 0 V$ to 7 V,<br>All other pins = 0 V except $V_{BB} = -5 V$ |     |      | ±10 | μA   |

| 10    | Output current (leakage)  | $V_0 = 0$ to 5.5 V,<br>CAS high                                    |     |      | ±10 | μΑ   |

| IBB1  | Average operating current |                                                                    |     | 50   | 200 | μA   |

| ICC1* | during read or write      | Minimum cycle time                                                 |     |      | 4   | mA   |

| DD1   | cycle                     |                                                                    |     | 27   | 35  | mA   |

| IBB2  |                           | After 1 memory cycle                                               |     | 10   | 100 | μA   |

| ICC2  | Standby current           | RAS and CAS                                                        |     |      | ±10 | μA   |

| IDD2  |                           | high                                                               |     | 0.5  | 1.5 | mA   |

| IBB3  |                           | Minimum cycle time                                                 |     | 50   | 200 | μA   |

| ICC3  | Average refresh current   | RAS cycling,                                                       |     |      | ±10 | μA   |

| IDD3  |                           | CAS high                                                           |     | 20   | 27  | mA   |

| IBB4  | A                         | Minimum cycle time                                                 |     | 50   | 200 | μA   |

| ICC4* | Average page-mode         | RAS low,                                                           |     |      | 4   | μA   |

| DD4   | current                   | CAS cycling                                                        |     | 20   | 27  | mA   |

${}^{*}V_{CC}$  is applied only to the output buffer, so I  $_{CC}$  depends on output loading. Output loading is two standard TTL loads.

# capacitance over recommended supply voltage range and operating free-air temperature range, f = 1 MHz

|                    | PARAMETER                             | TYPT | MAX | UNIT |

|--------------------|---------------------------------------|------|-----|------|

| Ci(A)              | Input capacitance, address inputs     | 4    | 5   | рF   |

| C <sub>i(D)</sub>  | Input capacitance, data input         | 4    | 5   | pF   |

| C <sub>i(RC)</sub> | Input capacitance, strobe inputs      | 8    | 10  | pF   |

| C <sub>i(W)</sub>  | Input capacitance, write enable input | 8    | 10  | рF   |

| Co                 | Output capacitance                    | 5    | 7   | pF   |

# switching characteristics over recommended supply voltage range and operating free-air temperature range

| PARAMETER          |                                           | TEST CONDITIONS                                              | ALTERNATE<br>SYMBOL | TMS 4116-15 |     | TMS 4116-20 |     | TMS 4116-25 |     |      |

|--------------------|-------------------------------------------|--------------------------------------------------------------|---------------------|-------------|-----|-------------|-----|-------------|-----|------|

|                    |                                           |                                                              |                     | MIN         | MAX | MIN         | MAX | MIN         | MAX | UNIT |

| t <sub>a</sub> (C) | Access time from<br>column address strobe | C <sub>L</sub> = 100 pF,<br>Load = 2 Series 74 TTL gates     | <sup>t</sup> CAC    |             | 100 |             | 135 |             | 165 | ns   |

| t <sub>a</sub> (R) | Access time from row address strobe       | tRLCL = MAX,<br>CL = 100 pF,<br>Load = 2 Series 74 TTL gates | <sup>t</sup> RAC    |             | 150 |             | 200 |             | 250 | ns   |

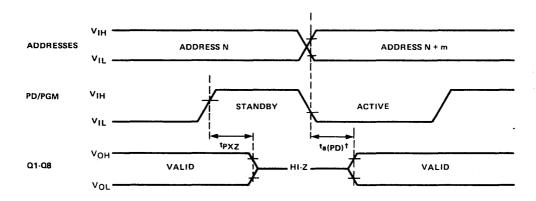

| <sup>t</sup> PXZ   | Output disable time                       | CL = 100 pF,<br>Load = 2 Series 74 TTL gates                 | <sup>t</sup> OFF    | 0           | 40  | 0           | 50  | 0           | 60  | ns   |

<sup>†</sup>All typical values are at  $T_A = 25^{\circ}C$  and nominal supply voltages.

# timing requirements over recommended supply voltage range and operating free-air temperature range

|                       | BADAMETED                                                   | ALTERNATE        | TMS 4   | 108-15 | TMS 4108-20 |        | TMS 4108-25 |        |      |

|-----------------------|-------------------------------------------------------------|------------------|---------|--------|-------------|--------|-------------|--------|------|

| PARAMETER             |                                                             | SYMBOL           | MIN MAX |        | MIN MAX     |        | MIN MAX     |        | UNIT |

| <sup>t</sup> c(P)     | Page mode cycle time                                        | tPC              | 170     |        | 225         |        | 275         |        | ns   |

| tc(rd)                | Read cycle time                                             | tRC              | 375     |        | 375         |        | 410         |        | ns   |

| t <sub>c</sub> (W)    | Write cycle time                                            | twc              | 375     |        | 375         |        | 410         |        | ns   |

| tc(RW)                | Read-modify-write cycle time                                | tRWC             | 375     |        | 375         |        | 515         |        | ns   |

| <sup>t</sup> w(CH)    | Pulse width, column address strobe high                     | tCP              | 60      |        | 80          |        | 100         |        | ns   |

|                       | (precharge time)                                            |                  |         |        | 00          |        | 100         |        | ns   |

| tw(CL)                | Pulse width, column address strobe low                      | tCAS             | 100     | 10,000 | 135         | 10,000 | 165         | 10,000 | ns   |

| <sup>t</sup> w(RH)    | Pulse width, row address strobe high                        | tRP              | 100     |        | 120         |        | 150         |        | ns   |

|                       | (precharge time)                                            |                  |         |        |             |        |             |        |      |

| <sup>t</sup> w(RL)    | Pulse width, row address strobe low                         | tRAS             | 150     | 10,000 | 200         | 10,000 | 250         | 10,000 | ns   |

| tw(W)                 | Write pulse width                                           | twp              | 45      |        | 55          |        | 75          |        | ns   |

| <sup>t</sup> T        | Transition times (rise and fall) for RAS and CAS            | t <sub>T</sub>   | 3       | 35     | 3           | 50     | 3           | 50     | ns   |

| tsu(AC)               | Column address setup time                                   | tASC             | -101    |        | -101        |        | -101        |        | ns   |

| t <sub>su</sub> (AR)  | Row address setup time                                      | tASR             | 0       |        | 0           |        | 0           |        | ns   |

| t <sub>su</sub> (D)   | Data setup time                                             | tDS              | 0       |        | 0           |        | 0           |        | ns   |

| t <sub>su</sub> (rd)  | Read command setup time                                     | tRCS             | 0       |        | 0           |        | 0           |        | ns   |

| t <sub>su</sub> (WCH) | Write command setup time before CAS high                    | tCWL             | 60      |        | 80          |        | 100         |        | ns   |

| t <sub>su</sub> (WRH) | Write command setup time before RAS high                    | tRWL             | 60      |        | 80          |        | 100         |        | ns   |

| th(CLA)               | Column address hold time after CAS low                      | <sup>t</sup> CAH | 45      |        | 55          |        | 75          |        | ns   |

| th(RA)                | Row address hold time                                       | tRAH             | 20      |        | 25          |        | 35          |        | ns   |

| th(RLA)               | Column address hold time after RAS low                      |                  | 95      |        | 120         |        | 160         |        | ns   |

| th(RLC)               | CAS hold time after RAS low                                 | tCSH             | 150     |        | 200         |        | 250         |        | ns   |

| th(CLD)               | Data hold time after CAS low                                | <sup>t</sup> DH  | 45      |        | 55          |        | 75          |        | ns   |

| th(RLD)               | Data hold time after RAS low                                | <sup>t</sup> DHR | 95      |        | 120         |        | 160         |        | ns   |

| th(WLD)               | Data hold time after W low                                  | <sup>t</sup> DH  | 45      |        | 55          |        | 75          |        | ns   |

| th(rd)                | Read command hold time                                      | <sup>t</sup> RCH | 0       |        | 0           |        | 0           |        | ns   |

| th(CLW)               | Write command hold time after CAS low                       | twch             | 45      |        | 55          |        | 75          |        | ns   |

| th(RLW)               | Write command hold time after RAS low                       | tWCR             | 95      |        | 120         |        | 160         |        | ns   |

| tCHRL                 | Delay time, column address strobe high to                   |                  |         |        |             |        |             |        |      |

|                       | row address strobe                                          | tCRP             | -20†    |        | -201        | ינ     | 20†         |        | ns   |

| <sup>t</sup> CLRH     | Delay time, column address strobe low to                    | tRSH             | 100     |        | 135         |        | 165         |        |      |

|                       | row address strobe high                                     |                  |         |        |             |        |             |        | ns   |

| <sup>t</sup> CLWL     | Delay time, column address strobe low to $\overline{W}$ low |                  |         |        |             |        |             |        |      |

|                       | (read, modify-write cycle only)                             | tCWD             | 70      |        | 95          |        | 125         |        | ns   |

| t <sub>rf</sub>       | Refresh time interval                                       | tREF             |         | 2      |             | 2      |             | 2      | ms   |

| <sup>t</sup> RLCL     | Delay time, row address strobe low to column                | tRCD             | 20      | 50     | 25          | 65     | 35          | 85     | ns   |

|                       | address strobe low (maximum value specified                 |                  |         |        |             |        |             |        |      |

|                       | only to guarantee access time)                              |                  |         |        |             |        |             |        |      |

| <sup>t</sup> RLWL     | Delay time, row address strobe low to $\overline{W}$ low    | tRWD             | 120     |        | 160         |        | 200         |        | ns   |

|                       | (read, modify-write cycle only)                             |                  |         |        |             |        |             |        |      |

| tWLCL                 | Delay time, $\overline{W}$ low to column address strobe     | twcs             | -20†    |        |             |        |             | -+     |      |

|                       | low (early write cycle)                                     |                  |         |        | -20†        |        | -20†        |        | ns   |

<sup>†</sup>The algebraic convention where the more negative limit is designated.as minimum is used on this data sheet for logic voltage levels and time invervals.

.

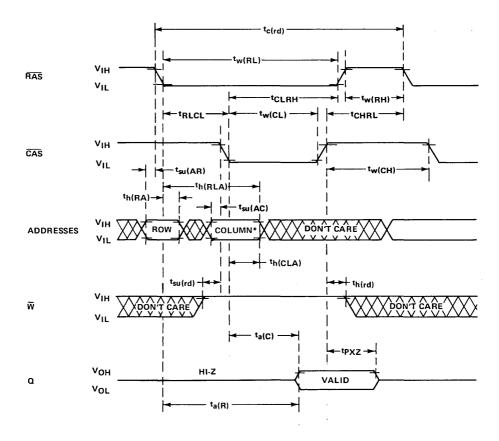

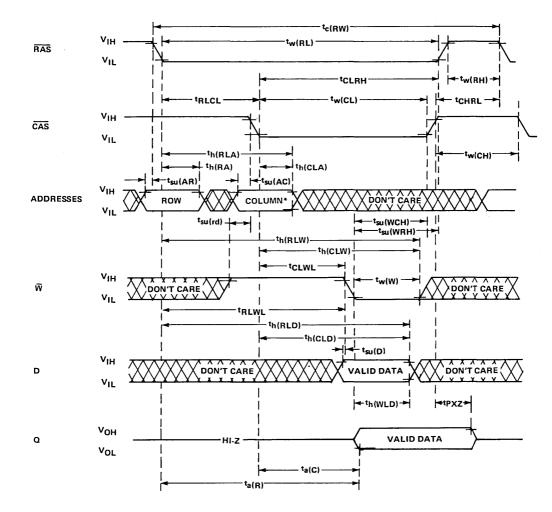

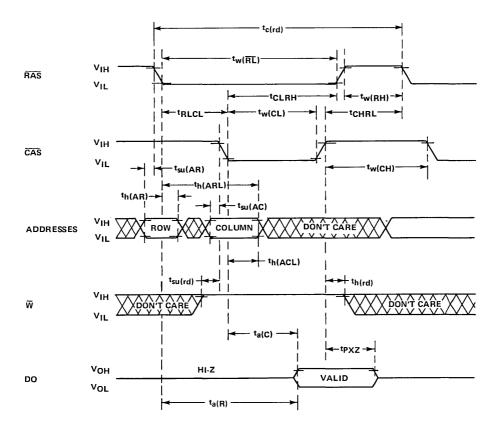

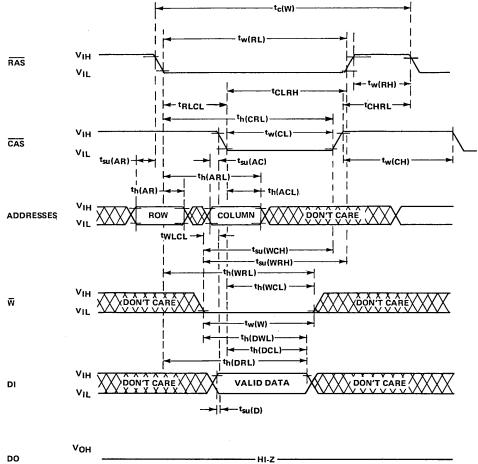

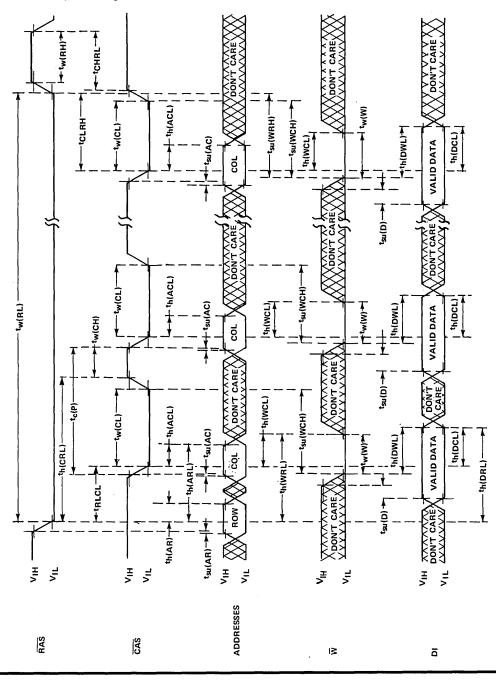

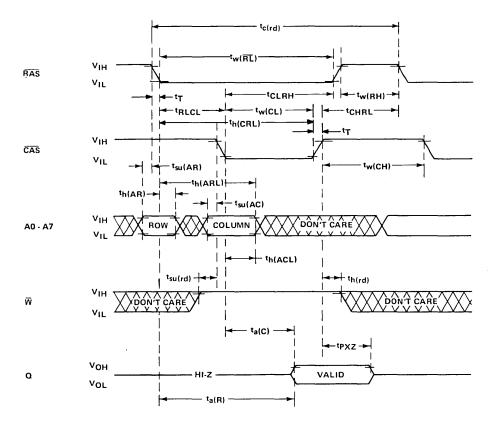

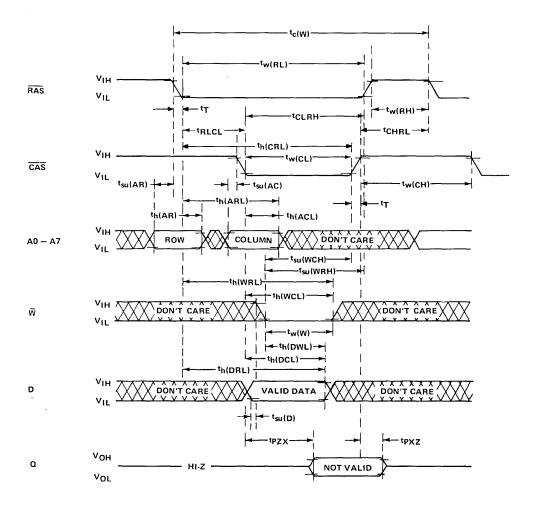

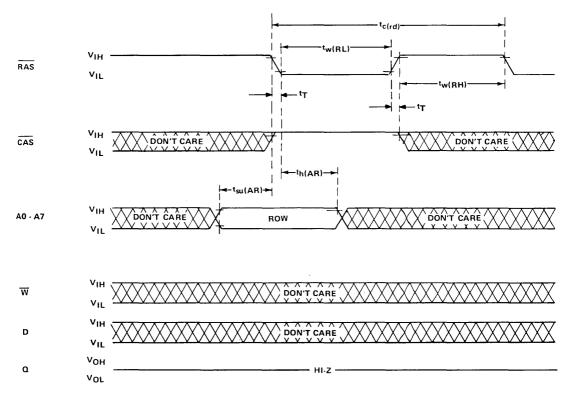

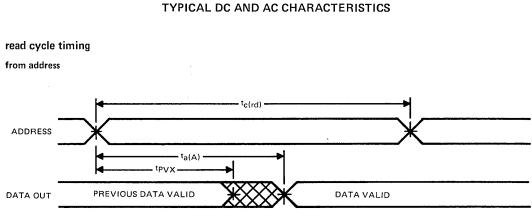

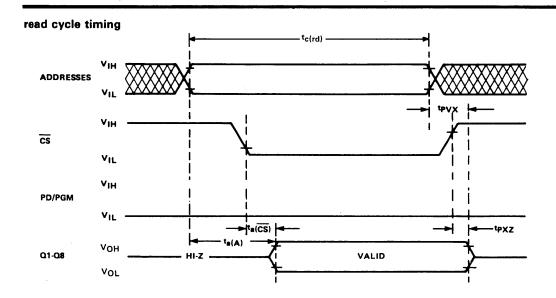

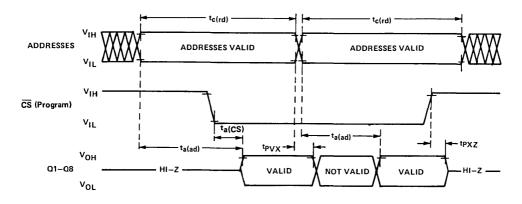

read cycle timing

\*For Column Address: A0 must be at V<sub>1L</sub> for TMS 4108-0 A0 must be at V<sub>1H</sub> for TMS 4108-1

TEXAS INSTRUMENTS INCORPORATED POST OFFICE BOX 225012 • DALLAS, TEXAS 75265

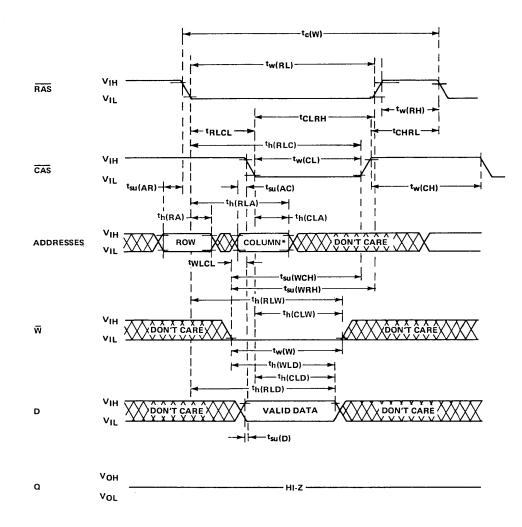

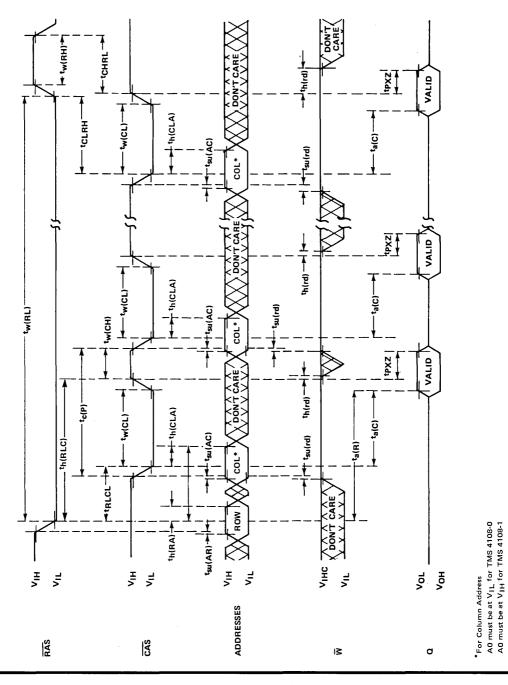

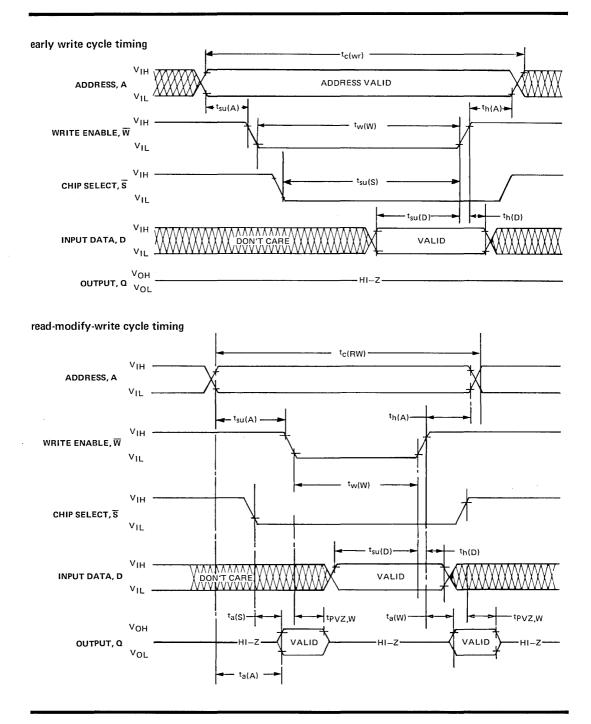

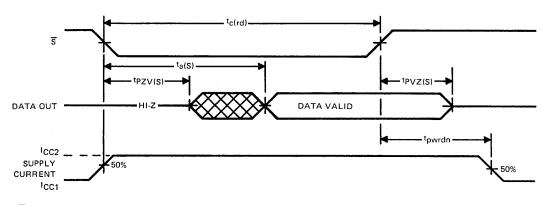

early write cycle timing

\*For Column Address:

A0 must be at V  $_{IL}$  for TMS 4108-0 A0 must be at V  $_{IH}$  for TMS 4108-1

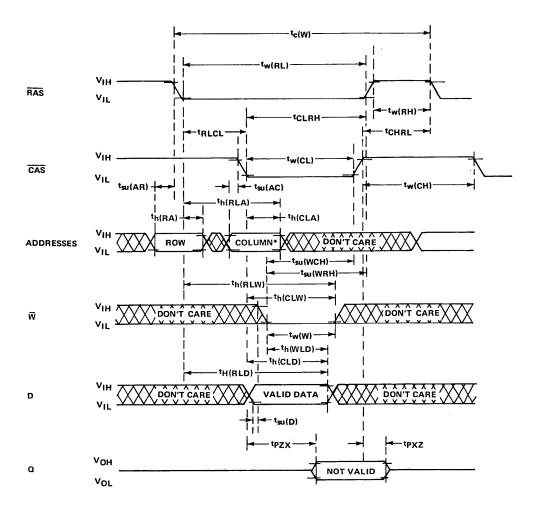

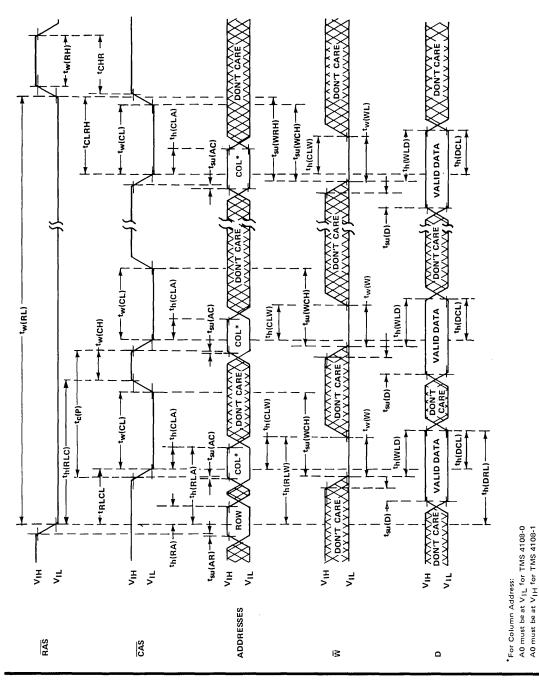

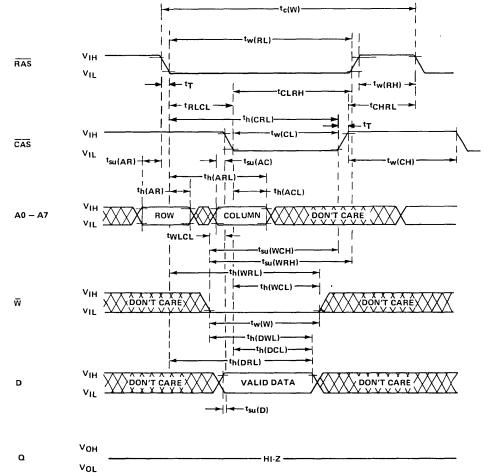

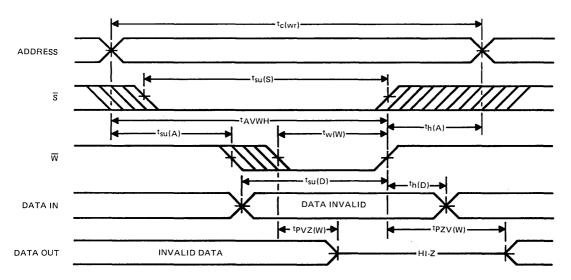

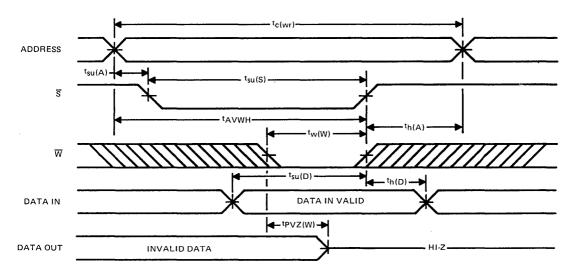

write cycle timing

\*For Column Address:

A0 must be at V<sub>IL</sub> for TMS 4108-0 A0 must be at V<sub>IL</sub> for TMS 4108-1

TEXAS INSTRUMENTS INCORPORATED POST OFFICE BOX 225012 • DALLAS, TEXAS 75265

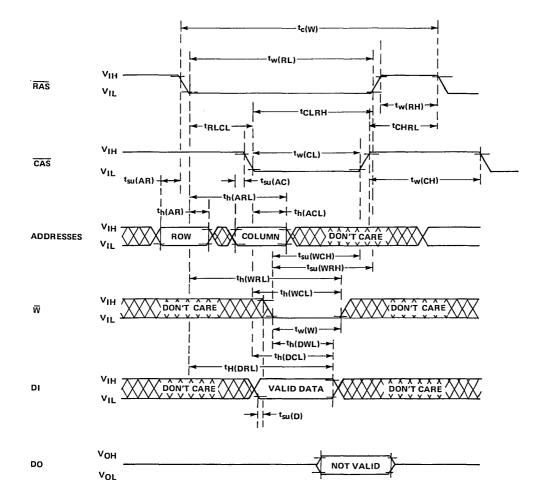

### read-write/read-modify-write cycle timing

\*For Column Address:

A0 must be at V<sub>IL</sub> for TMS 4108-0 A0 must be at V<sub>IL</sub> for TMS 4108-1

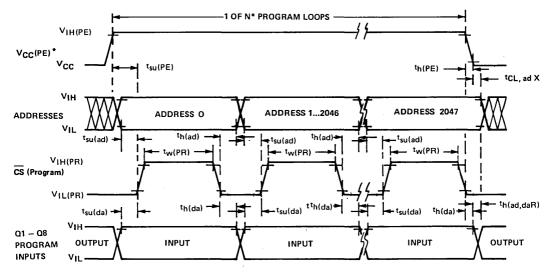

# TMS 4108 NL 8,192-BIT DYNAMIC RANDOM-ACCESS MEMORY

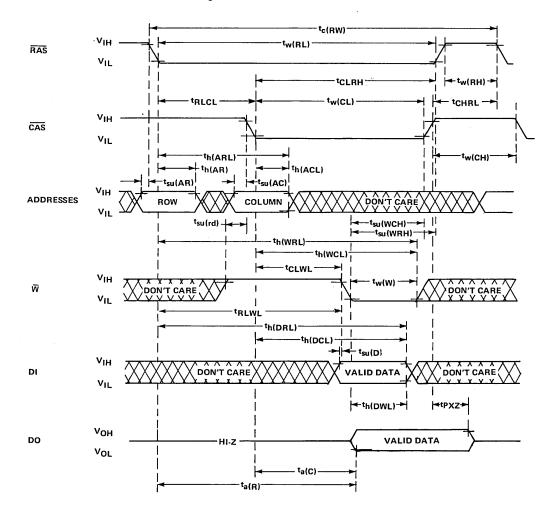

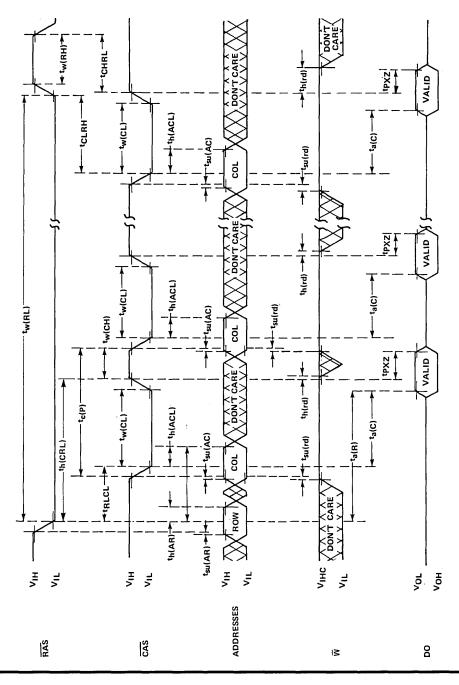

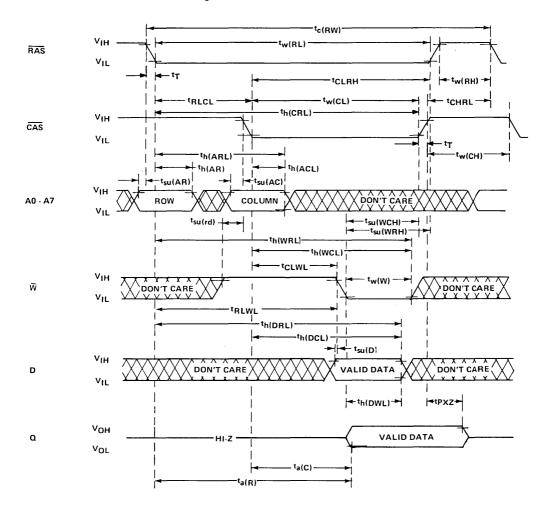

page-mode read cycle timing

TEXAS INSTRUMENTS

POST OFFICE BOX 225012 • DALLAS, TEXAS 75265

## TMS 4108 NL 8,192-BIT DYNAMIC RANDOM-ACCESS MEMORY

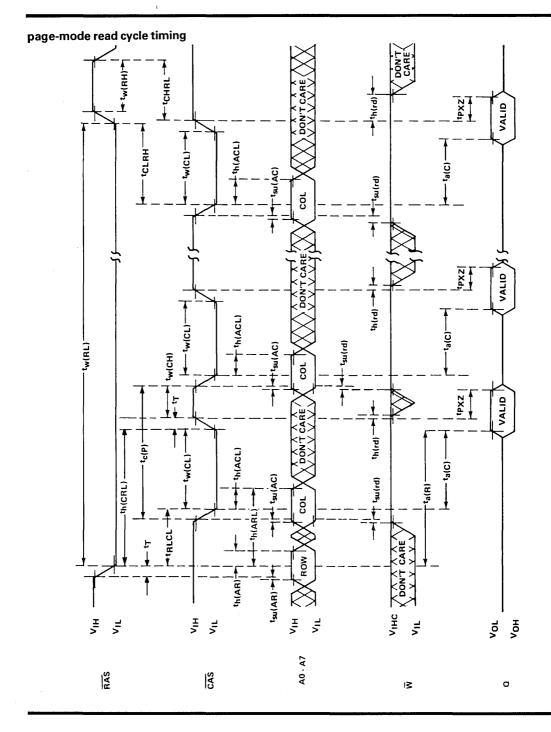

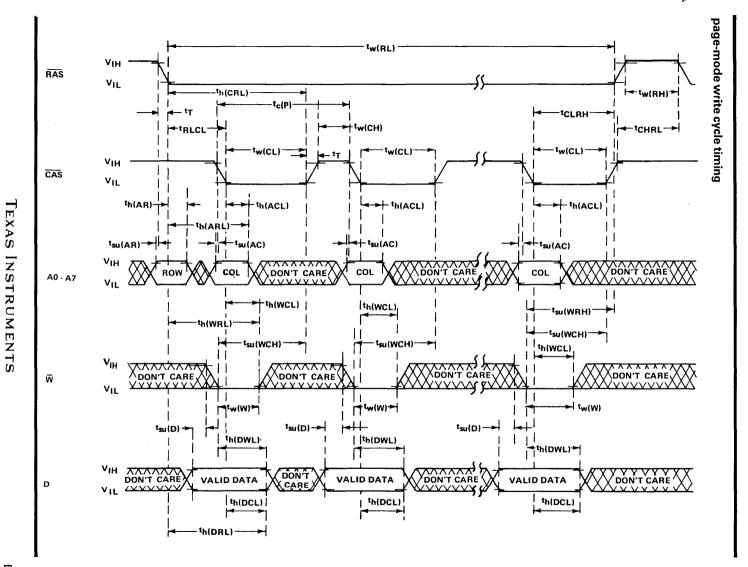

page-mode write cycle timing

TEXAS INSTRUMENTS

POST OFFICE BOX 225012 • DALLAS, TEXAS 75265

35

# TMS 4108 NL 8,192-BIT DYNAMIC RANDOM-ACCESS MEMORY

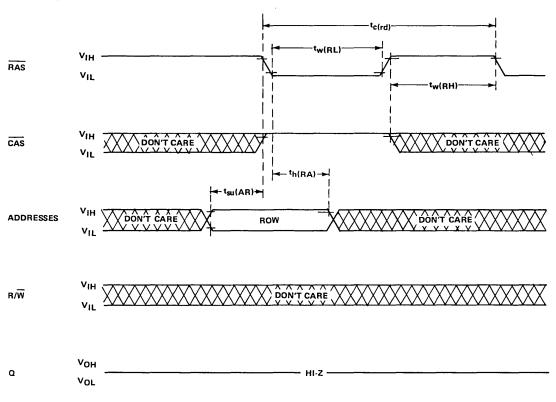

**RAS**-only refresh timing

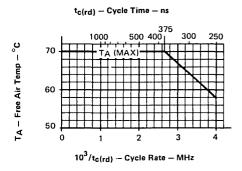

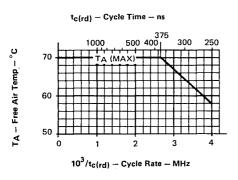

#### CYCLE RATE (& TIME) VS TEMPERATURE

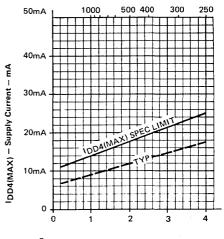

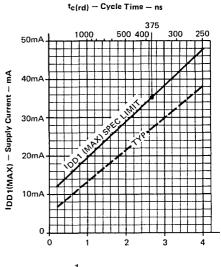

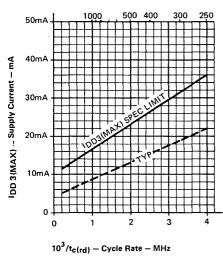

CYCLE RATE (& TIME) vs MAX SUPPLY CURRENT, I<sub>DD1</sub> t<sub>c</sub>(rd) — Cycle Time — ns

###

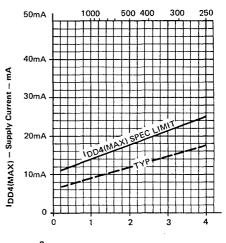

#### PAGE-MODE CYCLE RATE (& TIME) vs MAX SUPPLY CURRENT, IDD4

10<sup>3</sup>/t<sub>c(p)</sub> - Page-Mode Cycle Rate - MHz

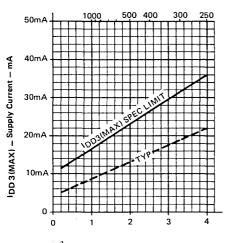

#### CYCLE RATE (& TIME) vs MAX SUPPLY CURRENT, IDD3

tc(rd) - Cycle Time - ns

10<sup>3</sup>/t<sub>c(rd)</sub> - Cycle Rate - MHz

### Texas Instruments

INCORPORATED POST OFFICE BOX 225012 • DALLAS, TEXAS 75265 PRINTED IN U.S.A. TI cannot assume any responsibility far any circuits shown ar represent that they are free from patent infringement.

37

TEXAS INSTRUMENTS RESERVES THE RIGHT TO MAKE CHANGES AT ANY TIME IN ORDER TO IMPROVE DESIGN AND TO SUPPLY THE BEST PRODUCT POSSIBLE.

<sup>10&</sup>lt;sup>3</sup>/t<sub>c(rd)</sub> - Cycle Rate - MHz

MOS

### TMS 4116 JDL, NL 16,384-BIT DYNAMIC RANDOM-ACCESS MEMORY

OCTOBER 1977

| • 10% Tolerand                                 | 6,384 X 1 Organization<br>10% Tolerance on All Supplies<br>All Inputs Including Clocks TTL <sub>-</sub> Compatible<br>Jnlatched Three-State Fully TTL-Compatible |                  |                  |            |       | 16-PIN CERAMIC AND PLASTIC<br>DUAL-IN-LINE PACKAGES<br>(TOP VIEW) |               |                 |    |                  |  |  |

|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|------------|-------|-------------------------------------------------------------------|---------------|-----------------|----|------------------|--|--|

| -                                              | -                                                                                                                                                                |                  | •                |            |       | v <sub>BB</sub>                                                   | 1             | )               | 16 | v <sub>ss</sub>  |  |  |

| 3 Performanc                                   | e Ranges:                                                                                                                                                        |                  |                  |            |       | D                                                                 | 2 [           |                 | 15 | CAS              |  |  |

|                                                | ACCESS<br>TIME                                                                                                                                                   | ACCESS<br>TIME   | READ<br>OR       | REA<br>MOD | •     | w                                                                 | 3 [           |                 | 14 | Q                |  |  |

|                                                | ROW                                                                                                                                                              | COLUMN           | WRITE            | WRI        |       | RAS                                                               | 4             | P               | 13 | A6               |  |  |

|                                                | ADDRESS<br>(MAX)                                                                                                                                                 | ADDRESS<br>(MAX) | CYCLE<br>(MIN)   | CYC<br>(MI |       | AO                                                                | 5 [           | þ               | 12 | A3               |  |  |

| TMS 4116-15<br>TMS 4116-20                     | 150 ns<br>200 ns                                                                                                                                                 | 100 ns<br>135 ns | 375 ns<br>375 ns | 375<br>375 |       | A2                                                                | 6 [           | þ               | 11 | A4               |  |  |

| TMS 4116-25                                    | 250 ns                                                                                                                                                           | 165 ns           | 410 ns           | 515        | ns    | A1                                                                | 7             |                 | 10 | A5               |  |  |

| Page-Mode O                                    |                                                                                                                                                                  |                  |                  | ł          |       | VDD                                                               | 8             | )               | 9  | vcc              |  |  |

| <ul> <li>Common I/O<br/>Feature</li> </ul>     | Capability                                                                                                                                                       | with "Earl       | y Write"         |            |       |                                                                   |               |                 |    |                  |  |  |

| Low-Power D                                    | -                                                                                                                                                                | <i>,</i> ,       |                  |            |       |                                                                   | PIN NOME      |                 | 2F |                  |  |  |

| <ul> <li>Operating</li> <li>Standby</li> </ul> | 462 mW<br>20 mW                                                                                                                                                  | • •              |                  |            | A0-A6 | Address Ir                                                        |               | W               |    | rite Enable      |  |  |

| •                                              |                                                                                                                                                                  |                  | <b>.</b> .       |            | CAS   | Column a                                                          | ddress strobe | V <sub>BB</sub> | !  | 5-V power supply |  |  |

|                                                | 1-T Cell Design, N-Channel Silicon-Gate                                                                                                                          |                  |                  |            | D     | Data input                                                        |               | Vcc             | +5 | 5-V power supply |  |  |

| rechnology                                     | Technology                                                                                                                                                       |                  |                  |            | ٥     | Data output                                                       |               | VDD             |    |                  |  |  |

| • 16-Pin 300-M                                 | il (7.62 mm                                                                                                                                                      | n) Package       | Configura        | ition      | RAS   | Row addr                                                          | ess strobe    | VSS             | 0  | V ground         |  |  |

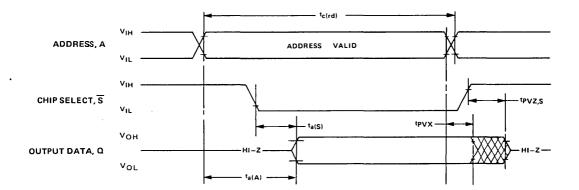

description

The TMS 4116 JL series is composed of monolithic high-speed dynamic 16,384-bit MOS random-access memories organized as 16,384 one-bit words, and employs single-transistor storage cells and N-channel silicon-gate technology.

All inputs and outputs are compatible with Series 74 TTL circuits including clocks: Row Address Strobe  $\overline{RAS}$  (or  $\overline{R}$ ) and Column Address Strobe  $\overline{CAS}$  (or  $\overline{C}$ ). All address lines (A0 through A6) and data-in (D) are latched on chip to simplify system design. Data out (Q) is unlatched to allow greater system flexibility.

Typical power dissipation is less than 350 milliwatts active and 6 milliwatts during standby (V<sub>CC</sub> is not required during standby operation). To retain data, only 10 milliwatts average power is required which includes the power consumed to refresh the contents of the memory.

The TMS 4116 series is offered in 16-pin dual-in-line sidebraze (JDL suffix), and plastic (NL suffix) packages and is guaranteed for operation from  $0^{\circ}$ C to  $70^{\circ}$ C. Packages are designed for insertion in mounting-hole rows on 300-mil (7.62 mm) centers.

#### operation

#### address (A0 through A6)

Fourteen address bits are required to decode 1 of 16,384 storage cell locations. Seven row-address bits are set up on pins A0 through A6 and latched onto the chip by the row-address strobe ( $\overline{RAS}$ ). Then the seven column-address bits are set up on pins A0 through A6 and latched onto the chip by the column-address strobe ( $\overline{CAS}$ ). All addresses must be stable on or before the falling edges of  $\overline{RAS}$  and  $\overline{CAS}$ .  $\overline{RAS}$  is similar to a chip enable in that it activates the sense amplifiers as well as the row decoder.  $\overline{CAS}$  is used as a chip select activating the column decoder and the input and output buffers.

<sup>†</sup>The term "read-write cycle" is sometimes used as an alternative title to "read-modify-write cycle".

#### write enable (W)

The read or write mode is selected through the write enable  $(\overline{W})$  input. A logic high on the  $\overline{W}$  input selects the read mode and a logic low selects the write mode. The write enable terminal can be driven from standard TTL circuits without a pull-up resistor. The data input is disabled when the read mode is selected. When  $\overline{W}$  goes low prior to  $\overline{CAS}$ , data-out will remain in the high-impedance state for the entire cycle permitting common I/O operation.

#### data-in (D)

Data is written during a write or read-modify write cycle. The latter falling edge of  $\overline{CAS}$  or  $\overline{W}$  strobes data into the on-chip data latch. This latch can be driven from standard TTL circuits without a pull-up resistor. In an early write cycle  $\overline{W}$  is brought low prior to  $\overline{CAS}$  and the data is strobed in by  $\overline{CAS}$  with setup and hold times referenced to this signal. In a delayed write or read-modify write cycle,  $\overline{CAS}$  will already be low, thus the data will be strobed in by  $\overline{W}$  with setup and hold times referenced to this signal.

#### data-out (Q)

The three state output buffer provides direct TTL compatibility (no pull-up resistor required) with a fan-out of two Series 74 TTL loads. Data-out is the same polarity as data-in. The output is in the high-impedance (floating) state until  $\overline{CAS}$  is brought low. In a read cycle the output goes active after the enable time interval  $t_a(C)$  that begins with the negative transition of  $\overline{CAS}$  as long as  $t_a(R)$  is satisfied. The output becomes valid after the access time has elapsed and remains valid while  $\overline{CAS}$  is low;  $\overline{CAS}$  going high returns it to a high-impedance state. In an early write cycle, the output is always in the high-impedance state. In a delayed write or read-modify-write cycle, the output will follow the sequence for the read cycle.

#### refresh

A refresh operation must be performed at least every two milliseconds to retain data. Since the output buffer is in the high-impedance state unless  $\overline{CAS}$  is applied, the  $\overline{RAS}$  only refresh sequence avoids any output during refresh. Strobing each of the 128 row addresses (A0 through A6) with  $\overline{RAS}$  causes all bits in each row to be refreshed.  $\overline{CAS}$  remains high (inactive) for this refresh sequence, thus conserving power.

#### page mode

Page mode operation allows effectively faster memory access by keeping the same row address and strobing successive column addresses onto the chip. Thus, the time required to setup and strobe sequential row addresses on the same page is eliminated. To extend beyond the 128 column locations on a single RAM, the row address and RAS is applied to multiple 16K RAMs CAS is decoded to select the proper RAM.

#### power-up

VBB must be applied to the device either before or at the same time as the other supplies and removed last. Failure to observe this precaution will cause dissipation in excess of the absolute maximum ratings due to internal forward bias conditions. This also applies to system use, where failure of the VBB supply must immediately shut down the other supplies. After power up, eight memory cycles must be performed to achieve proper device operation.

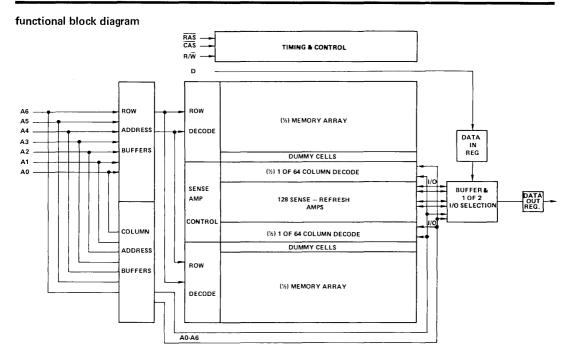

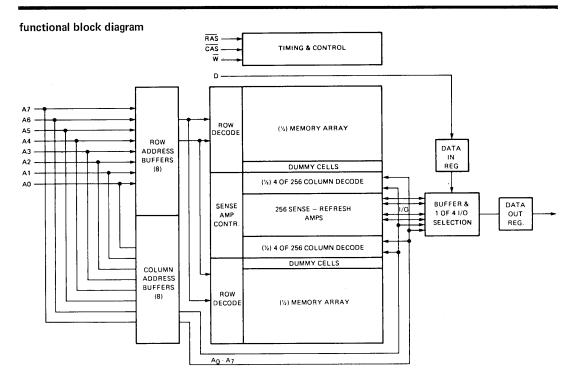

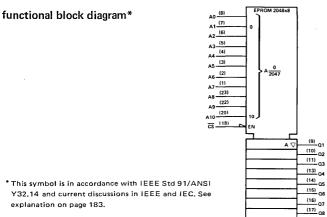

#### functional block diagram

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)\*

| Voltage on any pin (see Note 1)              |     |   |   |     |   |     |   |   |   |   |   |   |   | 0.5 to 20 V    |

|----------------------------------------------|-----|---|---|-----|---|-----|---|---|---|---|---|---|---|----------------|

| Voltage on VCC, VDD supplies with respect to | Vss |   |   |     |   |     |   |   |   |   |   |   |   | 1 to 15 V      |

| Short circuit output current                 |     |   |   |     |   |     |   |   |   |   |   |   |   | 50 mA          |

| Power dissipation                            |     |   |   |     |   | • • |   |   |   |   |   |   |   | 1W             |

| Operating free-air temperature range         |     |   |   |     |   |     |   |   |   |   |   |   |   | . 0°C to 70°C  |

| Storage temperature range                    | • • | • | • | ••• | · |     | · | · | • | · | · | • | • | -65°C to 150°C |

NOTE 1: Under absolute maximum ratings, voltage values are with respect to the most-negative supply voltage, VBB (substrate), unless otherwise noted. Throughout the remainder of this data sheet, voltage values are with respect to VSS.

\*Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the "Recommended Operating Conditions" section of this specification is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### recommended operating conditions

| PARAMETER                          |                                   | MIN  | NOM | MAX  | UNIT |

|------------------------------------|-----------------------------------|------|-----|------|------|

| Supply voltage, VBB                |                                   | -4.5 | -5  | -5.5 | V    |

| Supply voltage, V <sub>CC</sub>    |                                   | 4.5  | 5   | 5.5  | V    |

| Supply voltage, V <sub>DD</sub>    |                                   | 10.8 | 12  | 13.2 | V    |

| Supply voltage, VSS                |                                   | ·    | 0   |      | V    |

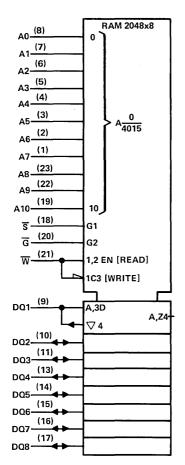

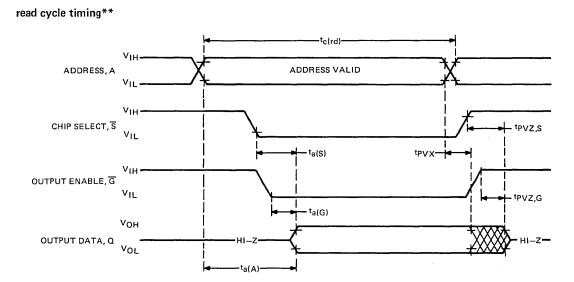

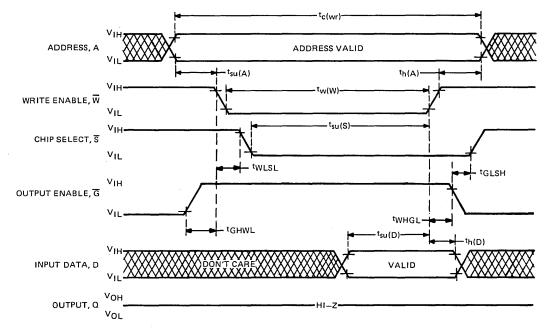

|                                    | All inputs except RAS, CAS, WRITE | 2.4  |     | 7    |      |