# Linear and Interface Circuits Applications

Volume 2: Line Circuits, Display Drivers

## Linear and Interface Circuits Applications

## Volume 2

## Line Circuits and Display Drivers

D.E. Pippenger and E.J. Tobaben Linear Applications

Contributors C.L. McCollum and Field Applications Engineering

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes in the devices or the device specifications identified in this publication without notice. TI advises its customers to obtain the latest version of device specifications to verify, before placing orders, that the information being relied upon by the customer is current.

TI warrants performance of its semiconductor products, including SNJ and SMJ devices, to current specifications in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems such testing necessary to support this warranty. Unless mandated by government requirements, specific testing of all parameters of each device is not necessarily performed.

In the absence of written agreement to the contrary, TI assumes no liability for TI applications assistance, customer's product design, or infringement of patents or copyrights of third parties by or arising from use of semiconductor devices described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor devices might be or are used.

ISBN-0-89512-185-9

Copyright © 1985, Texas Instruments Incorporated

## Contents

#### *Title* Section 8 Display Drivers

| DISPLAY DRIVERS                                                 | 8.1  |

|-----------------------------------------------------------------|------|

| Introduction to Display Driver Technology                       |      |

| LED Display Drivers                                             |      |

| SN75491 and SN75491A Quad LED Segment Drivers                   |      |

| SN75492 and SN75492A Hex LED Digit Drivers                      |      |

| SN75492 and SN75492A Hex LED Digit Drivers                      |      |

| SN75494 Hex LED Digit Diver                                     |      |

|                                                                 |      |

| Driving LED Displays                                            |      |

| Other Applications                                              |      |

| DC Plasma Display Drivers                                       |      |

| SN75480 DC Plasma Driver                                        |      |

| SN75480 Application                                             |      |

| SN75581 Gas Discharge Source Driver                             |      |

| SN75581 Application                                             |      |

| SN75584A High-Voltage 7-Segment Latch/Decoder/Cathode Driver    |      |

| SN75584A Application                                            |      |

| AC Plasma Display Drivers                                       |      |

| AC Plasma Display Technology                                    |      |

| Construction                                                    |      |

| The Functional Cell                                             |      |

| Control Circuitry Implementation with the SN75500A and SN75501C | 8-17 |

| The Functional Waveforms                                        | 8-19 |

| SN75500A AC Plasma Display Axis Driver                          | 8-21 |

| SN75501C AC Plasma Display Axis Driver                          | 8-24 |

| Functional Adaptation of the SN75500A and SN75501C              | 8-24 |

| Strobing and Sustaining                                         | 8-24 |

| Floating Driver Considerations                                  | 8-25 |

| Data Coupling Considerations                                    | 8-27 |

| Vacuum Fluorescent Displayer                                    | 8-29 |

| Introduction                                                    | 8-29 |

| The VFD Panel                                                   | 8-29 |

| Construction                                                    | 8-29 |

| Panel Performance                                               | 8-30 |

| VFD Timing Requirements                                         | 8-31 |

| Drive Electronics                                               | 8-31 |

| The UCN4810A 10-Bit VFD Driver                                  | 8-31 |

| The TL4810A 10-Bit VFD Driver                                   | 8-32 |

| The SN75512A 12-Bit VFD Driver                                  | 8-33 |

| The SN75513A 12-Bit VFD Driver                                  | 8-33 |

| The SN75514 High Voltage 12-Bit VFD Driver                      |      |

| The SN75518 32-Bit VFD Driver                                   |      |

| The SN75501C as a 32-Bit High-Voltage VFD Driver                |      |

| VFD Driver Applications                                         |      |

| Driving a Vacuum Fluorescent Character Display                  |      |

| Driving a Dot Matrix Display                                    |      |

|                                                                 | 0.50 |

Page

#### Tiltle

| Tiltle                                                | Page |

|-------------------------------------------------------|------|

| AC Thin Film Electroluminescent Display Drivers       | 8-42 |

| AC TFEL Display Technology                            | 8-42 |

| Factors Affecting TFEL Display Brightness             | 8-42 |

| AC TFEL Pixel Equivalent Circuit                      | 8-43 |

| Drivers for AC TFEL Panels                            | 8-43 |

| SN75551 and SN75552 Electroluminescent Row Drivers    | 8-44 |

| SN75553 and SN75554 Electroluminescent Column Drivers | 8-44 |

| Driving AC TFEL Panels                                | 8-44 |

| Practical Refresh Drive Scheme                        | 8-44 |

| Theory of Operation                                   | 8-44 |

| Interconnecting the Drivers to the Panel              | 8-47 |

| Row Driver Operation                                  | 8-47 |

| Column Driver Operation                               | 8-47 |

| Row and Column Driver Requirements                    | 8-47 |

| Row Driver Voltage Supply                             | 8-48 |

| Composite Row Driver                                  | 8-49 |

| Specifying Driver Requirements                        | 8-50 |

### Section 9

#### **Data Transmission**

| DATA TRANSMISSION                                           | 9-1  |

|-------------------------------------------------------------|------|

| General Purpose Data Transmission                           | 9-1  |

| General Requirements                                        | 9-1  |

| Types of Transmission Lines                                 | 9-1  |

| Single Wire and Ground Plane                                | 9-1  |

| Two-Wire Interconnect                                       | 9-2  |

| Twisted Pair                                                | 9-2  |

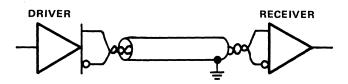

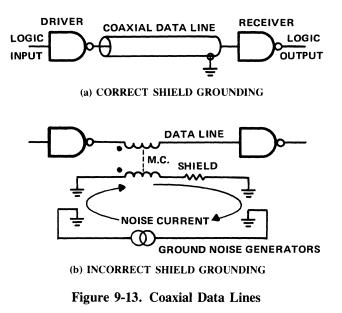

| Coaxial Lines                                               | 9-4  |

| Line Drivers                                                | 9-4  |

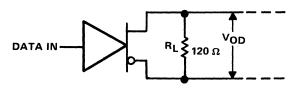

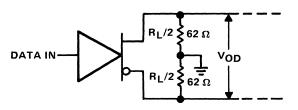

| Basic Driver Modes                                          | 9-5  |

| Types of Transmission                                       | 9-5  |

| Single-Ended Transmission                                   | 9-5  |

| Single-Ended Application for High-Speed Bus Communication   | 9-8  |

| Differential Line Drivers and Receivers                     | 9-11 |

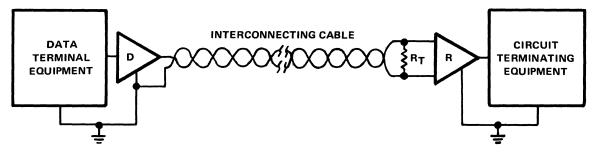

| Terminating Differential Data Transmission                  | 9-12 |

| Current-Mode Drivers in Differential Data Line Transmission | 9-13 |

| Receiver Performance                                        | 9-15 |

| Input Sensitivity                                           | 9-15 |

| Common-Mode Voltage Range                                   | 9-15 |

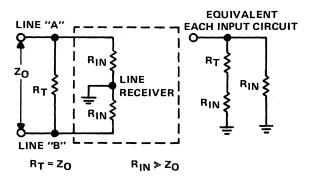

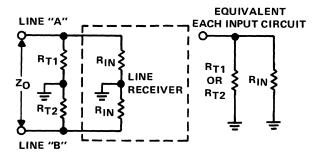

| Input Termination Resistors                                 | 9-16 |

| Reference Voltage                                           | 9-16 |

| Input Limitations                                           | 9-17 |

| SN55/75107A Series Applications                             | 9-17 |

| Connection of Unused Inputs and Outputs                     | 9-17 |

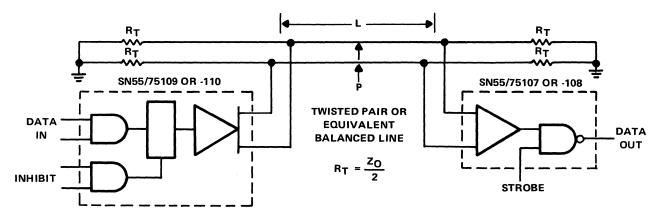

| One-Channel Balanced Transmission System                    | 9-17 |

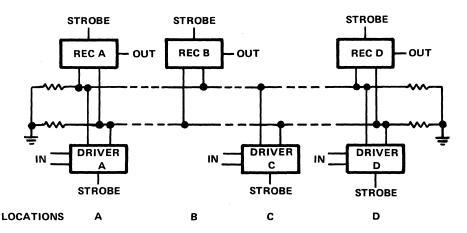

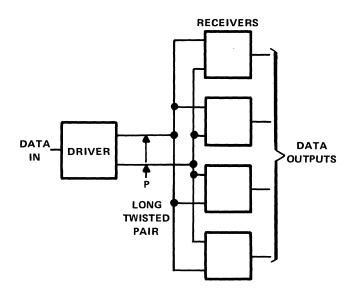

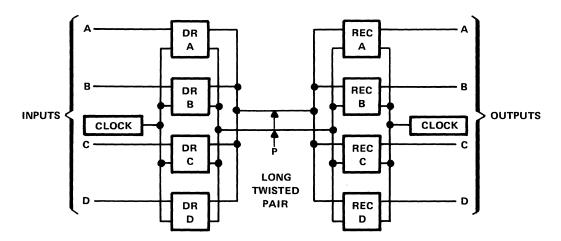

| Differential Party-Line Systems                             | 9-17 |

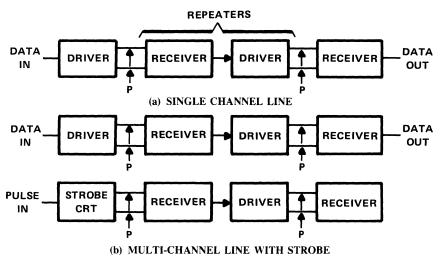

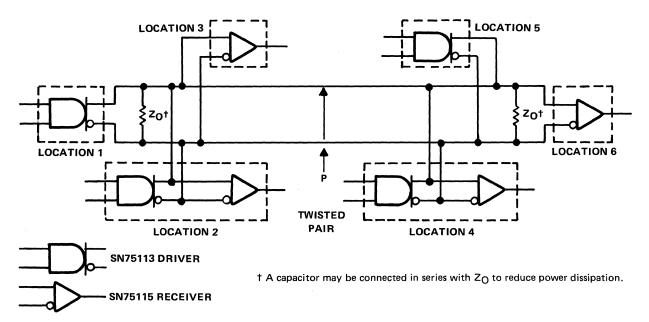

| Repeaters for Long Lines                                    | 9-18 |

| Standard Voltage-Mode Differential Drivers and Receivers    | 9-19 |

| EIA Standard RS-232-C Circuits and Applications             | 9-22 |

| Typical Drivers for EIA RS-232-C Applications               | 9-22 |

| SN75150 Dual Data Line Driver                               | 9-22 |

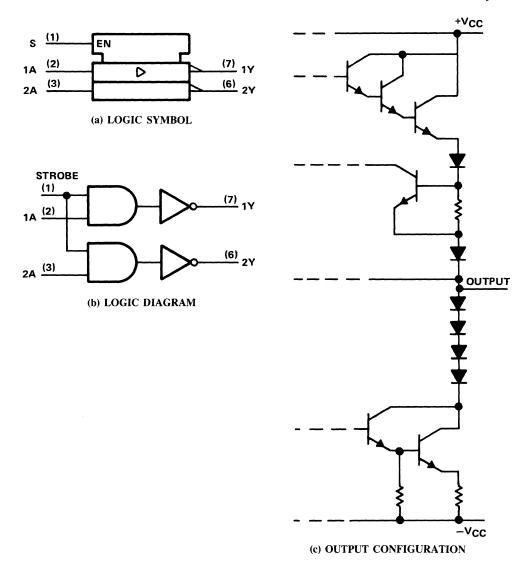

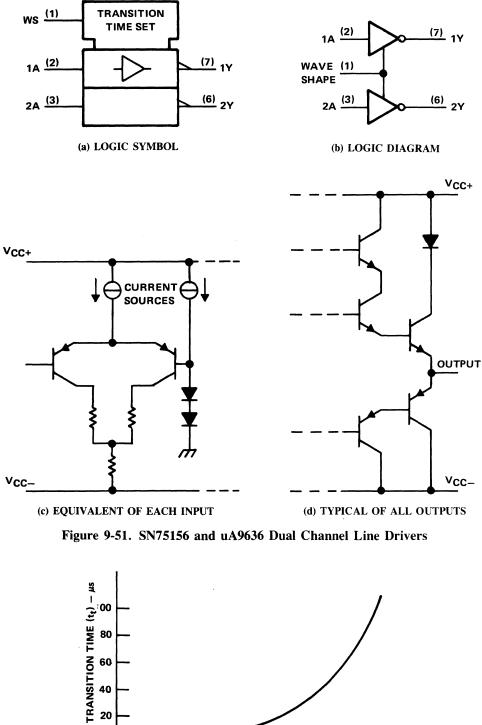

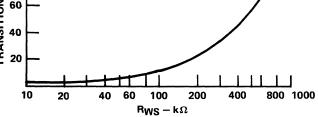

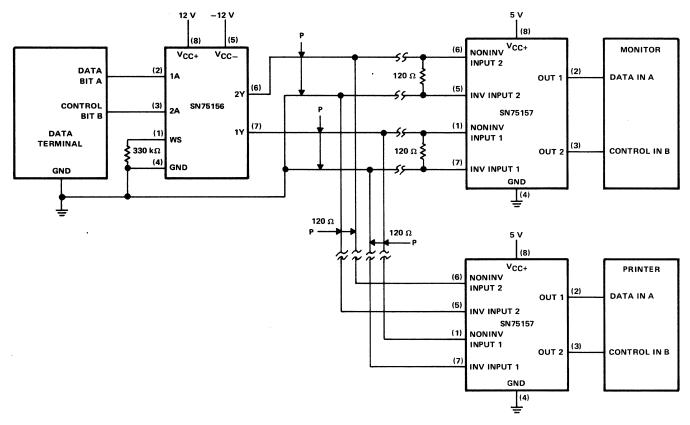

| SN75156/uA9636 Dual Line Driver                             | 9-22 |

| SN75188/MC1488 Quad Line Driver                             | 9-24 |

| Title                                                          | Page |

|----------------------------------------------------------------|------|

| Typical Receivers for EIA RS-232-C Applications                | 9-24 |

| SN75152 Dual Data Line Receiver                                | 9-24 |

| SN75154 Quad Data Line Receiver                                |      |

| SN75189, SN75189A, MC1489 and MC1489A Quad Line Receivers      | 9-29 |

| RS-232-C Applications                                          | 9-32 |

| Interface Using SN75150 and SN75154                            |      |

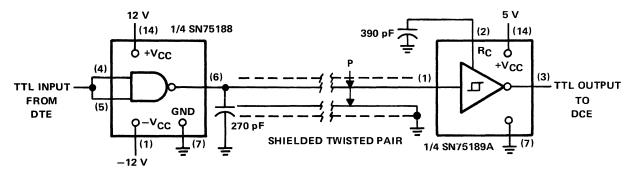

| Typical Interface Using SN75188 and SN75189A                   | 9-33 |

| EIA Standard RS-423-A Circuits and Applications                | 9-33 |

| RS-423-A Standard                                              | 9-33 |

| RS-423-A Devices                                               |      |

| RS-423-A Drivers                                               |      |

| RS-423-A Receivers                                             |      |

| Basic RS-423-A Application                                     | 9-36 |

| EIA Standard RS-422-A and RS-485 Circuits and Applications     |      |

| RS-422-A Standard                                              |      |

| RS-422-A Applications                                          | 9-40 |

| Typical Application                                            | 9-40 |

| Short-Line Application                                         | 9-40 |

| EIA RS-485 Standard                                            | 9-40 |

| Unit Load Circuit                                              |      |

| Drivers and Receivers                                          | 9-41 |

| Driver Details                                                 | 9-42 |

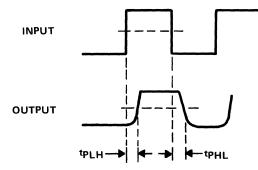

| Driver Speed Characteristics                                   | 9-43 |

| Receiver Details                                               | 9-44 |

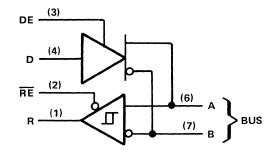

| Transceivers                                                   | 9-45 |

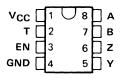

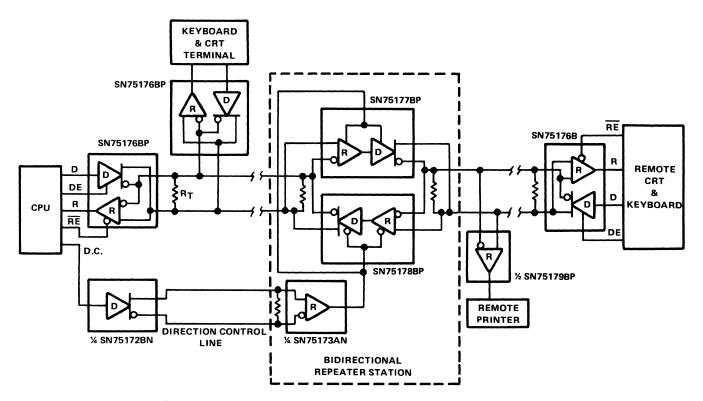

| SN75176B, SN75177B, SN75178B and SN75179B Transceiver Features | 9-45 |

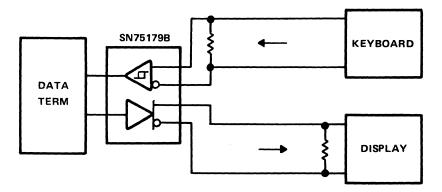

| Basic Transceiver Application                                  | 9-45 |

| Long-Line Application                                          | 9-46 |

| SN75179B Application                                           | 9-46 |

| IEEE 488-1978 Transmission Systems                             | 9-46 |

| The IEEE-488 Standard                                          | 9-46 |

| General Information                                            | 9-46 |

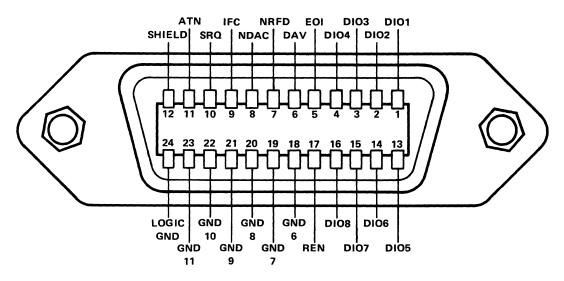

| Connectors                                                     | 9-48 |

| Cable                                                          | 9-49 |

| Logic Convention                                               | 9-49 |

| Functions                                                      | 9-49 |

| Messages or Commands                                           | 9-50 |

| Bus Interface Devices                                          | 9-51 |

| Electrical Specifications                                      | 9-52 |

| Driver Requirements                                            | 9-52 |

| Driver Specifications                                          | 9-52 |

| Receiver Specifications                                        | 9-52 |

| Composite Load Requirements                                    | 9-52 |

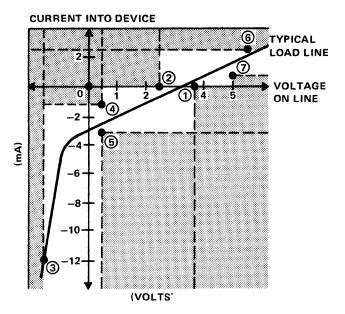

| Device DC Load Line Boundaries                                 | 9-52 |

| Device AC Load Line Limit                                      | 9-52 |

| Device Capacitive Load Limit                                   | 9-52 |

| Timing Values                                                  | 9-53 |

| Data Rates                                                     |      |

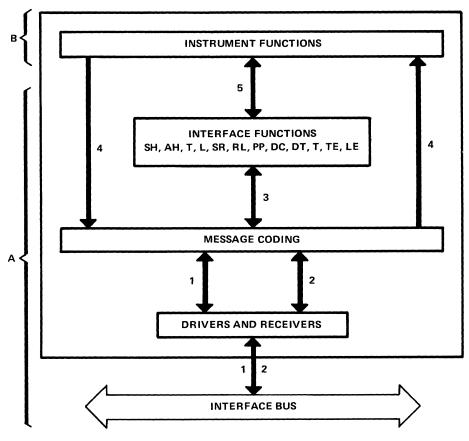

| Interfacing to the IEEE Standard 488 Bus                       | 9-53 |

| SN75160A Octal GPIB Transceiver                                |      |

| SN75163A Octal GPIB Transceiver                                | 9-54 |

| SN75161A and SN75162A Octal GPIB Transceiver                   |      |

| MC3446 Quad Bus Transceiver                                    | 9-56 |

| Typical Applications                                           |      |

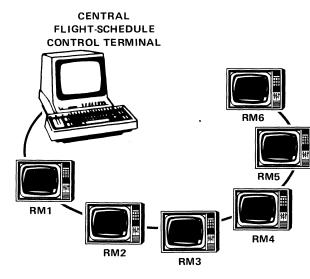

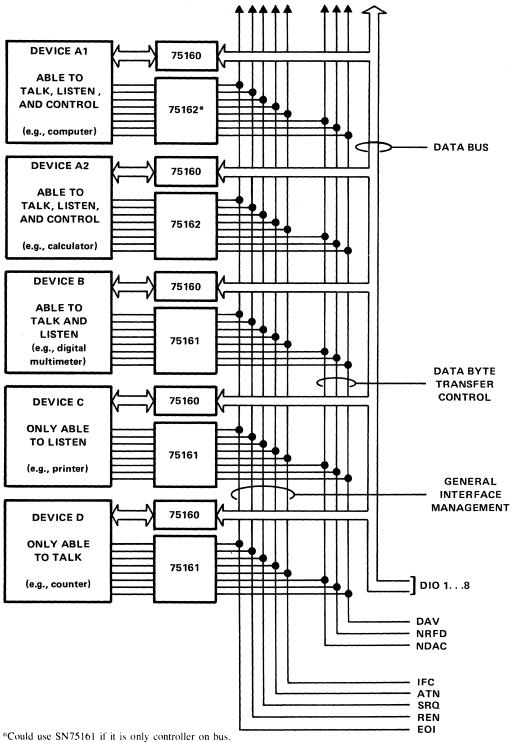

| A Typical IEEE-488 System Application                          | 9-57 |

ί,

٨

| Title                                               | Page |

|-----------------------------------------------------|------|

| IBM System 360/370 Interfacing Circuits             | 9-58 |

| Driver and Receiver Requirements                    |      |

| Driver Requirements                                 | 9-59 |

| Receiver Requirements                               | 9-62 |

| General Physical and Electrical Requirements        | 9-62 |

| Line Terminations                                   | 9-62 |

| Voltage Levels                                      | 9-62 |

| Cable                                               | 9-62 |

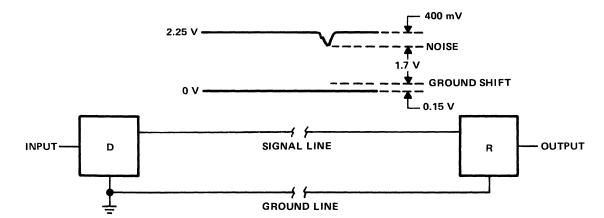

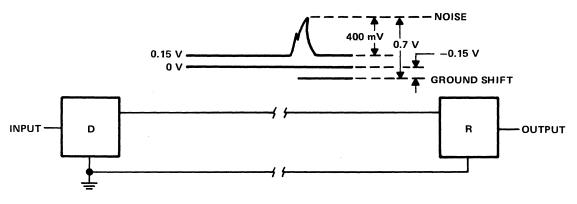

| Ground Shift and Noise                              | 9-62 |

| Fault Conditions                                    | 9-62 |

| Electrical Characteristics for Select Out Interface | 9-63 |

| Receiver Requirements                               | 9-63 |

| Driver Requirements                                 | 9-63 |

| IBM System/360 and System/370 Data Line Drivers     | 9-63 |

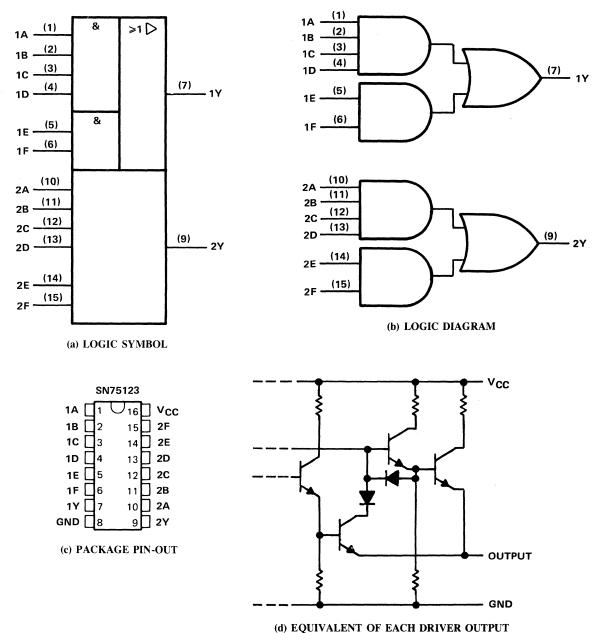

| SN75123 Dual Line Driver                            | 9-63 |

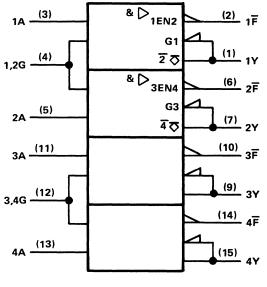

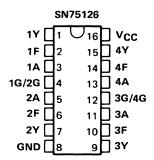

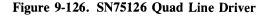

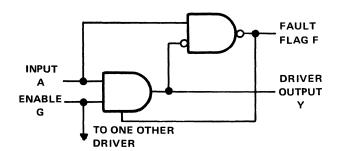

| SN75126 Quadruple Line Driver                       | 9-64 |

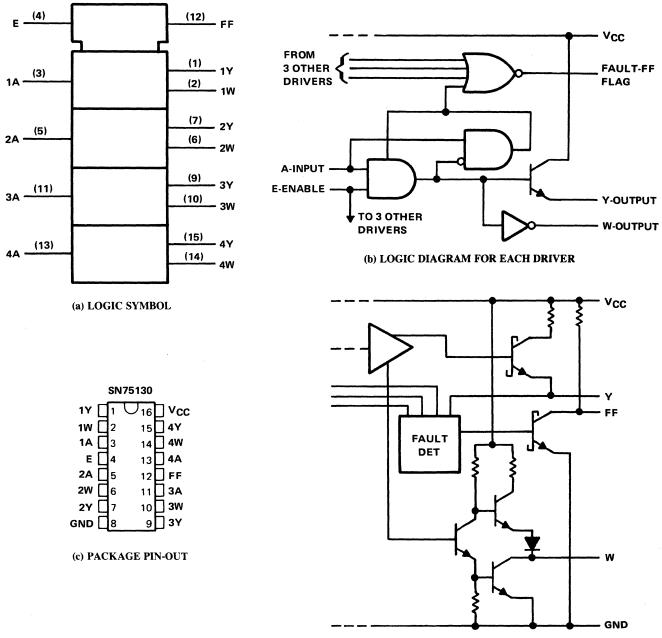

| SN75130 Quadruple Line Driver                       | 9-65 |

| IBM System/360 and System/370 Data Line Receivers   | 9-65 |

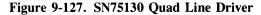

| SN75124 Triple Line Receiver                        | 9-65 |

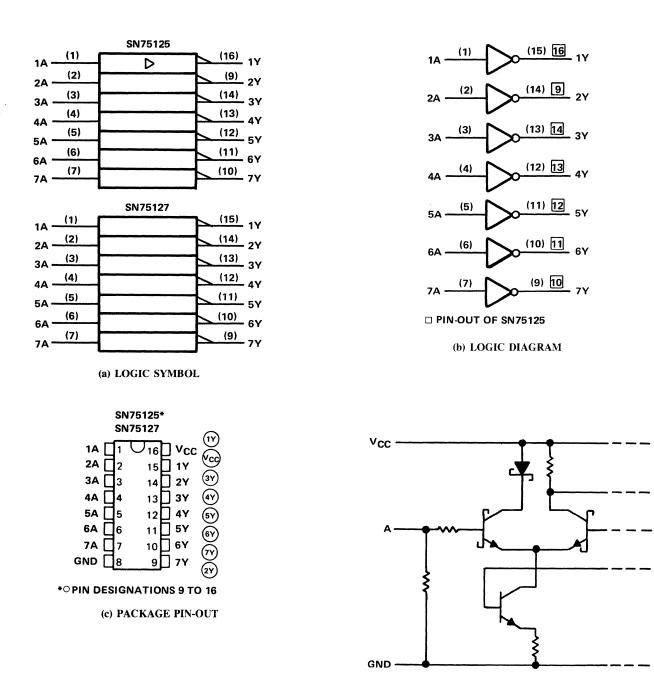

| SN75125 and SN75127 Seven-Channel Line Receivers    | 9-66 |

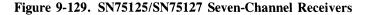

| SN75128 and SN75129 Octal Line Receivers            | 9-67 |

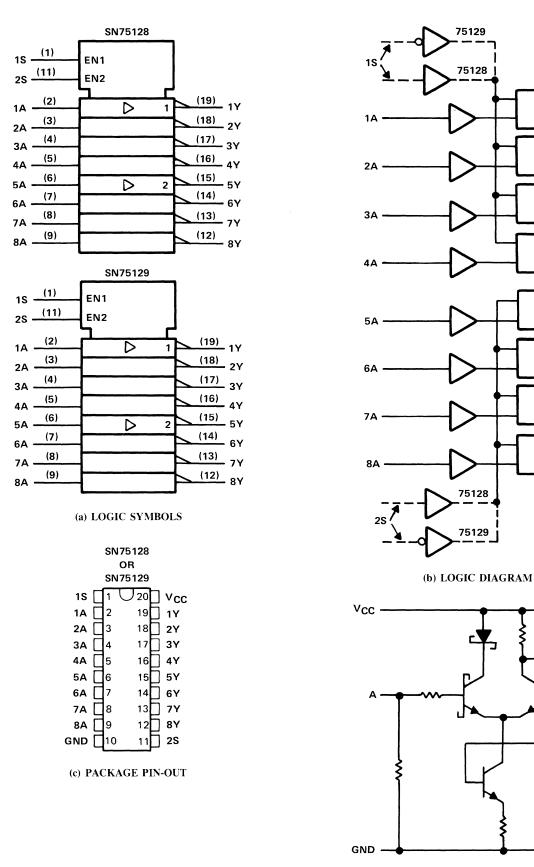

| IBM System 370 Application                          | 9-67 |

| Drivers                                             | 9-67 |

| Cable                                               | 9-68 |

| Receivers                                           | 9-68 |

## List of Illustrations

| Figure | Title                                                                     | Page |

|--------|---------------------------------------------------------------------------|------|

| 8-1    | BIDFET Cell Cross Section                                                 | 8-1  |

| 8-2    | RBSOA Curve and Load Line                                                 | 8-2  |

| 8-3    | Breakdown Characteristics                                                 | 8-2  |

| 8-4    | Characteristic Waveforms                                                  | 8-2  |

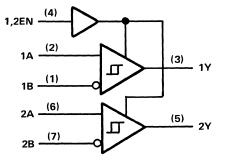

| 8-5    | SN75491 and SN75491A                                                      | 8-3  |

| 8-6    | SN75492 and SN75492A                                                      | 8-3  |

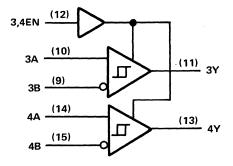

| 8-7    | SN75494                                                                   | 8-4  |

| 8-8    | SN75497 and SN75498                                                       | 8-5  |

| 8-9    | 12-Digit LED Numeric Display and Drive                                    | 8-6  |

| 8-10   | Quad or Hex Relay Driver                                                  | 8-7  |

| 8-11   | Quad or Hex Lamp Driver                                                   | 8-7  |

| 8-12   | Quad or Hex High-Current P-N-P Transistor Driver                          | 8-7  |

| 8-13   | Base/Emitter Select N-P-N Transistor                                      | 8-7  |

| 8-14   | MOS to TTL Level Shifter                                                  | 8-7  |

| 8-15   | Quad High-Current N-P-N Transistor Driver                                 | 8-7  |

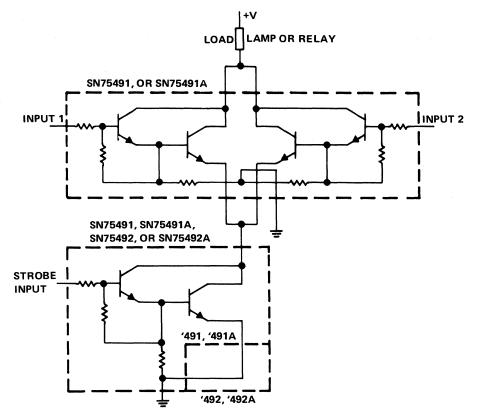

| 8-16   | Strobed NOR Driver                                                        | 8-8  |

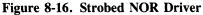

| 8-17   | SN75491/SN75491A Used as an Interface Circuit Between the Balanced 30-MHz | 00   |

| 0 17   | Output of an RF Amplifier and a Coaxial Cable                             | 8-8  |

| 8-18   | SN75480 DC Plasma Driver                                                  | 8-9  |

| 8-19   | SN75480 Function Table                                                    | 8-10 |

| 8-20   | Basic Digital Display Drive                                               | 8-11 |

| 8-21   | SN75581 Gas Discharge Driver                                              | 8-12 |

| 8-22   | SN75581 Typical Operating Sequence                                        | 8-12 |

| 8-23   | Typical SN75581 Application                                               | 8-13 |

| 8-24   | SN75584A DC Plasma Segment Driver                                         | 8-13 |

| 8-25   | SN75584A Segment Output Current vs Program Resistance                     | 8-14 |

| 8-26   | SN75584A Function Table                                                   | 8-14 |

| 8-27   | Three-Digit Display Driver Application                                    | 8-15 |

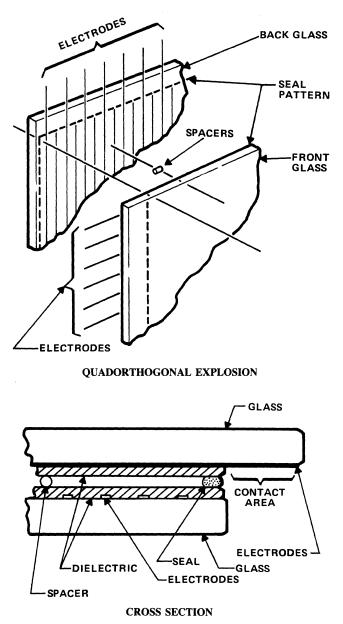

| 8-28   | Panel Construction                                                        | 8-16 |

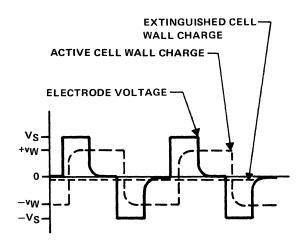

| 8-29   | Cell Waveforms                                                            | 8-17 |

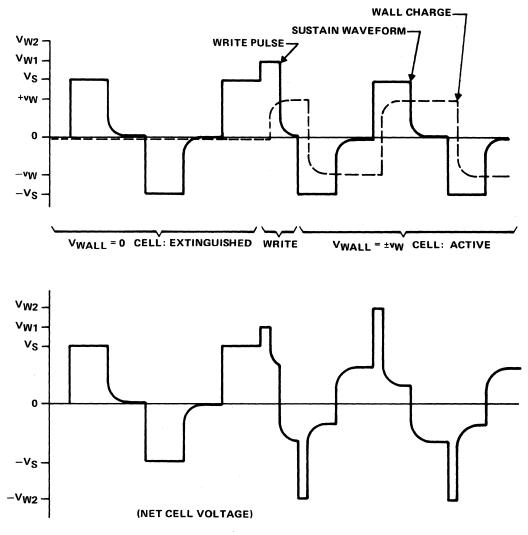

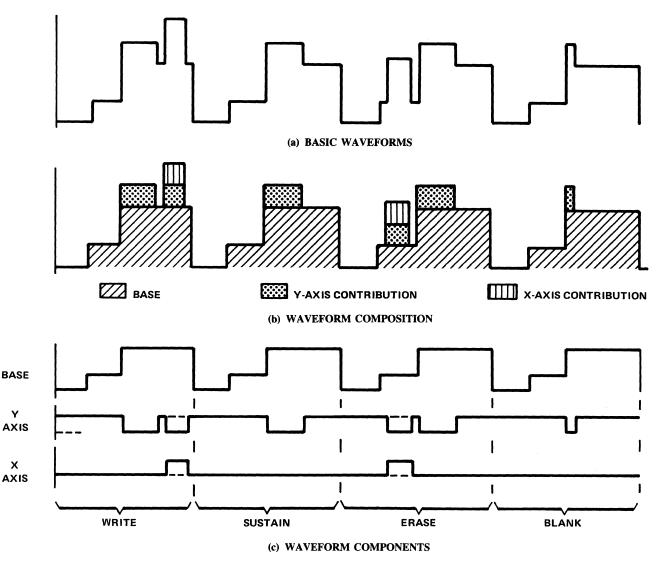

| 8-30   | Write-Sustain Cycle Cell Waveforms                                        | 8-18 |

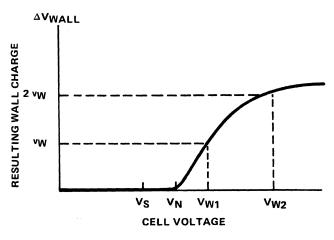

| 8-31   | Charge Transfer Characteristics of AC Plasma Cell                         | 8-18 |

| 8-32   | Sustain-Erase Cycle Cell Waveforms                                        | 8-19 |

| 8-33   | Functional Waveforms                                                      | 8-20 |

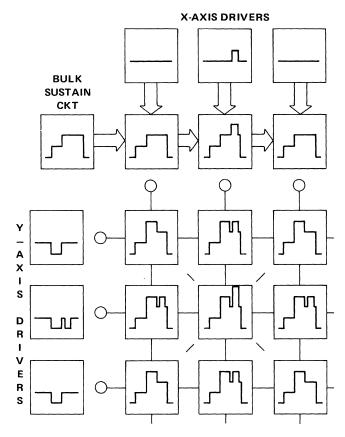

| 8-34   | Write Waveform Array and Origin                                           | 8-20 |

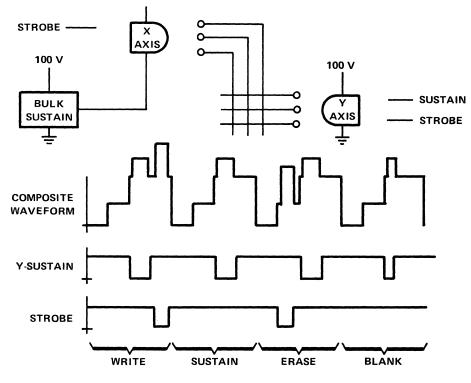

| 8-35   | Control Signal Timing                                                     | 8-21 |

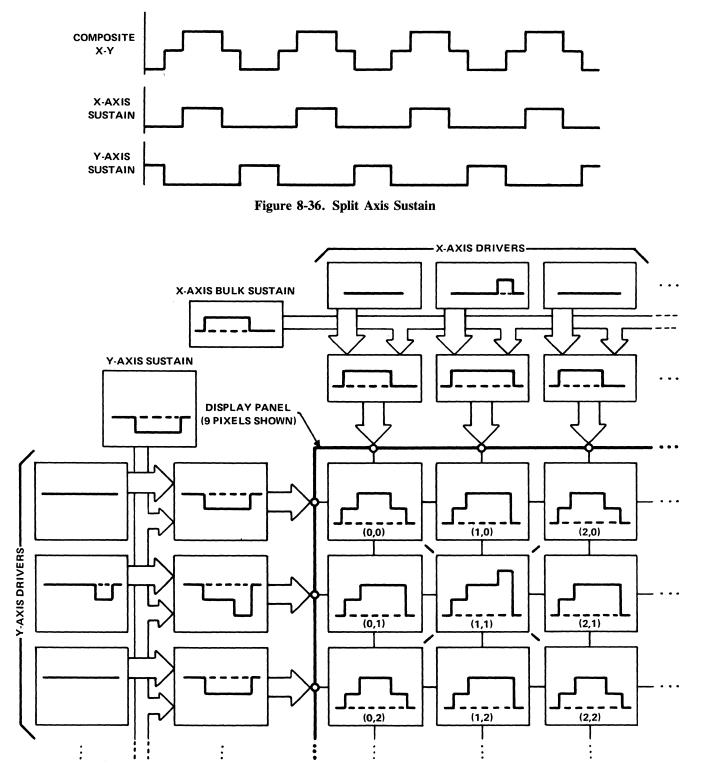

| 8-36   | Split Axis Sustain                                                        | 8-22 |

| 8-37   | Write Waveform Array and Origin Split Axis Sustain — Blanking Select      | 8-22 |

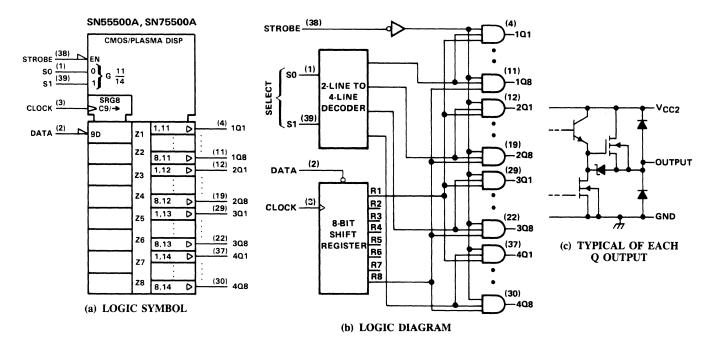

| 8-38   | SN55500A and SN75500A                                                     | 8-23 |

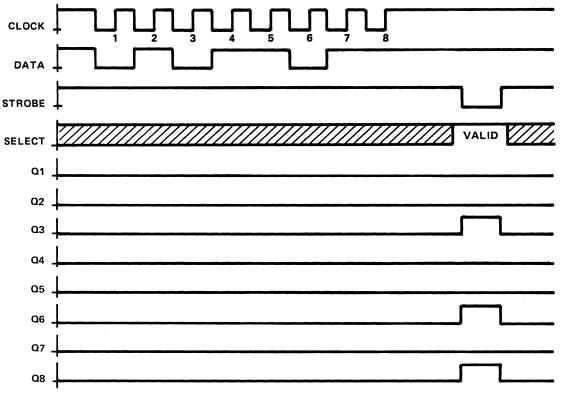

| 8-39   | Typical Operating Sequence — SN75500A                                     | 8-23 |

| 8-40   | SN55501C and SN75501C                                                     | 8-24 |

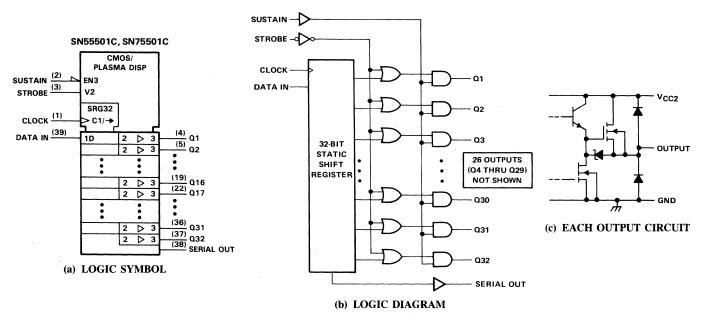

| 8-41   | Typical Operating Sequence — SN75501C                                     | 8-24 |

| 8-42   | SN75500A and SN75501C Output Structure                                    | 8-25 |

| 8-43   | Floating SN75501C Current Paths                                           | 8-25 |

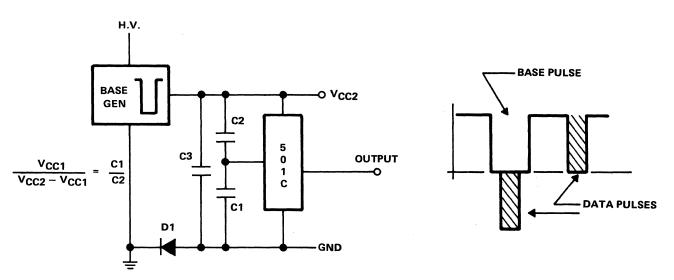

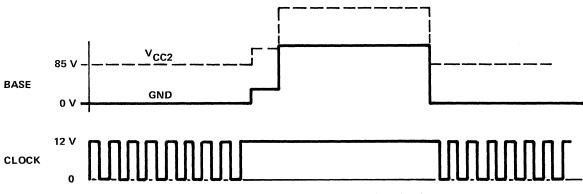

| 8-44   | SN75501C with Pulsed V <sub>CC2</sub>                                     | 8-26 |

| 8-45   | Floating SN75501C Fixed Bias                                              | 8-26 |

| 5 75   | 1 Journey 014/05/010 1 IAOU DI05                                          | 0-20 |

| Figure       | Title                                                                 | Page         |

|--------------|-----------------------------------------------------------------------|--------------|

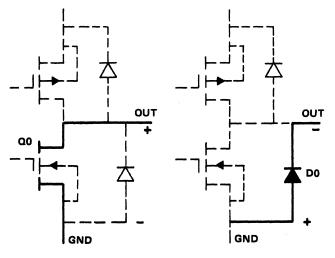

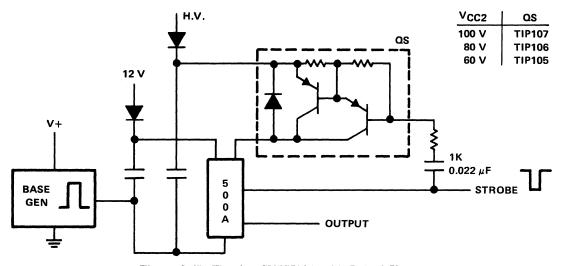

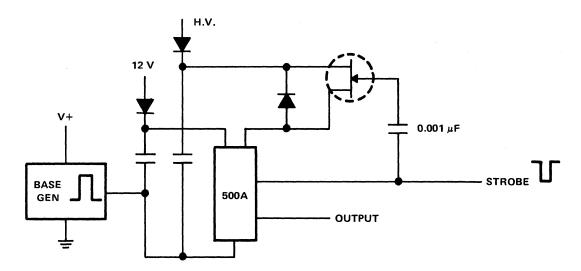

| 8-46         | Floating SN75500A Current Paths                                       | 8-27         |

| 8-47         | Floating SN75500A with Pulsed V <sub>CC2</sub>                        | 8-27         |

| 8-48         | Floating SN75500A with FET Pulsed V <sub>CC2</sub>                    | 8-28         |

| 8-49         | Gated Clock for Floating Applications                                 | 8-28         |

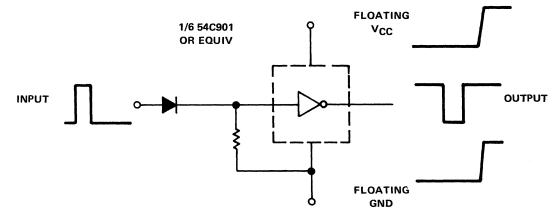

| 8-50         | Positive Base Signal Data Buffer Circuit                              | 8-28         |

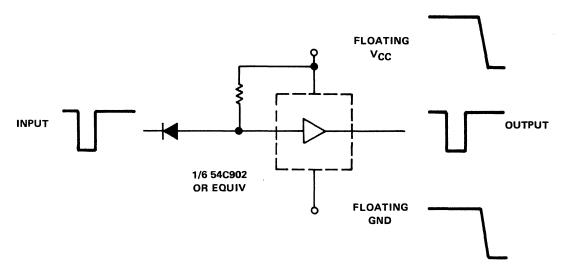

| 8-51         | Negative Base Signal Data Buffer Circuit                              | 8-29         |

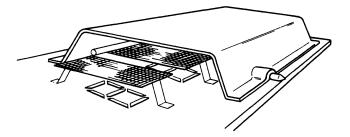

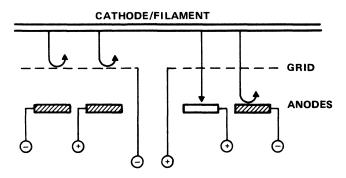

| 8-52         | Vacuum Fluorescent Display Construction                               | 8-29         |

| 8-53         | Vacuum Fluorescent Display Electron Flow                              | 8-29         |

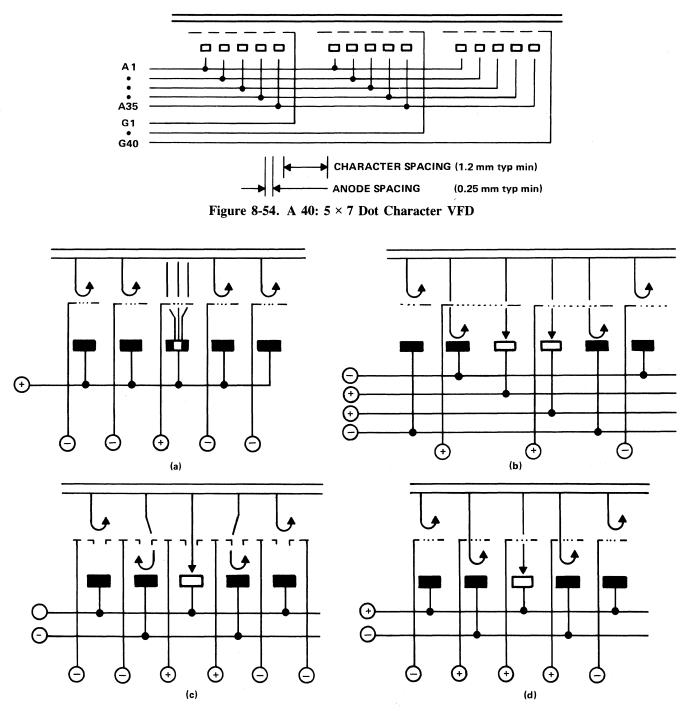

| 8-54         | A 40: 5 × 7 Dot Character VFD                                         | 8-30         |

| 8-55         | Grid-Anode Configurations of Dot Matrix VFDs                          | 8-30         |

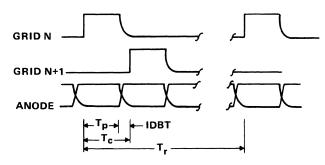

| 8-56         | VFD Timing Diagram                                                    | 8-31         |

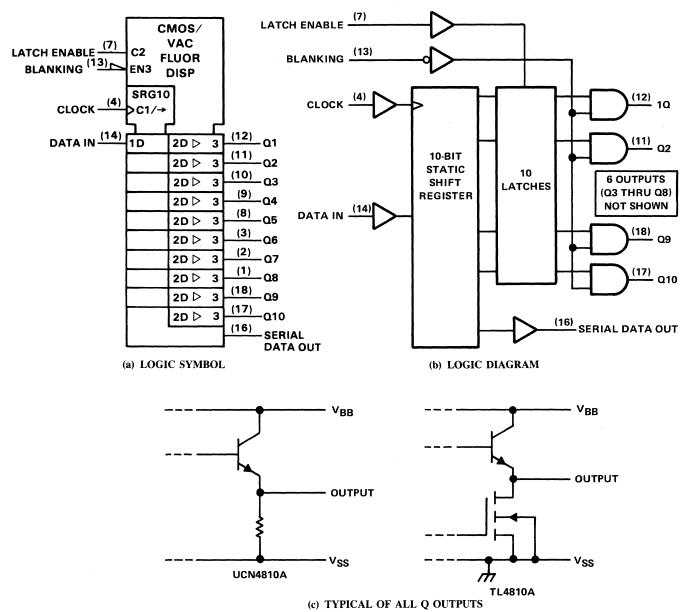

| 8-57         | UCN4810A and TL4810A VFD Display Drivers                              | 8-32         |

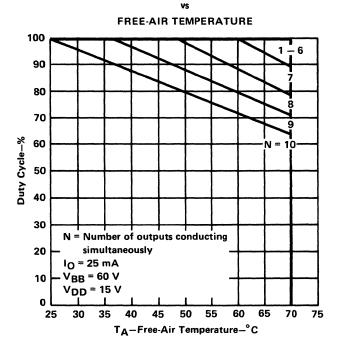

| 8-58         | UCN4810A Operational Duty Cycle                                       | 8-33         |

| 8-59         | SN75512A 12-Bit VFD Driver                                            | 8-34         |

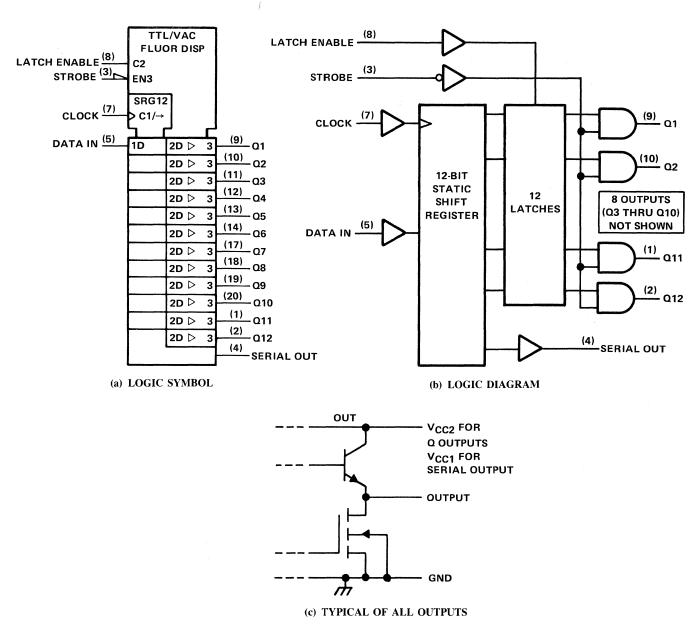

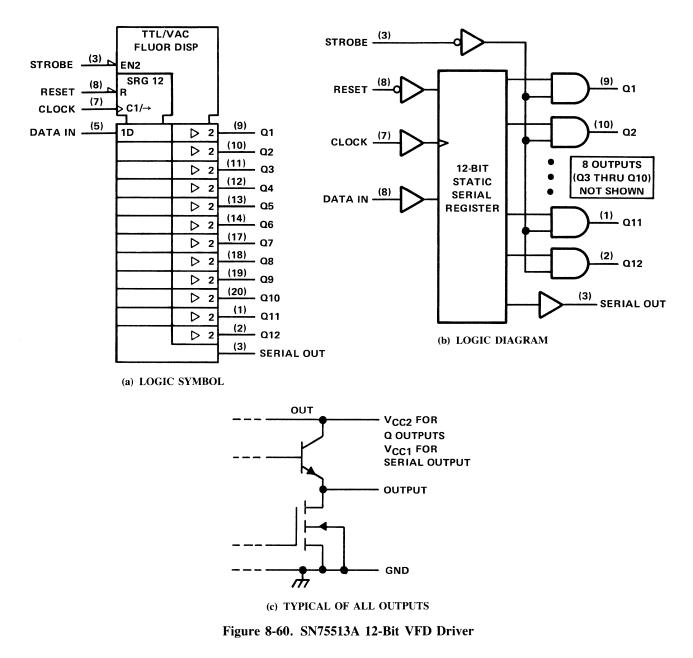

| 8-60         | SN75513A 12-Bit VFD Driver                                            | 8-35         |

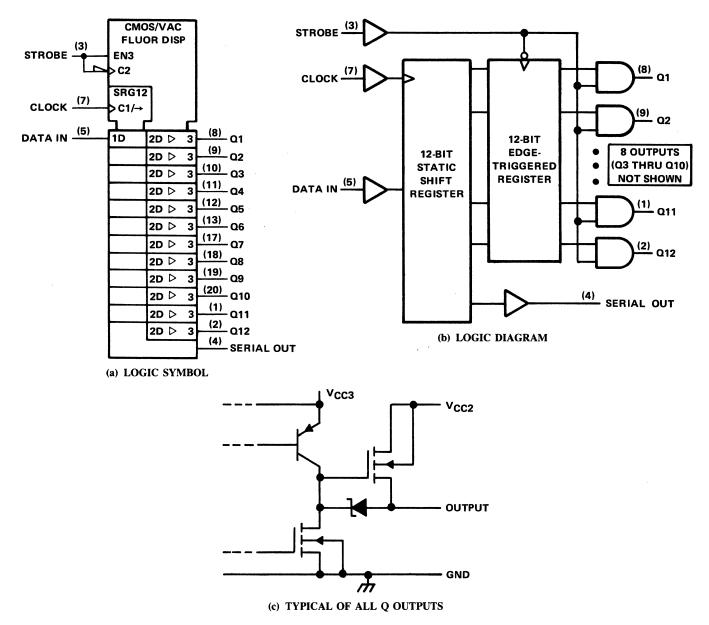

| 8-61         | SN75514 12-Bit VFD Driver                                             | 8-36         |

| 8-62         | SN75518 VFD Driver                                                    | 8-37         |

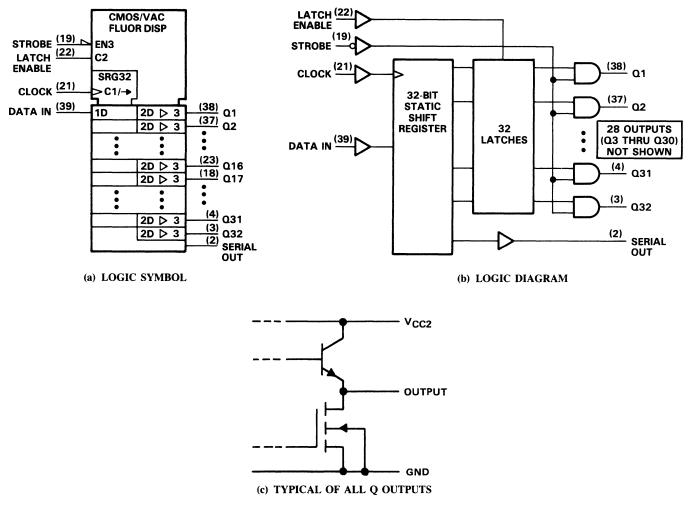

| 8-63         | SN75501C VFD Driver                                                   | 8-38         |

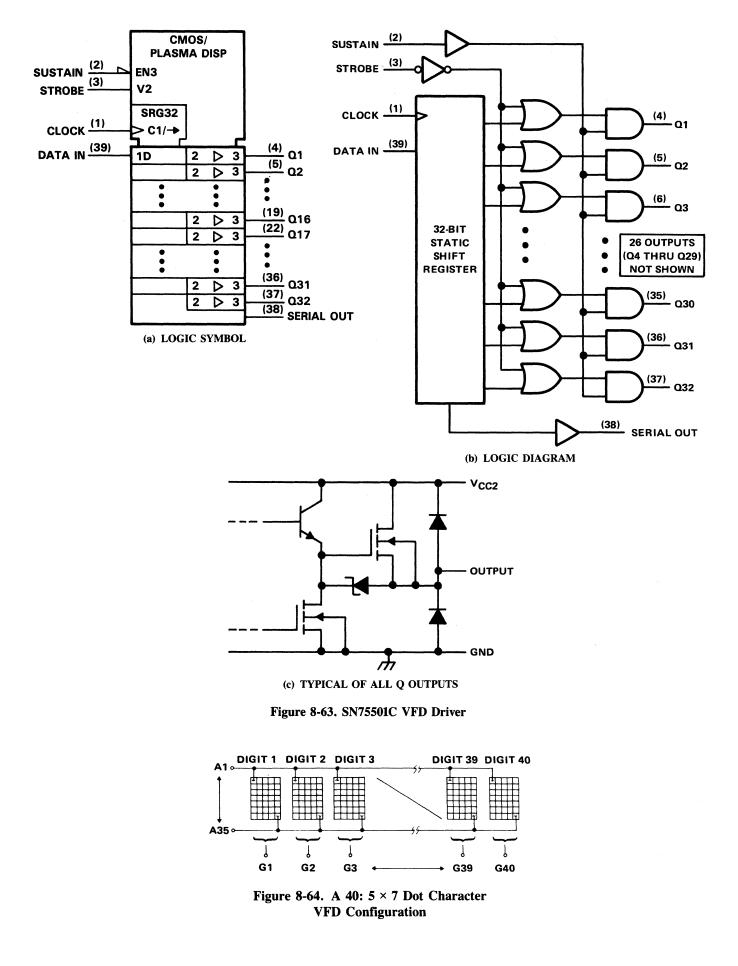

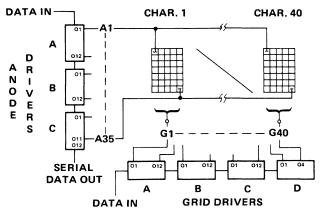

| 8-64         | A 40: $5 \times 7$ Dot Character VFD Configuration                    | 8-38         |

| 8-65         | A 40: $5 \times 7$ Dot Character VFD Drive Scheme                     | 8-39         |

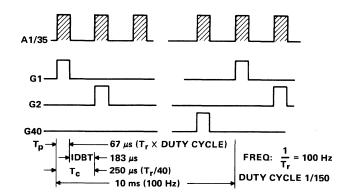

| 8-66         | A 40 Character VFD Timing Diagram                                     | 8-39         |

| 8-67         | Data Registration of an SN75512 12-Bit VFD with Latch                 | 8-39         |

| 8-68         | A $256 \times 64$ Dot Matrix VFD Pinout                               | 8-39         |

| 8-69         | Timing Diagram for VFD of SN75512                                     | 8-40         |

| 8-70         | A $128 \times 128$ Dot Matrix VFD Pinout                              | 8-40         |

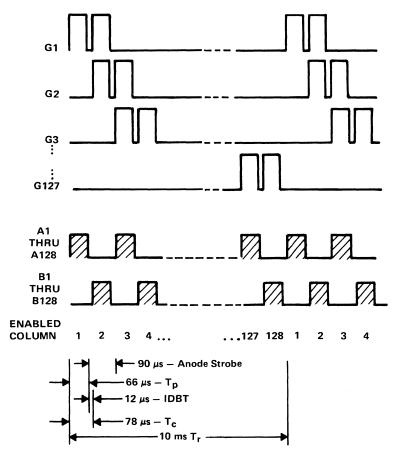

| 8-71         | Timing Diagram for VFD 1128 $\times$ 128 Dot Matrix                   | 8-41         |

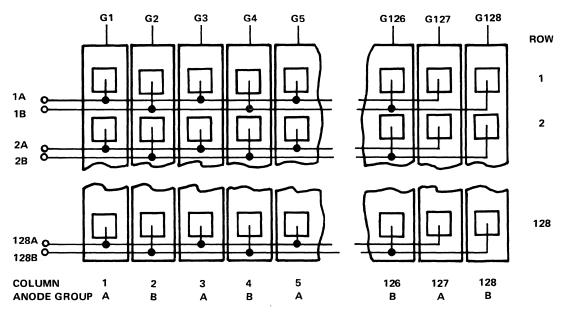

| 8-72         | A $128 \times 128$ Dot Matrix VFD Pinout                              | 8-41         |

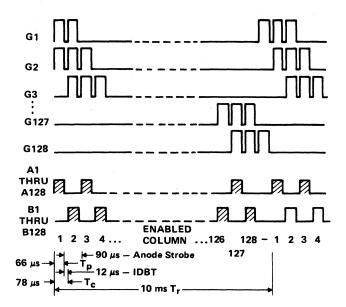

| 8-73         | Timing Diagram for VFD of $128 \times 128$ Dot Matrix Pinout          | 8-42         |

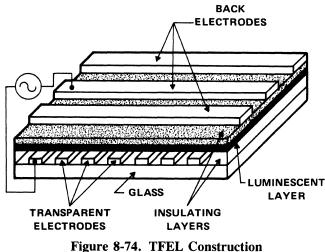

| 8-74         | TFEL Construction                                                     | 8-42         |

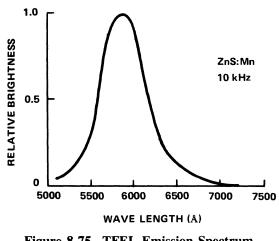

| 8-75         | TFEL Emission Spectrum                                                | 8-42         |

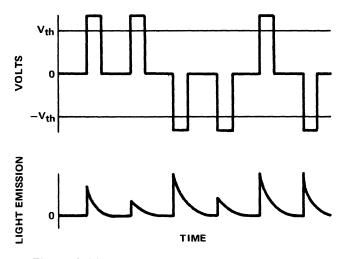

| 8-76         | Brightness Dependence on Polarity                                     | 8-43         |

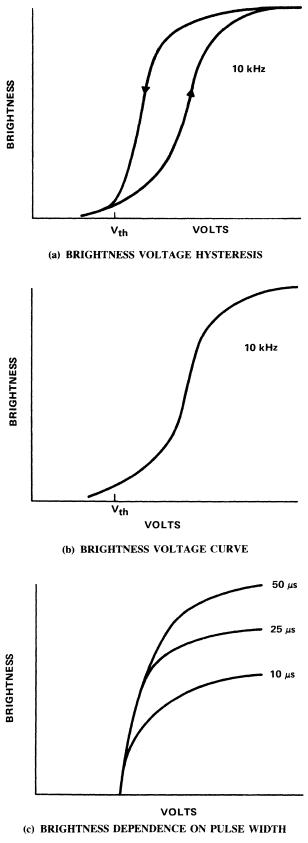

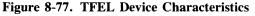

| 8-77         | TFEL Device Characteristics                                           | 8-43         |

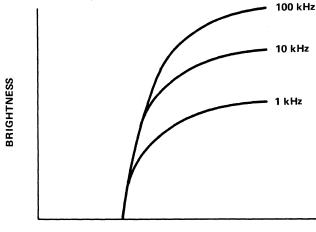

| 8-78         | Brightness Dependence on Frequency                                    | 8-43         |

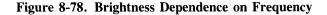

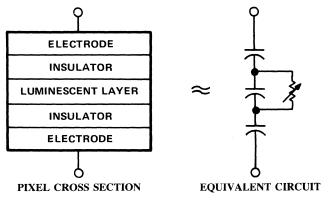

| 8-79         | Pixel Equivalent Circuit                                              | 8-44         |

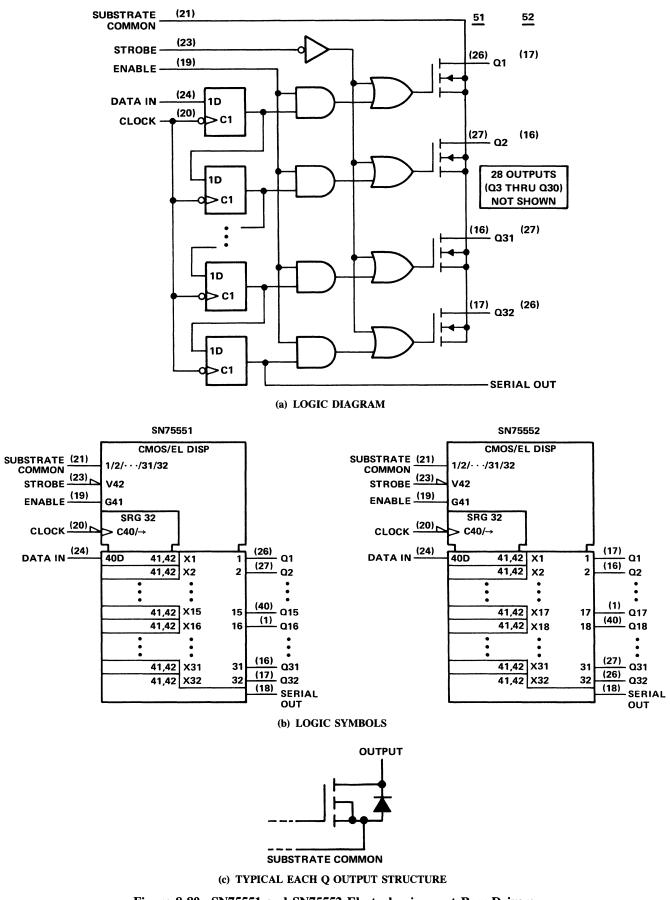

| 8-80         | SN75551 and SN75552 Electroluminescent Row Drivers                    | 8-44<br>8-45 |

| 8-81         | SN75551 and SN75552 Electroluminescent Row Drivers                    | 8-45         |

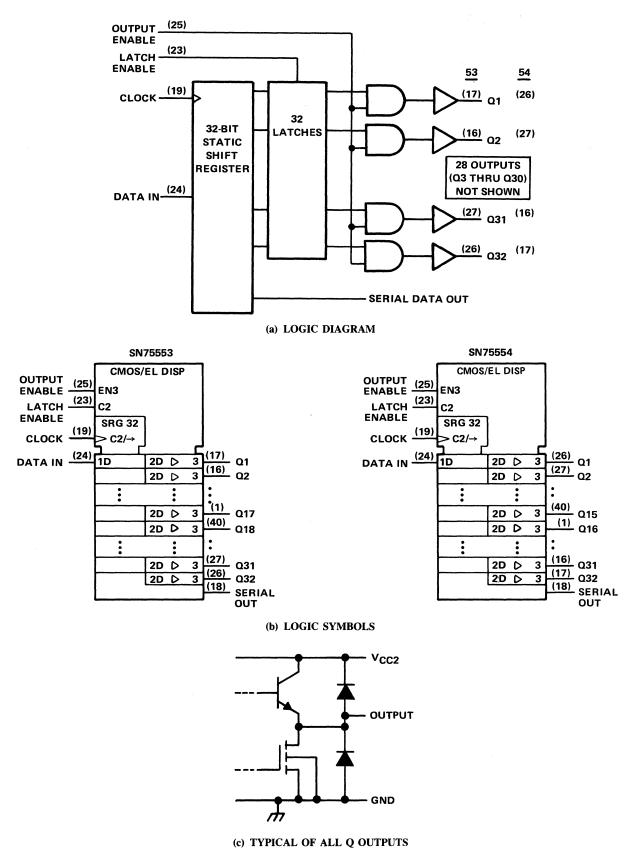

| 8-82         |                                                                       | 8-40         |

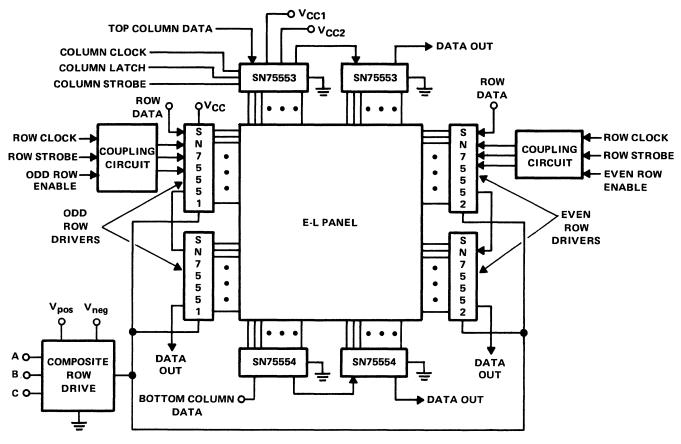

| 8-82         | Display Block Diagram                                                 | 8-47         |

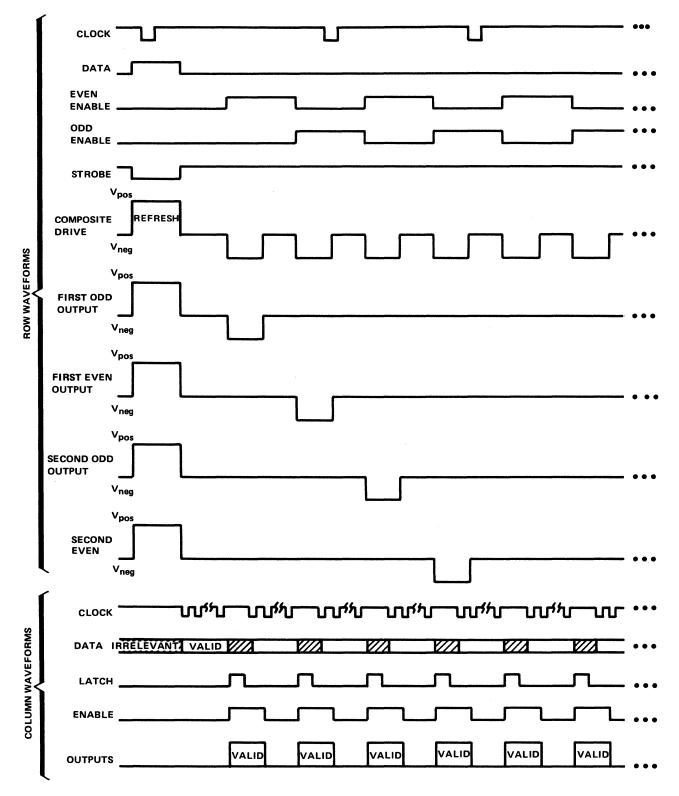

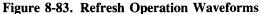

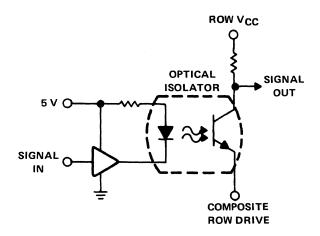

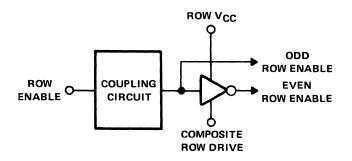

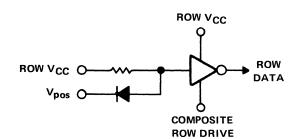

| 8-84         | Coupling Circuit                                                      | 8-49         |

| 8-85         | Odd and Even Enable Circuits                                          | 8-49         |

| 8-85         | Row Data Circuit                                                      | 8-49<br>8-49 |

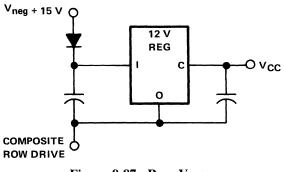

| 8-80<br>8-87 | Row V <sub>CC</sub>                                                   | 8-49         |

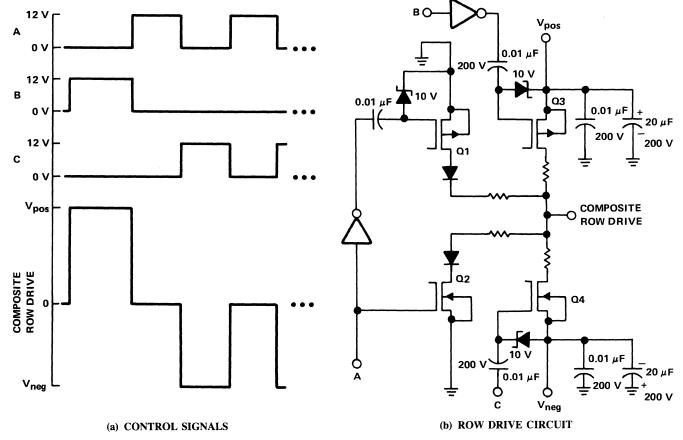

| 8-88         | Composite Row Drive Generation                                        | 8-49<br>8-49 |

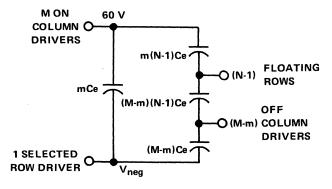

| 8-89         | Panel Equivalent Circuit                                              |              |

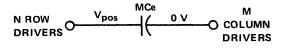

| 8-89<br>8-90 |                                                                       | 8-50         |

| 0-90         | Refresh Equivalent Circuit                                            | 8-50         |

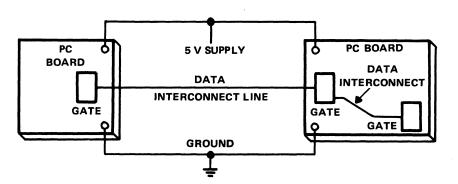

| 9-1          | Single Wire and Ground Plane                                          | 0.1          |

| 9-1<br>9-2   | Single Wire and Ground Plane                                          | 9-1          |

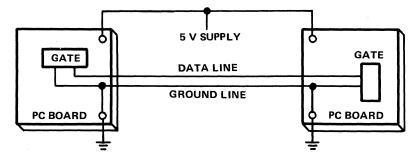

| 9-2<br>9-3   | Ribbon Cable                                                          | 9-2          |

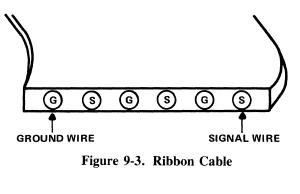

| 9-3<br>9-4   |                                                                       | 9-2          |

|              | Twisted Pair Lines                                                    | 9-2          |

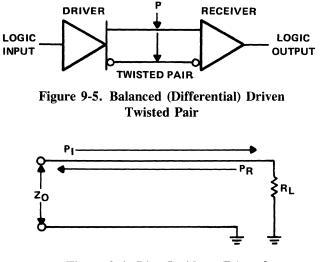

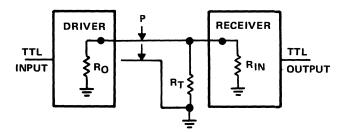

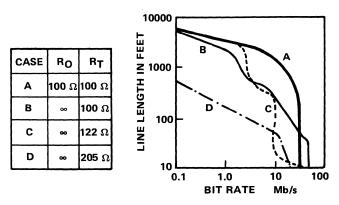

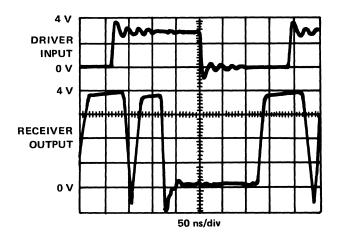

| 9-5<br>0.6   | Balanced (Differential) Driven Twisted Pair                           | 9-3          |

| 9-6<br>9-7   | Line Incident (P <sub>I</sub> ) and Reflected (P <sub>R</sub> ) Power | 9-3          |

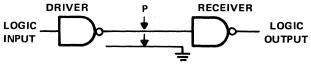

| 9-7<br>9-8   | Basic, Single Ended, Line Terminations                                | 9-3<br>9-3   |

| 7-0          |                                                                       | 9-1          |

| Figure | Title                                                                                         | Page |  |  |  |

|--------|-----------------------------------------------------------------------------------------------|------|--|--|--|

| 9-9    | Case C Voltage Waveform                                                                       |      |  |  |  |

| 9-10   | Line-to-Line Termination                                                                      | 9-4  |  |  |  |

| 9-11   | Termination to Ground                                                                         | 9-4  |  |  |  |

| 9-12   | Shielded Twisted Pair Transmission                                                            | 9-4  |  |  |  |

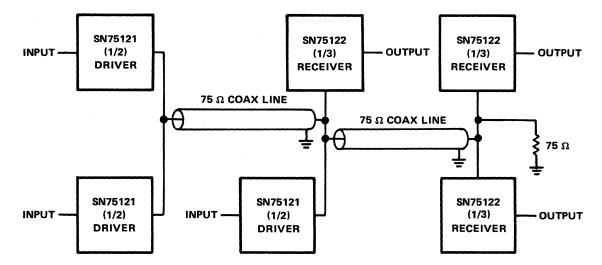

| 9-13   | Coaxial Data Lines                                                                            | 9-4  |  |  |  |

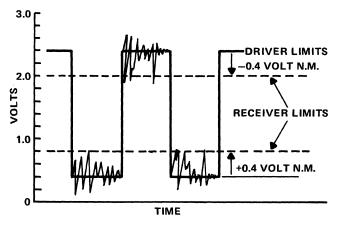

| 9-14   | TTL Gate Noise Margins                                                                        | 9-4  |  |  |  |

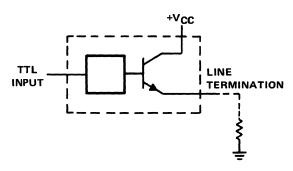

| 9-15   | Active Pull-Up Configuration                                                                  | 9-5  |  |  |  |

| 9-16   | Active Pull-Down Configuration                                                                | 9-5  |  |  |  |

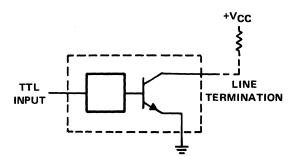

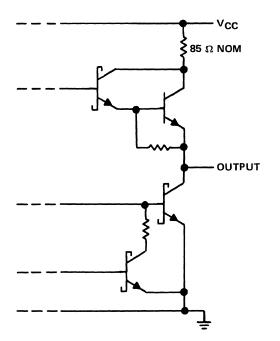

| 9-17   | Totem-Pole Configuration                                                                      | 9-5  |  |  |  |

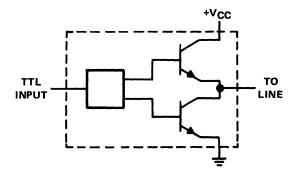

| 9-18   | Current-Mode Configuration                                                                    | 9-5  |  |  |  |

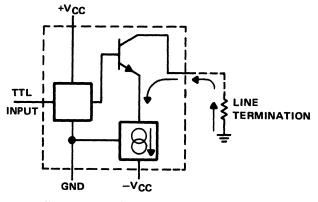

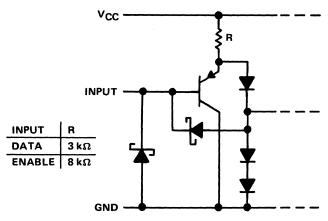

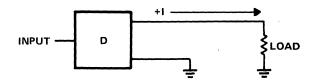

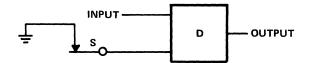

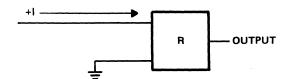

| 9-19   | High Level Driver                                                                             | 9-7  |  |  |  |

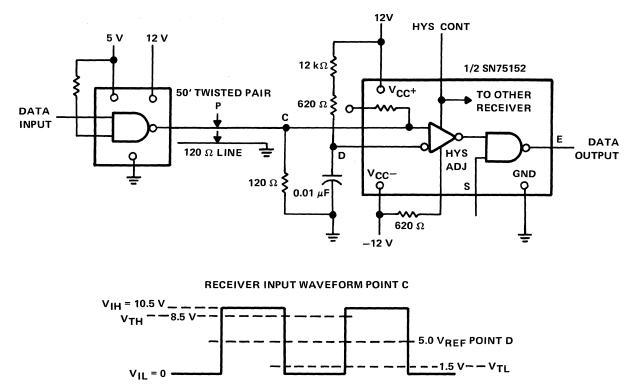

| 9-20   | Single-Ended Transmission with Receiver Adjusted for High Noise Immunity                      | 9-8  |  |  |  |

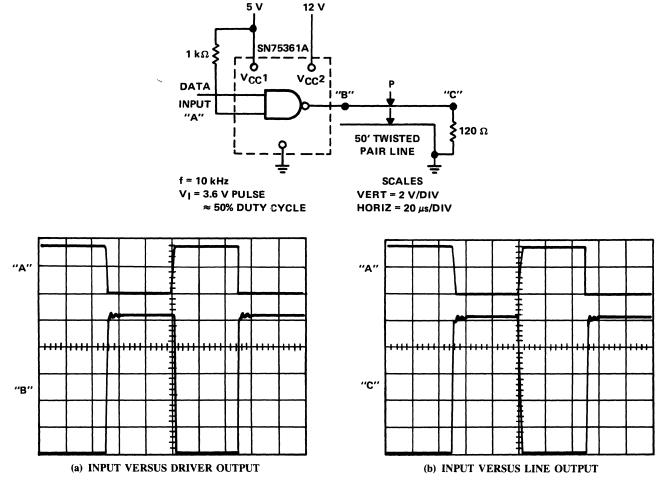

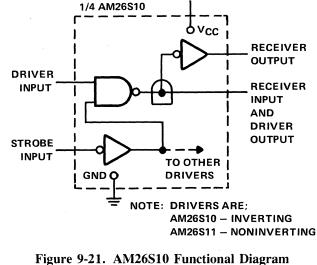

| 9-21   | AM26S10 Functional Diagram                                                                    | 9-8  |  |  |  |

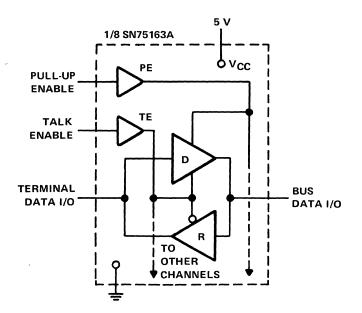

| 9-22   | SN75163A Functional Diagram                                                                   | 9-9  |  |  |  |

| 9-23   | Single-Ended Party-Line Bus Application                                                       | 9-9  |  |  |  |

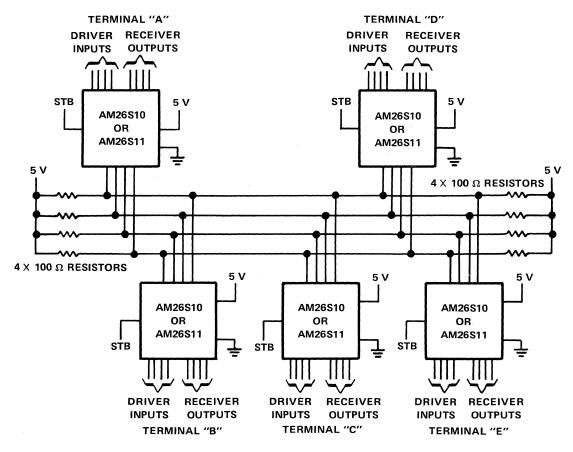

| 9-24   | Single-Ended Party-Line Application                                                           | 9-10 |  |  |  |

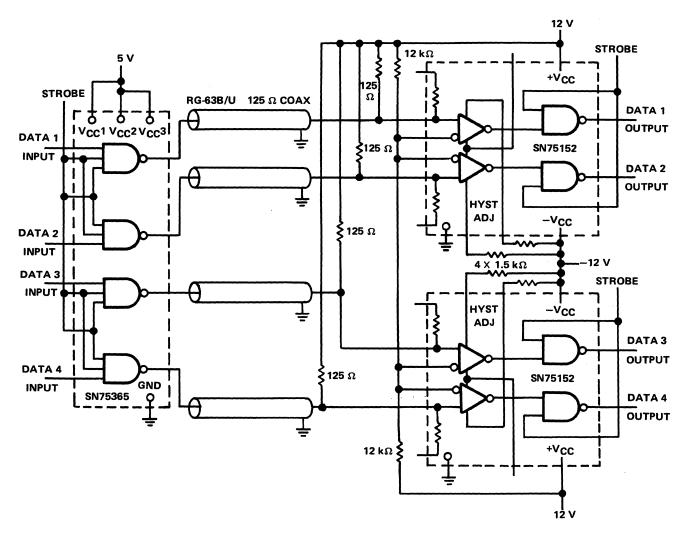

| 9-25   | Quad Transmission System with High Noise Immunity                                             | 9-10 |  |  |  |

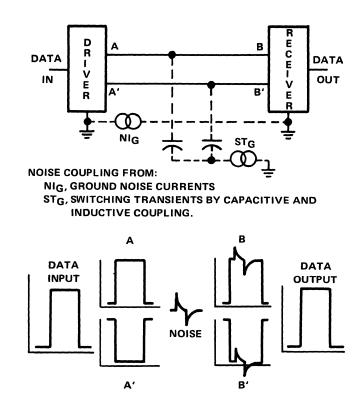

| 9-26   | Basic Noise Sources and Results                                                               | 9-11 |  |  |  |

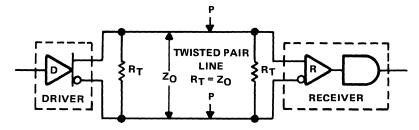

| 9-27   | Terminating Balanced Twisted Pair Lines                                                       | 9-13 |  |  |  |

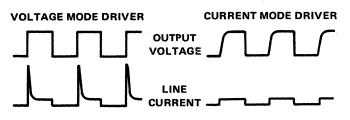

| 9-28   | Line Current Comparisons                                                                      | 9-14 |  |  |  |

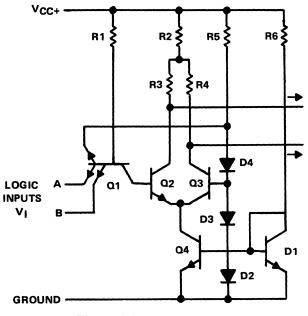

| 9-29   | Input Circuit                                                                                 | 9-14 |  |  |  |

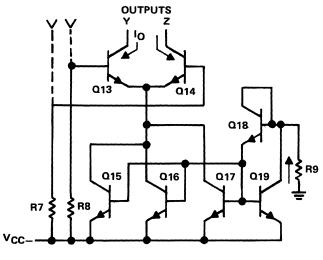

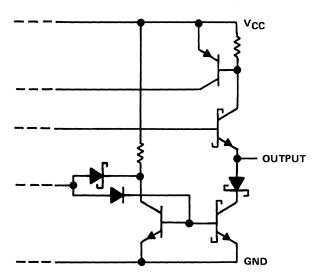

| 9-30   | Output Circuit                                                                                | 9-14 |  |  |  |

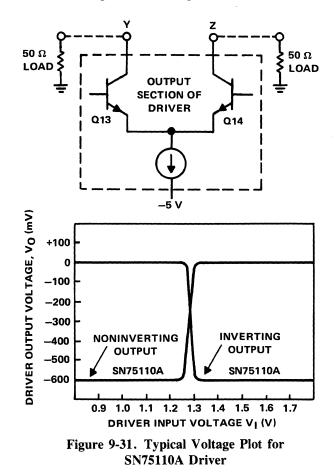

| 9-31   | Typical Voltage Plot for SN75110A Driver                                                      | 9-14 |  |  |  |

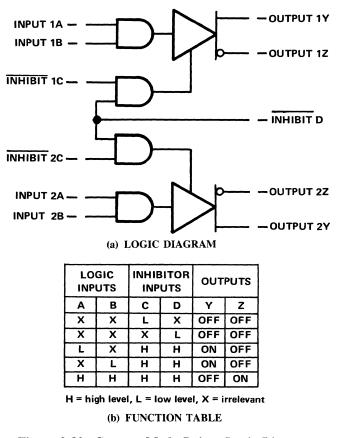

| 9-32   | Current-Mode Driver Logic Diagram and Function Table                                          | 9-15 |  |  |  |

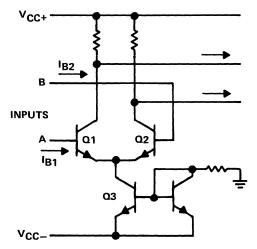

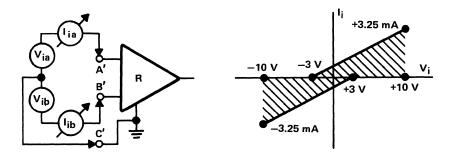

| 9-33   | Receiver Input Stage, Input Current Source, and Bias Circuit                                  | 9-15 |  |  |  |

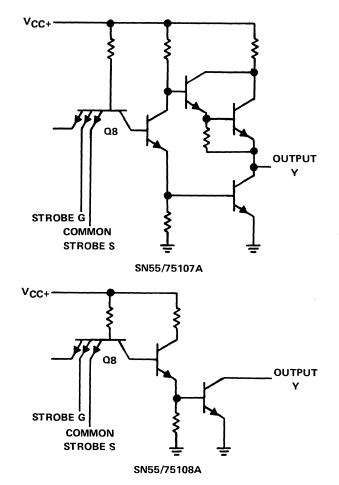

| 9-34   | Output Gates of SN55/75107A and SN55/75108A Compared                                          | 9-15 |  |  |  |

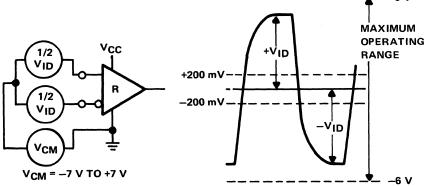

| 9-35   | Common-Mode Circuit for Testing Input Attenuators                                             | 9-16 |  |  |  |

| 9-36   | Some Methods of Referencing Receiver Inputs                                                   | 9-16 |  |  |  |

| 9-37   | "Safe Operating Region" for Receiver Inputs                                                   | 9-17 |  |  |  |

| 9-38   | Oscilloscope Displays of Typical Noisy Inputs and Noise-Free Output of SN75108 Line Receiver  | 9-18 |  |  |  |

| 9-39   | Use of SN55107 Series Devices in a Typical Single-Driver, Single-Receiver Transmission System | 9-18 |  |  |  |

| 9-40   | Simple Party-Line System with Driving and Receiving Stations Scattered                        |      |  |  |  |

|        | Along the Receiving Stations Scattered Along the Line                                         | 9-18 |  |  |  |

| 9-41   | Party-Line Concept of One Driver Transmitting to One of Many Receivers                        | 9-19 |  |  |  |

| 9-42   | Conceptual Diagram of Four Transmission Channels Sharing the Same Party Line                  | 9-19 |  |  |  |

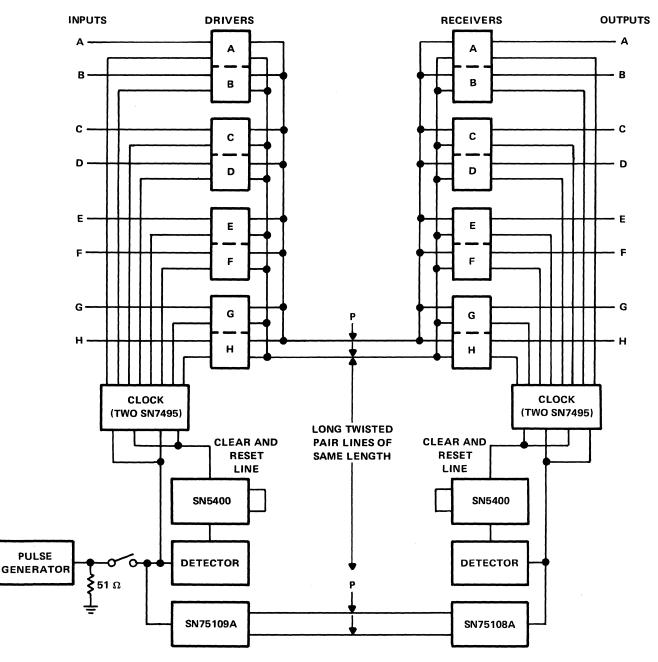

| 9-43   | A Multi-Channel System with Clocking                                                          | 9-20 |  |  |  |

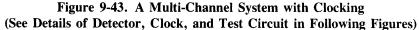

| 9-44   | Detector Circuit for Clearing SN7495 Clock in Figure 9-43                                     | 9-21 |  |  |  |

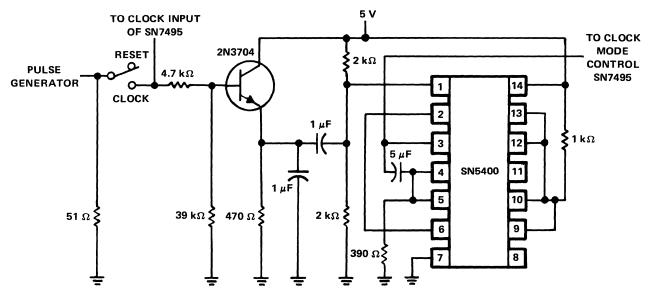

| 9-45   | SN7495 Clock for Strobing Drivers and Receivers in Figure 9-43                                | 9-21 |  |  |  |

| 9-46   | Driver-Receiver Repeaters                                                                     | 9-21 |  |  |  |

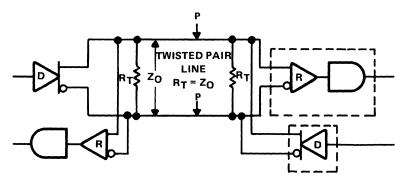

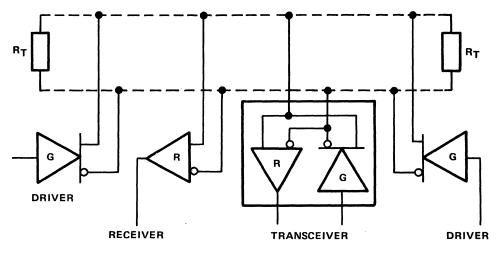

| 9-47   | Basic Party-Line Differential Data Transmission                                               | 9-22 |  |  |  |

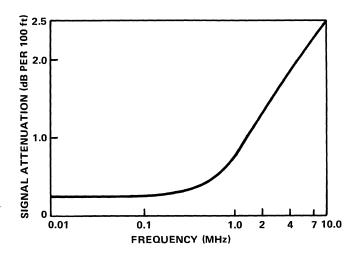

| 9-48   | Signal Attenuation with Frequency in Twisted Pair Transmission Line                           | 9-22 |  |  |  |

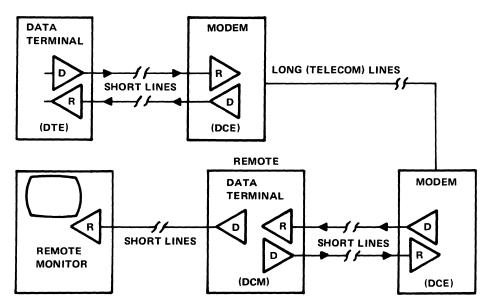

| 9-49   | RS-232-C Drivers and Receivers in a Basic Data Communications System                          | 9-23 |  |  |  |

| 9-50   | SN75150 Dual Line Driver                                                                      | 9-23 |  |  |  |

| 9-51   | SN75156 and uA9636 Dual Channel Line Drivers                                                  | 9-25 |  |  |  |

| 9-52   | SN75156 Transition Time vs R <sub>WS</sub>                                                    | 9-25 |  |  |  |

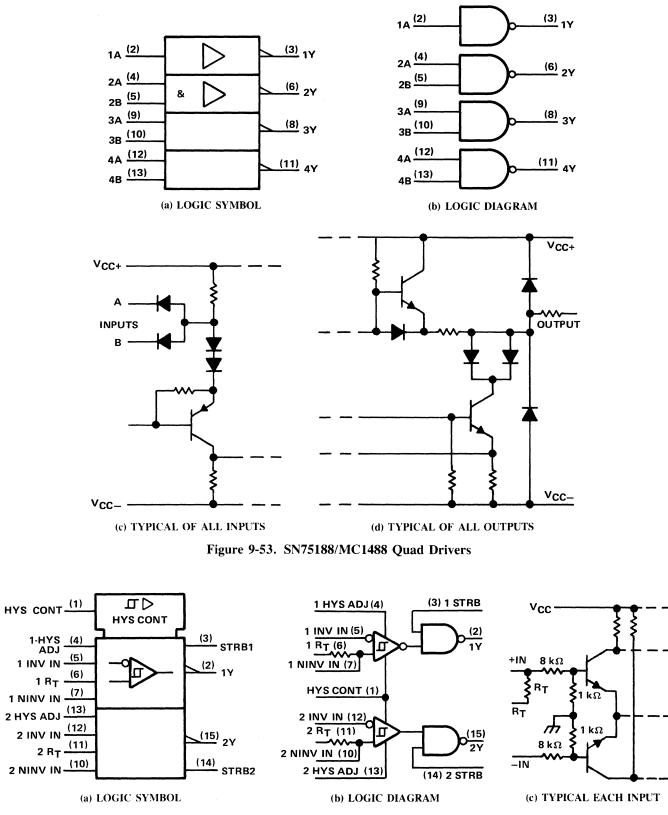

| 9-53   | SN75188/MC1488 Quad Drivers                                                                   | 9-26 |  |  |  |

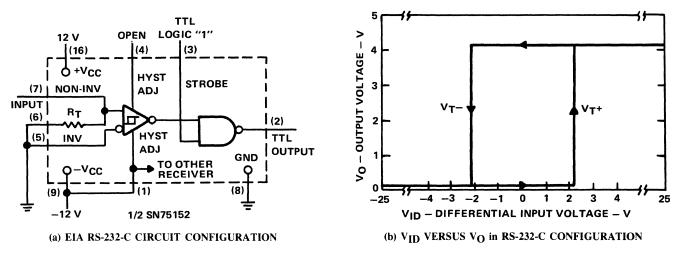

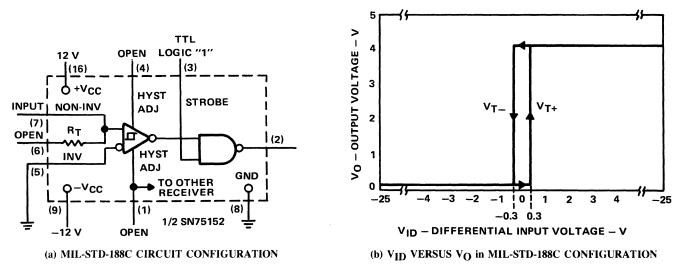

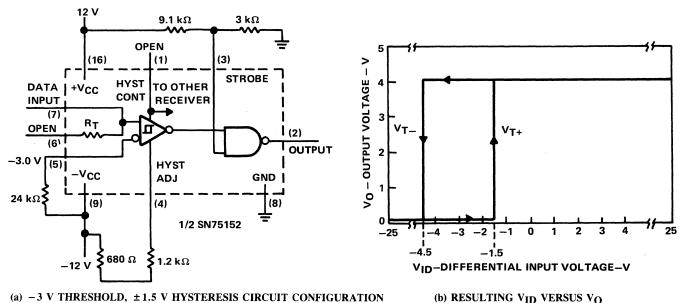

| 9-54   | SN75152 Dual Line Receiver                                                                    | 9-26 |  |  |  |

| 9-55   | SN75152 Circuit Connections and Results for EIA RS-232-C Application                          | 9-27 |  |  |  |

| 9-56   | SN75152 Circuit Connections and Results for MIL-STD-188C Application                          | 9-27 |  |  |  |

| 9-57   | Circuit Connections and Results for a Positive-Going Threshold of $-1.5$ V and a              |      |  |  |  |

| _      | Negative-Going Threshold of -4.5 V                                                            | 9-27 |  |  |  |

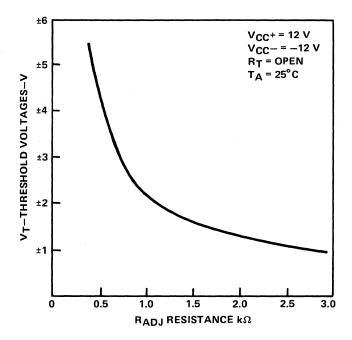

| 9-58   | Threshold Voltage Versus Hysteresis Adjust Resistance                                         | 9-28 |  |  |  |

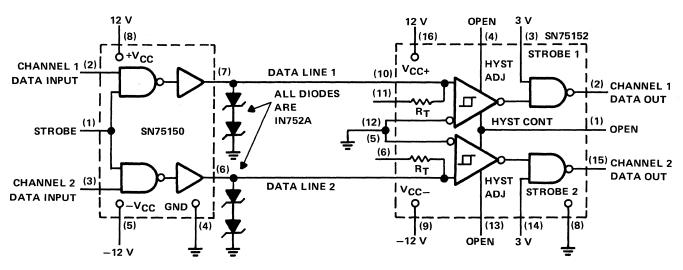

| 9-59   | MIL-STD-188C Dual Channel Application with SN75150 and SN75152                                | 9-28 |  |  |  |

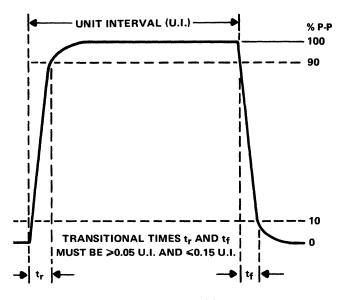

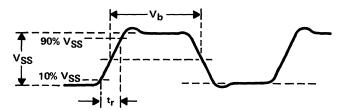

| 9-60   | MIL-STD-188C Wave Shape Requirements                                                          | 9-29 |  |  |  |

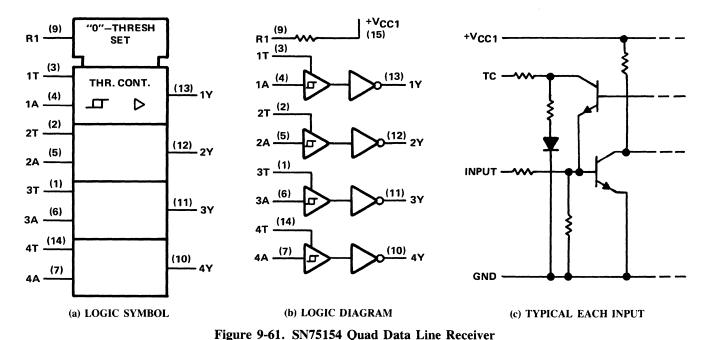

| 9-61   | SN75154 Quad Data Line Receiver                                                               | 9-29 |  |  |  |

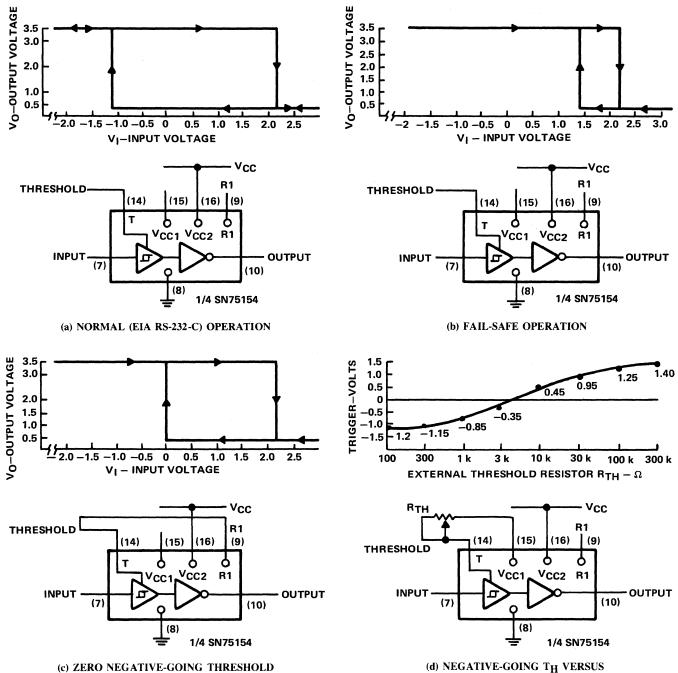

| 9-62   | SN75154 Hysteresis Modes of Operation                                                         | 9-30 |  |  |  |

| Figure         | Title                                                                    | Page         |

|----------------|--------------------------------------------------------------------------|--------------|

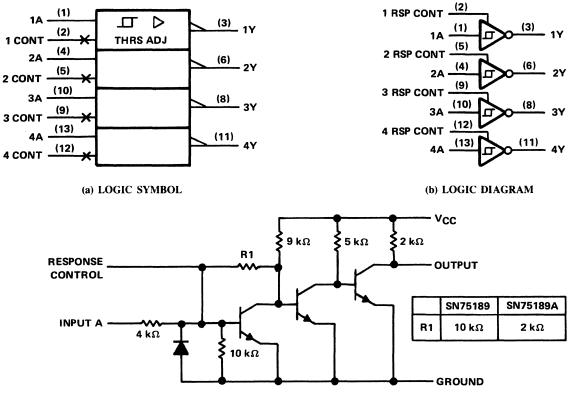

| 9-63           | SN75189/189A Quad Receiver                                               | 9-31         |

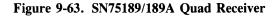

| 9-64           | Output Voltage Versus Input Voltage for Various Control Pin Terminations | 9-31         |

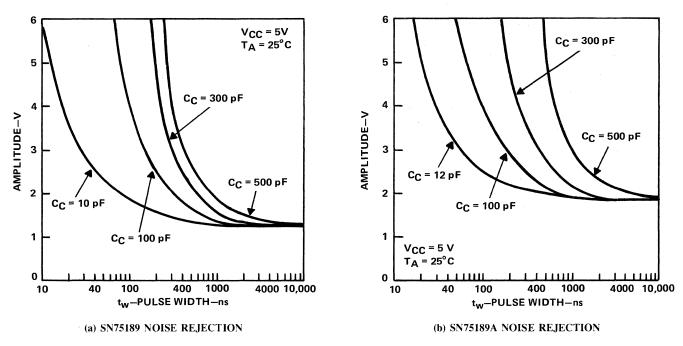

| 9-65           | Noise Rejection Versus Compensation Capacitance for SN75189 and SN75189A | 9-32         |

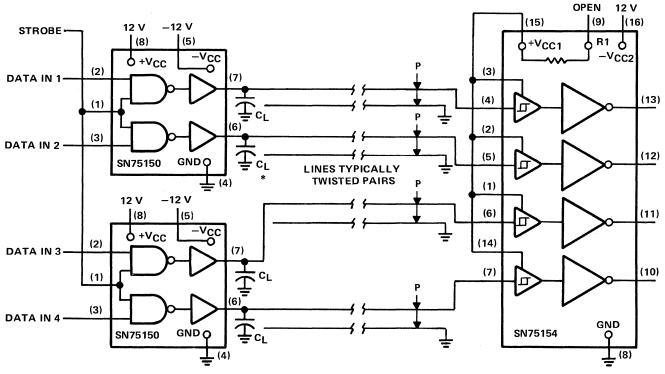

| 9-66           | Basic RS-232-C Data Line Interface Using SN75150 and SN75154             | 9-32         |

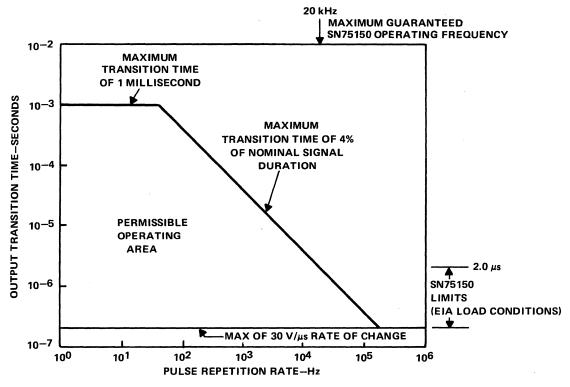

| 9-67           | Pulse Repetition Rate Versus Output Transition Time of SN75150           | 9-33         |

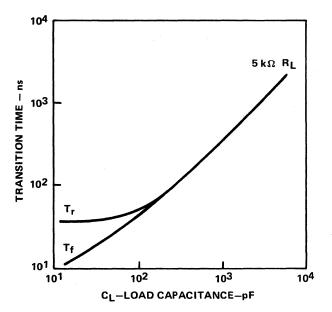

| 9-68           | Output Transition Times Versus Total Load Capacitance                    | 9-34         |

| 9-69           | Typical EIA RS-232-C Interface Using SN75188 and SN75189A                | 9-34         |

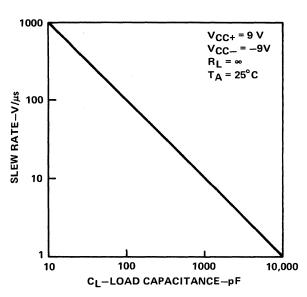

| 9-70           | Slew Rate Versus Load Capacitance                                        | 9-34         |

| 9-71           | Basic RS-423-A Unbalanced Digital Interface                              | 9-35         |

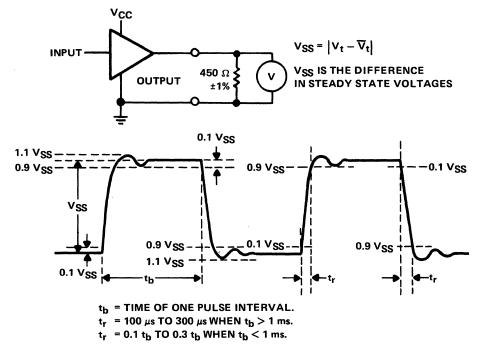

| 9-72           | Signal Wave Shaping Requirement                                          | 9-35         |

| 9-73           | Receiver Input Current-Voltage Measurement                               | 9-35         |

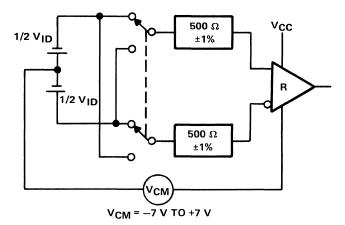

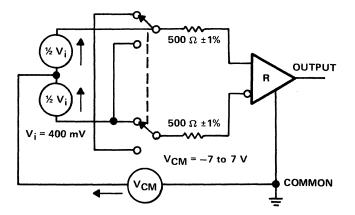

| 9-74           | Receiver Input Sensitivity Test                                          | 9-36         |

| 9-75           | Receiver Input Balance Test                                              | 9-37         |

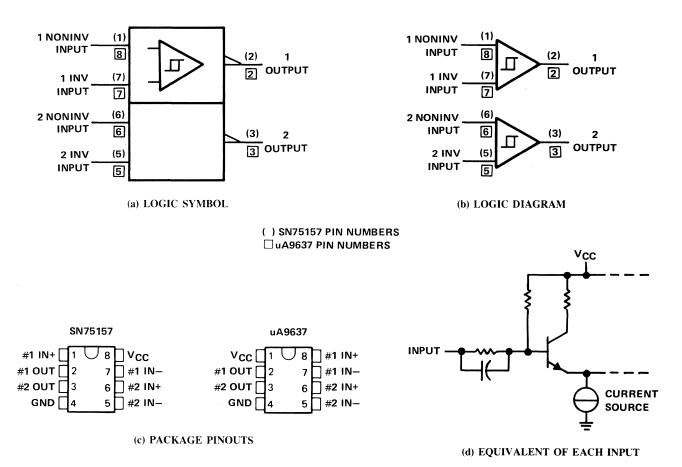

| 9-76           | SN75157 and uA9637 Dual RS-423-A Receivers                               | 9-37         |

| 9-77           | Basic EIA RS-423-A Application                                           | 9-38         |

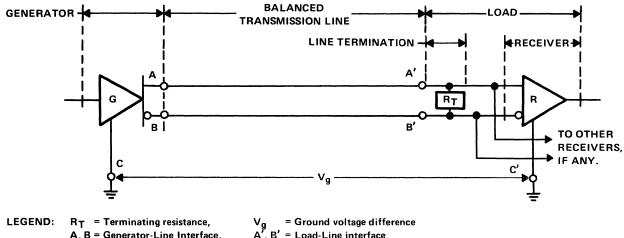

| 9-78           | Balanced Digital Interface                                               | 9-39         |

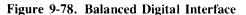

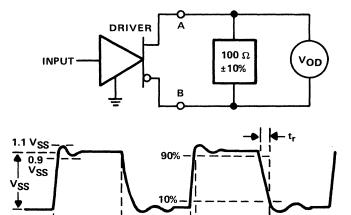

| 9-79           | Driver Output Voltage Test Circuit                                       | 9-39         |

| 9-80           | Driver Transitional Characteristics                                      | 9-39         |

| 9-81           | Receiver Input Balance Test                                              | 9-39         |

| 9-82           | Basic RS-422-A Application                                               | 9-40         |

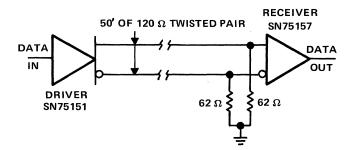

| 9-83           | Short Line RS-422-A Application                                          | 9-40         |

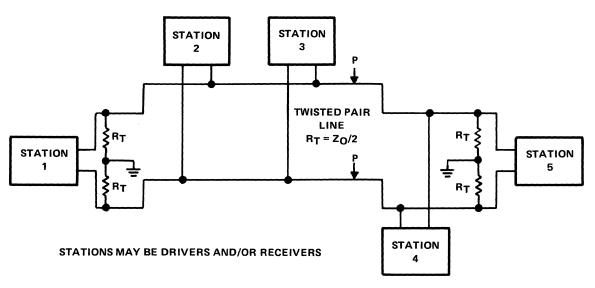

| 9-84           | Multipoint Balanced Digital Interface                                    | 9-41         |

| 9-85           | Quad Differential Line Driver AM26LS31 and SN75172B                      | 9-42         |

| 9-86           | Quad Differential Line Receiver AM26LS32A and SN75173A                   | 9-42         |

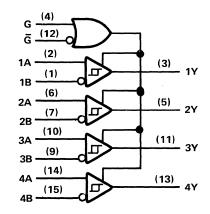

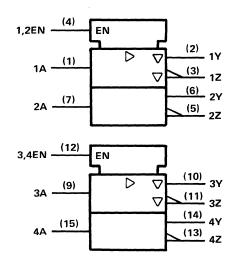

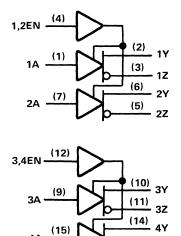

| 9-87           | Quad Differential Line Driver MC3487 and SN75174B                        | 9-43         |

| 9-88           | Quad Differential Line Receiver MC3486 and SN75175A                      | 9-43<br>9-43 |

| 9-89           | Equivalent Driver Input Circuit                                          | 9-44<br>9-44 |

| 9-90           | Equivalent Each Driver Output                                            | 9-44<br>9-44 |

| 9-90<br>9-91   | Line-to-Line Termination                                                 | 9-44<br>9-44 |

| 9-91<br>9-92   | Line-to-Ground Termination                                               | 9-44<br>9-44 |

| 9-92<br>9-93   | Driver Output Waveform                                                   | 9-44<br>9-44 |

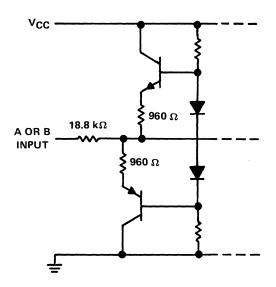

| 9-93<br>9-94   | Equivalent Receiver A or B Input                                         | 9-44<br>9-44 |

| 9-94<br>9-95   | Equivalent Receiver A of B input                                         | 9-44<br>9-45 |

| 9-95<br>9-96   | Receiver Propagation Delays                                              | 9-45<br>9-45 |

| 9-90<br>9-97   | SN75176B                                                                 | 9-45<br>9-45 |

| 9-97<br>9-98   |                                                                          | 9-43<br>9-45 |

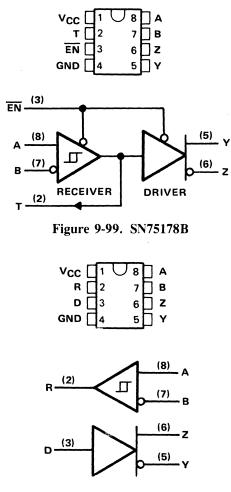

| 9-98<br>9-99   | SN75177B                                                                 | 9-45<br>9-46 |

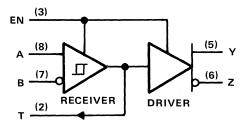

| 9-99<br>9-100  | SN75178B                                                                 | 9-40<br>9-46 |

| 9-100<br>9-101 | SN75179B                                                                 | 9-46<br>9-46 |

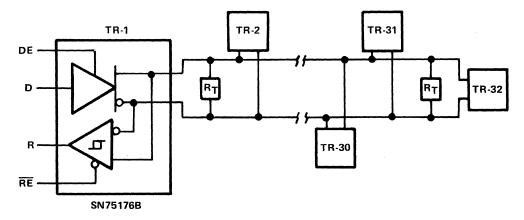

|                | SN75176B Transceivers on Multi-Station Bus                               | 9-40<br>9-47 |

| 9-102          | SN75177B and SN75178B Allow Bidirectional Long Line Communication        |              |

| 9-103          | SN75179B Independent Driver and Receiver                                 | 9-47         |

| 9-104          | Typical IEEE-488 Interface System                                        | 9-48         |

| 9-105          | Interface Connector                                                      | 9-49         |

| 9-106          | Functional Partitioning Within an Instrument or Apparatus                | 9-51         |

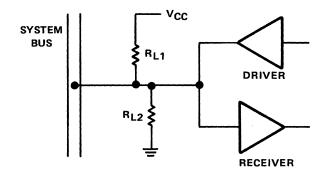

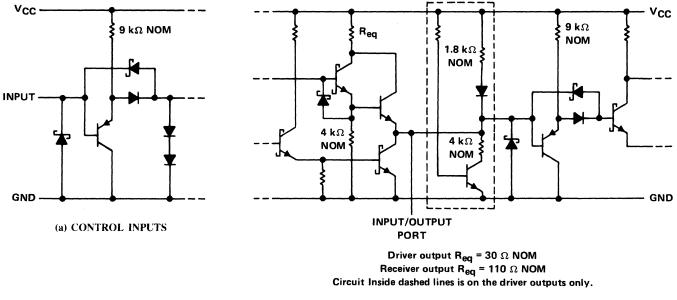

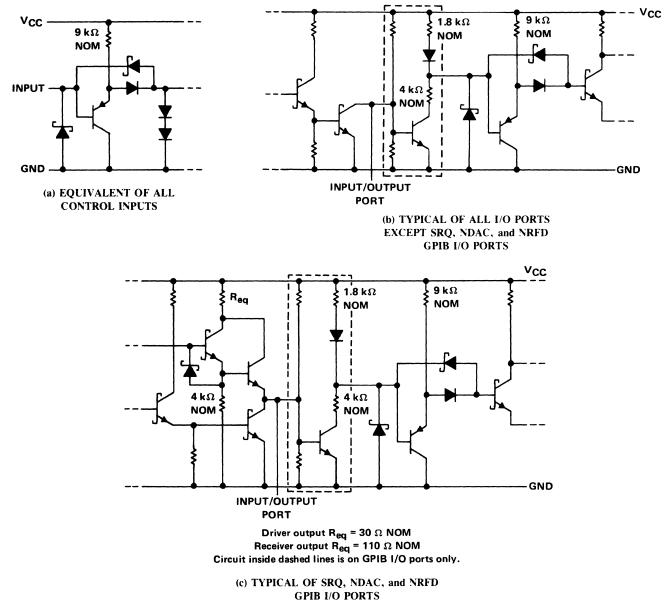

| 9-107          | Typical Signal Line I/O Circuit                                          | 9-52         |

| 9-108          | DC Load Line Permissible Operating Area                                  | 9-53         |

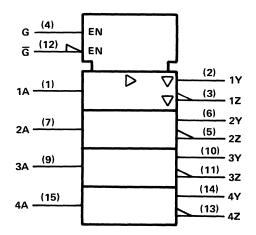

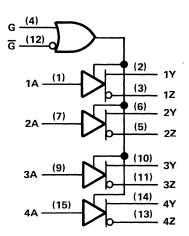

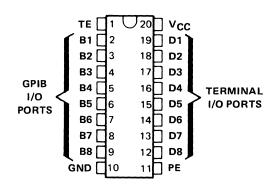

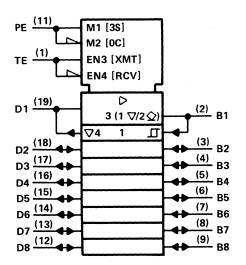

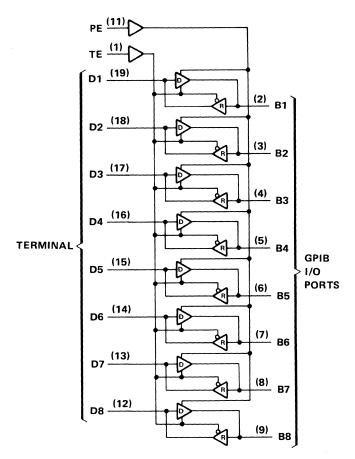

| 9-109          | SN75160A Pinout and Function Tables                                      | 9-53         |

| 9-110          | SN75160A Logic Symbol and Logic Diagram (Positive Logic)                 | 9-54         |

| 9-111          | Equivalent Schematics of SN75160A Input and Output Sections              | 9-55         |

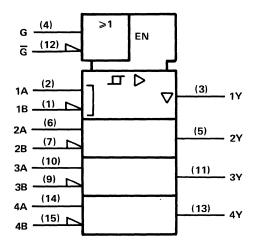

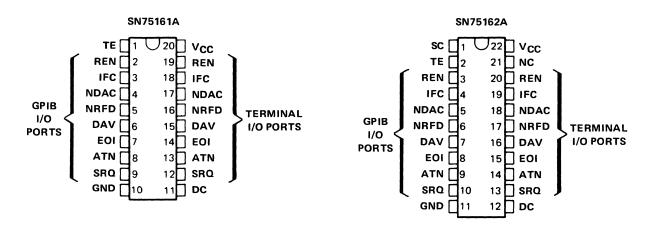

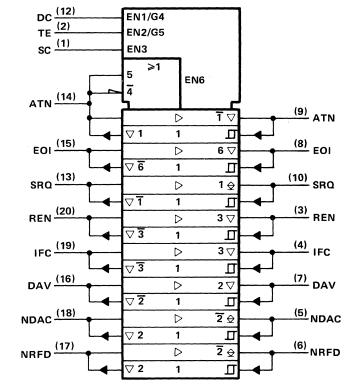

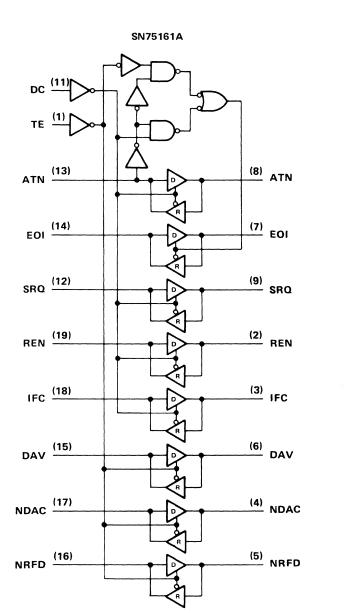

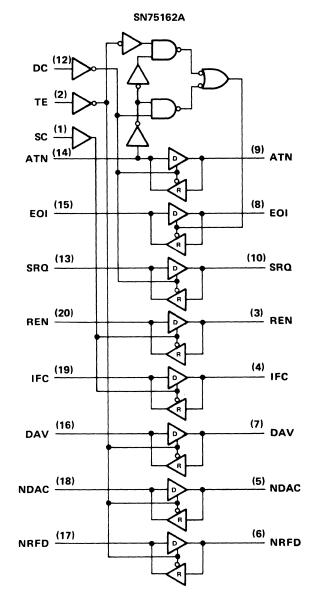

| 9-112          | SN75161A and SN75162A Pinouts and Table of Abbreviations                 | 9-55         |

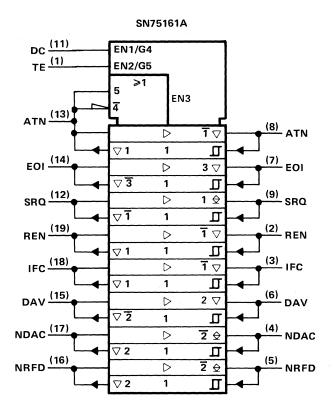

| 9-113          | Logic Symbols for SN75161A and SN75162A                                  | 9-56         |

| 9-114          | Logic Diagrams (Positive Logic) of SN75161A and SN75162A                 | 9-57         |

| 9-115          | Input/Output Sections of SN75161A and SN75162A                           | 9-59         |

| 9-116          | MC3446 Logic Diagram and Function Tables                                 | 9-60         |

| Figure | Title                                        | Page |

|--------|----------------------------------------------|------|

| 9-117  | MC3446 Input and Output Equivalent Circuits  | 9-60 |

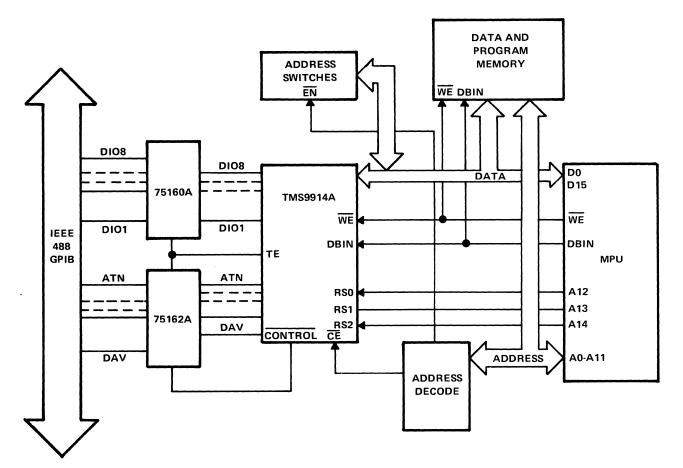

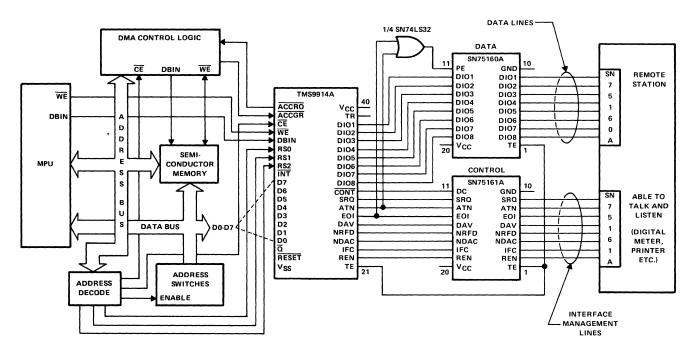

| 9-118  | Typical TMS9914A Application Block Diagram   | 9-61 |

| 9-119  | Typical IEEE-488 System Application          | 9-61 |

|        | Driver Current Polarity                      | 9-62 |

| 9-121  | Driver Control Gate Switch (S)               | 9-62 |

| 9-122  | Receiver Input Current Polarity              | 9-62 |

| 9-123  | Negative Noise Spikes                        | 9-63 |

| 9-124  | Positive Noise Spikes                        | 9-63 |

| 9-125  | SN75123 Dual Line Driver                     | 9-64 |

| 9-126  | SN75126 Quad Line Driver                     | 9-65 |

| 9-127  | SN75130 Quad Line Driver                     | 9-66 |

| 9-128  | SN75124 Triple Line Receiver                 | 9-67 |

| 9-129  | SN75125/SN75127 Seven-Channel Receivers      | 9-68 |

| 9-130  | SN75128/SN75129 Eight-Channel Line Receivers | 9-69 |

| 9-131  | Typical IBM 370 Interface Application        | 9-70 |

## List of Tables

| Table | Title                                                                                     | Page |

|-------|-------------------------------------------------------------------------------------------|------|

| 8-1   | Select Input Truth Table                                                                  | 8-23 |

| 8-2   | VFD Operating Ranges                                                                      | 8-29 |

| 8-3   | VFD Configuration Comparison                                                              | 8-31 |

| 8-4   | SN75112A—SN75513A Operational Duty Cycle                                                  | 8-34 |

| 8-5   | Dot Character VFD Driver Requirements                                                     | 8-34 |

| 8-6   | Dot Matrix VFD Driver Requirements                                                        | 8-42 |

| 9-1   | Single-Ended Drivers                                                                      | 9-6  |

| 9-2   | Single-Ended Receivers                                                                    | 9-6  |

| 9-3   | Single-Ended Transceivers                                                                 | 9-6  |

| 9-4   | Differential Drivers                                                                      | 9-11 |

| 9-5   | Differential Receivers                                                                    | 9-12 |

| 9-6   | Differential Transceivers                                                                 | 9-12 |

| 9-7   | Typical Propagation Delays for Receiver with Attenuator Test Circuit Shown in Figure 9-35 | 9-16 |

| 9-8   | RS-232-C Driver Requirements                                                              | 9-24 |

| 9-9   | RS-232-C Receiver Requirements                                                            | 9-24 |

| 9-10  | RS-423-A Driver Requirements                                                              | 9-34 |

| 9-11  | RS-423-A Receiver Requirements                                                            | 9-36 |

| 9-12  | Popular General Purpose EIA Line Circuit Standards                                        | 9-38 |

| 9-13  | Time Values                                                                               | 9-53 |

| 9-14  | SN75161A and SN75162A Receive/Transmit Function Tables                                    | 9-58 |

xii

#### Preface

This is the second volume in a three-volume series of Linear and Interface Circuit Applications books. To maintain overall continuity in the series, the section numbers in this book follow those in Volume 1. Volume 1 presented information on operational amplifiers, voltage regulators, and timers. Volume 2 provides information on display drivers and data line drivers, receivers, and transceivers. Volume 3 will provide information on peripheral drivers, data acquisition circuits, and special functions.

The purpose of this series of books is to present linear and interface circuit applications in a manner that will give the reader a basic understanding of the products and provide simple but practical examples for typical applications. Care has been taken to choose illustrations which are of interest, at least by analogy, to a wide class of readers. This material is written for not only the design engineer but also for engineering managers, engineering technicians, system designers, and marketing or sales people with some technical background. The authors have attempted to avoid lengthy mathematical analyses for technical elegance, so that the important points may be clearly emphasized and not obscured by distracting derivations. In cases where a rigorous derivation has been omitted, an attempt has been made to state the results precisely and to emphasize limitations that are practically significant.

To facilitate their use, the sections have been made basically independent. The primary goal of the books is to assist the user in selecting the proper device for a particular application. To accomplish this, key features of devices are presented along with discussions of device or system theory and requirements.

Potential uses of the devices are demonstrated in circuit applications. These applications are not intended to be a how-to for specific circuits but to be examples of how the device might be used to solve your specific design requirements. In each case, a data book or data sheet should be referred to for complete device characteristics and operating limits. The circuit examples selected for this book have accrued from numerous customer inquiries and related laboratory simulations.

This series of books has been written primarily by two members of the Linear Applications Staff. They would like to express their appreciation for the helpful inputs and assistance from members of the Linear Applications Lab, Product Engineering Staff, Field Application Engineering, and the European Applications Staff.

xir

## Section 8 Display Drivers

#### INTRODUCTION TO DISPLAY DRIVER TECHNOLOGY

Visual displays exist in a wide range of complexities from the simple incandescent bulb or light emitting diode (LED) indicators to complex full digital read-out or large flat-screen display panels. Until recently, many discrete transistors were required to drive the more complex visual display systems.

As the complexity of display systems grew, alternatives to discrete transistor drivers became imperative. An increasing number of monolithic integrated circuits are becoming available for driving many types of display systems, some of which were not considered practical until recently. Monolithic ICs that have been developed to drive digital and more complex displays include:

> Light Emitting Diode Display Drivers DC Plasma (Gas Discharge) Display Drivers AC Plasma Display Drivers Vacuum Fluorescent Display Drivers Electroluminescent Display Drivers Electrophoretic Display Drivers

Reliability of the higher voltage display drivers (all except LED drivers) has been poor in the past. In fact, ac plasma and electroluminescent display drivers were considered impractical because their complexity and high voltage required the use of many discrete power transistors and logic circuits. "BIDFET"\* technology has made monolithic IC drivers possible by providing the voltage capability and complexity required for 64 power output transistors and control logic on a single chip.

\*Bipolar, double diffused. N-Channel and P-Channel MOS transistors on

the same chip - a patented process.

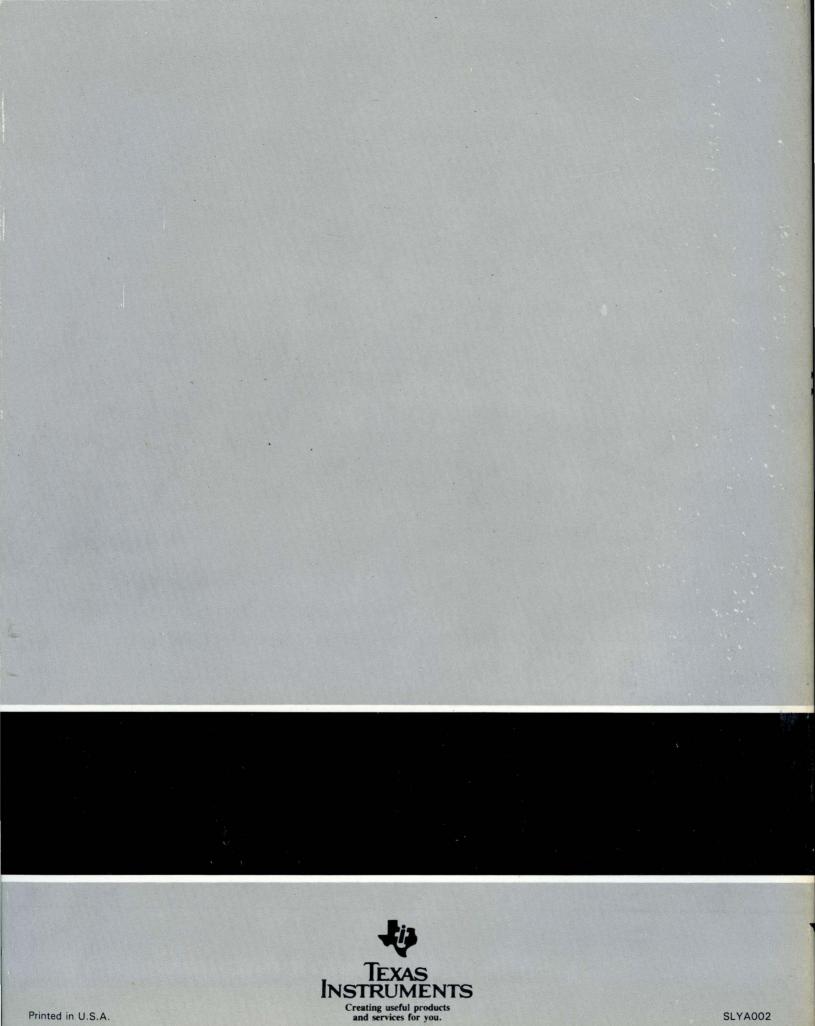

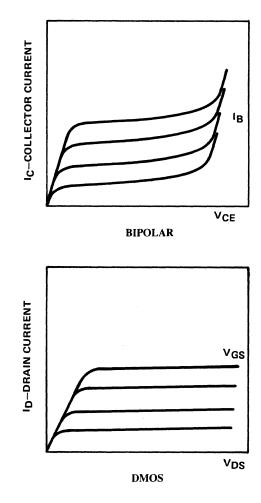

BIDFET is a rugged, low-cost wafer processing technology which merges precision control, self-isolated CMOS logic and high-voltage interface circuitry on a common monolithic substrate. It is manufactured using standard junction isolation techniques (see Figure 8-1). Many multitechnology processes have been developed, but BIDFET is the only merged process which alleviates the high voltage limitations of conventional integrated circuits while retaining their LSI logic capabilities. BIDFET devices are being produced with working voltages to 250 V and breakdown voltages exceeding 300 V. This has been achieved by replacing the conventional bipolar output stage with a Double-Diffused MOS (DMOS) transistor structure. The two output stage structures are compared in the following paragraphs.

First let us consider the limitations imposed by operating a bipolar switch within the Reverse Bias Safe Operating Area (RBSOA).

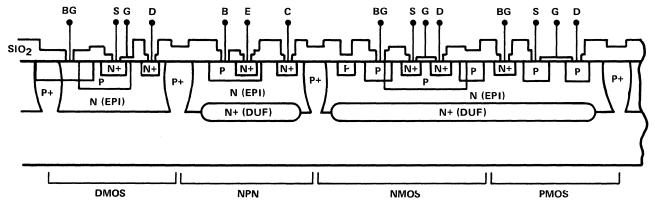

Figure 8-2 shows the typical load line characteristics of a switch operated within the device's RBSOA and  $V_{CES(SUS)}$  ratings. If the load line penetrates the RBSOA, a destructive condition occurs. Thus, reliable operation may be limited to the  $V_{BR(CEO)}$  rating of the switch.

With common topologies used in conventional integrated circuits, breakdown voltages [ $V_{BR(CEO)}$ ] are limited by the thickness of the epitaxial layer. Practical limitations on the thickness of conventional junction isolated integrated circuits limits  $V_{BR(CEO)}$  to 70 V.

The DMOS structure, on the other hand, is a surface (lateral) device whose breakdown characteristic is limited only by bulk junction avalanching and horizontal topology (channel length). Breakdown ratings are governed by doping levels and surface area, which is an economic consideration, instead of a physical limitation. Unlike NPN transistors,

Figure 8-1. BIDFET Cell Cross Section

Figure 8-2. RBSOA Curve and Load Line

Figure 8-3. Breakdown Characteristics

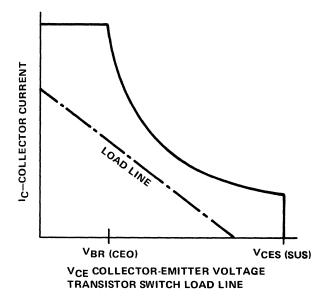

DMOS can operate safely to its breakdown voltage limit without risk of destructive secondary breakdown or sacrifice of reliability. Figure 8-3 shows the superior breakdown characteristics of the DMOS structure as compared to the bipolar structure.

Characteristic waveforms (Figure 8-4) show the virtual independence of the output current to the output voltage of a DMOS structure. The Early voltage, as well as the stored charge characteristics of the DMOS structure, is superior to that of the bipolar transistor in switching applications.

Figure 8-4. Characteristic Waveforms

Using the variety of structures offered by the BIDFET process, design engineers can optimize high voltage circuits by partitioning them and using the optimum technologies for the various sections. The bipolar structure offers durability and is very forgiving of input conditions. CMOS allows increased circuit complexity while requiring minimal power consumption and bar area. The DMOS structure's benefits have been presented herein. The result is a high-voltage interface circuit which is capable of performing data registration, manipulation or decoding functions to reduce the requirements on system electronics.

#### LED DISPLAY DRIVERS

LED displays have generally been fairly simple systems. Applications vary from one or two discrete LEDs to small

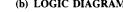

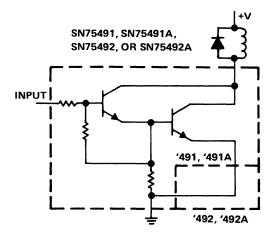

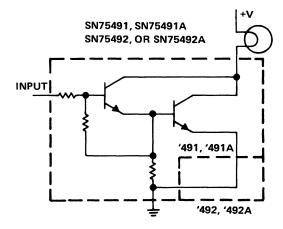

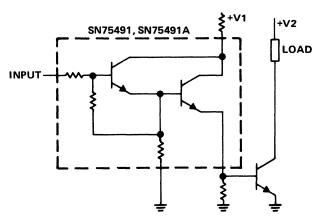

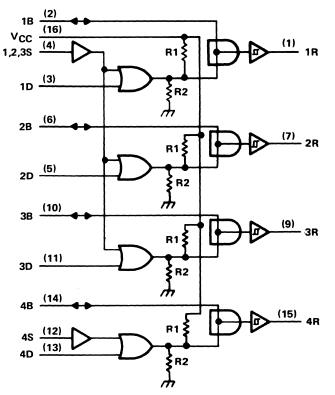

#### SN75491 AND SN75491A QUAD LED SEGMENT **DRIVERS** (Figure 8-5)

#### Features

- 50 mA source or sink capability

- '491 rated for 10 V operation

- '491A rated for 20 V operation

- MOS compatible inputs

- Low standby power

- High gain Darlington circuits

arrays and digital displays. A variety of multichannel drivers have evolved that allow easy implementation of the drives required. Some examples of these devices follow:

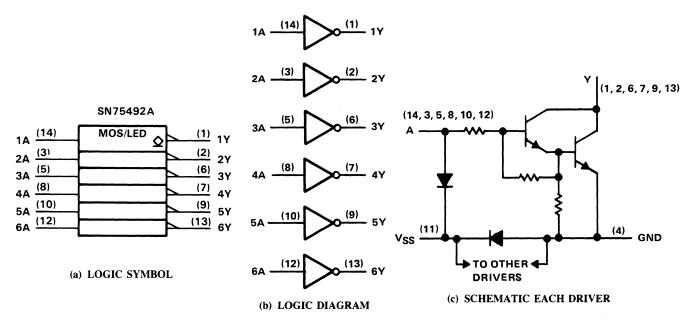

#### SN75492 AND SN75492A HEX LED DIGIT DRIVERS (Figure 8-6)

#### Features

- 250 mA sink capability

- '492 rated for 10 V operation

- '492A rated for 20 V operation

- MOS compatible inputs

- Low standby power

- High-gain Darlington circuits

Figure 8-6. SN75492 and SN75492A

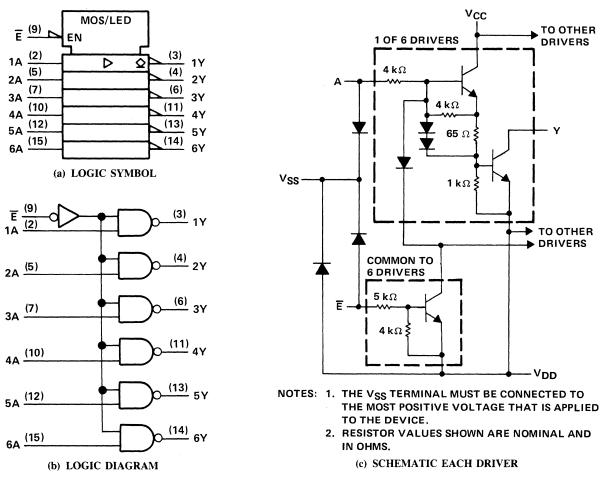

#### SN75494 HEX LED DIGIT DRIVER

The SN75494 (Figure 8-7) provides the same basic function as the SN75492 but with some key differences:

- Operates from lower V<sub>CC</sub> voltages; as low as 3.2 V.

- In addition to V<sub>SS</sub> and ground the '494 provides access to predriver collectors via its V<sub>CC</sub> pin thus allowing good saturation of output transistors for low-voltage applications.

- An enable input is provided to allow display blanking.

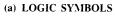

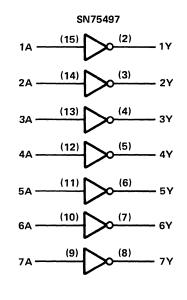

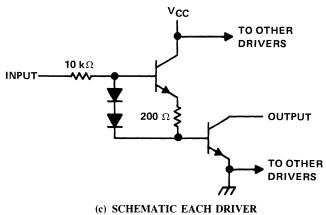

## SN75497 7-CHANNEL and SN75498 9-CHANNEL LED DRIVERS (Figure 8-8)

#### **Features:**

- 100 mA output sink capability

- Low-voltage operation (2.7 V min)

- MOS and TTL compatible inputs

- Low standby power

#### DRIVING LED DISPLAYS

Light emitting diodes exist in a variety of sizes and operating current requirements. Typical digital displays require 10 to 20 mA forward current for normal operating brightness levels.

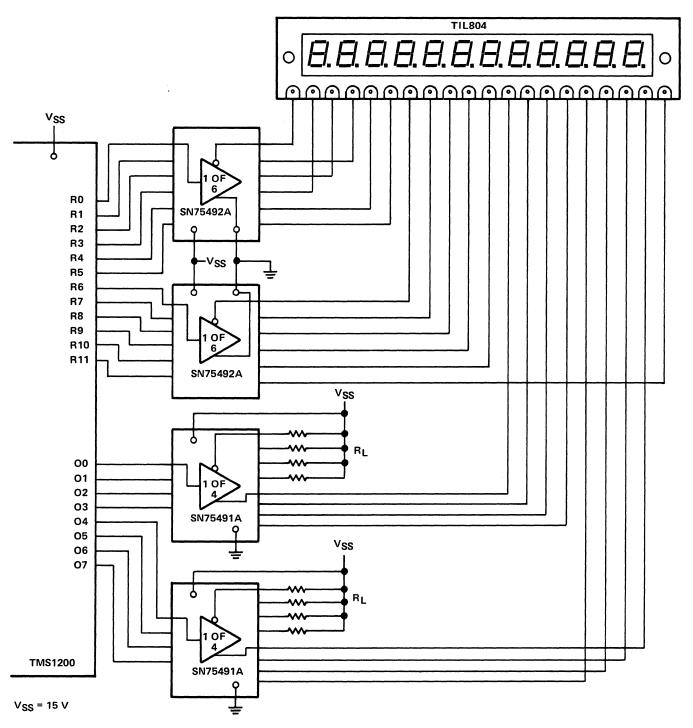

Digital displays are usually driven using time-multiplex techniques to minimize the number of drivers required. A segment-address selection and digit-scan method of multiplexing is used in the application (Figure 8-9) for a 12-digit display.

The TIL804 used in this application is a 12-digit numeric LED display with right-hand decimal points. It consists of common-cathode red LED digits. Twenty tab connections allow control of the 84 segments and 12 decimal points. The segments, and decimal points, are addressed by the "0" outputs of a TMS1200 microcomputer chip. Each digit of the display is connected in a common-cathode configuration and the anodes of like-position segments of all digits are connected together for multiplex drive. Normal operation of each digit is 8.3% (1/12) duty cycle. For an average

Figure 8-7. SN75494

|                | SN75498              |                |

|----------------|----------------------|----------------|

| 1A <u>(19)</u> | <sup>MOS/LED</sup> ☆ | ( <u>2)</u> 1Y |

| 2A (18)        |                      | ( <u>3)</u> 2Y |

| 3A (17)        |                      | (4)<br>3Y      |

| 4A (16)        |                      | (5)<br>4Y      |

| 5A <u>(15)</u> |                      | (6)<br>5Y      |

| 6A (14)        |                      | (7) 6Y         |

| 7A (13)        |                      | (8) 7Y         |

| 8A (12)        |                      | ( <u>9)</u> 8Y |

| 9A (11)        |                      | (10)<br>9Y     |

|                                                 | SN75497 |                |

|-------------------------------------------------|---------|----------------|

| 1A <mark>(15)</mark>                            | MOS/LED | (2) 1Y         |

| 1441                                            |         | (3) 2Y         |

| $2A \frac{(14)}{(13)} \\ 3A \frac{(12)}{(12)} $ |         | (4) 3Y         |

| 4A (12)                                         |         | (5)<br>4Y      |

| 5A (11)                                         |         | (6)<br>5Y      |

| 6A (10)                                         |         | (7)<br>6Y      |

| 7A <del>(9)</del>                               |         | ( <u>8)</u> 7Y |

|                                                 |         | -              |

(b) LOGIC DIAGRAMS

Figure 8-8. SN75497 and SN75498

forward current of 5 mA a pulse current of 60 mA will be required. System operation may be from a single 15 V supply as shown, or the SN75491A source drivers may be operated from a separate supply of typically 5 V. The current limit resistors,  $R_L$  may be calculated as follows:

$$R_{L} = \frac{V_{SS} - V_{CE(ON)}(SN75491A) - V_{OL}(SN75492A) - V_{F}(LED)}{I_{FM}(LED)}$$

#### **Typical Parameters**

$$\begin{array}{rcl} V_{SS} &=& 12 \ V \\ V_{CE(ON)} &=& 1.2 \ V \\ V_{OL} &=& 1.2 \ V \\ V_F &=& 1.7 \ V \\ I_{FM} &=& 60 \ mA \\ R_L &=& 130 \ \Omega \end{array}$$

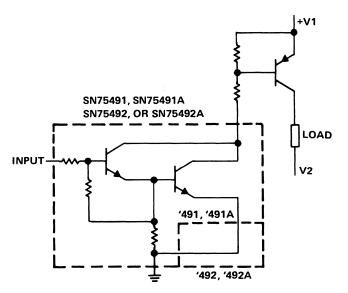

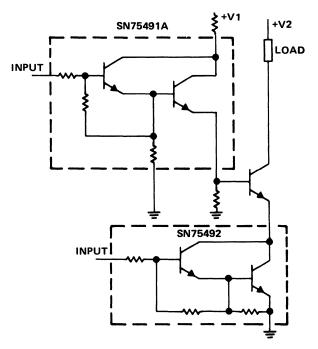

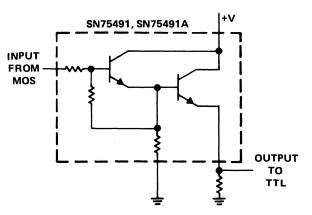

#### **OTHER APPLICATIONS**

Although the multichannel drivers shown here were designed specifically for driving light emitting diodes, they are basically Darlington transistor drivers and as such they

Figure 8-10. Quad or Hex Relay Driver

Figure 8-11. Quad or Hex Lamp Driver

Figure 8-12. Quad or Hex High-Current P-N-P Transistor Driver

have many other uses. The circuits shown in Figure 8-10 through 8-17 are examples of the variety of applications that may be implemented with these devices.

Figure 8-13. Base/Emitter Select N-P-N Transistor

Figure 8-14. MOS to TTL Level Shifter

Figure 8-15. Quad High-Current N-P-N Transistor Driver

Figure 8-17. SN75491/SN75491A Used as an Interface Circuit Between the Balanced 30-MHz Output of an RF Amplifier and a Coaxial Cable

#### DC PLASMA DISPLAY DRIVERS

DC plasma has been popular for many years as the media for digital displays. DC plasma provides a relatively bright display ideal for panel meters and various types of test equipment. Numerical 7-segment displays are used in most cases, and therefore the display drivers for dc plasma are configured specifically for this application. DC plasma displays require a rather high voltage to fire (ionize) the gas and maintain conduction. Firing voltages are generally in excess of 100 V and operating current levels are from 0.2 mA to 3 or 4 mA depending on the display's physical size and the brightness required. Multiplexing may be used in some applications to minimize the number of parts required.

(a) LOGIC SYMBOL

(b) LOGIC DIAGRAM

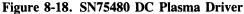

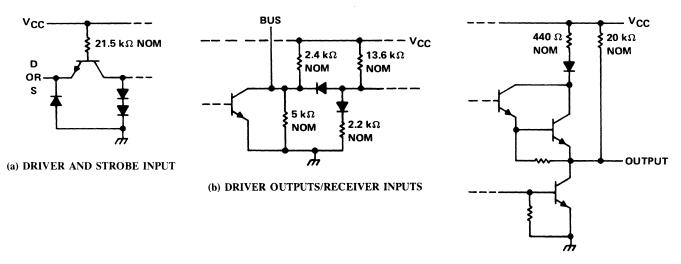

#### SN75480 DC PLASMA DRIVER

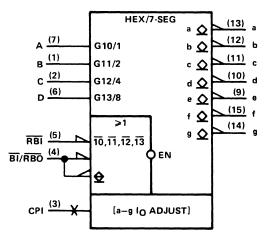

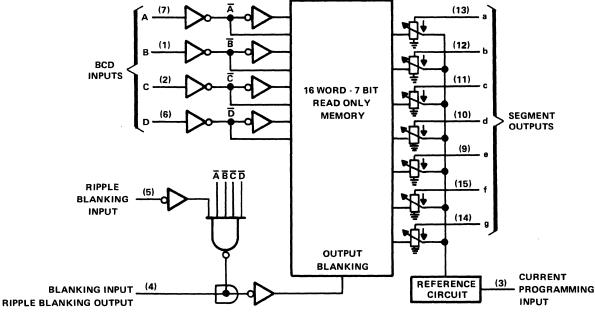

The SN75480 (Figure 8-18) is a bipolar high-voltage 7-segment decoder/cathode driver for dc plasma displays. Off-state output voltage capability is 80 V minimum. It is designed to decode four lines of hexadecimal input and drive a seven-segment Panaplex II\* type gas-filled (dc plasma) display tube. The SN75480 employs a 112 bit read only memory to provide input decoding and output segment on or off control in accordance with the function table (Figure 8-19).

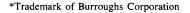

Segment drive outputs are constant-current sinks with adjustable operating levels. The current sink level is adjustable by connecting an external program resistor ( $R_p$ ) from  $V_{CC}$  to the current programming input in accordance with the curve shown in Figure 8-18(c). Output current may be adjusted from nominally 0.2 mA up to 1.5 mA in order to drive various tube types and permit multiplex operation.

Output sink currents for other segments are proportional to the b-segment current to provide even illumination of all segments. Each sink output (Figure 8-18) is regulated to ensure a constant brightness level across the display even with fluctuating supply voltages. Typical on-state currents are within 1% for voltage changes from 3 to 50 V. Off-state voltages can vary from 3 to 80 V. The blanking input (pin 4) provides unconditional blanking of all outputs, while the A through D inputs (pins 1, 2, 6 and 7) and the ripple blanking input (pin 5) into the blanking circuit, allow simple leading or trailing zero blanking.

| DECIMAL INPUTS |     |   |   |   |   | BI/RBO |     | DISPLAY |     |     |     |     |     |         |

|----------------|-----|---|---|---|---|--------|-----|---------|-----|-----|-----|-----|-----|---------|

| FUNCTION       | RBI | D | с | в | Α |        | а   | b       | С   | d   | e   | f   | g   | DISPLAY |

| 0              | н   | L | L | L | L | н      | ON  | ON      | ON  | ON  | ON  | ON  | OFF |         |

| 1              | х   | L | L | L | н | н      | OFF | ON      | ON  | OFF | OFF | OFF | OFF | 1       |

| 2              | х   | L | L | н | L | н      | ON  | ON      | OFF | ON  | ON  | OFF | ON  | 2       |

| 3              | х   | L | L | н | н | н      | ON  | ON      | ON  | ON  | OFF | OFF | ON  | Ξ       |

| 4              | x   | L | н | L | L | н      | OFF | ON      | ON  | OFF | OFF | ON  | ON  | 4       |

| 5              | x   | L | н | L | н | н      | ON  | OFF     | ON  | ON  | OFF | ON  | ON  | 5       |

| 6              | x   | L | н | н | L | н      | ON  | OFF     | ON  | ON  | ON  | ON  | ON  | 6       |

| 7              | x   | L | н | н | н | н      | ON  | ON      | ON  | OFF | OFF | OFF | OFF | 7       |

| 8              | х   | н | L | L | L | н      | ON  | ON      | ON  | ON  | ON  | ON  | ON  | 8       |

| 9              | х   | н | L | L | н | н      | ON  | ON      | ON  | ON  | OFF | ON  | ON  | 9       |

| 10             | x   | н | L | н | L | н      | ON  | ON      | ON  | OFF | ON  | ON  | ON  | R       |

| 11             | х   | н | L | н | н | н      | OFF | OFF     | ON  | ON  | ON  | ON  | ON  | Ь       |

| 12             | х   | н | н | L | L | н      | ON  | OFF     | OFF | ON  | ON  | ON  | OFF | Ľ       |

| 13             | х   | н | н | L | н | н      | OFF | ON      | ON  | ON  | ON  | OFF | ON  | d       |

| 14             | х   | н | н | н | L | н      | ON  | OFF     | OFF | ON  | ON  | ON  | ON  | Ε       |

| 15             | ×   | н | н | н | н | н      | ON  | OFF     | OFF | OFF | ON  | ON  | ON  | F       |

| ві             | х   | х | х | х | х | L      | OFF | OFF     | OFF | OFF | OFF | OFF | OFF |         |

| RBI            | L   | L | L | L | L | L†     | OFF | OFF     | OFF | OFF | OFF | OFF | OFF |         |

H = high level, L = low level, X = irrelevant

<sup>†</sup>BI/RBO is wired AND logic serving as a blanking input (BI) and/or ripple-blanking output (RBO). When RBI and inputs A, B, C; and D are all low, all segment outputs go off and RBO goes to a low-level (response condition).

Figure 8-19. SN75480 Function Table

#### **SN75480** Application

In the basic application circuit, Figure 8-20, a serial count from a controller or microprocessor is fed to the "A" input of an SN7493A binary counter. The SN7493A output is a BCD representation of the decimal number to be displayed. To hold the last input until time for an update, an SN7475 4-bit latch is used. The BCD input is decoded by the SN75480 to provide proper segment drive resulting in a displayed hexadecimal value in accordance with the function table (Figure 8-19).

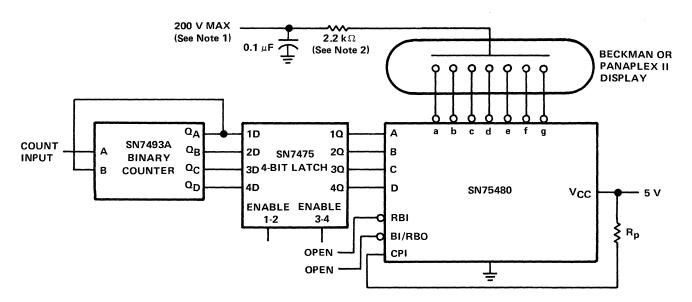

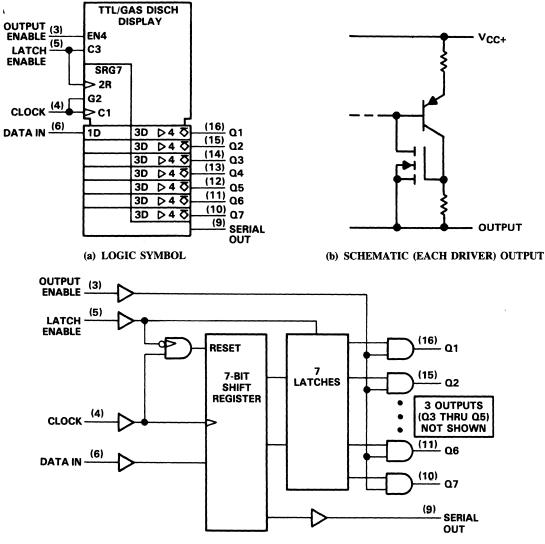

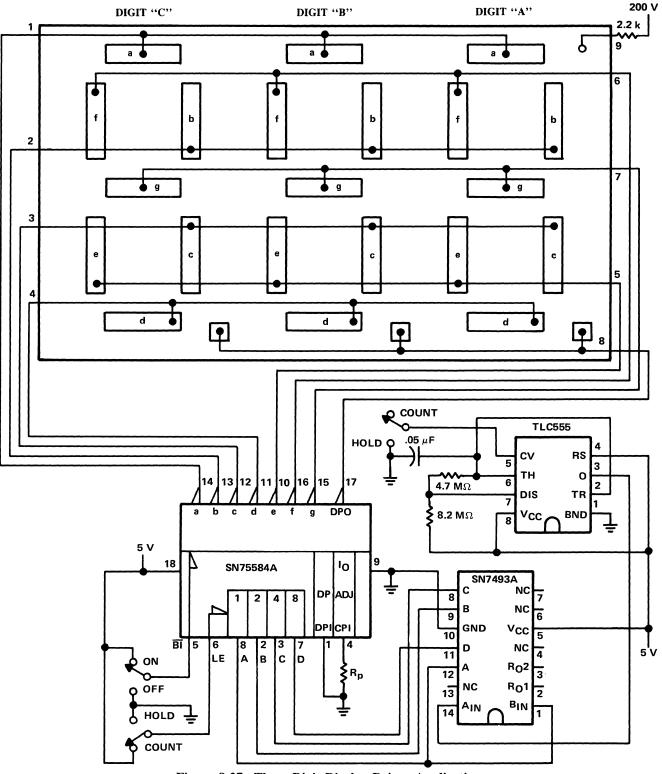

#### SN75581 GAS DISCHARGE SOURCE DRIVER

The SN75581 (Figure 8-21) is a high-voltage (150 V), 7-channel, source output monolithic BIDFET integrated circuit designed to drive a dot matrix or segmented display. Its output characteristics make this driver compatible to several display types including vacuum fluorescent and dc plasma displays.

All device inputs are diode-clamped pnp inputs and, when left open, assume a high logic level. The nominal input threshold is 1.5 V. Outputs are open source DMOS transistors for excellent high voltage characteristics and reliability.

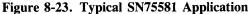

The device consists of a 7-bit shift register, seven latches, and seven output AND gates. Serial data is entered into the shift register on the low-to-high transition of the Clock input. When the Latch Enable input is high, data is transferred from the shift registers to the latch outputs. When Latch Enable makes a high-to-low transition, the shift register is cleared. Taking the Output Enable input high enables all outputs simultaneously. The Serial Output is not affected by the Output Enable input. See Figures 8-22 and 8-23.

#### SN75581 Application

A typical SN75581 gas discharge display driver application is shown in Figure 8-23. Serial data is clocked into the SN75581 under microprocessor control. When the latch enable input is high, the data is transferred from input shift registers to the latches. The latches store the data until output enable goes high, which enables all outputs (pins 9 through 16). The outputs are connected to a seven segment display (a through g). Individual segments (a through g) will fire if a data bit turns on the corresponding DMOS output transistor connected to that segment. Serial output is not utilized.

#### SN75584A HIGH-VOLTAGE 7-SEGMENT LATCH/DECODER/CATHODE DRIVER

The SN75584A is a BIDFET integrated circuit and has high voltage DMOS outputs. The SN75584A (Figure 8-24) is designed to decode four lines of BCD data and drive a seven segment (plus decimal point) gas display tube such as the Beckman and Panaplex II displays. Latches are provided to store the four data and decimal point inputs while the enable input is at a low logic level voltage.

This circuit employs a read only memory to provide output decoding for the BCD input digits 0 to 9. For input data codes greater than 9, the segment outputs are blanked. Each sink output is a constant current, regulated to ensure uniform brightness of the display even with fluctuating supply voltage. On-state output current is essentially constant over the output voltage range of 4 V to 100 V. Each current sink is normalized to the "b" segment output current as required for even illumination of all segments. Output currents may be varied from 0.1 mA to 4 mA for driving various displays.

- NOTES:1. This voltage will be different for different displays. It must be set to ensure that the on-state and off-state voltages do not exceed 55 V and 80 V at the SN75480.

- In all applications peak transient segment current must be limited to 50 mA. This may be accomplished by connecting a 2.2 kΩ resistor as shown or current limiting in an anode driver in multiplex applications.

#### Figure 8-20. Basic Digital Display Drive

(c) LOGIC DIAGRAM (POSITIVE LOGIC)

Figure 8-21. SN75581 Gas Discharge Driver

| CLOCK                         | MMM                         |            |        |            |  |  |  |  |  |  |  |  |

|-------------------------------|-----------------------------|------------|--------|------------|--|--|--|--|--|--|--|--|

| DATA<br>IN                    | IRRELEVANT VALID IRRELEVANT |            |        |            |  |  |  |  |  |  |  |  |

| SHIFT<br>REGISTER<br>CONTENTS |                             | NEW DA     | ATA    | CLEARED    |  |  |  |  |  |  |  |  |

| LATCH<br>ENABLE               |                             |            |        |            |  |  |  |  |  |  |  |  |

| LATCH<br>CONTENTS             | PREVIOUSLY S                | TORED DAT  | A   1  |            |  |  |  |  |  |  |  |  |

| OUTPUT<br>ENABLE              |                             |            |        |            |  |  |  |  |  |  |  |  |

| Q<br>OUTPUTS                  | PR                          | EVIOUS DAT | ra New | DATA VALID |  |  |  |  |  |  |  |  |

Figure 8-22. SN75581 Typical Operating Sequence

١

Figure 8-24. SN75584A DC Plasma Segment Driver

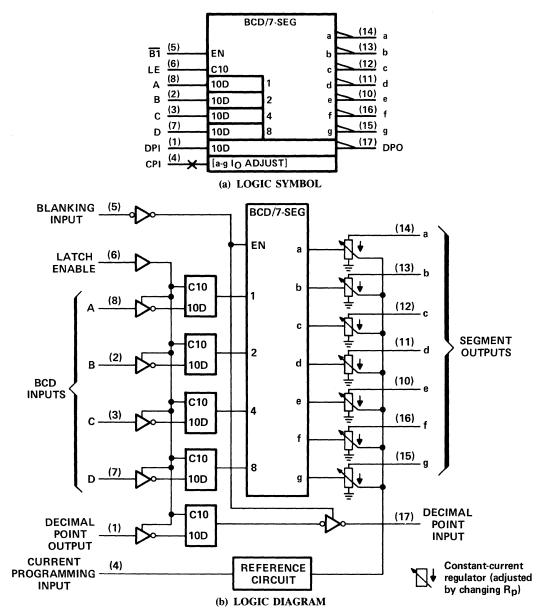

The output current is adjusted by connecting an external programming resistor ( $R_p$ ) from the current programming input to ground. Figure 8-25 shows the "b" segment output current versus programming resistance.  $I_{O(b)}$  in mA = 3.616/ $R_p$  in k $\Omega$ . The blanking input provides unconditional blanking of all segment outputs including the decimal point output. The enable input allows data to be stored internally while input data is changing. When enable is at a high level voltage, the outputs will reflect conditions on the A, B, C, D, and DP inputs in accordance with the function table in Figure 8-26. A transition from a high level voltage to a low level voltage at enable will cause the input data set up prior to the transition to be latched. In the latched state, the A, B, C, D, and DP inputs are in a high-impedance state to minimize input loading.

Thermal protection circuitry will blank the display, regardless of input conditions, whenever junction temperature exceeds approximately 150 °C.

Figure 8-25. SN75584A Segment Output Current vs Program Resistance

| e //c IDENTIFICATION |    |    |      |      |     |    |                 |     |     |     |     |     |     |             |            |

|----------------------|----|----|------|------|-----|----|-----------------|-----|-----|-----|-----|-----|-----|-------------|------------|

| DECIMAL              | DP | вс | D IN | NPUT | rs† |    | SEGMENT OUTPUTS |     |     |     |     |     |     |             |            |

| OR<br>FUNCTION       |    | D  | С    | B    | Α   | BI | a               | b   | C   | d   |     | f   | g   | OUT-<br>PUT | DISPLAY    |

| 0                    | ×  | L  | L    | L    | L   | н  | ON              | ON  | ON  | ON  | ON  | ON  | OFF | ×           | 5          |

| 1                    | ×  | L  | L    | L    | н   | н  | OFF             | ON  | ON  | OFF | OFF | OFF | OFF | ×           | 1          |

| 2                    | ×  | L  | L    | н    | L   | н  | ON              | ON  | OFF | ON  | ON  | OFF | ON  | ×           | יני ניי כי |

| 3                    | ×  | L  | L    | н    | н   | н  | ON              | ON  | ON  | ON  | OFF | OFF | ON  | ×           |            |

| 4                    | ×  | L  | н    | L    | L   | н  | OFF             | ON  | ON  | OFF | OFF | ON  | ON  | ×           | '-'        |

| 5                    | ×  | L  | н    | L    | н   | н  | ON              | OFF | ON  | ON  | OFF | ON  | ON  | ×           | יחיקר-     |

| 6                    | ×  | L  | н    | н    | L   | н  | ON              | OFF | ON  | ON  | ON  | ON  | ON  | ×           | 5          |

| 7                    | ×  | L  | н    | н    | н   | н  | ON              | ON  | ON  | OFF | OFF | OFF | OFF | ×           | 7          |

| 8                    | x  | н  | L    | L    | L   | н  | ON              | ON  | ON  | ON  | ON  | ON  | ON  | ×           | 89         |

| 9                    | ×  | н  | L    | L    | н   | н  | ON              | ON  | ON  | ON  | OFF | ON  | ON  | ×           | 3          |

| 10                   | ×  | н  | L    | н    | L   | н  | OFF             | OFF | OFF | OFF | OFF | OFF | OFF | ×           |            |

| 11                   | ×  | н  | L    | н    | н   | н  | OFF             | OFF | OFF | OFF | OFF | OFF | OFF | ×           |            |

| 12                   | ×  | н  | н    | L    | Ľ   | н  | OFF             | OFF | OFF | OFF | OFF | OFF | OFF | ×           |            |

| 13                   | ×  | н  | н    | L    | н   | н  | OFF             | OFF | OFF | OFF | OFF | OFF | OFF | ×           |            |

| 14                   | ×  | н  | н    | н    | L   | н  | OFF             | OFF | OFF | OFF | OFF | OFF | OFF | ×           |            |

| 15                   | ×  | н  | н    | н    | н   | н  | OFF             | OFF | OFF | OFF | OFF | OFF | OFF | ×           |            |

| BI                   | ×  | ×  | х    | x    | х   | L  | OFF             | OFF | OFF | OFF | OFF | OFF | OFF | OFF         |            |

| DP                   | н  | x  | ×    | x    | x   | н  | ×               | x   | x   | x   | x   | x   | x   | ON          |            |

| DP                   | L  | x  | x    | x    | x   | н  | x               | x   | x   | x   | x   | x   | x   | OFF         |            |

SEGMENT

H = high level, L = low level, X = irrelevant

<sup>†</sup>Table is valid for the indicated BCD and decimal point inputs while enable is high. See description.

Figure 8-26. SN75584A Function Table

#### **SN75584A** Application

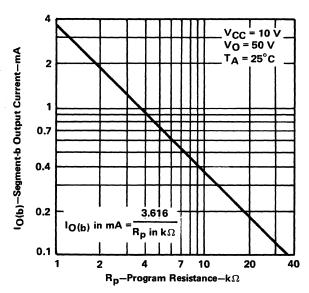

A basic circuit (Figure 8-27) that automatically counts 0 through 9, resets and counts through again is used to demonstrate the SN75584A's ease of operation and drive capabilities.

The display is a 3-digit display with decimal points requiring a 180 V supply and typical segment operating currents of 1 mA.

The TLC555 provides clock pulses at about 1.6 Hz to an SN7493A 4-bit binary counter which in turn drives the A, B, C and D inputs of the SN75584A display driver in accordance with its count sequence. Sequencing through the binary input codes results in the output segment drivers cycling from 0 through 9. For all input codes over 9 all segment outputs are blanked off. Thus the display will be blanked off for about four seconds before the count sequence

Figure 8-27. Three-Digit Display Driver Application

starts over with zero. Blanking of all output drives (including decimal point) is accomplished by switching pin 5, the blanking input, to ground. If the latch enable input, pin 6, is connected to 5 V the SN75584A continues to sequence. Switching the latch enable to ground prevents further transferring of data to the 584A outputs and the segment outputs are held (latched) in the mode they were in just prior to switching. Setting pin 6 high again allows data present in the 584A memory to again control the outputs. The driver output may also be held by simply stopping the clock. This is accomplished by switching pin 5, control voltage input, of the TLC555 to ground. In this application, pin 4 of the SN75584A, (the current programming input) is connected through a 3.3 k $\Omega$  resistor to ground allowing about 1 mA of segment drive current. The decimal point input, pin 1, is grounded which leaves the decimal point on at all times except when blanked. A TTL logic high level at pin 1 could turn off the decimal point output.

#### AC PLASMA DISPLAY DRIVERS

The persistent interest in flat panel information displays has stimulated development of the gas discharge display. Their safety, thinness, durability, and compact screen size have been the primary advantages over conventional display technologies. The following sections discuss ac plasma gas discharge displays and display drivers.

#### AC PLASMA DISPLAY TECHNOLOGY

The ac plasma display is an X-Y matrix gas discharge display. The basic display element is the gas discharge that occurs at the intersection of selected electrodes when the applied voltage between the electrodes exceeds the breakdown voltage of the media gas with which the display is filled. When the breakdown voltage of the gas is exceeded, the gas is ionized and the discharge that occurs emits a visible spot of light at the intersection of the selected electrodes. Once initiated, the display element can be maintained active without further selective control. The data retention property of the ac plasma display eliminates the necessity of a memory map for simple information displays.

#### Construction

The simple construction techniques employed are another feature encouraging the development of the ac plasma display panel. The panel envelope is essentially two flat pieces of ordinary glass spaced apart and sealed around the peripheral edges as shown in Figure 8-28.

The electrodes are deposited on the internal surfaces of the glass plates and then covered by an insulating dielectric layer prior to their joining. The space between the glass plates is evacuated and filled with a media gas under low pressure (approximately one-fifth atm.). Unlike the dc plasma display panel where the electrodes are immersed in the media gas, the electrodes of the ac plasma panel are isolated from the media gas by the dielectric layer. This dictates ac operation utilizing capacitive coupling to the insulated ac plasma display cell.

Figure 8-28. Panel Construction

Early panels utilized a third piece of perforated glass, which defined the individual display cell or pixel. Current panels, however, use an open-cell structure which eliminates the masking glass. Individual cells thus constructed are defined by properly ratioed media gas pressure, electrode width and resolution, glass spacing, and excitation and sustaining potentials. Individual cells are defined as the area located at the intersection of the mutually perpendicular electrodes of the front and back plates. The parallel electrodes of each plate of the panel are usually divided, every other electrode exiting from opposing edges of the plate, to allow easier access for the mechanical interface required to connect the electrodes to the control circuitry. The simple construction of the ac plasma panel yields a rugged sandwich containing only a few cubic centimeters of inert gas. There is no danger of implosion as found with conventional vacuum tube displays, and no danger of contact with high voltages through the glass faceplate. In addition to the low cost of the ac plasma display panel, the construction techniques yield one of the safest display panels in today's marketplace.

#### The Functional Cell

Light is emitted from the ac plasma cell as a result of the energy release that occurs when the media gas is ionized. This is accomplished by simply applying sufficient potential across the cell to break down the media gas. Since the actual cell is only capacitively coupled to the electrode potential, the voltage waveform, frequency and amplitude are interdependent for reliable plasma display operation.

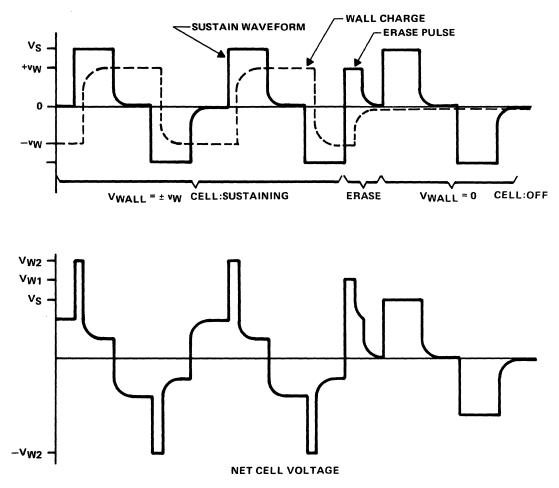

When ionization of the gas occurs, a charge buildup is created by the high electron and ion currents present in the ionization discharge sequence. This charge buildup, or wall charge as it is commonly identified, plays an important role in the ability of the ac plasma panel to maintain display information without further selective control. Figure 8-29 shows a typical applied ac waveform and the wall charge waveforms of an active and extinguished cell. These relationships are observed at all cell locations during that period of time in which no panel information is being altered (written or erased). This is normally identified as the sustain mode.

Figure 8-29. Cell Waveforms

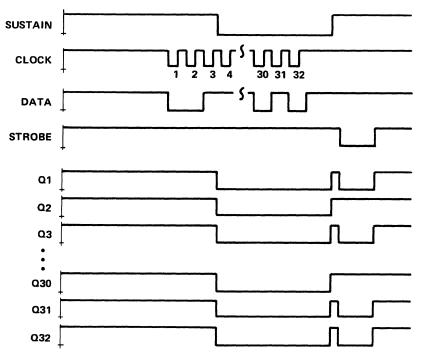

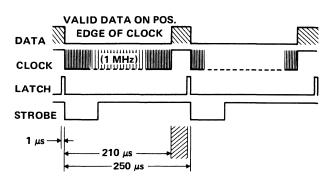

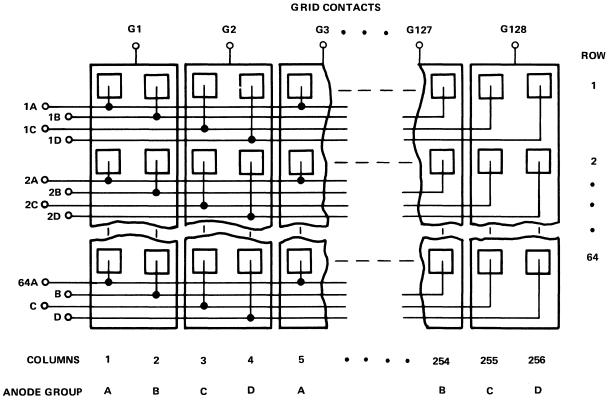

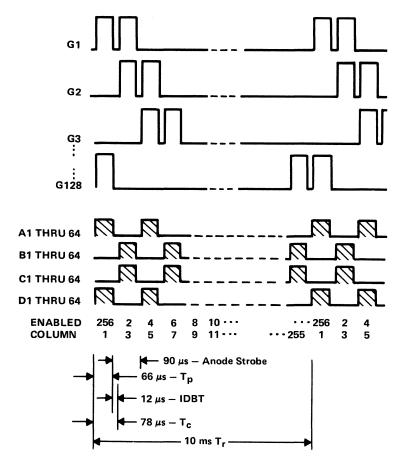

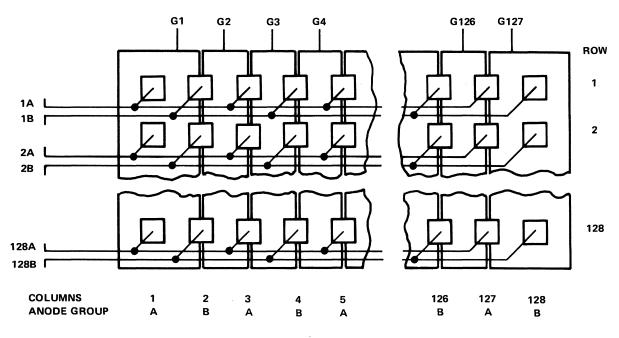

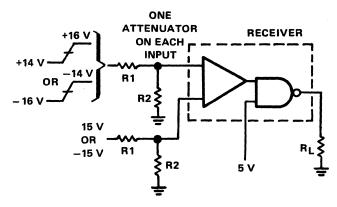

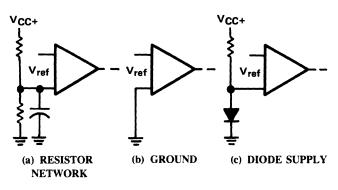

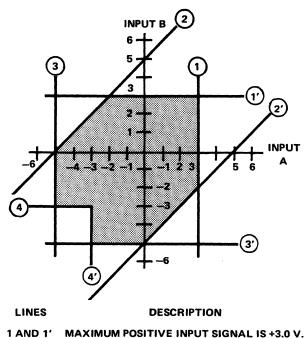

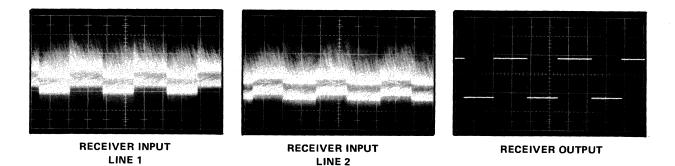

A typical write-sustain cycle waveform is shown in Figure 8-30. The electrode potential and resulting wall charge are plotted to show their interdependence in writing (initializing) and sustaining a selected cell.