# User's Guide

i

User's Guide

Sensor Signal Processors 1992

1992

# **TSS400 FAMILY USER'S GUIDE**

- Part II: TSS400/4 User's Guide

- Part III: TSS400(/4) Software User's Guide

- Part IV: TSS400 Standard User's Guide

TSS400 Family User's Guide

# Part I

Sensor Signal Processors

TSS400 Family User's Guide

# TSS400 USER'S GUIDE October 1991

Revision 3.2, October 1991

1

# **Table of Contents**

# **Purpose and Conventions**

| Paragraph | Title                                             | Page |

|-----------|---------------------------------------------------|------|

| 1         | TSS400                                            | 7    |

| 1.1       | Functional Specifications                         | 8    |

| 1.2       | Memory Structure                                  | 10   |

| 1.3       | Subroutine Stack Operation                        | 11   |

| 1.4       | Digit Latches/R Outputs                           | 12   |

| 1.5       | DAM Operation                                     | 13   |

| 1.6       | ALU                                               | 14   |

| 1.7       | CKB Memory Map Description                        | 15   |

| 1.8       | K-line Structure                                  | 16   |

| 1.9       | I/O Structure                                     | 17   |

| 1.10      | Clock                                             | 18   |

| 2         | Operational Description                           | 19   |

| 2.1       | ROM Decode                                        | 19   |

| 2.2       | Program Counter and Subroutine Register           | 20   |

| 2.3       | ROM Page Address Register and Page Buffer         | 20   |

| 2.4       | Instruction Decode                                | 21   |

| 2.5       | Processor Enable and Time Base Multiplexer        | 22   |

| 2.6       | Processor Frequency                               | 23   |

| 2.7       | Timer Oscillator                                  | 24   |

| 2.8       | Time Data Multiplexer                             | 25   |

| 2.9       | CKB (Constant, K-lines, Bit and Time Multiplexer) | 26   |

| 2.10      | Branch/Call Control                               | 26   |

| <b>TSS400</b> | User's | Guide |

|---------------|--------|-------|

|---------------|--------|-------|

| 2.11 | RAM Address/Character Decode Multiplexer | 26 |

|------|------------------------------------------|----|

| 2.12 | Write Multiplexer                        | 27 |

| 2.13 | X-Decode                                 | 27 |

| 2.14 | RAM Word Decode                          | 27 |

| 2.15 | Character Decode                         | 27 |

| 2.16 | Segment Latches                          | 27 |

| 2.17 | Segment Drivers                          | 28 |

| 2.18 | Power Up Clear                           | 28 |

| 2.19 | Status                                   | 28 |

| 2.20 | P-Multiplexer                            | 29 |

| 2.21 | N-Multiplexer                            | 29 |

| 2.22 | Adder-Comparator                         | 29 |

| 2.23 | Accumulator and Y-Register               | 29 |

| 3    | Analog/Digital Converter (ADC)           | 30 |

| 3.1  | Description of Conversion                | 32 |

| 3.2  | Battery Check                            | 34 |

| 3.3  | Current Source                           | 35 |

| 4    | Display                                  | 38 |

| 4.1  | Gate Level PLA                           | 38 |

| 4.2  | Common Select Lines                      | 39 |

| 4.3  | Select Lines                             | 40 |

| 4.4  | Display Drive Waveform                   | 42 |

| 5    | Instruction Set Description              | 43 |

| 5.1  | •                                        |    |

| -    | Functional Description                   | 44 |

| 5.2  | 9-Bit Instruction Map                    | 50 |

| 4   | Т                                      | SS400 User's Guide |

|-----|----------------------------------------|--------------------|

| 6   | Electrical Description                 | 52                 |

| 6.1 | Absolute Maximum Ratings               | 52                 |

| 6.2 | TSS400 Operating Conditions            | 53                 |

| 6.3 | TSS400 Operating Characteristics       | 54                 |

| 6.4 | TSS403 Operating Conditions            | 76                 |

| 6.5 | TSS403 Operating Characteristics       | 77                 |

| 6.6 | TSS405 Operating Conditions            | 95                 |

| 6.7 | TSS405 Operating Characteristics       | 96                 |

| 6.8 | Typical RC-MOS Oscillator Characterist | ics 113            |

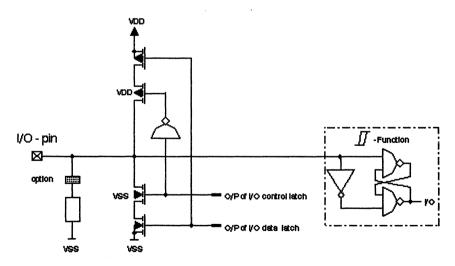

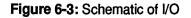

| 6.9 | Schematics of Inputs/Outputs           | 114                |

|     |                                        |                    |

| APPENDIX A | Software Restrictions       | 116 |

|------------|-----------------------------|-----|

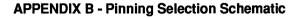

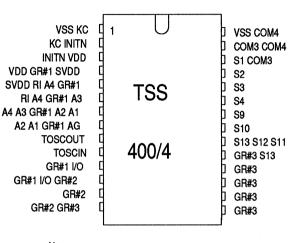

| APPENDIX B | Pinning Selection Schematic | 119 |

| APPENDIX C | User Options                | 125 |

# List of Figures

| Figure | Title                                     | Paragraph                  |

|--------|-------------------------------------------|----------------------------|

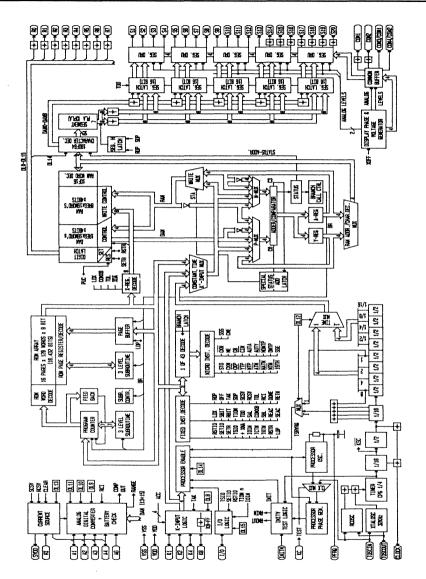

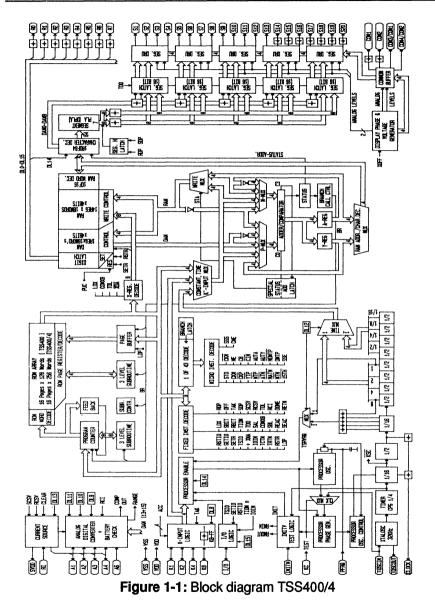

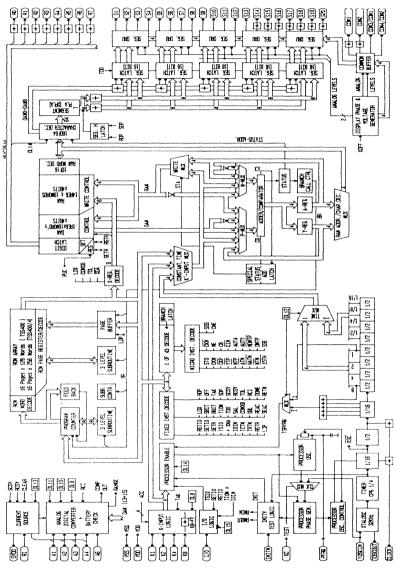

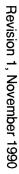

| 1-1    | Blockdiagram TSS400                       | 1.1                        |

| 1-2    | X-REG Values which Address Memory         | 1.2                        |

| 1-3    | Subroutine Stack Operation                | 1.3                        |

| 1-4    | Digit Latches/R Outputs                   | 1.4                        |

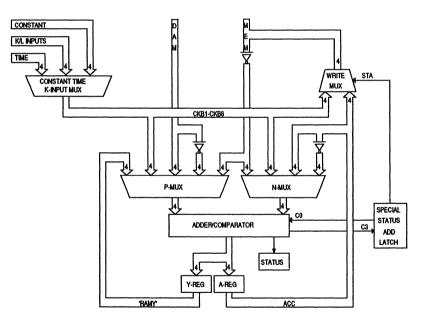

| 1-5    | Blockdiagram of ALU                       | 1.6                        |

| 1-6    | Instruction Restrictions                  | 1.7                        |

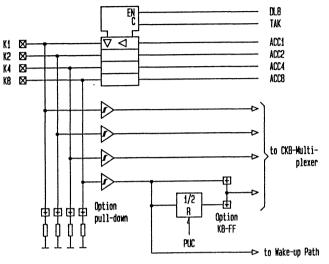

| 1-7    | K-line Structure                          | 1.8                        |

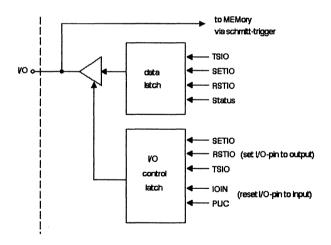

| 1-8    | I/O Structure                             | 1.9                        |

| 2-1    | Machine Status                            | 2                          |

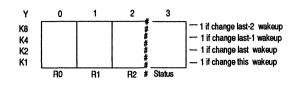

| 2-2    | Table for ext. Wake-up Conditions         | 2.5                        |

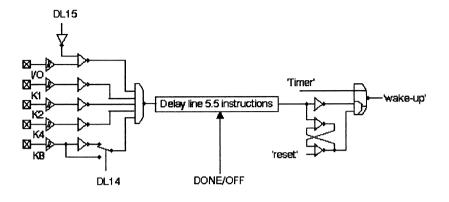

| 2-3    | Schematic of Wake-up Path                 | 2.5                        |

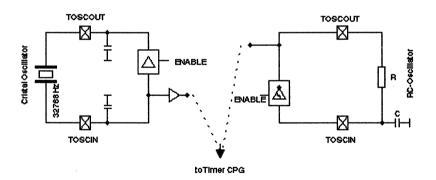

| 2-4    | Option TIMOSC                             | 2.7                        |

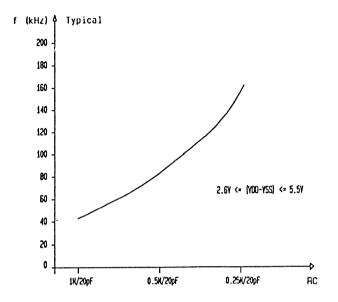

| 2-5    | TRC Oscillator Frequency                  | 2.7                        |

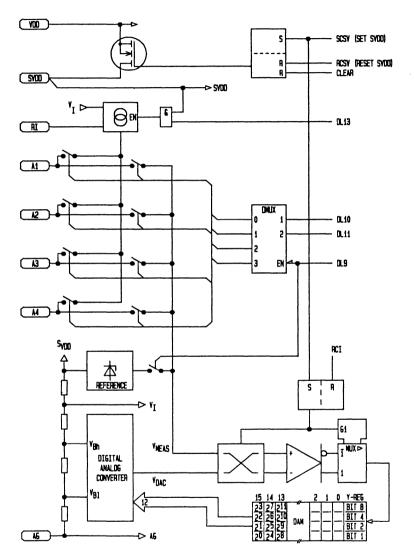

| 3-1    | Principle of A/D-Converter                | 3                          |

| 3-2    | Principle of Current Source               | 3.3                        |

| 3-3    | Current Source with Current Option        | 3.3                        |

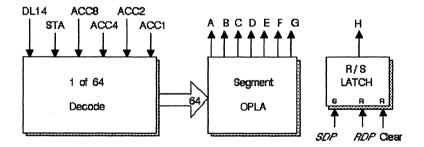

| 4-1    | Decode and OPLA for Segment Output        | 4.1                        |

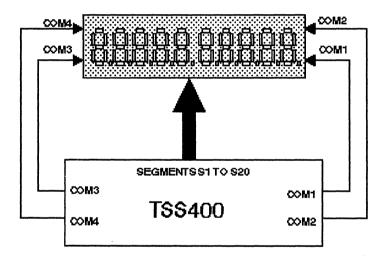

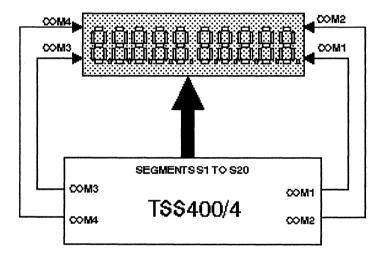

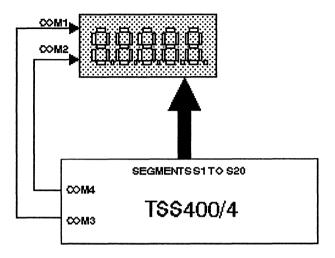

| 4-2    | 4Mux LCD Application Example              | 4.2                        |

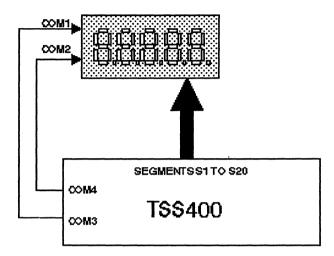

| 4-3    | 2Mux LCD Application Example              | 4.2                        |

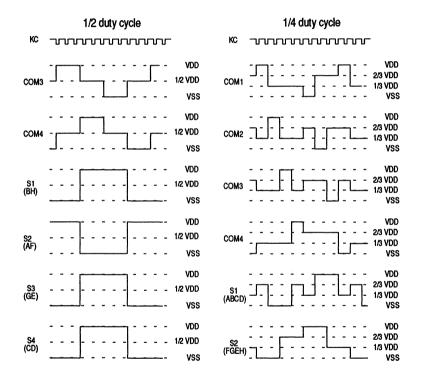

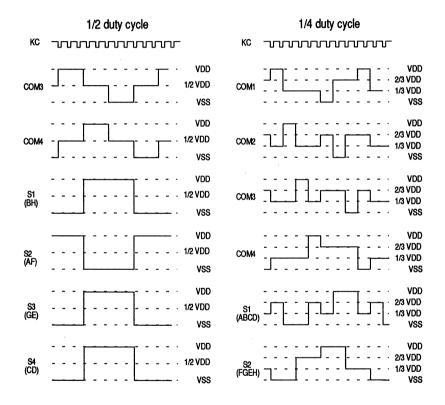

| 4-4    | Display Drive Waveform                    | 4.4                        |

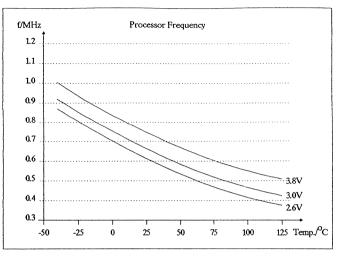

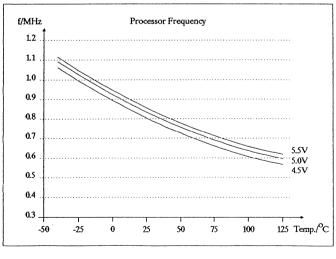

| 6-1    | Typical RC-MOS Oscillator Characteristics | 6.8                        |

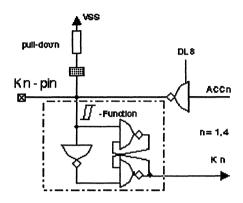

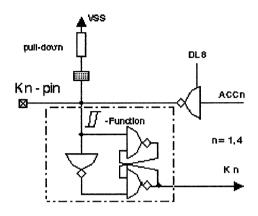

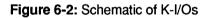

| 6-2    | Schematic of K-I/O's                      | 6.9                        |

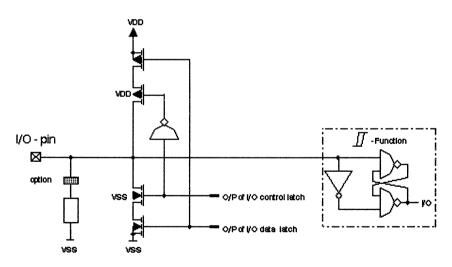

| 6-3    | Schematic of I/O                          | 6.9                        |

| 6-4    | Schematic of XTAL Oscillator              | 6.9                        |

| 6-5    | Schematic of SVDD                         | 6.9                        |

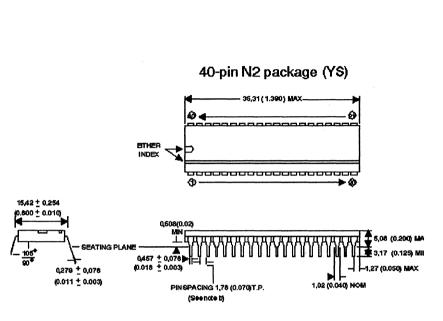

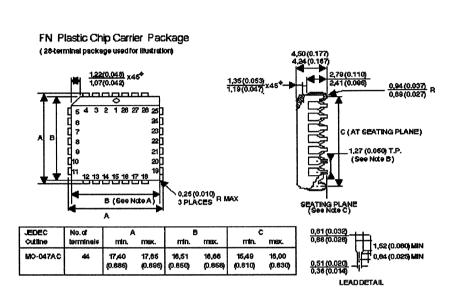

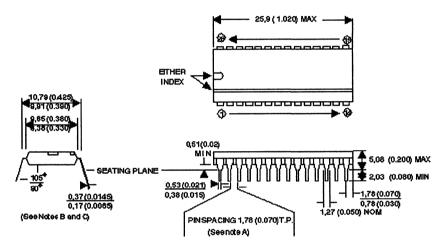

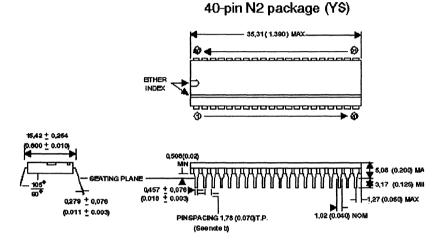

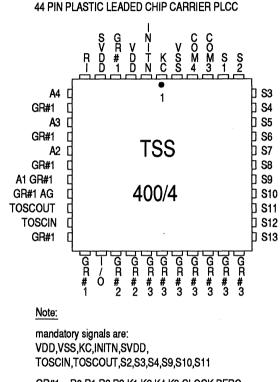

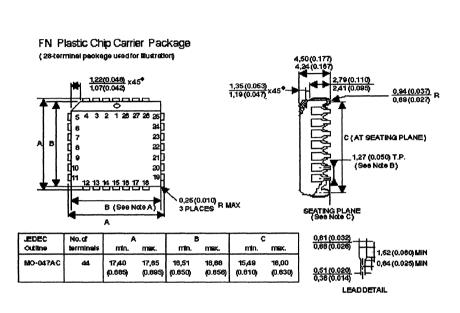

|        | 28pin DIP<br>40pin DIP<br>44pin PLCC      | App. B<br>App. B<br>App. B |

5

# **Purpose and Conventions**

The TSS400 User's Guide is intended to aid the development of TSS400 products by collecting and presenting hardware and software information in a manner that will be quickly accessible to engineers and programmers.

The following substitutes have been adopted because typographical limitations do not allow the use of some conventional symbols:

| Symbol | Meaning          | Example |

|--------|------------------|---------|

| <>     | "Not equal"      | Y <> A  |

| 0      | Subscript number | R[0]    |

| ۸      | Exponent         | T^2     |

| µsec   | Microsecond      |         |

| msec   | Millisecond      |         |

| >XX    | Hex-Value        | >3F4    |

# 1 TSS400

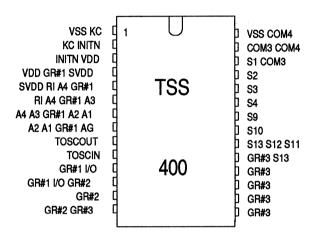

This document describes in detail the functional and electrical characteristics of a 4-bit CMOS sensor signal processor with computing capability. Its key applications are A/D conversions, calculating, controlling and displaying information on an LCD display. The part easily interfaces with sensors and actuators.

Typical applications are:

- temperature measurements: calculating, controlling, warning

- pressure and acceleration measurements

- home appliances

- intelligent keyboard and display driver

- timer with control functions

- intelligent subsystem

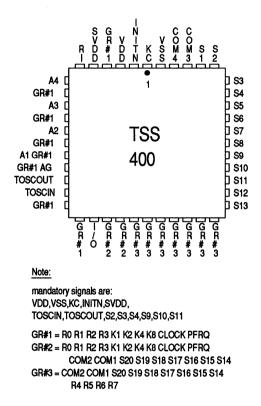

#### 1.1 Functional Specification

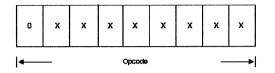

- 2048 nine bit words of ROM

- 576 bit static RAM

- Three instruction BCD addition

- 64 character, 7 segment output PLA (DP switchable independently)

- Three levels of subroutine

- Timekeeping capability (32 768 Hz XTAL)

- Direct drive of LCD: (32 768 Hz XTAL)

Option 2MUX: 1/2 duty cycle containing up to 40 segments

Option 4MUX: 1/4 duty cycle containing up to 80 segments

- Low power silicon gate CMOS process:

Low power consumption at sleep mode (active timer/RAM)

very low power consumption at off mode (active RAM)

- 12 Bit A/D-Converter with 4-MUX-inputs and programmable ranges

- Programmable current source from 0.15 to 2.4 mA x VDD/V

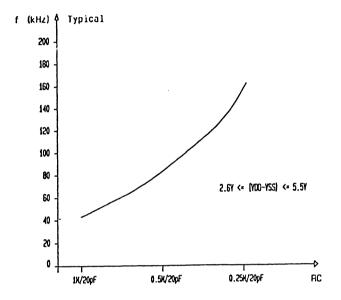

- Internal MOS oscillator (see Figure 6-1)

- Instruction execution time: 5.5  $\mu$ s (@f<sub>proc</sub> = 1.1 MHz) 15.0  $\mu$ s (@f<sub>proc</sub> = 400 KHz)

- Processor frequency determined either by the internal RC-MOS oscillator or the external clock input

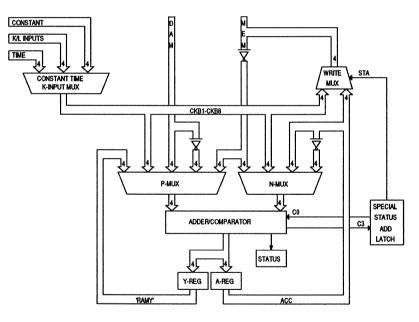

Figure 1-1: Block diagram TSS400

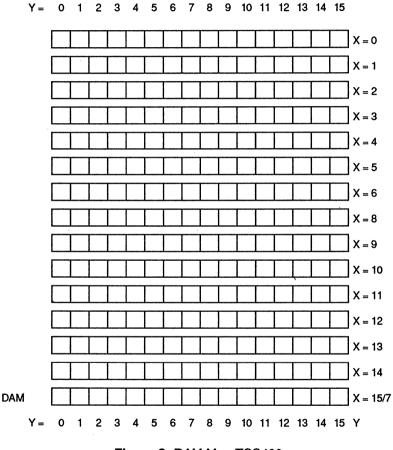

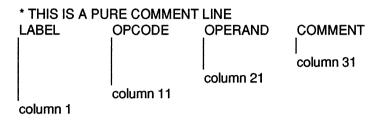

#### 1.2 Memory Structure

The TSS400 has nine (9) registers with sixteen (16) four-bit words per register.

Eight (8) registers are random access memories (RAM) and one (1) register is a direct access memory (DAM).

The 9 registers can be addressed by the X-REG. The content of the X-REG (4 bits) is controlled by the software instructions LDX, TDL, COMX8.

The Y-Register (4 bits) addresses the word within the selected Register. There are several different software instructions that control the contents of the Y-REG.

Since the TSS400 has 9 registers, some values of the X-REG do not address any memory. Figure 1-2 is a list of which values will address memory.

| X-REG | HEX | TYPE |

|-------|-----|------|

| 0001  | 1   | RAM  |

| 0010  | 2   | RAM  |

| 0011  | 3   | RAM  |

| 0100  | 4   | RAM  |

| 1001  | 9   | RAM  |

| 1010  | A   | RAM  |

| 1011  | В   | RAM  |

| 1100  | C   | RAM  |

| 0111  | 7   | DAM* |

| 1111  | F   | DAM* |

\* Both >7 and >F address the same register (the DAM). Figure 1-2: X-REG Values which Address Memory

In addition to the memory controlled by the X-REG and the Y-REG there are sixteen (16) digit latches which can be set and reset by software instructions. These digit latches are reset by hardware during power-up or by  $\overline{INIT}$ . The digit latches are addressed by Y-REG (4 bits) values >0 - >F.

#### 10

#### **1.3 Subroutine Stack Operation**

The Subroutine Stack has the following registers:

- 1) Page ROM Address Stack Register (3)

- 2) Program Counter Stack Registers (3)

The interaction of Page Register, Page ROM Address and Stack is shown for the execution of subroutines.

| P-Reg                     | x  | x  | 2  | 2  | 2  | 3  | 3 | 4 | 4 | 5 | 5 | 6 | 6 | 6  | 6  | 6  | 6  | 6  | 6  | 6  | 6  |

|---------------------------|----|----|----|----|----|----|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|

| ROM<br>Addr.<br>Reg.      | 15 | 15 | 15 | 15 | 15 | 15 | 3 | з | 4 | 4 | 5 | 5 | 6 |    | 4  | 4  | 4  | 4  | 3  | 3  | 3  |

| Sub-<br>routine<br>Reg. A | x  | 15 | 15 | x  | x  | x  | x | x | 3 | 3 | 4 | 4 | 5 | 4  | 3  | 3  | 4  | 3  | 15 | 15 | 15 |

| Sub-<br>routine<br>Reg. B | x  | x  | x  | x  | x  | x  | x | x | x | x | 3 | 3 | 4 | 3  | 15 | 15 | 3  | 15 | 15 | 15 | 15 |

| Sub-<br>routine<br>Reg. C | x  | x  | x  | x  | x  | x  | x | x | x | x | x | x | 3 | 15 | 15 | 15 | 15 | 15 | 15 | 15 | 15 |

|                           | Р  | с  | L  | R  | в  | L  | в | L | с | L | С | L | С | R  | R  | в  | с  | R  | R  | R. | R  |

|                           | υ  | A  | D  | E  | R  | D  | R | D | A | D | A | D | A | E  | E  | R  | A  | Е  | Ε  | E  | E  |

|                           | с  | L  | Р  | т  |    | Р  | • | Р | L | Р | L | Р | L | т  | т  |    | L  | т  | т  | т  | т  |

|                           |    | L  | 2  | N  |    | 3  |   | 4 | L | 5 | L | 6 | L | N  | N  |    | L  | N  | N  | N  | N  |

|                           |    |    |    |    |    |    |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |

\* This branch is executed (branch occurs).

Figure 1-3: Subroutine Stack Operation (See Section 2.2 and 2.3 for more details.)

## 1.4 Digit Latches/R Outputs

| Digit Latch | Hardware Function                                                                                                                                    |                                                   |  |  |  |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--|--|--|--|

| DL0-DL7     | Stat. o<br>available                                                                                                                                 | utputs R0-R7 $\rightarrow$ max. 8 R outputs<br>e  |  |  |  |  |

| DL8         | Control                                                                                                                                              | of K-Port: DL8 = 0 Input<br>DL8 = 1 Output        |  |  |  |  |

| DL9-DL11    | Analog<br>check                                                                                                                                      | Mux for ADC: A1-A2-A3-A4 or Battery               |  |  |  |  |

| DL12        | Selection of 1 Hz (DL12=0) or selection of mask<br>programmed frequency for wake-up of the<br>processor. Also selection of time info to CKB-<br>BUS. |                                                   |  |  |  |  |

| DL13        | DL13 Function                                                                                                                                        |                                                   |  |  |  |  |

|             | 0 constant current off<br>1 constant current on                                                                                                      |                                                   |  |  |  |  |

| DL14        | MSB of character decode and selection of K8<br>wake-up edge: leading (DL14 = 0) or trailing<br>(DL14 = 1)                                            |                                                   |  |  |  |  |

| DL15        | DL15 Function                                                                                                                                        |                                                   |  |  |  |  |

|             | 0<br>1                                                                                                                                               | wake-up of I/O enabled<br>wake-up of I/O disabled |  |  |  |  |

Figure 1-4: Digit Latches/R Outputs

PUC-signal will reset all Digit Latches.

The digit latches are set by the SETR instruction and are reset by the RSTR instruction.

The value of the Y-REG determines which digit latch is affected. The data of the Digit Latches will be retained when the product is in Sleep mode or Off mode as long as the power is maintained.

### 1.5 DAM Operation

The DAM outputs are transferred into the ALU input regardless the values of the X-REG. This allows operation on data in DAM and one of the 8 memory banks (RAM) at the same time. The DAM instruction is an example

To write into the DAM, the content of the X-REG has to be 0111 or 1111. This can be accomplished by a LDX 7, LDX 15, or a TDL instruction.

If DAM is addressed by the X-REG, all instructions operating on memory will operate on DAM. An example of this is the execution of a TMA instruction while the X-REG contains a 7. This causes the transfer of the DAM into the ACC.

If X-register is 0111 or 1111 instructions which use RAM and DAM will use DAM only. An example of this is the DMEA instr.:

$\mathsf{DAM} + \mathsf{MEM} (= \mathsf{DAM}) + \mathsf{SS} \rightarrow \mathsf{ACC} \qquad \mathsf{DAM^{*}2} + \mathsf{SS} \rightarrow \mathsf{ACC}$

### 1.6 ALU

The ALU (Arithmetic Logic Unit) can perform addition, subtraction (by two's complement) and comparison of 2 four bit numbers. Data from the Y-register, DAM, CKB multiplexer or RAM is selected by the P-multiplexer and added to or compared with data from CKB, Accumulator or RAM selected by the N-multiplexer. The adder-comparator portion of the ALU adds or compares the data. The status will be set or reset depending on the result. Data from the adder can be transferred to the Accumulator, the Y-register, or can be dumped in case the data is needed for comparison only.

Figure 1-5: Block diagram of ALU

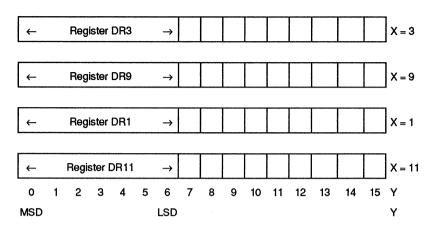

## 1.7 CKB Memory Map Description

The TSS400 has a 4-bit wide bus line (CKB) that may carry constant data, K-line data, timekeeping data or bit data (SBIT, RBIT, TBIT, TBITA, TCTM, TIOM). Any of these instructions determine which data are valid on the bus line at that time. In order to minimize the physical size of the CKB logic, certain portions of the instruction map are reserved by the CKB logic for data from one (1) of the four (4) sources to be on the CKB bus line.

| Instruction Map Locations | Source of Data on CKB Bus            |

|---------------------------|--------------------------------------|

| 008 → 00F                 | K-lines                              |

| 018 → 01F                 | TKP lines (timekeeping)              |

| 020 → 02F                 | Bit data for TBIT, TCTM              |

| 0A0 → 0AF                 | Bit data for<br>SBIT,RBIT,TBITA,TIOM |

| 040 → 07F                 | Constant data (I5 $\rightarrow$ I8)  |

| $0C0 \rightarrow 0FF$     | Constant data (I5 $\rightarrow$ I8)  |

Figure 1-6: Instruction Restrictions

As shown in Figure 1-6, certain areas of the instruction map are decoded by the CKB logic and the CKB bus line will use data from one of its sources. Use micro-instructions CKM, CKP, or CKN to transfer data to another portion of the processor. Please note that the source of data on the CKB bus is solely determined by a location in the instruction map as shown above.

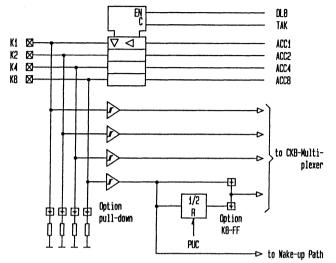

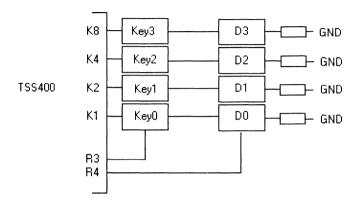

#### 1.8 K-Line Structure

Figure 1-7: K-Line Structure

The present state of Digit latch DL8 defines the state of K-Lines to be Input or Output:

Input if DL8 = "0" Output if DL8 = "1".

PUC signal will reset DL8 to "0" - Input.

The TAK instruction latches the 4 bit ACC into the output data register. If DL8 is "1" the data is available at the K-Lines:

K1 --- ACC1 K2 --- ACC2 K4 --- ACC4 K8 --- ACC8 The signals, applied at the K-pins, are read or tested directly or divided:

| Option K8-FF not used       | Option K8-FF used             |

|-----------------------------|-------------------------------|

| K1 $\rightarrow$ ACC1, MEM0 | K1 $\rightarrow$ ACC1, MEM0   |

| $K2 \rightarrow ACC2, MEM1$ | K2 $\rightarrow$ ACC2, MEM1   |

| K4 $\rightarrow$ ACC4, MEM2 | K4 $\rightarrow$ ACC4, MEM2   |

| K8 → ACC8, MEM3             | K8/2 $\rightarrow$ ACC8, MEM3 |

Three instructions are implemented to read or test the information, applied at the K-Lines:

TKA, TKM and KNEZ.

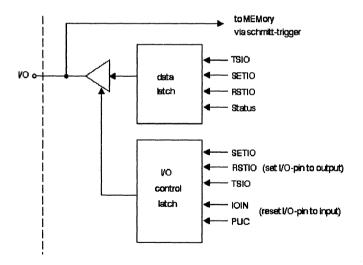

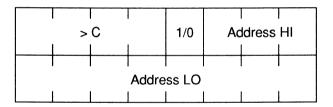

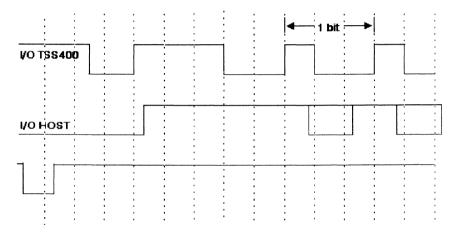

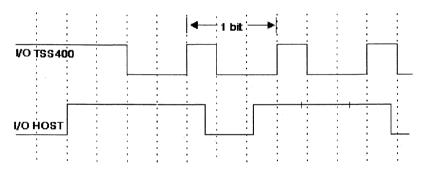

## 1.9 I/O Structure

Figure 1-8: I/O Structure

The PUC signal as well as the IOIN instruction will reset the I/O pin to be an input (output buffer is 3-state).

Three instructions define the state of the I/O pin to be an output and will determine the data to be output:

- SETIO : set I/O pin to "1"

- RSTIO : reset I/O pin to "0"

- TSIO : output Status from the previous instruction output.

#### 1.10 Clock

The Clock Output has 3 options that can be selected:

NONE : not selected

256 Hz :  $f_{Clock} = \frac{f_{TOSCIN}}{128}$

1024 Hz :  $f_{Clock} = \frac{f_{TOSCIN}}{32}$

When the processor is forced into the OFF mode, the oscillator is stopped and the TOSCIN pin is forced to  $V_{DD}$  via a p-channel transistor. The signal at the pin 'Clock' remains at the logical level it had during executing the OFF instruction.

When using the Clock Signal together with the OFF mode pay attention to the application S/W and H/W.

If a defined logical level is necessary in the application - e.g. to avoid current consumption - the logical level has to be read e.g. by K-input to check the state of the Clock Signal before executing the OFF instruction.

Note: The signal at the pin 'Clock' is not the same as the signal at the Pin "TOSCIN".

# 2 Operational Description

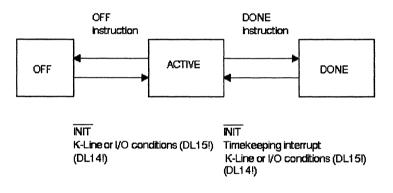

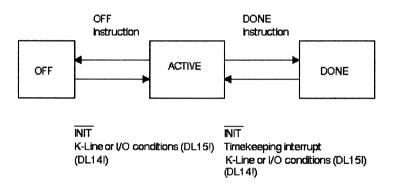

There are three different machine states: DONE, ACTIVE and OFF. During the DONE state only display and timekeeping circuitry are active. DONE is a low power state.

In the ACTIVE state the chip is executing instructions from its internal ROM and maximum power is dissipated.

In the OFF state only RAM/DAM and the actual level of I/O, R outputs and K-I/O's remain unchanged. This is true in the DONE state as well.

The machine state transitions are illustrated in Figure 1-12.

Figure 2-1: Machine Status

# 2.1 ROM Decode

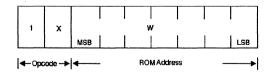

The ROM on the TSS400 has sixteen (16) pages with 128 words per page and nine bits per word. The ROM page address is contained in the ROM Page Address Register. The ROM word address is derived from the program counter.

The four bits of the page register are decoded in a 1 of 16 decode. A bus runs from the 1 of 16 page decode to the ROM and addresses the proper page.

Revision 3.2, October 1991

The seven bits of the program counter are decoded in a 1 of 128 decode. A bus runs from the 1 of 128 word decode to the ROM and addresses one word on each page. Page and word decode select together the particular word.

## 2.2 Program Counter and Subroutine Register

A bus from the program counter (PC) runs to a 1 of 128 decode and to a feedback network, which is used to change the state of the program counter in order to obtain the next ROM word address. When a CALL instruction is executed, the seven PC bits are stored in the first of a three level subroutine stack. Each successful CALL instruction pushes down the stack. As many CALL instructions as necessary may be executed, but only the three most recent return addresses are stored. All previous return addresses are lost. Each RETN instruction, up to a maximum of three consecutive, pops up the stack. Any RETN instructions encountered when the device is not in a subroutine will be treated as no-op instructions.

# 2.3 ROM Page Address Register and Page Buffer

The ROM page address register, like the program counter, is capable of three levels of subroutines.

When a CALL instruction is executed, the four page-address bits are stored in the first of a three level subroutine stack. Each successful CALL instruction pushes down the stack. As many CALL instructions as necessary may be executed, but only the three most recent return addresses are stored. All previous addresses are lost. Each RETN instruction, up to a maximum of three consecutive, pops up the stack. Any RETN instruction encountered when the device is not in a subroutine will be treated as a no-op instruction.

When a LDP instruction is executed, the page address is loaded into the Page Buffer. The Page Address is transferred to the ROM Page Address Register when a CALL or BRANCH instruction is successfully executed. If the CALL or BRANCH instruction is unsuccessful or an RETN instruction is

executed between the LDP and CALL instructions, the Page Buffer and the ROM Page Address Register remain unchanged.

After an LDP-RETN sequence, the ROM page Address Register remains unchained by CALL and BRANCH instructions.

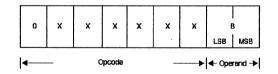

### 2.4 Instruction Decode

First a nine-bit word from the ROM goes to the instruction decode, where three types of instructions are decoded:

- programmable instructions

- fixed instructions

- CKB instructions

If 1 of the 48 programmable instructions is decoded as true, a set of microinstructions will be decoded. These micro-instructions control lines which handle one space too much various logic blocks.

If 1 of the 29 fixed instructions is decoded as true, the output of the respective instruction will set a control line used by a particular logic circuit.

If a CKB instruction is decoded as true, the 4 least significant bits of the ROM word, or the 4 K-lines, or the 4 timekeeping lines are passed into the ALU (depending on which instruction is decoded).

## 2.5 Processor Enable and Time Base Multiplexer

The software determines when the processor is disabled by executing a DONE instruction. The hardware keeps a timer up to 15 seconds; the software must keep time for all times part 15 seconds (minutes, hours, a.m/p.m., day of the week, date, and month). A calculation must not take longer than 15 seconds. In case a calculation does take longer by software an periodical interrupt of the calculation must occur to enable the timekeeping update.

The processor enable logic "wakes-up" the processor from DONE state depending on DL12, to allow the update of the timekeeping.

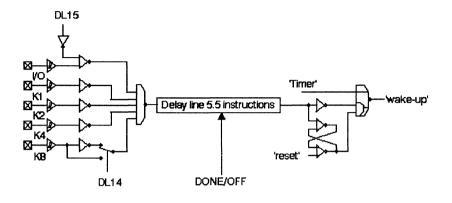

The processor logic-enable-also senses the K-lines K1, K2, K4, K8 and I/O line.

"Wake-up" from OFF state is only possible via Init, K-lines or I/O line; program execution starts at page 15, PC = >7F.

| DL14   | DL15   | K1 K2 K4 K8 1/0 | conditions for external wake-up                                    |

|--------|--------|-----------------|--------------------------------------------------------------------|

| 0<br>0 | 0<br>0 |                 | before wake-up will be accepted transition to wake-up processor    |

| 1      | 0<br>0 |                 | before wake-up will be accepted<br>transition to wake-up processor |

| 0      | 1<br>1 |                 | before wake-up will be accepted<br>transition to wake-up processor |

| 1      | 1<br>1 |                 | before wake-up will be accepted<br>transition to wake-up processor |

Note: 'v' - logical OR, ' ^ ' - logical AND, X - don't care

### Figure 2-2: Table for ext. Wake-up Conditions

Note: Wake-up occurs when 'wake-up' signal is Low AND processor in DONE/OFF mode Delay line is active if processor is active (5 to 6 instructions) Delay line is inactive if processor is in DONE/OFF mode: No Delay DL14 selects the logical state of K8 for 'wake-up' signal

Figure 2-3: Schematic of Wake-up Path

### 2.6 Processor Frequency

The processor frequency is derived from the internal RC-MOS Oscillator. The typical characteristic of this Oscillator is shown in Figure 6-1.

This internal MOS Oscillator frequency can be overwritten by an external Oscillator connected to Pin PFRQ. The frequency range for the external Oscillator is defined in Chapter 6.2 Operating Conditions.

#### 2.7 Timer Oscillator

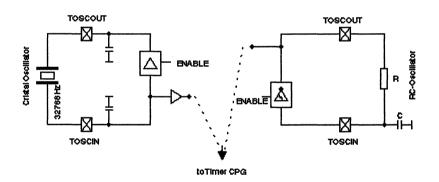

#### Crystal Oscillator

A 32.768 Hz signal of the crystal oscillator is fed into the crystal clock generator, which divides the frequency by four and generates four phase clocks. These clocks are divided down through a series of divide-by-two circuits into the frequencies needed for timekeeping functions. A signal KSC is produced by the dividing circuit. This signal is used on the logic of the Common Generator, to generate the signals on the two or four common lines.

#### RC Oscillator

Using the RC oscillator (OPTION "TRC") instead of the crystal oscillator, the same applies as described in Section 2.7 (see Figure 2-4).

### Figure 2-4: Option TIMOSC

Figure 2-5: TRC Oscillator Frequency

#### 2.8 Time Data Multiplexer

The TSS400 processor does not need to be active all the time. The processor is turned on only when needed to perform a software function or to update timekeeping. The processor can "wake-up" to update timekeeping either once per second or x-times per second (Option).

This is determined in the Time Data Multiplexer. When DL12 is high, the processor wakes-up  $x^*$ -times per second, and when DL12 is low, the processor wakes-up once per second. This also determines the data used timekeeping.

\* Options for x: 128 or 64 or 32 or 16 or 8

When DL12 is high, the 4-bit timekeeping data represents a time of 0/16 to 15/16 of a second, and when DL12 is Low, the data represent a time of 0 to 15 seconds.

The timekeeping can be accessed via CKB-Bus by software.

### 2.9 CKB (Constant, K-lines, Bit and Time Multiplexer)

All constant data used by the Y-REG, the Accumulator, or memory must pass the CKB. The logic of the CKB determines according to the used instruction whether to select constant, K-lines, bit logic, or timekeeping data to be transferred to various parts of the TSS400.

# 2.10 Branch/Call Control

When a BRANCH is encountered the Branch/Call Control Logic effects the program counter to dump the present ROM word address and accept a new one. When a CALL is encountered the Branch/Call Logic effects the program counter and the ROM page register to move their present contents into the subroutine latches and accept new addresses. A RETN forces the Branch/Call Control Logic to return the program counter to the stored address plus one. The stored address id the address when the call was encountered. The ROM page address register returns to the address it contained before the CALL. If a RETN is encountered while the CPU is not busy in a subroutine, it is regarded as a no-op and ignored. (See Status paragraph).

# 2.11 RAM Address/Character Decode Multiplexer

The RAM Address/Character Decode Multiplexer combines 2 blocks:

- 1) Multiplexer between the Y-Reg and the Accumulator. The output of the multiplexer is fed into the Decoder.

- 2) Decoder which decodes either the RAM word address from the Y-Register or the LCD character address from the Accumulator.

#### 2.12 Write Multiplexer

The Write Multiplexer determines whether data is to be put into the RAM, the DAM, or the P-Multiplexer in the ALU. The data is taken from the CKB logic or from the Accumulator. The Write Multiplexer is controlled by software.

## 2.13 X-Decode

The X-REG is decoded by the X-Decode to select a particular RAM bank. Tthe value of the DAM latch, which enables DAM and disables RAM or vice versa is also decoded by the X-REG.

#### 2.14 RAM Word Decode

The RAM Address/Character Decode Multiplexer feeds all 4 bits of the Y-REG into a 1 of 16 decode. The state of the sixteen outputs of the RAM word decode which of the sixteen words in each bank of the RAM and DAM or which of the sixteen Digit latches is addressed.

#### 2.15 Character Decode

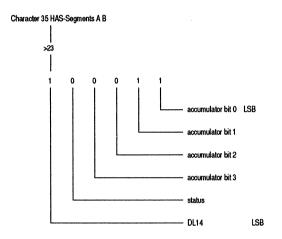

The Character Decode uses DL14, status, and the four Accumulator bits to do a 1 of 64 character decode. The 64 signals are then transferred into the output PLA, where they are converted into a seven-segment output. (The Character Decode is illustrated in the Gate Level PLA paragraph.)

### 2.16 Segment Latches

After decoding and converting the characters into segment outputs, they are latched in Segment latches when the proper Y-pointer is set and a TDO instruction is executed.

#### 2.17 Segment Drivers

The segment data is transferred to the Multiplexing Segment Drivers which convert the seven segments and the Segment H information into 2Mux or 4Mux segment information, which is output and used to turn on the LCD segments.

In test mode some of the LCD-Outputs do have other functions.

#### 2.18 Power Up Clear

There is an time interval between power is applied to the TSS400 and the starting of the clocks. The Power Up Clear (PUC) signal sets the page and word address and enables the PC after the clocks have started.

When the voltage is applied, <u>PUC</u> starts the program execution on page 15, PC = >00. A low signal at <u>INIT</u> pin creates the same function as power being applied.

When the Processor is activated from Done or OFF mode via a K-input-I/O or by a timekeeping update, the program execution begins at Page 15, PC = >7F.

#### 2.19 Status

Status is held in a single bit latch. When this bit is set, which is its normal state, and a BR or CALL is encountered, the BR or CALL will be executed. When status is reset immediately before a CALL or BR, the instruction will not be executed successfully and the Program Counter will continue incrementing.

Status will remain reset (0) for only one instruction cycle. Status can be unconditionally reset by instruction ACACC 0. Status can be unconditionally set by instruction ACYY 0.

#### 2.20 P-Multiplexer

The P-Multiplexer part of the ALU selects data from the Y-REG, the CKB, the RAM, or the DAM, and feeds this data to the Adder-Comparator part of the ALU. (See Figure 1-5)

#### 2.21 N-Multiplexer

The N-Multiplexer part of the ALU selects data from the CKB, the Accumulator, or the RAM, and feeds this data to the Adder-Comparator portion of the ALU. (See Figure 1-5)

#### 2.22 Adder-Comparator

The Adder-Comparator portion of the ALU simultaneously adds and compares the data in the N and P Multiplexers. Information from the comparator is used in determining status. Data from the Adder can be sent to the Accumulator or the Y-REG, or can be dumped if the data is needed for comparison only.

#### 2.23 Accumulator and Y-Register

The Accumulator is a four-bit register that gets its content from the Adder-Comparator. The Y-Register (Y-REG) holds the RAM word address and is used to select one of sixteen Digit latches.

# 3 Analog/Digital-Converter (ADC)

The A/D-Converter is specially designed for:

- 1-2 KOhm-temperature Si-sensors

- Pt100/Pt500/Pt1000 Elements in conjunction with internal current source

- Silicon pressure sensors

It is in no way restricted to those applications.

The A/D-Converter compares the external analogue input voltage with an internal voltage.

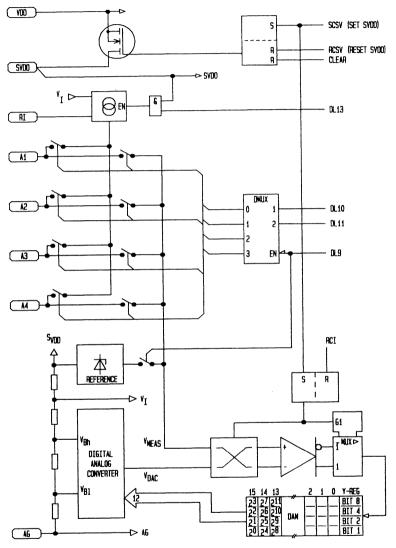

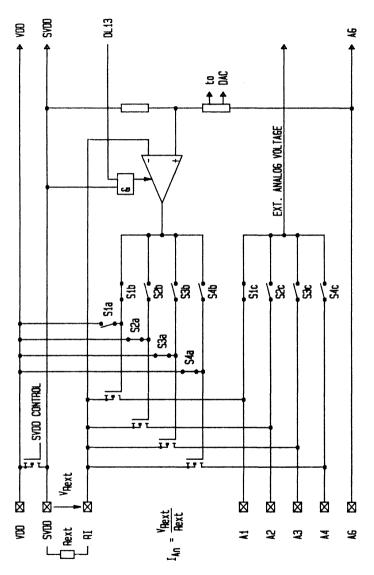

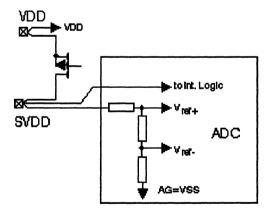

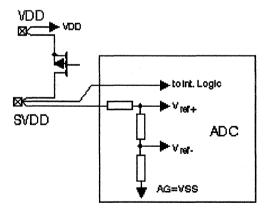

Figure 3-1: Principle of A/D-Converter

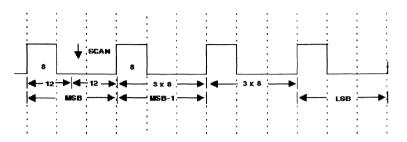

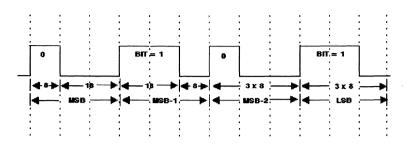

#### **Description of Conversion** 3.1

The A/D-Conversion is done by executing a software program.

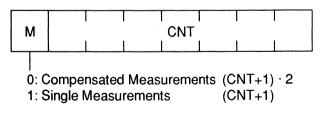

Five instructions are added to the instruction set for controlling the ADC:

- SCSV: switch converter's supply voltage on

- reset converter's supply voltage - RCSV:

- reset converter's comparator inputs to inverted - RCI:

- TCTM n: transfer comparator (output) to memory selected by X-REG and Y-REG while n identifies the bit - and set the next lower bit to high (if n is 2,3,4).

- TRTM n: transfer range to memory bit n (n =1,2,3,4).

The A/D-converter consists of:

- a D/A converter (DAC) as voltage reference source

- a Comparator

- an analog switch to interchange input signals at comparator

- an analog multiplexer (4 to 1)

- a constant current source; programmable by one external resistor and enabled or disabled by DL13

- the SV<sub>DD</sub> control

- a voltage source (for battery check)

As shown in the Figure 3-1, the instruction SCSV switches the supply voltage to the A/D Converter and PIN SVDD on - instruction RCSV switches it off. The voltage is also switched-off during Power on/INIT and if the processor is in DONE/OFF mode.

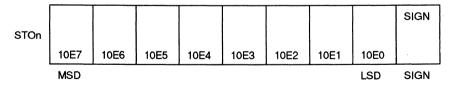

The D/A converter is controlled by 12 bits. These 12 bits are memory bits located in the DAM.

|       |                | DAM            |                |                |

|-------|----------------|----------------|----------------|----------------|

| Y-REG | BIT3           | BIT2           | BIT1           | BIT0           |

| 13    | 211            | 210            | 2 <sup>9</sup> | 2 <sup>8</sup> |

| 14    | 27             | 2 <sup>6</sup> | 25             | 24             |

| 15    | 2 <sup>3</sup> | 2 <sup>2</sup> | 21             | 20             |

D 4 1 4

The content of the 12 DAM bits is linearly converted into an analogue voltage by the DAC. This output voltage is fed into the analogue cross bar switch in front of the comparator. The comparator compares this voltage with the analogue input voltage at the selected input A1 ... A4.

A special instruction TCTM is available to do a simple successive approximation by software. This instruction transfers the comparator output to the pre-selected DAM-bit and sets the next lower bit at the same DAM address.

The starting value should be >800 (midpoint of range). The time constant of the DAC network requires some wait cycles between the TCTM instructions:

| affected bit | instructions before TCTM |

|--------------|--------------------------|

| MSB          | 5                        |

| MSB-1        | 5                        |

| MSB-2        | 5                        |

| MSB-3        | 5                        |

| MSB-4        | 4                        |

| MSB-5        | 4                        |

| MSB-6        | 4                        |

| MSB-7        | 4                        |

| MSB-8        | 3                        |

| MSB-9        | 3                        |

| MSB-10       | 3                        |

| LSB          | 3                        |

Instruction SCSV sets the analog crossbar switch at the comparator input and instruction RCI resets it. Two conversions - one with set and one with reset switch - eliminate the offset of the comparator. The two conversion results are added. The sum is twice the value of the conversion formula.

To ensure that the measurement is within the valid range, a special instruction TRTM is included. This instruction sets the addressed RAM bit to "0" if the measured value is greater than >000 and less than >FFF. Otherwise the bit is set ("1"): selected analog input voltage out of A/D-conversion range.

Optionally, there are four conversion ranges for the ADC available. One and only one must be selected. This selection is done in connection with the ROM programming.

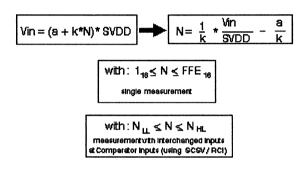

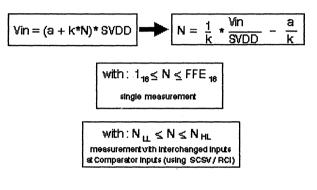

# Conversion formula: (for nominal values)

with: all voltages are referenced to AG

| Range large       | : | a = 0.101213203; k = 0.00009609  | 0233 *N |

|-------------------|---|----------------------------------|---------|

| Range small       | : | a = 0.231271438; k = 0.00004304  | 8228 *N |

| Range medium-low  | : | a = 0.1002948411; k = 0.00007381 | 6955 *N |

| Range medium-high | : | a = 0.2326179386; k = 0.00006541 | 1591 *N |

Note:  $N_{LL}$  = digital value analog input voltage lower limit.  $N_{HL}$  = digital value analog input voltage higher limit.

# 3.2 Battery Check

The stable internal voltage source (V<sub>REF</sub>) is applied to the comparator instead of an external voltage signal at the analog inputs. To the other input of the comparator, the DAC output voltage is applied. This DAC output (V<sub>DAC</sub>) is a linear function of SV<sub>DD</sub>, that is nearly identical to V<sub>DD</sub>:

$V_{DAC} = (a + K \cdot N) \cdot SV_{DD}$

The comparator allows to determine the N value for which  $V_{DAC} = V_{REF}$  and it follows:

$$SV_{DD} = V_{DD} = \frac{V_{REF}}{a \cdot K \cdot N}$$

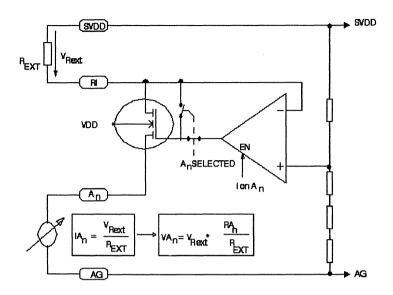

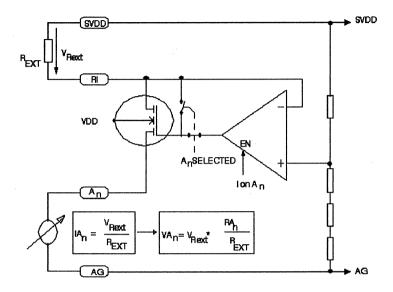

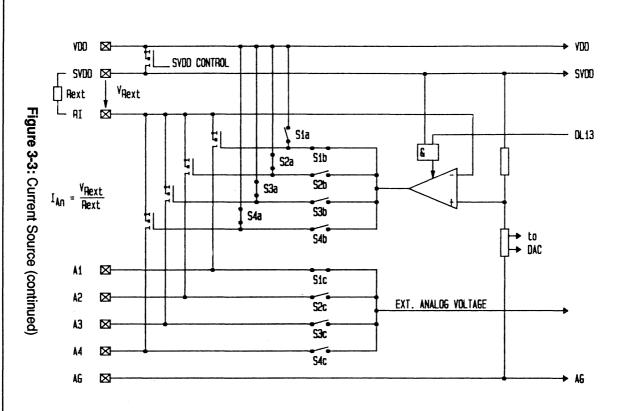

## 3.3 Current Source

The current source and the A/D converter are ratiometric. Voltage used for A/D conversion and the reference voltage (V<sub>I</sub>) used to set the current of the current source are proportional to  $SV_{DD}$  and have a fixed ratio to each other. This ensures optimum tracking. The current source is activated with DL13 set AND with  $SV_{DD}$  on; both conditions are necessary to switch on the current source.

The current, passed via an analog input to a sensor, is calculated:

$$I_{An} = \frac{V_{Rext}}{R_{ext}}$$

The current, flowing through a sensor (e.g. resistive temperature sensor), generates a voltage drop at the sensor which is available at the analog input for measurement with the A/D converter:

$$V_{in} = I_{An} \cdot R_{in}$$

with  $R_{in}$  is sensor's resistance

$V_{in} = V_{Rext} \cdot \frac{R_{in}}{R_{ext}}$

Figure 3-2: Principle of Current Source

| <br>DL13 | DL11 | DL10 | DL9 | analog input selected,<br>Current Source (CS) on/off |

|----------|------|------|-----|------------------------------------------------------|

| <br>0    | 0    | 0    | 0   | A1, CS off                                           |

| 0        | 0    | 1    | 0   | A2, CS off                                           |

| 0        | 1    | 0    | 0   | A3, CS off                                           |

| 0        | 1    | 1    | 0   | A4, CS off                                           |

| 1        | 0    | 0    | 0   | A1, CS on                                            |

| 1        | 0    | 1    | 0   | A2, CS on                                            |

| 1        | 1    | 0    | 0   | A3, CS on                                            |

| 1        | 1    | 1    | 0   | A4, CS on                                            |

| Х        | Х    | X    | 1   | battery check, CS off                                |

Figure 3-3: Current Source

Figure 3-3: Current Source (continued)

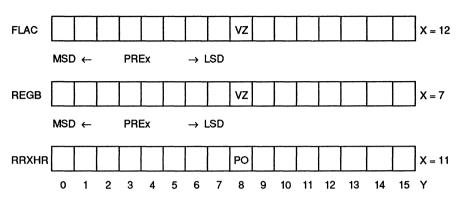

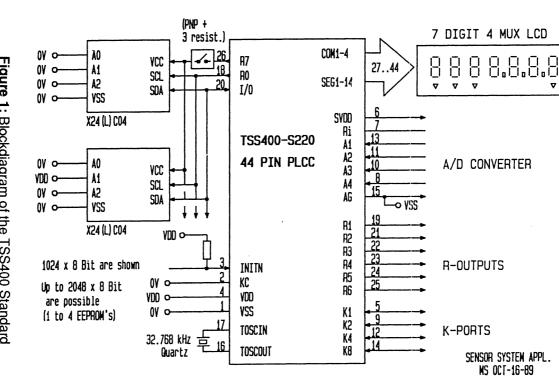

# 4 Display

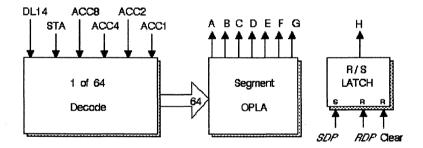

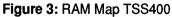

# 4.1 Gate Level PLA

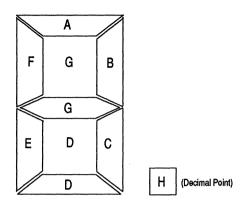

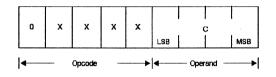

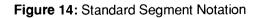

The TSS400 has a 1 of 64 decode for character output. The decode has six input lines; from the Most Significant Bit (MSB) to the Least Significant Bit (LSB) they are:

- DL14

- Status bit

- The four Accumulator bits from ACC8 to ACC1.

The decoded information is then transferred to a bus to the Segment PLA. The Segment PLA can be gate-level programmed to set the state of each of the seven segment lines, A-G, high or low depending on the decode information.

The Segment H is controlled by SDP/RDP instruction.

Figure 4-1: Decode and OPLA for Segment Output

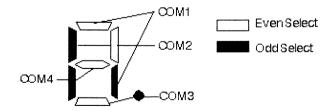

# 4.2 Common Select Lines

There are four Common Select Lines. Each has a unique output waveform that when used in combination with the twenty (20) Select Lines can control 40/80 different segments on a liquid crystal display (LCD).

The combination of Common Select Lines to Segment Lines is shown in the next paragraph.

Figure 4-2: 4Mux LCD Application Example

Figure 4-3: 2Mux LCD Application Example

# 4.3 Select Lines

Up to twenty Select Lines are available as outputs. Each Select Line defines two/four Segments as shown below. A 64-term gate programmablesegment PLA (decoded by ACC1, ACC2, ACC4, ACC8 Status, DL14) and SGH determines which segments are to be turned on.

These are then loaded into the Segment Latches by Y-Decoder/TDO instruction and time-multiplexed to the Output Select Lines.

# **TSS400 Segment Latch Structure**

(Standard Common-Segment-Y option) \*).

# 1/2 duty cycle (2 mux) 1/4 duty cycle (4 mux)

| Select<br>LineSegments<br>byLoaded<br>bySelect<br>LineSegments<br>byLoaded<br>byCCOCCCOMMCCCCOMMMMMMM34123412S1BHY0/TDOS1AACY0/TDOS2AFY0/TDOS2FGHS3GEY0/TDOS3ABCY1/TDOS4CDY0/TDOS4FGHY1/TDOS5BHY1/TDOS5ABCY2/TDOS6AFY1/TDOS7ABCY3/TDOS8CDY1/TDOS8FGHY4/TDOS10AFY2/TDOS10FGHY4/TDOS11GEY2/TDOS11ABCY5/TDOS12CDY2/TDOS12FGHY6/TDOS13BHY3/TDOS13ABCY7/TDOS16CDY3/TDOS16FGHY6/TDOS16CDY3/TDOS16FGHY6/TDOS18AFY4/TDOS18FGHY6/TDOS1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |          |        |      |          |        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|--------|------|----------|--------|

| C C C         O O         C C C C         O O O           M M         3 4         1 2 3 4           S1         B H         Y0/TDO         S1         A B C D         Y0/TDO           S2         A F         Y0/TDO         S2         F G E H         Y0/TDO           S3         G E         Y0/TDO         S2         F G E H         Y0/TDO           S4         C D         Y0/TDO         S3         A B C D         Y1/TDO           S5         B H         Y1/TDO         S4         F G E H         Y2/TDO           S6         A F         Y1/TDO         S6         F G E H         Y2/TDO           S8         C D         Y1/TDO         S7         A B C D         Y3/TDO           S9         B H         Y2/TDO         S9         A B C D         Y4/TDO           S11         G E         Y2/TDO         S10         F G E H         Y4/TDO           S11         G E         Y2/TDO         S11         A B C D         Y5/TDO           S12         C D         Y2/TDO         S11         A B C D         Y5/TDO           S13         B H         Y3/TDO         S13         A B C D         Y7/TDO                                                                 | 1    | Segments |        |      | Segments |        |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Line |          | by     | Line |          | by     |

| M M         M M M         M M M M           3 4         1 2 3 4           S1         B H         Y0/TDO         S1         A B C D         Y0/TDO           S2         A F         Y0/TDO         S2         F G E H         Y0/TDO           S3         G E         Y0/TDO         S2         F G E H         Y0/TDO           S4         C D         Y0/TDO         S4         F G E H         Y1/TDO           S5         B H         Y1/TDO         S5         A B C D         Y2/TDO           S6         A F         Y1/TDO         S6         F G E H         Y2/TDO           S7         G E         Y1/TDO         S7         A B C D         Y3/TDO           S8         C D         Y1/TDO         S8         F G E H         Y3/TDO           S9         B H         Y2/TDO         S9         A B C D         Y4/TDO           S11         G E         Y2/TDO         S10         F G E H         Y4/TDO           S11         G E         Y2/TDO         S11         A B C D         Y5/TDO           S12         C D         Y2/TDO         S12         F G E H         Y5/TDO           S13         B H <td></td> <td>СС</td> <td></td> <td></td> <td>CCCC</td> <td></td> |      | СС       |        |      | CCCC     |        |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      | 00       |        |      | 0000     |        |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      | ММ       |        |      | мммм     |        |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      | 34       |        |      | 1234     |        |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | S1   | вн       | Y0/TDO | S1   | ABCD     | Y0/TDO |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | S2   | AF       | Y0/TDO | S2   | FGEH     | Y0/TDO |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | S3   | GE       | Y0/TDO | S3   | ABCD     | Y1/TDO |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | S4   | CD       | Y0/TDO | S4   | FGEH     | Y1/TDO |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | S5   | ВН       | Y1/TDO | S5   | ABCD     | Y2/TDO |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      | AF       | Y1/TDO | S6   | FGEH     | Y2/TDO |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | S7   | GE       | Y1/TDO | S7   | ABCD     | Y3/TDO |

| S10         A F         Y2/TDO         S10         F G E H         Y4/TDO           S11         G E         Y2/TDO         S11         A B C D         Y5/TDO           S12         C D         Y2/TDO         S12         F G E H         Y5/TDO           S13         B H         Y3/TDO         S13         A B C D         Y6/TDO           S14         A F         Y3/TDO         S14         F G E H         Y6/TDO           S15         G E         Y3/TDO         S14         F G E H         Y6/TDO           S16         C D         Y3/TDO         S15         A B C D         Y7/TDO           S16         C D         Y3/TDO         S16         F G E H         Y7/TDO           S17         B H         Y4/TDO         S17         A B C D         Y8/TDO           S18         A F         Y4/TDO         S18         F G E H         Y8/TDO           S19         G E         Y4/TDO         S19         A B C D         Y9/TDO                                                                                                                                                                                                                                         | S8   | CD       | Y1/TDO | S8   | FGEH     | Y3/TDO |

| S11         G E         Y2/TDO         S11         A B C D         Y5/TDO           S12         C D         Y2/TDO         S12         F G E H         Y5/TDO           S13         B H         Y3/TDO         S13         A B C D         Y6/TDO           S14         A F         Y3/TDO         S14         F G E H         Y6/TDO           S15         G E         Y3/TDO         S14         F G E H         Y6/TDO           S15         G E         Y3/TDO         S15         A B C D         Y7/TDO           S16         C D         Y3/TDO         S16         F G E H         Y7/TDO           S17         B H         Y4/TDO         S17         A B C D         Y8/TDO           S18         A F         Y4/TDO         S18         F G E H         Y8/TDO           S19         G E         Y4/TDO         S19         A B C D         Y9/TDO                                                                                                                                                                                                                                                                                                                             | S9   | ВН       | Y2/TDO | S9   | ABCD     | Y4/TDO |

| S12         C D         Y2/TDO         S12         F G E H         Y5/TDO           S13         B H         Y3/TDO         S13         A B C D         Y6/TDO           S14         A F         Y3/TDO         S14         F G E H         Y6/TDO           S15         G E         Y3/TDO         S15         A B C D         Y7/TDO           S16         C D         Y3/TDO         S16         F G E H         Y7/TDO           S17         B H         Y4/TDO         S17         A B C D         Y8/TDO           S18         A F         Y4/TDO         S18         F G E H         Y8/TDO           S19         G E         Y4/TDO         S19         A B C D         Y9/TDO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | S10  | AF       | Y2/TDO | S10  | FGEH     | Y4/TDO |

| S13         B         H         Y3/TDO         S13         A         B         C         D         Y6/TDO           S14         A         F         Y3/TDO         S14         F         G         H         Y6/TDO           S15         G         E         Y3/TDO         S15         A         B         C         D         Y7/TDO           S16         C         D         Y3/TDO         S16         F         G         E         Y7/TDO           S16         C         D         Y3/TDO         S16         F         G         E         Y7/TDO           S17         B         H         Y4/TDO         S17         A         B         C         D         Y8/TDO           S18         A         F         Y4/TDO         S18         F         G         H         Y8/TDO           S19         G         E         Y4/TDO         S19         A         B         C         D         Y9/TDO                                                                                                                                                                                                                                                                             | S11  | GE       | Y2/TDO | S11  | ABCD     | Y5/TDO |

| S14         A F         Y3/TDO         S14         F G E H         Y6/TDO           S15         G E         Y3/TDO         S15         A B C D         Y7/TDO           S16         C D         Y3/TDO         S16         F G E H         Y7/TDO           S17         B H         Y4/TDO         S17         A B C D         Y8/TDO           S18         A F         Y4/TDO         S18         F G E H         Y8/TDO           S19         G E         Y4/TDO         S19         A B C D         Y9/TDO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | S12  | CD       | Y2/TDO | S12  | FGEH     | Y5/TDO |

| S15         G E         Y3/TDO         S15         A B C D         Y7/TDO           S16         C D         Y3/TDO         S16         F G E H         Y7/TDO           S17         B H         Y4/TDO         S17         A B C D         Y8/TDO           S18         A F         Y4/TDO         S18         F G E H         Y8/TDO           S19         G E         Y4/TDO         S19         A B C D         Y9/TDO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | S13  | ВН       | Y3/TDO | S13  | ABCD     | 1      |

| S16         C D         Y3/TDO         S16         F G E H         Y7/TDO           S17         B H         Y4/TDO         S17         A B C D         Y8/TDO           S18         A F         Y4/TDO         S18         F G E H         Y8/TDO           S19         G E         Y4/TDO         S19         A B C D         Y9/TDO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | S14  | AF       | Y3/TDO | S14  | FGEH     | Y6/TDO |

| S17         B H         Y4/TDO         S17         A B C D         Y8/TDO           S18         A F         Y4/TDO         S18         F G E H         Y8/TDO           S19         G E         Y4/TDO         S19         A B C D         Y9/TDO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | S15  | GE       | Y3/TDO | S15  | ABCD     | Y7/TDO |

| S18         A F         Y4/TDO         S18         F G E H         Y8/TDO           S19         G E         Y4/TDO         S19         A B C D         Y9/TDO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | S16  | CD       | Y3/TDO | S16  | FGEH     | Y7/TDO |

| S19 GE Y4/TDO S19 ABCD Y9/TDO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | S17  | ВН       | Y4/TDO | S17  | ABCD     | Y8/TDO |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | S18  | AF       | Y4/TDO | S18  | FGEH     | Y8/TDO |

| S20 C D Y4/TDO S20 F G E H Y9/TDO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | S19  | GE       | Y4/TDO | S19  | ABCD     | Y9/TDO |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | S20  | CD       | Y4/TDO | S20  | FGEH     | Y9/TDO |

\*) Note: The Y-Address of each Segment Group is configurable to application needs. The definition is done together with the ROM programming (via mask).

#### 4.4 Display Drive Waveforms

Display-Drive waveforms are shown in Figure 4-4 for 1/2 and 1/4 duty cycle LCD. The internal logic signal KSC initiates voltage changes in the display voltages.

KSC has a frequency of 512 Hz and is active for 122 micro-seconds ( $f_{TOSCIN} = 32768$  Hz).

#### Figure 4-4: Display Drive Waveforms (Standard Gate Placement) e.g. Number 4: Segment 'BCFG' on - 'ADEH' off

# 5 Instruction Set Description

The following abbreviations will be used in describing the Instruction Set:

| CONSTANT =<br>LSB =<br>MEM =<br>MSB =<br>REG =<br>SS =<br><> = | Accumulator<br>= 0-15<br>= Least Significant Bit<br>= Memory as pointed to by X and Y Registers<br>= Most Significant Bit<br>= Register<br>= Special Status Latch<br>= not equal<br>= not Accumulator |

|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|