# Telecom Datacom & System Timing

TriQuint (

Telecom Datacom & SystemTiming 8661

## *Telecom, Datacom & System Timing*

## **Product Catalog**

PN 1003600

Revision 1.0.A First printed October 1997

An ISO-9001 Registered Company TUV Certified Registration No. 09 100 4518

Copyright © 1997 TriQuint Semiconductor, Inc. All rights reserved.

TriQuint and the TriQuint logo are registered trademarks of TriQuint, Inc. TriQuint product names are trademarks of TriQuint , Inc. All other trademarks are the property of their respective holders.

The information provided herein is believed to be reliable; TriQuint assumes no liability for inaccuracies or omissions. TriQuint assumes no responsibility for the use of this information, and all such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. TriQuint does not authorize or warrant any TriQuint product for use in life-support devices and/or systems.

ii

SEMICONDUCTOR, INC.

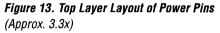

## Table of Contents

| Overview                     | Section 1 |

|------------------------------|-----------|

| Telecommunications Products  | Section 2 |

| Digital Switching Products   | Section 3 |

| Data Communications Products | Section 4 |

| Mixed Signal Products        | Section 5 |

| System Timing Products       | Section 6 |

| Application Notes            | Section 7 |

| Sales and Distribution       | Section 8 |

OVERVIEW

TQS

## Section 1 — Overview

| Product Summary    | <br>1-3 |

|--------------------|---------|

| Company Background | <br>1-6 |

TQS

## Product Summary

### **Telecommunications Products**

| Part           | Description                                                                                               | PLL Features                      | Low-Speed I/O | High-Speed I/O | Loopback | Page |

|----------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------|---------------|----------------|----------|------|

| <b>TQ</b> 8101 | 622/155 Mb/s SONET/SDH<br>8:1 Mux and 1:8 Demux                                                           | Includes 622 Mb/s<br>transmit PLL | s TTL         | ECL            | Yes      | 2-3  |

| TQ8103         | 622 Mb/s SONET/SDH<br>Clock and Data Recovery                                                             | Includes<br>622 Mb/s PLL          | TTL           | ECL            |          | 2-17 |

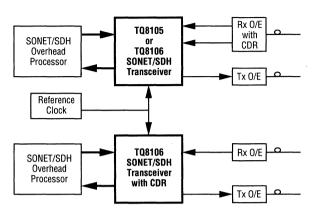

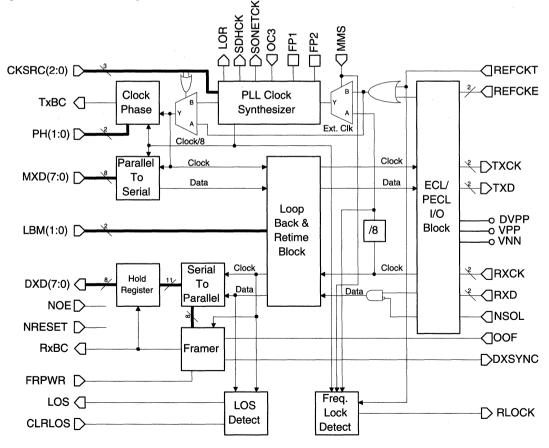

| TQ8105         | 622/155 Mb/s Enhanced SONET/SDH<br>8:1 Multiplexer, 1:8 Demultiplexer,<br>Framer, and PLL (single supply) | Includes 622 Mb/s<br>transmit PLL | s TTL         | ECL or PECL    | Yes      | 2-27 |

| TQ8106         | TQ8105 with clock and data recovery                                                                       | Includes 622 Mb/s<br>CDR          | s TTL         | ECL or PECL    | Yes      | 2-27 |

### **Digital Switching Products**

| Part           | Description                                            | Propagation Delay | I/O      | Skew (max.) | Jitter       | Page |

|----------------|--------------------------------------------------------|-------------------|----------|-------------|--------------|------|

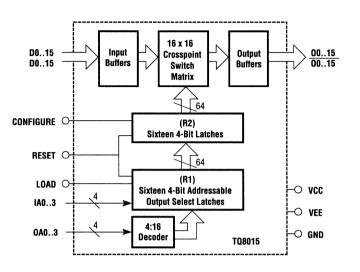

| <b>TQ80</b> 15 | 1.25 Gb/s/port 16x16 ECL<br>Digital Crosspoint Switch  | 2000 ps           | ECL      | 500 ps      | 150 ps pk–pk | 3-3  |

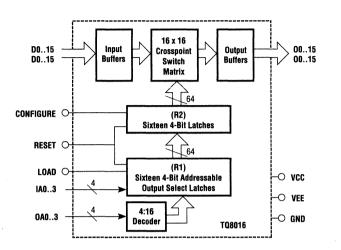

| TQ8016         | 1.3 Gb/s/port 16x16 ECL<br>Digital Crosspoint Switch   | 2000 ps           | ECL      | 400 ps      |              | 3-11 |

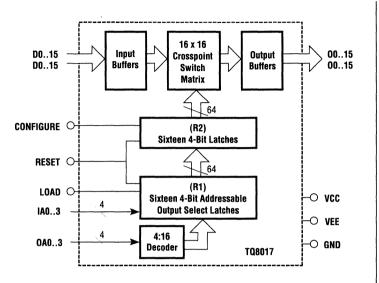

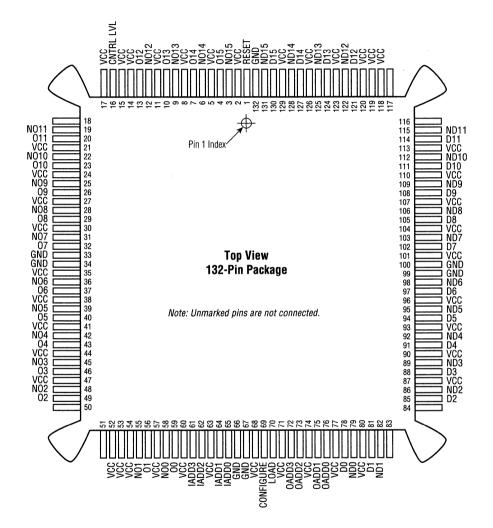

| <b>TQ80</b> 17 | 1.25 Gb/s/port 16x16 PECL<br>Digital Crosspoint Switch | 2000 ps           | PECL     | 500 ps      | 150 ps pk–pk | 3-21 |

| TQ8025         | 2.5 Gb/s/port 16x16 PECL<br>Digital Crosspoint Switch  | 2000 ps           | PECL/CML | 200 ps      | 100 ps pk–pk | 3-29 |

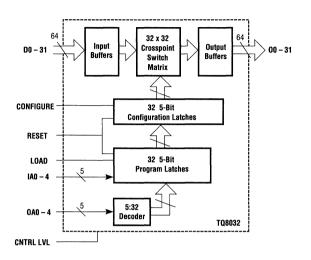

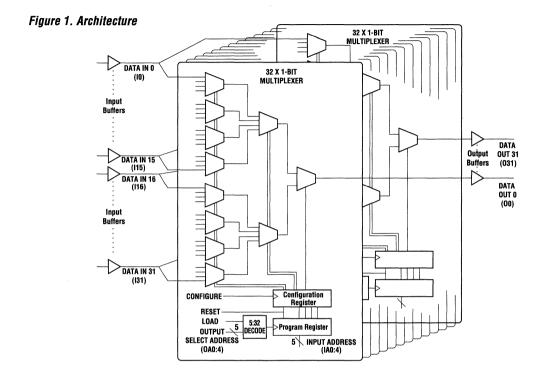

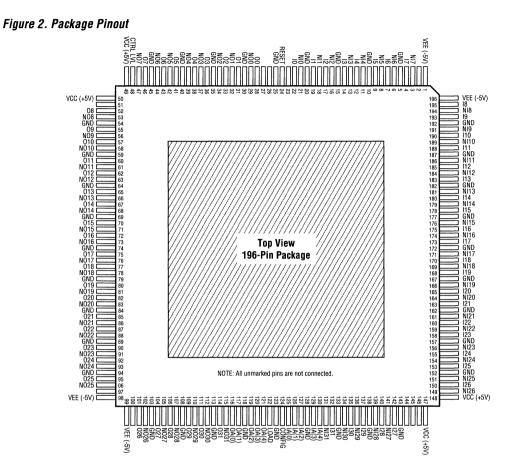

| TQ8032         | 800 Mb/s/port 32x32 ECL<br>Digital Crosspoint Switch   | 2300 ps           | ECL      | 500 ps      | 150 ps pk–pk | 3-37 |

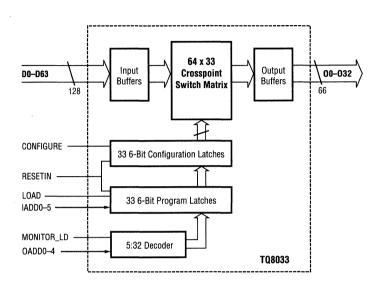

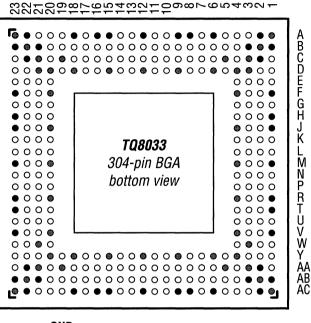

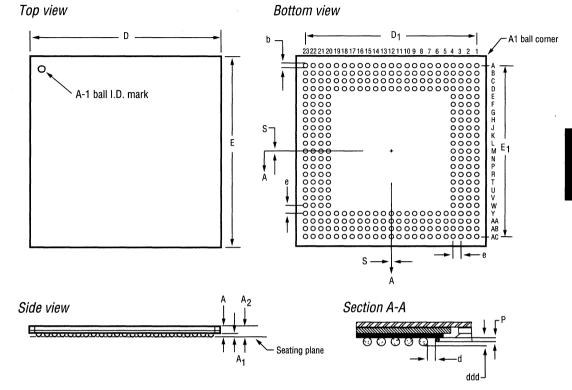

| TQ8033         | 1.5 Gb/s/port 64x33 PECL<br>Digital Crosspoint Switch  | 2500 ps           | PECL     | 150 ps      | 150 ps pk–pk | 3-45 |

## Data Communications Products

| Part           | Description                                                | Page |

|----------------|------------------------------------------------------------|------|

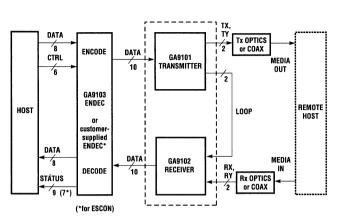

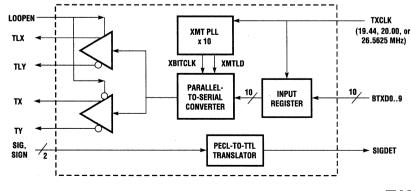

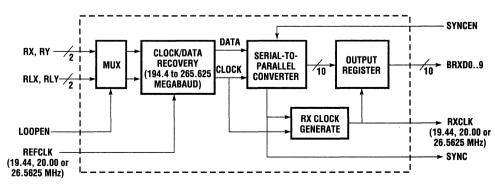

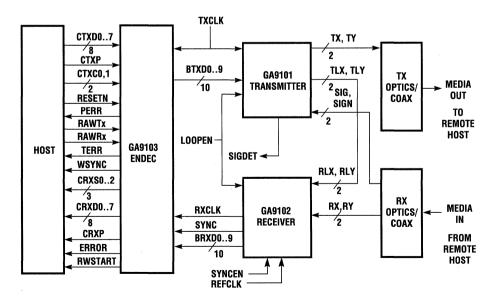

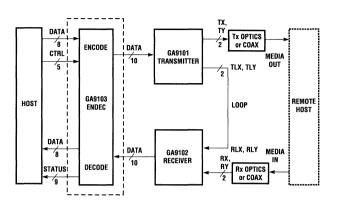

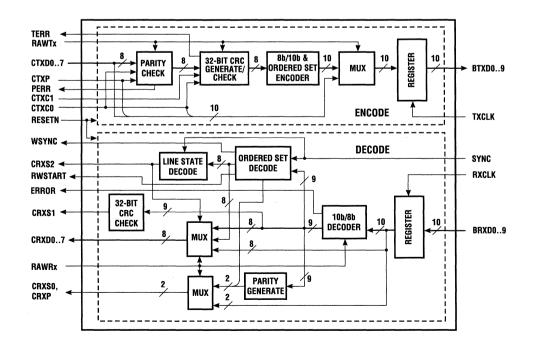

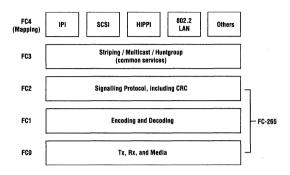

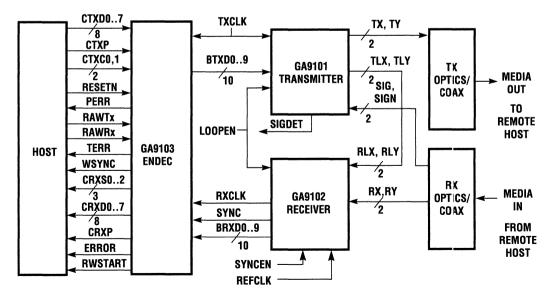

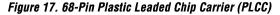

| GA9101, GA9102 | 266/200 Mbaud Fibre-Channel ESCON Transmitter and Receiver | 4-3  |

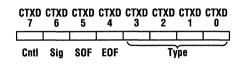

| GA9103         | 266 Mbaud Fibre-Channel Encoder/Decoder                    | 4-17 |

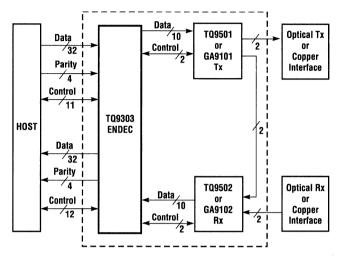

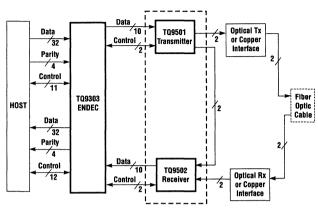

| TQ9303         | 531/1063 Mbaud Fibre-Channel Encoder/Decoder               | 4-35 |

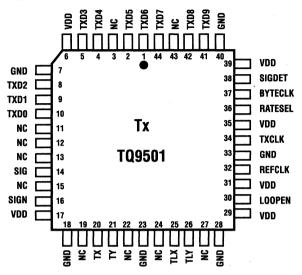

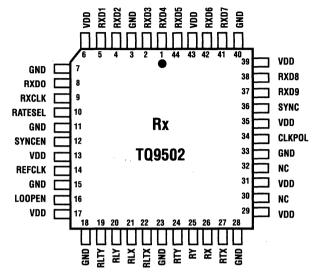

| TQ9501, TQ9502 | 531/1063 Mbaud Fibre-Channel Transmitter and Receiver      | 4-61 |

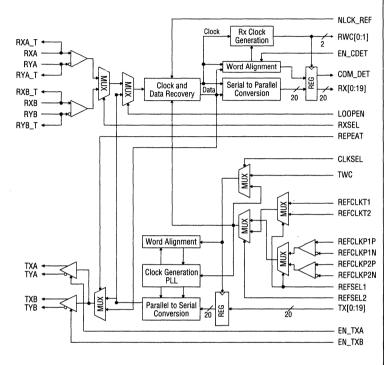

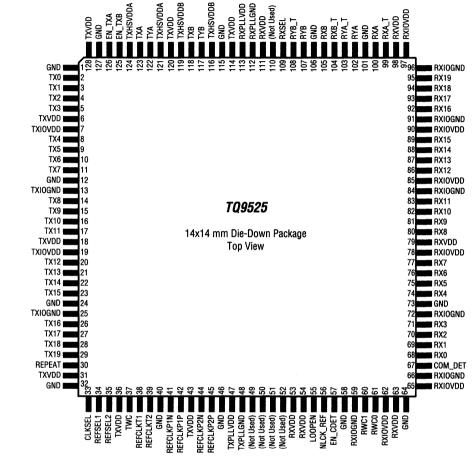

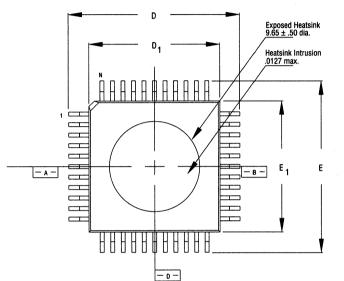

| TQ9525         | 2.5 Gb/s 20-bit Transceiver                                | 4-77 |

## Product Summary (continued)

### **Mixed Signal Products**

| Part   | Description                               | Page |

|--------|-------------------------------------------|------|

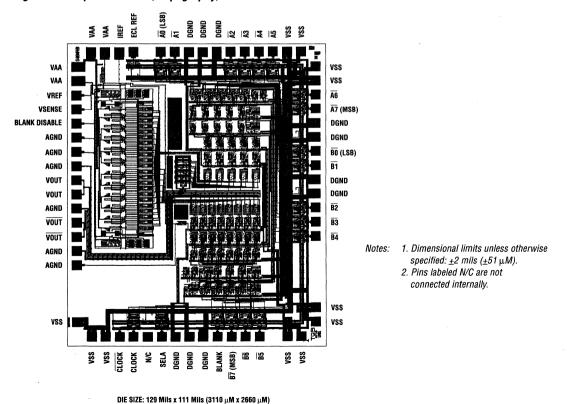

| TQ6122 | 1 GS/s 8-Bit Digital-to-Analog Converter  | 5-3  |

| TQ6124 | 1 GS/s 14-Bit Digital-to-Analog Converter | 5-27 |

### System Timing Products

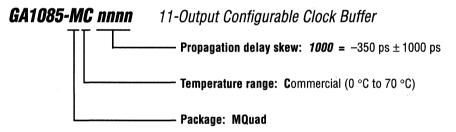

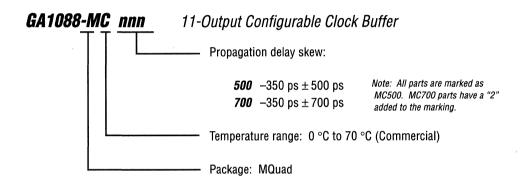

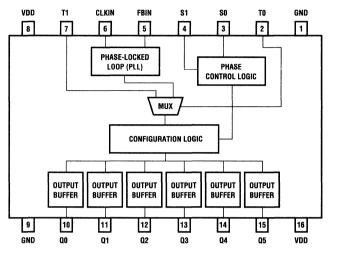

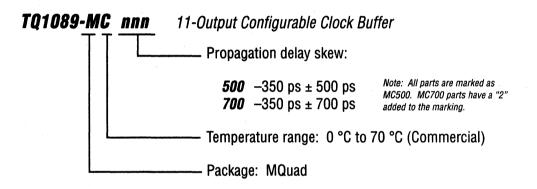

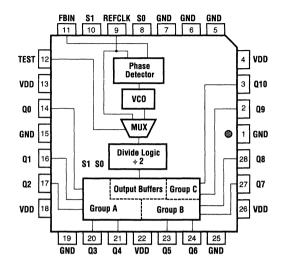

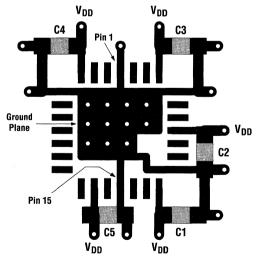

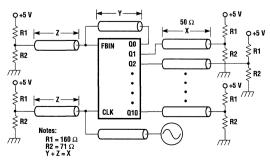

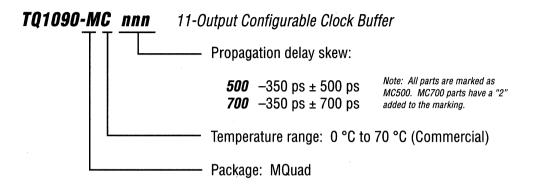

#### Eleven-Output Clock Buffers

| Part   | Prop. Delay                                                    | Input Freq.                           | Output Freq.                          | Configuration                                                                                                        | I/O                           | Skew (max.)                                          | Jitter                                                         | Page |

|--------|----------------------------------------------------------------|---------------------------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------|-------------------------------|------------------------------------------------------|----------------------------------------------------------------|------|

| GA1085 | –350 ps ± 1000<br>(−MC1000)                                    | 24–105 MHz                            | 24–105 MHz                            | 2@ <sup>1</sup> /2x <sup>w</sup> /phase shift,<br>4@1x, 4@ <sup>1</sup> /2x<br>or<br>2@1x <sup>w</sup> /phase shift, | TTL<br>±30 mA<br>output drive | 150 ps<br>within group<br>—<br>350 ps<br>group—group | 200 ps (max.)<br>period-period<br><br>400 ps (max.)<br>random  | 6-3  |

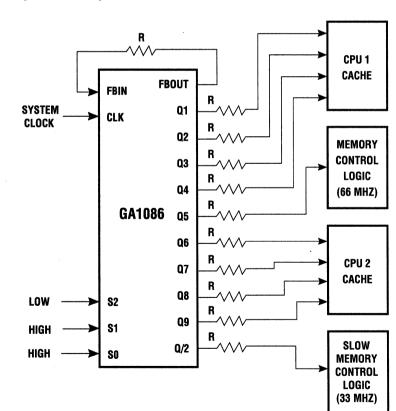

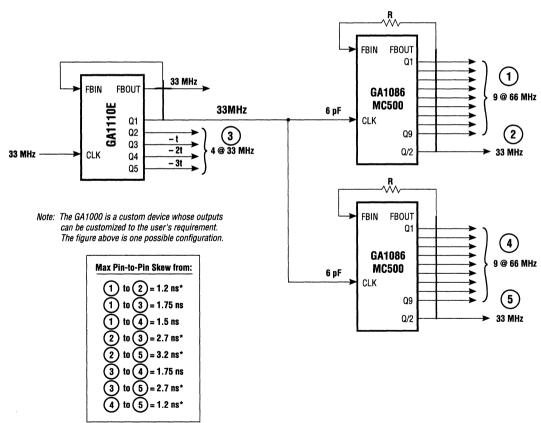

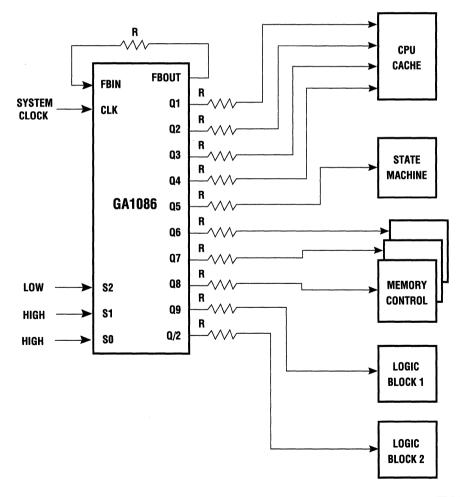

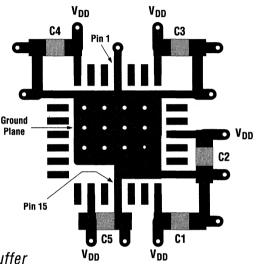

| GA1086 | -350 ps ± 500<br>(-MC500)<br>or<br>-350 ps ± 1000<br>(-MC1000) | 30–67 MHz                             | 15–67 MHz                             | 9@1x, 1@ <sup>1</sup> /2x                                                                                            | TTL<br>±30 mA<br>output drive | 250 ps<br>within group                               | 75 ps (typ.)                                                   | 6-13 |

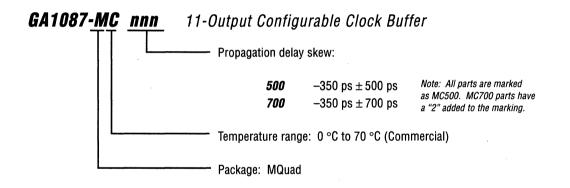

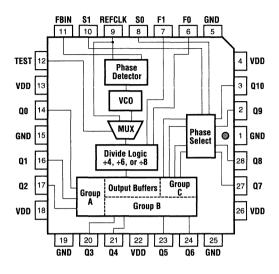

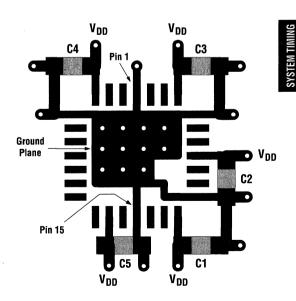

| GA1087 | -350 ps ± 500<br>(-MC500)<br>or<br>-350 ps ± 700<br>(-MC700)   | 24–105 MHz                            | 24–105 MHz                            | 5@1x, 5@ <sup>1</sup> /2x<br>or<br>6@2x, 4@1x                                                                        | TTL<br>±30 mA<br>output drive | 150 ps<br>within group<br>—<br>350 ps<br>group–group | 200 ps (max.)<br>period-period<br><br>400 ps (max.)<br>random  | 6-25 |

| GA1088 | -350 ps ± 500<br>(-MC500)<br>or<br>-350 ps ± 700<br>(-MC700)   | 18–105 MHz                            | 18–105 MHz                            | 4@1x <sup>w</sup> /phase shift,<br>3@1x, 3@1/2x<br>or<br>2@1x, 4@2x,<br>4@2x <sup>w</sup> /phase shift               | TTL<br>±30 mA<br>output drive | 150 ps<br>within group<br>—<br>350 ps<br>group–group | 200 ps (max.)<br>period–period<br>400 ps (max.)<br>random      | 6-35 |

| TQ1089 | −350 ps ± 700<br>(−MC700)                                      | 130–180 MHz<br>65–90 MHz              | 130–180 MHz<br>65–90 MHz              | 1@1x, 9@1/2x<br>or<br>2@2x, 8@1x                                                                                     | TTL<br>±30 mA<br>output drive | 150 ps<br>within group<br>—<br>350 ps<br>group–group | 200 ps (max.)<br>period-period<br><br>400 ps (max.)<br>random  | 6-71 |

| TQ1090 | -350 ps ± 700<br>(-MC700)                                      | 33–45 MHz<br>65–90 MHz<br>130–180 MHz | 33–45 MHz<br>65–90 MHz<br>130–180 MHz | 3@1x, 5@ <sup>1</sup> /2x, 2@2x<br>or<br>4@1x, 4@2x, 2@4x                                                            | TTL<br>±30 mA<br>output drive | 150 ps<br>within group<br>—<br>350 ps<br>group–group | 200 ps (max.)<br>period–period<br>—<br>400 ps (max.)<br>random | 6-81 |

## Product Summary (continued)

### System Timing Products (continued)

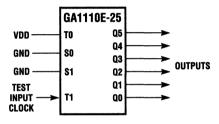

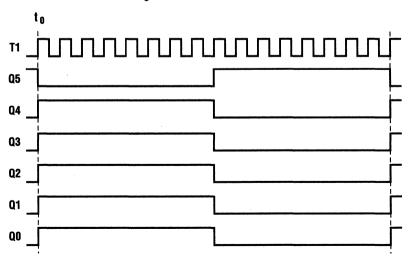

#### Six-Output Clock Devices

| Part    | Prop. Delay | Input Freq.                                                             | Output Freq. | Configuration                                                    | I/O                           | Skew (max.)             | Page |

|---------|-------------|-------------------------------------------------------------------------|--------------|------------------------------------------------------------------|-------------------------------|-------------------------|------|

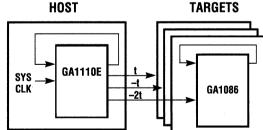

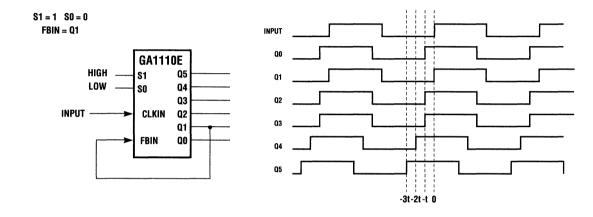

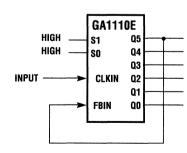

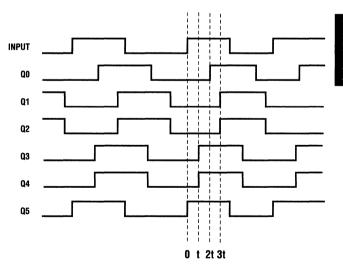

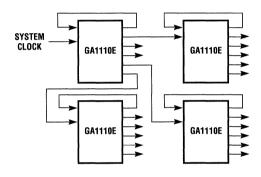

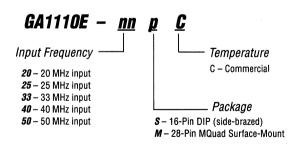

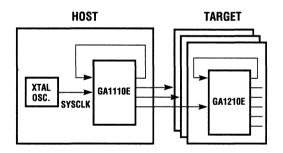

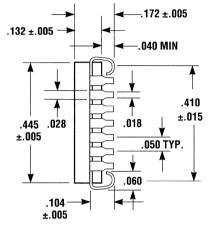

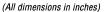

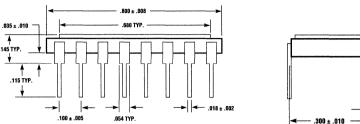

| GA1110E | ±1 ns       | -20: 20 MHz<br>-25: 25 MHz<br>-33: 33 MHz<br>-40: 40 MHz<br>-50: 50 MHz | 20–50 MHz    | 6@1x <sup>w</sup> phase shift                                    | TTL<br>±24-mA<br>output drive | 1000 ps<br>within group | 6-45 |

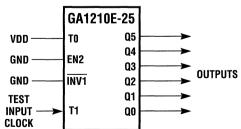

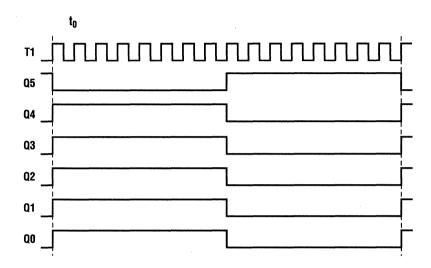

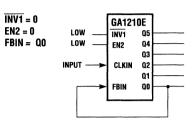

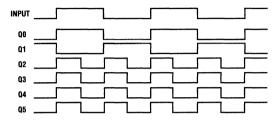

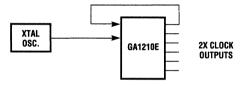

| GA1210E | ±1 ns       | -20: 20 MHz<br>-25: 25 MHz<br>-33: 33 MHz<br>-40: 40 MHz<br>-50: 50 MHz | 20–100 MHz   | 2@1x, 4@2x<br>or<br>2@1x, 2@2x,<br>2@1x <sup>w</sup> phase shift | TTL<br>±24-mA<br>output drive | 1000 ps<br>within group | 6-59 |

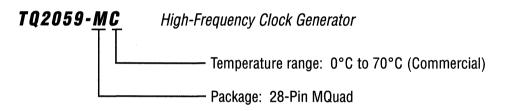

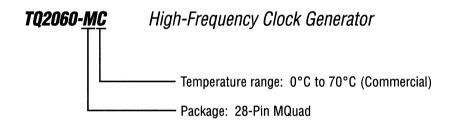

#### **High-Frequency Clock Generators**

| Part   | Input Freq. | Output Freq. | I/O      | Jitter                     | Page  |

|--------|-------------|--------------|----------|----------------------------|-------|

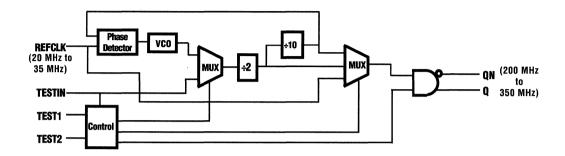

| TQ2059 | 20–35 MHz   | 200–350 MHz  | TTL/PECL | 30 ps (typ.) period-period | 6-91  |

| TQ2060 | 35–50 MHz   | 350–500 MHz  | TTL/PECL | 25 ps (typ.) period-period | 6-97  |

| TQ2061 | 25–35 MHz   | 500–700 MHz  | TTL/PECL | 25 ps (typ.) period-period | 6-103 |

### Wireless Communication Products and Foundry Services

For information on TriQuint's wireless communications products and foundry services, refer to the *Wireless Communications Products Data Book*.

TQS

## **Company Background**

#### Introduction

TriQuint Semiconductor designs, develops, manufactures and markets a broad range of highperformance analog and mixed-signal gallium arsenide (GaAs) integrated circuits (ICs) for the telecommunications, data communications, computing, and wireless communications markets.

TriQuint engineers apply the company's proprietary GaAs technology to produce high-performance, lowcost ICs that give customers a competitive edge in their product strategies.

Inherent physical properties allow electrons to move approximately five times faster in GaAs than in silicon. This enables GaAs ICs to operate at much higher frequencies than silicon ICs — or to perform as fast while using substantially less power. GaAs also provides more linear amplification, can receive weaker signals due to its low-noise characteristics, and can transmit strong clean signals at lower voltages.

The company's major markets are currently growing at 35-50% annually. End-user customers include Alcatel, Cisco Systems, Digital Equipment, Ericsson, DSC Communications, Hughes, IBM, Lucent Technologies, Motorola, Nortel, Panasonic, Philips, Qualcomm, Siemens and StorageTek.

#### History

TriQuint Semiconductor was founded in 1985 at the Beaverton, Oregon, laboratories of Tektronix by a group who had undertaken the first GaAs research and development work in 1978.

Following a strong production-oriented approach from inception, TriQuint in 1988 became the first GaAs IC manufacturer to make the transition to 100 mm (4-inch) wafers.

In 1990, TriQuint was the first company to offer GaAs ICs in plastic packages for high-volume, low-cost radio frequency (RF) applications. That year the company also shipped its first space-qualified products for nonmilitary communication satellite applications.

In 1991, three pioneering GaAs semiconductor companies — Gazelle Microcircuits, Gigabit Logic and TriQuint — merged under the TriQuint Semiconductor name. The focus of the new company was communications – cellular and other wireless phones, satellite communications, the long-distance fiber optic telecommunications market and computer networking. This focus has enabled TriQuint to average 30-35% annual growth.

TriQuint became a public company in December 1993, raising approximately \$17 million in its initial public offering. A follow-on stock offering in September 1995 raised a further \$48 million. TriQuint's stock trades under the symbol TQNT on NASDAQ.

In 1995, the overall growth rate increased to 50%, with year-end revenues of approx. \$46 million. Strong growth continued during 1996, as revenues increased to approximately \$60 million.

Also in 1996, TriQuint launched its Total Quality Management initiative, called Continuous Process Improvement (CPI). Quality Improvement Teams are formed from natural work groups or across departments to address specific quality issues, improve processes and increase the value to customers of TriQuint's services and products. Teams work on clearly defined tasks, document and analyze problems and processes, test and implement solutions, then track progress and monitor results.

In the fourth quarter of 1996, TriQuint became the first semiconductor company to install the innovative management information system designed by SAP. This leading-edge software combines real-time manufacturing, financial and sales information in a totally integrated on-line system to improve business efficiency and productivity.

In January 1997, TriQuint started moving operations to the new 27-acre corporate campus in Hillsboro. The 160,000 square foot complex includes a new wafer fabrication facility with greatly expanded production capability, with expanded sections for product testing and product and process development.

Output from the new facility is expected to meet anticipated demand though the year 2000. Additional space on the site will allow the company to further expand manufacturing operations in the future.

#### Technology and Markets

TriQuint has organized its GaAs design and manufacturing operations into two divisions, both addressing high-growth market segments: telecommunications/data communications and wireless communications.

TriQuint's Telecom/Datacom Division is one of two product divisions in the company. It serves the longdistance fiber optic telecommunications market, and also provides specialized products for general computing and electronics industries.

Telecom/Datacom is meeting the rising demand for GaAs solutions resulting from the increased bandwidth needs of new communications technologies, such as "fiber to the curb," asynchronous transfer mode (ATM), multimedia on the Internet and wireless local loop.

Computing products supplied by this Division are primarily targeted at high-speed serial data communication. Standard products include high-performance transmission and switching devices, high-speed digitalto-analog convertors, and system timing components.

The Wireless Communications Division serves the fastgrowing markets for mobile telephones and computing. Wireless is moving to higher frequencies, requiring high-performance mobile phones. TriQuint's products and technology help meet the explosive global demand for portable, battery-powered communications devices.

Regulatory agencies around the world have created whole new communications markets by opening up additional frequencies for mobile telephony usage.

Many leading manufacturers of high-frequency digital wireless communications devices are implementing TriQuint's integrated gallium arsenide MESFET technology in wide variety of communications applications. GaAs' superior linearity and noise performance provide higher signal fidelity. Other benefits include more gain at low voltages and better power efficiency for longer battery life.

The higher levels of RF integration possible with TriQuint's GaAs technology reduces overall system costs by shortening the design cycle and speeding product development.

As cellular handsets become smaller and retail prices continue to plunge, a GaAs RFIC can replace the 20-30 discretes found in earlier generations of analog cellular phones, providing better performance, lower cost, smaller size, ease of manufacturing and faster time to market.

#### Manufacturing

TriQuint has recently relocated its manufacturing operations to an all new 160,000 square feet facility located on 27 acres in Hillsboro, Oregon. Fabrication facilities occupy 38,000 square feet and include 16,000 square feet of Class 10 clean room. The new facility will be capable of quadrupling current production rates by the year 2000. Product design, support and administrative offices are also located at the new site.

TriQuint's wafer fabrication facility produces 4-inch wafers using the company's high-volume, low-cost ionimplanted metal semiconductor field effect transistor (MESFET) processes. The company also provides foundry and manufacturing services. All TriQuint's operations are ISO 9001 certified. TriQuint works with a number of strategic assembly and packaging houses in the US and overseas to meet demand for product. All wafer and final product testing is done at the TriQuint test facilities, primarily on highvolume automatic test equipment and associated handlers.

#### Partnerships

Since 1993, TriQuint has had a manufacturing partnership with Lucent Technologies, formerly AT&T Bell Labs. Under a joint development agreement, TriQuint has rights to certain intellectual property of Lucent. As part of a manufacturing services agreement, TriQuint processes GaAs wafers for Lucent.

TriQuint has ongoing manufacturing partnerships with Cirrus Logic, Cellnet and Motorola and in 1996 signed new agreements with Philips Semiconductors and Qualcomm.

Under a wafer sourcing and technology sharing agreement with Philips Semiconductors, TriQuint will manufacture a new range of GaAs monolithic microwave integrated circuit (MMIC) power amplifiers compatible with all emerging digital cellular and cordless telephone standards.

The agreement with Qualcomm is to jointly develop RFICs for CDMA PCS phones, including an RF receive component critical for compliance with the IS-95 CDMA standard and other RF ICs for wireless local loop and the Globalstar satellite system. Products and Services

TriQuint's standard products include high-performance, low-cost digital, analog and mixed-signal GaAs RFICs used in communications systems. The company also provides application-specific and custom circuit

solutions for major communication system original equipment manufacturers.

#### Telecommunications

TriQuint has a growing portfolio of products for broadband systems based on the system operation at synchronous optical network (SONET), synchronous digital hierarchy (SDH) and ATM standards. Typical functions include multiplexing and demultiplexing, clock generation and clock recovery.

Telecom and datacom applications include ATM, digital cross-connects, switch interfaces, wide area network (WAN) hubs and routers, SONET transmission and switching systems, workstations, servers, network interface cards, proprietary links and central office equipment.

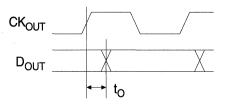

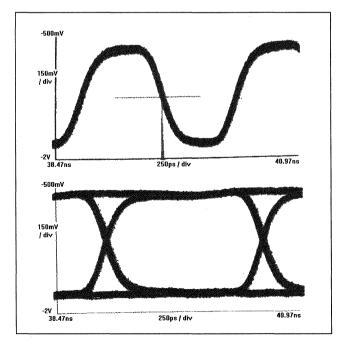

TriQuint leads the market in low-jitter telecom products. Bellcore-compliant standard products at 622 Mbps provide unparalleled waveform fidelity with high edge rates, exceptionally wide eye openings and ultra-low jitter tolerance.

High quality mixed-signal phase-lock loop (PLL) technology enables TriQuint to produce telecommunications transceiver and serializer and deserializer chips with the best performance in the industry. These devices provide physical layer interfacing between industry-standard optoelectronic modules and industry-standard overhead processor and cellmapping products.

TriQuint is the world leader in crosspoint switches above 500 MHz, providing digital switching solutions with aggregate bandwidths of over 50 Gbps and channel bandwidths of up to 2.5 Gbps with standard crosspoint products. In addition to telecom and datacom switches, TriQuint is a major supplier of switching products to the digital video market. Though operating at switching rates lower than maximum capacity, these products provide high video signal fidelity for greater design margins and higher-integrity data transfer.

The Telecom/Datacom Division's biggest market is SONET applications, where the company has established a strong market presence. TriQuint combines expertise in high-speed SONET circuit design with the proprietary process technology to deliver custom application-specific IC solutions.

#### Data Communications

In the datacom market, TriQuint focuses on high-speed serial data communications, the preferred method for high-volume data transfer. Data communication chipsets are available for the new 1 Gbps Fibre Channel standard and for proprietary serial links.

A broad range of serial communications devices incorporating exceptionally low-jitter, high-frequency PLL technology perform the serialization, CDR and deserialization functions. These support the physical interface requirements of Fibre Channel, ESCON, Gigabit Ethernet and proprietary links. In addition, TriQuint offers encoder/decoder (ENDEC) products for complete point-to-point serial communication links.

Operating at data rates from 200 Mb/s to 2.50 Gb/s, standard datacom products are compatible with copper and optical media drivers from original equipment manufacturers.

Combining high-noise immunity with low-jitter data transmission and exceptional jitter tolerance, TriQuint's

phase lock loop technology allows increased transmission length over fiber and copper transmission media at the low bit error rates required for advanced digital communication. Typical applications are disk arrays, high-speed ribbon cable replacement, data acquisition systems and other inter-system communications.

TriQuint also manufactures system timing components to synthesize and distribute precise clock signals in high-performance digital computing systems.

These products provide very low clock skew and increased timing margins for high-speed systems, using low-jitter, controlled-delay PLL technology and clock distribution buffers compatible with very highfidelity transistor-transistor logic/complementary metal oxide semiconductor (TTL/CMOS) and positive emitter coupler logic (PECL).

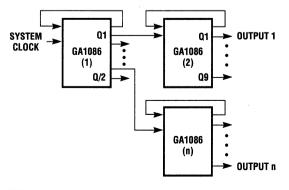

TriQuint makes standard system timing products for designs based on Pentium<sup>™</sup>, PowerPC<sup>™</sup> and Alpha AXP<sup>™</sup> processors serving applications from 20 MHz to 700 MHz. Applications include low-skew clock distribution, board-to-board clock synchronization, multiphase clocking and high-frequency clock generation.

#### **Wireless Communications**

Standard products supplied to wireless communications markets worldwide serve as the essential building blocks for multi-purpose applications in RF and microwave systems.

TriQuint applies its GaAs design and manufacturing technologies to supply industry-standard products for PCS networks, analog and digital cellular phones, satellite communication, satellite receivers for TV broadcast, wireless transceivers for data networks, hand-held navigation systems based on the global positioning satellite (GPS) standard, wireless local area networks (WLANs) and wireless modems.

TriQuint's wireless communications standard products focus on simplifying the complex requirements of RF front end design. These devices address the essentials of radio frequency applications – power amplification, frequency conversion and switching.

Signal amplification is important for both transmit and receive functions. A receiver must be able to amplify weak incoming signals without adding noise. Above 500 MHz, as frequency increases, TriQuint power amplifiers generate less noise than silicon, while the power-added efficiency of GaAs enables them to operate at lower supply voltages and at higher efficiency.

TriQuint's GaAs technologies add significant value to frequency conversion functions. Incoming RF signals are down-converted to lower frequencies for easier processing and processed signals are up-converted before transmission. TriQuint downconverter and upconverter ICs reduce inter-signal interference and provide superior signal power gain during conversion, especially at higher operating frequencies.

Switches route signals between receiver, transmitter and other processing devices. TriQuint's low-loss switches minimize the loss of signal quality and signal strength. Switching devices are frequency integrated with frequency converters, low-noise amplifiers and power amplifiers.

Among TriQuint's newest wireless standard products is a dual-mode RF power amplifier IC for mobile phones operating in most of the cellular and PCS standards; a low-voltage RFIC downconverter for cellular and PCS frequencies; a monolithic transmit/receive amplifier/ switch for spread-spectrum applications; a single-

supply single-pole double-throw (SPDT) RF switch; and dual-band products.

The company is also a world leader in foundry services to wireless markets, providing components for the global Groupe Speciale Mobile (GSM), DCS1800 and Personal Handyphone System (PHS) standards.

During 1996, TriQuint announced a total of 47 design wins in wireless handset applications involving 19 different customers. Most were for cellular and PCS applications and several were for wireless local loop systems, a new segment of the wireless communications market.

For more information on TriQUint's wireless communications products, refer to the *Wireless Communications Products Data Book*.

#### **Contract Manufacturing Services**

Electronics companies often need to integrate the functions of proprietary RF or high-speed mixed-mode systems into custom ICs to improve manufacturability, minimize component insertions, achieve higher yields and reduce costs. Since 1985, TriQuint engineers have developed the design tools and manufacturing infrastructure to serve the special needs of customers who design and develop their own GaAs circuits. Manufacturing services range from wafer fabrication to test engineering and plastic packaging. Complete postfabrication and product engineering services help customers better manage yields.

Expert staff guide customers through design to finished IC, providing full security for intellectual property while minimizing time to market. Design services include tools, training and support and referrals to design houses familiar with TriQuint's high-performance GaAs process technologies. Design tools include a digital and analog cell library of over 150 pre-designed components.

Several high-performance GaAs MESFET processes are available to implement IC designs. TriQuint's 1-micron enhancement/depletion mode MESFET processes is widely used for RF and mixed analog/digital circuits, supporting RF applications up to X-band and digital circuits of LSI complexity.

Newly available is the TQTRx, a next-generation 0.6micron enhancement/depletion mode MESFET process that offers true integration of RF transmit and receive functions.

For more information on TriQUint's foundry services, refer to the *Wireless Communications Products Data Book*.

SEMICONDUCTOR, INC.

## Section 2 — Telecommunications Products

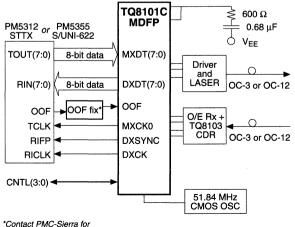

The TQ8101C is a SONET/SDH transceiver that integrates Multiplexing, Demultiplexing, SONET/SDH Framing, clock synthesis PLL (MDFP), and loopback functions in a single monolithic integrated circuit. Implementation with the TQ8101C requires only a simple external RC loop filter and standard TTL and ECL power supplies. For optimal performance, the TQ8101C MDFP is packaged in a 68-pin multilayer ceramic (MLC) surface-mount package with an integral CuW heat spreader. The TQ8101C provides an integrated solution for physical interfaces intended for use in STS-12/STM-4 (622.08-Mb/s) and STS-3/STM-1 (155.52-Mb/s) SONET/SDH systems.

The TQ8101C meets ANSI, Bellcore, and ITU requirements for a SONET/ SDH device. With a 51.84-MHz reference clock, the phase-locked loop (PLL) provides 77.76-MHz or 19.44-MHz output for the multiplexer and 77.76-MHz or 19.44-MHz and 51.84-MHz output for the demultiplexer.

Typical SONET/SDH system applications for the TQ8101C include:

- Transmission system transport cards

- Switch and cross-connect line cards

- Repeaters

- ATM physical layer interfaces

- Test equipment

- Add/drop multiplexers

#### Figure 1. Logical Application

application note.

## TQ8101C

## 622/155 Mb/s SONET/SDH MDFP

#### Features

- Byte-wide Multiplexing, Demultiplexing, Framing, and PLL (MDFP) in one device

- Choice of STS-12/STM-4 or STS-3/STM-1 transmission rates

- Configurable master or slave reference clock generation and PLL bypass for external clocking

- 77.76 MHz or 19.44 MHz output for the multiplexer; 77.76 MHz or 19.44 MHz and 51.84 MHz output for the demultiplexer

- External RC loop filter

- Pass-through mode and three loopback modes for enhanced filed diagnostics

- Frame-synchronous and bytealigned demultiplexer output, compliant with SONET and SDH

- Search, detect, and recovery of framing on out-of-frame input

- Standard TTL and differential or single-ended ECL I/O (except TXCK)

- Tristate TTL output for factory circuit-board testability

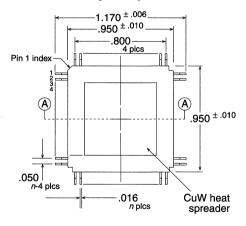

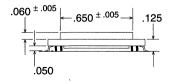

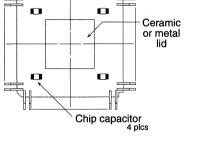

- 68-pin TriQuint MLC controlled-Z surface-mount package with integral heat spreader

- Dual-supply operation (+5V, -5.2V)

- Low power dissipation (2.3W nom.)

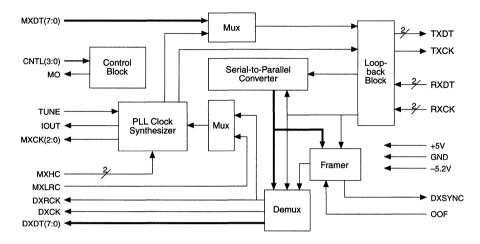

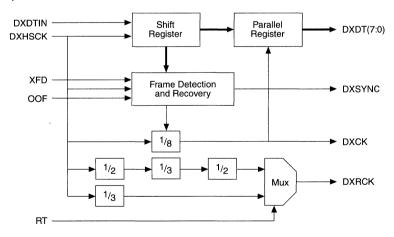

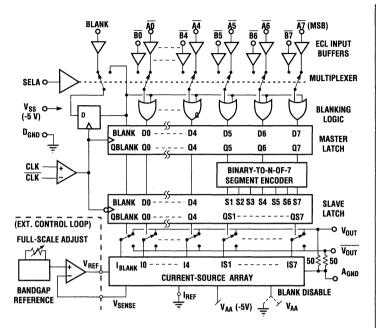

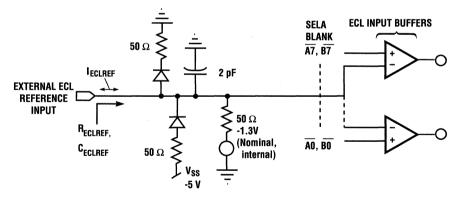

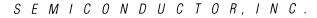

Figure 2. TQ8101C Block Diagram

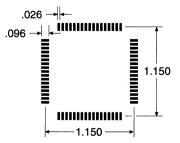

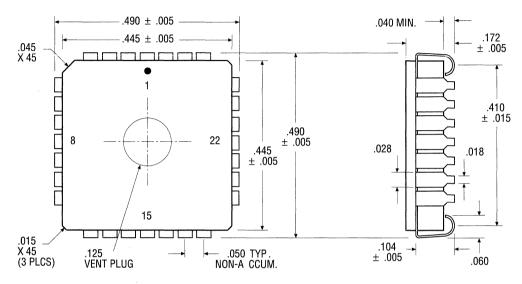

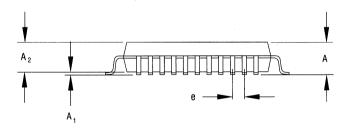

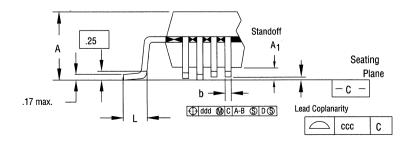

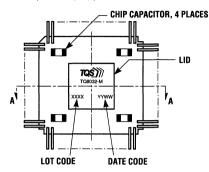

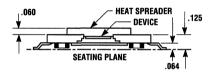

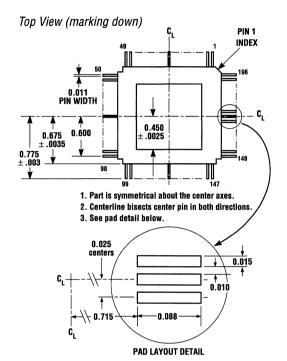

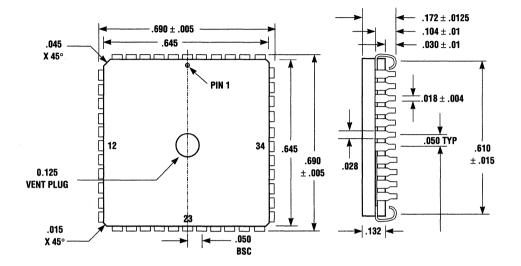

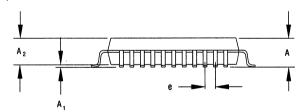

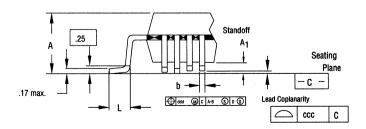

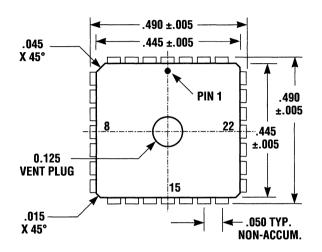

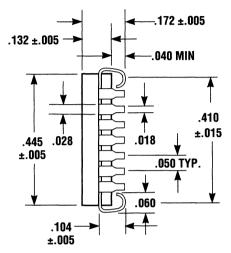

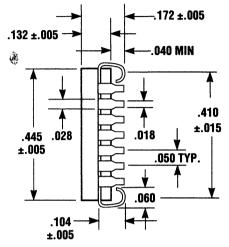

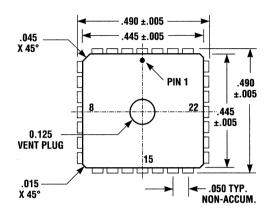

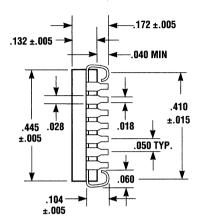

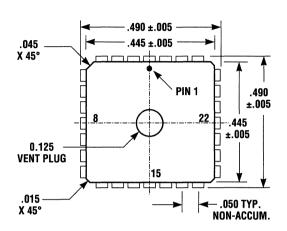

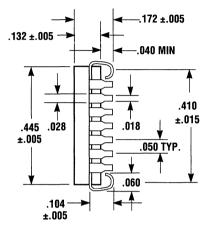

Figure 3. TQ8101C Package—68-pin MLC

TOP VIEW

SECTION (A).(A)

**BOTTOM VIEW**

### TQ8101C

### Functional Description

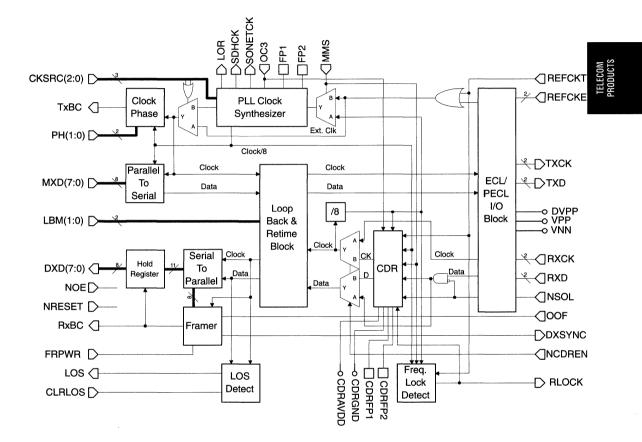

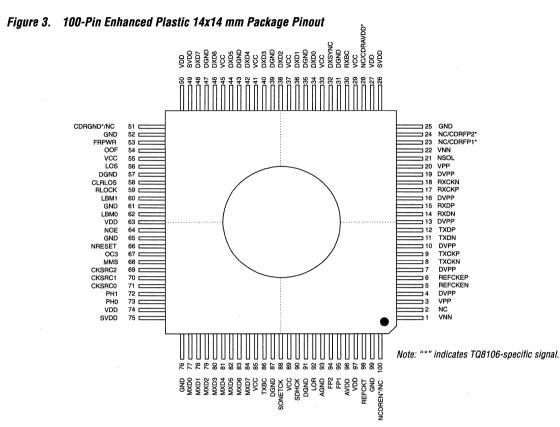

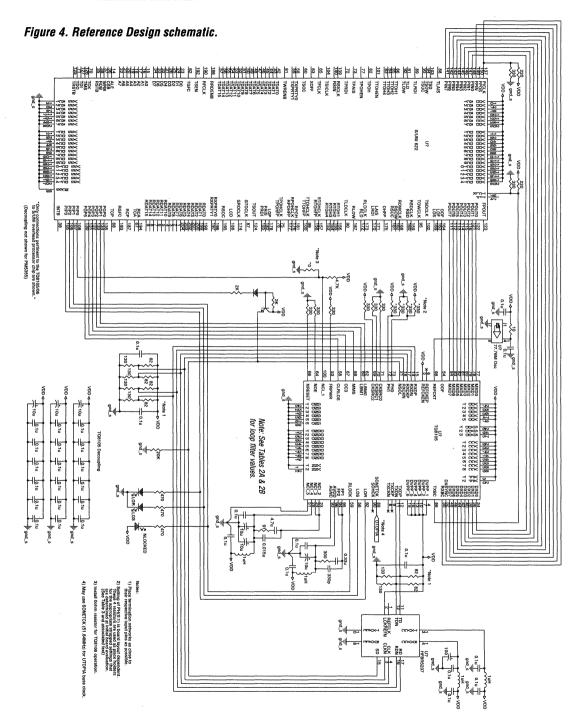

Figure 2 shows a block diagram of the TQ8101C multiplexer, demultiplexer, framer, and PLL clock synthesizer (MDFP). The primary purpose of TQ8101C is to integrate the conversion of serial and parallel SONET/SDH data with bit alignment and clock synthesis in a single device.

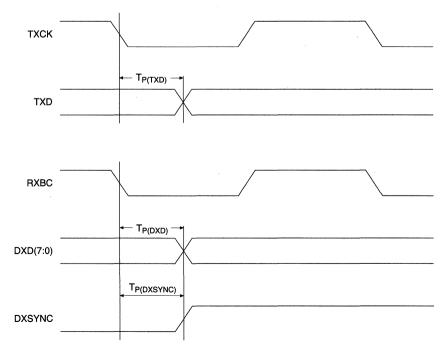

#### Multiplexing

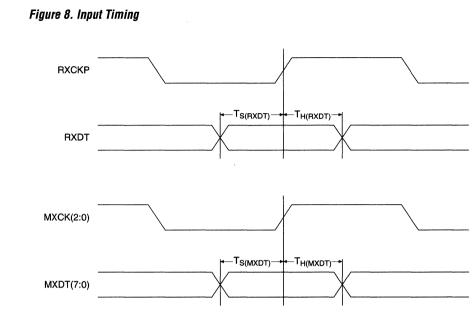

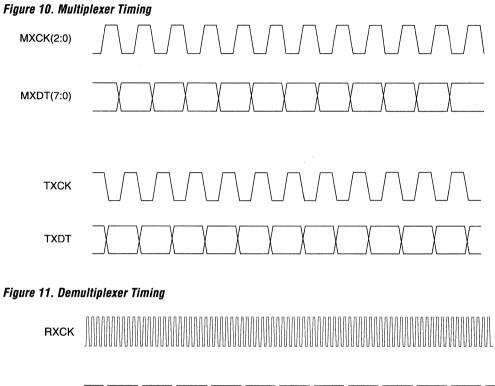

Byte-wide input data on MXDT(7:0)<sup>1</sup> is continuously strobed into the multiplexer on the rising edge of the multiplexer clock output, MXCK(2:0).<sup>2</sup> Any of these three MXCK pins may be used as a reference point for relative timing. (See Table 8 for setup, hold, and skew times. See Table 1 for clock selection options.)

Either an on-chip synthesized clock (see "PLL Clock Synthesis") or an external high-speed multiplexer

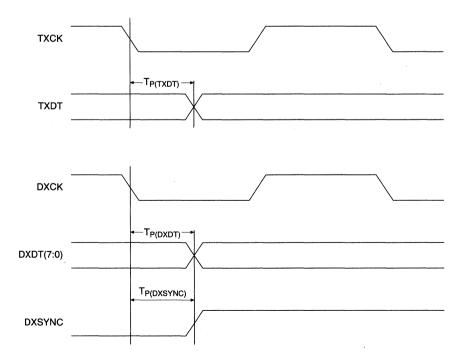

clock, MXHC, serializes the input data bytes. In the normal mode of operation, the serial data is then buffered as ECL-compatible output on TXDT. An ECL output is provided for the transmit clock, TXCK.

#### Demultiplexing

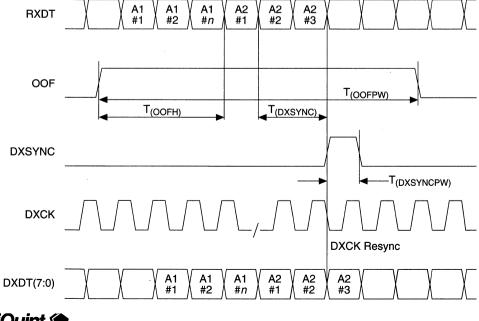

As shown in Figure 4, The demultiplexer block converts incoming serial data on DXDTIN<sup>3</sup>. Byte-wide output data is presented on DXDT(7:0)<sup>4</sup> slightly after the falling edge of the output demultiplexer clock, DXCK. (See Table 8 for setup, hold, and skew times.)

The demultiplexer block also includes clock divider circuitry, which is used by the demultiplexer to control divide-by-8 output on DXCK. The MDFP provides a divide-by-3 or divide-by-12 output, DXRCK. (See Table 1 for mode selection options.)

#### Figure 4. Demultiplexer Functional Block

*Notes:* 1. *MXDT(0) is defined as the least significant bit.*

- 2. MXCK(2:0) nominally runs at 77.76 MHz in STS-12/STM-4 mode, and at 19.44 MHz in STS-3/STM-1 mode.

- 3. Internal signal. See Figure 5, "TQ8101C Loopback Modes."

- 4. DXDT (0) is defined as the least significant bit.

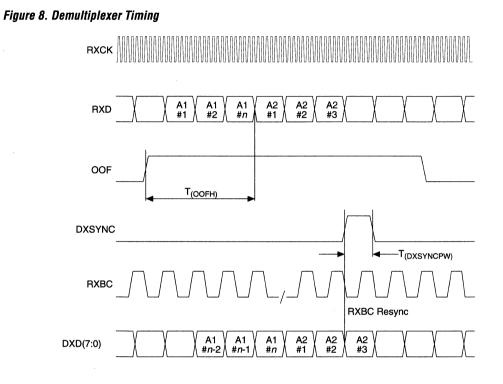

#### Framing

The demultiplexer block (see Figure 2) includes a frame-detection and recovery block. Regardless of the state of the OOF input signal, this block takes DXSYNC high for one period of DXCK whenever it detects a pattern of three "A1" bytes followed by three "A2" bytes.

Frame recovery is initiated by the rising edge of the OOF input signal. The recovery process involves a search for a bit rotation that satisfies the three-"A1"- three-"A2" byte pattern specified for SONET/SDH. Once the pattern is found, DXSYNC goes high and the bit rotation is synchronized to the correct byte boundaries. No further byte boundary adjustments are made, regardless of "A1"-"A2" indication, unless they have been preceded by an OOF rising edge.

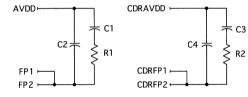

#### PLL Clock Synthesis

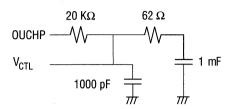

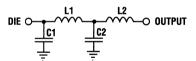

The PLL utilizes a monolithic voltage-controlled oscillator with a typical tuning constant of 50 to 100 MHz per volt on the TUNE input. This configuration provides jitter performance superior to other technologies. In a typical SONET/SDH application the TUNE input and charge pump output IOUT are connected and tied to  $V_{EE}$  through a 600-ohm resistor and 0.68-µF capacitor.

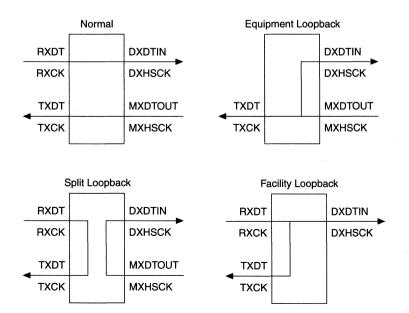

#### Loopback

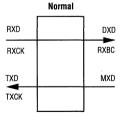

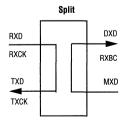

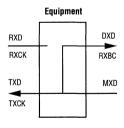

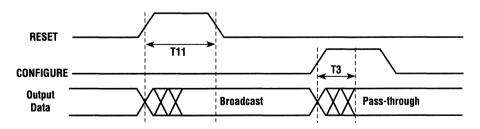

The TQ8101C features four loopback modes: normal (pass-through), equipment loopback, split loopback, and facility loopback. Loopback modes are controlled by pins CNTL(3:0). Note that the loopback mode does not affect the latched selection of clock modes and rates. Note that the RXCK input is directly connected to the TXCK output in most loopback modes (see below).

#### Figure 5. TQ8101C Loopback Modes

## TQ8101C

#### Control

The signals on pins CNTL(3:0) can be used to control the clock rate, clock mode, loopback scheme, and tristate pins. Also, the internal PLL high-speed clock may be disabled, allowing an external clock source to be used on the MXHCN and MXHCP pins.

Note that the NAND tree enable normally is used only for device testing of the  $V_{\rm IH}$  and  $V_{\rm IL}$  parameters.

At power-up or during initialization, CNTL(3) should be set to logic 1. During reset, all internal counters, dividers, and loopback states, and the phasefrequency detector, are reset or deactivated. Note that frame search is initiated only by a rising edge on OOF.

#### Table 1. Modes of Operation

| CNTL(3:0) | Modes of operation                                 |

|-----------|----------------------------------------------------|

| Qh        | Reset                                              |

| 1h        | Tristate all TTL outputs except DXRCK and MO       |

| 2h        | NAND-tree test all TTL inputs except CNTL(3:0)     |

| 3h        | DXRCK tristate                                     |

| 4h        | Frame recovery disable                             |

| 5h        | Equipment loopback                                 |

| 6h        | Facility loopback                                  |

| 7h        | Split loopback                                     |

| 8h        | Bypass, slave, internal VCO disabled, STS-3 rate   |

| 9h        | Bypass, master, internal VCO disabled, STS-3 rate  |

| Ah        | Bypass, slave, internal VCO disabled, STS-12 rate  |

| Bh        | Bypass, master, internal VCO disabled, STS-12 rate |

| Ch        | Normal, slave, internal VCO enabled, STS-3 rate    |

| Dh        | Normal, master, internal VCO enabled, STS-3 rate   |

| Eh        | Normal, slave, internal VCO enabled, STS-12 rate   |

| Fh        | Normal, master, internal VCO enabled, STS-12 rate  |

Notes: • "Bypass" indicates the use of the external high-speed clock in lieu of the internal transmit PLL.

• "Normal" indicates use of the internal transmit PLL.

• "Master" derives PLL timing from the reference 51.84-MHz oscillator input, MXLRC

• "Slave" derives PLL timing from the demultiplexer clock input, RXCK.

| Parameter            | Symbol          | Level | Minimum               | Maximum               | Unit |

|----------------------|-----------------|-------|-----------------------|-----------------------|------|

| Positive supply      | V <sub>CC</sub> |       | 0                     | 7                     | v    |

| Negative supply      | V <sub>EE</sub> |       | -7                    | 0                     | V    |

| Output voltage       | Vo              | ECL   | V <sub>EE</sub> - 0.5 | +0.5                  | V    |

| Output current       | lo              | ECL   |                       | 40                    | mA   |

| Input voltage        | VI              | ECL   | V <sub>EE</sub> - 0.5 | +0.5                  | V    |

| Input current        | lı lı           | ECL   | -1                    | 1                     | mA   |

| Output voltage       | Vo              | TTL   | -0.5                  | V <sub>CC</sub> + 0.5 | V    |

| Output current       | I <sub>0</sub>  | TTL   |                       | 20                    | mA   |

| Input voltage        | Vi              | TTL   | -0.5                  | V <sub>CC</sub> + 0.5 | V    |

| Input current        | lı              | TTL   | -1                    | 1                     | mA   |

| Junction temperature | TJ              |       | 55                    | +150                  | °C   |

| Storage temperature  | T <sub>S</sub>  |       | 65                    | +175                  | °C   |

#### Table 2. Absolute Maximum Ratings

#### Table 3. Recommended Operating Conditions

| Parameter                     | Symbol          | Minimum | Nominal | Maximum | Unit |

|-------------------------------|-----------------|---------|---------|---------|------|

| Positive supply               | V <sub>CC</sub> | 4.75    | 5       | 5.25    | V    |

| Negative supply               | V <sub>EE</sub> | -5.5    | -5.2    | -4.75   | ٧    |

| Operating ambient temperature | To              | 0       |         | 70      | °C   |

#### Table 4. Power Consumption

| Function                          |                 | +5 V supply | -5.2    | V supply | Unit   |

|-----------------------------------|-----------------|-------------|---------|----------|--------|

| Nominal                           |                 | 40          |         | 320      | mA     |

| Max                               |                 | 55          |         | 420      | mA     |

| Parameter                         | Symbol          | Level       | Minimum | Maximum  | Unit   |

| Thermal resistance, junction-case | θ <sub>JC</sub> |             |         | 4        | °C / W |

#### 33 DXSYNC DXDT0 DXDT2 DXDT3 DXDT1 DXDT4 DXDT6 DXDT7 DXDT5 DXCK GND GND GND GND GND GND 200 31 ស្ត 22 21 20 8 ß 54 6 8 8 53 28 27 26 ស្ល 35 V<sub>EE</sub> ] 17 GND 16 DXRCK 36 GND 37 MXDT7 [ ] 15 OOF ] 14 GND 38 MXDT6 [ 39 GND ] 13 MO 40 MXDT5 [ 12 TXDTN 41 MXDT4 [ ] 11 GND TQ8101C 42 GND 10 TXDTP **MDFP** 43 MXDT3 [ Э 9 ТХСК 44 MXDT2 3 8 GND 45 GND ] 7 RXDTP 46 MXDT1 [ 🗆 6 RXDTN 47 MXDT0 [ 5 GND 48 GND ☐ 4 RXCKN 49 MXCK2 [ 3 RXCKP 50 MXCK1 [ 2 GND 51 GND ] 1 V<sub>EE</sub> MXHCN MXHCP MXCK0 MXLRC CNTL3 CNTL2 CNTLO TUNE **CNTL1** GND GND 1001 GND GND GND GND × د< 23 25 24 55 56 57 ŝ 23 8 8 8 5 <u>8</u>2 61 98 67 88

#### Figure 6. Pinout Diagram

(heat spreader side-top view)

#### Table 5. Signal Descriptions

| Pin | Signal          | Туре    | Description                                                                |

|-----|-----------------|---------|----------------------------------------------------------------------------|

| 1   | V <sub>EE</sub> |         | Negative power supply input (-5.2V)                                        |

| 2   | GND             |         | Ground                                                                     |

| 3   | RXCKP           | In      | Receive bit-serial clock; differential ECL, positive                       |

| 4   | RXCKN           | In      | Receive bit-serial clock; differential ECL, negative                       |

| 5   | GND             |         | Ground                                                                     |

| 6   | RXDTN           | In      | Receive bit-serial data (MSB first); differential ECL, negative            |

| 7   | RXDTP           | In      | Receive bit-serial data (MSB first); differential ECL, positive            |

| 8   | GND             |         | Ground                                                                     |

| 9   | ТХСК            | Out     | Transmit bit-serial clock; single-ended ECL level                          |

| 10  | TXDTP           | Out     | Transmit bit-serial data (MSB first); differential ECL, positive           |

| 11  | GND             |         | Ground                                                                     |

| 12  | TXDTN           | Out     | Transmit bit-serial data (MSB first); differential ECL, negative           |

| 13  | MO              | Out     | NAND tree monitor output; TTL level                                        |

| 14  | GND             |         | Ground                                                                     |

| 15  | 00F             | In      | Out of frame; TTL level; rising-edge initiated frame search                |

| 16  | DXRCK           | Tri Out | Demultiplexer reference clock; TTL level; 50-pF backplane driving capacity |

| 17  | GND             |         | Ground                                                                     |

| 18  | V <sub>CC</sub> |         | Positive power supply input (+5.0V)                                        |

| 19  | GND             |         | Ground                                                                     |

| 20  | DXDT7           | Tri Out | Demultiplexer byte-serial data (bit 7); TTL level                          |

| 21  | DXDT6           | Tri Out | Demultiplexer byte-serial data (bit 6); TTL level                          |

| 22  | GND             |         | Ground                                                                     |

| 23  | DXDT5           | Tri Out | Demultiplexer byte-serial data (bit 5); TTL level                          |

| 24  | DXDT4           | Tri Out | Demultiplexer byte-serial data (bit 4); TTL level                          |

| 25  | GND             |         | Ground                                                                     |

| 26  | DXDT3           | Tri Out | Demultiplexer byte-serial data (bit 3); TTL level                          |

| 27  | DXDT2           | Tri Out | Demultiplexer byte-serial data (bit 2); TTL level                          |

| 28  | GND             |         | Ground                                                                     |

| 29  | DXDT1           | Tri Out | Demultiplexer byte-serial data (bit 1); TTL level                          |

| 30  | DXDT0           | Tri Out | Demultiplexer byte-serial date (bit 0); TTL level                          |

| 31  | GND             |         | Ground                                                                     |

| 32  | DXCK            | Tri Out | Demultiplexer byte-serial clock; TTL level                                 |

| 33  | DXSYNC          | Tri Out | Demultiplexer synchronization; TTL level                                   |

| 34  | GND             |         | Ground                                                                     |

(Continues on next page)

#### Table 5. Signal Descriptions (continued)

| Pin | Signal          | Туре     | Description                                                                       |

|-----|-----------------|----------|-----------------------------------------------------------------------------------|

| 35  | V <sub>EE</sub> |          | Negative power supply input (-5.2V)                                               |

| 36  | GND             |          | Ground                                                                            |

| 37  | MXDT7           | In       | Multiplexer byte-serial data (bit 7); TTL level                                   |

| 38  | MXDT6           | In       | Multiplexer byte-serial data (bit 6); TTL level                                   |

| 39  | GND             |          | Ground                                                                            |

| 40  | MXDT5           | In       | Multiplexer byte-serial data (bit 5); TTL level                                   |

| 41  | MXDT4           | In       | Multiplexer byte-serial data (bit 4); TTL level                                   |

| 42  | GND             |          | Ground                                                                            |

| 43  | MXDT3           | In       | Multiplexer byte-serial data (bit 3); TTL level                                   |

| 44  | MXDT2           | In       | Multiplexer byte-serial data (bit 2); TTL level                                   |

| 45  | GND             |          | Ground                                                                            |

| 46  | MXDT1           | In       | Multiplexer byte-serial data (bit 1); TTL level                                   |

| 47  | MXDT0           | In       | Multiplexer byte-serial data (bit 0); TTL level                                   |

| 48  | GND             |          | Ground                                                                            |

| 49  | MXCK2           | Tri Out  | Multiplexer byte-serial clock (bit 2); TTL level. See Table 1 for output rate.    |

| 50  | MXCK1           | Tri Out  | Multiplexer byte-serial clock (bit 1); TTL level. See Table 1 for output rate.    |

| 51  | GND             |          | Ground                                                                            |

| 52  | V <sub>CC</sub> |          | Positive power supply input (+5.0V)                                               |

| 53  | GND             |          | Ground                                                                            |

| 54  | MXCK0           | Tri Out  | Multiplexer byte-serial clock (bit 0); TTL level. See Table 1 for output rate.    |

| 55  | MXLRC           | In       | Multiplexer low-speed reference clock (51.84 MHz); TTL level                      |

| 56  | GND             |          | Ground                                                                            |

| 57  | MXHCN           | In       | Multiplexer high-speed reference clock (max. 640 MHz); differential ECL, negative |

| 58  | MXHCP           | In       | Multiplexer high-speed reference clock (max. 640 MHz); differential ECL, positive |

| 59  | GND             |          | Ground                                                                            |

| 60  | CNTL3           | In       | Control (bit 3); TTL level                                                        |

| 61  | IOUT            | Out      | Tristate charge pump output (analog); connect to pin 63                           |

| 62  | GND             |          | Ground                                                                            |

| 63  | TUNE            | In       | VCO tune (analog); connect to external loop filter and pin 61                     |

| 64  | CNTL2           | In       | Control (bit 2); TTL level                                                        |

| 65  | GND             |          | Ground                                                                            |

| 66  | CNTL1           | In       | Control (bit 1); TTL level                                                        |

| 67  | CNTLO           | In       | Control (bit 0); TTL level                                                        |

| 68  | GND             |          | Ground                                                                            |

|     |                 | <u> </u> |                                                                                   |

TELECOM PRODUCTS

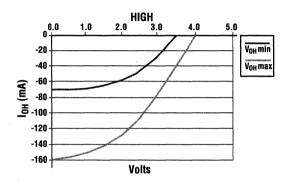

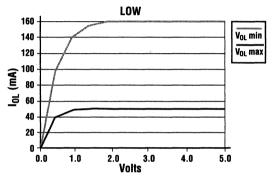

#### Table 6. DC Characteristics—ECL I/O (1)

| Parameter              | Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Symbol            | Minimum               | Nominal              | Maximum | Unit |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------|----------------------|---------|------|

| Internal ECL reference | (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>REF</sub>  |                       | 0.26 V <sub>EE</sub> |         | mV   |

| Common mode voltage    | (3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>COM</sub>  | -1500                 |                      | -1100   | mV   |

| Differential voltage   | (3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>DIFF</sub> | 200                   |                      | 1200    | mV   |

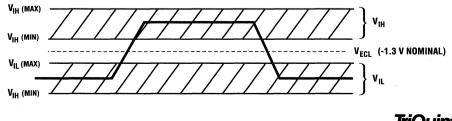

| Input HIGH voltage     | (4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>IH</sub>   | -1100                 |                      | -400    | mV   |

| Input LOW voltage      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | VIL               | V <sub>EE</sub>       |                      | -1500   | mV   |

| Output HIGH voltage    | (5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>OH</sub>   | -1000                 | 0                    | -500    | mV   |

| Output LOW voltage     | (5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>OL</sub>   | V <sub>TT</sub> – 100 |                      | -1600   | mV   |

| Input HIGH current     | VIH (MAX)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | IIH               |                       |                      | 30      | mA   |

| Input LOW current      | VIL (MIN)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | IIL               |                       |                      | -30     | mA   |

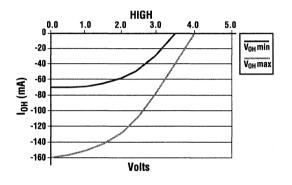

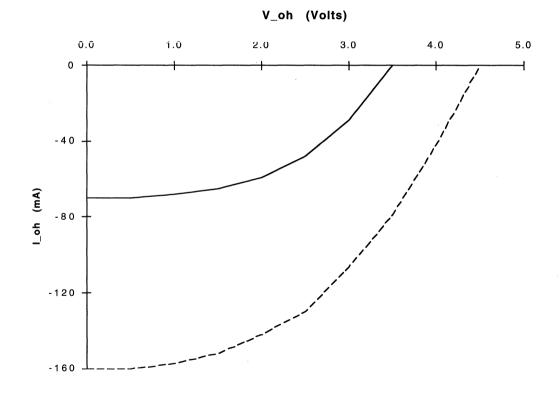

| Output HIGH current    | (6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | I <sub>OH</sub>   | 20                    | 23                   | 30      | mA   |

| Output LOW current     | (6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | IOL               | -2                    | 5                    | 8       | mA   |

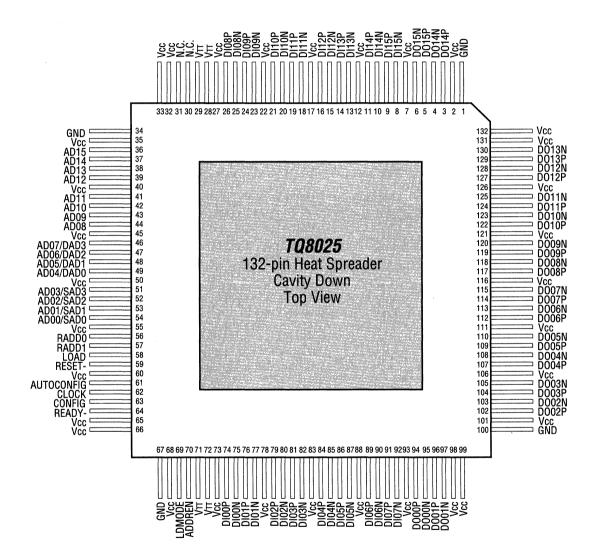

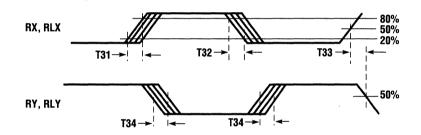

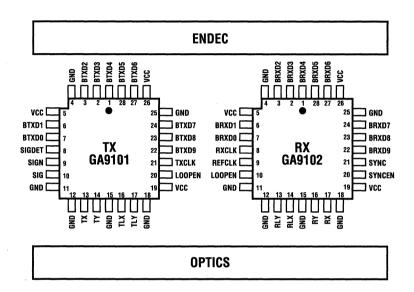

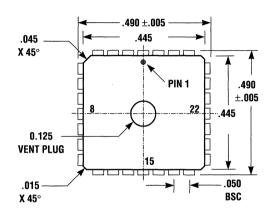

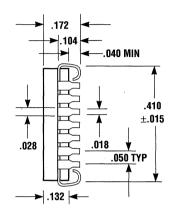

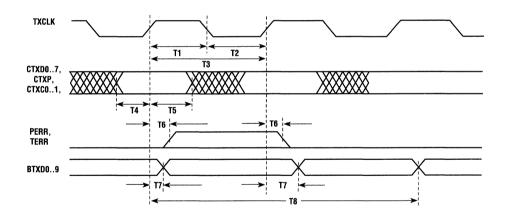

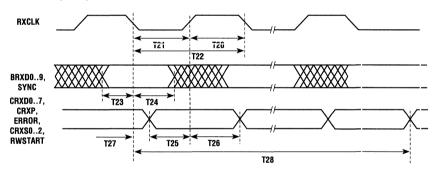

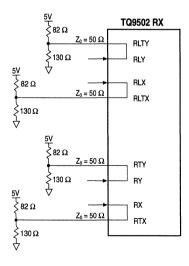

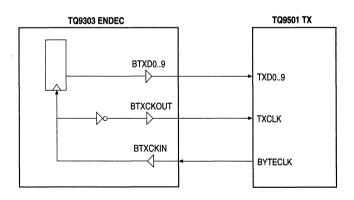

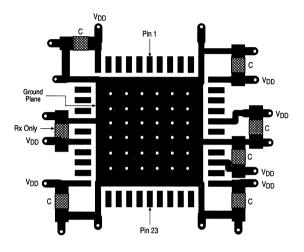

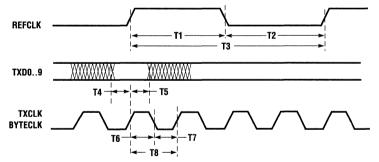

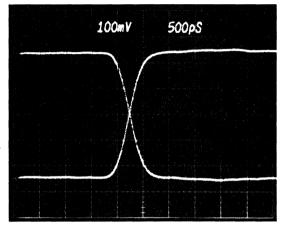

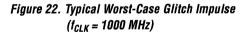

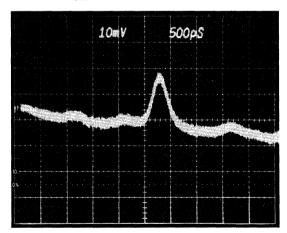

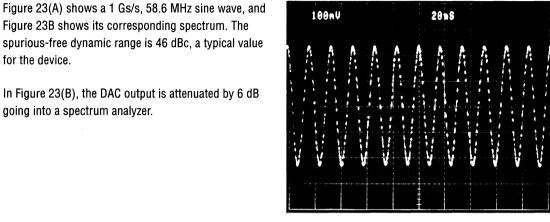

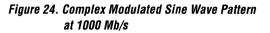

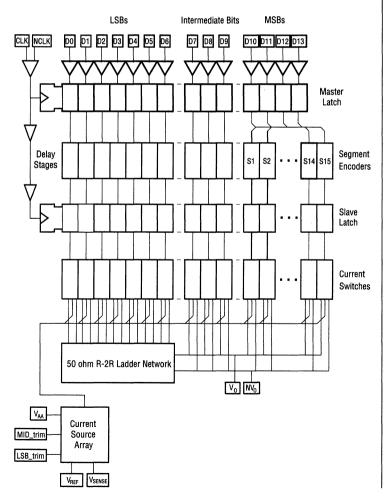

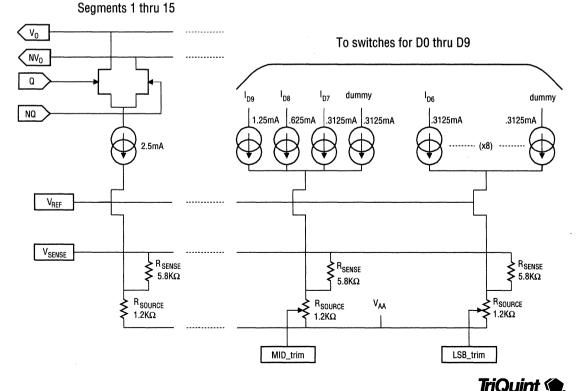

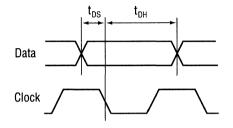

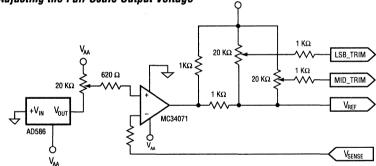

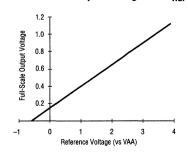

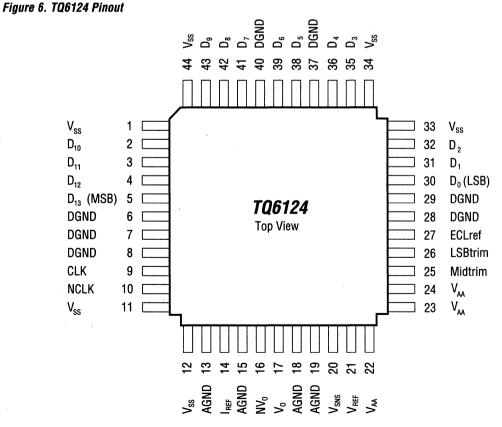

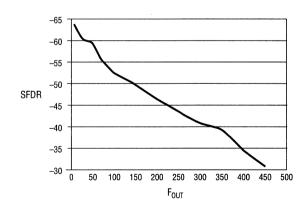

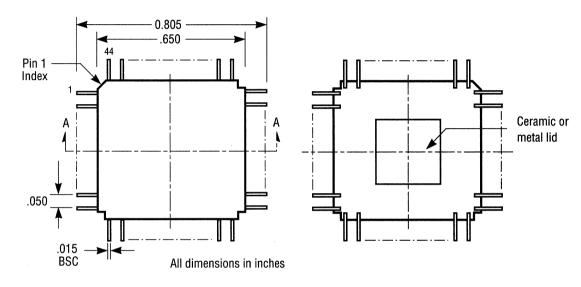

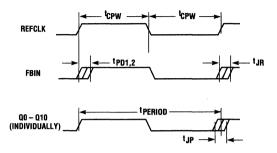

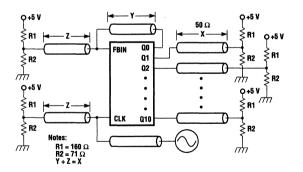

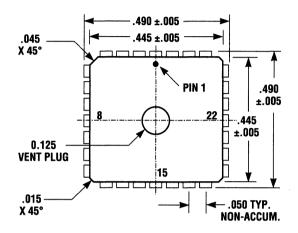

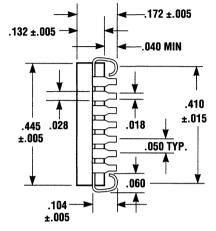

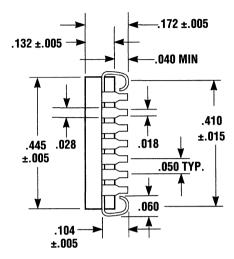

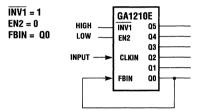

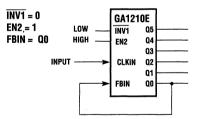

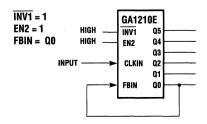

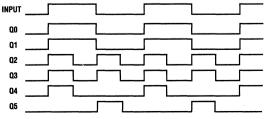

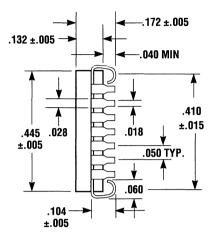

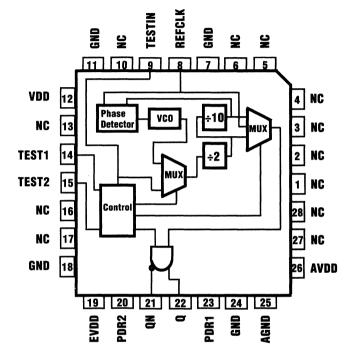

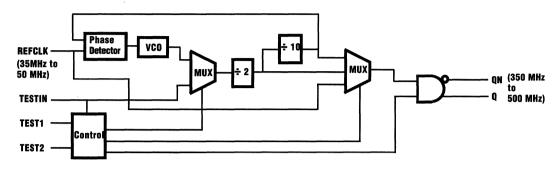

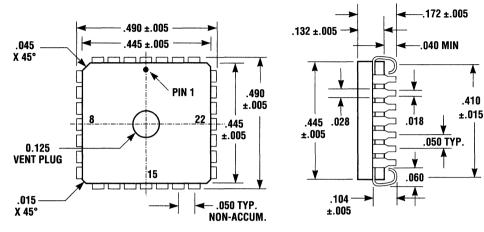

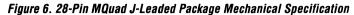

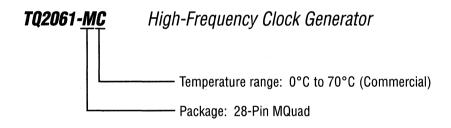

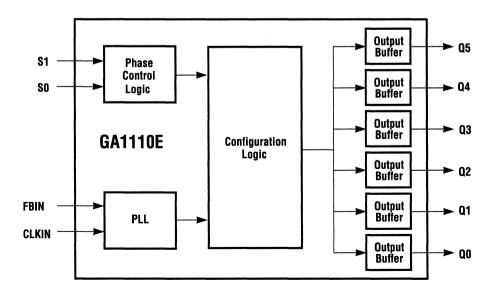

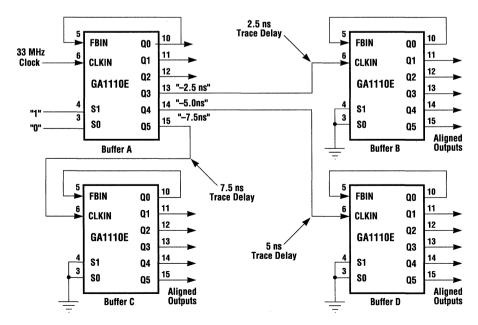

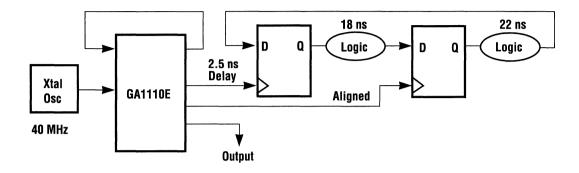

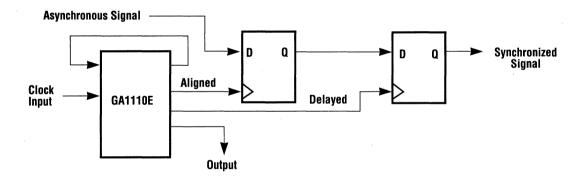

| Input capacitance      | 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - 101 - | CIN               |                       | 3                    |         | pF   |