# **Table of Contents**

| Product Specifications                                                              | Product Number              | Page |

|-------------------------------------------------------------------------------------|-----------------------------|------|

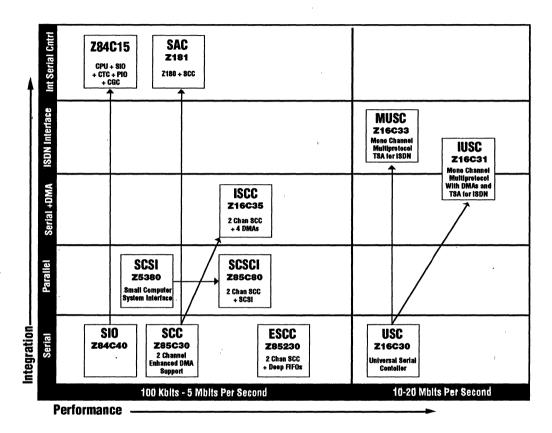

| Product Migration Chart                                                             |                             |      |

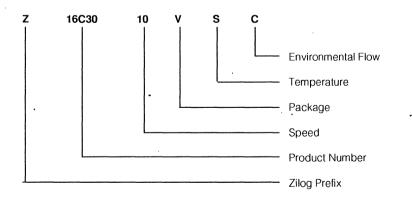

| Product Migration Chart<br>Z16C30 CMOS USC™Universal Serial Controller              | Z16C3010VSC/VEC/GEE         | 3    |

| Z16C31 IUSC™Integrated Universal Serial Controller                                  |                             |      |

| Z16C33 CMOS MUSC™Mono-Universal Serial Controller                                   |                             |      |

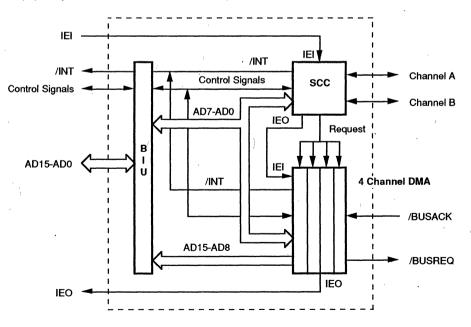

| Z16C35 CMOS ISCC™ Integrated Serial Communications Controller                       | Z16C3510VSC/16VSC           |      |

| Z16C50 DDPLL™Dual Digital Phase Locked Loop Microcontroller                         | Z16C5010PSC/20PSC           |      |

| Z5380 CMOS SCSI Small Computer System Interface                                     |                             |      |

| Z85230 CMOS ESCC™Enhanced Serial Communication Controller                           | Z8523010PSC/VSC, 20PSC/VSC  |      |

| Z80C30/Z85C30 CMOS Z-BUS <sup>®</sup> SCC™Serial Communication Controller           | Z80C3008PSC/VSC, 10PSC/VSC  |      |

|                                                                                     | Z85C3008PSC/PEC/VSC/VEC/CEE |      |

|                                                                                     | Z85C3010PSC/PEC/VSC/VEC/CEE |      |

|                                                                                     | Z85C3016PSC/VSC             |      |

| Z8030/Z8530 Z-BUS <sup>®</sup> SCC™Serial Communication Controller                  | Z803006PSC/DSE/VSC          |      |

| · · · ·                                                                             | Z803008PSC/DSE/VSC          |      |

|                                                                                     | Z0853004PSC                 |      |

|                                                                                     | Z0853006PSC/DEC/DSE/VSC     |      |

| ·                                                                                   | Z0853008PSC/DSE/DEA/VSC     |      |

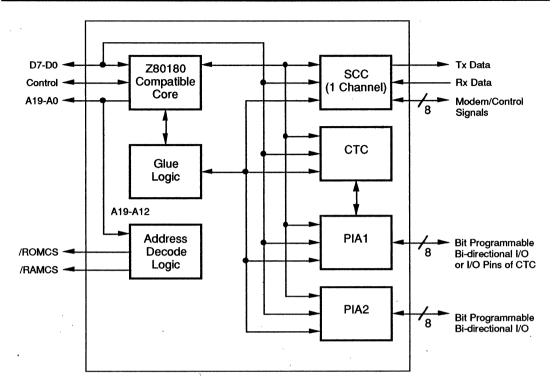

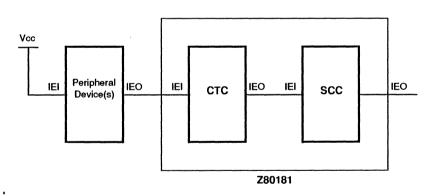

| Z80181 CMOS SAC™Smart Access Controller                                             |                             |      |

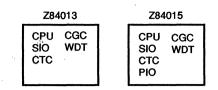

| Z84013/015 Z84C13/C15 IPC™Intelligent Peripheral Controller                         | Z8401306VEC/10VEC           |      |

|                                                                                     | Z84C1306VEC/10VEC           |      |

|                                                                                     | Z8401506FEC/10FEC           |      |

| 1                                                                                   | Z84C1506/10FEC              |      |

| Z8440/Z84C40 SIO (See Ordering Information for available speeds, "XX" replacements) | Z08440XXPSC/DSE             | 505  |

|                                                                                     | Z08441XXPSC/DSE             |      |

|                                                                                     | Z08442XXPSC/DSE             |      |

|                                                                                     | Z08444XXVSC                 |      |

|                                                                                     | Z844C40XXPEC/DEE            |      |

|                                                                                     | Z84C41XXPEC/DEE             |      |

|                                                                                     | Z84C42XXPEC/DEE             |      |

| í.                                                                                  | Z84C43XXFEC                 |      |

|                                                                                     | Z84C44XXVEC                 |      |

| Z85C80 SCSCI™Serial Communication and Small Computer Interface                      | Z85C8010VSC                 | 529  |

# Application Notes

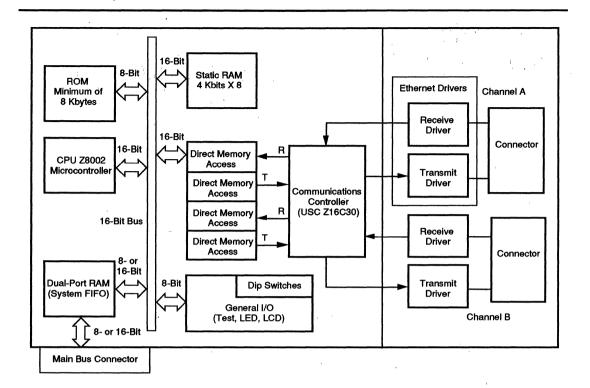

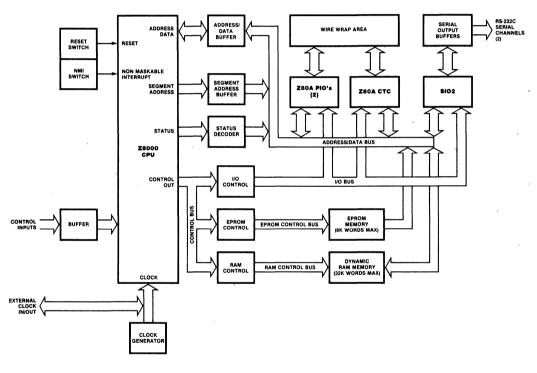

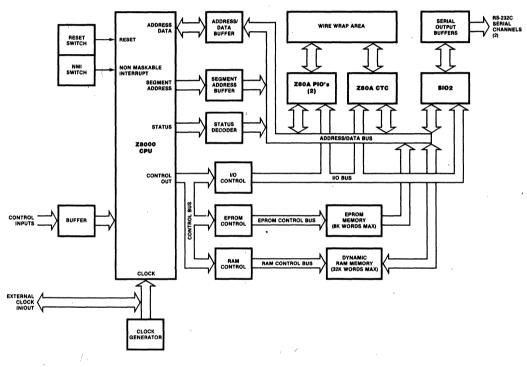

| Design a Serial Board to Handle Multiple Protocols                  | 591 |

|---------------------------------------------------------------------|-----|

| Using the Z16C30 USC Universal Serial Controller with MIL-STD-1553B | 603 |

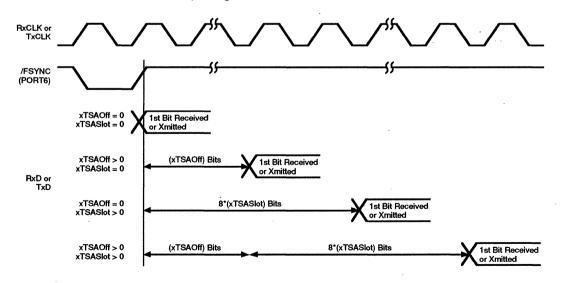

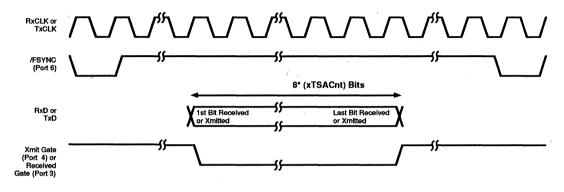

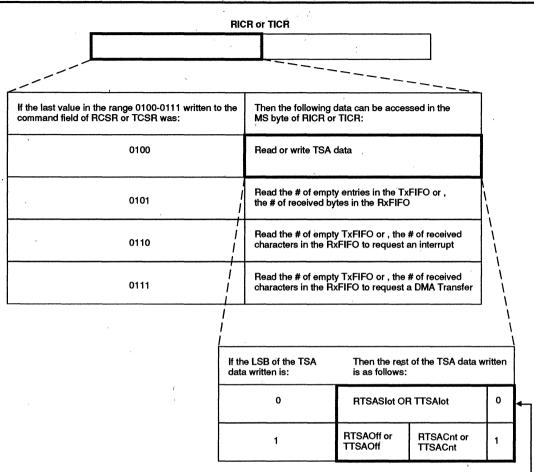

| Datacommunications IUSC/MUSC Time Slot Assigner                     | 617 |

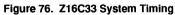

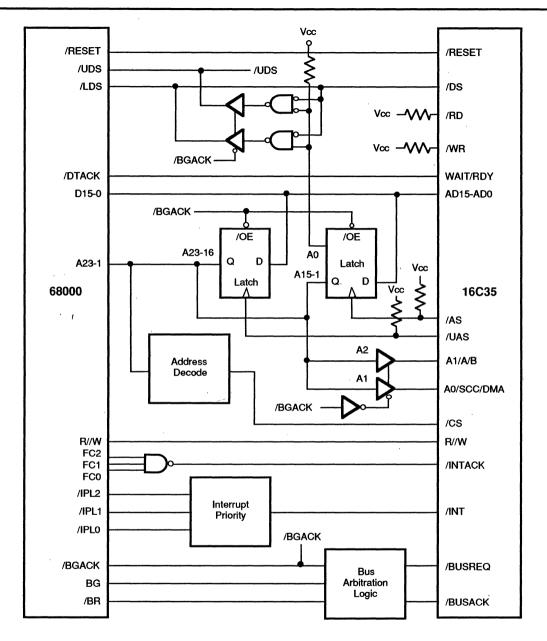

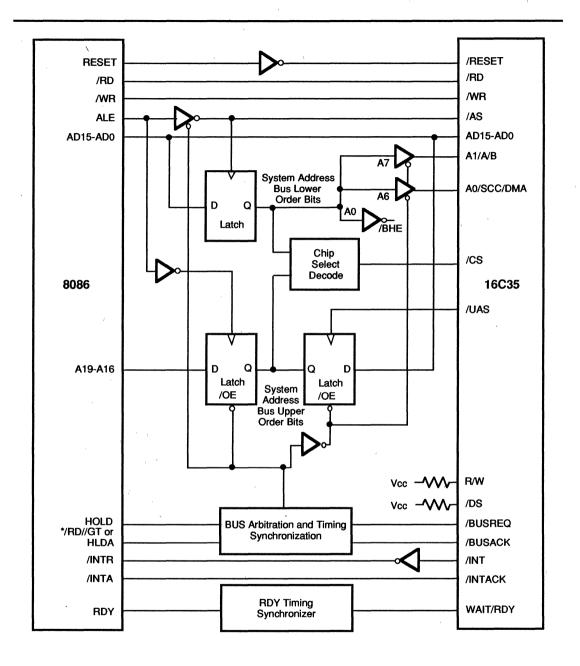

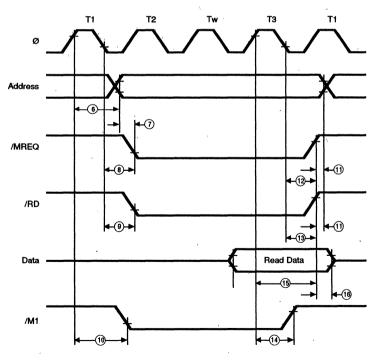

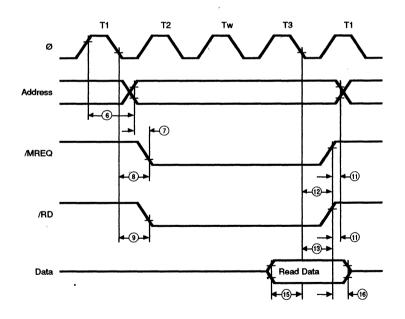

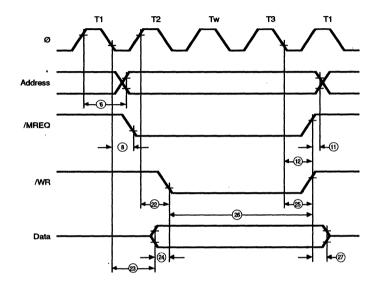

| ISCC Interface to the 68000® and 8086®                              | 621 |

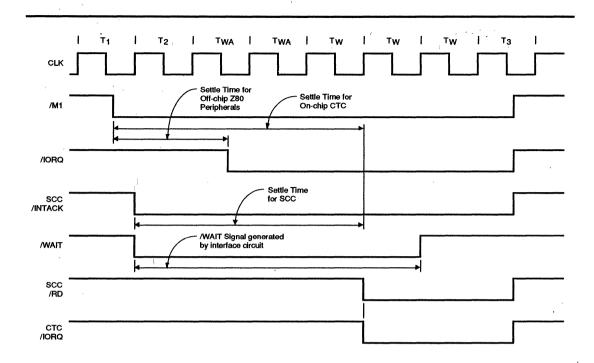

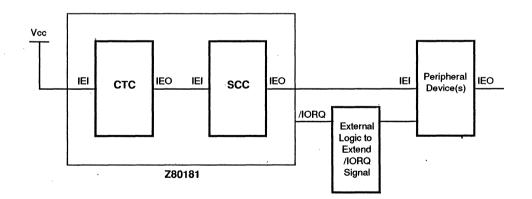

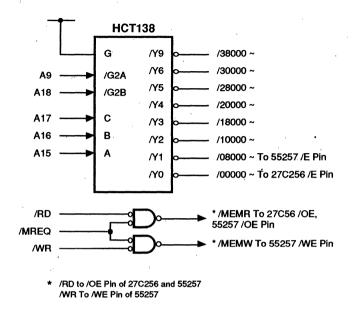

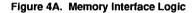

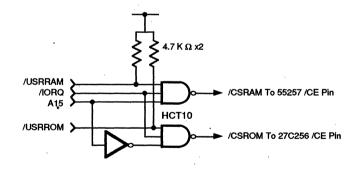

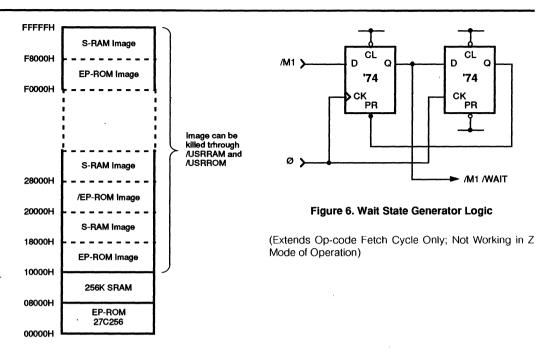

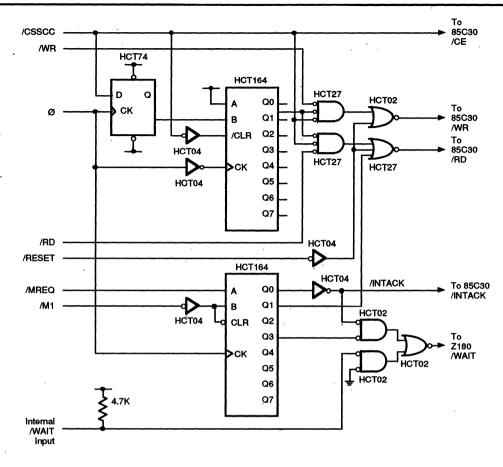

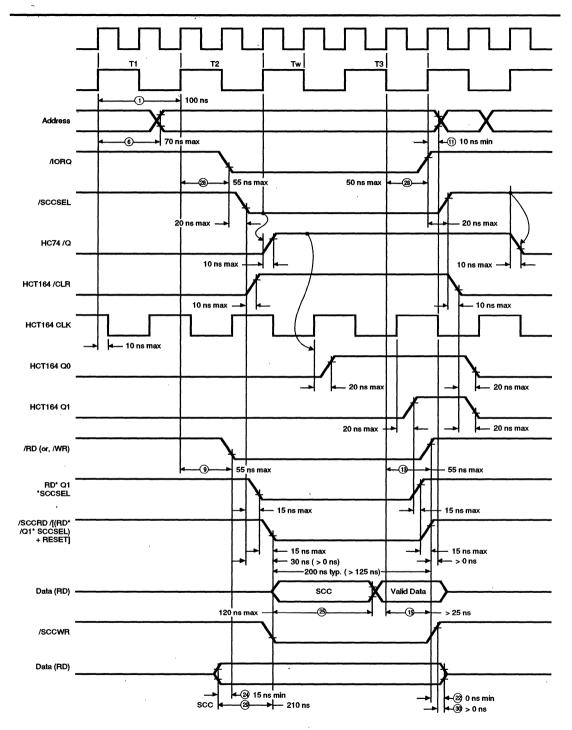

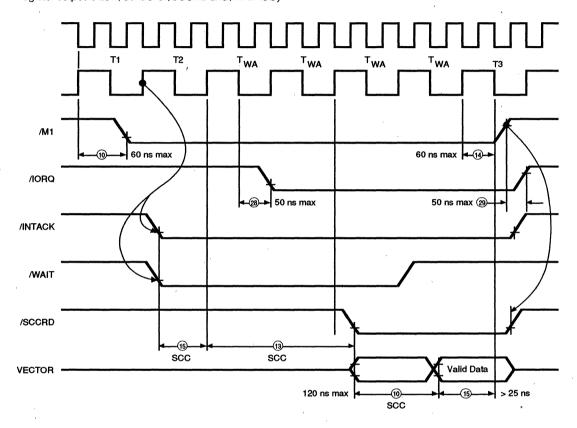

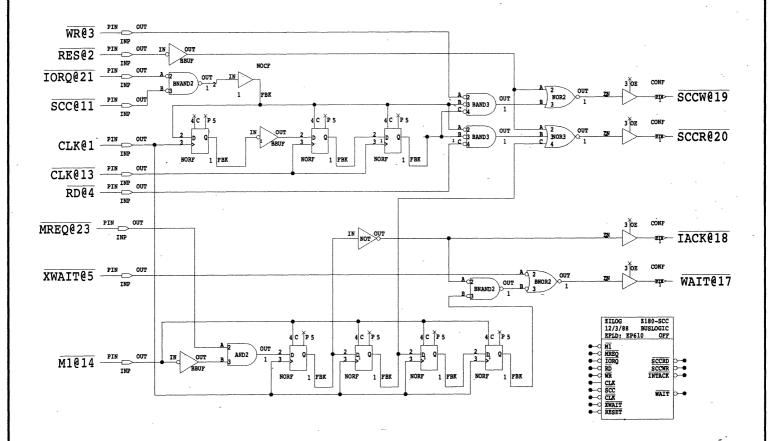

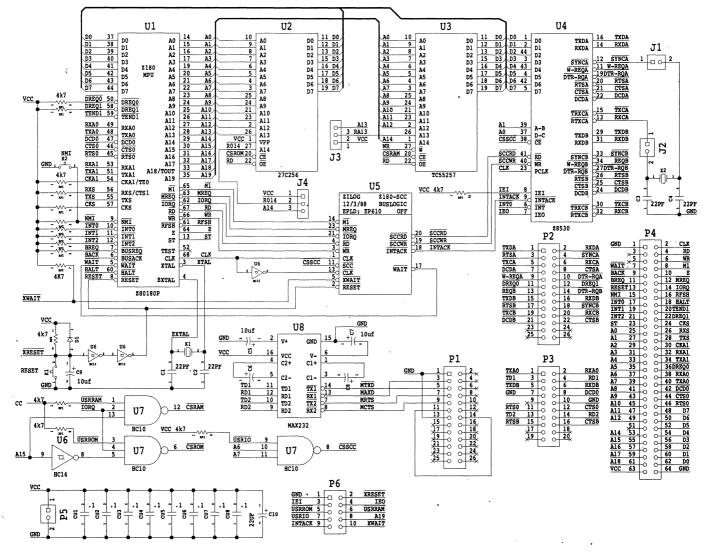

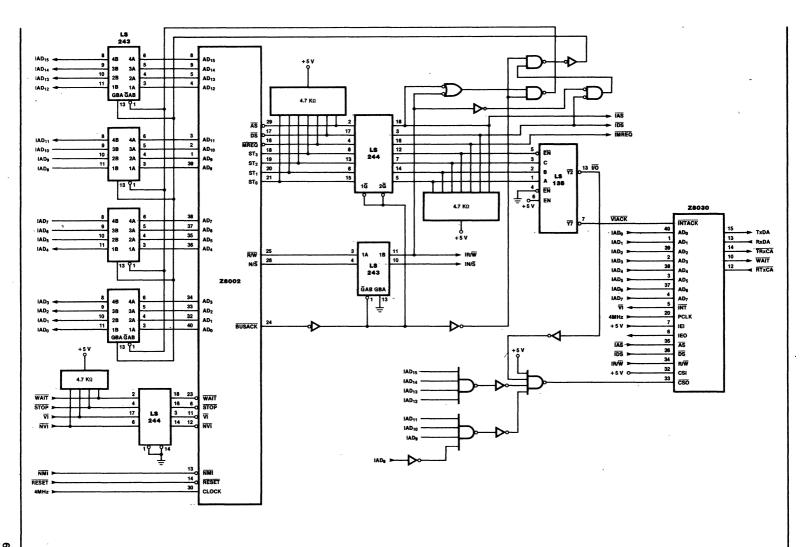

| The Z180 SCC Interfaced with the SCC at 10 MHz                      | 631 |

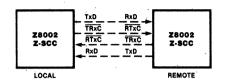

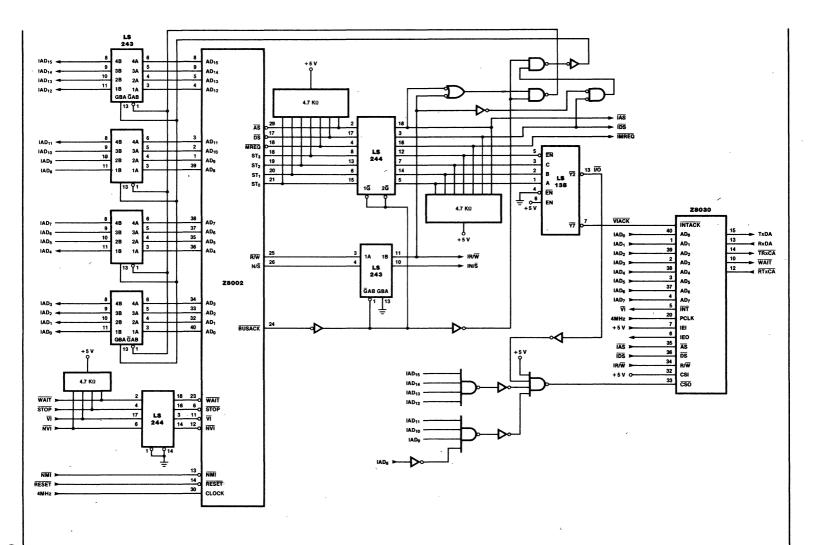

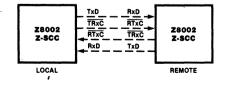

| Using SCC with Z8000 <sup>®</sup> in SDLC Protocol                  | 665 |

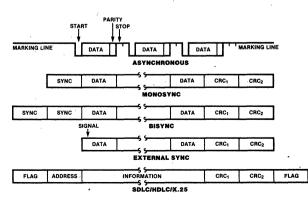

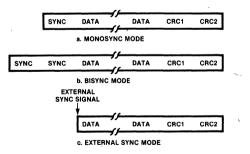

| SCC In Binary Synchronous Communications                            | 677 |

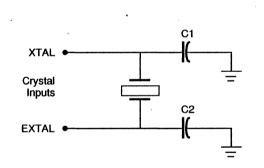

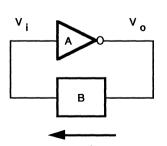

| On-Chip Oscillator Design                                           |     |

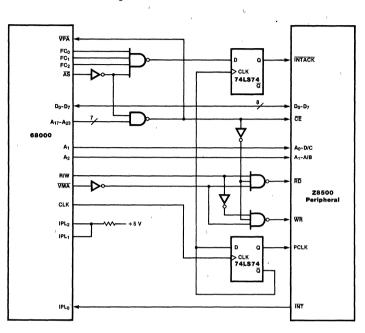

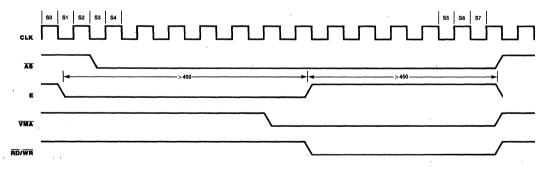

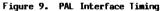

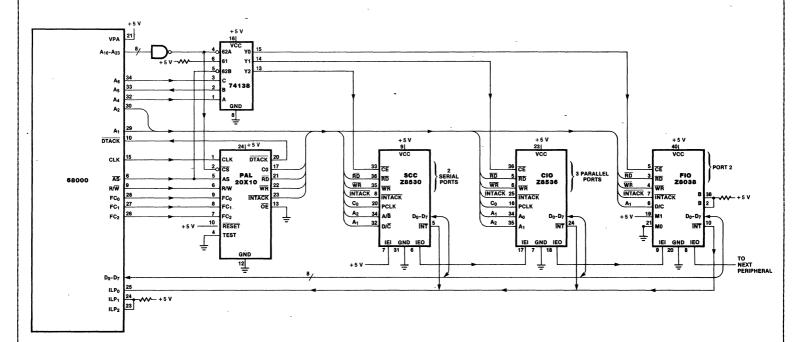

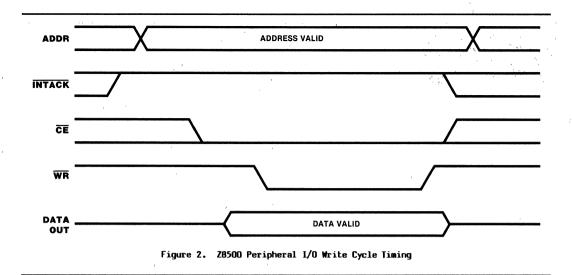

| Interfacing the Z8500 Peripherals to the 68000                      | 697 |

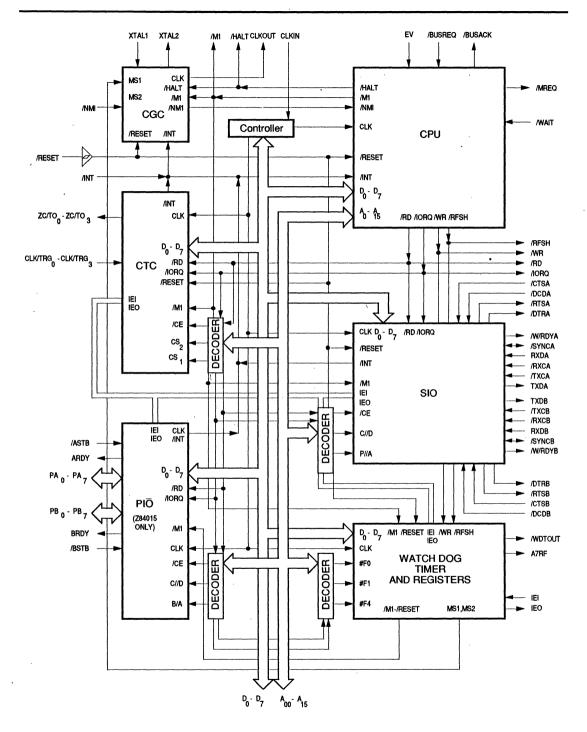

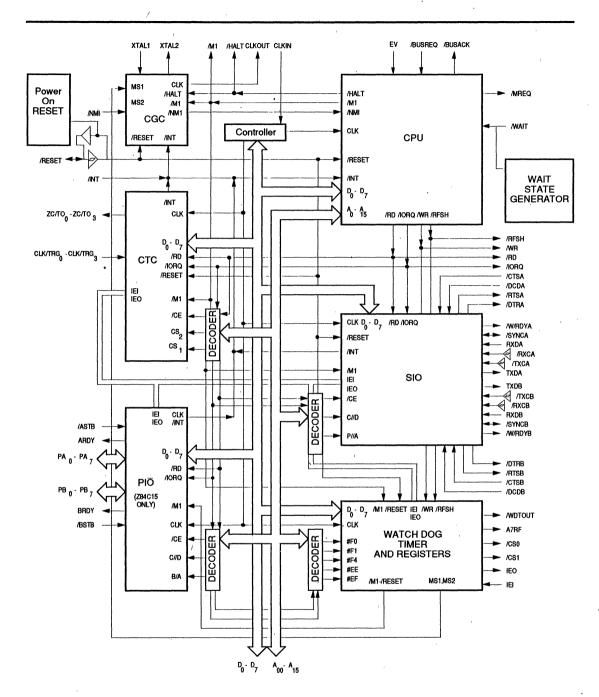

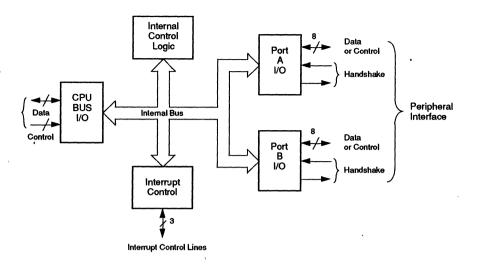

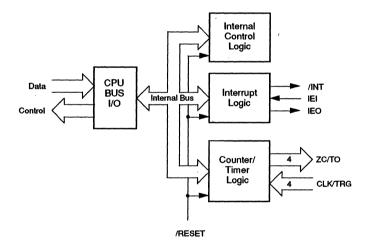

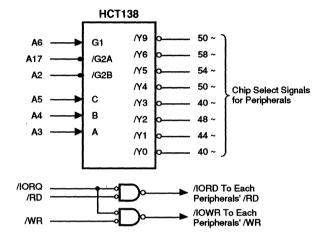

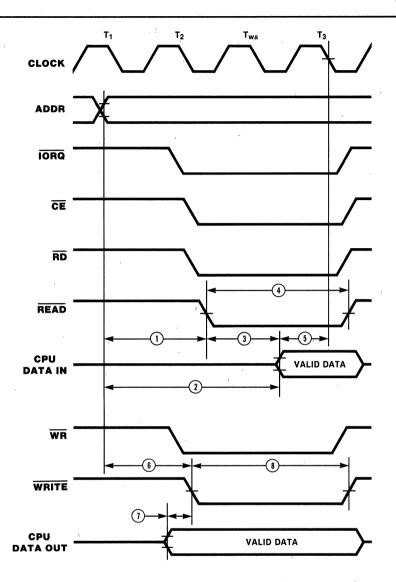

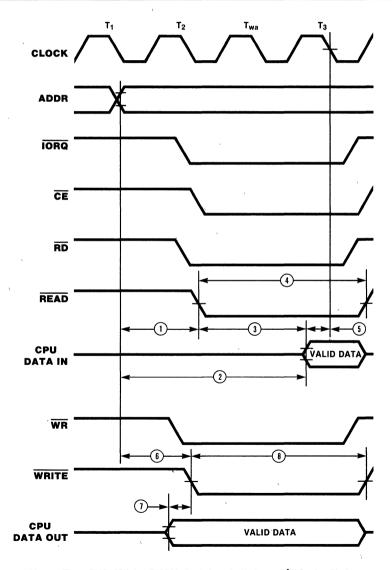

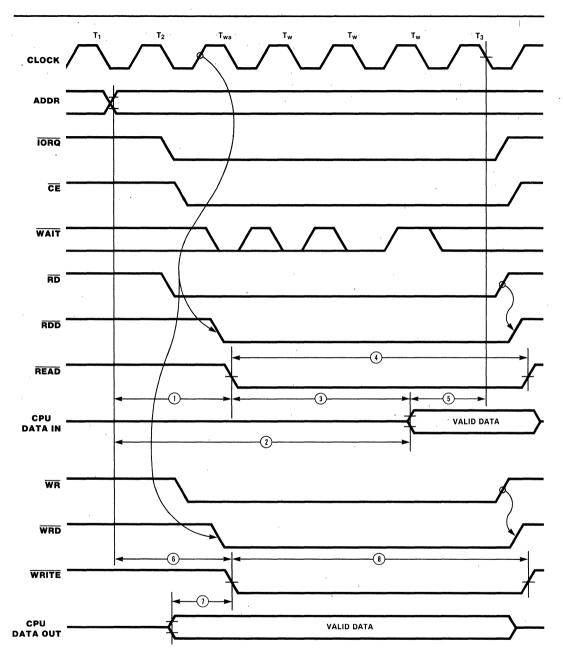

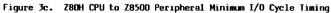

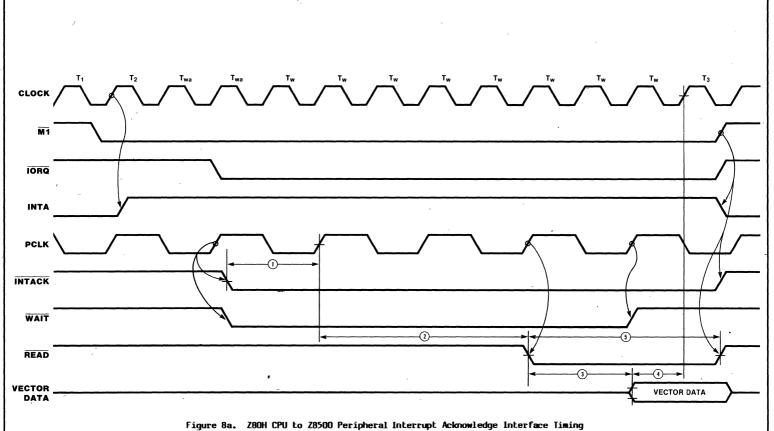

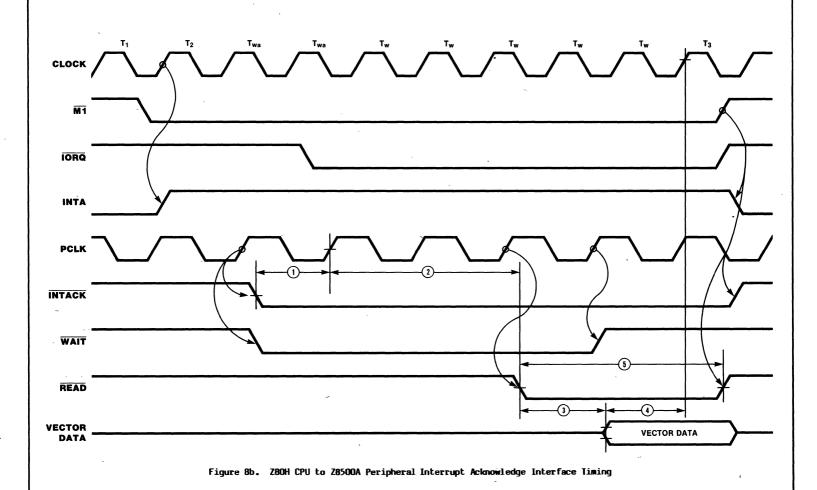

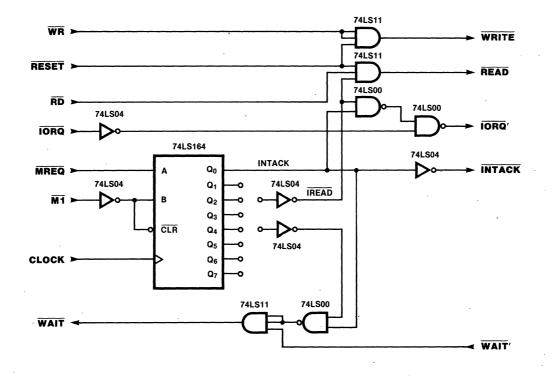

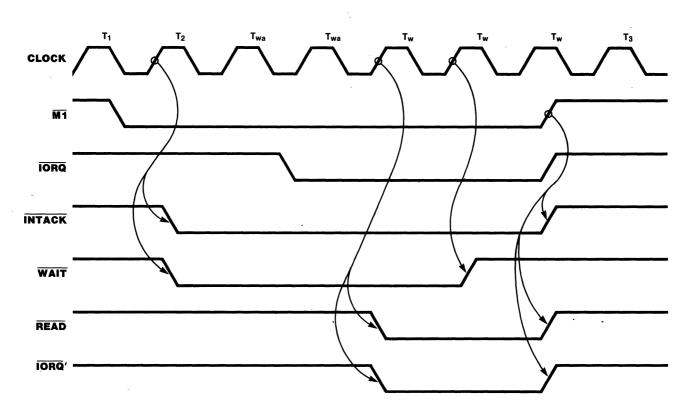

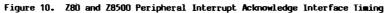

| Interfacing Z80 CPUs to the Z8500 Peripheral Family                 | 709 |

|                                                                     |     |

# **Additional Information**

| Datacom Product Support             | 733 |

|-------------------------------------|-----|

| Military Qualified Datacom Products | 739 |

| Quality and Reliability             |     |

| Literature Guide                    |     |

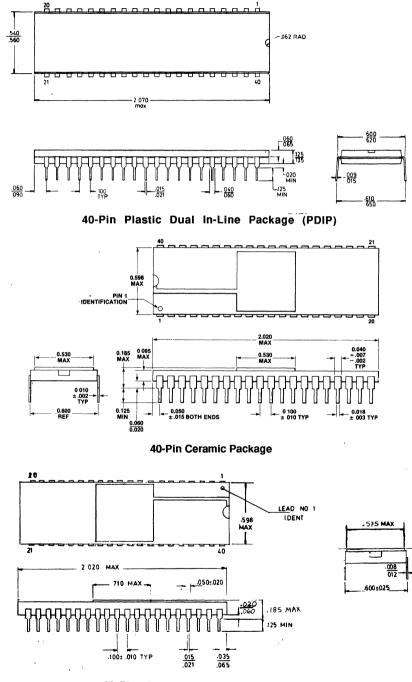

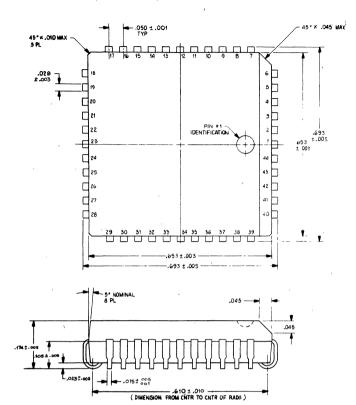

| Package Information                 |     |

| Ordering Information                |     |

-----

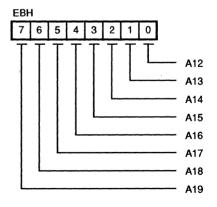

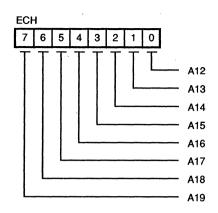

The second second

· · ·

**DATACOM PRODUCTS**

ι.

PRODUCT SPECIFICATION

# **Z16C30** CMOS USC UNIVERSAL SERIAL CONTROLLER

# FEATURES

- Two independent, 0 to 10 Mbit/sec, full duplex channels, each with two baud rate generators and one digital phase-locked loop for clock recovery.

- 32-byte data FIFO's for each receiver and transmitter

- 12.5 MByte/sec (16-bit) data bus bandwidth

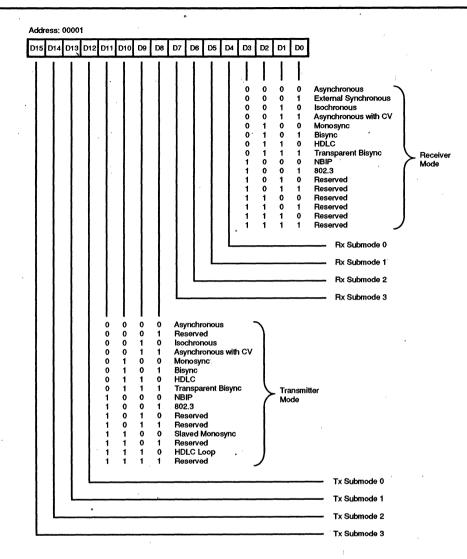

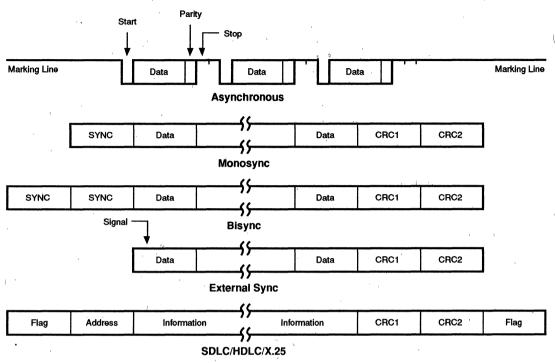

- Multi-protocol operation under program control with independent mode selection for receiver and transmitter.

- Async mode with one to eight bits/character, 1/16 to 2 stop bits/character in 1/16 bit increments; programmable clock factor; break detect and generation; odd, even, mark, space or no parity and framing error detection Supports one Address/Data bit and MIL STD 1553B protocols.

- Byte oriented synchronous mode with one to eight bits/character; programmable idle line condition; optional receive sync stripping; optional preamble transmission, 16- or 32-bit CRC and transmit-to-receive slaving (for X.21)

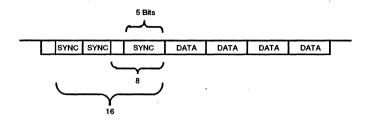

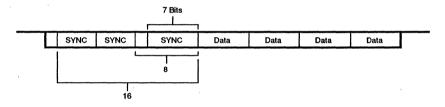

- Bisync mode with 2- to 16-bit programmable sync character; programmable idle line condition; optional receive sync stripping; optional preamble transmission; 16- or 32-bit CRC.

- Transparent Bisync mode with EBCDIC or ASCII character code; automatic CRC handling; programmable idle line condition; optional preamble transmission; automatic recognition of DLE, SYN, SOH, ITX, ETX, ETB, EOT, ENQ and ITB.

- External character sync mode for receive

- HDLC/SDLC mode with eight bit address compare, extended address field option; 16- or 32-bit CRC, programmable idle line condition; optional preamble transmission and loop mode.

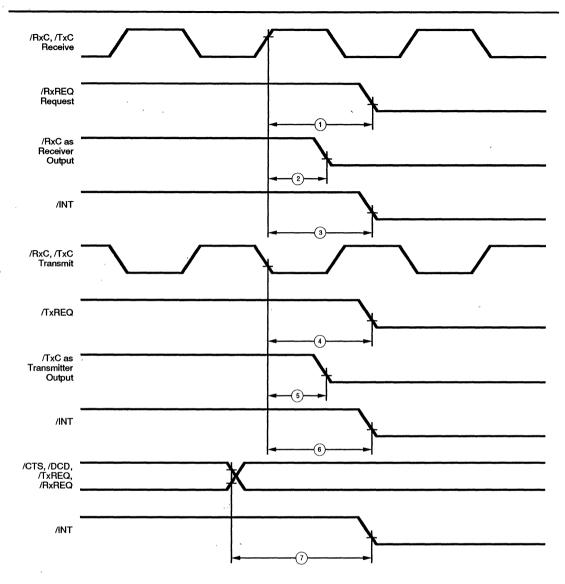

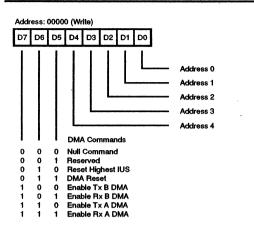

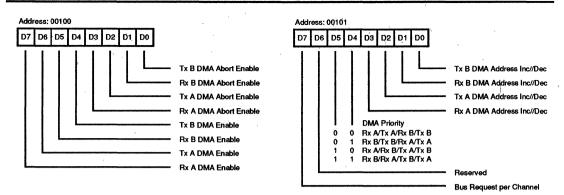

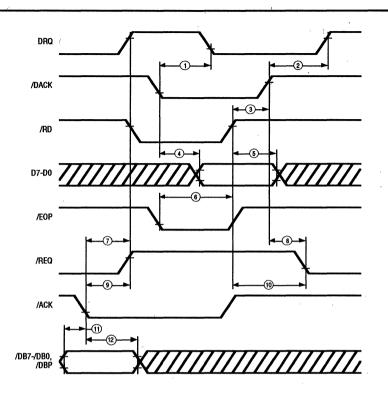

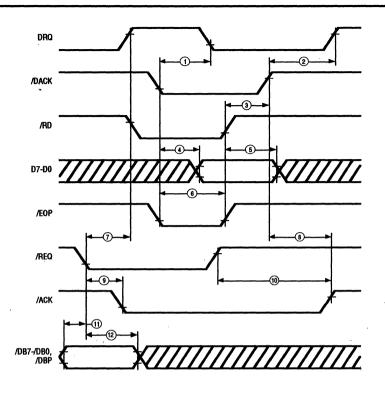

- DMA interface with separate request and acknowledge for each receiver and transmitter.

- Channel load command for DMA controlled initialization.

- Flexible bus interface for direct connection to most microprocessors; user programmable for 8 or 16 bits wide Directly supports 680X0 family or 8X86 family bus interfaces.

- Low power CMOS

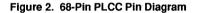

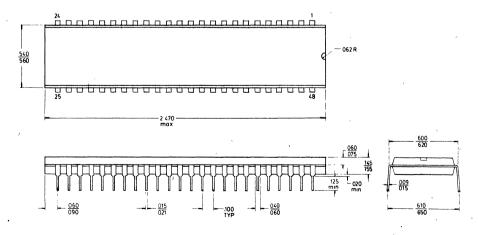

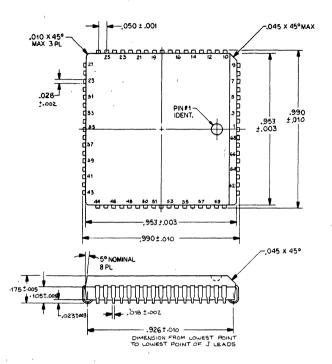

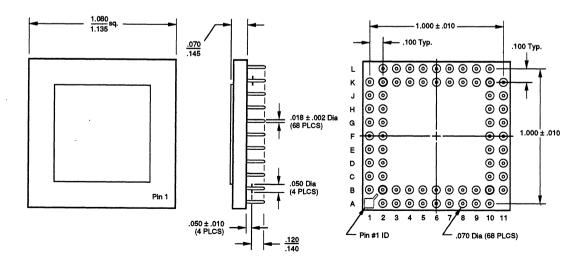

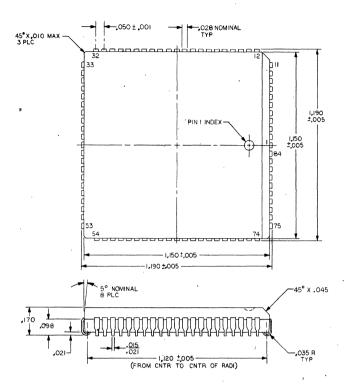

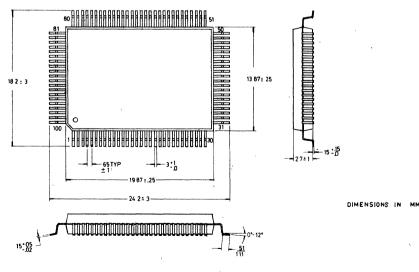

- 68-pin PLCC package

# **GENERAL DESCRIPTION**

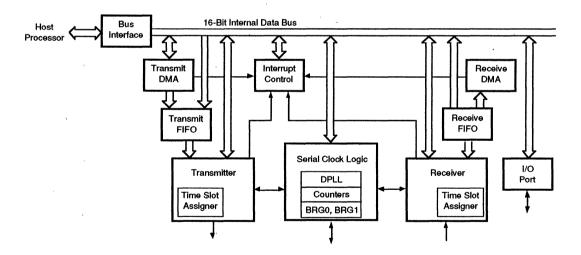

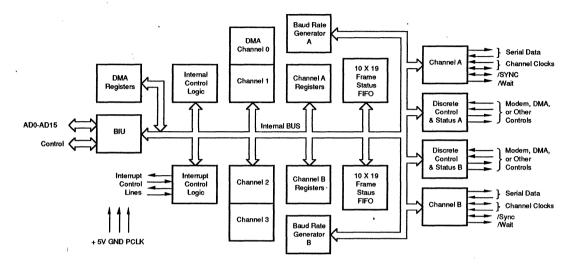

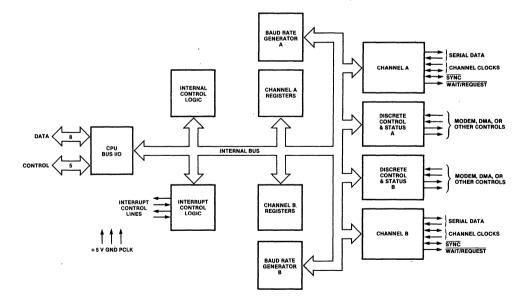

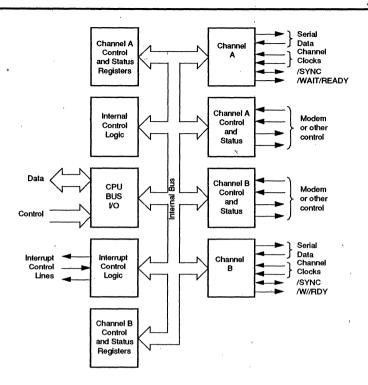

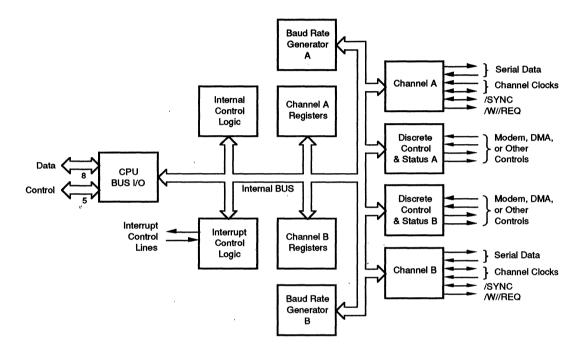

The USC Universal Serial Controller is a dual-channel multi-protocol data communications peripheral designed for use with any conventional multiplexed or non-multiplexed bus. The USC functions as a serial-to-parallel, parallel-to-serial converter/controller and may be software configured to satisfy a wide variety of serial communications

applications. The device contains a variety of new, sophisticated internal functions including two baud rate generators per channel, a digital phase-locked loop per channel, character counters for both receive and transmit in each channel and 32-byte data FIFO's for each receiver and transmitter.

# **GENERAL DESCRIPTION** (Continued)

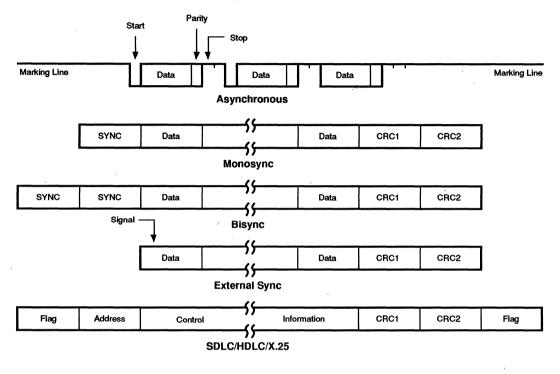

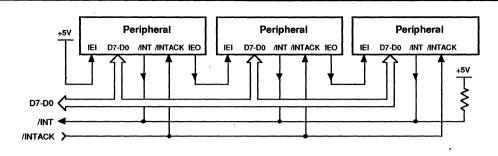

The USC handles asynchronous formats, synchronous byte-oriented formats such as BISYNC and synchronous bit-oriented formats such as HDLC. This device supports virtually any serial data transfer application.

The device can generate and check CRC in any synchronous mode and can be programmed to check data integrity in various modes. The USC also has facilities for modem controls in both channels. In applications where these controls are not needed, the modem controls may be used for general-purpose I/O. The same is true for most of the other pins in each channel.

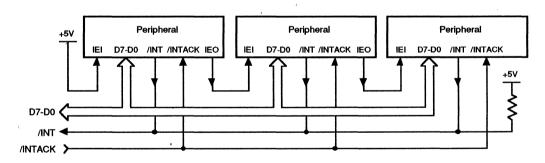

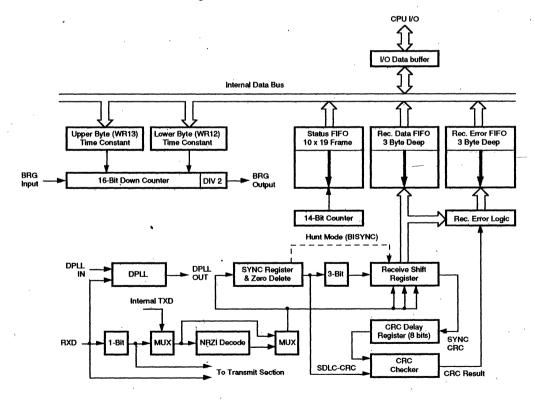

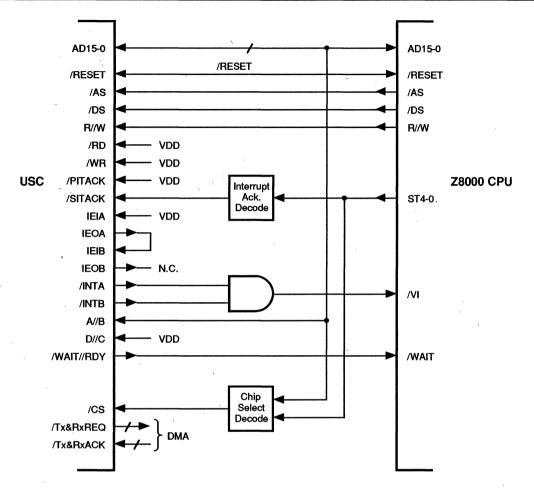

Interrupts are supported with a daisy-chain hierarchy, with the two channels having completely separate interrupt structures.

High-speed data transfers via DMA are supported by a Request/Acknowledge signal pair for each receiver and

transmitter. The device supports automatic status transfer via DMA and also allows device initialization under DMA control.

To aid the designer in efficiently programming the USC, support tools are available. The Technical Manual describes in detail all features presented in this Product Specification and gives programming sequence hints. The Programmer's Assistant is a MS-DOS disk-based programming initialization tool to be used in conjunction with the Technical Manual. There are also available assorted application notes and development boards to assist the designer in the hardware/software development.

Note: All Signals with a preceding front slash, "/", are active Low, e.g.: B//W (WORD is active Low); /B/W (BYTE is active Low, only); /N//S (NORMAL and SYSTEM are both active Low).

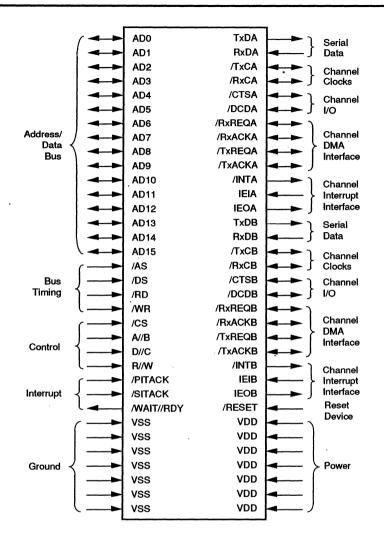

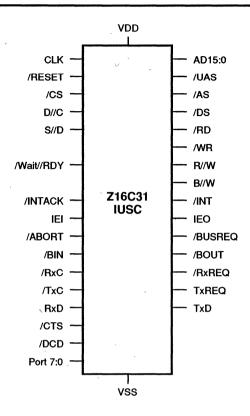

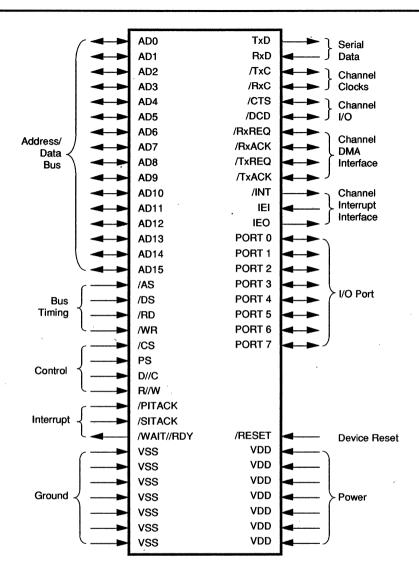

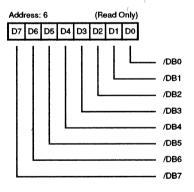

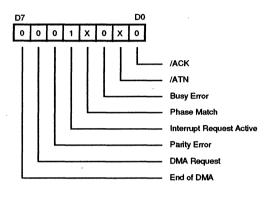

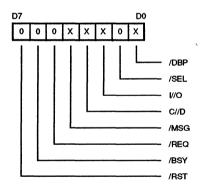

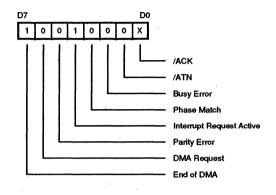

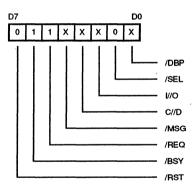

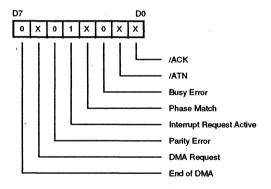

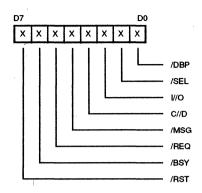

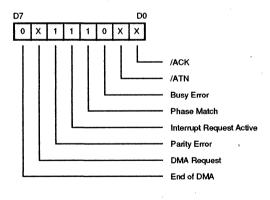

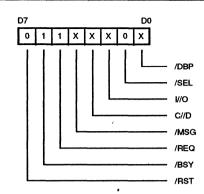

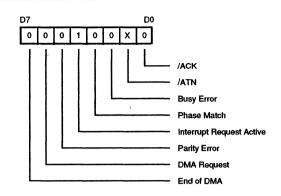

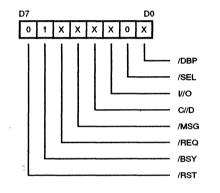

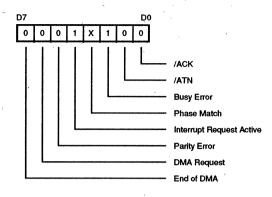

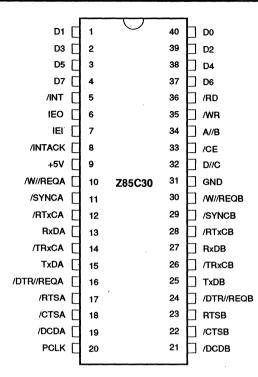

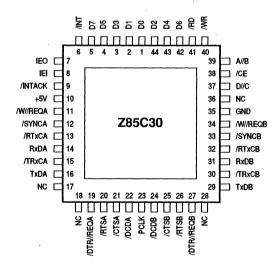

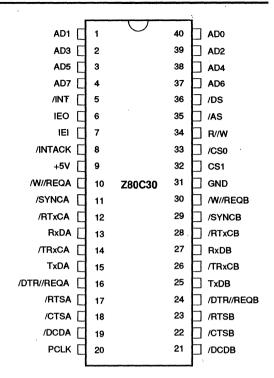

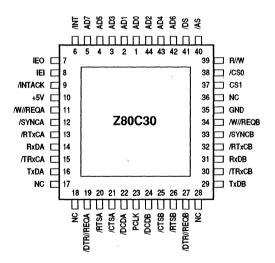

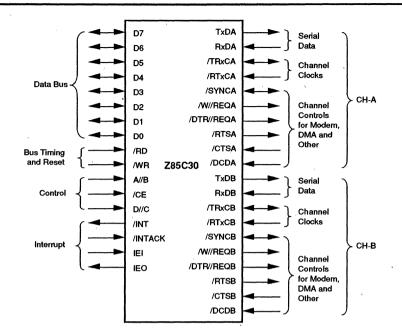

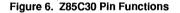

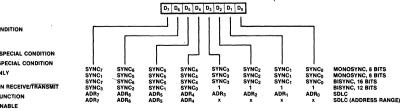

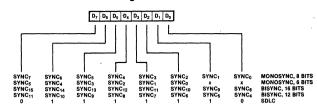

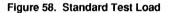

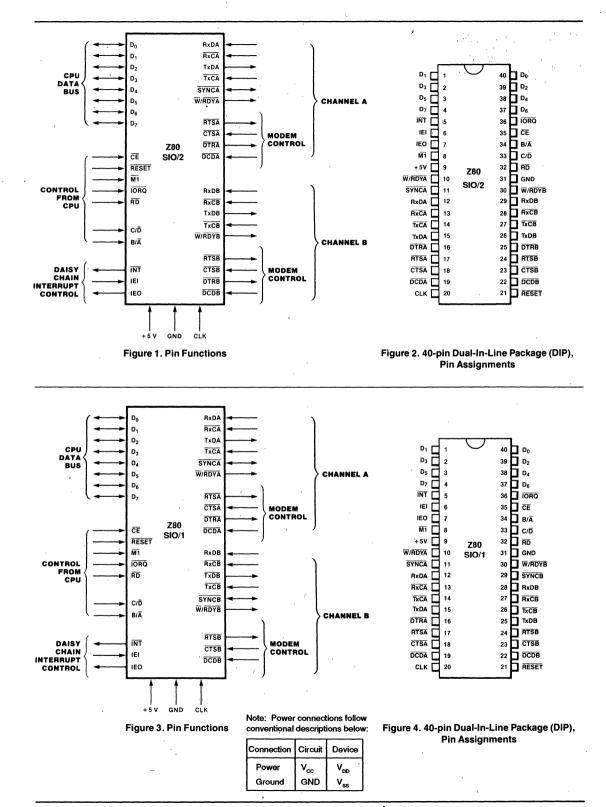

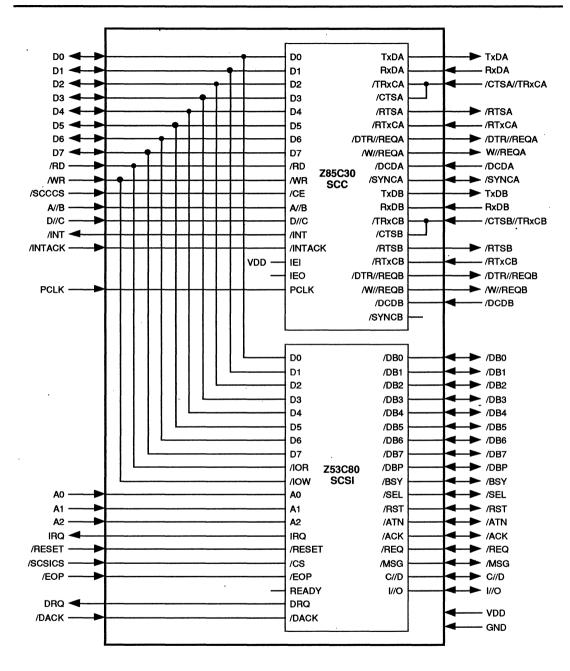

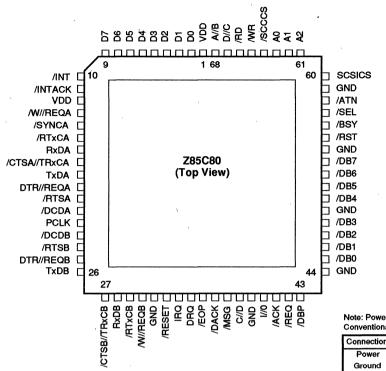

Figure 2. Pin Functions

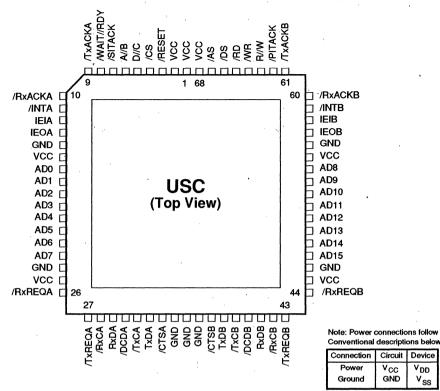

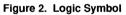

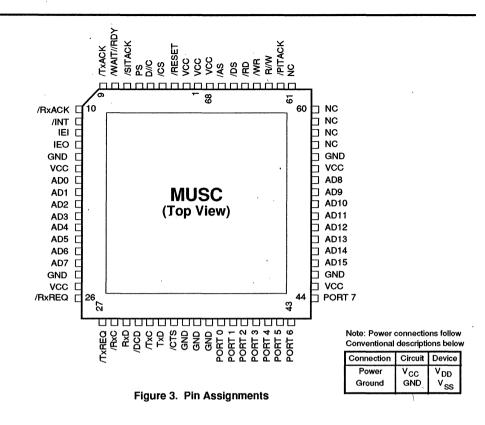

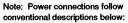

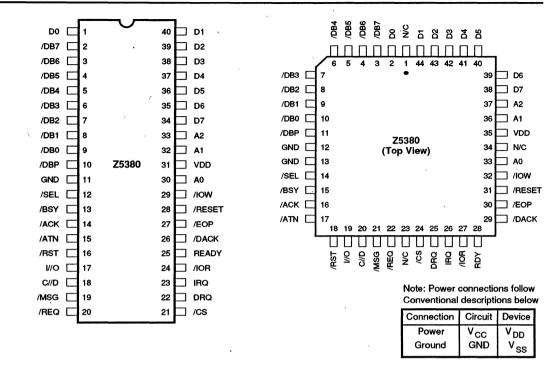

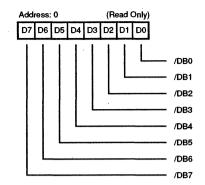

Note: Power connections follow conventional descriptions below:

| Connection | Circuit         | Device          |

|------------|-----------------|-----------------|

| Power      | V <sub>cc</sub> | V <sub>dd</sub> |

| Ground     | GND             | V <sub>ss</sub> |

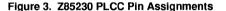

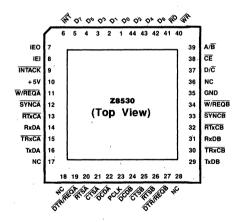

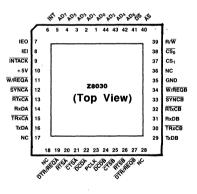

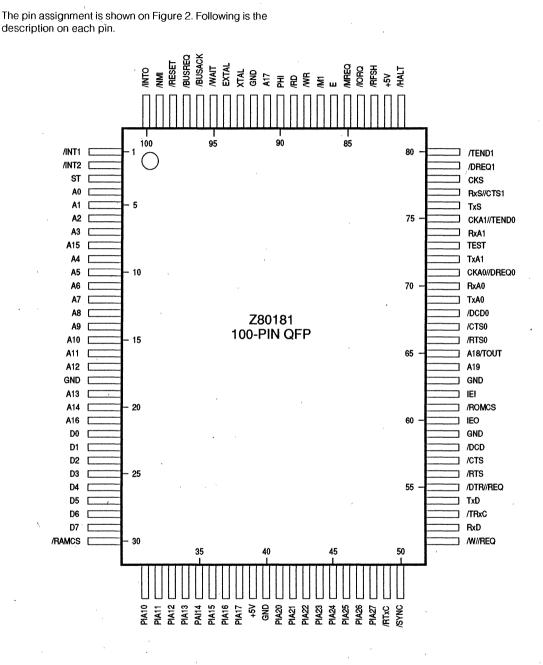

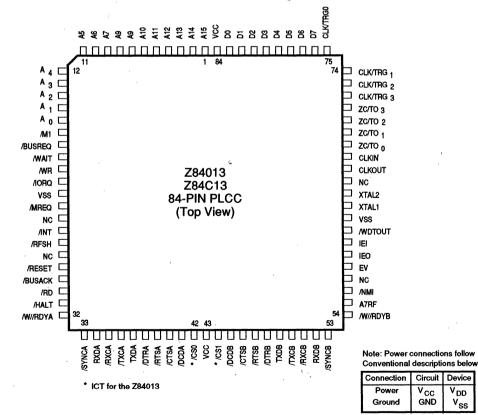

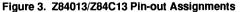

Figure 3. Pin Assignments

# **PIN DESCRIPTION**

The device contains 13 pins per channel for channel I/O, 16 pins for address and data, 12 pins for CPU handshake and 14 pins for power and ground.

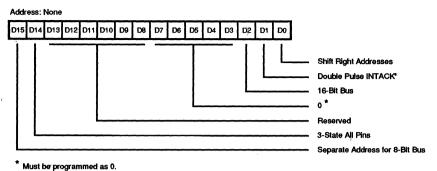

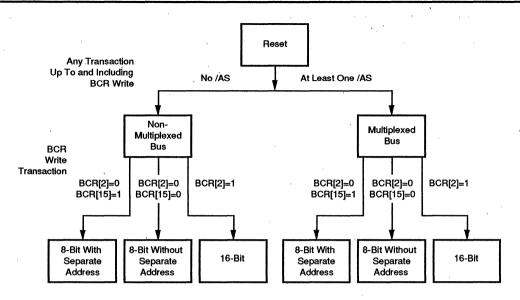

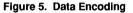

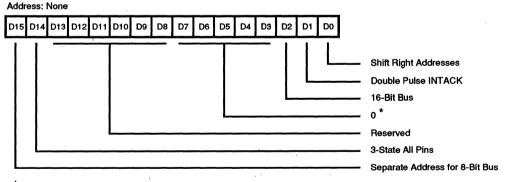

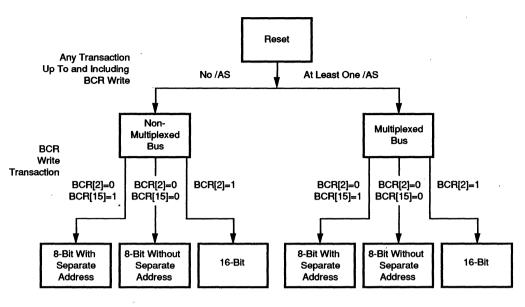

Three separate bus interface types are available for the device. The Bus Configuration Register (BCR) and external connections to the AD bus control selection of the bus type.

A 16-bit bus is selected by setting BCR bit 2 to a 1.

The 8-bit bus is selected by setting BCR bit 2 to zero and tying AD15 - AD8 to VSS.

The 8-bit bus with separate address is selected by setting BCR bit 2 to zero and, during the BCR write, forcing AD15 to a 1 and forcing AD14-AD8 to zero.

The multiplexed bus is selected for the USC if there is an Address Strobe prior to or during the transaction which

writes the BCR. If no Address Strobe is present prior to or during the transaction which writes the BCR, a non-multiplexed bus is selected (See Figure 6).

The section below describes in detail the USC pin assignment.

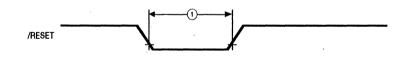

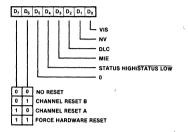

**RESET.** *Reset* (input, active Low). This signal resets the advice to a known state. The first write to the USC after a reset accesses the BCR to select additional bus options for the device.

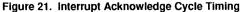

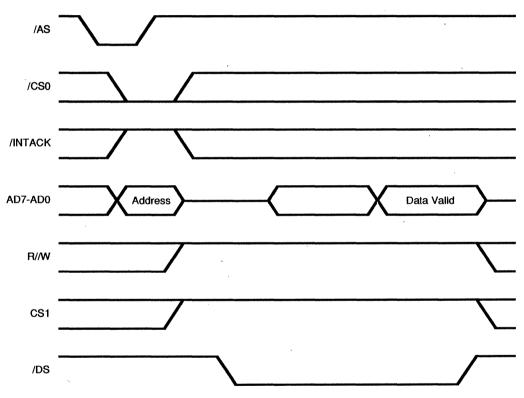

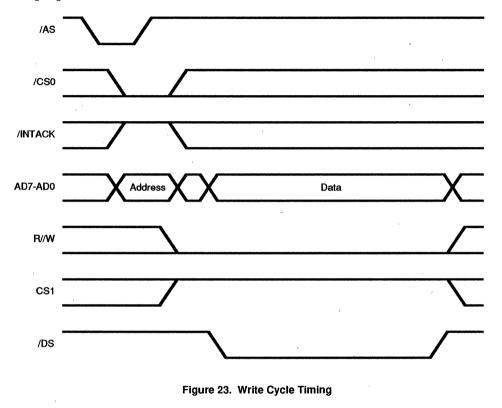

**/AS.** Address Strobe (input, active Low). This signal is used in the multiplexed bus modes to latch the address on the AD lines. The /AS signal is not used in the non-multiplexed bus modes and should be tied to VDD.

**/DS.** Data Strobe (input, active Low). This signal strobes data out of the device during a read and may strobe an interrupt vector out of the device during an interrupt

acknowledge cycle. /DS also strobes data into the device on the state of R//W.

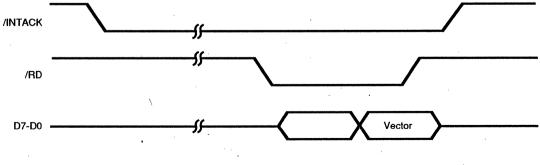

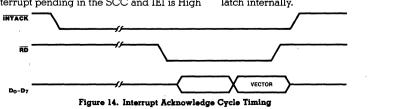

**/RD.** *Read Strobe* (input, active Low). This signal strobes data out of the device during a read and may strobe an interrupt vector out of the device during an interrupt acknowledge cycle.

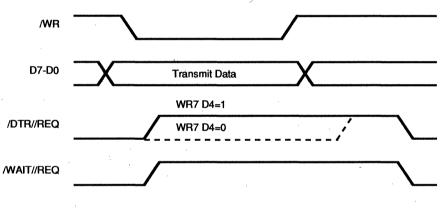

**/WR.** *Write Strobe* (input, active Low). This signal strobes data into the device during a write.

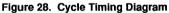

**R**//**W**. *Read*/*Write* (input). This signal determines the direction of data transfer for a read or write cycle in conjunction with /DS.

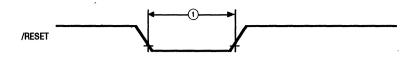

/CS. *Chip Select* (input, active Low). This signal selects the device for access and must be asserted for read and write cycles, but is ignored during interrupt acknowledge and fly-by DMA transfers. In the case of a multiplexed bus interface, /CS is latched by the rising edge of /AS.

A//B. Channel A/Channel B Select (input). This signal selects between the two channels in the device. High selects channel A and Low selects channel B. This signal is sampled and the result is latched during the BCR (Bus Configuration Register) write. It programs the sense of the /WAIT//RDY signal appropriate for different bus interfaces. See /WAIT//RDY below.

**D//C.** *Data/Control Select* (input). This signal, when High, provides for direct access to the RDR and TDR. In the case of a multiplexed bus interface, D//C High overrides the address provided to the device.

/SITACK. Status Interrupt Acknowledge (input, active Low). This signal is a status signal that indicates that an interrupt acknowledge cycle is in progress. The device is capable of returning an interrupt vector that may be encoded with the type of interrupt pending during this acknowledge cycle. This signal is compatible with 680X0 family microprocessors.

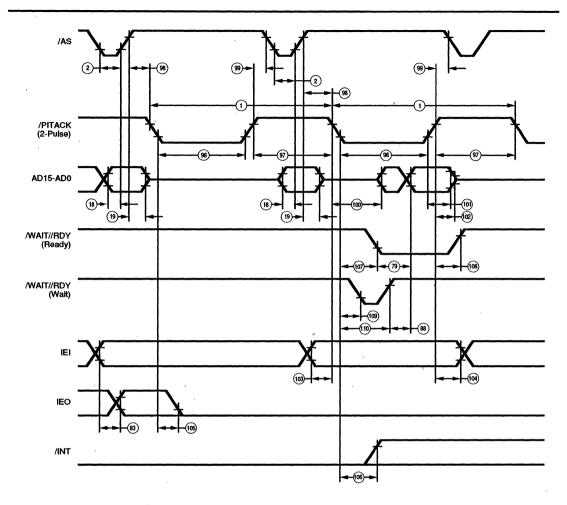

**/PITACK.** Pulsed Interrupt Acknowledge (input, active Low). This signal is a strobe signal that indicates that an interrupt acknowledge cycle is in progress. The device is capable of returning an interrupt vector that may be encoded with the type of interrupt pending during this acknowledge cycle. /PITACK may be programmed to accept a single pulse or double pulse acknowledge type. This programming is done in the BCR. With the double pulse type selected, the first /PITACK is recognized but no action takes place. The interrupt vector is returned on the second pulse if the no vector option is not selected. The double pulse type is compatible with 8X86 family microprocessors.

**(WAIT//RDY.** *Wait/Data Ready* (output, active Low). This signal serves to indicate when the data is available during a read cycle, when the device is ready to receive data during a write cycle, and when a valid vector is available during an interrupt acknowledge cycle. It may be programmed to function either as a Wait signal or a Ready signal using the state of the A//B pin during the BCR write. When A//B is High during the BCR write, this signal functions as a wait output and thus supports the READY function of 8X86 family microprocessors. When A//B is Low during the BCR write, this signal functions as a ready output and thus supports the DTACK function of 680X0 family microprocessors.

AD15-AD0. Address/Data Bus (bidirectional, active High, 3-state). The AD signals carry addresses to, and data to and from, the device. When the 16-bit non-multiplexed bus is selected, AD15-0 carry data to and from the device. Addresses are provided using a pointer within the device that is loaded with the desired register address. When selecting the 8-bit non-multiplexed bus (without separate address) only AD7-0 are used to transfer data. The pointer is used for addressing, with AD15-8 unused. When selecting the 8-bit non-multiplexed bus (with separate address), AD7-0 are used to transfer data with AD15-8 used as address bus. When the 16-bit multiplexed bus is selected. addresses are latched from AD7-0 and data transfers are sixteen bits wide. When selecting the 8-bit multiplexed bus (without separate address) only AD7-0 are used to transfer addresses and data, with AD15-8 unused. When the 8-bit multiplexed bus with separate address is selected, only AD7-0 are used to transfer data, while AD15-8 are used as an address bus.

/INTA, /INTB. Interrupt Request(outputs, active Low). These signals indicate that the channel has an interrupt condition pending and is requesting service. These outputs are NOT open-drain.

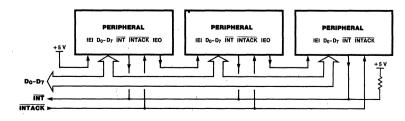

**IEIA, IEIB.** Interrupt Enable In (inputs, active High). The IEI signal for each channel is used with the accompanying IEO signal to form an interrupt daisy chain. An active IEI indicates that no device having higher priority is requesting or servicing an interrupt.

**IEOA, IEOB.** Interrupt Enable Out (outputs, active High). The IEO signal for each channel is used with the accompanying IEI signal to form an interrupt daisy chain. IEO is Low if IEI is Low, an interrupt is under service in the channel, or an interrupt is pending during an interrupt acknowledge cycle.

**(TxACKA, /TxACKB.** *Transmit Acknowledge* (inputs or outputs, active Low). The primary function of these signals is to perform fly-by DMA transfers to the transmit FIFOs They may also be used as bit inputs or outputs.

**/RxACKA, /RxACKB.** Receive Acknowledge (inputs or outputs, active Low). The primary function of these signals is to perform fly-by DMA transfers from the receive FIFOs. They may also be used as bit inputs or outputs.

TxDA, TxDB. *Transmit Data* (outputs, active High, 3-state). These signals carry the serial transmit data for each channel.

**RxDA, RxDB.** *Receive Data* (inputs, active High). These signals carry the serial receive data for each channel.

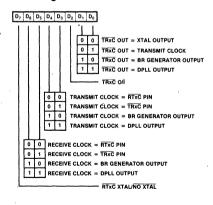

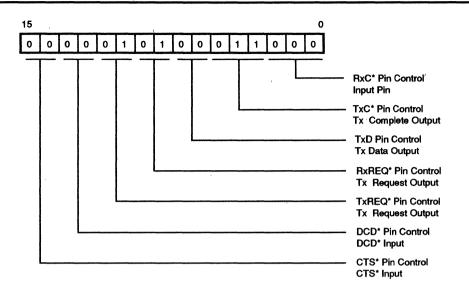

/TxCA, /TxCB. *Transmit Clock* (inputs or outputs, active Low). These signals are used as clock inputs for any of the functional blocks within the device. They may also be used as outputs for various transmitter signals or internal clock signals.

**/RxCA, /RxCB.** Receive Clock (inputs or outputs, active Low). These signals are used as clock inputs for any of the functional blocks within the device. They may also be used as outputs for various receiver signals or internal clock signals.

/TxREQA, /TxREQB. *Transmit Request* (inputs or outputs, active Low). The primary function of these signals is to request DMA transfers to the transmit FIFOs. They may also be used as simple inputs or outputs.

/RxREQA, /RxREQB. Receive Request (inputs or outputs, active Low). The primary function of these signals is to request DMA transfers from the receive FIFOs. They may also be used as simple inputs or outputs.

/CTSA, /CTSB. Clear To Send (inputs or outputs, active Low). These signals are used as enables for the respective transmitters. They may also be programmed to generate interrupts on either transition or used as simple inputs or outputs.

**/DCDA, /DCDB.** Data Carrier Detect (inputs or outputs, active Low). These signals are used as enables for the respective receivers. They may also be programmed to generate interrupts on either transition or used as simple inputs or outputs.

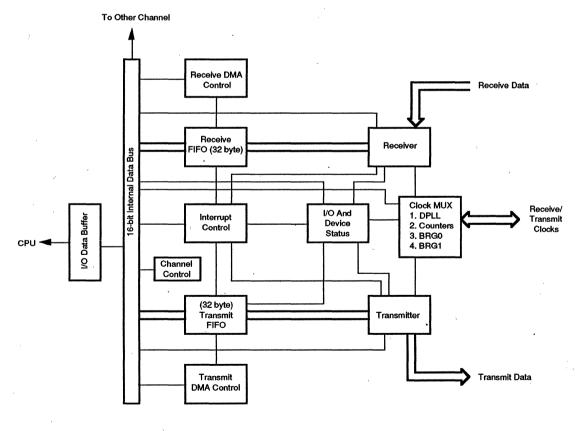

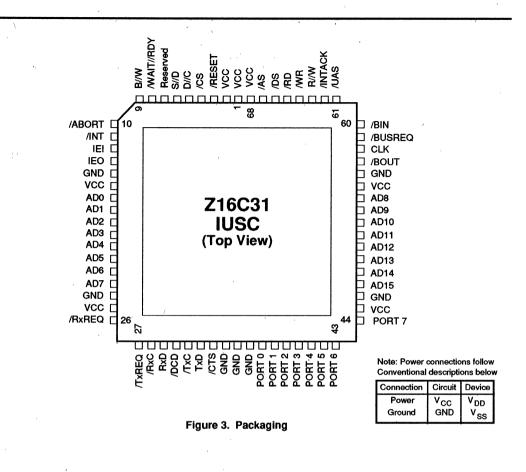

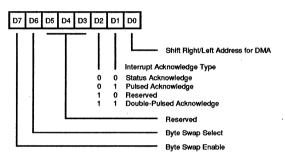

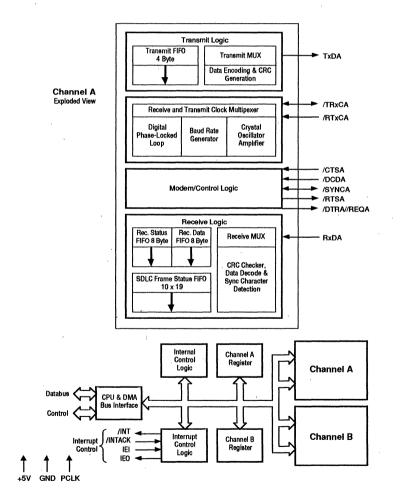

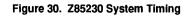

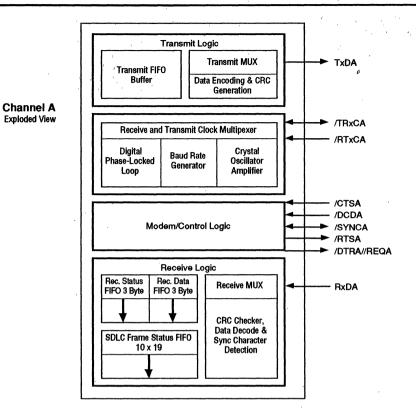

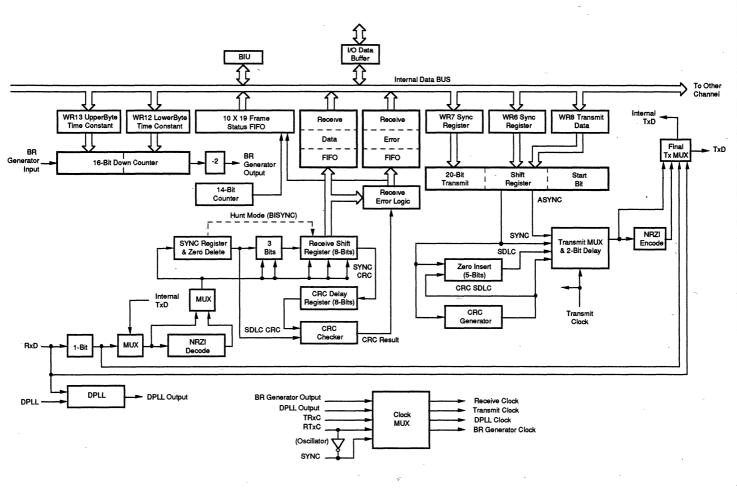

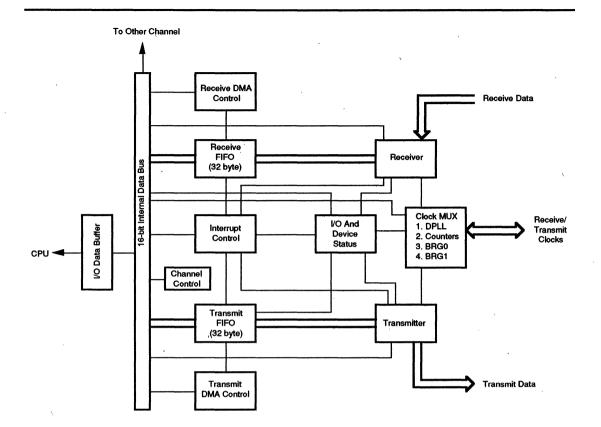

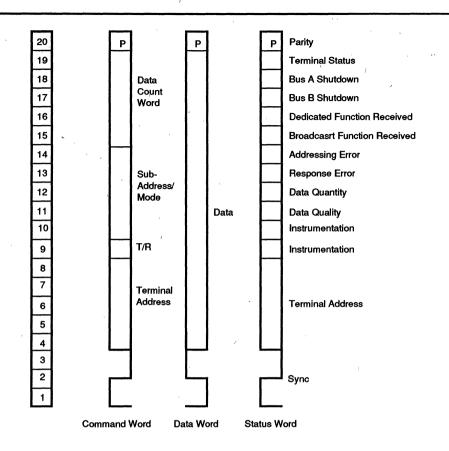

# ARCHITECTURE

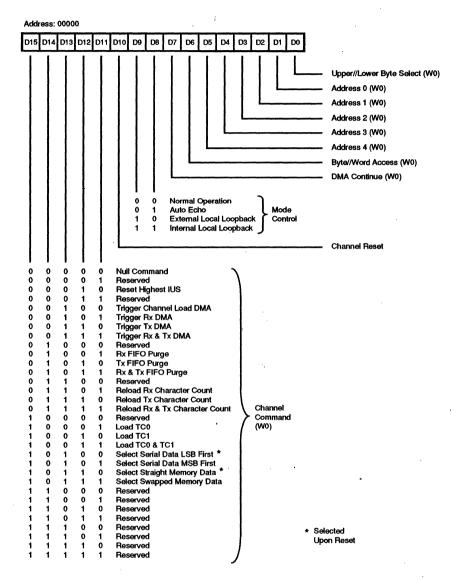

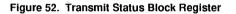

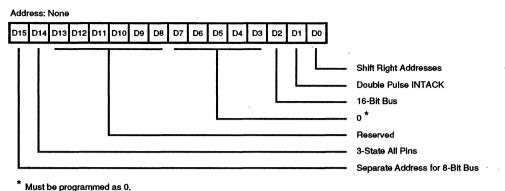

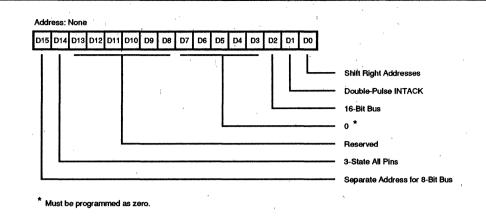

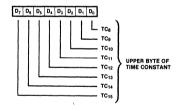

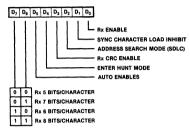

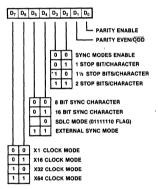

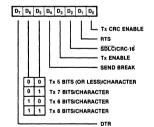

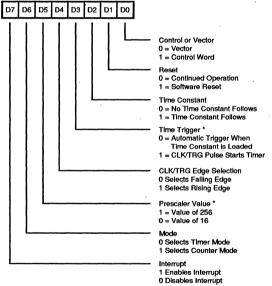

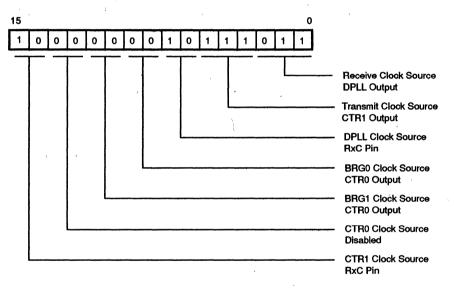

The USC internal structure includes two completely independent full-duplex serial channels, each with two baud rate generators, a digital phase-locked loop for clock recovery, transmit and receive character counters and a full-duplex DMA interface. The two serial channels share a common bus interface. The bus interface is designed to provide easy interface to most microprocessors, whether they employ a multiplexed or non-multiplexed, 8-bit or 16-bit bus structure. Each channel is controlled by a set of thirty 16-bit registers, nearly all of which are readable and writable. There is one additional 16-bit register in the bus interface used to configure the nature of the bus interface. The BCR functions are shown in Figure 4.

in an programmed do e.

Figure 4. Bus Configuration Register

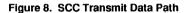

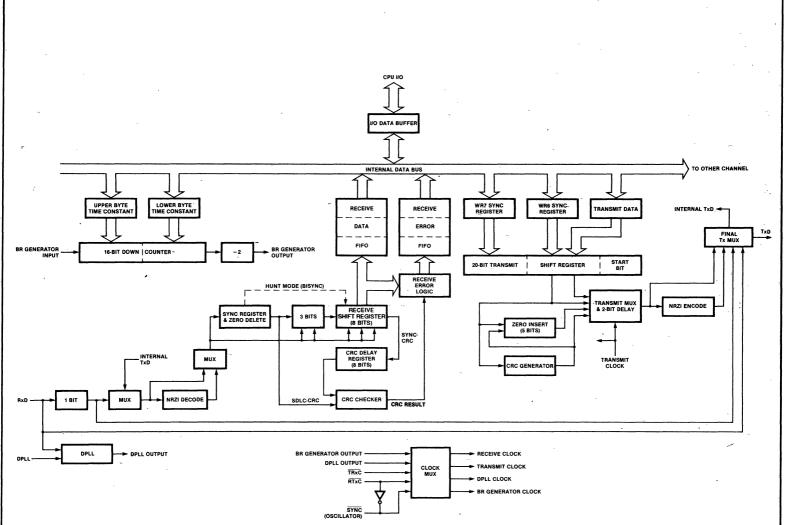

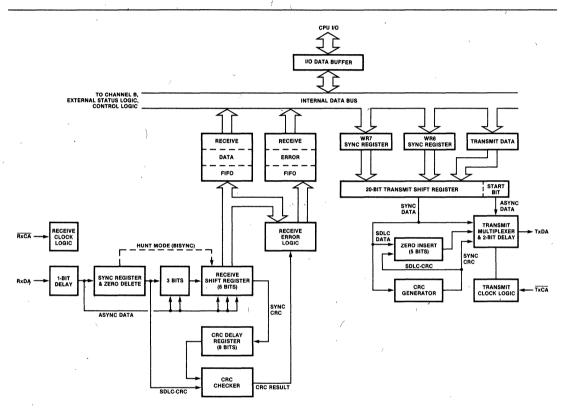

# DATA PATH

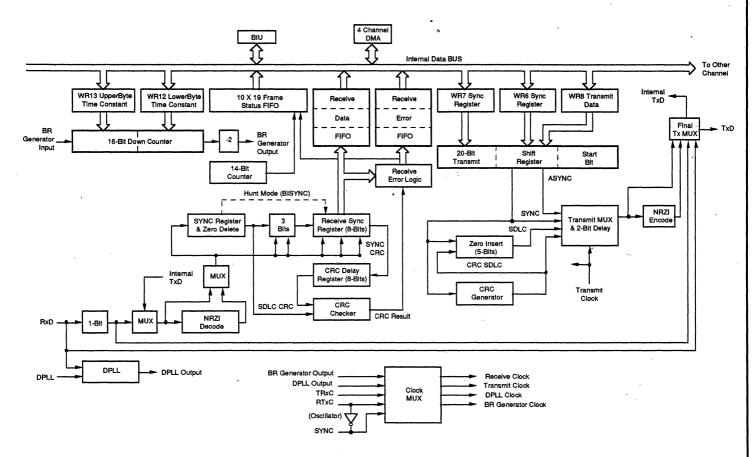

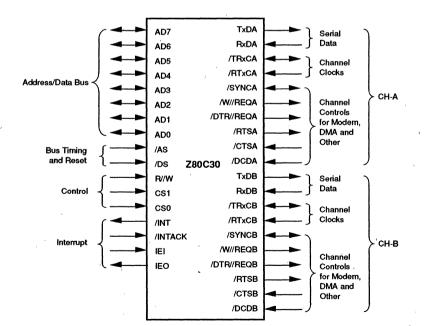

Both the transmitter and the receiver in the channel are actually microcoded serial processors. As the data shifts through the transmit or receive shift register, the microcode watches for specific bit patterns, counts bits, and at the appropriate time transfers data to or from the FIFOs. The microcode also checks status and generates status interrupts as appropriate.

# FUNCTIONAL DESCRIPTION

The functional capabilities of the USC are described from two different points of view: as a data communications device, it transmits and receives data in a wide variety of data communications protocols; as a microprocessor peripheral, the USC offers such features as read/write registers, a flexible bus interface, DMA interface support and vectored interrupts.

#### **Data Communications Capabilities**

The USC provides two independent full-duplex channels programmable for use in any common data communication protocol. The receiver and transmitter modes are completely independent, as are the two channels. Each receiver and transmitter is supported by a 32-byte deep FIFO and a 16-bit message length counter. All modes allow optional even, odd, mark or space parity. Synchronous modes allow the choice of two 16-bit or one 32-bit CRC polynomial. Selection of from one to eight bits-percharacter is available in both receiver and transmitter, independently. Error and status conditions are carried with the data in the receive and transmit FIFOs to greatly reduce the CPU overhead required to send or receive a message. Specific, appropriately timed interrupts are available to signal such conditions as overrun, parity error, framing error, end-of-frame, idle line received, sync acquired,

transmit underrun, CRC sent, closing sync/flag sent, abort sent, idle line sent and preamble sent. In addition, several useful internal signals such as receive FIFO load, received sync, transmit FIFO read and transmission complete may be sent to pins for use by external circuitry.

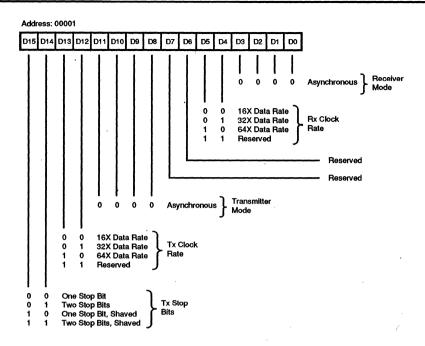

Asynchronous Mode. The receiver and transmitter can handle data at a rate of 1/16, 1/32, or 1/64 the clock rate. The receiver rejects start bits less than one-half a bit time and will not erroneously assemble characters following a framing error. The transmitter is capable of sending one, two, or anywhere in the range of 1/16th to two stop bits per character in 1/16 bit increments.

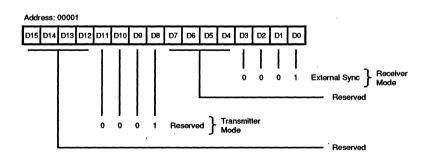

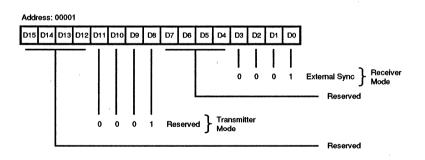

**External Sync Mode.** The receiver is synchronized to the receive data stream by an externally-supplied signal on a pin for custom protocol applications.

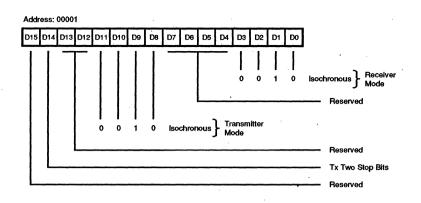

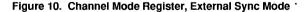

**Isochronous Mode.** Both transmitter and receiver may operate on start-stop (async) data using a 1x clock. The transmitter can send one or two stop bits.

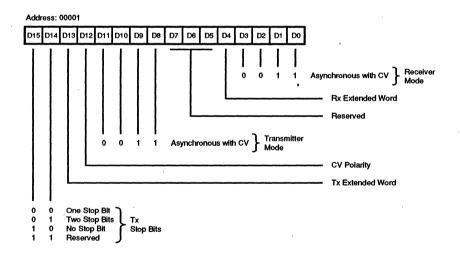

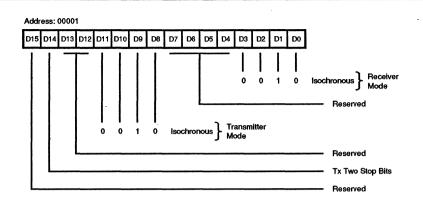

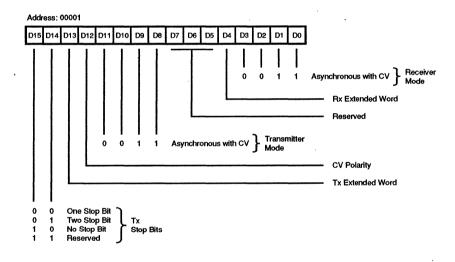

Asynchronous With Code Violations. This is similar to Isochronous mode except that the start bit is replaced by a three bit-time code violation pattern as in MIL-STD 1553B. The transmitter can send zero, one or two stop bits.

# FUNCTIONAL DESCRIPTION (Continued)

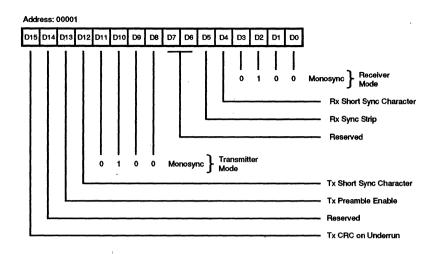

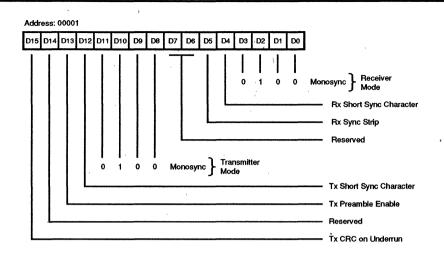

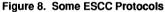

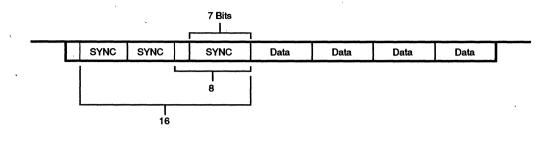

Monosync Mode. In this mode, a single character is used for synchronization. The sync character can be either eight bits long with an arbitrary data character length, or programmed to match the data character length. The receiver is capable of automatically stripping sync characters from the received data stream. The transmitter may be programmed to automatically send CRC on either an underrun or at the end of a programmed message length.

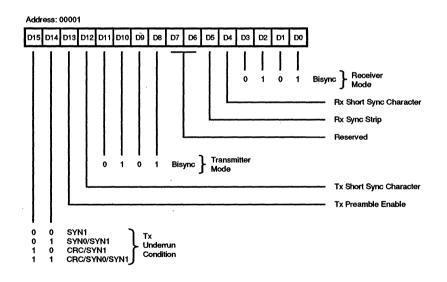

**Bisync Mode.** This mode is identical to monosync mode except that character synchronization requires two successive characters for synchronization. The two characters need not be identical.

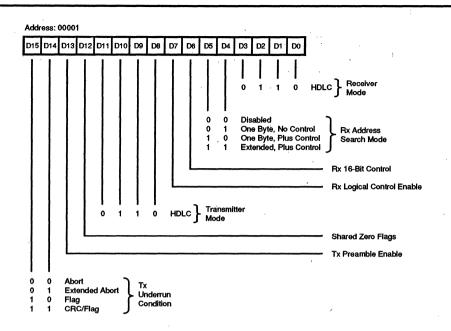

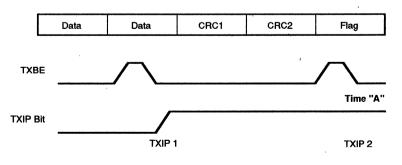

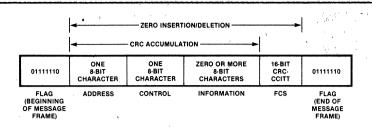

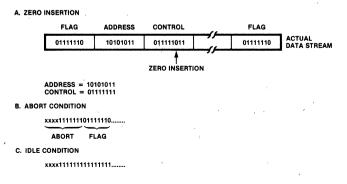

HDLC Mode. In this mode, the receiver recognizes flags, performs optional address matching, accommodates extended address fields, 8- or 16-bit control fields and logical control fields, performs zero deletion and CRC checking. The receiver is capable of receiving shared-zero flags, recognizes the abort sequence and can receive arbitrary length messages. The transmitter automatically sends opening and closing flags, performs zero insertion and can be programmed to send an abort, an extended abort, a flag or CRC and a flag on transmit underrun. The transmitter can also automatically send the closing flags with optional CRC at the end of a programmed message length. Shared-zero flags are selected in the transmitter and a separate character length may be programmed for the last character in the frame.

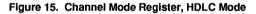

Bisync Transparent Mode. In this mode, the synchronization pattern is DLE-SYN, programmable selected from either ASCII or EBCDIC encoding. The receiver recognizes control character sequences and automatically handles CRC calculation without CPU intervention. The transmitter can be programmed to send either SYN, DLE-SYN, CRC-SYN, or CRC-DLE-SYN upon underrun and can automatically send the closing DLE-SYN with optional CRC at the end of a programmed message length.

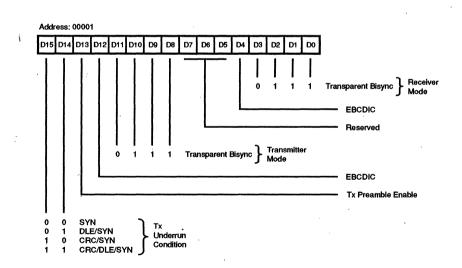

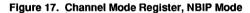

**NBIP Mode.** This mode is identical to async except that the receiver checks for the status of an additional address/ data bit between the parity bit and the stop bit. The value of this bit is FIFO'ed along with the data. This bit is automatically inserted in the transmitter with the value that is FIFO'ed with the transmit data.

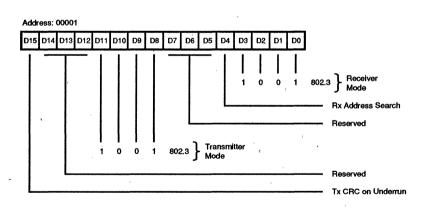

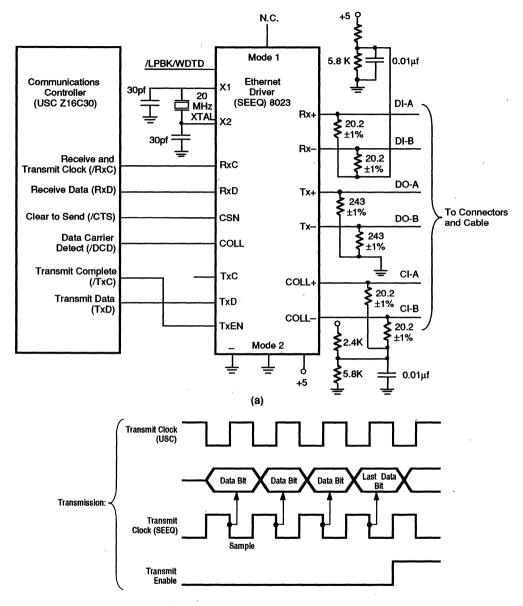

**802.3 Mode.** This mode implements the data format of IEEE 802.3 with 16-bit address compare In this mode, /DCD and /CTS are used to implement the carrier sense and collision detect interactions with the receiver and transmitter.

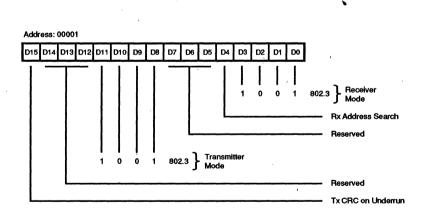

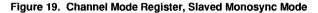

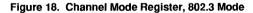

Slaved Monosync Mode. This mode is available only in the transmitter and allows the transmitter (operating as though it were in monosync mode) to send data that is byte-synchronous to the data being received by the receiver.

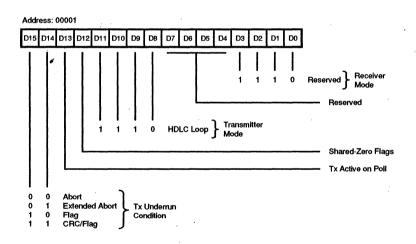

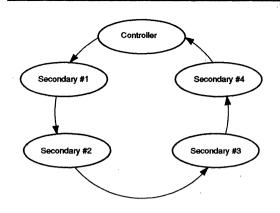

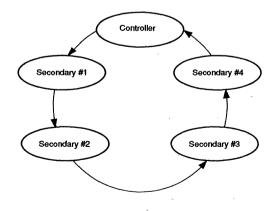

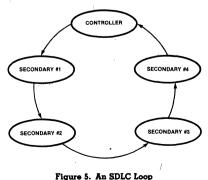

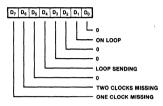

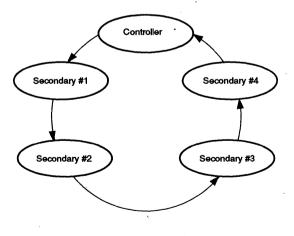

HDLC Loop Mode. This mode is also available only in the transmitter and allows the USC to be used in an HDLC loop configuration. In this mode, the receiver is programmed to operate in HDLC mode so that the transmitter echos received messages. Upon receipt of a particular bit pattern (actually a sequence of seven consecutive ones) the transmitter breaks the loop and inserts its own frame(s).

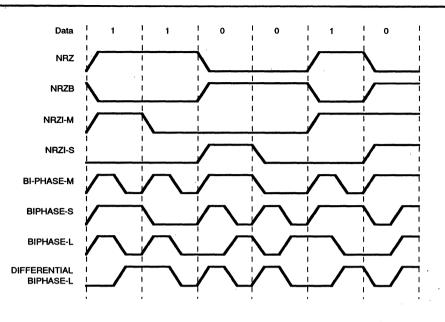

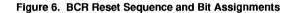

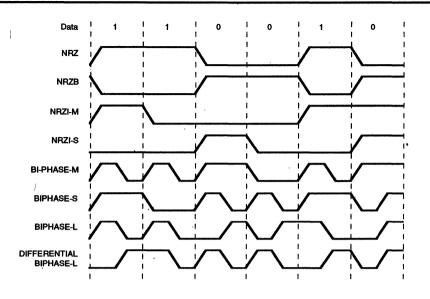

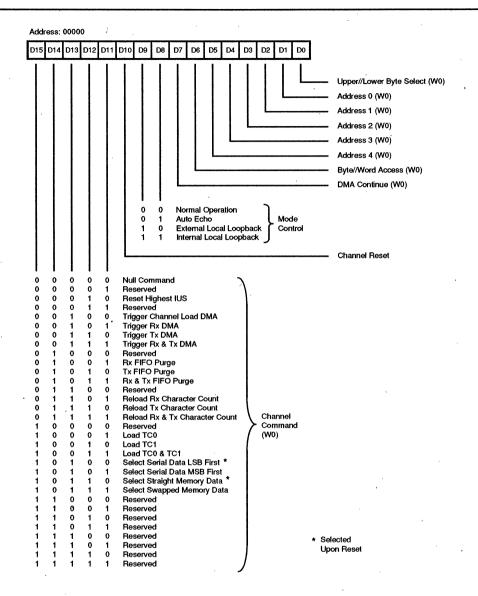

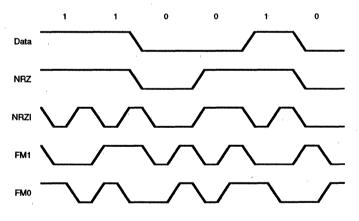

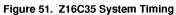

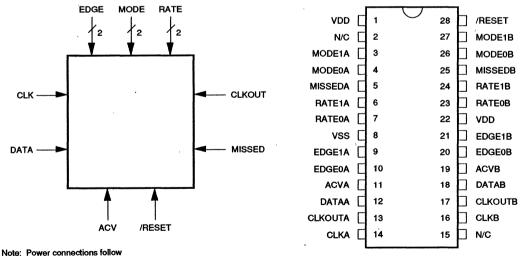

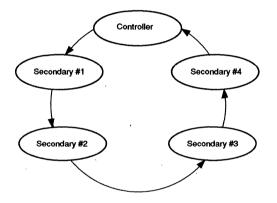

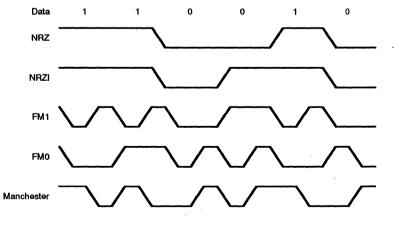

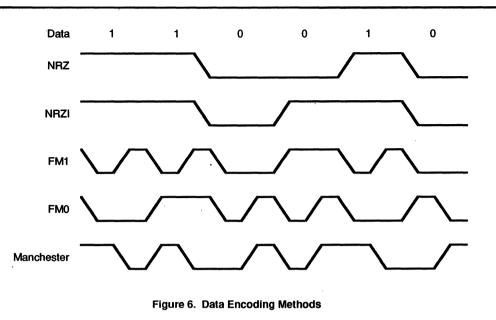

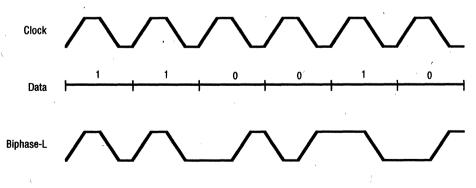

#### Data Encoding

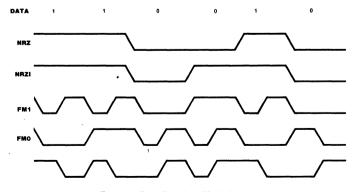

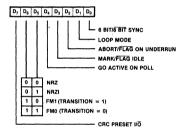

The USC may be programmed to encode and decode the serial data in any of eight different ways as shown in Figure 5. The transmitter encoding method is selected independently of the receiver decoding method.

**NRZ.** In NRZ, a 1 is represented by a High level for the duration of the bit cell and a 0 is represented by a Low level for the duration of the bit cell.

NRZB. Data is inverted from NRZ.

**NRZI-Mark.** In NRZI-Mark, a 1 is represented by a transition at the beginning of the bit cell That is, the level present in the preceding bit cell is reversed. A 0 is represented by the absence of a transition at the beginning of the bit cell.

**NRZI-Space.** In NRZI-Space, a 1 is represented by the absence of a transition at the beginning of the bit cell. That is, the level present in the preceding bit cell is maintained. A 0 is represented by a transition at the beginning of the bit cell.

**Biphase-Mark.** In Biphase-Mark, a 1 is represented by a transition at the beginning of the bit cell and another transition at the center of the bit cell. A 0 is represented by a transition at the beginning of the bit cell only.

**Biphase-Space.** In Biphase-Space, a 1 is represented by a transition at the beginning of the bit cell only. A 0 is represented by a transition at the beginning of the bit cell and another transition at the center of the bit cell.

**Biphase-Level.** In Biphase-Level, a 1 is represented by a High during the first half of the bit cell and a Low during the second half of the bit cell. A 0 is represented by a Low during the first half of the bit cell and a High during the second half of the bit cell.

Figure 5. Data Encoding

Differential Biphase-Level. In Differential Biphase-Level, a 1 is represented by a transition at the center of the bit cell, with the opposite polarity from the transition at the center of the preceding bit cell. A 0 is represented by a transition at the center of the center of the bit cell with the same polarity as the transition at the center of the preceding bit cell. In both cases there may be transitions at the beginning of the bit cell to set up the level required to make the correct center transition.

#### **Character Counters**

Each channel in the USC contains a 16-bit character counter for both receiver and transmitter. The receive character counter may be preset either under software control or automatically at the beginning of a receive message. The counter decrements with each receive character and at the end of the receive message the current value in the counter is automatically loaded into a four-deep FIFO. This allows DMA transfer of data to proceed without CPU intervention at the end of a received message, as the values in the FIFO allow the CPU to determine message boundaries in memory. Similarly, the transmit character counter is loaded either under software control or automatically at the beginning of a transmit message. The counter is decremented with each write to the transmit FIFO. When the counter has decremented to zero, and that byte is sent, the transmitter automatically terminates the message in the appropriate fashion (usually CRC and the closing flag or sync character) without requiring CPU intervention.

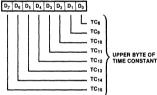

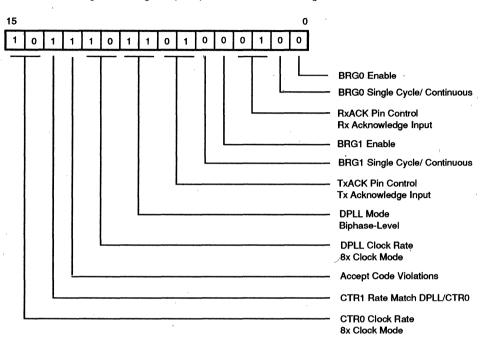

#### **Baud Rate Generators**

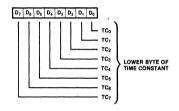

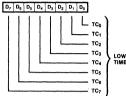

Each channel in the USC contains two baud rate generators Each generator consists of a 16-bit time constant register and a 16-bit down counter. In operation, the counter decrements with each baud rate generator clock, with the time constant automatically reloaded when the count reaches zero. The output of the baud rate generator toggles when the counter reaches a count of one-half of the time constant and again when the counter reaches zero. A new time constant may be written at any time but the new value will not take effect until the next load of the counter. The outputs of both baud rate generators are sent to the clock multiplexer for use internally or externally. The baud rate generator output frequency by the following formula

> Output frequency = Input frequency/(time constant + 1)

This allows an output frequency in the range of 1 to 1/65536 of the input frequency, inclusive.

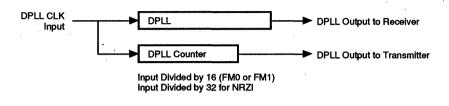

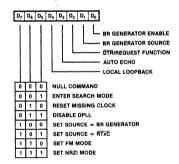

## **Digital Phase-Locked Loop**

Each channel in the USC contains a Digital Phase-Locked Loop (DPLL) to recover clock information from a data stream with NRZI or Biphase encoding. The DPLL is driven by a clock that is nominally 8, 16 or 32 times the receive data rate. The DPLL uses this clock, along the data stream, to construct a clock for the data. This clock may then be routed to the receiver, transmitter, or both, or to a pin for use externally. In all modes, the DPLL counts the input clock to create nominal bit times. As the clock is counted, the DPLL watches the incoming data stream for transitions. Whenever a transition is detected, the DPLL makes a count adjustment (during the next counting cycle), to produce an output clock which tracks the incoming bit cells. The DPLL provides properly phased transmit and receive clocks to the clock multiplexer.

#### Counters

Each channel contains two 5-bit counters, which are programmed to divide an input clock by 4, 8, 16 or 32. The

## **I/O INTERFACE CAPABILITIES**

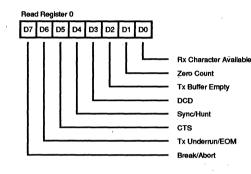

The USC offers the choice of polling, interrupt (vectored or non-vectored) and block transfer modes to transfer data, status and control information to and from the CPU.

# Polling

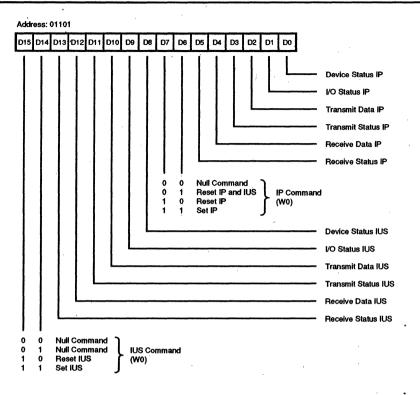

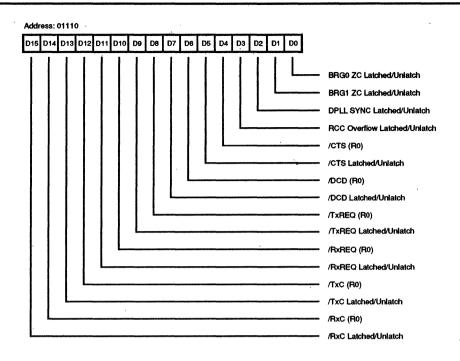

All interrupts are disabled. The registers in the USC are automatically updated to reflect current status. The CPU polls the Daisy Chain Control Register (DCCR) to determine status changes and then reads the appropriate status register to find and respond to the change in status. USC status bits are grouped according to function to simplify this software action.

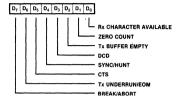

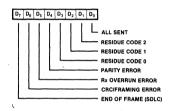

# Interrupt

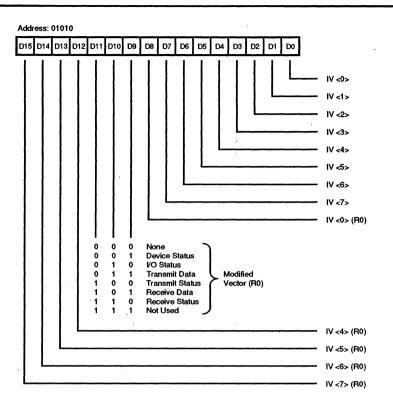

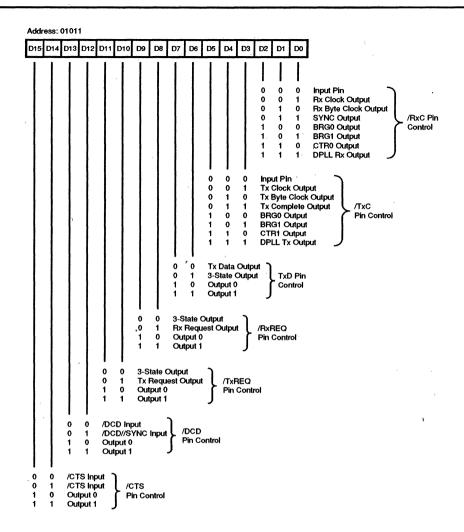

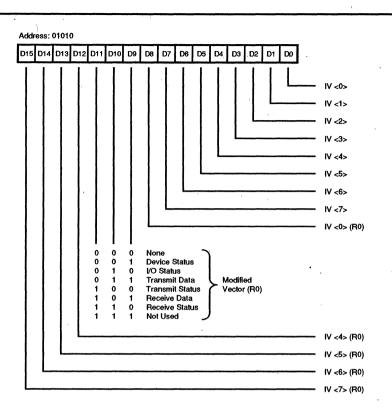

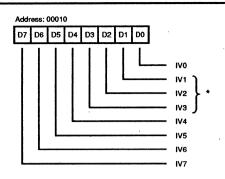

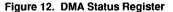

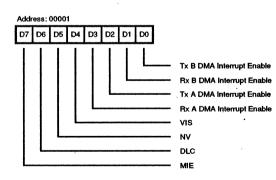

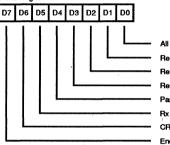

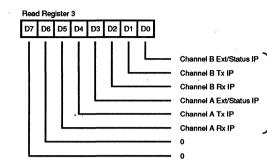

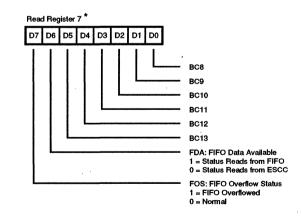

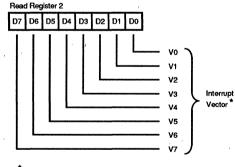

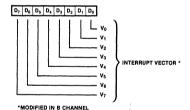

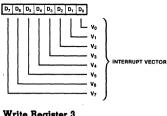

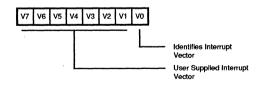

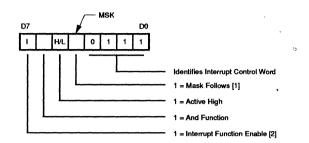

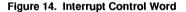

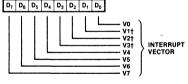

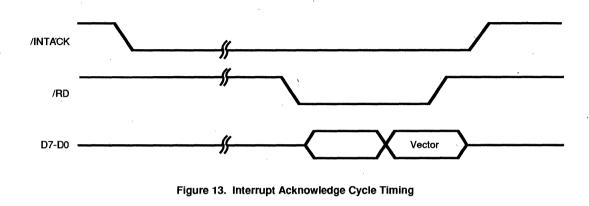

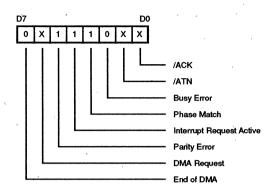

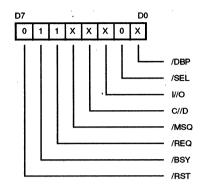

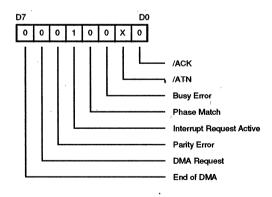

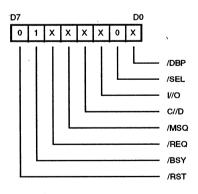

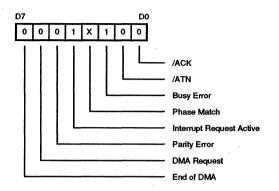

When a USC responds to an interrupt acknowledge from the CPU, an interrupt vector may be placed on the data bus. This vector is held in the Interrupt Vector Register (IVR). To speed interrupt response time, the USC modifies three bits in this vector to indicate which type of interrupt is being requested.

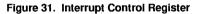

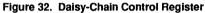

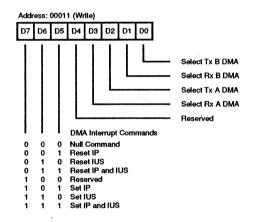

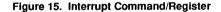

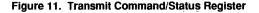

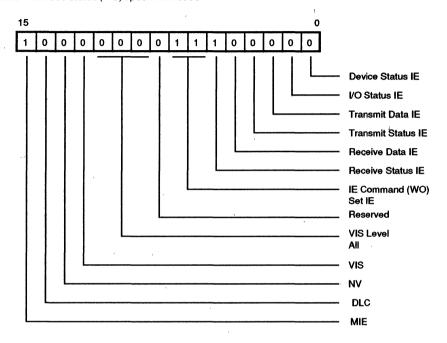

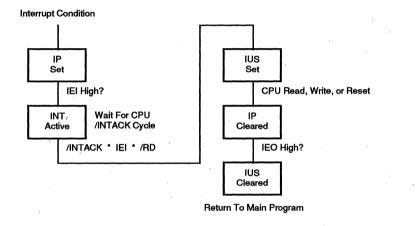

Each of the six sources of interrupts in each channel of the USC (Receive Status, Receive Data, Transmit Status, Transmit Data, I/O Status and Device Status) has three bits associated with the interrupt source: Interrupt Pending (IP), Interrupt-Under-Service (IUS) and Interrupt Enable (IE). If the IE bit for a given source is set, that source can request interrupts. Note that individual sources within the

inputs of these two counters are sent to the clock multiplexer. The counters are used as prescalers for the baud rate generators, or to provide a stable transmit clock from a common source when the DPLL is providing the receive clock.

# **Clock Multiplexer**

The clock multiplexer in each channel selects the clock source for the various blocks in the channel and selects an internal clock signal to potentially be sent to either the /RxC or /TxC pin.

# Test Modes

The USC is programmed for local loopback or auto echo operation. In local loopback, the output of the transmitter is internally routed to the input of the receiver. This allows testing of the USC data paths without any external logic. Auto echo connects the RxD pin directly to the TxD pin. This is useful for testing serial links external to the USC.

six groups also have interrupt enable bits which are set for the particular source. In addition, there is a Master Interrupt Enable (MIE) bit in each channel which globally enables or disables interrupts within the channel.

The other two bits are related to the interrupt priority chain: A channel in the USC may request an interrupt only when no higher priority interrupt source is requesting one, e g., when IEI is High for the channel. In this case the channel activates the /INT signal. The CPU then responds with an interrupt acknowledge cycle, and the interrupting channel places a vector on the data bus.

In the USC, the IP bit signals that an interrupt request is being serviced. If an IUS is set, all interrupt sources of lower priority within the channel and external to the channel are prevented from requesting interrupts. The internal interrupt sources are inhibited by the state of the internal daisy chain, while lower priority devices are inhibited by the IEO output of the channel being pulled Low and propagated to subsequent peripherals. An IUS bit is set during an interrupt acknowledge cycle if there are no higher priority devices requesting interrupts.

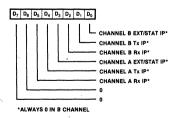

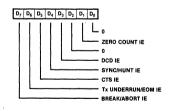

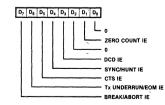

There are six sources of interrupt in each channel Receive Status, Receive Data, Transmit Status, Transmit Data, I/O Status and Device Status, prioritized in that order within the channel There are six sources of Receive Status interrupt, each individually enabled: exited hunt, idle line, break/ abort, code violation/end-of-transmission/end-of-frame, parity error and overrun error. The Receive Data interrupt is generated whenever the receive FIFO fills with data beyond the level programmed in the Receive Interrupt Control Register (RICR).

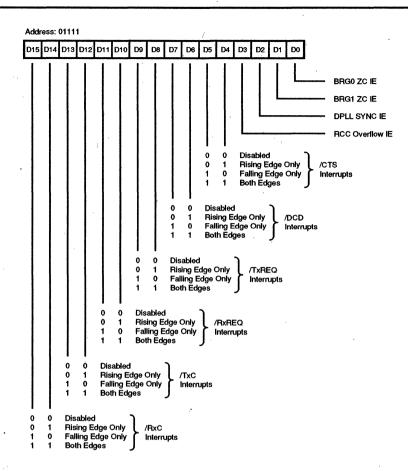

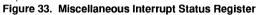

There are six sources of Transmit Status interrupt, each individually enabled: preamble sent, idle line sent, abort sent, end-of-frame/end-of-transmission sent, CRC sent and underrun error. The Transmit Data interrupt is generated whenever the transmit FIFO empties below the level programmed in the Transmit Interrupt Control Register (TICR). The I/O Status interrupt serves to report transitions on any of six pins. Interrupts are generated on either or both edges with separate selection and enables for each pin. The pins programmed to generate I/O Status interrupts are /RxC, /TxC, /RxREQ, /TxREQ, /DCD and /CTS. These interrupts are independent of the programmed function of the pins. The Device Status interrupt has four separately enabled sources: receive character count FIFO overflow, DPLL sync acquired, BRG1 zero count and BRGO zero count.

#### Block Transfer Mode

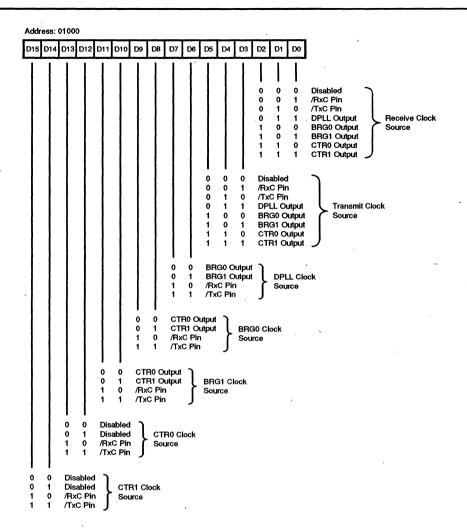

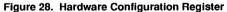

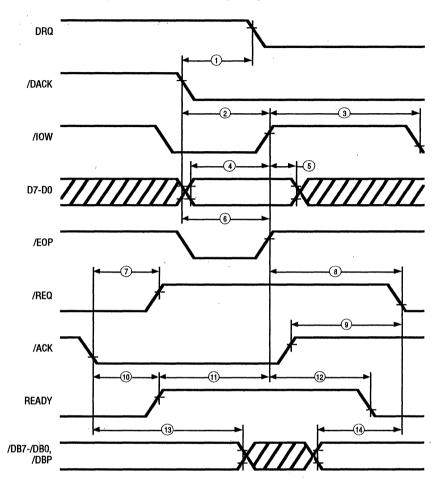

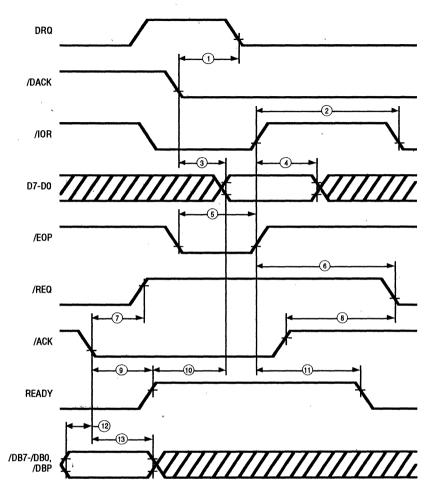

The USC accommodates block transfers via DMA through the /RxREQ, /TxREQ, /RxACK and /TxACK pins. The /RxREQ signal is activated when the fill level of the receive FIFO exceeds the value programmed in the RICR. The DMA may respond with either a normal bus transaction or by activating the /RxACK pin to read the data directly (flyby transfer). The /TxREQ signal is activated when the empty level of the transmit FIFO falls below the value programmed in the TICR. The DMA may respond either with a normal bus transaction or by activating the /TxACK pin to write the data directly (fly-by transfer). The /RxACK and /TxACK pin functions for this mode are controlled by the Hardware Configuration Register (HCR). Then using the /RxACK and /TxACK pins to transfer data, no chip select is necessary; these are dedicated strobes for the appropriate FIFO.

#### PROGRAMMING

The Programmers Assistant (MS DOS based) and Technical Manual are available to provide details about programmming the USC. Also included are explanations and features of all registers in the USC

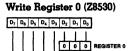

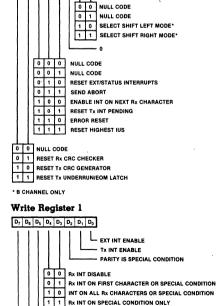

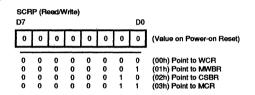

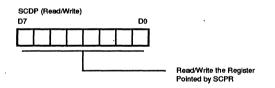

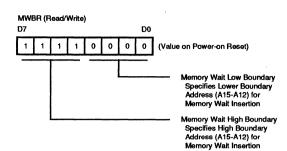

The registers in each USC channel are programmed by the system to configure the channels. Before this can occur, however, the system must program the bus interface by writing to the Bus Configuration Register (BCR). The BCR has no specific address and is only accessible immediately after a hardware reset of the device. The first write to the USC, after a hardware reset, programs the BCR. From that time on the normal channel registers may be accessed. No specific address need be presented to the USC for the BCR write; the USC knows that the first write after a hardware reset is destined for the BCR.

In the multiplexed bus case, all registers are directly addressable via the address latched by /AS at the beginning of a bus transaction. The address is decoded from either AD6-AD0 or AD7-AD1. This is controlled by the Shift Right/ Shift Left bit in the BCR. The address maps for these two cases are shown in Table 1. The D//C pin is still used to directly access the receive and transmit data registers (RDR and TDR) in the multiplexed bus; if D//C is High the address latched by /AS is ignored and an access of RDR or TDR is performed.

In the non-multiplexed bus case, the registers in each channel are accessed indirectly using the address pointer in the Channel Command/Address Register (CCAR) in each channel. The address of the desired register is first

written to the CCAR and then the selected register is accessed; the pointer in the CCAR is automatically cleared after this access. The RDR and TDR are accessed directly using the D//C pin, without disturbing the contents of the pointer in the CCAR.

#### Table 1. Multiplexed Bus Address Assignments

| Address Signal           | Shift Left | Shift Right |

|--------------------------|------------|-------------|

| Byte//Word Access        | AD7        | AD6         |

| Address 4                | AD6        | AD5         |

| Address 3                | AD5        | AD4         |

| Address 2                | AD4        | AD3         |

| Address 1                | AD3        | AD2         |

| Address 0                | AD2        | AD1         |

| Upper//Lower Byte Select | AD1        | AD0         |

There are two important things to note about the USC. First, the Channel Reset bit in the CCAR places the channel in the reset state. To exit this reset state either a word of all zeros must be written to the CCAR (16-bit bus) or a byte of all zeros must be written to the lower byte of the CCAR (8-bit bus). The second thing to note is that after reset, the transmit and receive clocks are not connected. The first thing that should be done in any initialization sequence is a write to the Clock Mode Control Register (CMCR) to select a clock source for the receiver and transmitter.

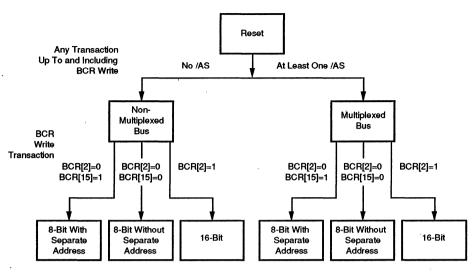

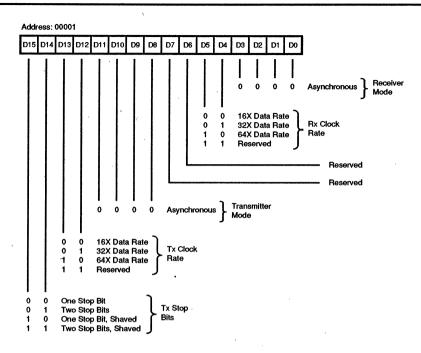

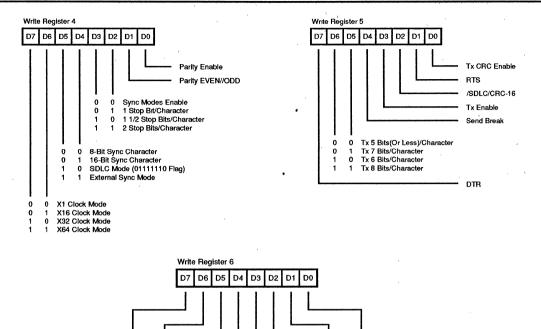

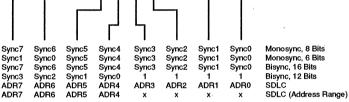

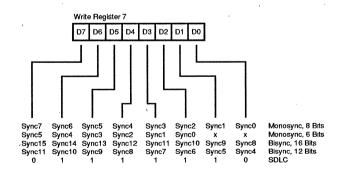

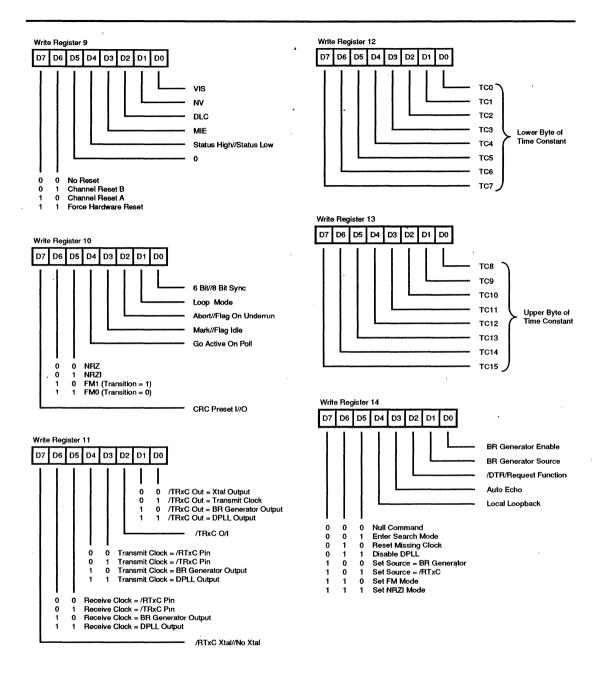

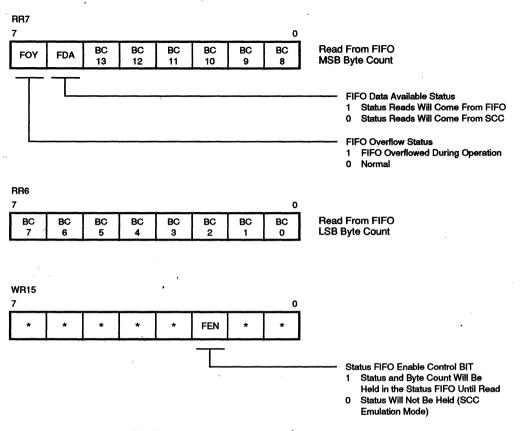

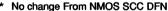

The register addressing is shown in Table 2. and the bit assignments for the registers are shown in Figure 6.

Note:

The presence of one transaction with an /AS active, between reset up to and including the BCR write, chooses a multiplexed type of bus.

| Address<br>A4-AØ | <b>;</b> |                                   | Address<br>A4-AØ | 3    | -                                   |

|------------------|----------|-----------------------------------|------------------|------|-------------------------------------|

| 00000            | CCAR     | Channel Command/Address Register  | 10010            | RCSR | Receive Command/Status Register     |

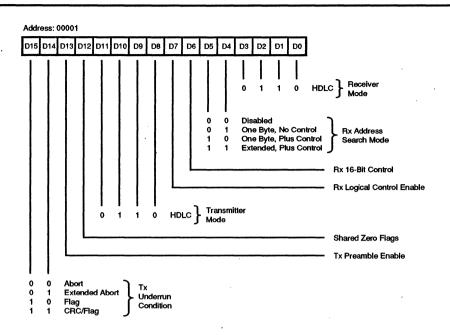

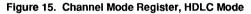

| 00001            | CMR      | Channel Mode Register             | 10011            | RICR | Receive Interrupt Control Register  |

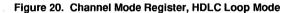

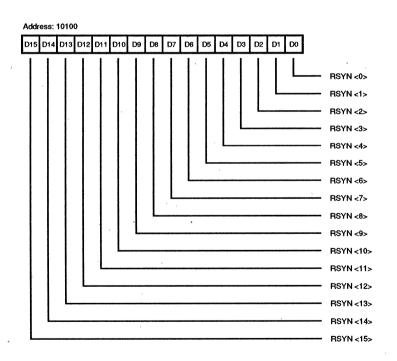

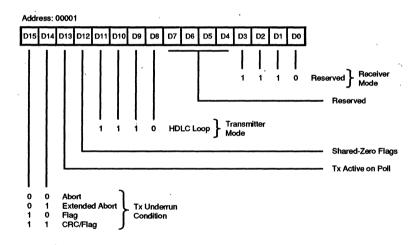

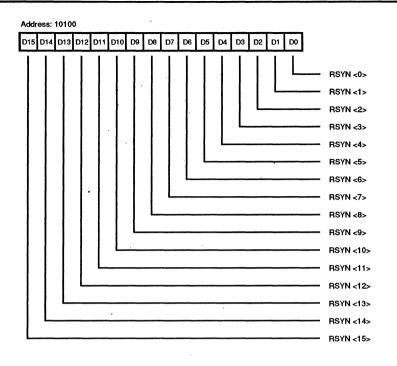

| 00010            | CCSR     | Channel Command/Status Register   | 10100            | RSR  | Receive Sync Register               |

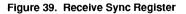

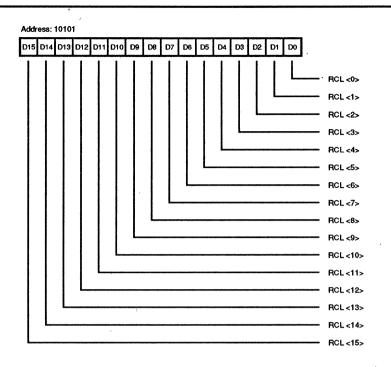

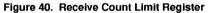

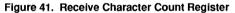

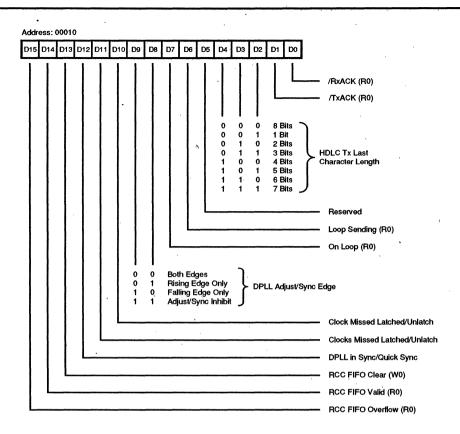

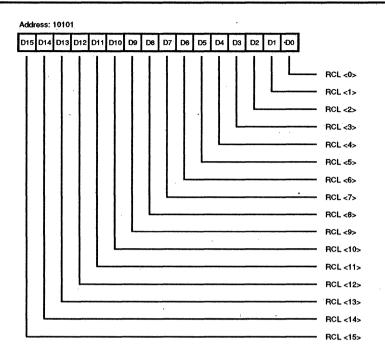

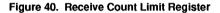

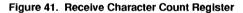

| 00011            | CCR      | Channel Control Register          | 10101            | RCLR | Receive Count Limit Register        |

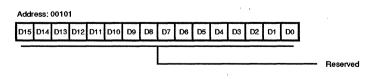

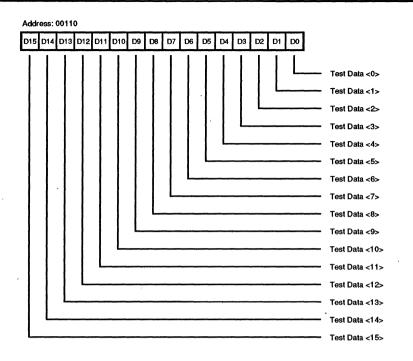

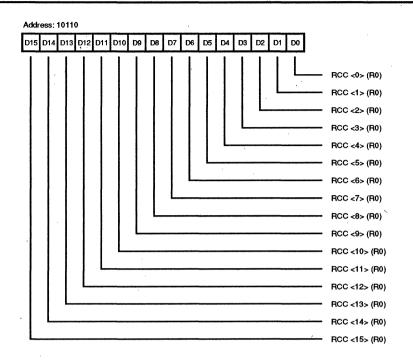

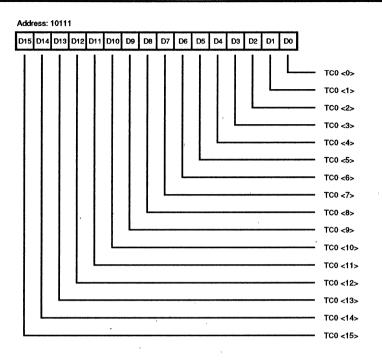

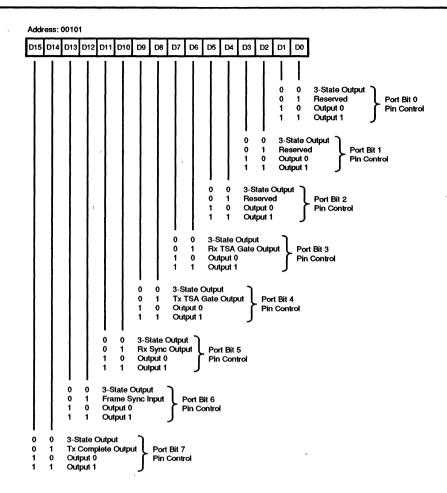

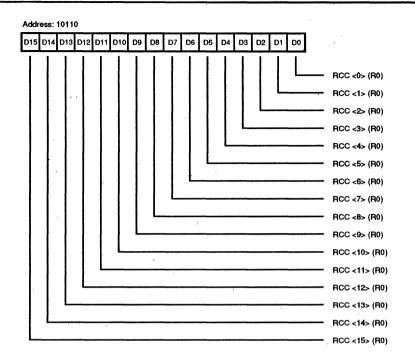

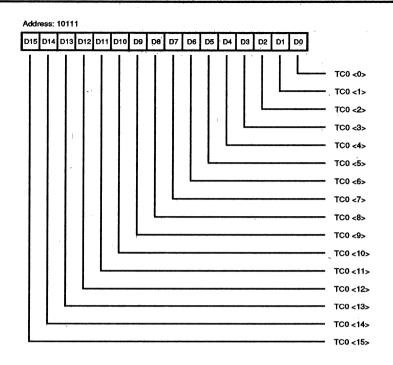

| 00110            | TMDR     | Test Mode Data Register           | 10110            | RCCR | Recieve Character Count Register    |

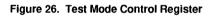

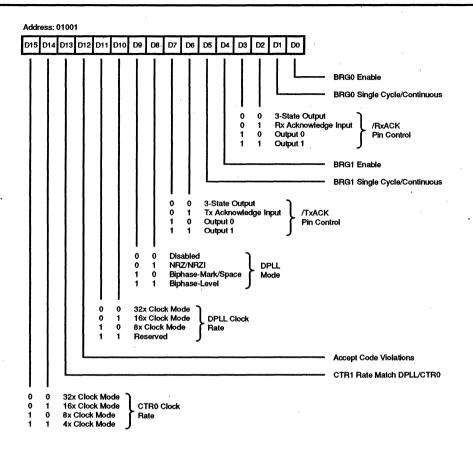

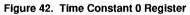

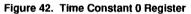

| 00111            | TMCR     | Test Mode Control Register        | 10111            | TCOR | Time Constant 0 Register            |

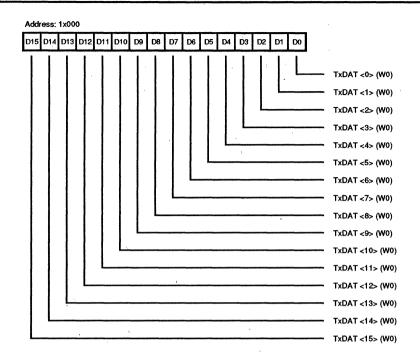

| 01000            | CMCR     | Clock Mode Control Register       | 1X000            | TDR  | Transmit Data Register (Write Only) |

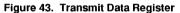

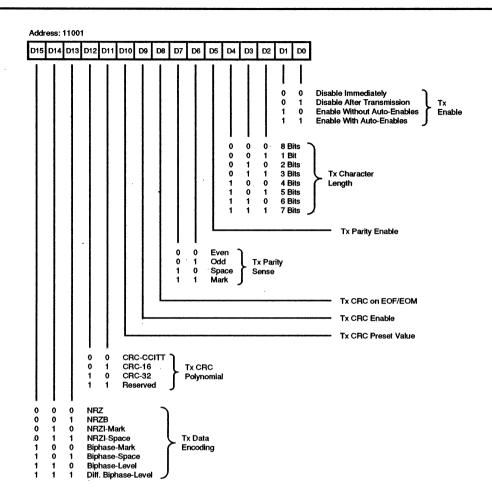

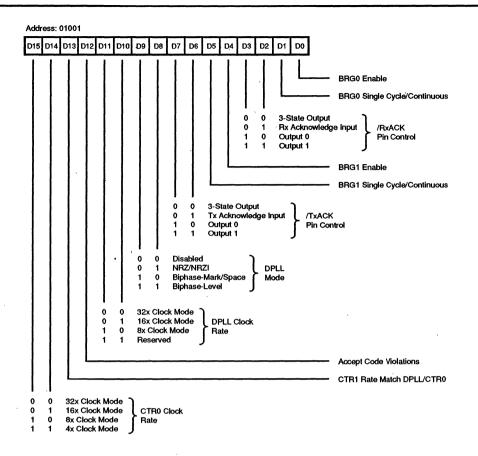

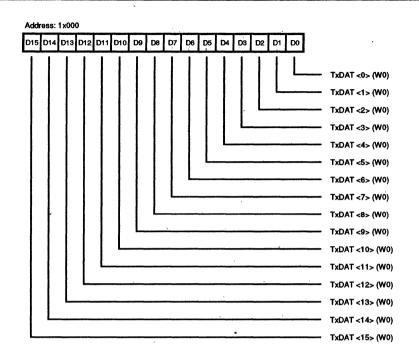

| 01001            | HCR      | Hardware Configuration Register   | 11001            | TMR  | Transmit Mode Register              |

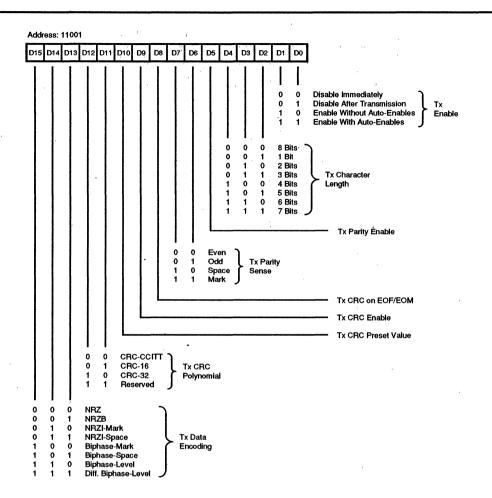

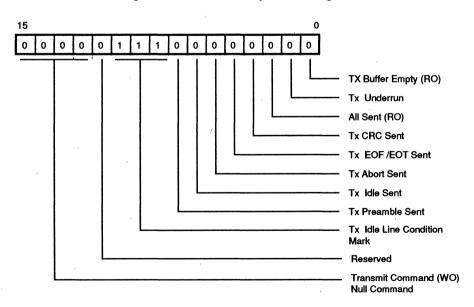

| 01010            | IVR      | Interrupt Vector Register         | 11010            | TCSR | Transmit Command/Status Register    |

| 01011            | IOCR     | I/O Control Register              | 11011            | TICR | Transmit Interrupt Control Register |

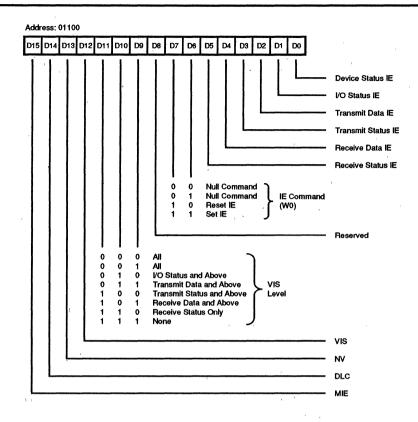

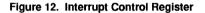

| 01100            | ICR      | Interrupt Control Register        | 11100            | TSR  | Transmit Sync Register              |

| 01101            | DCCR     | Daisy-Chain Control Register      | 11101            | TCLR | Transmit Count Limit Register       |

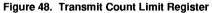

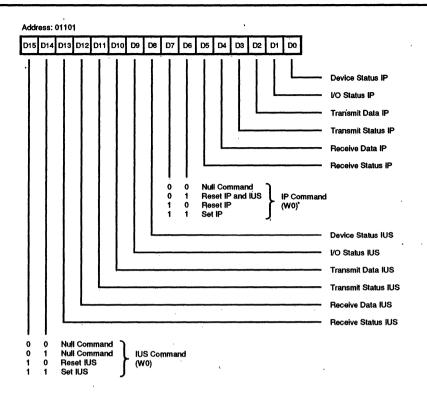

| 01110            | MISR     | Misc Interrupt Status Register    | 11110            | TCCR | Transmit Character Count Register   |

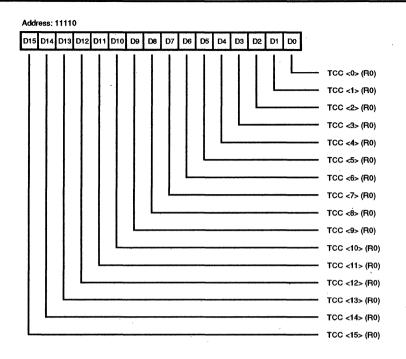

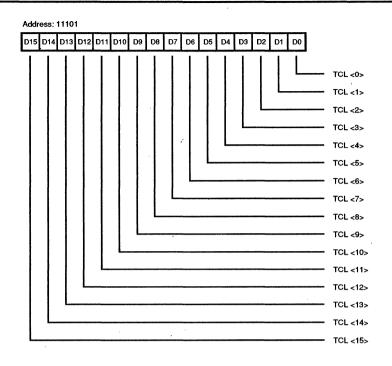

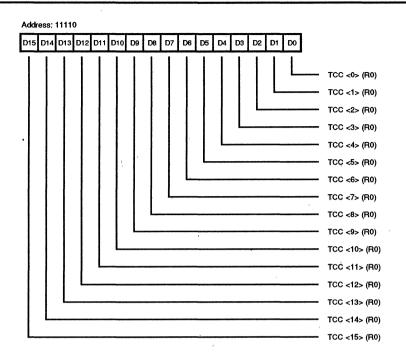

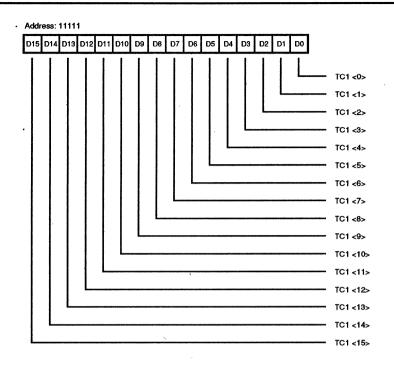

| 01111            | SICR     | Status Interrupt Control Register | 11111            | TC1R | Time Constant 1 Register            |

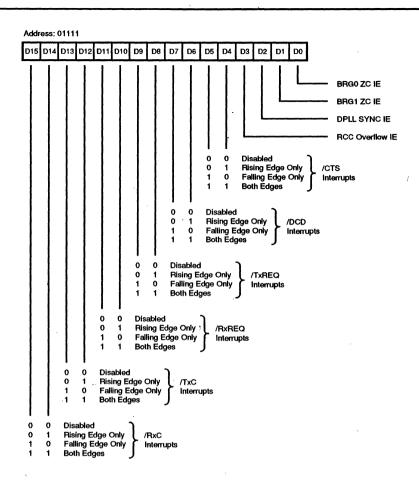

| 1X00Ò            | RDR      | Receive Data Register (Read Only) |                  |      | 4 E                                 |

| 10001            | RMR      | Receive Mode Register             | XXXXX            | BCR  | Bus Configuration Register          |

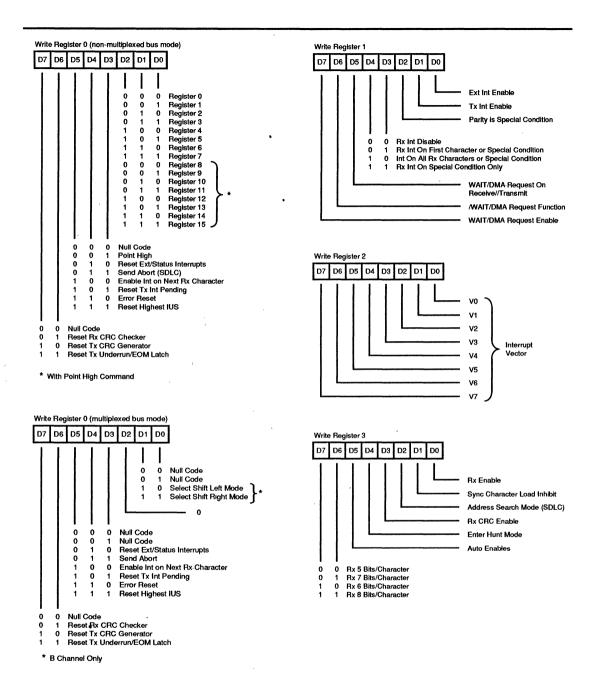

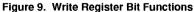

# **CONTROL REGISTERS**

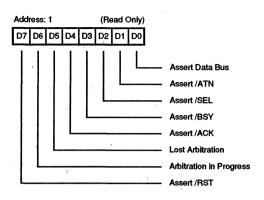

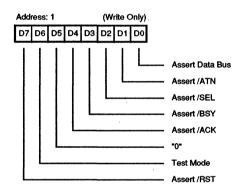

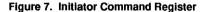

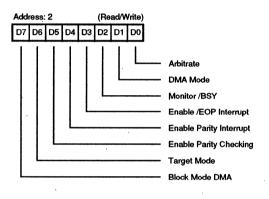

Figure 7. Channel Command/Address Register

• 1

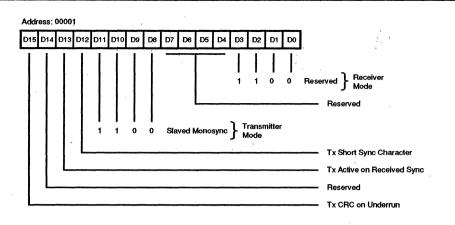

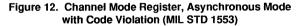

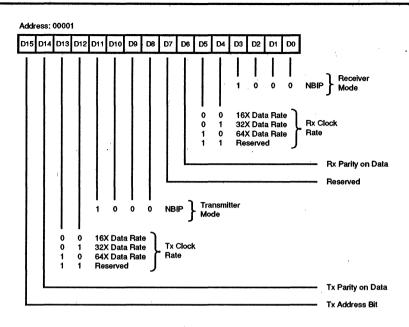

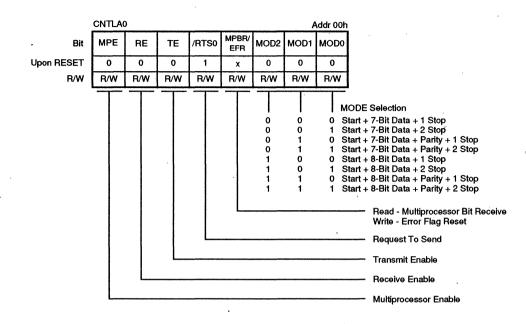

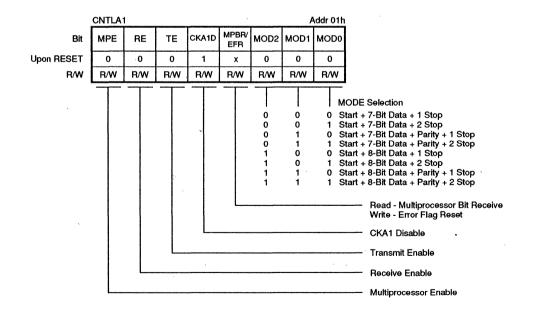

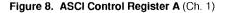

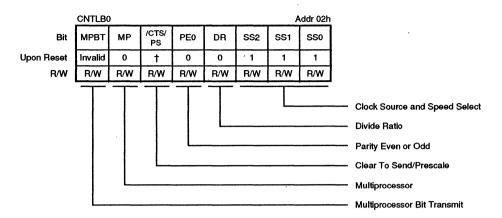

Figure 9. Channel Mode Register, Asynchronous Mode

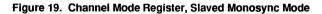

Figure 13. Channel Mode Register, Monosync Mode

Figure 14. Channel Mode Register, Bisync Mode

Figure 16. Channel Mode Register, Transparent Bisync Mode

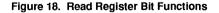

Figure 18. Channel Mode Register, 802.3 Mode

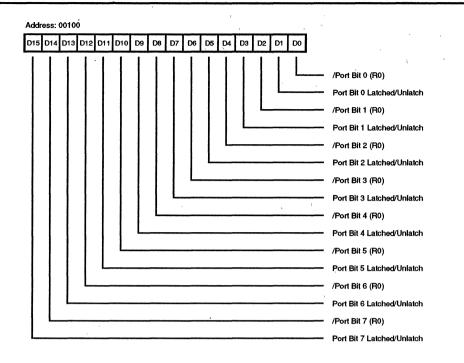

Figure 21. Channel Command/Status Register

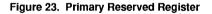

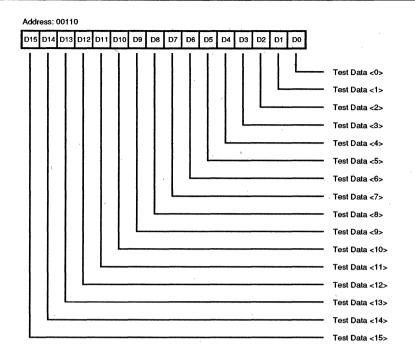

Figure 24. Secondary Reserved Register

| 5 D14 D13 D12 D11 | D10 D9 | ) D8 | D7 | D6 | D5 | D4 | D3 | D2  | D1 | DO | х с <b>т</b>                  |           |

|-------------------|--------|------|----|----|----|----|----|-----|----|----|-------------------------------|-----------|

|                   |        |      |    |    |    |    | 1  | 1   | ľ  | ], |                               |           |

|                   |        |      |    |    |    | 0  | 0  | 0   | 0  | 0  | Null Address                  | <b>`</b>  |

| х.<br>Х           |        |      |    |    |    | ō  | ō  | ·.0 | ŏ  | 1  | High Byte of Shifters         | 1         |

|                   |        |      |    |    |    | ŏ  | ŏ  | ŏ   | 1  | ò  | CRC Byte 0                    |           |

|                   |        |      |    |    |    | ō  | ō  | ō   | 1  | 1  | CRC Byte 1                    |           |

|                   |        |      |    |    |    | ō  | ō  | 1   | ò  | ò  | Rx FIFO (Write)               |           |

|                   |        |      |    |    |    | ō  | ō  | 1   | ō  | 1  | Clock Multiplexer Outputs     |           |

|                   |        |      |    |    |    | ŏ  | ŏ  | i   | Ť  | ò  | CTR0 and CTR1 Counters        |           |

|                   |        |      |    |    |    | ŏ  | ō  | 1   | i  | 1  | Clock Multiplexer Inputs      | 1         |

|                   |        |      |    |    |    | ō  | 1  | ò   | ò  | ò  | DPLL State                    |           |

|                   |        |      |    |    |    | ŏ  | 1  | ŏ   | ŏ  | 1  | Low Byte of Shifters          | 1         |

|                   |        |      |    |    |    | 0  | 1  | 0   | 1  | 0  | CRC Byte 2                    |           |

|                   |        |      |    |    |    | Ó  | 1  | Ó   | 1  | 1  | CRC Byte 3                    |           |

|                   |        |      |    |    |    | 0  | 1  | 1   | Ó  | Ó  | Tx FIFO (Read)                |           |

|                   |        |      |    |    |    | Ó  | 1  | 1   | 0  | 1  | Reserved                      | 1         |

|                   |        |      |    |    |    | 0  | 1  | 1   | 1  | 0  | I/O and Device Status Latches | 1         |

|                   |        |      |    |    |    | 0  | 1  | 1   | 1  | 1  | Internal Daisy Chain          | Test      |

|                   |        |      |    |    |    | 1  | 0  | 0   | 0  | 0  | Reserved                      | Register  |

|                   |        |      |    |    |    | 1  | 0  | 0   | 0  | 1  | Reserved                      | / Address |

|                   |        |      |    |    |    | 1  | 0  | 0   | 1  | 0  | Reserved                      | 1         |

|                   |        |      |    |    |    | 1  | 0  | 0   | 1  | 1  | Reserved                      |           |

|                   |        |      |    |    |    | 1  | 0  | 1   | 0  | 0  | Reserved                      |           |

|                   |        |      |    |    |    | 1  | 0  | 1   | 0  | 1  | Reserved                      |           |

|                   |        |      |    |    |    | 1  | 0  | 1   | 1  | 0  | Rx Count Holding Register     |           |

|                   |        |      |    |    |    | 1  | 0  | 1   | 1  | 1  | Reserved                      |           |

|                   |        |      |    |    |    | 1  | 1  | 0   | 0  | 0  | Reserved                      |           |

|                   | •      |      |    |    |    | 1  | 1  | 0   | 0  | 1  | Reserved                      |           |

|                   |        |      |    |    |    | 1  | 1  | 0   | 1  | 0  | Reserved                      |           |

|                   |        |      |    |    |    | 1  | 1  | 0   | 1  | 1  | Reserved                      |           |

|                   |        |      |    |    |    | 1  | 1  | 1   | 0  | 0  | Reserved                      |           |

| '                 |        |      |    |    |    | 1  | 1  | 1   | 0  | 1  | Reserved                      | 1         |

|                   |        |      |    |    |    | 1  | 1  | 1   | 1  | 0  | Reserved                      | 1         |

|                   |        |      |    |    |    | 1  | 1  | 1   | 1  | 1  | Reserved                      | /         |

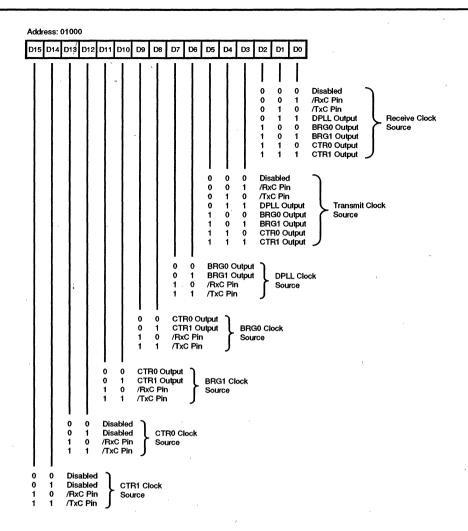

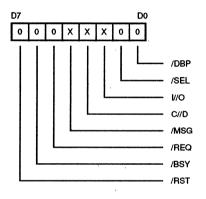

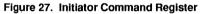

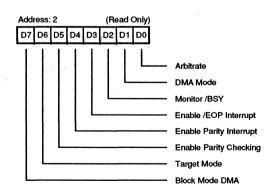

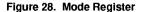

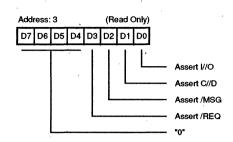

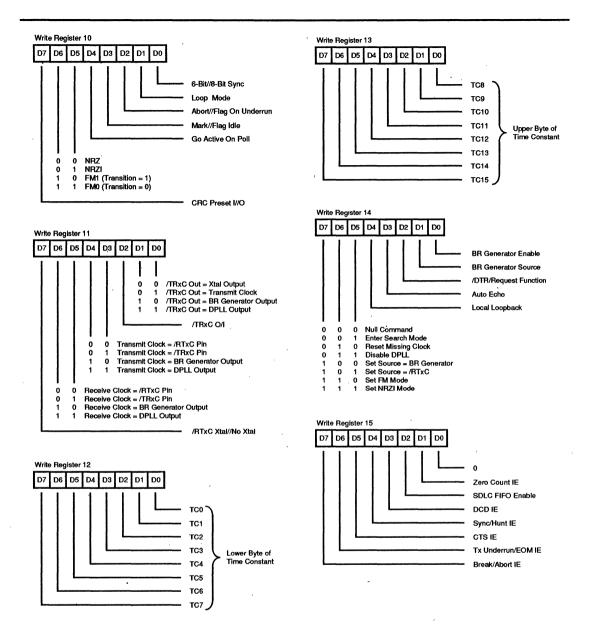

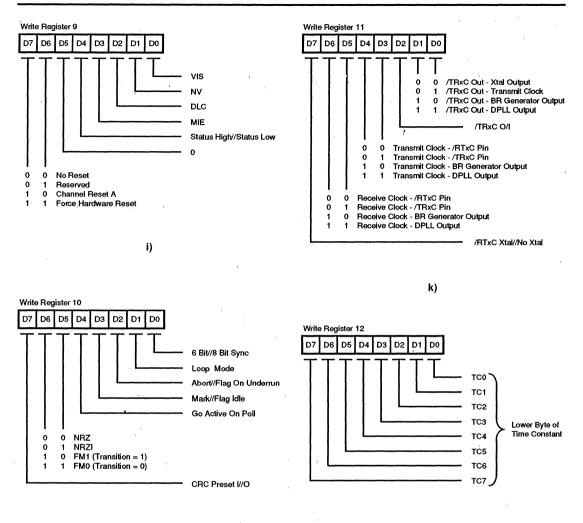

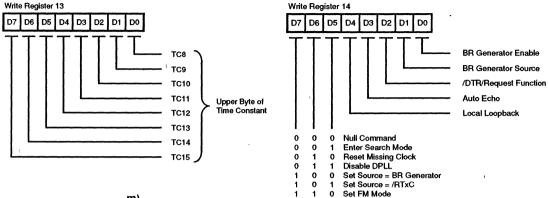

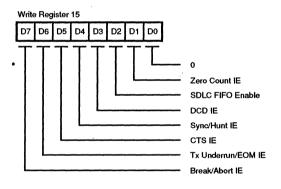

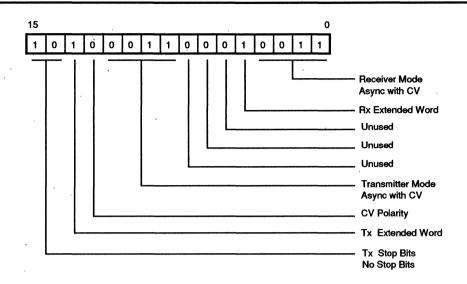

Figure 27. Clock Mode Control Register

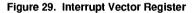

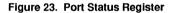

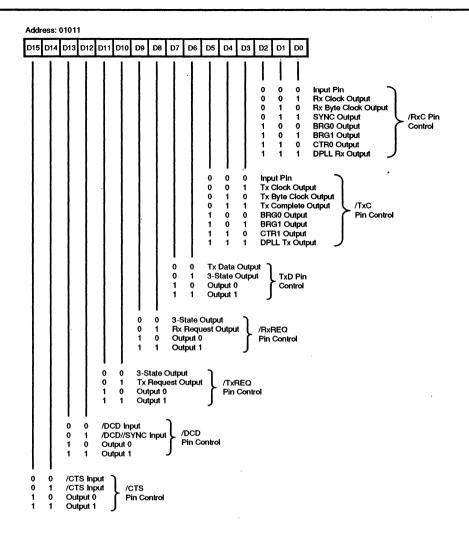

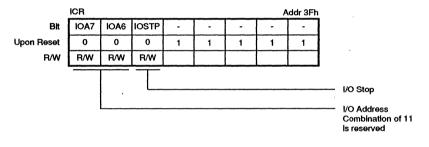

Figure 30. I/O Control Register

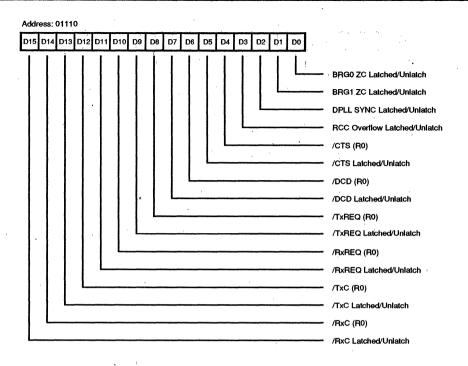

Figure 33. Miscellaneous Interrupt Status Register

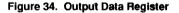

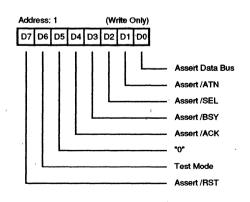

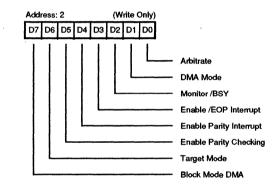

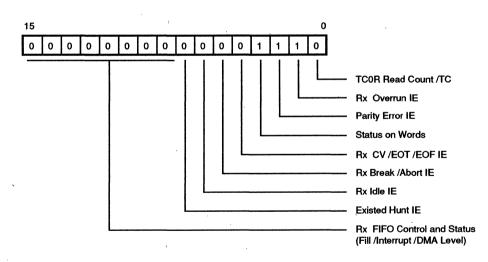

Figure 34. Status Interrupt Control Register

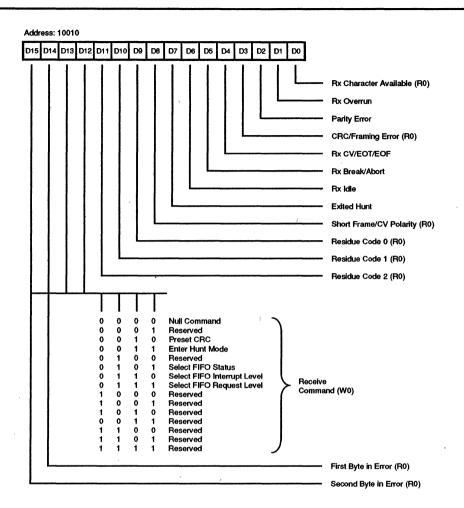

Figure 37. Receive Command Status Register

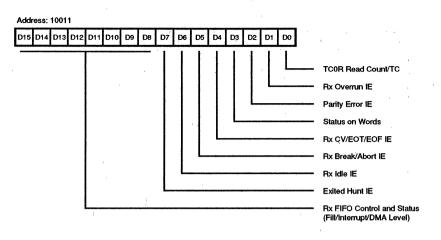

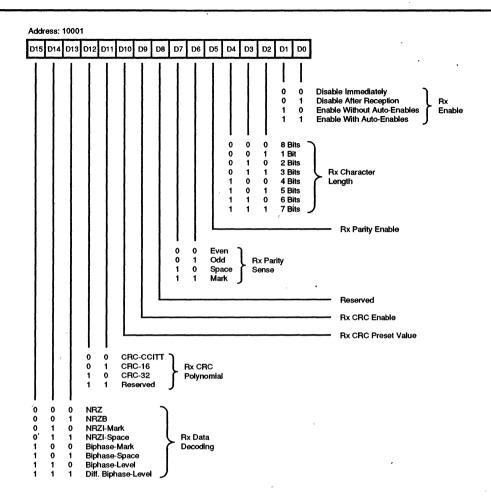

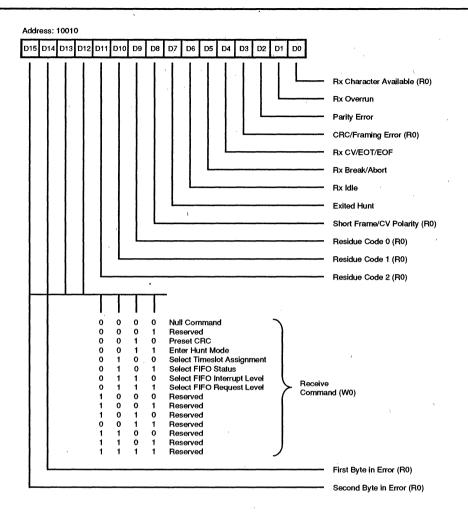

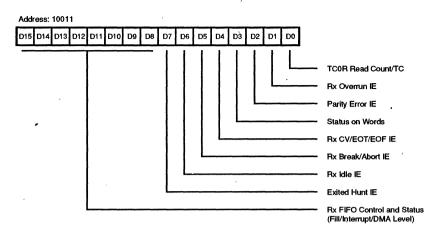

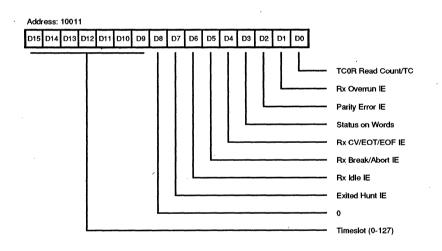

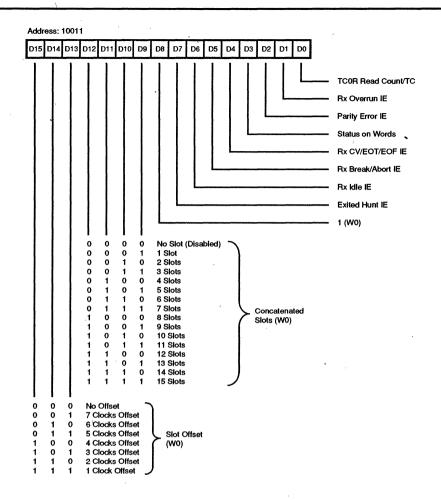

Figure 38. Receive Interrupt Control Register

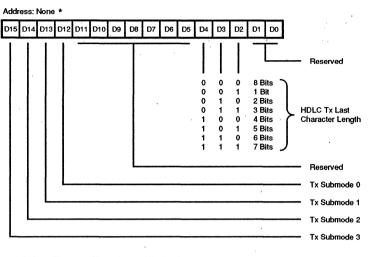

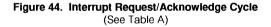

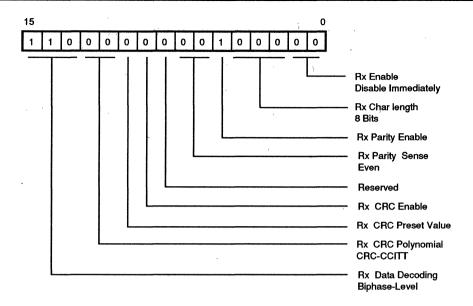

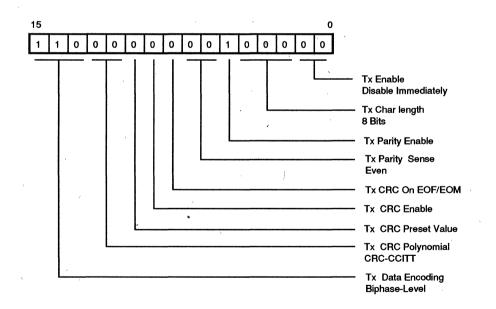

Figure 44. Transmit Mode Register

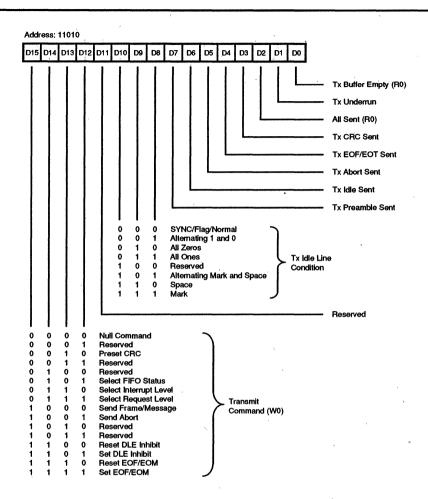

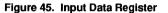

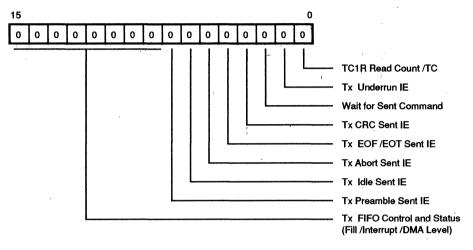

Figure 45. Transmit Command/Status Register

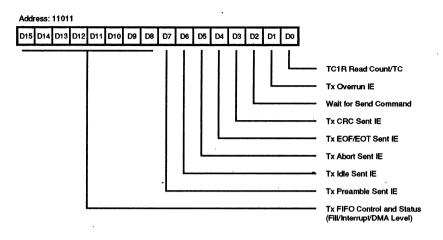

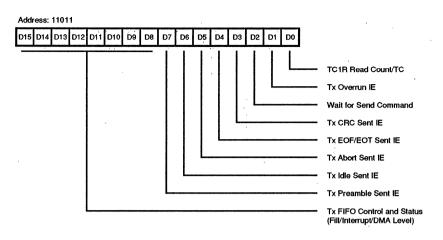

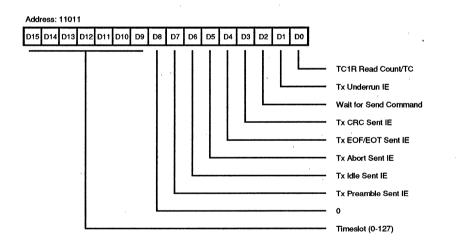

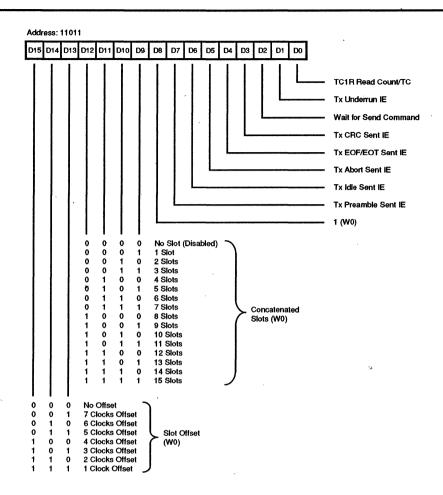

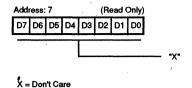

Figure 46. Transmit Interrupt Control Register

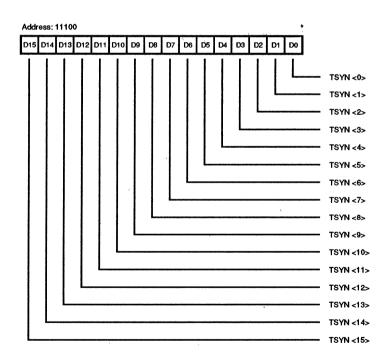

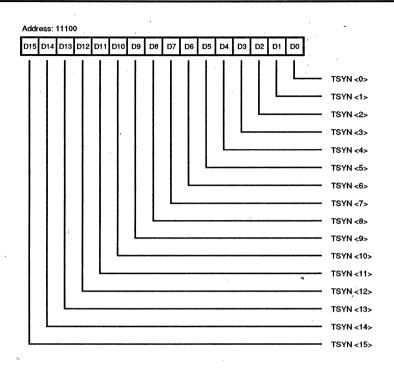

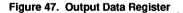

Figure 47. Transmit Sync Register

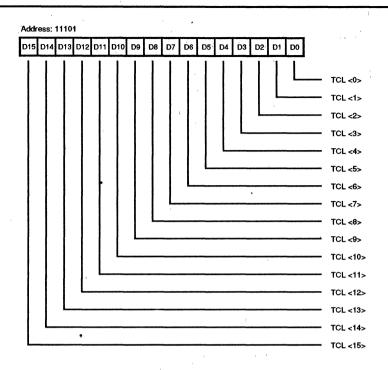

Figure 49. Transmit Character Count Register

\* Refer to Figure 22 (Channel Control Register) Bits 6-7 for Access Method

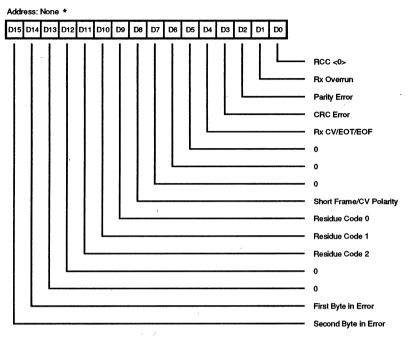

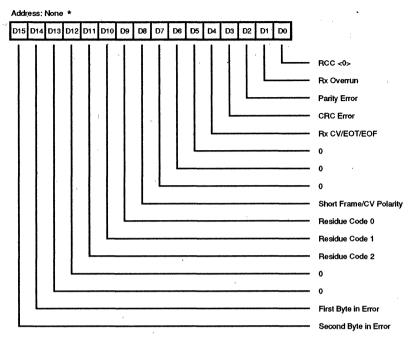

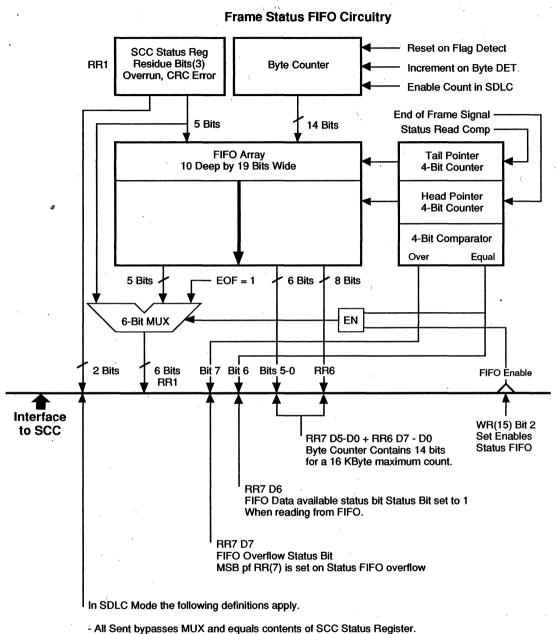

Figure 51. Receive Status Block Register

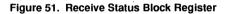

\* Refer to Figure 22 (Channel Control Register) Bits15-14 for Access Method

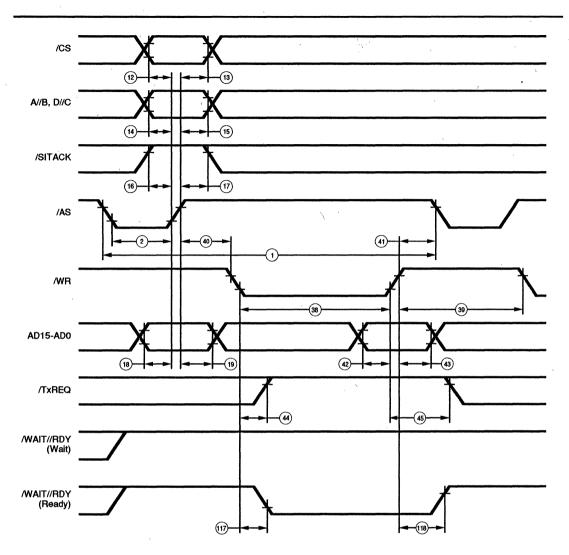

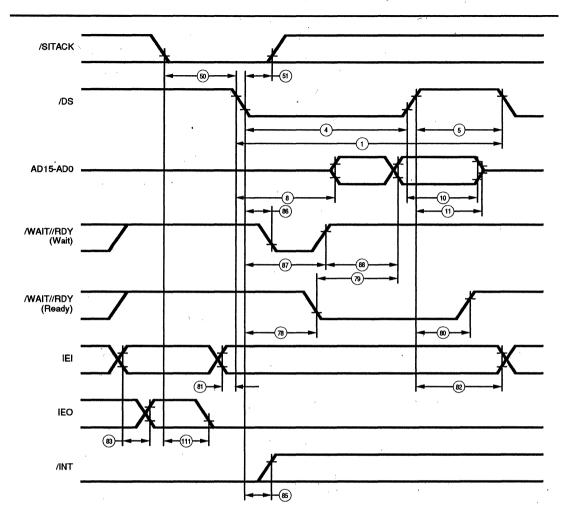

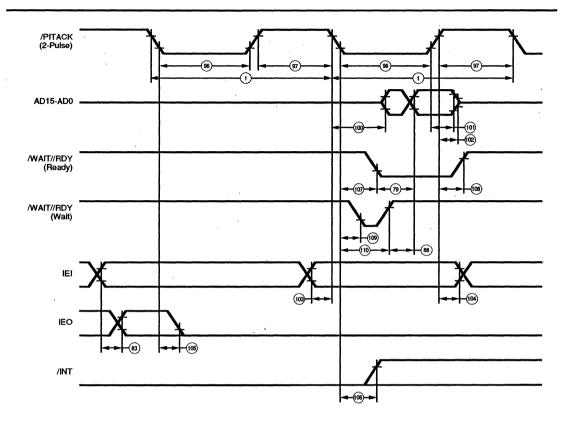

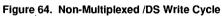

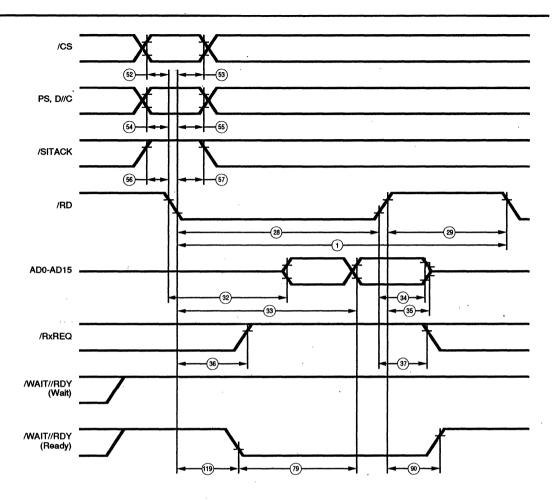

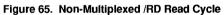

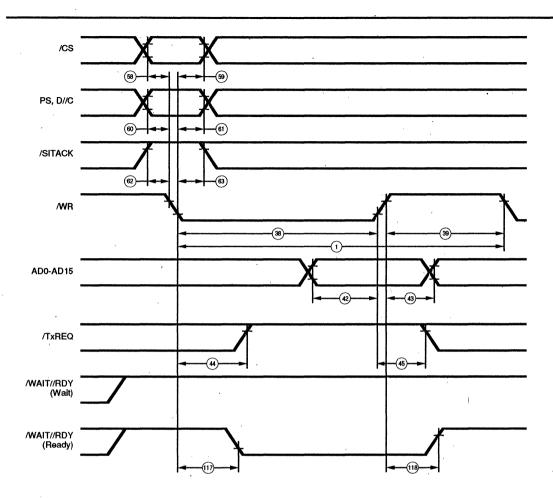

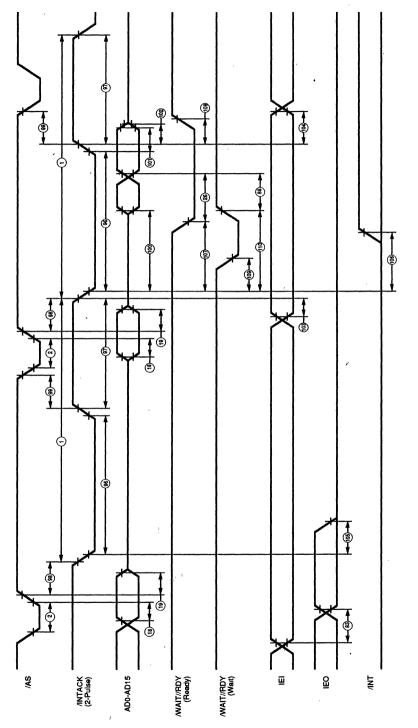

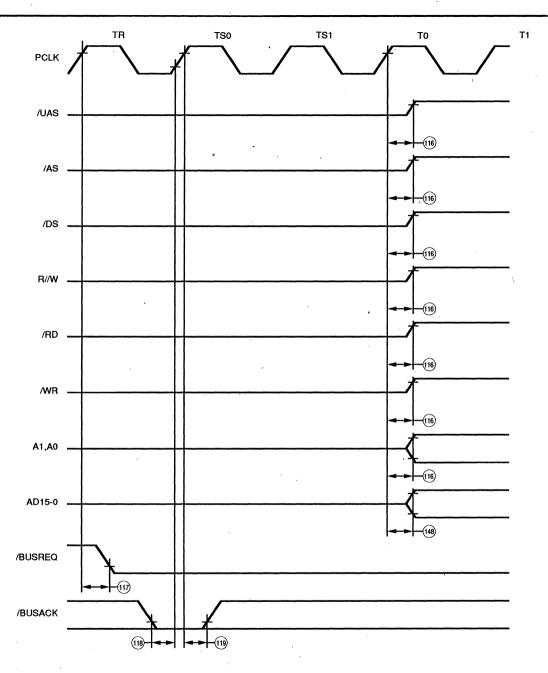

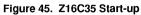

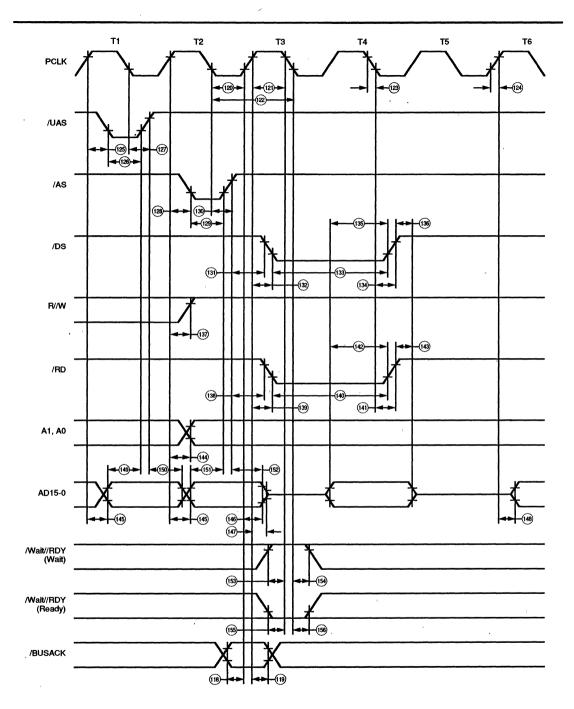

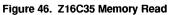

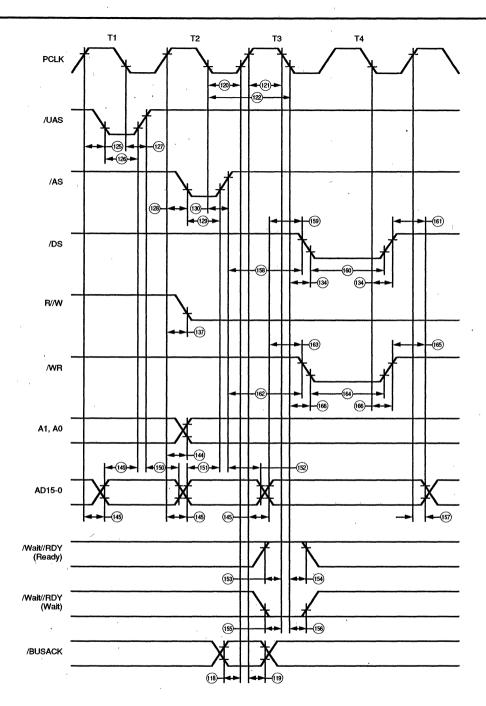

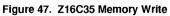

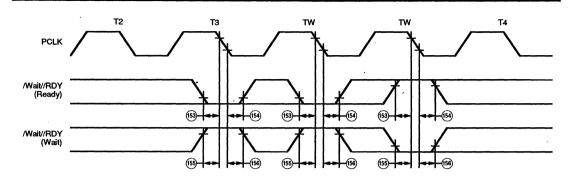

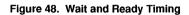

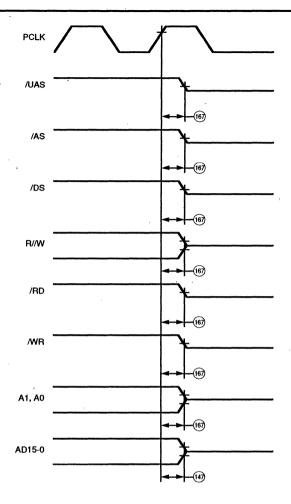

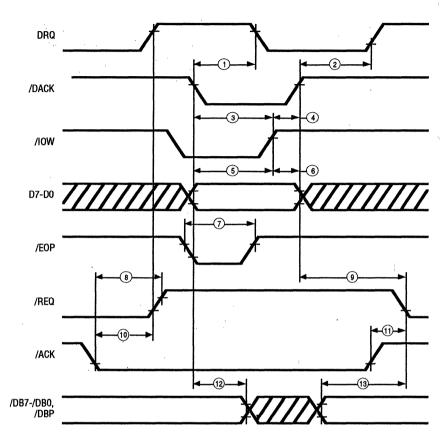

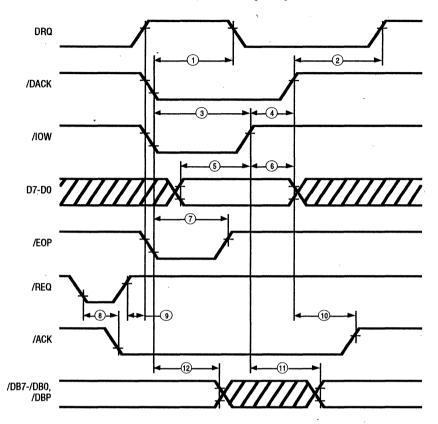

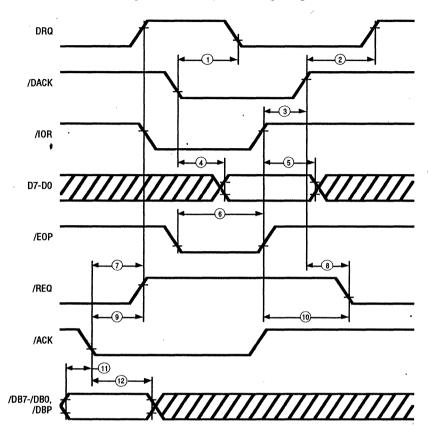

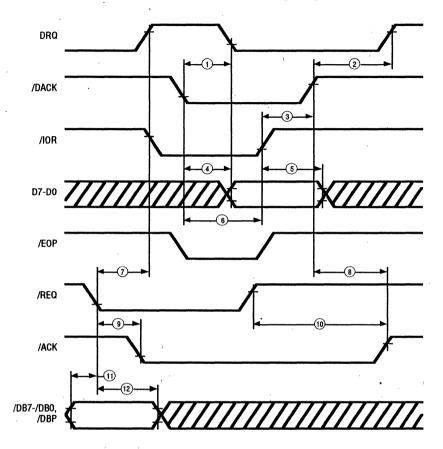

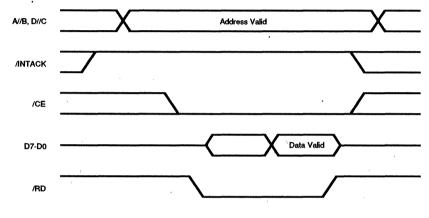

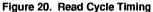

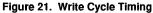

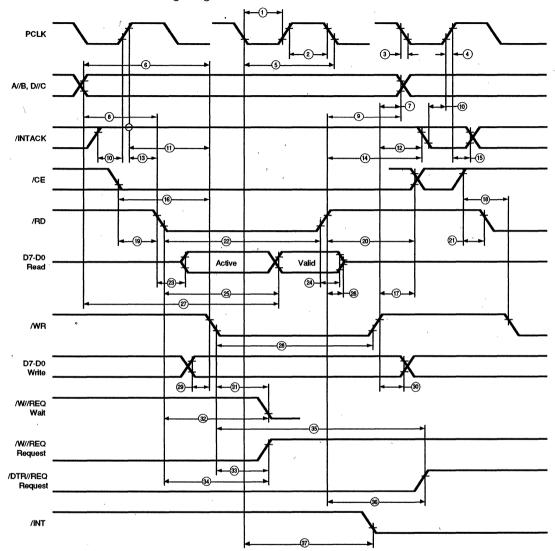

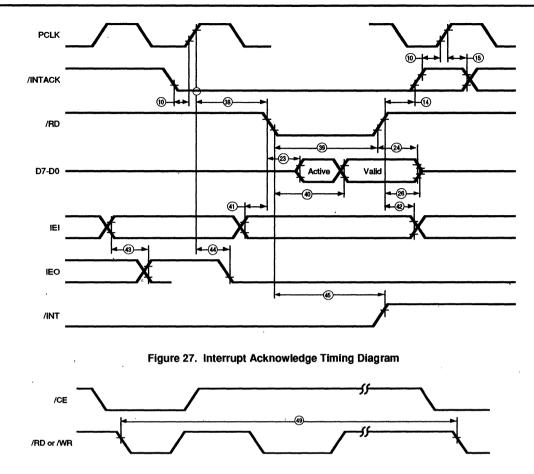

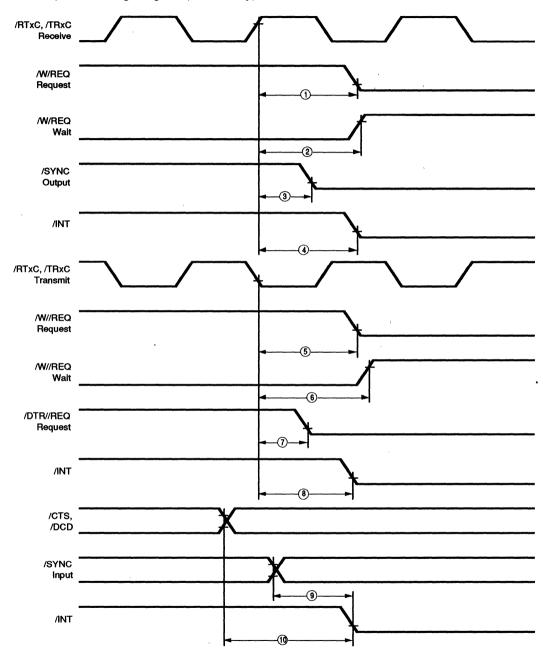

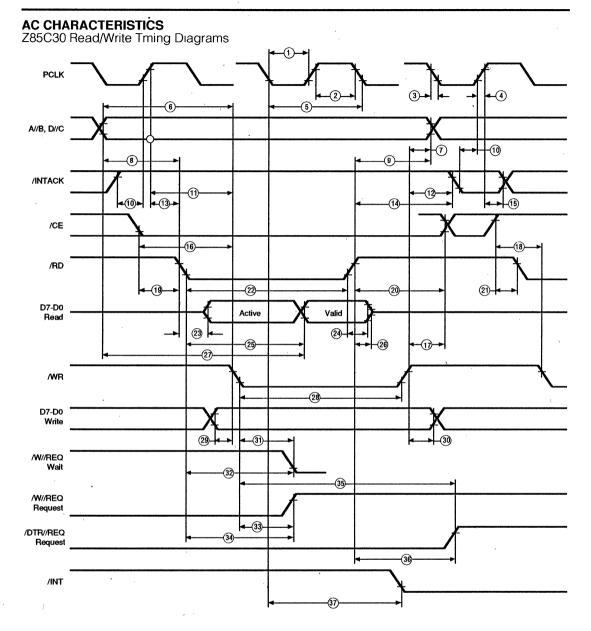

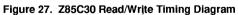

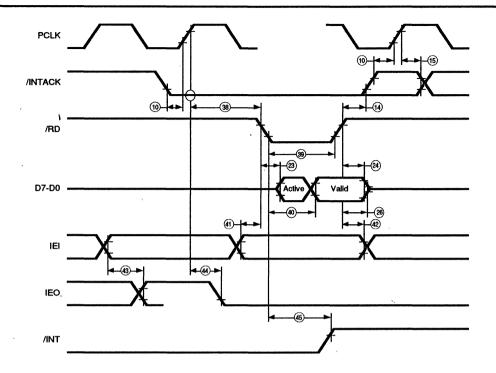

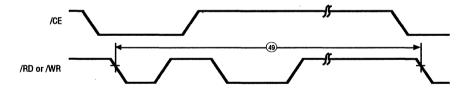

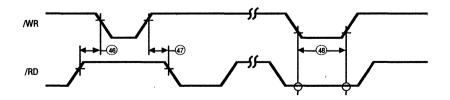

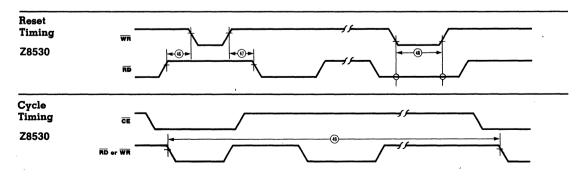

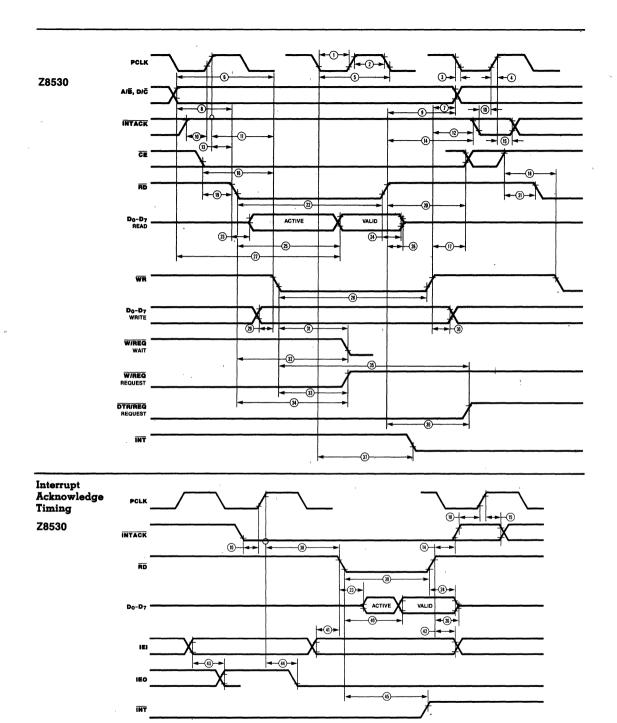

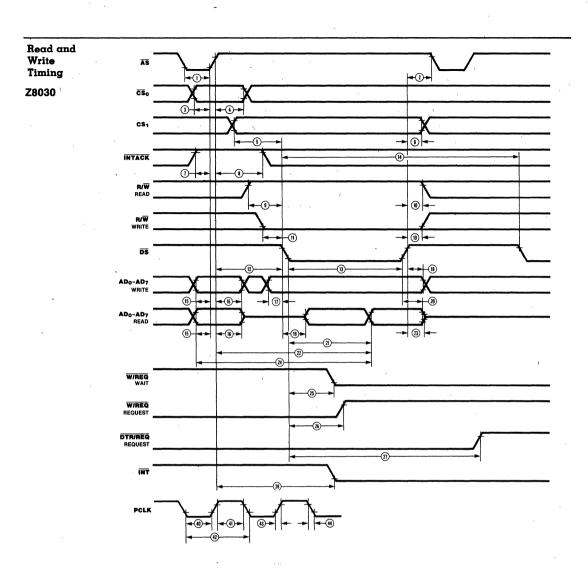

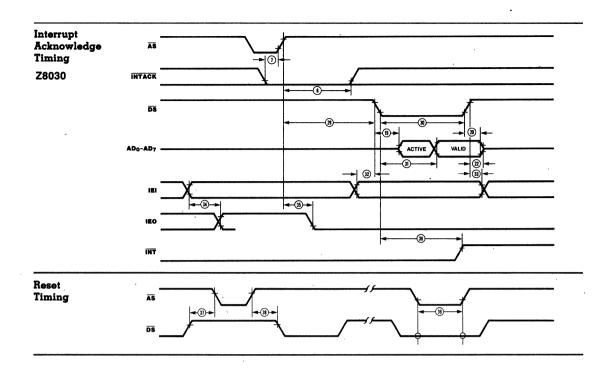

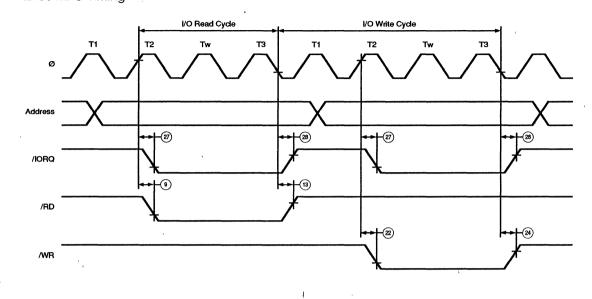

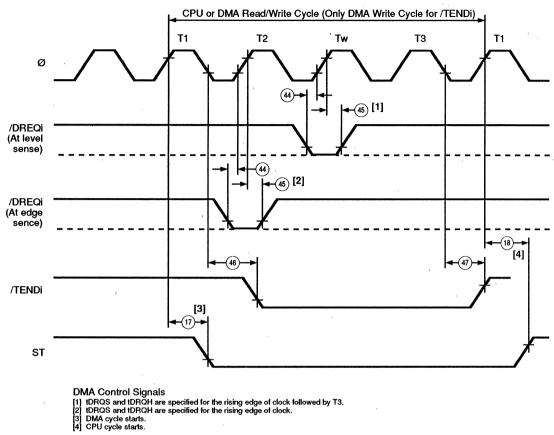

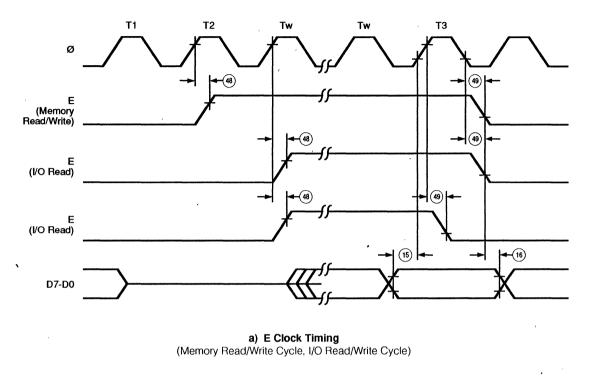

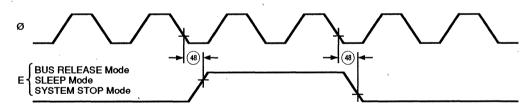

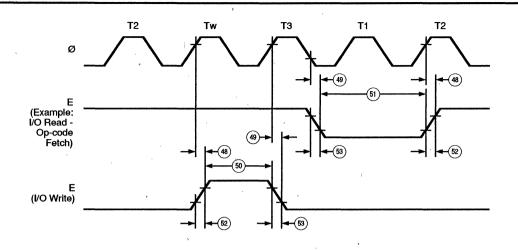

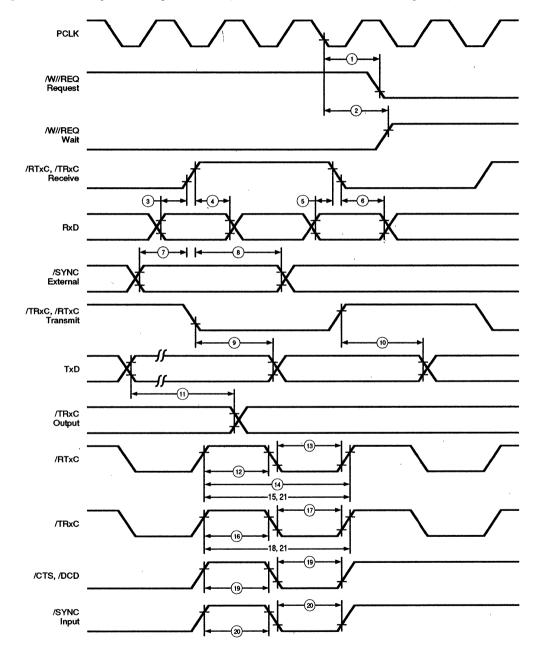

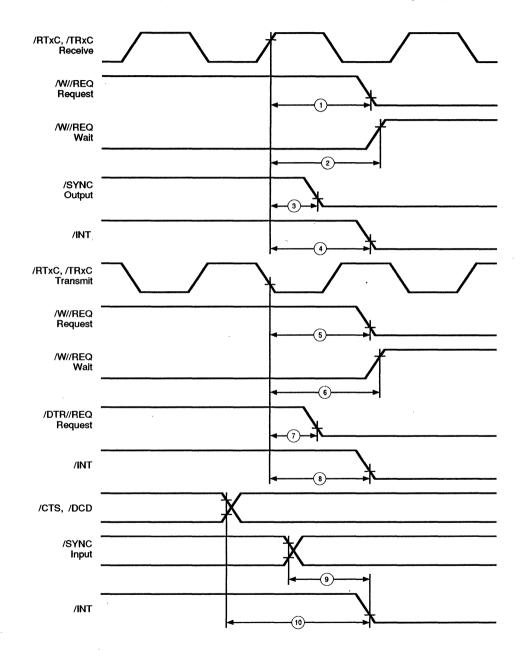

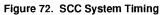

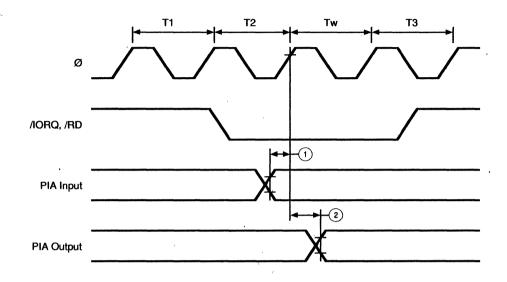

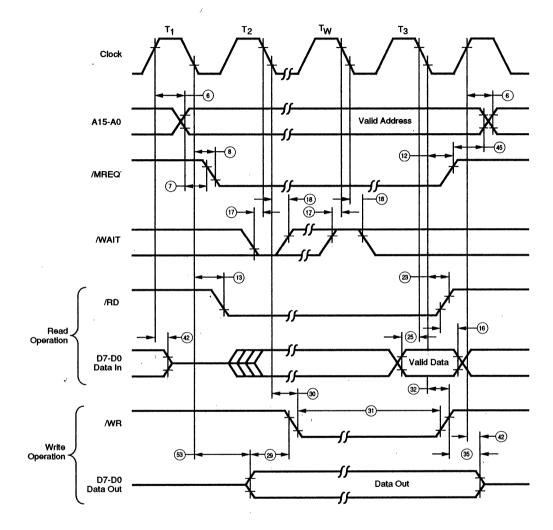

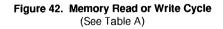

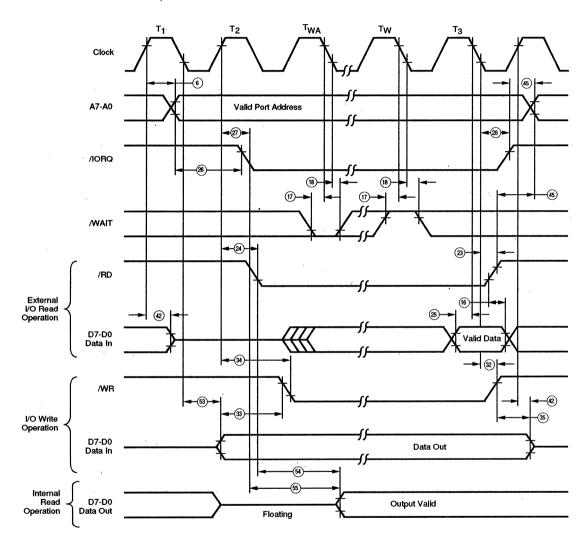

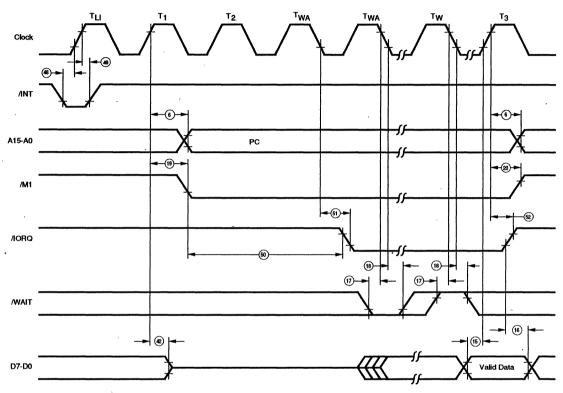

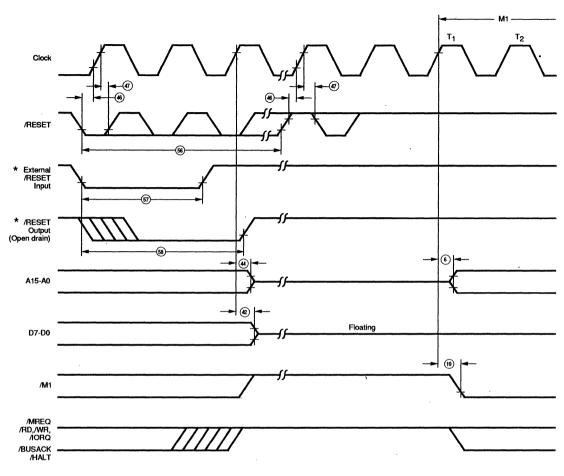

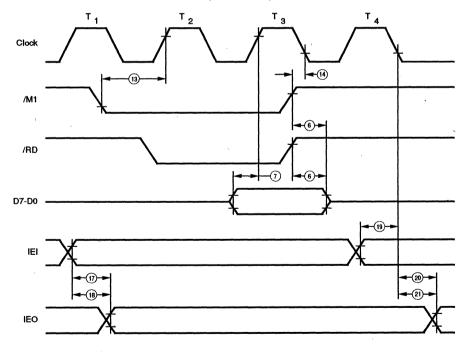

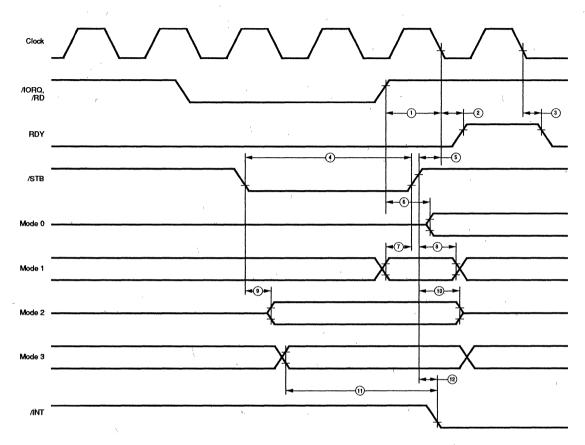

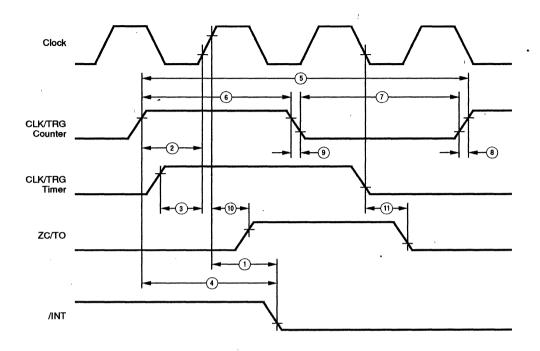

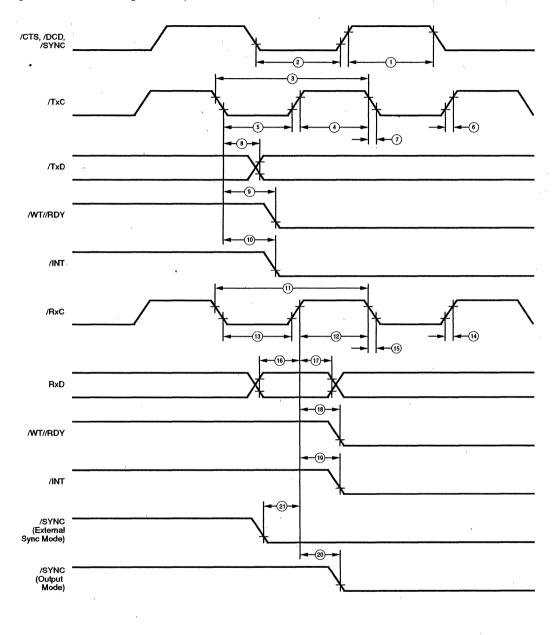

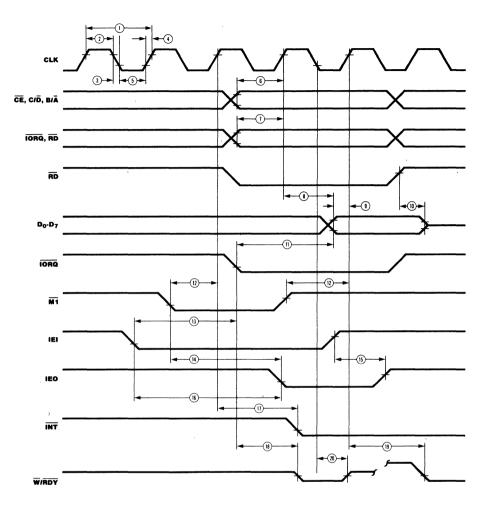

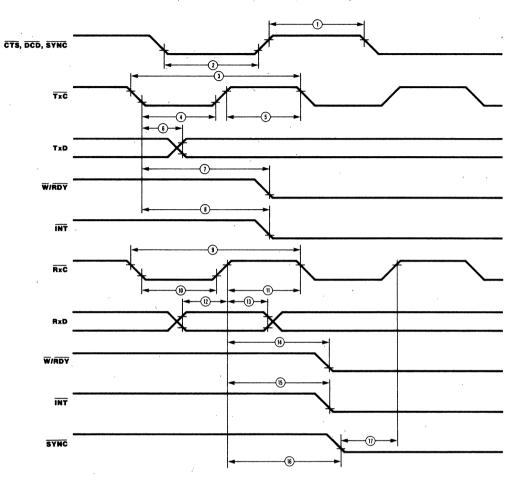

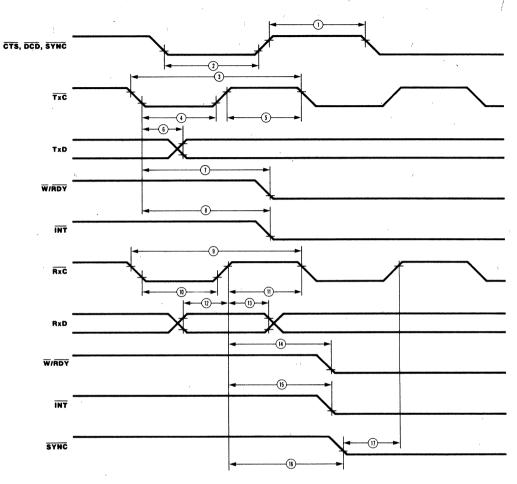

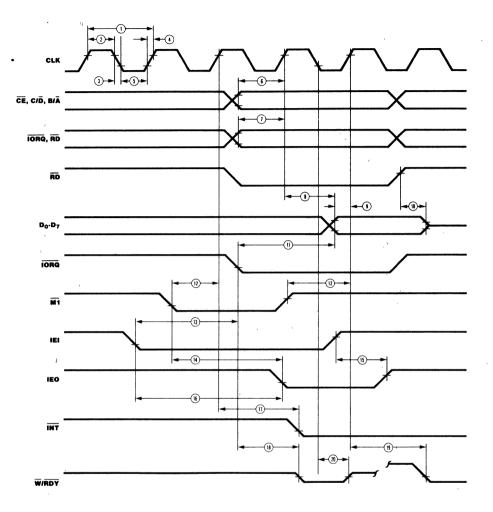

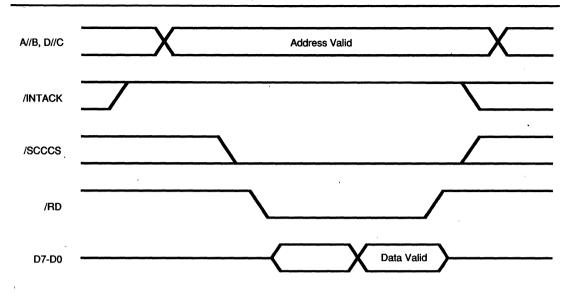

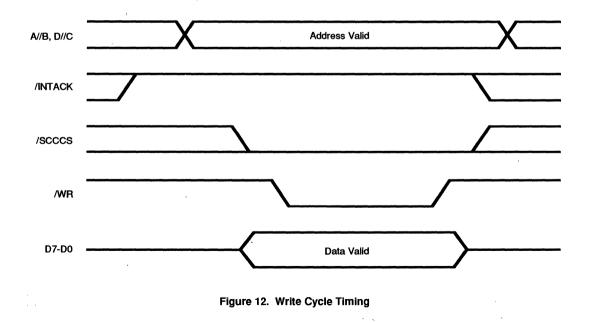

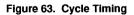

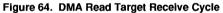

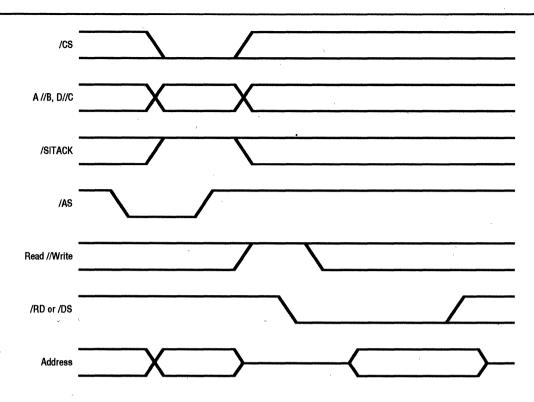

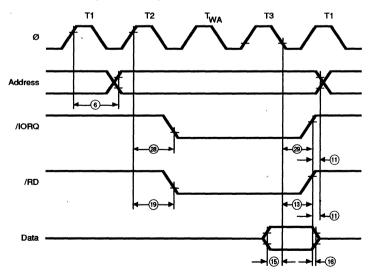

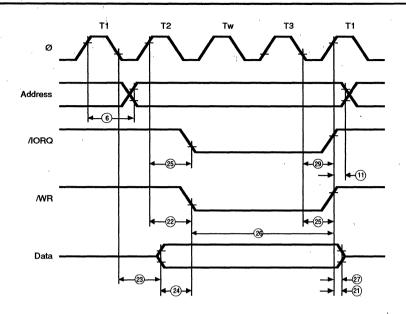

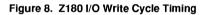

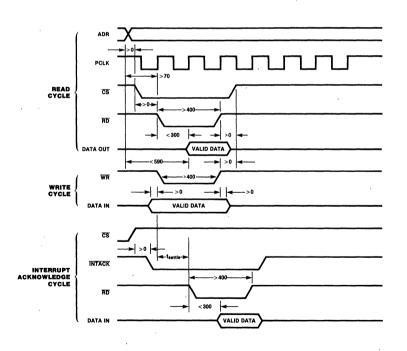

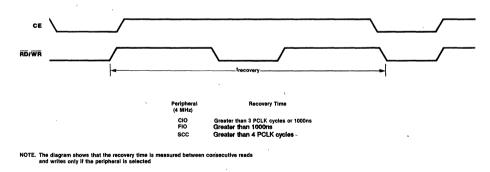

### **USC TIMING**

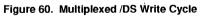

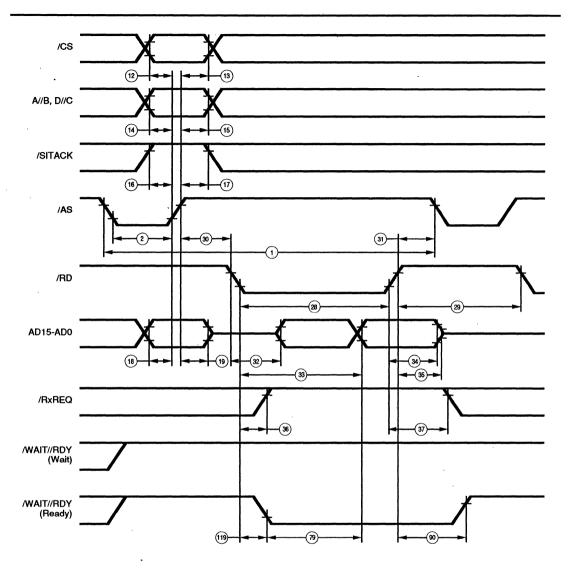

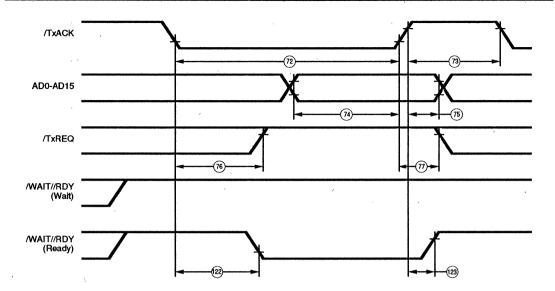

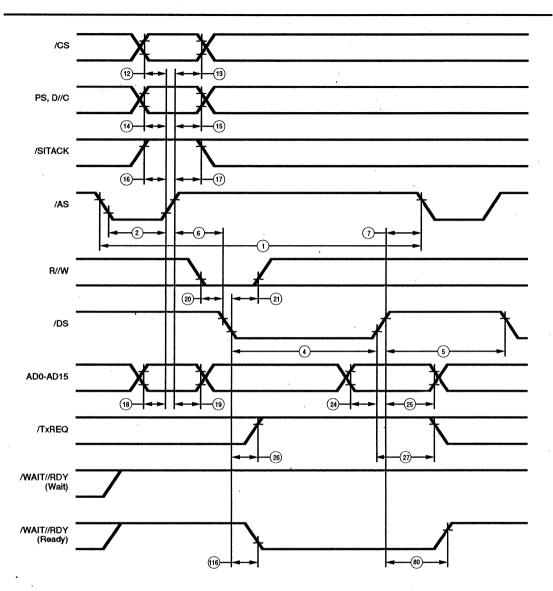

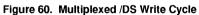

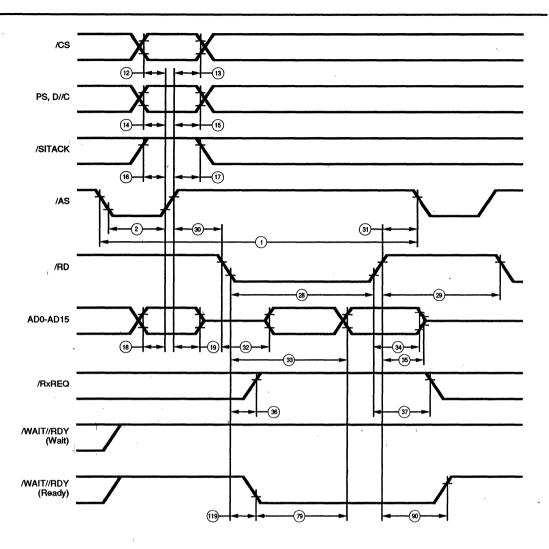

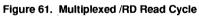

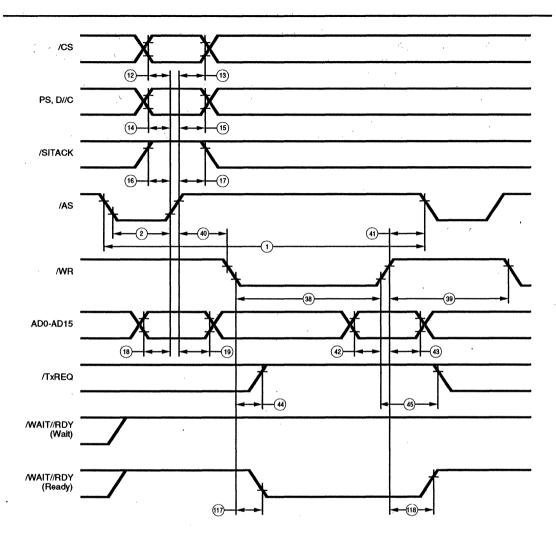

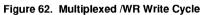

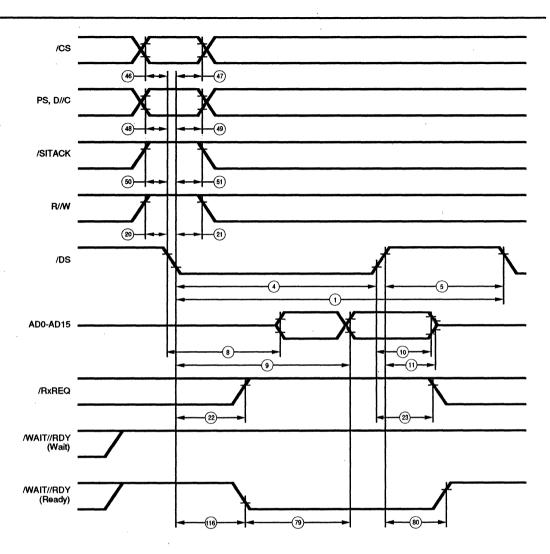

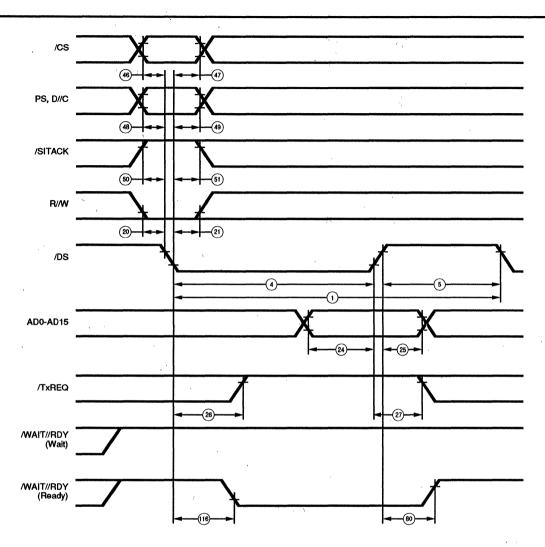

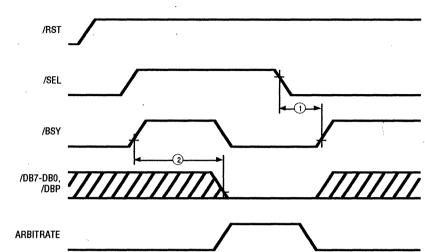

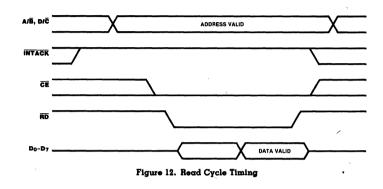

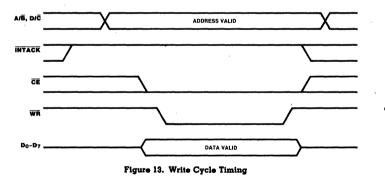

The USC interface timing is similar to that found on a static RAM, except that it is much more flexible. Up to eight separate timing strobe signals may be present on the interface. /DS, /RD, /WR, /PITACK, /RxACKA, /RxACKB, /TxACKA and /TxACKB, Only one of these timing strobes may be active at any time Should the external logic activate more than one of these strobes at the same time the USC will enter a pre-reset state that is only exited by a hardware reset. Do not allow overlap of timing strobes. The timing diagrams, beginning on the next page, illustrate the different bus transactions possible, with the necessary setup, hold and delay times.

### **ABSOLUTE MAXIMUM RATINGS**

| Voltages on all pins                 |

|--------------------------------------|

| with respect to Vss0.3 V to +7.0 V   |

| Voltages on all inputs               |

| with respect to Vss0.3V to Vcc +0.3V |

| Operating Ambient                    |

| TemperatureSee Ordering Information  |

| Storage Temperature65°C to +150°C    |

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device This is a stress rating only; operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

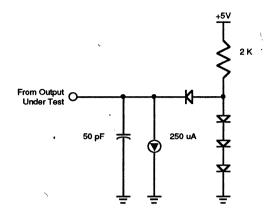

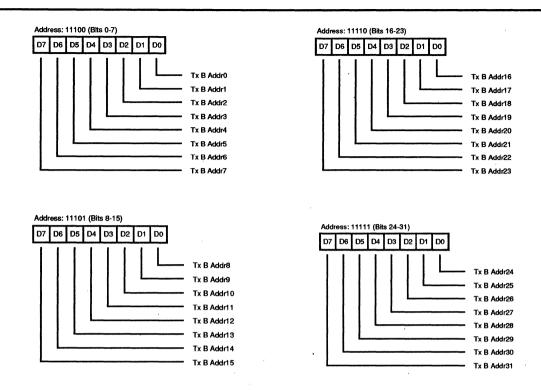

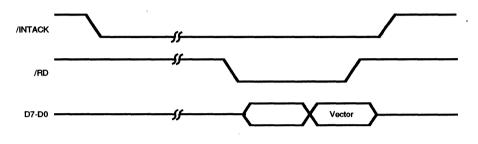

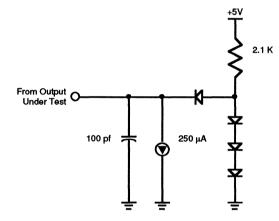

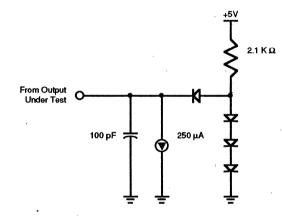

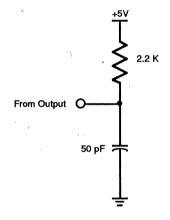

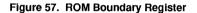

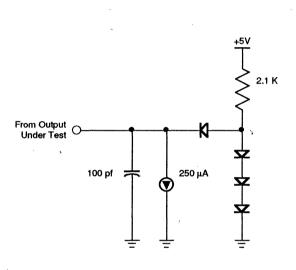

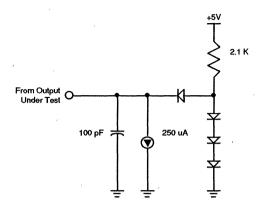

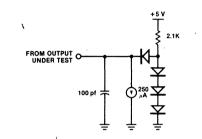

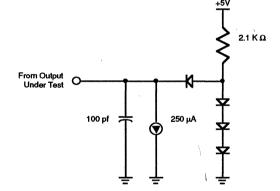

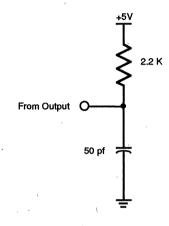

## STANDARD TEST CONDITIONS

The DC Characteristics and Capacitance section below 'apply for the following standard test conditions, unless otherwise noted. All voltages are referenced to GND. Positive current flows into the referenced pin. Standard conditions are as follows:

> +4.5 V < V<sub>cc</sub> < +5.5 V GND = 0 V T<sub>A</sub> as specified in Ordering Information

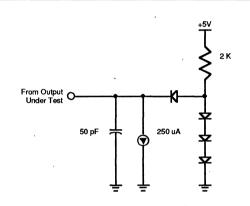

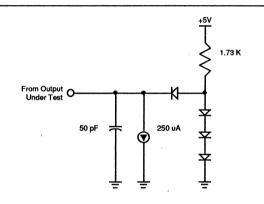

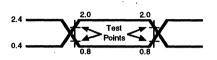

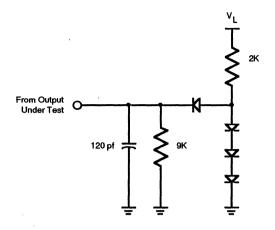

Figure 54. Standard Test Load

#### CAPACITANCE

| Symbol                              | Parameter                 | Min | Max | Unit | Condition          |

|-------------------------------------|---------------------------|-----|-----|------|--------------------|

| C <sub>IN</sub>                     | Input Capacitance         |     | 10  | pf   | Unmeasured Pins    |

| C <sub>IN</sub><br>C <sub>OUT</sub> | Output Capacitance        |     | 15  | pf   | Returned to Ground |

| C <sub>ivo</sub>                    | Bidirectional Capacitance |     | 20  | pf   |                    |

Note:

f=1MHz, over specified temperature range. Unmeasured pins returned to ground

MISCELLANEOUS Transistor Count - 174,000

### DC CHARACTERISTICS Z16C30

| Symbol            | Parameter                      | Min                  | Тур | Max                  | Unit | Condition                             |

|-------------------|--------------------------------|----------------------|-----|----------------------|------|---------------------------------------|

| VIH               | Input High Voltage             | 22                   |     | V <sub>cc</sub> +0.3 | V    |                                       |

| V                 | Input Low Voltage              | -0.3                 |     | ŏ.8                  | V    |                                       |

| V <sub>он</sub> 1 | Output High Voltage            | 2.4                  |     |                      | V    | I <sub>он</sub> = -1.6mA              |

| V <sub>oH</sub> 2 | Output High Voltage            | V <sub>cc</sub> -0.8 | ·   |                      | V    | l <sub>он</sub> = -250 µА             |

| V <sub>OL</sub>   | Output Low Voltage             |                      |     | 0.4                  | V    | I <sub>oL</sub> = +2.0 mA             |

| I.                | Input Leakage                  |                      |     | ±10.00               | μA   | $0.4 < V_{IN} < +2.4V$                |

| l <sub>ol</sub>   | Output Leakage                 |                      |     | ±10.00               | μA   | $0.4 < V_{out} < +2.4V$               |

| I <sub>CCI</sub>  | V <sub>cc</sub> Supply Current |                      | 7   | 50                   | mΑ   | $V_{cc} = 5VV_{H} = 4.8VV_{I} = 0.2V$ |

Note:

$V_{cc}\text{=}5V\pm$  10% unless otherwise specified, over specified temperature range.

# AC CHARACTERISTICS Z16C30

| No | Symbol     | Parameter                             | Min | Max                                      | Units      | Note                                   |

|----|------------|---------------------------------------|-----|------------------------------------------|------------|----------------------------------------|

| 1  | Тсус       | Bus Cycle Time                        | 160 |                                          | ns         |                                        |

| 2  | TwASI      | /AS Low Width                         | 40  |                                          | ns         |                                        |

| 3  | TwASh      | /AS High Width                        | 90  |                                          | ns         |                                        |

| 4  | TwDSI      | /DS Low Width                         | 70  |                                          | ns         |                                        |

| 5  | TwDSh      | /DS High Width                        | 60  |                                          | ns         |                                        |

| 6  | TdAS(DS)   | AS Rise to /DS Fall Delay Time        | 5   | ,                                        | ns         |                                        |

| 7  | TdDS(AS)   | /DS Rise to /AS Fall Delay Time       | 5   |                                          | <b>PIS</b> |                                        |

| 8  | TdDS(DRa)  | /DS Fall to Data Active Delay         | 0   |                                          | ns         |                                        |

| 9  | TdDS(DRv)  | /DS Fall to Data Valid Delay          |     | 85                                       | ns         | <b>991 (1997) (1997) (1997) (1997)</b> |

| 10 | TdDS(DRn)  | /DS Rise to Data Not Valid Delay      | 0   |                                          | ns         |                                        |

| 11 | TdDS(DRz)  | /DS Rise to Data Float Delay          |     | 20                                       | ns         |                                        |

| 12 | TsCS(AS)   | /CS to /AS Rise Setup Time            | 15  |                                          | ns         |                                        |

| 13 | ThCS(AS)   | /CS to /AS Rise Hold Time             | 0   |                                          | ns         |                                        |

| 14 | TsADD(AS)  | Direct Address to /AS Rise Setup Time | 15  |                                          | ns         | [1]                                    |

| 15 | ThADD(AS)  | Direct Address to /AS Rise Hold Time  | 5   |                                          | ns         | [1]                                    |

| 16 | TsSIA(AS)  | /SITACK to /AS Rise Setup Time        | 15  |                                          | ns         |                                        |

| 17 | ThSIA(AS)  | /SITACK to /AS Rise Hold Time         | 5   |                                          | ns         |                                        |

| 18 | TsAD(AS)   | Address to /AS Rise Setup Time        | 15  |                                          | ns         | ,                                      |

| 19 | ThAD(AS)   | Address to /AS Rise Hold Time         | 5   |                                          | ns         |                                        |

| 20 | TsRW(DS)   | R//W to /DS Fall Setup Time           | 0   |                                          | ns         |                                        |

| 21 | ThRW(DS)   | R//W to /DS Fall Hold Time            | 25  | te en al plotado en antidad à dere didam | ns         |                                        |

| 22 | TsDSf(RRQ) | /DS Fall to /RxREQ Inactive Delay     | 5   | 60                                       | ns         | [4]                                    |

| 23 | TdDSr(RRQ) | /DS Rise to /RxREQ Active Delay       | 0   |                                          | ns         |                                        |

| 24 | TsDW(DS)   | Write Data to /DS Rise Setup Time     | 30  |                                          | ns         |                                        |

| 25 | ThDW(DS)   | Write Data to /DS Rise Hold Time      | 0   |                                          | ns         |                                        |

| 26 | TdDSf(TRQ) | /DS Fall to /TxREQ Inactive Delay     |     | 65                                       | ns         | [5]                                    |

| 27 | TdDSr(TRQ) | /DS Rise to /TxREQ Active Delay       | 0   |                                          | ns         |                                        |

| 28 | TwRDI      | /RD Low Width                         | 70  |                                          | ns         |                                        |

# AC CHARACTERISTICS Z16C30

| No | Symbol                 | Parameter                             | Min | Max | Units | Note |

|----|------------------------|---------------------------------------|-----|-----|-------|------|

| 29 | TwRDh                  | /RD High Width                        | 60  |     | ns    |      |

| 30 | TdAS(RD)               | /AS Rise to /RD Fall Delay Time       | 5   |     | ns    |      |

| 31 | TdRD(AS)               | /RD Rise to /AS Fall Delay Time       | 5   |     | ns    |      |

| 32 | TdRD(DRa)              | /RD Fall to Data Active Delay         | 0   |     | ns    |      |

| 33 | TdRD(DRv)              | /RD Fall to Data Valid Delay          |     | 85  | ns    |      |

| 34 | TdRD(DRn)              | /RD Rise to Data Not Valid Delay      | 0   |     | ns    |      |

| 35 | TdRD(DRz)              | /RD Rise to Data Float Delay          |     | 20  | ns    |      |

| 36 | TdRDf(RRQ)             | /RD Fall to /RxREQ Inactive Delay     |     | 60  | ` ns  | [4]  |

| 37 | TdRDr(RRQ)             | /RD Rise to /RxREQ Active Delay       | 0   |     | ns    |      |

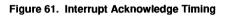

| 38 | TwWRI                  | /WR Low Width                         | 70  |     | ns    |      |

| 39 | TwWRh                  | /WR High Width                        | 60  |     | ns    |      |

| 40 | TdAS(WR)               | /AS Rise to /WR Fall Delay Time       | 5   |     | ns    |      |

| 41 | TdWR(AS)               | /WR Rise to /AS Fall Delay Time       | 5   |     | ns    |      |

| 42 | TsDW(WR)               | Write Data to /WR Rise Setup Time     | 30  |     | ns    |      |

| 43 | ThDW(WR)               | Write Data to /WR Rise Hold Time      | 0   |     | ns    |      |

| 44 | TdWRf(TRQ)             | /WR Fall to /TxREQ Inactive Delay     |     | 65  | ns    | [5]  |

| 45 | TdWRr(TRQ)             | /WR Rise to /TxREQ Active Delay       | 0   |     | ns    |      |

| 46 | TsCS(DS)               | /CS to /DS Fall Setup Time            | 0   |     | ns    | [2]  |

| 47 | ThCS(DS)               | /CS to /DS Fall Hold Time             | 25  |     | ns    | [2]  |

| 48 | TsADD(DS)              | Direct Address to /DS Fall Setup Time | 5   |     | ns    | [1,2 |

| 49 | ThADD(DS)              | Direct Address to /DS Fall Hold Time  | 25  |     | ns    | [1,2 |

| 50 | TsSIA(DS)              | /SITACK to /DS Fall Setup Time        | 5   |     | ns    | [2]  |

| 51 | ThSIA(DS)              | /SITACK to /DS Fall Hold Time         | 25  |     | ns    | [2]  |

| 52 | TsCS(RD)               | /CS to /RD Fall Setup Time            | 0   |     | ns    | [2]  |

| 53 | ThCS(RD)               | /CS to /RD Fall Hold Time             | 25  |     | ns    | [2]  |

| 54 | TsADD(RD)              | Direct Address to /RD Fall Setup Time | 5   |     | ns    | [1,2 |

| 55 | ThADD(RD)              | Direct Address to /RD Fall Hold Time  | 25  |     | ns    | [1,2 |

| 56 | TsSIA(RD)              | /SITACK to /RD Fall Setup Time        | 5   |     | ns    | [2]  |

| 57 | ThSIA(RD)              | /SITACK to /RD Fall Hold Time         | 25  |     | ns    | [2]  |

| 58 | TsCS(WR)               | /CS to /WR Fall Setup Time            | 0   |     | ns    | [2]  |

| 59 | ThCS(WR)               | /CS to /WR Fall Hold Time             | 25  |     | ns    | [2]  |

| 60 | TsADD(WR)              | Direct Address to /WR Fall Setup Time | 5   |     | ns    | [1,2 |

| 61 | ThADD(WR)              | Direct Address to /WR Fall Hold Time  | 25  |     | ns    | [1,2 |

| 62 | TsSIA(WR)              | /SITACK to /WR Fall Setup Time        | 5   |     | ns    | [2]  |

| 63 | ThSIA(WR)              | /SITACK to /WR Fall Hold Time         | 25  |     | ns    | [2]  |

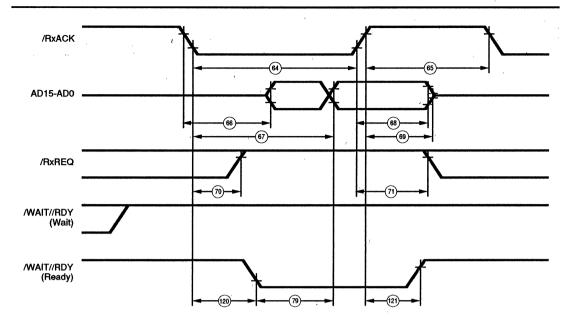

| 64 | TwRAKI                 | /RxACK Low Width                      | 70  |     | ns    | [    |

| 65 | TwRAKh                 | /RxACK High Width                     | 60  |     | ns    |      |

| 66 | TdRAK(DRa)             | /RxACK Fall to Data Active Delay      | 0   |     | ns    |      |

| 67 | TdRAK(DRv)             | /RxACK Fall to Data Valid Delay       | -   | 85  | ns    |      |

| 68 | TdRAK(DRn)             | /RxACK Rise to Data Not Valid Delay   | 0   |     | ns    |      |

| 69 | TdRAK(DRz)             | /RxACK Rise to Data Float Delay       |     | 20  | ns    |      |

| 70 | TdRAKf(RRQ)            | /RxACK Fall to /RxREQ Inactive Delay  |     | 60  | ns    | [4]  |

| 71 | TdRAKr(RRQ)            | /RxACK Rise to /RxREQ Active Delay    | 0   | 00  | ns    | [*]  |

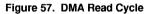

| 72 | TwTAKI                 | /TxACK Low Width                      | 70  |     | ns    |      |

|    | · •• • • • • • • • • • |                                       | 10  |     | 110   |      |

# AC CHARACTERISTICS Z16C30

| No  | Symbol      | Parameter                                | Min | Max                                      | Units | Note |

|-----|-------------|------------------------------------------|-----|------------------------------------------|-------|------|

| 73  | TwTAKh      | /TxACK High Width                        | 60  | r                                        | ns    |      |

| 74  | TsDW(TAK)   | Write Data to /TxACK Rise Setup Time     | 30  | ,                                        | ns    |      |

| 75  | ThDW(TAK)   | Write Data to /TxACK Rise Hold Time      | 0   |                                          | ns    |      |

| 76  | TdTAKf(TRQ) | /TxACK Fall to /TxREQ Inactive Delay     |     | 65                                       | ns ,  | [5]  |

| 77  | TdTAKr(TRQ) | /TxACK Rise to /TxREQ Active Delay       | 0   | a an | ns    |      |

| 78  | TdDSf(RDY)  | /DS Fall (INTACK) to /RDY Fall Delay     |     | 200                                      | ns    |      |

| 79  | TdRDY(DRv)  | /RDY Fall to Data Valid Delay            |     | 40                                       | ns    |      |

| 80  | TdDSr(RDY)  | /DS Rise to /RDY Rise Delay              |     | 40                                       | ns    |      |

| 81  | TsIEI(DSI)  | IEI to /DS Fall (INTACK) Setup Time      | 60  |                                          | ns    |      |

| 82  | ThIEI(DSI)  | IEI to /DS Rise (INTACK) Hold Time       | 0   |                                          | ns    |      |

| 83  | TdIEI(IEO)  | IEI to IEO Delay                         |     | 60                                       | ns    |      |

| 84  | TdAS(IEO)   | /AS Rise (Intack) to IEO Delay           |     | 60                                       | ns    |      |

| 85  | TdDSI(INT)  | /DS Fall (INTACK) to /INT Inactive Delay |     | 200                                      | ns    |      |

| 86  | TdDSI(Wf)   | /DS Fall (INTACK) to /WAIT Fall Delay    |     | 40                                       | ns    |      |

| 87  | TdDSI(Wr)   | /DS Fall (INTACK) to /WAIT Rise Delay    |     | · 200                                    | ns    |      |

| 88  | TdW(DRv)    | /WAIT Rise to Data Valid Delay           |     | 40                                       | ns    |      |

| 89  | TdRDf(RDY)  | /RD Fall (INTACK) to /RDY Fall Delay     |     | 200                                      | ns    |      |

| 90  | TdRDr(RDY)  | /RD Rise to /RDY Rise Delay              |     | 40                                       | ns    |      |

| 91  | TsIEI(RDI)  | IEI to /RD Fall (INTACK) Setup Time      | 60  |                                          | ns    |      |

| 92  | ThIEI(RDI)  | IEI to /RD Rise (INTACK) Hold Time       | 0   |                                          | ns    |      |

| 93  | TdRDI(INT)  | /RD Fall (INTACK) to /INT Inactive Delay |     | 200                                      | . ns  |      |

| 94  | TdRDI(Wf)   | /RD Fall (INTACK) to /WAIT Fall Delay    |     | 40                                       | ns    |      |

| 95  | TdRDI(Wr)   | /RD Fall (INTACK) to /WAIT Rise Delay    |     | 200                                      | ns    |      |

| 96  | TwPIAI      | /PITACK Low Width                        | 70  |                                          | ns    |      |

| 97  | TwPIAh      | /PITACK High Width                       | 60  |                                          | ns    |      |

| 98  | TdAS(PIA)   | AS Rise to /PITACK Fall Delay Time       | 5   |                                          | ns    |      |

| 99  | TdPIA(AS)   | /PITACK Rise to /AS Fall Delay Time      | 5   |                                          | ns    |      |

| 100 | TdPIA(DRa)  | /PITACK Fall to Data Active Delay        | 0   |                                          | ns    |      |

| 101 | TdPIA(DRn)  | /PITACK Rise to Data Not Valid Delay     | 0   |                                          | ns    |      |

| 102 | TdPIA(DRz)  | /PITACK Rise to Data Float Delay         |     | 20                                       | ns    |      |

| 103 | TsIEI(PIA)  | IEI to /PITACK Fall Setup Time           | 60  |                                          | ns    |      |

| 104 | ThIEI(PIA)  | IEI to /PITACK Rise Hold Time            | 0   |                                          | ns    |      |

| 105 | TdPIA(IEO)  | /PITACK Fall to IEO Delay                |     | 60                                       | ns    |      |

| 106 | TdPIA(INT)  | /PITACK Fall to /INT Inactive Delay      | · · | 200                                      | ns    |      |

| 107 | TdPIAf(RDY) | /PITACK Fall to /RDY Fall Delay          |     | 200                                      | ns    |      |

| 108 | TdPIAr(RDY) | /PITACK Rise to /RDY Rise Delay          |     | 40                                       | ns    |      |

| 109 | TdPIA(Wf)   | /PITACK Fall to /WAIT Fall Delay         | ,   | 40                                       | ns    |      |

| 110 | TdPIA(Wr)   | /PITACK Fall to /WAIT Rise Delay         | 1   | 200                                      | ns    |      |

| 111 | TdSIA(INT)  | /SITACK Fall to IEO Inactive Delay       |     | 200                                      | ns    | [2]  |

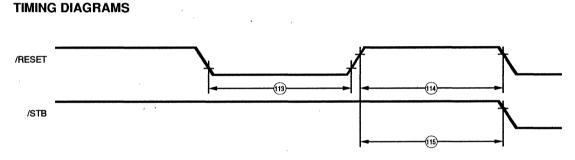

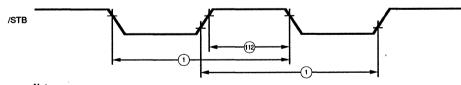

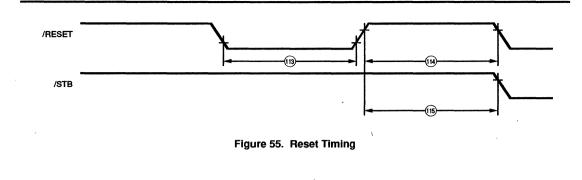

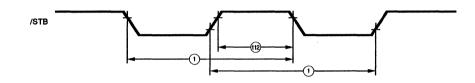

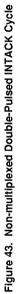

| 112 | TwSTBh      | /Strobe High Width                       | 60  |                                          | ns    | [3]  |

| 113 | TwRESI      | /RESET Low Width                         | 170 |                                          | ns    |      |

| 114 | TwRESh      | /RESET High Width                        | 60  |                                          | ns    |      |

| 115 | Tdres(STB)  | /RESET Rise to /STB Fall                 | 60  |                                          | ns    | [3]  |

| 116 | TdDSf(RDY)  | /DS Fall to /RDY Fall Delay              |     | 50                                       | ns    |      |

ς,

# AC CHARACTERISTICS Z16C30

|     | -           |                                |     |     |       |      |

|-----|-------------|--------------------------------|-----|-----|-------|------|

| No  | Symbol      | Parameter                      | Min | Max | Units | Note |

| 117 | TdWRf(RDY)  | /WR Fall to /RDY Fall Delay    |     | 50  | ns    |      |

| 118 | TdWRr(RDY)  | /WR Rise to /RDY Rise Delay    |     | 40  | ns    |      |

| 119 | TdRDf(RDY)  | /RD Fall to /RDY Fall Delay    |     | 50  | ns    |      |

| 120 | TdRAKf(RDY) | /RxACK Fall to /RDY Fall Delay |     | 50  | ns    |      |

| 121 | TdRAKr(RDY) | /RxACK Rise to /RDY Rise Delay |     | 40  | ns    |      |

| 122 | TdTAKf(RDY) | /TxACK Fall to /RDY Fall Delay |     | 50  | ns    |      |

| 123 | TdTAKr(RDY) | /TxACK Rise to /RDY Rise Delay |     | 40  | ns    |      |

|     |             |                                |     |     |       |      |

#### Notes:

[1] Direct address is any of A//B, D//C or AD15-AD8 used as an address bus.

The parameter applies only when /AS is not present.

Strobe (/STB) is any of /DS, /RD, /WR, /PITACK, /RxACK or /TxACK.

Parameter applies only if read empties the receive FIFO.

[5] Parameter applies only if write fills the transmit FIFO.

Note: /STB is any of /DS, /RD, /WR, /PITACK, /RxACK, or /TxACK.

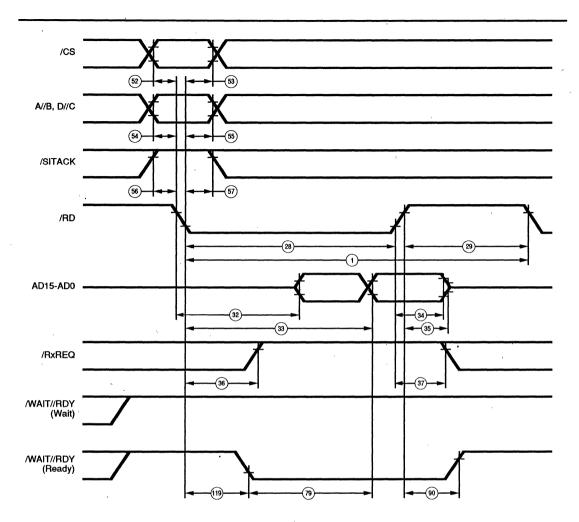

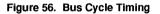

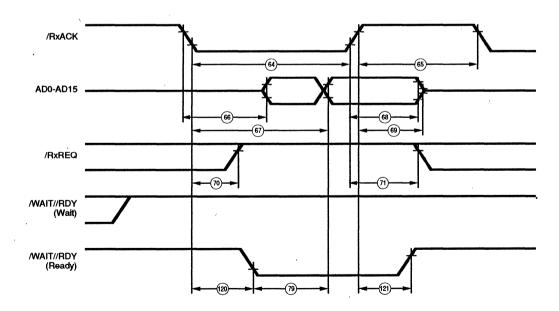

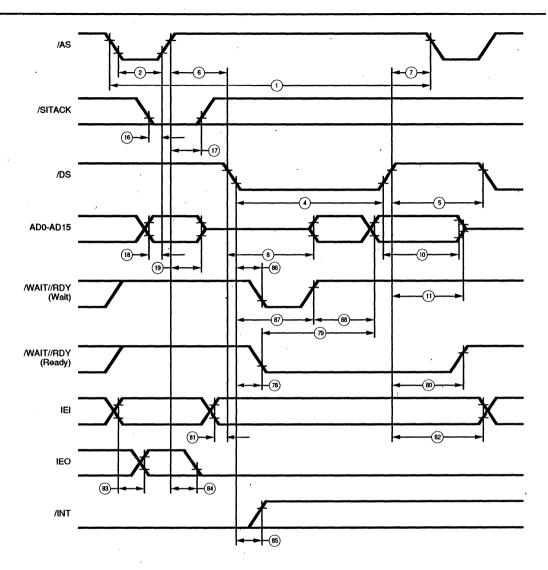

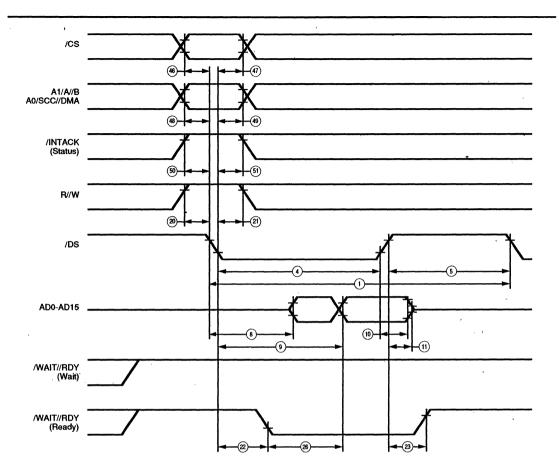

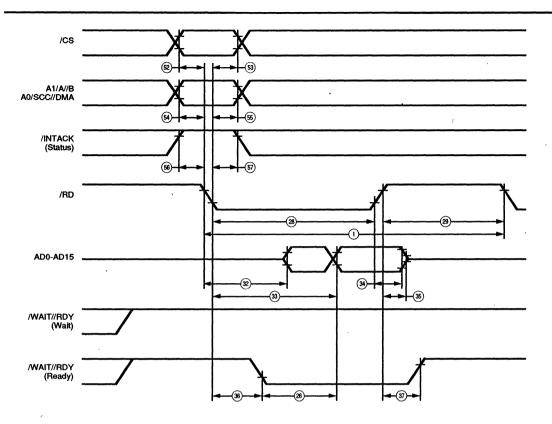

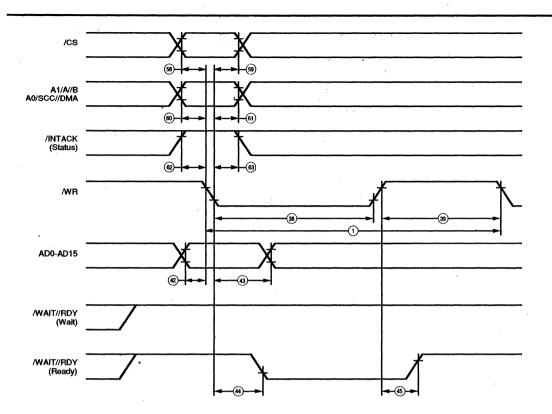

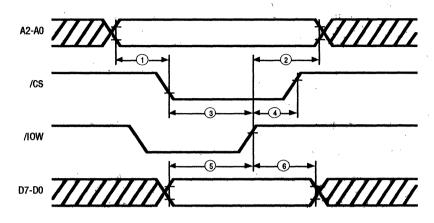

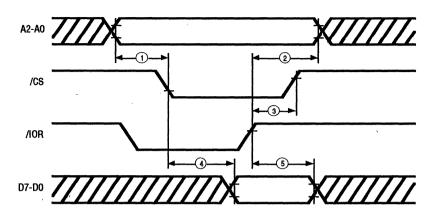

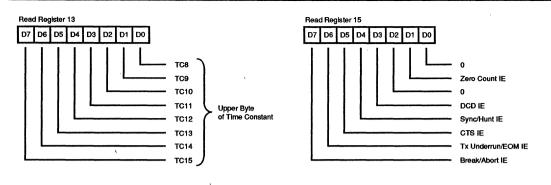

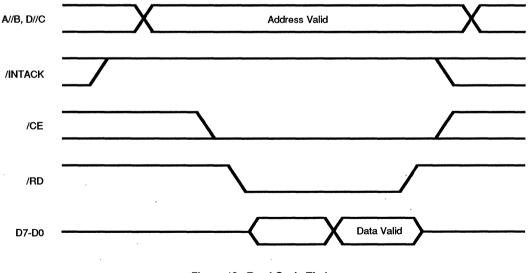

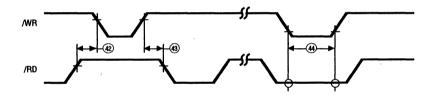

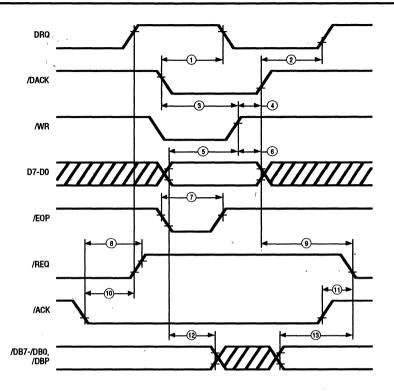

Figure 56. Bus Cycle Timing

•• /

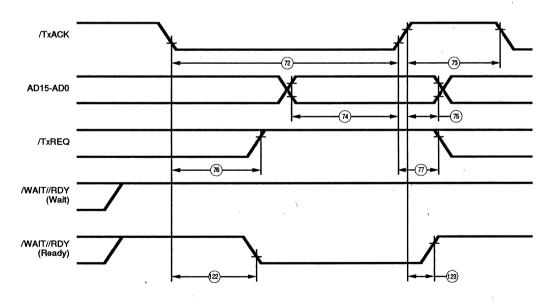

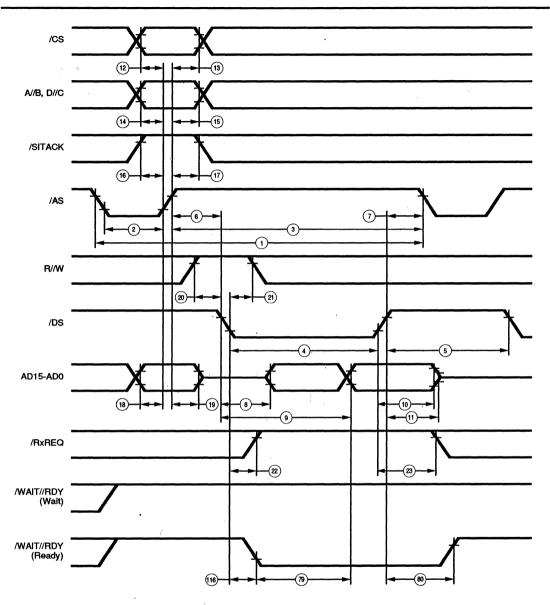

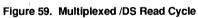

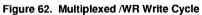

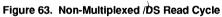

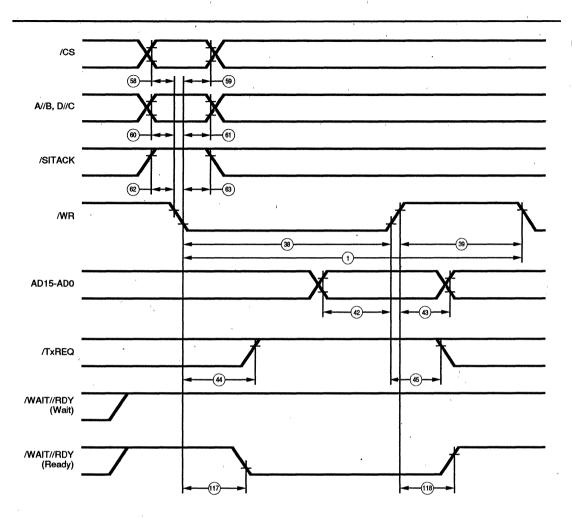

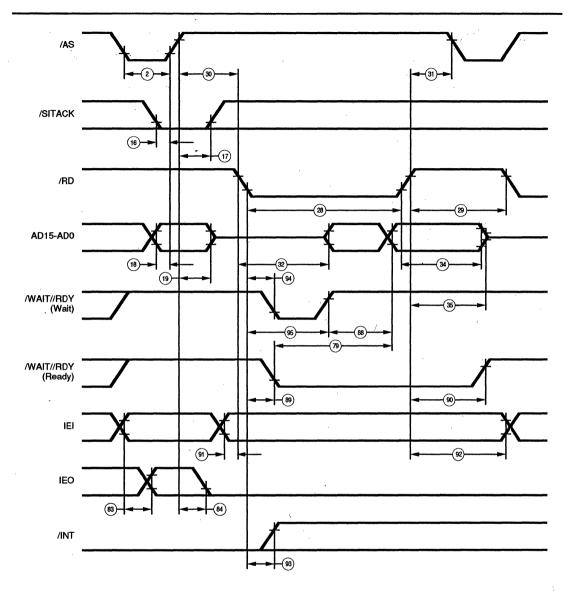

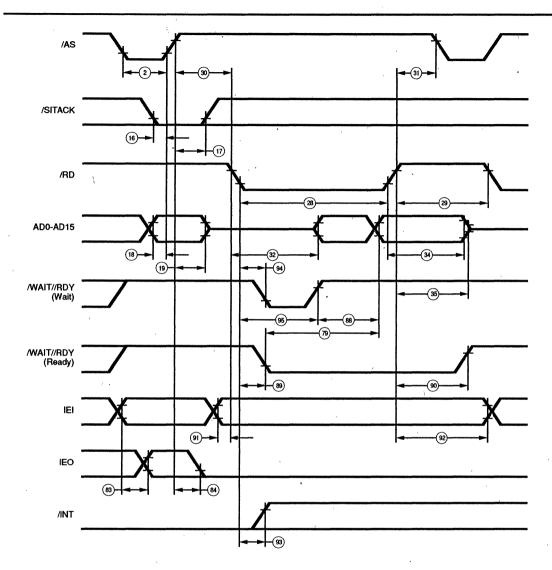

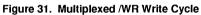

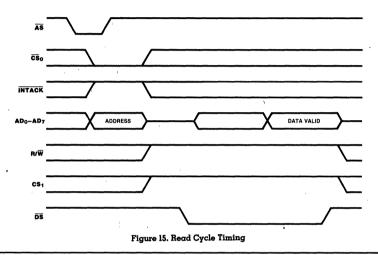

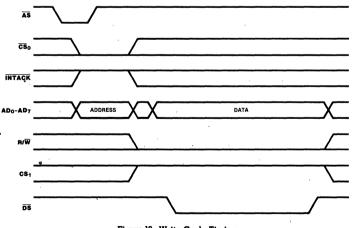

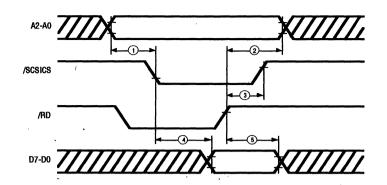

Figure 61. Multiplexed /RD Read Cycle

.

١.

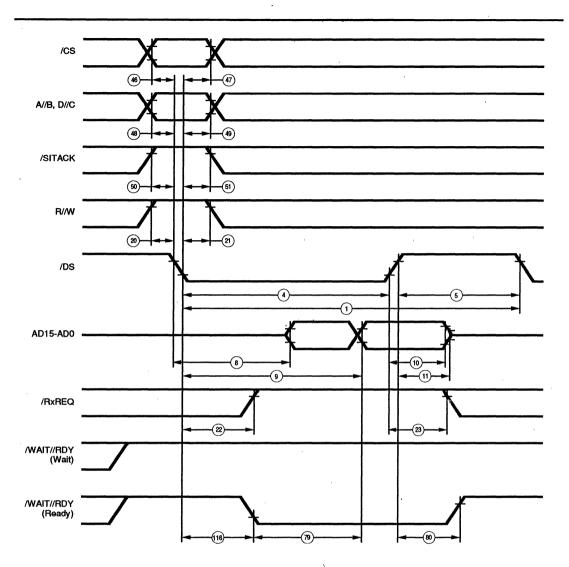

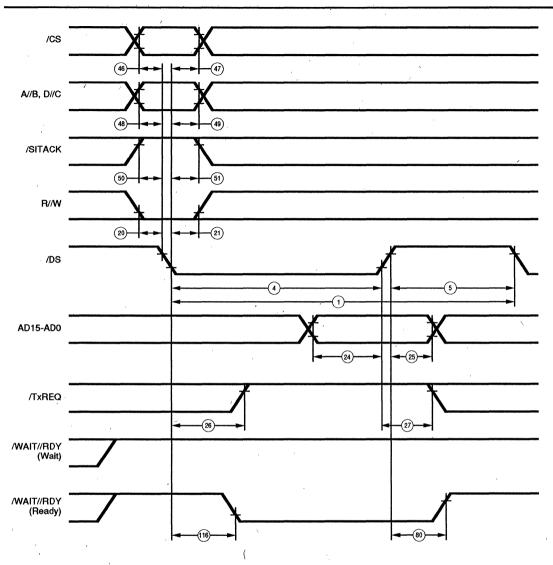

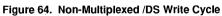

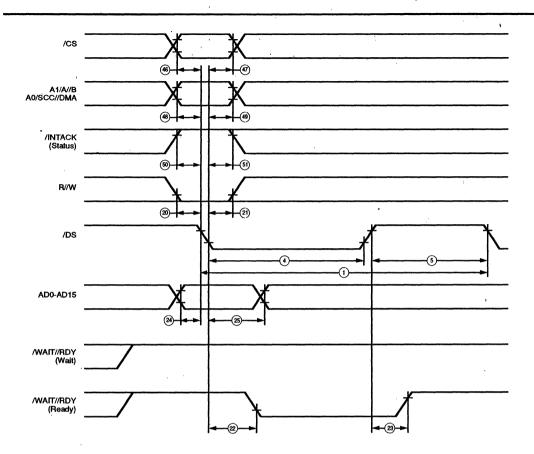

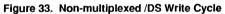

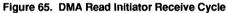

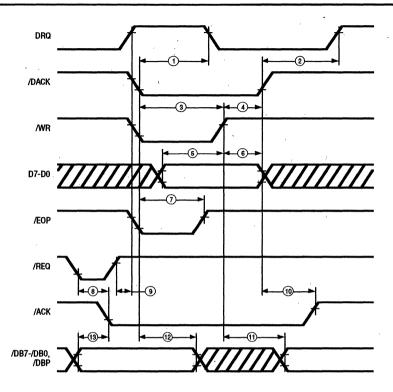

Figure 65. Non-Multiplexed /RD Read Cycle

a

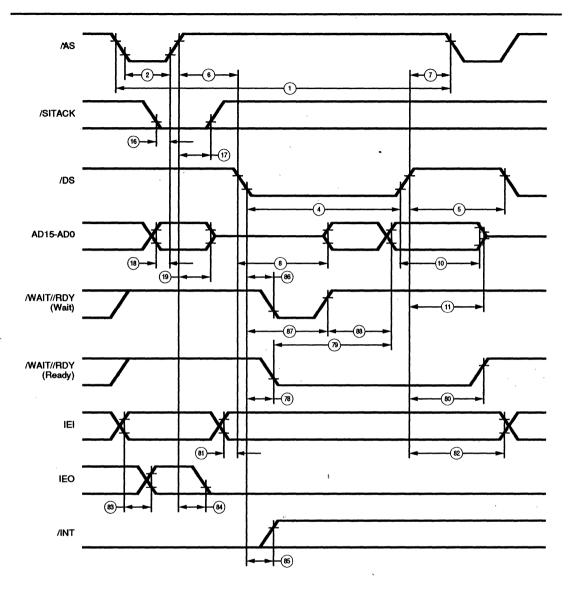

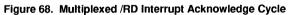

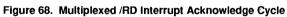

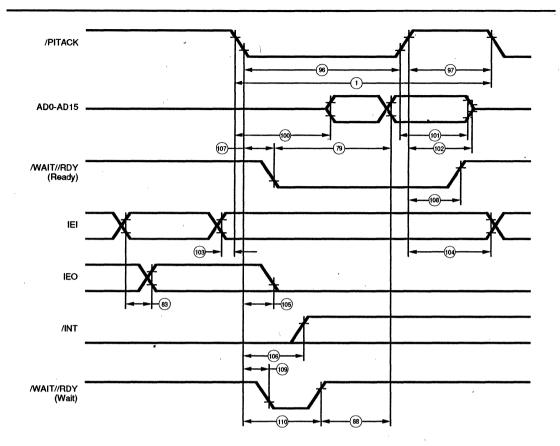

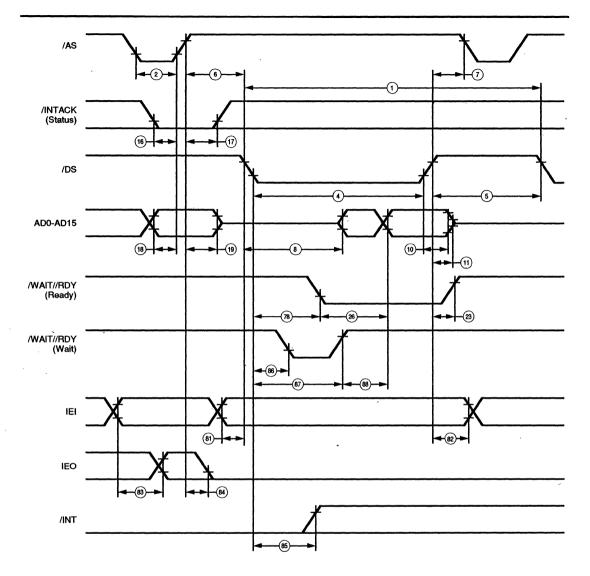

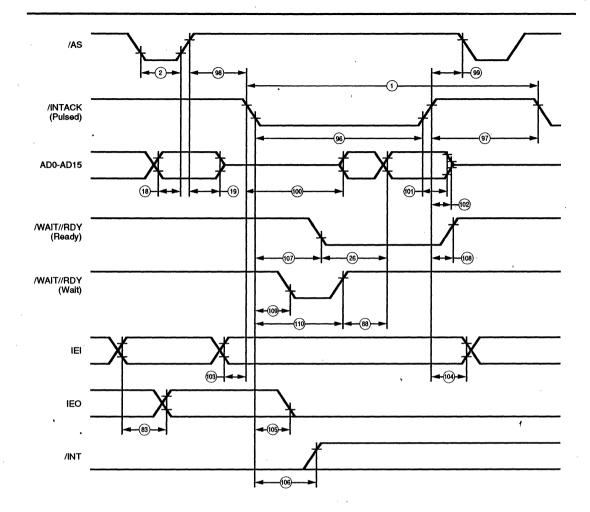

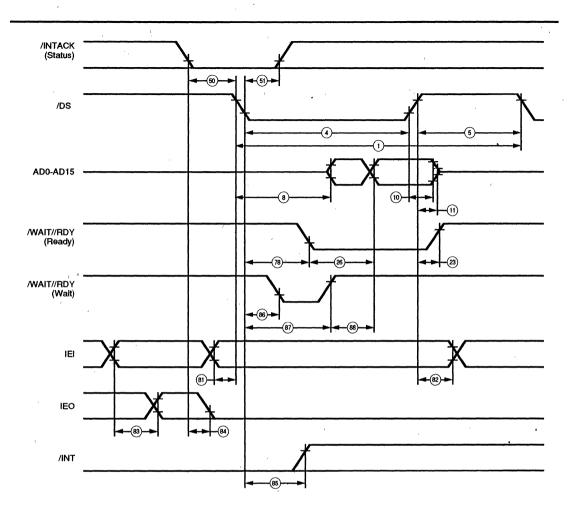

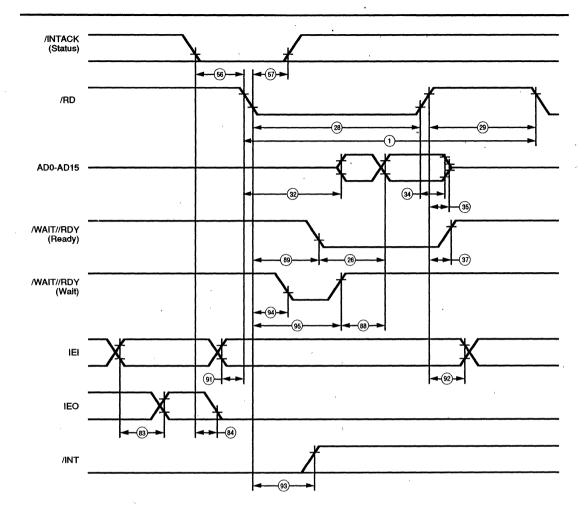

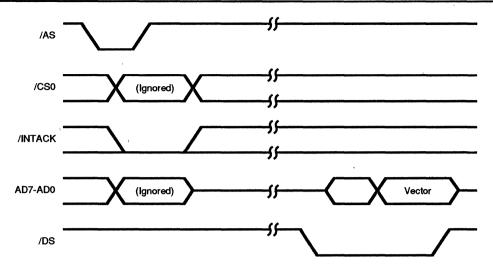

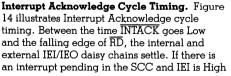

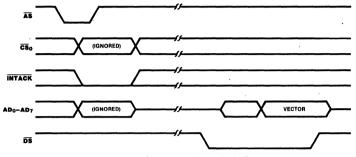

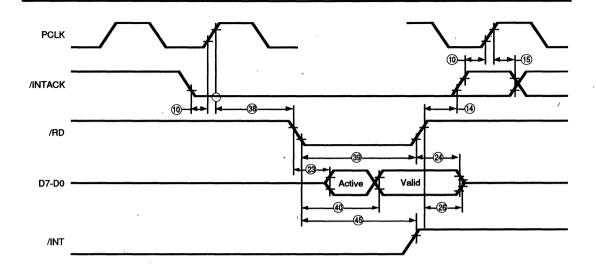

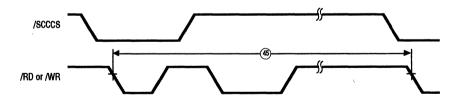

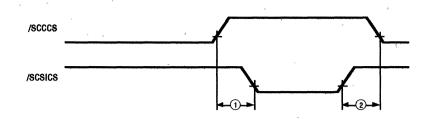

Figure 69. Multiplexed Pulsed Interrupt Acknowledge Cycle

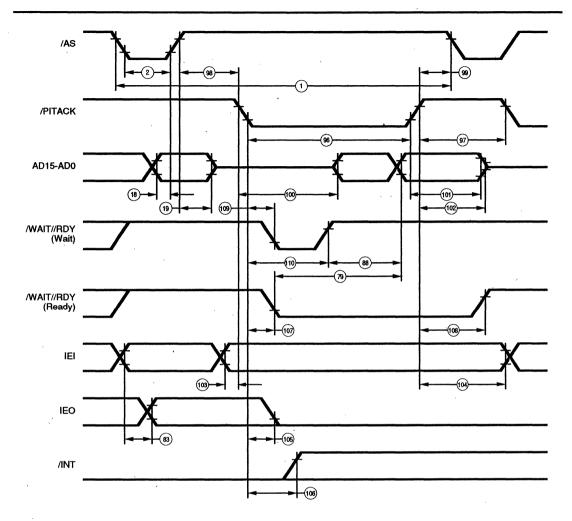

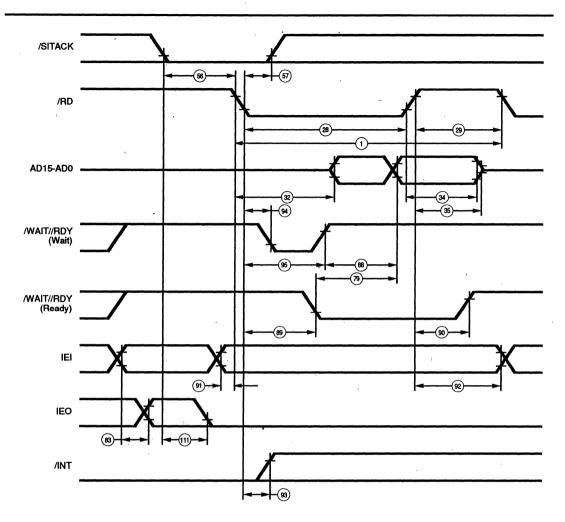

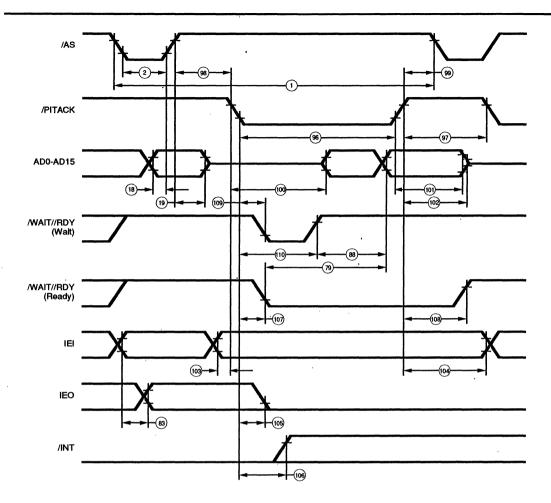

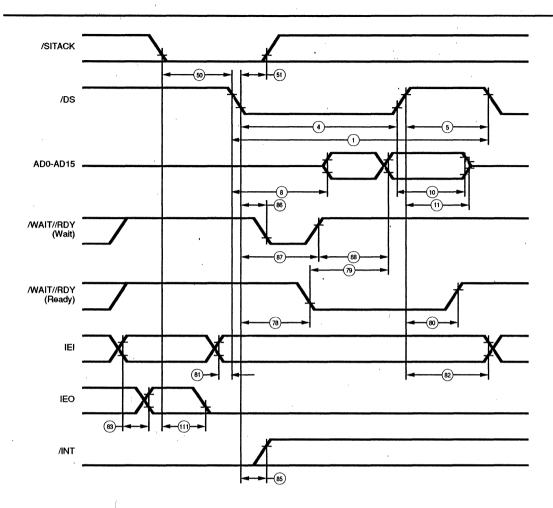

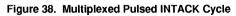

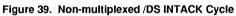

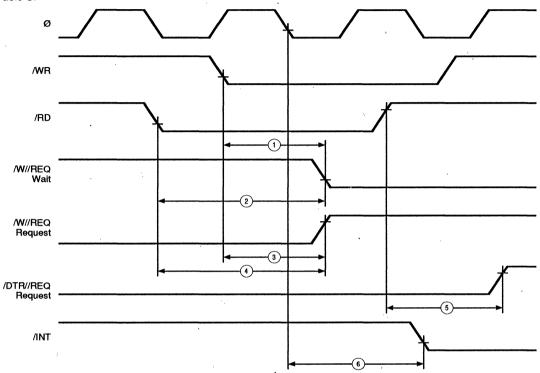

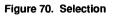

Figure 70. Non-Multiplexed /DS Interrupt Acknowledge Cycle

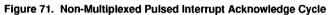

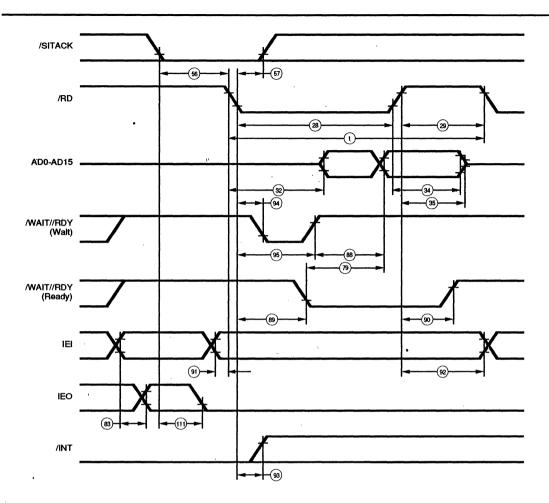

Figure 72. Non-Multiplexed /RD Interrupt Acknowledge Cycle

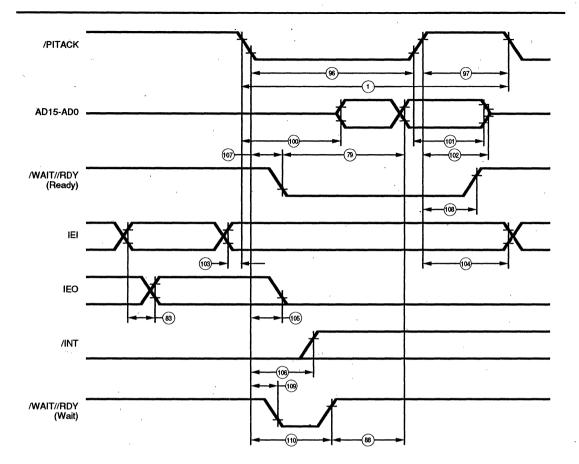

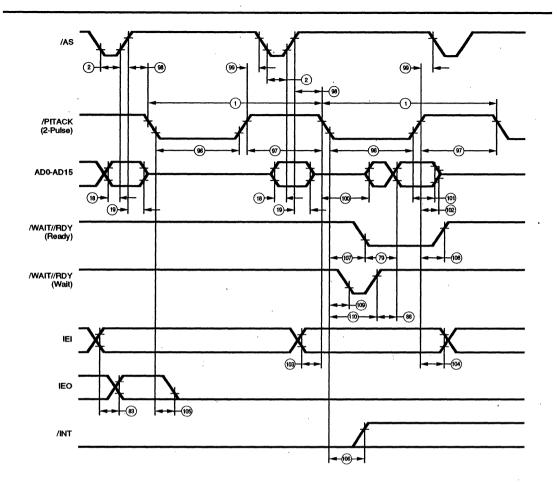

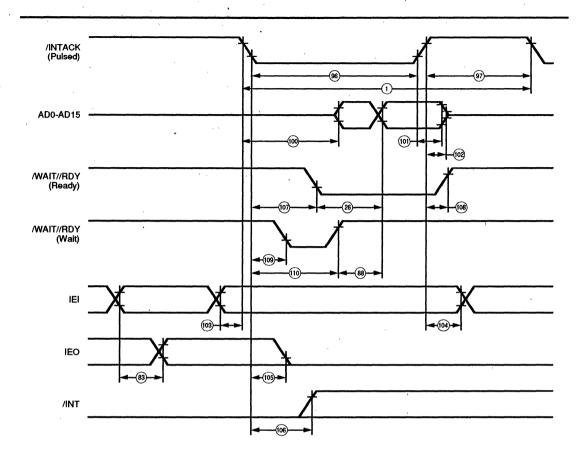

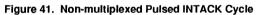

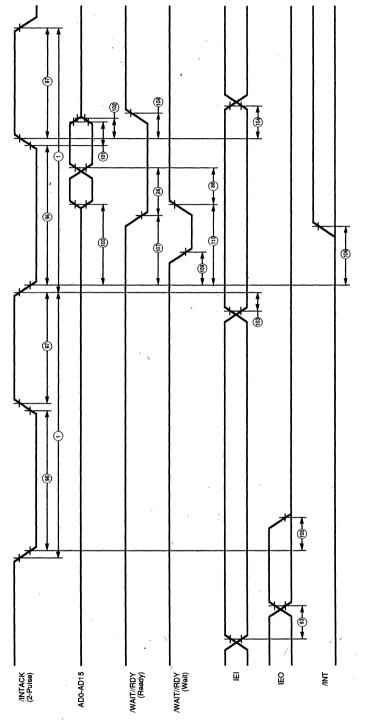

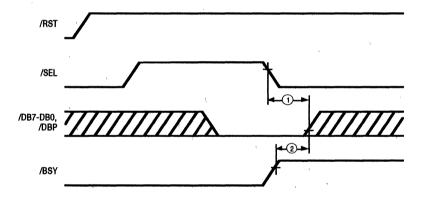

Figure 73. Multiplexed Double-Pulse Intack Cycle

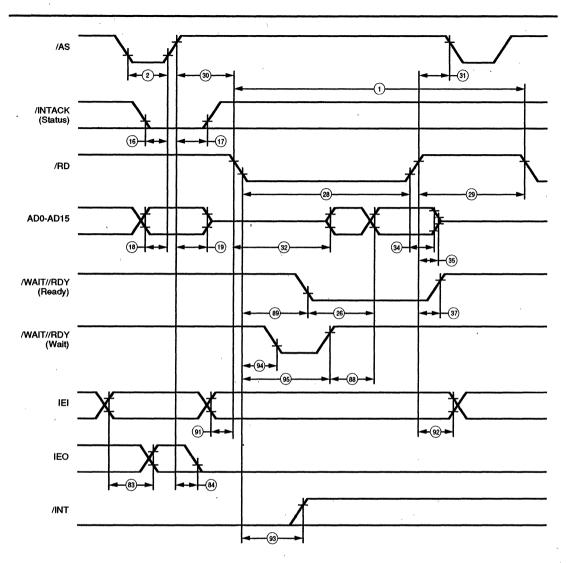

. "

•

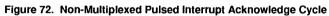

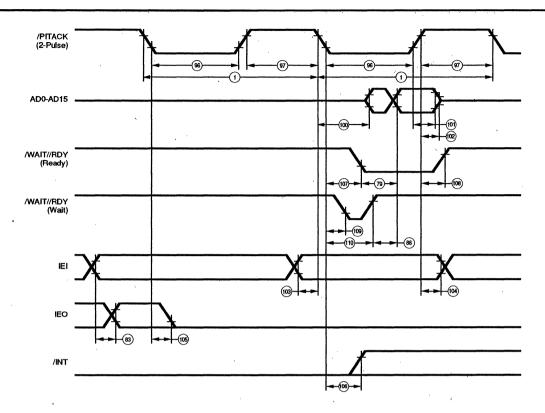

Figure 74. Non-Multiplexed Double-Pulse Intack Cycle

• .

.

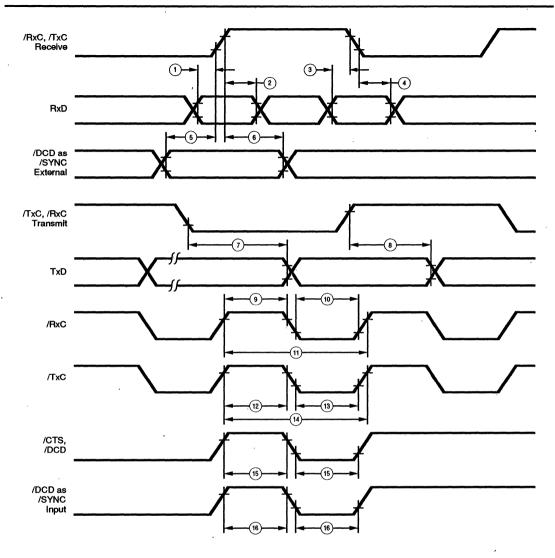

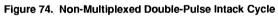

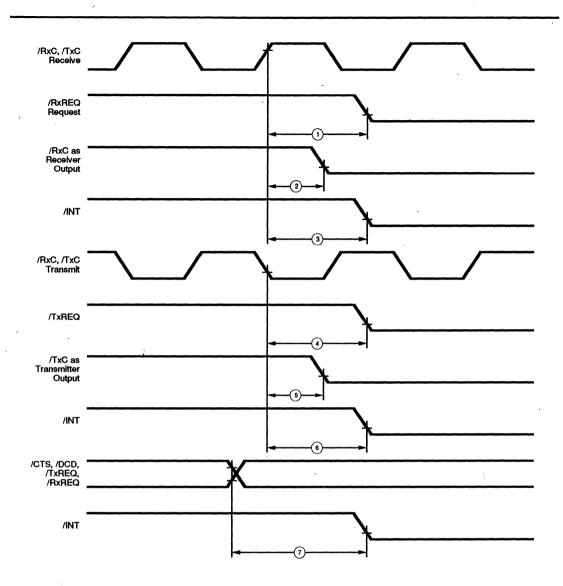

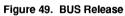

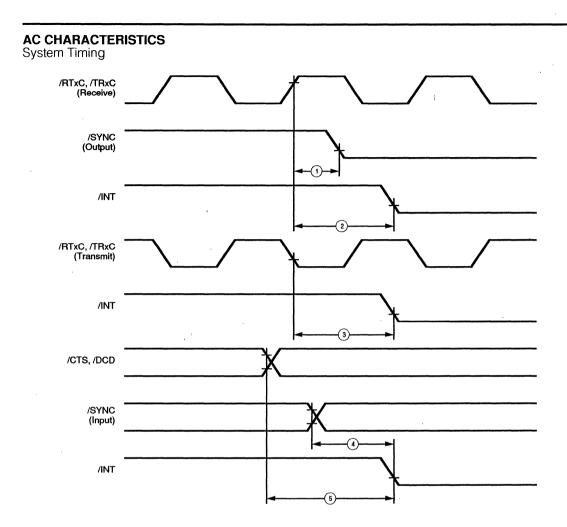

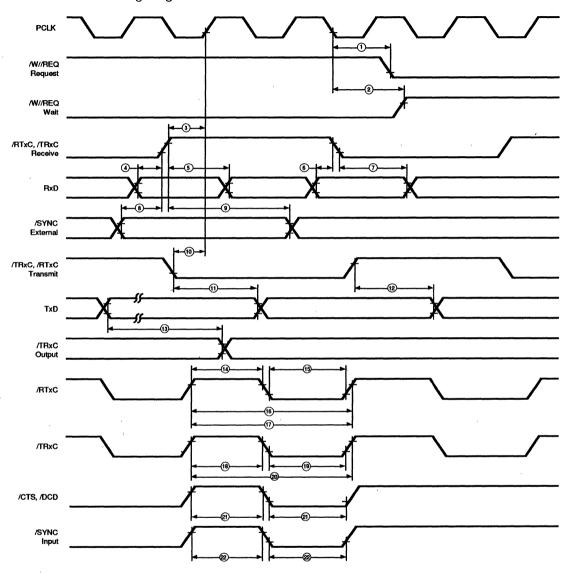

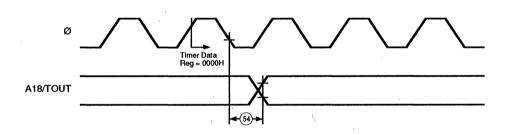

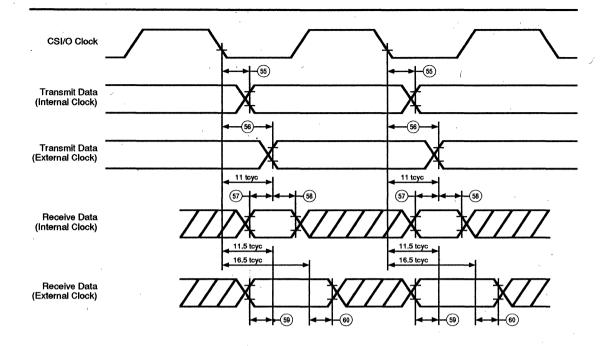

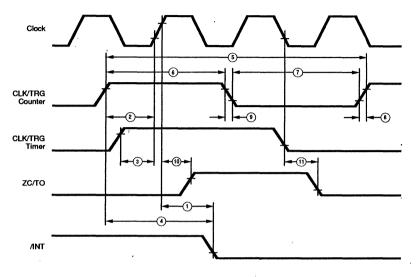

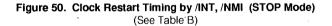

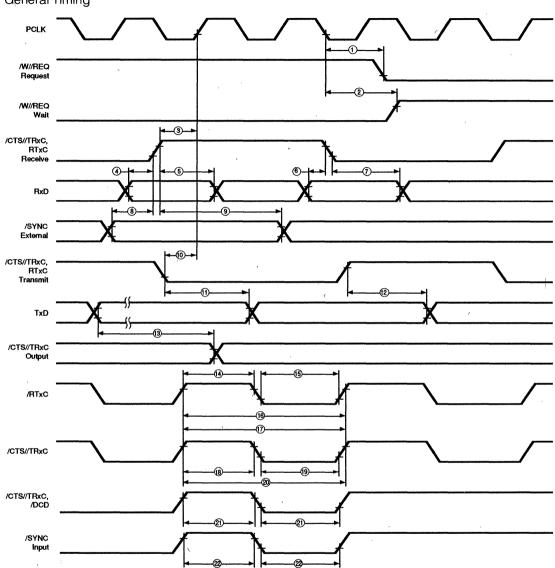

Figure 75. Z16C30 General Timing

## AC CHARACTERISTICS Z16C30 General Timing

| No | Symbol      | Parameter                                      | Min | Max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Units | Note                                      |

|----|-------------|------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------------------------|

| 1  | TsRxD(RxCr) | RxD to /RxC Rise Setup Time (x1 Mode)          | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ns    | [1]                                       |

| 2  | ThRxD(RxCr) | RxD to /RxC Rise Hold Time (x1 Mode)           | 40  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ns    | [1]                                       |

| 3  | TsRxd(RxCf) | RxD to /RxC Fall Setup Time (x1 Mode)          | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ns    | [1,3]                                     |

| 4  | ThRxD(RxCf) | RxD to /RxC Fall Hold Time (x1 Mode)           | 40  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ns    | [1,3]                                     |

| 5  | TsSy(RxC)   | /DCD as /SYNC to /RxC Rise Setup Time          | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ns    | [1]                                       |