# DESIGN SOFTWARE MANUAL

C

# DESIGN SOFTWARE MANUAL

1985 EDITION

PUBLISHED BY ZyMOS CORPORATION 477 N. MATHILDA AVENUE SUNNYVALE, CA 94086

C Copyright 1985, ZyMOS Corporation, Sunnyvale, Ca. All Rights Reserved ZyMOS Corporation believes the information contained herein to be accurate and reliable, however ZyMOS Corporation makes no warranty for the use of this documents contents and assumes no responsibility for any errors which may appear in the document, nor does it make a commitment to update this information. ZyMOS retains the right to make changes to the information or specifications contained herein at any time, without notice.

e de la competencia d

ZyP is a trademark of ZyMOS Corporation.

PRIMOS is a trademark of Prime Computer, Inc.

VAX and VMS are trademarks of Digital Equipment Corporation

TYMNET is a trademark of Tymnet Inc.

| Zyp Design System Introduction          | 1  |  |  |  |

|-----------------------------------------|----|--|--|--|

| Zypnet-Prime User's Guide               | 2  |  |  |  |

| Zypnet-Vax User's Guide                 | 3  |  |  |  |

| Zypsim User's Guide                     | 4  |  |  |  |

| Zypsim Reference Manual                 | 5  |  |  |  |

| Zypsim Test Language Manual             | 6  |  |  |  |

| Zyp Specification and Test User's Guide | 7  |  |  |  |

| Zytest User's Guide                     | 8  |  |  |  |

| Zyspec User's Guide                     | 9  |  |  |  |

| Zypee User's Guide                      | 10 |  |  |  |

| Mailbox User's Guide                    | 11 |  |  |  |

| ZL User's Guide                         | 12 |  |  |  |

| Zymem User's Guide                      | 1  |  |  |  |

| Zyprom User's Guide                     |    |  |  |  |

| Zyce User's Guide                       | 1  |  |  |  |

| Zyspice User's Guide                    | 1  |  |  |  |

| Zyspice Reference Manual                | 1  |  |  |  |

| Zypart Reference Manual                 | 1  |  |  |  |

| Zypar Reference Manual                  | 1  |  |  |  |

ZyP DESIGN SYSTEM

## **ZyP DESIGN SYSTEM INTRODUCTION**

ZyMOS Corporation believes the information contained herein to be accurate and reliable, however ZyMOS Corporation makes no warranty for the use of this documents contents and assumes no responsibility for any errors which may appear in the document, nor does it make a commitment to update this information. ZyMOS retains the right to make changes to the information or specifications contained herein at any time, without notice.

ZyP is a trademark of ZyMOS Corporation.

(C) Copyright 1981, 1982, 1983, 1984 ZyMOS Corporation.

| 20-010-001 Rev: G Issued: August 1984 |

|---------------------------------------|

|---------------------------------------|

ZYMOS CORP., 477 NO. MATHILDA AVE., SUNNYVALE, CA. P.O. BOX 62379, SUNNYVALE, CA 54065 TEL. (406) 730-8600. TWX 910-339-6530 ZYMOS SUVL

#### List of effective pages

#### PAGE

#### REVISION

| TitleRev: G                 |  |

|-----------------------------|--|

| Cable of ContentsRev: G     |  |

| Pages 1-1 through 1-2Rev: G |  |

| Pages 2-1 through 2-3.      |  |

| Page 3-1Rev: G              |  |

| Pages 4-1 through 4-2Rev: G |  |

| Pages 5-1 through 5-3Rev: G |  |

| Page 6-1Rev: G              |  |

| °age 7-1Rev: G              |  |

| Page 8-1Rev: G              |  |

na de la constante El Marine de Cartes El Dinas de Cartes des

Doc: 20-010-001 Rev: G

Start Pr

PRIMOS is a trademark of Prime Computer, Inc.

VAX and VMS are trademarks of Digital Equipment Corporation

TYMNET is a trademark of Tymnet Inc.

ZyP is a trademark of ZyMOS Corporation

and the operation of the second se

a seren por a seren en en estado en el como de la como d La como de la Seren de la como de la c

### TABLE OF CONTENTS

| 1 | OVERV                         | IEW                                                                                     |                               |  |  |  |  |

|---|-------------------------------|-----------------------------------------------------------------------------------------|-------------------------------|--|--|--|--|

| ~ | 2 Zyp System documentation2-1 |                                                                                         |                               |  |  |  |  |

| 2 |                               |                                                                                         | 20-010-1012-1                 |  |  |  |  |

|   | 2 2 2                         |                                                                                         |                               |  |  |  |  |

|   | 2.2 2                         | ZYPNET PRIME USER'S MANUAL                                                              | 20-010-1032-1                 |  |  |  |  |

|   | 2.3 2                         | ZYPNET PRIME USER'S MANUAL<br>Zy40000 SERIES CMOS CELL LIBRARY<br>Zyspicz usepis Manual | 20-010-1072-1                 |  |  |  |  |

|   | C.7 (                         | LYSFICE USER'S MANUAL                                                                   | 20-010-1082-1                 |  |  |  |  |

|   |                               | ZyPSIM USER'S MANUAL                                                                    | 20-010-1092-1                 |  |  |  |  |

|   |                               | LyP SPECIFICATION AND TEST USER'S MANUAL                                                | 20-010-1102-1                 |  |  |  |  |

|   |                               | Zy40000 ANALOG CMOS CELL LIBRARY                                                        | 20-010-1112-2                 |  |  |  |  |

|   |                               | ZyCOMP-4 USER'S MANUAL                                                                  | 20-010-1122-2                 |  |  |  |  |

|   | -                             | ZyPLIB - MEMORIES                                                                       | 20-010-1142-2                 |  |  |  |  |

|   |                               | ZyPART USER'S MANUAL                                                                    | 20-010-1152-2                 |  |  |  |  |

|   |                               | ZyP UTILITIES                                                                           | 20-010-1162-2                 |  |  |  |  |

|   |                               | Ly50000 SERIES CHMOS CELL LIBRARY                                                       | 20-010-1172-2                 |  |  |  |  |

|   |                               | ZyPNET VAX USER'S MANUAL                                                                | 20-010-1182-2                 |  |  |  |  |

|   |                               | Zy80C49 USER'S MANUAL                                                                   | 20-010-1192-3                 |  |  |  |  |

|   | 2.15 2                        | ZyP MACRO'S MANUAL                                                                      | 20-010-1212-3                 |  |  |  |  |

| 3 | ZVPNET                        |                                                                                         |                               |  |  |  |  |

| - |                               | ZYPNET DATA NETWORK                                                                     |                               |  |  |  |  |

|   |                               | ZYPNET VAX                                                                              |                               |  |  |  |  |

|   |                               | ZYPNET PRIME                                                                            |                               |  |  |  |  |

|   |                               |                                                                                         |                               |  |  |  |  |

| 4 |                               | CATION SOFTWARE SUMMARY                                                                 |                               |  |  |  |  |

|   |                               | ZyPSIM                                                                                  |                               |  |  |  |  |

|   |                               | ZySPICE                                                                                 |                               |  |  |  |  |

|   |                               | Zy PART                                                                                 |                               |  |  |  |  |

|   |                               | ZyTEST                                                                                  |                               |  |  |  |  |

|   |                               | LyP SOFTWARE UTILITIES                                                                  |                               |  |  |  |  |

|   | 4.6 M                         | MICROPROCESSOR DEVELOPMENT AIDS                                                         |                               |  |  |  |  |

| 5 | GETTIN                        | IG STARTED                                                                              | 5-1                           |  |  |  |  |

| 2 |                               | COMPUTER SYSTEM                                                                         |                               |  |  |  |  |

|   |                               | 5.1.1 OPERATING SYSTEM                                                                  |                               |  |  |  |  |

|   | -                             | 5.1.2 FILE STRUCTURE                                                                    |                               |  |  |  |  |

|   | -                             | 5.1.3 EDITOR                                                                            |                               |  |  |  |  |

|   |                               | 5.1.4 LOGGING IN                                                                        |                               |  |  |  |  |

|   |                               | CELL LIBRARIES                                                                          |                               |  |  |  |  |

|   |                               |                                                                                         |                               |  |  |  |  |

|   |                               | 5.2.1 Zy40000 SERIES CMOS CELL LIBRARY                                                  |                               |  |  |  |  |

|   |                               | 5.2.2 Zy50000 SERIES CHMOS CELL LIBRARY                                                 |                               |  |  |  |  |

|   |                               | SIMULATION.                                                                             |                               |  |  |  |  |

|   | 2.4 A                         | ADDITIONAL DETAILS                                                                      | ••••••••••••••••••••••••••••• |  |  |  |  |

~

|   | DESIGN COMPLETION | 1 |

|---|-------------------|---|

| 7 | SUMMARY7-         | 1 |

| 8 | APPENDICES        | 1 |

#### 1 OVERVIEW

Welcome to ZyP. ZyP is a state-of-the-art, standard cell, computer aided design system specifically developed by ZyMOS for the design of custom circuits. ZyP is a user friendly software system which includes application rograms and libraries, linked through an integrated data base, to facilitate custom circuit development. ZyP has been operational since 1981 and includes many advanced features and technologies such as memory compilers, core microprocessors, analog MOS, and CHMOS. All ZyP applications software has been developed by ZyMOS specifically for standard cell design. This software is readily available to users via time-share facilities and is also available under license.

Central to the ZyP system is a library of standard cells. Electrical and topological cell data is manipulated by ZyP to verify network performance and to generate network artwork used in the custom circuit manufacturing cycle.

Standard cells offer advantages by being pre-defined. One important advantage is the ability to electrically characterize cell performance at the silicon level. When a set of cells is used in a custom circuit, the electrical data is used to verify cell operation in the network environment and accurately simulate silicon level network performance.

opment time and cost. But in addition, it offers

the flexibility required to maintain a competitive edge. No restrictions on number or types of cells incorporated in a specific circuit is imposed. No new structured design methodology or actual silicon layout design will be required or implied. Rather, the user is supported, at his own facility, at low cost, without the need for special equipment, in the design of systems. ZyP translates systems to silicon.

Cells range from simple to complex, standard to custom, analog to digital. Each has a detailed data sheet and each is incorporated in a number of different applications libraries. Cells are provided in the basic ZyMOS CMOS production technologies,

- Zy40000 Silicon Gate CMOS

- Zy50000 Silicon Gate CHMOS

Extensive ZyP documentation has been developed to assist users in understanding the ZyP system, learning how to apply ZyP to custom circuit development, and as reference documents. ZyP documentation is routinely updated and enhanced. We welcome your suggestions and comments.

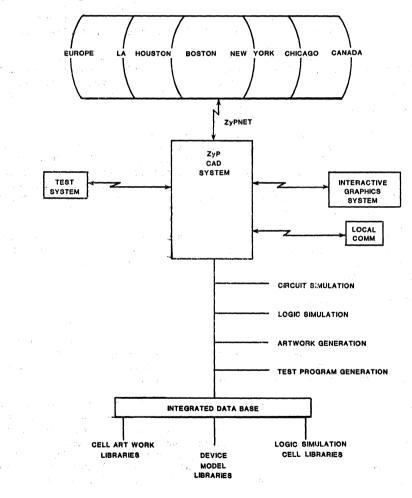

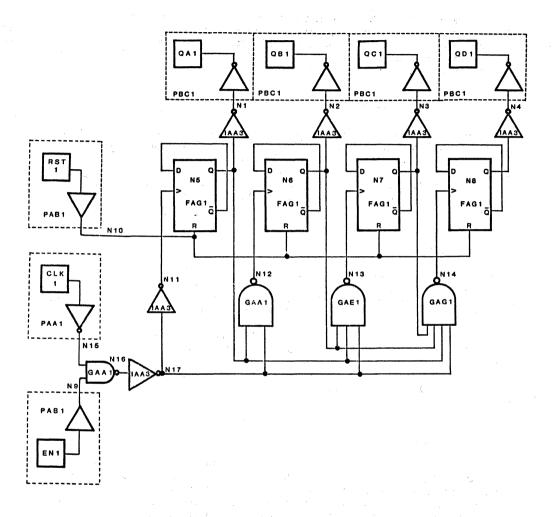

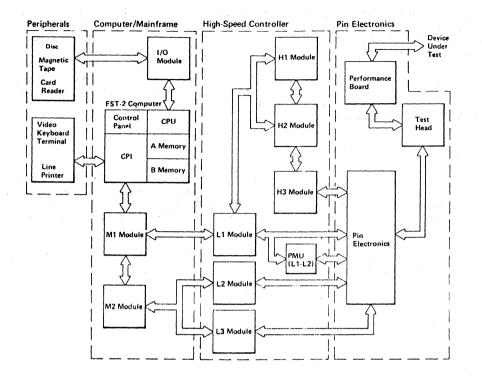

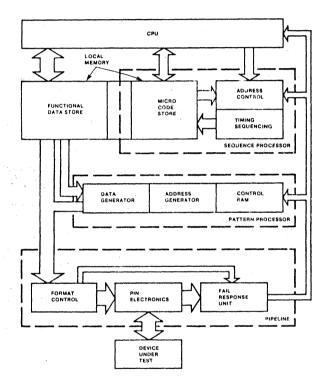

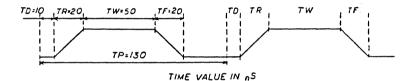

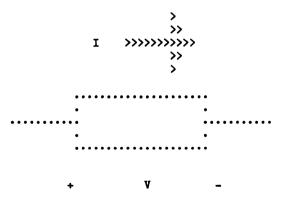

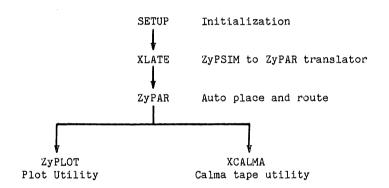

A functional ZyP overview is presented in Figure 1. At the top of the figure, a graphical presentation is made of ZyPNET. ZyPNET is an international data network used to access the ZyP design system. The lower portion of Figure 1 shows the software programs and application libraries which comprise the ZyP system. Circuit simulation (ZySPICE), logic simulation (ZyPSIM), artwork generation (ZyPART), and test program generation (ZyTEST) software packages are linked via an integrated data base to cell libraries and device models.

Doc: 20-010-001 Rev: G

Introduction

Initially, users will spend most of their time studying cell data sheets and describing networks to the logic simulator. ZyMOS will transfer the network file, after verification, over ZyPNET to complete the composite generation and test program.

The overall objective of ZyP is to provide the tools, techniques, and design technology data base required to successfully design custom CMOS integrated circuits. There are few restrictions, but there are rules and the need for good design practices. The designer must invent, innovate, and interpret -ZyP will analyze, verify, and check.

The remaining sections of the ZyP System Introduction summarize the ZyP system documentation, ZyPNET, applications software, how to get started, and how to complete a design.

#### FIGURE 1. Zyp SYSTEM OVERVIEW

Doc: 20-010-001 Rev: G

1-2

August 1984

#### ZyMOS Corporation

#### Introduction

#### 2 ZyP SYSTEM DOCUMENTATION

ZyP system documentation is organized into various documents, some of which have several volumes. The documents are numbered 20-010-1XX and each focuses on a specific area of ZyP. The beginning user should read this Introduction and the ZyP Preparation Guide in 20-010-101, study ZyPNET VAX or Prime for accessing ZyP, study ZyPSIM in 20-010-109, and review the desired cell library.

The following is a summary description of the ZyP documents.

#### 2.1 ZyP DESIGN SYSTEM INTRODUCTION, DOC: 20-010-101

The ZyP Design System Introduction provides an overview of the ZyP system with summaries of the system software. It also includes a ZyP Preparation Guide with guidelines for starting your ZyP design.

#### 2.2 ZyPNET PRIME USER'S MANUAL, DOC: 20-010-103

The ZyPNET Prime User's Manual includes an introduction on accessing ZyP on the ZyMOS Prime computer. Also included are the Prime User's Guide, PRIMOS operating system reference guide, and the PRIMOS editor reference guide.

#### 2.3 Zy40000 SERIES CMOS CELL LIBRARY, DOC: 20-010-107

The Zy40000 Series CMOS Cell Library contains silicon gate CMOS design data, examples, and cell library data sheets.

اردار با المحرية الرام

# 2.4 ZySPICE USER'S MANUAL, DOC: 20-010-108

The ZySPICE User's Manual includes an overview on using ZySPICE, a description of the ZyMOS process models, and the ZySPICE reference manual.

#### 2.5 ZyPSIM USER'S MANUAL, DOC: 20-010-109

The ZyPSIM User's Manual includes an overview of the ZyMOS generated ZyPSIM MOS logic simulator and the ZyPSIM reference manual. A document on the ZyPSIM Test Language is also included.

#### 2.6 ZyP SPECIFICATION AND TEST USER'S MANUAL, DOC: 20-010-110

The ZyP Specification and Test User's Manual provides ZyP device specification forms, a user's guide on design criteria and requirements for test, and the ZyTEST User's Manual. Also provided is the ZySPEC User's Guide.

2-1

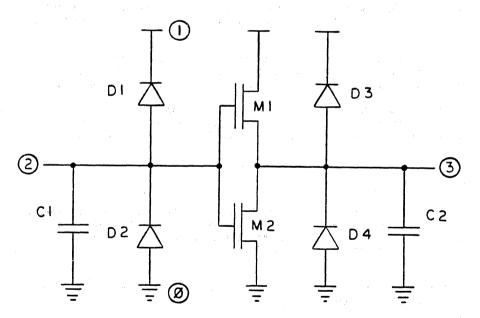

#### 2.7 Zy40000 SERIES ANALOG CMOS CELL LIBRARY, DOC: 20-010-111

The Zy40000 Series Analog Cell Library contains design data, examples, and cell data sheets for the analog cell library. Analog design is one of the advanced ZyP features and enables integration of mixed analog and digital See Subsystèmes. Sciences de la grande de la grande de la construcción de la construcc

### 2.8 ZyCOMP-4 USER'S MANUAL, DOC: 20-010-112

The ZyCOMP-4 User's Manual contains a detailed description of the ZyCOMP-4 4 bit core processor cell, the ZYCOMP4 cross assembler, and the ZYCOMP-4 Emulator Board User's Guide. ZyCOMP-4 is a general purpose 4 bit microprocessor implemented in the Zy40000 library. It has advanced architectural features including eight memory reference addressing modes, two index registers, and vectored interrupts. When integrated with RAM, ROM, and I/O cells, it becomes a powerful customer specific single chip computer.

#### 2.9 ZyPLIB - MEMORIES, DOC: 20-010-114

The ZyPLIB - Memory manual contains design data, examples, and cell data sheets for generating RAM, ROM, and PLA component macro cells. The ZyMEM User's Guide describes the procedure for memory element compilation. These memory 'super cells' can be combined with random logic, ZyCOMP-4, and other 'super cells' to integrate complex subsystems.

#### 2.10 ZyPART USER'S MANUAL DOC: 20-010-115

The ZyPART User's Manual contains user guides for the collection of composite generation software referred to as ZyPART. This document is only available with installations.

## 2.11 ZyP UTILITIES, DOC: 20-010-116

The ZyP Utilities Manual contains user guides for general ZyP utility programs. These include ZyPEE (ZyP Error Eliminator), MAILBOX, ZL, and various operating utilities.

#### 2.12 Zy50000 SERIES CHMOS CELL LIBRARY, DOC: 20-010-117

na shekara wa mwa na shekara kwa shekara kwa s

The Zy50000 Series CHMOS Cell Library contains design data, examples, and cell library data sheets for the Zy50000 CHMOS process.

#### 2.13 ZyPNET VAX USER'S MANUAL, DOC: 20-010-118

The ZyPNET VAX User's Manual includes an introduction on accessing ZyP on the ZyMOS VAX computer and the VAX/VMS Primer.

Doc: 20-010-001 Rev: G

#### 2.14 Zy80C49 USER'S MANUAL, DOC: 20-010-119

The Zy80C49 User's Manual contains a detailed description of the 80C49 core microprocessor cell. The Zy80C49 is a true mask compatible cell version of the standard 80C49 microcomputer. It is implemented in Zy50000 CHMOS technology and is fully compatible with the Zy50000 Series CHMOS Cell library as well as the 8749 EPROM device.

#### 2.15 ZyP MACRO'S MANUAL, DOC: 20-010-121

The ZyP MACRO'S manual contains design information, examples, and datasheets for the ZyP Predefined Macro's library. This library contains logic equivalent functions for the 7400 series TTL and 4000B series CMOS standard product IC's in both Zy50000 CHMOS and Zy40000 CMOS technologies.

ان از میکند کرد. با این میکند به میکند به میکند با میکند کار میکند با از میکند با از میکند به این میکند. از مان از میکند کرد به میکند به میکند با این میکند به میکند با این میکند با از میکند به میکند کرد. میکند و میکن از مان میکند به میکند به میکند با این میکند به میکند به میکند به میکند کرد. از میکند میکند به میکند میکند میکند میکند به میکند میکند به میکند میکند میکند. میکند میکند م

a Na shekara n

#### **3 ZyPNET**

The term ZyPNET refers to the data network and computer resource used to access and execute ZyP designs. ZyPNET references the network developed by ZyMOS but it can also reference a network established for a specific company. The terms ZyPNET VAX and ZyPNET Prime refer specifically to the VAX and Prime versions of ZyPNET and both are currently available at ZyMOS.

#### 3.1 ZyPNET DATA NETWORK

The ZyPNET data network is implemented via Tymnet at 300 and 1200 baud. Accessing the system requires only a user terminal, modem, and printer.

#### 3.2 ZyPNET VAX

The ZyMOS VAX computer system is available to ZyP users for executing ZyP designs in a time share environment. Users have access to the various ZyP applications programs, libraries, and utilities. Upon completion of a design, ZyMOS will transfer the user's design files to an in-house directory for artwork (ZyPART) generation and test program completion.

Document 20-010-118 provides detailed information on ZyPNET VAX.

#### 3.3 ZyPNET PRIME

The ZyMOS Prime computer system is also available to ZyP users for executing ZyP designs in a time share environment. Selection between VAX and Prime is at the user's discretion. Users have access to the various ZyP applications programs, libraries, and utilities. Please contact ZyMOS as to the availability of specific software modules or releases.

Document 20-010-103 provides detailed information on ZyPNET Prime.

. Meeters of

g Bargeta 🐻

ا الإسلام المادة في المادة المحلة المادة الأنونية مسائلا من ويعم المحلة على المادة العمر المعلم المعلم الأردي ا المادة الإيرانية المحلة العليم المحلة المحلة المحلة المحلة المحلة المحلة المحلة المحلة المحلة المعلم الأمان الم المحلة المحل المحلة المحلة

しょうがい あきに 名にる あが

and the second second

an an Arran Arra an Arra. Arra an Arra an

الا المستحكم المستحك المستحكم الم المستحكم الم المستحكم الم

and the second second

#### **4 APPLICATION SOFTWARE SUMMARY**

ZyP is a software system which links, via an integrated data base, various software modules and cell oriented applications libraries for the purpose of verifying designs and automating the artwork and test program generation process. The following is a summary of the basic software modules. Many additional software modules are available such as ZyPEE, ZyMEM and ZySPEC, which are described elsewhere in the ZyP documentation.

#### 4.1 ZyPSIM

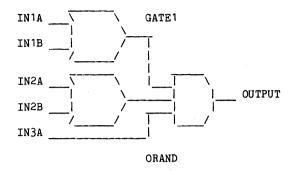

ZyPSIM is a ZyMOS proprietary general purpose MOS logic simulator specifically developed for the ZyP system. It is supported with standard cell model libraries enabling networks of standard cells to be simulated based on actual standard cell performance.

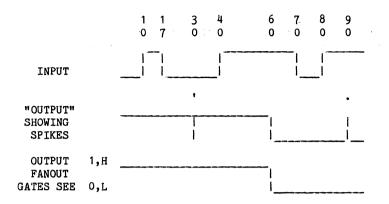

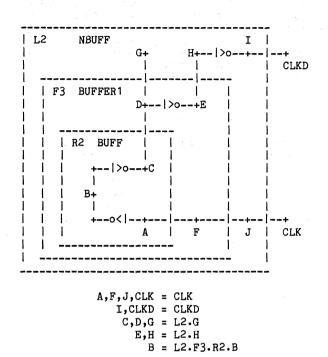

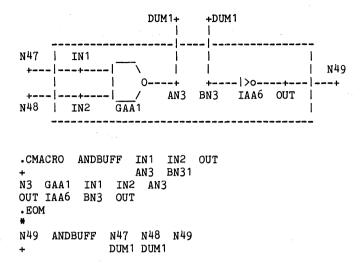

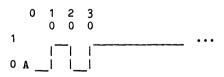

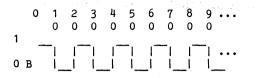

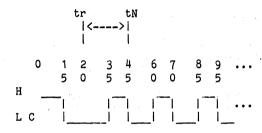

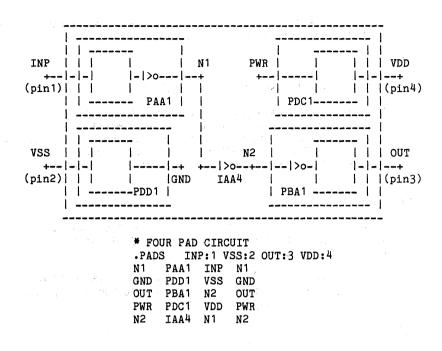

The logic simulator is the primary interface between the user and the ZyP system. Simulation of a network is the main design verification tool for ZyP based designs. Accurate simulation of a network of standard cells guarantees IC functionality and establishes IC dynamic performance capability. In addition to logic simulation, the ZyPSIM network file is used as the source data file for artwork generation. The simulation output file is used for test program development. ZyPSIM supports numerous sophisticated design features including hierarchical design, artwork capacitance estimation, and guardbanding over different operating conditions.

Document 20-010-109 provides detailed information on ZyPSIM.

#### 4.2 ZySPICE

ZySPICE is a ZyP variant of the UC Berkeley generated SPICE circuit simulator. It includes model modifications and model files for the ZyMOS production processes. ZySPICE supports DC and TRANSIENT analysis of transistor level circuits.

Document 20-010-108 provides detailed information on ZySPICE.

#### 4.3 ZyPART

ZyPART is a set of ZyMOS proprietary programs which convert a logic simulator network file to circuit artwork used in the tooling generation cycle.

Document 20-010-115 provides detailed information on ZyPART.

4-1

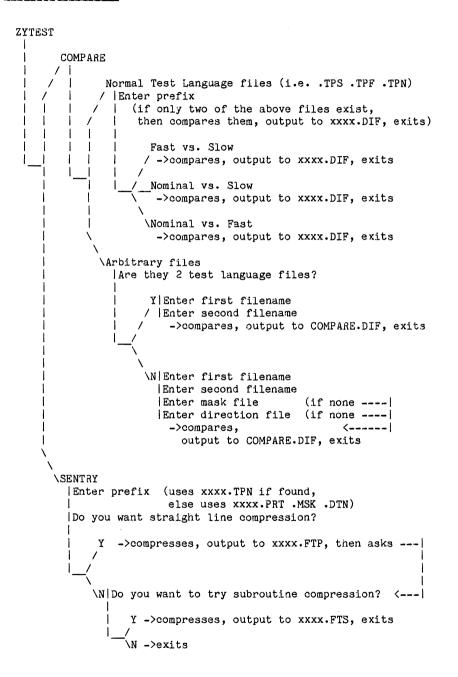

#### 4.4 ZyTEST

ZyTEST is a set of ZyMOS proprietary software modules which process the ZyPSIM output file, translate the data to Fairchild Sentry compatible code, and compact the file to minimize test vectors. ZyTEST also allows users to compare simulation output files to verify design guardbanding for voltage and temperature extremes.

Document 20-010-110 provides detailed information on ZyTEST.

#### **4.5 ZyP SOFTWARE UTILITIES**

- ZyPEE: ZyPEE is the ZyP Error Eliminator, it is the ZyMOS expert system software. ZyPEE can analyze a circuit's network description and identify complex design errors with respect to IC design technique, IC testing, mask generation, and production.

- ZyMEM: ZyMEM is a powerful memory compiler program enabling the user to automatically generate RAM, ROM, and PLA circuits. From a high level organizational description (ex; # of words, # of bits/word, etc.) ZyMEM will create the logic coding, mask information, programming files, and datasheets, for the user's specific memory.

- ZL: ZL provides Prime user's the capability to display the ZyPSIM Logic Simulation Models for all standard cells.

- ZySPEC: ZySPEC will automatically generate a circuit specification for a ZyP standard cell: IC. This specification fully defines a ZyP circuit for production and test.

- BUGME: BUGME is a convenient tool for ZyPNET Prime users for reporting and documenting the occasional ZyP system software bug. It automatically notifies the ZyP Design Support staff of your need for assistance.

#### 4.6 MICROPROCESSOR DEVELOPMENT AIDS

ZyMOS offers numerous development tools in support of our microprocessor core cells. Included are assemblers such as the ZyPCOMP4 (ZyCOMP4 uP), and the ASM49 (80C49), data transfer and formatters such as ZyPROM and ZyCE, and hardware emulator boards for use with commercially available development systems.

Doc: 20-010-001 Rev: G

#### **5 GETTING STARTED**

Having gained some familiarity with what ZyP is about, the next step is to start applying the system. It is recommended that beginning users follow the procedure outlined below.

#### 5.1 COMPUTER SYSTEM

ZyP is available on ZyPNET VAX or Prime or an equivalent in house computer system. Having defined your host system, review the following information in the appropriate document.

#### 5.1.1 OPERATING SYSTEM

The computer operating system is a general purpose utility that assigns resource (eg storage) and applications software to the user. For VAX, the operating system is called VMS and for Prime, it is called PRIMOS.

The introductory document for VMS is the VAX/VMS Primer located in document 20-010-118. The introductory document for PRIMOS is The Prime User's Guide, located in document 20-010-103. These introductory guides should be studied to familiarize the user with the appropriate operating system.

#### 5.1.2 FILE STRUCTURE

Files in general are lines (or strings) of text which have some collective meaning and must be preserved. For example, a network description is a file. VMS and PRIMOS assume a certain file structure which should be understood and is discussed in the introductory guides referenced above.

#### 5.1.3 EDITOR

Editors are used for creating and modifying files. Once the operating system and file structure are understood, the editor is invoked to create a new user file. The VMS editor EDT is described in the VAX/VMS Primer. This is a screen and line editor. To use the screen editor, you must have a VT100 terminal or equivalent. The line editor is compatible with most standard terminals. The PRIMOS editor is described in The New User's Guide to Editor and Runoff in document 20-010-103. This is a line editor only. New users should familiarize themselves with the creation, editing, and saving of files as described in the reference documents.

# 5.1.4 LOGGING IN

Once the items discussed above have been studied the user can access the target system by following the log-in procedure described in the Introduction section of the appropriate ZyPNET document. To access the system, you must have a password assigned by ZyMOS. It is recommended that you try logging in to understand the log-in procedure and verify your password. It is also suggested that you create, save, and reaccess a file using the editor.

ZyPNET VAX and Prime are available to users over Tymnet. The user should have a 24 line, 80 character per line terminal and a 300 or 1200 baud modem. The terminal should be configured for 8 bit word length, 1 stop bit, no parity, and full duplex. The modem should be Bell 103 compatible at 300 baud or Bell 212A at 1200 baud. A printer connected to the terminal printer port is also a necessity.

Contact ZyMOS ZyP Applications for Tymnet and ZyPNET access codes as well as assistance with any login problems.

#### 5.2 CELL LIBRARIES

Having gained an understanding of operating systems and accessing ZyP, the next step is to review the cell libraries and generic data for the desired technology. The standard ZyP technologies are as follows.

#### 5.2.1 Zy40000 SERIES CMOS CELL LIBRARY

The Zy40000 silicon gate CMOS technology is a high performance isoplanar bulk CMOS process using 5u design rules. It provides approximately twice the performance of metal gate CMOS with a 40% increase in density. This process operates from 1.1 to 6 volts, -55 to 125 degree C. Document 20-010-107 provides cell data sheets and process generic data.

#### 5.2.2 Zy50000 SERIES CHMOS CELL LIBRARY

The Zy50000 silicon gate CHMOS technology is a high performance, Nwell, CMOS process. It provides up to a 40% increase in performance over the 5u CMOS process with a substantial increase in density. The CHMOS process operates from 2 to 6 volts, -55 to 125 degree C. Document 20-010-117 provides cell data sheets and process generic data.

#### 5.3 SIMULATION

The ZyP system provides simulation software design aids for the circuit designer. The simulators use predefined process models (ZySPICE) and cell models (ZyPSIM) to simplify the designer's task and permit him to concentrate on design while the computer automates analysis. The ZyP simulators are the primary user interfaces to the ZyP system. Two ZyP manuals are provided as tutorial and reference documents on using the simulators. The user should study the appropriate documents and become familiar with the capabilities, commands, files, and operation of the simulators for application to the design task.

#### 5.4 ADDITIONAL DETAILS

A ZyP Preparation Guide is available which provides background information along with a simple, detailed example of the procedure for beginning a ZyP IC design. The ZyP Preparation Guide is located in the ZyP Design System Introduction, Doc: 20-010-101.

المجموع من المحمد ال المحمد المحمد

#### 6 DESIGN COMPLETION

One of the primary advantages of ZyP design is being able to routinely integrate full custom designs successfully, quickly, and economically. ZyMOS has established a number of formalized procedures and forms to support design completion. The forms (with the exception of the ZyP device specification) are located in the Appendix and should be copied as needed. Each is summarized below.

#### 6.1 SPECIAL CELL DEFINITION

The user should make every effort to utilize existing standard cells to complete the design. However, specific designs may require cells which are not available. ZyMOS designates these as special cells, where a special cell is either a standard cell not currently in the library or a custom cell. The Special Cell Definition form is provided to allow users to define special cells.

#### 6.2 ZyP DEVICE SPECIFICATION

ZyP device specifications are generated for the user by the application program ZySPEC. ZySPEC should be run at the conclusion of the design to generate a final IC specification document.

#### 6.3 Zyp File TRANSFER CHECKLIST

The ZyP File Transfer Checklist is the formal transfer form. Acceptance of this form by the user and ZyMOS initiates the integration process and guarantees proper completion of all necessary tasks.

#### 6.4 ZyP BUG REPORT

ZyMOS has extensively tested all applications software and libraries. However, we recognize that with a design system of the complexity of ZyP, bugs may occur. The ZyP online utility, BUGME, is provided to assist the reporting of bugs as well as their correction. The ZyP Bug Report form in the appendices is an overlay of the report generated by BUGME.

and the state of the state of the

#### 7 SUMMARY

ZyP opens a new dimension in custom circuit development. It assists design, tooling, and production. Production is guaranteed. Pricing is determined up front. Alternate technologies are available. Access is worldwide. Welcome to the system which is setting the standard in custom VLSI.

ZyMOS is committed to ZyP. We are developing new libraries, new technologies, and new software tools. ZyP is your long term VLSI solution.

#### 8 APPENDICES

Forms described in section 6 follow and can be copied as needed.

magna 1999 - Charles Martin, an Albert an State and State 1999 - State and State 1999 - State and State

| ZyMOS CORPORATION<br>477 N. Mathilda Ave. SPECIAL CELL DEFINITION<br>Sunnyvale, CA 94086 (Send c/o ZyP™ Marketing Mgr.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ZyP™ DESIGN SYSTEM  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--|--|--|--|

| COMPANY NAME:ADDRESS:<br>PURCHASING CONTACT:<br>TECH. CONTACT:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Tel#<br>Tel#        |  |  |  |  |

| PROCESSOPERATING TEMP<br>OPERATING VOLTAGEMAX. FREQUENCY<br>SPECIAL SPECS/REQUIREMENTS (Attach ZySPICE simulation for model generation)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                     |  |  |  |  |

| CIRCUIT DIAGRAM (Show port diagram, logic diagram, and transistor level circuit diagram<br>with device sizes. Use reverse side if necessary)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                     |  |  |  |  |

| TO BE COMPLETED BY ZyMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                     |  |  |  |  |

| MKT RECEIVED DATE:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:BY:_BY: | ORK AVAIL:<br>OVAL: |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     |  |  |  |  |

a second a s A second a se A second a s

CIRCUIT DIAGRAM:

.

and the second second

. . .

|                                                                                                                                                                                                                                                                                                                                                                                                | ZyP FILE SUBMITTAL CHE |                    |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------------|--|--|--|

| ZyMOS CORPORATION<br>477 N. Mathilda Ave.                                                                                                                                                                                                                                                                                                                                                      |                        | ZyP DESIGN SYSTEM  |  |  |  |

| Sunnyvale, CA 94086                                                                                                                                                                                                                                                                                                                                                                            |                        | (408) 730-8800     |  |  |  |

| (Please                                                                                                                                                                                                                                                                                                                                                                                        | send c/o ZyP Marketing | ; Program Mgr.)    |  |  |  |

| CUSTOMER NAME:                                                                                                                                                                                                                                                                                                                                                                                 | C                      | USTOMER CHIP NAME: |  |  |  |

| ADDRESS:                                                                                                                                                                                                                                                                                                                                                                                       |                        |                    |  |  |  |

| PURCHASING CONTACT:                                                                                                                                                                                                                                                                                                                                                                            |                        | TELEPHONE:         |  |  |  |

| TECHNICAL CONTACT:                                                                                                                                                                                                                                                                                                                                                                             |                        | TELEPHONE:         |  |  |  |

| STANDARD ZyP                                                                                                                                                                                                                                                                                                                                                                                   | SPECI                  | AL ZyP             |  |  |  |

| Files Transferred:                                                                                                                                                                                                                                                                                                                                                                             | chip.SPC               | chip.COM           |  |  |  |

| NET File Requirements      No ZyPSIM primitives (except CAP)      PADS included for pinout        All telescoping cells defined as macros      TPRINT statement - ordered pin list        No node names greater than 23 characters      GUARDBAND included        NORUN and .NOSPIKE included      ZyPEE verification complete        INPUT included for capacitance estimation      ZyPEC run |                        |                    |  |  |  |

| COMMENT File Requirements<br>Critical nets (capacitance, resistance, timing)<br>Customer data<br>Pin out options                                                                                                                                                                                                                                                                               |                        |                    |  |  |  |

| Documentation<br>ZyP format circuit schematic included (required)<br>Customer functional circuit description (optional)                                                                                                                                                                                                                                                                        |                        |                    |  |  |  |

| Test Requirements<br>Simulation run at guardband extremes<br>Total test time less than 5 seconds<br>Total test vectors less than 4K                                                                                                                                                                                                                                                            |                        |                    |  |  |  |

| Special Requirements<br>Special cell required<br>Memory (RAM, ROM, PLA), analog cells, or core processor<br>Non standard packaging<br>Non standard testing<br>If any of the above items are checked, contact the ZyP Marketing Project Manager prior<br>to net submission for schedule/cost information.                                                                                       |                        |                    |  |  |  |

| FILE ACCEPTANCE APPROVALS                                                                                                                                                                                                                                                                                                                                                                      |                        |                    |  |  |  |

| Approval (ZyMOS to complete)                                                                                                                                                                                                                                                                                                                                                                   |                        |                    |  |  |  |

| Signatures                                                                                                                                                                                                                                                                                                                                                                                     |                        |                    |  |  |  |

| CUSTOMER:                                                                                                                                                                                                                                                                                                                                                                                      | FILE SUBM              | IT DATE:           |  |  |  |

| ZyMOS Engineer:                                                                                                                                                                                                                                                                                                                                                                                | FILE ACCE              | PTANCE DATE:       |  |  |  |

| ZyMOS Mkt.:                                                                                                                                                                                                                                                                                                                                                                                    | # Grids:               | ZyMOS Device #     |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                |                        |                    |  |  |  |

المحكم المحكم

and the second

|                                          |         | and a          |           |

|------------------------------------------|---------|----------------|-----------|

| an a |         | t tagin the    | ar araa a |

|                                          |         |                |           |

|                                          |         |                |           |

|                                          | 80.00 C | tea 🦛 \cdots e |           |

|                                          |         |                |           |

and the second second

|                                         | Zyp BUG REPORT                                                                                                                                          |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                         | GENERAL INFORMATION                                                                                                                                     |

| COMPANY:                                | DATE:                                                                                                                                                   |

| NAME:                                   | PHONE NO                                                                                                                                                |

| ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | SOFTWARE INFORMATION                                                                                                                                    |

| Please check progra                     |                                                                                                                                                         |

| / 1 1 5 1                               | ZYPSIM MODELSZYSPICEZYSPICE MODELS<br>ZYPARTZYPEEZYP DOCUMENTATION<br>ase specify REV #)OTHER                                                           |

| INPUT FILES:<br>(.NET, etc.)            |                                                                                                                                                         |

| OUTPUT FILES:<br>(.PRINT, etc.)         |                                                                                                                                                         |

|                                         | EXPLANATION / COMMENTS                                                                                                                                  |

|                                         |                                                                                                                                                         |

|                                         |                                                                                                                                                         |

| ****                                    |                                                                                                                                                         |

| ····                                    |                                                                                                                                                         |

|                                         |                                                                                                                                                         |

|                                         |                                                                                                                                                         |

| ######################################  |                                                                                                                                                         |

|                                         |                                                                                                                                                         |

|                                         |                                                                                                                                                         |

| UF                                      | RGENCY OF SOLUTION (Please check one)                                                                                                                   |

| Major bug<br>Minor bug<br>Miscellaneo   | : Has halted project progress, immediate fix.<br>: Will prevent project completion, short term.<br>ous bug: Error that must be corrected, non-critical. |

| *******                                 | FOR ZyMOS INTERNAL USE ONLY                                                                                                                             |

| Bug I.D                                 |                                                                                                                                                         |

| To be fixed by:                         | Completion date:                                                                                                                                        |

| Disposition of soft                     | tware affected:                                                                                                                                         |

|                                         |                                                                                                                                                         |

| RETURN THIS FORM TO                     | 2: Zymos corporation (408)730-8800                                                                                                                      |

|                                         | D: ZYMOS CORPORATION (408)730-8800<br>477 N. MATHILDA AVE.<br>SUNNYALE, CA. 94084<br>ATTN: ZyP DESIGN SUPPORT                                           |

|                                         | ATTN: Zyp design support Rev. A 8/83                                                                                                                    |

ZyMos Corporation

```

ZyP Bug Report

6-1

в

1-1,1-2,

ZyP Design System

2-1,2-2,2-3,

BUGME

4-2,6-1

3-1, 4-1, 4-2,

5-1,5-2,5-3,

6-1,7-1,8-1

С

ZyP Device Specification

2-1,

1-1,5-2

Cell Libraries

6-1

3-1,5-1

ZyP File Transfer

6-1

Computer System

2-3

ZyP Macro's

2-1.5-3

D

ZyP Preparation Guide

ZyP Software Utilities

4-2

6-1

2-2

Design Completion

ZyP Utilities

1-1,2-2,3-1,4-1

ZyPART

2-2,4-1,4-2

Е

ZyPEE

ZyPLIB - Memories

2-2

2-1,5-1,5-2

1-1,1-2,3-1,5-2

Editor

ZyPNET

ZyPNET Data Network

3-1

F

ZyPNET Prime

2-1,3-1

2-1,2-2,3-1,5-1,5-2

ZyPNET VAX

1-1,2-1,4-1,4-2,5-3

File Structure

5 - 1

ZyPSIM

2-1, 4-1, 4-2, 6-1

ZySPEC

G

ZySPICE

1-1,2-1,4-1,5-3

1-1,2-1,4-2

ZyTEST

Getting Started

5-1

L

Logging In

5-2

М

Microprocessor 2-2,2-3,4-2

0

Operating System

2-1,5-1

Ρ

Prime

2-1,3-1,4-2,5-1,5-2

S

1-1,4-1,4-2,5-3

Simulation

Special Cell Definition

6-1

2 - 1

Specification and Test

z

2-2,4-2

ZL

Zy80C49

2-3

2-2

ZyCOMP-4

2-2, 4-1, 4-2

ZyMEM

```

n an Standard († 1997) 1970 - Maria Alexand, francés 1970 - Standard († 1997) 1970 - Standard († 1997) 1970 - Standard († 1997)

.

e Angelet (1997) - Steffinger (1997)

. .

| Zyp Design System Introduction          | 1  |

|-----------------------------------------|----|

| Zypnet-Prime User's Guide               | 2  |

| Zypnet-Vax User's Guide                 | 3  |

| Zypsim User's Guide                     | 4  |

| Zypsim Reference Manual                 | 5  |

| Zypsim Test Language Manual             | 6  |

| Zyp Specification and Test User's Guide | 7  |

| Zytest User's Guide                     | 8  |

| Zyspec User's Guide                     | 9  |

| Zypee User's Guide                      | 1( |

| MAILBOX USER'S GUIDE                    | 1  |

| ZL USER'S GUIDE                         | 1  |

| Zymem User's Guide                      | 1  |

| Zyprom User's Guide                     | 1  |

| Zyce User's Guide                       | 1  |

| Zyspice User's Guide                    | 1  |

| Zyspice Reference Manual                | 1  |

| Zypart Reference Manual                 | 1  |

| Zypar Reference Manual                  | 1  |

a da marina da cana da Mana da cana da Mana da cana da na se anna an taon an tao a Tao an and the second and start strate ten i kari n

## Zypnet prime user's guide

ZyMOS Corporation believes the information contained herein to be accurate and reliable, however ZyMOS Corporation makes no warranty for the use of this documents contents and assumes no responsibility for any errors which may appear in the document, nor does it make a commitment to update this information. ZyMOS retains the right to make changes to the information or specifications contained herein at any time, without notice.

ZyP is a trademark of ZyMOS Corporation.

(C) Copyright 1981, 1982, 1983, 1984 ZyMOS Corporation

Doc: 20-010-003 Rev: E

Issued: January 1984

<u>ZYMUS</u>

ZYMOS CORP., 477 NO. MATHILDA AVE., SUNNYVALE, CA. P.O. BOX (22379, SUNNYVALE, CA 94088 TEL. (408) 730-8800. TWX 910-339-9530 ZYMOS SUVL  $\frac{1}{2} \left[ \left( \frac{1}{2} - \frac{1}{2} \right) + \frac{1}{2} \left( \frac{1}{2} - \frac{1}{2} \right) \right]$

· •

j. Ar bankar a Ar bankar a

.

19 17 ZyMOS Corporation ZyPNET Prime User's Guide ZyP Design System

PRIMOS is a trademark of Prime Computer, Inc.

TYMNET is a trademark of Tymnet Inc.

ZyP is a trademark of ZyMOS Corporation.

.

### Table of Contents

| 1 | INTRODUCTION                                                                                                                                                                                             |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | LOGIN AND LOGOUT PROCEDURE                                                                                                                                                                               |

| 3 | FILE STRUCTURE.3-13.1 LISTING DIRECTORIES.3-13.2 CREATING NEW DIRECTORIES.3-13.3 ATTACHING TO A DIRECTORY.3-23.4 DELETING FILES.3-33.5 COPYING FILES.3-33.6 BASIC DIRECTORY AND FILE COMMAND SUMMARY.3-3 |

| 4 | EDITOR                                                                                                                                                                                                   |

| 5 | PRIMOS COMMANDS                                                                                                                                                                                          |

| 6 | APPLICATIONS PROGRAMS                                                                                                                                                                                    |

| 7 | JOB CONTROL7-17.1 BUILDING A ZyPSIM .NET FILE7-17.2 COMMAND FILES7-27.2.1 COMMAND INPUT7-27.2.2 COMMAND OUTPUT7-27.3 JOB CONTROL FILE7-37.4 JOB EXECUTION7-3                                             |

| 8 | SUMMARY                                                                                                                                                                                                  |

#

a de la companya de la comp

#### **1 INTRODUCTION**

The ZyPNET Prime User's Guide introduces the Prime version of ZyPNET. The term ZyPNET refers to the data network and computer resource used to access the ZyP system and execute ZyP designs. ZyPNET references the network developed by ZyMOS and it can also reference a network established for a specific company. The term ZyPNET-Prime refers specifically to the Prime version of ZyPNET (ZyPNET-VAX is an alternate version) and is available at ZyMOS.

The ZyP system can be accessed over voice-grade phone lines using a standard terminal. A typical configuration consists of a CRT terminal, modem. and printer. A suggested terminal is the Televideo 950 with printer port.

1.1 NOTATION USED IN THIS MANUAL

- Upper Case: The text must be typed exactly as specified with only the underlined portion required. For example, LOGOUT may be typed as either LO or LOGOUT.

- Lower Case: The word in lower case is to be specified by the user. It refer to a filename or any of several optional mav parameters. For example, to invoke the editor, the command would be:

ED fname

If the file was A.NET, the command would be typed as:

ED A.NET

#### **1.2 UNIVERSAL EDITING CHARACTERS**

The Prime will recognize two keys as special editing keys at all times. They are used to correct spelling errors in the current line. The backspace key will erase the most recent character typed. Multiple backspaces are allowed, until the beginning of the line is reached. The DEL key will delete everything on the current line. Thus,

EX NET(DEL)ED A.NET would be interpreted as: ED A.NET

ZyMOS has changed the standard Prime character and line delete keys. Prime documentation will reference (') as character delete and (?) as line delete.

المحالة في مراكز المحالة المحالة

الكريمية معرفة معرفة من المحمد المعرفة معرفة من المعرفة من المركز المحمول من المحمد المحمد

and the second secon

an 1990 - Antonio Anto Antonio Antonio

<sup>.</sup>

#### 2 LOGIN AND LOGOUT PROCEDURE

The Prime can be accessed over normal voice-grade phone lines at 300 or 1200 baud. Since the ZyMOS computer is connected to TYMNET, it may be accessed from most major cities, worldwide, with a local phone call. Accessing the Prime over TYMNET is a two step procedure. TYMNET login and ZyMOS Prime login.

#### TYMNET login:

- 1. Dial the number provided by ZyMOS. When you hear the high-pitched tone, place the phone in the acoustic coupler, or push the 'data' button on your modem or phone set.

- 2. Type a carriage return if you are operating at 300 baud, or the character a if you are operating at 1200 baud with a video terminal.

- 3. TYMNET will ask you to log in. ZyMOS will assign you a TYMNET ID which is used to respond to the TYMNET log in request.

please log in: ZyMOS assigned TYMNET ID

4. Next, TYMNET will ask for a password. The TYMNET password is also assigned by ZyMOS. Enter the password. It will not echo to your terminal. Type a Carriage Return. When the plus sign appears, type another carriage return. You are now connected to the ZyMOS Prime computer and will receive a message similar to the following:

PRIMENET XX.X ZSVX

#### Prime login:

1. Type: LOGIN name

where name is the Prime user ID assigned to you by ZyMOS.

2. You will then be asked for your Prime password, initially assigned by ZyMOS. Again, it will not echo to your terminal:

Password? Prime password

3. The computer will respond with:

name (xx) logged in Thursday, 12 Jan, 84 20:04:12 Welcome to PRIMOS version xx.x Last login Wednesday, 11 Jan 84 12:00:45

Welcome to ZyMOS

OK,

When you are first assigned a Prime user ID, you will also be assigned a Prime password. It is a good practice to change your password from time to time to prevent unauthorized access to your files. Once you have logged in, you can change your password with the following command:

<u>CPW</u> old password. (You will be prompted for a new password.)

When you are finished using the system, type:

LOGOUT

#### 2.1 PROBLEMS IN LOGGING IN

There are several error messages or problems you may encounter when logging in. The following are examples of the most common problems.

1. Invalid command Login please ER!

Response to keyboard activity before login.

2. Invalid user id or password; please try again Login please ER!

Response to wrong user name or password.

3. llooggiinn

Terminal set to half duplex. Switch to full duplex.

4. No response.

Your terminal is off-line, not connected to your modem, or you are configured for the wrong baud rate.

المراجعة الم المراجعة الم المراجعة الم

#### **3 FILE STRUCTURE**

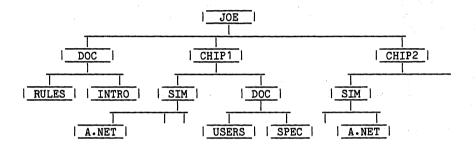

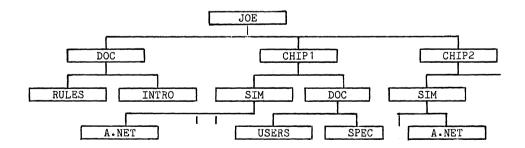

Under the Prime Operating System (PRIMOS), related files can be grouped together into directories. A directory may contain not only files, but other directories as well. Thus, you could have a directory for each chip you are working on. Within each chip's directory could be sub-directories containing logic simulation files, documentation, circuit simulation files for special cells, etc. In this manner, files can be organized in an orderly fashion, permitting easy location. New users often ignore this feature and find it necessary to go back and reorganize their directories. The directory structure of PRIMOS is of fundamental importance in understanding file management. Refer to chapters 2 and 4 of The New User's Guide to Editor and Runoff and chapter 2 of the Prime User's Guide for more information.

#### 3.1 LISTING DIRECTORIES

When you have first logged in, you will be 'attached' to your main directory, also called UFD for User File Directory. To list all the files within it. type:

#### LD

In the example directory on the next page, if you had logged in with user name JOE, and had typed LD, the names CHIP1, CHIP2, and DOC would be listed.

#### 3.2 CREATING NEW DIRECTORIES

To create a sub-directory (also called sub-UFD), type:

#### CREATE sub-directory-name

Using the directory on the next page, if you wished to create a directory to hold all files for a third chip, you would type: CR CHIP3. (Note: main directories, UFD's, sub-UFD's, and sub directories will all be referred to as directories. The context of the directory will define its position within the structured hierarchy.)

### 3.3 ATTACHING TO A DIRECTORY

The easiest way to work with files in a directory is to 'attach' to the directory. This is done by typing:

#### ATTACH directory-name

Once attached to a directory, you may access the files within it by their simple name. For example, in the directory below, if you had logged in as JOE, and typed: <u>A JOE>DOC</u>, you could access the file JOE>DOC>RULES by its simple name: RULES. If you then wished to access JOE>CHIP1>SIM>A.NET, you would have to type the entire name, or first attach to JOE>CHIP1>SIM, i.e. type: A JOE>CHIP1>SIM

The argument in the above attach command, JOE>CHIP1>SIM, is called a path name or tree name. It starts at the top of the UFD and specifies the path thru the directory to get to the desired sub-UFD. The greater-than symbol (>) is used as the delimiter in path names and is called a path or tree separator.

Doc 20-010-003 Rev: E

3.4 DELETING FILES

To delete a file, type:

DELETE fname

```

e.g. ATTACH JOE>CHIP1>DOC

DELETE SPEC

DELETE JOE>DOC>RULES

```

3.5 COPYING FILES

To copy a file, type:

COPY fname1 fname2

where fname1 is moved to fname2. For example,

1. To create a copy of a file within the current directory, type:

A JOE>DOC>CHIP1 COPY SPEC OLDSPEC

2. To copy a file from one directory to another:

COPY JOE>CHIP1>DOC>SPEC JOE>CHIP2>DOC>SPEC

3.6 BASIC DIRECTORY AND FILE COMMAND SUMMARY

1. LD - lists all files in a directory and the current directory pathname.

2. CREATE (sub-UFD-name) - creates new sub-UFD.

3. ATTACH (pathname) - attaches to the new directory specified by pathname.

4. DELETE (fname or sub-UFD-name) - deletes file or sub-UFD.

5. COPY (pathname1 pathname2) - copies files or sub-UFD's.

There are additional file commands defined in the Prime User's Guide.

.27

### 4 EDITOR

The PRIMOS Editor is a line editor and is used to create and edit files containing your logic network, test cases and documentation. It creates a copy of the file you wish to edit, and makes all changes and additions to the copy. It will not update the original file unless specifically told to do so.

This section is intended to present only the basic commands needed to use the EDITOR. For complete information, refer to the New User's Guide to Editor and Runoff.

To edit an already existing file, type: ED fname

To create a new file, Type: ED

4.1 EDIT VS INPUT MODE

Once you have started the editor, there are two modes of operation: EDIT mode and INPUT mode. You can toggle back and forth between these modes by typing a carriage return at the beginning of any line. The editor will respond with 'INPUT' if you are entering INPUT mode or 'EDIT' if you are entering EDIT mode.

#### 4.2 SPECIAL CHARACTERS

INPUT mode is used to enter text. What you type is entered immediately following the current line at which you are positioned. Other than the backspace and DEL key (see introduction), the only other common special character is the back-slash character: \. Whenever it is typed, the current column is set to the next tab stop. The default tab stops are at columns 6, 12, and 30. For example, if you had typed:

OUT\GAA1\IN1 IN2 OUT

It would be entered into your file as:

OUT GAA1 IN1 IN2 OUT

#### 4.3 SUMMARY OF EDIT COMMANDS

Edit mode is used to reposition the current line to a different location in the file, to print several lines, to change a phrase, to delete lines, etc. The most commonly used edit commands are:

| C. De la Contrata de l<br>contrata de la contrata | - ジャン・キャック ション・ション かいしょう ション・ション しょうしょう かくしょう                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Change the frirst occurence of XXX to YY in the current line.                                                              |