Joe Costello on Concurrent Engineering

FOR ELECTRONIC ENGINEERS & ENGINEERING MANAGERS

# 30 years in the transformation

# of electronics and the world

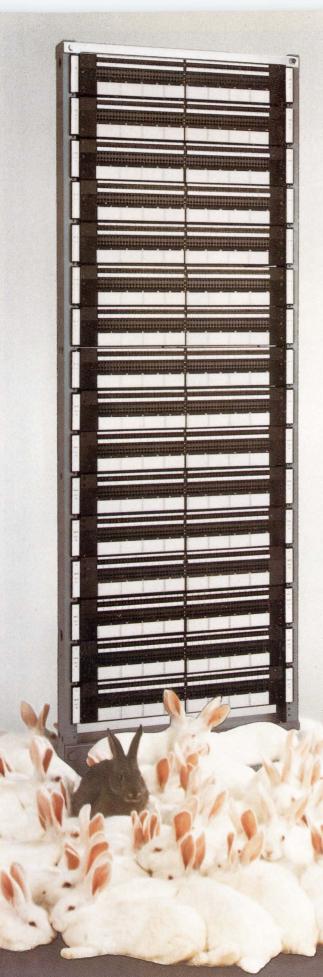

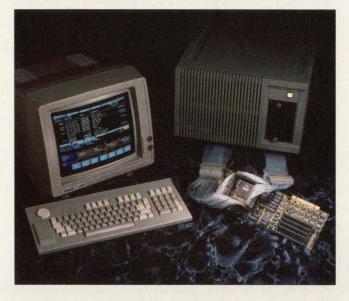

# At Last, a <u>Truly</u> Industrial **386 PC AT System for the OEM**

Easy to mount Eurocard hardware with optional power supply. Can be rack mounted or bolted into any embedded system.

Two boards make a complete 386 computer with your choice of EGA or VGA display.

(

(

0

(1

1

01

01

01

01

01

(1

1, 2, 4 or 8 Mbytes of on board. Full support for LIM EMS and **BIOS** shadowing.

On board . support for COM1, COM2, LPT, keyboard, clock, floppy disk, and IDE hard disk.

Compact single height Eurocard board format (100 x 160 mm) that doesn't flex or bend and withstands the toughest shock and vibration.

Small price to help you compete.

Three side mechanical bond into the card cage, yet easy to access for simplified maintenance.

Full 32-bit expansion bus for easy system expansion and customization with up to 20 slots.

16 or 20 MHz

80386SX CPU

and 80387 Arithmetic Unit

**USA - CANADA** 50 West Hoover Ave. Mesa, Arizona 85210 USA Tel. (602) 962-5559 Fax. (602) 962-5750

**CIRCLE NO. 1**

FRANCE Z.I. les Playes 83500 La Seyne France Tel. 94 30 34 34 Fax. 94 87 35 52 INTERNATIONAL

18, Chemin des Aulx CH-1228 Geneva Switzerland Tel. (022) 794 3400 Fax. (022) 794 6477

Introducing the first 386 PC AT system originally designed to be embedded into your machinery or instrumentation.

With the GESPAC AT system, "ruggedized PC" no longer describes a desktop PC in a stronger black box. Instead it is an architecture made to last by design, with such features as small and robust board format, and ultrareliable pin-in-socket connector.

What's more, the GESPAC System is built for performance with Intel's original 16 or 20 MHz 80386SX processor and 80387SX Arithmetic Unit. In fact, this system is the most compact implementation of the 386 in the market today.

The powerful G-64/96 bus interface lets you customize your AT system with any of the 200-plus system components available from GESPAC, to match virtually any system requirement.

Take advantage of GESPAC's 12 years of experience in serving the OEM marketplace. Call today to receive your free data sheet and GESPAC's catalog of board level microsystem products. Ask about GESPAC's exclusive Guaranty of OEM Long Term Delivery.

Unprecedented selection of inexpensive I/O functions, from the simplest parallel and serial I/O, to high performance networking, MIL 1553. motion control, and computer vision.

Call Toll Free 1-800-4-GESPAC

or call (602) 962-5559.

New

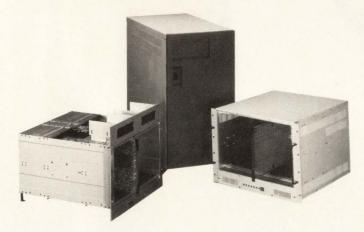

Easy Access = Maximum Accessibility Quick access saves time in assembly, test, and maintenance. Loosen two captive fasteners and the front, top, and sides slide off for maximum access to all of the internal components. Each internal component comes out with two screws, or remove five hex nuts and the entire system lifts out of the bottom, tray to provide a free-standing, fully functional development platform!

### Peripherals Just Slide In

Up to eight half-height 51/4" peripherals simply slide into their mounting brackets.

The Quietest Backplane

Plug your VME system into the quietest backplane ever! Our new 10-LAYER VME backplanes handle the fastest VME signals with the absolute minimum distortion, crosstalk. and noise.

Engineered Cooling Airflow is directed over the components that need cooling — the power supply and your boards. Separate chambers maximize cooling by channeling airflow and restricting recirculation.

**Configured for Your**

configurations are available for rack and tabletop models as well as floor-standing DeskMate™ verions that accept 9U × 400mm cards. Or let our team of engineers provide a packaging solution tailored to your specifications — from configuring the front panel LEDs to customizing the rear panel. Designing enclosures to meet your specific needs is our specialty.

Optimum Power Output Choose from 175 to 1000 Watts to satisfy the demands of your system.

# The Last Word in System Packaging

Now you can benefit from 12 years of design experience and innovation that has made Electronic Solutions the industry leader in system packaging. The Omega<sup>™</sup> Enclosures will give your VME or Multibus system the attractive exterior your image demands with a rugged, welldesigned interior to withstand the most demanding environments. And besides the Electronic Solutions' full 3-Year warranty, the Omega bears FCC approvals and is UL, CSA, and TUV

listed to get your system to an international market in the shortest time possible.

Call Electronic Solutions for the latest information about the best choice for your system package. It's the last system enclosure you'll need to see.

6790 Flanders Drive, San Diego, CA 92121 (619) 452-9333 FAX: 619-452-9464 Call TOLL FREE (800) 854-7086 in Calif. (800) 772-7086

**CIRCLE NO. 2**

100% full-parallel flash ADC performance for 10% of the price.

Save money and get an extra effective bit every time you convert video from A to D...with the new Philips 8-bit video ADCs.

Giving full-parallel flash performance at up to 1/10 the cost of full-parallel flash converters, these ADCs provide professional performance at a consumer price. How? Our new folding-and-inter-

polation technique slashes on-chip component count, thus reducing cost

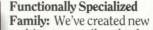

| Туре           | MSPS      | Diss.(mW) | Features                          |

|----------------|-----------|-----------|-----------------------------------|

| TDA 8703°      | 40        | 290       | Voltage Reg.                      |

| TDA 8713°      | 50        | 290       | TTL I/O                           |

| TDA 8715°      | 50        | 325       | ECL I/O                           |

| TDE 8715       | 50        | 325       | Mil. Temp. Range                  |

| TDA 8708°      | 30        | 365       | Clamp/AGC<br>CVBS Signal          |

| TDA 8709°      | 30        | 380       | Clamp/Adj. Gain<br>R,G,B,Y,U,V, C |

| ° in DIL and S | SO versio | INS.      | Signals                           |

while enhancing performance. It also lowers power consumption up to 70%. For example, the TDA8713 consumes as little as

> 290mW and gives 7.5 effective bits with an input frequency of 4.43MHz (40MHz clock)...ideal for a wide range of professional and consumer video applications. For more information, contact Philips Components, Marketing Communications Dept., Building BAF-1, PO. Box 218, 5600 MD Eindhoven, The Netherlands. Telex: 35000phtc nl/nl je vmc. FAX:31-40-724825.

### **Philips Components**

# PHILIPS

Joe Costello on Concurrent Engineering Page 21

#### **TECHNOLOGY UPDATES**

#### **Integrated Circuits**

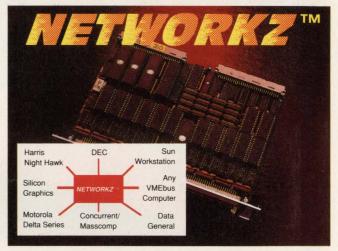

Controller-level network could

#### Software

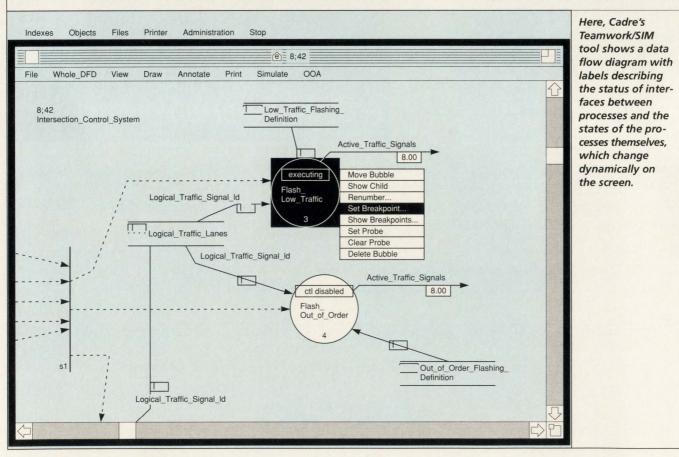

CASE tool adds dynamic simulation of requirements analysis ......40

#### **Design and Development Tools**

Network-distributed processing reduces run times for complex PC-based board design tools

#### **Computers and Subsystems**

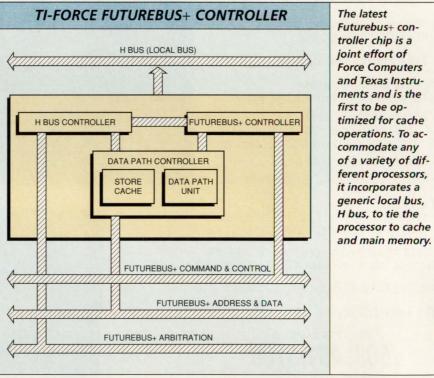

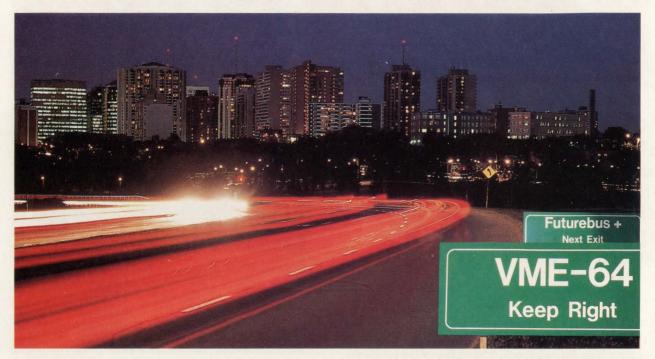

Futurebus+ gains support from chip-development agreement ......46

Page 36

Page 52

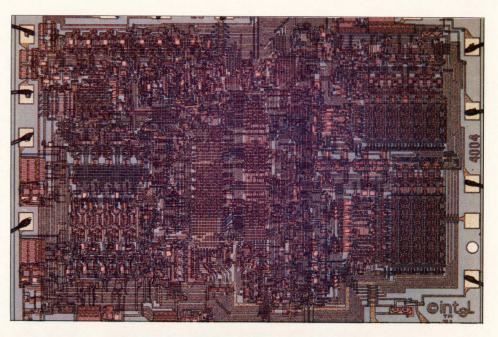

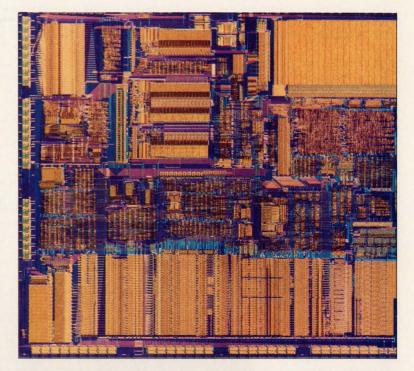

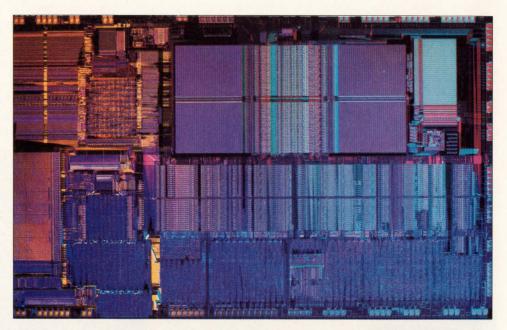

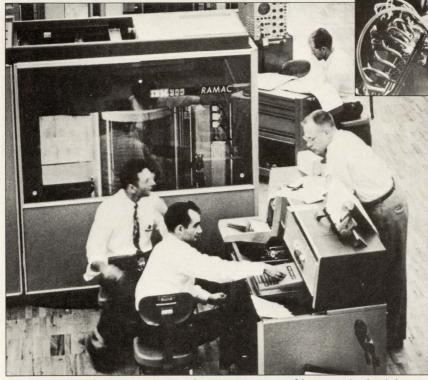

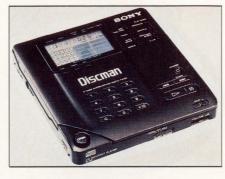

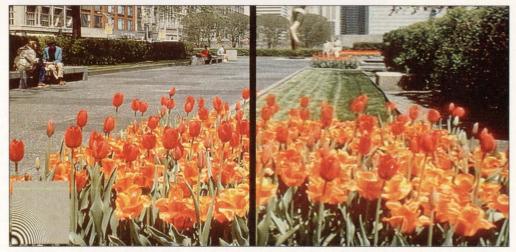

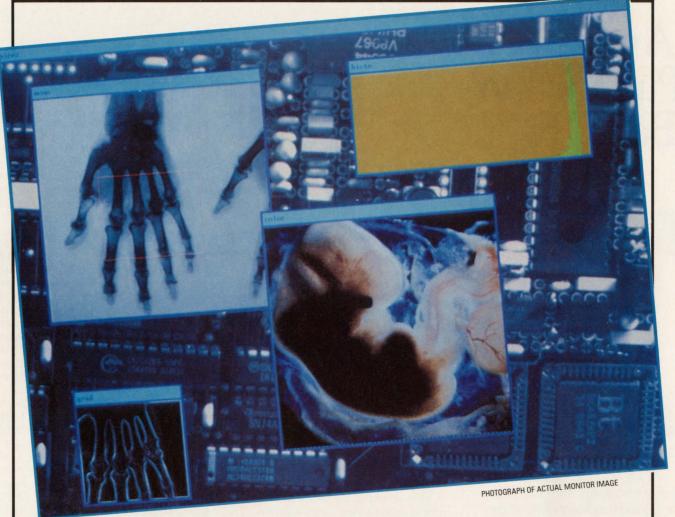

#### THIRTY YEARS IN THE TRANSFORMATION OF ELECTRONICS AND THE WORLD

| IC, storage and display technologies have turned the world digital      | .52 |

|-------------------------------------------------------------------------|-----|

| Computers get personal                                                  | .65 |

| Digital communications link the world on wires, lightwaves and airwaves | .75 |

| Digital designs conquer consumer                                        |     |

music and video......83

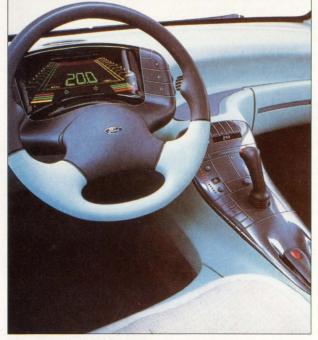

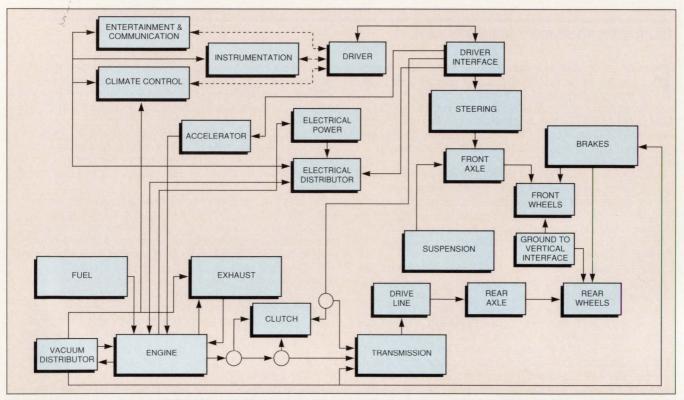

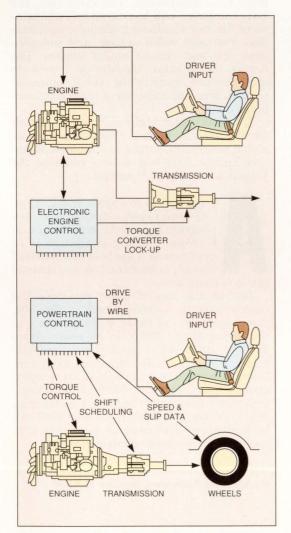

| Automobiles and electronics:<br>a long courtship promises a<br>productive marriage | 91  |

|------------------------------------------------------------------------------------|-----|

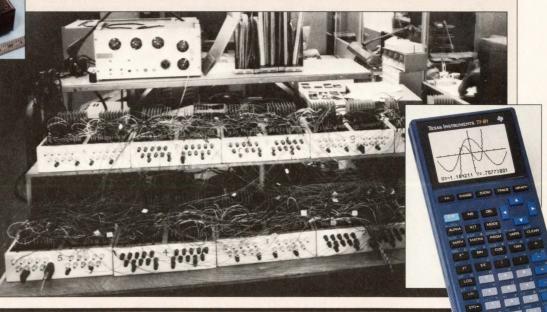

| Digitization broadens the scope of measurement and analysis                        | .99 |

| EDA—a success story<br>in three decades                                            | 107 |

Page 113

#### NEW PRODUCT HIGHLIGHTS

#### **PRODUCT FOCUS**

Logic analyzers offer RISC support and ease-of-use ......113

#### **Design and Development Tools**

PC-based circuit board design tool incorporates framework technology .. 120

#### **Integrated Circuits**

| PC chip set provides more-          |   |

|-------------------------------------|---|

| sophisticated cache architecture122 | 1 |

| Oki unveils 8051-like controller    |   |

| family124                           | ł |

#### **Computers and Subsystems**

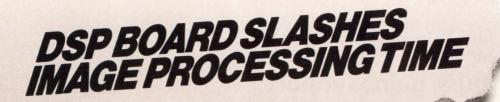

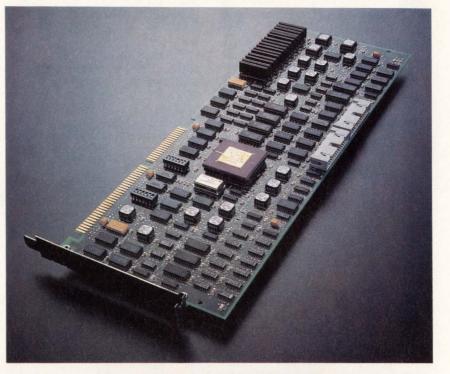

32-bit DSP board delivers 25-MFlops on STD Bus.....127

#### Software

Development module supports knowledge-based real-time systems ... 128

| <b>DEPARTMENTS</b>   |  |  |  |  |

|----------------------|--|--|--|--|

| News Briefs 8        |  |  |  |  |

| Editorial12          |  |  |  |  |

| Calendar16           |  |  |  |  |

| Advertisers Index154 |  |  |  |  |

|                      |  |  |  |  |

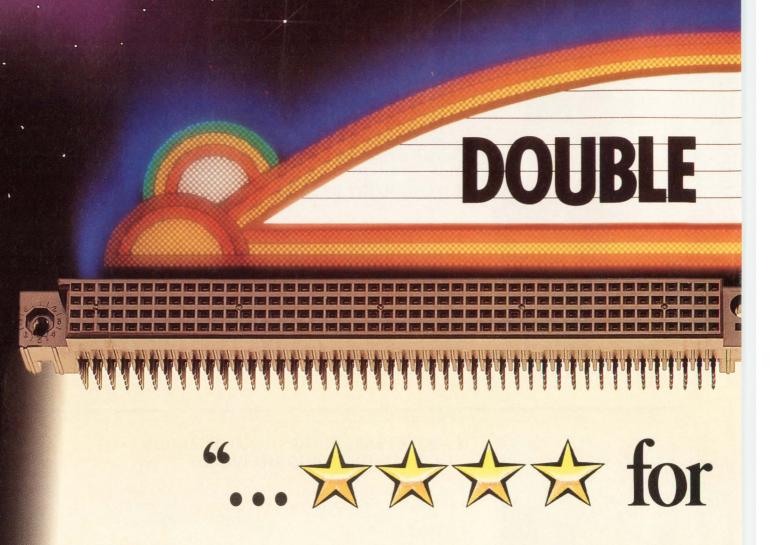

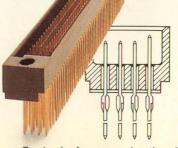

AMP TBC (Twin-Beam Contact) Connectors steal the show for highdensity, high-pin-count affordability. Three- and four-row versions deliver compelling performances in 32 to 540 position roles.

The twin-beam receptacle at

the heart of the TBC Connector represents the very best of AMP engineering—the greatest economy of material consistent with design excellence. It provides two-point contact (with gold-over-nickel plating), and the BeCu base assures high normal forces of 50 grams/contact (end of life minimum) for solid dependability.

There's more here than economy, though. Tightly controlled, short pointof-contact geometry allows two levels of mating for make-first break-last sequencing of power and ground pins. The same design reduces insertion

Two levels of sequenced mating allow "hot" connect/disconnect. Compliant pin option for solderless pcb insertion.

AMP and AMP-HDI are trademarks of AMP Incorporated.

# cost reduction."

force, and provides outstanding contact wiping action: .070" on short pins, and a minimum of .100"

FEATURE

Unique twin-beam receptacle delivers outstanding reliability in an affordable high-density connector. on long. (Coming soon: TBC Plus Connectors, with six rows of contacts and three levels of sequencing.)

AMP TBC Connectors are fully polarized, with closed-entry design to eliminate stubbing, and they come in high-temp materials ready for vapor-phase and IR reflow soldering. And TBC receptacle assemblies intermate with our popular AMP-HDI pin header assemblies, to give you immediate daughter card cost-reduction, without redesign.

Call 1-800-522-6752 and ask about the AMP TBC Connector Series. AMP Incorporated, Harrisburg, PA 17105-3608.

CIRCLE NO. 4

Interconnecting ideas

# LSI HA ANOTH

© LSI Logic Corporation 1990. Sun Microsystems is a registered trademark of Sun Microsystems, Inc. SPARC is a registered trademark of SPARC International, Inc., and SPARCstation is used under license therefrom. UNIX is a registered trademark of AT&T Bell Labs.

May '90 SPARCstation SLC

July '90 SPARCstation IPC

SJUST MADE ERSUNSHING

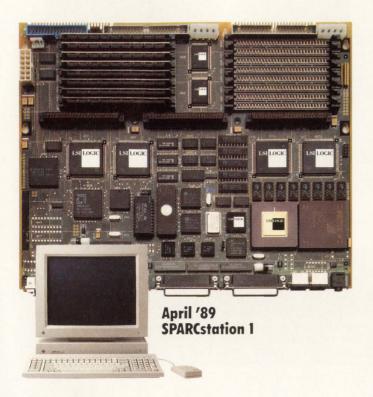

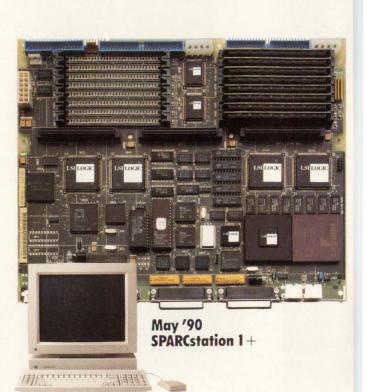

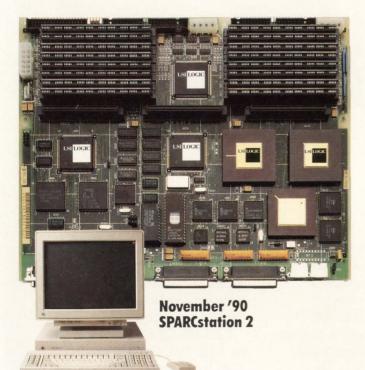

Since introducing SPARCstation 1 in April '89, Sun has utilized LSI Logic's RISC and ASIC technology and design methodology to pack more processing power into smaller footprints.

This strategic partnership has enabled Sun to compress time to market to an unbelievable four months between new product announcements and has reduced their time to volume. Forever altering the rules on time to market. And capturing the dominant position in the workstation market in the process.

Sun's latest creation, SPARCstation 2, is a shining example. This powerful new workstation was brought to market just four months after the introduction of the SPARCstation IPC. By leveraging the power of LSI Logic's RISC and ASIC technology, Sun has quickly introduced a whole new level of price/performance in UNIX workstations.

If you have some brilliant new product concepts on your horizon, with windows of opportunity opening as often as every four months, call us at 1-800-451-2742, or write to LSI Logic, 1551 McCarthy Blvd, MS D102, Milpitas, CA 95035.

We'd like to show you how quickly your new product can see the light of day.

### NEWS BRIEFS NEWS BRIEFS NEWS BRIEFS NEWS BRIEF

#### Silicon breakthrough boosts system speeds

IBM (Armonk, NY) has succeeded in growing silicon on a nonconductive substrate, an advance that not only boosts transistor switching speed, but also prevents power leakage and reduces an IC's vulnerability to radiation. IBM has already used the technique to make CMOS transistors that are three times faster than conventional devices, though the company admits that the discovery won't result in faster computers for a couple of years. The announcement is expected to extend the useful life of silicon technology, which many IC vendors fear is approaching the limits of its abilities. IBM's advance should allay those concerns and reduce the urgency of developing more expensive alternatives, such as gallium arsenide.

— Mike Donlin

#### Wafer-scale integration powers neural computer

Hitachi (Tokyo, Japan) has unveiled a prototype general-purpose neural computer system that could be used as a super-high-speed back-end processor or coprocessor for workstations. The system uses wafer-scale integration to achieve what Hitachi claims is the highest learning performance ever posted by a neural computer—up to 2.3 billion operations per second.

At the heart of the system are 5in. wafers, made with submicron CMOS processing, that pack up to 20 million transistors divided into 60 very-high-density gate arrays on a single subsystem board. There are eight subsystem boards in the computer that host a total of 1,152 neurons.

Hitachi's prototype was able to perform a signature verification in just two seconds, a task that could previously be performed only by a large supercomputer. The system achieves this performance by simulating the dynamic and parallel processing functions of the human brain, albeit with a much smaller network. — Mike Donlin

### 0.5-µm CMOS process refined

Motorola (Austin, TX) has developed a new CMOS process that could become a feasible way for building ultra-dense circuits with design rules below  $0.5 \ \mu m$ . The process uses disposable sidewall spacers to protect source and drain areas during thermal annealing.

While previous research at Motorola unearthed the possibilities of using sidewall spacers fabricated from polysilicon, new research demonstrates that the polysilicon can be removed without damaging the underlying device structure. This was accomplished by adding an additional silicon nitrate to a thin polysilicon frame, making it impervious to the acid used to remove the sidewall structure.

Research results indicate that the silicon nitrate layer permits finer definition of transistor structures, leading to reproducible functioning devices under a half  $\mu$ m. The new process could form the foundation of a practical and economical ultra-large-scale circuit process. — Jeffrey Child

#### Intergraph seeks framework partners

In an attempt to grab a larger share of the EDA market, Intergraph (Huntsville, AL) has unveiled Interlink, a program designed to integrate third design tools into Intergraph's newly named Simultaneous Engineering Environment framework. The program already encompasses existing OEM relationships, but Intergraph is aggressively seeking alliances with other vendors to broaden its base of EDA productsan area in which it has been relatively weak. By labeling and publicizing a framework that it has had

for some time, Intergraph is signaling a more competitive stance against rivals Mentor Graphics and Cadence Design Systems who traditionally tout the benefits of their framework offerings. Though strong in mechanical CAD, Intergraph's market share is small about 1.5 percent, according to Dataquest figures. — Jeffrey Child

#### Synthesis objectives outlined by new Mentor division

Mentor Graphics (Beaverton, OR), aggressively pursuing a leadership position in synthesis technology, recently gave further details of its new Design Synthesis Division. Created last fall, the synthesis division resides within Mentor's Systems Group and is responsible for ASIC, IC and programmable logic device synthesis products. It will also oversee the digital signal processor synthesis technology being developed at the European Development Center (Leuven, Belgium), test synthesis technology from the company's Simulation and Test Division, and analog synthesis products from the Silicon Design Division.

The synthesis software Mentor currently offers can be traced to the acquisitions of Trimeter Technologies and Silicon Compiler Systems, a technology purchase agreement with Minc (Colorado Springs, CO) and internal development efforts. Mentor has completed the integration of the AutoLogic synthesis and optimization toolset for IC design—part of Silicon Compiler Systems' previous product offerings-into its Software Release 7.0 EDA environment. The LogicLib library of technology-independent macrofunction generators has also been integrated.

What the industry is really holding its collective breath for, though, is the release of the Design Consultant VHDL synthesis tool that Mentor expects to ship

Continued on page 10

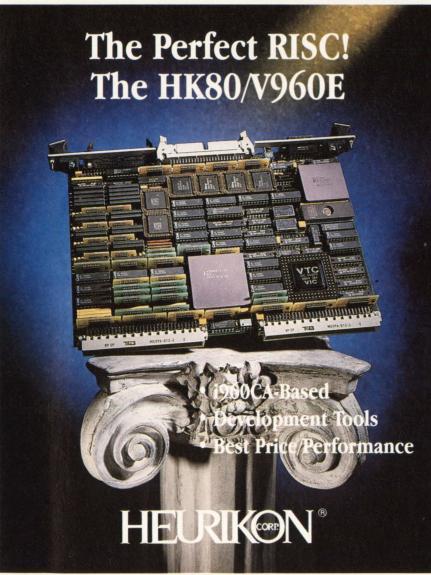

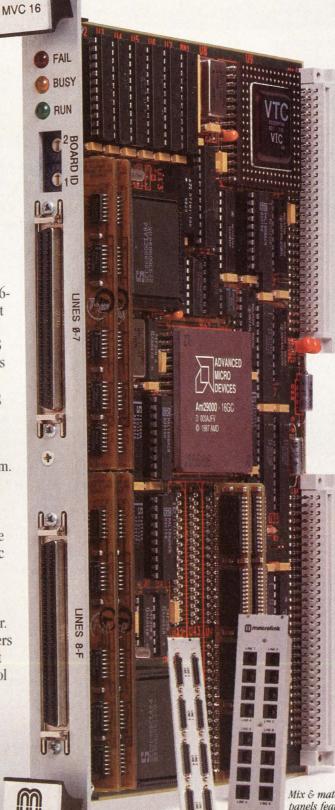

# Top Real-Time Performance for VME

#### PERFORMANCE

Based on the powerful Intel i960CA, Heurikon's HK80/V960E Single Board Computer packs the best RISC or CISC price/performance on the market today. With 40,000 Dhrystones at 33MHz, the HK80/V960E is the *ideal* platform for critical real-time applications including embedded control, image processing and intelligent I/O. The HK80/V960E sports 2 or 8 Mbytes of fast dual access, static column RAM. It also delivers a host of networking and I/O capabilities including on-card SCSI, Ethernet, Centronics compatible parallel I/O, and four RS-232C serial I/O ports. The VIC068 VME Interface Chip maximizes the VMEbus transfer rate and implements the full VMEbus interface with 4-level arbitration.

#### **DEVELOPMENT TOOLS**

Powerful real-time development tools are available for a variety of hosts with full support from Heurikon.

Available for Delivery

• VxWorks Real-Time Operating System allows the user to work in partnership with UNIX while running real-time targets. Code can be debugged using either a source-level debugger residing on the host systems or a symbolic debugger residing on the target. VxWorks, with driver support for SCSI and Mil Std 1553A, is available on Sun and Heurikon hosts with both backplane, and Ethernet target interface support.

• GEN-960 for refining ROM or RAM code when setting up standalone embedded applications.

• ASM-960 assembler allows macroassembler users to fine tune application code as well as provide utilities for developing, debugging and maintaining application code.

• Intel and GNU compilers optimized for the 80960 family of embedded processors.

#### PRICE

Prices for the HK80/V960E series are very competitive with traditional CISC architectures...and it's available now! Call us now for more information on the HK80/V960E.

> Heurikon Corporation 8000 Excelsior Drive Madison, Wisconsin 53717

1.800.356.9602

Ext. 915 FAX: 608/831-4249 TEL: 608/831-0900

960CA and Intel are trademarks of Intel Corporation. VxWorks is a trademark of Wind River Systems, Inc. UNIX is a trademark of AT&T Bell Laboratories, Inc.

### NEWS BRIEFS NEWS BRIEFS NEWS BRIEFS NEWS BRIEF

#### Continued from page 8

with phase II of Software Release 8.0 in the second quarter of this year. Beyond that, the workstationbased design system for DSP synthesis being developed in Europe is likely to be one of the hottest attractions at DAC '91 in San Francisco this June where Mentor expects to demo it for the first time.

— Barbara Tuck

# What exactly is programmable interconnect?

Venture capitalists backing a programmable interconnect technology being developed by start-up firm Aptix (San Jose, CA) are evidently betting on the company's ability to develop the innovative technology demanded by changes in systems design. As for details on the product, currently in the process of being physically defined, Amr Mohsen, chairman, president and CEO of Aptix, says only that the first round of venture funding will allow the company to concentrate on developing "component interconnect technologies that will enable systems designers to achieve greater control and flexibility in the systems design process.

The Aptix description of its technology as "field-programmable integrated solutions for component interconnects" might leave some blank spots for those looking for a detailed product definition. But the empty spaces fill in rather quickly when industry trends are taken into account along with Mohsen's background as founder and former president and CEO of Actel.

A look at the company's management team roster is also revealing. It includes, among others, a former packaging engineering guru from National Semiconductor, a former software development director from Cadence and a former senior vice-president of marketing from Daisy/Cadnetix. Nevertheless, it will be interesting to follow this technology as it unfolds into product. — Barbara Tuck

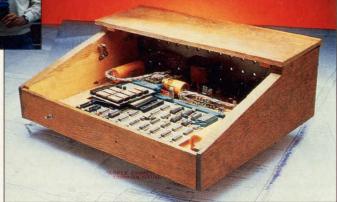

### Acorn RISC machine resurfaces at Apple

The Acorn RISC CPU, developed by Acorn Computer (Cambridge, England), has been one of the most obscure but most widely produced RISC processors. Built by VLSI Technology (Tempe, AZ), the chip has gone through several generations and has been used in Acorn personal computers as well as embedded applications. The device is remarkable primarily for its simplicity, small size and high speed for the money.

Now Apple Computer (Cupertino, CA) has formed a joint venture with Acorn and VTI called ARM to produce yet another generation of RISC chips on the Acorn architecture. Acorn and VTI will presumably get new products for their respective ventures-personal computers and custom embedded controllers—from the joint development effort. But the big question is Apple's interest in the little RISC chips. Speculation runs from the possibility of ARM CPUs as controllers for peripherals-laser printers, perhaps-to the notion of ARM-based portable or hand-held computers.

In any case, the move has to look like a repudiation of Apple's traditional CPU vendor, Motorola. That company has supplied all the CPUs for the Macintosh family and has been aggressively shrinking and integrating its 68000 CPU cores. In addition, Motorola has reportedly tried very hard to sell Apple on the 88000 RISC family. No matter how Apple intends to use the ARM chips, it will be in place of some major element of Motorola's product line. — Ron Wilson

#### Motorola ships 68040, sort of

Motorola (Austin, TX) has announced that it's finally shipping the production 25-MHz version of the 68040 microprocessor, but still only in limited quantities. The part was announced with considerable enthusiasm in March 1989 as the 68000 family's next-generation, RISC-beating CPU. And in fact the chip showed performance figures as good as those of any RISC processor shipping in 1989. The device's performance was impressive enough to draw design wins from the likes of workstation vendor Hewlett-Packard. But the chip has not been shipping. Reportedly a number of serious design, rather than manufacturing, problems have held up the device. Now Motorola feels confident in its mask set and is ready to take on the problems of ramping up such a complex die to full production status under its Baldrige-winning quality requirements. But in the beginning of 1991, the first question will be not whether Motorola can produce the 68040 in volume, but whether there remains, nearly two years after the announcement, a significant market for the chip. - Ron Wilson

### S3 puts multiprocessing chip set on hold

S3 (Santa Clara, CA), the startup that recently outlined its plans for a multiprocessing personal computer chip set, has put the idea on indefinite hold. In an effort to conserve cash, and perhaps in recognition of the absence of customers for multiprocessing architectures, the company has decided to focus all its efforts on a set of graphics products. The graphics design was originally intended to fit into the multiprocessing architecture, but now appears more marketable by itself. The change involved cutting about half of S3's technical and support staff. The company claims that it's still committed to the multiprocessing architecture and is seeking licensees to pursue further development. But without the designers who actually implemented the complex scheme in silicon. it's difficult to see how S3 could transfer the technology effectively should a licensee appear.

-Ron Wilson

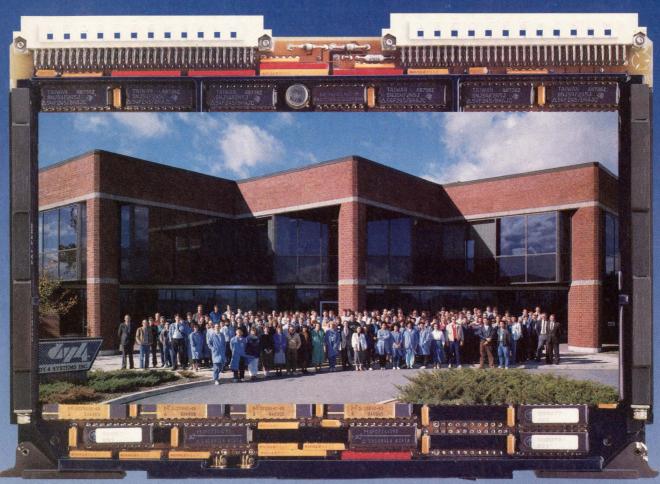

# **Pride of Achievement**

At DY 4, we trust in our ability to give you the customer – our best effort. Being one of the first companies in the development of VMEbus products and the forerunner in fully supported MIL-SPEC and ruggedized bus/board products, we have grown with your needs and we earn your trust year in and year out. In 1990, our philosophy of "Customer First – Quality Always" has been rewarded by a record year.

### Record Sales • Record Earnings • Record New Orders

At DY 4, we are taking this opportunity to express our gratitude to our new and old customers worldwide, and to confirm our dedication to your needs, today and throughout the decade of the nineties.

#### Your trust makes our pride of achievement possible.

DY4 Systems Inc.

Customer First, Quality Always 21 Fitzgerald Road Nepean, Ontario K2H 9J4 Tel: (613) 596-9911 Fax: (613) 596-0574

Campbell, CA Tel: (408) 377-9822 Fax: (408) 377-4725 Hammel, Denmark Tel: +45-86-963624 Fax: +45-86-962575 Nashua, NH Tel: (603) 595-2400 Fax: (603) 595-4343 Pennant Hills, Australia Tel: +61-2-484-6314 Fax: +61-2-875-1665

CIRCLE NO. 7

The digital IC has turned nearly everything more complex than a pencil sharpener into a computer.

John C. Miklosz Associate Publisher/ Editor-in-Chief

### A digital way of life

here have been many technological turning points throughout the evolution of mankind that transformed forever the human condition. We can look back to the discovery of fire, the wheel, bronze, iron, gunpowder, paper, and the printing press. More recently we've had the development of the steam engine, as well as the discovery of petroleum and the subsequent invention of the internal combustion engine, the automobile and the airplane. The genesis of electronic technologies can be traced back to the discovery of electricity and the invention of the electric motor, the telegraph and the telephone, which was followed by the invention of the vacuum tube, and then radio, television and the electronic computer.

The two most recent turning points in this whirlwind of development were the invention of the transistor in 1947 and the invention of the IC in 1958. While the transistor was the seminal invention, the IC has been the primary driving force behind the digital transformation of our world—a transformation that's been underway now for about three decades and will essentially be complete before this decade is out.

This digital transformation has changed the nature of just about every product we touch. It also has resulted in other transformations that were undreamed of—even more significantly, were *impossible*—before the invention of the digital IC. In a very real sense, the digital IC, in its multiple variants, from microprocessor to memory, has turned nearly everything more complex than a pencil sharpener into a computer. It has made computers the most pervasive aspect of technological progress in our lives.

A computer, in the guise of a digital clock, is the first thing most of us hear and see in the morning and one of the last things we touch at night. While commuting to work, a computer in an engine controller lowers emissions and improves the mileage of our automobiles, and a computer in a braking system can keep our cars from skidding on slippery roads. At the office, computers take the shape of telephones, fax machines, copiers, and printers. Back home in the evening, a computer known as a compact disc player surrounds us with better sound than many of us can hear.

This digital transformation has special significance for all of us at *Computer Design* because we began publishing our magazine 30 years ago. That was, coincidentally, the same year that commercial—albeit primitive—digital ICs became a reality. We decided, then, to celebrate the beginning of this transformation with a Special Report that details some of the developments that occurred during those 30 years. There have been so many that the best we could do was give you a sampling. We hope that you enjoy reading it, and that you'll be as excited about the next 10 years as we are.

# "THEY LAUGHED WHEN WE PLUGGED A PC IN OUR VME SYSTEM...

**"The pressure was on.** Shorten our design cycle. Cut our software costs. Deliver the "gee-whiz" features customers wanted. But the old solutions weren't working. We needed a new approach. We looked to the PC. Others looked

at us like we were nuts. They sent memos. **The** *PC*

is not a real computer.' ... 'Not

enough horsepower' ... 'Just

a pretty user interface'

...'It can't survive that environment.'

**But the PC**

places. Over

40 million are in use; 4 million

in industrial

environments.

floor this year.

Another 1.4 million

are expected on the plant

the moment we plugged in a

RadiSys Embedded PC, we

understood why. Software

for PCs is abundant and

inexpensive. We had two dozen

software houses fiercely competing

to sell us high quality, man-machine interface software. Why should we reinvent

From

the wheel? Kor multi-tasking operating systems,

VRTX - all with integrated VMEbus support from RadiSys.

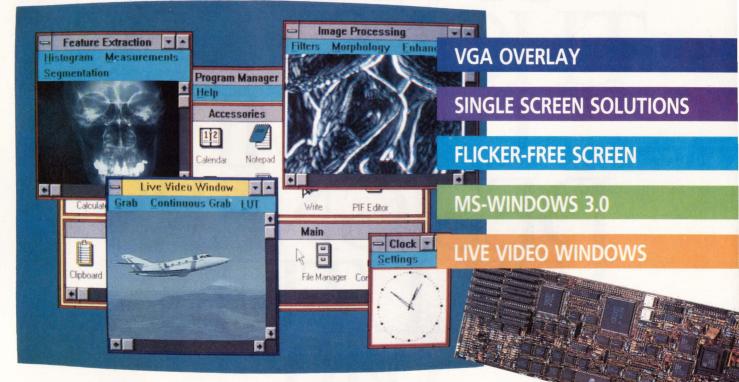

we could choose from Windows 3.0, OS/2, UNIX,

is going

There is a wealth of development tools available to shorten design time. No wonder the PC is the world's most popular software development

host. And PC-based networking is light-years ahead. **PC versatility is unmatched.** We can give customers what

We can give customers what they want, right now. More options. Proven features. Everybody knows how to use the PC, our own team and our customers. And it's a sure bet that future application programs, languages

and OS standards will run on it. **PC horsepower is up there.** The new Embedded 386 and 486 PCs have more than enough power to handle our mix of user interface and control functions. **We got the best of both worlds.** Plugging a RadiSys Embedded PC directly

into the VMEbus gave us the full performance, ruggedness and reliability of the VME form factor, plus all the PCs software advantages. **You know the rest** of the story. That Embedded PC has the *whole company* laughing.

All the way to the bank."

BUSCON/91-WEST JANUARY 29-31, 1991 SANTA CLARA CONVENTION CENTER SANTA CLARA, CA BOOTH 745 NEW 486-BASED EPC

Join the party! Call RadiSys at 800/950-0044 (fax requests: 503/690-1228) for a catalog of Embedded PC Products and brochure "Open New Windows of Opportunity With Embedded PCs."

#### The Inside Advantage

19545 NW Von Neumann Dr. Beaverton, OR 97006 USA (800) 950-0044 (503) 690-1229 Fax (503) 690-1228

Copyright © 1990 RadiSys Corporation, Inc. All rights reserved. EPC is a registered trademark and RadiSys is a trademark of RadiSys Corporation. Windows 3.0 is a trademark of Microsoft Corporation. OS/2 is a trademark of International Business Machines Corporation. UNIX is a registered trademark of AT&T. VRTX is a registered trademark of Ready Systems, Inc. 386 and 486 are trademarks of Intel Corporation.

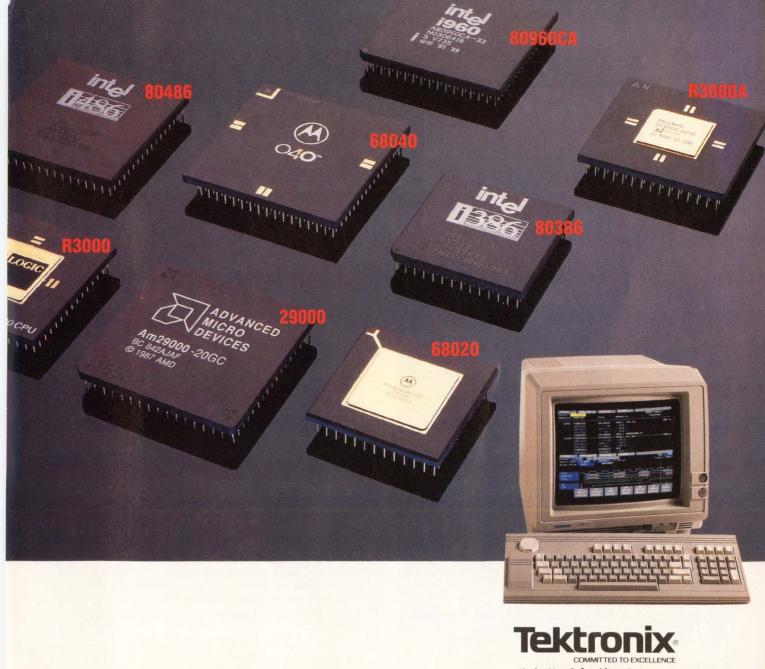

# NOW, LOGIC ANA AT THE SPEED

The NEW Tek Centurion: 400 MHz timing analysis. 100 MHz state analysis. 100 MHz complex triggering. 100 MHz synchronous clocking. 100 MHz timestamp. RISC chips. CISC chips. High-speed busses. At the leading edge of clock speeds, channel counts and complex integration, one logic analyzer is equal to the test. The Tek Centurion.

Centurion supplies an unprecedented 400 MHz timing. Plus 100 MHz synchronous acquisition on 96 channels at once *all on one card.* You can expand to hundreds of channels in a single mainframe, with up to 32K memory depth per channel!

Add the most revealing disassembly in the industry, for any processor pictured here. Add the easiest, most compact probing. Get real powers of analysis, not just ordinary acquisition capabilities.

Call 1-800-426-2200 to learn more about this great leap forward in logic analysis. Or see your Tek sales engineer for a personal demo soon.

Rental units available from your local rental company. Copyright © 1990 Tektronix, Inc. All rights reserved. DAS-065

Circle No. 9 for Literature Circle No. 10 for Sales Contact

# i860

### SUPERCOMPUTER PERFORMANCE

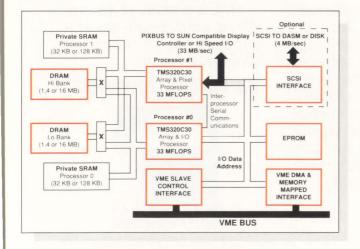

#### The AL860 VME or AT Board WILL GIVE YOU:

- An Intel i860 RISC microprocessor rated at 80 MFLOPS at 40 MHz (66 MFLOPS at 33 MHz)

- 2 to 64 Mbytes of 0 wait state local memory

- Optional SCSI and DT-Connect interfaces, and 120 Mbyte/sec interconnection bus

- DOS and UNIX interfaces, compilers, and scientific subroutine library software available

71 Spitbrook Road, Suite 204 • Nashua, NH 03060 Telephone: (603) 891-2750 • FAX: (603) 891-2745

Trademarks are property of their respective holders.

**CIRCLE NO. 11**

#### BRADYTOUCH TRANSPARENT TOUCH SCREENS

#### Matrix or analog designs.

- Unique "total surface" opticaladhesive reduces transmission losses, resulting in improved clarity.

- Made of durable, yet

- lightweight plastics. Abrasion-resistant,

- non-glare finishes available for particularly demanding applications.

Let us help you with your touch screen needs. Call or write today.

# BRADY

#### W. H. BRADY COMPANY THIN FILM PRODUCTS 8225 W. Parkland Ct. • P.O. Box 571 Milwaukee, Wisconsin 53201

**CIRCLE NO. 12**

Phone: 414-355-8300 • Fax: 414-354-0453 Copyright 1990 W. H. Brady Co. All rights reserved. CALENDAR

#### CONFERENCES

#### January 14-17

#### ATE & Instrumentation Conference

Disneyland Hotel, Anaheim, CA. This conference for test professionals will offer almost 50 sessions in design, manufacturing, manage-

sessions in design, manufacturing, management, service test, and systems integration. Session topics include "Testing in the 21st Century" and "Testing—the Competitive Edge." In addition, a four-day educational tutorial will follow the basics of design for test through to an actual production example of an integrated design and test board. Information: Miller Freeman Expositions, 1050 Commonwealth Ave, Boston, MA 02215-1135, (800) 223-7126. Circle 366

#### January 17-19 Landex '91 Southern California

Hyatt Regency, Irvine, CA. Targeted to LAN resellers, Landex '91 will feature seminars pertaining to training and basics, technology, and

taining to training and basics, technology, and business building, as well as super sessions. Specific topics include "High-Performance Topologies" and "The Successful VAR Formula." The LAN Dealers Association will also offer its certification examinations. Information: LANDA, 360 W Butterfield Rd, Suite 260, Elmhurst, IL 60126, (708) 279-2255. Circle 367

#### January 22-24

AFCEA/West

San Diego Convention Center, San Diego, CA. Co-sponsored by the U.S. Naval Institute, the 12th AFCEA Western Conference and Exposi-

tion will present exhibits from more than 150 companies. The three-day program will offer events featuring government, military and industry leaders in computers, communications, information systems, aircraft, R&D, and shipbuilding. Information: AFCEA Programs Office, 4400 Fair Lakes Ct, Fairfax, VA 22033-3899, (703) 631-6125. Circle 368

#### January 29-31 Buscon/91-West

Santa Clara Convention Center, Santa Clara,

CA. More than 150 exhibits will be featured at

this bus- and board-systems conference. Technical seminar topics include Futurebus+, VMEbus, Multibus II, PC bus platforms, embedded controller/systems programming, emerging bus architectures, and military applications. Information: Conference Management Corp, 200 Connecticut Ave, Norwalk, CT 06856-4990, (800) 243-3238. Circle 369

#### February 5-7

#### AFCEA 2nd Annual Military/Government Computing Conference and Exposition

Hyatt Regency Crystal City, Arlington, VA. The exposition will offer the latest in computer software and hardware products to link mili-

tary and government needs with the latest industry technologies, applications and services. The conference will also feature tutorials and technical tracks. Information: AFCEA Programs Office, 4400 Fair Lakes Ct, Fairfax, VA 22033-3899, (703) 631-6125. Circle 370

16 JANUARY 1, 1991 COMPUTER DESIGN

## Frustrated with microprocessor system debugging?

How the right preprocessor interface can simplify logic analysis.

## Here's free help in making the connections.

PACKARD

Plug into our new series of application notes today. And learn how to save time and aggravation when you're debugging microprocessor systems and busses.

Find out how an HP preprocessor literally makes it a snap to connect your microprocessor to an HP logic analyzer. And see how completing your HP logic analysis system with a preprocessor will speed and simplify measurements and data analysis. You'll also discover the industry's broadest selection of preprocessors – over 60 models support more than 70 microprocessors and busses including 100 MHz support for RISC and high-performance CISC processors.

So call **1-800-752-0900** today. Ask for **Ext. 1402** or mail the reply card and we'll send the application information you need from our FREE series of six industryspecific application notes.

There is a better way.

## SINGLE BOARD / AT COMPUTERS

#### 80486-25MHz

- 25MHz 80486 CPU w/Internal CACHE & Co-Processor Up to 16Mb of SIMM Memory

- 8Kbytes of Internal CACHE 128Kb or 512Kb Secondary

- CACHE Daughter Cards Ávailable

- 2/4 Way page Interleave Memory BIOS Shadowing

- · Reset/Speaker/Keylock Connector

- ROM Based Utilities

- On-Board Lithium Battery

"19 Years of Quality Service"

**Diversified** Technology An Ergon Co. 1-800-443-2667 112 E State St. • Ridgeland, MS 39157 80386-25MHz

- Up to 25MHz CPU w/CACHE

- . Up to 8Mb of RAM Memory Supports up to 20Mb with DTI's Memory Daughter Card • Optional 80387 Math Co-Processor

- Multi-Function I/O Cards Available

#### 80386-33MHz

- 33MHz 80386 CPU

- 32,64 or 128Kb of CACHE

- 6 or 8MHz Bus Speed

- · Up to 32Mb RAM

- COM 1 & COM2 (Up to 115Kb)

LPT1 w/Bidirectional Mode

- Up to 2 Floppy Drives

Future Domain Compatible SCSI Port

- PS/2 Mouse Port

- IDE Disk Drive Port

/AT is a tradename of the IBM Corp.

**CIRCLE NO. 15**

#### If you thought Multibus 1 couldn't handle complex tasks... Think Again!

From Robotics to CAD, Embedded Controllers to Host and Network Systems, MULTIBUS 1 by Zendex delivers Proven, Cost Effective Solutions that reach out and grab you!

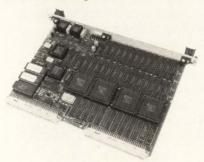

The ZX-386/20 pictured here features 20MHz clock speed and on-board SCSI,

supports up to 8MB of high-speed on-board dual-port RAM (or 16MB in PVAM), and has two 8/16-bit iSBX connectors. For Real-Time processing applications, Zendex's TRU-32 mode turns MULTIBUS 1 into a screaming 32-bit system capable of addressing 256 MB of RAM, yet is fully compatible with MULTIBUS 1 products.

For more information on our complete family of MULTIBUS 1 products, call or write Zendex today!

6780 Sierra Court Dublin, CA 94568 Phone: (415) 828-3000 FAX: (415) 828-1574

ASSOCIATE PUBLISHER/EDITOR-IN-CHIEF John C. Miklosz (508) 392-2114

#### SENIOR EDITORS

Ron Wilson, Integrated Circuits (503) 284-3432 Warren Andrews, Computers & Subsystems (508) 283-2102 Barbara Tuck, ASICs (516) 744-2984

Michael G. Donlin, Design and Development Tools (508) 392-2123 Tom Williams, Software (408) 335-5514

SECTION EDITORS Ron Wilson, Technology Updates (503) 284-3432 Jeffrey Child, New Product Highlights (508) 392-2126

> EDITOR: News Edition John H. Mayer (508) 392-2118

**NEWS EDITOR:** News Edition Elizabeth A. Stein (508) 392-2116

MANAGING EDITOR: John Donovan (508) 392-2115

MANAGING EDITOR: News Edition Barbara-Ann Scofidio (508) 392-2121

> ASSISTANT EDITORS: Sue Cavallaro, Anne Holm

PRESENTATION MANAGER: Richard D. Sarno

ASSISTANT PRESENTATION MANAGER: Claire Coupal

EDITORIAL ASSISTANTS: Claire Ellis, Terrie Robertson

ART DIRECTOR: Jan Horner

ILLUSTRATORS: Fred Lomas, Manuel King COVER ART: Gary M. Torrisi

AD TRAFFIC MANAGER: Betsy Anderson

**CIRCULATION DIRECTOR:** Robert P. Dromgoole **CIRCULATION MANAGER:** George Andrew

PUBLISHER

David L. Allen (508) 392-2111 ASSOCIATE PUBLISHER/NATIONAL SALES MANAGER:

Tim L. Tobeck (516) 883-8815

Advanced Technology Group L. John Ford, Senior Vice-President Leslie P. Cypret, Vice-President, Administration **One Technology Park Drive** P.O. Box 990 Westford, MA 01886 Tel:(508) 692-0700 Fax:(508) 692-0525

Postmaster: Send change of address form 3579 to COMPUTER DESIGN circulation Department, Box 3466, Tulsa, OK 74101

'BPA

# HITACHI'S DK515, 51/4", 780 MB WINCHESTER

From any point of view, this 51/4" disk drive reflects Hitachi's superior technical expertise, high-performance, and quality.

The DK515 features a fast 2.46 MB/ sec. data transfer rate, an average access time of 16 ms, and a choice of ESDI, SCSI, or ESMD interfaces.

Like all Hitachi drives, the DK515 reflects quality, because all critical components—including heads, media, and servo systems are designed, engineered, and manufactured by Hitachi.

Then, to make sure that Hitachi's strict standards of lence are maintained, each and every drive is 100% burned-A Reflection of Quality in and tested. The final result: a clear reflection of Hitachi's commitment

#### Available now

For more information about Hitachi disk drives, cali vot loca Hitachi Disrr Hitachi at 1-800-283-408 Ext. 877

> Hitachi America Computer Divisio Hitachi Plaza ierra Point Parkway 1e. CA 94005-1819

#### $(\mathbf{0})$ Our Standards Set Standards

#### Authorized Distributors

CONSAN 612-949-0053 (IA, IL, IN, KS, KY, MI, MN, MO, ND, NE, OH, Pittsburgh, PA, SD, WI)

GENTRY ASSOCIATES 800-877-2225 (AL, D.C., FL, GA, LA, MD, MS, NC, SC, TN, VA)

R SQUARED 800-777-3478 (AZ, CA, CO, NM, OR, UT, WA, WY)

SIGNAL 800-228-8781 (CT, MA, ME, NH, RI, VT)

SPECIALIZED SYSTEMS TECHNOLOGY 800-688-8993 (AR, LA, OK, TX)

## WHEN MANY THINGS COME TOGETHER, BREAKTHROUGHS HAPPEN.

# Now Available! A Real Breakthrough In DSP: 400MOPS Array Processing Chip Sets.

The world's fastest DSP product family is now together as a complete system solution from Array Microsystems. We started by gathering world leaders in digital signal processing to build a new company dedicated to supplying the next generation of DSP. Our products are a response to the needs of E-Systems, Tektronix, United Technologies, and our other industry development partners. Together, we pioneered VAST<sup>™</sup> tech-

nology, the first architecture to perform a complete DSP algorithm while operating on entire arrays of data in parallel — in real time, on a single silicon chip. Not only does array processing make 400 million operations per second possible, its high-level instructions make programming nearly trans-

| SOLUTION       | 1K<br>complex<br>FFT | 64K<br>complex<br>FFT | 2K tap<br>FIR |

|----------------|----------------------|-----------------------|---------------|

| Array A66      | 12 Martin            |                       |               |

| 1 processor    | 131                  | 13.1                  | 2.3           |

|                | μSec                 | mSec                  | MHz           |

| Fully cascaded | 26µSec               | 1.6mSec               | 25MHz         |

|                | (5)                  | (8)                   | (13)          |

parent. For example, eight simple instructions execute a complex 64K-point FFT. Array Microsystems delivers complete solutions, not just DSP chips. The A66 family includes everything you need: chip sets, software development tools, complete array processor boards,

and custom memory ICs and modules. The Digital Array Signal Processor (DASP) is the heart

of the chip set, and executes 16 highlevel functions, including FFT butterflies, windowing, complex multiplies, and general-purpose functions. The Programmable Array

**CIRCLE NO. 18**

Controller (PAC) manages the entire system, including address generation for DASP and memory, and I/O up to 80 MHz. For even higher performance, you can cascade DASP/PAC chip sets (see table) You'll see A66 solutions in next-generation aerospace and defense systems, test equipment. medical instruments, and other breakthrough applications like HDTV. Join us by calling our DSP hotline. We'll help put the world's fastest DSP into your next application.

1420 Quail Lake Loop, Colorado Springs, Colorado 80906 • Call 719-540-7999, FAX 719-540-7950.

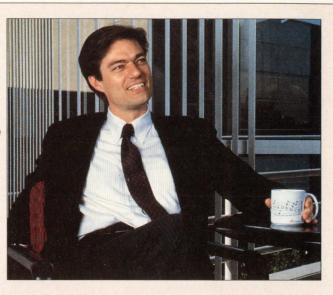

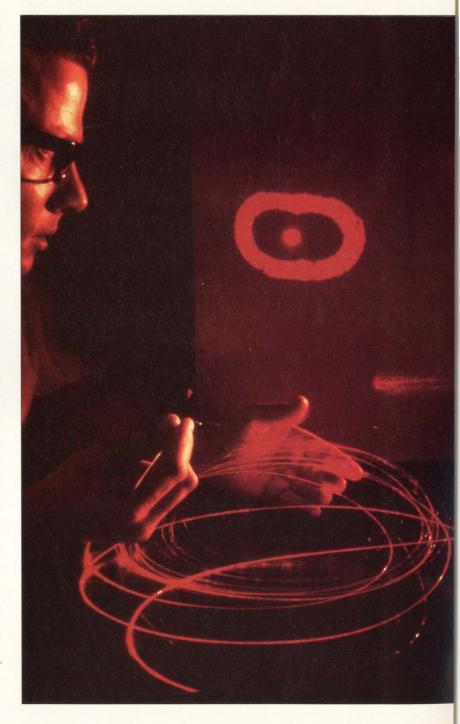

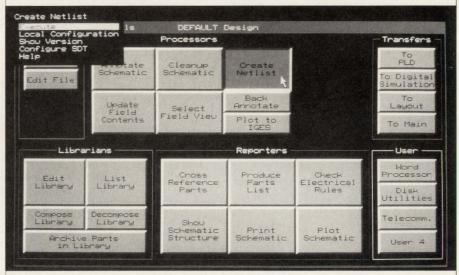

# Joe Costello on: Concurrent Engineering

s the electronics industry enters the '90s, electronics manufacturers face greater challenges in delivering higher-quality, more-sophisticated products in ever-shortening market windows. Design automation can play a major role in helping organizations meet this time-to-market challenge.

Design automation is no longer simply a set of drafting tools or complex switch simulators available to a handful of designers. Instead, design automation delivers a bread range of same

delivers a broad range of capabilities that are now used throughout the product development process. To meet the market challenges of the '90s, organizations are looking to change both the way they approach individual engineering tasks and the entire design methodology.

An emerging design methodology that has received much attention, concurrent engineering is a methodology customers

are addressing with design automation. This methodology promises to be a major factor in accelerating product development (see "Concurrent engineering: the official definition," p 22).

The goal of concurrent engineering is to shorten significantly the product development process by reducing the number of design iterations that result from failure to consider issues such as manufacturability or reliability early enough in the design cycle. In this context, design automation provides a key part of the infrastructure through which a company can begin to use concurrent engineering techniques.

But concurrent engineering isn't a product. A customer can't buy concurrent engineering from an EDA vendor. Customers must implement new design methodologies. Still, they can augment the process by using computer-based facilitators. It's important to differentiate between methodologies, such as concurrent engineering, and computer-based facilitators, such as design automation.

There is no one correct way of implementing new

design methodologies. An organization's ability to implement successfully a methodology such as concurrent engineering is highly dependent on changes in design philosophy in an organization, and on the type of products being developed.

It's also important to understand that the role of design automation in concurrent engineering isn't limited to a set of technical requirements that any single CAD vendor can deliver. Multiple design auto-

Customers can augment the concurrent engineering process by using a computer-based facilitator such as design automation. mation disciplines and vendors within EDA, as well as mechanical CAD and CAM, should be able to be used in any concurrent engineering implementation. The responsibility of EDA

vendors in helping customers meet the challenges of the '90s therefore goes beyond just providing products that might be labeled as concurrent engineering. Vendors must deliver the solutions, frameworks and tools that make it possible for custom-

ers to build environments that best suit their design requirements and methodologies. This, in turn, implies that the EDA industry must drive and support a broad set of standards within EDA. These standards must reach out to other design disciplines so that customers can choose the mix of suppliers that meets their requirements.

Customers that implement concurrent engineering must address the organizational and computer-based structures and communication mechanisms. Design automation is a facilitator that can help an organization change its design practices, but it's not a substitute for making those cultural changes.

Although not a magic formula, design automation will have a profound impact on the proficiency with which a methodology such as concurrent engineering is implemented and practiced. As noted in the sidebar, computer-based initiatives are critical to concurrent engineering in that they provide an infrastructure to support the organizational changes.

There are three key initiatives that EDA vendors

#### Concurrent engineering: the official definition

he Institute for Defense Analysis (IDA) report on concurrent engineering says it's "a systematic approach to the integrated, concurrent design of products and their related processes, including manufacture and support. This approach is intended to cause the developers, from the outset, to consider all elements of the product life cycle from conception through disposal, including quality, cost, schedule, and user requirements."

Organizations that adopt concurrent engineering try to get designers to identify critical dependencies between disciplines early in the design cycle. They do this by institutionalizing the process by which design teams explore optimization alternatives so that design changes will least affect the cost and duration of a project.

Though changing organizational behavior is always difficult at best, the benefits often outweigh the costs. The findings of an IDA survey of 11 companies that adopted some degree of concurrent engineering showed that it could shorten time-to-market. The study claims that concurrent engineering contributed to the following results: a 50 percent reduction in engineering change orders in early production; a 40 to 60 percent reduction in development cycle time; a 30 to 40 percent reduction in manufacturing costs; and a 75 percent reduction in scrap and rework.

The consistent comment among those that have adopted concurrent engineering is that there's no one best way to implement this methodology. However, the IDA survey did identify three complementary initiatives associated with successful implementation, and all the success stories placed varying degrees of emphasis on each of them. These three initiatives include engineering process initiatives (such as the formation of multidisciplinary teams), computerbased support initiatives, and the use of formal methods.

Engineering process initiatives are actions taken by management to improve the organizational structure and design process used to develop products. This requires making whatever cultural changes are necessary (often a difficult task) to increase communication between design disciplines. Computer-based support initiatives are the installation of facilitating technologies such as design automation and verification tools, frameworks, and integrated design environments. Levels of sophistication vary, but a common theme is a drive to establish a design framework to provide consistency and compatibility of tools within and between design disciplines.

Formal methods vary greatly and are difficult to tightly categorize. They are best described as "a range of quality engineering techniques used to manage system trade-offs and to find optimum design and production process parameters." The fundamental goal of formal methods is to incorporate a scientific approach to identifying problems and solving them.

As is true with any major change in design methodology, successful implementation of concurrent engineering will be driven by new technology combined with substantive organizational realignment and cultural change. So significant commitment and participation is required by management to support the implementation of concurrent engineering.

and the EDA industry must adopt to support organizations' efforts to implement new design methodologies such as concurrent engineering. They are as follows: delivering open solutions that can be used with concurrent design practices; supporting industry standards to increase customers' flexibility and choice in building custom environments; and practicing what we preach, especially with regard to delivering quality products on schedule.

#### Open solutions

First, we must deliver open solutions that can support our customers' ability to automate the methodologies of their choice, including concurrent engineering. And the biggest step toward providing open solutions is propagating the use of design frameworks.

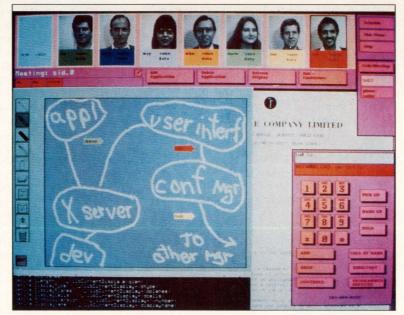

Within the realm of concurrent engineering, the key technical issue is to provide a framework that supports the flow of information between tasks, engineers, and the overall product development process. Different types of information flow are required for different concurrent processes.

An ASIC designer, for example, needs to know his design data and will want to see major changes to board logic, but will not want to know about every change related to the board layout. Only when the board layout designer has reached a certain level of completion in his design tasks will the information become relevant to the ASIC designer. Design frameworks provide the most efficient infrastructure for facilitating the right level of communication between tasks, and allowing an organization to extend and modify a design environment.

There are three levels at which frameworks can support concurrent engineering practices:

Tool to tool during the engineering process;

Designer to designer within an engineering team;Team to team.

At these levels the frameworks must be open. In any one environment, tools and frameworks will be supplied by multiple vendors. Reality suggests that no one vendor can provide the best-in-class tools spanning the entire development cycle. So frameworks must have the capability to integrate thirdparty commercial tools, proprietary tools, and other frameworks seamlessly into the design environment.

#### Information concurrency

It's useful to consider the different classes of user organization as levels in a hierarchy for implementing design concurrency. At the first level, one engineer could be using two or more tools together so that changes in a basic logical or physical representation of a circuit are rapidly reflected in the analysis tools. In the classic case, the engineer might be using a gate-level schematic design tool with a digital simulator, though in today's design environments he also might be using behavioral models, synthesis and timing analyzers on the same circuit.

Ideally, in this first case, changes in the schematic design tool or in the logic simulator are reflected in the other as the engineer debugs the circuit. An update in the logic produces a change in the results of the analysis.

At the second level, several members of a team are working together on a single project. The project might involve digital designers, analog engineers, or printed circuit board or IC layout specialists. They may be sharing several tools integrated on one framework, different framework-based systems, or standalone tools with no explicit framework and from different vendors.

Within the second level, the information concurrency required can be very different. Every change made by each engineer shouldn't necessarily be communicated, nor should all data used by one engineer be downloaded to another. According to an organization's policies and methodologies,

only relevant team data will be exchanged.

For example, engineers might have private workspaces where logic design iterations can be made, and policies would exist for how work should be checked into a central design space. Likewise, printed circuit board layout data would be checked in only after it has passed manufac-

turability tests. At that point, logic designers would receive only the layout data that was relevant to back annotation or logic simulation.

At the third level, multiple teams from completely different disciplines are working as part of a single design environment. Mechanical, electronic, manufacturing, and computer-aided software engineering teams with different frameworks and tools from multiple vendors are working together. Again, very different types of information concurrency, subject to an organization's policies, are required. Much as in the team design process, only subsets of the data are transferred between teams. These subsets reflect major changes in the project. This information concurrency will be governed by release procedures, engineering change order policies, and other company-specific processes.

It's essential to recognize that each level of concurrency is highly dependent on the tasks, on the mix of vendors and tools, and on a company's methodology and policies. Different framework facilities are needed to support each class of data interchange and concurrency. Multidisciplinary engineering teams from different departments will choose the EDA, CASE and mechanical tools that best meet the requirements of a specific design, and integrate them into this environment.

This is why it's so essential for us, as EDA vendors, to deliver open framework-based solutions. The frameworks provide the glue that links the design teams and individuals together. Just as there's no single "right" set of tools needed for design, there's no one way to implement concurrent engineering. We must deliver the products and solutions that make it possible for a customer to take advantage of design automation in the context of the organization's methodologies and policies, whether it's concurrent engineering or another approach.

#### Promoting industry standards

Openness, as provided by any one vendor, isn't enough, however. The EDA industry must evolve to the point where we collectively can provide customers with the flexibility to build solutions to best support their design processes. Truly open solutions will only become a reality if we as an industry band together to drive real industry standards such as frameworks and electronic data interchange.

Creation of the CAD Framework Initiative (CFI) was the first essential step in defining meaningful industry standards to support users' requirements for building their solutions. The CFI has already taken major steps toward the development of guidelines for frameworks in some areas. A demonstration was pre-

> sented at the Design Automation Conference last June, and vendors can move toward the overall proposal by adopting known standards such as Unix and the X Window System.

> The first guidelines from CFI are scheduled to be released by mid-year 1991. We, as an industry and as vendors, must commit to implementing these guidelines in our frameworks, where

appropriate, within one year of the standards' release. In other words, make the CFI guidelines real in 1992. Achieving this goal depends on real commitment of technical and business resources from CFI participants to drive the standards process.

#### Where should we be going?

Another step the EDA industry must take is to practice what we preach. The EDA industry has received notoriously low marks on delivery of high-quality solutions in a timely fashion. As individual companies, and as an industry, we need to invest in methodologies that will help us to correct this behavior. We need to instill the "quality first" philosophy and make the necessary changes in our design processes so that our stated product goals are actually supported.

And we need to keep the big picture in mind. Our basic charter as EDA vendors is to develop solutions that enable customers to deliver more sophisticated, higher-quality products in ever-shortening market windows.

But electronic design is only one of many functions that are necessary to get quality products to market, and today we're looking at only the first standards proposal from CFI. The EDA industry needs to continue to drive the standards initiatives for its own products, and to expand its framework vision to interconnect with other parts of the design process. Only then will we have done our job, as vendors and as an industry, in supporting our customers in their efforts to achieve the engineering and time-to-market challenges of the '90s.

Joseph Costello is president and CEO of Cadence Design Systems (San Jose, CA).

#### providing a framework that supports different types of information flow.

...

A key technical issue is

### FLUKE.

PACKARD LOBIC ANALYZE

# All logic analyzers give you integrated state and timing, sooner or later.

ВС

7 B 4 5

6

#### Why not now?

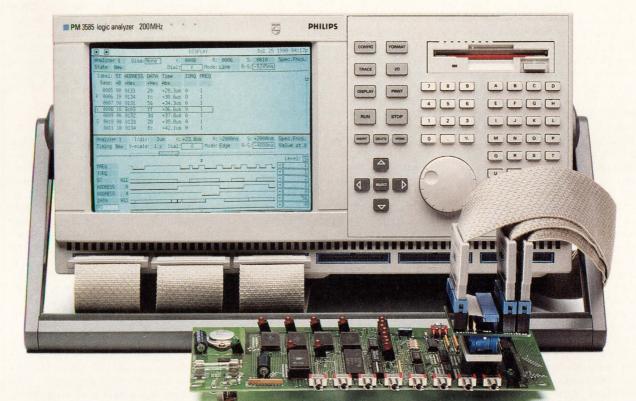

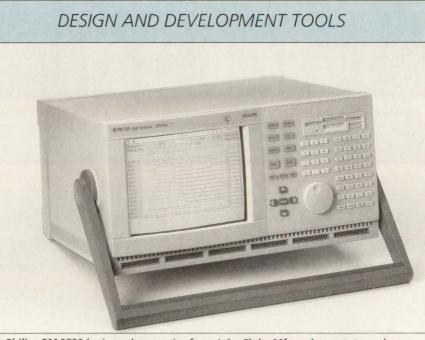

Introducing the new Philips PM 3580 family of logic analyzers from Fluke: the first instrument architecture to give you state and timing together on each channel – with a single probe.

Connect the probe to your board for state and you're automatically hooked up for timing. Or vice versa.

This means no more dual probing – a pain anytime and the source of loading problems – and no reconfiguration between state and timing. Which makes

| A basic comparison: Record all state and timing data<br>on an 8-bit microprocessor with multiplexed bus,<br>8-bits for address, 3 control signals and a clock. | HP<br>1654B                         | Tek<br>Prism/MPM                      | Philips<br>PM 3580/30 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|---------------------------------------|-----------------------|

| Probing:<br>Channels used<br>One connection                                                                                                                    | 481<br>No                           | 48 <sup>2</sup><br>No                 | 20<br>Yes             |

| Setups                                                                                                                                                         | Two                                 | Two+                                  | One                   |

| Interfaces to learn                                                                                                                                            | Two                                 | Two+                                  | One                   |

| Integrated<br>state & timing<br>triggering                                                                                                                     | No, only<br>one arming<br>condition | No, only<br>indirect 4-bit<br>Teklink | Yes,<br>8 levels      |

| State & timing data per pin                                                                                                                                    | No                                  | No                                    | Yes                   |

| Price                                                                                                                                                          | \$6700                              | \$8600                                | \$4250                |

these analyzers simple to learn and use.

Plus, the pop-up menus and keyboard shortcuts guide you quickly through setup and data analysis. No matter if you use it every day or once a year.

What's more, capturing an elusive bug has never been easier with eight unrestricted trigger levels that let you select from state and ALLIANCE IN TEST & MEASUREMENT

PHILIPS

# Why not sooner?

timing trigger conditions on each level.

But being simple doesn't mean simplistic. Basic performance of the PM 3580 family ranges from 32 to 96 channels, each with 50 MHz state and up to 200 MHz timing, plus 3 nanosecond glitch capture and 2K of memory per channel. For 8-, 16and 32-bit processors.

And you get all this for nearly half the cost of comparable analyzers.

We'd like to send you a video. Or show you how to make state and timing measurements at your workplace – in 30 minutes or less.

We'll even bring the stopwatch so you can time us. And you can keep it to time the competition.

So call us today at 1-800-44-FLUKE. Ask for extension 720.

Because sooner is better.

John Fluke Mtg. Co., Inc., P.O. Box 9090, M/S 250C, Everett, WA 98206-9090. U.S. (206) 356-5400. Canada (416) 890-7600. Other countries: (206) 356-5500. © 1990. All rights reserved. Ad No. 00001.

FAST ANSWERS.

**CIRCLE NO. 19**

#### INTEGRATED CIRCUITS

# Controller-level network could revolutionize connectivity

Ron Wilson, Senior Editor

LAN would be the perfect solution to many control problems. If you could just put the sensors and actuators of your VCR on a network, you could save a bundle on cabling and drivers. If you could connect your VCR, kitchen appliances, lights and climate control on a network, you could achieve the automated house. Similar thoughts have driven auto makers, manufacturing equipment vendors and even the designers of office towers to investigate control networks.

But existing network technology can't do the job. Ethernet and its relatives are comfortable only with large data packets, not with the small messages common in device control applications. Software for the seven-layer International Standards Organization protocol stack is too big and expensive to put in 8-bit microcontrollers. And the hardware cost of an Ethernet node—even with the latest 10Base-T technology—is far too high for use inside a piece of consumer electronics, an automobile or a suburban home.

These limitations have led design-

ers to try other approaches. Inside boxes, engineers have tried point-topoint wiring with synchronous serial interfaces—a common approach for small networks of 8-bit microcontrollers. On larger designs a variety of specialized local networks have sprung up, such as the Controller Area Network for automotive use.

But now a Silicon Gulch start-up may have a general solution to the problem. Echelon (Palo Alto, CA), started by Apple cofounder Mike Markkula, has developed a network architecture that addresses the throughput, cost and complexity issues of control networks.

"Back in 1986," says Echelon vicepresident of marketing Beatrice Yormark, "Markkula was wiring his house. He wanted to be able to centrally control most of the electrical things in the house, but the problem of running control wiring to all the individual pieces was a nightmare. There were control systems that used power lines for communication, but they weren't reliable enough to count on. He realized that what he needed didn't exist—a control network with a reliable protocol and the ability to use all the media at hand, but costing only about \$10 per node. So he started another company."

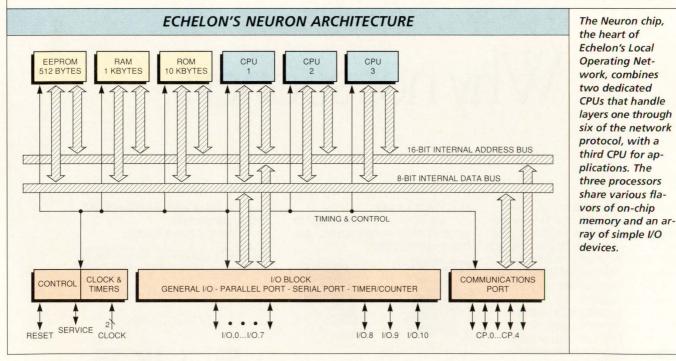

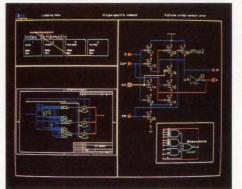

Echelon calls its development a LON (Local Operating Network). The architecture includes an ISOstyle seven-layer protocol, a singlechip network termination, operating and protocol software, a development system, and a variety of transducers that let the network operate over any medium from local RF to infrared to power lines.

#### Silicon at the center

The only way Echelon could meet vice-chairman Markkula's cost criterion was by designing the architecture around the capabilities of a single piece of silicon. This focus is called a Neuron chip. Each Neuron serves as both network termination and, in many cases, local microcontroller for the device it connects to the network. This means the chip must handle the entire seven-layer ISO protocol stack, including an application layer that often includes simple control algorithms. That's a substantial computing order.

To meet it, Echelon developed a unique approach to on-chip multiprocessing—a set of three CPUs with separate register sets, but shared memory and a shared ALU. Each CPU executes on its own cycle

26 JANUARY 1, 1991 COMPUTER DESIGN

# We wrote the books on real-time.

When it comes to real-time system software, Microware Systems Corporation leads the way. Now, we offer two books that provide you with complete real-time solutions — the OS-9 and OS-9000 Catalogs.

Microware offers the broadest range of real-time solutions in the industry. Data sheets and flyers just weren't enough to tell our story, so we wrote these books to tell you about our real-time operating systems. These catalogs are chock-full of more than 330 pages of useful information about our operating systems including networking, graphics, language compilers and productivity tools. OS-9 is the world's leading real-time operating system for 680X0-based systems. OS-9 has been designed into thousands of embedded applications from industrial automation to consumer electronics.

OS-9000 is a portable real-time operating system written in C for advanced CISC and RISC processors. The ability to port OS-9000 to various hardware platforms "future-proofs" your real-time software investment through the 1990s.

Put the world's real-time leader to work for you today.

For Your Free Catalogs, Call **1-800-475-9000** In California, call (408) 980-0201

Michoumano

#### MICROWARE SYSTEMS CORPORATION

1900 N. W. 114th Street • Des Moines, Iowa 50322 Phone: (515) 224-1929 • Fax: (515) 224-1352

Microware is a registered trademark of Microware Systems Corporation. OS-9 and OS-9000 are trademarks of Microware Systems Corporation. All other brand or product names are trademarks or registered trademarks of their respective holders.

MORE CHOICES • MORE OPTIONS • TOTAL SUPPORT

CIRCLE NO. 20

#### TECHNOLOGY UPDATES

#### INTEGRATED CIRCUITS

of a three-phase clock, allowing the processors to share hardware. "You have essentially three 1-Mips CPUs in the chip," explains Echelon vicepresident of engineering Michael Gilbert. "To achieve both low cost and concurrency, we dedicated the CPUs to separate functions."

One of the specialized Echelon processors is dedicated to the media access control layer of the stack, another handles layers two through six, and a final CPU—this one available to the user—handles layer seven, the application layer. "The user sees a stack-oriented C engine," Gilbert says.

The lower two CPUs operate transparently, their services available to applications through a set of system calls in a ROM-based multitasking kernel. So the user just works with variables that may be shared with other applications on other Neuron chips.

In addition to having the network connection, the user has enough resources to perform a simple control application. The Neuron contains 1 kbyte of SRAM, 512 bytes of EE-PROM—where users would normally put their application code and a variety of serial ports, parallel ports and counter/timers.

For more-involved applications, the Neuron will need to work with additional I/O and processing chips, and perhaps additional memory. In these situations, the Neuron can act as an 8-bit peripheral chip to a conventional microcontroller. A version of the Neuron will also be available with 2 kbytes of SRAM and, in place of the ROM, an external memory interface. This permits the device to reach up to 64 kbytes of external memory, and provides an emulation chip for development.

#### Onto the network

The Neuron actually talks to the LON through a special pair of pins called a LONtalk port. In one mode, the port communicates in differential Manchester-encoded data streams. "For simple applications where you're communicating within a box, you don't need a transceiver you can just let the Neuron chips talk to each other," Gilbert maintains. But when the devices are connected through more-complex media, such as power-line modulators, the chip needs external Echelon-designed transceivers. Some of these transceivers use their own modulation schemes and need to control the data rate of the LONtalk port, so a second, handshaking mode is available for interfacing to them.

The Neuron implements a quite sophisticated network over its variety of media. The protocol is basically collision-sensing, but with retry algorithms that improve predictability and maintain maximum network bandwidth on saturated networks, according to Echelon. In addition, the scheme provides for prioritized messages and master/slave polling arrangements.

#### The LON may be a gateway to new levels of automation, not just another technology in which a design can become mired.

#### ...

The underlying network runs at a maximum rate of around 1 Mbit/s, although this is highly medium-dependent. Echelon claims to get only about 10 kbits/s through a power line, for instance. Everything, from the architecture of the CPUs to the memory size to the protocol, is optimized around small messages—typically 10 to 15 bytes. This choice clearly reflects the LON's bias toward control applications, and away from the big packets used for transferring files on Ethernets.

Using these small messages over a 1-Mbit/s link, the network can handle about 800 packets/s, according to Gilbert. A single Neuron chip can process about 100 to 150 packets/s.

#### Help for developers

One barrier that Echelon will face is social, not technical—most of the target customers for the LON concept aren't experienced network developers. Instead, they're system designers interconnecting the subsystems in an appliance or television, or automotive engineers laying out the instruments, sensors and lights on a new car, or architects designing the HVAC (heating, ventilation and air conditioning) systems for an office. These people don't intend to take the summer off to learn about ISO networks.

Echelon has taken several steps to solve this problem. First, the workings of the network have been rendered as transparent as possible. One can simply program the Neuron application CPU in C or assembler, declaring network-global variables and using LON system calls to the embedded operating system. Second, the company has put together an elaborate development environment, including object-oriented development software, a C compiler for the Neuron's application processor, a ROM-based executive, a Neuron emulator, prototyping aids, evaluation boards for the Echelon transceivers, and a protocol analyzer. All these capabilities are configured around a PC/AT.

The company also recognizes that such a novel idea, no matter how valuable, can be hamstrung if it's available only from a start-up. "From the beginning," says Yormark, "our strategy has been to develop the technology and then license it, so that the idea can spread rapidly." Hence the Neuron chips aren't actually built by Echelon. Rather, they're being introduced by Motorola (Austin, TX) and Toshiba (Irvine, CA).

With a combination of novel technology, seasoned management and powerful partners, Echelon is in good shape to support rapid growth. But perhaps the most significant ingredient is the system-level solution that Echelon has devised, leaving almost nothing of the network architecture to be dealt with by the user. This may make the LON a solution to system design problems and a gateway to new levels of automation, not just another technology in which a design can become mired.

For more information about the technologies, products or companies mentioned in this article, call or circle the appropriate number on the Reader Inquiry Card.

| Echelon        |            |

|----------------|------------|

| (800) 258-4566 | Circle 201 |

| Motorola       |            |

| (512) 891-2000 | Circle 202 |

| Toshiba        |            |

| (714) 455-2000 | Circle 203 |

|                |            |

# **Count On IDT**

#### The R3001 RISController™: The Embedded Processing Solution

The R3001 is the first derivative of the R3000 processor designed specifically for embedded control applications. Compared to the Intel 960 and AMD 29K processors, the R3001 is the most cost-effective solution for these applications—we have the data to prove it! Call and ask for KIT CODE 0091A to get an R3001 Performance Comparison Report.

#### BiCEMOS<sup>™</sup> ECL SRAMs: Technology for the '90s

The SyncFIFO<sup>™</sup> Family:

**Double Your FIFO Performance**

World's Fastest FIFOs

Design the fastest systems with IDT's BiCEMOS ECL family. At 7ns, the IDT10494 is the fastest BiCMOS 64K ECL SRAM in production. 256K and synchronous self-timed SRAMs are also available in 10K/100K/101K configurations. Call and ask for **KIT CODE 0091B** to get a copy of the **BiCEMOS ECL Product Information** booklet.

SyncFIFOs offer leading-edge

performance that is 50% faster

nous architecture is easy to

implement and reduces chip

count 9-to-1. SyncFIFOs have

18-bit buses and are ideal for 32-

bit systems. Ask for **KIT CODE**

with the IDT SyncFIFOM.

0091D to get AN-60: Designing

than other FIFOs. The synchro-

#### FCT-T Logic: Fastest Speed/ Lowest Ground Bounce