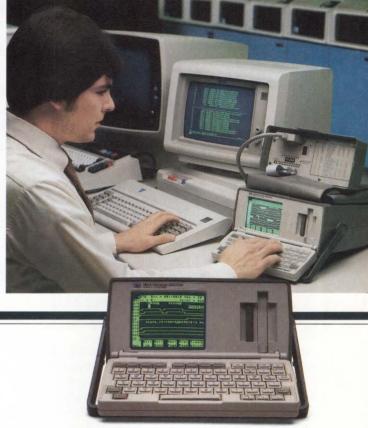

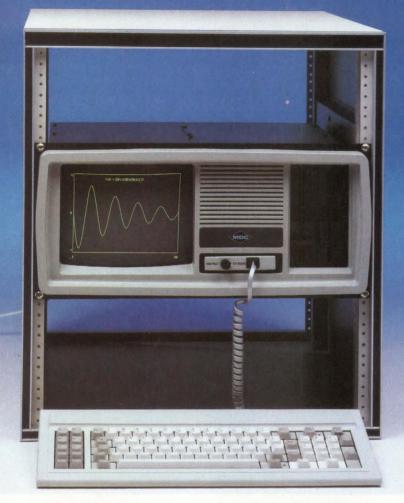

# Before TEMPLATE, graphics software hat ran on mainframes and minis and micros all looked like this.

Which is to say. nonexistent. Some manufacturers make graphics software packages for main-

frames. Others for minis. Still others make it for micros. But no one made high-level graphics software that ran on all three.

TEMPLATE just changed all that. By becoming the *only* high-level graphics software available on micros, minis and mainframes. And it took our extensive experience in graphics software to do it.

Now all computer-using design engineers and scientists can utilize the industry's finest software. And bring mainframe applications right to the bench. Or vice versa. Which means TEMPLATE's device-intelligence and computer-independence is even further enhanced. And you get the graphics functionality for mechanical and electrical CAD.

scientific analysis. seismic work, VLSI, and molecular modeling that puts TEMPLATE in a class by itself. In

any environment, whether it's batch or

interactive, 2D or 3D.

TEMPLATE features table-driven architecture, 3D software display lists, metafile capability over 250 user-callable FORTRAN routines, workstation model, post processing capability, run-time selection, and complete support functions.

So when you're looking for graphics software that'll run on all your computers,

call Megatek.

And find out all about TEMPLATE.

The product that just gave micros, minis, and mainframes a

new computer graphics image.

See us at SIGGRAPH, Booth 1018, July 24-26. Making History out of State-of-the-Art

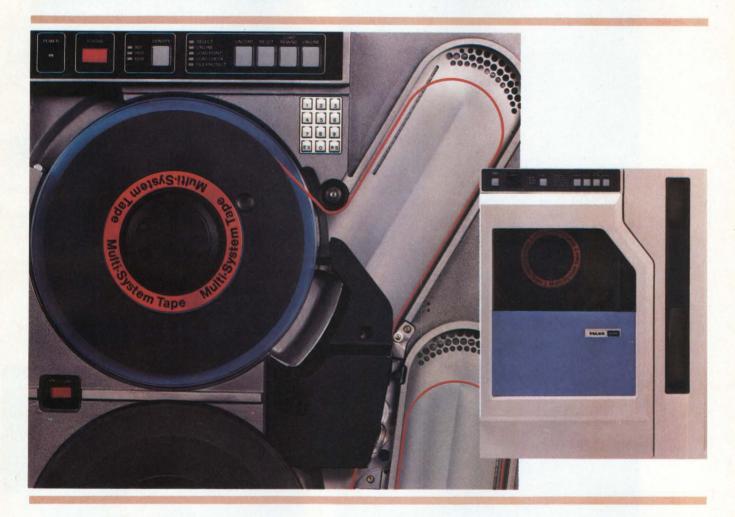

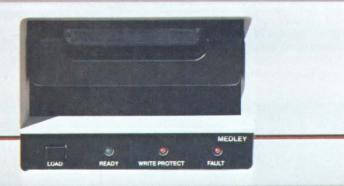

# THE PERIPHERAL DESERT

Many tri and tri again — but never make it.

Model 9400 GCR tape system—the latest in a long and honored line of Kennedy products. Products that have always been first in innovation, design, and performance. Model 9400 carries on this tradition of 'first across the line'. For complete details on the industry's premier tri-density, hi-performance tape system, write or call today.

### KENNEDY

An Allegheny International Company 1600 Shamrock Ave., Monrovia, CA 91016 (818) 357-8831 • ITT TELEX 472-0116 KENNEDY TWX 310-472-0116 KENNEDY

KENNEDY: BUALITY: COUNT ON IT

## **COMPUTER DESIGN®**

### System technology

21 Test & development: Protocol analyzers take on functions to deal with network complexities

25 Software: Dual-port operating system attacks Unix compatibility problems

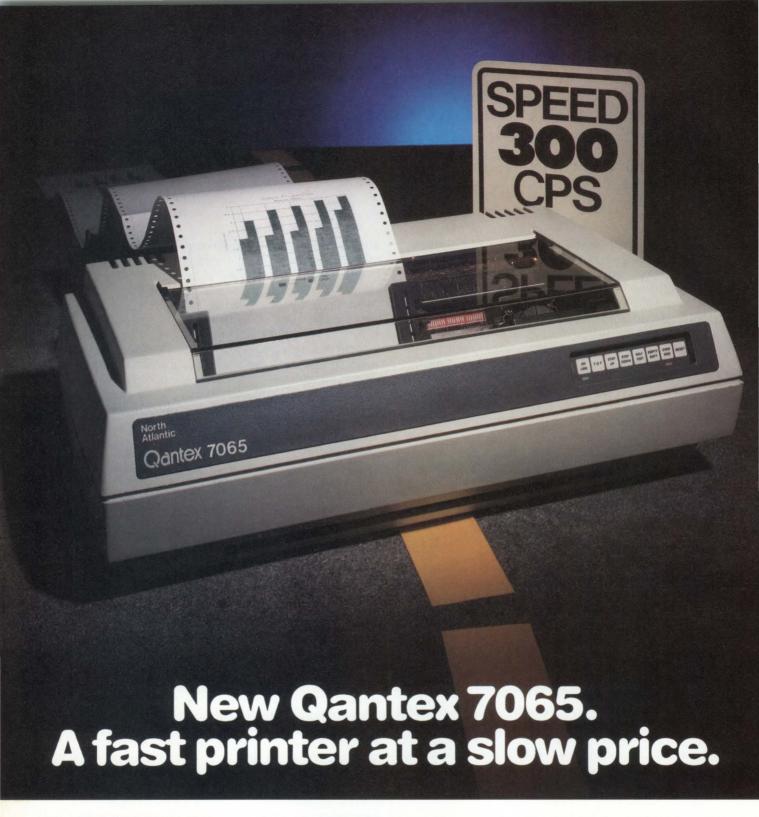

Printwheel technology ups speed, adds intelligence

34 Interface: The VMEbus to get larger slice of 16/32-bit board pie

### System design

Page 57

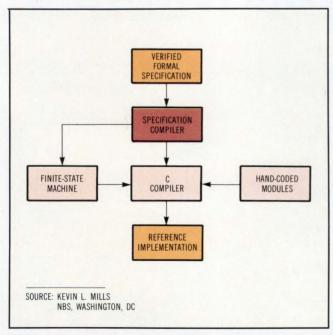

57 Data communications: Formal protocol specification ready to make its mark

by Harvey J. Hindin-Specification, implementation, validation, and test procedures are under development worldwide to help computer communication gurus define international and national protocols.

- 69 Computers: Practical and continuous speech recognition by Steve Ross and Jeff MacAllister—A continuous speech recognition system that accepts sentences of any length permits cost-effective voicedata entry in demanding real-world environments.

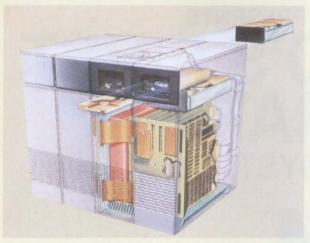

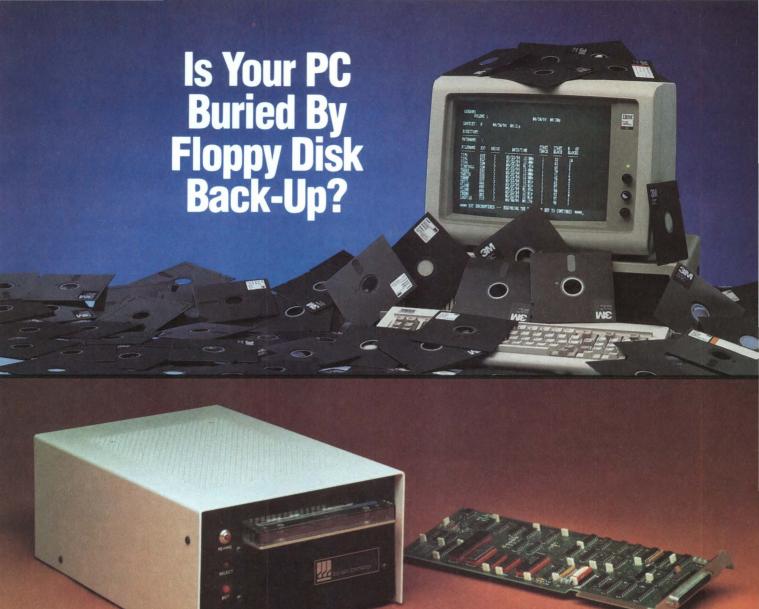

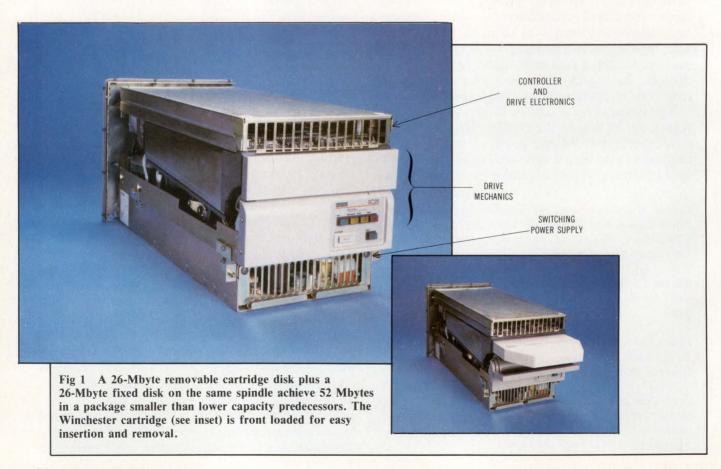

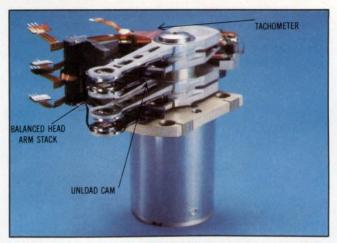

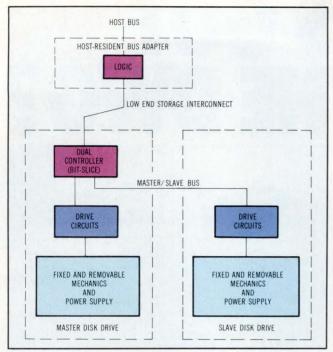

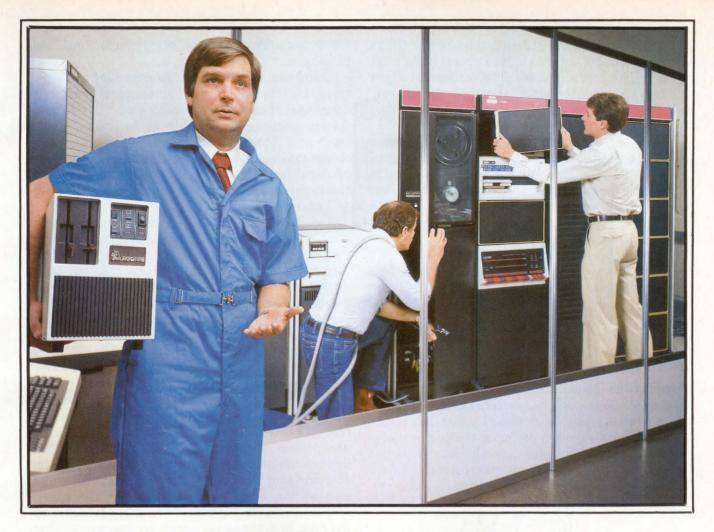

- 81 Peripherals: Removable disk drive provides high end muscle by Carl J. Blatchley, Shyam C. Parikh, Fernando A. Zayas, and Jack Cole—To keep ahead of the competition, designers set their sights on a compact Winchester drive with a removable cartridge, borrowing heavily from the world of larger, fixed-platter memories.

### SIGGRAPH '84

43 A thorough mix of technology elements has been maintained in the planning of the SIGGRAPH '84 technical program. Paper presentation and panel sessions, backed up by a variety of pertinent courses, cover a wide range of general subjects such as CAD/CAM/CAE and visual synthesis. These, in turn, contain more specific topics, including raster graphics, color perception, computer interfaces, interactive systems, and visible surface algorithms. Particular emphasis is evident in the coverage of the Japanese influence on the technology and the current status of CIM in Japan.

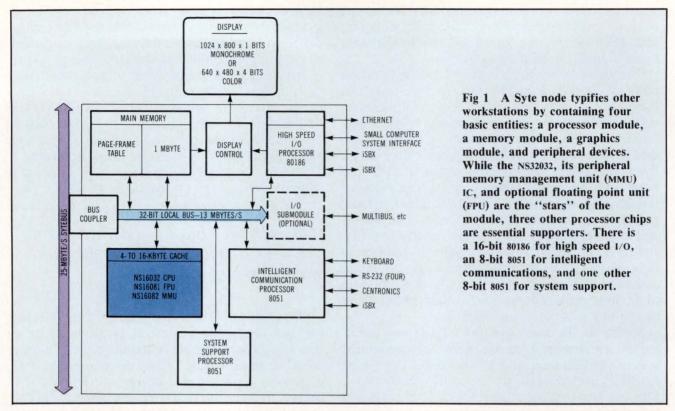

### Special report on microprocessors/microcomputers—Part II

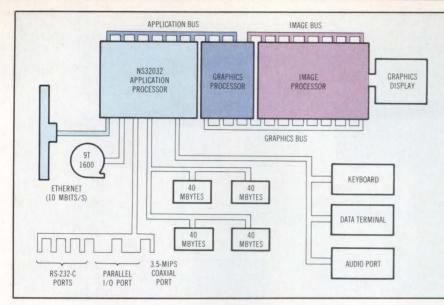

93 Thirty-two bit power can either be a boost or a bust. Although the next-generation microprocessors feature mainframe-like processing power, designers are now faced with the task of fitting these 32-bit chips into their system designs. This is a bigger job than it was with 16- and 8-bit micros. The following report looks at some early 32-bit processor implementations in engineering workstations, and knowledgeable contributors discuss leading 32-bit buses in various configurations. The choice for the system designer is both awesome and challenging.

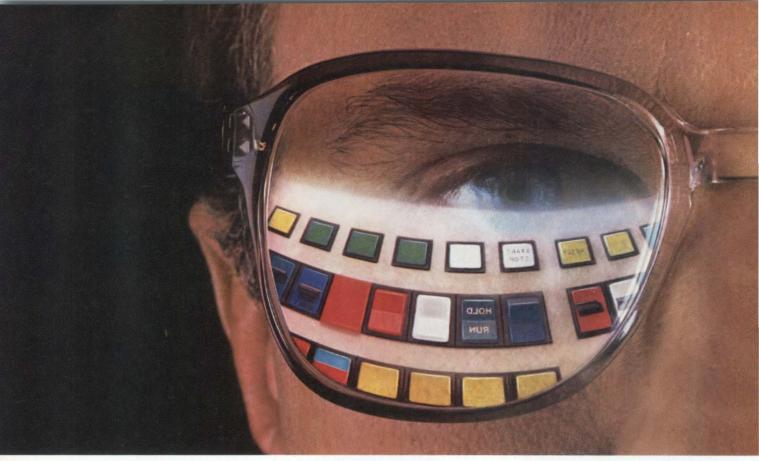

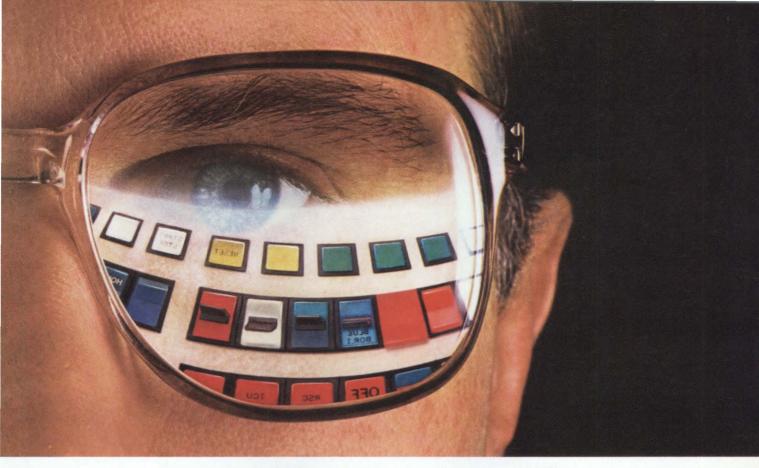

This month's cover was created and designed by Mark Lindquist, Joe Pasquale, and Anezka Sebek. Parts of the design for this cover and the June I cover were based on material supplied by Pyramid Technology.

### **NCC** product preview

165 Hundreds of computer industry companies chose NCC '84 as a key site to display or announce their newest products. This Product Preview contains many of those products that are of interest to the computer-based system designer.

165 Computers

168 Memory systems

174 Interface

176 Peripherals

179 Packaging & power

183 Software

184 Data communications

186 System elements

187 Test & development

### **Departments**

5 Up front

19 System showcase

13 Editorial

197 Advertisers' index

198 Literature

199 Recruitment

190 Calendar

190 Designer's bookcase

201 Change of address card

COMPUTER DESIGN © 1984 (ISSN-0010-4566) is published monthly, with a thirteenth and fourteenth issue respectively in June and October by PennWell Publishing Company, Advanced Technology Group, 119 Russell Street, Littleton, MA 01460. Second-class postage paid at Littleton, MA 01460 and additional mailing offices. COMPUTER DESIGN is distributed without charge to U.S. and W. Europe-based engineers and engineering managers responsible for computer-based equipment and systems design. Subscription rate for others is \$50 in U.S.A. and \$75 elsewhere. Single copy price is \$5.00 in U.S.A. and \$7.50 elsewhere. Microfilm copies of COMPUTER DESIGN are available and may be purchased from University Microfilms, a Xerox Company, 300 North Zeeb Road, Ann Arbor, Michigan 48106. POSTMASTER: CHANGE OF ADDRESS-FORM 3579 to be sent to COMPUTER DESIGN, Circulation Department, P.O. Box 593, Littleton, MA 01460 (USPS 127-340).

Officers of PennWell Publishing Company, 1421 S. Sheridan, Tulsa, OK 74101: P. C. Lauinger, Chairman; Philip C. Lauinger, Jr., President; Joseph A. Wolking, Senior Vice President; H. Mason Fackert, Group Vice President; Carl J. Lawrence, Group Vice President; V. John Maney, Vice President/Finance; L. John Ford, Vice President.

**VBPA SABP**

<sup>©</sup> COMPUTER DESIGN is a registered trademark. All rights reserved. No materials may be reprinted without permission. Phone (617) 486-9501.

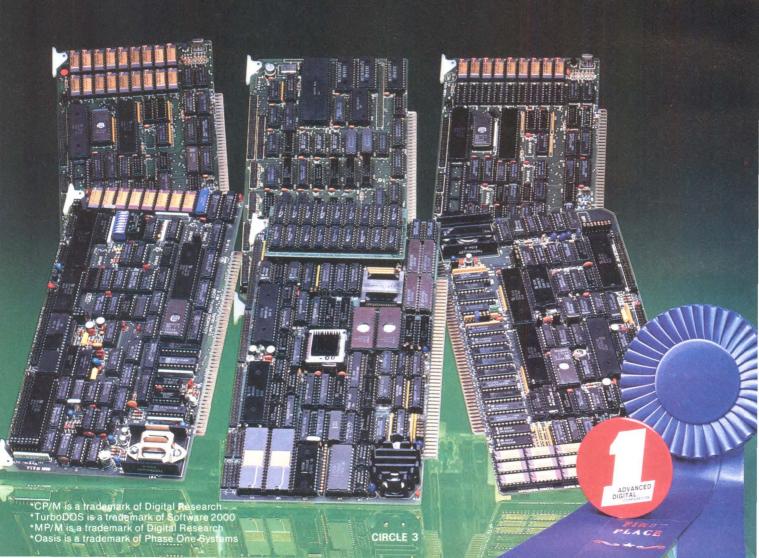

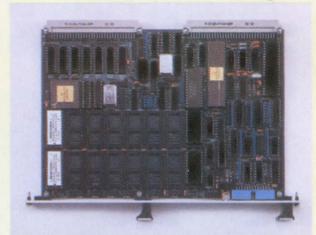

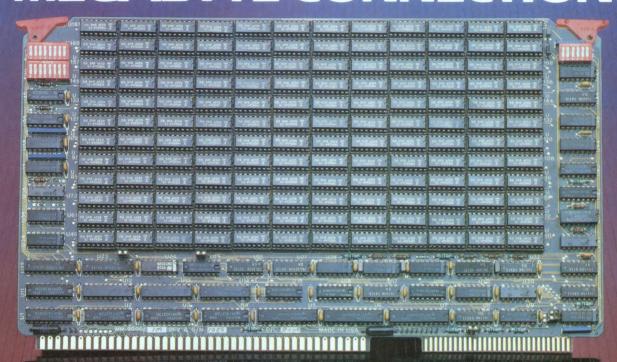

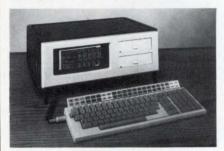

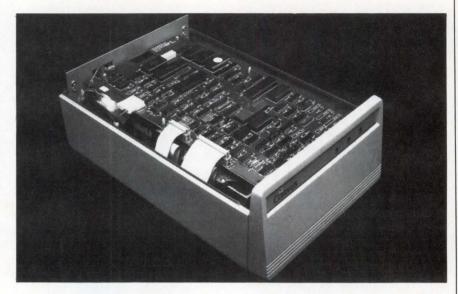

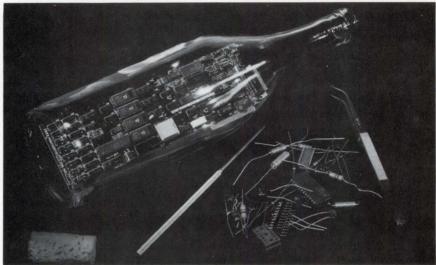

# We've Earned The Right To Be #1 By Being First So Often

When it comes to being FIRST with technology-leading products, *Advanced Digital* wears its #1 button with pride. We were *FIRST* to introduce an 8-Bit, single board S-100 computer... We were *FIRST* to introduce a 6MHz, 128KByte single board computer... We were *FIRST* to introduce a 6MHz, 128KByte Slave Processor board. And our record for being FIRST continues with...

The introduction of SUPER EIGHT – an 8MHz master with Winchester and Floppy disk controller on one board.

The introduction of SUPER SLAVE II – A dual slave processor that will support two users under TurboDOS.

• The introduction of our new SUPER 186 – the FIRST 16-Bit, single board S-100 computer that performs at twice the speed of older technologies. Loaded with features such as on-board floppy disk controller and up to 1MByte of RAM, the SUPER 186 is designed to function as a bus Slave or Master. Advanced Digital's SUPER 186 permits you to take advantage of vast libraries of sophisticated applications software.

Advanced Digital boards are IEEE 696 compatible, run under a variety of operating systems such as CP/M2.2,\* CP/M 3.0, Concurrent CP/M, MP/M,\* OASIS,\* and TurboDOS\*

(Top row L to R: Super Slave 128, HDC-1001, Super Slave 64, Bottom row L to R: Super Quad, Super 186, Super Six)

and are available with CPU speeds of 4, 6, or 8 MHz. On-board memory capacities range from 64 KBytes to 1 MByte.

When it comes to selecting your \$-100 boards, go with Advanced Digital – The Company that earned the right to be #1.

See your local computer dealer or contact Advanced Digital today... We'll help you become #1.

### Leading the Microcomputer Technology

### Advanced Digital

5432 Production Drive, Huntington Beach, CA 92649 Tel. (714) 891-4004 • Telex 183210 ADVANCED HTBH

#### In Europe:

### Advanced Digital U.K. Ltd.

27 Princess St., Hanover Square

London WIR8NQ • United Kingdom

409-0011 • 409-3359 Telex 265840 FINEST

### **UP FRONT**

### DisplayWriter-to-PC connection is no bargain

Just-introduced, the IBM board-and-cable kit that allows the IBM-PC (and compatibles) to communicate with the IBM DisplayWriter dedicated word processor is raising some eyebrows. Until now, DisplayWriters could communicate only with 5520 Administrative systems and System 38s. But now, Big Blue says, for a mere \$495 per connection board, a DisplayComm bisync program at another \$375. and \$299 for DisplayWrite2 software to emulate the DisplayWriter's commands for editing and formatting—an \$1169 total just to hook up—design managers can integrate their DisplayWriter with a PC to run DBMSs, spreadsheets, integrated packages, computer aided design programs and more. A DisplayWriter costs about 2½ times the price of a fully equipped PC. Since a PC costs little more than \$1169, and since (for most applications), a DisplayWriter cannot easily compete with current PC word-processing packages (which go for \$200 to \$500 or less), the hook-up is not feasible for many users. IBM has not said it is phasing out the DisplayWriter, but its more functional PC is a competitor for a high percentage of the dedicated word-processing customer base.—H.H.

### Technology marriage results in second product

A technology exchange pact forged three years ago by Intel Corp (Santa Clara, Calif) and Harris Corp (Melbourne, Fla) has borne its second fruit with the introduction of Harris Semiconductor's 80C88 CMOS 8/16-bit microprocessor. Coming one year after the debut of the 80C86 (a 16-bit CMOS microprocessor), the 80C88 displays full software compatibility with the earlier chip, as well as compatibility at the microcode level with NMOS 8086 and 8088 devices, according to Harris. The new CPU has a 16-bit internal architecture linking with memories and peripherals via an 8-bit bus. I/O is TTL/CMOS-compatible. Static CMOS circuit design results in a maximum standby current of 500  $\mu$ A while maximum operation current is 10 mA/MHz. This marks an 85 percent reduction in power dissipation over NMOS systems. Reduced size and battery-operated systems appear among the likely targets for this microprocessor—J. V.

### New supercomputer architecture features tens of billions of bytes

A Massive Memory Machine (MMM) is the latest innovation for a supercomputer architecture to handle memory-bound computations. According to proposers Hector Garcia-Molina and Richard J. Lipton of Princeton University (Princeton, NJ) and Jacobo Valdes of Imagen Corp (Mountain View, Calif), the machine would have a primary physical memory of tens of billions of bytes. With orders of magnitude above what is normally available in memory, the MMM would be ideal for applications where computations are simply memory bound. There, a classic von Neumann machine (even with a relatively slow 1 to 10 MIPS processor) could outperform developmental supercomputers and, as a bonus, be easier to program. Program development would be enhanced, the trio claims, because new programs written for the MMM would trade available memory space for running time. Of course, there are design problems—but a novel hardware and bus architecture now under study could lead to reduced memory access times, controllable costs, and minimal memory errors. Extensions to the machine would determine the best I/O mechanisms, virtual storage, programming language, and special processors. Among the applications: database machines, VLSI design, and artificial intelligence.-H.H.

### IBM lays cable for future token-passing LAN

To transmit data between remotely located electronic equipment within a building, a cable distribution network must be installed. Now IBM Information Systems Group (Rye Brook, NY) offers its own cabling system for its large base of office electronic equipment. Unlike Xerox's Ethernet, however, which requires a coaxial cable, IBM's cabling system uses data-grade twisted-pair wires that connect wall sockets to wiring closets. This makes for fairly easy connection for data and voice transmissions to both computers and PBXs. Computers are connected via patches at the wiring closets. This starwired system has twisted-pair cables fanning out from each of the closets that can hold up to 64 cables. Equipment is plugged into the network via special wall outlets. Both data and voice connectors can be installed, thus making a natural connection to PBXs. The cabling system is the backbone of IBM's token-passing protocol scheme for data transmission on a local area network, slated to be fully operational by 1986.—N.M.

### Will microprocessor cooperation agreement affect the NuBus?

Intel-backed Multibus II and Motorola/Signetics/Mostek-backed VMEbus devotees are already hinting (and NuBus advocates are saying no) that future versions of the Texas Instruments' NuBus will not be fully independent of National Semiconductor's Series NS32000 microprocessors. National and TI have joined forces (Computer Design, June 1, 1984, p 5) to make a name for themselves in the 32-bit microprocessor marketplace. For multiprocessing environments, NuBus has hurt its two competitors because it is said to be the most microprocessor-independent of the new breed of 32-bit buses. Whether or not TI will feel obliged to come up with a 32-bit bus specifically designed for the NS32000 remains to be seen. Unlike Multibus II and VMEbus, NuBus is a single, general purpose bus that uses reads and writes only to handle its data bits. It is too early to say if there is a better way for the NS32000—H.H.

### Lower dislocations add promise for GaAs ICs

Japan's Sumitomo Electric Industries, Ltd, has announced developments of a large dislocation-free liquid encapsulated chochralski (LEC) gallium arsenide (GaAs) crystal. Present GaAs dislocation rates typically measure 2000 to 10,000/cm<sup>2</sup>. This vastly curtails their widespread use. The firm claims dislocations ranging from 0 to 200/cm<sup>2</sup>, and foresees defect-free GaAs ICs sporting 100,000 devices/chip, as well as the possibility of accelerated GaAs production. Targeted for supercomputers and optoelectronic communications, the dislocation-free LEC GaAs FETs are expected in large quantities next year.—J.V.

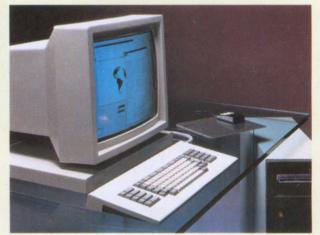

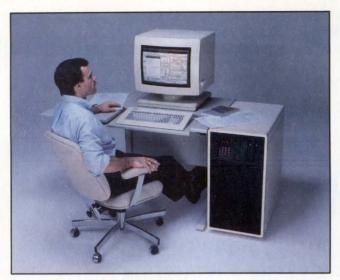

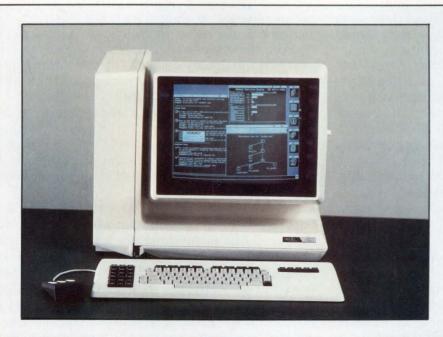

### 'Tis the year of the single-user 32-bit workstation

Thirty-two seems to be the minimum bit number that allows a single user to work at a station and derive computational results equal to those of mainframe processing. Indeed, 1984 may well be the year of the 32-bit thoroughbred. In evidence at the National Computer Graphics Association Conference were 32-bit workstations from such companies as Ridge Computers (Santa Clara, Calif), Paragon Technology (Pleasant Hill, Calif), Perq Systems Corp (Pittsburgh, Penn), and Saber Technology Corp (San Jose, Calif). Most have communication options that allow single-user stations to share resources with other workstations and large computers in a manner similar to the Apollo and Sun Microsystems networks (see Computer Design, June 15, 1984, p 97).—N.M.

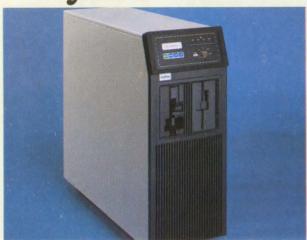

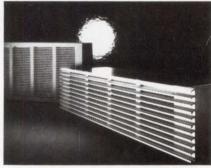

200 MB/second!

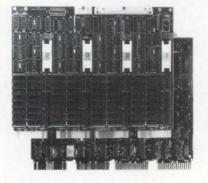

### World's Fastest Bulk Memory System

It's true. Dataram's WIDE WORD memory system delivers an incredible data rate of 200 MB/sec! Achieved by utilizing 80 or 160 bits per word and four-way interleaving

Much faster than even the fastest minicomputers can handle...but not too fast for your real-time applications, image processing, array processing or data acquisition needs.

Multi-port capability enables you to bring WIDE WORD speed to your host minicomputer. Simply connect one port to your high-speed input; the other to your mini

Our library of dedicated interfaces allows you to run with Digital Equipment, Data General, Ampex, Control Data, CSPI, Honeywell, Intel (MULTIBUS), MODCOMP, Motorola (VERSAbus), Perkin-Elmer, ROLM, and SEL. And, possibly even more importantly, we can work with you to develop a custom WIDE WORD interface.

WIDE WORD. 128 MB of high-performance memory in a compact 153/4" system. Word lengths up to 160 bits. And, of course, a data rate of 200 MB/second.

Our new WIDE WORD brochure will tell you more. And you can have it at no charge by circling the Reader Response

Number or calling us at (609) 799-0071. WIDE WORD is a trademark of Dataram Corporation. MULTIBUS is a registered trademark of Intel Corporation. VERSAbus is a trademark of Motorola, Inc.

WIDE Memory 200 MB/sec

Princeton Road

Cranbury, NJ 08512 (609) 799-0071 TWX: 510-685-2542

CIRCLE 4

### **UP FRONT**

### Spreadsheets can aid computer designer in design as well as finance

VisiCalc, Perfect Calc, SuperCalc and some three dozen other microcomputer spreadsheets are often used by design managers for project monitoring and control, and "what-if" analyses. But design engineers are missing a bet if they do not use them as an aid in such chores as sinusoidal steady-state analysis, time-domain analysis, sensitivity calculations, and logic design. Recent work at the University of Arizona (Tucson, Ariz) by electrical engineering guru Lawrence P. Huelsman has shown that the ubiquitous spreadsheet—its paper form has been around since medieval Italy—is ideal for checking how the response of a design to an input will change as the design parameters change (the "what-if" function). Not only can output data be generated, but graphs can be plotted. Inexpensive spreadsheets offer self-prompting as well as organized structure design formats that need be set up only once. What is more, most spreadsheet analysis programs directly implement Boolean logic operations so that a variety of digital systems can be simulated. According to Huelsman, some spreadsheets like SuperCalc Version 1.4 even allow feedback circuits. Those that do not can be modified. It is even possible to simulate integrated circuits and their wiring.—H.H.

### Fall Joint Computer Conference to rise again

Bearing a familiar name, a new annual technical conference and computer equipment exhibition, entitled the Fall Joint Computer Conference (FJCC), has just been announced. It is the result of a joint agreement between the IEEE Computer Society and the Association of Computing Machinery (ACM). The first conference is planned for November 1986, with the site as yet to be determined. The two societies have a combined worldwide membership of over 125,000 computer professionals. Two representatives from each society will be appointed to serve as the FJCC steering committee. A joint news conference to be held during the July NCC meeting in Las Vegas will provide more detailed information about the new FJCC.—J.H.

### Unix-compatible operating system supports 11 users on IBM XT

Taking part in the trend to design microcomputer operating environments rather than operating systems (see Computer Design, July 1984), Network Consulting, Inc (NCI) (Burnaby, British Columbia) has come up with a realtime version of the Mark Williams Co (Chicago, Ill) Coherent operating system for the IBM XT. Unix Version 7-compatible (165 commands rewritten in assembler for faster execution), with System V memory routines, NCI Coherent supports an 8-line serial port card that, with the addition of two regular IBM serial lines, services up to 11 users. In short, NCI Coherent offers multi-user capability with Unix compatibility. Unlike Unix or its look-alikes, the license for the rewritten kernel operating system includes multi-users. This application-oriented operating system allows the XT to serve as a data multiplexer, protocol converter, network interface to IEEE 802 or 488 networks, database machine, or control processor. The latter functions are made even easier since the realtime operating system can run on intelligent peripheral boards; can be burned into PROM; and supports 11 different hard disks. With an eye to the needs of software developers and system integrators, the operating system also supports an IEEE-format math library, extra programming commands, screen editor, source code control system, lexical analyzer, compiler-compiler, Pro-Log interpreter for artificial intelligence applications, and the running of MS-DOS programs.—H.H.

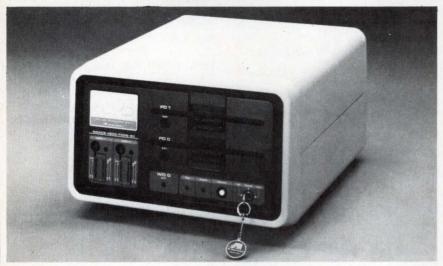

The new Telex 9250 tape subsystem

# Finally! Full-Performance GCR Made Affordable. Telex Shamrock

It took Telex to introduce a GCR subsystem with all the performance, all the reliability of larger subsystems — and make it affordable for minicomputer and mid-range mainframe manufacturers.

The Telex 9250 GCR tape drive is the first 50 ips unit to appreciably lower the cost of GCR without sacrificing performance. Advanced LSI gate array technology and vacuum column design offer advantages like low cost, low power and low noise

(before offered only on old tension arm systems) — plus all the performance that only vacuum column technology can deliver, including . .

- ANSI standard (0.3") interblock gap

- Faster access time (0.3 millisecond write, 3.4 millisecond read)

- Higher data reliability

- Greater media integrity

- No adjustments

- Low maintenance

Other features include autoload, autothread, 1x4 option, resident diagnostics and tri-density option to offer the most ingenious application of vacuum technology to date.

Performance and savings — it's what you've come to expect from Telex.

For more information, contact the nearest Telex OEM Sales Office listed or phone our OEM Marketing Department in Tulsa: (918) 627-1111.

### TELEX® SHAMROCK 🖸

### The innovation continues . . .

Telex Computer Products, Inc. Terminals/Peripherals/OEM Products 6422 East 41st/Tulsa, Oklahoma 74135 (918) 627-1111

### **Telex Regional Offices**

- Amherst, NH (603) 673-9272

- Garden Grove, CA (714) 898-9833Houston, TX (713) 497-6770

#### International

Telex Computer Products, Inc. -P.O. Box 128/Addison, TX 75001 (214) 931-8511/telex: 730612 TLXINTL ADDI

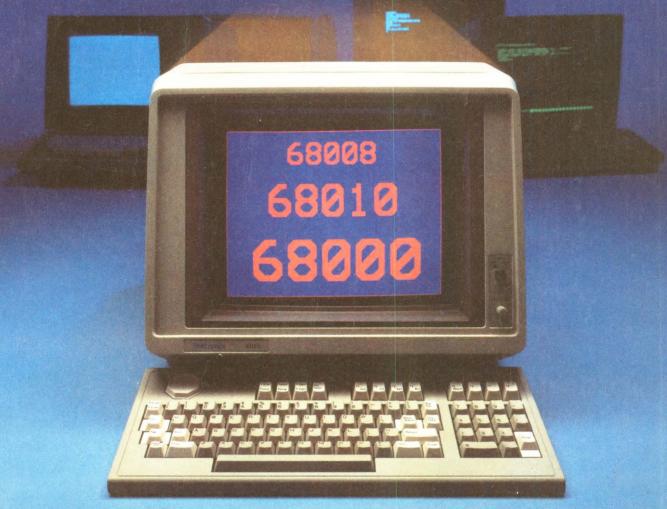

# Motorola's 68000 MPUs - the common systems from some of the industry's

Callan Data Systems uses the 68010 because "it's the fastest, most advanced microprocessor available."

"Motorola has established the 68000 product line as the **de facto** standard for the new generation of UNIX™ based super micro workstations and computer systems. Implementation of the chip on Callan's UNISTAR super micros is a perfect example.

"In the 16/32-bit UNIX-based microprocessor race, the 10 MHz virtual memory 68010 microprocessor, the heart of our UNISTAR 300 super micro, is the fastest, most advanced microprocessor available. It will remain one step ahead of the rest in the 16/32-bit UNIX microprocessor race."

Bill Pohlman, Vice President of Engineering, Callan Data Systems

Apollo Computer uses the MC68010 as the heart of its DOMAIN DN300 to deliver mainframe-like CAD/CAE functions in a desktop unit.

"Apollo's DOMAIN (Distributed Operating Multi-Access Interactive Network) is a high-performance local area network of dedicated computers operating in a distributed environment.

"The MC68010 microprocessor allows each Apollo DOMAIN to directly support virtual memory management in a network-wide demand paging environment. The performance and memory requirements of distributed CAD/CAE applications could only be satisfied with a design that incorporates microprocessors from the M68000 Family of devices.

Edward J. Zander, Vice President Marketing, Apollo Computer

Omnibyte uses the 68000 in the single-board computer market for its proven reliability and quality.

"The single-board computer market that Omnibyte serves requires not only high performance, but also quality and proven reliability. For these reasons, Omnibyte chose the Motorola M68000 Family.

"The OB68K/VME1 incorporates the fast 12.5 MHz 68000R12. Its small-size, pin-grid array package allows room for more features on this sophisticated board-level computer."

Peter A. Czuchra, Marketing Manager, Omnibyte Corporation

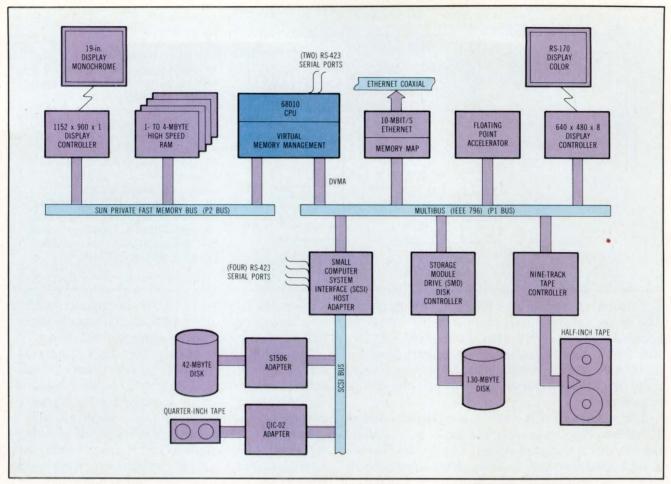

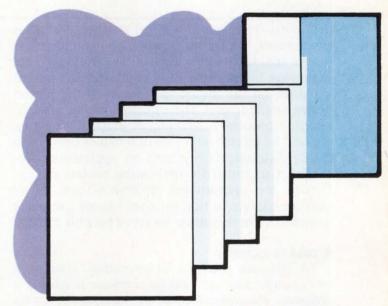

The Sun Workstation® uses the MC68010 to achieve superminicomputer performance.

"The MC68010 is key to the architecture of our multipurpose technical workstations. We designed a special no-wait-state memory to take full advantage of the speed of the 68010.

"The 68010's symetric instruction set and virtualmemory capability are the foundations of a cost-effective implementation of UNIX. And UNIX is key to Sun's commitment to industry standards in hardware and software."

Lloyd Fugate, Vice President of Marketing, Sun Microsystems, Inc.™

# denominator for high performance most innovative manufacturers.

### Convergent Technologies uses the 68010 as the heart of its MegaFrame system.

"The Motorola 68010, with its virtual memory, allowed us to build features typically found in mainframes and super-minis — features like demand page virtual memory — into our MegaFrame. So our MegaFrame is not a super-micro, it is a mini-computer, because of the 68010.

"Also, the 68010's linear address space is a real benefit for UNIX. We use up to 16 68010s in each system, all running on UNIX, all part of the 68000 architecture." Steven Blank, Marketing Manager, Convergent Technologies

### Intergraph uses the 68000 for improved screen response and more workstations per host.

"Creation of a screen image  $\dots$  is conducted up to three times faster than on a VAX-11/780.

"The MC68000 works with several Intergraphdesigned processors to generate and manipulate graphic images locally . . . at the workstation. Offloaded of these burdens, the host computer is able to support many more workstations, such as executing database updates, running third party software and performing other background support tasks."

Bruce E. Imsand, Executive Technical Manager, Intergraph Corp.

Motorola's M68000 — the upward-compatible 8/16/32-bit microprocessor family — is today's common denominator for high performance systems.

Consider the overall cost/performance leadership of the M68000 Family and make your commitment. Your present and future generation products will be better for it. Get the inside story. Ask your design engineering management.

M68000: The upward-compatible 8/16/32-bit microprocessor family.

MOTOROLA INC.

Semiconductor Products Sector, P.O. Box 20912, Phoenix, AZ 85036

P.O. Box 8, 1211 Geneve 20, Switzerland

• P.O. Box 80300, Cheung Sha Wan Post Office, Hong Kong

### UNIX IS A DINOSAUR CP/M & MS-DOS ARE TOYS

**MULTI SOLUTIONS PRESENTS**

# THE WORLD'S FIRST 4th GENERATION

**OPERATING SYSTEM**

A SERIOUS OPERATING SYSTEM SI

### FOR TODAY AND TOMORROW

- PORTABLE

- MODULAR

- MULTIUSER

- MULTITASKING

- MULTI PROCESSING

- PARALLEL PROCESSING

- 64 CHARACTER NAMES

- 3 COMMAND PROCESSORS

- REAL TIME

- NETWORKING

- DISTRIBUTED PROCESSING

- HIERARCHICAL DIRECTORIES

- KEYED FILES

- · ISAM

- · VSAM

- · B-tree

- RECORD LOCKING

- UNIX SOURCE COMPATIBLE

- WINDOWING

- BIT MAPPED DISPLAYS

- FULL SCREEN MANAGEMENT

- FULL SCREEN EDITING

- FULL MEMORY MANAGEMENT

- VIRTUAL MEMORY

- SEMAPHORES & LOCKS

- EXTENSIVE UTILITIES

- · AND MUCH, MUCH MORE

S1 IS THE ONLY OPERATING SYSTEM WORTHY OF THE TITLE:

"THE NEXT WORLD STANDARD."

### **ONLY S1 DOES IT ALL.**

NO OTHER OPERATING SYSTEM

COMES CLOSE. CUTS DEVELOPMENT

TIME FROM MAN YEARS TO MAN MONTHS.

MULTI SOLUTIONS INC. Multi Solutions, Inc.

Multi Solutions, Inc. 123 Franklin Corner Rd. Lawrenceville, N.J. 08648 609-896-4100 Telex: 821073

Please send for our FREE S1 Book or Call 609-896-4100

IN TIME, ONLY THE BEST WILL SURVIVE: S1

### THE MARKET FOR COMPUTER GRAPHICS

Recently, a magazine aimed at advertising and marketing people asked me to write an article on the "vertical market for computer graphics." My initial impulse was to tell the magazine's editor that I was the wrong person for the job. The assignment seemed much more appropriate for someone from our sister publication, Computer Graphics World. After all, I thought, that magazine concentrates exclusively on computer graphics, while Computer Design covers the design of all types of computer systems. In the jargon of the publishing business, we have a "horizontal" audience, while they have a "vertical" one.

However, after doing some research and thinking things over, I realized that you, our readers, are really the key people in the computer graphics market. Several factors led me to that conclu-

sion. Firstly, of course, graphics has become so pervasive that all types of computer systems (even inexpensive personal computers) offer graphics capability wherever it can be effective. Secondly, the largest application area for high resolution graphics is computer aided design and engineering—an area in which you are involved both as system designers and users. Thirdly, computer graphics is still in its infancy, and software standards are still being hammered out. Therefore, software has to be designed or specified by knowledgeable system engineers—the sort of people who read *Computer Design*. Last, but not least, high resolution graphics systems are expensive. So, their purchase must be authorized by management level people whose technical judgment can be trusted—in other words, by people like you.

Because you need to know how other engineers are coping and what's on the horizon, we devoted our May Special Report to a discussion of existing and proposed graphics standards. And, because you most likely have a dual involvement with workstations (both as designers and users), we used them as application examples in this issue's special report on designing with advanced microcomputers. Why then was I surprised to learn the importance of your role in the computer graphics market?

The answer to this question is simple. Because I am an editor and an engineer—not an advertiser or a salesman—I tend to think of technologies rather than markets. Of course, a technology (such as computer graphics) may also be an important market. But my viewpoint is different from that of our advertisers. I think of our readers as creative designers and problem solvers with specific information needs, not as potential customers in a market.

Yet, when one starts to look at computer graphics from a marketing viewpoint, it is easy to get caught up in the excitement. It is easy to see why so many startup companies concentrate on computer graphics—because the potential prize for the winners looms large in the distance. For all types of computer graphics workstations (which is by no means the entire graphics market), Frost and Sullivan forecasts that the total annual dollar market will climb from \$335 million in 1983 to a very respectable \$2.82 billion in 1990. And for intelligent workstations, those with the most built-in computing power and, hence, the most engineering value added, the market research organization sees rapid growth from just \$65 million in 1983 to \$1.03 billion in 1990. This would seem to ensure a bright future for the increasingly large number of system designers involved in graphics.

Although my brief excursion into the marketing realm gave me new insights into the computer business, I think my initial impulse was probably a sound warning. Perhaps I was the wrong person to write a marketing article—not because I work for the wrong magazine, but because it could give me the wrong perspective on the industry. After all, if too many engineers start to get excited about the markets for computer graphics, they might decide to become entrepreneurs and sales people. Then who would be left to design the systems?

mild Certil

Michael Elphick Editor in Chief

# MICROSOFT STRIKES GOLD.

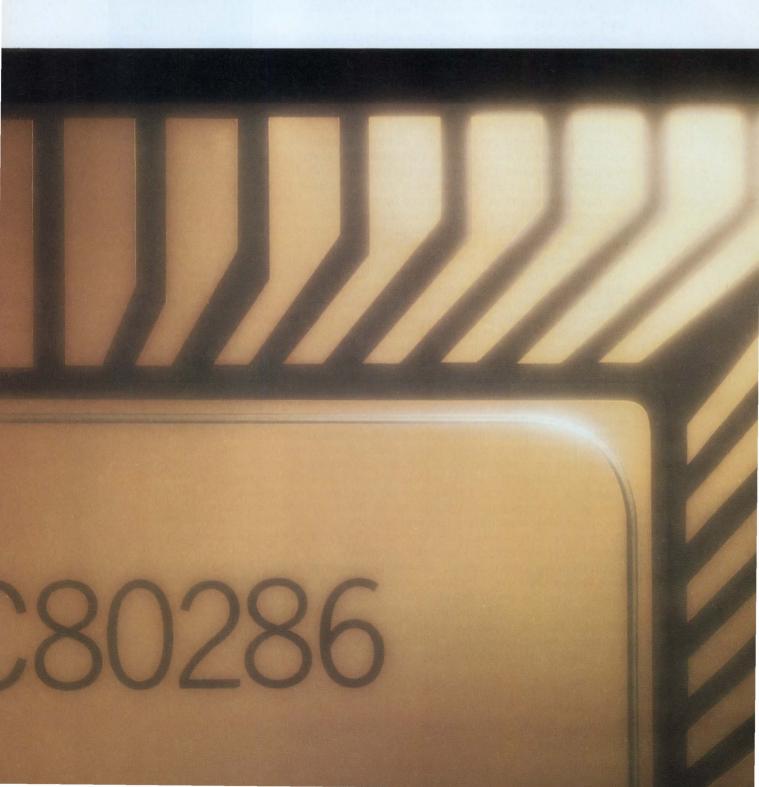

This is what paydirt looks like when it's turned into silicon.

Intel's iAPX 80286 microprocessor.

Together, Microsoft and Intel used this gem to create another: the XENIX\* 286 Operating System. The most powerful implementation of UNIX\* on the market today for any micro-

processor. And the most reliable, functional, commercial enhancement of the UNIX operating system ever created.

The XENIX 286 Operating System includes UNIX enhancements available from both AT&T™ and U.C. Berkeley. But Microsoft has also added loads of other commercial enhancements to make your life richer, in more ways than one. For instance, there are record and file locks, semaphores to help manage multiuser/multitasking

data, and automatic disk recovery for better reliability.

Which makes XENIX 286 an ideal Operating System for applications software development. Over

opment. Over Chairman of Microsoft Corp.

one hundred and fifty in the volume of the ware packages have been developed for XENIX, making it one of the most useable multiuser Operating Systems available today.

Chairman of Microsoft Corp.

Why

deeper, free at 0

672-183

Lit. Dep

For Microsoft, the unique advantages of Intel's 80286 microprocessor were most appealing. As Bill Gates, chairman of Microsoft, said, "On-chip memory management and protection offered by the 286 ensures code compat-

ability and makes it easy to port XENIX between different OEM systems."

In addition, its ability to run in fast 8086 mode makes the 286 the only processor that can support both XENIX 286 and MS-DOS without additional hardware. "With this ability, users get the best of both worlds in one piece of hardware," said Gates.

What's more, it's the only microprocessor architecture with the flexibility to offer you entry at whatever level of inte-

gration you choose: chips, boards, or complete systems (including, of course, our new 286/310 supermicro system.) So you get to market when you want,

in the way you want.

Why not dig a little deeper, and call us toll-free at (800) 538-1876. In California, (800) 672-1833. Or write Intel, Lit.Dept.#\$9,3065Bowers Avenue, Santa Clara, CA 95051.

And don't be surprised if you hear shouts of "Eureka!" coming from your product development team.

<sup>\*</sup>XENIX and MS-DOS are trademarks of Microsoft Corporation. UNIX is a trademark of Bell Labs, Inc. AT&T is a trademark of American Telephone & Telegraph. © 1984 Intel Corporation.

Bill Gates,

Teamwork is making a comeback in America. Cooperation on the production line helped America win World War II. We're in another kind of battle today — a fight for economic survival in an increasingly competitive world market. Cooperation in the workplace is helping us meet this challenge too.

In plants and offices throughout the country, management is asking employees for their ideas on how to increase productivity and improve the work environment. And workers and their unions are responding with a wealth of practical suggestions and a renewed spirit of cooperation.

For information about how others are working better by working together, contact:

Cooperative Labor-Management Programs U.S. Department of Labor Washington, D.C. 20216 202-523-6098

### U.S. Department of Labor

Printed by this publication as a public service Photograph: Lange Collection, Oakland Museum

### **COMPUTER DESIGN**

The PennWell Building, Littleton, MA 01460. Tel (617) 486-9501 Editorial/Executive Offices

Editor in Chief, Michael Elphick Managing Editor, Sydney F. Shapiro Senior Editor, John Bond Senior Editor, Peg Killmon Special Features Editor, James W. Hughes Senior Associate Editors. Malinda E. Banash, Deb Highberger Associate Editor, Jack Vaughan Assistant Managing Editor. Leslie Ann Wheeler Copy Editors,

Helen McElwee, Jane E. Shattuck, Lauren A. Stickler

Editorial Assistants, Julia E. Cote, Cynthia L. Podesta

Editorial Field Offices: New York, NY (212) 986-4310 Senior Editor, Nicolas Mokhoff Special Features Editor, Harvey J. Hindin

Sunnyvale, CA (408) 745-0715 West Coast Managing Editor, Tom Williams Editorial Assistant, Robin Mock

San Francisco, CA (415) 398-7151 Field Editor, Sam Bassett

Long Beach, CA (213) 426-1172 Field Editor, Joseph A. Aseo

Publisher, Frederic H. Landmann

Marketing Director, Robert A. Billhimer Circulation Director, Robert P. Dromgoole Promotion Director, Steve Fedor Marketing Services/PR Manager, Linda G. Clark

Publishing Director, Gene Pritchard

Production Director, Linda M. Wright Production Manager, Philip Korn Art Director, Lou Ann Morin Ad Traffic Coordinator, Debra Friberg Printing Services, Padraic Wagoner

### **PennWell**

Advanced Technology Group 119 Russell St, Littleton, MA 01460 Tel (617) 486-9501

H. Mason Fackert, Group Vice President Saul B. Dinman, Editorial Director David C. Ciommo, Controller John M. Abernathy, MIS/DP Director Patricia M. Armstrong, Administrative Services Manager

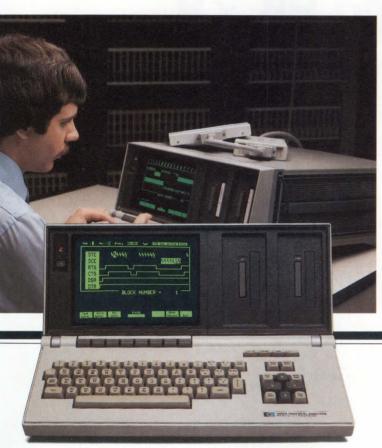

### Tek's out in front with 68000 support.

### Designing with the 68000, 68008 or 68010? Call us.

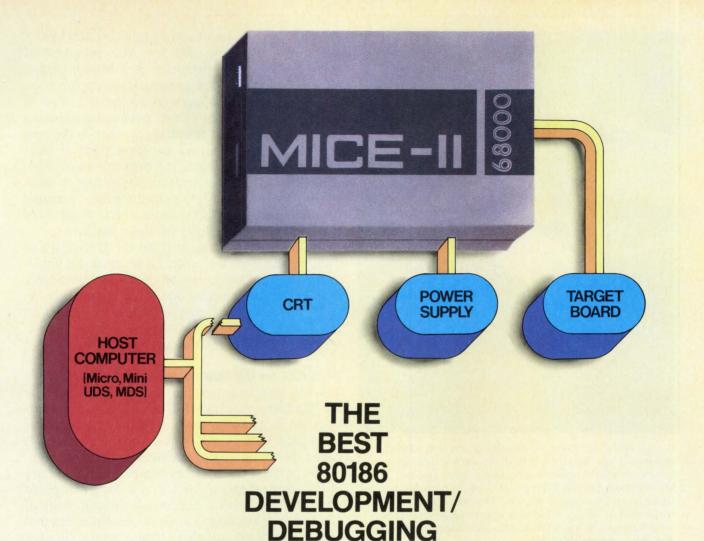

**Tektronix Microprocessor** Development Systems support you from your first line of code clear to your last line of debug, in Assembly, C or Pascal. Our systems match your environment, too-from one to eight users. And we can even harness the power of your VAX™computer and turn it into a powerful microprocessor development system.

If you're working with the 68000, 68008 or 68010, call your Tektronix Sales Engineer. And find out why Tek is leading the pack in microprocessor development.

**Tektronix Microprocessor Development Systems.**

Call 1-800-547-1512

™ VAX is a registered trademark of Digital Equipment

U.S.A., Asia, Australia, Central & South America, Japan: Tektronix, Inc., P.O. Box 1700, Beaverton, OR 97075. For additional literature, or the address and phone number of the Tektronix Sales Office nearest you, contact: Phone: (800) 547-1512. Oregon only: (800) 452-1877, TWX: (910) 467-8708, TLX: 151754. Cable: TEKWSGT

Europe, Africa, Middle East; Tektronix Europe B.V. European Headquarters, Postbox 827, 1180 AV Amstelveen. The Netherlands, Phone: (20) 471146, Telex: 18312-18328

Canada: Tektronix Canada Inc., P.O. Box 6500, Barrie, Ontario L4M 4V3, Phone: (705) 737-2700

Copyright ©1984, Tektronix, Inc. All rights reserved, MIA-129.

Circle 11 for Literature Circle 12 for Sales Contact

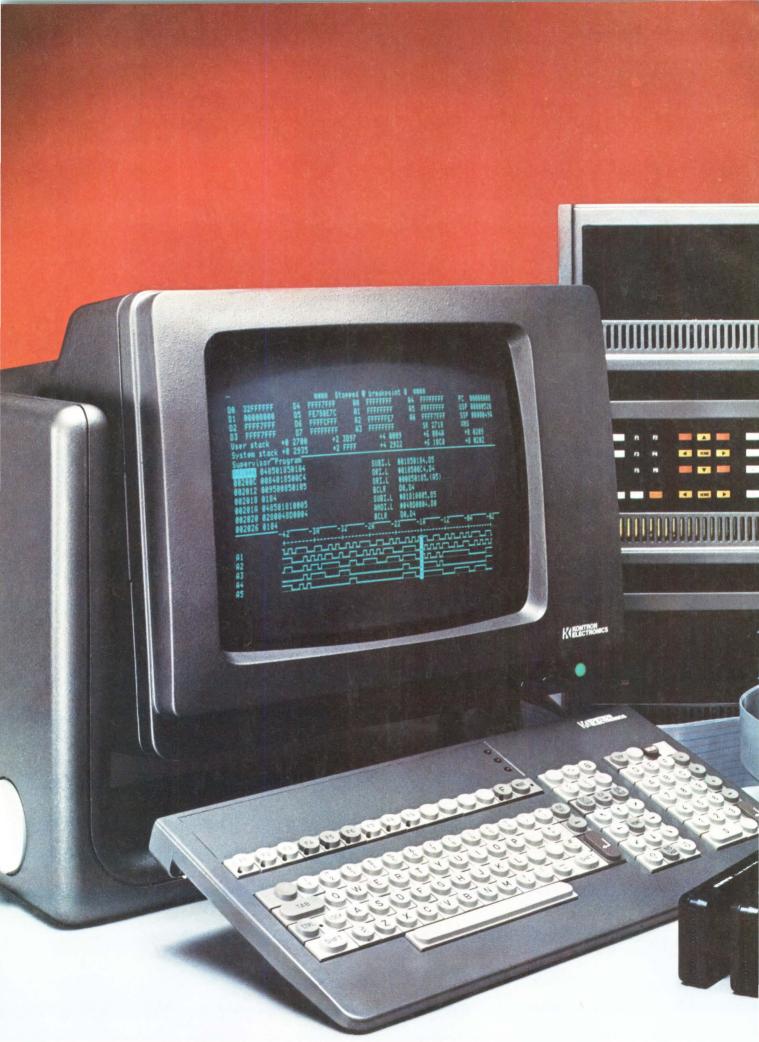

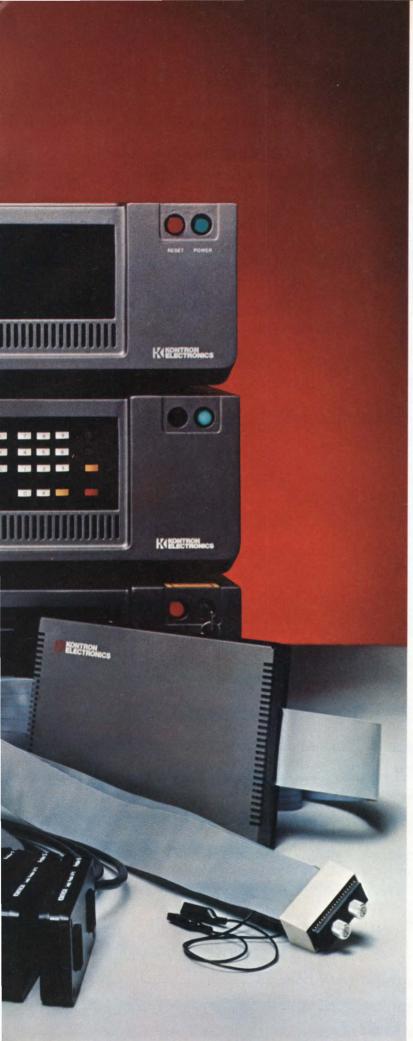

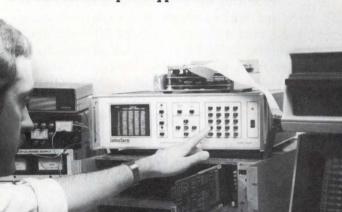

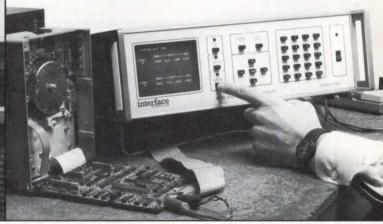

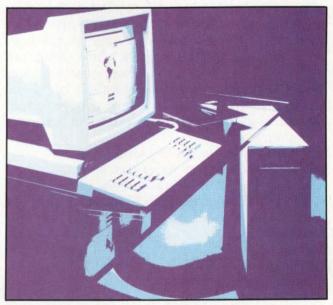

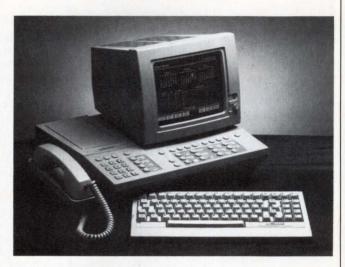

### **Kontron KDS** The Ultra-productive **Multifunction Development System**

Producing the next wave of smart products isn't enough. You've got to be first! To be first and stay there you need a development system that makes your designers more efficient, a system that speeds up the time-consuming task of developing and integrating hardware and software.

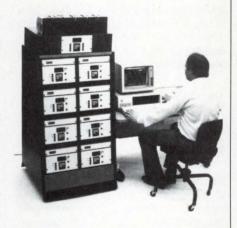

The ultra-productive environment you need is available now in the KDS. Kontron's field-proven CPU, mass storage, slave in-circuit emulation and logic analysis capabilities are perfectly blended in this user-configurable, ergonomically designed workstation. The KDS solution starts with stackable, card-configurable modules that may be located wherever convenient. Add the detached keyboard and adjustable CRT, and a truly productive working environment emerges. You can tilt, swivel, raise or lower the CRT to suit your viewing angle. The detached keyboard gives you control over all systems and the ability to display all functions on the extra-large (15-inch), easy-toread screen. Two 51/4" floppy disk drives are incorporated in the CPU; an optional 10 Mbyte hard disk plugs in if you need it. Software, emulation and logic analysis are fully integrated.

You have complete control over up to four KSE slave emulators and one KSA logic analyzer. Emulation support is available for most popular 8- and 16-bit chips. You can select the 32-, 48and 64-channel logic analyzer (to 100 MHz) that suits your needs for timing and state analysis.

KDS comes complete with all the applications software you need. Editors, linkers and assemblers are provided for assembly language programming and for use with Pascal compilers. Software developed on other Kontron systems can be ported to the KDS via an RS-232 link. Industry-standard operating systems\* make KDS even more versatile, opening the door to third party software and many new applications. Find out how much more the KDS Multifunction Development System can do for you. Write for a demonstration.

### ADVANCED VA KONTRON **ELECTRONIC** INSTRUMENTATION !

In the United States: KONTRON ELECTRONICS 630 Price Avenue Redwood City, CA 94063 TWX: (910) 378-5207

(800) EMULATE; (800) 227-8834 In California:

(415) 361-1012

In Europe: Kontron Messtechnik GmbH Breslauer Strause 2

8057 Eching West Germany (0 89) 31901-1 Telex: 05 22 122

\*CP/M is a registered trademark of Digital Research, Inc. \*UNIX is a trademarked product of Bell Laboratories.

Circle 63 for Literature

Circle 98 for Demonstration

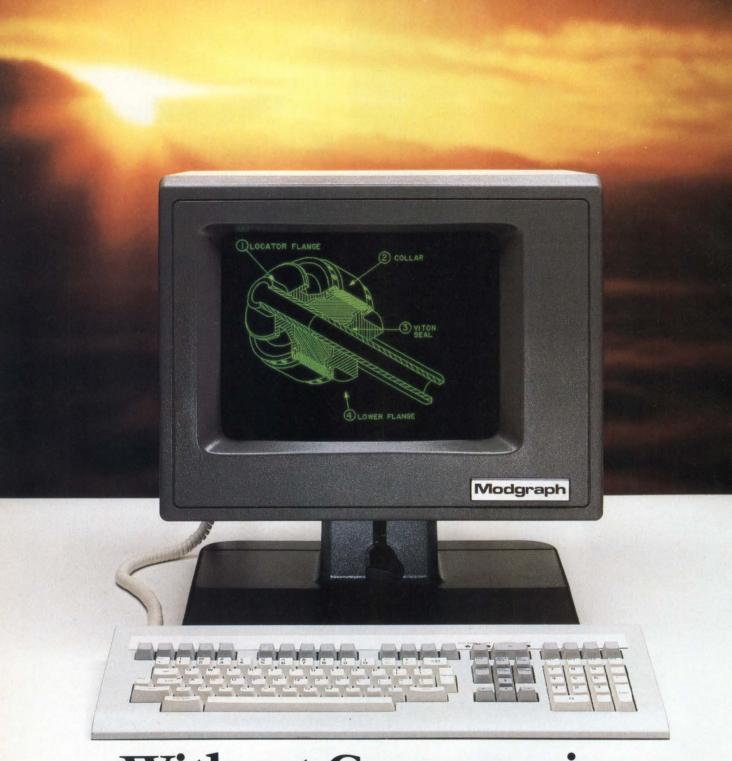

### Without Compromise.

The Modgraph GX-1000.

- ☐ 1024 X 780 Resolution

- ☐ 4010/4014 Emulation

- ☐ 15 inch CRT

- ☐ 132 Column Text Display

- □ VT100/VT52 Emulation

- □ \$2795

See us at the Siggraph Show July 23-27

Modgraph, Inc., 1393 Main Street, Waltham, MA 02154 (617) 890-5764

• 4010/4014 are trademarks of Tektronix, Inc. • VT100/VT52 are trademarks of Digital Equipment Corporation • The Screen image is courtesy of Computervision Corporation

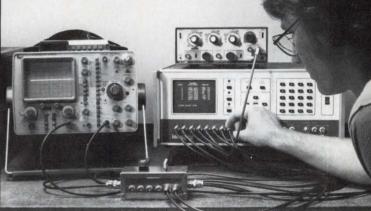

### Protocol analyzers take on functions to deal with network complexities

Communication networks, essential to virtually every computer installation, have recently assumed critical proportions. When AT&T relinquished its stranglehold on the communication business, it also gave up supporting individual installations. This has forced network operators to take on the task of network maintenance—an uncomfortable role for many. Accustomed to "one-stop shopping," operators must now, instead of simply calling the phone company, diagnose network disorders, as well as define the equipment at fault.

Add to these problems those created by the ever more complex networks, the proliferation of protocols and interfaces, and the shrinking store of skilled diagnostic personnel. The network environment is populated with a variety of vendors whose gear must communicate. While valiant attempts at standardization are underway, the available equipment still uses a confusing array of protocols that must be supported until those efforts yield fruit.

On top of all this, economic pressures are being brought to bear by the increasing costs of having a network go down. In crisis situations, losses due to outages can run to \$1000 per minute. This demands that operator setup time and diagnostic time be kept to an absolute minimum. The result, when all of these factors are considered, is a tremendous need for sophisticated network diagnostic tools that can be quickly and effectively used, even in the hands of relatively unskilled personnel.

### Tools for troubleshooting

Equipment designed with these criteria in mind is emerging. Characteristically, it supplies sufficient intelligence and degree of programmability to reduce the skill level necessary to troubleshoot complicated networks.

Combining power with simple operation, the Simon 5 protocol simulator/monitor serves as a central console instrument or portable field unit. Diagnostics range from standard bit and block times to response time measurements on SNA cluster controllers.

Operating at high speeds to match the trend toward higher speed networks, intelligent instruments also provide large amounts of data storage. This facilitates the isolation of problems by allowing repeated analysis of exactly the same data stream.

Specialized units such as response time analyzers, spectrum analyzers, and data line monitors, as well as network analyzers all serve in this complex arena. Each handles a single important element of the overall network function. Combining functions into a single intelligent piece of test equipment, protocol analyzers simplify the task of dealing with network complexity, whether charged with network maintenance or with aiding in the development of network software.

Designed for today's fast transmission speeds, the model 800 from Digilog Inc's Network Control Division (1370 Welsh Rd, Montgomeryville, PA 18936) looks to sophisticated software to handle bit-oriented multilevel protocols. In combination with smart hardware, this approach allows the relatively unskilled person to handle monitor and test functions, and provides seasoned operators with the tools to work more effectively.

Need for the sophisticated features displayed by this unit, and others of its type, stems from changes that have taken place within the communication field over the last several years. While data line monitors dating from the sixties established a window into the network, they were limited

(continued on page 22)

### Protocol analyzers

(continued from page 21)

to simple protocols and relatively slow transmission speeds. As line speeds increased, however, protocols also changed from easy-to-memorize character patterns to difficult to understand, bit-oriented multilevel protocols.

These challenges are met by designing intelligence into the diagnostic units. Thus, they can give the operator specific information detailing what went wrong with the protocol (whether character or bit oriented), as well as designate which device within the network created the problem.

Operating capabilities of Digilog's family of protocol analyzers encompass automatic setup, interchangeable electrically erasable PROM packs, and menu-guided operation, provided by the low end model 200 at transmission speeds to 19.2 kbits/s. Midrange units graphically display network interface timing at up to 72 kbits/s. On the high end, the model 800 can simulate high level protocols, memorize line performance, and display online statistics for lines operating at up to 256 kbits/s. The 10-Mbyte

hard disk drive in this unit stores both programs and data off the line. Online statistics are displayed in color on its 10½-in. CRT.

### Simplifying protocol definition

The programming process plays an important part in getting a tester to function in a specific communication environment. Recognizing the difficulty that programmers face in protocol definition, Atlantic Research Corp's Teleproducts Division (7401 Boston Blvd, Springfield, VA 22153) has provided tools to simplify that task. Based on a programming technique that facilitates protocol definition, the company's protocol analyzers enable programming to be done by less than high level programmers.

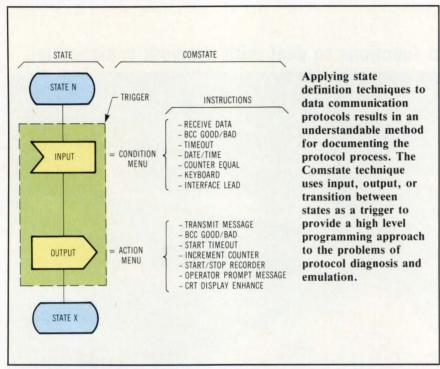

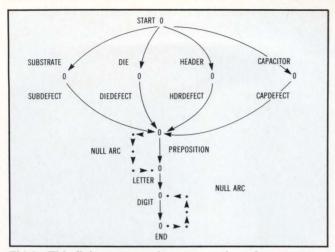

The technique applies state diagrams to protocol definition to provide an easily understandable means of documenting the protocol process and uses the concept of triggers as a high level programming approach. Defined as a protocol sequence look for condition (input), take action (output), and/or transition to another state—triggers allow an operator to easily develop a test from a state diagram. Instead of trying to remember lengthy lists of instructions and their abbreviations, a user merely selects a desired input from a trigger condition menu and a desired output from a trigger action menu.

Embedded in the technique, as implemented in Atlantic Research's Interview Comstate protocol analyzers, are test development features that address and substantially eliminate unknowns. One is a display that summarizes details of up to eight triggers in a single state. Another display lists all states by name with a count of the number of triggers in each state. Using these displays it is easy to verify that the test parallels the state diagram definition of the protocol.

The technique provides, in every trigger, a descriptive prompt message that can print a record of the event. This allows the documentation required for network certification testing to be generated. The printout supplies a sequential record of each trigger occurrence and each state transition during test execution. The same state/prompt trace can also be displayed on the unit's CRT.

In addition, the Comstate II allows the use of up to 128 triggers in any state test, and up to 16 triggers in a single state. Testing requirements of X.25 networks are handled using mnemonic descriptions of receive and transmit frames and packets. This facility allows breakout of types, causes, and other extensions, while providing access to every bit. In SNA and BSC applications, the instrument can be used for host or network emulation, thus supplying diagnostic monitor tracing.

A portable unit that subscribes to the same general thesis, the Chameleon, from Tekelec Inc (2932 Wilshire Blvd, Santa Monica, CA 90403), uses a menu structure in conjunction with a simple programming language to

guide users through test setup. This is complemented with a help level that displays a detailed explanation of any term or feature.

Provision of multiple triggers allows data to be captured to the 16-Kbyte buffer or direct to the disk, which provides storage for 700 Kbytes of data. Analysis allows selective display of user-defined data from a prerecorded file. Selected data is displayed in full intensity, while all other data is visible in half intensity. Split-screen display enables both sides of a link to be studied simultaneously.

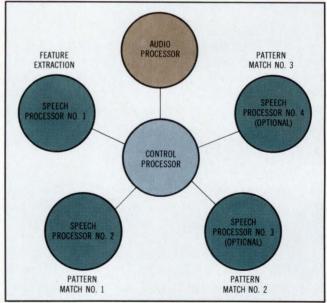

The multiprocessor architecture handles physical and link level on one processor programmed to handle HDLC, SDLC, Bisync, or transparent Bisync link access protocols. The second processor supports simulation packages that take care of higher level protocol procedures and data generation. A simulation trace in each package supplies simultaneous display of transmitted and received data. Trace packages provide display of a full interpretation of SNA and X.25 protocols. Traffic may be viewed live from the line or stored to disk for later analysis.

#### Programming with soft keys

Focusing on the shortage of skilled diagnosticians, the Simon 5 from Dynatech Data Systems (7644 Dynatech Ct, Springfield, VA 22153) builds on the menu approach used in the earlier DynaTest 1600. It adds soft keys, a help key, and removable hard disk to form a powerful, yet easy to use, protocol simulator/monitor. Each of four operating modes is accessed by pressing a single mode key. Standard menu selections include trapping, event counting, transmission testing, and bit-error rate testing. Once the format is chosen, the remaining parameters are automatically selected.

Menu mode pinpoints problems such as parity and block check errors, faulty addressing, and link initialization failures. Prestored menu tests accessed under protocol mode—monitor, event count, and BERT—are complete with operating parameters.

Programs to simulate and test virtually any protocol are built by simply selecting instructions on the soft key line of the display. Scroll mode searches captured data for specified pattern, event, or error. Data can be displayed in English or hexadecimal, compared to the interface status, checked for errors, or printed via the hardcopy port.

Programs are stored in up to 4 Kbytes of nonvolatile memory. These stored programs can interact either with data coming off the line or with data stored on the removable cartridge hard disk drive. Data rates range from 50 to 19.2 kbits/s internal. External clock rates can be 64 kbits/s full duplex. At this rate, 2 Mbytes of data and interface status can be stored on the disk. The internal buffer handles up to 8 Kbytes.

Packed in a portable 14-lb unit, the 4951A, developed by Hewlett Packard's Colorado Telecommunications Division (5070 Centennial Blvd, Colorado Springs, CO 80933), provides X.25 capability for testing sophisticated networks. Simulation capability allows detailed measurements to be made at physical interface, link level, and network levels. Success by relatively unskilled operators is assured by software driven keys.

These six software driven keys access the unit's troubleshooting capability, controlling the performance of network component simulation, data transmission monitoring, and bit-error rate tests. A single key—auto-configure—automatically determines line protocol, data code, speed, parity, and error checking. When combined with the other soft keys, the result is quick performance of complex tasks. Full benefit of the soft keys is realized in monitor and simulate menus. Here, the keys lead the operator through the measurements by presenting relevant choices at each decision point.

All data, timing, and lead status information is stored in the unit's 32 Kbytes of nonvolatile memory. An additional segment of memory provides storage for test setups and monitor and simulate programs. Data analysis, thus, can occur either in realtime or in post processing mode.

Whether designed for central site or remote use, instruments of this genre provide the tools necessary for network maintenance. Taking full advantage of the intelligent hardware and high level programmability, the units handle the complex protocols and diverse interfaces prevalent within today's networks. The high level of functionality available within a single instrument allows operators to not only detect problems within a network but to isolate faults to the piece of equipment responsible for them. Thus, the maintenance task is simplified not only by the level of function provided, but by the operator aids supplied through software.

-Peg Killmon, Senior Editor

SYSTEM TECHNOLOGY

(continued on page 25)

### Like to write?

The editors invite you to write technical articles for Computer Design. For a free copy of our Author's Guide, circle 503 on the Reader Inquiry Card.

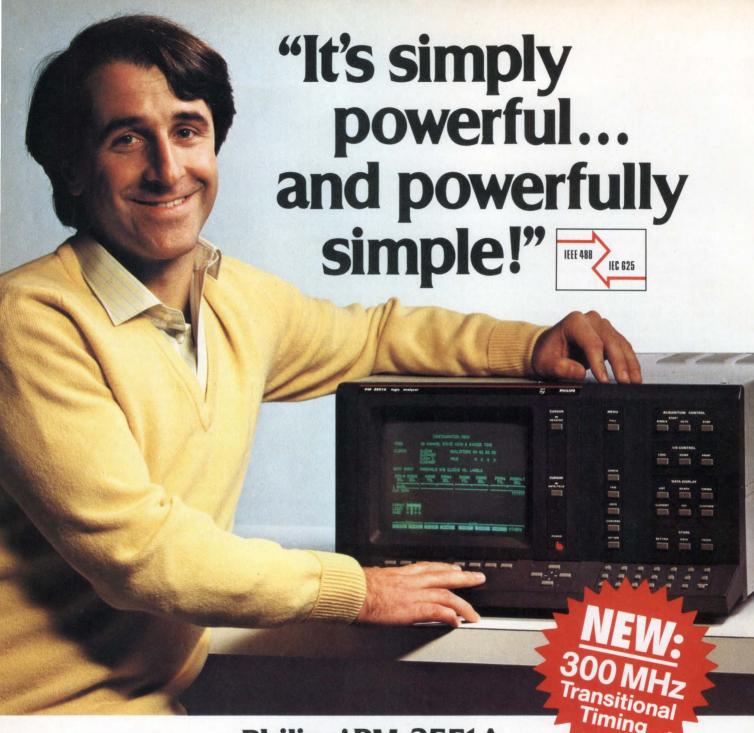

Philips' PM 3551 A...

in Logic Analyzers it's the logical choice

"Sophisticated yet simple. That's the PM 3551A. A dedicated state analyzer plus a dedicated timing analyzer working simultaneously in one instrument.

Its powerful SYNC mode gives you state and timing analysis at the same time – a real advantage if you're integrating hardware and software design.

Transitional timing saves memory without losing resolution.

And simplicity! Clear menus and soft-key entry let you use all its power from day one. You've disassembly of any 8 or 16 bit micro-processor at the press of a button – without adding extra boxes.

And that's just the beginning. To learn all the reasons why it's the logical choice.

For full details call: 800-631-7172 except Hawaii, Alaska and New Jersey. In New Jersey call collect (201) 529-3800 or write to 85 McKee Drive, Mahwah, NJ 07430."

Test & Measuring Instruments

**PHILIPS**

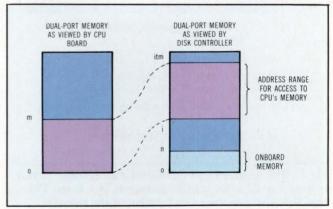

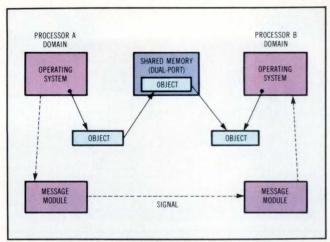

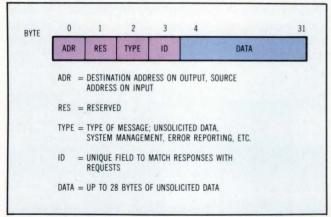

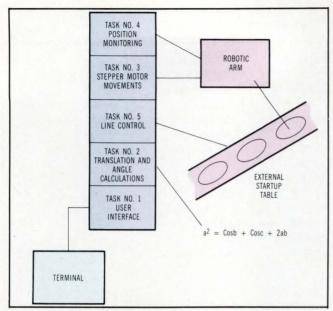

### Dual-port operating system attacks Unix compatibility problems

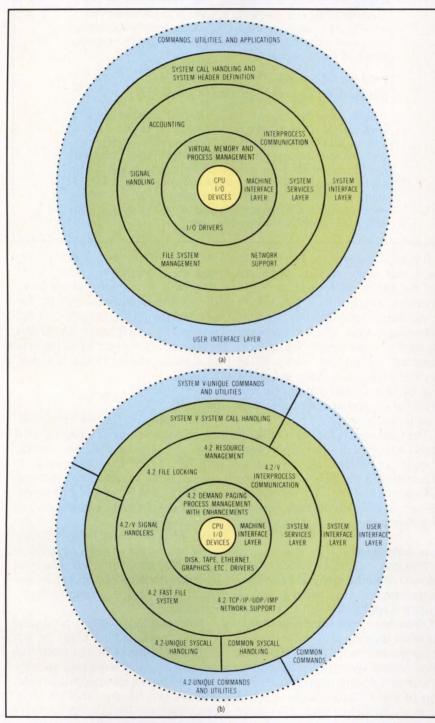

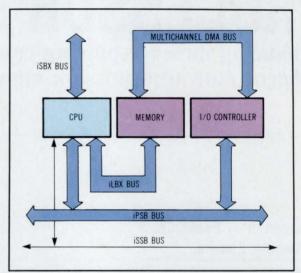

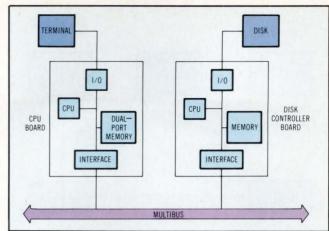

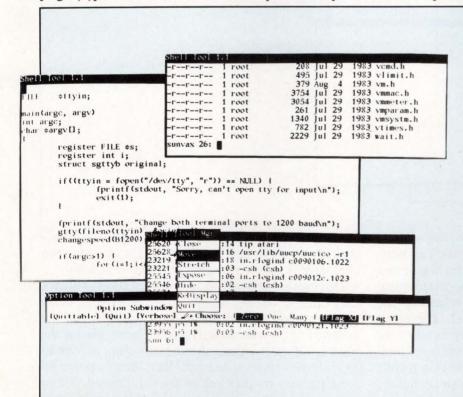

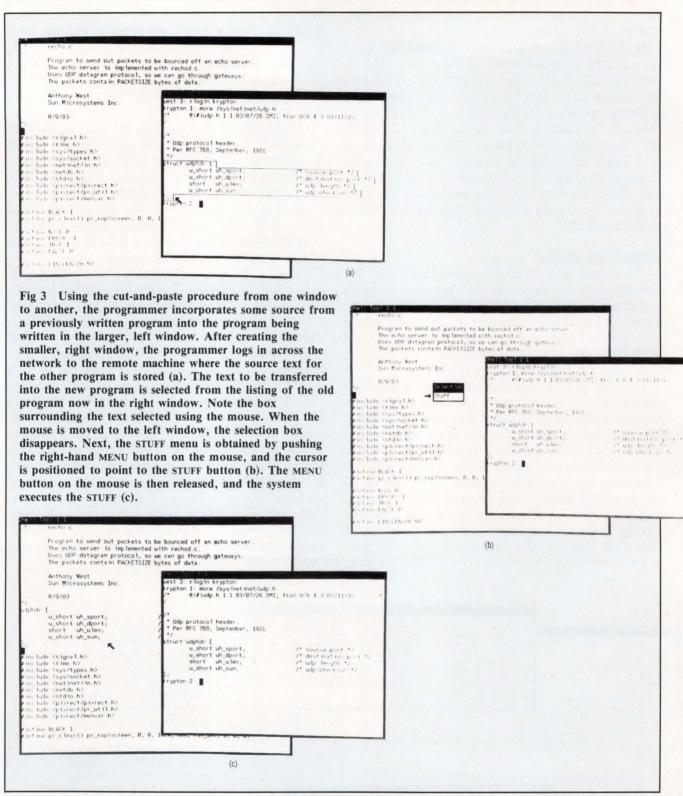

The classic Unix operating system is divided into layers that handle various machine, system, and user functions. Layers are isolated and communicate with calling conventions so software changes may be implemented modularly, and another system interface layer can be added on top of an existing one (a). With osx, the system interface layer is split or segmented (b). Another system interface layer is not added.

Both the University of California at Berkeley's 4.2 BSD Unix version and the AT&T Bell Labs' System v Unix have attributes that make them ideal for superminicomputer applications. But, they also have basic incompatibilities that limit how easily and efficiently application programs may be transported from one of these Unix environments to another.

Pyramid Technology Corp (1295 Charleston Rd, Mountain View, CA 94043) attempts to solve this incompatibility problem with its OSx operating system. This system was designed to be a compatible dual-port version of 4.2 BSD and System v Unix versions, without being just another Unix, according to Ross A. Bott, operating systems project manager for the company.

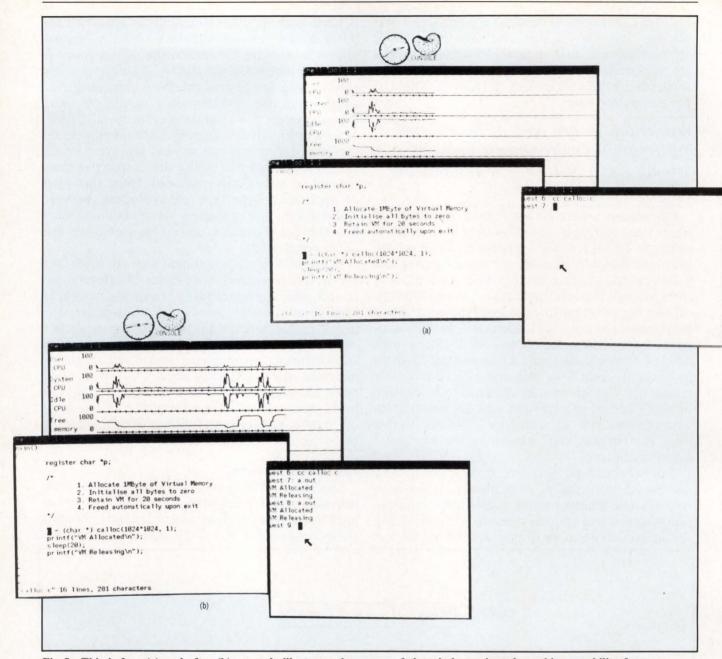

Bott claims that with OSX, one Unix environment, furnished by one of the ports and complete unto itself, can take advantage of the other environment. What is more, he adds, the OSX environment is ported on a 128-user, reduced instruction set, a 32-bit CPU, and 4 Gbytes of virtual memory address space. All this enables series 90x superminis to provide a gateway between networks using the two Unix environments.

OSx is also useful to the Unix community for other reasons. For one, as Bott said at January's Uniforum meeting in Washington, DC, OSx allows superminicomputer programmers to successfully develop programs in the 4.2 BSD environment, even if these programs will be run in the System v environment. The reverse is also true. According to Bott, superminicomputer programmers prefer the 4.2 BSD environment because its virtual memory support and file access mechanisms are superior to what is currently available in System v. It also has superior I/O performance and networking support. However, Bott admits that the upcoming enhancements in System v may possibly eliminate these differences.

(continued on page 26)

# SYSTEM TECHNOLOGY/ SOFTWARE

When workers aren't there, business doesn't work.

> Each year cancer strikes 120,000 people in our work force, and causes our economy to lose more than \$10 billion in earnings. Earnings that American workers might still be generating if they had known the simple facts on how to protect themselves from cancer

> Protect your employees, your company, and yourself. . . call your local unit of the American Cancer Society and ask for their free pamphlet, "Helping Your Employees to Protect Themselves Against Cancer." Start your company on a policy of good health today!

This space contributed as a public service

**Dual-port operating system** (continued from page 25)

### Getting in and out

A program developer or another user determines the initial universe in the osx operating system at log-in time. This is done by an entry in an /etc/u\_ universe file maintained for each user. An alternate universe is obtained by entering either of two commands:

warp att (or just att) - to enter System v warp ucb (or just ucb) - to enter 4.2 BSD

Both warp commands fork a shell within the alternate universe. A ^ D command returns to the original universe, and the universe command lists the universe in operation.

In addition, the user has the advantages of both Unix environments. For example, a command in one universe can be accessed while operating in another by prefixing that command with the prefix att or ucb. Inputs or outputs of different universe commands can be piped to each other with both wild card expansion and redirection.

It is important for the Unix user to know that some industry observers feel the battle between 4.2 BSD and System v may well be decided more by marketing clout than by superior technology. AT&T Bell Labs is pushing hard to make System v a de facto standard. In contrast, many of the key Berkeley people have left and it may be that 4.2 BSD will not be promoted or supported as well as System V or its successors.

The final reason for OSx's utility is that it is designed with the necessary "hooks" or pointers in place to allow future Berkeley or Bell versions to be incorporated. Thus, osx can always be compatible with the latest version of either popular operating system.

### New design needed

Previous operating systems have allowed computer designers and users to transparently run either 4.2 BSD or System v application software. Many of these have used what is known as software layering to allow both operating systems to function. However, conventional layering, such as putting a System v system interface layer on top of the 4.2 BSD system interface layer, is inefficient and slows down application program execution because of the additional software translation involved.

A 4.2 BSD operating system that wants to handle both 4.2 BSD and System v must make most of its soft-

ware changes in the 4.2 BSD system interface level, with some lesser changes at the system service level. The former are drastic, while the latter concern new feature addition (eg. System v's semaphores). A similar procedure is followed when the fundamental operating system is System v based.

#### **Dual-port**

The OSx solves the overhead problem of conventional layering by splitting or segmenting the system interface layer into three partscommon call handling, 4.2 BSD call handling, and System v call handling. Thus, software connection can be made directly to the innards of the OSx. This approach helps alleviate performance penalty (which could be up to 50 percent in a conventional layered system) when operating system input data or commands are reformatted.

The company avoided producing another nonstandard Unix by not including features in the operating system kernel that would have accommodated both Unix versions. Instead, with the OSx design, program developers need only log in which operating system they prefer. Then, commands, libraries, header files, and system calls appear as expected. To do this, the OSx always pulls in the appropriate directory or command from the

(continued on page 29)

# DIFFISION SERIES

### DEC COMPATIBLE CONTROLLERS

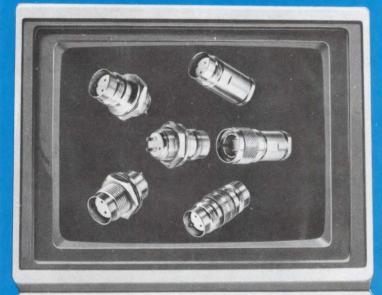

The Wespergroup Dimension series expands twofold in three dimensions. Wespergroup introduces six exciting new additions to the tape and disk dimension series:

THE TAPE DIMENSION Q-BUS COUPLERS TDQ-I AND TDQ-II. These couplers easily support the new tri-density "formatted tape drives" both in Start/Stop or Streaming modes. The TDQ-I supports Pertec interface tape drives, while the TDQ-II supports high speed Pertec, STC and Telex interface tape drives using a 64k byte data buffer. Both couplers emulate the DEC TSVO5.

THE DISK DIMENSION DEC UNIBUS CONTROLLERS DD-I AND DD-II. These controllers sustain up to four industry standard SMD interface disk drives. The DD-II handles up to two megabyte/second data transfer rate of the new SMD interface disk drives. The DD-I and DD-II

emulate DEC RM02/03, RM05, and RP06 disk drives.

THE TAPE DIMENSION DEC UNIBUS COUPLERS TD-III AND TD-IV. These couplers support the new "formatted tape drives" with either STC, Telex or Pertec interfaces in Start/Stop or Streaming modes. The TD-IV includes a 64k byte multi-stage data buffer to upgrade the efficiency of the Streaming Drive in the write mode. Both couplers emulate the DEC TS II drives.

Call or write today for the complete Wespergroup catalog. WESPERGROUP, Div. of WESPERCORP (USA), 14321 New Myford Road, Tustin, CA 92680, Tel: (714) 730-6250, Cable WESPER, TWX 910-595-1775, Telex 4720629. (Germany) GmbH, Tel: 089 982420. (U.K.) Tel: (44) 0276-20934.

DEC, Unibus and Q-Bus are registered trademarks of Digital Equipment Corporation.

WESTERN PERIPHERALS

WESPER INTERNATIONAL

WESPERGROUP

Division of WESPERCORP

CIRCLE 16

DATASYSTEMS WESPERLINE

### THIS YEAR AT NCC, DSD WILL ADD A NEW TWIST TO DEC-COMPATIBLE STORAGE.

It's called Cyclone.™

High performance. Higher capacity. From the people who made DEC®-compatibility a good idea. Come by and see us at Booth H518.

It'll blow you away.

**DATA SYSTEMS DESIGN**

### SYSTEM TECHNOLOGY/ SOFTWARE

### **Dual-port operating system**

(continued from page 26)

operating system that the user has specified. Only one version of functions that are identical in both systems is maintained.

Since the presently available version of 4.2 BSD has larger file blocking sizes, more efficient access algorithms and flexibile file names. in addition to the features mentioned earlier, it was chosen as the heart of the OSx. However, as OSx Product Manager David Gewirtz said, although the current 4.2 BSD is more suitable for running large superminis, if System v enhancements prove superior, it will be incorporated as the OSx heart.

### Inside story

The two separate 4.2 BSD and System V universes exist in the same file structure and share a common kernel. And, as mentioned, the directory structure for command binaries. libraries, and header files look exactly the way users of each universe expect. Moreover, there is compatibility with the shell files and other programs that make assumptions about where certain files are in directories.

These "two universe" features and capabilities are possible because the OSx operating system can implement conditional symbolic links. These links are similar to 4.2 BSD's normal symbolic links except that the directory or file to which the symbolic name points is dependent upon which universe is in use. Also, conditional symbolic links work as fast as the more conventional symbolic links and have little overhead penalty.

Conditional symbolic links allow separate underlying library and header directories that may be accessed at will. To do this, for each directory that needs to maintain different files or contents in each universe, a dual symbolic directory is established which contains the conditional symbolic links to each.

The Unix Is command is a good example of conditional symbolic link usage. This command's function is to list the files in a directory (/bin). The actual listing on the user's terminal differs in format depending on the universe in use. A specific format is expected when the file /bin/ls is executed. In the OSx, /bin/ls executes

/.ucbbin/ls in the 4.2 BSD universe and /attbin/ls in the System v universe. All this is user transparent and the conditional symbolic link amounts to a pointer to the specific command that corresponds to the current working universe.

Other features of the OSX such as software development interfaces, signal processing, terminal drivers, and pipes will be discussed in the Special Report section of a forthcoming issue of Computer Design.

> -Harvey J. Hindin, Special Features Editor

> SYSTEM TECHNOLOGY (continued on page 32)

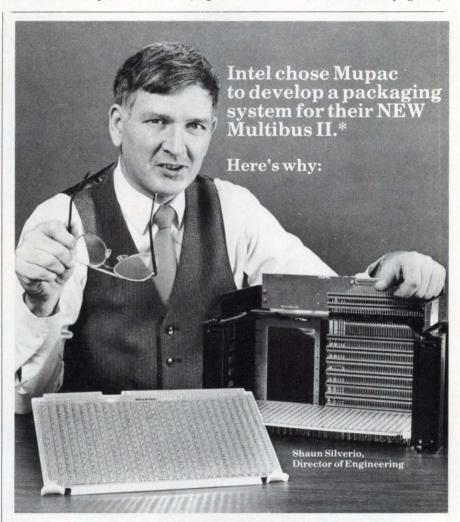

Intel liked the systems approach of our standard packaging hardware. It's modular, it's flexible and it's designed to work as one integrated system to solve your special packaging needs. This same approach is used with Multibus compatible packag-

ing, making Mupac the ideal choice for your Multibus packaging

requirements.

Our system is flexible, compact and reliable. It can handle from 2 to 26 panels in easy to use modular increments. Features include panel guides on .60 and .75 inch centers, a backplane designed to eliminate crosstalk and noise, terminated bus lines and provisions for parallel priority. Look to Mupac for the same reasons that Intel chose us to develop a packaging system for Multibus II. We're FIRST with multiple solutions to Multibus compatible packaging.

\*Multibus is a registered trademark of Intel Corporation.

10 Mupac Drive, Brockton, MA 02401 TEL (617) 588-6110 TWX (710) 345-8458

# MEMORIES.

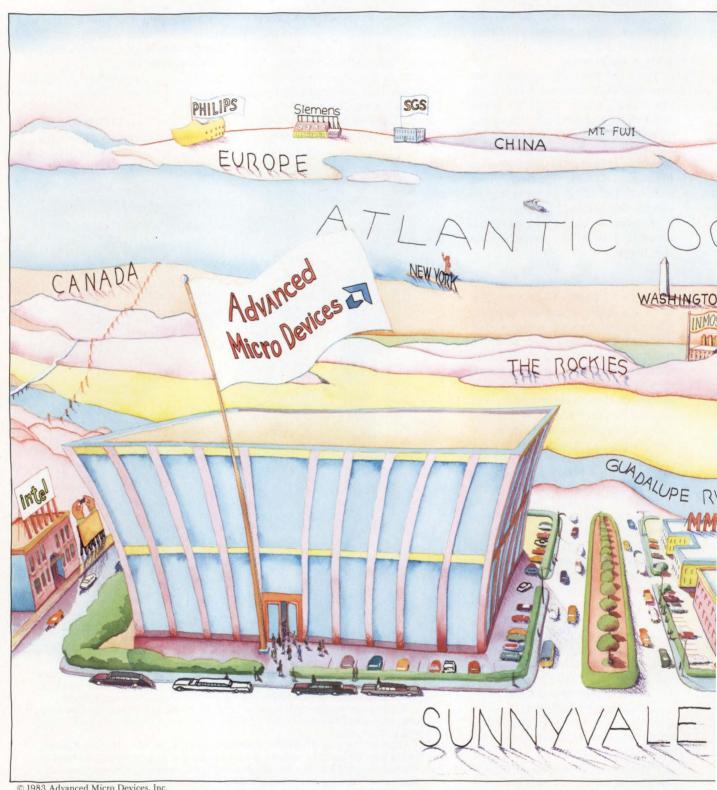

© 1983 Advanced Micro Devices, Inc.

# A WORLD PERSPECTIVE.

If you're looking for the world's fastest MOS static RAMs, don't look in Holland.

Searching for the world's fastest bipolar PROMs? Forget Texas or Arizona.

And you won't find the world's fastest EPROMs anywhere near Mt. Fuji.

They're all right here in Sunnyvale. At Advanced Micro Devices.

### Everything we make is fast. Including the Am27256, the world's fastest 256K EPROM.

The Am27256 is 170ns fast. It's the only EPROM quick enough to keep up with a 10MHz MPU without a wait state.

And we've got the 40ns Am27S43A, the world's fastest 32K bipolar PROM. And the 35ns Am2167, the world's fastest 16K static RAM.

With leading-edge parts like these, it's no wonder memories account for half our total sales.

And our other products are just as hot. Controllers. Bipolar and MOS microprocessors. Communications circuits. Signal processors. We've got 'em all, and then some.

And every single chip meets or exceeds the International Standard of Quality.

The International Standard of Quality guarantees a 0.1% AQL on all electrical parameters, AC and DC, over the entire operating range.

Next time your design demands high performance memories,

or any high-performance parts, look us up.

We put high performance on the map.

Write or call for a free Sunnyvale

poster and all the facts on our memories.

### Advanced Micro Devices 2

901 Thompson Place, P.O. Box 3453, Sunnyvale, CA 94088 For direct factory response call (408) 749-5000. Outside California, call toll free (800) 538-8450, ext. 5000.

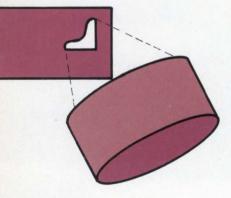

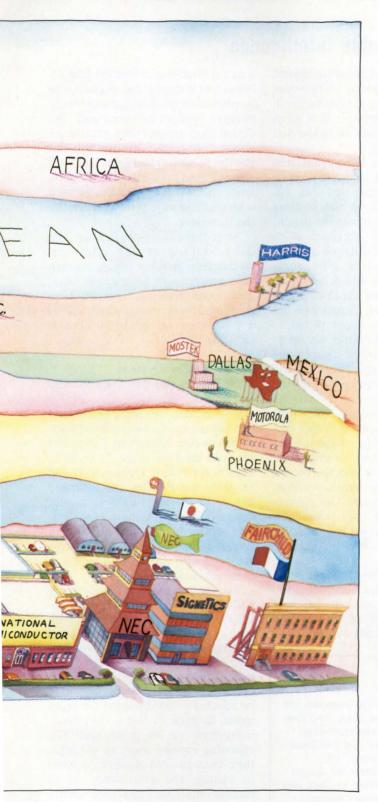

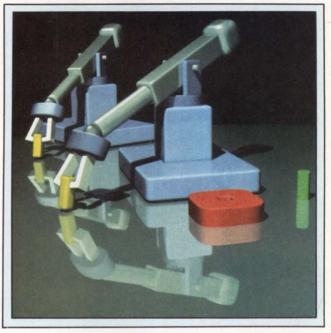

### Printwheel technology ups speed, adds intelligence

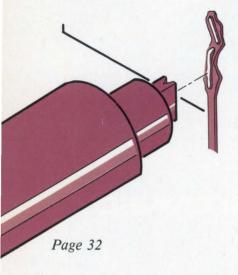

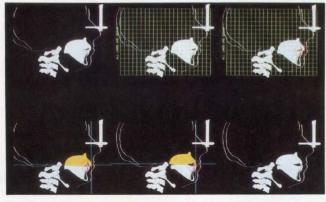

A recent daisy wheel printing technology greatly reduces parts count, yet preserves the ability to print a 200-char extended character set on a single printwheel without shifting the carriage. In addition, the technology packages the plastic printwheel in a snap-in cartridge. This cartridge is encoded to let the printing system recognize the currently inserted printwheel.

### Opting for a dual-hammer technique

Extended character set (ECS) printing without physical shifting is done by using a dual-hammer technique. One hammer is used to print characters on the printwheel's outer circumference, while the second hammer strikes only those in the inner circumference. The hammers themselves are aligned with the print line, but the characters have a unique arrangement.

For example, the unshifted version of each character is located nine spokes ahead of its shifted counterpart on the wheel. When a given spoke is in the vertical position, the shifted character (in the inner ring) is aligned with the first hammer. At the same time, its unshifted (eg, italic, or alternate font) counterpart is aligned with the second hammer on the print line, but ahead of the first hammer's position on the paper.

The characters on the outer ring are tilted with respect to the line of the spoke. This ensures that they are

upright on the print line when aligned with the second hammer. A firmware algorithm examines the line buffer in the printer to determine if a given character is to be printed by the first or second hammer.

Since the entire line is buffered before it is printed, characters can be arranged in the order that they will actually be struck as the printing mechanism moves across the platen. They do so with notation as to whether they will be struck by hammer one or two. As a result, some characters may be struck as far as nine print positions ahead of a previous character. But, all such gaps are filled in as the line is completed.

The printing technique incorporates several methods of improving speed and accuracy. These include position encoders and a closed-loop stepper motor for the printwheel mechanism, and wedge capture for the hammers and spokes. Wedge capture uses small wedge-shaped pieces behind the characters on the wheel. with corresponding notches on the hammers. When the hammer strikes, it captures the wedge. This ensures exact positioning and eliminates minute position variations caused by the settling of the wheel's motion, or by vibration.

The use of a closed-loop stepper motor for the printwheel mechanism allows a more precise calculation of wheel position (from information provided by the encoders), as well as a calculation of acceleration and deceleration energies. In addition, the combination of dual-hammer technology, wedge capture, and the closed-loop stepper can greatly increase throughput by printing onthe-fly. As the printwheel mechanism moves across the platen, information from its position encoders is used with that from the printwheel to fire the hammers.

Since there is no physical up and down shifting of the printwheel mechanism, motion can be smooth and continuous. Mechanical parts count and mass are reduced. The combination of these factors allows a print speed of up to 80 chars/s (55 typical).

### Incorporating new features

Diablo Systems (901 Page Rd, PO Box 5030, Fremont, CA 94537) estimates that the basic printwheel technology can be easily incorporated in low cost printers with end-user prices in the \$500 range. In order to demonstrate the technique's full range of possibilities, the company has built it into a new printer designed for networking applications. The 80IF printer is intended to run largely unattended and is thus equipped with various automatic and communication features.

The 80IF has a dual-bin sheet feeder with an envelope feeder, and a longlife ribbon. It can be equipped with multiple buffers or a 64-k optional spooler. Moreover, its communication capabilities let a remote user query the printer's status and select options to the same extent they could be selected onsite by using the front panel. Integral to this is the encoding present on the printwheel. The encoding enables users to see what they have, to send an operator alert to change the printwheel, or to handle malfunctions not easily resolved from a remote site.

> -Tom Williams, West Coast Managing Editor

> > SYSTEM TECHNOLOGY (continued on page 34)

The twin hammers are on the same print line with corresponding shifted and unshifted characters. The characters are spaced and tilted to align with the proper hammer. Notches in the hammers capture and align each character as it is struck.

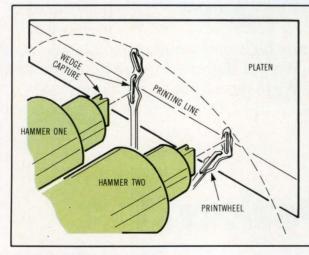

# Vectrix has the graphics system for your next system. Already.

For whatever system you're designing there's already an advanced color graphics system to go with it. Either the economical, easy to use VX128A or the versatile VX384A with its 16.8 million color palette and 512 simultaneously viewable colors.

When you add one of the Vectrix Systems to your system you turn your computer into a powerful graphics workstation with a fully integrated graphic command processor, a bit mapped graphics frame buffer, and a 672 x 480 pixel high resolution flicker-free monitor. Both systems deliver high quality, high performance color graphics. Because the simple command set works with any computer and any programming language, Vectrix makes any system a valuable tool for CAD/CAM, business graphics, medical imaging, video processing, computer assisted instruction, control systems, weather displays, or any of a host of graphics applications in demand.

The Vectrix VX128A and VX384A, part of an expanding line of graphics

products that do the job better, including the Midas System for the IBM PC XT and the Vectrix Paint Program.

If graphics should be a part of your system, Vectrix should be a part of your plan. Let us tell you just how we fit your system. Vectrix Corporation, 2606

Branchwood Drive, Greensboro, North Carolina 27408. Phone (919) 288-0520, Telex 574417.

Vectrix

THE COMPUTER GRAPHICS COMPANY

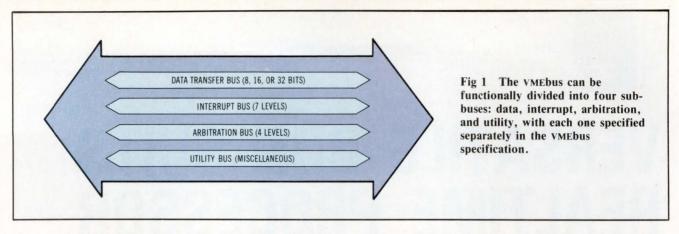

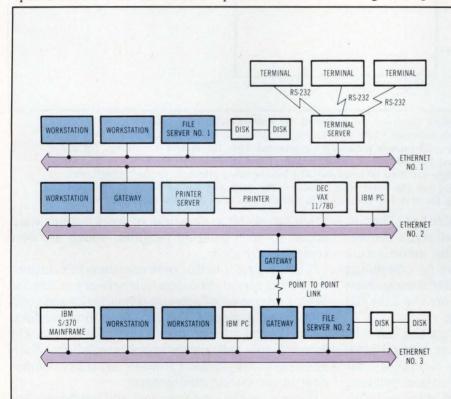

### The VMEbus to get larger slice of 16/32-bit board pie

Early in a project's life cycle, computer system integrators and designers must choose a bus and incorporate it into their workstations and computers. This bus of choice must, of course, be well suited to the realtime/ interactive, commercial, and technical marketplaces these workstations and computers serve. Also, the microcomputer and peripheral board designers need to know the bus or buses for which they should design their boards.

Until now, there has been a lack of detailed projections about how the various buses will fare over the next few years. Also lacking have been analyses of who the major board manufacturers are, as well as their individual strengths and weaknesses.

#### A new report

Those interested in this subject will be happy to hear that Zebu Corp (663 S Bernardo, Suite 222, Sunnyvale, CA 94087) has published proprietary investigations and a report about what the 16/32-bit board market will do in the next three years. Combining this report with additional statistical information from Dataquest, Inc (San Jose, Calif) and Ironoak, Inc (La Jolla, Calif) provides a first-class picture of what is going on with 16/32-bit board/buses and how new chip and bus technology affects them.

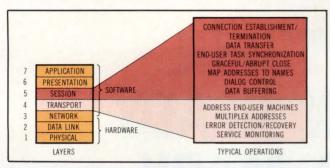

According to Zebu's president, microcomputer consultant Richard Main, the total board market will grow from \$400 million this year to \$490 million next year and \$600 million in 1986. Main also says that the VMEbus's 16-percent share of this year's market will more than double. reaching 33 percent by 1986. Since Digital Equipment Corp's buses will stay at a 30-percent share in the same time period, it is Intel's Multibus and the planned Multibus II that will lose almost half of their market share. This reflects a drop from a dominant 50 percent this year to 30 percent in 1986 (see Computer Design, Feb 1984, p 27 for a bus update).

|                                     | 1983          | 1984          | 1985          | 1986          |

|-------------------------------------|---------------|---------------|---------------|---------------|

| Total board market                  | \$350 million | \$400 million | \$490 million | \$600 million |

| VMEbus sales                        | \$30 million  | \$65 million  | \$150 million | \$200 million |

| VMEbus market sales                 | 8.5 percent   | 16 percent    | 30 percent    | 33 percent    |

| Multibus market share DEC Q-bus, BI | 60 percent    | 50 percent    | 40 percent    | 30 percent    |

| market share                        | 30 percent    | 30 percent    | 30 percent    | 30 percent    |

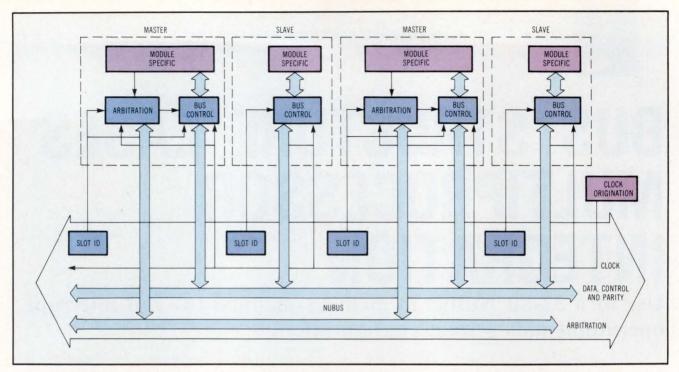

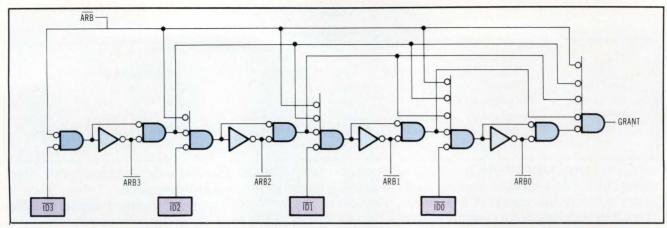

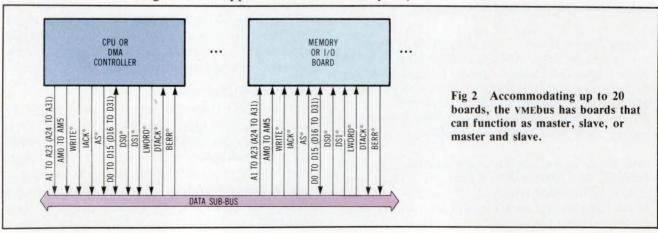

Main claims that market share trading and VMEbus growth is due to the appeal of the bus's Eurocard construction, as well as the scarcity of board and bus design, and production resources in general. He adds that the growing importance of standards is another factor leading to the growth of buses in general, and of the VMEbus in particular. For instance, asynchronous VMEbus is already an IEEE standard and synchronous Multibus II is being considered by the IEEE 896.2 synchronous bus committee.