MAY 15, 1988

#### A PennWell Publication **GONDOUTER DESIGN** THE MAGAZINE OF SYSTEM DESIGN AND INTEGRATION

10

30

30

### RISC ARCHITECTURES TAKE ON HEAVYWEIGHT APPLICATIONS

LINEAR ARRAYS FORGE IMPROVEMENTS IN PERFORMANCE AND FLEXIBILITY

20

INSTRUCTIONS

ISDN PIECES BEGIN TO FALL INTO PLACE

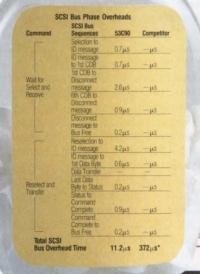

# WANT TO TALK SCSI? CALL CIPRICO AT 1-800-SCSI-NOW.

Why talk SCSI with Ciprico? To start with, we're the only vendor with a complete line of high-performance SCSI host bus adapters for Multibus\* I, VMEbus, and Multibus II. Each board was designed to optimize performance with its system bus. And consider our experience. Ciprico has over 50,000 boards installed worldwide. Our design expertise provides you with the highest possible performance at the lowest possible price.

But that's not all. Ciprico has respondability. We have the largest staff of customer support engineers in the industry to help you resolve any integration problems. Plus software drivers for all major operating systems.

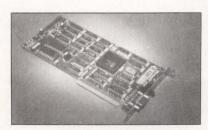

Our SCSI adapters are all based on an 80186 microprocessor, providing a command queuing, pass-through SCSI command software interface. Each board supports SCSI disconnect/reconnect and asynchronous and synchronous transfer rates of 2MB/s and 5MB/s respectively. And a floppy port is optional for cost effective system design.

So if you're currently designing a system based on Multibus I, VMEbus, or Multibus II, give us a call to talk SCSI.

RIMFIRE 1500 SCSI Adapter for Multibus\* I

**RIMFIRE 3510**

SCSI Adapter for VMEbus

> RIMFIRE 2500 SCSI Adapter for Multibus<sup>®</sup> II

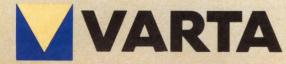

# **Record-Shattering CPU Performance!**

Sustained 20-MIPS, 7-MFlop throughput in a 32-bit CMOS CPU and FPU.

#### Nothing else comes close.

What happens when you blend our ultra-fast PACE Technology™ with MIPS, the top-performing RISC architecture?

Simple—a breakthrough of major proportions. A 32-bit CPU/Floating point processor set that delivers *sustained* throughput of 20-MIPS, and 7-MFlop single precision, LINPACK, or 4-MFlop double precision. (Peak throughput exceeds 25-MIPS.)

There's more. The market-rattling performance of the PaceMips<sup>™</sup> R3000 and R3010 is supported by 256K bytes each of high-speed instruction and data cache memory. The speed, as you might expect, is made possible by our 64K, 16K and 4K SRAMs—the world's fastest—in x1, x4 and x8 organizations.

If record-shattering performance interests you, you'll call our marketing HOT LINE today at (408) 734-9000 for more information. On pricing. Operating systems. Compilers. Development systems. And fast static RAMs.

The PaceMips R3000 and R3010. Ready now. With champion performance that can make your next system a winner, too.

Performance Semiconductor Corporation 610 E. Weddell Drive, Sunnyvale, CA 94089 Telephone (408) 734-9000

PACE Technology is a trademark of Performance Semiconductor Corporation. PaceMips is a joint trademark of Performance Semiconductor Corporation and MIPS Computer Systems, Inc.

CIRCLE NO. 2

# Now you can grab, store, and process 16 images in Real Time on the PC AT.

The DT2861 Arithmetic Frame Grabber can process 4 times as many images as any other frame grabber built for the PC AT.

With a built-in processor, the DT2861 also lets you process 4 images in parallel, or switch display instantaneously from as many as 16 images. The DT2861 grabs images off virtually any video source,

including CAT scanners, scanning electron microscopes, line-scan cameras, as well as

ordinary video cameras and VCRs. It even ships with IRIStutor<sup>™</sup> softwarefor free!

For more information about the Frame Grabber

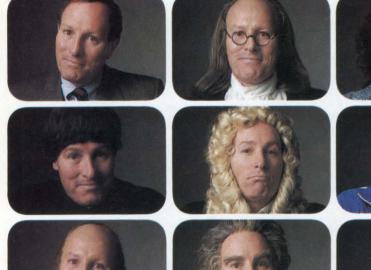

The many faces of Fred Molinari, President.

that's 4 times better than anything else made for PCs, give us a call today.

#### (617) 481-3700.

■ DT-Connect<sup>™</sup> is an open interface specification which permits the direct connection of stand-alone data acquisition and frame grabber boards to processor boards for greatly accelerated signal (DSP) and image processing.

| Image<br>Processing<br>Board | Computer  | Resolution | Gray Levels | RS-170, NTSC,<br>RS-330, CCIR,<br>PAL Compatible | VCR<br>Compatible | Slow Scan | Number<br>of Video<br>Inputs | Real-Time<br>Frame Grab | On Board<br>8-bit ALU | Memory-Mapped<br>Frame-Store<br>Memory     | Zoom, Pan,<br>Scroll | Software<br>Support  | Price  |

|------------------------------|-----------|------------|-------------|--------------------------------------------------|-------------------|-----------|------------------------------|-------------------------|-----------------------|--------------------------------------------|----------------------|----------------------|--------|

| DT2861<br>Frame<br>Grabber   | IBM PC AT | 512x512    | 256         | Yes                                              | Yes               | 0–12 MHz  | 8*                           | Yes                     | Yes                   | 16 buffers<br>512x512x8 each<br>(4 Mbytes) | Yes                  | DT-IRIS<br>IRIStutor | \$4995 |

\*With DT2859 1/2 size multiplexer board (\$395).

World Headquarters: Data Translation, Inc., 100 Locke Drive, Marlboro, MA 01752-1192, (617) 481-3700 Tix 951646 United Kingdom Headquarters: Data Translation Ltd., The Mulberry Business Park, Wokingham, Berkshire RG11 2QJ, U.K. (0734) 793838 Tix 94011914 West Germany Headquarters: Data Translation Burbh, Stuttgarter Strasse 66, 7120 Biettgheim-Bissingen, West Germany 07142-54025 International Sales Offices: Australia (2) 662-4255; Belgium (2) 735-2135; Canada (416) 625-1907; Chile (2) 25-3689; China (408) 727-8222, (8) 721-4017; Denmark (2) 274511; Finland (90) 372-144; France (1) 69077802; Greece 951-4944, 527-039; Hong Kong (3) 771-8585; India (22) 23-1040; Israel (3) 32-4298; Italy (2) 82470.1; Japan (3) 502-5550, (3) 375-1551, (3) 355-1111; Korea (82) 756-9954, Netherlands (70) 99-6360; New Zealand (9) 504-759; Norway (02) 55 90 50; Portugal 545313; Singapore 7797621; South Africa (12) 46-9221; Spain (1) 455-8112; Sweden (8) 761-7820; Switzerland (1) 723-1410; Taiwan (2) 709-1394; United Kingdom (0734) 739838; West Germany 07142-54025.

CIRCLE NO. 3

May 15, 1988

This issue's cover was designed by John Bonner.

#### COLUMNS

16 Editorial 104 Design for Testability

#### DEPARTMENTS

9 Up Front 103 System Showcase

108 Advertisers' Index

COMPUTER DESIGN © 1988 (ISSN-0010-4566) is published twice monthly, except one issue in July and December, by the Advanced Technology Group of PentWell Publishing Company, PO Box 417, 119 Russell St., Littleton, MA 01460. Second-class postage paid at Tulsa, OK 74112. Rates for non-qualified subscribers: \$70 in U.S.A. and \$95 elsewhere. Single-copy price is \$6.00 in U.S.A. and \$8.50 elsewhere. SUBSCRIPTION INQUIRIES: (918) 831-9401, 8 am-5 pm E.S.T. \* COMPUTER DESIGN is a registered trademark. All wicks essented No materialte may be retrinted without

rights reserved. No materials may be reprinted without permission. Phone (617) 486-9501. POSTMASTER: Send change of address form 3579 to

COMPUTER DESIGN, Circulation Department, Box 3466, Tulsa, OK 74101 (USPS 127-340). COMPUTER DESIGN

#### SYSTEM TECHNOLOGY

Design and Development Tools

24 VHDL simulator provides interactive verification

#### **Computers and Computer Subsystems**

28 Moderately parallel supercomputer avoids vector hardware

#### Peripherals and Memory Systems

30 Erasable optical drives ready to move in on Winchester turf

#### **TECHNOLOGY AND DESIGN REPORTS**

#### Technology Focus on Analog Gate Arrays

**37** Linear arrays forging improvements in performance and flexibility

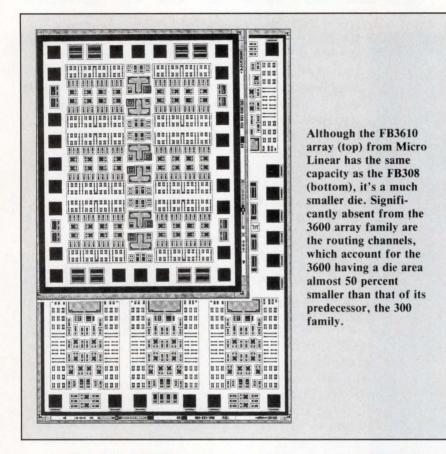

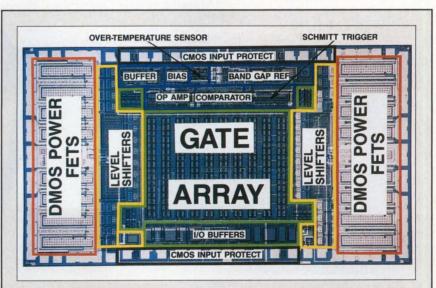

Within the last year, linear arrays have begun to catch up to their digital counterparts. Developments in base silicon, array architecture and CAD environments are combining to give the analog designer higher performance and more flexibility.

#### **Technology Focus on Communication ICs**

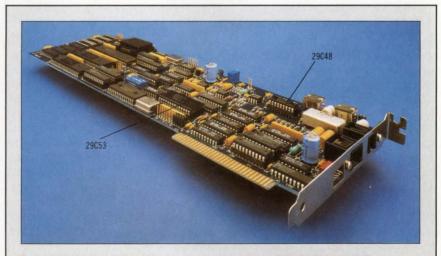

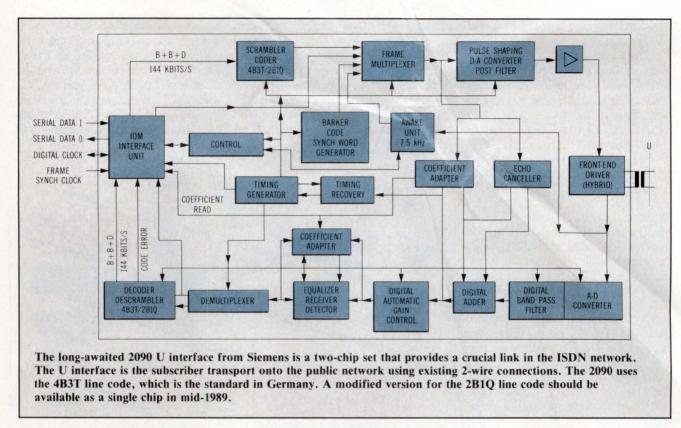

**48** The ISDN puzzle takes shape as the pieces fall into place Recent announcements indicate an industry-wide commitment to ISDN. Vendors are integrating higher levels of performance into new S and T interface chips while expanding their offerings to support other points in the network. Even more significant, development boards are starting to appear.

#### Special Report on RISC Processors

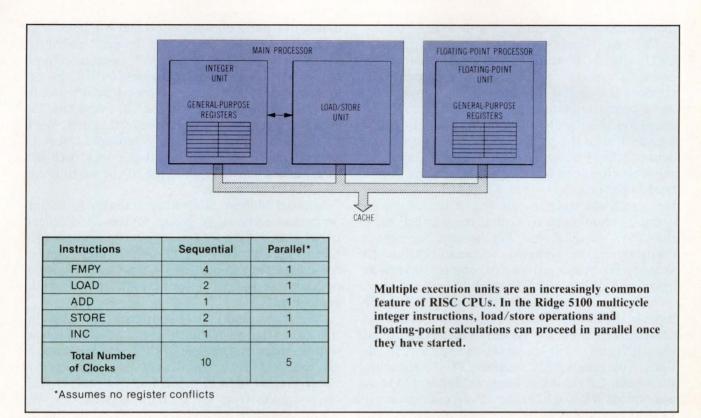

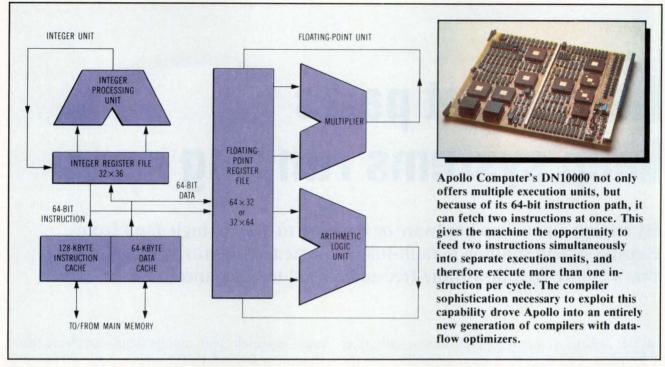

**59** RISC architectures take on heavyweight applications The concepts that define RISC architecture have left the lab and are working their way into superminis, workstations and embedded computers.

#### System Design

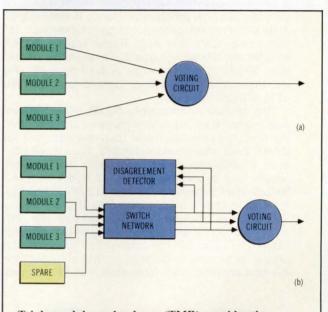

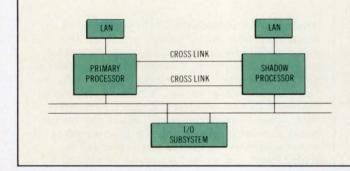

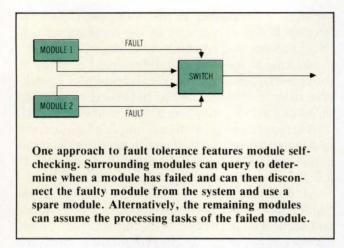

80 Redundant parts keep systems running

By relying on backup hardware or software to keep a single fault from causing system shutdown, fault-tolerant systems can provide computing that's failure-free, downtime-free and almost maintenance-free.

#### SYSTEM PRODUCTS

#### Memory Systems

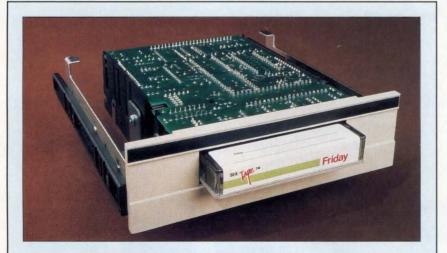

88 <sup>1</sup>/<sub>4</sub>-in. tape drives follow desktop directions

#### **Integrated Circuits**

96 Chip integrates XT/AT Winchester disk control functions

#### Software

**98** Real-time operating system for 80386 offers comprehensive solution

#### **Computers and Computer Subsystems**

99 Low-cost DSP board supports popular workstations

#### **Design and Development Tools**

100 Software and library simplify programmable gate array use

#### **Data Communications**

102 VME controllers optimize Ethernet performance

# FROM NOW ON, THFRF'S **ONLY ONE RISC**\* WORTH TAKING.

#### INTRODUCING THE MOTOROLA 88000 MICROPROCESSOR FAMILY: THE GREATEST RISC OF ALL.

The future of RISC computing has been reduced to three small, but amazingly powerful chips.

Namely, the Motorola 88000 family. One awesome microprocessor unit, supported by two cache memory management units. Designed to take RISC architecture far beyond anything else in the marketplace.

The 88000 runs at a blistering 14-17 MIPS, 7 million floating point operations per second, and an incredible 50 MIPS in parallel processing applications (using just four 88000 chip sets on our HYPERmodule<sup>®</sup> card).

Which makes everything from multi-user business systems to fault tolerant on-line transaction processing systems to artificial intelligence systems several times faster and more powerful than ever before.

What's more, it comes with absolutely every bit of hardware and software needed to build your system of the future, today. In fact, many leading hardware and software companies, including those in the independent consortium 880pen, are already designing systems around the 88000. And many more will follow.

So make sure your future is as rewarding as it can possibly be. Call us for more information at 1-800-441-2447. Or write Motorola Inc., P.O. Box 20912, Phoenix, AZ 85036.

Because the greater the RISC, the greater the reward.

\*Reduced Instruction Set Computer

© 1988, Motorola Inc. HYPERmodule is a trademark of Motorola Inc.

Unless you're using AT&T data cables, the 1988 fire codes could be cause for alarm.

8

e

EA

Gea

T

Ba

1.00

41-01

0

D

000

35

S

Ea

ECA

Φ

-

15

0

3

9

Rest assured. AT&T is ready now with a complete line of UL-listed data cable products that conform to the new National Electrical Code.

Whether you're concerned with building installations. or the interconnection of computer components, don't risk being burned by the new NEC fire safety standards, effective July '88.

The revised NEC specifies that only listed cable may be placed in buildings for data communications circuits. Yet many suppliers have been slow to respond to the stricter standards.

> The component of quick response.

AT&T is ready right now to deliver UL-listed digital cable\*\* for a wide range of high data-rate applications:

LAN cables for buildingwide voice and data communications-all CMlisted—as the Code requires for single-cable voice/data operation.

Enhanced Performance data cables, including coax replacement cable. As replacements for coax and other types of signaling wire, AT&T Enhanced Performance data cables are smaller and-at a fraction of coaxial price-much more cost-efficient.

A full line of conventional data cables to meet vour routine needs, all CM-listed.

#### AT&T, Department O,

P.O. Box 1278, Morristown, NJ 07960-1278 Please send me information on AT&T's UL-listed data communications cables, and the location of my nearest distributor. Name.

State.

Zip

Title.

City.

Company\_

Address

The component of innovation. Enhanced by advanced technology, our data cables have, in most cases, been assigned a higher UL listing-CM versus CL2-than many competitive products, as shown below. These products handle a

NEC ARTICLES 800 725 780 PLENUM ISER PURPOSE **GENERAL** MC LEGEND RESIDENTIAL LISTED TYPE CM = COMMUNICATIONS CM = COMMON CL3 = CLASS 3 POWER LIMITED POWER LIMITED POWER LIMITED POWER LIMITED FIRE PROTECTIV SIGNALING P = PLENUM R = RISER X - EXEMPT FROM PASSING A LARGE SCALE FIRE TEST B CABLE A MAY BE USED IN PLACE OF CABLE B CABLE A MAY BE USED IN PLACE OF CABLE B WITH RESTRICTIONS

AT&T data cables, in most cases, carry a higher UL listing than competitive products.

enabling you to reduce your cable variety inventory. And in addition to 300V CM-listed cables, many of our cables carry a UL-recognition, and include a complete list of

CD 5/15/88

the specifications necessary for cabling your components.

# AT&T: The components of success.

The component of quality. AT&T's quality assurance wider range of applications, program includes the full commitment of AT&T Bell Laboratories, along with an industry-pacing, threetiered inspection and audit

> program. So don't wait. Mail the coupon, or call AT&T at 1800 PICK-ATT, Ext. 300 for more information and the location of your nearest distributor.

\*Registered trademark of the National Fire Protection Association \*\*Western Electric Products @ 1988 AT&T

## "YOU NAME THE APPLICATION -WE'VE GOT THE MODEM IC."

#### For Today's Designs

A quick glance at our Selection Chart shows that at data transfer speeds of 300 to 2400 BPS for U.S. or world-wide market applications, Silicon Systems has the industry's most advanced family of pin-compatible, single-chip modems available now for your current designs.

#### For Tomorrow's Designs

We call this versatile family the SSI K-Series line of single-chip modems. These CMOS integrated circuits are all software and hardware compatible, allowing for easy product upgrading over the entire Bell and CCITT ranges of full-duplex, split-band telecom standards needed for your present and future designs.

#### **Special Features For Special Applications**

The family includes an easy-to-use microprocessor control interface, and versatile features suitable for a wide variety of applications. The "U" versions integrate an industry standard UART with the modem function in a design optimized for integral bus applications, and the low-power "L" versions operate from a single + 5 volt supply, making portable, battery, or line powered designs possible.

For more information on the K-Series Family, or our complete line of Tone Signaling, Telephony, and Digital Telecom products, send for our Modem and Telecom brochures today. Silicon Systems, 14351 Myford Road, Tustin, California 92680.

INNOVATORS IN INTEGRATION

|                                                                                                             |                         | MOD                 |                     | ELECTIO                     |                                    |                                  |                                              |                                                                           |

|-------------------------------------------------------------------------------------------------------------|-------------------------|---------------------|---------------------|-----------------------------|------------------------------------|----------------------------------|----------------------------------------------|---------------------------------------------------------------------------|

| APPLICATIONS                                                                                                | PRODUCTS                | 1. 100 10           |                     | OPERATIN                    | and the second second              | and the second second            | 1.1                                          | 1                                                                         |

| MARKETS<br>SERVED                                                                                           | SSI<br>DEVICE<br>NUMBER | 103<br>0-300<br>BPS | 212A<br>1200<br>BPS | <b>V.21</b><br>0-300<br>BPS | <b>V.22</b><br>600/<br>1200<br>BPS | V.22 bis<br>1200/<br>2400<br>BPS | V.23<br>0-1200<br>BPS                        | PRODUCT<br>FEATURES                                                       |

| UNIVERSAL<br>APPLICATIONS<br>Stand-Alone or                                                                 | 73K212                  |                     |                     |                             |                                    |                                  |                                              | High perform-<br>ance single-<br>chip modems                              |

| Integral Modem<br>Designs                                                                                   | 73K221                  |                     |                     |                             |                                    |                                  |                                              | with easy-<br>to-use cost-<br>effective                                   |

|                                                                                                             | 73K222                  |                     | -                   |                             |                                    |                                  |                                              | features.                                                                 |

|                                                                                                             | 73K224                  |                     |                     |                             |                                    |                                  |                                              |                                                                           |

| LOW POWER<br>APPLICATIONS<br>• Lap Tops<br>• Portable                                                       | 73K212L                 |                     |                     |                             |                                    |                                  |                                              | High perform-<br>ance single-<br>chip modems<br>providing                 |

| Terminals<br>• Line Powered<br>Modems                                                                       | 73K221L                 |                     |                     |                             |                                    |                                  |                                              | low-power<br>operation<br>from a single<br>+ 5 volt<br>supply.            |

| Battery-Powered     Units                                                                                   | 73K222L                 |                     |                     |                             |                                    |                                  |                                              |                                                                           |

| DEDICATED                                                                                                   |                         |                     |                     |                             |                                    |                                  |                                              | Enhanced                                                                  |

| INTEGRAL<br>APPLICATIONS<br>• Bus-Oriented                                                                  | 73K212U                 | BUT ST              |                     | 5                           |                                    |                                  | sing<br>mod<br>with<br>integ<br>16C4<br>func | single-chip<br>modems<br>with a fully                                     |

| Systems • Credit Verification                                                                               | 73K221U<br>73K222U      |                     |                     | TENSOR                      |                                    |                                  |                                              | integrated<br>16C450 UART<br>function, and                                |

| <ul> <li>Automatic Teller<br/>Machines</li> <li>Pay Telephones</li> <li>Diagnostic<br/>Equipment</li> </ul> |                         |                     |                     |                             |                                    |                                  |                                              | added circuitr<br>to simplify<br>integral<br>designs.                     |

| EUROPEAN<br>DATA COM<br>APPLICATIONS<br>Multi-standard                                                      | 73K322*                 |                     |                     |                             |                                    |                                  |                                              | Single-chip<br>modems add<br>V.23 and spe-<br>cial features               |

| modems<br>requiring<br>videotex                                                                             | 73K322L <sup>•</sup>    |                     |                     |                             |                                    |                                  |                                              | to standard<br>operating<br>modes;                                        |

| compatibility                                                                                               | 73K324L                 |                     |                     |                             |                                    |                                  |                                              | available in<br>+ 12 volt or<br>+ 5 volt<br>versions.<br>• Available 1988 |

"Where we design to your applications."

CIRCLE NO. 6 FOR PRODUCT INFORMATION CIRCLE NO. 7 FOR CAREER INFORMATION

## **UP FRONT**

#### Tandy announces breakthrough in erasable optical media

The search for truly erasable optical media may have ended with an announcement by Tandy (Fort Worth, TX) of a new media technology called Thor (Tandy High-intensity Optical Recording). While the company won't disclose the details, the media is written by laser heating, which causes the layered material structure to buckle inward, forming a small depression on the surface that can be read by the read laser. Reheating causes the depression to flatten out again, leaving the surface in its original form. Tandy's plans are for erasable audio recording on the same format as compact disks, but data storage—using CD ROM format and larger platters—is also feasible. If the technology proves workable, it could compete with CDs and digital audio tape in the consumer arena and with CD ROM, write-once optical and magneto-optical recording in the computer industry.—*Tom Williams*

#### Behavioral logic synthesis joins EDA marketplace

A long-standing dream of electronic design automation (EDA) vendors the ability to translate behavioral inputs into gate-level schematics and net lists—is closer to being reality. Silc Technologies (Burlington, MA) is introducing Silcsyn, a logic-synthesis tool that can map behavioral descriptions into commercial application-specific IC libraries. Silcsyn includes an input language based on Lisp, a functional simulator and a static timing verifier. Initially available on workstations from Mentor Graphics (Beaverton, OR), Silcsyn can synthesize sequential or combinational logic. At least two other vendors will introduce commercial logic-synthesis toolsets within the next four weeks.—*Richard Goering*

#### Electroluminescent displays pare power, boost brightness

Planar Systems (Beaverton, OR), the market leader in thin-film electroluminescent displays, has now cut power consumption to make its displays more competitive with twisted liquid crystal displays. Using power recovery circuitry and more efficient drivers, Planar has reduced the maximum power rating on its  $640- \times 400$ -pixel display to 14 W—still three times the power needed for a comparable backlit supertwisted LCD. To help make the trade-off more palatable, the company has also increased brightness by 50 percent from 20 to 30 fL, or about four times that of the backlit supertwisted LCD.—John Mayer

#### Texas Instruments plans CASE tools for embedded systems

Having had some success with its Information Engineering Facility (IEF), a computer-aided software engineering (CASE) system designed to develop information systems, Texas Instruments (Dallas, TX) hopes to be among the first to deliver a completely integrated system for realtime embedded systems. Like IEF, the proposed system would automate software design, from planning and analysis to code generation. But don't look for it any time soon. "By the early 1990s, we expect to have a product...that takes the IEF approach," says Michael Watters, TI's manager of advanced information management. With such a product, developers of embedded systems might find benefits similar to the 4:1 productivity enhancements over conventional system development methods already provided by implementations of IEF.—John Mayer

(continued on page 10)

#### **UP FRONT**

(continued from page 9)

#### High-performance real-time system abandons Multibus for VME

The recently unveiled 68030-based computer systems from Masscomp (Westford, MA) provide the company with a formidable weapon in its attack on the real-time scientific market. But one of the more intriguing aspects of the product line is the company's decision to move from the Multibus I-based designs of earlier products to a VMEbus-based architecture rather than to Multibus II. "Looking at industry trends, we saw that the direction was toward VME," says product manager Judith La-Rocque. "VME has much more support than Multibus II. Upward compatibility with our Multibus I-based systems is retained by supporting up to six Multibus-to-VME interface modules."—John Mayer

#### Valid Logic to become largest full-custom IC CAD supplier

By acquiring the IC layout product line from Calma (Milpitas, CA), Valid Logic (San Jose, CA) will soon become the industry's largest fullcustom IC CAD supplier. The acquisition agreement, which effectively removes Calma, a subsidiary of General Electric, from the electronic design automation market, brings Valid an installed base of more than 2,700 users. When the agreement is complete, Valid will assume all sales and development responsibilities for the GDS-II (Graphics Design System) and EDS-III (Electronics Design System).—*Richard Goering*

#### Trade association promotes Nubus for industrial applications

Claimed to be a cost-effective alternative to both the low-end STD Bus and Multibus I but having performance capabilities comparable to the high-end VMEbus and Multibus II, Nubus is potentially the bus-ofchoice for many industrial applications, according to its supporters who met earlier this month in Atlanta during Comdex/Spring. The group will develop a charter, objectives and membership requirements prior to a full promotional effort for Buscon/East in October, according to Jennifer Maher, marketing project manager at Mizar (St. Paul, MN), who led the meetings. Seven companies are involved in the association, including Apple Computer (Cupertino, CA), which chose Nubus for its Macintosh II; Texas Instruments (Austin, TX), an early developer of the bus; and Mizar. For more information on the association, contact Anne Weber at (714) 669-1201.—Sydney Shapiro

#### ASIC microcontroller cores grow to 16 bits

National Semiconductor (Santa Clara, CA) has announced the conversion of its HPC 16-bit microcontroller to an application-specific IC megacell. The company claims the HPC Core is the first 16-bit microcontroller to be made available in a cell library. The cell, which National says can be tailored to suit the needs of individual designs, already includes a variety of memory and peripheral blocks, including RAM, timer/counters, an interrupt controller and a Microwire/Plus serial interface. The speed of the CPU core and the variety of included devices make the HPC Core a significant advance over existing 8-bit cores, according to sources at National.—*Ron Wilson*

Microfilm copies of COMPUTER DESIGN are available and may be purchased from University Microfilms, a Xerox Company, 300 North Zeeb Rd., Ann Arbor, MI 48106. Officers of PennWell Publishing Company, 1421 S. Sheridan, Tulsa, OK 74101; Philip C. Lauinger, Jr., Chairman and Chief Executive; Joseph A. Wolking, President; P.C. Lauinger, Chairman Emeritus; L. John Ford, Senior Vice President; Carl J. Lawrence, Senior Vice President; V. John Maney, Vice President/Finance.

# DRAMATIC!

#### Now...Highest speeds AND production... 60/70/80ns 1Mb AND 256K DRAMS...

FUTUREFAST

Exclusively from NMB Semiconductor - the high speed DRAM specialist - we've broken the speed barrier with FutureFast<sup>™</sup> 256K and 1Mb DRAMS...first with access times of 60/70/80ns. This means designers can now have true "0" wait state systems without using complex, expensive cache memory techniques.

| 1Mb  | DRAM | Access | Time (I  | ns)   | 256K DRAM Access Time (ns) |      |       |          |       |

|------|------|--------|----------|-------|----------------------------|------|-------|----------|-------|

|      |      | Com    | petitors |       |                            |      | Com   | petitors |       |

|      | NMBS |        |          |       | NA                         | IBS  |       |          |       |

| 60ns | 80ns | 100ns  | 120ns    | 140ns | 60ns                       | 80ns | 100ns | 120ns    | 140ns |

We've broken the delivery barrier too. NMBS offers much higher volume production than our competitors. These dramatic advances are made possible in the most advanced CMOS/VLSI plant in the world optimized for volume production of high speed DRAMS. With computerized operation and robot control in Class 1 ultra-clean rooms. Plus state-of-the-art design, processing and testing.

| Product Line Summary |                       |                      |                        |                                        |  |

|----------------------|-----------------------|----------------------|------------------------|----------------------------------------|--|

| Series*              | Access Time           | Organization         | Package**              | Availability                           |  |

| AAA2800<br>256K      | 60/70/80<br>(ns)      | 256Kx1               | P-DIP<br>PLCC<br>C-DIP | Production<br>Production<br>Production |  |

| AAA1M100<br>1Mb      | 100/120<br>(ns)       | 256Kx4<br>1Mbx1      | P-DIP<br>SOJ<br>ZIP    | Production<br>Production<br>Production |  |

| AAA1M200<br>1Mb      | 60/70/80<br>(ns)      | 256Kx4<br>1Mbx1      | P-DIP<br>SOJ<br>ZIP    | 2Q88<br>2Q88<br>2Q88                   |  |

|                      |                       |                      |                        |                                        |  |

| * All Series availa  | able in Static Column | and Page Modes ** SI | MM'S and SIPS availa   | able for each series                   |  |

Available in the packages and organizations designers want for high performance projects.

More good news. We're now shipping qualification samples of our new 1Mb DRAM.

So for complete specs, evaluation units, quantity prices and delivery call NMBS - the high speed DRAM specialists - today. Prove to yourself that with FutureFast<sup>™</sup> DRAMS, your future is now.

21/11: NMB TECHNOLOGIES INCORPORATED

SEMICONDUCTOR DIVISION

9730 Independence Ave. • Chatsworth, CA 91311 Tel: 818/341-3355, FAX: 818/341-8207, TLX: 651340

# Odds are 50-50 your perfect ASIC is a perfect dud the first time you plug it in.

## That's why Mentor Graphics lets you combine ASIC and board circuitry in a single simulation.

#### Trouble in ASIC paradise.

The big day has arrived.

Your first gate array is back from the foundry. With high expectations, you plug it into your board and power up.

It doesn't work.

Don't feel alone. Over 50% of ASICs aren't operational when first installed in their target system. Even though 95% pass their foundry tests with flying colors.

#### An immediate solution.

Mentor Graphics shifts these even odds heavily in your favor with our QuickSim<sup>™</sup> logic simulator, which lets you simulate both your ASIC and board circuitry in a single run.

With QuickSim, you not only track the internal operations of your ASIC circuitry, but also its transactions with the system at large. If there's a problem, you see precisely where it's located, either inside or outside your ASIC. All in a single, interactive simulation environment, where you can view and graphically "probe" the circuitry created by our NETED<sup>™</sup> schematic editor.

#### Check out our libraries.

Library support is an ideal benchmark to gauge the true worth of an electronic design automation system. The more diverse and plentiful the component modeling libraries, the greater the design capability. It's as simple as that.

By this simple, yet decisive measure, Mentor Graphics brings you unequaled design capability. While other EDA vendors scurry to produce their own ASIC libraries (with little guarantee of accuracy), more ASIC vendors put their libraries on Mentor Graphics workstations than any other. And in most cases, we're the first workstation supported, which means you have the first shot at exploiting new chip technologies.

With Mentor Graphics, you get a breadth of LSI and VLSI component models, both hardware and software based. All of which can be mixed with ASICs in a single simulation that cuts your run time to an absolute minimum.

#### To be continued.

So much for the present. We're already developing new systems EDA tools that will extend to every dimension of electronic product development. From high-level systems descriptions to CASE. It's what our customers expect. It's what we'll deliver.

It's all part of a vision unique to Mentor Graphics, the leader in electronic design automation. Let us show you where this vision can take you.

Call us toll-free for an overview brochure and the number of your nearest sales office.

Phone 1-800-547-7390 (in Oregon call 284-7357).

Yourideas. Our Experience.

# (Forward Thinking, Re

It takes more than desk-changing for two companies to merge. They need to have a shared vision of the world and the future.

With AMD and MMI, the calling was clear. To produce advanced programmable logic devices for a wide range of needs. To lower system costs. To develop higher performance designs. And to get your products to market as soon as possible.

We're delivering on this promise of the future in myriad ways. With a product line that doesn't stop halfway. With the first 10ns parts for designs where speed's important. In CMOS, we have the broadest line of parts, including the industry standard, C22V10. And for high density, no one can beat our programmable gate arrays. We've got the best selection of PAL® parts around. (And no one sells more to the military.)

We're bringing new meaning to the term "product availability." Our combined manufacturing capacities mean we have more PAL chips coming out of our pipeline. Ready to be put into yours.

And more Field Application Engineers give you more answers to get

# sponsive, Meticulous)<sup>2</sup>

projects up and running.

Because it's impossible to create great designs without great software, we also offer PALASM<sup>®</sup> software, the industry standard. We're investing heavily to keep PALASM as current as our hardware.

With the best network of distributors, we can now offer a whole new concept in distributor support: TestPro Centers. Now you can speed through programming and testing at authorized centers.

Just bring your logic pattern to your closest TestPro Center. They'll program and they'll test the parts to factory quality standards. Relieving you of the burden of test vector generation.

And we'll always be here with immediate and expert help in getting your design moving. Just call AMD at (800) 222-9323.

Or write Advanced Micro Devices, Inc., 901 Thompson Place, P.O. Box 3453, Sunnyvale, CA 94088.

One try and you'll be sharing our vision, too.

PAL and PALASM are registered trademarks of Monolithic Memories. Inc., a wholly owned subsidiary of Advanced Micro Devices. Inc. © 1988 Advanced Micro Devices. Inc.

#### **EDITORIAL**

# Putting their houses in order

n a whirlwind tour of the Midwest and Southwest last month, I visited a variety of board and computer houses, from small companies that ship a few hundred pieces a month

to large operations crunching through tens of thousands of products every 30 days. All the trends we've read about were evident in varying degrees at one company or another: design for testability and manufacturability, "soft" prototyping through design simulation, sophisticated materials-management systems, highly automated assembly equipment and so forth. What struck me most on my plant tours, though, was the excellent use of computers in the coordination and integration of all the parts of an operation and, in a few select places, the impressive use of Japanese principles to turn out better products by more highly motivated manufacturing personnel.

Two of the companies I visited had recently completely revamped their manufacturing operations. At both, operations managers steeped in the assembly-line tradition had thrown much of their training and experience out the window and enthusiastically embraced a foreign approach. In terms of job lots, "the bigger the better" is no longer the rule at these companies. In terms of work flow at individual manufacturing stations, "the quicker the better" no longer holds. As for component suppliers, "the more sources the better" has also become a part of the past. And no longer do these companies, or their customers, want to maintain large inventories of component products when just-in-time deliveries provide a much smoother manufacturing flow.

Virtually all the companies I visited have been willing to pay the up-front costs of producing a more efficient operation and a more reliable, more competitive product. The capital equipment costs can, of course, be staggering, the time and energy required to make major transitions are great, and the early stages of the learning curve can be very disruptive. Yet, not one company has failed to perceive a payback or, at least, clear indications that a payback is on its way.

At those companies where the Japanese influence is most apparent, one of the biggest up-front costs seems to be time. It takes time, first of all, for assembly personnel to make the psychological transition from being anonymous cogs in a machine to being, in essence, their own manufacturing managers, quality-control supervisors and, in some cases, maintenance personnel. And even once this transition is made, volume is typically below what it was. Yet even in the early stages, the beginning of the payback can be seen in the state of the products at the end of the manufacturing cycle. Despite the initial reduction in the volume of products produced, there's also typically a substantial reduction in both the number of products that require time-consuming in-house rework and the number that fail in the field.

David Liebeman

David Lieberman Senior Editor

# How To Wring Workstation-Level PCB Designs Out Of Your PC.

#### P-CAD's new Master Designer turns an ordinary PC into a full-fledged PCB workstation.

WORK.

MASTER

TYPICAL PC SOFTWARE

NUMBER OF USERS

When you need to wring every drop of performance out of your next PCB design, you need Master Designer<sup>™</sup> software.

Master Designer provides all the horsepower you'd expect only from workstations priced from \$50K up to as much as \$200K.

With Master Designer you can tackle the really big jobs. Board designs with 500 EICs, 32,000 pins and 2,500 nets are just the beginning. P-CAD's Master Designer routes multiple layers simultaneously cutting the number of vias and unrouted subnets in half. So, you'll wring out cleaner designs and higher completion rates (up to 100%). For forward annotation of logic changes and "history independent" back annotation, Master Designer also has an ECO processing option.

If you're interested in wringing every penny out of your PCB design station instead of wringing your hands, ring P-CAD. Let P-CAD show you how to turn a PC into a high-powered workstation.

P-CAD is a registered trademark and Master Designer is a trademark of Personal CAD Systems, Inc.

# WREN FRE

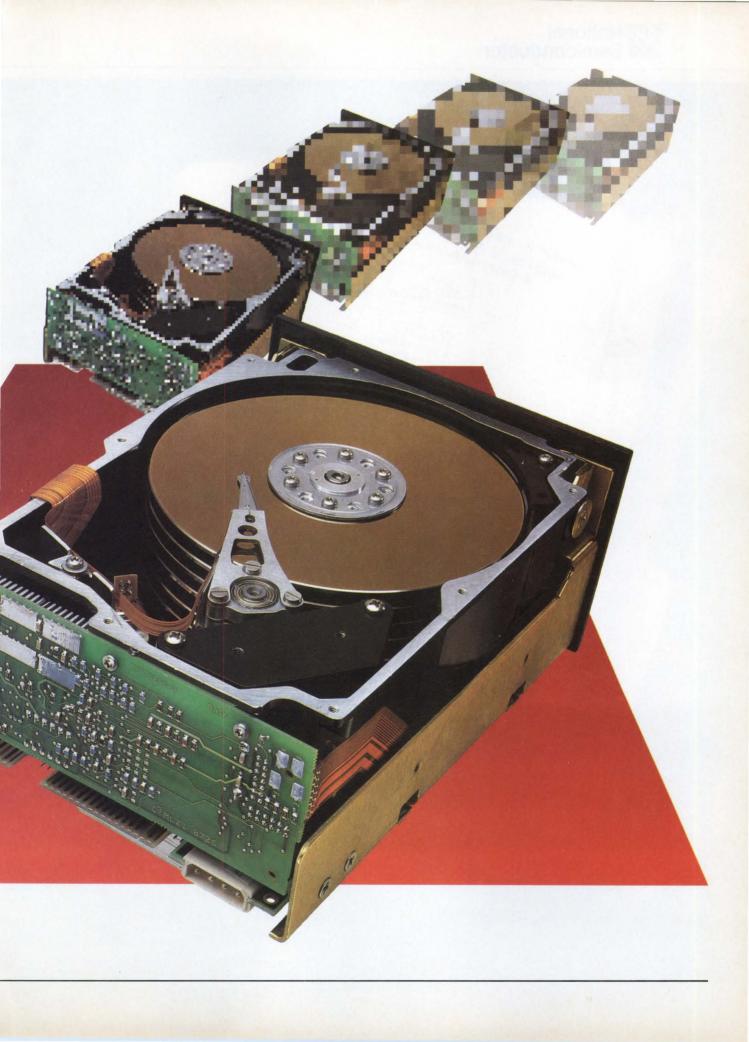

#### THE BEST 5<sup>1</sup>/<sub>4</sub> INCH DISK DRIVE AVAILABLE UNTIL WE BUILD WREN VI.

#### INTRODUCING WREN V

The fastest, most reliable 5¼" disk drives are now better than ever. The new WrenV with bigger capacity has up to 574 Mbytes formatted with the SCSI interface, or 442 Mbytes of unformatted capacity using the ESDI.

#### PERFORMANCE SECOND TO NONE

Wren V *is* high performance. Average seek is a blistering 14.5 ms. A patented, balanced straight-arm actuator, employing less mass than other designs, results in precision positioning and faster seek times.

#### DESIGNED-IN RELIABILITY

New Wren disk drives are better than ever thanks in part to lower power consumption, special shock mounts, advanced electronics packaging, and synchronized spindle capability for high performance subsystem applications. You can count on years of trouble-free use.

#### A COMMITMENT TO QUALITY

Manufacturing quality products and backing them with top-notch service and customer support is our commitment to you. We're with you every step of the way; from system's design to post-sales service in a true customer manufacturer partnership.

Get the high performance edge— Wren disk drives from Control Data. For more information, call 1-800-828-8001, ext. 82.

| Model         | Capacity<br>(Mbytes) | Avg. Seek<br>(ms) | Interface  | Transfer Rate<br>(MHz) |

|---------------|----------------------|-------------------|------------|------------------------|

| Wren V        | 574                  | 16                | SCSI       | 10-15                  |

| Wren V        | 442                  | 16                | ESDI       | 10                     |

| Wren V        | 383                  | 14.5              | ESDI       | 10                     |

| Wren V        | 344                  | 16.5              | SCSI       | 10-15                  |

| Wren V H.H.   | 190                  | 18                | SCSI       | 10-15                  |

| Wren IV       | 307                  | 16.5              | SCSI       | 10-15                  |

| Wren III      | 182                  | 16.5              | ESDI       | 10                     |

| Wren III      | 160                  | 16.5              | SCSI       | 10                     |

| Wren III H.H. | 106                  | 18                | ESDI       | 10                     |

| Wren III H.H. | 91                   | 18                | SCSI       | 10                     |

| Wren II       | 96                   | 28                | ST506,ESDI | 5                      |

| Wren II H.H.  | 51                   | 28                | ST506      | 5                      |

H.H. = Half High Models

SCSI models list usable capacity formatted in 1024 Byte sectors. Wren III, IV, V-344 Mb SCSI models have 40,000 Hr. MTBF (others: 30,000 Hr. MTBF).

**G**DCONTROL DATA

CIRCLE NO. 12

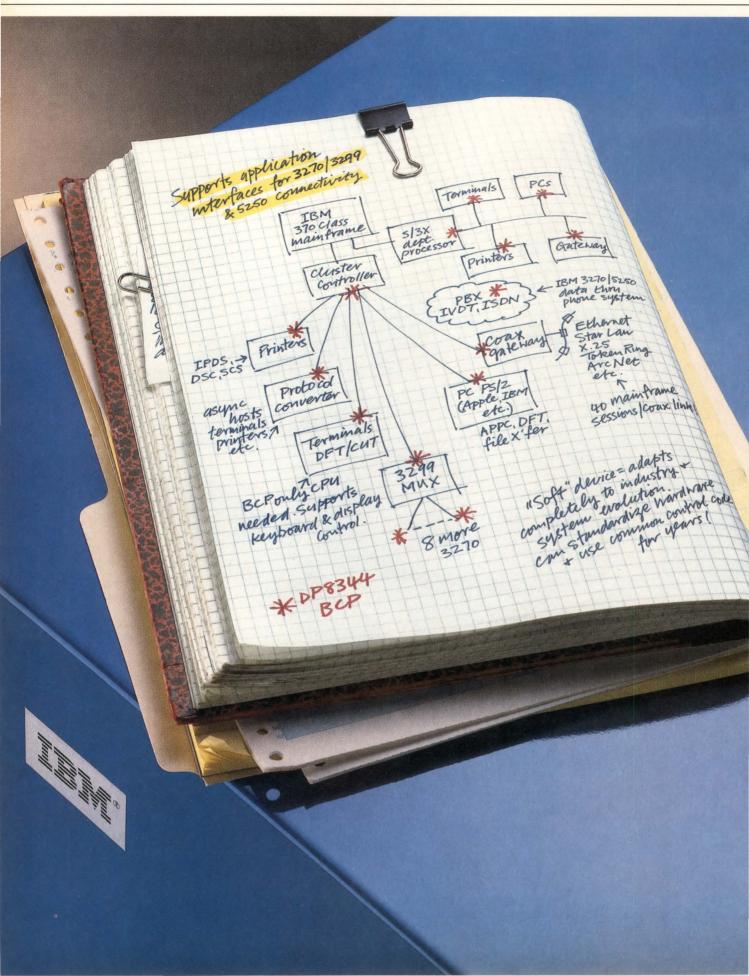

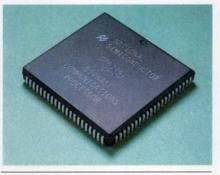

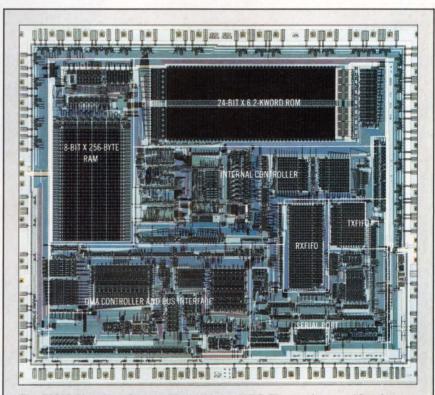

#### Now anyone can draw on the power of the mainframe with a single chip.

#### INTRODUCING THE DP8344 – THE EASY, AFFORDABLE WAY TO IBM CONNECTIVITY

At last there's a one-chip solution to processing IBM 3270, 3299 and 5250 communication protocols—the programmable DP8344 Biphase Communications Processor.

The BCP<sup>™</sup> is easily integrated into cluster controllers, PCs, terminals and printers, so now anyone can design a plug-compatible interface for IBM mainframe and departmental processors.

You can also use the DP8344 in a PBX or to build a gateway to various local- and wide-area networks.

You can use it in a protocol converter to give inexpensive peripherals access to the power of the main-frame. Or in a PC or IBM PS/2 to provide 3270 or 5250 terminal emulation.

In fact, providing IBM connectivity is now so simple and inexpensive that a host of new applications are being developed. The BCP has been designed in by more than 100 companies — including Hewlett-Packard, Local Data, Pathway Designs, Lee Data, Centronics, and Memorex.

© 1988 National Semiconductor Corporation BCP is a trademark of National Semiconductor Corporation IBM and PS/2 are registered trademarks of International Business Machines Corporation.

#### IT GIVES YOU A LOT OF POWER IN A VERY SMALL SPACE

A full system, supporting all three IBM protocols can be implemented in an area not much larger than a credit card.

The BCP integrates an intelligent transceiver and a high-performance CPU on the same low-power CMOS chip.

Powerful enough to operate as the sole system processor, the BCP also incorporates a flexible bus interface with on-chip arbitration logic, enabling communication with other processors.

With a 20-MHz, 50-nanosecond T-state processor, 30 instruction types, full-function ALU, and an instructioncycle time ranging from 100 to 200 nanoseconds, the DP8344 supports the 3270 protocol using only 20 percent of the CPU bandwidth.

Fast and flexible interrupt and subroutine capabilities, with on-chip stacks, make the remaining bandwidth readily available for other system tasks. In fact, enough power is available to eliminate other system processors entirely.

#### IT COULDN'T BE MORE FLEXIBLE

The BCP features a softwareconfigurable transceiver that supports not only IBM 3270, 3299 and 5250 protocols but also general eight-bit protocols.

A simple line interface connects the BCP to the communications line. The receiver includes an on-chip analog comparator and provides a TTL-level input for added flexibility.

#### WE'LL GIVE YOU ALL THE SUPPORT YOU NEED

The DP8344 is backed by a development package that includes a demo/evaluation board with a monitor/debugger program, insystem emulation features, and demonstration software for complete 3270 terminal emulation on an IBM PC.

On the system level, we offer both 3270 and 5250 controller emulators and analysis tools.

Application support is available through a worldwide network of technical support centers.

For more information on the DP8344 BCP— the easy, inexpensive way for you to provide IBM connectivity—please contact your National Sales Engineer.

Or write National Semiconductor, MS 23/200, P. O. Box 58090, Santa Clara, CA 95052-8090.

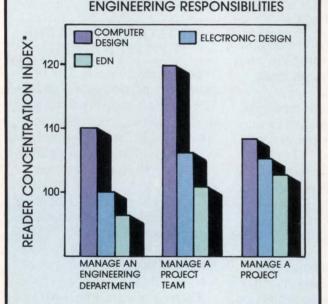

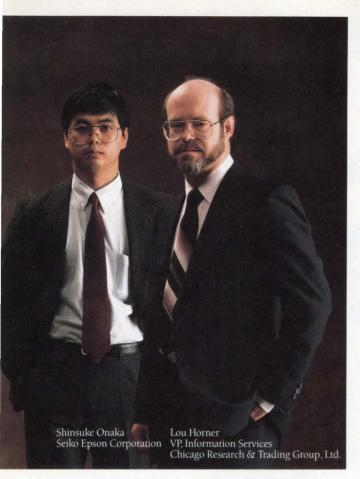

#### CONCENTRATION WHERE IT COUNTS...

Decisions about system design are made on several levels at the same time. They're made on the chip level, the board level, and the "box," or OEM computer level.

Because the people making these decisions are the design engineering managers and senior design engineers who supervise departments, project teams and individual projects, COMPUTER DESIGN—the magazine of *system* design and integration—targets its circulation and its editorial at this important group.

As a reader of COMPUTER DESIGN, you need information about many things. About ICs, about ASICs, about buses and boards, about CAE/CAD and development tools, about software, and about systems and system architecture. But you're in good company. In select company. Above-average company. COMPUTER DESIGN company.

\*Data based on the Adams Company 1987 Electronics Market Study. The reader concentration index is a measure of a publication's concentration of readers with a specific engineering or purchase responsibility. An index of 100 is the average for the reader universe sampled in the study.

## **COMPUTER DESIGN**

THE MAGAZINE OF SYSTEM DESIGN AND INTEGRATION

ASSOCIATE PUBLISHER/EDITOR-IN-CHIEF: John C. Miklosz

#### **TECHNOLOGY EDITORS:**

Ron Wilson, Integrated Circuits (Portland) Richard Goering, Design & Development Tools (Santa Clara) David Lieberman, Computers & Computer Subsystems Tom Williams, Graphics & Imaging (Santa Clara) John H. Mayer, Computers & Computer Subsystems Sydney F. Shapiro, Data Acquisition & Control

#### **CONTRIBUTING EDITORS:**

David Gabel, Computers & Computer Subsystems Warren Andrews, Integrated Circuits Steven L. Martin, Integrated Circuits Howard Falk, Software Art DeSena, Testing & Manufacturing

**RESEARCH/SPECIAL PROJECTS MANAGER:** Sydney F. Shapiro

SECTION/SPECIAL PROJECT EDITORS:

Ron Wilson, *System Technology* David Lieberman, *System Design* John H. Mayer, *System Products* Patti Villandry, *Directories*

MANAGING EDITOR: Susan R. Nykamp

COPY EDITORS: Richard Dagley, Kerstin L. Rosenquist, Deborah A. Caty

EDITORIAL ASSISTANT: Claire Ellis

#### WEST COAST OFFICES MANAGING EDITOR: Tom Williams EDITORIAL ASSISTANT: Deborah Reinke

3333 Bowers Ave, Suite 100

Santa Clara, CA 95054, Tel: (408) 982-0288

1111 S.W. Gaines, No. 8

Portland, OR 97201, Tel: (503) 224-9396

PUBLISHER: L. John Ford

MARKETING SERVICES MANAGER: Mary M. Gregory CIRCULATION DIRECTOR: Robert P. Dromgoole

**ART DIRECTOR:** Jan Horner **ILLUSTRATOR:** Christopher Hipp

PRODUCTION DIRECTOR: Jan M. Lopez PRODUCTION MANAGER: Mari Rodriguez ADVERTISING COORDINATOR: Shari L. Hasche COMPOSITION: Holly Kersey COVER ART: John Bonner

#### PUBLISHING COMPANY

Advanced Technology Group P.O. Box 417 119 Russell St, Littleton, MA 01460 Tel: (617) 486-9501

# SOYOU WANT SNA COMPATIBILITY. WHAT ARE YOU DOING FOR THE NEXT TWO YEARS.

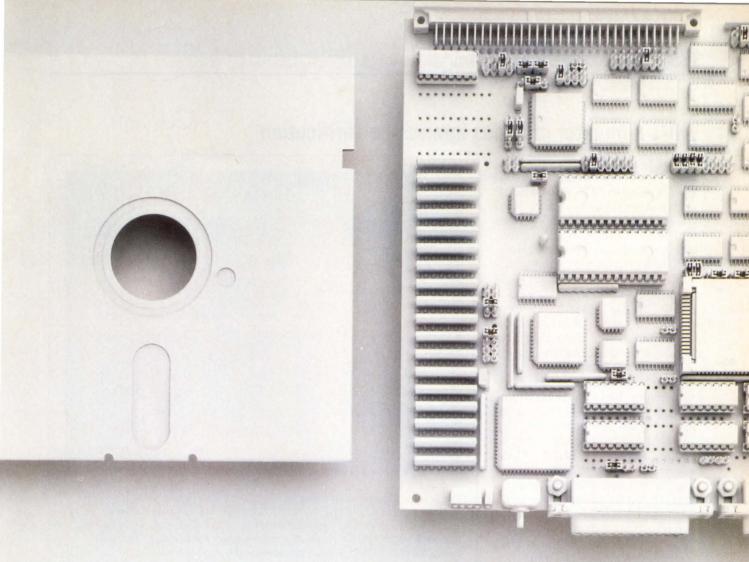

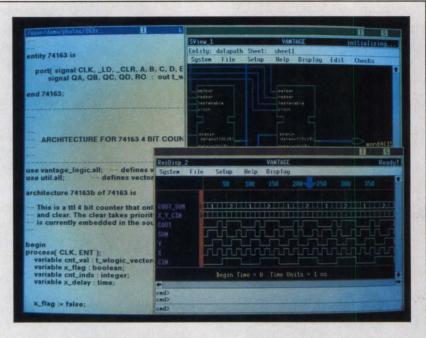

#### **VHDL** simulator provides interactive verification

What may be the first commercial logic simulator to provide a full implementation of the VHSIC Hardware Description Language (VHDL) is now available on workstations from Mentor Graphics (Beaverton, OR). The real story behind the simulator, however, may be the interactivity it allows the designer while simulation is underway.

The Vantage Spreadsheet from Vantage Analysis Systems (Fremont, CA) is newsworthy because it provides a complete implementation of the new IEEE standard, VHDL 1076. With a mandate for VHDL expected from the Department of Defense, designers in the military/aerospace market are scrambling for tools that will let them describe and simulate designs in VHDL. Many designers in the commercial world would also like to use an industrystandard hardware description language, and VHDL is on its way to becoming that standard.

But David Coelho, executive vicepresident of Vantage, has more than VHDL on his mind. "The most important thing we're bringing to the marketplace is the ability to make real-time changes to the schematic during simulation," he says. "This lets designers do a what-if analysis they never could do in the past. VHDL is just an opportunistic thing that we're leveraging."

#### **Compilation bottleneck**

One of the most frustrating aspects of logic simulation is the time it takes to change a design and then resimulate it. Designers usually must stop the simulation, return to the original schematic, change that schematic, and then recompile it into a net list for simulation. If a large design is involved, this process can take hours. Incremental compilation techniques may let designers recompile just a portion of the design, but they still have to get out of simulation and go back to the original schematic.

#### Richard Goering Senior Editor

The Vantage Spreadsheet from Vantage Analysis Systems provides a full implementation of the IEEE VHSIC Hardware Description Language 1076 standard. An even more important feature of the simulator, according to the company, is the provision of a multiwindow environment in which users can interactively change schematics during simulation.

Vantage provides a specialized schematic editor that lets the engineer make on-the-fly changes to the design. The original schematic data is moved from Mentor Graphics' Neted editor into Vantage's SView schematic viewer. Once the schematic data is in SView, users can zoom and pan within the schematic, probe signals and make design changes without exiting the simulation. Vantage's net-list generator adds the changes to an existing net list, compiling only the new data that's added.

This ability to make rapid design changes makes the Vantage Spreadsheet analogous to the spreadsheets used for financial analysis. "Simulation is no longer a batch verification capability; it's a real-time tool," says Coelho. "We're predicting a one- to two-minute turnaround for most design changes. This capability could change the way designers feel about simulation."

Vantage's interactive capabilities

will attract many designers, although in the short run, VHDL is likely to be its strongest selling point. By supporting the full VHDL standard, the Vantage Spreadsheet permits a mix of behavioral- and gatelevel models. VHDL models are difficult to find, but as the standard becomes more widespread, a number of VHDL libraries should become available. Any model that conforms to the standard should run on the Vantage Spreadsheet.

VHDL doesn't currently support fault simulation, and neither does the Vantage Spreadsheet. That could pose a problem for military/aerospace companies, since they're the biggest consumers of fault simulation. The Vantage Spreadsheet also lacks an automatic worst-case timing verification capability, and the initial release doesn't support hardware modeling. But these limitations may be overshadowed by the simulator's interactivity and its complete support of VHDL.

## IF YOU'RE SPENDING TOO MUCH TIME ON SNA DESIGN, YOU'RE LEAVING OUT ONESTEP."

Most likely, if you need SNA compatibility, you'll buy the software source code from one company and hardware from another. Then you'll spend several months desperately working out the integration.

Or worse, you'll design it from scratch.

Systech knows you've got better things to do with your time. So we've created a way to cut down that lengthy process. With OneStep.<sup>TM</sup>

OneStep is a complete SNA/DCP board package. Which makes it the quickest and easiest off-the-shelf solution for IBM communication. In fact, with our help, the OneStep can be up-and-running in just five days.

To make this unique integration

work, we teamed up with the most reputable and experienced company in IBM compatibility around— Systems Strategies, Inc. With their superb emulation software and Systech's modular design, OneStep gives you the wide-area links you need for VME and Multibus systems. What's more, the OneStep takes a load off your CPU. That way, you have more power and improved system performance overall.

Systems Strategies, Inc.'s extensive variety of popular protocols includes SNA 3270, RJE and LU6.2. BSC 3270 and RJE. Plus, X.25 and QLLC. All thoroughly tested and successfully ported to Systech's hardware.

Along with easy installation, the

OneStep will keep your up-front costs down. And its modularity makes it easy to maintain and upgrade.

Most importantly, with the experience and expertise of Systech and Systems Strategies, Inc., you'll be in step with the latest software and hardware developments. And you'll always be OneStep ahead of the competition.

For a demonstration or more information, call Systech at (619) 453-8970. Or write: Systech Corp., 6465 Nancy Ridge Dr., San Diego, CA 92121.

SYSTECH WE OPEN UP A LOT OF POSSIBILITIES.

> OneStep is a trademark of Systech Corporation. CIRCLE NO. 16

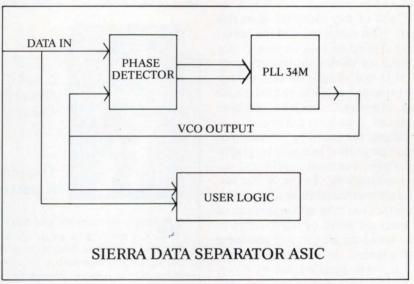

# PHASE LOCK LOOP. ANALOG/DIGITAL ASIC.

# NO ONE ELSE HAS THE COMBINATION.

System level designers can access new levels of integration designing products with a combination of advanced analog/digital circuitry on a single ASIC. Obtaining the smallest form factor, lowest power, and highest performance in data capture applications is now possible.

Consider our 34MHz Phase lock loop subsystem – the PLL34M – an ideal solution for data separators.

The PLL34M is an open loop phase lock subsystem containing a voltage controlled oscillator, digitally controlled charge pump, trimmable reference voltage, and high speed driver I/O circuitry.

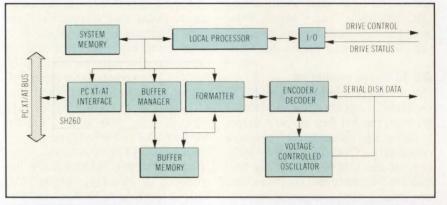

Combined with our other analog and digital standard cells, the PLL34M is ideal for increasing system integration of disk drive systems. (See application diagram.)

For designers seeking to incorporate analog processing functions, such as amplification, filtering, and data conversion, Sierra offers a wide range of solutions for applications in disk and tape drive systems, local area networks, and servo controllers. SIERRA integrates PLL onto a single data separator ASIC.

Lock into our CMOS standard cell library which includes over 250 digital standard cells, 50 analog standard cells, and 20 EEPROM standard cells. Our Triple Technology<sup>™</sup> gives you the flexibility to combine analog, digital, and E<sup>2</sup> on the same chip.

Sierra reduces packaging size and cost by offering low profile, surface mount packages including SOIC, PLCC, and PQFP Gull wing packages.

CMOS analog standard cells are available now in the same design environment as digital. Importantly, on-site mixed analog/digital simulation is easily achieved through access to our MIXsim<sup>™</sup> software tools, which verify design functionality and assure first time silicon success.

Access the unbeatable combination of analog/digital ASIC from Sierra. Lock into the latest data on our CMOS standard cell library and provide your customers with the most advanced products. Just write or call today for our complete library card.

#### Sierra Semiconductor Triple Technology. In CMOS.

2075 North Capitol Avenue, San Jose, California 95132. Telephone (408) 263-9300

#### Moderately parallel supercomputer avoids vector hardware

About 18 months after the separa-tion of Evans & Sutherland Computer (Salt Lake City, UT)-a leading vendor of high-end graphics, modeling and simulation products-into multiple divisions, the new computer division (Mountain View, CA) has revealed some details about its mission and its first product, which will see the light of day sometime later this year. "Our aim is to build the fastest general-purpose supercomputer optimized for solving the vast majority of high-end simulation and modeling problems encountered in science and industry," explains division president Jean-Yves Leclerc.

Despite the recent proliferation of supercomputers, minisupers, graphics supers, personal supers and superworkstations, Evans & Sutherland claims that all these alternatives are either too slow or too specialized to meet the needs of most complex, real-world simulation and modeling applications. As the company sees it, the overspecialization of Cray, Cray-like and mini-Cray-type machines lies in their vector orientation.

Vector processing has been the mainstay of supercomputing since the early 1970s-long enough, according to Evans & Sutherland, to firmly establish its limitations. "The key to attaining high performance in vector-processing supercomputers is the ability to vectorize the bulk of application code-say, 85 to 95 percent," says Leclerc. "But scientists and engineers have found that typically they're able to achieve this level of vectorization for only a handful of problems and in a narrow range of applications, and there's a significant performance penalty when a vector machine has to handle unvectorized code. As a result, the sustained performance rates of the machines average only 5 to 20 percent of the peak performance potential."

Evans & Sutherland has gathered an impressive array of user testimony on the vectorization problem.

David Lieberman Senior Editor The company cites, for example, studies conducted at the Los Alamos and Lawrence Livermore National Laboratories, which show that, on the average, the labs have been able to vectorize only 70 percent of their code. "Faced with this sobering assessment of where we stand after 10 years of vectorization, I'm beginning

to wonder whether vectorization has a substantial place in future supercomputer architectures," says Los Alamos spokesman Olaf Lubeck. He estimates that Cray machines used at Los Alamos achieve only 12 percent of their potential performance.

Leclerc admits, however, "Vector math is useful for such applications as weather mapping and fluid dynamics, where a data set is subdivided and a number of calculations

David C. Evans President Evans & Sutherland Computer

#### The push for interactive supercomputing

What's needed for the next giant step forward in scientific problem solving is a mix of raw horsepower, interaction and tightly coupled graphics. The driving force behind today's high-performance computing movement is the need of scientists and engineers to perform mathematical modeling: simulating with a computer the way complex processes or devices will behave in real life. The ability to model these phenomena with computer tools represents a qualitative leap forward in science and engineering—a leap that will have a major impact on every technical discipline from drug research to integrated circuit design. The potential benefits are enormous: faster time to market, reduced reliance on costly prototyping, better quality and, most importantly, the ability to solve previously unsolvable problems.

Through modeling and simulation, computers offer a much more efficient and productive alternative to conventional means of testing ideas and designs, such as manual calculation, experimentation and observation, or prototyping. Furthermore, computer-based modeling and simulation can provide the only practical way to test theories about problems beyond the scope of actual physical modeling or trials—problems raised in such diverse fields as astrophysics, cosmology and molecular dynamics.

Computer modeling and simulation has been the enabling factor for ground-breaking developments in a wide range of scientific and engineering fields, encouraging the vanguard of commercial suppliers to continually push out the bounds of visualization technology. Where chemists were once content to model molecules statically, they now want to view such simulations in real time, interactively manipulating data and watching the results. And where mechanical engineers have modeled individual parts of larger systems, they now want to simulate entire large-scale, supercomplex systems under dynamic real-world conditions and interactively adjust design parameters. Interactive modeling and simulation lets the user visualize the results of complex calculations, make intuitive judgments during processing and perform modifications to programs on the fly. The more interactive the dialog between man and machine, the more intuition, human judgment and experience can become an integral part of the computational process.

# A new direction in interconnection technology.

1237

1231

1243

1758

I114

1558

1739

1303

1214

1208

Concerned about crosstalk? Critical length? Not enough packaging density?

Diagonal Wiring can solve such problems, and Hitachi Chemical routinely uses this space age technique on a multitude of down to earth configurations.

1218

1170

1251

1249

1171

1555

8521

1332

1217

I211

IZ1

1708

Ŋ

High density, 45° diagonal polyimide insulated wiring reduces parallel lengths of critical conductors and decreases point to point routing distance. This minimizes crosstalk, facilitates critical length considerations, isolates special logic families like ECL, and greatly increases packing density. Multiwire® interconnection technology also makes controlled impedance easy.

Let us help you with your next board design. Hitachi offers a different angle with Multiwire interconnection boards including SMT and the latest trends.

#### HITACHI CHEMICAL COMPANY AMERICA LTD.

Sales Offices: 3469 Lawrenceville Hwy. Suite 205 Tucker, GA 30085 (404) 938-9388 420 Lexington Ave. New York, NY 10170 1-800-227-1529 4141 Blue Lake Circle Dallas, TX 75234 (214) 960-9675 1333 Lawrence Expwy. Santa Clara, CA 95051 (408) 244-2570 2000 West Park Drive Westborough, MA 01581 (617) 366-4092

1205

1734

1735

1333

1736

200

1551

1727

1302

1733

N

N

ES

NA

25

20

Multiwire® is a registered U.S. trademark of the Kollmorgen Corp.

CIRCLE NO. 18

are applied uniformly to each section." The architecture of the coming Evans & Sutherland machine, thus, will provide for high-speed vector-type processing as well as scalar power but won't use dedicated vector hardware to balance its Mips/ MFlops performance.

Evans & Sutherland's machines will consist of two to eight processors, each with 16 computational units. Each of these units can run an application on its own or with other computational units, or it can manage a segment of an application that has been parallelized and assigned to multiple units. Each computational unit contains three functional units: one for handling floating-point adds, one for floating-point multiplies and one for integer operations. "This approach will let the machine provide a high number of both Mips and MFlops without actually using vector-processing hardware," says Leclerc. The range of expected machine configurations will deliver from 300 Mips/MFlops to over 1 Gips/GFlops. Pricing will be from \$3 million to \$8 million.

While it's clear that the ability to assign tasks to the computational units as befits the application provides for a lot of flexibility, Evans & Sutherland has yet to explain the architectural wrinkles that will manage the overall process. The heart of the system, though, will be three types of semicustom CMOS VLSI chips residing in 340-pin packages and configured in six-chip sets. The system will include a large shared memory (256 Mbytes per processor) and will provide a 10-Gbyte/s I/O bandwidth between computational units. It will be, as one might expect, a highly pipelined machine that, when desired, can be moderately parallel.

#### Against the grain

Evans & Sutherland has a second major objection to vectorization, which it perceives as a form of finegrain parallelism. In both vector machines and the so-called massively parallel computers, restructuring existing code to take advantage of finegrain parallelism and, hence, get the most out of the machines is a difficult and time-consuming chore, and one that's often beyond the programming expertise of the ultimate user, claims Leclerc. "Machines with the power for complex problems-such as Cray-type vector machines and massively parallel machines-are of limited, special-purpose use due to the magnitude of programming effort required to tap their power," he says. Evans & Sutherland, therefore,

has opted to implement only very

high-level, coarse-grain parallelism in its new machines. "That doesn't require going deeply into the fundamental structure of existing code,' Leclerc explains. Taking advantage of the machine's parallelism still requires conversion of a small amount of code, however, But, Leclerc says, "The conversion is much more intuitive because it takes place logically at a higher, more natural level for the application, using larger portions of the existing code." By the time the machines are introduced, an application development environment will be available to aid in parallel programming.

The Evans & Sutherland machines will use an operating system based on Unix 4.3 BSD with Mach extensions. Optimizing C and Fortran compilers will also be available, as will an object-code generation facility, a source language debugger, performance profilers and other development tools. "Scientists and engineers shouldn't be required to understand the details of computer science to vectorize programs at the lowest level of parallelism," comments Leclerc. "Rather, they should define the high-level modules of the natural parallelism within the application and then let development tools implement the computer science part of the problem." CD

#### **Peripherals and Memory Systems**

#### **Erasable optical drives ready** to move in on Winchester turf

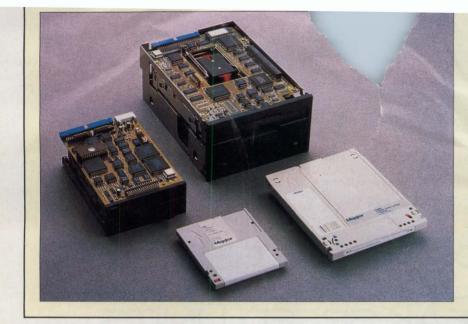

A family of erasable optical disk Adrives with removable media is poised to challenge the performance of mid-range Winchesters while at the same time topping the capacity of high-end hard disks. The first members of the line from Maxtor (San Jose, CA) are Tahiti I, a 5<sup>1</sup>/<sub>4</sub>-in.

**Tom Williams** Western Managing Editor drive offering up to 600 Mbytes of on-line total storage, and Fiji I, a 3<sup>1</sup>/<sub>2</sub>-in. drive with 160 Mbytes of online unformatted storage. Average seek times for the two drives are 30 and 100 ms, respectively. Tahiti I's data transfer rate of 10 Mbits/s is comparable to rates found on many Winchester drives. Fiji I has a data transfer rate of 1.9 Mbits/s.

The capacities are quoted as for-

matted or unformatted, depending on whether a drive's small computer system interface (SCSI) controller is embedded or separate. The controller on the 5<sup>1</sup>/<sub>4</sub>-in. drive is embedded on the drive, while the 3<sup>1</sup>/<sub>2</sub>-in. drive has a separate SCSI controller, making it easy for designers to integrate different controllers and data formats. One recommended use for the Fiji I is as a floppy replacement for backup in laptop systems. Its capacity has been tailored such that it can back up a full disk of Maxtor's 170-Mbyte (unformatted) 31/2-in. Winchester drive.

#### IN VANCOUVER, WASHINGTON, WE'VE JUST ISSUED PERMITS TO BREAK SPEED LIMITS.

How do you keep ninety of the country's hottest design engineers

happy? First, give them permission to pull out all the Sharp's new LH52252 64k x 4 SRAM high-speed

stops. Then give them a place to do it.

That's exactly what we've done at our new Sharp Microelectronics Technology Center in Vancouver, Washington. There we've provided our outstanding staff with the most advanced CAD systems available. And we've backed them with a world-class 1.2 micron production facility in Japan, along with a national network of salespeople and distributors.

selves by creating a select line of

chips. Like the new

Sharp LH52252, our

64k x 4 SRAM that operates at 35 ns cycle time and consumes just 100 microamps in standby mode. It's the first of many high per-

formance products you can expect from our new design center. And it's available right

now at Marshall, Milgray, Western Microtechnology, Space Electronics, and Added Value.

If you have specific questions, we invite you to call Sharp at (201) 529-8757. Especially if moving at 35 ns or faster

| SHARP'S NEW HIGH-SPEED CMOS SRAMS |              |                    |              |  |  |  |

|-----------------------------------|--------------|--------------------|--------------|--|--|--|

| DEVICE#                           | ORGANIZATION | ACCESS TIME        | AVAILABILITY |  |  |  |

| LH52252                           | 64k x 4      | 35 ns/45 ns/55 ns  | Immediate    |  |  |  |

| LH52259                           | 32k x 9      | 35 ns/45 ns/55 ns  | 3Q 1988      |  |  |  |

| LH52251                           | 256k x 1     | 35 ns/45 ns/55 ns  | 3Q 1988      |  |  |  |

| LH52256                           | 32k x 8      | 70 ns/90 ns/120 ns | Immediate    |  |  |  |

| LH5261                            | 64k x 1      | 25 ns/35 ns        | 1Q 1989      |  |  |  |

| LH5262                            | 16k x 4      | 25 ns/35 ns        | 4Q 1988      |  |  |  |

sounds appealing. Because if you like breaking speed limits, Sharp has just the ticket.

IF IT'S SHARP. IT'S CUTTING EDGE." © 1988 Sharp Electronics Corporation, Sharp Plaza, Mahwah, N.J. 07430.

CIRCLE NO. 19

ELECTRONIC COMPONENTS DIVISION

Two drives from Maxtor's erasable optical disk drive family have attained Winchester-class performance. The 5<sup>1</sup>/<sub>4</sub>-in. Tahiti I provides 1 Gbyte of formatted data storage as well as seek times of less than 30 ms. Fiji I is a low-cost-per-Mbyte 3<sup>1</sup>/<sub>2</sub>-in. drive that provides 160 Mbytes of storage and an average seek time of 100 ms. Both drives use removable media and feature the small computer system interface.

According to Skip Killsdonk, vicepresident of marketing at Maxtor, the two drives represent an advance in that they have caught up with Winchester-class performance. Optical drives have long been characterized by slower seek times and data transfer rates due to the mass of laser heads and the time needed to deliver enough laser energy to the media to write data. Apparently, Maxtor has sufficiently finessed the parameters to approach low- to midrange hard disk performance in its 5¼-in. offering.

Erasable optical recording uses magneto-optic technology: the heat of a laser beam is used to orient the magnetic polarization of the media to that of an ambient magnetic field. The polarity of the media then affects the polarization of an incipient laser read beam, thus determining whether a spot on the disk is a one or a zero. This means that to write a track on the disk, the track must first be erased by switching the ambient field coil to zero polarity and writing all bits, which become zero. Then the field coil is switched to one polarity for the write operation, and the laser is turned on for only those bits that are to be written as ones. Magneto-optic technology, therefore, will always write more slowly than comparable Winchester technology because it takes two revolutions to do a write. Read operations, however, don't have this restriction.

#### **Media options**

The 51/4-in. Tahiti I has taken advantage of the intelligence that can be built into an embedded SCSI controller to offer a range of media options. Not only can users set the sectors at either 1,024 bytes or 512 bytes per sector, but they can also choose between an ANSI standard cartridge (for easy portability between drives of different manufacturers) and a special higher-capacity media cartridge. The standard cartridge offers a 600-Mbyte (300 per side) capacity, while the special higher-capacity media cartridge developed by Maxtor offers a 1-Gbyte (500 Mbytes per side) capacity.

The higher capacity is achieved by formatting the disk for zoned, or constant density, recording. Zoned recording takes advantage of the fact that the outer tracks of a disk have more linear room for data than the inner tracks. In the past, linear bit densities have been limited by the capacity of the inner tracks, which also have the highest linear velocity and, hence, the highest data rate. Intelligent buffers on the SCSI controller let a drive vary the data rate of the read/write channel and match that rate to the constant data transfer rate of the host interface. Thus, as one moves out from the center, each time a track is able to accommodate an additional full sector, one is added and the data rate increases accordingly. With this method, Maxtor has managed to achieve a 40 percent capacity increase.

According to Killsdonk, the 5<sup>1</sup>/<sub>4</sub>in. Tahiti I will find a home in such applications for storing drawings as desktop CAD stations and network file servers as well as in image archiving systems. The security advantages of removable cartridges will be a plus, as will be the fact that removable media effectively increases the overall capacity of a drive, if not the instant availability of that capacity.

Despite the power demands of the motor and the actuator and the additional need for the field coil, maximum power consumption for the two drives is quoted as 35 W for Tahiti I and 17 W for Fiji I. Both drives are expected to begin shipping early this fall, with volume pricing around \$2,500 for the 5<sup>1</sup>/<sub>4</sub>-in. drive and less than \$1,000 for the 3<sup>1</sup>/<sub>2</sub>-in. drive. Volume prices for media for the 5<sup>1</sup>/<sub>4</sub>-in. Tahiti I and the 3<sup>1</sup>/<sub>2</sub>-in. Fiji I are \$175 and \$49, respectively.

# Militarized VMEbus Solutions...

# From Clouds Above, to Fathoms Below

Field-proven VMEbus systems are the preferred choice.

CIRCLE NO. 50

# VMEbus System Solutions...

#### Chosen for many good reasons.

High performance, industry standard, multiprocessing architectures, applicable to Mil-Spec applications, field-proven ... DY-4's VME solutions satisfy the most stringent performance issues, regardless of the environment.

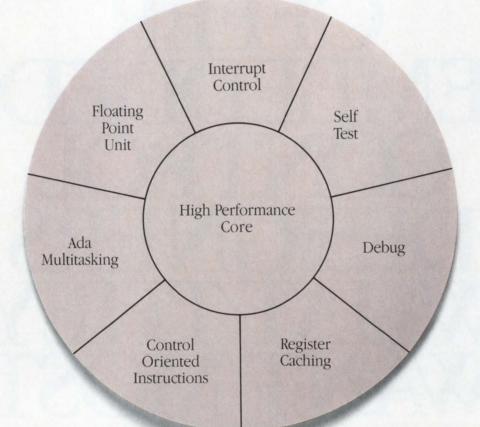

DY-4, a leader in Mil-Spec VME system solutions provides you with more than high-performance boards. We understand the specialized needs of mission-critical programs. Our products are many — boards, chassis, system-level diagnostics, RTOS, and application software supported by program management, ILS, QA, configuration management and proposal support.