A PENNWELL PUBLICATION

COMPUTER OCTOBER 1, 1988

THE FIRST MAGAZINE OF SYSTEM DESIGN, DEVELOPMENT AND INTEGRATION

ASIC memories: bigger, faster, and customized

> Innovative packages emerge to carry faster, denser chips Page 35

PHI

Automated optimization refines SIMD microcode Page 67 Linear power supplies survive in low-power applications Page 100

ALL DE LE DE

# This year, you'll hear a lot of claims that "systems" design automation has arrived.

## At Mentor Graphics, we know better. And so do our customers.

#### They preach. We practice.

Skeptical about "systems" electronic design automation?

You should be. Because in many cases, it's a triumph of form over content. In the end, there's only one practical yardstick for evaluating a systems design solution. And that's how many successful products it has produced.

Apply this measure and the field narrows dramatically. Essentially, down to a single vendor.

Mentor Graphics.

For over five years, our customers have been turning out sophisticated board products with our EDA tool set.

#### Test their claims.

Here are some interesting (and essential) questions that you should ask any potential EDA vendor:

Does your tool set have a common

ics, database and user interface? Does it extend from design definition through to PCB layout and output to manufacturing?

Do you have more ASIC libraries supported on your workstation than any other EDA vendor? Can you include ASICs in board simulations?

Are your tools capable of managing over 1000-page product documentation projects from start to finish?

Have you integrated mechanical packaging and analysis into the electronic design and layout process?

Anything less than a perfect score is a total loss. And a perfect score does not mean just a check in every box. Each item must be backed with the production-proven performance only Mentor Graphics can provide.

## Experience makes the difference.

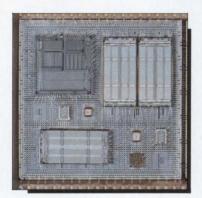

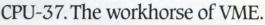

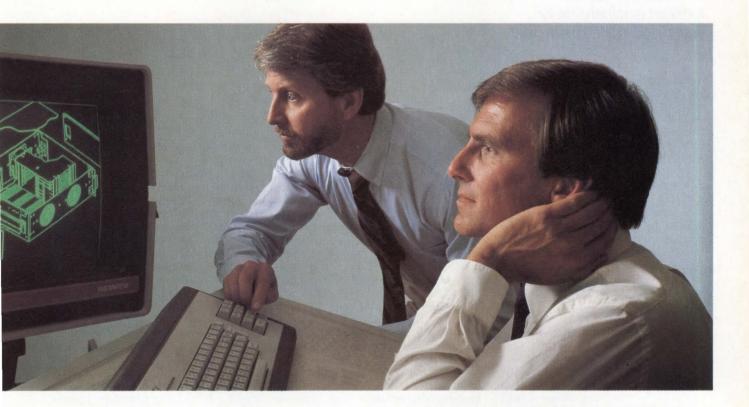

When we speak about systems design automation, we speak from experience. We have the largest customer base in the electronic design automation industry. And with good This 32-bit processor board was designed and simulated on **Mentor Graphics** workstations by Sequent Computer Systems for its multi-processor Symmetry computer system. It contains over 175 IC components including 80386 processors, a 14,000gate standard cell and two 10,000gate arrays.

reason. Over 70% are repeat customers who've realized genuine value added from our products and seek to expand their competitive advantage.

It's all part of a vision unique to Mentor Graphics, the leader in electronic design automation. Let us

show you where this vision can take you.

Call us toll-free for an overview brochure and the number of your nearest sales office. Phone 1-800-547-7390. (In Oregon, call 284-7357).

Yourideas. Our experience.

## The VME Volksclosure. \$995. Ready to Run.

Finally. The economies of mass production catch up with VME and Multibus II enclosures.

Introducing the Volksclosure, Electronic Solutions' economy model enclosure with turbo performance. All you do is add cards and peripherals for a complete, attractive desktop computer.

With the Volksclosure (also known as our Model One) everything comes standard: six VME or Multibus II slots, space for three half-height 5¼" disk drives, and a high-performance six-layer backplane all in a highly tooled enclosure with our handsome front panel that hides those ugly connectors and cables.

You do get a choice between two multiple-output power supplies: 190 Watts with 19A at + 5V or 270 Watts with 30A at + 5V. You can also choose a J2 backplane for VME extended addressing or iLBX II for a Multibus II system. Most important, while the Volksclosure costs less, you

> don't get less. It fully reflects Electronic Solutions' commitment to quality and performance. For example, it meets UL and CSA

safety standards and FCC Class A EMI/RFI specs to the letter. The New Volksclosure. Ho

The New Volksclosure. How to get a lot more mileage from your packaging budget. Call right now for complete details.

### We'll FAX you the facts

Want the latest data in a hurry? Nothing is faster than Electronic Solutions' new "FAX the FACTS" program. If you have a FAX machine, just call our "800" number, give us your FAX number and type of FAX machine, and the information you need from us. We'll FAX it to you immediately.

6790 Flanders Drive, San Diego, CA 92121 · (619) 452-9333 Telex II(TWX): 910-335-1169 Call Toll Free: (800)854-7086 In Calif: (800)772-7086

CIRCLE NO. 2

Today, this memory card will travel 15,000 miles, perform massive data collection, transfer data to a central data file and...

### do it all before being tucked safely away for the night.

Now, with Mitsubishi's transportable memory cards, you can have the flexibility of carrying 32K Bytes to 2M Bytes of SRAM, OTPROM or masked ROM in your pocket. That means read/ write capability (without a disk drive), remote from central data storage, plus the flexibility to interchange memory types

(SRAM, OTPROM, masked ROM), upgrade and downgrade memory density, and change data width (8 bits, 16 bits). All with an extremely rugged device that's the size of a credit card (86mm x 54mm x 3.4mm).

#### The Applications Are Virtually Endless.

From personal computers to printers, portable equipment to telecommunications, the applications are as creative and endless as the imagination. Anywhere transportable memory and massive data storage are required, Mitsubishi's transportable cards offer the highest memory densities available on a device this small.

#### Save On Systems Design Costs.

Mitsubishi's transportable memory cards offer standardized card connectors and pin assignments for easy memory interchange and density upgrade, without designing multiple host system models. Plus, future system redesign is simplified or eliminated.

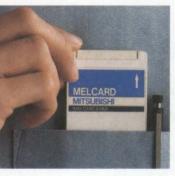

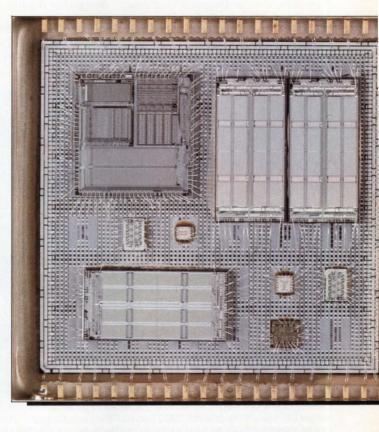

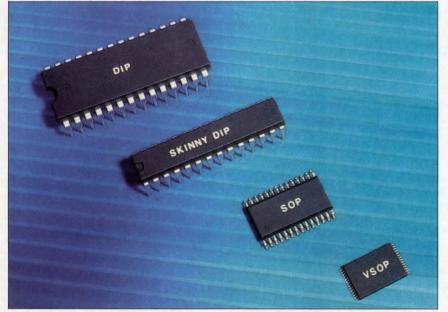

#### **Extremely High Density Memory.**

The key to Mitsubishi's extremely high density memory cards is the VSOP (very-small-outlinepackage). Pioneered by Mitsubishi, the VSOP is over four times smaller (in overall volume) than its equivalent pin

count, standard surface mount package. In fact, the VSOP is smaller than the footprint of the equivalent chip-on-board technology making it possible to pack up to 16 memory ICs, plus standard interface circuitry on one card.

#### "Transportable" Means "Rugged."

Mitsubishi designed its memory cards specifically for transportable applications. And, that means cards that are rugged and reliable. Even if a card is dropped, loss of valuable data is virtually eliminated, due to Mitsubishi's flexible, four-layer PCB and enhanced soldering techniques.

Additionally, the cards are ESD protected to 25K volts, with connectors guaranteed for 10,000 insertions.

If you want to design-in massive, transportable data storage with the flexibility to interchange memory types and densities, Mitsubishi memory cards give you the maximum memory mileage. For more information call or write today: Mitsubishi Electronics America, Inc., Semiconductor Division, 1050 East Arques Avenue, Sunnyvale, CA 94086. (408) 730-5900.

### Quality Through Commitment.

Regional Offices:

SOUTH CENTRAL, Carrollton, TX (214) 484-1919

NEW ENGLAND, Woburn, MA (617) 938-1220

NORTHWEST, Sunnyvale, CA (408) 730-5900

NORTHERN, Minnetonka, MN (612) 938-7779

MID-ATLANTIC, Piscataway, NJ (201) 981-1001

SOUTHWEST, Torrance, CA (213) 515-3993

NORTH CENTRAL, Mt. Prospect, IL (312) 298-9223

SOUTH ATLANTIC, Norcross, GA (404) 368-4850

OUTHEAST, Boca Raton, FL (407) 487-CANADA, St. Laurent, Quebec, (514) 337-6046

THE FIRST MAGAZINE OF SYSTEM DESIGN, DEVELOPMENT AND INTEGRATION

Page 20

#### TECHNOLOGY UPDATES

#### Software

Software machine model blazes trail for parallel processing ......20

#### The Bus Platform

Industry leaders speak out on the critical issues facing designers of openarchitecture computers, including the three R's—RISC, real-time computing and real interconnectivity ......83

#### **Product Debuts**

A preview of the products in the spotlight at Buscon/88-East ......92

Page 35

#### TECHNOLOGY AND DESIGN FEATURES

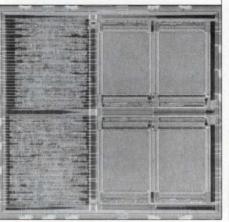

#### COVER STORY ASIC memories: bigger, faster, and customized

The goal? Develop super-performing specialty memories. The strategy?

#### Automated optimization refines SIMD microcode for efficient programming

Page 100

#### NEW PRODUCT HIGHLIGHTS

#### **PRODUCT FOCUS**

Linear power supplies survive in low-power applications ......100

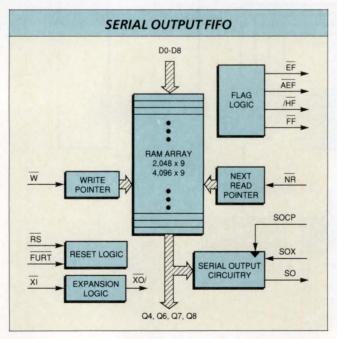

#### Integrated Circuits Bidirectional FIFO eases data exchange, enhancing system throughput ......108

####

#### DEPARTMENTS/COLUMNS

| News Briefs9                 |

|------------------------------|

| Editorial14                  |

| New Products Index112        |

| Advertisers Index113         |

| Calendar114                  |

| Design for Testability116    |

| Technology Market Directions |

| Literature                   |

|                              |

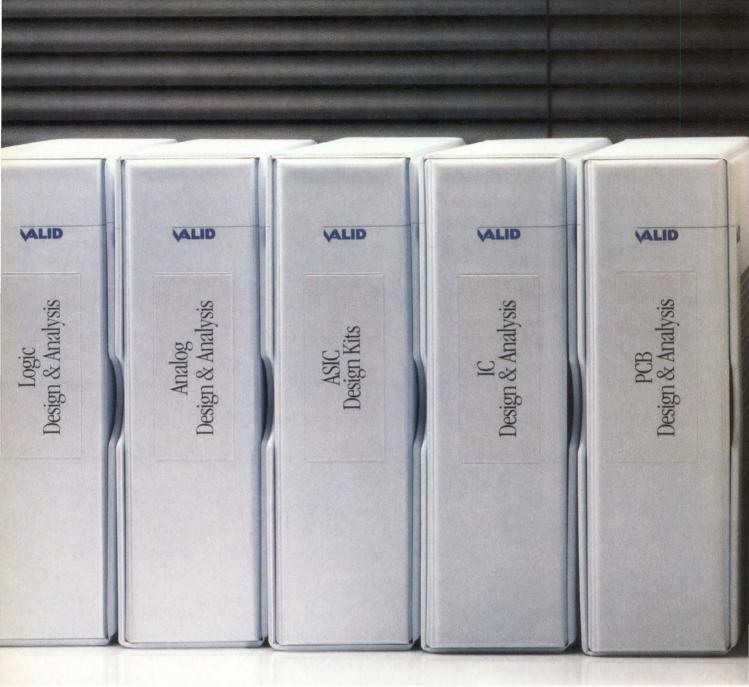

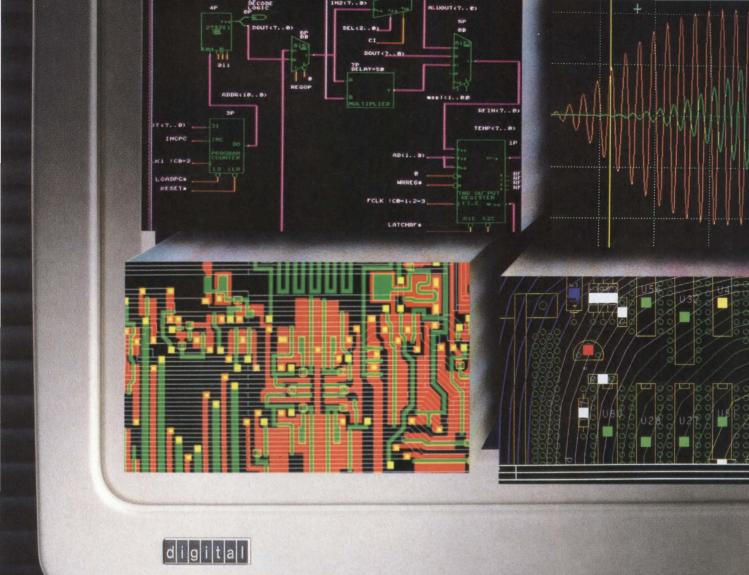

## The Best Tools

digital VAX station 3200

Now Experience Electronic Design As It Was Meant To Be With The New Digital VAXstation<sup>™</sup> 3000 Series, And The Full Line Of Valid CAE/CAD Software.

From Digital Equipment Corpora-

tion and Valid comes the ideal combination for Electronic Design Automation. A dynamic system you need to tackle today's critical design demands.

It all begins with the powerful new VAXstation 3000 Series of workstations from Digital. The VAXstation 3000 offers you incredible performance and high-speed graphics in a package suited perfectly for Electronic Design.

Next comes the full line of Valid state-of-the-art software to address even your toughest Design needs. Included are tools for digital and analog design and analysis. As well as design and analysis for ICs and PCBs. Plus documentation and links to test, and mechanical CAE.

Digital and Valid are able to bring you this synergy through the use of industry standards. Like the Ethernet<sup>™</sup> network with DECnet<sup>™</sup>, TCP/IP protocols, which let your entire design team work together in unison. And VMS<sup>™</sup>

# For The Job.

operating system that allows Valid software to run on all VAXstations and VAX computers.

#### Working together makes the difference.

Digital and Valid products work cooperatively to ensure that your people can work more productively, more creatively, and more efficiently. This offers you the benefits of a customized solution that integrates applications, hardware, networking, and support services — providing you with a key competitive edge in meeting your engineering design needs. The right people with the right tools working together. Digital, Valid, and You. To find out how Electronic Design was truly meant to be with customized application, hardware, networking and support services from industry leaders, call 1-800-821-9441 (outside CA), or 408-432-9400 ext. 2311 (inside CA), or your nearest Digital or Valid Sales Office.

© 1988 Valid Logic Systems, Digital Equipment Corporation. Valid is a trademark of Valid Logic Systems. Digital logo, VAXstation, VAX, VMS and DECnet are trademarks of Digital Equipment Corporation. Other brands or product names are trademarks of their respective holders. 42,000 dhrystones with a <u>single</u> 32-bit RISC chip. Sustained. Seventeen MIPS. Real world MIPS. 25Mhz clock speed. Fifty MIPS by 1991. Blazing fast even with lowcost memory. 5x the system throughput of the 68030. 2x the 80960 at half the system cost. In CMOS. On the shelf. Now.

## Advanced Micro Devices' 29K. The next platform.

Call toll-free (800) 222-9323. Advanced Micro Devices, Inc., 901 Thompson Place, P.O. Box 3453, Sunnyvale, CA 94088. 29K logo is a trademark of Advanced Micro Devices, Inc. © Advanced Micro Devices, Inc. 1988.

CIRCLE NO. 5

## WRITING MICROCODE ISN'T CHILD'S PLAY...

## But We Just Made It A Whole Lot Easier!

The speed and flexibility available from microcode architectures carry a price which must be paid by designers—complexity. But even complexity can be moderated with the right tools, and HILEVEL has them.

We've designed an array of microcode development systems and software to suit projects ranging from simple device controllers to complex real-time radar processors.

Write your programs in C using our new, reconfigurable crosscompiler, or use our meta-assembler

to write time-critical programs in assembly code. Modules from either can be linked together, and there is a comprehensive source code editor and disassembler to simplify integration and debugging.

To support your hardware, we offer the only control-store emulator with memory in its pods. This dramatically improves access times. But more important, the memory configuration is determined in software. Now you can use this system for a variety of projects, with control stores up to 512 bits x 64K, without replacing pods or other hardware.

You can monitor all critical activity up to 256 bits at full speed, using the logic state analyzer in the development system. And, our performance measurement features will even help you find ways of improving your design.

Don't make your project more difficult than it has to be. Call HILEVEL today and let us show you how writing microcode just became easier!

DIAL TOLL FREE: 1-800-HILEVEL In California, 1-800-541-ASIC

At The Leading Edge Of Microcode Development

31 Technology Drive Irvine, CA 92718 (714) 727-2100

CIRCLE NO. 6 FOR DEMONSTRATION CIRCLE NO. 65 FOR LITERATURE

©Copyright 1988, HILEVEL Technology, Inc.

## NEWS BRIEFS NEWS BRIEFS NEWS BRIEFS NEWS E

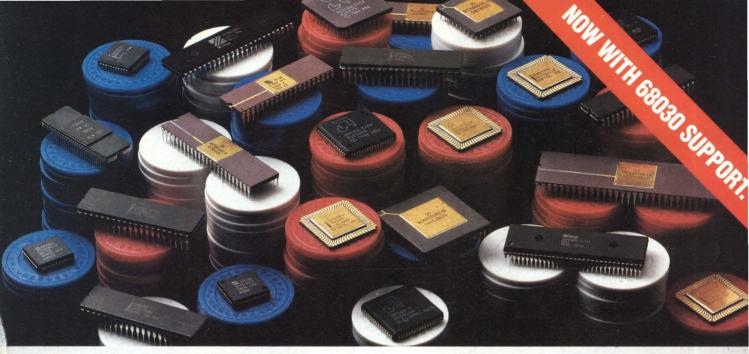

## Apple beats competition with 68030-based system

Despite the hoopla surrounding RISC-based processors, expectations have been building that Motorola's latest generation CISC processor will begin to appear in popular personal computer and workstation configurations. Steve Jobs' company, Next (Palo Alto, CA), is reportedly planning a 68030based workstation for introduction at Comdex Fall in November, and Sun Microsystems (Mountain View, CA) is also rumored to have a system in the works.

But the first and potentially biggest splash has come from Apple Computer (Palo Alto, CA). Apple has unleashed the Macintosh IIx, a machine built around a 16-MHz 68030 and a 68882 floating-point processor. The new system executes most applications about 15 percent faster than the older 68020-based Macintosh II. Using a NuBus architecture much like the Mac II, the IIx offers six expansion slots and 4 Mbytes of on-board RAM. Only time will tell how the supercharged Mac IIx will fare when competing against Unix-based engineering workstations. Such a direct challenge to Sun and Apollo may force Apple to face issues regarding operating system, networking, system support and application software. from which the company has been shielded in the personal computing market.-John Mayer

#### Consortium challenges the Micro Channel

A consortium of more than 60 companies involved in manufacturing personal computers, mainframes, peripherals and software, including such giants as Compaq, Epson America, Hewlett-Packard, NEC Information Systems, Tandy and Zenith, has announced a direct challenge to the IBM Personal System/2 Micro Channel bus. Claiming that the Micro Channel hasn't been accepted in the PC market, the group has made a commitment to develop and use a new 32-bit PC bus structure, called the Extended Industry Standard Architecture, or EISA.

The new bus will provide the appropriate bandwidth for 32-bit CPUs, but will retain compatibility with existing PC/AT-bus cards. Amid growing concern about IBM PS/2 sales, increasing criticism of the OS/2 operating system and emerging challenges from the Macintosh family and 80386-based Unix workstations, the announcement casts grave doubts on IBM's ability to sustain its PS/2 strategy. But for the PC option card developer, the announcement may only add further uncertainty to an already risk-laden decision: which buses to support, and how many? -Ron Wilson

#### Motorola and Cypress square off over new RISC venture

Motorola Semiconductor (Austin, TX) has been granted a temporary restraining order that will bar five ex-Motorola employees, including Roger Ross and four other key members of the 88000 introduction team, from participating in the planning or development of "any semiconductor devices," pending an October hearing. The five left Motorola to form Ross Technology, a consulting firm involved in designs built around Sun Microsystems' Sparc (Scalable Processor Architecture). Cypress Semiconductor (San Jose, CA) has provided some funds to Ross Technology, and the two companies are said to be discussing licensing and foundry agreements.

Motorola's suit charges that Cypress conspired with members of the 88000 design and marketing teams to bring about the formation of Ross Technology. The suit seeks to bar the departed employees from entering Motorola's area of business, and asks for \$8 million in damages from the ex-employees and Cypress. Following closely on suits regarding trade secrets and patent infringement from National Semiconductor and Advanced Micro Devices, the Motorola action leaves Cypress facing three major legal actions at once.—Ron Wilson

#### **Backing into the future**

With the introduction of the Personal System/2 Model 30 286, IBM (Armonk, NY) has reentered the AT market that it created and then abandoned. In April 1987, IBM claimed that it was replacing the AT architecture with the PS/2 Micro Channel bus because it offered advanced features such as multiprocessing and automatic system configuration. This move signaled the cloners to jump into the lucrative AT market and offer enhancements such as 80386 processors and increased memory speed, which dampened enthusiasm for the PS/2.

IBM's "new" Model 30 286 will be based on the Intel 80286 microprocessor but will use an impressively streamlined mother board, thanks to a five-chip logic set developed by VLSI Technology (San Jose, CA) that will reduce the chip count to about 17 percent of a standard AT's 88 ICs. The 10-MHz system will use the DOS 4.0 operating system and support up to 16 Mbytes of memory.—Michael Donlin

## Laptops offered first 2½-in. Winchester disk drive

The pieces for low-cost, highperformance laptops continue to fall into place. Flat-panel display manufacturers are finally developing displays with high resolutions at lower prices. Now a disk drive manufacturer is introducing a significant space savings in disk storage. Prairie Tek (Longmont, CO) has unveiled the first 21/2-in. hard disk drive for laptops. Occupying just 30 percent of the volume of a standard 3½-in. drive and weighing a featherlike 9 oz, the 1-in.-high Prairie 220 packs 20 Mbytes and an AT-compatible or SCSI controller into its compact footprint. Average seek time is a respectable 28 ms, and power consumption averages 1.5 W. That's a 25 percent improvement in power usage over the lowprofile 3<sup>1</sup>/<sub>2</sub>-in. Winchesters available from Conner Peripherals (San Jose, CA) and Seagate (Scotts Valley, CA).

The success of the Prairie Tek

(continued on page 10)

## **NEWS BRIEFS NEWS BRIEFS NEWS BRIEFS NEWS B**

drive will hinge on its ability to hurdle two obstacles: convincing the industry to follow the company to the new 2½-in, format and making sure the drive proves to be reliable. Prairie Tek is attempting to address the reliability issue with a couple of design innovations. A unique ramploading mechanism ensures that during an unintentional powerdown the disk heads are safely unloaded and locked on the ramp structure. The design helps eliminate stiction, a common mode of failure for plated media drives. The company claims that its drive will withstand a 100-g force at 11 ms in a nonoperating environment. Adding to the drive's reliability is an actuator roughly one-half the mass of a typical coil actuator on a 3½-in. drive.-John Mayer

#### Imaging and neural nets to jointly attack machine-vision problem

For years, companies in the imageprocessing arena have tried to solve the problem of machine vision, with varying and less-than-satisfactory results. Imaging systems have been very good at enhancing image quality and extracting important features for the recognition process. But they've failed in establishing sets of rules by which objects can be recognized, and they've generally been limited to template-matching techniques, which limit the vision process to a very small subset of problems.

Now, however, two imaging companies, Datacube (Peabody, MA) and Imaging Technology (Woburn, MA), have joined forces with a neural network company, Nestor (Providence, RI). The Nestor Development System neural network software can be used to create intelligent pattern-recognition systems that can learn to recognize images presented to them by example rather than trying to classify them according to a set of rules dictated by a programmer. The imaging equipment will enhance and filter images to present a set of features on which the system can base its recognition decisions.—Tom Williams

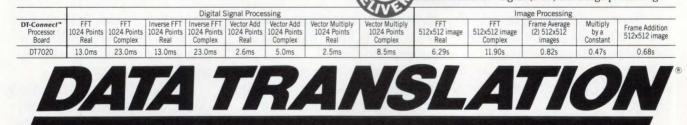

#### Board maker doubles as vendor of Micro Channel ASICs

Forced to design its own applicationspecific IC to overcome the size constraints of its Personal System/2 board, which is 38 percent smaller than the IBM PC AT boards it had been designing for several years, Data Translation (Marlboro, MA) now has decided to market the device to other board manufacturers. A complete Micro Channel controller for either memory or I/O adapters, this CMOS ASIC also helps to overcome the limited power that's available per expansion slot for the PS/2.

The device will support multifunction I/O controllers, programmable option select, two DMA channels for multifunction interfaces, simultaneous dual controllers (either input or output or both), and continuous data transfers across DMA block boundaries. It meets all IBM-specified timing and drive specifications. Although designed for 84-pin plastic leaded chip carrier sockets, the ASIC can also be used in surface applications so that users will be able to inventory only one chip for both interface board designs.—Sydney Shapiro

#### IBM to employ Next's user interface

IBM has reportedly licensed a user interface system from Steve Jobs' company, Next (Palo Alto, CA), for use on a forthcoming version of the RT PC RISC-based Unix workstation. The interface software was developed by Next for use in its asvet-unfinished 68030-based desktop computer, running under the Unixlike Mach operating system. IBM will presumably use the interface design to construct a user-friendly front-end for its new RISC workstation, which is reportedly taking shape under the guidance of RISC pioneer John Cocke at the company's Austin, TX facility. If nothing else, the agreement, with its reported \$10 million in licensing fees to cash-hungry Next, should temper Jobs' renowned hostility toward IBM for a while.-Ron Wilson

## Intel moves Multibus II to system level

At Buscon East this week, Intel (Hillsboro, OR) will introduce an extension of its Multibus II board architectural concept for system-level architectures The Multibus II Systems Architecture (MSA) is intended not only to make it easier for designers to implement Multibus II board-based systems, but also to make the architecture available to other vendors for incorporation into their boards or firmware. MSA is also expected to help overcome the multiprocessing overhead burden inherent in some complex systems.

But not to ignore Multibus I, Intel will also introduce a second-generation series of 16- and 20-MHz, 80386-based CPU boards, several I/O boards, and additional packaging. In addition, the company will introduce a graphics subsystem that can be used in a real-time system without degrading system performance. Intel will also announce expanded networking options across the company's entire product line.—Sydney Shapiro

#### Graphics interface targets multitasking, real-time systems

Applications developers for multitasking, real-time systems now have a graphics interface based on the popular Gem Application Program Interface. Digital Research (Monterey, CA) will unite its Gem graphics development toolkit with its FlexOS real-time target operating system to provide sophisticated automation graphics for multitasking systems "We'll do it without jeapordizing performance from a real-time perspective," claims Frank Iverson, vice-president for worldwide marketing. The multitasking version of Gem, called XGem, will be 100 percent compatible with existing Gem applications. The interface has already been submitted to the Open System Foundation (OSF) for consideration as the standard user environment for **OSF's Application Environment** Specification.-John Mayer

The P-CAD Software That Made This Famous Laptop Computer Is Now Made To Fit Your Budget.

When Zenith Data Systems needed to pack power into their laptop computers they turned to P-CAD<sup>®</sup>'s Master Designer <sup>™</sup> printed circuit board software.

Why? Because only Master Designer was powerful enough to meet their tough requirements.

Today, the same software used by Zenith Data Systems and over 10,000 others is available to PCB designers everywhere. Modular software that costs about half what you'd expect.

For starters, Master Designer's schematic capture and interactive layout lets you design using the latest through-hole and surface mount technologies.

Master Designer also features full forward and back annotation. A 6,000 component library manager. Automatic placement and 100% routing. Extensive analog design support. Highspeed graphics. And more.

In fact, you'll find it so productive, you're likely to see a return on your investment in 30 days.

And that'll help you justify even more modules. Such as ripup and re-try routing. Thermal analysis. Gerber previewing and editing. Analog circuit simulation. A DXF interface for mechanical design and technical publications.

And even though Master Designer costs less, it comes with our full complement of update services and training. Including support from over 50 reseller locations nationwide.

No wonder over 100,000 boards a year are designed with P-CAD software.

For more information call 800-523-5207. In California, dial 800-628-8748. Or send us this coupon and we'll mail you a free preview copy of our PCB Design User's Guide. Complete with a CAD Buyers Guide to help you select the CAD system that's right for you.

And do it now. Because an opportunity like this doesn't fall in your lap every day.

P-CAD is a registered trademark and Master Designer is a trademark of Personal CAD Systems, Inc.

| Send me a free<br>preview copy<br>of P-CAD's<br>PCB Design<br>User's Guide. |  |

|-----------------------------------------------------------------------------|--|

| Name                                                                        |  |

| Title                                                                       |  |

| Company                                                                     |  |

| Address                                                                     |  |

| City                                                                        |  |

| City                                                                        |  |

1290 Parkmoor Avenue San Jose, California 95126 800-523-5207 U.S.A. In California, 800-628-8748

CIRCLE NO. 7

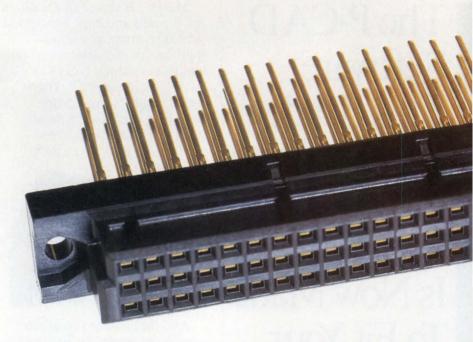

## The AMP Eurocard. Don't leave

The AMP Eurocard is now manufactured around the world. So all the benefits you expect from AMP—selection, delivery,

Available nearby: a variety of AMP Eurocard sizes and styles for packaging flexibility in DIN 41612 and IEC 603-2 applications.

specials—are that much closer to home, wherever you are.

In the U.S., for example, production covers types C, R, B, and Q. Plus half sizes. Plus expanded 2 and 3 row specials, including our 150-position style.

You choose the tail configuration you need—including our ACTION-PIN compliant pins. Our latest housing design allows

solderless insertion with standard "flat rock" tooling.

AMP Eurocard connectors and packaging are designed with

## Made worldwide. home to get it.

automation in mind, too, with hightemp housings, close tolerance tails. Position data are identical on throughhole and surface-mount housings, for easy tooling transition to SMT designs.

And the support you need to take advantage of all this—from technical expertise to prototypes, to specials, to full systems supportis right in place, right around the corner.

For technical information or product literature, call 1-800-522-6752. AMP Incorporated, Harrisburg, PA 17105-3608. For characterized backplane assemblies, contact AMP Packaging Systems, Inc., P.O. Box 9044, Austin, Texas 78766, (512) 244-5100.

Interconnecting ideas

CIRCLE NO. 8

When they work together, a multitude of ''little guys'' can have a greater impact than any one ''big guy.''

David Lieberman Senior Editor

## **IBM** takes it on the chin

t's always a tantalizing temptation to applaud an event that's likely to frustrate IBM, the industry giant that invariably attracts a combination of awe and resentment in virtually everyone who deals with them. The revelation on September 13 of a cooperatively developed AT-compatible alternative to IBM's Micro Channel, however, was laudable for nobler reasons than for the mere bashing of Big Blue. It's a case of a number of major players in the evolution of personal computing taking control of their own destinies in a meaningful way. It's also a case of open-architecture computer companies taking the open-architecture philosophy seriously—that is, when they work together, a multitude of "little guys" can have a greater impact than any one "big guy." Though, admittedly, the PC AT bus was created by Father IBM, the kids are now completely on their own.

During the last year and a half since Micro Channel first appeared, the future of personal computing has been up in the air. With the licensing debacle, ongoing delays in OS/2, severe space and power constraints and high entry costs, Micro Channel hasn't had the look of a popular platform for tomorrow's personal machines. On the other hand, the AT's 16-bit data path plus its clumsy multimastering capabilities and other quirks made it look like a dead end. Vendors using the de facto standard 80386 microprocessor for high-end desktop systems have had to make due with proprietary solutions to make up for the AT's deficiencies—adding a private memory bus here or a kludgey facility there. The future still floated, unclear and undefined.

On September 13, Compaq, Hewlett-Packard, Tandy, Zenith, Epson, NEC, Olivetti and many others came together to direct the future toward an enhanced AT architecture based on the newly defined Extended Industry Standard Architecture (EISA) bus. Though, at press time, the technical particulars of the EISA weren't known, its intent is clear: to bridge the best of the past and future by blending compatibility with the wealth of available AT boards and the type of high-bandwidth multiprocessing capabilities that future systems will demand. Nearly simultaneously with the EISA announcement, IBM announced a new PS/2 model based on what looks remarkably like the AT bus and, in fact, uses one of the open-market chip sets. Add one more name to the list of cloners.

David Liebeman

## CONTROLDATA JUST CHANGED THE DISK DRIVE INDUSTRY FOR GOOD.

Control Data has just created a new, separate subsidiary called Imprimis Technology Incorporated. But you can just call us Imprimis. It means "in the first place." We think it fits because we are. And we intend to remain there. First in high-performance, high-capacity disk drives. First in quality. First in service and customer satisfaction.

We introduced the world's first 200 megabyte disk drive in a 3½ inch form factor: the SWIFT.<sup>™</sup> WREN<sup>™</sup> 5¼ inch disk drives were the first to break the sub-20 millisecond seek time barrier and they're still the fastest 5¼ inch drives in the world. The SABRE<sup>™</sup> 8 inch disk drive was the first drive of its size to offer over 1,200 megabytes of storage. And in survey after survey of the OEM drive business, we ranked first in customer service.

So, just because we changed the name doesn't mean we're going to change our ways. We're going to stay the world's leading supplier of OEM data storage products.

CIRCLE NO. 9

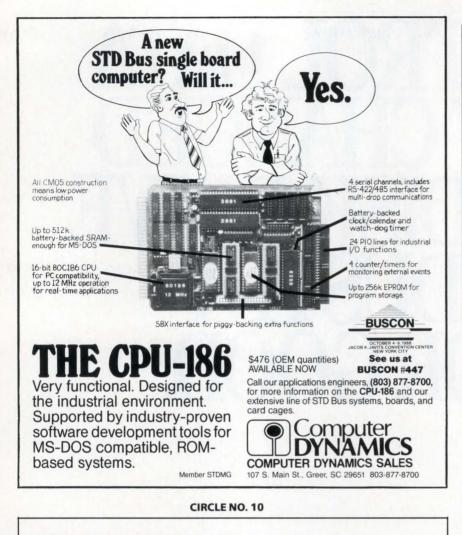

### This issue's cover. .

hat more appropriate symbol is there for memory than the pachyderm? They're big, they're fast (despite their size), and they never forget. Who among us doesn't hold dear the childhood tale about the elephant who, about to stomp on a miniscule mouse, remembers the friend made years before when the mouse removed a thorn from the elephant's foot? Or was that a lion who had the thorn in his foot? Or a tiger? Or a leopard? It doesn't matter because our pachyderms, like ASIC memories, can be whatever we want them to be.

COMPUTER DESIGN DESIGN THE FIRST MAGAZINE OF SYSTEM DESIGN, DEVELOPMENT AND INTEGRATION

> PUBLISHER David L. Allen

ASSOCIATE PUBLISHER/EDITOR-IN-CHIEF: John C. Miklosz

#### **TECHNOLOGY EDITORS:**

Ron Wilson, Integrated Circuits (Portland) Richard Goering, Design & Development (Santa Clara) David Lieberman, Computers & Subsystems Tom Williams, Graphics & Imaging (Santa Clara) John H. Mayer, Computers & Subsystems

Sydney F. Shapiro, Data Acquisition & Control

CONTRIBUTING EDITORS: Warren Andrews, Integrated Circuits S. Louis Martin, Integrated Circuits William Harding, Design & Development Howard Falk, Software Art DeSena, Testing & Manufacturing

RESEARCH/SPECIAL PROJECTS MANAGER: Sydney F. Shapiro

SECTION/SPECIAL PROJECT EDITORS: Ron Wilson, Technology Updates David Lieberman, Contributed Articles Michael G. Donlin, New Products Patti Villandry, Directories

MANAGING EDITOR: Susan R. Nykamp

ASSISTANT EDITOR: Kerstin L. Rosenquist

COPY EDITORS: Richard Dagley, Barbara-Ann Scofidio

EDITORIAL ASSISTANTS: Claire Coupal, Claire Ellis

WEST COAST OFFICES MANAGING EDITOR: Tom Williams

3333 Bowers Ave, Suite 100 Santa Clara, CA 95054, Tel: (408) 982-0288

1111 S.W. Gaines, No. 8 Portland, OR 97201, Tel: (503) 224-9396

> ART DIRECTOR: Jan Horner ILLUSTRATOR: Christopher Hipp

PRODUCTION DIRECTOR: Jan M. Lopez PRODUCTION MANAGER: Mari Rodriguez ADVERTISING COORDINATOR: Adrienne Adler COMPOSITION MANAGER: Holly Kersey COMPOSITION/REDESIGN: Jan Kasiecki COVER ART: Sergio Roffo

**CIRCULATION DIRECTOR:** Robert P. Dromgoole

#### Dennwell PUBLISHING COMPANY

Advanced Technology Group L. John Ford, Senior Vice-President Leslie P. Cypret, Vice-President, Administration P.O. Box 417 119 Russell St, Littleton, MA 01460 Tel: (508) 486-9501 Fax: (508) 486-9397 Postmaster: Send change of address form 3579 to COMPUTER DESIGN, Circulation Department, Box 3466, Tulsa, OK 74101

Cover design by Sergio Roffo

## TEK'S 1241 MICRO ANALYSIS SYSTEM: AT \$9,950, THE CHIPS ARE REALLY STACKED IN YOUR FAVOR!

Tek's 1241 microprocessor analysis system includes the Tek 1241 Logic Analyzer. The micro support package of your choosing. Plus performance analysis, storage and communications options. At a total price of \$9,950. If you're looking for a system to minimize your risk and maximize your return, this is the package you can bet on.

It's proven. The 1241 is known and accepted worldwide as the best of the leading logic analyzers.

It supports more than 45 microprocessors, microcontrollers and digital signal processors. That's more than any other logic analyzer. You can add additional micro support for as little as \$400.

000

It comes with a specialist.

Tek's dedicated logic analysis sales and applications engineers give you expert support whenever you need it.

It's the best deal on the table. For immediate value and long-term practicality,

nothing else can touch it.

Call us. Talk to your local Tek sales representative, or call 1-800-245-2036 for more information about the total

the total Tek 1241 package.

CIRCLE NO. 11 FOR LITERATURE CIRCLE NO. 63 FOR SALES CONTACT

Copyright © 1988, Tektronix, Inc. All rights reserved. 5EW-LAA-555-1-2-88-INTL-1

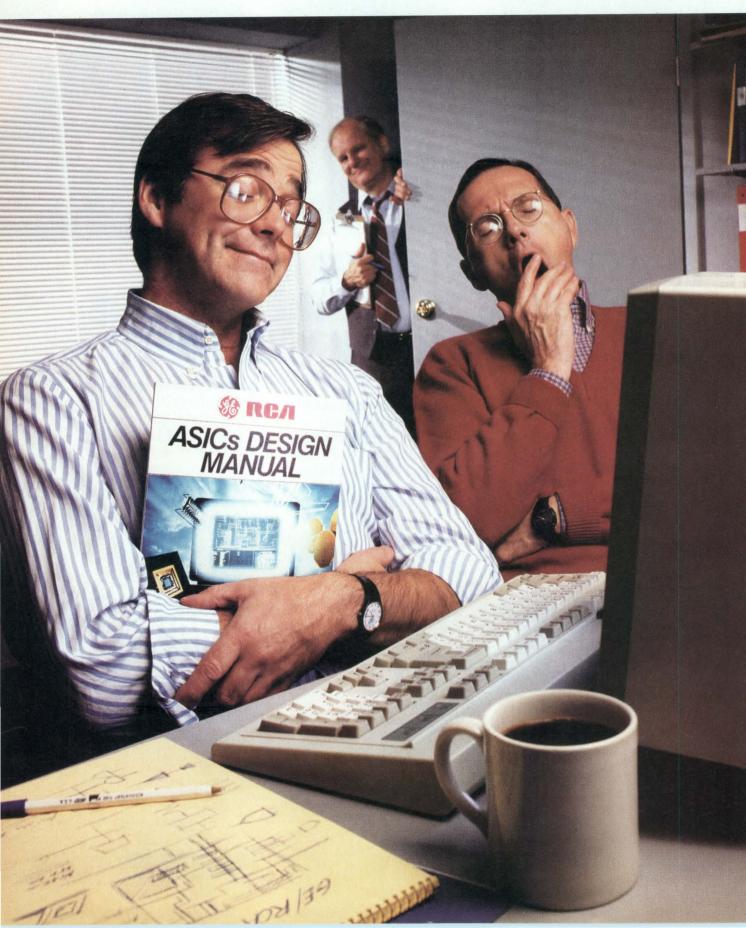

# Our ASICs

# are boring.

## They're easy to design. They're ready on time. And first-time success is virtually 100%.

You've heard all about the excitement of ASICs.

They improve performance, lower costs and make many new designs possible.

But, unfortunately, you've probably also heard about one big potential problem: while many ASICs pass the tests specified by the designer, they don't always work in the real world. And that causes excitement you can do without.

#### How to get first-time success.

It starts with our Design Simulation Software. It's been rated the best in the industry by the people who should know—designers who have used it. Within three days, you can be up to speed, working at any of the major workstations in the industry, creating and revising your ASIC with ease.

#### The standard cell advantage.

You'll really appreciate the power of our standard cells, which allow you to integrate a whole system, including macros, memories, logic and peripherals, onto a single chip.

We have cells with effective gate length as small as  $1.5\mu$  (.9 $\mu$  coming soon). And double-level metal for higher-density chips that can handle higher clock speeds.

You can choose from a wide range of Supercells, including the leading-edge RS20C51 core micro, RAMs, analog functions, bit-slice processors, HC/HCT logic, Advanced CMOS Logic, and high-voltage cells.

If they aren't enough, we can even generate

Supercells to your specs.

And we're also in the forefront of silicon compiler technology. So we can offer you the ability to create designs that are heavily BUSstructured, with your ROMs, RAMs, PLAs and ALUs compiled right into the design.

We also bring you the resources of some very powerful partners, thanks to our alternatesource agreements with VLSI on standard cells; WSI on macrocells and EPROMs; and a joint-development agreement with Siemens and Toshiba on the Advancell<sup>®</sup> library of small-geometry cells.

#### Gate arrays, too.

If gate arrays are better for your design, you'll be able to choose from our full line up to 50,000 gates, with effective gate length as small as  $1.2\mu$  and sub 1 ns gate delays.

These gate arrays use "continuous gate" technology for up to 75% utilization. They are an alternate source to VLSI Technology arrays.

We also alternate source the LSI Logic 5000 series.

And we have a unique capability in high-rel ASICs, including SOS. Our outstanding production facilities here in the U.S. produce high-quality ASICs in high volume at very low costs.

It almost sounds exciting for something so boring, doesn't it?

For more information, call toll-free today 800-443-7364, ext. 25. Or contact your local GE Solid State sales office or distributor.

In Europe, call: Brussels, (02) 246-21-11; Paris, (1) 39-46-57-99; London, (276) 68-59-11; Milano, (2) 82-291; Munich, (089) 63813-0; Stockholm (08) 793-9500.

#### TECHNOLOGY UPDATES

#### SOFTWARE

#### Software machine model blazes trail for parallel processing

Tom Williams, Western Managing Editor

parallel-processing environment developed by researchers at Yale University, known as Linda, is beginning to appear in commercially available parallel-processing systems. Linda isn't a language or an operating system. It's more of a machine model and a programming methodology that could conceivably be implemented as the underlying kernel of an operating system, or built into a programming language or a hardware architecture-or some combination of the three. Linda has ble, they'll have to give an eye to standards issues to ensure portability of parallel applications.

While there are no clear-cut standards for parallelizing compilers, or even operating systems, an industry committee has been formed to address the issues of software standards for the T800 Transputer chip from Inmos (Colorado Springs, CO), an increasingly popular vehicle for implementing parallel multiprocessor systems. But it appears that before committee members can discuss

as many as make sense for the application. language or operating system stan-

'workers," or iden-

the added advantage of requiring relatively minor modifications to popular languages to make them Linda-compatible.

As with any maturing technology, parallel processing today is spawning plenty of activity, as well as a great deal of diversity, in terms of systems that implement parallelism. In fact, it often seems that every new idea for a multiprocessing parallel system brings with it not only a brand-new hardware architecture, but also a new software operating environment. As multiprocessing systems struggle to become commercially viadards, they must first have an understanding of some basic underlying paradigm on which to build these standards.

It could be said that the underlying paradigm on which current standards are built is the von Neumann architecture and its variations. But actually there are many approaches to hardware architectures for parallel processing, each with its own champions and detractors. The underlying paradigm for parallel systems will probably be some sort of software machine model that can find its incarnation in various forms of parallel hardware architectures. One candidate is Linda, though it's by no means the only competitor. Even those implementations of Linda that are finding their way into the market aren't yet compatible with each other.

#### The concept of tuple space

In addition to needing an environment that accommodates portability and can be implemented on a variety of processors and machine architectures, programmers shouldn't have to deal in detail with structural and scheduling dependencies among parallel processes. In turn, a process shouldn't be concerned with whatever other process or processes are going to use its results. And similarly, a process shouldn't have to be loaded and running at the same time results are generated in order to be able to use those results. Freed from these scheduling worries, programmers are better able to concentrate on the problem at hand.

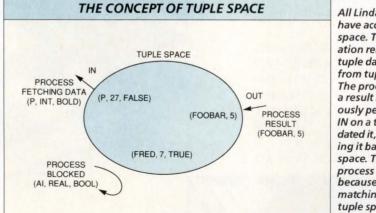

The Linda model uncouples parallel processes from their time and space dependencies. Processes never interact directly, as is the case when messages are passed using flags and semaphores. Rather, they communicate by acting on data elements called tuples, which are kept in a conceptual shared memory called tuple space. Tuple space is accessible to all processes running on the system, and there can be as many running processes as there are physical processors. Tuples themselves are ordered sets of values that can be active data structures (processes themselves, for example) or passive data structures. Tuples are accessed by logical name rather than by address.

If a running process has data that it needs to communicate to another process, it adds that data to the tuple space. The target process need not be running at the time. When the process comes on-line, it will search tuple space for tuples that match its template. A process called (P, int I, bool B), for example, would look for a tuple with the name P that has some actual integer and some actual Boolean value.

Once the process has found the tuple, it removes it from tuple space so it can't be grabbed by any other pro-

# A Worksmart Workshop For PCB Design.

You probably already know there are better ways to design PC boards out there. You know there are strategies for designing denser, more efficient boards. And you already know that today's CAD tools are revolutionizing the very way we think about PCB design, engineering and manufacturing.

But even if you know all this, where can you go to ask the really tough questions? To find out about the latest developments in CAM? Photoploting? Autorouting? SMT? And where do you go to get information on integrating mechanical design software with PCB CAD and desktop publishing? Or, how do you get started in PCB CAD without making all the common mistakes?

Our guess is you'd probably like to learn about the latest PCB design technology and ask your toughest questions at one time. In one place.

That's why P-CAD\* is offering a series of free nationwide PCB design workshops. Special seminars designed for engineers already familiar with the basics, as well as those who are just getting started.

Whether you know a little or know a lot, P-CAD has a workshop for you.

So what are you waiting for? Call P-CAD for a detailed agenda and reserve your worksmart space today. Call Toll-Free 1-800-628-8748 (CA) 1-800-523-5207 (Outside CA). Ask for Cynthia.

#### How To Get Started In PCB CAD

CAD for Analog Board Design

BOSTON October 3 1:30 P.M.-5 P.M. Howard Johnson Hotel

PARSIPPANY, N.J. October 4 9 A M -Noon Aspen Hotel

> Tyson's Corner OTTAWA

October 25 9 A.M.-Noon

October 5

9 A.M.-Noon

Holiday Inn

October 6 9 A.M.-Noon Holiday Inn, Oakbrook

CHICAGO

9 A.M.-Noon Marriott

**IRVING, TEXAS** October 11

SHERMAN OAKS (S. CAL.) October 12 9 A.M.-Noon Sherman Oaks Valley Hilton

SANTA CLARA October 13 9 A.M.-Noon Techmart 3

CHICAGO

November 28

9 A.M.-Noon

Oakbrook Marriott

MONTREAL October 24 9 A M -Noon Ramada Inn

SHERMAN OAKS (S. CAL.)

Sherman Oaks Valley Hilton

November 29

1:30-4:30

Baron's Motor Inn

9 A.M.-Noon

VANCOUVER October 27 9 A.M.-Noon **Discovery Park**

9 A.M.-Noon

Parsippany Hilton

FORT LAUDERDALE December 7 9 A.M.-Noon **Embassy Suites**

1290 Parkmoor Ave. San Jose, California 95126 Telephone (408) 971-1300

P-CAD is a registered trademark of Personal CAD Systems, Inc.

SANTA CLARA

November 30

9 A.M.-Noon

Techmart

WASHINGTON D.C.

TORONTO October 26

Cara Inn

BOSTON December 5 1:30-4:30 Newton Marriott

#### TECHNOLOGY UPDATES

#### SOFTWARE

cess. Tuples are never altered while in tuple space. They're removed, acted upon and/or updated, and then reinserted. This makes it possible for many processes to share access to tuple space without elaborate priority or semaphore schemes to ensure orderly access to data. By definition, if a tuple is present in tuple space and a process is running that can use it, it's usable. If a running process doesn't find a tuple that matches its template, it loops until the required tuple is placed into tuple space.

#### Only four Linda operations

Linda consists of four operations: OUT places a passive tuple into tuple space; IN removes a tuple for operation by a process with a matching template; READ reads a tuple's data without removing it from tuple space; and EVAL places an active tuple (a process) into tuple space. Once the active tuple has finished evaluating, it becomes a passive tuple. By far, the most common operations are

#### A vehicle for parallel processing

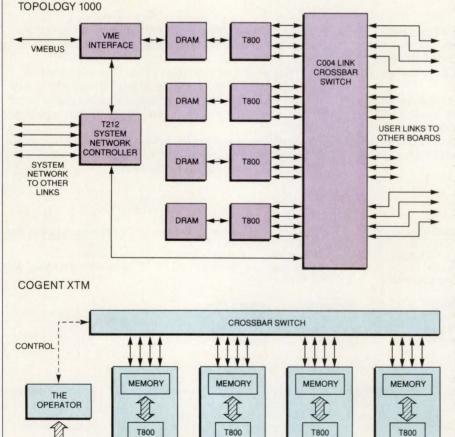

**B**oth the Topology 1000 from Topologix (Denver, CO) and the Compute Card from Cogent Research (Beaverton, OR), which forms the basic building block of the XTM desktop supercomputer, use a similar approach in their hardware architecture. The Topology 1000, which includes four T800

Transputer chips from Inmos (Colorado Springs, CO), is based on the VMEbus. The Compute Card, with two Transputers, is based on the NuBus. But both systems can be connected and networked to an almost arbitrary number of processing nodes.

Each Transputer has its own local

Û

BUS

memory array and can communicate over the system bus as well as via serial direct memory access links that are part of the Transputer chip. Requests for data or for communications linkups are usually sent via the system bus. For data transfers between the local memories of different processors, the system establishes a DMA link by means of the crossbar switch.

The main difference between the two approaches is that the Cogent system uses a separate processor called an operator to service communications requests and set up links automatically. In the Topology 1000, on the other hand, the user has direct access to the network links via a graphics display and a mouse. The Topology 1000 user, therefore, can set up different interconnect topologies before or at run time and experiment to find the most efficient interconnect scheme for the application. In addition, the Cogent XTM is a stand-alone system, while the Topology 1000 is designed to run under Unix on a Sun-3 workstation.

In the Linda system as implemented on the Cogent system, each local processor keeps a complete copy of the list of requests for tuples, which each processor broadcasts on the bus every time it looks for a tuple. If a local processor finds that a tuple on the request list is in its local memory, it signals the operator to establish a DMA link with the requesting processor, and the data flows over that link. Similarly, if a processor stores, or OUTS, a tuple to its local memory, it checks the request list to see if there's a request pending from another process. In this way, tuple space is maintained on a conceptual and functional level even though actual tuples may be stored in separate physical locations.

# -Spec

# VMEbus Field-Proven System NDI & Off-The-Shelt Products Available **Solutions** from DY-4

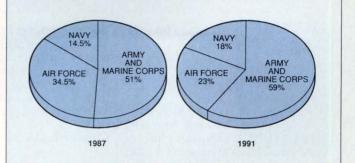

Durability, flexibility and performance. All fieldproven in our militarized VMEbus solutions now used in C<sup>3</sup>, army, navy, air force and air-traffic control applications.

Designed to perform in the most challenging situations. DY-4 VMEbus solutions address the system integrator's major program concerns:

- Environmental requirements

- Reliability

- · Testability with card and system-level diagnostics

- QA and QC to MIL-Q-9858A

- Multiprocessing architecture .

- Redundancy .

If you need Mil-Spec, field-proven VMEbus solutions, call us today. We're ready to discuss your specific requirements.

| CanadianCorpora  | ate            |

|------------------|----------------|

| Headquarters     | (613) 596-9911 |

| California       | (408) 377-9822 |

| Los Angeles      | (714) 549-2559 |

| Washington       | (301) 964-5554 |

| Massachusetts    | (617) 692-9308 |

| Denmark          | (06) 963624    |

| Ferranti Compute | er Systems     |

| United Kingdom   |                |

|                  |                |

**CIRCLE NO. 13**

## A Simple Solution to Automation:

## ECX Bolt-in Computer

It's easy to implement control, monitoring, and automation systems using the ECX "bolt-in computer"<sup>TM</sup> because:

- You get all the power you need in a rugged 8.5" x 5.5" package (25% faster than an IBM-PC XT)

- You save weeks of startup time because integral firmware starts up as soon as you apply 5V

- You can program in C, BASIC, or assembly language on an IBM-PC, and transfer your program to ECX in EPROM's or RAM

- You have your choice of digital, analog, timing, and communication interface signals

All you do is attach the necessary inputs and outputs and enter your program. You concentrate on using a computer, not building one. Call or write today for your free copy of the 40 page ECX Design Guide.

#### ■ TECHNOLOGY UPDATES

#### SOFTWARE

OUT and IN.

One of Linda's most powerful features is its ability to replicate a process in order to create a given number of "workers," or identical processes, that can work on a large set of tuples, says Charles Vollum, president of Cogent Research (Beaverton, OR). Since Linda deals with processes, it can replicate as

#### "Linda is certainly the cleanest parallel software paradigm that I've seen."

–Jack Harper, Topologix

####

many as make sense for the application. "You can have 100 processes on one processor or 100 processes on 100 processors," says Vollum. In the former case, only one process would run at a time; the others would be blocked and pending. In the latter case, all processes could run, and the speedup would be almost linear.

Vollum cites as an example of how replicated workers can attack a highly parallel task a ray-tracing program that computes pixel values in terms of scan lines. If each scan line is a tuple in tuple space, then a given number of copies of the scan-line raytracing algorithm can arbitrarily IN scan lines, compute their pixel values and OUT them back into tuple space. The master process would then IN the computed scan lines and send them to the frame buffer.

"When a worker does an IN, he doesn't know which scan line he's going to get," Vollum says. "With many processors, the easy scan lines will be done first. One processor may do only one scan line, if it's a difficult one to compute, while another may do 100." The resulting image will appear on the screen line by line in a seemingly random fashion until the entire image is completed.

#### Two approaches to Linda

Implementations of Linda are beginning to make their way into commercial products, albeit in varying forms. Two approaches are the Cogent XTM desktop parallel supercomputer and the Topology 1000 from Topologix (Denver, CO), a plug-in board for use with Sun workstations. These approaches use similar hardware architectures based on the T800 Transputer chip, but their Linda implementations reflect different views of what users need.

In the Cogent XTM, according to Vollum, "We pushed Linda right down to the bottom," building it into the Unix operating system kernel. Topologix took a different approach altogether in its plug-in board by embedding Linda into the Common Lisp programming language as an option. "We want to market a general-purpose machine that's not restricted to one paradigm," explains Jack Harper, president.

Embedding Linda in the operating system kernel tends to make the system a Linda-only machine, but it distributes operating system services over as many processors as are available. A request for a disk read, for example, is dropped into tuple space and is immediately grabbed by the file-server process. The file-server

All Linda processes have access to tuple space. The IN operation removes the tuple data structure from tuple space. The process storing a result has previously performed an IN on a tuple, updated it, and is OUTing it back to tuple space. The blocked process is looping because there's no matching tuple in tuple space.

## A lot of performance took just a little extra common sense.

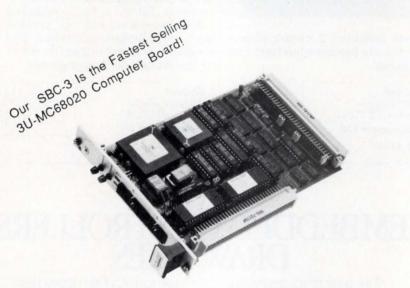

### Introducing our fully Intel-compatible 80386 SBC.

Edilit Elitetetetetete

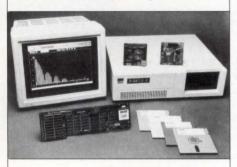

The 20MHz 80386 processor supplies the power, but solid common sense design accounts for the performance of Central Data's Multibus\*I CD21/8386.

For spectacular memory throughput, our board offers four interleaved banks of 32-bit-wide fast page RAM to achieve zero-wait-states for most accesses and eliminate the need for caching.

To get the data in and out, we provide 2 SBX connectors. Intel's board has one.

To get it to memory, our board supports DMA. Intel's doesn't.

Our board lets you use both Weitek WTL 1167 and 80387 floating point co-processors. Intel makes you choose between them.

Like all our Multibus SBCs, the CD21/8386 is fully hardware and software compatible with corresponding Intel boards . . . in this case with the SBC 386/3X series. But our board is not just loaded with features, it's got the right features to capitalize fully on the 80386's extra power and wide data path in any application. That's common sense design.

And Central Data backs it up by our industryleading performance in the areas of manufacturing standards, user support, and on-time delivery.

Give Mike Heins, SBC product manager, a call today and he'll be happy to tell you all about it.

1602 Newton Drive, Champaign, IL 61821-1098 1-800-482-0315 (In Illinois 217-359-8010) FAX 217-359-6904 \*Multibus is a trademark of Intel Corporation. Visit us at Buscon East Booth #226

#### TECHNOLOGY UPDATES

#### SOFTWARE

process pulls the requested data off disk and puts it into tuple space, where it's available for the requesting application process or processes. "Linda makes the operating system a distributed program that runs on all these processors, but what the user sees is old, familiar Unix," according to Vollum.

#### Built-in commands for Linda

In the Topologix approach, the Linda mechanisms for creating tuples and managing tuple space are built into the language, along with a variety of commands to invoke Linda functions. Lisp is expected to be available in the near future, to be followed by a version of C with embedded Linda functionality.

When creating Linda-capable languages (Fortran and C++) for the XTM, Cogent built in elements that fit with the syntax of the language but invoke the Linda functionality embedded in the operating system kernel. OUT in Fortran, for example, is CALL OUT. By embedding statements to do IN, OUT, READ and EVAL into what is otherwise standard source code, programmers can define tasks and tuples, and create parallel programs. Programmers can also decide exactly how many worker tasks, or copies of a task, they want to create. The number can be changed without having to recompile the program.

While keeping a range of options open for his customers to configure the Topology 1000, Harper confesses to being a real Linda fan. "When I first looked at it, I thought, 'This is ridiculous. It's too simple," he says. "To my mind, it's certainly the cleanest parallel software paradigm that I've seen. Linda's ability to distribute itself over an arbitrary number of processors is vital to ease of program development and debugging.

"The key is that I can build software with Linda, run it on a single processor, debug it and make it work, and then turn it loose," he continues. "And it will propagate into the parallel-processing world and will work. To me, that's just astonishing."

#### COMPUTERS AND SUBSYSTEMS

#### Cache board delivers turbocharge to VMEbus systems

David Lieberman, Senior Editor

ne of the most popular means of charging up performance in new-generation microprocessors, CPU boards and assorted controller boards is cache memory, which reduces the need to access data and/or instructions from an external source, and eliminates the wait states induced by doing so. Although caching gives a real boost to memoryintensive and/or time-critical applications, it typically increases system cost and complexity as well.

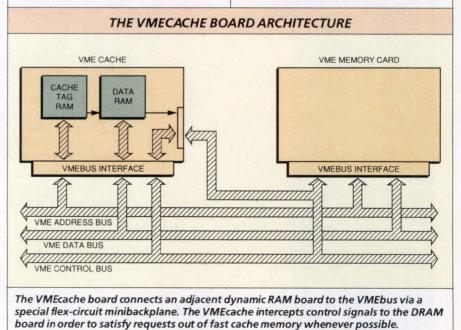

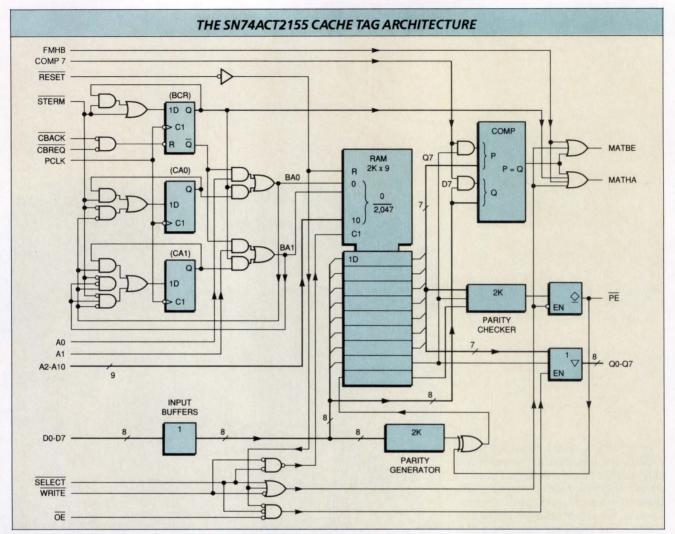

A new caching board, however, gives a cost-effective, transparent turbocharge to existing VMEbus systems without requiring CPU upgrades, hardware redesign or software reconfiguration. The VMEcache board from Ovation Systems (Great Milton, Oxfordshire, UK) provides a simple direct-mapped writethrough cache system consisting of 8 kbytes of 32-bit, 35-ns cache tag static RAM and either 16 or 32 kbytes of 35-ns data cache SRAM.

The VMEcache board is installed by removing an existing dynamic RAM board and inserting the board in its place. The DRAM board is then reinserted between the slots of a backplane and reconnected through the VMEcache to the VMEbus via a special flex-circuit minibackplane. The interim position of the VMEcache lets it monitor certain signals on the bus to determine, for example, if a data request can be serviced from its own cache SRAM or if it must be passed through to the DRAM board. When requested data is resident in the cache, the VMEcache disables the DRAM board and drives the requested data onto the bus.

■ Cache doubles peak performance The VMEcache doesn't rest content with mere caching; it also ensures that its own operations don't add delays to memory accesses and, there-

#### COMPUTERS AND SUBSYSTEMS

fore, undermine its benefits, "Very high-performance cache-tag memory lets a cache-hit detection occur within the address set-up portion of the VMEbus cycle," says Ovation's tech-nical director, R.P. Gregory. "As a re-sult, the data is ready to be driven onto the bus before the cycle strobes have even been asserted." The board can provide a 40-ns access to data on a cache hit, according to Gregory. "For a 16-MHz 68020, this removes three wait states involved in accessing system memory and gives the potential of one-wait-state access to memory over the bus-as fast as many CPU cards can execute from on-board memory.

"This will almost double peak performance and provide a 50 percent typical performance improvement to systems using VMEbus memory, and up to 200 percent speed improvement to systems where the bus bandwidth becomes limited by DRAM cycle time rather than by its access time," Gregory continues. "This is particularly noticeable in multiprocessor systems where total memory bandwidth becomes just as limited by the DRAM's intercycle recovery period as by the access period."

The VMEcache board maintains entries of the most frequently and most recently read memory locations. When a data request must be serviced by the DRAM board, VMEcache stores the new data for subsequent accesses. Cache entries are also made during long-word write cycles and during write cycles to previously cached locations, automatically updating previously cached data. All cache entries in the VMEcache are cleared on VMEbus reset and may also be cleared if a read-modify-write cycle occurs within the cacheable address range. "This gives the CPU the option of clearing the cache when it's using memory that's actively dualported independently from the cache," says Gregory. VMEcache provides hardware selection of the cacheable address range to prevent caching of noncacheable locations.

The VMEcache board, however, has no practical effect on the efficiency of write cycles. A typical CPU spends only about 20 percent of its time performing write operations, according to Gregory. "And many DRAM boards provide their own write-cycle buffering, which inherently improves write access time."

#### Applications for many systems

Despite its virtues, the VMEcache isn't for every system. It won't, for example, operate with VMEbus block transfer cycles and may cause coherency problems when used in conjunction with dual-ported boards. Improvements in access time will be limited for systems using memorymanagement units, since MMUs im-

## Guaranteed Portability for your real-time systems.

#### A real-time, multi-tasking, ROMable kernel for C programs.

Now you can have a portable base for embedded systems that lets you grow from 8- to 16- to 32-bit systems. CISC or RISC, now your kernel can be as portable as your real-time application.

C EXECUTIVE is especially suited for high volume, low cost board level products for instrumentation, control, data acquisition, and other real-time applications.

#### Features

- Real-time, fully-preemptive task scheduler.

- Optional file system available.

- Fast context switching time  $-17\mu$ s on 25 MHz MC68020.

- Standard I/O and data flow design facilities are built in.

- Highly portable—supports Motorola MC68000/MC68010, MC68020/MC68030, MC6809, Intel

8080/8085, 8086/8088, 80186, 80286, 80386, DEC LSI-11, Zilog Z80, Z280, AT&T WE32100, Texas Instruments TMS34010, Intergraph CLIPPER, and the National Semiconductor Series 32000.

High Level Language Support written in C, provides built-in interface to user applications code.  Rapid prototyping—test under UNIX, DOS, VMS, etc., then download to your choice of microprocessor.

KECUTIVE

- Use the latest microprocessor— C EXECUTIVE is being ported to a wide variety of both CISC and RISC processors.

- JMI Portable C Library—a complete ROMable and sharable library is included.

#### **Order Now**

The JMI C EXECUTIVE single unit binary price is \$575. Source code for all I/O drivers is included. Quantity discounts are available.

To order, or for more information, write or call JMI Software Consultants, Inc., 215-628-0846.

Registered Trademarks: UNIX—AT&T; MC6809, MC68000—Motorola, Inc. Distributors: Sweden, Unisoft AB, Vastra Hamngatan 8, S-411 17 Göteborg, Phone: 46-31.176050; West Germany, Staub Computer Integrations GmbH, Lochhamer Schlag 19, D-8032 Graefelfing, Phone: 089/853987; France, COSMIC, 52, quai des Carrières, 94227 Charenton Le Pont CEDEX, Phone: (1) 378-83-57; Switzerland, RETIS Realtime Software AG, CH-5001 Aarau, Bahnhofstrasse 96, Phone: 064-24-77-76; United Kingdom, Real Time Systems, Ltd., PO. Box 70, Viking House, Nelson Street, Douglas Isle of Man, British Isles, Phone: 624-26021; Japan, Advanced Data Controls Corp., Nihon Seimei Otsuka Bldg., No. 13-4, Kita Otsuka 1 chome, Toshima-ku, Tokyo 170, Phone: 576-5351.

#### TECHNOLOGY UPDATES

#### COMPUTERS AND SUBSYSTEMS

pose an extra wait state for all accesses.

But for many existing systems, the board avoids the wait states imposed when a CPU needs to go off-board for data or code. "Since most software routines spend considerable time in loops, it's very likely that previously accessed program data will be found in the cache," says Gregory. "Studies have shown that such a cache will typically achieve a 70 percent hit rate for program execution."

The VMEcache also offers comparable performance for applications that recurrently access a limited amount of data, such as data base manipulations, according to Gregory. These applications result in more effective bus utilization—a major benefit for multiprocessing systems. The board can also benefit those CPU boards that are based on the newer microprocessors with their own onchip caches, says Gregory, since these caches are so small that they seldom contain all the program or data space the processor requires.□

#### DESIGN AND DEVELOPMENT TOOLS

## Standardization effort targets data management for CASE

Richard Goering, Senior Editor

sers of computer-aided software engineering (CASE) tools have a severe problem managing data when tools from different vendors are combined. An emerging standardization effort spearheaded by Atherton Technology (Sunnyvale, CA) and Digital Equipment Corp (Marlboro, MA) may soon alleviate this problem by defining a way for CASE tools to link into a consistent data-management system.

Initiated by Atherton and DEC in May, this standardization effort has since attracted participants from Apollo Computer, Cadre Technologies, Ford Aerospace, Hewlett-Packard, IBM, Index Technology, Interactive Development Environments, Interleaf, RCA, Rockwell and Sun Microsystems. The group met for the third time at the recent conference of OOPSLA-88 (Object-Oriented Programming: Systems, Languages and Applications).

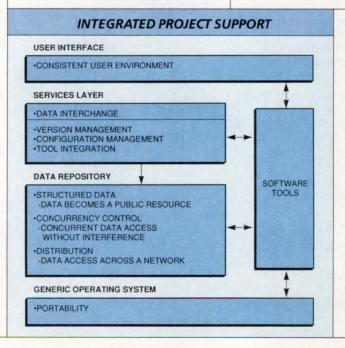

The standard under discussion has been given the temporary name Atherton Tool Integration Services (ATIS). Its starting point was Atherton's Software Backplane, an integrated project support environment that provides such features as a consistent user interface, management services, a common data base and a portable operating system. ATIS focuses on management services such as version control and on data-storage issues such as concurrent data access. Due to input from DEC and other vendors, ATIS has evolved to the point where it now varies considerably from Atherton's Software Backplane. ATIS will be a public-domain, nonproprietary standard, and so the group that's guiding it is now looking for a name that doesn't include Atherton in the title.

#### ATIS goes beyond EDIF

The ATIS effort parallels an attempt to adapt the Electronic Design Interchange Format (EDIF) to CASE tools. By providing a neutral interchange format, EDIF will let CASE tools from different vendors exchange data. ATIS, however, allows a deeper level of integration by defining a common way of managing multivendor data.

"We're not talking about merely the ability to interchange data," says Bob Abramson, senior product manager of CASE tools at DEC. "You want to implement version control for the output of tools in a common fashion and establish relationships between the data produced by different tools. You want to go back and have an audit trail of changes made to data. And, ultimately, you want to tie in source-code modules and test programs as well."

Although not a data base standard, ATIS represents a move toward a common data-storage methodology for CASE tools. "Most previous propo-

The starting point for the standardization effort was Atherton Technology's Software Backplane, an integrated project support environment that provides a consistent user interface, a management services layer, a data repository and a portable operating system. The proposed standard addresses management services such as version control and data repository issues such as concurrency control. It does not, however, mandate a specific type of data base.

#### DESIGN AND DEVELOPMENT TOOLS

sals for integration have been at the file level," says Tony Wasserman, president of Interactive Development Environments (San Francisco, CA). "That's okay, but it's a very passive way to link tools. Here we have the idea of a shared repository through which tools can communicate."

#### Object-oriented approach

As currently conceptualized, ATIS fulfills two functions. First, it defines an object-oriented methodology that provides an interface between CASE tools and data-management services. Second, it establishes models for such procedures as version control, security and access control, and transaction control.

The tool interface is based on a predefined, single-inheritance hierarchy of data types. As is typical in object-

#### "If ATIS moves into a nonproprietary format and Sun and Apollo contribute, we'll have the best of all worlds."

—Lou Mazzucchelli, Cadre Technologies

oriented programming, each type has associated messages (such as open, merge and check-in), methods (pieces of code that implement messages) and properties (such as child and parent). To add a new tool, the tool integrator can either use existing types or add a new subtype. A subtype can inherit existing methods and messages, or new methods and messages can be added.

Once a tool is added to this hierarchy, it can use an ATIS-compatible project support environment. Since ATIS manipulates objects rather than files, integration can take place at a deep level. An ATIS-based management system could, for example, define a relationship between a bubble in a diagram and a paragraph in a document.

The ability to add new types, messages and methods lets most existing tools use management services without modifying the tool. "The tool is completely blind to the fact that it's being controlled on the outside," says Bill Paseman, Atherton vice-president of technology. "The tool vendor doesn't have to make any changes." But the tool integrator must understand the interface the tool uses to communicate with the outside world.

Tool integration won't be automatic for all vendors, however. "If you don't have concepts such as object relationships, object management and navigation, there's no problem," says Lou Mazzucchelli, chairman of the board at Cadre Technologies (Providence, RI). "But if you do have these concepts, you have to figure out how your object management affects the integration tool."

In any case, a new tool that's designed with ATIS in mind can be integrated more efficiently than an existing tool. By supporting the predefined types, the tool can exchange data more efficiently and avoid duplicating storage, notes Paseman. Whatever evolves from ATIS will thus affect future tool development, and tool vendors may someday wish to label their tools as "ATIS-compatible."

#### Management models

ATIS doesn't mandate a specific system for implementing management services, nor does it dictate a specific type of data base. It does, however, set forth some conceptual models that describe the execution of messages. Under the current versioncontrol model, for example, two users can open a file concurrently and update it locally. After the files are checked in, the management system merges them into a new version.

ATIS also provides several other types of models, including those for security and access control, which determine who has clearance to access data; those for naming services, which establish a file-naming methodology; and those for transaction control, which guarantee data base consistency during concurrent multiuser access. All ATIS models are under development and are subject to change.

One area that the ATIS group plans to address is correspondence control, which establishes relationships between objects in the data base. Another area that will be considered is data access and communications across a network.

To develop data-management mod-

More design engineers choose ABEL™, Data I/O®'s high-level design software. Because this universal, industry-standard tool offers more PLD choices.

#### **UNIVERSAL DEVICE SUPPORT.** ABEL supports virtually every PAL<sup>®</sup>, PLA, FPLA, EPLD, FPGA, and GAL<sup>™</sup> on the market, including both simple and complex architectures.

UNIVERSAL VENDOR COVERAGE. ABEL supports 100% of the semiconductor manufacturers.

**UNIVERSAL INPUT METHODS.** Describe your design in behavioral terms using high-level equations, truth tables, or state diagrams—

whichever works best for the particular circuit. UNIVERSAL PLATFORM SUPPORT. ABEL runs on multiple hardware

platforms including Sun, PC, Apollo, and VAX.

To find out more, call today for our free PLD Development Kit.

PLD Development Kit

Corporation

DATA I/O

#### TECHNOLOGY UPDATES

#### DESIGN AND DEVELOPMENT TOOLS

els, the ATIS group can draw not only on the Software Backplane experience, but on data-management systems such as the Domain Software Engineering Environment (DSEE) from Apollo Computer (Chelmsford, MA) and the Network Software Environment (NSE) from Sun Microsystems (Mountain View, CA). "If ATIS moves into a nonproprietary format and Sun and Apollo contribute their ideas, then I think we'll have the best of all possible worlds," says Cadre's Mazzucchelli.

In any case, ATIS should be able to fit on top of NSE or DSEE and provide a way for tools to use these systems. "ATIS is defining a consistent tool interface. It doesn't add functionality NSE doesn't have," says George Simons, CASE product line manager for Sun Microsystems. Since NSE, DSEE and the Software Backplane are all competing products, Simons believes that the ATIS group now needs an independent third party to assume the leadership role.

The emerging standardization effort lets existing tools use management services without being modified, claims Bill Paseman, Atherton Technology's vice-president of technology. "The tool is completely blind to the fact that it's being controlled on the outside," he says. "The tool vendor doesn't have to make any changes."

#### Other standardization efforts

The ATIS effort may complement other standardization efforts. The Portable Common Tool Environment (PCTE), which is strong in Europe, is an attempt to develop a portable environment in which software development tools can operate. The Information Resource Dictionary Standard (IRDS), a project of the National Bureau of Standards, concerns a common tool interface to data dictionaries. Now established as a standard in electronic CAE/CAD, EDIF will probably define the data-interchange standard for CASE. And the prevalence of the X Window System will help set a user-interface standard.

The net effect of all these standards will help create truly integrated software development environments. But standards only work if there's widespread cooperation among tool vendors, workstation vendors and users. "For a standardization effort to succeed, people need to talk to each other," says Atherton's Paseman.□

## Frame builder and back annotator link CASE to development tools

Richard Goering, Senior Editor

B ecause computer-aided software engineering (CASE) tools are seldom linked to code development or testing, the transition from CASE to compiled code is usually tedious and error-prone. Two new products from Microcase (Beaverton, OR) attack this problem, however, by tying the Teamwork CASE tools from Cadre Technologies (Providence, RI) to the rest of the software development cycle.

The first of these tools is the Source Frame Builder, which can automatically translate a Teamwork structure chart's module specifications into C source file frames. The other tool, the Back Annotator, attaches performance parameters from Microcase's Software Analysis Workstation to design objects in Teamwork SD (Structured Design). "We're unifying the front-end design tools, which were islands of automation by themselves, into the microprocessor development environment," says Caine O'Brien, Microcase CASE products marketing manager.

Since late September, Microcase has been a value-added reseller of Cadre Technologies' Teamwork

"We're unifying the front-end design tools into the microprocessor development environment."

-Caine O'Brien, Microcase

tools. Microcase also sells compilers and source-level debuggers from Microtec Research (Santa Clara, CA) and in-circuit emulators from Microtek International (Hsinchu, Taiwan). Microcase's Software Analysis Workstation is a nonintrusive analysis tool that's hosted by the IBM PC. By combining all these tools with the Source Frame Builder and the Back Annotator, Microcase is able to offer an end-to-end solution to embedded software developers.

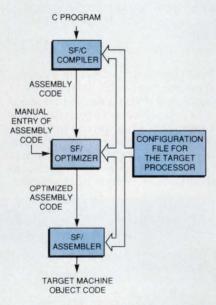

#### Not code generation