## APRII 1 1989

## COMPUTER DESIGN.

THE FIRST MAGAZINE OF SYSTEM DESIGN, DEVELOPMENT AND INTEGRATION

Software protocols smooth the path to a standard graphics interface

- 80860 CPU positions Intel to take on minisupers Page 20

- Emerging standards, hardware and software light the way to FDDI Page 51

- Static RAMs race to keep up with RISC Page 59

## Mentor Graphics delivers the only Electronic Design Automation system that grows in size and power at the same time.

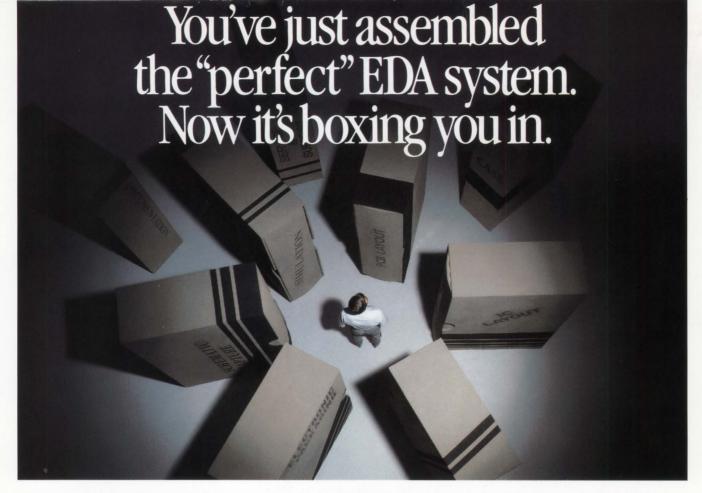

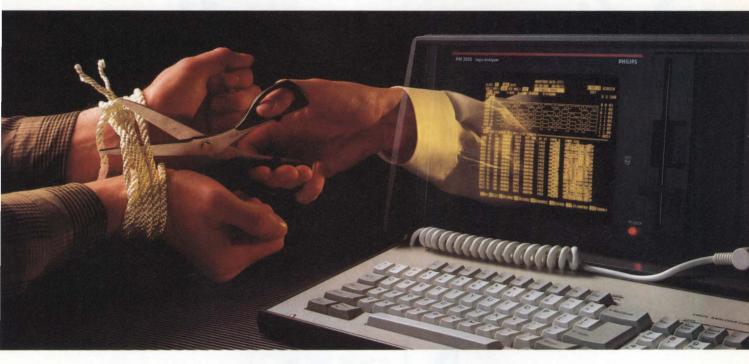

**Engineer or referee?**

The time has come. You're about to take on a major design project, so you assemble a little of this and a little of that to construct the "perfect" EDA system. And quickly discover it's too little too late.

Why? Because unless all your tools are on speaking terms, you spend more time patching up arguments than you do designing. And the further you expand your system, the more boxed in you become.

Fortunately, there's a single, simple solution. Mentor Graphics' EDA tools.

The sum of the parts.

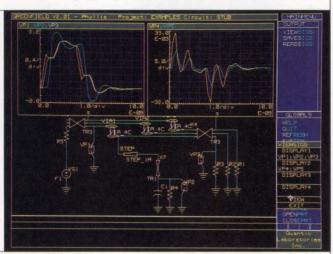

No other EDA vendors provide the rich inter-tool communications paths found within our IDEA Series™ EDA system. From schematic capture to output for manufacturing, your design data flows freely from one tool to the next.

Nor do they offer the broad array of tools you need to actually get your design out the door. Whether you're designing ICs, ASICs, PCBs, systems or embedded software, Mentor Graphics' tools cover the entire design cycle.

Nor can other vendors claim the experience we've accumulated. Cur-

rently, there are over 12,000 Mentor Graphics workstations producing everything from 32-bit VLSI microprocessors to 108 MIPS parallel computers. And our continuous dialogue with these customers gives us invaluable feed-

back in designing subsequent generations of EDA tools.

Mentor Graphics also provides a single source of service and support for your entire EDA tool set. No more finger pointing. No more delays. Our support organization takes care of all your hardware and software needs.

## To be continued.

It's all part of a vision unique to Mentor Graphics, the leader in electronic design automation. Let us show you where this vision can take you.

Before you open all those strange

boxes, call us toll-free for an overview brochure and the number of your nearest sales office.

Phone 1-800-547-7390 (in Oregon call 284-7357).

Yourideas. Our experience.

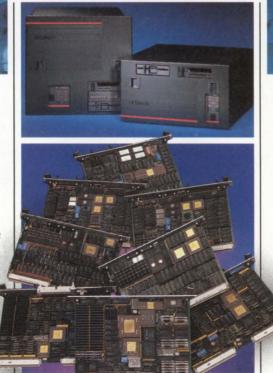

## Packaging Makes the Difference

If you want your system to look its very best, look to Electronic Solutions.

The first thing you'll find is that the beauty we add to your board level system is a lot more than skin deep. It will look better, sell better, and work better in an Electronic Solutions enclosure, for a lot of reasons:

**Engineered Cooling** for maximum performance from the new, high-density cards.

**Built from Experience:** We've been the enclosure experts since board-level systems began.

**Safety and EMI/RFI Approvals** by UL, CSA, TUV(IEC380) and the FCC.

## Off the Shelf or Built to Order:

From simple needs like paint and labeling to complete reshaping for the most unusual requirements—we do it all. Most of the time we have a big head start.

See how packaging can make the big difference to your system. Give us a call today on our toll-free numbers.

## Huge Selection of Complete Enclosures

Tabletop 4,7,10,12,15 slots 3½" Rack 4 slots 7" Rack 7,10 slots 10½" Rack 12,15 slots DeskMate 7,10,12,15 slots

Tabletop 3,5,6,7,12, 20,32,40 slots 3½" Rack 3 slots 7" Rack 5,7 slots 10½" Rack 12,20,32,40 slots DeskMate 5,7,12 slots

Tabletop 6,7,12,20 slots 7" Rack 7 slots 14" Rack 12,20 slots

## We'll FAX you the facts.

Want the latest data in a hurry? Nothing is faster than Electronic Solutions' new "FAX the FACTS" program. Call our "800" number and give us the information you need from us. We"II FAX it to you immediately.

6790 Flanders Drive, San Diego, CA 92121 (619) 452-9333 Telex II(TWX): 910-335-1169

Call Toll Free: (800)854-7086 In Calif: (800)772-7086 CIRCLE NO. 2

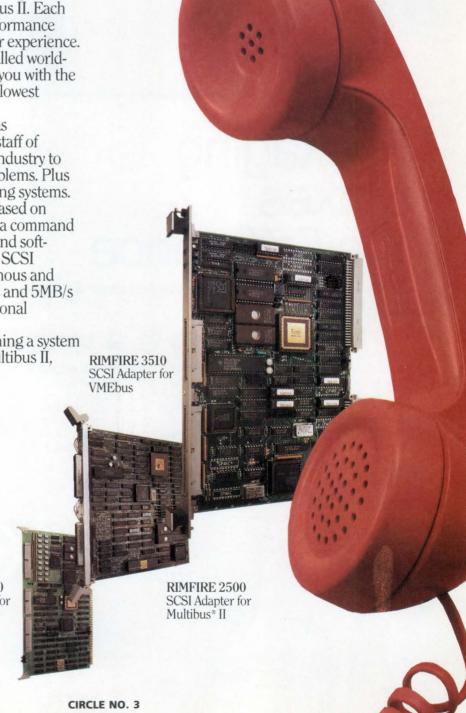

# WANT TO TALK SCSI? CALL CIPRICO AT 1-800-SCSI-NOW.

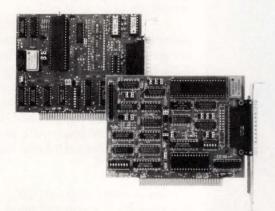

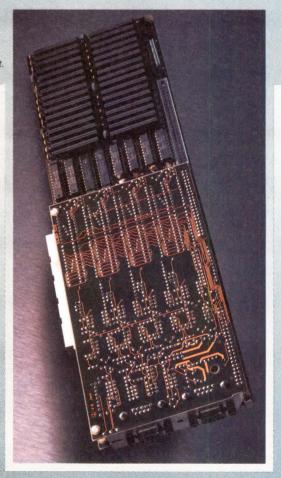

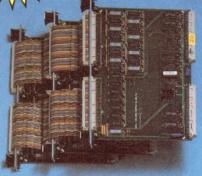

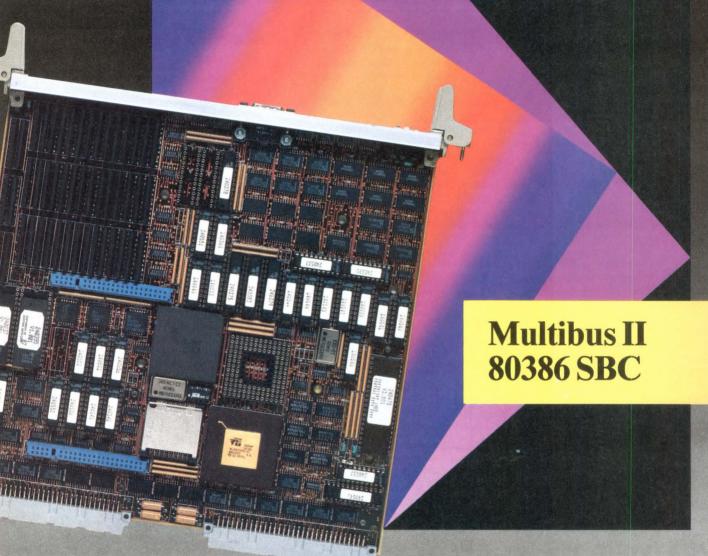

Why talk SCSI with Ciprico? To start with, we're the only vendor with a complete line of high-performance SCSI host bus adapters for Multibus\* I, VMEbus, and Multibus II. Each board was designed to optimize performance with its system bus. And consider our experience. Ciprico has over 50,000 boards installed worldwide. Our design expertise provides you with the highest possible performance at the lowest possible price.

But that's not all. Ciprico has respondability. We have the largest staff of customer support engineers in the industry to help you resolve any integration problems. Plus software drivers for all major operating systems.

Our SCSI adapters are all based on an 80186 microprocessor, providing a command queuing, pass-through SCSI command software interface. Each board supports SCSI disconnect/reconnect and asynchronous and synchronous transfer rates of 2MB/s and 5MB/s respectively. And a floppy port is optional for cost effective system design.

So if you're currently designing a system based on Multibus I, VMEbus, or Multibus II, give us a call to talk SCSI.

CIPRICO LISTENS. AND RESPONDS.

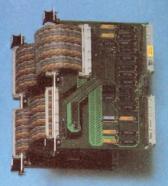

RIMFIRE 1500 SCSI Adapter for Multibus\* I

## COMPUTER

## DESIGN

THE FIRST MAGAZINE OF SYSTEM DESIGN, DEVELOPMENT AND INTEGRATION

Page 44

## **■ TECHNOLOGY UPDATES**

| Integrated Circuits                                                      |    |

|--------------------------------------------------------------------------|----|

| 80860 CPU positions Intel to take on minisupers                          | 20 |

| 80860 blends vector processing into a RISC-like architecture             | 25 |

|                                                                          |    |

| <b>Computers and Subsystems</b>                                          |    |

| Computers and Subsystems Languishing STD Bus receives a late-life kicker | 28 |

## **Major System Components**

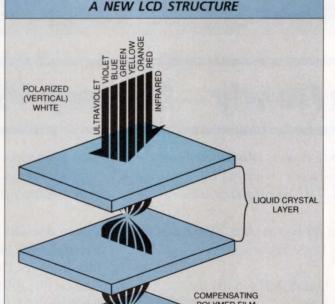

| New twist in LCD designs makes them thin, light power-savers              |    |

|---------------------------------------------------------------------------|----|

| Design and Development Tools Niche simulators tackle special applications | 14 |

Page 59

## ■ TECHNOLOGY AND DESIGN FEATURES

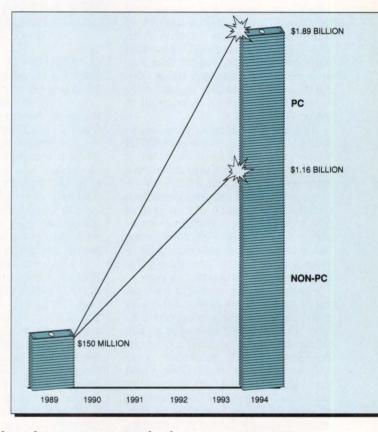

Emerging standards, hardware and software light the way to FDDI Within two years, FDDI will be established as the dominant high-end LAN for the 1990s......51

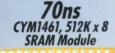

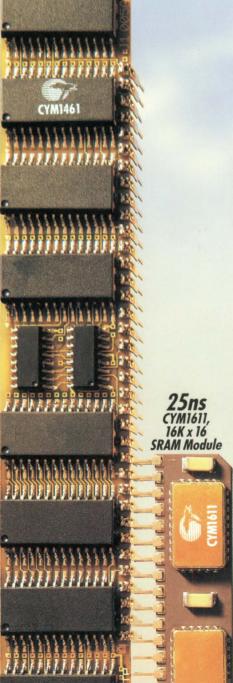

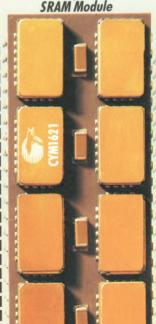

## Static RAMs race to keep up with RISC

### **COVER STORY**

Page 100

### ■ NEW PRODUCT HIGHLIGHTS

## **Integrated Circuits**

| capture into single-chip solution                                         |    |

|---------------------------------------------------------------------------|----|

| RISC processor posts burst speeds of 50 million operations/s9             | 93 |

| 32-bit graphics microprocessor makes desktop peripherals 10 times faster9 | )4 |

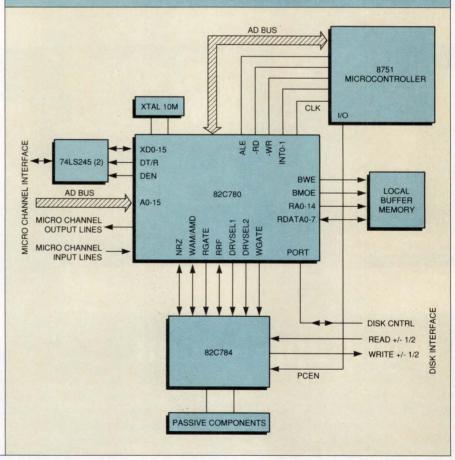

| New two-chip set shrinks Micro Channel hard disk controllers9             | 96 |

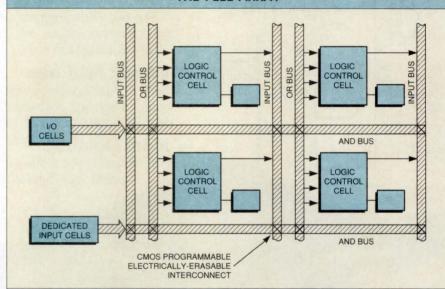

| ICT unveils high-density programmable logic architecture                  | 8  |

|                                                                           |    |

## **Design and Development Tools**

| Design tool selects PLD, partitions |     |

|-------------------------------------|-----|

| designs                             | 100 |

| Simulator accesses internal device  |     |

| registers                           | 102 |

| Hardware modeling system interfaces |     |

|-------------------------------------|-----|

|                                     | 103 |

### Computers and Subsystems

| Computers and Subsystems                    |     |

|---------------------------------------------|-----|

| RISC coprocessor gives AT a boost           | 105 |

| Intelligent NuBus I/O modules               |     |

| fit ruggedized Macintosh<br>for factory use | 106 |

| VME SCSI adapter has four-bus               |     |

| architecture                                | 107 |

## **■ DEPARTMENTS/COLUMNS**

| News Briefs       |    | 9 |

|-------------------|----|---|

| Editorial         | 1  | 4 |

| Advertisers Index | 11 | 2 |

# Get the kit. Forget You'll move a whole

INTRODUCING

THE ONE-CHIP, HIGHPERFORMANCE SOLUTION

TO FLOPPY-DISK CONTROL.

This new device is actually a complete floppy-disk controller kit in a single chip. It gives you everything you need — a precision analog data separator, pin-programmable write precompensation, and cable and bus interface buffers.

All you have to add is an address decoder, a crystal, and a few passive components.

Think of how quick and easy this kit will be to design with. The nitty-gritty work has already been done. And the DP8473 is fully compatible with the NEC µPD765A, the current industry standard. So all you have to do is drop it into your design. (And eliminate about 20 other chips.)

The DP8473 will control up to four floppy-disk drives in an IBM PC-XT,\* PC-AT,\* or any PS/2\* model personal computer.

Market State Land

THE KIT.

National's one-chip solution to floppy-disk control.

AND THE CABOODLE.

Other solutions carry a lot of excess baggage.

# the caboodle. lot quicker without it.

## QUICKER DESIGNS, QUICKER PROFITS.

In addition to your tremendous savings in real estate, your savings in raw components, inventory, and assembly could add up to more than \$10 a board. So you not only get to market sooner, you also make a quicker profit.

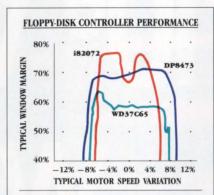

Even more important, the DP8473 gives you better performance than any other integrated floppy-disk controller solution on the market.

Unlike most competitors, its on-board data separator is analog rather than digital.

## THE QUICKER WAY TO HIGH PERFORMANCE.

Because it has the continuous tracking ability of an analog phase-locked loop, the DP8473 is less sensitive to motor speed variation and bit shift. So it has a larger dynamic window margin.

In fact, its window margin is greater than any other integrated solution on the market—analog or digital. And, of course, the bigger your window margin, the better your data integrity. And the faster the data rates you can handle.

## • ADVANCED • PERIPHERALS

No other integrated data separatoranalog or digital – can give you a 70 percent window margin at ±8 percent variation in motor speeds.

## A QUICK PATH TO THE FUTURE.

The DP8473's analog data separator can handle transfer rates from 250k up to 1M bps. And disk drives with as many as 4,000 tracks.

You may not need that capacity right now, but the next generation of low-cost floppy-disk drives is already on the drawing table. And the DP8473 is ready to handle the data rates those drives will require.

It's also manufactured using low-power CMOS technology, so it's even ready for the next generation of battery-powered laptops. In fact, the DP8473 is the floppy-disk controller used in **Compaq's** new laptop computer, the SLT/286.

## QUICK DELIVERY.

The DP8473 is in stock at your distributor now. So you can start taking advantage of its many benefits right away.

With the addition of this new floppy-disk controller, National's mass-storage chip set is now the most complete in the industry.

We can provide the ideal drive-control solution for every application — from PC to mainframe.

## NATIONAL'S MASS STORAGE FAMILY

Floppy-Disk Data Controller DP8473

Hard-Disk Data Controller DP8466A

Data Synchronizers/Separators DP8451 DP8455 DP8459 DP8461 DP8462 DP8465

Pulse Detectors DP8464B

DP8468B

2,7 Encoder/Decoder

DP8463B

Async SCSI I/O DP5380

DP8490

With data rates up to 25M bps. We also offer a complete line of hard-disk-drive support chips. For more information — quick — contact your National distributor. Or call us toll-free at 800-227-1817, ext. 17.

We have 8 CMOS PAL® chips. That totals up to 8 million different ways to program your logic. Quite enough of a choice to meet your most exacting low power logic needs. From universal PAL architectures to zero stand-by power PAL devices. You can have the system you want without compromise. And without costly delays.

Our all-purpose CMOS architectures give flexibility without draining precious power. The 24-pin industry standard

PALC22V10 uses just 90mA—even when it's running at 25ns.

If you liked us in bipolar, you should see us in CMOS.

We have five CMOS ZPAL™ devices based on familiar bipolar architectures. You can use them in battery powered and low duty-cycle applications. And they use virtually no power when in stand-by. Two versions are electrically erasable. You can get the functions you're used to and you can change your design as fast as

you change your mind.

What did you expect from the people who invented PAL devices?

The largest and most experienced Field Application Engineer force is as close as your phone all during your designin process.

Our TestPro™ Centers give you access to superior testing and programming support. Just call your AMD sales office for the center nearest you.

And we've kept the classic PALASM®

software up to date with our parts and your needs.

Most important, you can get your hands on our parts. They're all in high volume supplies.

Call (800) 222-9323. It's hard enough to get what you want in life without passing up 8,000,000 more chances.

## Advanced Micro Devices Amenolithic Memories

901 Thompson Place, P.O. Box 3453, Sunnyvale, CA 94088.

## VxWorks. More than Ready for Real-Time.

| VxWorks Believers                                        | VxWorks Advantages                               |

|----------------------------------------------------------|--------------------------------------------------|

| Amdahl<br>Supercomputing                                 | Seamless partnership with UNIX                   |

| Bendix<br>Aerospace testing                              | High-speed optimized real-time kernel            |

| Boeing<br>Flight simulation                              | Support for CISC and RISC architectures          |

| Carnegie Mellon<br>Robotics control                      | Ethernet, TCP/IP, sockets, RPC, NFS              |

| loneywell, Inc.<br>Systems research                      | Easily configurable multiprocessor support       |

| lughes Aircraft<br>Flight simulation                     | Host and target hardware independent             |

| et Propulsion Labs<br>Robotics and teleoperation         | Tailorable (kernel to complete operating system) |

| itton Industries<br>Image processing                     | Fully re-entrant and sharable code and library   |

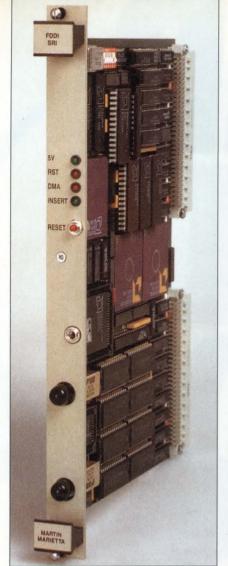

| lartin Marietta<br>Land vebicle navigation               | Over 600 callable utility functions              |

| IIT—Haystack Observatory<br>Telescope control            | Fully integrated network file system             |

| lational Bureau of Standards<br>Robotics control         | Source-level and symbolic debugging tools        |

| acific Bell<br>Network research                          | Dynamic and incremental linking and loading      |

| CA Corporation Telerobitic control                       | Support for high-level languages – C and Ada     |

| ockwell<br>Space shuttle telemetry                       | Unlimited on-line support                        |

| tanford University<br>Computing research and development | Responsive and engineering-oriented company*     |

| ektronix<br>Instrumentation control                      | rlogin, telnet, ftp, rsh                         |

<sup>&#</sup>x27;And the only one with an in-house pinball arcade!

A pplication developers designing sophisticated systems are seeking a real-time operating system that is fast, completely integrated and supported by a rich UNIX development environment.

Only one real-time operating system satisfies these requirements.

VxWorks.

But don't take our word for it. Evaluate VxWorks. Rigorously. Unmercifully. Compare it with products from Ready Systems and other competitors. Contrast it to your in-house operating system design. Then make up your own mind.

That's what the VxWorks Believers did. They compared and contrasted. They considered the performance versus effort, time and money trade-offs. Then they all selected VxWorks. Except one firm that opted to do it in-house. A year later they called back...

## for VxWorks.

Get more than ready for a revolution in real-time. Call us at 1-800-545-WIND.

Become a Believer.

Wind River Systems, Inc. 1351 Ocean Avenue Emeryville, CA 94608 CIRCLE NO. 6

## NEWS BRIEFS NEWS BRIEFS NEWS BRIEF

## Consortium to spark optical IC development

If a plan proposed by the David Sarnoff Research Center (Princeton, NJ) comes to pass, a U.S. fab will be producing optoelectronics ICs in volume by 1996. The proposed industry consortium, which requires about \$155 million in funding, was presented to 30 chip and system vendors at the Commerce Department last month.

The proposal is designed to keep U.S. production in step with similar plans in Japan and Europe. If established, the consortium would coordinate an initial research and development phase aimed at integrating the optical transmitter and receiver into a silicon VLSI chip. A second, two-year phase would focus on prototype development, and a final phase would lead to manu--John Mayer facturing.

## Arbitrator weakens AMD's hopes for 80386 rights

The battle between Advanced Micro Devices (Sunnyvale, CA) and Intel (Santa Clara, CA) over rights to Intel's 80386 microprocessor has moved a step closer to settlement with an initial ruling by arbitrator J. Barton Phelps.

In the dispute, AMD claims that terms of a 1982 technology exchange agreement give the company rights to the technology in Intel's 32-bit CPU, which AMD hoped to obtain in exchange for rights to the Quad Pixel Dataflow Manager (QPDM) chip. In the first phase of the disagreement under arbitration, Intel claimed that AMD had failed to meet its responsibilities under the agreement, thereby losing the right to 80386 data, and AMD claimed that Intel had failed to act in good faith. Both parties are claiming breach of contract.

In his initial ruling, Phelps found that AMD and Intel had in fact not reached an agreement to exchange the QPDM for the 80386 data. Further, Phelps found that Intel had failed to negotiate in good faith over the specifications of the QPDM. AMD, therefore, is entitled to some as-yet-undetermined damages, Phelps said. The judge's ruling included a statement that relief

could be in the form of money. rather than manufacturing rightsapparently putting AMD further from its goal of obtaining rights to the 80386. A final settlement of the dispute isn't expected until the end of the year. -Ron Wilson

## Joint effort yields seamless 1750A development environment

Four companies have teamed to produce an integrated environment for MIL-STD-1750A applications development. The 1750A 16-bit instruction set is mandated by the U.S. Air Force for airborne and spaceborne computer systems for avionics and control.

The catalyst for the joint effort is the Orbiter board from Sabtech Industries (Yorba Linda, CA). The Orbiter plugs into an AT-compatible platform and uses the two-chip 1750A implementation from LSI Logic (Milpitas, CA). Both board and chip set currently run at 20 MHz but are designed to go to 30 MHz. The Orbiter uses 2 Mbytes (1M 16-bit words) of dual-port RAM that can be mapped into a 64-kbyte window in PC address space. This lets the designer inject data to internal registers without the application under development being aware of it.

A complete set of real-time Ada development tools supplied by Ready Systems (Sunnyvale, CA) includes host-based CASE tools, an Ada compiler and debugger, a target-based real-time run-time environment and the RTAda/OS real-time operating system based on Ready Systems' VRTX real-time kernel. Ån 80386based laptop computer from Grid Systems (Fremont, CA) includes a two-card snap-in tray to hold the Orbiter and a bus interface card.

-Tom Williams

## ISDN alliance to boost chip integration

With the integrated services digital network (ISDN) sitting on the brink of widespread implementation, Mitel (Kanata, Ontario) and International Microelectronics Products (San Jose, CA) have announced a joint technology exchange agreement that should not only broaden access to ISDN ICs, but also speed development of application-specific products.

Under the agreement, IMP will gain manufacturing rights and act as an alternate source for four Mitel chips. The devices include an S interface chip; a D-phone, or integrated digital telephone circuit; an H-phone, or integrated digital telephone circuit with high-level datalink control; and a crosspoint switch. Mitel benefits from access to IMP's ACL1.2-DCL1.2 cell libraries and its 1.2-micron CMOS process, which IMP claims is the industry's smallest mixed analog/digital process.

But the primary dividend coming from this alliance may lie in the development of future products. Once the basic products are entered as core cells in the library, both companies will be able to reconfigure the four Mitel chips. And both companies will codevelop macrocells to augment their design libraries for voice and data communications. "The real benefit will lie in our continuing cooperation in developing the macrocell library," says John Freeman, vice-president of marketing for Mitel's Semiconductor -John Mayer Division.

## Analogy links Saber analog simulator with digital simulators

Analogy (Beaverton, OR) has reached agreements with Gateway Design Automation (Lowell, MA) and Genrad (Concord, MA) to link Analogy's Saber analog simulator with Gateway's Verilog and Genrad's Hilo digital simulators. Under the agreements, Saber will be linked with Verilog and Hilo in much the same way that it's currently linked with the Cadat digital simulator from HHB Systems (a subsidiary of Daisy Systems of Mountain View, CA).

These agreements help support Analogy's claim that Saber is the "emerging standard" among analog simulators. With links to Cadat, Verilog and Hilo, Saber now supports mixed-mode simulation with the digital simulators that control 90 percent of the stand-alone digital simulator market, according to

(continued on page 10)

## NEWS BRIEFS NEWS BRIEFS NEWS BRIEF

(continued from page 9)

Doug Johnson, Analogy's vice-presi-

dent of marketing.

Saber also provides analog simulation capability to a number of other companies, including Valid Logic Systems (through Valid's acquisition of Analog Design Tools, a Saber user), Racal-Redac, Computervision, NCR and Schlumberger.

-Bill Harding

## GaAs op amp soars to 10 GHz

Engineers at Hughes Research Laboratories (Malibu, CA) have shattered previous op amp bandwidth specs with a gallium arsenide device that posts a 10-GHz unity gain bandwidth. Designed for use in high-speed data converters and line drivers, the amp shows a better than threefold performance improvement over existing devices.

Advances in MESFET processing let designers overcome typical GaAs problems of excessive backgating, low intrinsic transistor gain and light sensitivity. The new device uses a low-temperature buffer grown directly underneath the active channel to eliminate backgating and light sensitivity while improving intrinsic gain. Transistors on the chip are connected with air bridges to hold down overall circuit capacitance, and a single high-gain differential stage is used to maximize bandwidth. -Mike Donlin

## Backplane bus daisy chains instruments

Although very similar to VMEbus, the MXIbus to be introduced this month by National Instruments (Austin, TX) differs in that it's multiplexed. MXIbus combines the GPIB form factor with the VME communication protocol—the reverse of VXIbus. But it extends VXIbus across multiple instruments and directly and transparently couples the VXIbus to industrystandard personal computers and other instruments that won't fit on a VXI module.

MXIbus has all of the advantages of an embedded VXIbus CPU, but at a much lower price, according to Ron Wolfe, strategic marketing manager at National Instruments. "MXIbus maps the hardware memory addresses of several systems together so that the individual systems think that they are one big system," he says. "And because the systems don't have to contend with communication protocol software, MXIbus obtains high performance at a relatively lower

The first modules for this bus, not available before July, will consist of an MXI-VXI interface board and an AT-MXI interface board. Wolfe indicated that other bus interfaces can be expected in the future.

-Sydney F. Shapiro

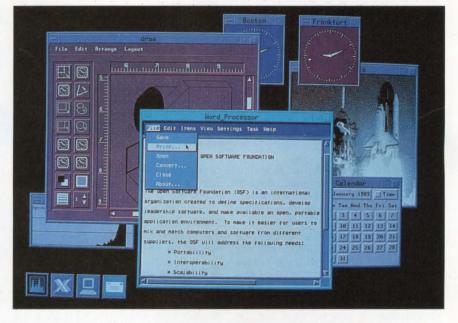

## On Technology and Nixdorf join Apollo's NCS bandwagon

Apollo Computer (Chelmsford, MA) has won two more converts for its Network Computing System (NCS). Nixdorf Computer (Waltham, MA) and On Technology (Cambridge, MA) are the latest in a large group of companies (including IBM, Digital Equipment Corp and Hewlett-Packard) to adopt what Apollo calls "the standard for creating open multivendor computer networks.'

Apollo has offered NCS to the Open Software Foundation (OSF) as a base technology for the OSF open software environment. If chosen, the NCS influence would be widespread. -Bill Harding

## Neural net software lowers entry costs

Many of those who would like to explore the possibilities of neural networking have been put off by the high entry costs involved. Now, however, neural net pioneer Hecht-Nielsen Neurocomputers (San Diego, CA) has broadened the potential user base by introducing neurocomputing software packages that run on the omnipresent Sun family of workstations.

Although the Sun hardware is unlikely to run many neurocomputing applications optimally without the assist of a special-purpose coprocessor, the relatively low entry costs of a software-only solution

should help justify a lot of new development activity and bring many programmers up to speed. -David Lieberman

## SBX PC comes to life

While it's not at all unusual when a board company builds a PC clone, a new entry from Zendex (Dublin, CA) breaks new ground by putting its PC on a little SBX module. The SBX, a daughterboard interface originally developed by Intel for Multibus I, has found long-term success among a number of buses, most particularly for prototyping purposes and easy customization of singleboard computers.

The concept of the SBX PC has been around for several years. Today's technology makes it feasible. and today's market makes it worth implementing. The rampant activity in PC clone chips has given designers the needed functionality per square inch, while advances in application-specific ICs, packaging and board technology have further expanded their potential to overcome real-estate constraints.

- David Lieberman

## Growth slows in office and computing equipment

Office and computing equipment sales in the United States grew by 7.6 percent—the lowest growth since 1972—according to figures released by market watcher In-Stat (Scottsdale, AZ). If it continues, the reduction in growth could have profound effects in the industry.

On the positive side, office and computing equipment vendors are major consumers of dynamic RAMs, and a softening in the demand for their equipment could ease DRAM availability problems for everyone. On the negative side, these same vendors are also consumers of a spectrum of other ICs, boards and modules that provide much of the industry's revenue.

A sustained slowing in the sales of office and computing equipment could put pressure on research and development, slow introduction of new ICs, and threaten the viability of some companies that have become overly dependent on a -Ron Wilson single market.

# WHEN YOU INSTALL THE NETWORK AT THE WORLD ENTERPRISE NETWORKING SHOW, YOU'D BETTER MAKE SURE IT WORKS.

When Deere Tech

Services of Moline, III., took

part in installing the demonstration network at the

1988 Enterprise Networking Show, they knew that

for the event's five days the

network had to be faultless.

So they used an Excelan

LANalyzer\* to set up,

troubleshoot and monitor it.

Deere Tech Services knew that few companies have as much experience in connecting heterogeneous systems as Excelan.

And that Excelan's LANalyzer would be up to the lob.

The Baltimore show's network was based on the Manufacturing Automation Protocol (MAP) running on broadband and the Technical and Office Protocol (TOP) running on Ethernet.

### UP AND RUNNING.

It had to support large numbers of systems running several different protocols, all needing to be up and running in days.

But because LANalyzer, with it's mouse and menu driven interface, is extremely easy to use and provides high performance under heavy traffic, the network was ready in time for the show.

All of this was accomplished, because LANalyzer

The brands or product names mentioned are trademarks or registered trademarks of their respective holders.

provides such features as simultaneous data capture and display, flexible multichannel filtering, and summary real-time monitoring, along with the ability to decode network protocols including TCP/IP, DECnet, AppleTalk and XNS.

### PERFORMANCE NOT PROMISES.

The end result was that for the full five days of the show the network performed faultlessly with no downtime.

It's no wonder that many LANalyzer customers are repeat purchasers. Excelan's LANalyzer provides a user friendly, cost effective method of network analysis. And it's available as a stand alone unit or as a kit which can be installed in any IBM PC/AT or compatible.

And best of all, LANalyzer is made by the company that networks networks. Excelan.

To find out how the LANalyzer can solve your network problems, and to receive a free demo diskette, call 1-800-243-8526. Or write to us at 2180 Fortune Drive, San Jose, California 95131.

**EXCELAN**

WE NETWORK NETWORKS.

**⊕ EXCELAN**

Ф OS/2 Ф EXCELAN

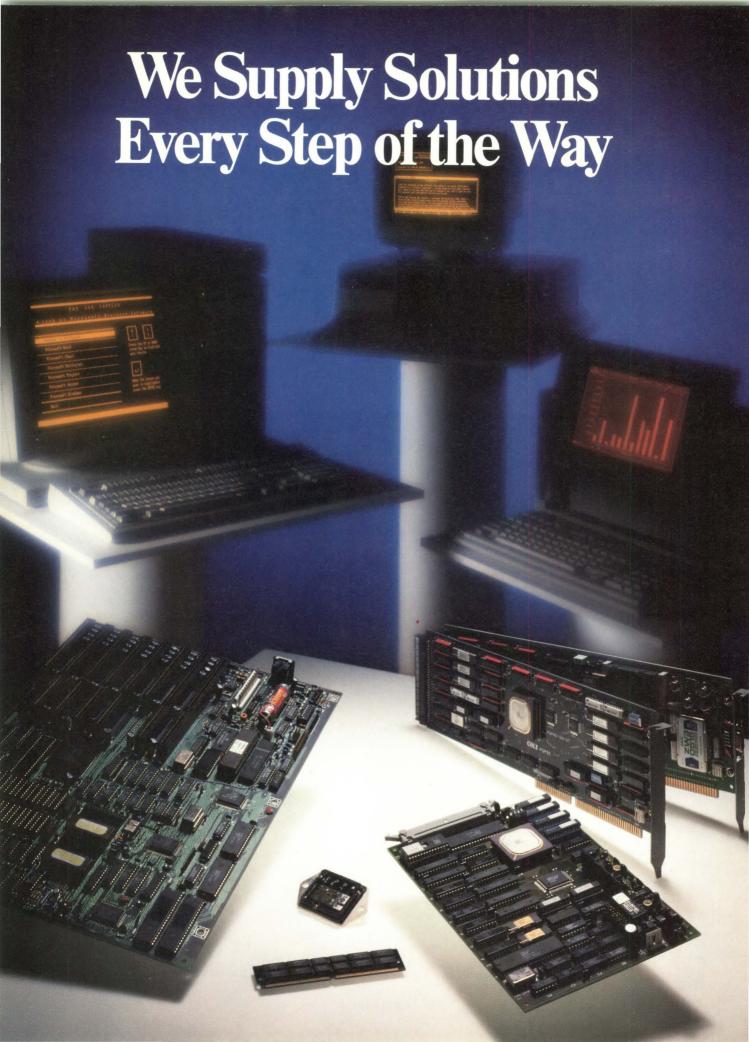

## From single ICs to board-level development, Oki's systems approach gives you a competitive edge

Oki Semiconductor offers you a unique array of products, leading-edge technologies, and comprehensive support services. But what really sets us apart is our unique way of applying them. We call it *System Technologies for Customer Solutions*.

## Oki systems thinking

Rather than just taking your order as other suppliers might do, we join with you as a partner and work to understand your product concept as a whole, before determining its component technologies. Then to meet your goals, we draw on a tremendous range of expertise and worldwide resources others simply cannot match.

## Expertise at every level

As the only company that can deliver standard IC, ASIC, packaging, and value-added capabilities *from a single source*, we can uncover options and alternatives at many levels of system development and fabrication—opportunities others would not perceive. So we can assist you with everything from single ICs to value-added products, at any stage you require.

The result of this integrated, single-source approach is a solution that's precisely tailored to your needs. A solution that can help you achieve real competitive advantages—by speeding product development, getting you to market faster, lowering costs substantially, enhancing your product with new features, or making production more efficient.

## Partnerships that work

Unlike many companies, Oki is willing to share resources to co-develop products and technologies. We back this commitment with comprehensive design and support tools, as well

as highly capable people who help you make the most of our resources. If you'd like to gain the kind of competitive edge Oki customers already enjoy, call us today or complete and mail the coupon below. And find out how Oki's unique blend of partnership and systems thinking can make a real difference for you.

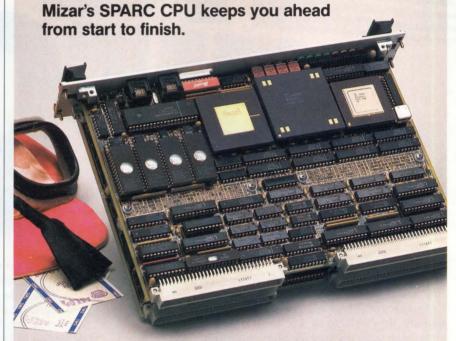

|                                                           | om start to finish. unical information on Oki products                                                      |  |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--|

| ☐ Memory<br>☐ DSP<br>☐ Microcontrollers & microprocessors | ☐ ASICs ☐ Board-level solutions ☐ Packaging capabilities                                                    |  |

| Business Phone Name                                       |                                                                                                             |  |

| Title                                                     |                                                                                                             |  |

| Corporate Customer Ser                                    | ss card or letterhead and mail to:<br>vice, Oki Semiconductor, 785 N. Mary<br>94086. Phone: (408) 720-1900. |  |

An interpretation of "look and feel" should take into account the needs of both software users and software developers.

John C. Miklosz Associate Publisher/ **Editor-in-Chief**

## Look, but don't touch?

he dance card at the "look and feel" ballroom keeps getting crowded. Apple Computer is suing Microsoft and Hewlett-Packard; Lotus Development is suing Paperback Software International and Mosaic Software; Ashton-Tate is suing Fox Software; and in an ironic "twist," the developers of Visicalc are chasing after Lotus for the same reason Lotus is after Paperback Software and Mosaic. Each of the aggrieved parties is claiming copyright protection for what's come to be known as the "look and feel" of their respective software creations.

On one level, look and feel can apply only to the obvious user interface with a software package—that is, what the user sees on a display and how he or she provides input. Displaying information in a particular style of window, using a trash can as an icon and pointing to it with a mouse are examples, and they're what Apple Computer's suit is all about. On a deeper level, look and feel is also being used to describe clone software that has essentially the same user interface. logical constructs, language syntax, and algorithms as the original. Clones of this type—or perhaps we should avoid the euphemism and say copies—are at the heart of Lotus's and Ashton-Tate's suits.

The distinction is important because in the first case, a broad selection of products with identical, or similar, look and feel to the user interface directly benefits the end user. I underscored that point in an earlier editorial (see Nov. 15, 1988), when I described our experiences with a number of software packages developed to work with Ventura Publisher. (We still haven't found any with the same look and feel). It's the look and feel of the user interface—even for applications where the logical constructs, language syntax, algorithms, and so forth may be as different as those needed for a pagemakeup package compared to those needed for a relational data base that's at the heart of the Macintosh's success. That look and feel is still missing in the MS-DOS world, even though the seeds have been there in Microsoft's Windows (a threat that Apple is now addressing) and Digital Research's GEM (too little penetration to be a threat).

In the second case, users also benefit. Clones—or copies—that essentially duplicate every aspect of the originals are always cheaper than the originals. That's as true for software as it is for literature, art and designer clothes. But the cloner also benefits because he's saved the inspiration and perspiration (that is, time and money) that the creation of a truly original product requires. Let's all be honest and admit that cloning at this level isn't being done for the greater good of the user but, rather, for the good that comes to the cloners from greater profits.

With an interpretation of look and feel that takes into account both the needs of software users and those of software developers for copyright protection (that is, Apple should lose its suit, but Ashton-Tate should probably win), we'll ultimately end up with a much broader range of products that are all much easier to use.

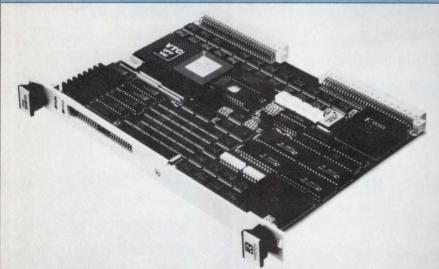

## Check DY-4 for the widest choice in VIME commercial, ruggedized and Mil-Spec NDI

OF-4 offers the widest variety of Non-Developmental Items (NDIs) right across the board: commercial NDIs for developmental projects; ruggedized NDIs; and Mil-Spec NDIs fully compliant with MIL-E-4158, 5400, and 16400 specs.

All DY-4 NDIs are manufactured in accordance with AQAP-1 and include advanced features like built-in test and system-level diagnostics.

For the most and the best NDIs, call DY-4 — one of the world's leading suppliers of board-level products for commercial and military applications.

California: (408) 377-9822 Los Angeles: (714) 549-2559 Washington: (301) 964-5554 Massachusetts: (508) 692-9308 Canada: (613) 596-9911 Denmark: (06) 963824 Germany: (089) 903 9206

**CIRCLE NO. 9**

| PRODUCT                              | COMMERCIAL | RUGGEDIZED | MIL-SPEC |

|--------------------------------------|------------|------------|----------|

| Single Board Computers (680x0/88000) | V          | V          | v 1      |

| Military / Communications Interfaces |            |            |          |

| MIL-STD-1553 B                       | V          | ~          | ~        |

| NTDS (Serial and Parallel)           | ~          |            | 1977     |

| Digital-to-Synchro                   | ~          | V          |          |

| Digital-to-Resolver                  | ~          | ~          |          |

| Synchro-to-Digital                   | ~          | ~          |          |

| Resolver-to-Digital                  | V          | V          |          |

| ARINC 429 / 561                      | ~          | V          |          |

| Memory Modules                       |            |            |          |

| SRAM                                 | ~          | V          | ~        |

| EPROM                                | ~          | ~          | ~        |

| EEPROM                               | ~          | ~          | ~        |

| DRAM                                 | ~          | V          | V        |

| System Controllers                   | V          | ~          | ~        |

| Serial I / O                         | ~          | V          | ~        |

| Intelligent Serial I / O             | ~          | V          | ~        |

| Parallel I / O                       | ~          | ~          | ~        |

| Analog-to-Digital                    | V          | ~          | ~        |

| Digital-to-Analog                    | ~          | ~          | ~        |

| Graphics Engines                     |            |            |          |

| Medium Performance (34010)           | ~          | V          | ~        |

| High Performance (68020 / QPDMs)     | ~          | ~          |          |

| Very High Performance (RISC / QPDMs) | V          |            |          |

| IEEE-802.3 LAN                       | ~          | V          |          |

| ANSI X3T9.5 LAN (FDDI)               | ~          |            |          |

| SCSI                                 | ~          | ~          | ~        |

| SASI                                 | ~          | ~          |          |

| 9-Track Tape Controller              | ~          |            |          |

| Relational Database Processor        | ~          |            |          |

| Chassis Systems                      | ~          | ~          | ~        |

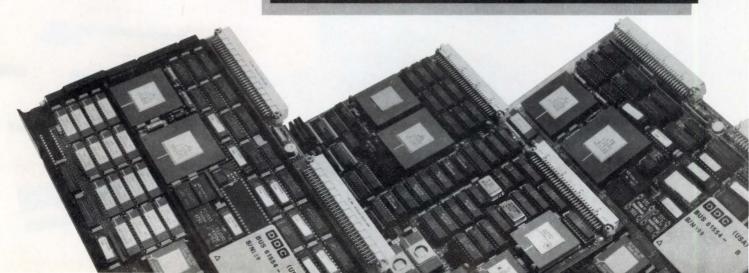

## TEXAS INSTRUMENTS REPORTS ON

## HIGH-PERFORMANCE

IN THE ERA OF MEGACHIP™ TECHNOLOGIES

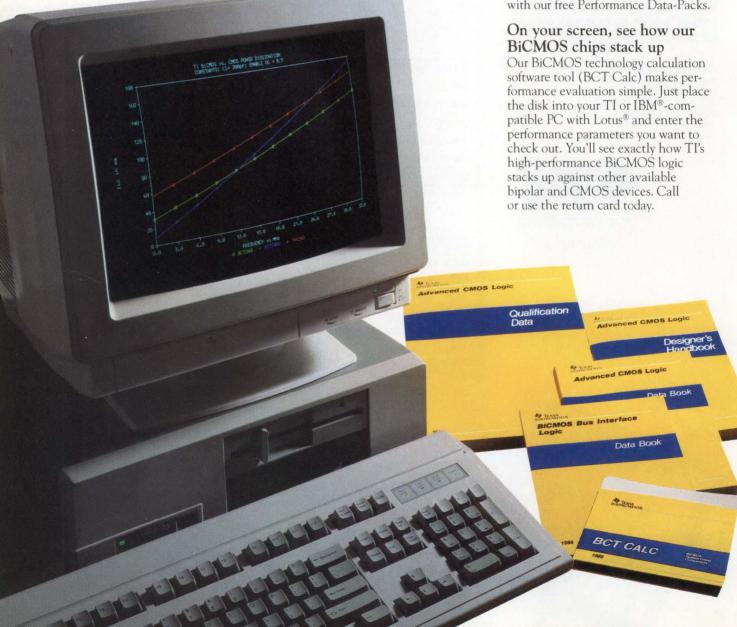

Speed, power, drive, noise — system logic design can be a long series of trade-offs. To put the odds in your favor, get our free BiCMOS and ACL Performance Data-Packs.

oosting system performance and cutting power consumption is a common design goal, but getting there needn't involve as many trade-offs as it used to. Because now, Tl's BiCMOS and Advanced CMOS Logic (ACL) families combine the speed and drive you need with low-power operation and enhanced signal integrity. We want to prove it to you with our free Performance Data-Packs.

## LOW-POWER LOGIC

TI's BiCMOS logic: Use it to cut power without compromising performance By combining bipolar and CMOS technologies, TI BiCMOS gives you

the best of everything.

Switching speeds are comparable to advanced bipolar devices. You get the 48/64-mA drive current needed for high-capacitive loads and backplanes. This meets the drive requirements of industry-standard buses such as Multibus® and VMEbus™.

Yet TI's BiCMOS family can reduce disabled currents as much as 95% and active currents as much as 50% compared to bipolar equivalents. As a result, total system power savings can be more than 25%.

TTL I/O provide enhanced signal integrity, power-down backplane interface, and backplane-level standards.

There are more than 60 members in the BiCMOS family, including 8-, 9-, and 10-bit latches, buffers, drivers, and transceivers—whatever you need to make your bus-interface design a highperformance reality.

Again, check it all out for yourself with our BiCMOS Performance Data-Pack.

## TI's EPIC ACL logic family: Use it to keep performance up and squelch "ground bounce'

This is the first advanced CMOS logic family designed to improve system performance while reducing the simultaneous switching noise or

"ground bounce."

Performance is comparable to advanced bipolar devices, supporting frequencies up to 125 MHz and providing the 24-mA output capable of driving 50-ohm transmission lines. It's a perfect match for core and local bus interface.

The family is fabricated using TI's EPIC™ one-micron CMOS process, so power consumption is the lowest of any CMOS family, essentially zero standby.

Noise levels are as much as 50% lower compared to conventional advanced CMOS logic. That's because TI's family has two distinctions going for it: Innovative packaging and a circuit-design technique called OEC (Output Edge Control) that smooths the sharp edges of the output waveform which are a major cause of simultaneous switching noise.

A unique pinout arrangement creates a "flow-through" architecture. This simplifies board design and can save up to 32% in board space because you don't need passive components to control noise as you usually do with

end-pin devices.

TI's more-than-300-member family includes versions compatible with CMOS and TTL voltage levels. Simulation models are available for both BiCMOS and ACL devices. • TLACL Data Book that contains detailed specifications and applications information on family members. • TI ACL Qualification Data that provides reliability and characterization data, die photos, and application derating factors. It's all free and it's all yours by making a call or by completing the return card, today. ™ MegaChip, EPIC, and OEC are trademarks of Texas Instruments Incorporated

Call 1-800-232-3200,

Inquiry 3004, for your free

BiCMOS Performance Data-Pack on

formance calculation software and our

Our ACL family Performance Data-

its way to you. Included are our per-

BiCMOS data book and product

• TI ACL Designer's Handbook that

describes methods for handling the

technical issues facing advanced-logic

bulletin.

Pack includes:

design engineers.

Performance Data-Packs

A call or a card will start your

**CIRCLE NO. 12**

08-8451

® IBM is a registered trademark of International Business

Machines Corporation. Lotus is a registered trademark of Lotus Development Corporation. Multibus is a registered trademark of Intel Corporation.

© 1989 TI

VMEbus is a trademark of Motorola, Inc.

## VME I/O **THAT GROWS** WITH YOU.

Start with just a few digital or analog I/O channels and grow to over a 1000. Burr-Brown's affordable. expandable MPV940 Series brings intelligent VMEbus I/O interfacing to process control, robotics, simulators, data acquisition and more. The MPV940 controller serves as a stand-alone computer, as a monomaster VME system or as a Master/ Slave in a multi-processor configuration. RS232 or VMEbus control and software loading. Compatible with Burr-Brown's PCI-20000 termination panels. Call or write for MPV940 facts, plus new full-line catalog: Burr-Brown Corporation, 1141 W. Grant Road, MS#131, Tucson, AZ 85705. (602) 746-1111.

@1988 5800-8155

**CIRCLE NO. 10**

MPV940 10 MHz 68000 CPU Controller board can be fitted with two Burr-Brown analog or digital multichannel I/O modules and still occupy one VMEbus slot. MPV941 Analog I/O MPV942 Digital I/O expansion board proexpansion board provides 128 input chanvides 32 I/O lines plus nels & 8 output 32 input lines with channels. change of state monitor.

## Eliminate the Jitters.

With VideoWindows, turn any IBM PC into a real-time, framegrabbing, interactive digital video system and eliminate the interlaced video jitters. Affordably.

> Combine any two video sources with VGA or EGA graphics on your

Multiple windows of digital video. Graphic overlays. No jitter.

60Hz RGB monitor without jitter. Position multiple video windows - any size, anywhere. Create computer-controlled transitions, zooms, pans, and fades.

> Digital video technology makes it flexible. New Media Graphics makes it affordable.

## VideoWindows®

New Media Graphics 780 Boston Road Billerica, MA 01821 (508) 663-0666

**CIRCLE NO. 11**

## COMPUTER

### **PUBLISHER**

David L. Allen (508) 392-2111

### ASSOCIATE PUBLISHER/EDITOR-IN-CHIEF

John C. Miklosz (508) 392-2114

### **TECHNOLOGY EDITORS**

Ron Wilson, Integrated Circuits (503) 224-9396 Warren Andrews, Integrated Circuits (201) 825-1317 Bill Harding, Design & Development (408) 729-1005 David Lieberman, Computers & Subsystems (508) 392-2117

Tom Williams, Software, Graphics & Imaging (408) 335-5514

John H. Mayer, Computers & Subsystems (508) 392-2118

Sydney F. Shapiro, Data Acquisition & Control (508) 392-2116

### CONTRIBUTING EDITORS

Ernest Meyer, Design & Development (408) 378-6241 Howard Falk, Software (201) 783-4050

## RESEARCH/SPECIAL PROJECTS MANAGER

Sydney F. Shapiro (508) 392-2116

## SECTION/SPECIAL PROJECT EDITORS

Ron Wilson, Technology Updates (503) 224-9396 Michael G. Donlin, New Products (508) 392-2123 Patti Kenney, Directories (508) 392-2124

MANAGING EDITOR: Susan R. Nykamp

ASSISTANT EDITOR: Kerstin R. Feldman

COPY EDITOR: Barbara-Ann Scofidio

EDITORIAL ASSISTANTS: Claire Coupal, Claire Ellis

ART DIRECTOR: Jan Horner **ILLUSTRATOR:** Fred Lomas

PRODUCTION DIRECTOR: Jan M. Lopez PRODUCTION MANAGER: Mari Rodriquez ADVERTISING COORDINATOR: Adrienne Adler COVER ART: Sergio Roffo

CIRCULATION DIRECTOR: Robert P. Dromgoole

**Advanced Technology Group** L. John Ford, Senior Vice-President Leslie P. Cypret, Vice-President, Administration One Technology Park Drive P.O. Box 990 Westford, MA 01886

Tel: (508) 692-0700 Fax: (508) 692-0525

Postmaster: Send change of address form 3579 to COMPUTER DESIGN, Circulation Department, Box 3466, Tulsa, OK 74101

**NEW MEDIA GRAPHICS**

A MATRIX COMPANY

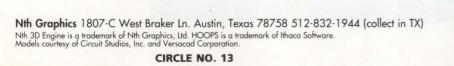

## BRINGING WORKSTATION 3-D GRAPHICS TO THE PERSONAL COMPUTER.

## **NTH 3D ENGINE.**

## Interactive 3-D Performance on a PC

- Fast 10 MIPS, 3 MFLOPS Graphics Processor on the Board

- 2nd Pipelined Processor Coupled with Custom ASIC for Fast Rendering

- •Resolutions from 640 x 480 up to 1280 x 1024

- •256 Colors from a Palette of 16.8 Million

- Standard On-Board 3-D Display List and Optional Z-Buffer

- On-Board Hardware Floating Point Math

## Realistic Display of Complex Objects and Data

- Flat Shading at a Continuous 5000 polygons/sec

- Gouraud Shading at a Continuous 3000 polygons/sec

- •3-D Vectors Transformed at a Continuous 40,000/sec

- •2-D Vectors Transformed at a Continuous 50,000/sec

## Complete with Powerful HOOPS Graphics Software Tool Kit - On the Board

- Full DOS 640k Available for Application Software

- Object-Oriented with Hierarchical Segmented Object-Oriented Database

- Hidden Surface and Line Removal, Smooth and Flat Shading Routines, Multiple Light Sources, Transparency, Built-in Windowing and Picking, Event Manager, and a lot more

- Bindings for "C", FORTRAN and Pascal Easy to Interface

Prices Start at \$6995

For More Information, Call 800-624-7552

## INTEGRATED CIRCUITS

## 80860 CPU positions Intel to take on minisupercomputers

Ron Wilson, Senior Editor

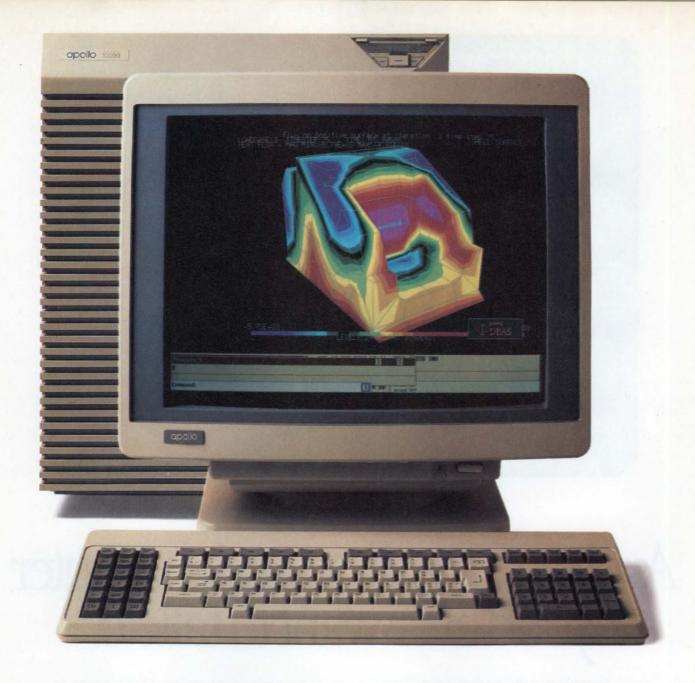

he first thing that catches one's attention about the Intel 80860 CPU-formerly known only by rumor as the N10-is the sheer size of the numbers involved. Numbers such as 120 million operations/s, 90,000 Dhrystones or 21 Linpack MFlops sound as if they belong in the supercomputer world, not the microprocessor world. And numbers such as 1 million transistors on a single die sound as if they belong in science fiction. Yet the 80860 CPU is real, and in the hands of selected beta sites, according to Intel (Santa Clara, CA). The new processor, which can be used as either a Unixbased host CPU or a dedicated application engine, is likely to change one branch of computing forever.

That branch is personal supercomputing, the territory originally outlined by mini-Cray vendors, explored by startups like Ardent Computer (Sunnyvale, CA) and Stellar Computer (Newton, MA), and recently invaded by the high-end DN10000 from Apollo Computer (Chelmsford, MA). In this arena, enormous floating-point programs analyze mechanical structures, predict fluid flow or simulate airframes. Users interact with these huge programs through dynamic three-dimensional renderings on high-res-

olution displays.

The superworkstations that serve this market must provide a fast Unix platform, tremendous floatingpoint throughput and prodigious 3-D drawing capability. It's not unusual for such systems to offer 5 to 10 Linpack MFlops and to be able to draw 150,000 3-D polygons/s.

## A chip for supercomputing

In the past, superworkstations generally contained at least three discrete processors: an integer CPU implemented with either a RISC microprocessor or a multichip proprietary design, a vector processor based on a specialized floating-point chip set, and a proprietary graphics board usually built from semicustom VLSI. Naturally, such a processor

cluster was expensive, and the number of interconnections between chips, or even boards, in the design built unavoidable delays into execution cycles.

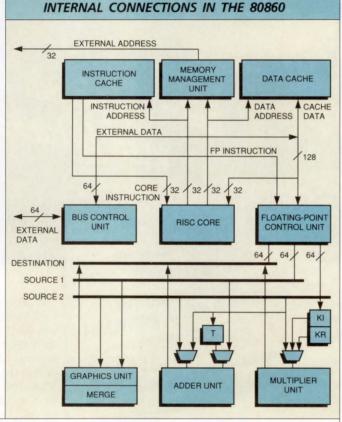

But the new Intel part offers to change this architecture entirely. Taking a cue from the multipleexecution design of the Apollo DN10000, the 80860 CPU contains three execution units, two register files, an 80386-compatible memorymanagement unit and a set of large caches on a single, million-transistor die. The result provides a cost and space savings, but more important, the ability for the entire multiunit

processor to execute at 40 MHz or more over large sections of code, translating high peak Mips numbers into staggering benchmark results.

Where multiboard processors have been achieving 10 Linpack MFlops, the single-chip 80860 reportedly hits 21. Where separate proprietary graphics pipelines generate 150,000 polygons/s, a single 80860 CPU achieves 50,000 triangles/s, a somewhat comparable measure of transformed drawing speed. Since polygon generation seems to be an application that adapts well to parallelism, multi-80860 graphics accelerators could go well into the hundreds of thousands of polygons per second.

## Not RISC, but RISC-like

Two sets of concepts are fundamental to this sort of execution speed. First, the 80860 relies on RISC concepts such as simple, one-cycle-per-

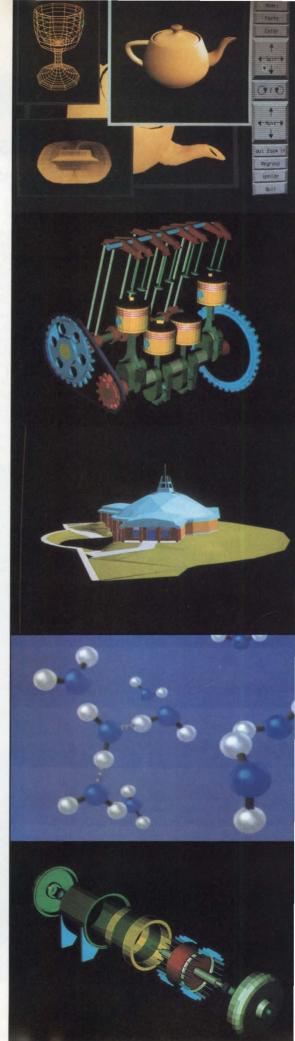

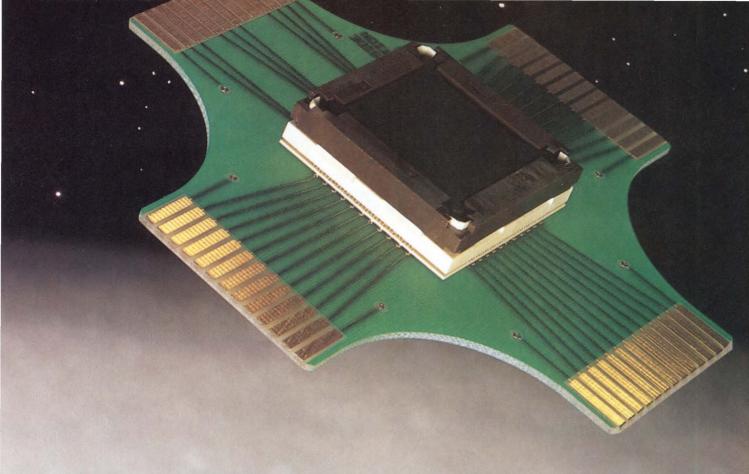

The Intel 80860 CPU packs 1 million transistors onto a 10- × 15-mm die. About a third of the die is used for the RISC-like integer unit, a third for the vector floating-point hardware, and a third for instruction and data caches.

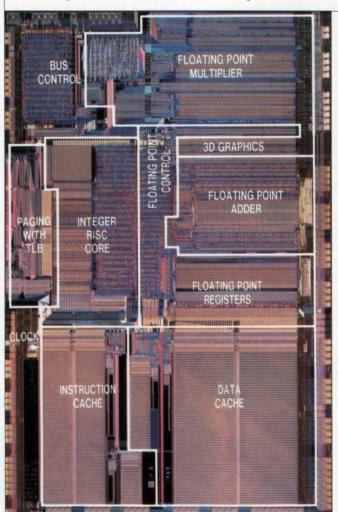

You've always known about Hitachi's well-deserved reputation for high quality, high reliability disk drives. Now, there's more good news. It's the *super-high density DK515-78 780MB 5.25-inch drive*, the latest addition to Hitachi's comprehensive selection of Winchesters, magnetic tape subsystems and ultra-high density optical disk drive subsystems.

The performance you want.

Our new DK515-78 5.25-inch drive has it all. It features a full 780MB of storage capacity, lightning fast 16ms average access time, and a blazing 2.4MB/sec. data transfer rate. Plus, it offers a choice of SCSI or ESDI interfaces.

The reliability you demand.

When you specify Hitachi, you get more than high performance. You get unbeatable Hitachi reliability. Our DK515-78 is designed and manufactured to use our own motors, heads, microprocessors and LSIs. In-house design and production of all these major components and the most stringent quality assurance program in the industry, gives the DK515-78 a remarkable 40,000 hour MTBF.

The partnership you can trust. Do business with Hitachi, and you won't get stuck with yesterday's news. You'll get a reliable business partner who can deliver the drives you need, when you need them. Next time, specify Hitachi.

Fast Action:

To get information or product literature immediately, CALL TOLL FREE 1-800-538-8157, Ext. 877. In California, 1-800-672-3470, Ext. 877. Ask for literature number APB-002.

Regional Sales Offices: Waltham, MA 617/890-0804, Dallas, TX 214/991-7983, Brea, CA 714/993-1610, San Bruno, CA 415/872-1902.

Hitachi America, Ltd. Computer Division 950 Elm Avenue, Suite 100 San Bruno, CA 94066

## INTEGRATED CIRCUITS

instruction design to achieve high clock frequencies and high execution rates in the integer execution unit. "We don't view RISC as an architecture, but rather as an idea," claims Bill Rash, microprocessor marketing manager at Intel. "In the integer unit, we use one-clock instructions, delayed branches and a load-store units. This concept, which has been gaining popularity since the introduction of the multichip Apollo DN10000 CPU last year, simply observes that, at a given clock frequency, the Mips can be doubled if two instructions are executed at once.

Of course, in practice it's not as easy as that. The CPU must be able

actual application codes is more than a matter of execution-unit design. In a multiple-execution-unit CPU, the bandwidth necessary to keep instructions and data moving through the execution units can be a more serious problem than the instruction execution times. Consequently, the Intel design team lavished effort and silicon on the network of caches. register files and buses that surround the execution units.

The most obvious result of this attention is in the third of the die dedicated to caches. The 80860 uses a pair of 32-bit caches: an 8-kbyte data cache and a 4-kbyte instruction cache. "It was important at these speeds not to restrict the cache bandwidth by making an off-chip connection," claims Rash. "So we simply put in as much cache as we could on a manufacturable die." The importance of having the caches on-chip becomes obvious when one looks at the way these memories are connected to the execution units: the 64bit path for the instruction cache and 128-bit path for the data cache would have put impossible strain on the pin count of any reasonable package.

In fact, the 80860 uses wide internal data paths heavily. While the RISC core processor works on 32-bit integers, the floating-point unit and its register file are 64-bit, as is the graphics execution unit. These devices are interconnected by a lattice of 64- and 128-bit paths. "One of our foremost challenges was sustaining the floating-point performance," says Rash. "We learned from the example of discrete floating-point units that offer high instantaneous speed but lack the I/O bandwidth to keep themselves fed."

The thicket of data paths on the 80860 can provide an instruction each to the integer and floatingpoint units, an operand to the integer unit, and two operands to the floating-point unit, while returning a result to the floating-point register file, on each cycle. That works out to an aggregate on-chip bandwidth of nearly 1 Gbyte/s.

The internal data paths can keep all the execution units fed as long as data and instructions are coming from cache. But in the event of a cache miss, the microprocessor is dependent on its external bus. Here,

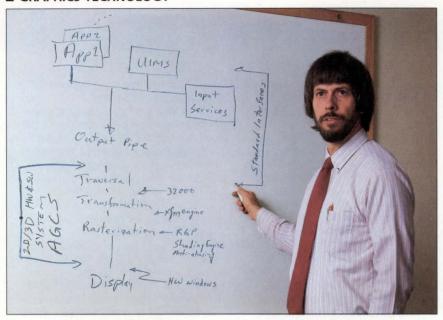

Much of the benchmark performance of the 80860 is due not to the speed of the execution units, but to the bandwidth of the on-chip data paths. Internal connections let the integer and floatingpoint units run concurrently, taking an instruction and a set of operands on each clock cycle.

architecture with a file of thirty-two 32-bit registers."

But Rash goes on to explain that the 80860 departs from pure RISC ideas in many ways. As examples, he cites the extensive floating-point hardware, which takes up about a third of the die area, and the dedicated graphics hardware. The graphics unit, which shares the floating-point data paths, performs pixel filling, Zbuffering and other hard-to-simulate operations in hardware. "The important thing is not that the instruction set is reduced, but that it supports real languages for real applications," Rash says.

Second, and equally important to the 80860's high processing speed, is the notion of multiple execution

to fetch two instructions at once and be sure that the instructions are independent: that one doesn't require data produced by the other. The 80860 normally fetches one 32bit instruction at a time from its instruction cache, but it has an operating mode in which it, like the Apollo DN10000, fetches an integer instruction and a floating-point instruction in one 64-bit cycle. These two instructions then execute in parallel in their separate pipelined execution units. Once the instructions are fetched, though, keeping things running gets complicated.

### Managing bandwidth

The ability to achieve sustained performance on complex benchmarks or

## INTEGRATED CIRCUITS

too, Intel has paid attention to speed. The external bus is 64 bits wide and provides a next-cycle-in-page signal for static-column dynamic RAMs. In addition, the bus has a pipelined operating mode that lets three read operations be pending at once. This gives the DRAM six clocks, or 150 ns at 40 MHz, to respond and keeps the bus controller running at full speed. But it does mean that for operations on large data sets, where operands will have to come from memory instead of cache, the 80860's throughput will drop substantially.

But is it manufacturable?

The greatest question hanging over the 80860 has to be manufacturability. At 1 million transistors on a  $10-\times15$ -mm die, the part is probably the densest nonmemory standard product ever introduced. Yet the die isn't all that large, and the process is already well-characterized. "It's the same 1-micron process we use for the 80386," explains Rash. Certainly, Intel doesn't have a history of manufacturing failures.

As further proof of the company's confidence. Intel sources claim that 80860 beta units are already in the hands of selected accounts, and that much of the system software is already completed or in development. C and Fortran compilers and a Fortran vectorizer are said to be available, and a multiprocessing version of Unix System V release 4 is also underway.

Rash claims that the chip is already designed into some graphics accelerator applications where Unix availability wasn't a gating factor. This raises the possibility that in terms of actual application starts, as opposed to CPU-on-a-board products, the 80860 may be as far along as the Motorola 88000 or any of the newer Sparc chips. In terms of product availability, at least, the picture is good: 33-MHz samples are available, with production at that speed expected in the third quarter of 1989. Samples at 40 MHz should be available in the second half of 1989.

Taken in perspective, though, the 80860 isn't a direct challenge to most of the 32-bit RISC microprocessors on the market. Many of those chips are simply incapable of achieving the floating-point and graphics performance offered by the Intel de-

sign. Instead, the 80860 should thrive in the area of personal supercomputers, a market now dominated by proprietary multichip CPU designs with separate, multichip floating-point units and graphics processors. In its chosen area, the new Intel device should completely change the economics of workstation For more information about the technologies, products or companies mentioned in this article, call or circle the appropriate number on the Reader Inquiry Card.

**Apollo Computer** 08) 256-6600, ext. 7702..... Circle 316 **Ardent Computer** (408) 732-0400 Circle 317 (408) 765-4851 Circle 318 Stellar Computer

# Does your windowing package leave you hanging?

Frustrated with the limitations of your windowing package?

ÆWINDOS is a high-powered set of tools designed to interactively create windows at light speed with both DOS and UNIX systems.

Written entirely in portable "C", it includes the complete source code and even make files, so changes are

quick and easy.

Don't wait until you're caught in a bind, call us today. Modular, portable, and efficient, ÆWINDOS won't leave you hanging.

1-800-634-5494 BBS (303) 449-5714 \* UNIX is a trademark of AT&T

**CIRCLE NO. 15**

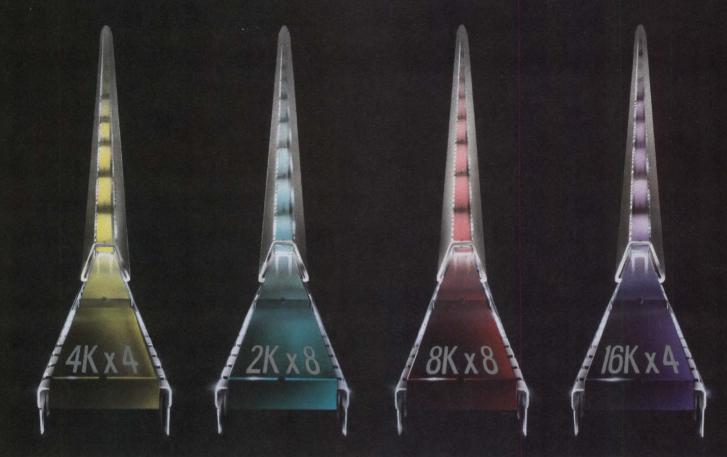

## PERFORMANCE means 15ns wide word SCRAMs

## 15ns

SCRAMs are Static CMOS Random Access Memories from Performance Semiconductor. At 15ns address access time these 64K's and 16K's are the world's fastest. SCRAMs are manufactured in Performance's six inch class 1 fabrication facility using PACE II 0.7 micron gate length technology which has set the standard for memory speed.

There is immediate availability of 15ns 64K and 16K bit SCRAMs compatible with JEDEC standard pinouts. Also available from stock are 17, 20 and 25ns speed versions.

## 15NS SCRAM PRODUCT GUIDE

| PART    | CONFIG. | SPEED | AVAIL. |

|---------|---------|-------|--------|

| P4C164  | 8K x 8  | 15ns  | NOW    |

| P4C188  | 16K x 4 | 15ns  | NOW    |

| P4C198  | 16K x 4 | 15ns  | NOW    |

| P4C198A | 16K x 4 | 15ns  | NOW    |

| P4C1982 | 16K x 4 | 15ns  | NOW    |

| P4C1981 | 16K x 4 | 15ns  | NOW    |

| P4C168  | 4K x 4  | 15ns  | NOW    |

| P4C169  | 4K x 4  | 15ns  | NOW    |

| P4C170  | 4K x 4  | 15ns  | NOW    |

| P4C1682 | 4K x 4  | 15ns  | NOW    |

| P4C1681 | 4K x 4  | 15ns  | NOW    |

| P4C116  | 2K x 8  | 15ns  | NOW    |

## FAST, COOL, & AFFORDABLE

For further information or to order 15ns SCRAMs call or write: Performance Semiconductor 610 E. Weddell Drive.

Sunnyvale, CA 94089 Telephone: 408 734 · 9000

## INTEGRATED CIRCUITS

## 80860 blends vector processing into a RISC-like architecture

Ron Wilson, Senior Editor

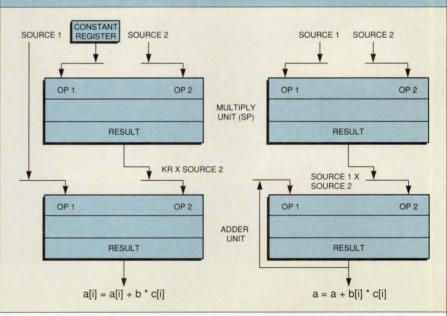

n the minisupercomputing world for which the new 80860 CPU from Intel (Santa Clara, CA) is intended, the heaviest computing tasks tend to be matrix operations. These processes involve multiplying an enormous vector or matrix by another enormous vector to compute the state of a structure, a flowing fluid, a three-dimensional image or a digitized waveform.

Taking advantage of the inherent order in these calculations, vendors have in the past designed specialized floating-point vector-processing hardware to boost the throughput of their systems. This hardware generally relies on a deeply pipelined floating-point unit, dedicated operand memories, and dedicated operand buses to achieve high computational rates.

By building a pipelined multiplier-accumulator configuration, designers can achieve several floating-point operations per clock cycle. And by keeping data in dedicated memories hard-wired to the pipeline inputs, the designers can ensure that the pipeline stays full.

But such a hard-wired approach to floating-point design seems incompatible with the architecture of a general-purpose computer, which lacks dedicated memory areas. The architects of the 80860 CPU have attempted to blend the data-flow notions of vector processing into the more general architecture of a RISC-like CPU, achieving an interesting compromise.

### A flow-through model

Normally, a microprocessor has a scalar FPU: once an operation is started, the unit will accept no more operands until the first operation is completed. This simplifies both the hardware design and the programming model of the FPU, but at the expense of performance. In contrast, most building-block FPUs have a pipelined mode, which lets a new set of operands be loaded on every clock.

The 80860 FPU provides both modes, via two sets of floating-point

instructions. Scalar instructions load a set of operands from the floating-point registers and store the result after one to four clocks. Pipelined operations load a set of operands and simultaneously store the result coming from the end of the three-stage pipeline, starting a new set of operations on each clock. (There are additional delays in double-precision mode, since the multiplier is effectively a two-stage, four-clock device in that mode.)

isters, it can perform multiply-accumulates at 80 MFlops.

Instead of the dedicated static RAM used in building-block vector processors, the 80860 relies on its floating-point register file and its data cache to provide operands to the pipeline. Extra-wide paths and a special instruction-fetch mode help with the monumental task of moving up to four operands per clock.

The path between the data cache and the floating-point register file is 128 bits wide, so two 64-bit operands can be loaded from cache in a single cycle. Three 64-bit paths connect the register file to the floating-point execution unit, so the pipeline can take in two operands and store one result in each cycle.

## A MULTIPLIER-ACCUMULATOR PIPELINE

By chaining the floating-point adder to the multiplier, the Intel 80860 can effectively convert its floating-point unit into a pipelined multiplier-accumulator. In single-precision mode, the pipeline will produce a result on every cycle of the chip's 40-MHz clock. Consequently, some linear operations can be executed at the rate of two floating-point computations per clock.

Since the floating-point multiplier and adder are independent units, they can be chained together to form a multiplier-accumulator pipeline. This capability lets the 80860 execute two floating-point operations, a multiply and an add or subtract, on each clock cycle. As long as the chip can keep its pipeline fed from the thirty-two 32-bit floating-point reg-

Further, the 80860 provides a dual-instruction mode, which fetches one integer-unit instruction and one floating-point instruction on each clock cycle. In this mode, the integer unit can execute a floating-point load or store while the FPU performs pipelined operations. One can thus think of the entire FPU as executing directly out of data cache, with input

## INTEGRATED CIRCUITS

and output pipeline registers actually residing in the floating-point register file.

### Precise exception handling

New! MEK

This level of concurrency is wonderful for processing speed, but such archi-

Oasys presents

for VAX, Sun, Apollo

LINK

MASM

tectures are notoriously difficult when exception conditions occur. If an overflow occurs and the hardware can't report which of the operations in the pipeline caused the exception, it can take the software several milliseconds to unravel the mess.

The 80860 provides two features to help with this problem. "The chip conforms to all IEEE exception-handling requirements," claims Bill Rash, Intel microprocessor marketing manager. "Also, hardware marks the location of an exception in the pipeline, and the floating-point instructions are restartable. So the exception trap routine can quickly identify the problem, take corrective action and get the pipeline flowing again."

And the 80860 pipeline, with its multhreatens to be complex indeed.

But Intel is working on this issue as well. Green Hills Software (Glendale, CA), one of the most experienced optimizer houses in the industry, will supply an optimizing C compiler for the chip. Pacific Sierra Research (Los Angeles, CA), a firm with considerable experience on vector-supercomputers, will write a vectorizing preprocessor for Fortran code. These tools should help users exploit the pipelined hardware more effectively.

the Intel approach. The limited size of the 80860's data cache, the limitation of one integer operation per clock, the relatively low speed of the external dynamic RAM connection, and the small floating-point register file will all impede the execution of large array operations. But as a compromise between the dedicated data-flow architectures of pure vector-processing machines and the unacceptably high overhead of scalar microcomputers, the 80860 represents a challenging step forward in silicon architecture. The chip may establish an entirely new level of MFlops per dollar on actual application codes.

usefulness of a deeply pipelined architecture is compiler support. If the be handcrafted, few users will realize the potential speed of the hardware. tiple configurations, differing stage delays, and possibility of mixing sin-

A more serious challenge to the pipeline is so complex that codes must gle- and double-precision operations,

Naturally, there are limitations to

Prices start at \$500. New ports are underway. Call today for more information. OEM and end-user inquiries are encouraged. For more information about the technol-

**Microsoft**

tions on powerful centralized VAXs or net worked workstations.

New and available from OASYS is the Microsoft Embedded Kit (MEK). This recent addition to the Microsoft Development System provides Intel Embedded Developers with Microsoft C Run-Time Library Source which can then be customized as needed. MEK is available on VAX, Sun, and other

Regardless of where you choose to do development, OASYS provides the best tools, on the widest variety of hosts, with comprehensive support. Our exclusive relationship with Microsoft, the world's leading

supplier of MS-DOS software products, is

evidence of our commitment to provide evolving PC tools to OASYS customers.

230 Second Avenue, P.O. Box 8990 Waltham, MA 02254-8990 (617) 890-7889

MS-DOS, Microsoft and the Microsoft logo are registered trademarks of Microsoft Corp. Apollo is a trademark of Apollo Computer Inc. Trademarks are also acknowledged to DEC, Sun Microsystems, Inc., XEL, Inc.

CIRCLE NO. 17

Green Hills Software (818) 246-5555... Circle 313 Intel (408) 765-4851 Circle 314 Pacific Sierra Research (213) 820-2200 ... Circle 315

ogies, products or companies mentioned in this article, call or circle the appropriate number on the Reader Inquiry Card.

DEC VAX (VMS and Ultrix), Sun and Apollo

Those accustomed to using these superior Microsoft tools on a PC can now build MS-DOS applications on a VAX or workstation. OASYS guarantees that the unsurpassed speed, compactness, and flexibility of Microsoft C have been preserved. The OASYS/Microsoft Cross C Development System offers identical functionality to Microsoft C — no short-cuts, no alterations—reackaged to meet today's

no alterations — repackaged to meet today's demands for high performance/low cost development on non-MS-DOS systems.

With the OASYS/Microsoft Cross C Devel-

opment System you can maintain, or even ex-

tend, applications originally created on a PC

Software development teams can now build

large, complex MS-DOS (soon OS/2) applica-

# How P-CAD Put A Smile On Over 10,000 PCB Designers

Lower costs and higher productivity add profits to your bottom line.

Work with P-CAD\* and you'll be smiling every time you finish a design or a fiscal year.

Because we know successful PCB design requires more than software alone.

That's why we offer the industry's most complete PCB design solution. Including training. Superior tech support. User groups. Bug reports. Plus, the best maintenance, upgrades, user guides, and reference documentation you'll find.

All elements that help reduce redesign, project delays, rework, and manufacturing costs. But even all that wouldn't mean much if our system didn't deliver. And it does!

P-CAD software is modular, with a consistent system command structure. Learn one and you know how to use all our modules. That means greater productivity and lower training costs.

P-CAD also works with all current technologies—SMT, analog, high speed, and fine line. So designers who use P-CAD will always be the most competitive.

You get a complete, upward migration path, too. As your requirements grow, you can take your P-CAD investment with you. No throw-away software. No obsolescence.

Architecture? It's "open" for easy integration with CADAM, AutoCAD, Ventura, Interleaf, and other CAD

environments. So your options are open now, and in the future.

Finally, with over 10,000 users in 37 countries, we have the largest installed base in PCB design. So when you're looking for experienced P-CAD designers, there's no need to look far. They're everywhere.

Let us show you how increasing

PCB productivity can enhance your profits. Call now for details and a free copy of our PCB CAD Buyer's Guide: 800-523-5207, in California, 800-628-8748.

What we have to say will make you smile. P-CAD, 1290 Parkmoor Avenue, San Jose, CA 95126.

D-CCC

## COMPUTERS AND SUBSYSTEMS

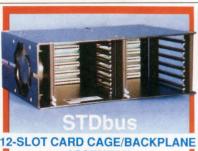

## Languishing STD Bus receives a late-life kicker

David Lieberman, Senior Editor

t's no secret that the STD Bus is suffering from a decline in use as designers migrate to buses with wider data paths and bigger bandwidths. Matrix (Raleigh, NC), however, intends to halt, or at least decelerate, the rate of STD defections with its recently unveiled STD backplane design. Called the Blackplane, it offers a combination of elements that let STD systems with clock rates as high as 16 MHz be reliably implemented. Most existing STD systems top out at 6 MHz or so. "We're expecting to add another three to five years of useful life to STD Bus," says Ray Alderman, Matrix vice-president.

The STD Bus community has migrated to ever higher-performance microprocessors over the years, jacking up the system clock as appropriate, with many moving into the Intel family processor camp to take advantage of PC software compatibility. As many are quick to point out, however, the STD Bus specification, formulated back in the Z80 age, isn't geared for high-frequency operation.

"The STD specs aren't very tight," laments Alan Beverly, engineering manager at Ziatech (San Luis Obispo, CA). "It's got no particular capacitive loading spec, no distance limitations on how far drivers and receivers should be from the backplane, no termination recommendation and so on. As bus speeds grow higher and higher, we've been see-ing a lot more problems with signal integrity, and those design rules that people have been somewhat lax about in the past are becoming extremely problematic."

Some place the blame for poorly performing systems not on any particular inadequacies in the bus spec, but on the generally poor quality of STD backplanes. "Not everybody has caught on to the fact that system speed can be severely limited by the design and construction of the backplane," says Kurt Priester, president of Computer Dynamics (Greer, SC). "Most don't pay a lot of attention to their backplanes and have to put up

with severely limited performance because they don't want to put in the money for shielding and noise suppression that's necessary in very high speed systems."

There has been substantial resistance, therefore, to pushing STD Bus speed. In many cases, the move to higher-frequency processors hasn't been accompanied by a faster system clock; rather, designers have let the processor run full throttle when accessing on-board resources, but they also implement a fallback frequency via slow-down logic when it comes time for bus transactions.

This provides an adequate solu-

lem," says Alderman, "but beyond that you start to bump into two nasty phenomena-ground shift and metastability. To deal with these two engineering problems, you also have to face another giant monster: transmission line effects.'

A large part of the problem with high-frequency STD, and much of the solution, lies with the backplane termination scheme. "An STD Bus backplane has passive terminatorsthat is, they're just snubbers, consisting of a capacitor and a resistor to ground," Alderman explains. "Impedance to ground on a backplane with passive terminators is such that there may not be enough of a path to ground and you wind up pulling ground up to some positive voltage level. Also, you can run into problems with metastability at higher frequencies where you're looking at clock edges, not levels. On the

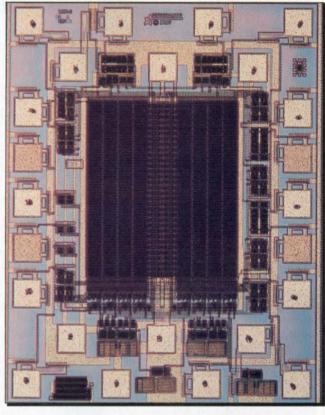

With the introduction of its Blackplane high-performance STD backplane, Matrix expects to expand STD's useful life by at least three to five years, according to Bill Harris (left), design engineer, and Rav Alderman, vicepresident.