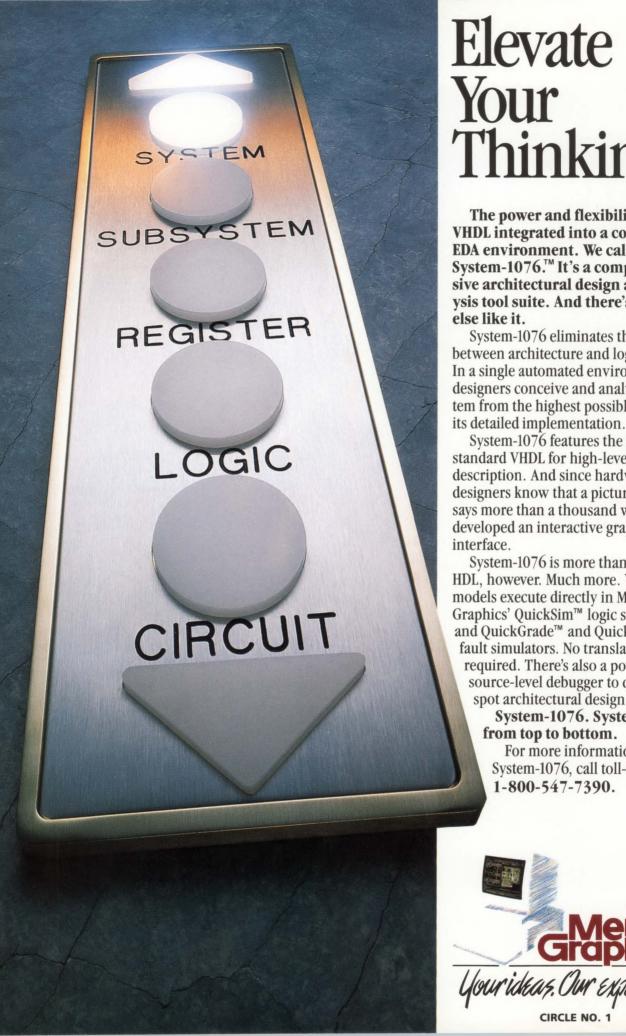

# Thinking.

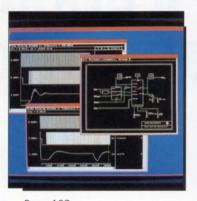

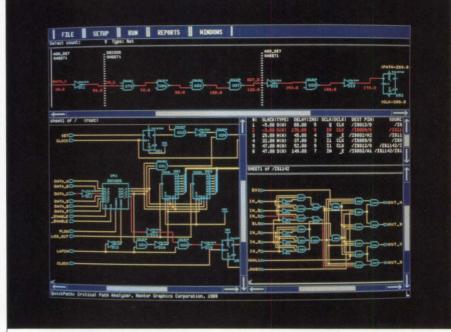

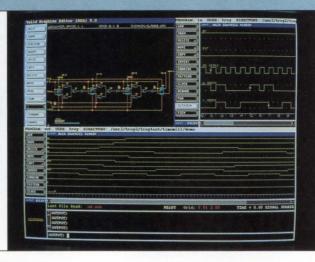

The power and flexibility of VHDL integrated into a complete EDA environment. We call it System-1076.™ It's a comprehensive architectural design and analysis tool suite. And there's nothing

System-1076 eliminates the barriers between architecture and logic design. In a single automated environment, designers conceive and analyze a system from the highest possible level to its detailed implementation.

System-1076 features the industrystandard VHDL for high-level design description. And since hardware designers know that a picture often says more than a thousand words, we developed an interactive graphical

System-1076 is more than a clever HDL, however. Much more. VHDL models execute directly in Mentor Graphics' QuickSim™ logic simulator, and QuickGrade™ and QuickFault™ fault simulators. No translations required. There's also a powerful source-level debugger to quickly spot architectural design flaws.

System-1076. System design

For more information about System-1076, call toll-free

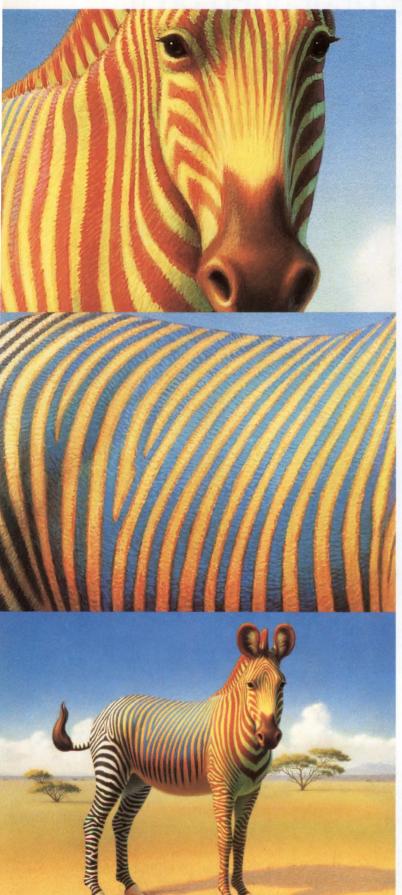

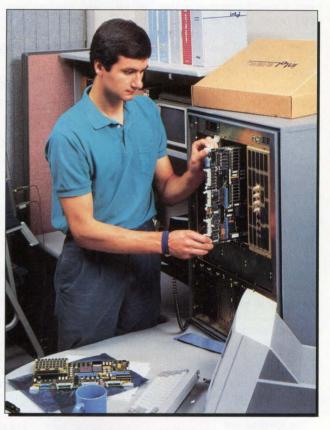

# We Stand Behind Every Custom Card Cage Like our Life Depended on it. Because it Does.

I'm Leonid Besprozvanny, and I stand behind every card cage we make. Or on top of it. Or whatever it takes to make it right. I earned my Ph.D.-EE degree at the Union

I earned my Ph.D.-EE degree at the Union Scientific Institute of Tractor in Moscow, where "delicate" was a dirty word. We were taught that every design had to stand up to the winter in Siberia. Or else the designer would.

about a custom cage, for instead of an order taker you'll be talking to an applications engineer. Someone who is equally knowledgeable about our high-speed VME and Multibus backplanes, the nuts and bolts of card cage mounting, and the BTU's of board-level system cooling. And who knows about tough engineering, too.

Call us today for a card cage, and you'll get a packaging solution. We've been building tough card cages for over 30 years, and if you're already an Electronic Solutions customer, you know they're tough — Because our life depends upon it.

#### We'll FAX you the facts.

Want the latest data in a hurry?

Nothing is faster than Electronic Solutions' new "FAX the FACTS" program.

If you have a FAX machine, just call our "800" number, give us your FAX our "800" number and type of FAX machine, and the information you need from us.

We'll FAX it to you immediately.

6790 Flanders Drive, San Diego, CA 92121 (619) 452-9333 Telex II(TWX): 910-335-1169

Call Toll Free: (800)854-7086 In Calif: (800)772-7086 SMC° introduces the most tightly integrated LAN system solution ever. Plus, you can change its stripes.

Check out SMC's new COM90C65. Clearly, it's a LAN controller. But there's also transceiver functions. And even support logic. So, when you step back and realize how it all comes together, you'll know we've got a whole new, remarkable type of animal here.

It's a single chip that takes SMC's industry standard ARCNET® technology to the next generation, combining LAN controller, transceiver, even PC bus interface all in one. Plus, it pulls "glue chip" functions such as the crystal oscillator and reset circuit on-board. Considering ARCNET's highly reliable token passing protocol, the COM90C65 is surely the most complete, tightly integrated LAN system solution ever on this earth.

But the COM90C65 doesn't stop there. As tightly integrated as it is, there's still room for SMC to add-on proprietary functions to your specifications, if desired. Change its stripes, so to speak. We call it our SuperCell™ adaptability capability; using all of SMC's considerable expertise to make the COM90C65 perfect for you. You'll call it incredible because it'll be done within budget and on time.

This approach can be applied to virtually all of our vast library of Standard ASICs; which is why we call them adaptable. And it means that our unique products can make your product unique. Without all that costly, from-scratch designing, endless engineering, complex manufacturing and acres of real estate.

SMC® is a registered trademark and SuperCell™ is a trademark of Standard Microsystems Corporation

| Yes! I'd like to know mo | re.                       | CD—5/89          |

|--------------------------|---------------------------|------------------|

| ☐ Please send me your    | Data Sheet on the COM     | 90C65.           |

| Please send me your      | most recent Short Form    | Product Catalog. |

| My need is immediate     | e. Please have a salesper | son call.        |

| NAME                     |                           | Market L         |

| TITLE                    |                           |                  |

| COMPANY                  |                           |                  |

| ADDRESS                  |                           |                  |

| CITY                     | STATE                     | ZIP              |

| TELEPHONE                |                           |                  |

CORPORATION

35 Marcus Boulevard, Hauppauge, NY 11788 516-273-3100

SMC-The Better Breed Of ASICs.

THE FIRST MAGAZINE OF SYSTEM DESIGN. DEVELOPMENT AND INTEGRATION

Page 59

#### **■ TECHNOLOGY UPDATES**

| Integrated Circuits                                                      |    |

|--------------------------------------------------------------------------|----|

| Intel 80486 carries complex instruction set to RISC speeds               | -  |

| 68040 moves toward RISC camp with redesigned pipelines, caches2          | 1  |

| Vendors ponder interconnect schemes in search for new PLD architectures2 |    |

| RISC CPUs tune up for embedded computing3                                | 36 |

| Graphics and Imaging                                                     |    |

### of graphics system architectures ......43

#### Computers and Subsystems

| Integrated environment  | eases |

|-------------------------|-------|

| development of military |       |

#### **Design and Development Tools**

| Timing verifiers branch of | out |

|----------------------------|-----|

| to overcome analysis cor   |     |

| Technical publishing tool  |     |

| documentation process.     | 59  |

#### Software

| Industry quartet | plays real-time | Ada |

|------------------|-----------------|-----|

| on Sparc         |                 |     |

Page 103

#### ■ TECHNOLOGY AND DESIGN FEATURES

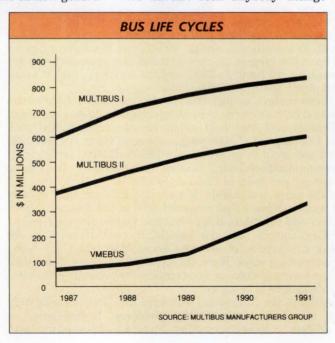

#### Designers hang on to Multibus I

A seemingly interminable upgrade path. The sometimes irresistible appeal of familiarity. This old bus is—at least for now-still in its prime ......69

#### Ada tools mature, but users debate language standards

Ada development tools improve for building real-time and distributed systems, but can the remaining language problems be resolved without defying rigid standards? ......77

#### **COVER STORY**

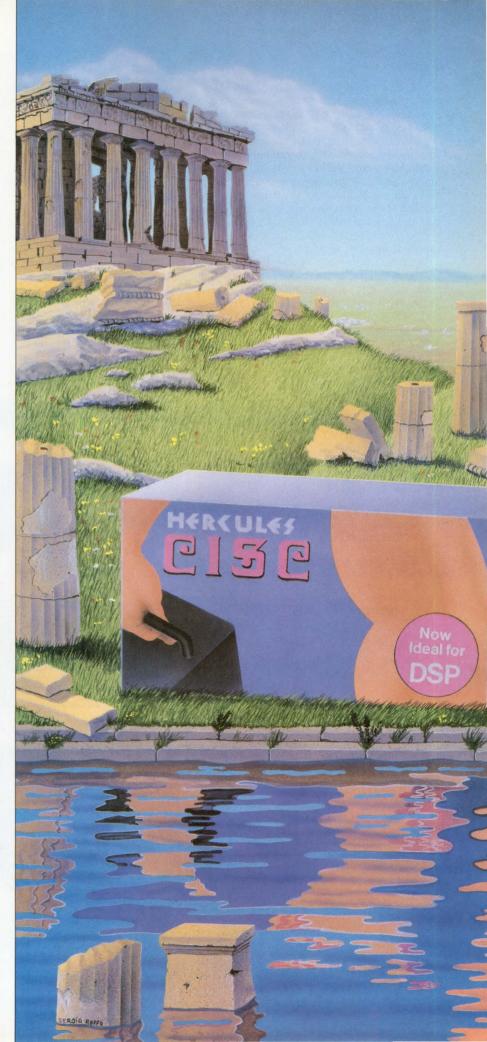

#### Distinctions blur between DSP solutions

A wide variety of chips move to increasingly higher levels of integration, making previous distinctions ambiguous and heralding a new generation of DSP technology ......86

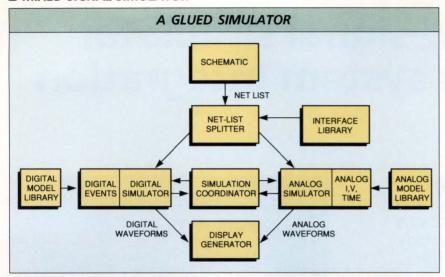

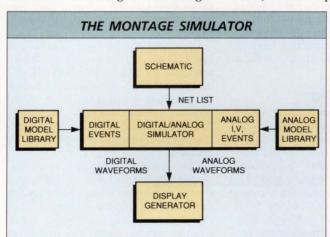

#### Mixed-signal simulator eases system integration

Designers need a simulator that can be used to quickly evaluate complex, mixed analog/digital VLSI chips without

Page 117

#### ■ NEW PRODUCT HIGHLIGHTS

#### **Integrated Circuits**

| National shrinks power needs for LAN interfaces in laptop applications | 1<br>108 |

|------------------------------------------------------------------------|----------|

| Quad Port message center loosely couples small groups of CPUs          | 110      |

| "Fuzzy" logic processor speeds embedded AI control applications        | 111      |

#### **Design and Development Tools**

| Magnetics library, Monte Carlo analys | is |    |

|---------------------------------------|----|----|

| expand simulator's capabilities       | 11 | 12 |

| Testing package helps designers       |    |    |

| develop ASIC verification programs    | 11 | 13 |

#### Computers and Subsystems

| compared and subsystems            |     |

|------------------------------------|-----|

| Programmable serial I/O controller |     |

| targets Micro Channel systems      | 114 |

| Powerful MS-DOS CPU rides |   |    |   |

|---------------------------|---|----|---|

| 8- or 16-bit STD Bus      | 1 | 15 | 5 |

#### Major System Components

| Virtual SCSI controller matches new drives to range of interfaces | 116 |

|-------------------------------------------------------------------|-----|

| Multiscan monitor boasts single-scan                              |     |

| performance                                                       | 117 |

#### ■ DEPARTMENTS/COLUMNS

| News Briefs         | 9 |

|---------------------|---|

| Editorial1          | 4 |

| Advertisers Index12 | 0 |

# At about strange things happen to

As rise times approach 3ns, all cable/connector assemblies become transmission line assemblies.

But not necessarily good ones.

Newer, faster logic families require controlled impedance cable assemblies. Designed for high-speed performance. Engineered for controlled impedance and propagation rate. And manufactured for absolute conformity to specifications.

Creating controlled impedance assemblies to these standards demands extensive CAD/CAE use. Plus a wide range of specialized connector choices. Plus the capability to custom design quickly. Plus intimate knowledge of the various termination techniques, including advanced wire attachment techniques.

Our people are equipped to work

## t<sub>r</sub>=3ns, ordinary cable assemblies.

with you early in the design stage to provide an optimum solution to your requirements. We help you determine the characteristics for impedance and propagation velocity that you need to match timing requirements, and the crosstalk figures you have to meet.

We engineer and manufacture controlled impedance assemblies in a way you'll especially appreciate.

Our manufacturing facilities are unmatched in the industry. Every assembly is individually inspected and 100% electrically tested. All work is part of the overall statistical process control system at AMP, and comes under our corporate-wide quality program.

For technical literature and more information on high-speed controlled impedance assemblies—for logic rise times from 3ns down to the sub-nanosecond range—call 1-800-522-6752. AMP Incorporated, Harrisburg, PA 17105-3608.

#### AMP Interconnecting ideas

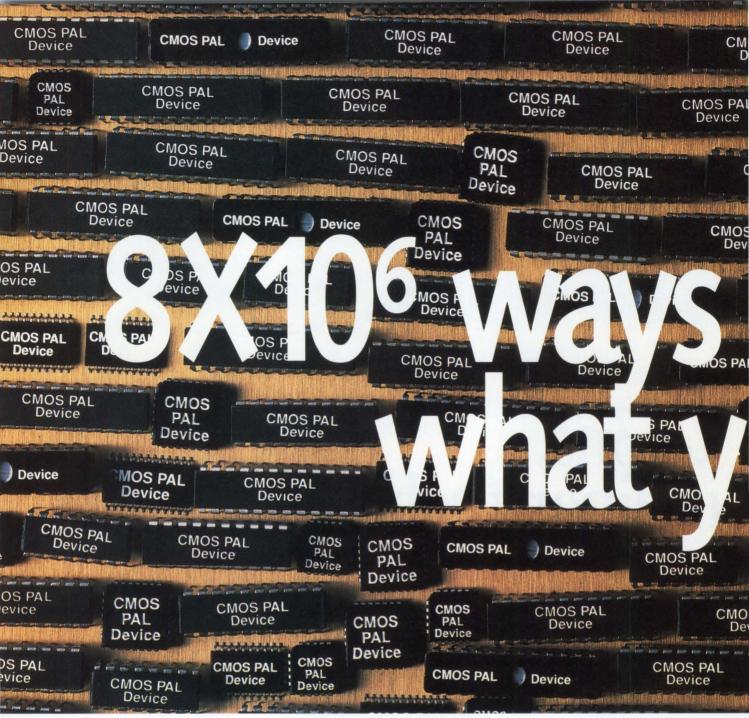

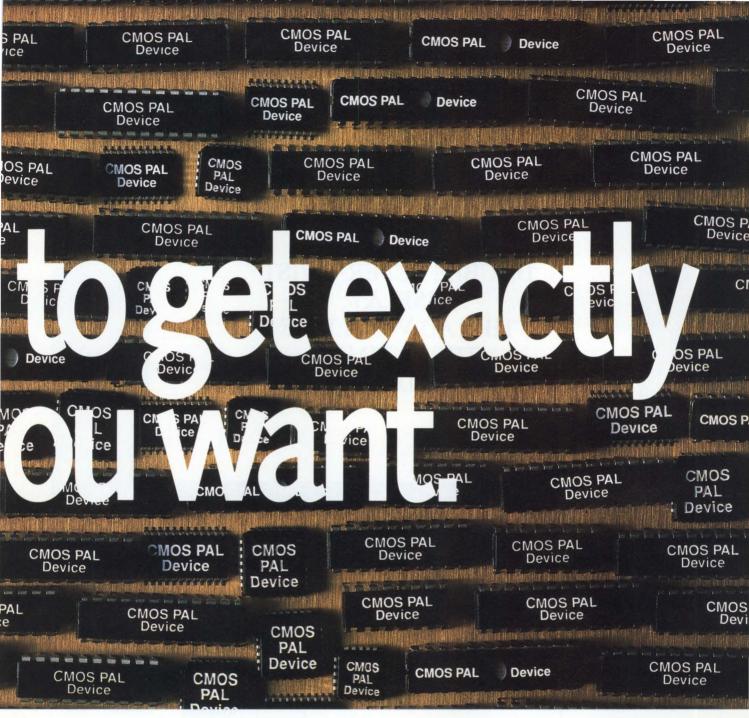

We have 8 CMOS PAL® chips. That totals up to 8 million different ways to program your logic. Quite enough of a choice to meet your most exacting low power logic needs. From universal PAL architectures to zero stand-by power PAL devices. You can have the system you want without compromise. And without costly delays.

Our all-purpose CMOS architectures give flexibility without draining precious power. The 24-pin industry standard

PALC22V10 uses just 90mA—even when it's running at 25ns.

If you liked us in bipolar, you should see us in CMOS.

We have five CMOS ZPAL™ devices based on familiar bipolar architectures. You can use them in battery powered and low duty-cycle applications. And they use virtually no power when in stand-by. Two versions are electrically erasable. You can get the functions you're used to and you can change your design as fast as

you change your mind.

What did you expect from the people who invented PAL devices?

The largest and most experienced Field Application Engineer force is as close as your phone all during your designin process.

Our TestPro™ Centers give you access to superior testing and programming support. Just call your AMD sales office for the center nearest you.

And we've kept the classic PALASM®

software up to date with our parts and your needs.

Most important, you can get your hands on our parts. They're all in high volume supplies.

Call (800) 222-9323. It's hard enough to get what you want in life without passing up 8,000,000 more chances.

## Advanced Micro Devices A Monolithic Memories

901 Thompson Place, P.O. Box 3453, Sunnyvale, CA 94088.

If it weren't for Sharp's new technology, chances are you'd still be trying to read the headline above. That's because our display screen offers unsurpassed brightness and clarity, with three times the contrast of conventional LCDs. Along with an increased viewing angle, our double super-twist display provides an image quality which approaches that of a printed page.

What's more, Sharp is the first to successfully develop and mass-produce this technology—

which means we have DST displays available now in

quantity. Each unit is fitted with a durable CCFT backlight for bright, clear display. And each offers low drive

voltage, low power consumption, and fewer temperature-dependent tone variations.

Since the days

of the first hand-held calculators, in Sharp has been an innovative

| SHA      | RP'S DO       | UBLE SUPER-T                  | WIST DISP                   | LAYS               |

|----------|---------------|-------------------------------|-----------------------------|--------------------|

| MODEL#   | DOT<br>FORMAT | OUTLINE DIMENSIONS WxHxD (mm) | VIEWING<br>AREA<br>WxH (mm) | DOT<br>SIZE<br>WxH |

| LM24010Z | 240x128       | 176x96x22                     | 134x76                      | 0.49x0.49          |

| LM64135Z | 640x400       | 300x166x26                    | 218x139                     | 0.30x0.30          |

| LM64148Z | 640x480       | 280x180x25.5                  | 205x155                     | 0.28x0.28          |

| LM64048Z | 640x480       | 310x240x25                    | 237x180                     | 0.33x0.33          |

| LM72060Z | 720x400       | 320.4x170.4x34                | 260x147                     | 0.32x0.32          |

leader in LCD displays. To find out more about our new double super-twist units, call

**HARP** (201) 529-8757.

#### IF IT'S SHARP, IT'S CUTTING EDGE."

© 1988 Sharp Electronics Corporation, Sharp Plaza, Mahwah, N.J. 07430.

#### NEWS BRIEFS NEWS BRIEFS NEWS BRIEF

#### Motorola unwraps 32-bit single-chip microcontroller

Motorola (Austin, TX) has unveiled its long-awaited 32-bit, singlechip controller, the 68332. The chip, designed around General Motors' requirements, surrounds a modified 68020 CPU core with a variety of intelligent peripheral modules and 2 kbytes of static RAM. Additional family members under development will add on-chip ROM

to the design.

In the 68332 design, the latent power of the 68020 CPU core is unleashed by protecting the core from event-driven interrupts. This is accomplished by upgrading the traditional serial, parallel and timer I/O devices into full-blown programmable processors in their own right, capable of performing even complex application-specific operations without CPU intervention. The timer module, for example, can accelerate, drive, coast and halt a stepper motor on its own, without CPU intervention.

Major modules on the 68332 include the CPU core, the programmable timer module, an intelligent synchronous/asynchronous serial communications module, the SRAM, and a system integration module (which contains most of the bus, control and debug functions normally implemented in off-chip logic). -Ron Wilson

#### Western Digital publishes 8514/A register specs

Third-party graphics software developers eager to write more efficient code to the IBM 8514/A display adapter will be able to get register specifications for the IBM silicon through Western Digital (Irvine, CA). IBM has declined to publish the register specification and has insisted instead that graphics developers write to a software protocol layer called the adapter interface (AI). Since many feel that the AI imposes a performance penalty, several companies have been rushing to discover the IBM register details and produce functionally equivalent silicon.

Western Digital is releasing the IBM registers that the AI uses, so developers can bypass the AI and

write directly to the registers. The chip set Western Digital is developing, called the PWGA-1, will have extended registers. Specifications for these extended registers will be offered to Western Digital's OEMs under nondisclosure agreement.

In addition to discovering the register specifications. Western Digital claims to have uncovered a memory conflict between the range used by IBM's 8514/A BIOS EPROM and that used by third-party extended VGA. The conflict could cause a system crash if both extended VGA and 8514/A are used in the same system. Western Digital is proposing standardization on BIOS address ranges for extended VGA and third-party 8514/A systems. In addition, the PWGA-1 will eliminate the need to use an interlaced monitor, a major hindrance of IBM's 8514/A. No availability date for the chip set has been announced.

-Tom Williams

#### **VESA** approves extended VGA standards

The Video Electronics Standards Association (VESA) has reached preliminary agreement on a standard BIOS interface for the 800-×600pixel 16-color Super VGA mode. The VESA standard is significant because Super VGA, a natural extension of IBM's 640-×480-pixel 16-color VGA mode, isn't an IBM standard. Each Super VGA card from every vendor, therefore, has required a different set of application drivers. The VESA standard has established a common mode number (6Ah) that will let software developers write one driver for all cards that follow the VESA standard.

Not addressed in the preliminary document is the issue of BIOS memory-range conflict reportedly discovered by Western Digital (Irvine, CA) in its research into the IBM silicon (see story above). Since the document covers software standards only, it likewise doesn't address the issue of differing monitor frequencies. According to VESA, these issues may be raised under new business when the association meets to formally organize and to vote on the standards document.

-Tom Williams

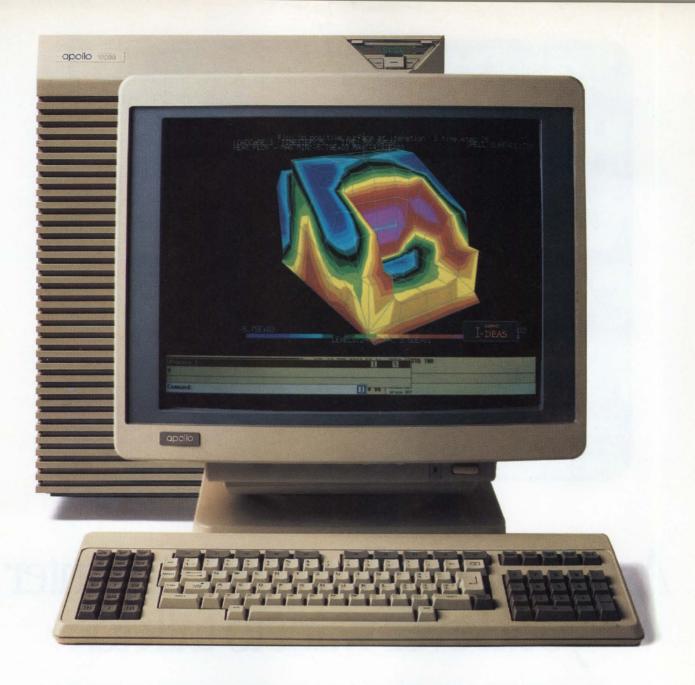

#### HP buy of Apollo draws mixed reaction

The \$476 million purchase last month of workstation pioneer Apollo Computer (Chelmsford, MA) by Hewlett-Packard (Palo Alto, CA) both surprised competitors and reassured customers. The move came as a shock to Apollo's competitors, notably Sun Microsystems (Mountain View, CA), which had been exploiting the financial uncertainty surrounding Apollo. Conversely, major Apollo customers cheered the move, saying the purchase removes any financial doubts about a supplier they perceive to be a technology leader.

Perhaps most directly affected by the purchase will be Apollo's major customer, Mentor Graphics (Beaverton, OR). "We can't imagine a better combination than Apollo's technology and HP's financial, market and support strengths," says Gerard Langeler, president and chief operating officer of Mentor. "It will make Mentor customers feel better about using Apollo products."

Mentor anticipates no conflict from HP's growing presence in the electronic CAE market. "They have handled a similar situation quite well already in their relationship with McDonnell-Douglas in the mechanical area," Langeler notes.

-Ron Wilson

#### Sun shows new lineup of Sparc workstations

The next generation of workstations announced by Sun Microsystems (Mountain View, CA) includes a number of firsts, including Sun's first response to Digital Equipment Corp's challenge in the under-\$10,000 arena and Sun's first use of the Cypress 7C601 Sparc processor.

Two lines of Sparc products were introduced: the Sparcstation 1, with a 20-MHz LSI Logic-supplied Sparc CPU based on the familiar Fujitsu Sparc implementation, and the Sparcsystem 300, using the Cypress Semiconductor Sparc integer unit at 25 MHz.

The Sparcstation 1 seems intended as a direct challenge to DEC's R2000-based DECstation 3100. The Sun system starts at \$8,995 for a

(continued on page 10)

#### NEWS BRIEFS NEWS BRIEFS NEWS BRIEF

(continued from page 9)

desktop unit with small monochrome monitor and no disk, and quickly moves up the price curve to a still-impressive \$15,495 for a system with color display and disk Sun rates the unit at 12.5 Mips. The Sparcsystem 300, meanwhile, is rated at 16 Mips, with prices ranging from roughly \$30,000 to \$74,000.

Many design automation vendors have already announced their support for the new machines. Vendors supporting the new systems include Valid Logic Systems (San Jose, CA), Teradyne EDA (Santa Clara, CA), Cadence Design Systems (San Jose, CA) and Daisy/Cadnetix (Mountain View, CA).

-Ron Wilson and Bill Harding

#### **Active-matrix LCD** displays 16 colors

At this month's SID (Society for Information Display) conference, IBM Japan and Toshiba America (Irvine, CA) will demonstrate a large, high-resolution active-matrix LCD that doubles the color capability of displays of this type. Whereas color LCDs typically use a triad of RGB filters to generate eight basic colors, this prototype 14.26-in.-diagonal, 720- × 550pixel display uses a quad-filter arrangement with a fourth, white filter that lends two brightness levels to whatever color is generated by RGB combinations. "You can, for example, have a deep, saturated red or a kinder, gentler red," says Denis Arvay, manager of informa-tion for IBM's Research Division (Yorktown Heights, NY).

Although the 16 colors possible with this display are nowhere near the 256-color capability that would make the thin-film LCD a viable CRT replacement for today's color graphics applications, its pseudograyscale capability should give it an advantage when true grayscale versions compete on the grounds of the depth of their color palettes.

- David Lieberman

#### **Heavy investment** pays off for Toshiba

The recent success of Toshiba (Tokyo, Japan) in the memory IC arena

is proof that long-term, steady investment can earn formidable dividends. In five of the last six years, the company has outspent its rivals on semiconductor manufacturing and on research and development. Not surprisingly, the Japanese manufacturer has maintained a dominating 30 percent market share of the 1-Mbit dynamic RAM market over the last two years. That's an uncommon achievement in the rapidly maturing and costsensitive DRAM market.

Toshiba appears ready to accomplish a similar feat in the 4-Mbit DRAM market. The company has already gained a lead in these nextgeneration memories with the introduction of twenty-four 4-Mbit parts in various speeds and configurations. Company officials expect to begin production on faster 60- and

70-ns devices shortly

Toshiba is also staking a claim to the high-speed SRAM pie. At Electro last month, Toshiba unveiled a series of 1-micron CMOS, 256-kbit SRAMs with speeds of up to 20 ns. The parts come in two 64k × 4-bit versions, one with output enable and one without. The company also offers a 32k×8-bit configuration and a 32k×9-bit part that allows for bit parity. — John Mayer

#### Parallel computing gets serious...and friendly

During the next three years, the Defense Advanced Research Projects Agency (DARPA) will reportedly sink \$7.6 million into a project on a massively parallel computing system. The system will link from 20 to 2,000 processing nodes based on Intel's recently announced 80860 chip.

Hypercube manufacturer Intel Scientific Computers (Beaverton, OR) will be responsible for developing the first prototype, code-named Touchstone, which is slated for first demonstration by the end of 1991. In its maximum configuration, Touchstone is expected to be able to crunch through more than 128 billion 64-bit Flops.

A significant portion of the DARPA funds will go toward making the prototype as easy to use as a garden-variety workstation, according to Justin Rattner, director of technology at Intel Scientific. "We

expect Touchstone to improve parallel-computing performance levels 100 times over what they are today," he says, "as well as to create a software environment to give these powerful machines the look and feel of conventional systems."

-David Lieberman

#### Widebus doubles I/O functions

Texas Instruments (Dallas, TX) will provide twice as many I/Os as standard 24- and 28-pin devices by using a space-saving, very small outline package in its new Widebus Series ICs.

Fabricated in 1-micron CMOS technology, the products will operate at speeds comparable to those of advanced bipolar chips but will effectively reduce the amount of board real estate needed for line drivers. transceivers, flip-flops and registers by using 25-mil center-to-center pin spacings.

Designers will be able to use each Widebus function at its full width or as dual, independently controlled 8-, 9- or 10-bit functions. TI hopes to have engineering samples by the third quarter of 1989, with production slated for the fourth quarter. -Mike Donlin

#### High-speed NuBus boards debut at Electro/89

In addition to the April Electro/89 introduction of its MXIbus backplane bus, National Instruments (Austin, TX) chose the same conference to introduce two very high-speed data-acquisition board additions to the company's line of Macintosh II NuBus products. One of these boards samples waveforms on one of four available channels at rates of up to 1 Msample/s with a 12-bit resolution, says Audrey Harvey, engineering manager. Use of all four channels simultaneously allows sampling at 250 ksamples/s on each channel.

In addition, a 32-bit block-mode DMA interface board offloads some of the work of the Macintosh II coprocessor by transferring data from a compatible data-acquisition board directly to memory. This offloading also lets the Mac II function as a

GPIB controller.

-Syd Shapiro

## Who gave Sun a license to speed?

## Hot Rod RISC.

Sun's new SPARCstations 330, 370 and 390 deliver 16 MIPS.

The engine? Our 7C601 RISC CPU, running at 25MHz.

An engine that is also available at 33MHz, for up to 24 MIPS. It is part of a complete RISC chipset that includes memory management, multiprocessing, floating point, and cache, all tailored to give you high performance at very competitive prices.

Plus access to the broadest library of applications, software, utilities, languages, graphics, and productivity software available under the Sun.

Cypress Hot Rod RISC 7C601. Another blast from our latest data book. Call for your copy.

Data Book Hotline: 1-800-952-6300 Ask for Dept. C11A\*

\*1-(800) 387-7599 in Canada. (32)2-672-2220 in Europe. ©1989 Cypress Semiconductor, 3901 North First Street, San Jose, CA 95134 Phone: (408)943-2600, Telex: 821032 CYPRESS SNJ UD, TWX: 910-997-0753.

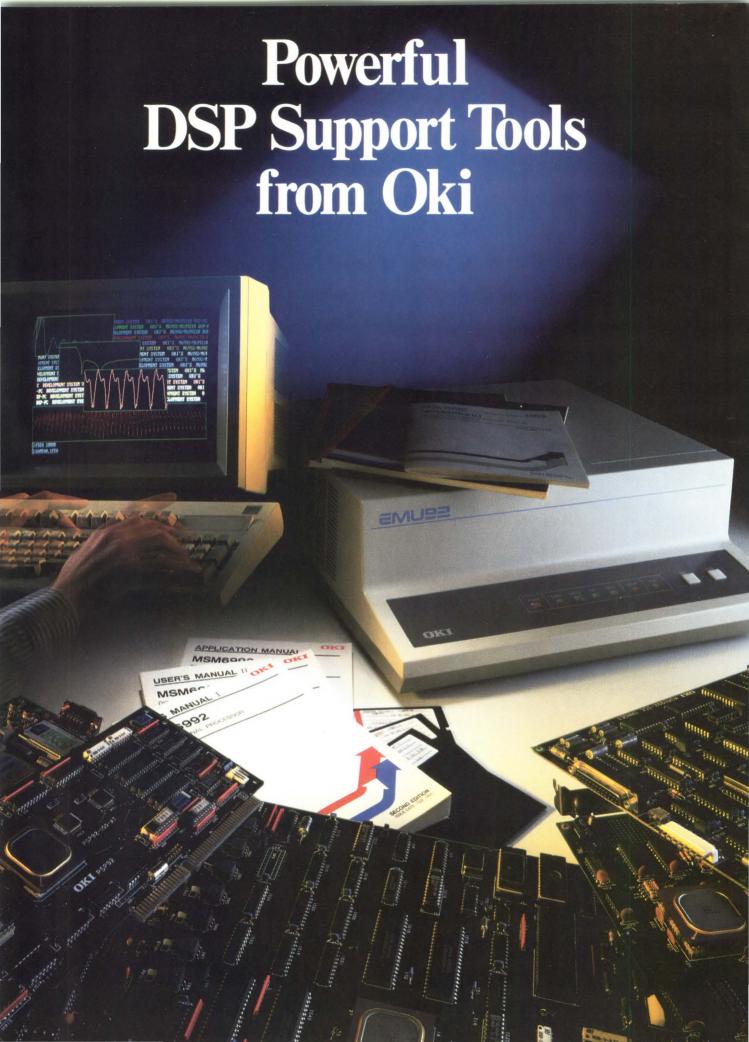

## Oki helps you achieve faster, easier DSP application development with a complete portfolio of support tools.

Oki Semiconductor meets your DSP needs by bringing you the best price/performance available, with our MSM6992 and MSM699210 DSP devices. We also offer powerful hardware and software support tools at various price points to speed and simplify your DSP application development.

#### A full set of powerful DSP support tools

- ► Software Simulator—the SIM92 simulates all internal operations of the MSM6992/10 devices, allowing you to test routines without hardware. It utilizes the emulator command set and offers advanced options such as a dump-restart facility, efficiency parameters, and histograms.

- ▶ High-Level Language—the OSL92 programs as a subset of C and speeds DSP software development, with one line of OSL92 code equivalent to six lines of assembly code. Specifically tailored for the 6992 architecture, it exhibits remarkable performance when compared to hand-assembled code, with efficiencies of up to 95%.

- ► *Emulators*—Oki offers a choice of stand-alone in-circuit emulators for real-time emulation, with the EMU92 and EMU92L.

- ► Software Libraries of User Routines—these libraries contain many of the most commonly used routines in DSP programming.

- Development System—the PSP92 permits realtime processing of analog signals through separate "digital" and "analog" PC-AT cards. It also allows for sophisticated 16-color EGA-compatible graphics.

#### The best DSP choice

Oki's full complement of DSP supports tools have the power to help you get your product to market faster. And Oki makes them easy to use. They are all PC-based, fully documented

and use the same debugger language. So if you are evaluating DSPs for a new design, make the smart choice. Oki gives you the devices *and* the support to streamline your DSP application development.

| our new brochure OSP application developed | 10                                                                                  | ki's MSM                                                                                                                   | 5992/10                                                                                                                                                    |

|--------------------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| e immediate needs.                         |                                                                                     |                                                                                                                            |                                                                                                                                                            |

| (                                          | ,                                                                                   | )                                                                                                                          |                                                                                                                                                            |

| E                                          | Business Phone                                                                      |                                                                                                                            |                                                                                                                                                            |

|                                            |                                                                                     |                                                                                                                            |                                                                                                                                                            |

|                                            |                                                                                     | 412                                                                                                                        |                                                                                                                                                            |

|                                            |                                                                                     |                                                                                                                            |                                                                                                                                                            |

| State                                      |                                                                                     | Zip Code                                                                                                                   | 9                                                                                                                                                          |

|                                            | OSP application developed in the policy of the portfolio of DS are immediate needs. | our new brochure OSP application developme echnical data/specs on O nplete portfolio of DSP s e immediate needs.  (  Busir | our new brochure OSP application development echnical data/specs on Oki's MSMe nplete portfolio of DSP support too e immediate needs.  ( )  Business Phone |

The time's arrived for a show where system designers can kick all the tires.

John C. Miklosz Associate Publisher/ **Editor-in-Chief**

#### Where can you go to kick the tires?

f you're interested in ICs, that's a tough question to answer. The second and third weeks in April brought the spring blossoming of electronics/computer shows. There was Electro in New York City, Comdex Spring in Chicago and NCGA in Philadelphia. But there's been a shift in focus in these shows over the past few years, which is making it hard for a designer or a design manager whose primary interest lies in ICs-microprocessors, SRAM and DRAM, A-D converters, op amps, PLDs, etc., etc.—to find enough to make it worthwhile to trek to the Big Apple, the Windy City or the place where W.C. Fields would rather be.

In this regard, Electro was a complete bust with no more than a half-dozen IC vendors showing their wares, among them Advanced Micro Devices, Analog Devices, Harris and Toshiba. An interest in design and development tools goes hand in hand with an interest in ICs, and here the representation was equally sparse with only Data I/O, P-CAD, Orcad and a few smaller players making a showing. And if you wanted to "kick the tires" at each of these vendors' exhibits, you had to hunt them out from a Miracle Mile of connector, cable, cabinet, switch, power supply and passive component vendors.

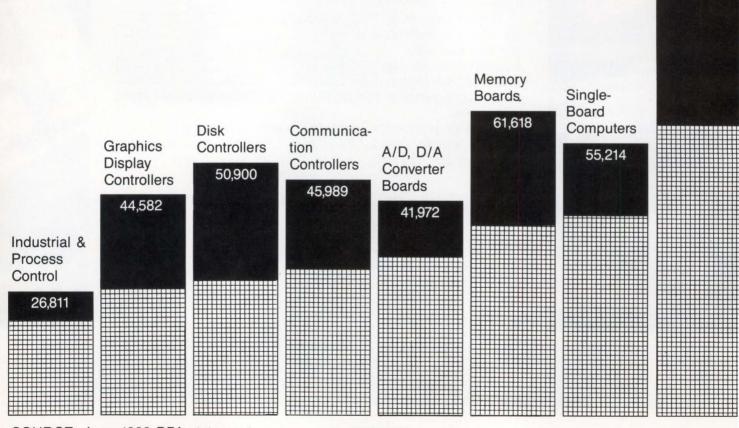

It's not that I have anything against cabinet, power supply and switch vendors; after all, you don't power up the microprocessor until you've turned on the switch. But there's no conference or exhibition running today-not Electro, not Wescon, not Comdex, not even the Design Automation Conference—whose primary appeal is to the designer or design manager who wants to talk about, learn about or sample the full breadth of the latest architectural components. By architectural components, I mean those components that determine the intrinsic functions, performance and features of an electronic/ computer product or system. Microprocessors, RAMs, EEPROMs, peripheral interface or controller chips, for example, are architectural components. So are single-board computers, graphics controller boards, digital-signal processor boards and I/O boards. And so, too, is software—operating systems and real-time kernels, for example.

From studies we've done of our readers, the odds are better than 60/40 that if a designer is using off-the-shelf boards, he (or she) is also designing boards or subsystems using standard ICs or ASICs. The reverse is also true; a large percentage of designers developing their own boards or subsystems are interested in off-the-shelf board-level products because there's no point in building what you can go out and buy.

For the most part, designers and, especially, design managers can no longer be pigeonholed into chip-level or board-level, or even hardware or software. More often than not, their responsibilities and interests span the complete spectrum of architectural concerns and architectural components. The time's arrived for something we'd call the Architectural Components Conference and Exposition. The time's arrived for a show where *system* designers can kick *all* the tires.

## Check DY-4 for the widest choice in VIVIE commercial, ruggedized and Mil-Spec NDI

offers the widest variety of Non-Developmental Items (NDIs) right across the board: commercial NDIs for developmental projects; ruggedized NDIs; and Mil-Spec NDIs fully compliant with MIL-E-4158, 5400, and 16400 specs.

All DY-4 NDIs are manufactured in accordance with AQAP-1 and include advanced features like built-in test and system-level diagnostics.

For the most and the best NDIs, call DY-4 — one of the world's leading suppliers of board-level products for commercial and military applications.

California: (408) 377-9822 Los Angeles: (714) 549-2559 Washington: (301) 964-5554 Massachusetts: (508) 692-9308 Canada: (613) 596-9911 Denmark: (06) 963824 Germany: (089) 903 9206

| PRODUCT                              | COMMERCIAL | RUGGEDIZED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MIL-SPEC  |

|--------------------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Single Board Computers (680x0/88000) | COMMENCIAL | NOGGEDIZED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | WIIL-SPEC |

| Military / Communications Interfaces |            | COMPANY OF THE PARTY OF THE PAR |           |

| MIL-STD-1553 B                       | V          | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | V         |

| NTDS (Serial and Parallel)           | V          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |

| Digital-to-Synchro                   | V          | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |

| Digital-to-Resolver                  | ~          | ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |

| Synchro-to-Digital                   | V          | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |

| Resolver-to-Digital                  | V          | ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |

| ARINC 429 / 561                      | ~          | ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |

| Memory Modules                       |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |

| SRAM                                 | ~          | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ~         |

| EPROM                                | ~          | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ~         |

| EEPROM                               | ~          | ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ~         |

| DRAM                                 | V          | ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ~         |

| System Controllers                   | ~          | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ~         |

| Serial I / O                         | ~          | ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ~         |

| Intelligent Serial I / O             | ~          | ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ~         |

| Parallel I / O                       | ~          | ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ~         |