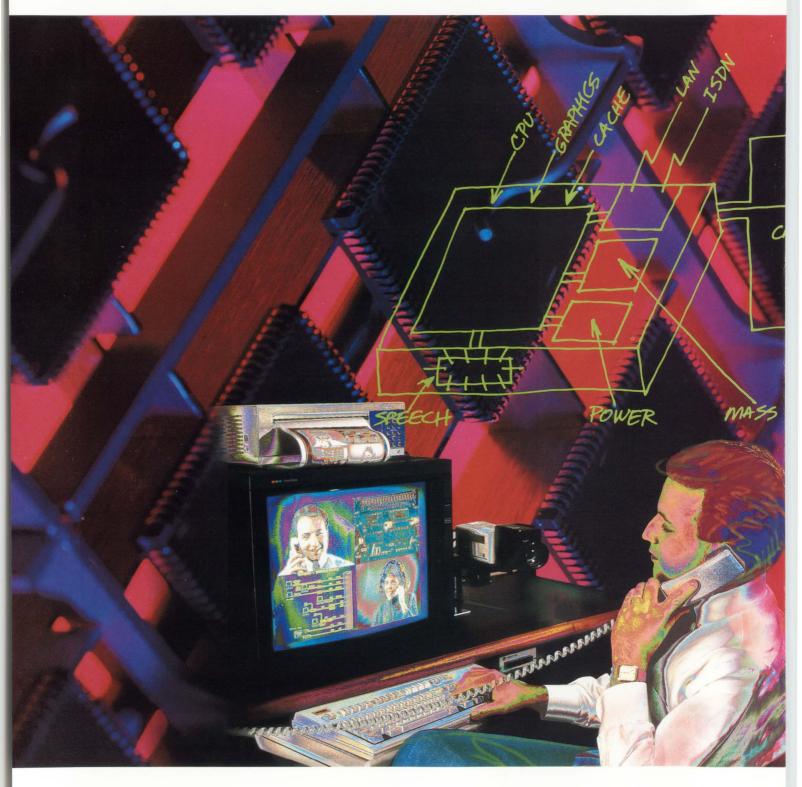

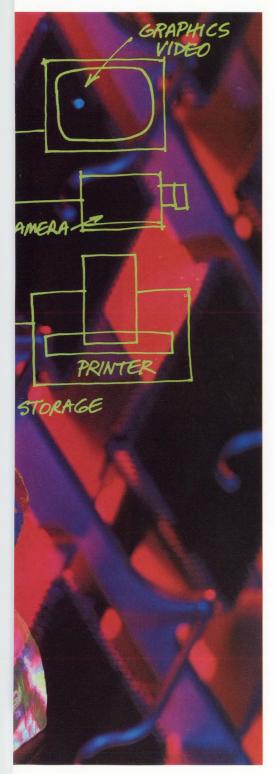

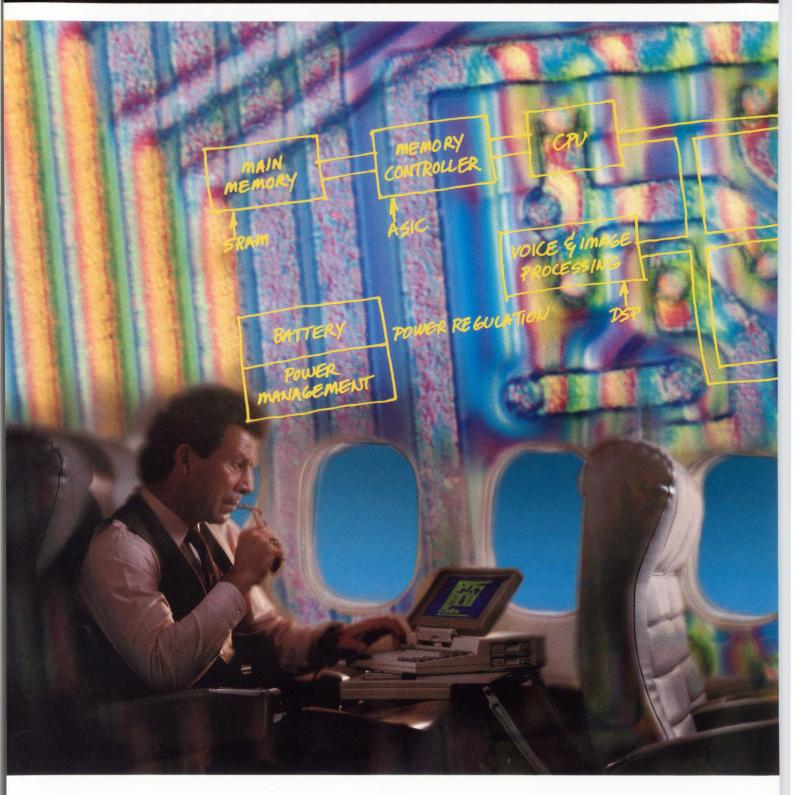

Bruce Bourbon on System-level design

FOR ELECTRONIC ENGINEERS & ENGINEERING MANAGERS

# Application determines best approach to multiprocessing

Design entry tools evolve to meet future needs

DRAM vendors address increasing specialization

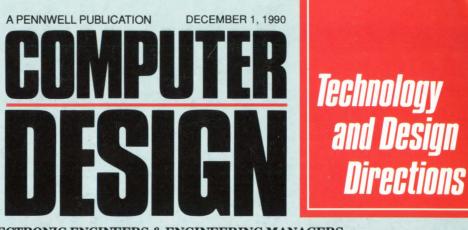

# Unparalleled, parallel performance.

### SCSI-2 is at your command with Rimfire® 6600 Series Parallel Disk Array Controllers.

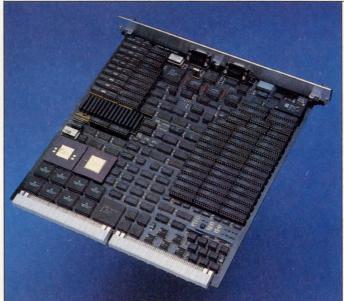

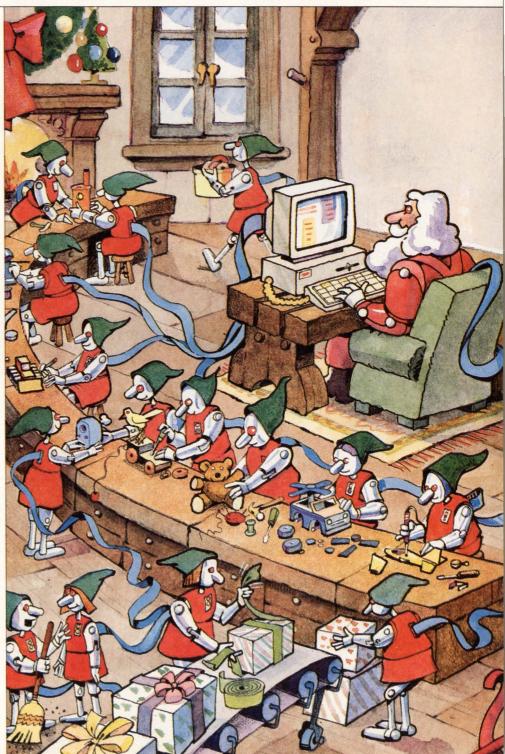

Discover unmatched performance and data integrity for mass storage applications – the Rimfire 6600 series of Parallel Disk Array (PDA) Controllers.

The first array controller offering SCSI-2 as its host interface, as well as the first offered as a board level product, the Rimfire 6600 Series supports four data drives plus a single redundant drive. Because all disk data transfers occur in parallel, the array appears to the host as a single SCSI drive. For you, that means excellent performance. Transfer rates and capacity four times that of an individual drive. And exceptional data availability.

In addition, the flexibility of the PDA controller allows the OEM to select drives from many vendors. It's compatible with SCSI, operates with off-the-shelf host adapters and is priced significantly lower than other solutions of equivalent capabilities.

For detailed information on the Rimfire 6600 Series, or other SCSI-2

compatible products, call Ciprico, the industry leader in technology, technical support, customer service and respondability at 1-800-SCSI-NOW (1-800-727-4669). European customers call our United Kingdom office, (0703) 330 403.

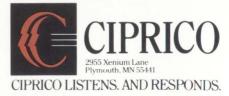

# New 10-Layer VME Backplane!

# There's Logic To Every Layer!

Look inside the first truly reliable, glitch-free VME backplane and you'll see the logic behind each detail of its design.

Start with the signal layers – four of them – with the most "noise sensitive" lines isolated from the others. The spacing and placement of the layers in this stripline (with embedded microstrip) design was calculated to enhance the backplanes' high frequency bypass characteristics.

It's the quietest backplane ever! Sharply reduced crosstalk is achieved by the increased separation of signal lines — both within and between the layers. Superior decoupling comes from the placement of both ceramic and tantalum capacitors between each slot. Low inductance, low impedance power distribution is insured by the close proximity of the dual power & ground planes and the strategic placement of power connectors for each voltage across the entire length of the backplane.

There's more logic on the outside. Schottky diode terminations. Interrupt and Bus Grant jumpers accessible from either side. Wire wrap pins with shrouds on the

> We'll FAX you the facts. Want the latest data in a hurry? Nothing is faster than Electronic Solutions' "FAX the FACTS'' program. Call our "800" number and give us the information you need from us. We'll FAX it to you immediately.

end slots of the J1 and every slot of the J2. Ground pins in between J2 slots to provide I/O cabling with interstitial grounds. And much more.

Choose any size from 2 to 21 slots in separate J1 or J2 or monolithic J1/J2 configurations. Call us today for the inside (and outside) story on the highest performance VME backplanes ever made. It's the logical thing to do.

6790 Flanders Drive, San Diego, CA 92121 (619) 452-9333 FAX: 619-452-9494 Call Toll Free: (800) 854-7086 In Calif.: (800) 772-7086

# SMC<sup>°</sup>. Above the rest.

Climbing takes skill, experience and teamwork. Reaching the top also takes leadership, forward thinking and focus. Since 1971, Standard Microsystems has applied this philosophy to the design and manufacture of standard and semi-custom integrated circuits.

Today, SMC's engineering expertise and extensive SuperCell<sup>™</sup> library allows us to offer innovative and timely solutions to your unique application needs. Our portfolio focuses on networking and mass storage controller devices for the computer industry.

The next time you face a networking or mass storage challenge, call SMC. Discover how our cost-effective and technically superior products can help you climb ahead of your competition.

The Standard for LAN and Mass Storage ICs.

35 Marcus Blvd., Hauppauge, NY 11788 (516) 273-3100 Fax (516) 231-6004

SuperCell is a trademark of Standard Microsystems Corporation CIRCLE NO. 3

Bruce Bourbon on System-level design Page 19

FOR ELECTRONIC ENGINEERS & ENGINEERING MANAGERS

Page 30

### TECHNOLOGY UPDATES

#### **Integrated Circuits**

| New chips whittle away<br>at networking costs                  | .24 |

|----------------------------------------------------------------|-----|

| As RISC wars escalate, simplicity<br>may be the first casualty | .27 |

### Software

### Computers and Subsystems

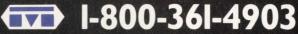

Futurebus + closes reality gap ......40

### **Design and Development Tools**

Page 55

### TECHNOLOGY AND DESIGN FEATURES

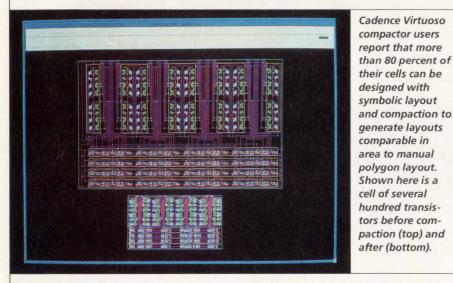

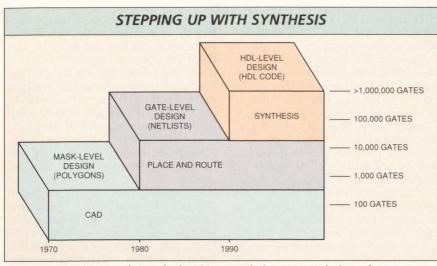

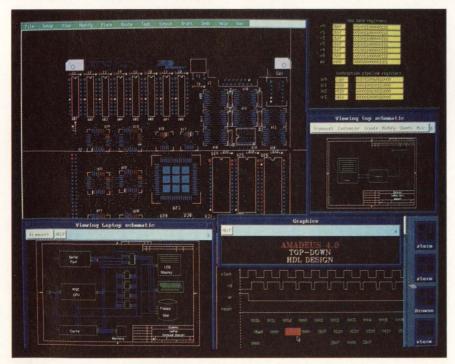

### Design entry tools evolve to meet future needs

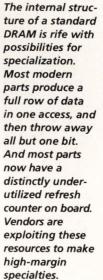

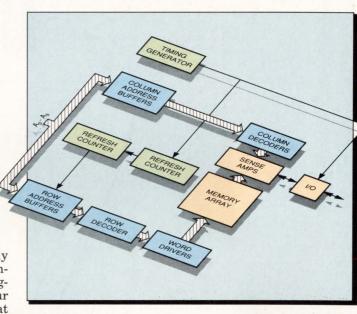

### DRAM vendors address increasing specialization

### **COVER STORY**

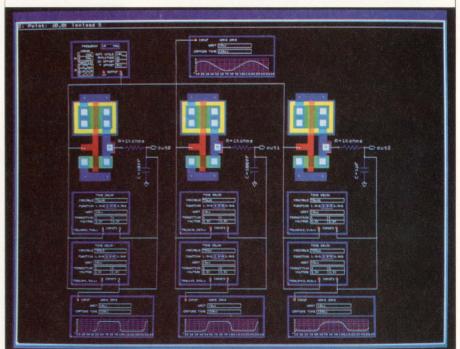

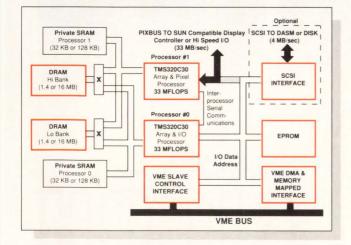

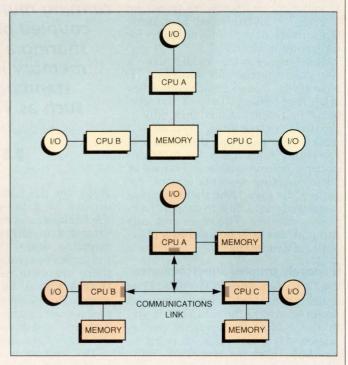

### Application determines best approach to multiprocessing

Multiprocessing gets around some of the shortcomings inherent in microprocessor design—not enough compute power. But applications determine which of a variety of multiprocessing schemes on standard or proprietary buses are used ......72

Page 89

### NEW PRODUCT HIGHLIGHTS

#### **PRODUCT FOCUS**

#### **Computers and Subsystems**

#### **Integrated Circuits**

| GaAs gate arrays integrate over 100k |     |

|--------------------------------------|-----|

| usable gates                         | 100 |

| 8-bit MCU gets 16-bit math speed     | 101 |

#### **Design and Development Tools**

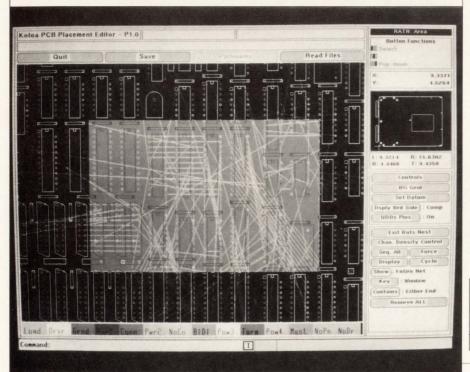

PCB tool targets high-density, mixed-technology architectures ...... 104

### Software

Image scaler/rotator teams with software in development toolkit ...... 107

### DEPARTMENTS

| News Briefs       | 8   |

|-------------------|-----|

| Editorial         |     |

| Advertisers Index | 124 |

# The newest system through space-time.

ali ali a

e li

The AMP Z-Pack Interconnection System is a scalable, high-density board-to-board/ cable-to-board system for nanosecond and subnanosecond applications, in 2 mm and .100" grid sizes to accommodate global packaging requirements.

10

15

> The fastest members use stripline technology, introduc

High-temp materials for SMT compatibility.

Twin-beam receptacles, 2 mm wipe.

3 1 1 4 4

Mall

Sequenced mating up to four levels.

2 mm versions accommodate two traces between lands.

Stripline versions isolate pin columns for 50 ohm interface.

Reliable compliantpin versions available.

ing reference planes between pin columns to retain maximum pin counts in a controlled impedance interface.

The design advantages are immediate: Z-Pack .100" stripline connectors accommodate 250 ps edge rates with no sacrifice in signal density: four rows = 40 lines per inch.

# Space: 40 lines/inch. Time: 250 ps.

2 mm stripline versions (500 ps) require just one pin row for reference, and open pin field versions in both centerlines handle 1.8 ns risetimes with a 3:1 signal/ground ratio. Standard spacing minimizes board redesign, and system modules stack end-toend with no loss of signal positions, offering true form/performance scalability in Futurebus-like applications.

For more information on the Z-Pack Interconnection System, call our Product Information Center at 1-800-522-6752. AMP Incorporated, Harrisburg, PA 17105-3608. For advanced design and manufacturing of complete characterized multilayer backplane systems, contact AMP Packaging Systems, Inc., P.O. Box 9044, Austin, Texas 78766, (512) 244-5100.

CIRCLE NO. 4

2

# THE SHAPE OF THINGS TO COME IN ASIC TECHNOLOGY.

VERTEX 📣 VERTEX 📣 VERTEX 📣 VERTEX 🎮 VERTEX 🎮 VERTEX 🙈 VERTEX 🙈 VERTEX 📣 VERTEX

As ever-advancing technology sends gate counts soaring above 300,000, the demands on ASIC designers

VERTEX & VERTEX & VERTEX

& VERTEX & VERTEX & VERTEX & VERTEX & VERTEX & VERTEX & VE

With Vertex tools and system-level expertise your ASIC design risk is reduced, making all your multi-chip ASIC designs first-time successes.

We complete the package through our

are steadily increasing. Fierce competition creates tremendous pressure to shorten time-to-market—even in the midst of rising design complexities. Chips *must* work right the *first* time.

Vertex Semiconductor Corporation is shaping the future for system-level ASIC designs. At Vertex, previously known as Integrated CMOS Systems, we've developed and refined a design methodology to tackle system-level issues. Our proprietary tools handle system partitioning, synthesis, timing analysis, and performance optimization, while supporting JTAG boundary and internal scan testing, to meet your toughest design challenges.

strategic alliance with Toshiba—giving us leading-edge fabrication from a world-class player. For more information, call us today: 408-456-8900. We're Vertex—your system-level ASIC solution company shaping the future.

VERTEX 📣 VERTEX 🙈 VERTEX 🙈 VERTEX 🙈 VERTEX 🙈 VERTEX 🙈 VERTEX

VERTEX

### NEWS BRIEFS NEWS BRIEFS NEWS BRIEFS NEWS BRIEF

### TI samples 16-Mbit DRAM

Texas Instruments (Dallas, TX) has begun sampling its 16-Mbit DRAM to a privileged few customers. TI is the first domestic supplier to sample the parts, joining the exclusive club that previously included only Hitachi, Toshiba and-to the consternation of the Japanese vendors-Korean giant Samsung. NEC is expected to begin sampling by the end of the month as well. TI is reportedly building the parts, which are said to be small enough for mass production, on a 0.6-µm line in Dallas. The next batch of parts will come from a new facility in Avezzano, Italy.

The pattern of announcements on 16-Mbit parts seems to indicate that DRAM design expertise has not become concentrated in Japan after all. The fact that a U.S. vendor, admittedly working with Hitachi on development, is among the first to sample parts, and that Samsung, going solo, has been able to leapfrog into the fledgling market, discredits the notion that one country could corner the market for advanced parts.

The number of entrants in the market at this early date must be keeping some executives awake nights. If price competition develops along national boundaries, erosion could severely harm all the players' efforts to recover their enormous investment in the 16-Mbit technology. — Ron Wilson

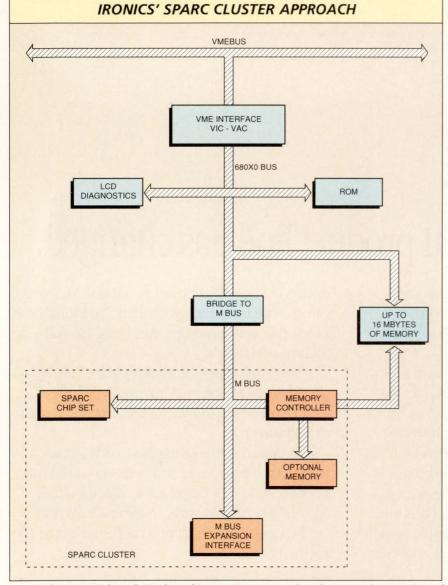

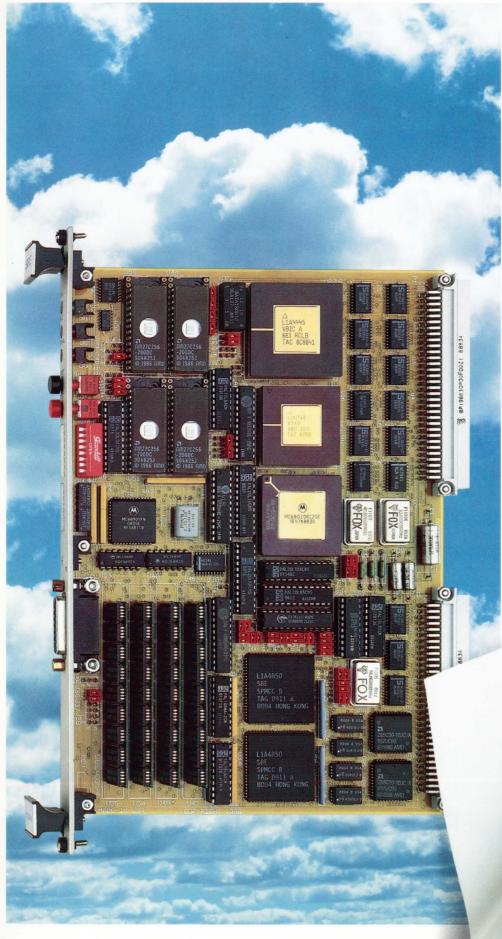

# Force and Sun ink deal in strategy tango

Under the terms of an agreement being completed between Force Computers (Campbell, CA) and Sun Microsystems (Mountain View, CA), Force will manufacture and market the Sun 1E, 6U VMEbus Sparc-based CPU card. While the move would seemingly end speculation as to what the two companies have been talking about—rumors had it that some Force equity was to be swapped for growth financing—the deal raises other significant questions. Is Sun abandoning the 6U VMEbus-board business? Will Force drop development efforts on the Motorola 88000 family?

Industry sources voice affirmation to both. Force's Fred Rehhausser, vice-president of operations, has been heard grumbling about Motorola's delay in introducing the next-generation parts. In addition, he claims the company has not properly promoted the chip, leaving it to Force (and other board and system vendors) to promote the architecture. Sounds like a variation of the restaurant quip, "The food is terrible, and besides, the portions are too small."

According to the same sources, Force will "have access" to Sun's proprietary ASICs, which are key to the board's performance and compactness. These include Sun's VME interface, its SCSI and Ethernet chips, and other internal drivers. No further terms of the deal—royalty payments, purchase agreements, other 6U Sun boards to be included at a future date, or exclusivity—were disclosed.

The move seems somewhat consistent with Sun's recent directions, which have been verbalized by Scott McNealy, the company's president, in numerous interviews: "We're going to put all our wood behind one arrow." And that arrow seems to be its workstation business. The board business could be interpreted as diluting the company's efforts.

By jumping on the Sparc bandwagon, Force might just be trading one set of problems for another. Sun is obviously going after the leading-edge workstation market, and to retain some significant share it must keep its position as performance leader. To do that, it has to maintain an edge in processor performance and in applications. Sun has already signaled its moves, shifting away from the Fujitsu processor to a next generation of its own design. to which it will have proprietary rights for at least the first iteration. This leaves all the clone makers hoping to compete in a "standards-driven marketplace" high and dry.

- Warren Andrews

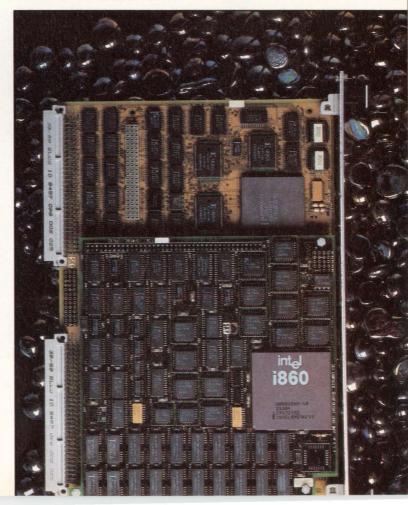

### Intel unveils plans for fastest supercomputer

Intel (Santa Clara, CA) has announced plans to build a \$10 million, massively parallel behemoth for the California Institute of Technology (Pasadena, CA) that theoretically will have a top speed of 30 GFlops. The supercomputer will contain 512 of Intel's 64-bit RISC i860 microprocessors, which is four times as many as used in Intel's largest supercomputer to date-a 128-processor system built for NASA's Ames Research Center. Plans for the new machine are a result of development efforts at Cal Tech and at the DARPAfunded Touchstone project, aimed at researching massively parallel microprocessor architectures.

- Tom Williams

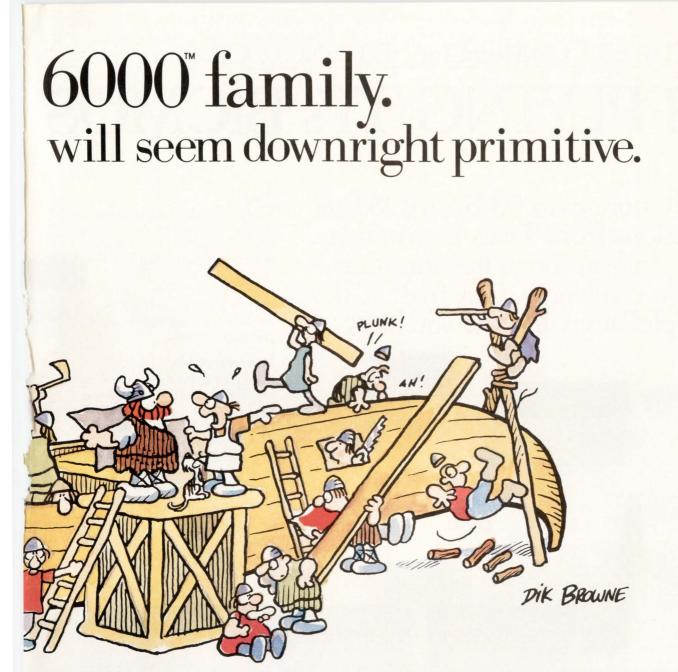

### IBM sets record for fastest RISC

Reaching just over 54 SPECmarks, the latest version of the IBM RISC System/6000 family is the current record holder for RISC workstation performance, edging out even the ECL-based Mips R6000. According to IBM (Armonk, NY), the speed of the new box, the Powerstation/Powerserver 550, comes from new silicon, rather than from architectural changes. The 550 uses new CPU components, fabricated in IBM's latest 0.5-µm CMOS technology and clocking at 41.6 MHz. This figure makes the multichip CPU faster than any announced singlechip CMOS RISC processor from merchant IC houses.

IBM's ability to achieve this speed and still maintain a good clocks-per-instruction ratio—as indicated by the nominal 56-Mips rating—are a further indication of the scalability of the R6000. The underlying architecture of the workstation is in fact that of the pioneering IBM 801 project, brought up to current thinking.

This architecture, in the hands of IBM, may well overcome a woefully late start to emerge as the machine to beat in high-end workstation applications.

- Ron Wilson

Continued on page 10

| Memory Displayed:<br>First Group Display<br>Data Format:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ed: Addr<br>Software Curson                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Cursor 1 = +000000<br>+Cursor 2 = +000004<br>+ = 13.560 µs                                                                       | Nemory Displayed: ACQNEN<br>First Trace Displayed: 000<br>Time/Div: 000 ns                                                                                                                                        | Cursor 1 • +0000000 ns<br>Cursor 2 • +0001128 ns<br>Cursor 4 • 1.128 µs |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| Loc Addr D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2X1<br>ata                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Time                                                                                                                             |                                                                                                                                                                                                                   |                                                                         |

| - 15 00F1E5B0 4<br>- 8 00F1E252 4<br>- 7 00F1E254 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 01C BRA.B 00F1E5AE<br>55F MOUEA.L (A7)+,A6<br>275 RTS<br>A00 TST.L D0<br>A08 BPL.B 00F1E25E<br>835 BTST.B 00F1E25E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | S - 556,919<br>S - 556,91<br>S - 556,91<br>S - 556,9<br>S - 556,<br>S - 556,                                                     |                                                                                                                                                                                                                   |                                                                         |

| 4 88F11848 6<br>9 88F11584 6<br>19 88F11584 6<br>19 88F11758 4<br>21 88F11758 4<br>23 88F11755 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 786 BEQ.B @071850<br>5FC MOVE #2700.5R<br>960 BSA.V 0071755<br>5E7 MOVENL AI0.DIA.0<br>FR LEA 0071775<br>188 MOVEQ #000018.0<br>818 ROVEQ #000018.0<br>818 ROVEQ #000018.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                  |                                                                                                                                                                                                                   |                                                                         |

| 32 88F11768 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 261 CLR.L D1<br>3F9 LER 00F30001,A1<br>218 NOVE.B (A0)+,D1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                  |                                                                                                                                                                                                                   |                                                                         |

| 34 88F1176C 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 398 NOVE.B (A0)+,(00,A1,D1.)<br>108 DBF D0,00F11768                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 43                                                                                                                               |                                                                                                                                                                                                                   | nnnnnnnnnnn                                                             |

| 41 80F11768 1<br>42 80F11768 5<br>43 80F1176C 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 218 NOVE.8 (H8)+,01<br>308 SUBQ.8 #1,00<br>398 NOVE.8 (A0)+,(80,A1,D1.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | u)                                                                                                                               |                                                                                                                                                                                                                   |                                                                         |

| 42 80F1176F 5<br>43 80F1176C 1<br>46 80F1176C 1<br>58 80F11768 5<br>51 80F11768 5<br>52 80F1176C 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3F9         LER 8078081.01           280         CER 807800           280         CER 602.01           280         CER 602.02           297         CER 602.02           297         CER 602.02           297         CER 602.02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                  | [H                                                                                                                                                                                                                |                                                                         |

| 55 80F11770 5<br>59 80F11768 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 198 DBF D8,88711768<br>188 DBF D8,88711768<br>188 MOVE.B (R0)+,D1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8 #5<br>8 #5                                                                                                                     | provide the second s                                                                                                   |                                                                         |

| earch + 1 Change 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Acques Processor Sear<br>o Refnes Support De                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Split<br>Display                                                                                                                 | Change   Reques<br>Cursors   To Reflet                                                                                                                                                                            | Search Russian Display Split<br>Def. Data Foracts Display               |

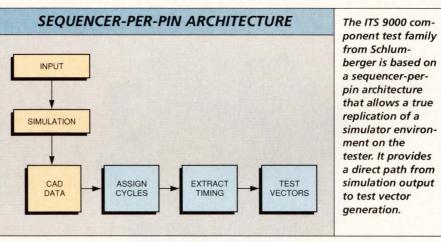

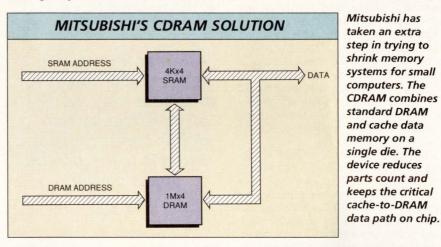

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | and the second states of the s                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                  |                                                                                                                                                                                                                   |                                                                         |