Pete Yeatman on board architecture

ME

MBI

Technology and Design Directions

FOR ELECTRONIC ENGINEERS & ENGINEERING MANAGERS

# Will performance win over sophistication in workstation buses?

FDDI chips struggle toward the desktop

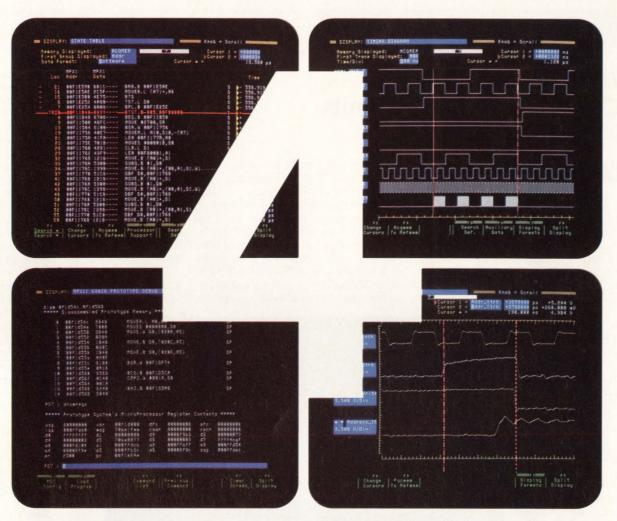

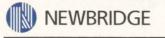

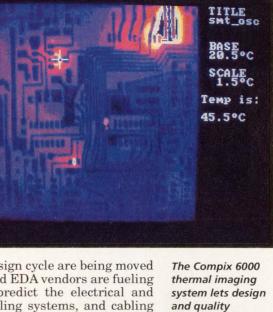

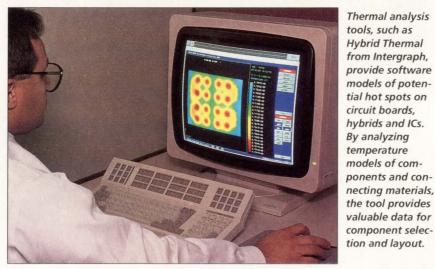

Tools bring vital information to early stages of system design

URBO

# Unparalleled, parallel performance.

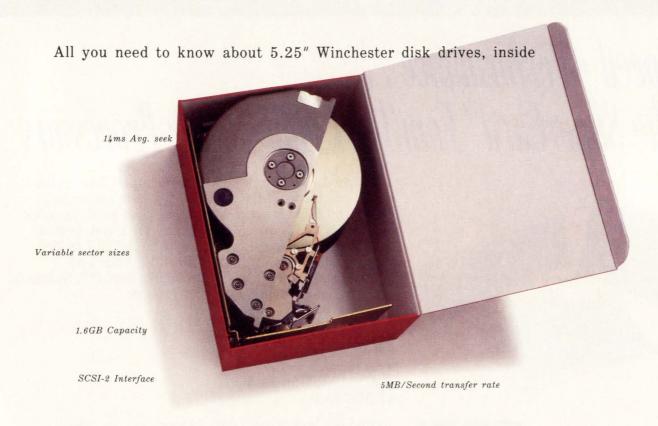

#### SCSI-2 is at your command with Rimfire® 6600 Series Parallel Disk Array Controllers.

Discover unmatched performance and data integrity for mass storage applications – the Rimfire 6600 series of Parallel Disk Array (PDA) Controllers.

The first array controller offering SCSI-2 as its host interface, as well as the first offered as a board level product, the Rimfire 6600 Series supports four data drives plus a single redundant drive. Because all disk data transfers occur in parallel, the array appears to the host as a single SCSI drive. For you, that means excellent performance. Transfer rates and capacity four times that of an individual drive. And exceptional data availability.

In addition, the flexibility of the PDA controller allows the OEM to select drives from many vendors. It's compatible with SCSI, operates with off-the-shelf host adapters and is priced significantly lower than other solutions of equivalent capabilities.

For detailed information on the Rimfire 6600 Series, or other SCSI-2 compatible products, call Ciprico, the industry leader in technology, technical support, customer service and respondability at 1-800-SCSI-NOW (1-800-727-4669). European customers call our United Kingdom office, (0703) 330 403.

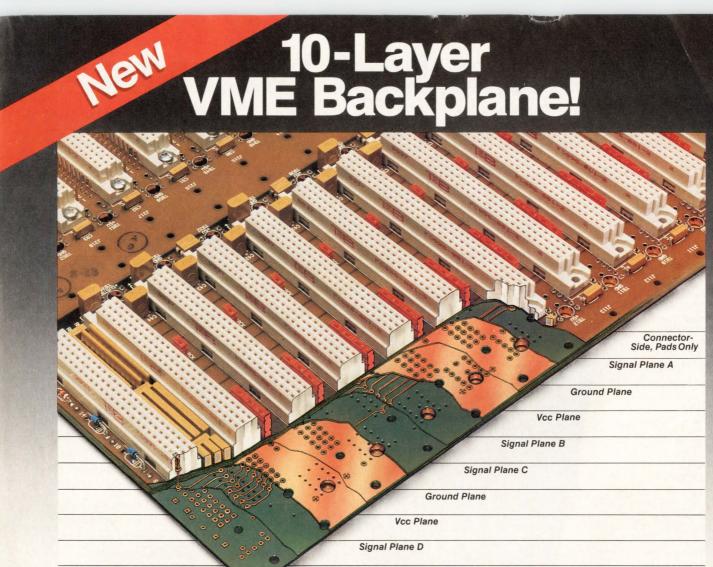

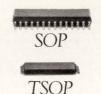

Solder-Side, Pads Only

# There's Logic To Every Layer!

Look inside the first truly reliable, glitch-free VME backplane and you'll see the logic behind each detail of its design.

Start with the signal layers – four of them – with the most "noise sensitive" lines isolated from the others. The spacing and placement of the layers in this stripline (with embedded microstrip) design was calculated to enhance the backplanes' high frequency bypass characteristics.

It's the quietest backplane ever! Sharply reduced crosstalk is achieved by the increased separation of signal lines — both within and between the layers. Superior decoupling comes from the placement of both ceramic and tantalum capacitors between each slot. Low inductance, low impedance power distribution is insured by the close proximity of the dual power & ground planes and the strategic placement of power connectors for each voltage across the entire length of the backplane.

There's more logic on the outside. Schottky diode terminations. Interrupt and Bus Grant jumpers accessible from either side. Wire wrap pins with shrouds on the

> We'll FAX you the facts. Want the latest data in a hurry? Nothing is faster than Electronic Solutions' "FAX the FACTS" program. Call our "800" number and give us the information you need from us. We'll FAX it to you immediately.

end slots of the J1 and every slot of the J2. Ground pins in between J2 slots to provide I/O cabling with interstitial grounds. And much more.

Choose any size from 2 to 21 slots in separate J1 or J2 or monolithic J1/J2 configurations. Call us today for the inside (and outside) story on the highest performance VME backplanes ever made. It's the logical thing to do.

6790 Flanders Drive, San Diego, CA 92121 (619) 452-9333 FAX: 619-452-9494 Call Toll Free: (800) 854-7086 In Calif.: (800) 772-7086

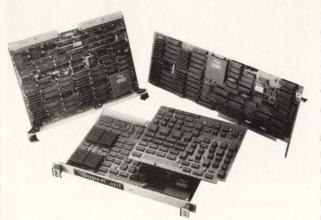

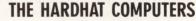

# At Last, a <u>*Truly*</u> Industrial 386 PC AT System for the OEM

Easy to mount Eurocard hardware with optional power supply. Can be rack mounted or bolted into any embedded system.

Two boards make a complete 386 computer with your choice of EGA or VGA display.

.

0

(

(1

(

01

11

(1

( ]

01

CI

01

0

4

C

1, 2, 4 or 8 Mbytes of on board. Full support for LIM EMS and BIOS shadowing.

On board support for COM1, COM2, LPT, keyboard, clock, floppy disk, and IDE hard disk.

Compact single / height Eurocard board format (100 x 160 mm) that doesn't flex or bend and withstands the toughest shock and vibration.

Small price to help you compete.

Three side mechanical bond into the card cage, yet easy to access for simplified maintenance.

\*\*\*\*\*\*

16 or 20 MHz 80386SX CPU and 80387 Arithmetic Unit. Introducing the first 386 PC AT system originally designed to be embedded into your machinery or instrumentation.

With the GESPAC AT system, "ruggedized PC" no longer describes a desktop PC in a stronger black box. Instead it is an architecture made to last by design, with such features as small and robust board format, and ultrareliable pin-in-socket connector.

What's more, the GESPAC System is built for performance with Intel's original 16 or 20 MHz 80386SX processor and 80387SX Arithmetic Unit. In fact, this system is the most compact implementation of the 386 in the market today.

The powerful G-64/96 bus interface lets you customize your AT system with any of the 200-plus system components available from GESPAC, to match virtually any system requirement.

Take advantage of GESPAC's 12 years of experience in serving the OEM marketplace. Call today to receive your free data sheet and GESPAC's catalog of board level microsystem products. Ask about GESPAC's exclusive Guaranty of OEM Long Term Delivery.

Unprecedented selection of inexpensive I/O functions, \_\_ from the simplest parallel and serial I/O, to high performance networking, MIL 1553, motion control, and computer vision.

FRANCE

France

Z.I. les Playes

83500 La Seyne

Tel. 94 30 34 34

Fax. 94 87 35 52

# Call Toll Free 1-800-4-GESPAC or call (602) 962-5559.

INTERNATIONAL 18, Chemin des Aulx CH-1228 Geneva Switzerland Tel. (022) 794 3400 Fax. (022) 794 6477

Full 32-bit expansion bus for easy system expansion and customization with up to 20 slots.

**USA - CANADA** 50 West Hoover Ave. Mesa, Arizona 85210 USA Tel. (602) 962-5559 Fax. (602) 962-5750

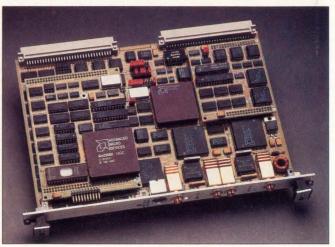

board architecture Page 23

VOL. 30, NO. 3

FEBRUARY 1, 1991

**COMPUTER Icchnology DESDED Icchnology DESDED Directions**

#### **TECHNOLOGY UPDATES**

#### Software

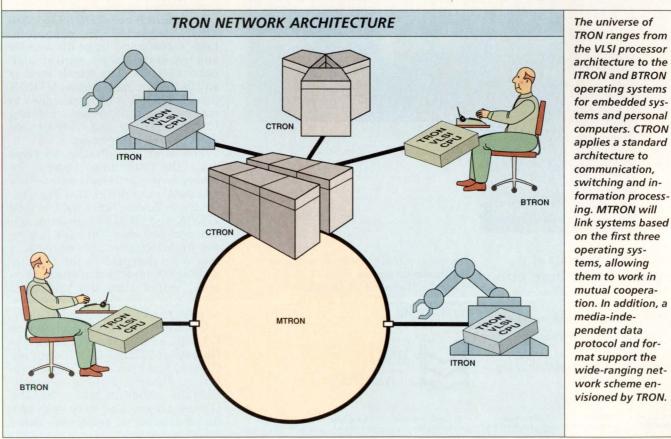

Japan's Tron initiative may be opportunity for U.S. manufacturers......35

#### **Design and Development Tools**

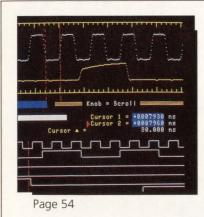

Page 71

#### **TECHNOLOGY AND DESIGN FEATURES**

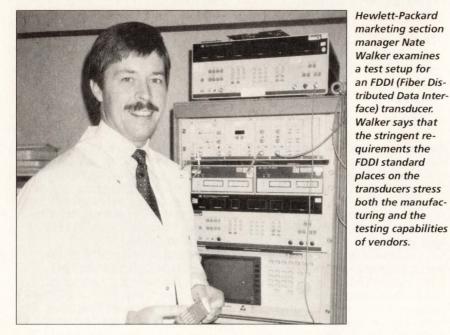

### FDDI chips struggle toward the desktop

The success of FDDI networking may stall at the high end unless workstations and PCs are included ......61

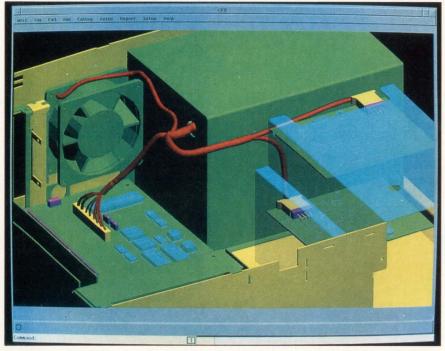

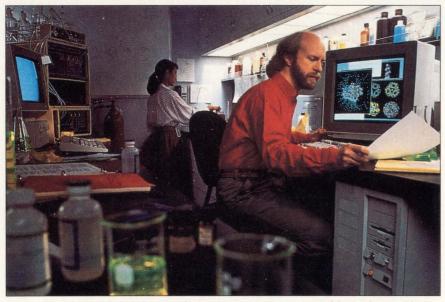

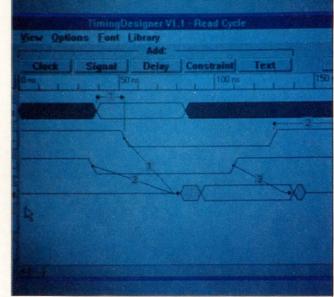

### Tools bring vital information to early stages of systems design

With shrinking design times and growing systems complexity, designers rely on tools that predict component behavior before prototyping......71

#### COVER STORY

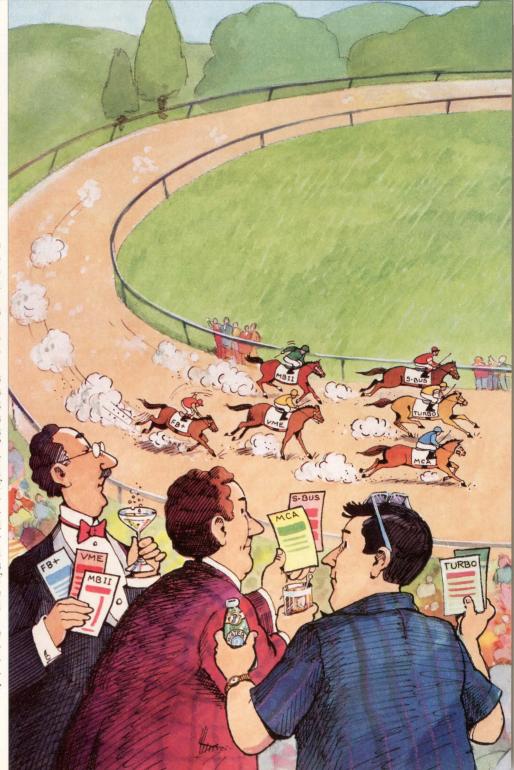

### Will performance win over sophistication in workstation buses?

A new class of standard bus has emerged to support the I/O requirements of compact desktop workstations. The continued growth of processor performance is driving these buses to higher speeds and minimal overhead at some cost in flexibility......78

Page 93

#### **NEW PRODUCT HIGHLIGHTS**

#### PRODUCT FOCUS

#### **Integrated Circuits**

| 100 |

|-----|

| 102 |

|     |

| 104 |

| 106 |

|     |

#### Software

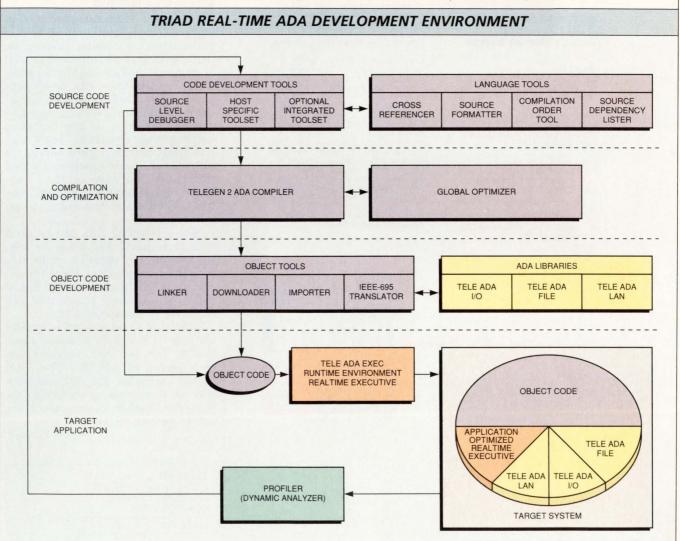

| Ada development environment |    |   |

|-----------------------------|----|---|

| is all Ada1                 | 07 | 7 |

#### **Design and Development Tools**

| Analog layout editor links            |

|---------------------------------------|

| schematics to physical design109      |

| Design tool solves timing problems110 |

#### DEPARTMENTS

| News Briefs       |   |

|-------------------|---|

| Editorial12       |   |

| Calendar16        | ; |

| Advertisers Index | ) |

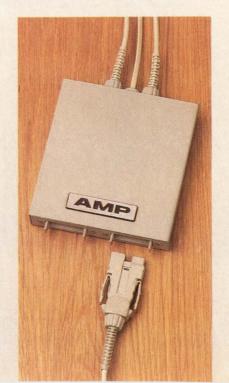

# FDDI. From deskwork to network.

Good news for networks!

The X3T9.5 Task Group, under the procedures of ANSI Accredited Standards Committee X3, has reaffirmed approval of the Media Interface Connector (MIC) for the proposed FDDI (Fiber Distributed Data Interface) Physical Layer Medium Dependent (PMD) document. More good news! AMP has the complete fiber optic interconnection system—the AMP OPTIMATE Fixed Shroud Duplex System—that meets all FDDI PMD requirements. And includes all the physical components you need to make your fiber optic network a reality.

Of special note: the transceiver is capable of operating at data rates up to 125 Mb/s. Available in standard or raised (+5v) ECL logic, it gives you a compact, board-mount data link in an industry-standard 22-pin package. Reliable duplex mating and electro-optic conversion are now easier than ever.

All system components, in fact, are easy to install and reconfigure. Our field termination kit makes short work of attaching duplex connectors to fiber cable. And because all interconnections use a floating interface, you get consistent, low-loss mating (0.6 dB typical) throughout.

You can also order complete, custom-built cable assemblies from us. Either way, you'll have the assured compatibility that comes from dealing with only one supplier for all your FDDI interconnection components. A supplier whose capability

THIS IS AMP TODAY.

in fiber optic technology is everything you'd expect from the world's largest connector company.

For technical literature and more information, call 1-800-522-6752. AMP Incorporated, Harrisburg, PA 17105-3608.

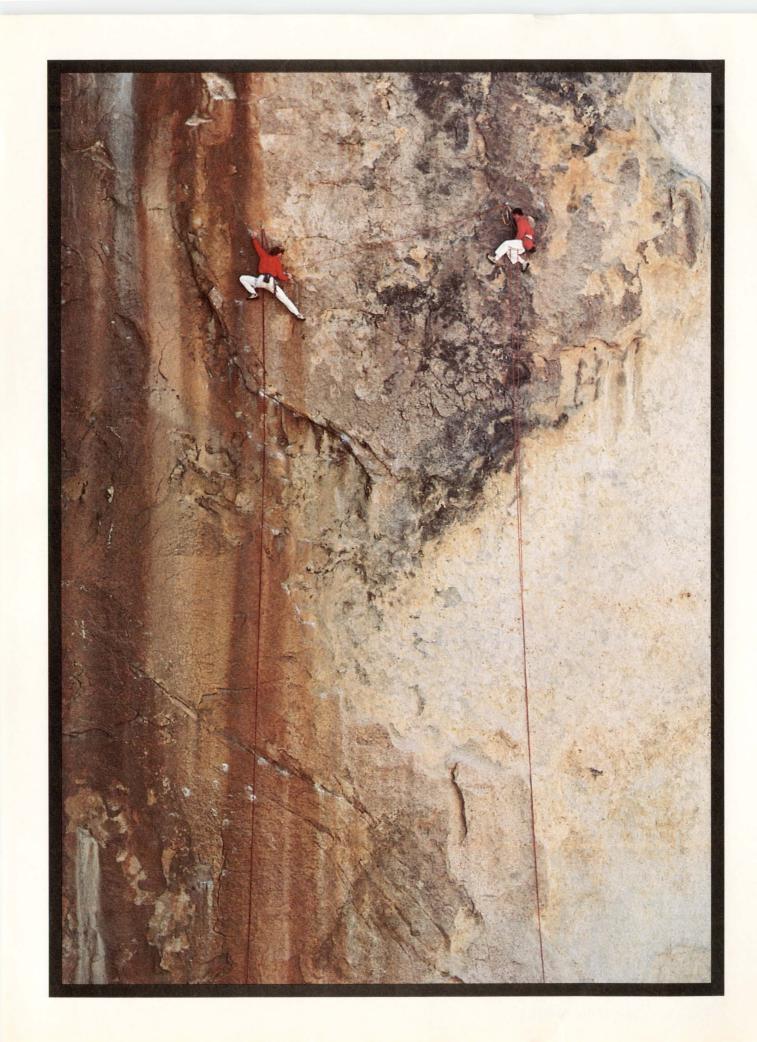

Networking challenges can often be formidable, nearly insurmountable. But by joining forces and working together, we can succeed in ways that didn't seem possible. That's "The Power Of Partnership."

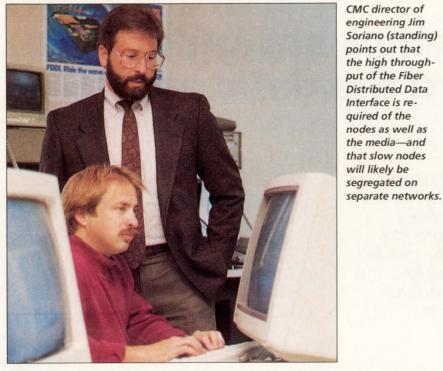

At CMC, The Power Of Partnership is our commitment to you – the system designer, integrator and manufacturer – to finding solutions to your most ambitious local and wide area networking enterprises. To providing you with a broad and flexible base of protocol software and intelligent Ethernet, FDDI and Primary Rate ISDN adapters, each linked to the expertise and support of a highly skilled technical team.

## The Power Of Partnership

For over a decade we have been providing high performance networking products to the world's leading computer companies. As a part of Rockwell International, our solutions-based approach to your most demanding networking problems means you can place your trust and confidence in our products and our people. We're here to help you succeed.

To scale new heights in connectivity call for *The Power Of Partnership.* Call 1-800-CMC-8023.

CIVIC A Rockwell International Company

125 Cremona Drive, Santa Barbara, CA 93117 • Phone: 1-805-562-3173, 1-800-CMC-8023 FAX: 1-805-968-6478 • In Europe: 44-81-577-2800

The Power Of Partnership and CMC are trademarks of CMC.

### NEWS BRIEFS NEWS BRIEFS NEWS BRIEFS NEWS BRIEF

#### Force inks deal to manufacture Sun boards

Force Computer (Campbell, CA) has finalized a contract with Sun Microsystems (Mountain View, CA) to manufacture Sun's 1E VME board and other Sparc-based technology. Meanwhile, a second generation, the 2E, is apparently already under development. According to Peter Palm, board-level marketing engineer at Sun, the 2E version will boast more than twice the performance of the 1E, promising 28 Mips and 4.5 MFlops.

Look for whatever Sparc 2E technology is surfacing to appear on both VME and Futurebus+ almost simultaneously. According to Scott McNealy, Sun's president and CEO, "Sun anticipates that the combined marketing and sales impact of the two companies will make Sparc the leading RISC architecture on VMEbus by the end of 1991." The move certainly emphasizes the push Sun is putting behind its Sparc architecture.

But the Sun/Force team may have some problems making Sparc the dominant RISC architecture on VME. Motorola is heavily pushing its 88K board, and it's rumored a few other VME companies (besides Force, which already offers an 88K board) will soon have offerings. The major player in the RISC/VME market. however, might just end up to be MIPS Computer Systems (Sunnyvale, CA). At least two companies, Lockheed Systems (Nashua, NH) and Omnibyte (West Chicago, IL), already offer MIPS R-3000 VME boards. Lockheed initially offered only a mil version, but at the Buscon/90-East show it entered the commercial market. Lockheed, with a board full of big, expensive ASICs, will probably be looking to faster processors (their current offering is clocked at 25 MHz) for an immediate jump in performance, while Omnibyte hopes to get an early entry in the R-4000 market. It's guessed Lockheed will close in on the 50-Mips performance range with its next-generation product.

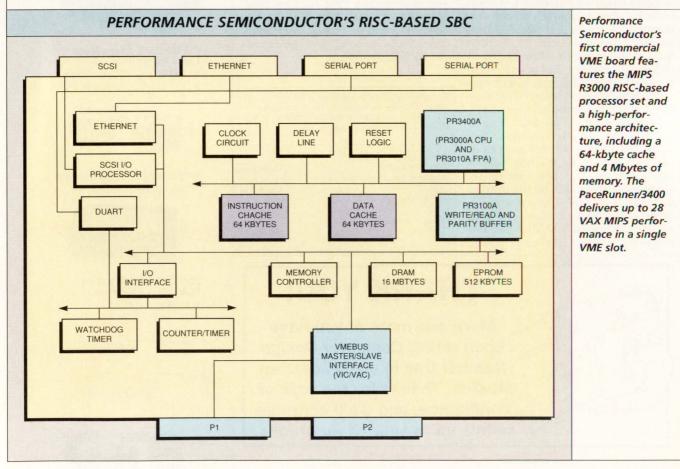

At this writing, it's expected that the Buscon/91-West show will see another entry in the MIPS Computer market: Performance Semiconductor (Sunnyvale, CA) will offer its first commercial board based on its own R-3000 chip set running at 25 MHz. Later in the year it expects to boost chip speed to 33 MHz and by year-end to 50 MHz. —Warren Andrews

#### Another HDTV team goes with all-digital simulcast system

After a year and a half of cooperative research, Zenith Electronics (Glenview, IL), AT&T Bell Laboratories (Murray Hill, NJ) and AT&T Microelectronics (Berkeley Heights, NJ) have expanded Zenith's spectrum-compatible high-definition television simulcast system. Unlike the original analog and digital approach, the new system incorporates new digital techniques for an all-digital simulcast HDTV system. Of the five contenders vying to be se-lected as the U.S. simulcast HDTV broadcast standard, the Zenith/ AT&T team is the third to go digital. Japan has committed itself to a combined analog and digital approach.

Interference is the largest deterrent to an all-digital simulcast HDTV system—one that will broadcast HDTV on currently unusable channels in the VHF and UHF broadcast spectrum simultaneously with today's National Television System Committee television stations. Zenith, responsible for system definition and transmission technology, has eliminated interference from the standard television signal by placing a digital filter at the HDTV transmitter and a complementary filter in the HDTV receiver. The new technology offers noise-free HDTV signals not only for terrestrial broadcasting, but also for cable, satellite, fiber, and VCRs.

Because all-digital HDTV systems require significantly more video compression than analog counterparts, AT&T Bell Laboratories has developed a video compression algorithm, featuring motion compensation and adaptive quantization, that squeezes the HDTV data into a 6-MHz channel without loss of resolution. Among the digital signal processing chips being developed by AT&T Microelectronics for prototype Zenith HDTV receivers is one that performs about 4 billion operations/s—1,000 times the performance of a typical desktop computer. —Barbara Tuck

#### Toshiba buys into DRAM futures, Moto buys out

Illustrating both its commitment to the memory market and the staggering price of admission to this exclusive game, Toshiba Corp, represented in the United States by Toshiba America (Irvine, CA), has announced the start of a new DRAM plant site in Yokkaichi, Japan. The plant, according to Toshiba, will manufacture 4-Mbit and 16-Mbit DRAMs, beginning production in 1992.

production in 1992. The 135,000-ft<sup>2</sup> facility is expected to peak at 3.5 million chips per month. Toshiba estimates the cost of the plant will total 100 billion yen. The size of the plant and the level of investment suggest that Toshiba doesn't expect a worldwide softening of DRAM demand in the long term, nor does the company seem to feel that surplus CMOS manufacturing capacity will be a big issue by 1992.

In a perhaps unrelated move. Motorola Semiconductor (Austin, TX) has announced that it won't manufacture 4-Mbit DRAMs after all. The company says it will focus its attention on its existing 1-Mbit DRAM capability and on future SRAM products. Motorola will rely on its relationship with Toshiba to provide for the company's future 4-Mbit and 16-Mbit DRAM requirements. This represents a turnabout from previous Motorola strategy, in which the company sought to acquire DRAM technology from Toshiba in exchange for 68000-family CPU technology.

-Ron Wilson

# Tough, rugged boards that handle shock, vibration, heat, cold and the budget squeeze

MATRIX VMEbus Rugged Series loves harsh environments. Designed to operate from -40° to +85°C, the Rugged Series surpassed these temperature specs and sus-

tained continuous operation during a series of severe environmental tests.\* At offthe-shelf prices, these boards are tough to beat.

Rugged 32-bit processors, memory boards, and a variety of specialty I/O boards make harsh environments manageable. Available in extended

\*Test results for the MATRIX Rugged Series show boards withstood 105 g's of shock for 6 ms and 10 g's of vibration at the first natural resonant frequency. temperature and/or rugged versions, these products provide all the power and flexibility VMEbus can offer. And at a fraction of the cost of full Mil-spec products.

> Call today for more information about our Rugged products. For less extreme applications, ask about our full line of VMEbus Industrial Quality systems, boards and enclosures. Telephone: 1-919-231-8000. FAX: 1-919-231-8001.

See us at Buscon West, Booth #809 1203 New Hope Road, Raleigh, NC 27610

### NEWS BRIEFS NEWS BRIEFS NEWS BRIEFS NEWS BRIEF

Continued from page 8

#### U.S., Japan eye joint Object standards

The efforts of a large consortium of vendors to establish standards for object-oriented computing in the form of the Object Management Group (OMG) appear to be bearing commercial fruit. Hyper-Desk (Westboro, MA), a new company formed from a project started within Data General, has announced that it will develop and market a new class of software that will give users access to applications across computer networks via a single-user interface. Hyper-Desk is being financed by ASCII (Tokyo, Japan), one of Japan's largest vendors of systems and application software for personal computers, workstations and network servers.

HyperDesk's software will be based on distributed object management concepts, and products will be submitted in response to **OMG's** first Request for Proposal in its effort to establish a common framework for object-oriented software and standards. The framework envisions programs as freestanding components, or objects that can be combined and rearranged and can communicate with each other across networks, hardware environments and operating systems. -Tom Williams

#### Stacked-trench structures target 64-Mbit DRAMs

Researchers at Toshiba America Electronic Components (Irvine, CA) have developed a new memory cell structure that advances the level of integration beyond that necessary for the development of 64-Mbit DRAMs. According to Toshiba, the asymmetrical stacked-trench (AST) structure reduces the area of individual cells to less than 60 percent of that of cells in the simpler trench structure used for 4-Mbit and many of the experimental 16-Mbit DRAM chips.

Whereas Toshiba's prototype 16-Mbit DRAMs use 0.6-µm technology, company researchers have achieved a 0.4- $\mu$ m lithography for the 1.53- $\mu$ m<sup>2</sup> 64-Mbit DRAM cell with Excimer Laser equipment. With trenches located asymmetrically in the AST structure rather than in parallel as in conventional trench structures, Toshiba achieves a 6- $\mu$ m separation between each adjacent trench cell, as well as between the electron-flow path and the storage capacitor, thus maintaining the minimum distance required to avoid leakage between and within cells.

According to Frank Stefan Becker, press officer for Siemens (Munich, Germany), issues of process simplicity and height differences over chip topology are as significant as leakage when striving for the miniaturization level required for a 64-Mbit DRAM. Siemens, which has partnered with IBM (Armonk, NY) on 64-Mbit DRAM development, is experimenting with a 1.62-µm<sup>2</sup> stackedtrench capacitor cell characterized by extremely thin capacitor electrodes combined with a 5-nm dielectric. Specifications of the experimental 64-Mbit DRAM, which requires a 3.3-V power supply, include 0.4-um lithography and a 40ns access time. -Barbara Tuck

## 1991—The year of the cache?

1991 will be "the year of the cache," according to Ray Alderman, technical director of the VFEA International Trade Association (Scottsdale, AZ). He believes that cache technology will dominate the design front and will be an element of all new high-performance systems. And while cache is accepted as critical to many processor and systems today—and is one of the critical elements of the Futurebus+ specification—it's not universally considered a panacea for all high-performance systems.

Some tend to look at cache as being analogous to a turbocharger on an automobile engine. Not too many years ago, turbochargers were looked at as the ideal way to increase auto horsepower without the weight associated with a larger displacement. Turbocharged engines are still made, and in the right applications provide enormous benefits for both automobiles and aircraft. But the benefits are not universal.

So it will be with cache, some believe. "1991 will be the year of the cache just as 1986 was the year of the turbocharger," speculates one system maker. "Cache will be a significant component in memory architectures; however, it will have to be treated with extreme caution not to have the wrong effect on performance. Particularly with today's processors. With multilevel pipelines, cache could actually reduce, rather than increase, performance."

-Warren Andrews

## U.S. semiconductor firms gain market share

For the first time in 12 years, U.S. semiconductor manufacturers gained ground against their Japanese counterparts. Falling DRAM prices, a new study says, is the foremost cause.

Figures from market research firm Dataquest (San Jose, CA) show that U.S. firms grew nearly 2 to 36.5 percent of the estimated \$58.4 billion worldwide market for semiconductors. Intel and Motorola, the two largest domestic chip makers, drove the trend. Both companies produce microprocessors and special-purpose ICs and benefited from a 23 percent worldwide increase in these markets. According to Dataquest, Intel leaped from eighth to fifth place in the rankings, while Motorola held its spot as the fourth largest supplier.

While hurt by DRAM price drops, Japanese chip makers continue to be the world's biggest chip suppliers. NEC, Toshiba and Hitachi still hold the top three spots, although each saw an estimated 1 percent decline in revenue because of a heavy reliance on memory chips, according to Dataquest. Despite high demand for these chips, there are plenty in supply. This scenario lead to sharply falling prices during the past year. —Jeffrey Child

# **DY 4 VME** When you must win!

For your "must-win" defense and aerospace programs, put the world's leading supplier of MIL-SPEC VMEbus systems on your team. Ready-to-run VMEbus systems from DY 4 are selected overwhelmingly by system integrators for aerospace and defense programs world-wide.

DY 4 provides performance, reliability and costeffectiveness through integration of a full range of open-system VMEbus products and services to military, ruggedized and commercial standards.

DY 4's system solutions incorporate non-developmental item (NDI) products from the broadest product line in

Customer First, **Quality Always**

21 Fitzgerald Road, Nepean, Ontario K2H 9H4 Tel: (613)596-9911 Fax: (613)596-0574

the business - CPUs... memories... communications controllers... analog I/O... high-performance graphics engines... chassis... Ada\* foundation software and built-in-test (BIT) diagnostics.

DY 4 provides a comprehensive quality program to MIL-Q-9858A and fully compliant configuration management to MIL-STD-483; design procedures conform to MIL-STD-1521 with manufacturing according to MIL-I-48604 (quality control) and soldering to MIL-STD-2000 in an ESD-controlled environment.

Campbell, CA Tel: (408) 377-9822 Fax: (408) 377-4725

Hanmel, Denmark Tel: +45-86-963624 Fax: +45-86-962575

Nashua, NH Tel: (603)595-2400 Fax: (603)595-4343

Pennant Hills, Australia Tel: +61-2-484-6314 Fax: +61-2-875-1665

1.

\*Ada is a trademark of the United States Department of Defense CIRCLE NO. 7

The United States isn't setting a standard; it's filling in an order form.

Tom Williams Senior Editor

## A confederation of fools

erhaps a good way to view the differences between American and Japanese business strategies is to consider the games of chess and go. In chess, the object is to capture individual pieces and corner the king. In go, the object is to occupy strategic positions to control territory. The acquisition of MCA by Matsushita serves as an example of the devastating effects of a go mentality vs. a chess mentality, and bodes ill for the future.

The first reactions in the press were that the U.S. culture was so lucrative that the Japanese probably would not block the release of films like *Tora! Tora! Tora!* This is the judgment of a player who thinks he has just lost a rook when in fact he has lost half of his maneuvering area. The MCA acquisition, along with the earlier acquisition by Sony of CBS Records, is really about digital audio tape and high-definition TV—and even more ominous issues beyond those.

The situation leaves the impression that the U.S. government and business elite is a confederation of fools—fools who treat employees like the enemy; who measure success in three-month increments; who can't bear to invest in research without assurance of an immediate return.

In the past few years the recording industry was obsessed with defending its queen—an outmoded revenue and royalty structure—from the DAT threat. U.S. manufacturers, cowed by the threat of lawsuits, failed to design and develop DAT products. While Congress dithered, the administration recited platitudes about free enterprise. During this pointless melodrama, small white stones were calmly being placed on the board.

The result is that the recording industry's foolish resistance to DAT has been broken. DAT will emerge in the market, but only from Japanese companies. The next stone awaits FCC approval of a U.S. HDTV standard.

A significant research investment by the U.S. television industry has developed key technologies—to the ultimate economic benefit of those controlling the manufacture of television sets, video cameras and, now, vast libraries of program material. While the FCC will proudly proclaim a U.S. standard, the Japanese will view it in its true form—a manufacturing specification. The United States isn't setting a standard; it's filling in an order form.

The costs of fab for advanced submicron ICs are so high that only the volume of the consumer market can absorb the expense. Thus he who controls the consumer market will eventually control the semiconductor market. Another white stone is placed on the board. Advances in semiconductor technology will flow not from the military and aerospace down to the consumer but from consumer applications into military and space fields by reason of simple economics. And, should the Go Masters become so inclined, it's only a short step to domination of military and space technologies.

Editor's Note: Tom recently returned from a two-week editorial visit to Japan. His observations confirmed some of our loudly voiced positions.

# "THEY LAUGHED WHEN WE PLUGGED A PC IN OUR VME SYSTEM...

**"The pressure was on.** Shorten our design cycle. Cut our software costs. Deliver the "gee-whiz" features customers wanted. But the old solutions weren't working. We needed a new approach.

We looked to the PC. Others looked at us like we were nuts. They sent memos. *The PC is not a* real *computer*.'...'Not *enough horsepower*'...'Just *a pretty user interface*' ...'It *can't survive that environment*.'

#### But the PC is going

places. Over 40 million are in use: 4 million in industrial environments. Another 1.4 million are expected on the plant floor this year. From the moment we plugged in a RadiSys Embedded PC, we understood why. Software for PCs is abundant and inexpensive. We had two dozen software houses fiercely competing to sell us high quality, man-machine

interface software. Why should we reinvent the wheel? For multi-tasking operating systems, we could choose from Windows 3.0, OS/2, UNIX, VRTX – all with integrated VMEbus support from RadiSys.

There is a wealth of development tools available to shorten design time. No wonder the PC is the world's most popular software development

host. And PC-based networking is light-years ahead. PC versatility is unmatched.

We can give customers what they want, right now. More options. Proven features. Everybody knows how to use the PC, our own team and our customers. And it's a sure bet that future application programs, languages and OS standards will run on it. PC horsepower is up there. The new Embedded 386 and 486 PCs have more than enough power to handle our mix of user interface and control functions. We got the best of both worlds. Plugging a RadiSys Embedded PC directly into the VMEbus gave us the full performance, ruggedness and reliability of the VME form factor, plus all the PCs software advantages. You know the rest of the story. That Embedded PC has the whole company laughing.

All the way to the bank."

Join the party! Call RadiSys at 800/950-0044 (fax requests: 503/690-1228) for a catalog of Embedded PC Products and brochure "Open New Windows of Opportunity With Embedded PCs."

### The Inside Advantage

19545 NW Von Neumann Dr. Beaverton, OR 97006 USA (800) 950-0044 (503) 690-1229 Fax (503) 690-1228

Copyright © 1990 RadiSys Corporation, Inc. All rights reserved. EPC is a registered trademark and RadiSys is a trademark of RadiSys Corporation. Windows 3.0 is a trademark of Microsoft Corporation. OS/2 is a trademark of International Business Machines Corporation. UNIX is a registered trademark of AT&T. VRTX is a registered trademark of Ready Systems, Inc. 386 and 486 are trademarks of Intel Corporation.

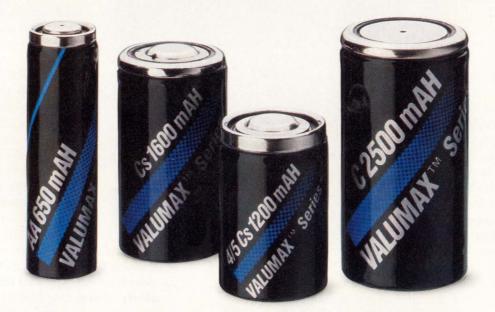

# Introducing the Highest Standards in the Industry.

## Gates New High Capacity VALUMAX<sup>™</sup> Line.

At Gates, our standards have reached new heights. With our VALUMAX line of Ni-Cd cells—the best value cells on the market.

VALUMAX cells are available in all the sizes you need to make virtually any product perform like no other standard cell can. For example, the VALUMAX C cell gives you up to 25% more run time. And our 4/5 Cs, Cs and AA cells deliver as much as 33% more capacity than even our closest competitor. In fact, with VALUMAX you get premium performance without paying the premium price. And that makes VALUMAX the best value—dollar for dollar—of any cell you can buy.

So isn't it time you raised your standards? Gates VALUMAX—we're setting the standard.

Gates Energy Products, Inc., P.O. Box 861, Gainesville, FL 32602, **1-800-67-POWER.**

The power of great ideas.

# You'd Have to Go to Great Lengths to Match the Capacity of Our New VALUMAX Cells.

At Gates, we've gone to great lengths to give you the longest possible run times in a wide range of cell sizes for virtually every application. For example, the VALUMAX C cell gives you up to 25% more run time

than any other standard C cell. And the VALUMAX 4/5 Cs, Cs and AA cells deliver as much as 33%

more run time than even our closest competitor.

In fact, with VALUMAX you get premium performance without paying the premium price. And that makes VALUMAX the best value-dollar for dollarof any standard cell you can buy.

The way we see it, the others still have a long way to go. And, at Gates, we think you shouldn't have to go to great lengths when you want a standard cell

that lasts a long time. Gates Energy Products, Inc., P.O. Box 861, Gainesville, FL

#### ▲ ronics now enables you to mix and match processor families. The *ultimate* in performance and flexibility.

**IRONICS**Call our Product

Hotline today

800 334 4812

ADVANCING VME MULTI-PROCESSING

#### CALENDAR

#### CONFERENCES

#### February 5-7

#### AFCEA 2d Annual Military/Government Computing Conference and Exposition

Hyatt Regency Crystal City, Arlington, VA. The exposition will offer the latest in computer software and hardware products to link mil-

itary and government needs with the latest industry technologies, applications and services. The conference will also feature tutorials, including "Open Systems Architecture" and "Information Engineering," and technical tracks, including "Technology Advances" and "Software Development/Maintenance." Information: AFCEA Programs Office, 4400 Fair Lakes Ct, Fairfax, VA 22033-3899, (703) 631-6125. Circle 366

#### February 24-28 Nepcon West '91

Anaheim Convention Center, Anaheim, CA. More than 1,000 exhibitors will display the latest in

products and technology for the design, fabrication, assembly, packaging, inspection, and test of printed circuits and electronic assemblies at this 29th annual conference and exhibition. Special features include over 50 sessions on surface-mount technology, several sessions on applicable environmental issues and a session on planning for the 1992 European Economic Community. Information: Cahners Exposition Group, 1350 E Touhy Ave, Des Plaines, IL 60018, (708) 299-9311.

#### March 13-20 Hannover Fair CeBIT '91

Hannover Fairgrounds, Hannover, Germany. The more than 4,000 exhibitors from 40 countries at CeBIT will attract computer and com-

munications professionals from 100 countries. The show will include NetWorld Europe, an exhibition and conference presenting 200 networking and connectivity firms from around the world. NetWorld will feature demonstrations such as EurOSInet and Multinet, as well as conferences and seminars on developments in network computing, LANs and wide area networks. Information: Hannover Fairs USA, 103 Carnegie Center, Princeton, NJ 08540, (609) 987-1202. Circle 369

#### April 8-11 NEMDE '91

McCormick Place, Chicago, IL. The National Electronic Manufacturing and Design Exposition and Conference is designed to present

a complete spectrum of products and equipment to the entire engineering and management team. The conference will include 14 technical sessions, 12 workshops and eight professional advancement courses. Sessions include "Design for Thermal Management," "Functional Test" and "Infrared Reflow Soldering Considerations." Information: Cahners Exposition Group, 1350 E Touhy Ave, PO Box 5060, Des Plaines, IL 60017-5060, (708) 299-9311. Circle 370

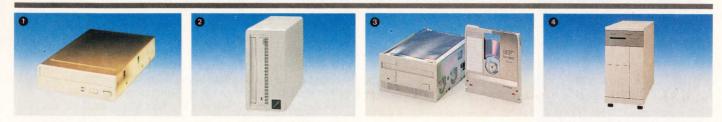

When it comes to mass storage needs, your choice is clear: Ricoh optical disc drives. From WORM and rewritable to bare drive and entire library units or subsystems, Ricoh offers a world of choice. Each drive boasts quality you can trust to safe-guard vital information. The kind of quality that comes from over 50 years of know-how in optics and image processing, in such products as cameras, copiers, facsimiles, telepress, laserprinters and scanners. Now you know why Ricoh is the world's leading supplier of 5-1/4" optical disc drives. For more information, call 1 (800) 955-FILE.

- RH5500/5-1/4" REMOVABLE CARTRIDGE HARD DISK DRIVE

- RS-9100H/5-1/4" HALF-HEIGHT WORM SUBSYSTEM

- **3** RO-5030EII/REWRITABLE OPTICAL DISK DRIVE

- BJ-5330E/MAGNETO-OPTICAL DISK LIBRARY UNIT

BEST FOR QUALITY. UNMATCHED FOR SERVICE.

RIGOH

RICOH CORPORATION (File Products Division) 5150 EI Camino Real, M/S D ~ 20, Los Altos, Ca 94022 U.S.A Phone: 415-962-0443 Fax: 415-962-0441 RICOH CORPORATION (Eastern Region Office) 59 Stiles Road, Suite 102, Salem, NH 03079 Phone: 603-893-0547 Fax: 603-893-4162

#### CALENDAR

#### CONFERENCES

#### April 9-12 SMTCON

Trump Plaza Hotel and Atlantic City Convention Center, Atlantic City, NJ. More than 250 @

suppliers will demonstrate products at the second annual Surface-Mount Technology Conference and Exposition. The exposition will offer a comprehensive range of components, equipment, materials, and services used in the design and manufacture of surface-mount and mixed technology products. The conference features advancement courses, technical forums, technical sessions, and workshops. Information: IC Management, 900 N Franklin St, Suite 700, Chicago, IL 60610, (312) 944-3434. Circle 371

#### April 30-May 2 Federal Computer Conference West

Disney Convention Complex, Anaheim, CA. This third annual conference will concentrate on advances in key computer and com-

munications technologies. A Solutions Showcase, which combines classroom sessions with live demonstrations, will cover solutions to computing applications needs made possible by advances in microcomputers and LANs. The conference will also feature in-depth seminars on microcomputers and networking. Information: Federal Computer Conference West, 8455 Colesville Rd, Suite 700, Silver Springs, MD 20910, (800) 343-6944. Circle 372

#### SEMINARS

#### February 13-14

Concurrent Engineering Seminar

Radisson Plaza Hotel, San Jose, CA. This twoday event is targeted toward the management and engineering team, including those in-

volved with quality assurance and design, test and manufacturing engineering. The one-day concurrent engineering seminar will focus on implementing the simultaneous design of products and the processes by which they're built, tested and supported. The one-day technical session will cover design for manufacturability, design for test and design for service. Seminar sessions in other locations will follow in March, April and May. Information: Logical Solutions Technology, 96 Shereen Pl, Suite 101, Campbell, CA 95008, (408) 374-3650. Circle 373

#### March 11-15

#### IEEE Software Engineering Seminars

Knickerbocker Chicago, Chicago, IL. The seven IEEE Standards Seminars will focus on software reviews and audits, quality assur-

LOGICAL

SOLUTIONS

ance, testing, project management, verification and validation, requirements specifications, and configuration management. Each seminar is two or three days long, is led by a team of industry experts and is targeted to specific groups in the software arena. Information: IEEE Standards Seminars, 445 Hoes La, PO Box 1331, Piscataway, NJ 08855-1331, (908) 562-3805. Circle 374

# ON JAN.29, THOUSANDS OF VME DESIGNERS WILLTURN 040.

They're not getting older, they're just getting better.

C

Because that's the day FORCE unveils the first 040 single board computer. Available in quantity. For immediate delivery.

S

B

U

So get FORCE for better performance, speed, functionality and compatibility. See us at BUSCON Booth #654, or call 1-800-BEST-VME, ext. 40. And give your competition some gray hairs.

0

FORCE Computers, Inc., 3165 Winchester Blvd. Campbell, CA 95008-6557 (408) 370-6300 ext. 40 © 1991 FORCE Computers, Inc.

5

4

6

#

N

20 FEBRUARY 1, 1991 COMPUTER DESIGN

# HITACHI'S DK515, 51/4", 780 MB WINCHESTER

# From any point of view, this 5<sup>1</sup>/<sub>4</sub>" disk drive reflects Hitachi's superior technical expertise, high-performance, and quality.

The DK515 features a fast 2.46 MB/ sec. data transfer rate, an average access time of 16 ms, and a choice of ESDI, SCSI, or ESMD interfaces.

Like all Hitachi drives, the DK515 reflects quality, because all critical components—including heads, media, and servo systems are designed, engineered, and manufactured by Hitachi.

Then, to make sure that Hitachi's strict standards of excellence are maintained, each and every drive is 100% burnedin and tested. The final result: a clear reflection of Hitachi's commitment to providing the very best in reliable, high-quality, highperformance disk storage. All this from a \$48 billion company.

#### Available now!

For more information about Hitachi disk drives, call your local Hitachi Distributor listed below, o Hitachi at 1-800-283-4080, Ext. 877.

> Hitachi America, Ltd. Computer Division, MS500 Hitachi Plaza 2000 Sierra Point Parkway Brisbane, CA 94005-1819

#### Authorized Distributors

CONSAN 612-949-0053 (IA, IL, IN, KS, KY, MI, MN, MO, ND, NE, OH, Pittsburgh, PA, SD, WI)

GENTRY ASSOCIATES 800-877-2225 (AL, D.C., FL, GA, LA, MD, MS, NC, SC, TN, VA)

R SQUARED **800-777-3478** (AZ, CA, CO, NM, OR, UT, WA, WY)

SIGNAL **800-228-8781** (CT, MA, ME, NH, RI, VT)

SPECIALIZED SYSTEMS TECHNOLOGY 800-688-8993 (AR, LA, OK, TX)

# A Reflection of Quality

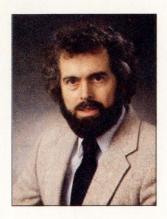

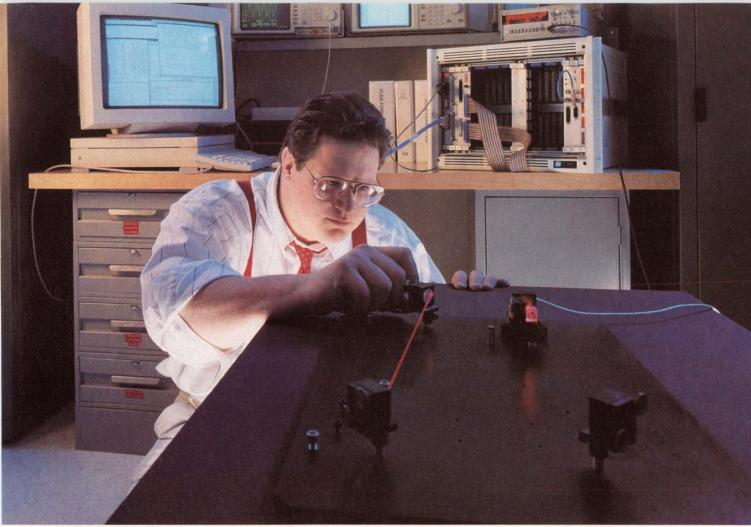

# Pete Yeatman on: Bus-board architectures

or the past 20 years I've heard all kinds of dire predictions about how the improvements in semiconductors—higher levels of integration, the combination of multiple functions and super high speed devices—were going to be the end of the standard board business. During that time, I've seen mainframe computers go from industry giants to near extinct dinosaurs; the once dominant minicomputer fade into obscurity to be replaced by desktop workstations; and the personal computer become the ubiquitous writing and graphic tool, replacing the typewriter, pencil and drafting tools.

What I haven't seen, though, is the demise of the board business. In fact, over that 20 years, I've seen the standard board business grow and mature from what some considered a stepchild of the computer business—a necessary evil—to a healthy self-sustaining business with a significant number of major players. And, according to current estimates, it's expected to grow at a double-digit compound annual rate over the next several years. No doubt the growth of the market for standard boards is a function of the growth of the larger market for computers. Outperforming the growth of the computer market, standard boards are capturing a growing share of that market's hardware spending by supplanting proprietary solutions.

The advances in standard boards haven't been free. They continue to be a direct consequence of the research invested in technological and design innovation by companies participating in this business. For the progress to continue, board and systems designers will have to be increasingly sharp to design products that take advantage of the latest silicon developments and serve ever-more complex applications. In addition, manufacturers will have to dig deeper and deeper into their R&D pockets to keep the magic happening. The challenge to the board manufacturing business, therefore, is to continue to provide the performance that systems makers would like to see with proprietary designs, on a standard bus platform. This will undoubtedly continue to kindle the best architectural genius in the industry.

The founding fathers of the standard buses—VMEbus, Multibus, STD, Futurebus, and the others—

demonstrated remarkable foresight when they developed standard architectures that remain alive today. VME, for example, was developed in the late 1970s and first introduced in 1981—the reign of the 8-bit processor. And while there were many provisions in the specification to handle growing semiconductor technology, its authors could not anticipate the rapid advances in silicon speed and density and in design turnaround time.

Yet these standards have remained viable, partially because the authors anticipated certain developments, and because the standard was too important to discard just because new technology came along. Instead, board designers buckled down to the task of adapting the newer technology to older buses.

Today the effort continues, and continues to be successful. The techniques used now to put new technology on VME and Multibus will undoubtedly be useful with the next generation of boards. And so it will be with Futurebus+. Despite the Herculean effort of the working committee, it's almost impossible to foresee the future's technological developments. Thus, designers will be working around the "restrictive" areas of standard buses for a long time despite prophesies that semiconductors will obsolete standard buses.

#### Silicon spurs board growth

Sure, new generations of semiconductors—microprocessors, logic, memory, and application-specific parts—are having, and will continue to have, a pronounced effect on the board-level industry and the directions it will grow in. But unlike some industry analysts, such as Andrew Allison of RISC Management (Freedom, CA), who believe the board industry is doomed by higher levels of IC integration, I believe just the opposite. The board business will see an unparalleled growth—because of the availability of new semiconductors—over the next several years.

Undoubtedly, the continuing advance of IC integration permits inclusion of ever-more functions on a single chip. Allison believes this progress is so pervasive that the functions now residing on a single board will be integrated on a single chip in the near future, obsoleting the need for a bus. I agree this level of compaction is, and will be, a reality. But all that means is that the functions of today's multiple-board system will be reduced to a single board. The fact is, some of the 68040-based boards available today provide complete system-level performance. Soon we'll have multiple system capability on one board. Next generation silicon won't hurt the board business; on the contrary, it will give us that much more power per square inch of board space and let systems designers achieve that much more performance and flexibility in a system.

Increasingly higher levels of IC integrations isn't the only force that will drive the board business to new heights in the coming years. Take a look, for example, at the computer powerhouses that are jumping on the open-bus-architecture bandwagon—DEC, Sun, Data General, Prime, IBM, Foxboro, GE, and the list goes on. For some of these companies, the buses will be used as I/O, not systems, buses. For others, the buses are the foundation of industrial control systems. Nonetheless, the participation of so many front-line companies—world-class computer companies—further legitimizes and gives impetus to the standard board industry.

The big computer companies don't want to waste their time or resources building boards to meet their unanticipated and often transitory board needs. In addition, to meet critical market windows, it's imperative to use the expertise of independent third-party vendors. Companies such as DEC, IBM, Sun, and others are willing to let the independent board manufacturers take those risks and enjoy that part of the business. It's so important that even when Sun and DEC developed their own new buses, SBus and Turbochannel, the companies made a major effort to enlist third-party board manufacturers and software companies. In fact, the board-level business grew partially by meeting those kinds of needs, as those of us from the DEC world well remember.

#### Standardization is key

What makes possible both the multiple-vendor sourcing of various computer functions (that is, boards) and the development of the open architecture board business is standardization. The social and economic climate is leaning increasingly away from proprietary solutions in favor of standards in all areas of the computer/electronics industry—hardware, software and even systems. With the fast-paced developments, nonstandard products are quickly made obsolete, and then must be totally discarded and replaced. But with systems based on standard products, upgrades can often be made within a fixed framework, causing only a small part of a machine, system or program to be discarded.

The standards issues are invading not only the commercial computer business, but also the indus-

trial process and machine control arena as well as a broad array of stationary and mobile (aircraft-, vehicle- or ship-based) military systems. Benefits accrue from standardized training and maintenance procedures, and from fast and relatively painless upgrades as new systems components emerge.

In discussing the board-level business, the concept of an open architecture remains the key and is supported on several fronts. The development of open buses like Multibus I, VMEbus, PC bus, and others has provided designers with an array of possibilities in terms of architectures, mechanical configurations and performance capabilities. Open buses also provide designers with a broad and widening range of boards and suppliers from which to choose.

By the same token, however, such open architectures are, by necessity, restricted. First, the standardization process itself takes long enough to assure a certain degree of obsolescence. Second, standardization can restrict performance and product differentiation. Third, manufacturers need some protection of their designs—which is best provided by a proprietary, rather than standard, architecture—to be economically and competitively viable. Finally, standards tend to keep creative efforts from blossoming into new product ideas.

Despite these obstacles—or perhaps because of them—the standard board business is more vital than ever. It becomes a key to understanding today's implementation of the open-bus strategy, to realize that the disadvantages mentioned above are largely nonexistent thanks to increased levels of IC integration. Designers have the freedom to develop a proprietary architecture on-board for a board that will become part of a system. As mentioned, many single boards are complete systems that operate in consort with other "systems" across a standard bus.

#### Performance or price?

Performance is another issue. It's a particularly interesting issue because it's a driving force—but by whom? The media? Some percentage of the marketplace? Some fear within certain suppliers' organizations that they'll be left behind? Looking at real applications—what's really needed—the final measurement is usually based on price/performance evaluations, rather than performance alone.

And while there's a significant focus on performance, it will not necessarily require dramatically new and different bus architectures in the immediate future. More likely it will depend on clever board and systems designs on whatever bus standard is used, whether it be VME, Multibus II, Futurebus+, or something we haven't heard of yet.

It's easy to look at the bus specifications alone and blame it for substandard operation, saying "we need to move to a faster bus." Often, the problem is not the bus. Equally often, a clever architectural approach can bring the product up to speed on the older bus at substantially lower cost and with fewer problems than designing for an unfamiliar bus. As we look at a period of relatively tight budgets, there's going to be a tendency to try to make the old bus last another generation or two—or three or more. This not only avoids the need for scrapping existing hardware, but it also preserves software investments as well as other assets such as parts inventory.

Arriving at the next level expected for systems performance requires an injection of additional computing horsepower. One of the favored approaches of the higher-horsepower processors today is multiprocessing. There are a number of variants on the approach, each with its advantages and disadvantages, and each with an edge in a different application. Looking forward, it's not clear that tightly coupled processors talking across a standard bus-whether simple VME or a cache-coherent Futurebus+---is ei-ther an efficient or practical approach to gain computer power in a standard bus system. Multiprocessing will undoubtedly be a major technique in systems based on standard board products, but it will probably comprise tightly coupled processors on a single board that will reside in systems where many such boards will be loosely coupled.

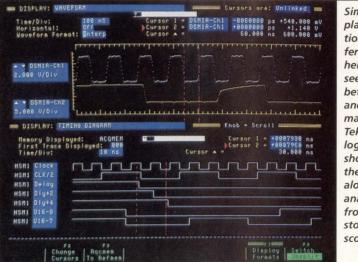

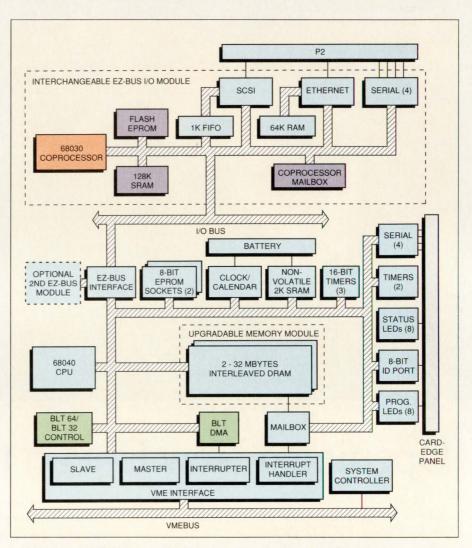

The key to making such systems work will be the individual board architecture that will include multiple internal buses of its own to prevent the main systems bus from being a bottleneck. In today's environment, these situations are handled by architectures designed specifically to accommodate the enormous throughput capability of the enhanced performance boards. To get out of these boards all of the performance that's been designed into them, processing bottlenecks have to be eliminated. Highly effective multiple processor/multiple local bus schemes have already been developed. In one, for example, a 68040 serves all the data processing functions while a separate independent on-board 68020 handles all I/O activities, leaving the 68040 free to flex its processing muscle totally unencumbered by I/O needs.

Boards like this, as well as others entering the market, illustrate how the board business can grow its capabilities without abandoning its existing architectures. And there's much to be said—for vendors and users alike—for upward migration within an architecture, or even with a single vendor's board family. Economies in software development alone make this kind of upward-performance mobility highly efficient, even if not as exciting as the emergence of a brand new bus architecture.

#### Software needs standards

Software remains one of the most critical, confounding and problematic issues in the standard bus/board industry. By rights the software, not the hardware, should be selected first for most applications that fall into the realm of standard boards. Unfortunately, though, this model is seldom exercised. Instead, the hardware is chosen first and the software selected on the basis of its appropriateness to the application and, of course, its availability for a particular board. Inappropriate emphasis on hardware during initial system specification is a problem perpetuated by users.

Another set of problems begins with software vendors. The board business is characterized by a highly independent network of board software vendors. Each has its own bag of tricks, and, as effective as those tricks may be, there is virtually no capability for interoperability between different software vendors' products.

Not too many years ago, users pleaded with board

makers to adhere to standards and specs in a way that would help assure plug-and-play interoperability between boards from different vendors. Today, that's largely been achieved, even if some tweaking and tuning is required. But on the software side, we don't even have standards yet. We should. The board business deserves that—needs that—to continue to serve its customers.

If the board-level business is to reach new levels of technical sophistication, the software wrinkles will have to be ironed out with new levels of software intercompatibility. We've already seen some effort in that direction within both the Posix group and the ad-hoc OBIOS (Open Basic Input/Output System) consortium. Progress, however, is painfully slow. Other efforts, such as Orkid (Open Real-time Kernel Interface Definition), failed because they didn't spark the minimum level of commonality. More needs to be done. Just as there are standard bus/board architectures, there should be the equivalent of standard software architectures so that the marketplace can avail itself of the benefits of multiple-vendor software, as now it does for hardware.

#### Design drivers

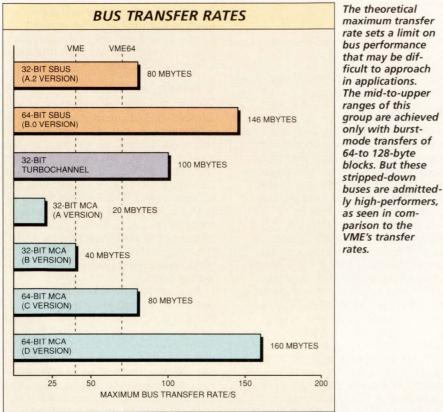

The computer industry, almost by definition, is in turmoil. And the standard board business, once a poor stepchild to the industry, is now a fully initiated member and well on its way to being a key-perhaps THE key-player in all new computer systems architectures. From workstations that have adopted their own set of open-standard buses-SBus, Turbochannel and Micro Channel-to the Futurebus+ platforms already on drawing boards for incredibly powerful compute servers, standard buses are on the move. In addition, vendors continue to integrate the latest IC technology onto board-level products providing a variety of on-board communications schemes to reduce potential bottlenecks. Even more clever techniques are on the horizon-extending the use of mezzanine boards with their own associated buses to increase transfer rates.

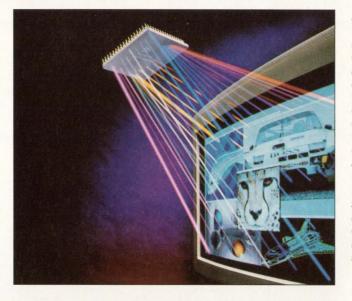

VMEbus, Multibus II and even the workstation buses are pitifully slow for the kind of data transfer speeds expected over the next several years. Networking standards such as Ethernet, for example, are under tremendous pressure to provide higher bandwidth communications between systems. The current work on Ethernet replacements such as FDDI (Fiber Distributed Data Interface) are already seen by some as falling short (at only 10 times Ethernet's performance). Higher-performance links, such as HIPPI (High-Performance Peripheral Interface), are on the horizon. The impact of networks operating at speeds over 100 Mbytes/s on systems bus transfer rates will be profound. The current generation of buses (even early versions of Futurebus+) won't be able to provide the required bandwidth. So, clever board architectures will have to provide the required speed, buffering the systems bus from the overwhelming demands of communications, memory transfers, and video data-just as they do now to satisfy other high-speed requirements.

Pete Yeatman is president of Radstone Technology (Montvale, NJ).

### IN THE ERA OF MegaChip<sup>®</sup> TECHNOLOGIES

# A lot has been said about company is doing a lot about

# testability, but only one it. Texas Instruments.

ology. In fact, SMT's charac

ou've seen the headlines and read the stories. Design-for-test (DFT) is a challenge but one that's now easier to live with. The reason: Texas Instruments is the first to develop products for implementing the JTAG/IEEE 1149.1 testability standard quickly and effectively.

#### To market faster at lower cost

By implementing testability into your system from the outset, you can create one that uses high-performance circuits and is readily manufacturable, one that is lower in total cost and on the market faster. You can expect:

- Test integration from silicon to system — that reduces debug and test time

- Reduced test software development time — generating test vectors is greatly simplified

- Reduced capital investment in test equipment

- Increased system fault coverage and reliability

#### SCOPE, our broad-based solution

To simplify and speed your design task, TI has developed its SCOPE<sup>™</sup> (System Controllability/Observability Partitioning Environment) family. It is a coordinated, broad-choice set of commercial and military products compatible with the IEEE 1149.1 standard.

Included are bus-interface devices, standard cells, gate arrays, and digital signal processors, as well as our ASSET™ (Advanced Support System for Emulation and Test) diagnostics software.

On the way are diary memories, a series of IEEE 1149.1 stand-alone

© 1990 TI

controllers, and microprocessors with boundary-scan and built-in self-test features.

#### We are in for the long haul

As a member of the Joint Test Action Group (JTAG), we contributed to the formulation of the IEEE 1149.1 standard and wholeheartedly support it. We are committed to growing our SCOPE family of products so that designing to the IEEE 1149.1 standard will be like second nature.

Your future competitiveness depends upon an engineering methodology where design teams bear the burden of testability, manufacturability, and reliability. The demands of concurrent engineering will be met in part by the extended capabilities accessed via the IEEE standard - from embedded system information that allows realtime availability of data throughout the design cycle to emulation and realtime system analyses capabilities built right into the silicon.

#### Get our floppy free, and learn more

Call 1-800-336-5236, ext. 3909, and we'll send you our unique floppy disk presentation. Just pop it into any MS-DOS<sup>™</sup>-compatible PC to find out more about DFT and TI's SCOPE testability family. What's more, the disk features a formula that allows you to calculate the cost-effectiveness of implementing testability in your system.

You will continue to read headlines about DFT. We intend to make many of them.

MegaChin, SCOPE, and ASSET are trademarks of Texas Megac.nip, 3007 is a una constructed. MS-DOS is a trademark of Microsoft Corporation. 08-0205

#### TECHNOLOGY UPDATES

#### INTEGRATED CIRCUITS

### **MIPS rethinks RISC** with superpipelining

Ron Wilson, Senior Editor

hase one of the RISC revolution has run out of steam. The simple, single-CPU RISC architectures that started it all have wrung as much speed as they can out of existing CMOS processes, forcing vendors to look for other tricks to get more Mips. Some companies have turned to faster processes, like ECL or gallium-arsenide, to get higher clock rates. These efforts have for the most part been disappointing, both because the CPUs proved hard to fabricate and because the system designs at such elevated frequencies proved intractable.

Other vendors have attacked the CPU architecture itself. These vendors reasoned that, if a simple RISC CPU maxed out at one instruction per clock and if raising clock frequencies into the stratosphere was temporarily impractical, the best option was parallelism, or increasing the number of CPUs. The first steps in this direction were taken not by chip vendors, but by system designers, who created multi-CPU processor boards

Intel followed close behind these initial efforts with its multiple-execution-unit 80960CA, and the term superscalar was born. The superscalar concept is simple: get several instructions out of the cache at once, and dispatch them simultaneously to several execution units. Use register scoreboarding to make sure that, even if the instructions finish out of sequence, data dependencies are respected.

In practice, superscalar proved difficult to implement. The dispatch and scoreboarding logic are so complex that no one has yet to do a completely general multiple-dis-patch unit. Because the dispatch unit will only work efficiently with certain sequences of instructions, compiler developers have been left with a tremendous burden. In addition, the amount of silicon absorbed by the control logic and the several execution units leaves little room for an even-more-critical resource-onchip cache.

#### Superpipeline approach

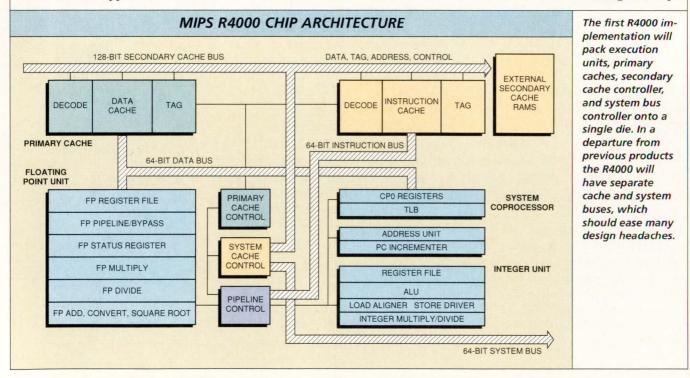

MIPS Computer (Sunnyvale, CA) has paved the way for the continuing evolution of RISC with a whole new set of ideas, embodied in the R4000 architecture. The company has developed a three-part manifesto against the general movement toward superscalar chips, focusing on multiple instruction issues, a true 64-bit architecture and integrated multiprocessing support.

On the first issue, MIPS has

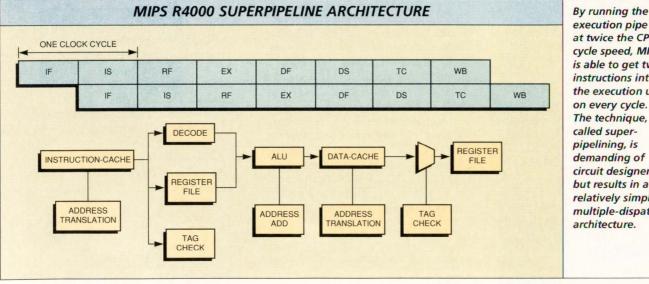

parted company with the superscalar advocates, introducing a concept it calls superpipelining. This idea is simple: by running the execution pipeline twice as fast as the instruction fetch logic, users can fetch two instructions at once and feed them both into the pipeline, half a cycle apart. The tricky part was implementing the idea in silicon.

To begin with, a 50-MHz R4000 would need a 100-MHz pipeline. Since the pipeline doesn't have to drive any external pins, such speeds were achievable with existing CMOS processes. "The circuitry necessary to let the pipeline take a new instruction every half cycle is fairly complicated. But at an architectural level, the design is much simpler than a superscalar approach," says MIPS vice-president of development Skip Stritter.

Additional complications came from data dependencies. What would happen, for instance, if the next instruction needed to use the results of the current instruction? The MIPS designers solved these issues not by scoreboarding, which would simply stall the pipeline until the key instruction finished, but by an elaborate set of bypass circuits. Thus, a following instruction can get at results while they are still in the pipe, before they're put back in the register file.

There are several advantages to the superpipeline approach. First, the dispatch logic is much simpler, and the single execution unit takes up less space than the

execution pipe at twice the CPU cycle speed, MIPS is able to get two instructions into the execution unit on every cycle. The technique, called superpipelining, is demanding of circuit designers but results in a relatively simple multiple-dispatch architecture.

28 FEBRUARY 1, 1991 COMPUTER DESIGN

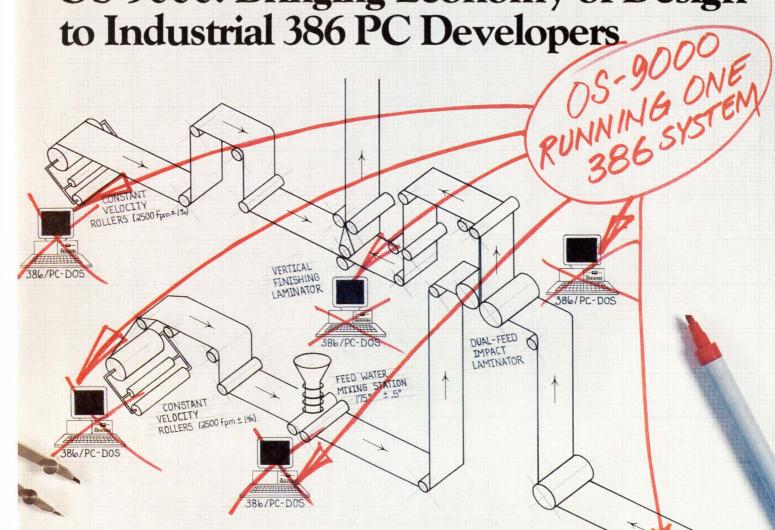

# **OS-9000.** Bringing Economy of Design to Industrial 386 PC Developers

Now, real-time high-performance system software is available for your industrial PC. Microware Systems Corporation, the world's leader in real-time VME system software, brings an economical real-time solution to industrial PC developers. Introducing OS-9000,<sup>™</sup> the first real-time operating system designed to unleash the power of your 386<sup>™</sup> hardware.

#### **Real-Time Response To Control Multiple Tasks**

Why waste the power of your 386 by letting it control only one function at a time? Unlike PC-DOS, OS-9000 is a true multiuser and multi-tasking real-time operating system. Now you can utilize a single PC as a powerful time-sharing system able to control multiple processes simultaneously. And by using industry-standard protocols (like Ethernet and Arcnet), OS-9000 allows PCs to be interconnected and connected to different computers to exchange data quickly and easily. This versatility tremendously increases your productivity, while it reduces development time and equipment costs. Plus, interfacing to standard or custom I/O controllers is a snap.

#### Get OS-9000 Today

Pre-configured versions of OS-9000 are now available for your 80386<sup>™</sup> PC-compatible hardware. These systems include integrated development tools such as a "shell" user interface, over 70 powerful utilities, a superlative C compiler, a C source-level debugger and a screen editor. Your full-featured, "plugand-play" OS-9000/386 system is now available for just \$995.

Call Microware® today to order your copy of OS-9000. Or order a FREE copy of the OS-9000 Catalog (your complete guide to the OS-9000 Real-Time Operating System).

**Call Microware Today!** 1-800-475 In California, call (408) 980-0201

386/PC-DOS

CONSTANT VELOCITY ROLLERS (2500 fpm 1 19)

MICROWARE SYSTEMS CORPORATION 1900 N. W. 114th Street • Des Moines, Iowa 50322 Phone: (515) 224-1929 • Fax: (515) 224-1352

PC-DOS is a trademark of IBM. 80386 and 386 are trademarks of Intel Corporation. All other brand or product names are trademarks or registered trademarks of their respective holders.

MORE CHOICES • MORE OPTIONS • TOTAL SUPPORT **CIRCLE NO. 19**

#### **TECHNOLOGY UPDATES**

#### INTEGRATED CIRCUITS

multiple execution units of a superscalar machine, allowing more-complex circuitry to achieve the higher speeds. This makes more space available on the die for wide data paths and large caches, both of which are critical to the success of any multiple-dispatch architecture.

A second important advantage is the robustness of the approach. Superscalar architectures are notoriously sensitive to instruction order, and can drop well below one instruction per cycle on many code sequences. But the superpipeline architecture delivers a significant performance boost on existing R3000 binaries without reordering of the instructions, according to MIPS claims. And users can get additional speed with the R4000 compiler, since the new compiler will know how to reorder multiple-cycle operations-integer multiplies and divides, for instance, and most floating-point codes-to avoid tripping the pipeline interlocks.

#### Less scalability?

On the minus side, superpipelining is theoretically less scalable than superscalar techniques. Running the pipeline twice as fast as the instruction cache is probably the limit for this generation of CMOS technology. So for now the approach will be stuck at around two instructions per clock.

A superscalar architecture, in contrast, could include an arbitrarily wide data bus and an arbitrary number of execution units, which would permit peak speeds of many instructions per clock. But practical considerations make this difference less significant than it might appear. In real silicon, the com-

#### "At an architectural level, the design is much simpler than a superscalar approach."

-Skip Stritter, MIPS Computer

plexity of superscalar dispatch hardware increases so fast that more than two-instruction dispatch may be impractical. And as the number of simultaneous instructions goes up, the complexity of the compiler necessary to avoid perpetual stalls goes through the roof. As a final argument should these problems be solved, "We can always put multiple superpipelined execution units on a chip," says Stritter. The second part of the MIPS manifesto may be even more controversial than the superpipeline concept: the company feels that it is time for high-performance microprocessors to move to full 64-bit architectures. By "full," MIPS means 64-bit data paths, 64-bit registers and 64-bit virtual addresses. This is a long step beyond just having a wide path between the CPU and the cache.

The company's reasoning is based on its previous experience as a systems vendor. "We have learned a great deal from the ECL R6000 system," claims Stritter, "not just about fast CPUs, but also about large memories and huge system configurations."

One of MIPS' observations is that the largest database, technical and graphics applications are about to outgrow the paltry 4-Gbyte flat-address space available on 32-bit CPUs. These programs, according to MIPS, must either undergo critical architectural changes in the way they organize data, or must have access to a larger virtual address range. Behind this claim is the fact that users of MIPS CPUs include companies such as Tandem and Silicon Graphics.

It's not clear whether the majority of customers who just want a faster CPU will be willing to accept

30 FEBRUARY 1, 1991 COMPUTER DESIGN

# A 68040 for data, a 68020 for I/O... for real real-time performance on a single VME board.

CECCECECCICC

Radstone's 68-41 Freeflow+ multiple microprocessor board with truly independent microprocessors for data and I/O gives you next generation VME performance...Now!

- 68040 with 16 Mbytes of dual-ported memory for maximum data throughput via concurrent, uninterrupted microprocessor operation up to 40 MHz

- 68020 with 4 Mbytes of dual-ported memory controlling extensive high performance on-board I/O facilities—all operating independently

- Multiple independent external buses-VME, VSB & APEX

- Multiple independent local buses-processor and I/O

- High performance DMAs

- Intelligent, high performance Ethernet and SCSI/SCSI-2

- ...and much, much more.

Radstone's Freeflow+ architecture takes VME to new performance levels. And now it's available with 040 processing punch. It's the very latest in Radstone's long line of leading edge commercial real-time VME board level products.

#### Extend your VME lead...and investment

For details on how to supercharge your VME system with Radstone's Freeflow+, and extend your current investment in VME hardware and software, call or write. Do it now, because your system is worth it!

Radstone Technology Corporation 20 Craig Road, Montvale, NJ 07645-1737 Call Toll-Free: (800) 368-2738 Eastern Region: (201) 391-2700 Central Region: (708) 397-0303 Western Region: (408) 727-4795

#### TECHNOLOGY UPDATES

#### INTEGRATED CIRCUITS

the extra silicon burden of a full 64-bit design. The R4000 will run existing R3000 code without modifications, but it will have a complete additional set of instructions for 64bit operation. Even if users don't need the 64-bit silicon, they have to buy the whole die.

Stritter argues that the actual overhead isn't that much. Once the large caches, bus control units, cache controllers, floating-point unit and associated hardware are packed onto the die, he says, it doesn't really make that much difference whether the integer ALU and register file are 32 bits or 64 bits. "If you look at a floor plan, you can see that the diflar to that of the R3000 cache bus. The controller is highly configurable, allowing selection of access times, cache organization and size (up to 4 Mbytes is possible). The secondary cache can be either unified or split between instruction and data.

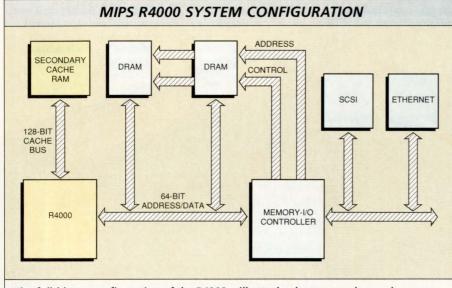

After listening to the problems system designers had in working with the cache bus on the R3000, MIPS decided to make a major change from the older architecture. The R4000 has a separate 64-bit system bus for connection to main memory, peripheral controllers and other R4000 CPUs, again with a highly configurable controller.

A host of features were included

The full-blown configuration of the R4000 will attach a large secondary cache on one bus and main memory on a second bus. MIPS will introduce a simpler version of the chip for desktop applications that will eliminate the secondary cache bus.

ference is a relatively small portion of the chip area—perhaps the equivalent of another 2 kbytes of cache," claims Stritter.

#### Packing the die

The initial implementation of the R4000 as disclosed by MIPS will be remarkably ambitious. The die will include the 64-bit integer unit and 64-bit FPU, an MMU for the 64-bit virtual addresses, 8 kbytes each of primary instruction and data cache, and a secondary cache controller.

The latter controller creates a secondary cache bus, a 128-data-bit monster that combines address, data, tag and control lines in a manner simiin the bus and cache controllers to solve the cache coherency problems that arise in multiprocessor configurations. Elaborate tag bits, snooping logic and primitives for virtually any sort of coherency protocol promise to make the R4000 compatible with almost anyone's notion of parallel architecture. In addition, control lines let the chip work in a master-slave relationship for fault-tolerant computing.

The initial R4000 package will be enormous—possibly the largest that has been attempted for a high-volume part. MIPS is confident that its silicon partners are ready to produce and test such devices. Shortly after it introduces the full-blown device, however, MIPS plans to roll out a reduced R4000 for more modest designs that will eliminate the secondary cache bus.

#### Next step: implementation

MIPS called its announcement this month an "architectural disclosure," not a chip release. The company had, as of the end of 1990, only taped out portions of the chip for testing purposes—no full R4000 die has been fabricated as of this writing. Many questions remain unanswered.

One is ac performance. MIPS is targeting a 50-MHz primary cache cycle time for the initial chip. Understandably, the power dissipation of the chip isn't stated yet, nor is it certain what the electrical behavior of a part that attempts to thrash 192 bus pins at that speed would be.

An added complication is that MIPS doesn't build its own silicon; the partners that supply its other CMOS CPUs will individually tape out and fabricate the parts. So a number of vendors will all be bringing the part up simultaneously on slightly different processes, probably with varying results. All of the devices, however, will be returned to MIPS for certification before they are declared to be R4000s.

When it does become available, the R4000 will represent a major rethinking of the evolution of RISC. The architecture represents a return to extreme circuit complexity on the die, but may actually make system implementation easier by reducing many of the critical timing requirements that characterized the R3000 bus.

By staking out new ground in 64bit operation and hardware support for multiprocessing protocols, MIPS is asserting its vision as a major vendor of large systems. Whether the answers MIPS has found will match the questions system designers are asking remains to be seen.

For more information about the technologies, products or companies mentioned in this article, call or circle the appropriate number on the Reader Inquiry Card.

MIPS Computer (408) 720-1700 ..... Circle 207

# If you're tired of pouring on SRAM to get 128Kbyte cache performance,

# Take a load off.

Introducing an amazing new cache chip that gives crowded motherboards a new lease on life. It's called 386<sup>™</sup>Smart Cache, a family of chips that integrate a cache controller with up to 16Kbytes of SRAM onto a single, one-million-transistor chip. The result is a 16Kbyte chip that really cleans up, equalling the performance of 128Kbyte caches.

Intel's 386 and 386SX Smart Cache are one-chip solutions that give you extra space on your motherboards for other applications. ©1990 Intel Corporation. 386 is a trademark of Intel Corporation. And when you stack them up against other caching solutions, you'll find their innovative architecture costs substantially less.

Give your motherboard a lift. Send in the attached card today for a free copy of our unique 386 Smart Cache video, performance report and documentation. Or if the card's been ripped off, call 1-800-548-4725, dept. HA47.

Because the reasons to look into 386 Smart Cache are really starting to pile up.

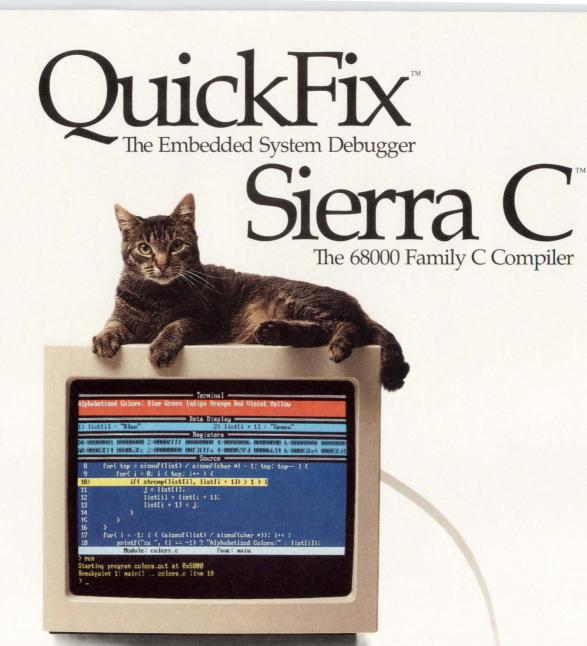

### The Purrrfect Combination

Speed your products to market with the QuickFix Debugger and Sierra C Compiler, the perfect combination for all your 68000 family embedded applications.

**The QuickFix Debugger** is the fastest and most easyto-use debugger available today. Besides the convenience of the multi-window display, commands feature a C-like syntax for extremely intuitive operation. Plus, a quick-connecting ROM communication cable and preconfigured drivers cut installation time from possibly weeks down to *minutes*!

**The Sierra C Compiler** generates the tightest code available today at blazing compilation rates. And it's not only fast — it's complete. Along with Sierra C's optimizing compiler, macro assembler and linker, you get a unique high speed parallel download system. Sierra C comforms to the ANSI C standard. Additionally, position independent, re-entrant and ROMable code can be generated to fit any memory configuration.