Inder Singh on Posix

TRA

HEN (HORN

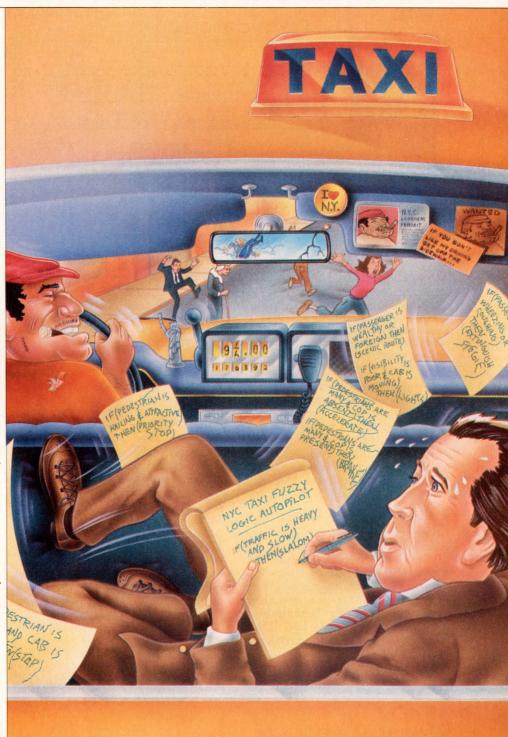

TAXI FUZZI

NYC

FOR ELECTRONIC ENGINEERS & ENGINEERING MANAGERS

## Fuzzy logic simplifies complex control problems

Many barriers slow quest for single-chip ethernet adapter Are mixed cells and arrays the solution ASIC vendors claim?

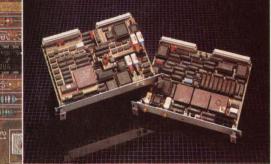

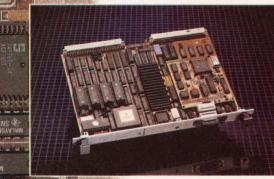

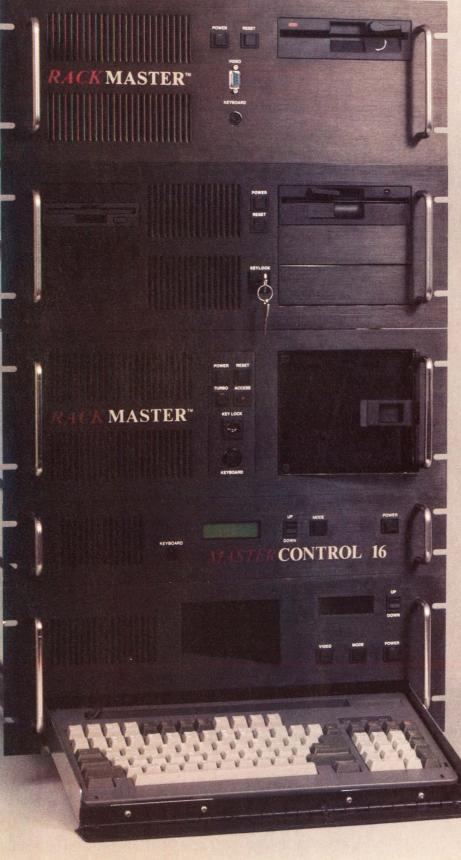

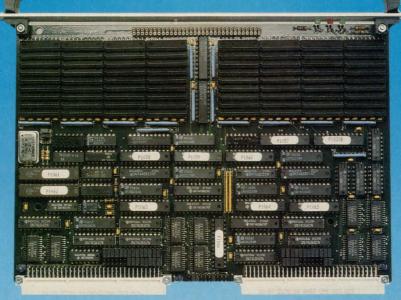

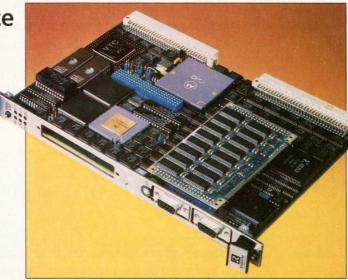

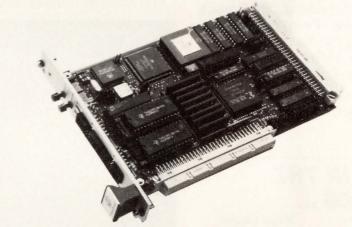

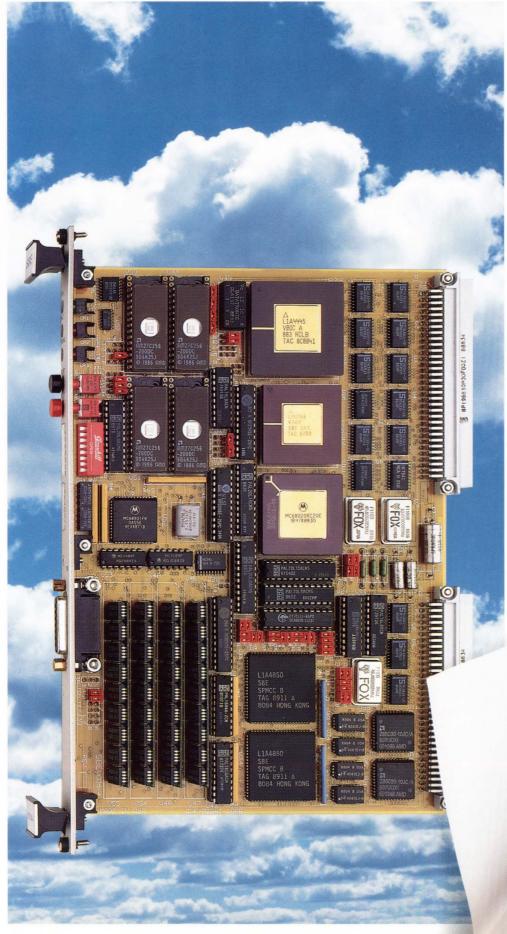

## At Last, a <u>*Truly*</u> Industrial 386 PC AT System for the OEM

Easy to mount Eurocard hardware with optional power supply. Can be rack mounted or bolted into any embedded system.

Two boards make a complete 386 computer with your choice of EGA or VGA display.

(

6

01

(1

( 1

(1

(1

(1

( 1

1

01

10

C

1, 2, 4 or 8 Mbytes \_\_\_\_\_\_ of on board. Full support for LIM EMS and BIOS shadowing.

On board support for COM1, COM2, LPT, keyboard, clock, floppy disk, and IDE hard disk.

Compact single / height Eurocard board format (100 x 160 mm) that doesn't flex or bend and withstands the toughest shock and vibration.

Small price to help you compete.

Three side mechanical bond into the card cage, yet easy to access for simplified maintenance.

EXTEREN

Full 32-bit expansion bus for easy system expansion and customization with up to 20 slots.

16 or 20 MHz

80386SX CPU

and 80387 Arithmetic Unit

**USA - CANADA** 50 West Hoover Ave. Mesa, Arizona 85210 USA Tel. (602) 962-5559 Fax. (602) 962-5750 **CIRCLE NO. 1**  Introducing the first 386 PC AT system originally designed to be embedded into your machinery or instrumentation.

With the GESPAC AT system, "ruggedized PC" no longer describes a desktop PC in a stronger black box. Instead it is an architecture made to last by design, with such features as small and robust board format, and ultrareliable pin-in-socket connector.

What's more, the GESPAC System is built for performance with Intel's original 16 or 20 MHz 80386SX processor and 80387SX Arithmetic Unit. In fact, this system is the most compact implementation of the 386 in the market today.

The powerful G-64/96 bus interface lets you customize your AT system with any of the 200-plus system components available from GESPAC, to match virtually any system requirement.

Take advantage of GESPAC's 12 years of experience in serving the OEM marketplace. Call today to receive your free data sheet and GESPAC's catalog of board level microsystem products. Ask about GESPAC's exclusive Guaranty of OEM Long Term Delivery.

Unprecedented selection of inexpensive I/O functions, – from the simplest parallel and serial I/O, to high performance networking, MIL 1553, motion control, and computer vision.

## Call Toll Free 1-800-4-GESPAC or call (602) 962-5559.

ADA

FRANCE

over Ave.

Z.1. les Playes

na

83500 La Seyne

France

France

2-5559

Tel. 94 30 34 34

62-5750

Fax. 94 87 35 52

INTERNATIONAL

18, Chemin des Aulx CH-1228 Geneva Switzerland Tel. (022) 794 3400 Fax. (022) 794 6477

New

Easy Access = Maximum Accessibility Ouick access saves time in assembly, test, and maintenance. Loosen two captive fasteners and the front, top, and sides slide off for maximum access to all of the maximum access to all of the internal components. Each internal component comes out with two screws, or remove five hex nuts and the entire system lifts out of the bottom tray to provide a free-standing, fully functional development platform!

Peripherals Just Slide In Up to eight half-height 5¼" peripherals simply slide into their mounting brackets.

## The Quietest Backplane

Available Plug your VME system into the quietest backplane ever! Our new 10-LAYER VME backplanes handle the fastest VME signals with the absolute minimum distration, created minimum distortion, crosstalk and noise.

## **Engineered** Cooling

Airflow is directed over the components that need cooling — the power supply and your boards. Separate chambers maximize cooling by channeling airflow and restricting recirculation.

## **Configured for Your**

Application With over 2000 standard configurations you can virtually design the enclosure yourself — and still get it off the shelf. Choose from 3 to 14 slots for VME or 4 to 18 slots for Multibus. Loads of perioheral ontions and of peripheral options and configurations are available for rack and tabletop models as well as floor-standing DeskMate<sup>TM</sup> verions that accept 9U  $\times$  400mm cards. Or let our team of engineers provide a packaging solution tailored to your specifications — from your specifications - from configuring the front panel LEDs to customizing the rear panel. Designing enclosures to meet your specific needs is our specialty.

Optimum Power Output Choose from 175 to 1000 Watts to satisfy the demands of your system.

## The Last Word in System Packaging

Now you can benefit from 12 years of design experience and innovation that has made Electronic Solutions the industry leader in system packaging. The Omega<sup>™</sup> Enclosures will give your VME or Multibus system the attractive exterior your image demands with a rugged, welldesigned interior to withstand the most demanding environments. And besides the Electronic Solutions' full 3-Year warranty, the Omega bears FCC approvals and is UL, CSA, and TUV

listed to get your system to an international market in the shortest time possible.

Call Electronic Solutions for the latest information about the best choice for your system package. It's the last system enclosure you'll need to see.

6790 Flanders Drive, San Diego, CA 92121 (619) 452-9333 FAX: 619-452-9464 Call TOLL FREE (800) 854-7086 in Calif. (800) 772-7086

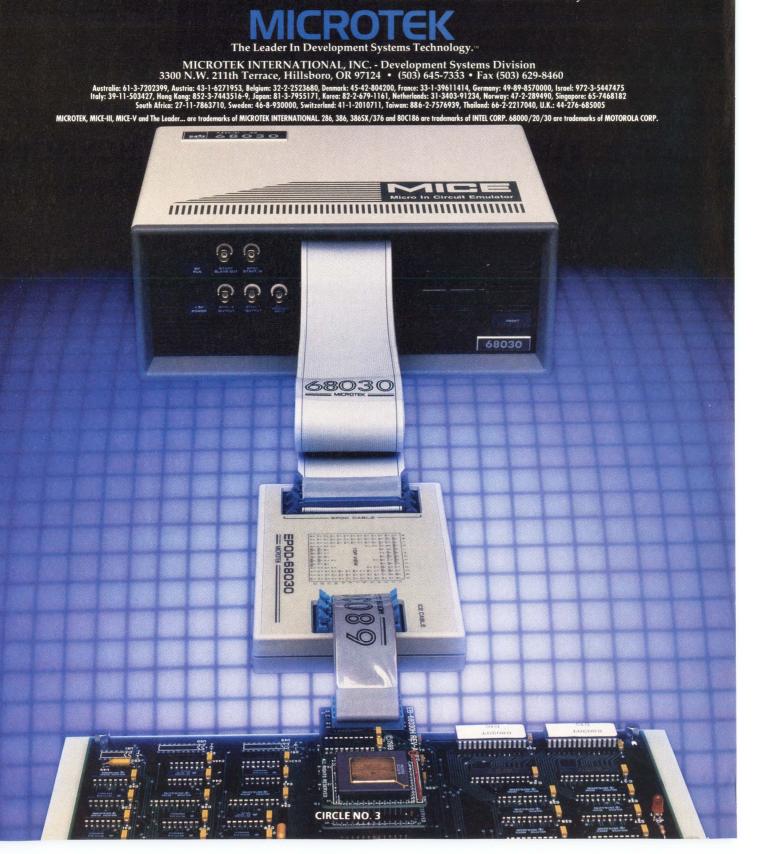

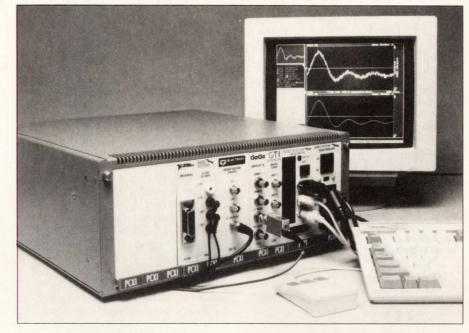

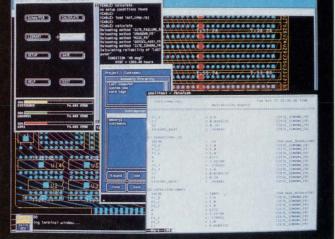

## **EMULATION MADE EASY!**

In the time it would take to select an emulator from all of the different options, install a configuration that wasn't hostile to your environment, read the manual and study the <u>Microtek also has in-circuit emulators for 286TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_386TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_387TM\_37TTM\_387TTM\_387TTM\_387TTM\_387TTM\_37TTM\_37TTM\_37TTTM\_37TTTTT</u> tutorial, check the application notes and then learn the interface(s) ... you could have debugged your product with the MICE-III.

MICE-III in-circuit emulators from Microtek. Easy-to-use 68000/20/30<sup>™</sup>, 80C186<sup>™</sup> support. Source debug. Fully-qualified

Microtek also has in-circuit emulators for 286<sup>™</sup>, 386<sup>™</sup>, 386SX/376<sup>™</sup>, i486<sup>™</sup>, Analog Devices ADSP-2101A, 2100, 2105 and other microprocessors.

So, if you'd rather be debugging than getting ready to debug, call Microtek. We've made emulation easy.

FOR ELECTRONIC ENGINEERS & ENGINEERING MANAGERS

## TECHNOLOGY UPDATES

Software Real-time Unix develops

**Design and Development Tools** Tool suites address elusive

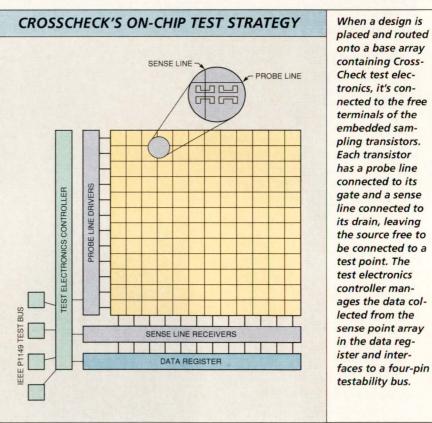

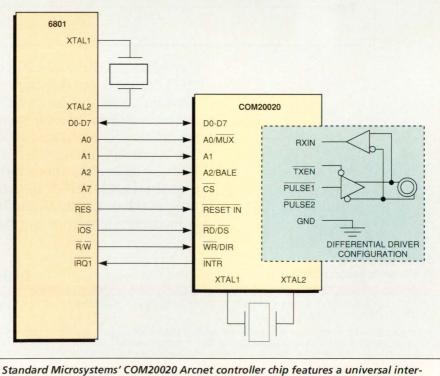

**Integrated Circuits** Embedded processor  JEDEC committee proposes standard CrossCheck testability reaches commercial gate array family......48 Single-chip controller eases Arcnet

Page 77

Page 32

## TECHNOLOGY AND DESIGN FEATURES

### Many barriers slow quest for single-chip Ethernet adapter

Like knights seeking the grail, vendors of Ethernet controller ICs are pursuing a single-chip LAN adapter ......67

### Are mixed cells and arrays the solution ASIC vendors claim?

Does embedding fully diffused blocks on gate arrays really offer designers the best of both worlds?.....77

## **COVER STORY**

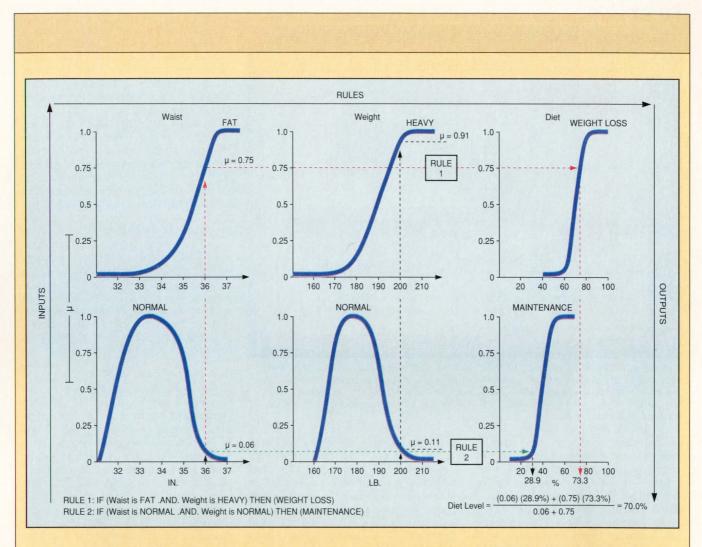

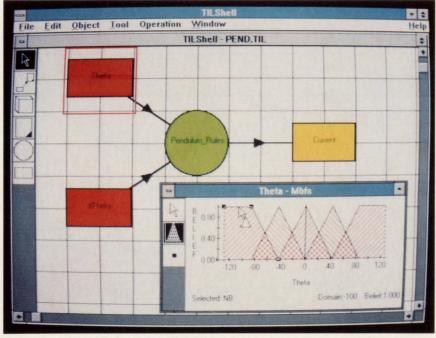

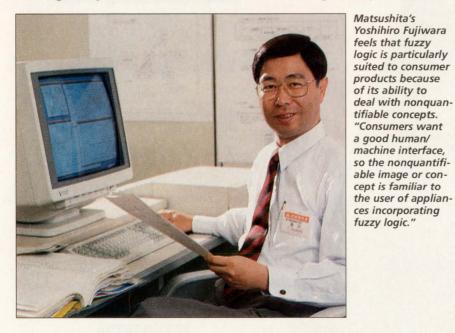

## **Fuzzy logic simplifies** complex control problems

Fuzzy logic is proving a powerful methodology for control applications. Over 2,000 patents have been issued in Japan. Now, development tools and hardware are becoming available in the United States, and application possibilities abound ......90

Page 105

## NEW PRODUCT HIGHLIGHTS

## PRODUCT FOCUS

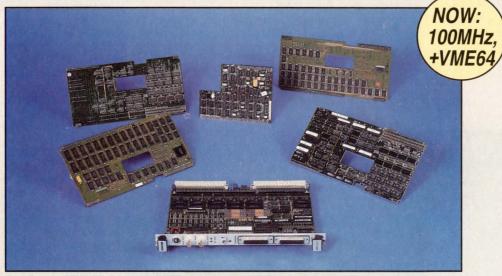

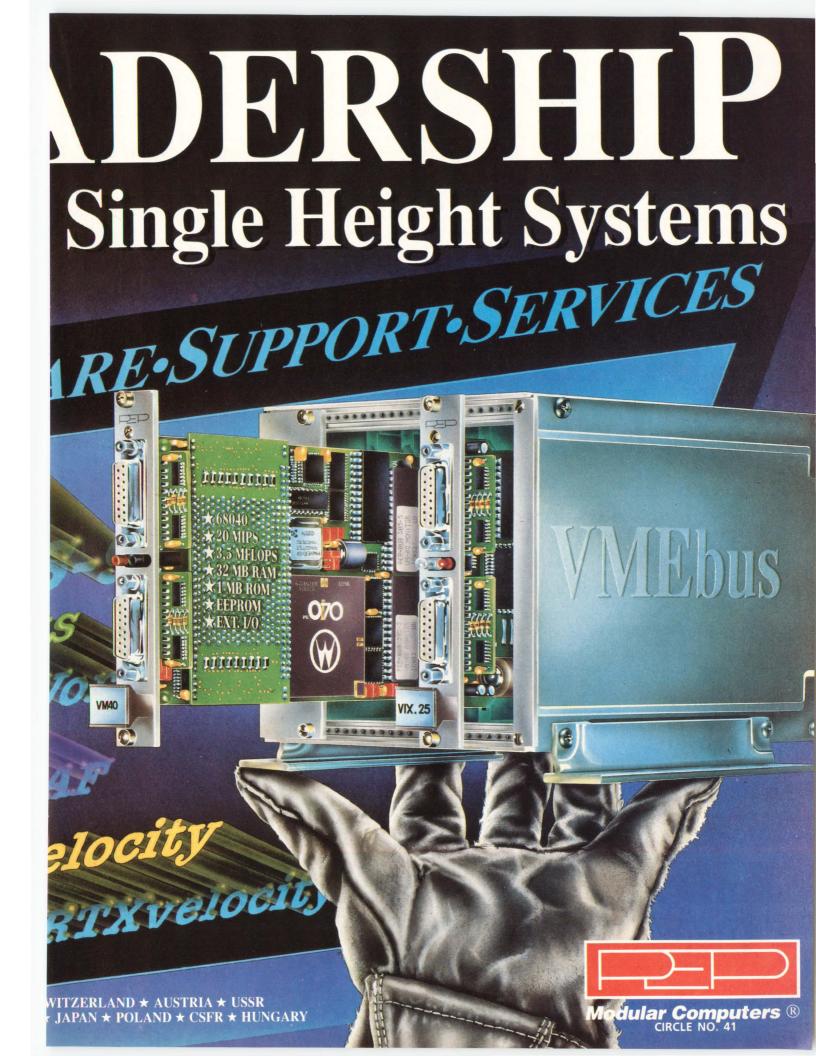

High-performance microprocessors push limits of VMEbus ......105

**Computers and Subsystems**

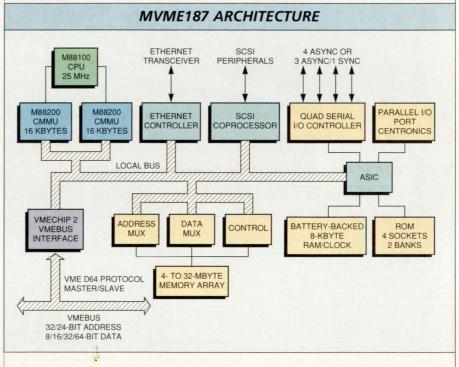

Single-board RISC computer puts it all together ......116

**Integrated Circuits**

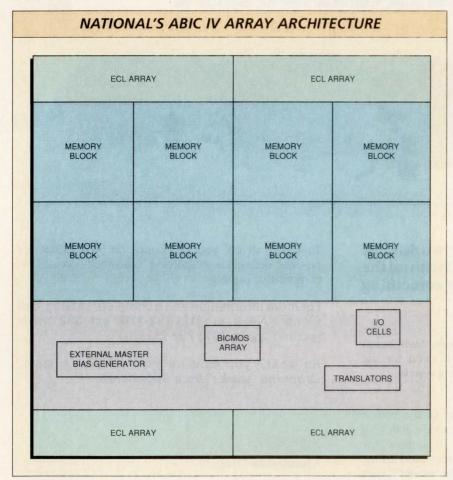

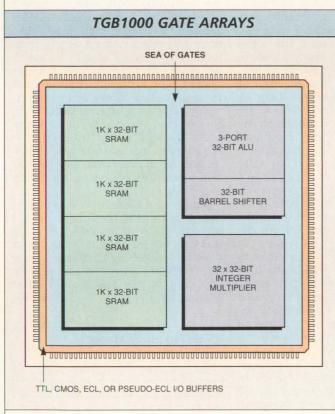

BiCMOS arrays up to 150,000 gates offer compiled memory......117

### **Design and Development Tools**

Circuit board reliability analysis moves up in the design cycle......118 Logic analyzer houses 1-Gsample/s oscilloscope ......119 Cadence integrates synthesis for front- to back-end design ......120

## DEPARTMENTS

| News Briefs          |

|----------------------|

| Editorial12          |

| Calendar16           |

| Advertisers Index127 |

|                      |

## Putting high-performance power distribution on the fast track.

## THIS IS AMP TODAY.

Designers of today's high-performance power distribution systems (PDSs) need a <u>practical</u> way to take advantage of the compact size, thermal efficiency, and low inductance of insulated flat copper power cable.

Our newest invention not only makes flat conductors practical, it adds powerful new options to the way you can design your 'flat power' PDS.

AMPOWER Wave Crimp

Assemblies let you specify direct taps on flat cable wherever you'd like, for efficient branching. And they give you a true modular approach to power—with separable printed circuit board connectors and sequenced Blind Mate drawer connectors—for fast assembly, and easy service and upgrade.

The exclusive crimp termination contacts an area 50% greater in cross section than the conductor itself. Result: no thermal penalties,

## Flat conductor PDS made practical.

no current restrictions, no compromise in the inherent low-noise properties of flat conductors. Electrical characteristics are consistently predictable.

To realize all the new opportu-

nity in flat power right now, call 1-800-522-6752 (fax 717-561-6110) and ask about AMPOWER Wave Crimp Assemblies. In Canada call 416-475-6222. AMP Incorporated, Harrisburg, PA 17105-3608.

## FLUKE

CO HEWLETT

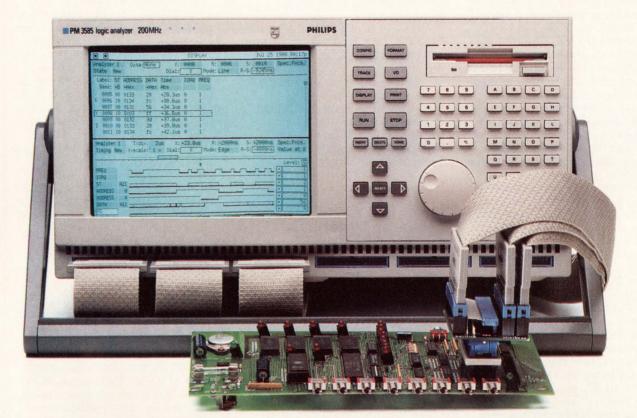

# All logic analyzers give you integrated state and timing, sooner or later.

8 9

## Why not now?

Introducing the new Philips PM 3580 family of logic analyzers from Fluke: the first instrument architecture to give you state and timing together on each channel – with a single probe.

Connect the probe to your board for state and you're automatically hooked up for timing. Or vice versa.

This means no more dual probing – a pain anytime and the source of loading problems – and no reconfiguration between state and timing. Which makes

| A basic comparison: Record all state and timing data<br>on an 8-bit microprocessor with multiplexed bus,<br>8-bits for address, 3 control signals and a clock. | HP<br>1654B                                                               | Tek<br>Prism/mpm | Philips<br>PM 3580/3 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------|----------------------|

| Probing:<br>Channels used<br>One connection                                                                                                                    | 481<br>No                                                                 | 48²<br>No        | 20<br>Yes            |

| Setups                                                                                                                                                         | Two                                                                       | Two+             | One                  |

| Interfaces to learn                                                                                                                                            | Two                                                                       | Two+             | One                  |

| Integrated<br>state & timing<br>triggering                                                                                                                     | No, only<br>one arming<br>condition No, only<br>indirect 4-bit<br>Teklink | Yes,<br>8 levels |                      |

| State & timing data per pin                                                                                                                                    | No                                                                        | No               | Yes                  |

| Price                                                                                                                                                          | \$6700                                                                    | \$8600           | \$4250               |

these analyzers simple to learn and use.

Plus, the pop-up menus and keyboard shortcuts guide you quickly through setup and data analysis. No matter if you use it every day or once a year.

What's more, capturing an elusive bug has never been easier with eight unrestricted trigger levels that let you select from state and ALLIANCE IN TEST & MEASUREMENT

PHILIPS

## Why not sooner?

timing trigger conditions on each level.

But being simple doesn't mean simplistic. Basic performance of the PM 3580 family ranges from 32 to 96 channels, each with 50 MHz state and up to 200 MHz timing, plus 3 nanosecond glitch capture and 2K of memory per channel. For 8-, 16and 32-bit processors.

And you get all this for nearly half the cost of comparable analyzers.

We'd like to send you a video. Or show you how to make state and timing measurements at your workplace – in 30 minutes or less.

We'll even bring the stopwatch so you can time us. And you can keep it to time the competition.

So call us today at 1-800-44-FLUKE. Ask for extension 720.

Because sooner is better.

John Fluke Mtg. Co., Inc., P.O. Box 9090, M/S 250C, Everett, WA 98206-9090, U.S. (206) 356-5400. Canada (416) 890-7600. Other countries: (206) 356-5500. © 1990. All rights reserved. Ad No. 00001.

## FAST ANSWERS.

## NEWS BRIEFS NEWS BRIEFS NEWS BRIEFS NEWS BRIEF

## Ramtron manufactures ferroelectric DRAM

Ramtron (Colorado Springs, CO) has combined breakthroughs in ferroelectric materials, electronic design, and processing to successfully manufacture the first nonvolatile DRAM, the FMx 1208 4-kbit ferroelectric DRAM. The new device combines the read/write characteristics of semiconductor RAM with nonvolatile retention of magnetic storage. And ferroelectric DRAMs can be used throughout a system because they consolidate the functions normally performed by nonvolatile memory, volatile memory, and nonvolatile data storage devices.

The 1208 uses a two-transistor, two-capacitor memory cell structure and has two operating modes: dynamic and nonvolatile. In the dynamic mode, the memory uses the high linear dielectric constant of its ferroelectric cells to store data as an electrical charge, and read/write endurance is unlimited. In this mode, the 1208 operates as a nonmultiplexed DRAM and requires, like a conventional DRAM, periodic refresh to retain data. But in the nonvolatile mode, refresh operations to all addresses prior to a power loss will cause an applied pulse to spontaneously polarize the ferroelectric cell, thereby retaining data for a minimum of one year without power.

The 1208 evaluation vehicle is available on a single-board development system. Ramtron is also expanding its technology to highdensity memory products and ASICs through strategic alliances. —Barbara Tuck

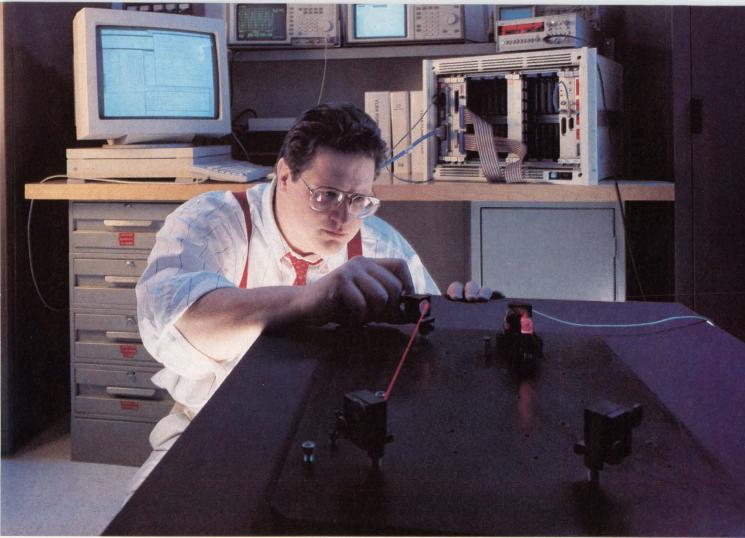

## Process could boost optical disk capacity

Researchers at Advanced Technology Materials (New Milford, CT) have discovered a new method for growing high-quality thin films of barium titanate, a nonlinear optical material used in optics research. The method promises to halve the cost of the optical-frequency doublers used in optical disk applications. With the new process, optics researchers can incorporate high-quality thin films of barium titanate in high-speed parallel optical processing designs.

Crystals grown from the barium titanate compound take the  $1-\mu m$  wavelength radiation from commercially available diode lasers and generate a strong, second harmonic signal in the visible spectrum. The higher-frequency light makes it possible to store four times as much information on optical disks, according to Advanced Technology Materials.

-Jeffrey Child

## Is '91 the year of the cache on VMEbus?

The year 1991 is the "year of the cache," predicts Ray Alderman, technical director of the VFEA International Trade Association (Scottsdale, AZ). Cache—or more precisely, cache coherency—has been one of the major buzzwords of Futurebus+, and the cache-coherency fever seems to be spreading. At Buscon/91-West, attendees of the VITA technical committee meeting were treated to a surprise suggestion that a cache-coherency mechanism be added to VMEbus.

Not all the merits of this scheme are clear, however. One advantage is that it would permit VME to map into Futurebus+ far more easily than the current scheme calls for. But outside of simplifying the bridge, the advantages may or may not outweigh the disadvantages.

First, the VITA technical committee is considering adding the cache-coherency mechanism to revision D of the VME64 specification before it's ratified and approved by the IEEE. This would effectively delay final approval of the VME64 spec. In addition, it's not clear at this time how the cache-coherency mechanism will work, or what will have to be sacrificed (in terms of pins, and so forth) to implement it.

Finally, there has been no great clamor for the capability. Like the

64-bit addressing capability of VME64, will cache coherency be something that no one uses? And will implementation of the spec call for a new generation of interface silicon?

The answers will become clear as more details of the proposal are unveiled. While VME may in some respects be too slow to use with a fully cache-coherent multiprocessor system, the proposed enhancement may bring some advantages to specific applications. And, depending on how a cache-coherency mechanism is implemented, it may also be useful for tasks other than updating caches. For example, it conceivably could be used as a technique for rapidly exchanging messages, once and for all standardizing message passing on VME. -Warren Andrews

## Real-time kernel runs on a DSP chip

In what may be the first port of a mainstream commercial real-time kernel to a digital signal processor, Ready Systems (Sunnyvale, CA) and Motorola (Tempe, AZ) have announced the availability of VRTX32 for the Motorola 56000 family of 24-bit, fixed-point DSPs.

With DSPs becoming ever more attractive for mass applications such as multimedia, voice and video compression, there's an increasing need for standard operating system interfaces. VRTX32 makes it possible for applications written in C for VRTX on standard microprocessors to be ported to the 56000.

Development environments for the 56000 are already in place. VRTX32/DSP56000 is available for personal-computer or Sun host platforms. Motorola provides an application development system board, a C compiler, assemblers, emulators, and a software simulator that run on PCs, Macintoshes, and Sun-3 workstations. In addition, Ariel (Highland Park, NJ) offers a development board for the Sparcstation, to which VRTX has been ported, as well as an SBus card. -Tom Williams

Continued on page 10

## NETWORKING SOLUTIONS

V/FDDI 4211 Peregrine V/FDDI 3211 Falcon

V/Token-Ring 4212 Owl

V/Ethernet 4207 Eagle V/Ethernet 3207 Hawk

## FDDI, TOKEN-RING AND ETHERNET COMMUNICATIONS

The need to network has never been greater. Diverse processing platforms, distributed architectures, client-server, departmental and workgroup environments all contribute to increased demands on the network. System and network designers need a proven source of technology solutions for the wide range of networking and communication application problems they face. Interphase delivers those solutions.

## FDDI, TOKEN-RING AND ETHERNET SOLUTIONS

Interphase has long led the industry in high-performance VMEbus peripheral controllers, and that same leadership is now evident in networking node controllers. Interphase has FDDI, Token-Ring and Ethernet solutions for virtually any VMEbus system application challenge.

## **PROVEN FDDI SPEED AND INTELLIGENCE**

Interphase's FDDI 100 Mb/s offerings are a logical choice for the industry. The V/FDDI 3211 Falcon received *UnixWorld* magazine's Product of the Year designation and was the industry's first 6U VMEbus FDDI solution. Interphase's newest FDDI product is the V/FDDI 4211 Peregrine, a RISC-based high-performance node controller capable of link level operation or on-board protocol processing. The Peregrine provides single or dual attach configurations, with SMT (Station Management Software) running on-board, all in one 6U VME slot.

## **TOKEN-RING RESULTS**

The V/Token-Ring 4212 Owl is an ultrafast Token-Ring node controller based on the partitioned architecture of Interphase's proven Eagle class of controllers. The Owl facilitates connectivity of UNIX<sup>®</sup> systems, workstations, supercomputers or any other VMEbus system into an IBM<sup>®</sup> environment using IEEE 802.5 Token-Ring. This multiple processor design provides an elegant queued interface to the system supporting IEEE 802.2 LLC, and a flexible 4 or 16 Mbit interface to the Token-Ring network.

## **ETHERNET CHOICES**

Interphase also offers two Ethernet design options. The V/Ethernet 4207 Eagle 32-bit protocol platform is the high-performance standard for the industry, and offers on-board TCP/IP support. The V/Ethernet 3207 Hawk is designed specifically for cost-sensitive VMEbus applications.

## GET YOUR NET WORKING NOW

No matter what your networking need – FDDI, Token-Ring or Ethernet – Interphase is ready to provide *the* solution. For more information call today:

(214) 919-9000

**OPEN SYSTEMS CONTROLLERS™**

Disk • Tape • Networking

13800 Senlac • Dallas, Texas 75234 • (214) 919-9000 • FAX: (214) 919-9200 • NASDAQ-NMS:INPH Interphase International Astral House, Granville Way • Bicester, Oxon 0X6 0JT • (01144) 869-321222 • FAX: (01144) 869-247720

Astral House, Granville Way

Bicester, Oxon 0X6 0J1

(01144) 809-321222

FAX: (01144) 809-247720

© 1990 Interphase Corporation. Interphase is a registered trademark of Interphase Corporation. Specifications subject to change without notice. UNIX is a registered trademark of At&T in the United States and other countries. IBM is a registered trademark of International Business Machines.

## NEWS BRIEFS NEWS BRIEFS NEWS BRIEFS NEWS BRIEF

Continued from page 8

## National standardizes on Silvar-Lisco tool

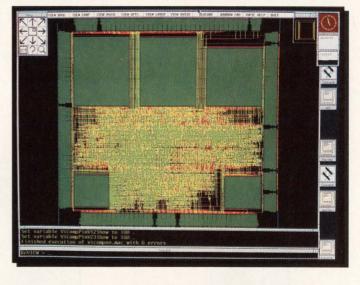

Intensive efforts by Silvar-Lisco (Sunnyvale, CA) to promote its two-to-N-layer-metal SL-Series of layout and analysis tools for gate arrays and cell-based designs appear to be paying off. National Semiconductor (Santa Clara, CA) has adopted the Silvar-Lisco SL-Array product as a standard for all National gate array products. With its hierarchical placement and linear routing algorithms, SL-Array addresses critical-path technology in arrays of up to 300,000 gates.

National's design automation director, Roy McGuffin, points to the "technical superiority of SL-Array" and "Silvar-Lisco's excellent customer service" as reasons for standardizing on the software and integrating it into National's DA4 design automation system. SL-Array reportedly has no problem accommodating the SRAMs embedded on National's new arrays.

Silvar-Lisco's SL-Array has a long way to go before it catches up with the industry's mainstay in gate array layout, Gate Ensemble from Cadence Design Systems (San Jose, CA). The tight coupling of the Cadence software to the company's other framework-based tools presents an argument in its favor before the user even does a performance comparison. The same holds true for the recently introduced Parade place-and-route software that Mentor Graphics (Wilsonville, OR) has integrated into its framework-based toolset. -Barbara Tuck

## IBM unlocks door to minilaser production

Scientists at an IBM research laboratory (Zurich, Switzerland) have developed a way to build as many as 20,000 lasers—each only a fraction of an inch long—on a semiconductor wafer just 2 in. across. According to IBM, it's the first time scientists have been able to both mass-produce and test semiconductor lasers on a complete wafer. Such lasers are now used in CD players, laser printers and fiberoptic transmission.

IBM scientists expect the new method, called full wafer technology, to be faster, some 50 percent cheaper and result in a much higher percentage of working lasers per wafer. The advancement also holds substantial promise for integration of the lasers, which range in length from <sup>1</sup>/<sub>32</sub> in. to <sup>1</sup>/<sub>64</sub> in., with other electronic components on "optoelectronic" chips that use both light and electric current to carry information. —*Mike Donlin*

## SBus off and running

SBus got another shot in the arm last month when Motorola (Tempe, AZ) announced plans for using the bus as a mezzanine bus in its Futurebus+ products. Though Motorola had previously endorsed Futurebus+ publicly, the company hadn't announced any product or product family based on the bus. Motorola's decision to back SBus provides yet another critical endorsement helping SBus on its way to becoming the highperformance I/O bus of choice for next-generation workstation products.

To keep pace in the commercial computer business, Motorola will have to go a step or two beyond what's available-or possible-on VME. Since the firm has already endorsed Futurebus+, that approach would be the most logical one for its server-based systems. But where will all the I/O come from? With its VMEbus-based systems, there are catalogs full of VME I/O cards, but that's not the case with Futurebus+. And if Motorola uses a 6U×160-mm form factor (the same as VME) for its Futurebus+ product line, as Motorola Computer Group vice-president Tom Beaver has hinted, there will be no readily available I/O to draw on.

Furthermore, Motorola has never developed its own mezzanine bus, as have some 20-odd other VME board makers. Motorola's move to take advantage of the already large base of SBus vendors (now topping the 140 mark) makes a lot of sense. SBus will do exactly what a standard bus is supposed to do-provide an industry-standard architecture to give OEMs and users more flexibility at a low cost while greatly speeding time-to-market. Motorola's decision to back SBus will probably shave as much as a year off the company's ability to get a complete Futurebus+ product to -Warren Andrews market.

## Intel launches review effort for compatibility

Bringing together a group of key industry representatives, Intel (Santa Clara, CA) has set up a review board to ensure the compatibility of binary applications across open-system software platforms targeted for 386- and 486-based hardware platforms. The first item on the board's agenda is the second edition of Intel's 386 Architecture Binary Compatibility Specification (iBCS-2).

With Intel acting as a neutral party in resolving any conflicts, the review board consists of four independent software vendors in the CAD, office automation, database, and graphics areas. OEM representatives involved include customers from Santa Cruz Operations, AT&T Unix Systems Laboratories, Open Software Foundation, and Interactive Systems. Also in the group is one end-user representative from the User Alliance of Open Systems.

Following the review of the iBCS-2 draft, the group will submit review comments for consideration by Intel prior to publishing the approved specification. A draft of the iBCS-2 will be available March 15. Intel plans to publish a final version in May.

-Jeffrey Child

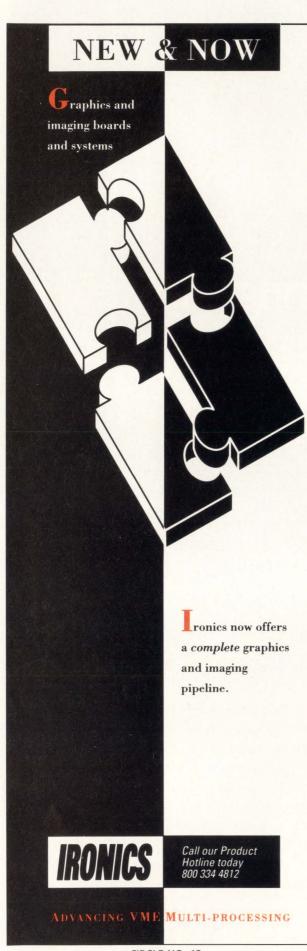

## DY4VME When you must wing

## NEW!

## **GRAPHICS CONTROLLER**

Conduction-cooled and air-cooled versions for military/aerospace applications:

High performance 32-bit Graphics System Processor (TMS34020) can be configured to operate in host-based or stand-alone system. Operates at 32 MHz rate, achieving instruction rates of up to 8 MIPS.

Modular Graphics Engine (MGEbus) interface allows two Graphic Controllers to operate in parallel with double performance and more bit planes.

Multiple video display formats from 480×480 to 1280×1024. From one to four buffers depending on format.

Composite video input accepted from remote video (e.g. image sensor). Video output port supports display of superimposed locally generated graphics on video input.

RGB video output port for color graphics display applications.

Campbell, CA Tel: (408) 377-9822 Fax: (408) 377-4725

Hammel, Denmark Tel: +45-86-963624 Fax: +45-86-962575 Nashua, NH Tel: (603) 595-2400 Fax: (603) 595-4343

Ready-to-run VMEbus systems from DY 4 are selected overwhelmingly by systems integrators for aerospace and defense programs world-wide.

> DY 4 provides performance, reliability and cost effectiveness through a full range of NDI VMEbus products and services to military, rugged and commercial standards.

> > DY 4's system solutions incorporate Ada™ board support packages (configured Ada run-time environment), drivers, and diagnostics.

DY 4 provides a comprehensive quality program

to MIL-Q-9858A and configuration management to MIL-STD-483; design procedures to MIL-STD-1521; manufacturing quality control to MIL-I-45608 and soldering to MIL-STD-2000 in an ESD-controlled environment.

Ada is a trademark of the United States Department of Defense

DY 4 Systems Inc.

21 Fitzgerald Road, Nepean, Ontario K2H 9J4 Tel : (613) 596-9911 Fax : (613) 596-0574

> Pennant Hills, Australia Tel: +61-2-484-6314 Fax: +61-2-875-1665

If we can make effective electronic weapons, why are foreign competitors beating us in commercial markets?

John C. Miklosz Associate Publisher/ Editor-in-Chief

## Will we now learn from our own example?

long with all of the anguish surrounding the Persian Gulf war, there's also a flush of high-tech euphoria. It's hard to resist the urge to root for a Patriot missile making a kill, or to remain calm when watching a video image of a laser-guided bomb being directed with incredible precision.

This is the first time that the general public has been exposed to this broad a sampling of U.S. high-tech weaponry, and everyone seems to have gone gaga, including more than a few radio and television commentators. With such a public display of potent high tech (barring the failures that the Pentagon may be keeping from view), an obvious question has popped up—if we can make such fantastic and effective electronic weaponry, why are foreign competitors beating us in key electronics and computer markets? It would be an interesting question if the answers weren't obvious.

First, military systems aren't price-sensitive. We, or rather, the Pentagon and Congress, have been prepared to pay whatever the high-tech systems have cost, barring utterly dismal performance (the Sargent York gun, for example) or a galactically outrageous price (the B1 stealth bomber, for example, which would have cost, literally, its weight in gold).

Second, the R&D of military systems is fully subsidized. A large amount of R&D at universities and government laboratories is subsidized directly, and the R&D done by contractors building systems is ultimately built into the price when it's not supported directly.

Third, the procurement of military systems has required a longterm commitment. While it's true that military systems are subject to annual budget review, the chances of a project being killed in midstream have traditionally been small. It took years to kill the Sargent York gun, for example; and the "hero" of the gulf war, the Patriot missile, went into service years ago. Compared to the consumer market, the military systems market is quite stable.

Fourth, the military systems market is a protected market. U.S. high-tech companies have the market to themselves—and rightly so in this case. We may now be relying on components manufactured overseas, but essentially all of the systems and subsystems suppliers in the United States have had the field to themselves.

A protected market, long-term commitment, subsidized R&D, and price insensitivity. Along with the genius, innovation and engineering skills that U.S. universities, laboratories and industry brought to the party, these other factors essentially guaranteed the kind of high-tech performance we've been seeing. The question we now have to answer is, what mix of the three bulwarks of our military systems development—a protected market, long-term commitment, and subsidized R&D—should we bring to bear on the battlefield of commercial competition?

Our competitors have used all these factors to ensure their success, and we've just proven to ourselves that they work. Will we now learn from our own example?

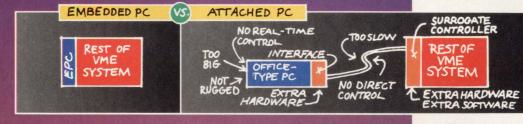

## **RADISYS GIVES VME** THE INSIDE **ADVANTAGE**

Integrating a PC with your VME system is a smart move. The "PC advantage" provides a superior human interface and access to the PC's huge base of system, application and development software.

The PC Advantage belongs inside your VME system. Not attached to it. By embedding a PC inside your VME card cage, instead of attaching it externally, you break through the inherent communications bottleneck that constricts system performance. You also eliminate the superfluous hardware and software needed to attach two system architectures.

**Only RadiSys EPC® Embedded PCs** completely integrate the strengths of PC and VME. An EPC, with its exclusive EPConnect<sup>™</sup> Software, is the only 386- or

486-based, PC-compatible computer with software that integrates the VMEbus into the DOS, Windows, UNIX and OS/2 environments. EPCs give your VME systems:

· Highest system performance from the realtime responsiveness of the direct 32-bit interface between the 386 or 486 and the VMEbus.

• Improved system packaging in 1/10th the volume, with integral VME ruggedness, and no bus link baggage.

And EPCs cost you less. EPC-based systems avoid the costly pitfalls of attached PC systems. No extra interfaces, cables, surrogate controllers, or the software to make them work.

Give your VME systems the EPC advantage. Call (800) 950-0044. We'll send all the details. No strings attached.

Mass Storage Modules

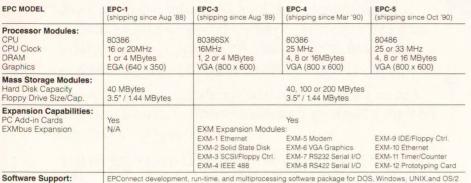

EPC Embedded PCs

EPConnect development, run-time, and multiprocessing software package for DOS, Windows, UNIX, and OS/2

## THE INSIDE ADVANTAGE

RadiSys Corporation 19545 NW Von Neumann Dr. Beaverton, OR 97006 USA (800) 950-0044 (503) 690-1229 Fax (503) 690-1228

| opyright © 1989 RadiSys Corporation. All rights reserved. RadiSys and EPC are registered trademarks and EPConnect is a trademark of      |

|------------------------------------------------------------------------------------------------------------------------------------------|

| ad/Sys Corporation. 386 and 486 are trademarks of Intel Corporation. OS/2 is a trademark of International Business Machines Corporation. |

| INIX is a trademark of American Telephone and Telegraph.                                                                                 |

CIRCLE NO. 8

EPConner

## Why Settle for $\frac{1}{2}$

040

.

.....

126222

.....

111111

You've chosen the '040 because you need maximum performance in your VME system. But look carefully, because other Single Board Computers may give you only half of what you expected from the '040.

Compare Synergy's SV430 performance to any other SBC. Compare bus speed, MIPs, support, flexibility, documentation, reliability, I/O intelligence or any spec you can think of. We think you'll find the same thing we did—the SV430 outperforms every other SBC on the market by as much as 150%.

Surprisingly, this kind of quality won't cost you any extra, because Synergy products lead in another important area—value. At Synergy, you don't have to pay a premium price for premium performance.

Let us show you just how far ahead your system can be with a Synergy processor board. Call us today, and get the <u>whole</u> '040 story.

Special Offer: Until May 1, 1991, order up to five SV430 SBCs at quantity 100 pricing! Call us at (619) 753-2191.

## an '040 Board?

## Compare our specs. Synergy is superior across the board!

VME Transfers VME64 doubles bus performance to 66 MB/s-and the SV430 is the only '040 board that has it. But we don't need VME64 to win this comparison.

Even normal 32-bit transfers race at 33 MB/s. That's 200% faster than Force or Motorola.

ance you're gaining. SV430 bursts are 26% faster than Force and Motorola

## 020 & 030 030 Only

### Compatibility Software compatibility between Synergy SBCs means users have simple upgrades to the SV430 from

DRAM

Burst

Rates

A 25 MHz '040

accessing mem-ory at 80 MB/s.

The closer you

are to this max-

imum, the more

'040 perform-

'020/'030

is capable of

'030 SBCs. Force offers compatibility only from the '030 level, and Motorola offers "upward migration"-a polite phrase that means rewriting your code.

DRAM Random Accesses

Non-burst '040 performance is measured in wait states. Fewer wait states mean higher performance. The SV430 is not only 66%

faster than Force or Motorola, it supports twice the on-board memory - 32 MB.

### **I/O Modules**

Synergy's EZ-Bus modules are compatible with our entire line of SBCs. This means Synergy's current line of 12 intelligent I/O modules are immediately available for the SV430-today. No other vendor comes close for selection, functionality or availability.

Data from Motorola MVME165 data sheet dated 2/90, and Force CPU-40 data sheet A1 Rev. 1. DRAM measurements shown are with parity. VMEbus transfers are to a 60ns slave.

VME64 is a trademark of Performance Technologies, Inc

our '020 and

### Product Warranty

Synergy backs the reliability of its SBCs with a two year standard warranty. Force and Motorola only offer vou one.

Synergy Microsystems, Inc. 179 Calle Magdalena Encinitas, CA 92024 (619) 753-2191 FAX: 619-753-0903

microsystems

ronics now offers the next generation system enclosure with superior cooling power.

Call our Product

Hotline today

800 334 4812

## CONFERENCES

CALENDAR

## March 13-20

Hannover Fairgrounds, Hannover, Germany. The more than 4,000 exhibitors from 40 countries at CeBIT will attract computer and communications professionals from 100 countries. The show includes NetWorld Europe, an exhibition and conference presenting 200 networking and connectivity firms from around the world. Information: Hannover Fairs USA, 103 Carnegie Center, Princeton, NJ 08540, (609) 987-1202. Circle 366

## March 26-28 Southcon '91

Georgia World Congress Center, Atlanta, GA. This concurrent electronics confer- Southcon / 91 ence and exhibition brings together de-

sign, test, manufacturing, and telesystems in one show. Exhibitors' products and technology are geared for the entire design and development team, from R&D through final test. Also, the National Telesystems Conference will be held in conjunction with the Southcon show. Information: Southcon '91, 8110 Airport Blvd, Los Angeles, CA 90045-3194, (800) 877-2668. Circle 367

## April 2-4 Idea '91

San Jose Convention Center, San Jose, CA. The International Design Engineering and ASIC exposition will offer exhibits from more

than 60 ASIC and EDA tool vendors, new product announcements, panels, and a technical/business education program. Topics include making price/performance and time-to-market trade-offs and ensuring first-time product success. Information: ASIC Technology and News, 480 San Antonio Rd, Suite 245, Mountain View, CA 94040, (800) 848-IDEA. Circle 368

## April 8-11 NEMDE '91

McCormick Place, Chicago, IL. The National Electronic Manufacturing and Design Exposition and Conference is designed to present a

complete spectrum of products and equipment to the entire engineering and management team. The conference will include 14 technical sessions, 12 workshops and 8 professional advancement courses. Sessions include "Design for Thermal Management," "Functional Test" and "Infrared Reflow Soldering Considerations." Information: Cahners Exposition Group, 1350 E Touhy Ave, PO Box 5060, Des Plaines, IL 60017-5060, (708) 299-9311. Circle 369

## April 9-12 **SMTCON**

Trump Plaza Hotel and Atlantic City Convention Center, Atlantic City, NJ. More than 250 SM suppliers will demonstrate products at the second annual Surface-Mount Technology Conference and Exposition. The exposition will offer a comprehensive range of components, equipment, materials, and services used in Continued on page 18

ADVANCING VME MULTI-PROCESSING

## If you're tired of pouring on SRAM to get 128Kbyte cache performance,

## Take a load off.

Introducing an amazing new cache chip that gives crowded motherboards a new lease on life. It's called 386<sup>™</sup>Smart Cache, a family of chips that integrate a cache controller with up to 16Kbytes of SRAM onto a single, one-million-transistor chip. The result is a 16Kbyte chip that really cleans up, equalling the performance of 128Kbyte caches.

Intel's 386 and 386SX Smart Cache are one-chip solutions that give you extra space on your motherboards for other applications. ©1990 Intel Corporation. 386 is a trademark of Intel Corporation. And when you stack them up against other caching solutions, you'll find their innovative architecture costs substantially less.

Give your motherboard a lift. Send in the attached card today for a free copy of our unique 386 Smart Cache video, performance report and documentation. Or if the card's been ripped off, call 1-800-548-4725, dept. HA47.

Because the reasons to look into 386 Smart Cache are really starting to pile up.

## CALENDAR

## CONFERENCES

### Continued from page 16

the design and manufacture of surface-mount and mixed technology products. The conference features advancement courses, technical forums, technical sessions, and workshops. Information: IC Management, 900 N Franklin St, Suite 700, Chicago, IL 60610, (312) 944-3434. Circle 370

## April 16-18 Electro/International

Jacob K. Javits Convention Center, New

York, NY. This three-day electronics con-ference and exhibition will feature International more than 500 exhibits and demonstrations: a technical program with tracks including digital systems and software and IC technology; a purchasing conference; and a VMEbus/Futurebus+ seminar. Information: Electronic Conventions Management, 8110 Airport Blvd, Los Angeles, CA 90045-3194, (800) 877-2668. Circle 371

......

## April 22-25 **NCGA '91**

McCormick Place North, Chicago, IL. The 12th annual conference and exposition sponsored by the National Computer Graphics As-

sociation will feature more than 200 exhibitors and a conference program geared toward computer graphics applications, including architecture, engineering, graphic design and publishing, and more. Information: National Computer Graphics Association, 2722 Merrilee Dr, Suite 200, Fairfax, VA 22031, (703) 698-9600. Circle 372

## April 30-May 1 The Canadian High Technology Show

Place Bonaventure, Montreal, Quebec. TECHNOLOGY Nearly 500 exhibitors from Canada, the United States, Europe, and Asia will dis-

play products in components and microelectronics, instrumentation, production and packaging equipment, and design automation systems. This electronics exhibition and conference-Canada's largest electronics show-attracts engineers, purchasers, management and marketers from high-tech industry, government and institutions. Information: Connelly Exhibitions, 2487 Kaladar Ave, Suite 214, Ottawa, Ontario K1V 8B9, (613) 731-9850. Circle 373

## April 30-May 2 EDS

Las Vegas Hilton Hotel, Las Vegas, NV. The three-day Electronic Distribution Show and Conference will feature exhibits, conferences and seminars on topics including limited distribution lines, market opportunities, and the distributor's role in enabling concurrent engineering. Information: Electronic Industry Show, 222 S Riverside Plaza, Chicago, IL 60606, (312) 648-1140. Circle 374

## For Those Who Like It HOT

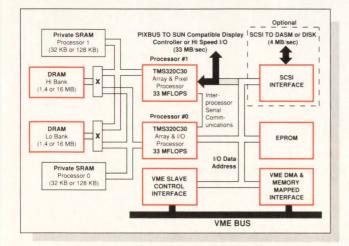

Announcing the MSP-6C30 66 MFLOP VME Array Processor

For Further Information Contact: Howard Cohen Analogic Corporation/CDA Division 8 Centennial Drive, Peabody, MA 01960-7987 Tel. (508) 977-3030, (800) 237-1011, FAX (508) 977-9220 The MSP-6C30 is a 66 MFLOP, floating-point, VME array processor optimized for signal and image processing. High performance is assured through a unique, multi-banked, crossbar memory architecture, and high bandwidth is achieved with multiple, fast, industry standard I/O ports. Also available in a PC-AT version with optional VGA compatible display controller.

## Features

- Under \$100/MFLOP (single qty.)

- Dual TI TMS320C30 Processors

- 66 MFLOP, 32 MIPS Peak Rate

- Up to 32 Mbytes On-board Dynamic RAM

- High Speed Private SRAM

- Optional SUN Compatible Frame Buffer

- Optional SCSI I/O (disk, tape, A/D, D/A, Video, DR11-W)

## Applications

- Medical

- Geophysics

- Defense

- Communications

- Digital Signal Processing

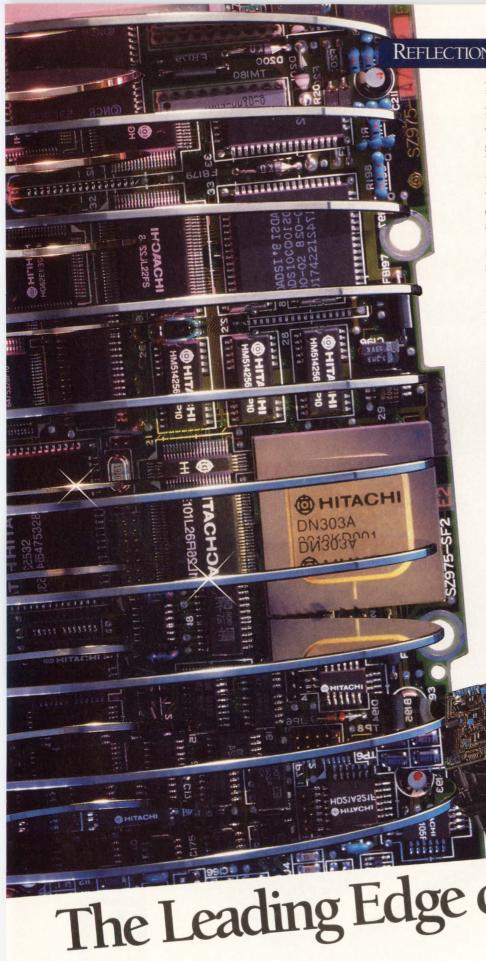

## **REFLECTIONS OF QUALITY...**

## 1.65 GB in a 5.25-inch Form Factor. Available Now Is the New Hitachi DK516C-16 Winchester.

To back-up the famous Hitachi quality, the DK516 series drives are offered with a 150,000 hour MTBF and a 5-year warranty.

## **Edge-to-Edge Performance**

The DK516C-16 uses Hitachi's advanced proprietary technology to deliver 1.65 GB of capacity and a fast 13.5 ms average access time.

Its SCSI interface provides a maximum data transfer rate of 5.0 Mbytes/sec (synchronous), with a 256 Kbyte data buffer and read look-ahead cache.

Or, if you have an ESDI application, look into Hitachi's new 1.54 GB DK516-15 with a 14 ms average seek time and a 2.75 MB/sec data transfer rate.

## Edge-to-Edge Quality

Choose the DK516 and you get a drive backed by the quality and reliability of Hitachi-a \$44 billion company. Unlike other drive manufacturers, we design, build, and test all key components in-house.

If your new system design is leading the edge, then there's only one disk drive choice: the new DK516, from Hitachi.

For more information about the DK516, or any Hitachi disk drive, call 1-800-HITACHI.

> Hitachi America, Ltd. Computer Division, MS500 Hitachi Plaza 2000 Sierra Point Parkway Brisbane, CA 94005-1819

## The Leading Edge of Capacity

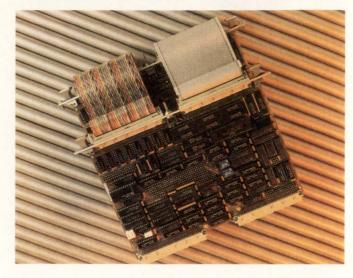

A 68040 for data, a 68020 for I/O... for **real** real-time performance on a single VME board. Radstone's 68-41 Freeflow+ multiple microprocessor board with truly independent microprocessors for data and I/O gives you next generation VME performance...Now!

- 68040 with 16 Mbytes of dual-ported memory for maximum data throughput via concurrent, uninterrupted microprocessor operation up to 40 MHz

- 68020 with 4 Mbytes of dual-ported memory controlling extensive high performance on-board I/O facilities—all operating independently

- Multiple independent external buses-VME, VSB & APEX

- Multiple independent local buses-processor and I/O

- High performance DMAs

- Intelligent, high performance Ethernet and SCSI/SCSI-2

- ... and much, much more.

Radstone's Freeflow+ architecture takes VME to new performance levels. And now it's available with 040 processing punch. It's the very latest in Radstone's long line of leading edge commercial real-time VME board level products.

## Extend your VME lead...and investment

For details on how to supercharge your VME system with Radstone's Freeflow+, and extend your current investment in VME hardware and software, call or write. Do it now, because your system is worth it!

Free Board Support Packages for all our 68040 boards, while they last. Call for details.

**Radstone Technology Corporation** 20 Craig Road, Montvale, NJ 07645-1737 **Call Toll-Free: (800) 368-2738** Eastern Region: (201) 391-2700 Central Region: (708) 397-0303 Western Region: (408) 727-4795 **CIRCLE NO. 18**

## Inder Singh on: Posix

ong dominant in the real-time field, proprietary kernels are faced with a shrinking market share due to the convergence of several strong market factors, not the least of which is the move toward standards.

During recent years, the computing world has made major progress toward standard, open systems based on the Unix operating system and the emerging Posix standards. The significant attractions of standard, open systems include vendor independence; protection from technological obsolescence; preservation of software investment; availability of off-the-shelf applications software from independent suppliers; availability of trained programmers familiar with standard environments; and connectivity between dissimilar computers within the user organization.

In stark contrast with this trend toward open, standard platforms, the world of real-time computer applications is fragmented: dozens of proprietary operating systems and restricted kernels with limited capabilities are in use. No single software environment has succeeded in capturing a significant portion of the market. This makes the development of real-time applications unnecessarily more complicated, unwieldy and expensive than that of other applications.

Developers of real-time applications find themselves stuck with a single kernel vendor, and often with specific hardware platforms. They are forced to start each project from scratch, and are unable to build upon previous work or mix solutions from multiple vendors. The lack of a standard platform (or even of a widely used one) has discouraged the development of a third-party software industry for real-time applications or development tools. The real-time kernels provide minimal facilities compared with those of complete operating systems such as Unix, forcing programmers to reimple-

ment features commonly available to the non-realtime developer.

Because of all the problems faced by real-time developers working with these proprietary kernels, there has been a strong and growing interest in Unix/Posix operating systems for real-time applications. All of the open-system benefits previously mentioned are equally applicable to real-time applications. As the only "open," fully featured, multitasking operating system that has been ported to many CPU architectures and which is available from many vendors, Unix is an extremely attractive candidate for a standard real-time operating system. The development environment of Unix is also quite popular among software developers.

## Will a Unix/Posix standard dominate?

The move toward open real-time systems based on Unix/Posix is gaining momentum with the emergence of standards such as the IEEE-1003.1 and -1003.4 Posix standards. Also contributing to this momentum is the commercial availability of products, such as LynxOS, that conform to the standards and eliminate the performance limitations of previous real-time Unix solutions. In fact, Unix/Posix will dominate the high-performance real-time world, just as it's beginning to dominate scientific, technical and other computing markets.

The IEEE-1003.1 Posix standard essentially defines a standard application programming interface for Unix, and the IEEE-1003.4 Posix standard defines a set of extensions to this interface for real time. Together, these provide for the first time a standard programming interface for real time. This opens up the possibility of writing portable real-

## INDER SINGH ON POSIX

time applications, something that has been sorely lacking in the real-time world. The fact that these standards specify the interface rather than the implementation is particularly significant, since Unix itself is notoriously poor for real time. This allows Posix-compliant operating systems such as LynxOS—which is implemented from the ground up for real time without using any actual AT&T code—to provide all the benefits of Unix and open systems without compromising on performance.

But why is a full-fledged operating system like Unix necessary for real time? Why can't the task be accomplished through the use of kernels and real-time executives, which, though restricted in functionality and limited in their non-real-time capabilities, have been the mainstay of the realtime market?

The reasons include the increasing complexity of real-time applications; the so-called RISC freeway effect; the federal policies on Posix and commercial off-the-shelf products; the cost savings provided by open systems; development time; and the availability of products that eliminate Unix' real-time limitations.

## Why were proprietary kernels popular?

Before discussing each of these reasons in detail, it may be helpful to examine the three main reasons why restricted real-time kernels have been popular despite their limited capabilities. Proprietary kernels were once popular because Unix couldn't meet the performance requirements of real-time applications, so developers had no choice but to use a proprietary, limited-function kernel. The key performance consideration was fast, bounded system response times to external events or timers. A new generation of Posix-compliant operating systems is becoming available that provide the fast, deterministic response times previously available only with the restricted kernels, along with all the functionality of a full-fledged operating system such as Unix.

In the past, most real-time applications were so simple that they didn't need a full-fledged operating system. As the complexity and sophistication of real-time applications increases, and software starts to dominate the costs of many projects, real-time developers will look for more help from the operating environment than restricted kernels can provide.

Small kernel size used to be important for costsensitive, high-volume embedded applications where the operating system must utilize as little RAM or ROM as possible. While memory isn't free, at under \$50 per megabyte it's much less expensive than in the past and not a predominant cost factor in most real-time applications.

Since real-time performance, simplicity and memory costs are the three primary advantages that restricted kernels provided, the emergence of highperformance, ROM-able Unix/Posix operating systems and the falling cost of memory are starting to rob these limited kernels of much of their market advantage. But why the market share of kernels will shrink as real-time Unix/Posix grows needs to be examined in greater detail.

## Complexity and the RISC freeway effect

As mentioned, two of the reasons for Unix/Posix' emergence as the dominant operating system in real time are the increasing complexity of real-time applications and the RISC freeway effect. These two phenomena are closely coupled. Real-time applications are growing more complex at the same time that users of real-time applications expect software to provide much of the user friendliness associated with non-real-time programs. In addition, these users increasingly expect that real-time systems will integrate well with other non-realtime systems in their environment.

Take a typical real-time application, such as a medical or scientific instrument, a data acquisition module, or a process controller. In the past, this type of application would have involved a simple control algorithm for a microprocessor-controlled piece of hardware with some lights and switches on a control panel. A real-time kernel provided a convenient base for implementing such an application. In fact, in many cases system developers implemented the code directly on the hardware, or they implemented a minimal home-brew kernel.

Today, the user of such a system—who's familiar with a wide variety of sophisticated, user-friendly non-real-time products on personal computers and workstations—has much higher expectations. He looks for a sophisticated user interface involving a CRT display (possibly with graphics and color), and on-line help. An inexpensive hard disk to log operational information or provide additional features isn't uncommon. Sooner or later, connecting this piece of equipment to other computer systems will also be required. Finally, users look for systems to be flexible and expandable.

To handle the increasing complexity demanded of today's real-time systems, the real-time applications developer needs the power and richness of a full-featured Posix operating system, particularly in such areas as graphical user interfaces, connectivity, and mass-storage support. With a Unix/Posix system, he has access to many standard facilities that save him from having to reinvent the wheel, and provide far more powerful and user-friendly solutions. In the user interface area, for example, he can build on X Windows and Motif. Connectivity solutions such as Transmission Control Protocol/Internet Protocol, Network File System, Open Systems Interconnection, and X.25 are easy to fold in. With RISC technology, increasing computing power to support these software tools is available at an affordable price.

Conversely, the availability of increased computing power at lower prices provided by RISC CPUs, along with the functionality provided by real-time Posix operating systems, creates an increasing appetite for ever more complex and demanding real-time systems. This is the phenomenon we call the RISC freeway effect, and it's analogous to the situation of a freeway being over capacity from the very day that it's opened. Despite the best traffic surveys of people traveling from point A to point B without a freeway, transportation planners find that the mere existence of the freeway and its convenience encourages people to travel between A and B, even though they didn't before the freeway was built.

## The impact of federal standards

Federal policies on Posix compliance and commercial off-the-shelf products not only demand Posixcompliant operating systems but require that those systems run on relatively inexpensive off-theshelf hardware. This means that custom hardware systems will be excluded from many contracts, as will kernels and operating systems that aren't fully Posix-compliant.

It's important to note that the government standards forcing the move toward Posix don't specify the actual implementation of a Unix version. Instead,

they require conformance with the Posix standard, which specifies the interface between the operating system and applications. The focus is on portability of applications—not on the code inside the operating system.

The U.S. government provides a test suite through the National Institute of Standards

and Technology to verify Posix 1003.1 compliance, and is establishing certification procedures for conformance testing. This can be expected to be extended to Posix 1003.4 as well. Posix conformance, as defined by the IEEE Posix committee, requires support of all interfaces as defined in the standard. Products that implement some Unix-like features or provide some mechanisms to work in conjunction with Unix won't qualify. Increasingly, Posix compliance will separate a successful contract bid from an also-ran.

## Reduced costs and development time

A Posix-compliant operating system running on commercial, off-the-shelf hardware brings more benefits to users than just the convenience of standardization: it reduces both hardware costs and development time (and reduced development time also results in further cost savings). Cost savings in hardware come from the use of readily available, mainstream products that are competitively priced and use the latest technology—examples of such products include PCs, workstations and generalpurpose computers.

Further, in later phases of a real-time system's life cycle, the user retains the option to migrate his application to the most cost-effective platform using the latest technology, perhaps from a different vendor.

The user can also achieve considerable savings in the costs of software development and maintenance. With restricted real-time kernels, the developer has to reinvent functions that are provided by a fully featured Posix-compliant operating system. Several off-the-shelf development tools are also available for the Unix/Posix environment.

In addition, applications developers don't have to learn two operating systems—one for development and another for run time—nor do they have to learn a specialized real-time programming language. With Posix and commercial off-the-shelf products, the user can develop applications in C or Ada and then run them without modification.

Training costs for both programmers and users are reduced since more and more people are already familiar with Unix.

Further cost savings come from the ability to use off-the-shelf software for numerous applications including graphics, networking, databases, and

A standard programming interface opens up the possibility of writing portable real-time applications.

spreadsheets. Further development cost savings result from the ability to migrate existing C or Ada applications to a real-time system.

The advent of the Posix standards, particularly Posix 1003.4, legitimizes the concept of Unix-compatible, real-time operating systems. We will see

an expanding role for full-featured, Posix-compliant operating systems and a shrinking market share for limited-function, proprietary real-time kernels. Widespread acceptance of open, Posixcompliant real-time operating systems will foster a market for third-party tools and applications, and facilitate the development of real-time applications. This will fuel a major growth in the overall size of the real-time market.

There will continue to be a significant niche for the proprietary real-time kernels for small, highvolume, cost-sensitive applications, but the big growth will be in the Posix area. We will see many of the proprietary kernel vendors come out with Posix-compatible libraries and extensions in an attempt to defend their market share.

Inder Singh is president of Lynx Real-Time Systems (Los Gatos, CA).

SOFTWARE

## Real-time Unix develops multiprocessing muscle

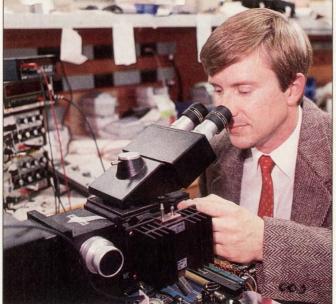

Tom Williams, Senior Editor

he attractions of the Unix operating system environment have spurred efforts by a number of companies to provide versions of the operating system that can be used for real-time applications. There are now efforts to expand the successful realtime adaptation of Unix to multiprocessor architectures.

At least two companies have made significant progress: Modcomp (Ft. Lauderdale, FL) with a multiprocessing version of its Realix realtime Unix system, and Lynx Real-Time Systems (Los Gatos, CA). Lynx offers several multiprocessing versions of its Lynx/OS that conform to the Portable Operating System Interface for Unix (Posix) standard. Realix is a functional superset of AT&T Unix System V, Release 3.2 and supports the Posix 1003.1 standard. It will incorporate the 1003.4 real-time extensions when they're finalized. Posix is a subset of the Unix application interface but doesn't provide compatibility with libraries and utilities often associated with Unix systems.

Lynx is tailoring versions of its Lynx/OS Posix-compliant operating system to three different multiprocessor architecture schemes. Lynx/ OS incorporates both the Posix 1003.1 interface standard and the 1003.4 real-time standard, draft 9. Later releases of the real-time standard will be supported as they're finalized, and draft 9 will continue to be supported for those who choose to design with it now.

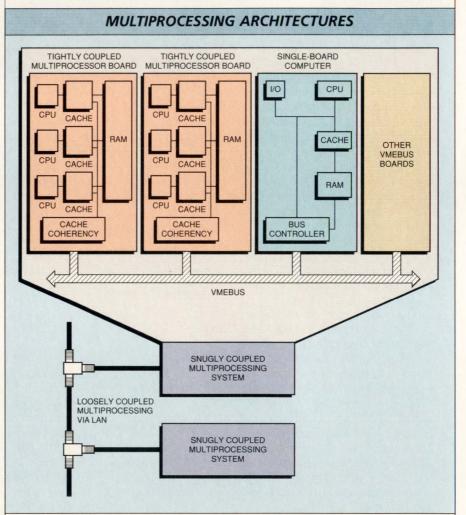

## Multiprocessing offers choices

Lynx has characterized the three multiprocessor architectures it supports as "tightly coupled," "snugly coupled" and "loosely coupled." According to Lynx vice-president of engineering, Mitch Bunnell, a symmetrical, tightly coupled multiprocessor system is one in which all memory and data structures are shared by all CPUs. Snugly coupled, a term Lynx coined, refers to a system with multiple CPU boards plugged into a backplane where certain areas of each CPU's memory are allocated for shared communication. Each CPU also has its own local memory that's not shared. In addition, separate memory boards can be plugged into the system to act as global, or shared, memory. The third characterization, loosely coupled, refers to a system where multiple CPUs pass messages via a LAN such as Ethernet. Often there's no shared memory in a loosely coupled system.

In snugly and loosely coupled systems, each CPU has its own copy of the kernel. In a tightly coupled system, there's one copy of the kernel that all CPUs use. In this system, where all CPUs potentially have access to all memory and kernel data structures, it's important to control access to critical kernel data structures while maintaining maximum performance. As Bunnell puts it, "The

A hierarchical multilevel multiprocessing system can encompass all three forms of multiprocessing. In the symmetrical, tightly coupled system, multiple CPUs on the same board share all memory and data structures via a single copy of the operating system kernel while maintaining cache coherency. They can coexist on a bus with other single-CPU boards in a "snugly" coupled arrangement. Communication between systems takes place via reserved areas of shared memory. Here, each board on the bus has its own copy of the kernel. Additionally, single-CPU board or snugly coupled systems can be configured in a loosely coupled system where interprocessor communication takes place over a LAN.

"To give our BowlerVision<sup>®</sup> system the greatest flexibility, we needed a full-function operating system. Microware's OS-9<sup>®</sup> gives us the ability to develop a real-time system right on the target hardware."

Brunswick Corporation is a 145 year old company whose business includes the design and manufacture of consumer recreation equipment, as well as defense contracting. Brunswick's Bowling and Billiards Division developed BowlerVision, a fullyintegrated control and supervisory system for bowling centers.

## "Microware's OS-9 Real-Time Operating System provides the functionality to easily incorporate new hardware."

As the heart of Brunswick's BowlerVision, OS-9 controls more than 25 processes, including communicating with the individual pinsetters and monitoring cash registers. Plans for BowlerVision called for the ability to add new features as the product evolved, as well as customizing systems to meet customers' needs. Brunswick needed a ROMable realtime operating system with I/O capabilities allowing field upgrades. "OS-9 is built around a powerful, ROMable real-time Kernel. But, no simple kernel can match the suite of sophisticated development tools and inherent I/O capabilities available under OS-9. These tools give us the ability to easily write device drivers to efficiently add new hardware to existing systems."

"As an intelligent product for consumers, BowlerVision had to be transparent to the bowler. The speed and reliability of OS-9 helped us achieve this transparency."

"Even though the BowlerVision system puts powerful features at the hands of bowling center proprietors, these people don't have to be software engineers. OS-9 was the natural choice. The system lets center proprietors concentrate on their customers and their profits, not solving system problems."

OS-9 and its comprehensive suite of real-time development tools provided a total solution for Brunswick. Find out how Microware can put OS-9 to work for you. Call us today to order a FREE copy of the OS-9 Catalog (your complete guide to the OS-9 Operating System).

MICROWARE SYSTEMS CORPORATION

1900 N.W. 114th Street • Des Moines, Iowa 50325-7077 Phone: (515) 224-1929 • Fax: (515) 224-1352

## **MORE CHOICES • MORE OPTIONS • TOTAL SUPPORT**

## TECHNOLOGY UPDATES

## SOFTWARE

more independently a CPU can run, the more throughput you'll get. On a tightly coupled system, other CPUs are going to steal some memory cycles, which is why you limit the number of processes." A normal Unix kernel is not pre-

emptable by real-time interrupts. Real-time developers either licensed the kernel from AT&T and modified it to support interrupt handling or wrote their own functional equivalents from scratch. Real-time kernels generally have areas defined

## PERFORMANCE + PORTABILITY $\heartsuit$ PRODUCTIVITY

### You Only Have to Write it Once

Oasys software tools save you time and money. Port your applications quickly without recoding. Our Green Hills' compilers ensure source code compatibility across all major hosts, targets, and operating systems. Portability is built in with complete compliance to industry standards:

- ANSI C and K&R C

- ISO Level 1 Pascal

- Support for IEEE 695+ ICE's

• C++ - OOP plus optimizations! • FORTRAN-77 (VAX VMS extensions)

· Interface to major RTOS environments

## **Optimizing Your Code is Key**

Develop more efficient, high quality software that maximizes your hardware performance, without writing assembly code. Take advantage of 50+ advanced optimizations implemented in Green Hills' compilers. Let Oasys' high performance tools optimize your code to produce the fastest, tightest executable.

## Oasys Integrated 680x0 & 88x00 Tool Kits

### Green Hills Native & Cross Compilers (C, C++, Pascal, FORTRAN) Oasys Cross Assembler/Linker System **Oasys** Simulator

Oasys UDB<sup>™</sup>- Universal Remote Debugger • HP/Apollo<sup>™</sup>

Other Tool Kits: 386TM, i860TM, TRONTM, Microsoft Cross CTM

One Cranberry Hill • Lexington, MA 02173 FAX: (617) 863-2633 or (617) 862-2427

**Tomorrow's Solutions Today** 386 and i860 are trademarks of Intel Corp. UDB is a trademark of CaseTools Inc., Microsoft Cross C is a trademark of Microsoft Corp. All other trademarks are acknowledged to their respective manufacturers.

Availability:

- Sun-3, Sun-4 SPARC™ DEC (VMS/Ultrix)™ IBM RT™ and RISC System/6000™

· More! Call for the complete list

Worldwide Support: Belgium Retime 32-2-376-5146, France Real Time Software 33-1-6986-1958, Germany Stollman 49+40-89088-0, Holland Computing & Systems Consultant 31-40-434-957, Israel Ankor Computers Ltd. 972-3-5447356, Italy Instrumatic 39-2-353-8041, Japan MCM Japan Ltd 81-3-487-8477, Spain CIDISA 34-1-563-3649, Scandinavia Traco AB 46-893-0000, Switzerland ZuhlkeEngineering AG 41-1-730-7055, UK Real Time Products 44-21-236-8070

> For Real Time Response, Call (617) 862-2002 CIRCLE NO. 20

where a higher-priority interrupt can preempt a running process without endangering data structures. According to Bunnell, Lynx has taken a different approach. They've written the kernel from scratch so there are few areas that can't be preempted.

## Predictable control

When one process has control of one of these nonpreemptable areas, other processes encounter a "spin lock," a busy wait loop, before they can have access. It can happen that a number of processes queue up for access to a spin-locked area. They would, of course, get access according to their priority. The designer must be able to calculate the worst-case time for any task to complete by figuring the number of tasks that could be pending ahead of it along with the number of such nonpreemptable areas it could encounter in the kernel.

Modcomp's Realix is tailored for a symmetrical, tightly coupled system using up to 10 Motorola MC68030 and 88000 processors and up to 512 Mbytes of 16-way interleaved main memory. The Modcomp operating system kernel uses spin locks to maintain data structure integrity when the lock time is very small-for example, less than the time of two context switches. For longer lock times, the system uses suspend locks, which allow execution to switch to another runnable process while the desired kernel resource is blocked. Realix supports only symmetric, tightly coupled multiprocessing.

In the snugly coupled scheme, CPUs communicate via areas of their own memory or system memory set aside to be shared while the loosely coupled scheme passes messages via the network. In each of these schemes every CPU has its own copy of the kernel, but the same preemption mechanism is used to handle local tasks of varying priorities.

## Real-time architectures

Although Lynx supports all three architectures, Bunnell thinks that the snugly coupled approach may be best for real-time. While the tightly coupled approach may have advantages in terms of overall throughput, it doesn't allow the designer to dedicate hardware resources to critical tasks. In the snugly coupled scheme, a critical task can be assigned a high

## **AWorld of Choice**

When it comes to mass storage needs, your choice is clear: Ricoh optical disc drives. From WORM and rewritable to bare drive and entire library units or subsystems, Ricoh offers a world of choice. Each drive boasts quality you can trust to safe-guard vital information. The kind of quality that comes from over 50 years of know-how in optics and image processing, in such products as cameras, copiers, facsimiles, telepress, laserprinters and scanners. Now you know why Ricoh is the world's leading supplier of 5-1/4" optical disc drives. For more information, call 1 (800) 955-FILE.

- RH5500/5-1/4" REMOVABLE CARTRIDGE HARD DISK DRIVE

RS-9100H/5-1/4" HALF-HEIGHT WORM SUBSYSTEM

- 3 RO-5030EII/REWRITABLE OPTICAL DISK DRIVE

- **4** RJ-5330E/MAGNETO-OPTICAL DISK LIBRARY UNIT

BEST FOR QUALITY. UNMATCHED FOR SERVICE.

RICOH CORPORATION (File Products Division) 5150 El Camino Real, M/S D ~ 20, Los Altos, Ca 94022 U.S.A Phone: 415-962-0443 Fax: 415-962-0441 RICOH CORPORATION (Eastern Region Office) 59 Stiles Road, Suite 102, Salem, NH 03079 Phone: 603-893-0547 Fax: 603-893-4162

## TECHNOLOGY UPDATES

priority and be set to run locally on a given CPU. Other, less-critical tasks can be made to run globally on whatever CPU is available. This means that bus timing has to be factored into the tasks' execution times, but it's still possible to maintain deter-

## SOFTWARE

ministic behavior. In the loosely coupled system, tasks can run deterministically on local CPUs, but due to the random nature of Ethernet's collision/retry communications, it's difficult or impossible to maintain determinism over the network.

**TASKTOOLS**<sup>™</sup>

The most

powerful set of

68000 software

development

tools available!

TASKTOOLS<sup>™</sup> offers you the

## STOP WASTING TIME & MONEY

BSO/TASKING'S new toolkit for developing software for the 68000 family, called TASKTOOLS<sup>™</sup>, beats all others on the maket today. Check out these features and benefits.

## C COMPILER

- · ANSI C · Highly optimized code

- · Reentrant code

- Direct control of I/O

- · Interrupt handlers may be written in C

- · Floating point support

- · 68040 and 68332 support

## CROSS VIEW<sup>™</sup> DEBUGGER

- · All major emulators supported

- · Multi-window interface

- · Code & data breakpoints

- · Source level tracing

- · Stack tracing

- · I/O simulation

## **ASSEMBLER & LINKER**

- Motorola compatible

- · FPU & MMU support

- · Fully featured

TaskTools and CrossView are trademarks of

CALL US 1-800-458-8276. Fax 617-894-0551.

Tasking EV Netherlands +31 33 558584

Modcomp's Realix system, while currently confining itself to symmetrical, tightly coupled architectures, does allow the programmer to dedicate resources. According to Joel Wagner, principal programmer I for multiprocessor operating systems, one can lock processes in local memory as well as a process to a processor. "Normally the system decides automatically where a process can run based on the least-busy CPU,' Wagner says. "We offer a choice. The default is complete load balancing, but you can ask for targeting."

## "The more independently a CPU can run, the more throughput you'll get."

-Mitch Bunnell, Lynx Real-Time Systems

##