## DATA

SHEET

Document Revision 2 December 1996

# AIC-4421A

Drive Manager Chip

## Gadaptec

## **General Features**

- 3.0 V to 5.5 V Operation

- Small Package Size (128 pin TQFP and MQFP available)

- Optimized Architecture for Disk Drive Motion Control

- High performance allows for the elimination of a host processor

## **DSP** Core

- 40 ns Cycle Time at 5 Volts

- 16-bit Fixed Point DSP

- 16x16-bit 2's Complement Parallel Multiplier with 32-bit Product

- Single Cycle Multiply and Accumulate

- 36-bit ALU with Two 36-bit Accumulators

#### **Host interface**

- Interrupt driven, Bidirectional three wire, Synchronous serial interface

- Configurable as Master

## **Data Acquisition**

- 10-bit, 2's Complement, 2-Step Flash A/D converter

- 8 Channels of Analog Data Input, 6 channels external

- 1.1us Total Mux. and Conversion Time per Channel (Pipeline Mode)

- Dedicated Data Acquisition Sequencer

- Pipelined and Single Channel Conversion Modes

- ALU Register Mapped Data Storage

- Supports Auto-Zeroing Input Processing

- Flexible Input Voltage Ranges Independent of the DAC Output Voltage Ranges

## VCM Control

• 12-bit 2's Complement Voltage Output DAC

#### Servo Decoder/Sequencer

- Programmable Servo Burst Sequencer

- Programmable Servo Timing Mark Sequencer

- Flexible Gating and Control Generation

- User Programmable Control Output Pins

- Allows Servo Format Flexibility

- Programmable Read Channel Interface

- Split Data Sector Support

- Separate clock input available

#### **Spindle Control**

- 8-bit Voltage Output DAC

- Digital Speed Control (FLL support)

#### **Power Management**

- Power Control Register

- Selectable on a Functional Block Basis

#### **Diagnostic Features**

- Real Time Data Output Port for Development and Diagnostics

- RS-232 Port for Diagnostic Terminal

## **Flexible Drive Management Functions**

- General Purpose I/O pins

- Two PWM outputs (GPIOs)

- Drive Fault Signal Generation

- Programmable Arm Electronics Safety Input

Copyright© 1996, 1997 Adaptec, Inc. All rights reserved. The information contained in this document (including all revisions) is the confidential, trade secret and proprietary of Adaptec, Inc. It may not be used, copied, distributed, or disclosed without the express written permission of Adaptec, Inc. Adaptec and the Adaptec logo are registered trademarks of Adaptec, Inc. All other trademarks used are owned by their respective owners. The information contained in this document is subject to change without notice.

| SECTION 2 | l - Over  | rview                                   |

|-----------|-----------|-----------------------------------------|

| 1.1       | Introdu   | action                                  |

|           | 1.1.1     | Conventions1                            |

| 1.2       | Feature   | es1                                     |

|           | 1.2.1     | General Features                        |

|           | 1.2.2     | DSP Core                                |

|           | 1.2.3     | Host interface                          |

|           | 1.2.4     | Data Acquisition                        |

|           | 1.2.5     | Servo Decoder/Sequencer                 |

|           | 1.2.6     | VCM Control                             |

|           | 1.2.7     | Spindle Control                         |

|           | 1.2.8     | Power Management                        |

|           | 1.2.9     | Diagnostic Features                     |

|           | 1.2.10    | Flexible Drive Management Functions     |

| SECTION 2 | 2 - Pin I | Descriptions                            |

| 2.1       | Pin De    | scriptions                              |

|           | 2.1.1     | Power and System                        |

|           | 2.1.2     | Analog Data Acquisition                 |

|           | 2.1.3     | DSP System                              |

|           | 2.1.4     | Servo Decoder                           |

|           | 2.1.5     | Host Interface                          |

|           | 2.1.6     | VCM Control                             |

|           | 2.1.7     | Spindle Control                         |

|           | 2.1.8     | External Memory Interface               |

|           | 2.1.9     | Other Pins                              |

| SECTION 3 | 3 - DSP   | System                                  |

| 3.1       | DSP C     | ore                                     |

| 3.2       | Memor     | ries                                    |

| 3.3       | Memor     | ry Controller                           |

|           | 3.3.1     | Common Memory Bus Contention Resolution |

|                                                           | 3.3.2                                                                                                                                                             | Chip Select Generation                                                                                                                                                                                                                                                                  |  |  |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                           | 3.3.3                                                                                                                                                             | Wait State Generation                                                                                                                                                                                                                                                                   |  |  |

|                                                           | 3.3.4                                                                                                                                                             | Support for Both 8- and 16-bit External Bus Widths                                                                                                                                                                                                                                      |  |  |

|                                                           | 3.3.5                                                                                                                                                             | PROM/Flash Programing Support                                                                                                                                                                                                                                                           |  |  |

|                                                           | 3.3.6                                                                                                                                                             | Memory Control Signal Generation                                                                                                                                                                                                                                                        |  |  |

|                                                           | 3.3.7                                                                                                                                                             | Internal Trace Mode                                                                                                                                                                                                                                                                     |  |  |

|                                                           | 3.3.8                                                                                                                                                             | Shadow Vector Register Control                                                                                                                                                                                                                                                          |  |  |

| SECTION 4                                                 | 4 - DSP                                                                                                                                                           | Peripherals                                                                                                                                                                                                                                                                             |  |  |

| 4.1                                                       | Clock                                                                                                                                                             | Generator                                                                                                                                                                                                                                                                               |  |  |

|                                                           | 4.1.1                                                                                                                                                             | Oscillator                                                                                                                                                                                                                                                                              |  |  |

|                                                           | 4.1.2                                                                                                                                                             | DSP Clock                                                                                                                                                                                                                                                                               |  |  |

|                                                           | 4.1.3                                                                                                                                                             | Bus Clock                                                                                                                                                                                                                                                                               |  |  |

|                                                           | 4.1.4                                                                                                                                                             | Servo Clock                                                                                                                                                                                                                                                                             |  |  |

|                                                           | 4.1.5                                                                                                                                                             | Peripheral Clocks                                                                                                                                                                                                                                                                       |  |  |

| 4.2                                                       | RS-232                                                                                                                                                            | 2C Serial Port                                                                                                                                                                                                                                                                          |  |  |

| 4.3                                                       | Diagno                                                                                                                                                            | stic Data Out Port                                                                                                                                                                                                                                                                      |  |  |

| 4.4                                                       | Timer                                                                                                                                                             |                                                                                                                                                                                                                                                                                         |  |  |

| 4.5                                                       | Interru                                                                                                                                                           |                                                                                                                                                                                                                                                                                         |  |  |

|                                                           |                                                                                                                                                                   |                                                                                                                                                                                                                                                                                         |  |  |

| 4.6                                                       | Genera                                                                                                                                                            | l Purpose Input/Output                                                                                                                                                                                                                                                                  |  |  |

|                                                           |                                                                                                                                                                   | Purpose Input/Output                                                                                                                                                                                                                                                                    |  |  |

|                                                           | 5 - Perij                                                                                                                                                         |                                                                                                                                                                                                                                                                                         |  |  |

| SECTION 5                                                 | 5 - Perij<br>Highlig                                                                                                                                              | oheral Port Interface                                                                                                                                                                                                                                                                   |  |  |

| SECTION 5<br>5.1                                          | 5 - Perij<br>Highlig                                                                                                                                              | pheral Port Interface                                                                                                                                                                                                                                                                   |  |  |

| SECTION 5<br>5.1                                          | 5 - Perij<br>Highlig<br>Master<br>5.2.1                                                                                                                           | oheral Port Interface       .41         ghts       .41         Mode Operation       .41                                                                                                                                                                                                 |  |  |

| <b>SECTION 5</b><br>5.1<br>5.2<br>5.3                     | 5 - Perij<br>Highlig<br>Master<br>5.2.1<br>Master                                                                                                                 | pheral Port Interface       .41         ghts       .41         Mode Operation       .41         Master Mode Serial Interface       .41                                                                                                                                                  |  |  |

| <b>SECTION 5</b><br>5.1<br>5.2<br>5.3                     | 5 - Perij<br>Highlig<br>Master<br>5.2.1<br>Master<br>5 - Serv                                                                                                     | oheral Port Interface .41   ghts .41   Mode Operation .41   Master Mode Serial Interface .41   Mode – Data Registers .44                                                                                                                                                                |  |  |

| <b>SECTION 5</b><br>5.1<br>5.2<br>5.3<br><b>SECTION 6</b> | 5 - Perij<br>Highlig<br>Master<br>5.2.1<br>Master<br>5 - Serv<br>Highlig                                                                                          | oheral Port Interface.41ghts.41Mode Operation.41Master Mode Serial Interface.41Mode – Data Registers.44o Decoder/Sequencer.45                                                                                                                                                           |  |  |

| SECTION 5<br>5.1<br>5.2<br>5.3<br>SECTION 6<br>6.1        | 5 - Perij<br>Highlig<br>Master<br>5.2.1<br>Master<br>5 - Serv<br>Highlig                                                                                          | oheral Port Interface.41ghts.41Mode Operation.41Master Mode Serial Interface.41Mode – Data Registers.44o Decoder/Sequencer.45ghts.45                                                                                                                                                    |  |  |

| SECTION 5<br>5.1<br>5.2<br>5.3<br>SECTION 6<br>6.1        | <ul> <li>5 - Perij</li> <li>Highlig</li> <li>Master</li> <li>5.2.1</li> <li>Master</li> <li>6 - Serv</li> <li>Highlig</li> <li>Function</li> </ul>                | oheral Port Interface.41ghts.41Mode Operation.41Master Mode Serial Interface.41Mode – Data Registers.44o Decoder/Sequencer.45ghts.45onal Description.46                                                                                                                                 |  |  |

| SECTION 5<br>5.1<br>5.2<br>5.3<br>SECTION 6<br>6.1        | <ul> <li>5 - Perij</li> <li>Highlig</li> <li>Master</li> <li>5.2.1</li> <li>Master</li> <li>6 - Serv</li> <li>Highlig</li> <li>Function</li> <li>6.2.1</li> </ul> | oheral Port Interface.41ghts.41Mode Operation.41Master Mode Serial Interface.41Mode – Data Registers.44o Decoder/Sequencer.45ghts.45onal Description.46Data Synchronizer.46                                                                                                             |  |  |

| SECTION 5<br>5.1<br>5.2<br>5.3<br>SECTION 6<br>6.1        | 5 - Perij<br>Highlig<br>Master<br>5.2.1<br>Master<br>6 - Serv<br>Highlig<br>Functio<br>6.2.1<br>6.2.2                                                             | oheral Port Interface.41ghts.41Mode Operation.41Master Mode Serial Interface.41Mode – Data Registers.44o Decoder/Sequencer.45ghts.45onal Description.46Data Synchronizer.46Servo Header and Gray Code Detection.49                                                                      |  |  |

| SECTION 5<br>5.1<br>5.2<br>5.3<br>SECTION 6<br>6.1        | 5 - Perij<br>Highlig<br>Master<br>5.2.1<br>Master<br>6 - Serv<br>Highlig<br>Functio<br>6.2.1<br>6.2.2<br>6.2.3                                                    | oheral Port Interface.41ghts.41Mode Operation.41Master Mode Serial Interface.41Mode – Data Registers.44o Decoder/Sequencer.45ghts.45onal Description.46Data Synchronizer.46Servo Header and Gray Code Detection.49Write Gate Qualification.49                                           |  |  |

| SECTION 5<br>5.1<br>5.2<br>5.3<br>SECTION 6<br>6.1        | <b>5 - Perij</b><br>Highlig<br>Master<br>5.2.1<br>Master<br><b>6 - Serv</b><br>Highlig<br>Functio<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4                             | oheral Port Interface.41ghts.41Mode Operation.41Master Mode Serial Interface.41Mode – Data Registers.44o Decoder/Sequencer.45ghts.45onal Description.46Data Synchronizer.46Servo Header and Gray Code Detection.49Write Gate Qualification.49Shock Sensor Input.50                      |  |  |

| SECTION 5<br>5.1<br>5.2<br>5.3<br>SECTION 6<br>6.1        | 5 - Perij<br>Highlig<br>Master<br>5.2.1<br>Master<br>6 - Serv<br>Highlig<br>Functio<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5                                  | oheral Port Interface.41Mode Operation.41Master Mode Serial Interface.41Mode – Data Registers.44o Decoder/Sequencer.45ohts.45ohts.45onal Description.46Data Synchronizer.46Servo Header and Gray Code Detection.49Write Gate Qualification.49Shock Sensor Input.50Drive Fault Signal.50 |  |  |

|                                                                            | 6.2.9 Sector Timing Control                                                                                                                                                                                                                                                                                                                                                                                                                                  | 58                               |

|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|                                                                            | 6.2.10 Sequencer/Decoder Registers                                                                                                                                                                                                                                                                                                                                                                                                                           | 60                               |

| SECTION                                                                    | 7 - Analog Data Acquisition                                                                                                                                                                                                                                                                                                                                                                                                                                  | 71                               |

| 7.1                                                                        | Highlights                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 71                               |

| 7.2                                                                        | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                       | 72                               |

| SECTION                                                                    | 8 - VCM DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 77                               |

| 8.1                                                                        | Highlights                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 77                               |

|                                                                            | 8.1.1 VCM DAC Register                                                                                                                                                                                                                                                                                                                                                                                                                                       | 77                               |

| SECTION                                                                    | 9 - Spindle Control                                                                                                                                                                                                                                                                                                                                                                                                                                          | 79                               |

| 9.1                                                                        | Highlights                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                  |

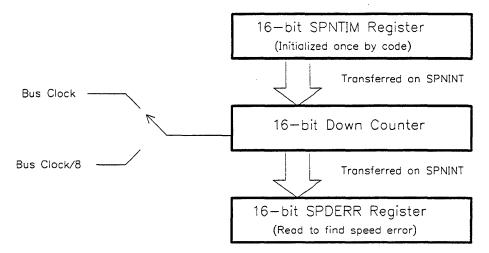

| 9.2                                                                        | Speed Regulation                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                  |

|                                                                            | 9.2.1 Spindle DAC Register                                                                                                                                                                                                                                                                                                                                                                                                                                   | 81                               |

|                                                                            | 9.2.2 Spindle Period Register                                                                                                                                                                                                                                                                                                                                                                                                                                | 81                               |

|                                                                            | 9.2.3 Speed Error Register                                                                                                                                                                                                                                                                                                                                                                                                                                   | 82                               |

|                                                                            | 9.2.4 Spindle Count Register                                                                                                                                                                                                                                                                                                                                                                                                                                 | 82                               |

|                                                                            | 9.2.5 Spindle Control Register                                                                                                                                                                                                                                                                                                                                                                                                                               | 82                               |

|                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                  |

| SECTION                                                                    | 10 - Power Control/Voltage References                                                                                                                                                                                                                                                                                                                                                                                                                        | 83                               |

| <b>SECTION</b><br>10.1                                                     | 10 - Power Control/Voltage References                                                                                                                                                                                                                                                                                                                                                                                                                        |                                  |

|                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 83                               |

|                                                                            | Power Control                                                                                                                                                                                                                                                                                                                                                                                                                                                | 83<br>83                         |

|                                                                            | Power Control                                                                                                                                                                                                                                                                                                                                                                                                                                                | 83<br>83<br>83                   |

|                                                                            | Power Control      10.1.1 Highlights      10.1.2 Functional Description                                                                                                                                                                                                                                                                                                                                                                                      | 83<br>83<br>83<br>86             |

| 10.1                                                                       | Power Control      10.1.1 Highlights      10.1.2 Functional Description      10.1.3 Power Control Summary                                                                                                                                                                                                                                                                                                                                                    | 83<br>83<br>83<br>86<br>87       |

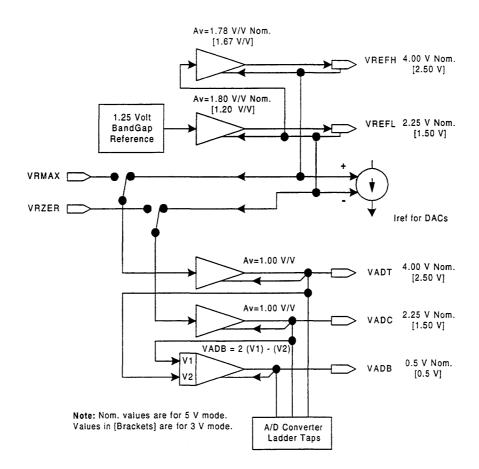

| 10.1<br>10.2                                                               | Power Control         10.1.1 Highlights         10.1.2 Functional Description         10.1.3 Power Control Summary         Voltage References                                                                                                                                                                                                                                                                                                                | 83<br>83<br>83<br>86<br>87<br>87 |

| 10.1<br>10.2                                                               | Power Control         10.1.1 Highlights         10.1.2 Functional Description         10.1.3 Power Control Summary         Voltage References         10.2.1 Highlights                                                                                                                                                                                                                                                                                      |                                  |

| 10.1<br>10.2<br>SECTION                                                    | Power Control         10.1.1 Highlights         10.1.2 Functional Description         10.1.3 Power Control Summary         Voltage References         10.2.1 Highlights                                                                                                                                                                                                                                                                                      |                                  |

| 10.1<br>10.2<br><b>SECTION</b><br>11.1<br>11.2                             | Power Control         10.1.1 Highlights         10.1.2 Functional Description         10.1.3 Power Control Summary         Voltage References         10.2.1 Highlights <b>11 - Electrical Specifications</b> Absolute Maximum Ratings                                                                                                                                                                                                                       |                                  |

| 10.1<br>10.2<br><b>SECTION</b><br>11.1<br>11.2                             | Power Control         10.1.1 Highlights         10.1.2 Functional Description         10.1.3 Power Control Summary         Voltage References         10.2.1 Highlights         11 - Electrical Specifications         Absolute Maximum Ratings         Recommended Operating Conditions                                                                                                                                                                     |                                  |

| 10.1<br>10.2<br>SECTION<br>11.1<br>11.2<br>SECTION                         | Power Control         10.1.1 Highlights         10.1.2 Functional Description         10.1.3 Power Control Summary         Voltage References         10.2.1 Highlights         11 - Electrical Specifications         Absolute Maximum Ratings         Recommended Operating Conditions         12 - Performance Specifications                                                                                                                             |                                  |

| 10.1<br>10.2<br>SECTION<br>11.1<br>11.2<br>SECTION<br>12.1                 | Power Control         10.1.1 Highlights         10.1.2 Functional Description         10.1.3 Power Control Summary         Voltage References         10.2.1 Highlights         11 - Electrical Specifications         Absolute Maximum Ratings         Recommended Operating Conditions         12 - Performance Specifications         General                                                                                                             |                                  |

| 10.1<br>10.2<br>SECTION<br>11.1<br>11.2<br>SECTION<br>12.1<br>12.2         | Power Control         10.1.1 Highlights         10.1.2 Functional Description         10.1.3 Power Control Summary         Voltage References         10.2.1 Highlights         11 - Electrical Specifications         Absolute Maximum Ratings         Recommended Operating Conditions         12 - Performance Specifications         General         Digital I/O Characteristics                                                                         |                                  |

| 10.1<br>10.2<br>SECTION<br>11.1<br>11.2<br>SECTION<br>12.1<br>12.2<br>12.3 | Power Control         10.1.1       Highlights         10.1.2       Functional Description         10.1.3       Power Control Summary         Voltage References       10.2.1         10.2.1       Highlights         11 - Electrical Specifications       Absolute Maximum Ratings         Recommended Operating Conditions       12 - Performance Specifications         General       Digital I/O Characteristics         Analog Data Acquisition (5 Volt) |                                  |

. .

| 12.7       | Spindle DAC                                            |  |  |

|------------|--------------------------------------------------------|--|--|

| 12.8       | Servo Decoder/Sequencer                                |  |  |

| 12.9       | Host Interface                                         |  |  |

| 12.10      | External Memory Interface                              |  |  |

| 12.11      | DSP System                                             |  |  |

| 12.12      | Clock Out                                              |  |  |

| 12.13      | Power Control                                          |  |  |

| SECTION 1  | 3 - Registers                                          |  |  |

| 13.1       | I/O Register Summary                                   |  |  |

|            | 13.1.1 Analog Data Acquisition Registers109            |  |  |

|            | 13.1.2 Programmable Clock Generator Registers          |  |  |

|            | 13.1.3 Diagnostic Data Out Port Registers              |  |  |

|            | 13.1.4 Host Interface Port Registers                   |  |  |

|            | 13.1.5 Interrupt Control Registers                     |  |  |

|            | 13.1.6 Configuration Registers                         |  |  |

|            | 13.1.7 VCM DAC Register                                |  |  |

|            | 13.1.8 Power Control Registers                         |  |  |

|            | 13.1.9 RS-232 Serial Port Registers113                 |  |  |

|            | 13.1.10 Write Gate Qualification/Drive Fault Registers |  |  |

|            | 13.1.11 Servo Decoder/Sequencer Registers115           |  |  |

|            | 13.1.12 Spindle Control Registers                      |  |  |

|            | 13.1.13 Timer Registers                                |  |  |

|            | 13.1.14 General-Purpose I/O Registers                  |  |  |

|            | 13.1.15 Manufacturing Test Registers                   |  |  |

|            | 13.1.16 Burst Sequencer RAM                            |  |  |

|            | 13.1.17 Timing Mark Sequencer RAM122                   |  |  |

|            | 13.1.18 Vector Shadow RAM                              |  |  |

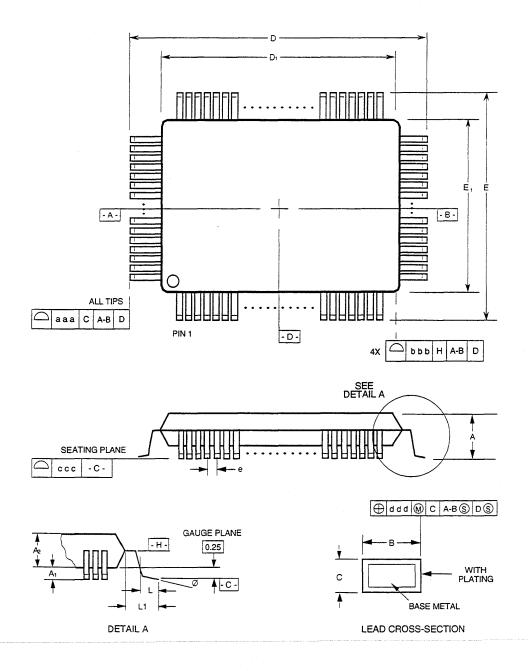

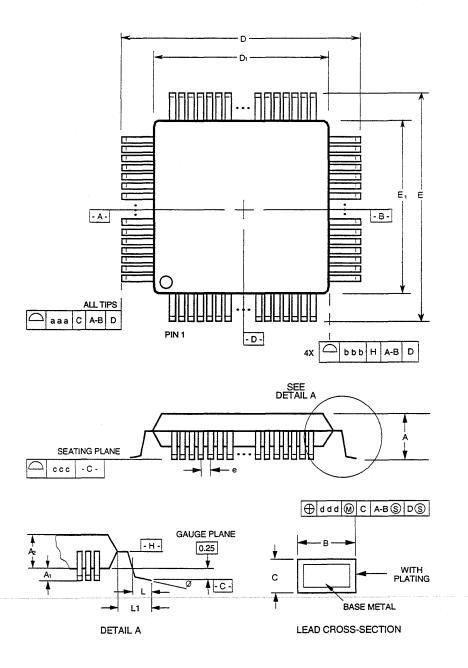

| SECTION 14 | 4 - Packaging Specifications                           |  |  |

| 14.1       | MQFP Packaging Specifications                          |  |  |

| 14.2       | TQFP Packaging Specifications                          |  |  |

| SECTION 1  | 5 - Additional References                              |  |  |

## List of Figures

| Figure 1-1  | Overall Block Diagram                           | 3  |

|-------------|-------------------------------------------------|----|

| Figure 1-2  | Typical Application Block Diagram               | 4  |

| Figure 2-1  | AIC-4421 TQFP Pinout (Top View)                 | 14 |

| Figure 2-2  | AIC-4421 MQFP Pinout (Top View)                 | 15 |

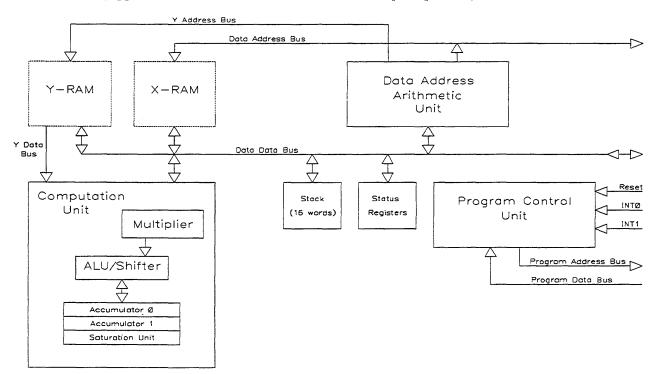

| Figure 3-1  | DSP Core Block Diagram                          | 17 |

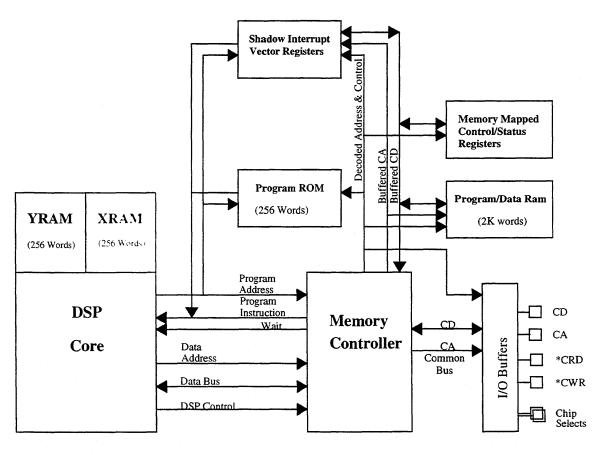

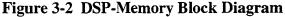

| Figure 3-2  | DSP-Memory Block Diagram                        | 18 |

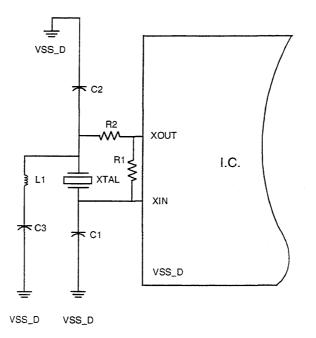

| Figure 4-1  | Crystal Oscillator Schematic                    |    |

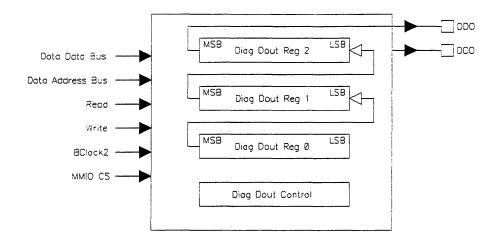

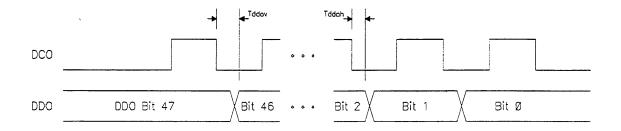

| Figure 4-2  | Diagnostic Data Out Port                        | 35 |

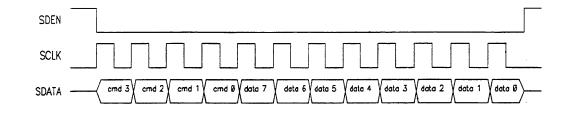

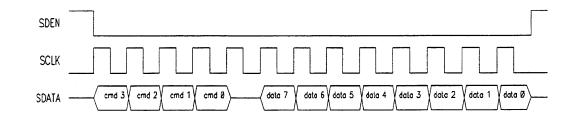

| Figure 5-1  | Master Mode Write Timing Example                | 43 |

| Figure 5-2  | Master Mode Read Timing Example                 | 43 |

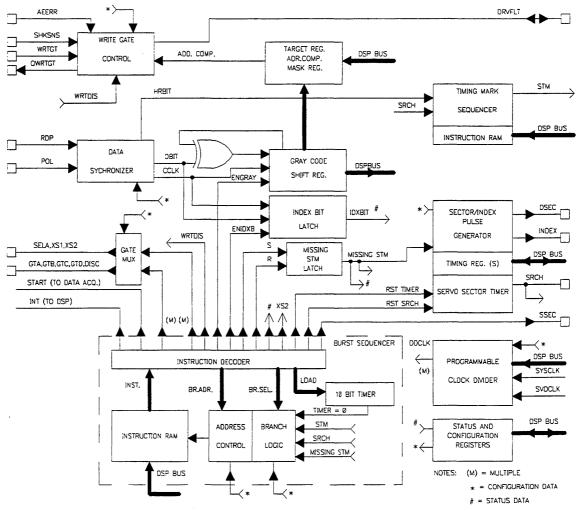

| Figure 6-1  | Servo Decoder/Sequencer Block Diagram           | 45 |

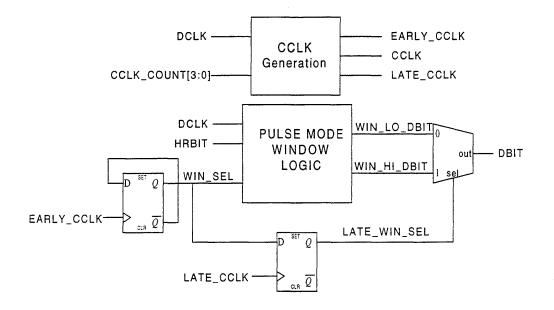

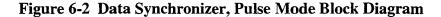

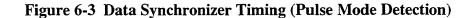

| Figure 6-2  | Data Synchronizer, Pulse Mode Block Diagram     | 47 |

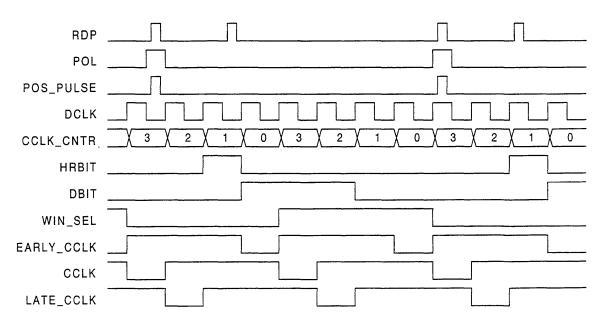

| Figure 6-3  | Data Synchronizer Timing (Pulse Mode Detection) | 47 |

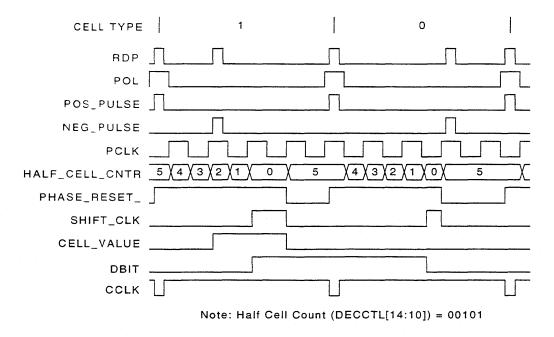

| Figure 6-4  | Data Synchronizer, Phase Mode Block Diagram     | 48 |

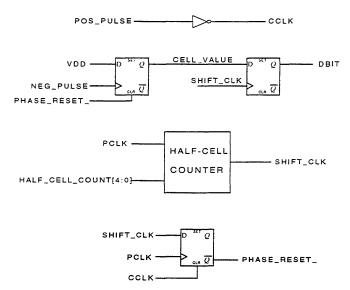

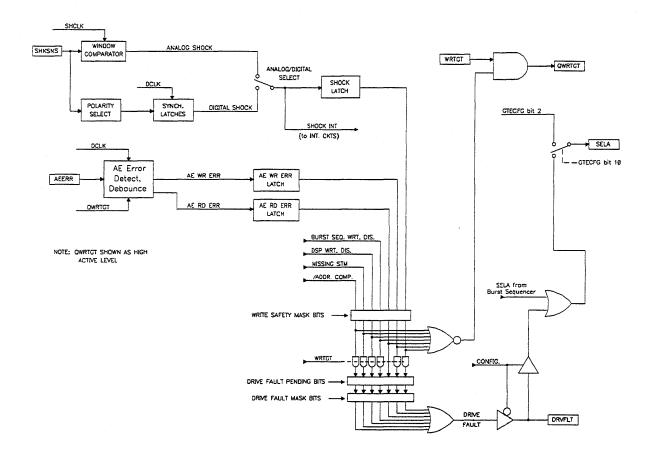

| Figure 6-5  | Data Synchronizer Timing (Phase Mode Detection) | 48 |

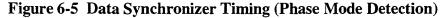

| Figure 6-6  | Write Gate/Drive Fault Circuits                 | 50 |

| Figure 6-7  | 2 of 3 Timing Mark Example                      | 51 |

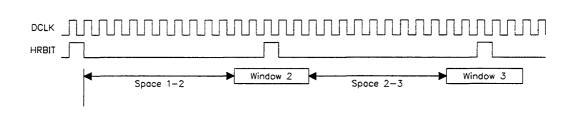

| Figure 6-8  | Timing Mark Sequencer Block Diagram             | 52 |

| Figure 6-9  | Timing Mark Sequencer Instruction Format        | 53 |

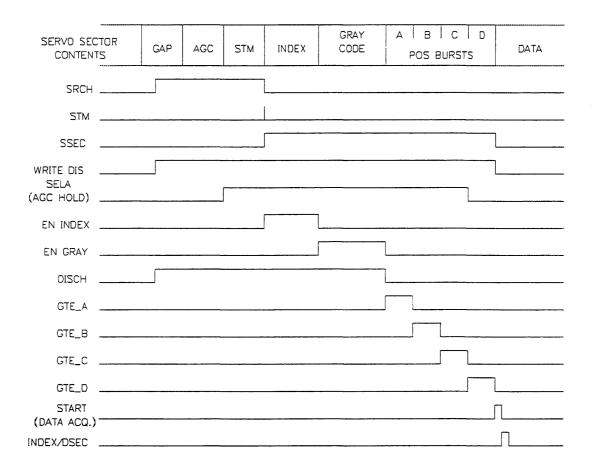

| Figure 6-10 | Servo Sector Timing Example                     | 55 |

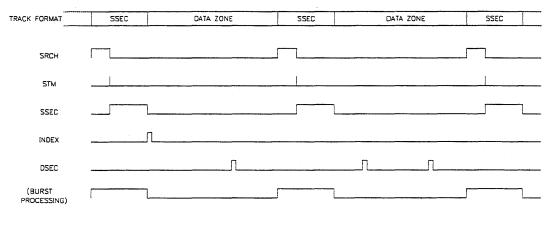

| Figure 6-11 | Track Timing Example                            | 58 |

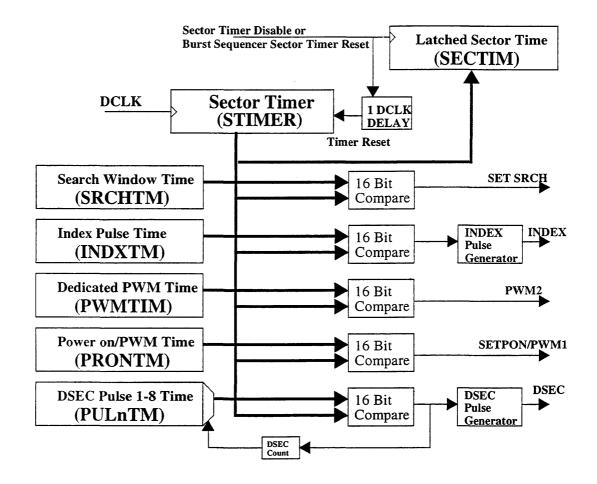

| Figure 6-12 | Sector Timing Control                           | 59 |

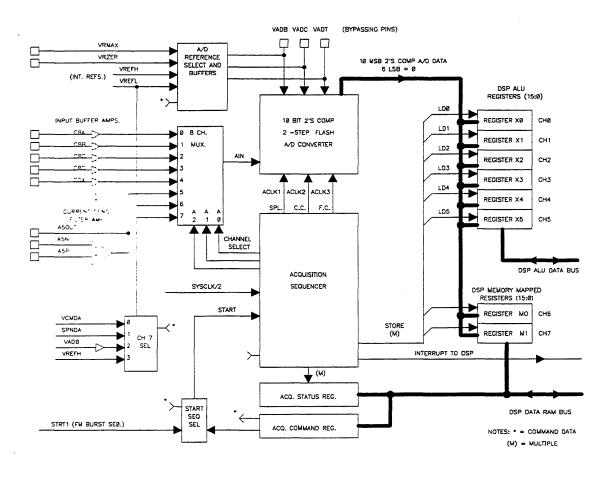

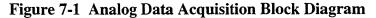

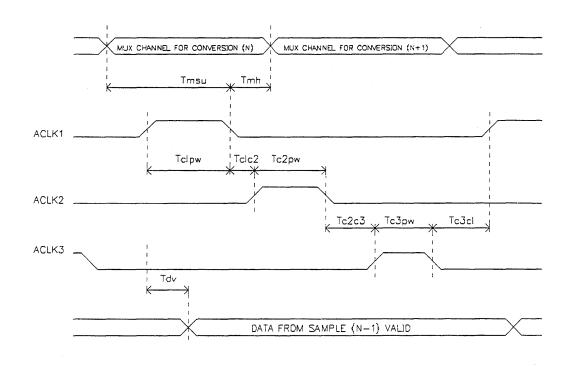

| Figure 7-1  | Analog Data Acquisition Block Diagram           | 71 |

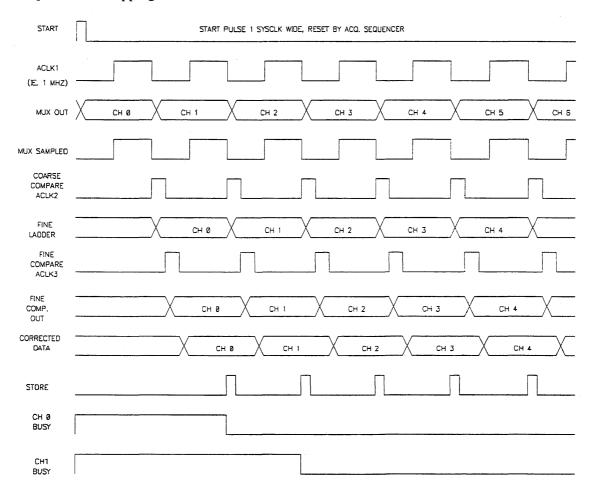

| Figure 7-2  | Pipeline A/D Converter Timing                   | 74 |

•

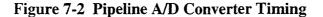

| Figure 9-1  | Spindle Interrupt Source Selection for Speed Regulation           |  |  |

|-------------|-------------------------------------------------------------------|--|--|

| Figure 9-2  | Speed Regulation Hardware81                                       |  |  |

|             |                                                                   |  |  |

| Figure 10-1 | Voltage Reference Generation                                      |  |  |

| Figure 12-1 | Analog Input Equivalent Circuit96                                 |  |  |

| Figure 12-2 | ACLKn Timing Requirements                                         |  |  |

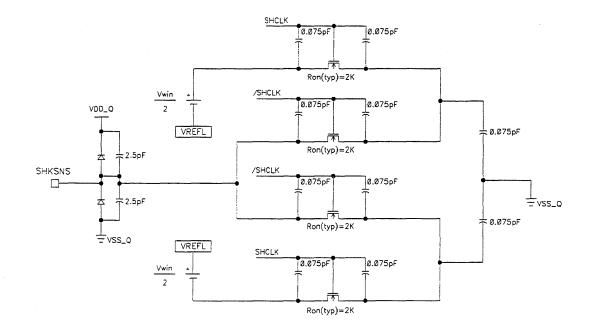

| Figure 12-3 | SHKSNS Pin Input Equivalent Circuit                               |  |  |

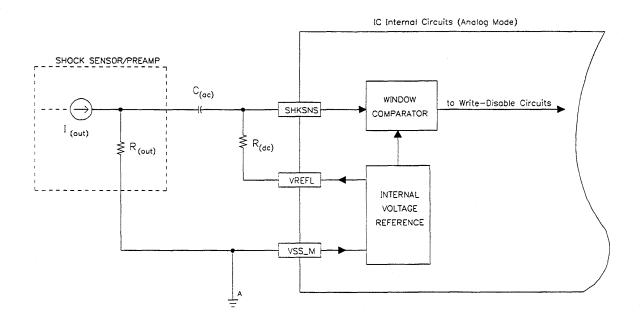

| Figure 12-4 | Analog Shock Sensor Input Connections                             |  |  |

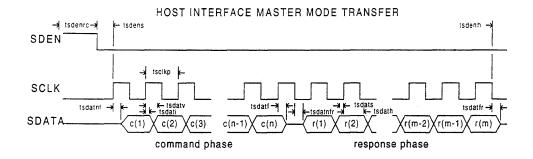

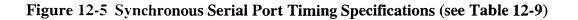

| Figure 12-5 | Synchronous Serial Port Timing Specifications (see Table 12-9)104 |  |  |

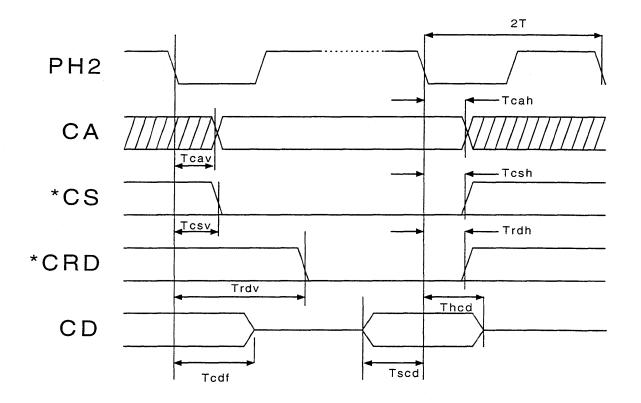

| Figure 12-6 | External Memory Read (see Table 12-10)106                         |  |  |

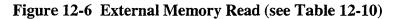

| Figure 12-7 | External Memory Write (see Table 12-10)                           |  |  |

| Figure 12-8 | Diagnostic Data Out Timing (see Table 12-11)107                   |  |  |

|             |                                                                   |  |  |

| Figure 14-1 | 128-Pin MQFP Package Outline                                      |  |  |

| Figure 14-2 | 128-Pin TQFP Package Outline                                      |  |  |

| Table 2-1  | Power and System Pin Descriptions                            | 5  |

|------------|--------------------------------------------------------------|----|

| Table 2-2  | Analog Data Acquisition Pin Descriptions                     | 7  |

| Table 2-3  | DSP System Pin Descriptions                                  | 8  |

| Table 2-4  | Servo Decoder/Sequencer Pin Descriptions                     | 9  |

| Table 2-5  | Host Interface Pin Descriptions                              | 11 |

| Table 2-6  | VCM Control Pin Descriptions                                 |    |

| Table 2-7  | Spindle Control Pin Descriptions                             |    |

| Table 2-8  | External Memory Interface Pin Description                    |    |

| Table 2-9  | Other Pin Descriptions                                       |    |

| Table 3-1  | Data Memory Map                                              | 19 |

| Table 3-2  | Program Memory Map                                           | 20 |

| Table 3-3  | External Program Space RAM/ROM Configurations                | 21 |

| Table 3-4  | Common Bus Transaction Sequences                             | 22 |

| Table 3-5  | Chip Configuration Register (CHPCFG)                         | 25 |

| Table 3-6  | Chip Revision Register (CHPREV)                              | 25 |

| Table 3-7  | Memory Configuration Register (MEMCFG)                       |    |

| Table 3-8  | Memory Access Cycle Times (16-bit Mode)                      | 27 |

| Table 3-9  | Memory Access Cycle Times (8-bit Mode)                       | 28 |

| Table 4-1  | Crystal Oscillator External Components (Third Overtone Mode) |    |

| Table 4-2  | Crystal Oscillator External Components (Fundamental Mode)    | 30 |

| Table 4-3  | Internal Clock Summary                                       |    |

| Table 4-4  | Clock Configuration Register 1 (CLCFG1)                      | 32 |

| Table 4-5  | Clock Configuration Register 2 (CLCFG2)                      | 32 |

| Table 4-6  | Serial Port Baud Rate Register (SPBAUD)                      |    |

| Table 4-7  | Baud Rate Generator Values                                   | 33 |

| Table 4-8  | Serial Port Status Register (SPSTAT)                         | 34 |

| Table 4-9  | Serial Port Transmit Register (TXCHAR)                       | 34 |

| Table 4-10 | Serial Port Receive Register (RXCHAR)                        | 34 |

| Table 4-11              | Diagnostic Data Out Control Register (DIAGDC)            | 35 |

|-------------------------|----------------------------------------------------------|----|

| Table 4-12              | Diagnostic Data Out Data Register 2 (DIAGD2)             | 35 |

| Table 4-13              | Diagnostic Data Out Data Register 1 (DIAGD1)             | 35 |

| Table 4-14              | Diagnostic Data Out Data Register 0 (DIAGD0)             |    |

| Table 4-15              | Timer Control Register (TM0CTL)                          |    |

| <sup>4</sup> Table 4-16 | Timer Initial Count Register (TM0SET)                    |    |

| Table 4-17              | Timer Current Count Register (TM0CNT)                    |    |

| Table 4-18              | Interrupt Mask Register (INTMSK)                         |    |

| Table 4-19              | Interrupt Pending Register (INTPND)                      |    |

| Table 4-20              | General Purpose I/O Control Register (GPIOCL)            |    |

| Table 4-21              | General Purpose I/O Data Register (GPIODT)               | 40 |

| Table 4-22              | General Purpose I/O Configuration Register (GPIOCF)      | 40 |

|                         |                                                          |    |

| Table 5-1               | Master Mode – Serial Interface Control Register (MSTCTL) |    |

| Table 5-2               | Master Mode Transfer Control Register (MMTCTL)           |    |

| Table 5-3               | Host Interface Data 1 Register (HSTDT1)                  | 44 |

| Table 5-4               | Host Interface Data 2 Register (HSTDT2)                  | 44 |

|                         |                                                          |    |

| Table 6-1               | Timing Mark Sequencer Instruction Format                 | 53 |

| Table 6-2               | Burst Sequencer Instruction Format                       |    |

| Table 6-3               | Drive Fault Configuration Register (DFLCFG)              | 60 |

| Table 6-4               | Write Gate Disable Drive Fault Register (WRGTDF)         | 61 |

| Table 6-5               | Drive Fault Pending Register (DFLTPD)                    |    |

| Table 6-6               | Data Sector Pulse 1 Time Register (PUL1TM)               |    |

| Table 6-7               | Data Sector Pulse 2 Time Register (PUL2TM)               | 62 |

| Table 6-8               | Data Sector Pulse 3 Time Register (PUL3TM)               | 62 |

| Table 6-9               | Data Sector Pulse 4 Time Register (PUL4TM)               | 63 |

| Table 6-10              | Data Sector Pulse 5 Time Register (PUL5TM)               | 63 |

| Table 6-11              | Data Sector Pulse 6 Time Register (PUL6TM)               | 63 |

| Table 6-12              | Data Sector Pulse 7 Time Register (PUL7TM)               | 63 |

| Table 6-13              | Data Sector Pulse 8 Time Register (PUL8TM)               | 63 |

| Table 6-14              | Decoder Configuration Register (DECCFG)                  | 64 |

| Table 6-15              |                                                          |    |

| 10010 0 10              | Decoder Control Register (DECCTL)                        | 65 |

| Table 6-17 | Target Address Register (TGTADR)          | 67 |

|------------|-------------------------------------------|----|

| Table 6-18 | Address Compare Mask Register (ADRMSK)    | 67 |

| Table 6-19 | Gray Code Shift Register (GRAYSH)         | 67 |

| Table 6-20 | Gating Configuration Register (GTECFG)    | 68 |

| Table 6-21 | Index Target Register (IDXTGT)            | 68 |

| Table 6-22 | Index Compare Mask Register (IDXMSK)      | 68 |

| Table 6-23 | Index Shift Register (INDXSH)             | 69 |

| Table 6-24 | Sector Time Register (SECTIM)             | 69 |

| Table 6-25 | Search Window Time Register (SRCHTM)      | 69 |

| Table 6-26 | Sector Timer Register (STIMER)            | 69 |

| Table 6-27 | Power On Time Register (PRONTM)           | 69 |

| Table 6-28 | Index Pulse Time Register (INDXTM)        | 70 |

| Table 6-29 | Dedicated PWM Time Register (PWMTIM)      | 70 |

|            |                                           |    |

| Table 7-1  | Acquisition Command Register (ADCCMD)     | 72 |

| Table 7-2  | Acquisition Status Register (ADCSTA)      | 75 |

| Table 7-3  | Data Storage Registers (ADCCH0 – ADCCH5)  | 76 |

| Table 7-4  | Data Storage Registers (ADCCH6, ADCCH7)   | 76 |

|            |                                           |    |

| Table 8-1  | VCM DAC Register (VCMDAC)                 | 77 |

|            |                                           |    |

| Table 9-1  | Source of SPNINT                          | 79 |

| Table 9-2  | Spindle DAC Register (SPNDAC)             | 81 |

| Table 9-3  | Spindle Period Register (SPNTIM)          | 81 |

| Table 9-4  | Speed Error Register (SPDERR)             | 82 |

| Table 9-5  | Spindle Count Register (SPNCNT)           | 82 |

| Table 9-6  | Spindle Control Register (SPNCTL)         | 82 |

|            |                                           |    |

| Table 10-1 | Reset and Power Control Register (PWRCTL) | 83 |

| Table 10-2 | Power Control Summary                     | 86 |

| Table 10-3 | VREFL Trimming Register (REFTRM)          | 88 |

|            |                                           |    |

| Table 11-1 | Absolute Maximum Ratings                  | 89 |

| Table 11-2 | Recommended Operating Conditions          | 89 |

| Table 12-1  | General Performance Specifications                     |              |  |  |

|-------------|--------------------------------------------------------|--------------|--|--|

| Table 12-2  | Digital I/O Performance Specifications                 | .93          |  |  |

| Table 12-3  | Analog Data Acquisition Performance Specifications (1) | .94          |  |  |

| Table 12-4  | ACLKn Timing Requirements                              | .97          |  |  |

| Table 12-5  | Shock Sensor Input (1)                                 | .99          |  |  |

| Table 12-6  | VCM DAC Analog Performance Specifications (1)1         | 101          |  |  |

| Table 12-7  | Spindle DAC Analog Performance Specifications(1)1      | 102          |  |  |

| Table 12-8  | Servo Decoder/Sequencer Performance Specifications1    | 103          |  |  |

| Table 12-9  | Host Interface Timing Specifications1                  | 103          |  |  |

| Table 12-10 | External Memory Interface Timing Specifications1       | 105          |  |  |

| Table 12-11 | Diagnostic Data Out Timing Specifications1             |              |  |  |

| Table 12-12 | DSP System Timing Specifications1                      | i <b>0</b> 7 |  |  |

| Table 12-13 | Clock Out Timing Specifications1                       |              |  |  |

| Table 12-14 | Power Control Specifications by Functional Block (1)1  | 108          |  |  |

|             |                                                        |              |  |  |

| Table 14-1  | 128-Pin MQFP Package Dimensions1                       | 125          |  |  |

| Table 14-2  | 128-Pin TQFP Package Dimensions1                       | 127          |  |  |

#### **1.1 Introduction**

This IC utilizes mixed signal CMOS large scale integration to provide the full motion control function for the Tracking and Spin systems of a disk drive. The IC architecture is designed around a high performance, low power DSP core with peripherals optimized to the DSP and the Disk Drive control functions. This combination of processing power and efficient peripherals provides a platform to process more advanced digital control algorithms resulting in higher performance products.

The IC uses a single power supply with performance specified for 5 Volt and 3.3 Volt levels. This specification describes 5V operation. 3.3V users should refer to the guide referenced in section 15. Many levels of power reduction can be programmed into the unit to match the application. CMOS technology, low-voltage design techniques, and high levels of integration provide a high function density needed to design small form factor drives.

This IC is highly flexible with the choice of format, read channel and host processors. The IC can operate in a "Master" mode in which no other host processor is required. In that mode the Data Path Control and all other drive control functions can be managed by this IC.

Diagnostic functions have been built into the IC to simplify the drive development process. Software and hardware tools are available to support the integration of this IC into the drive system.

#### 1.1.1 Conventions

When describing bit locations in registers or words, the LSB is bit 0 and MSB is bit N, where N is the leftmost or most-significant bit. Positive logic prevails in bit state descriptions. Setting a bit, bit N=1, and a bit is a high level are all equivalent statements. Unless noted, performance specifications are valid for a supply voltage of 5.0 V + 10%.

#### **1.2 Features**

#### **1.2.1 General Features**

- 3.0 V to 5.5 V Operation

- Small Package Size (128 pin TQFP and MQFP available)

- Optimized Architecture for Disk Drive Motion Control

- High performance allows for the elimination of a host processor

#### 1.2.2 DSP Core

- 40 ns Cycle Time at 5 Volts

- 16-bit Fixed Point DSP

- 16x16-bit 2's Complement Parallel Multiplier with 32-bit Product

- Single Cycle Multiply and Accumulate

- 36-bit ALU with Two 36-bit Accumulators

#### 1.2.3 Host interface

- Interrupt driven, Bidirectional three wire, Synchronous serial interface

- Configurable as a Master

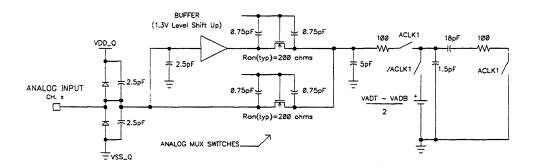

#### 1.2.4 Data Acquisition

- 10-bit, 2's Complement, 2-Step Flash A/D converter

- 8 Channels of Analog Data Input, 6 channels external

- 1.1 us Total Mux. and Conversion Time per Channel (Pipeline Mode)

- Dedicated Data Acquisition Sequencer

- Pipelined and Single Channel Conversion Modes

- ALU Register Mapped Data Storage

- Supports Auto-Zeroing Input Processing

- Flexible Input Voltage Ranges Independent of the DAC Output Voltage Ranges

#### 1.2.5 Servo Decoder/Sequencer

- Programmable Servo Burst Sequencer

- Programmable Servo Timing Mark Sequencer

- Flexible Gating and Control Generation

- User Programmable Control Output Pins

- Allows Servo Format Flexibility

- Programmable Read Channel Interface

- Split Data Sector Support

- Separate clock input available

#### 1.2.6 VCM Control

• 12-bit 2's Complement Voltage Output DAC

#### **1.2.7 Spindle Control**

- 8-bit Voltage Output DAC

- Digital Speed Control (FLL support)

#### **1.2.8 Power Management**

- Power Control Register

- Selectable on a Functional Block Basis

#### **1.2.9 Diagnostic Features**

- Real Time Data Output Port for Development and Diagnostics

- RS-232 Port for Diagnostic Terminal

#### **1.2.10** Flexible Drive Management Functions

- General-purpose I/O pins

- Two PWM outputs. (GPIOs)

- Drive Fault Signal Generation

٠

Programmable Arm Electronics Safety Input

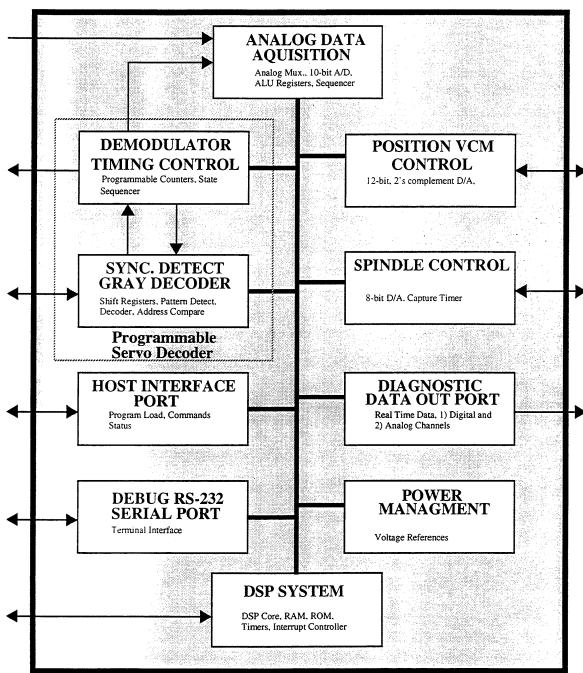

Figure 1-1 Overall Block Diagram

AIC-4421 Data Sheet

4

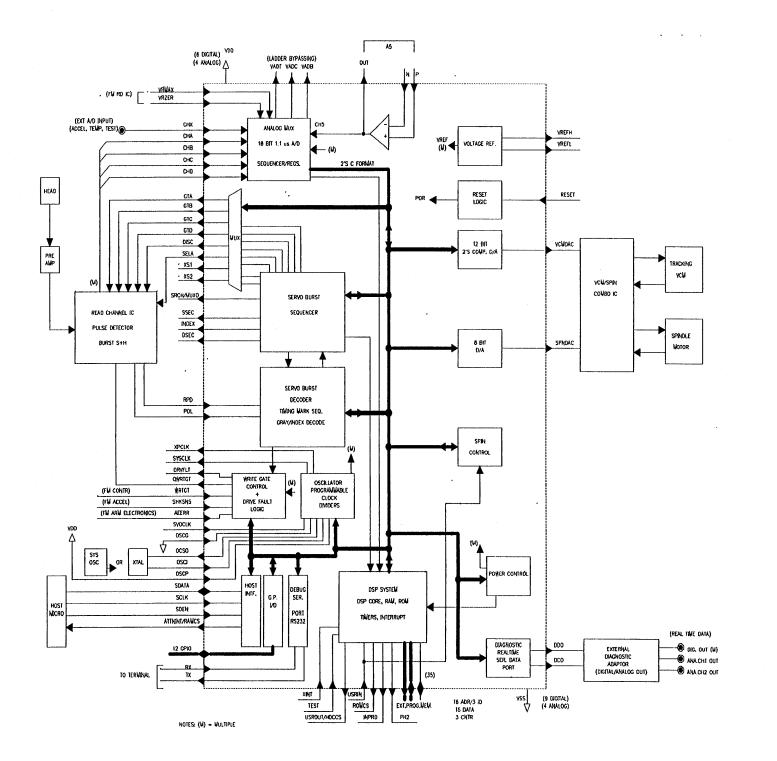

Figure 1-2 shows the block diagram of a typical application.

Overview

Section 1

## 2.1 Pin Descriptions

,

## 2.1.1 Power and System

## Table 2-1 Power and System Pin Descriptions

| Pin #<br>TQFP                                          | Туре            | Name   | Description                                                                                                               |

|--------------------------------------------------------|-----------------|--------|---------------------------------------------------------------------------------------------------------------------------|

| 10, 65,<br>80, 93,<br>94,<br>100,<br>118               | PWR             | VDD_D  | Digital Positive Power Supply.                                                                                            |

| 11, 23<br>64, 79,<br>86, 87,<br>96, 99,<br>112,<br>127 | PWR             | VSS_D  | Digital Power Supply Return. Pin 112 is the substrate connection.                                                         |

| 48                                                     | PWR             | VDD_A  | Analog Positive Power Supply for Amplifiers and D/A converters.                                                           |

| 51                                                     | PWR             | VSS_A  | Analog Power Return for Amplifiers and D/A converters.                                                                    |

| 44                                                     | PWR             | VDD_M  | Analog Positive Power Supply for Voltage reference.                                                                       |

| 43                                                     | PWR             | VSS_M  | Analog Power Supply Return for Voltage reference.                                                                         |

| 27,<br>39                                              | PWR             | VDD_Q  | Analog Positive Power Supply for A/D converter and Multiplexer.                                                           |

| 26,<br>38                                              | PWR             | VSS_Q  | Analog Power Supply Return for A/D converter and Multiplexer.                                                             |

| 95                                                     | IN <sup>2</sup> | XIN    | XTAL Connection 1 to internal system oscillator. Input for clock from external system oscillator. (SYSCLK).               |

| 97                                                     | OUT             | XOUT   | XTAL Connection 2 to internal system oscillator. Leave discon-<br>nected when supplying an external clock to the XIN pin. |

| 98                                                     | OUT             | SYSCLK | System Clock. This output is a buffered clock signal from the XTAL Oscillator or the external clock to the XIN pin.       |

| 70                                                     | IN <sup>2</sup> | SVOCLK | Servo Clock Input. This clock input may be used by the Servo Decoder/Sequencer instead of SYSCLK.                         |

| Pin #<br>TQFP | Туре                   | Name   | Description                                                                               |

|---------------|------------------------|--------|-------------------------------------------------------------------------------------------|

| 92            | OUT                    | XPCLK  | External Programmable Clock out.                                                          |

| 77            | IN <sup>2</sup><br>low | *RESET | External Reset Input. Schmitt Trigger Input.                                              |

| 46            | OUT<br>analog          | VREFL  | Buffered voltage reference output. Typically used as center of A/D and D/A ranges.        |

| 45            | OUT<br>analog          | VREFH  | Buffered voltage reference output. Typically used as maximum positive A/D and D/A ranges. |

| Table 2-1 | Power and | System | Pin Desc | riptions ( | (Continued) |

|-----------|-----------|--------|----------|------------|-------------|

|-----------|-----------|--------|----------|------------|-------------|

Note: See notes on page 13.

×

## 2.1.2 Analog Data Acquisition

| Table 2-2 Analog Data Acquisition Pin Description |

|---------------------------------------------------|

|---------------------------------------------------|

| Pin #<br>TQFP | Туре          | Name  | Description                                                                                                                                                      |

|---------------|---------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 42            | IN<br>analog  | VRZER | Voltage Zero Reference. Sets the center of voltage swing for the A/D system when in external reference mode.                                                     |

| 41            | IN<br>analog  | VRMAX | Voltage Max Reference. Sets the peak voltage swing of the A/D system when in external reference mode.                                                            |

| 36            | OUT<br>analog | VADT  | Bypassing pin for the A/D converter's top of the reference ladder.<br>VADT voltage equals VREFH or VRMAX depending on the bits<br>in the (ADCCMD) register.      |

| 37            | OUT<br>analog | VADC  | Bypassing pin for the A/D converter's center of the reference lad-<br>der. VADC voltage equals VREFL or VRZER depending on the<br>bits in the (ADCCMD) register. |

| 40            | OUT<br>analog | VADB  | Bypassing pin for the A/D converter's bottom of the reference lad-<br>der. VADB voltage = (2*VADC)-VADT.                                                         |

| 28            | IN<br>analog  | CHA   | Channel A. Analog input channel to mux.                                                                                                                          |

| 29            | IN<br>analog  | СНВ   | Channel B. Analog input channel to mux.                                                                                                                          |

| 30            | IN<br>analog  | СНС   | Channel C. Analog input channel to mux.                                                                                                                          |

| 31            | IN<br>analog  | CHD   | Channel D. Analog input channel to mux.                                                                                                                          |

| 32            | IN<br>analog  | СНХ   | Channel X. Analog input channel to mux.                                                                                                                          |

| 35            | OUT<br>analog | A5OUT | Mux Channel 5 amplifier output and input to mux.                                                                                                                 |

| 34            | IN<br>analog  | A5N   | Inverting input of Channel 5 amplifier.                                                                                                                          |

| 33            | IN<br>analog  | A5P   | Non-inverting input of Channel 5 amplifier.                                                                                                                      |

7

## 2.1.3 DSP System

| Table 2-3 | DSP | System | Pin | Descriptions |

|-----------|-----|--------|-----|--------------|

|-----------|-----|--------|-----|--------------|

| Pin #<br>TQFP | Туре                    | Name             | Description                                                                                                                                                          |

|---------------|-------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 85            | IN <sup>2</sup><br>high | USRIN            | User defined input directly readable by the DSP or may be used by the spin control circuitry.                                                                        |

| 117           | OUT<br>high/<br>prog    | USROUT<br>/HDCCS | Output defined by the memory configuration register. (MEMCFG)<br>USROUT: User defined output directly controllable by the DSP.<br>HDCCS: The HDC Chip select output. |

Note: See notes on page 13.

## 2.1.4 Servo Decoder

## Table 2-4 Servo Decoder/Sequencer Pin Descriptions

| Pin #<br>TQFP | Туре                    | Name          | Description                                                                                                                                                                            |

|---------------|-------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 63            | IN <sup>2</sup><br>prog | RDP           | Read Pulse from the read channel IC pulse detector.                                                                                                                                    |

| 62            | IN <sup>2</sup><br>prog | POL           | Pulse Polarity signal from the read channel IC pulse detector.                                                                                                                         |

| 61            | OUT<br>prog             | GTA           | Gate signal to read channel IC.                                                                                                                                                        |

| 60            | OUT<br>prog             | GTB           | Gate signal to read channel IC.                                                                                                                                                        |

| 59            | OUT<br>prog             | GTC           | Gate signal to read channel IC.                                                                                                                                                        |

| 58            | OUT<br>prog             | GTD           | Gate signal to read channel IC.                                                                                                                                                        |

| 57            | OUT<br>prog             | DISC          | Discharge signal to read channel IC.                                                                                                                                                   |

| 56            | OUT<br>prog             | SELA          | Control signal to read channel IC. Typically used for AGC control.                                                                                                                     |

| 76            | OUT<br>prog             | XS1           | Extra gate signal from Servo Burst Sequencer. Could be used as a Beginning of Sector (BOS) Signal.                                                                                     |

| 75            | OUT<br>prog             | XS2           | Extra gate signal from Servo Burst Sequencer. Could be used as a End of Sector (EOS) Signal.                                                                                           |

| 72            | OUT<br>high             | INDEX         | Index Pulse.                                                                                                                                                                           |

| 73            | OUT<br>high             | DSEC          | Data Sector Pulse.                                                                                                                                                                     |

| 71            | OUT<br>high             | SSEC          | Servo Sector Pulse (Hard Sector).                                                                                                                                                      |

| 74            | OUT<br>high             | SRCH/<br>MUXO | Search Window signal. This pin may also be programmed to out-<br>put one of several Servo Decoder/Sequencer internal signals. (see<br>Decoder Control Register (DECCTL).               |

| 68            | IN<br>prog              | WRTGT         | Write Gate input from data path controller.                                                                                                                                            |

| 67            | OUT<br>prog             | QWRTGT        | Qualified Write Gate to write circuits.                                                                                                                                                |

| 55            | IN <sup>2</sup><br>prog | AEERR         | Arm Electronics Error input. This input is exclusive or inclusive<br>ORed (programmable) with QWRTGT to detect an AE error. This<br>is used by the Write Gate Qualification circuitry. |

| Pin #<br>TQFP | Туре                  | Name   | Description                                                                                                                               |

|---------------|-----------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 47            | IN<br>prog/<br>analog | SHKSNS | Shock sensor input pin to write gate qualification circuitry. Can be configured as an analog or digital input.                            |

| 78            | BIDIR<br>high         | DRVFLT | Drive Fault. This pin can be configured as a Drive Fault output or<br>an input to directly control the SELA pin. (see<br>DECCFG register) |

## Table 2-4 Servo Decoder/Sequencer Pin Descriptions (Continued)

Note: See notes on page 13.

## 2.1.5 Host Interface

| Table 2-5 | Host | Interface | Pin | Descriptions |

|-----------|------|-----------|-----|--------------|

|-----------|------|-----------|-----|--------------|

| Pin #<br>TQFP | Туре               | Name               | Description                                                                                                                                                                         |

|---------------|--------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 88            | BIDIR<br>high      | SDATA              | Serial Data.                                                                                                                                                                        |

| 89            | BIDIR<br>high/prog | SCLK               | Serial Clock In/Out. Output when in Master Mode.                                                                                                                                    |

| 81            | BIDIR<br>low/prog  | SDEN               | Serial Data Enable. Output when in Master Mode.                                                                                                                                     |