-----

## **About This Chapter**

Read this chapter to find out

- A general overview of the AIC-7870 host adapter chip

- Features of the AIC-7870 host adapter chip

- Reference documents applicable to the AIC-7870 host adapter chip

## \* \* \* \* \*

### Introduction

The AIC-7870 provides advanced host adapter features in a single chip with a SCSI-2 bus controller and a full featured PCI 32-bit bus master with zero wait state transfer capability including PCI enhanced data transfer commands. The AIC-7870 chip incorporates a dedicated processor, the SCSI PhaseEngine<sup>™</sup> (RISC Sequencer), which executes a SCSI command described by a Sequencer Control Block (SCB). Sixteen SCBs may be stored in the internal SCB Array and with the addition of an external SRAM, a maximum of 256 SCBs may be stored for execution. These SCBs are executed independently of the SCSI target ID in the order that they are received. The SCB is a data structure which contains all information necessary for the execution of the command. The sequencer in the chip handles all phases of the SCSI bus, including the Disconnect/ Reconnect and Command Complete message. On the PCI host side, bus master transfers are made in a 64-bit address space at up to the maximum burst rate of 133 MBytes/ sec with data buffering of 256 bytes.

The AIC-7870 also provides a memory port for external access, an 8-bit ROM/EEPROM (for add-in card local BIOS support), a serial 1-bit EEPROM (for nonvolatile SCSI bus device and parameter storage, and/or adapter board assembly/serial/revision information), an 8/9-bit SRAM (for SCB expansion), and external board logic control.

### Feature Summary

- Automatic data threshold selection

- Power-down modes

- Scatter/Gather operations supported

- Extremely low SCSI command overhead

- Data residue reported on underruns

- One interrupt per command completion, multiple command completions may be queued on a single interrupt

- Queued commands per Target/LUN

- Overlapped command execution

- Modify Data Pointers message handled

- Tagged Queuing supported

- SCSI Configured AutoMagically (SCAM level 1 support)

- Data path from PCI bus to SCSI bus internally byte parity protected

- Hardware address breakpoint capability for software debug

- External BIOS ROM option with in-place BIOS update (EEPROM) capability

- Serial SEEPROM read/write option for saving SCSI bus device and adapter board parameters

1-3

- External SRAM (8/9-bit/parity) option for SCB expansion

- Memory Port Arbitration option including a lock feature for sharing external BIOS, SRAM and SEEPROM

- Device ID option for exchanging internal default value with an external value

- External Board Control option for controlling host adapter logic external to the AIC-7870 from the PCI bus

#### **SCSI Features**

- Fast (10 MHz) data transfers

- Wide data transfers

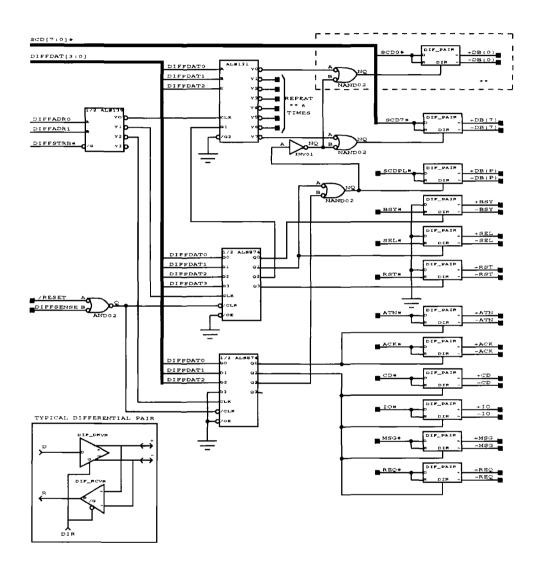

- Differential controls

- Flexible configuration

- One 8-bit Single-ended, Fast

- One 8-bit Differential, Fast

- One 16-bit Single-ended, Fast

- One 16-bit Differential, Fast

- Auto SCSI bus PIO

- Wide data connector indicator

- LED indicator control (SCSI busy, diagnostics, external ID clock) or general purpose control

- Selectable SCSI output active negation

- SCSI termination power down control or general purpose control

- SCAM level 1 support

- Digital filtering for incoming REQ and ACK signals

#### PCI 32-bit Interface

- Direct pin out connection to PCI 32-bit bus interface

- PCI bus master with zero wait state 32-bit memory data transfers at 133 MBytes/sec, capable of leading and trailing 32-bit boundary offset bytes, with a 32-bit address range within a selected 64-bit address page

- Supports both PCI single and dual address cycles

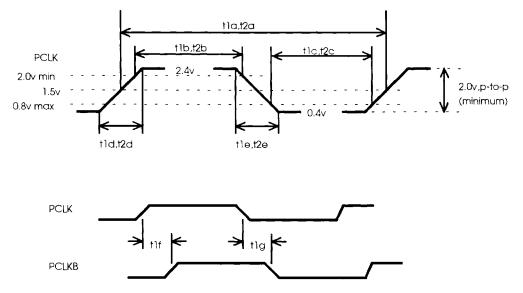

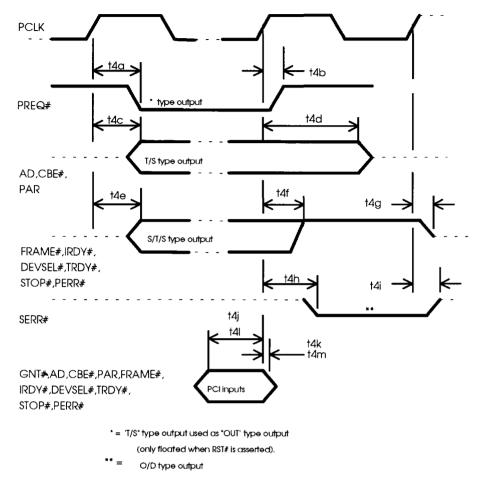

- PCI bus master/slave timing referenced to PCI signal PCLK (33.3 MHz max)

- Buffered PCI signal PCLK output for adapter card logic usage

- PCI bus master programmable Latency Timer, Cache Size, and Interrupt Line Select registers

- PCI bus access of AIC-7870 device registers from both PCI I/O and memory address spaces

- Supports exchange of internal device ID default value with an external value

- Supports medium PCI target device-select response time

- Supports enhanced PCI system memory data Read and Write commands

- Cache line streaming capability

- Supports PCI bus address and data parity generation and checking

- Supports PCI PERR and SERR requirements

- Supports 32-bit external ROM read access

- Data transfers may be selected to be initiated by CACHESIZE or data level thresholds

- Data FIFO data flush for transfers to system memory

- IRQA# interrupt generation from hardware, firmware and software controlled sources

- Supports reduced power requirements when not performing master data transfers

#### **Data Buffer**

- Data FIFO provides 256 bytes of storage, dual-ported RAM, with parity per byte

- Programmable data and cache size threshold levels to initiate PCI bus master requests

- Early FIFO full status

- Multi byte-width data ports: 8 (PCI), 2 (SCSI), 1 (sequencer or driver) byte with byte parity

- Byte write parity generation and byte read parity checking

- Read/write capable address counters

- Partial quad-word detection and adjustment

- Starting address byte offset capable

#### Scratch RAM

- 64 bytes of dual-ported SRAM, accessible by sequencer and host drivers

- Byte parity protected

#### Sequencer (SCSI PhaseEngine)

- RISC instruction per clock design

- Clock rate selectable for 8 or 10 MHz operation

- SRAM microcode storage, 512 29-bit words plus byte parity

- Sixteen instruction group types

- Operation may be paused by maskable interrupt condition or software driver

- Diagnostic single-step and address breakpoint

- SLEEP mode for chip power reduction

#### **SCB Array**

- Internal SCB array for storage of sixteen SCBs.

- SCB array expandable to 256 SCBs with external SRAM

- SCBPTR register for SCB page (32-bytes) selection

- SCBCNT register for auto SCB address increment

- SCB write supports 32-bit burst transfers

- Queue In FIFO (selectable entry depths of 16 or 255 with stored count status)

- Queue In CNT (selectable entry depths of 16 or 255 with stored count status)

- SCB, Queue In and Queue Out are byte parity protected

#### **Memory Port**

- Read only, write only, or read-modify-write for sequencer instruction access of SRAM/SEEPROM/external logic

- Read only or write only for software driver PCI access of SRAM/ROM/ EEPROM/SEEPROM/external logic

- Single ported 8 or 9-bit SRAM (20 nsec access) with direct connection for 8 KBytes

- Single ported 8-bit ROM/EEPROM (150 nsec access) with direct connection for 64 KBytes

- External SRAM presence buffered PCLK pin

- Serial SEEPROM with register based access with hardware timer support

- Multidevice arbitration (two wire) for sharing memory port connected devices

- SRAM, ROM, EEPROM three line interface for read/write control

- SEEPROM four line interface

- External logic six line interface

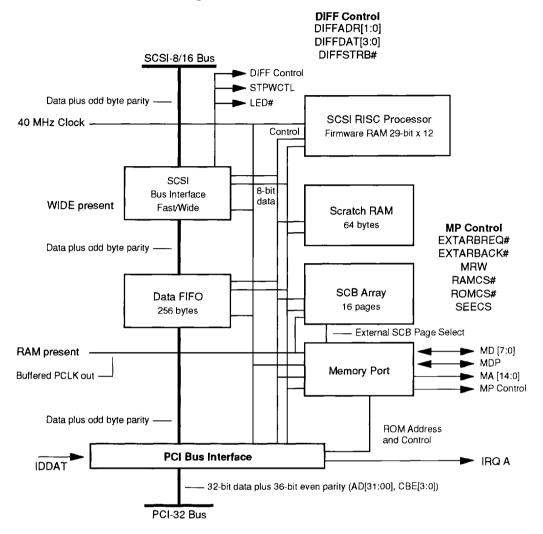

### AIC-7870 Block Diagram

Figure 1-1. AIC-7870 Block Diagram

### **Reference Documents**

Reference is made in this specification to the following additional documents:

Peripheral Component Interconnect (PCI) Local Bus Interface Specification, Rev. 2.0

------

- AIC-7770 Specification 707001, Adaptec Inc.

- SCSI-2 Specification ANSI Standard # X3T9.2 Rev 10h

## **About This Chapter**

Read this chapter to find out

- The PCI Master Bus Cycles

- The PCI Slave Bus Cycles

## ••••• 10

### **PCI Master Bus Cycles**

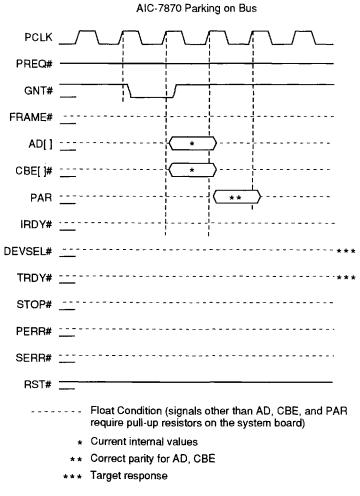

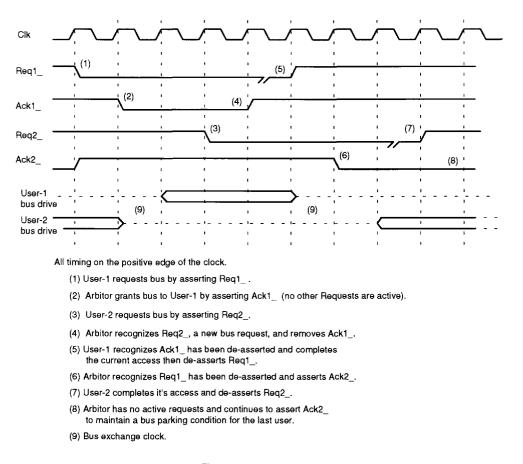

Figure 10-1. Master Parking on Bus

\* AIC-7870 target response

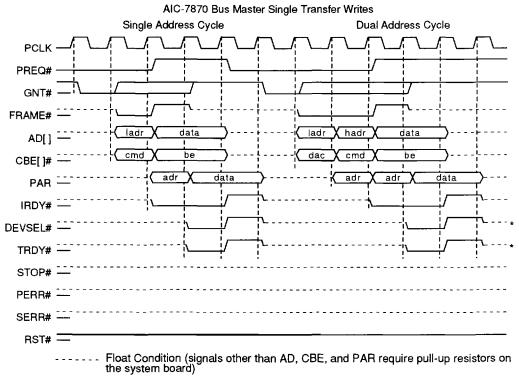

Figure 10-2. Master Single Transfer Write

\* AIC-7870 target response

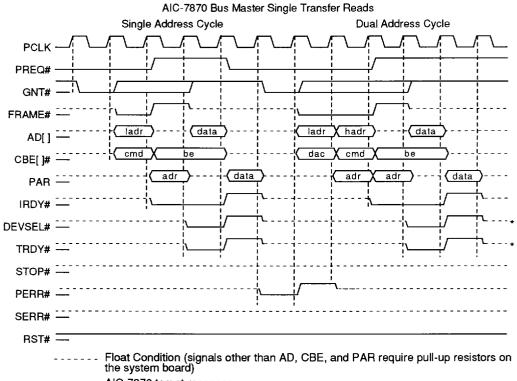

Figure 10-3. Master Single Transfer Read

The AIC-7870 is capable of cache line streaming, with no wait states, however the target disconnects at end of cache line

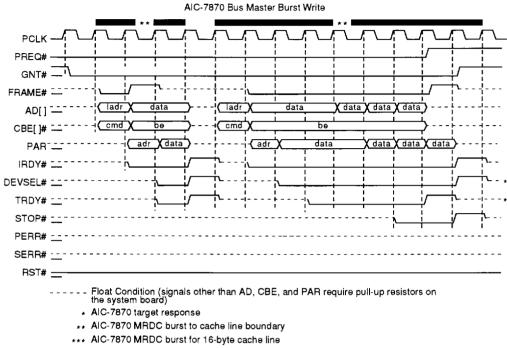

Figure 10-4. Master Burst Transfer Write

The AIC-7870 is capable of cache line streaming, with no wait states, however the target disconnects at end of cache line

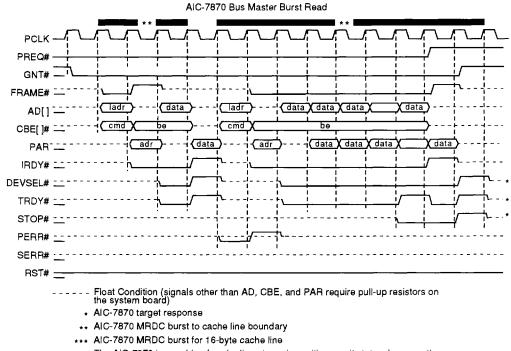

Figure 10-5. Master Burst Transfer Read

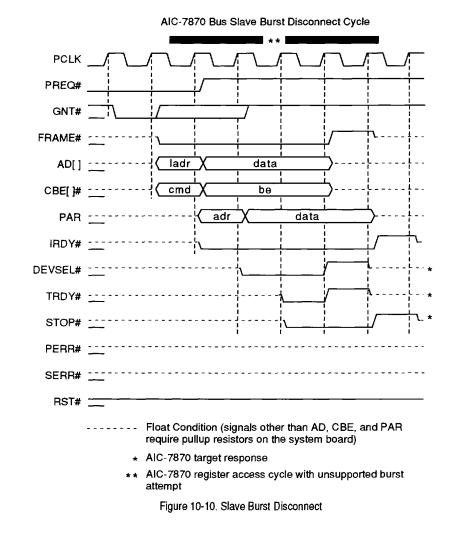

## **PCI Slave Bus Cycles**

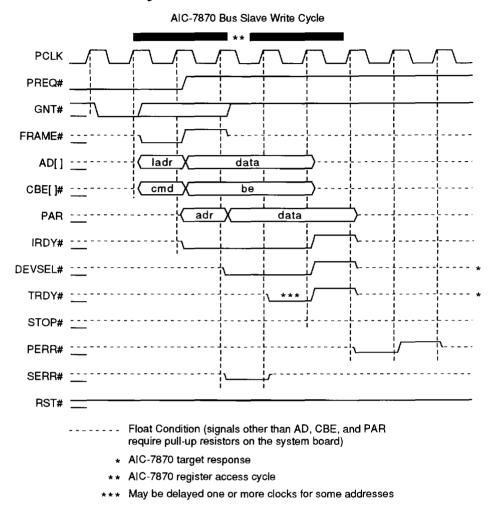

Figure 10-6. Slave Single Transfer Write

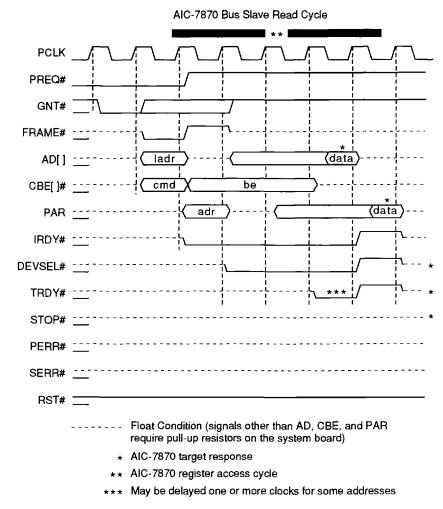

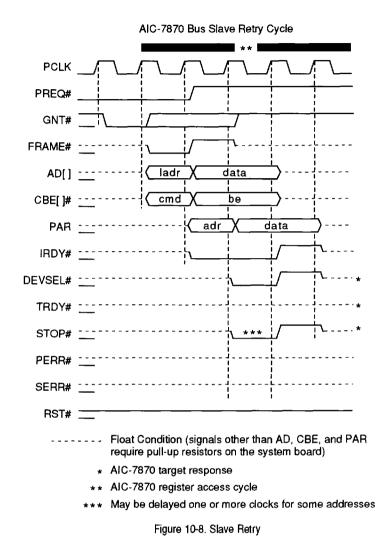

Figure 10-7. Slave Single Transfer Read

10-10

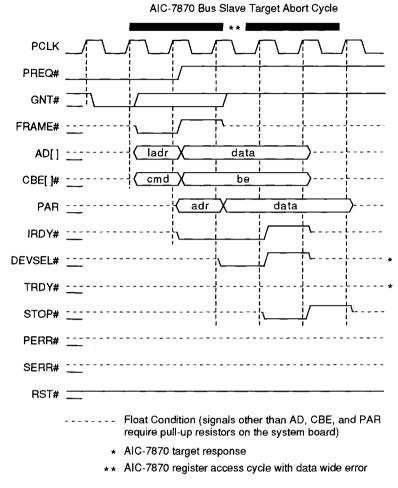

Figure 10-9. Slave Target Abort (width error)

## **About This Chapter**

Read this chapter to find out

• The timing of the differential cycles

# •••• 11

## **Differential Cycles**

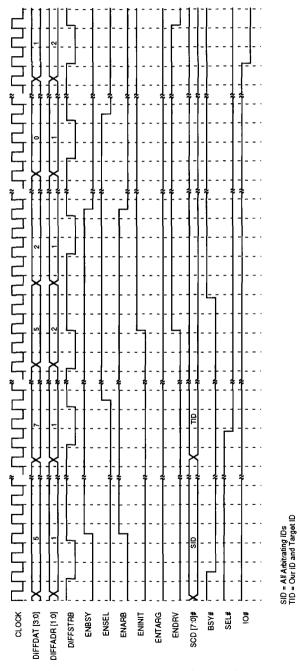

**SCSI Initiator Arbitration Selection**

Figure 11-1. SCSI Initiator Arbitration Selection

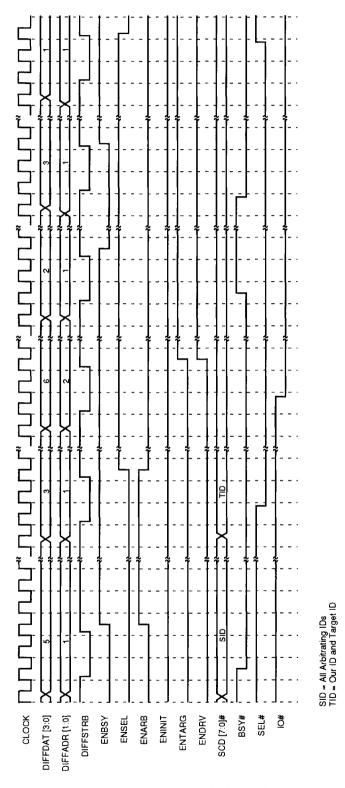

### **SCSI Target Arbitration Reselection**

Figure 11-2. SCSI Target Arbitration Reselection

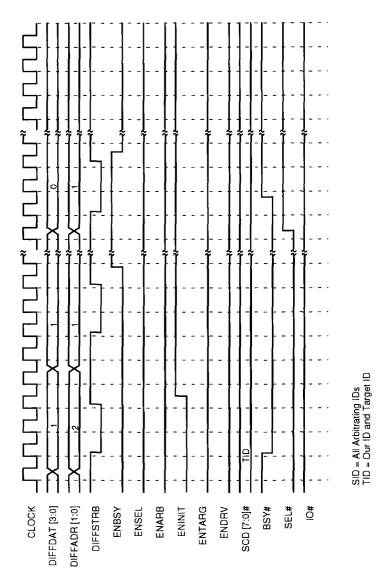

### **SCSI Initiator Reselection**

Figure 11-3. SCSI Initiator Reselection

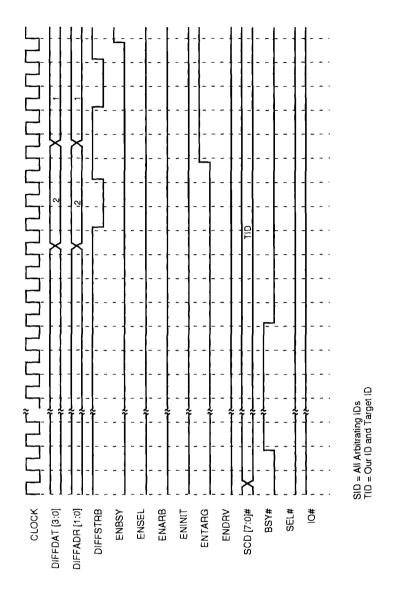

### **SCSI Target Selection**

Figure 11-4. SCSI Target Selection

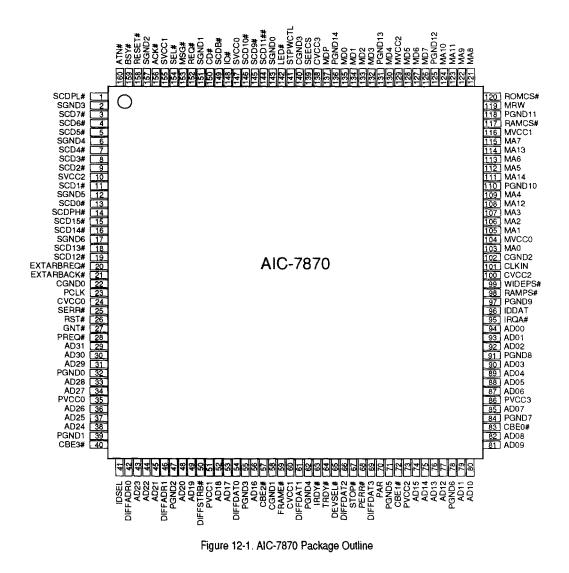

## **About This Chapter**

Read this chapter to find out

• A package outline of the AIC-7870

## ••••• 12

### AIC-7870 Package Outline

-----

12-3

### **About This Chapter**

Read this chapter to find out

- A summary of the pin pad type and signal assignment

- A detailed description of the supported PCI-32 pin and Memory Port pin signals

## ••••• 2

## **Pin Pad Type and Signal Assignment Summary**

The pins are summarized here, listing the name, pin number, if the pin is an input, and the type and drive of the outputs. The type definitions are listed in Table 2-1. A more complete description follows the summary.

| Туре  | Definition                                                |  |

|-------|-----------------------------------------------------------|--|

| l     | Input                                                     |  |

| 3ST/# | Tri-state Output/Min Drive Current in mA                  |  |

| OD/#  | Open Drain Output/Min Drive Current in mA                 |  |

| NOD/# | Negation Capable Open Drain Output/Min Sink Current in mA |  |

Table 2-1. Pin Type Definitions

### Host Interface

| Signal Name | Pin Number                                                                            | I/O Driver PCI<br>Master | I/O Driver PCI<br>Target | Notes |

|-------------|---------------------------------------------------------------------------------------|--------------------------|--------------------------|-------|

| AD[31:00]   | 29-31, 33, 34, 36-38, 43-45, 48,<br>49, 52, 53, 56, 74-77, 79-82, 85,<br>87-90, 92-94 | I, 3ST/6                 | I, 3ST/6                 |       |

| CBE[3:0]#   | 40, 57, 72, 83                                                                        | 3ST/6                    | 1                        |       |

| DEVSEL#     | 65                                                                                    | 1                        | 3ST/6                    | 1     |

| FRAME#      | 59                                                                                    | 3ST/6                    | I                        | 1     |

| GNT#        | 27                                                                                    | ł                        | NA                       |       |

| IDSEL       | 41                                                                                    | NA                       | I                        |       |

| IRDY#       | 63                                                                                    | 3ST/6                    | I                        | 1     |

| PAR         | 70                                                                                    | I, 3ST6                  | I, 3ST6                  |       |

| PCLK        | 23                                                                                    | I                        | l                        |       |

| PREQ#       | 28                                                                                    | 3ST/6                    | NA                       |       |

| PERR#       | 68                                                                                    | I, 3ST/6                 | I, 3ST/6                 | 1     |

| RST#        | 26                                                                                    | 1                        | 1                        |       |

| SERR#       | 25                                                                                    | NA                       | OD/6                     | 1     |

| STOP#       | 67                                                                                    | 1                        | 3ST/6                    | 1     |

| TRDY#       | 64                                                                                    | I                        | 3ST/6                    | 1     |

| IRQA#       | 95                                                                                    | 3ST/4                    | 3ST/4                    | 1     |

Table 2-2. Host Interface

<sup>1</sup> Signal requires external pull-up resistors.

### **SCSI Interface**

| Signal Name  | Pin Number                         | VO Driver | Notes |

|--------------|------------------------------------|-----------|-------|

| SCD15#-SCD8# | 15, 16, 18, 19, 144, 146, 145, 149 | I, NOD/48 | 1, 2  |

| SCD7#-SCD0#  | 3-5, 7-9, 11, 13                   | I, NOD/48 | 2     |

| SCDPH#       | 14                                 | I, NOD/48 | 1,2   |

| SCDPL#       | 1                                  | I, NOD/48 | 2     |

| CD#          | 150                                | 1, NOD/48 | 2     |

| 10#          | 148                                | I, NOD/48 | 2     |

| MSG#         | 153                                | I, NOD/48 | 2     |

| REQ#         | 152                                | I, NOD/48 | 2     |

| ACK#         | 156                                | I, NOD/48 | 2     |

| RESET#       | 158                                | I, OD/48  |       |

| SEL#         | 154                                | I, OD/48  |       |

| BSY#         | 159                                | I, OD/48  |       |

| ATN#         | 160                                | I, NOD/48 | 2     |

| DIFFDAT(3:0) | 69, 66, 61, 54                     | 3ST/4     |       |

| DIFFADR(1:0) | 46, 42                             | 3ST/4     |       |

| DIFFSTRB#    | 50                                 | 3ST/4     | 3     |

| LED#         | 142                                | 3ST/24    |       |

| STPWCTL      | 141                                | 3ST/4     |       |

| WIDEPS#      | 99                                 | 1         | 3     |

Table 2-3, SCSI Interface

<sup>1</sup> Pad output floats and input is disabled for 8-bit SCSI transfers.

<sup>2</sup> Pad supports active negation.

<sup>3</sup> Pad contains an internal pull-up.

### **Memory Port Interface**

| Signal Name | Pin Number                                                                   | VO Driver | Notes   |

|-------------|------------------------------------------------------------------------------|-----------|---------|

| EXTARBACK#  | 21                                                                           | 1         | 1       |

| EXTARBREQ#  | 20                                                                           | 3ST/8     |         |

| MA[14:0]    | 111, 114, 108, 123, 124, 122, 121, 115,<br>113, 112, 109, 107, 106, 105, 103 | 3ST/8     |         |

| MD[7:0]     | 126-128, 130, 132-135                                                        | l, 3ST/8  | 1, 2    |

| MDP         | 137                                                                          | I, 3ST/8  | 2, 3, 4 |

| MRW         | 119                                                                          | 3ST/24    |         |

| RAMCS#      | 117                                                                          | 3ST/24    | 5       |

| ROMCS#      | 120                                                                          | 3ST/4     | 5       |

| SEECS       | 139                                                                          | 3ST/4     | 5       |

#### Table 2-4. Memory Port Interface

<sup>1</sup> Pad contains an internal pull-up. Pad must be grounded for stand-alone mode.

<sup>2</sup> Pad for stand-alone mode when in idle state is driven for self termination. Note, for BRDCTL/SEECTL register use, or when no ROM/ EEPROM and for multiuser mode, external pull-up resistors are required to prevent float condition on inputs.

<sup>3</sup> Pad(s) is/are multifunction.

<sup>4</sup> Pad always requires a pull-up resistor when 9-bit SRAM is not used.

<sup>5</sup> External resistors required to prevent external logic float condition.

#### **Other Pins**

Table 2-5. Other Pins

| Signal Name | Pin Number | I/O Driver | Notes |

|-------------|------------|------------|-------|

| CLKIN       | 101        | l          |       |

| IDDAT       | 96         | ł          | 1     |

| RAMPS#      | 98         | I, 3ST/4   | 2, 3  |

<sup>1</sup> Pad contains an internal pull-up

<sup>2</sup> Pad for stand-alone mode when in idle state is driven for self termination. Note, for BRDCTL/SEECTL register use, or when no ROM/ EEPROM and for multiuser mode, external pull-up resistors are required to prevent float condition on inputs.

<sup>3</sup> Pad always requires a pull-up resistor when 9-bit SRAM is not used.

#### **Power Distribution Pins**

| Table | 2-6. | Power | Distribution | Pins |

|-------|------|-------|--------------|------|

|-------|------|-------|--------------|------|

| Signal Name | Pin Number                                                         | I/O Driver | Notes |

|-------------|--------------------------------------------------------------------|------------|-------|

| CVCC(3:0)   | 138, 100, 60, 24                                                   |            |       |

| CGND(3:0)   | 140, 102, 58, 22                                                   |            |       |

| SVCC(2:0)   | 10, 155, 147                                                       |            |       |

| SGND(6:0)   | 17, 12, 6, 2, 157, 151, 143                                        |            |       |

| PVCC(3:0)   | 86, 73, 51, 35                                                     |            |       |

| PGND(14:0)  | 136, 131, 125, 118, 110, 97, 91, 84, 78,<br>71, 62, 55, 47, 39, 32 |            |       |

| MVCC(2:0)   | 129, 116, 104                                                      |            |       |

CVCC = Core Logic Power Pin CGND = Core Logic Ground Pin SVCC = SCSI Pad Ring Power Pin SGND = SCSI Pad Ring Ground Pin PVCC = PCI Pad Ring Power Pin PGND = PCI Pad Ring Ground Pin MVCC = Memory Port Pad Ring Power Pin Note: The different ()VCC and ()GND pin strings are not internally connected

-----

### **Pin Signal Description**

The logical state of a signal name that does not end in a # symbol is asserted or active when high and is deasserted or inactive when low. The logical state of a signal name that ends in a # symbol is asserted or active when low and is deasserted or inactive when high.

#### Supported PCI-32 Pin Signals

Symbol: AD[31:00] Type: in-t/s

Address and data are multiplexed on the same PCI bus pin. During the first clock of a transaction AD[31:00] contain a physical byte address of (32-bits) called low address 31:00 for Single Address Cycles (SAC). During subsequent clocks, AD[31:00] contain data of (32-bits) called low data 31:00, except for Dual Address Cycles (DAC) where both the first (low address 31:00) and second (high address 63:32) clocks of a transaction contain address and the remaining clocks contain data (low data 31:00). The turn-around PCLK period for AD[31:00] is the idle cycle between transactions.

A PCI read or write bus transaction consist of one Address phase (SAC) or two Address phases (DAC) followed by one or more Data phases. Each PCI Data phase may consist of one or more PCLK periods. Little-endian byte ordering is used. AD[07:00] define the least significant byte and AD[31:24] the most significant byte. All 32 AD[31:00] bits must be driven to stable values (excluding turn around PCLK periods) during every Address and Data phase, to enable even-parity checking. All AD[31:00] bits must be decoded for memory and I/O phases to allow for future address expansion.

The use of AD[01:00] varies in the Address phase of the three different PCI address spaces:

■ In the PCI Configuration address space, AD[01:00] are used to identify the type of configuration space the access is intended for. AD[01:00] are a value of 0h to identify the configuration space as type 0 and a value of 1h for type 1, with values of 2h and 3h reserved. Type 0 configuration accesses are not propagated beyond the local PCI bus and must be claimed by a local device or terminated with master-abort. Type 1 configuration accesses are for targets that do not reside on the local PCI bus. For type 0, AD[07:02] define a 32-bit register address within the configuration address space. Thus, configuration address space defaults to Double Word (DWD) addressing aligned to the DWD boundary. Targets with multiple functions must contain a configuration space for each function. The value supplied on AD[10:08] is used to point to each space. The AIC-7870, as a single function target supporting type 0 address space, accesses with a single configuration space. The AIC-7870 as a target, uses positive address decoding over AD[07:02] along with CBE[3:0]# (command is CRDC or CWRC), IDSEL, AD[01:00] = 0h and FRAME# to validate the configuration register address decode, then asserts DEVSEL# to claim the transaction. IDSEL is normally connected to an ADn signal in the range of AD[31:11] of the PCI bus.

| AIC-7870 Configuration Space Address Format |                 |                 |                          |  |  |

|---------------------------------------------|-----------------|-----------------|--------------------------|--|--|

| Reserved for IDSEL<br>(single-bit)          | Function Number | Register Number | Configuration Space Type |  |  |

| AD[31:11]                                   | AD[10:08]       | AD[07:02)       | AD[01:00]                |  |  |

In the IO address space, all 32 AD lines are used to provide for direct byte address decoding. The AIC-7870 as a target uses positive address decoding over BASEADR0 register (stored value), AD[31:08] (for mapping), CBE[3:0]# (for command), AD[07:00] (for register address) and FRAME# to validate the Device Space register 256 decodes.

When the AIC-7870 as a target is enabled to allow access to its Device Space registers from the PCI IO address space, the use of AD[01:00] during the Address phase allows the AIC-7870 to validate the register address decode and claim the transaction (assert DEVSEL# = medium speed). TRDY# is deasserted for the first Data phase to allow the Data phase CBE value to become valid for byte steering to the internal 8-bit register path for a three PCLK data transfer cycle for register write. For register read, TRDY# is deasserted for the required AD[31:00] turnaround cycle, plus an additional PCLK for H/W registers, plus one or more to enable internal or external RAM data to become valid. Note, additional PCLKs are required for some addresses due to mode conditions.

In the PCl memory address space, AD[01:00] are excluded from the address decode and as such, the address defaults to Double Word (DWD) addressing aligned to the DWD boundary. The value AD[01:00] are used in the memory address space to indicate different Memory Address Transfer modes. A value of 0h indicates linear address increment mode, a value of 1h indicates Address Cache Line Toggle mode, and the values of 2h and 3h are reserved. The AIC-7870 as a master or target only supports the linear address increment mode.

When the AIC-7870 as a target is enabled to allow access to its Device Space registers from the PCI memory address space, it will use positive address decoding over BASEADR1 register (stored value), AD[31:02], CBE[3:0]# (command) and FRAME# to obtain the DWD access decode and claim the transaction by asserting (DEVSEL# = medium speed). Then use the CBE[3:0]# (data) value to complete the Device Space register decode. TRDY# is deasserted for the first Data phase to allow the Data phase CBE value to become valid for byte steering to the internal 8-bit register path for a three PCLK data transfer cycle for register write. For register read TRDY# is deasserted for the required AD[31:00] turn-around cycle, plus an additional PCLK for H/W registers, plus one or more to enable internal or external RAM data to become valid. Note, additional PCLKs are required for some addresses due to mode conditions.

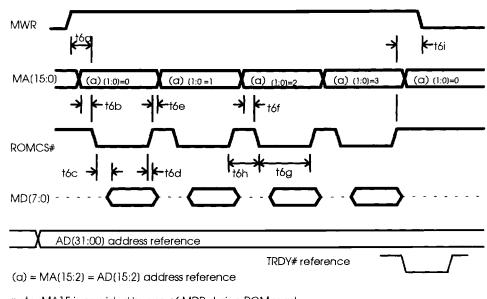

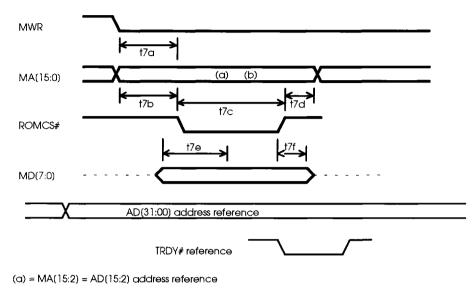

When the AIC-7870 as a target is enabled to allow access to the expansion ROM address space through the AIC-7870 memory port to a local 8-bit ROM/ EEPROM, the AIC-7870 will use positive address decoding over EXROMCTL register (stored value), AD[31:02], CBE[3:0]# (command) and FRAME# to obtain the DWD access decode and claim the transaction by asserting (DEVSEL# = medium speed).

For Memory Read commands, the AIC-7870 will perform a burst of four read accesses of the external ROM/EEPROM with MDP (MA15 equal to AD15, MA[14:2] equal to AD[14:02] and MA[1:0]) incrementing with values of 0, 1, 2, 3 to assemble a 32-bit value for the PCI Read command, regardless of the CBE[3:0]# value for the requested data. TRDY# is deasserted for additional PCLKs for the required AD[31:00] turn-around cycle and to enable the external ROM (150 nsec per cycle) data to become valid, and will be asserted when the 32-bits are valid.

For Memory Write commands, the AIC-7870 will write only the byte associated with the single asserted CBE[3:0]# to the external EEPROM. When no CBE[3:0]#

are asserted, the write will be treated as an NOP. TRDY# will be deasserted for the external EEPROM write cycle access time (150 nsec) then will be asserted to terminate the PCI write access.

**Note:** The ROM/EEPROM type and its connection to the AIC-7870 should be such that inadvertent writing when the type is ROM will not allow contention of the memory data bus.

For both Read or Write commands, access will be extended with TRDY# deasserted when an Automatic Access Pause (see HCNTRL register) is required, and/or until EXTARBACK# becomes active.

When a PCI burst is indicated it will be disconnected after the first Data phase.

The use of AD[31:00] varies in the Data phase of transactions as follows when the AIC-7870 is a bus master or a bus target:

- Bus target Data phase transactions to the AIC-7870's 8-bit Device Space registers will use the AD[31:00] byte indicated by a single asserted CBE# for all registers. Should more than one CBE# be asserted (indicates a nonsupported data width), the AIC-7870 will indicate Target Abort. When more than one Data phase is indicated (burst operation), the AIC-7870 will indicate Disconnect and only accept the first Data phase (except for SCB double word write, where bursting is allowed, with linear burst order only). When no CBE bits are asserted, the AIC-7870 will not store the associated data for (write) and will supply all AD[31:00] bytes with 0h value for (read).

- Bus target Data phase transactions to the AIC-7870's configuration space supports up to (32-bit) data transfers on AD[31:00] with the valid data bytes indicated with the CBE[3:0]# value for (write), for (read) the AIC-7870 will always source all bytes of the addressed register. Reading reserved configuration space register bytes/bits always return zero for the value. Data written to reserved configuration space register bits or bytes is discarded No error indication is made for reading or writing to reserved registers. When more than one Data phase is indicated (burst operation), the AIC-7870 will indicate Disconnect and only accept the first Data phase.

- The AIC-7870 as a master will always transfer leading offset data bytes, if they exist, to reach the next DWD boundary in the first Data phase of a transaction, providing the byte count is sufficient. Then four bytes will be transferred at a time from DWD boundary to DWD boundary until the last Data phase, which will transfer any trailing offset bytes that may exist, to expire the byte count.

Symbol: CBE[3:0]# Type: in-t/s

Bus Command and Byte Enables are multiplexed on the same PCI pins. During the Address phase of a transaction, CBE[3:0]# contain a Bus command that defines the function to be performed during the transaction. CBE[3:0]# command encodings are viewed on the bus where a 1 indicates a high voltage and 0 is a low voltage. During the Data phase of a transaction, CBE[3:0]# define which data bytes of AD[31:00] contain valid data. CBE0# applies to AD[07:00] and CBE3# to AD[31:24]. The AIC-7870 asserts CBE[3:0]# when in master mode to indicate the location of the first byte in a 32-bit boundary space and to match the data width being transferred. CBE[3:0]# are asserted (=0) by the system board or a bus master to access the AIC-7870 as a bus slave. No more than one CBE# may be asserted at a time for transactions to the AIC-7870's 8-bit Device registers without causing a Target Abort reply (except for SCB double word writes where bursting is allowed).

**Note:** Data phases that do not have at least one asserted CBEn# do not transfer data, however all data bytes must be stable so that parity may be developed, and appear as NOPs on the bus.

The turn-around PCLK period for CBE[3:0]# is the idle cycle between transactions. The commands assigned to CBE[3:0]# in the PCI specification are as follows:

|          |         |                             | AIC-7870 | ) Support |

|----------|---------|-----------------------------|----------|-----------|

| CBE[3:]# | Command | Туре                        | Target   | Master    |

| 0000     | IAC     | Interrupt Acknowledge       | No       | No        |

| 0001     | SSC     | Special Cycle               | No       | No        |

| 0010     | IORDC   | IO Read                     | Yes      | No        |

| 0011     | IOWRC   | IO Write                    | Yes      | No        |

| 0100     | RSVD    |                             | No       | No        |

| 0101     | RSVD    |                             | No       | No        |

| 0110     | MRDC    | Memory Read                 | Yes      | Yes       |

| 0111     | MWRC    | Memory Write                | Yes      | Yes       |

| 1000     | RSVD    |                             | No       | No        |

| 1001     | RSVD    |                             | No       | No        |

| 1010     | CRDC    | Configuration Read          | Yes      | No        |

| 1011     | CWRC    | Configuration Write         | Yes      | No        |

| 1100     | MRDMC   | Memory Read Multiple        | **       | Yes       |

| 1101     | DAC     | Dual Address Cycle          | No       | Yes       |

| 1110     | MRDLC   | Memory Read Line            | **       | Yes       |

| 1111     | MWRIC   | Memory Write and Invalidate | *        | Yes       |

**Address Phase**

\* Defaults to Memory Write

\*\* Defaults to Memory Read

| Data Phase |        |                     |

|------------|--------|---------------------|

| 00513-14   |        | ) Support<br>Master |

| CBE[3:]#   | Target | Master              |

| 1110       | acd    | m                   |

| 1101       | acd    | m                   |

| 1011       | acd    | m                   |

| 0111       | acd    | m                   |

| 1100       | ac     | m                   |

| 1001       | ac     | m                   |

| 0011       | ac     | m                   |

| 1000       | ac     | m                   |

| 0001       | ac     | m                   |

| 0000       | abc    | m                   |

| 1111       | n      | -                   |

The AIC-7870 CBE[3:0]# values used/accepted during a Data phase to indicate the valid data bytes are as follows:

a = External ROM/EEPROM read access

b = SCB doubleword write access

c = Configuration register 32-bit registers access

d = Device space 8-bit register or external EEPROM write access

m = System memory access (AIC-7870 outputs only listed CBE[3:0] values)

n = No data transfers (Note all AD[31:00] are driven for parity checking) with normal data phase timing

Symbol: DEVSEL#

Type: in-s/t/s

Device Select#. When asserted, indicates the driving device has decoded its address as the selected target of the current bus transaction. DEVSEL# once asserted cannot be deasserted until FRAME# is sampled deasserted, except for the target-abort case. Also DEVSEL# must be asserted for one or more PCLKs before a target-abort condition may be signaled. The AIC-7870 as a slave asserts DEVSEL# with medium speed timing when responding as a result of a valid and supported command directed to the AIC-7870's Configuration register space, and when enabled, to the Device register space, or to the external ROM. The AIC-7870 as a master, samples DEVSEL# when initiating a transaction to a selected target to determine if the target is capable of proceeding with the current transaction. In the case when DEVSEL# is not asserted by the selected target for six PCLKs (SAC) or seven PCLKs (DAC) after FRAME# is asserted, the AIC-7870 will perform a master-abort (on PCLK seven (SAC) or eight (DAC) deassert FRAME# on the next PCLK (if still asserted) and on the next PCLK deassert IRDY#). Alternately where FRAME# was deasserted after one PCLK (indicates only one Data phase in the transaction), the AIC-7870 will perform a master-abort (on PCLK seven (SAC) or eight (DAC) deassert IRDY#). The AIC-7870 will not retry transactions that resulted in a masterabort (no response from target) and will generate an interrupt to the driver with RMA status active. Intervention is required for the AIC-7870 to continue with bus master transactions. The turn-around PCLK period for DEVSEL# is the Address phase of a transaction. The AIC-7870 as a master never asserts DEVSEL#,

Symbol: FRAME# Type: in-s/t/s

**Frame#**. Asserted by the current master to indicate the duration of a bus transaction. The assertion of FRAME# identifies an Address phase of a transaction. The deassertion of FRAME# identifies the final data phase of the transaction (FRAME# cannot be deasserted while IRDY# is deasserted for the final data phase). An idle cycle (PCI bus free) occurs when both FRAME# and IRDY# are deasserted. The turn-around PCLK period for FRAME# is the idle cycle between transactions. See DEVSEL# for the AIC-7870 Master-Abort conditions. The AIC-7870 as a target never asserts FRAME#.

The AIC-7870 asserts FRAME# with the same PCLK that asserts an address value on AD[31:00] for SAC or DAC. When the transaction is a DAC, FRAME# remains asserted for the second PCLK Address phase and for all Data phases that follow, until the last data phase where FRAME# will be deasserted.

**Symbol:** GNT# **Type:** in

Grant#. Asserted indicates to a master that a bus transaction may be performed. This is a point-to-point signal with every master having its own GNT# signal. Only one GNT# may be asserted by the PCI System Board Central Resource Arbitrator at a time. The Arbitrator may deassert GNT# at any time (one PCLK period minimum assertion) and may also assert GNT# when the master is not asserting REQ# (park the bus) to require the master to drive bus signals AD[31:00], CBE[3:0]# (and PAR delayed by one PCLK) within eight PCLK (recommended value is by two to three PCLKs) to prevent bus float conditions. In the case where GNT# is deasserted and FRAME# is asserted on the same PCLK, the bus transaction is valid and will continue. One GNT# can be deasserted coincident with another GNT# being asserted if the bus is not idle. Otherwise a one PCLK delay is required between the deassertion of one GNT# and the assertion of the next GNT#. The newly granted master may not start a transaction until an IDLE cycle (FRAME# and IRDY# deasserted) is sampled. GNT# is held in a tri-stated condition while RST# is asserted. The AIC-7870 extends an asserted RST# internally and thus will not recognize GNT# in any state until after the extension expires. Except for the RST# condition, the AIC-7870 will drive AD[31:00] and CBE[3:0]# on the first PCLK, GNT# is sampled asserted with the PCI bus idle, then PAR one PCLK later. The AIC-7870 will also drive and assert FRAME# if PREQ# is asserted.

Symbol: IDSEL Type: in

**Initialization Device Select.** Used in lieu of the upper 24 ADn address signals and is valid only during configuration read and write transactions and is validated with FRAME# assertion and valid CBEn# values. IDSEL is a point-to-point signal with each agent having its own IDSEL. PCI convention is to connect a different AD[31:11] line to IDSEL input of each device on the bus, the AIC-7870 will respond to all accesses in its configuration address range.

Symbol:IRDY#Type:in-s/t/s

**Initiator Ready#**. Asserted to indicate the current master's ability to complete the current Data phase of a transaction. During a write, IRDY# indicates that the master is asserting valid data on AD[31:00]. During a read, it indicates the master is prepared to accept data on AD[31:00]. It is used in conjunction with TRDY#. Wait cycles are inserted until both IRDY# and TRDY# are asserted together. A Data phase is completed on any PCLK when IRDY# and TRDY# are both sampled asserted. An idle cycle (PCI bus free) occurs when both FRAME# and IRDY# are deasserted. The turn-around PCLK period for IRDY# is the Address phase of a transaction.

The AIC-7870 as a master asserts IRDY# with the same PCLK that starts a Data phase on AD[31:00].

Symbol: PAR Type: in-t/s

**Parity**. The even-parity bit that protects both AD[31:00] and C/BE[3:0]# signals. PAR is generated by the agent that is sourcing the 32-bit address of the transaction and/or the data of the transaction and includes the CBE[3:0] values even if not sourcing them. The state of PAR is valid for the value on AD[31:00] and CBE[3:0] during the previous PCLK period for address and for the PCLK that transferred data, excluding PAR turn-around PCLK periods which occur in the PCLK following the turn-around PCLK period of AD[31:00]. The agent detecting parity errors will set the DPE bit in the Configuration Status register without regard for the state of PERRESPEN bit. The AIC-7870 as a target indicates SERR for address parity error detection when both PERRESPEN and SERRESPEN are active. The AIC-7870 as a target will assert PERR for data parity errors when PERRESPEN is active.

Symbol: PCLK Type: cin

**PCI Bus Clock Input**. Provides timing for all transactions on the PCI bus. All other PCI signals are sampled on the rising edge of PCLK, and all parameters are defined with respect to this edge. PCLK is a controlled skew, point-to-point signal to each agent and is only driven by the PCI System Board Central Resource. The PCLK signal for the AIC-7870 is a maximum rate of 33.3 MHz. When POWRDN is active, the AIC-7870 Device registers which are accessible only from the PCI bus (not from the internal sequencer). PCLK signal used by other logic is maintained in the active state (=1) when POWRDN is active. Note, all internal logic is static allowing the PCLK and the CLKIN signals to be stopped externally if desired when no active SCSI commands are in process for maximum power down mode. See RAMPS# for a buffered version of PCLK for external adapter board use.

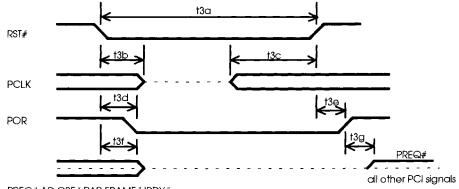

Symbol: PREQ# Type: t/s

**PCI Request#**. When asserted, indicates to the PCI System Board Arbitrator that a master desires use of the bus. This is a point-to-point signal with every master having its own PREQ#. Arbitration for the PCI bus is performed either when the bus is idle or in parallel with the transaction in process. When only a single Data phase is to be performed, PREQ# should be deasserted with the same PCLK that asserts FRAME#. When a

transaction is terminated by a target, the master must deassert its PREQ# for a minimum of two PCLK periods (one period must include the bus idle period). This allows another agent to use the bus while the previous target (that requested the STOP) prepares to continue.

**Note:** This is not required where the master deasserted FRAME# indicating the last Data phase of a transaction is in process. In this case, provided GNT# is still asserted, the master could start another transaction without deasserting PREQ#.

PREQ# is asserted by the AIC-7870 to become a bus master provided that the MASTEREN bit is active and either ISPACEEN or MSPACEEN bits (to allow access to the AIC-7870's Device registers) is/are active in the Configuration Command register for the following conditions:

- For system memory to data FIFO transfers (HDMAEN and DIRECTION are active and CACHETHEN inactive), when DFTHRSH or FIFOEMP becomes active. In this case, PREQ# remains asserted until DFSDH or FIFOFULL becomes active or STOP# is asserted, as long as HDMAEN is active, HCNT is not zero, and GNT# is asserted (or, if deasserted, until the latency timer has expired for pre-empt conditions and if performing a cache line referenced command MRDMC, until the in-process cache line transfer has been completed with MRDCEN not active. When MRDCEN is active, the in-process cache line transfer will be truncated).

- For system memory to data FIFO transfers (HDMAEN and DIRECTION are active and CACHETHEN inactive), when DFCACHETH becomes active. PREQ# will be asserted until the cache line is completed and DFCACHETH is inactive or (STOP# is asserted), as long as HDMAEN is active, HCNT is not zero, and GNT# is asserted (or, if deasserted, until the latency timer has expired for preempt conditions and if performing a Cache Line Referenced command MRDLC until the inprocess cache line transfer has been completed with MRDCEN not active. When MRDCEN is active, the in-process cache line transfer will be truncated).

- For data FIFO to system memory transfers (HDMAEN active and DIRECTION and CACHETHEN inactive), when DFTHRSH, DFSXDONE, or FIFOFULL becomes active. In this case, PREQ# remains asserted until FIFOEMP is active or STOP# is asserted, as long as HDMAEN is active, HCNT is not zero, and GNT# is asserted (or, if not asserted, until the latency timer has expired for pre-empt conditions and if performing a Cache Line Referenced command or (MWRIC), until the cache line transfer has been completed).

- For data FIFO to system memory transfers (HDMAEN and CACHETHEN active and DIRECTION inactive), when DFCACHETH becomes active. In this case, PREQ# remains asserted until the cache line is completed (or multiple cache lines are completed if DFCACHETH remains active), or STOP# is asserted, as long as HDMAEN is active, HCNT is not zero, and GNT# is asserted (or, if not asserted, until the latency timer has expired for pre-empt conditions and if performing a Cache Line Referenced command (MWRIC), until the cache line transfer has been completed).

**Note:** PREQ# output will be floated whenever RST# is asserted.

Symbol:PERR#Type:in-s/t/s

**Parity Error#**. May be asserted (pulsed for one PCLK period for each detected error provided that the Parity Error Response bit, PERRESPEN, is active in the Configuration Command register) only by the agent receiving the data. Also, a target cannot assert PERR# until it has claimed the access by asserting DEVSEL# and completing the data transfer. The turn-around PCLK for PERR# is the third PCLK period after the last address PAR period of an agent. PERR# is asserted for detected errors two PCLK periods after the data that contained the error as per the following sequence:

- **1** From PCLK N that transfers the data (both TRDY# and IRDY# are asserted) that data parity is to be generated for.

- 2 From PCLK N+1 PAR is asserted for the data asserted in PCLK N.

- **3** From PCLK N+2 assert PERR# when an even-parity error was indicated on the PCLK N+1 sample of data.

- **4** From PCLK (N+2)+1 deassert PERR# and when the last PERR# cycle wait for one more PCLK period before floating PERR#.

The AIC-7870 asserts PERR# only for detected data parity errors for received data when PERRESPEN is active but always sets DPE bit active in the Configuration Status register.

Symbol: RST# Type: in

**Reset#**. When asserted forces agents to a known initialization state. RST# may be asynchronous to PCLK when asserted or deasserted. Deassertion is guaranteed to be a clean, bounce-free edge.

- All n/o/d, t/s and s/t/s type signals are forced to a high impedance state.

- All o/d type signals are forced to float.

- All agent internal registers (Device and Configuration) are forced to specified states.

- All internal RAM data values should be considered indeterminate.

**Note:** The AIC-7870's internal Power-On-Reset (POR) activated by assertion of RST# is extended two CLKIN rising edges to ensure complete internal initialization, should short RST# assertions occur, and to provide an internally synchronized inactivation of the AIC-7870 initialization. POR is also activated by a write to the CHIPRST bit in Device HCNTRL register.

Symbol: SERR# Type: in-o/d

**System Error#**. May be asserted by a PCI agent that detects an address parity error (provided that PERRESPEN and SERRESPEN are active) during the Address phase of a transaction or for data parity errors on special cycles and for any other system error where the result will be a catastrophic error. The transaction master is solely responsible for reporting master or target aborts; targets do not assert SERR# when using target-abort termination. SERR# is restored only by a weak pull-up on the system board, and

may take several PCLK periods to recover to a deasserted state. SERR# is asserted (pulsed for one PCLK period) for detected address errors two PCLK periods after the address that contained the error as per the following sequence:

- **1** From PCLK N for the address that is being asserted, for which parity is to be generated for.

- 2 From PCLK N+1 PAR is asserted for the address asserted in PCLK N.

- **3** From PCLK N+2 assert SERR# when an even-parity error was indicated on the PCLK N+1 sample of the address.

- 4 From PCLK (N+2)+1 deassert SERR#.

The AIC-7870 as a target only asserts SERR# for all detected address parity errors when PERRESPEN and SERRESPEN are active. In all cases, DPE will be set active without regard for the enables.

Symbol: STOP# Type: in-s/t/s

**Stop**. When asserted, indicates the current target is requesting the master to stop the current Data phase of a transaction in process. STOP#, once asserted, must remain asserted until FRAME# is deasserted and data may or may not be transferred in the final Data phase of the transaction. The turn-around PCLK period for STOP# is the Address phase of a transaction.

The AIC-7870, when attempting to perform a transaction to a target that responds with Target-Stop (disconnect) or Target-Retry, will retry the transaction with the next address to be transferred. When the response is Target-Abort, the AIC-7870 will not retry and will set the RTA bit in the Configuration Status register active and generate an interrupt IRQA#. See the Device CLRINT register for clearing this interrupt.

**Note:** For Target-Abort this means the SCSI data segment transfer will stall and software/firmware intervention is required.)

The AIC-7870 as a target asserts STOP# (disconnect with data transferred) when FRAME# is indicating burst cycles (except for SCB double word write transactions where bursting is allowed). This is not an error condition.

| FRAME# | IRDY# | DEVSEL# | TRDY# | STOP# | Condition<br>Normal Master Ending |

|--------|-------|---------|-------|-------|-----------------------------------|

| N      | N     | N       | N     | N     | Bus idle                          |

| Y      | N     | N       | N     | N     | Master starts SAC                 |

| Y      | Y     | N       | N     | N     |                                   |

| Y      | Y     | Y       | Ν     | Ν     | Target responds                   |

| Y      | Y     | Y       | Y     | N     | Data transferred                  |

| Y      | Y     | Y       | Y     | N     | Data transferred                  |

| N      | Y     | Y       | Y     | N     | Last data transferred             |

| N      | N     | Ν       | N     | Ν     | Bus idle                          |

\_

| FRAME# | iRDY# | DEVSEL# | TRDY# | STOP# | Condition<br>Normal Master Ending |

|--------|-------|---------|-------|-------|-----------------------------------|

| N      | N     | N       | N     | Ν     | Bus idle                          |

| Y      | N     | N       | N     | N     | Master starts DAC                 |

| Y      | N     | Ν       | Ν     | N     |                                   |

| Y      | Y     | N       | N     | Ν     |                                   |

| Y      | Y     | Y       | N     | Ν     | Target responds                   |

| Y      | Y     | Y       | Y     | Ν     | Data transferred                  |

| Y      | Y     | Y       | Y     | N     | Data transferred                  |

| N      | Y     | Y       | Y     | N     | Last data transferred             |

| N      | N     | N       | N     | N     | Bus idle                          |

| FRAME# | IRDY# | DEVSEL# | TRDY# | STOP# | Condition<br>Target Disconnected with Data |

|--------|-------|---------|-------|-------|--------------------------------------------|

| N      | N     | N       | N     | N     | Bus idle                                   |

| Y      | N     | N       | Ν     | N     | Master starts SAC                          |

| Y      | Y     | N       | N     | N     |                                            |

| Y      | Y     | Y       | N     | Ν     | Target responds                            |

| Y      | Y     | Y       | Y     | N     | Data transferred                           |

| Y      | Y     | Y       | Y     | Y     | Last data transferred                      |

| N      | Y     | Ν       | N     | Y     | No data transferred                        |

| N      | Ν     | Ν       | N     | Ν     | Bus idle                                   |

·····

| FRAME#   | IRDY# | DEVSEL# | TRDY# | STOP# | Condition<br>Target Disconnected without Data |

|----------|-------|---------|-------|-------|-----------------------------------------------|

| N        | N     | N       | N     | N     | Bus idle                                      |

| Y        | N     | N       | N     | N     | Master starts SAC                             |

| Y        | Y     | N       | N     | N     |                                               |

| Y        | Y     | Y       | N     | N     | Target responds                               |

| Y        | Y     | Y       | Y     | N     | Data transferred                              |

| Y        | Y     | Y       | N     | Y     | No data transferred                           |

| N        | Y     | N       | N     | Y     |                                               |

| <u>N</u> | N     | N       | N     | N     | Bus idle                                      |

| FRAME#   | IRDY# | DEVSEL# | TRDY# | STOP# | Condition<br>Target Retry                     |

| N        | N     | N       | N     | N     | Bus idle                                      |

| Y        | N     | N       | N     | N     | Master starts SAC                             |

| Y        | Y     | N       | N     | N     |                                               |

| Y        | Y     | Y       | N     | Y     | Target responds                               |

| Ν        | Y     | Y       | N     | Y     | No data transferred                           |

| N        | Ν     | N       | Ν     | N     | Bus idle                                      |

|          |       |         |       |       | · · · · · · · · · · · · · · · · · · ·         |

| FRAME#   | IRDY# | DEVSEL# | TRDY# | STOP# | Condition<br>Target Abort                     |

| Ν        | N     | N       | Ν     | Ν     | Bus idle                                      |

| Y        | Ν     | Ν       | N     | N     | Master starts SAC                             |

| Y        | Y     | N       | N     | N     |                                               |

| Y        | Y     | Y       | N     | N     | Target responds                               |

| Y        | Y     | N       | Ν     | Y     | No data transferred                           |

| N        | Y     | Ν       | Ν     | Y     | No data transferred                           |

| N        | N     | N       | N     | N     | Bus idle                                      |

| FRAME#   | IRDY# | DEVSEL# | TRDY# | STOP# | Condition<br>Master Abort                     |

| N        | N     | N       | N     | N     | Bus idle                                      |

| Y        | Ν     | Ν       | Ν     | N     | Master starts SAC                             |

| Y        | Y     | N       | N     | N     |                                               |

| Y        | Y     | N       | N     | N     |                                               |

| Y        | Y     | N       | N     | N     |                                               |

| Y        | Y     | N       | N     | N     |                                               |

| Y        | Y     | N       | Ν     | N     |                                               |

| Y        | Y     | N       | N     | N     |                                               |

| Y        | Y     | N       | N     | N     | Master declares abort                         |

| N        | Y     | N       | N     | N     | FRAME/IRDY ending sequence                    |

| N        | N     | N       | N     | N     | Bus idle                                      |

Symbol: TRDY# Type: in-s/t/s

**Target Ready#**. Asserted to indicate the current slave's ability to complete the current Data phase of a transaction. During a read, TRDY# indicates that the slave is asserting valid data on AD[31:00]. During a write it indicates the slave is prepared to accept data. It is used in conjunction with IRDY#. Wait cycles are inserted until both IRDY# and TRDY# are asserted together. Wait cycles should be minimized, when more than eight are expected, except for the first transfer, the transaction should be disconnected by the target and retried by the master. A Data phase is completed on any PCLK when IRDY# and TRDY# are both sampled asserted. The turn-around PCLK period for TRDY# is the Address phase of a transaction.

The AIC-7870 as a target will always have TRDY# deasserted in the first PCLK period of the first Data phase so that the asserted CBE# value may be decoded for internal byte steering and for read access required AD[31:00] turn-around. TRDY# will also be deasserted for additional PCLKs for RAM data to become valid, and when PAUSEACK is not active and the access is to a register that requires it to be active for the host driver to access the register (see PAUSE[ACK] bit in the Device HCNTRL register), for SCB access (when RAMPSM is asserted), or for ROM/EEPROM access (see EXTARBREQ#/ EXTARBACK#). When TRDY# is not asserted within eight PCLKs for Data phases, the AIC-7870 will respond with Disconnect when the data transfers. Additionally, should TRDY# not be asserted before the Exceed Timer expires, the AIC-7870 will respond with Betry. The Exceed Timer is an escape timer that should only time out should a requested AIC-7870 address/register not be available for long periods of time (not a normal condition), and is provided to prevent hanging the system. Also see EXTARBACK#.

#### Non-supported PCI-32 Pin Signals

| IRQA# | SDONE# |

|-------|--------|

| IRQB# | TCK    |

| IRQC# | TDI    |

| IRQD# | TDO    |

| LOCK# | TMS    |

| SBO#  | TRST#  |

#### Non-supported PCI-64 Extension Signals

| ACK64#   | PAR64  |

|----------|--------|

| BE#[7:4] | REQ64# |

| D[63:32] |        |

# Supported PCI Pin Side Band Signal

Table 2-7. Supported PCI Pin Side Band Signals

| Symbol | Туре | Definition                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IRQA#  | o/d  | Interrupt Request A. IRQA# assertion state changes are synchronized to PCLK for<br>PCI type errors and parity errors. The AIC-7870 interrupt conditions cannot assert<br>IRQA# when the INTEN bit is not active or the POWRDN bit is active in the HCNTRL<br>register. For IRQA# assertion conditions see the INTSTAT register. Note IRQA#<br>output is floated when RST# is asserted and also used in test modes. |

### External PCI-32 Pin Signal Type Definition

Table 2-8. External PCI-32 Pin Signal Type Definition

| Туре     | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| cin      | Clock Input is a special clock high drive input-only receive signal.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| in       | Input is a standard input-only receive signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| t/s      | Three-state is an output signal with control enabled output driver.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| in-t/s   | In-three-state is a bidirectional signal, with control enabled output driver and an internally<br>connected standard input.                                                                                                                                                                                                                                                                                                                                                                        |

| in-s/t/s | Sustained Three-state is a bidirectional signal, active low three-state signal and driven by one,<br>and only one, agent at a time. The agent that drives an in-s/t/s signal low must drive it high for at<br>least one PCLK before letting it float. A new agent cannot start driving an in-s/t/s signal any sooner<br>than one clock after the previous owner floats it. A pull-up sustains the inactive state until another<br>agent drives it and is provided by the PCI bus central resource. |

| o/d      | Open Drain is an open drain output. The system board provides a light pull-up for o/d signals.<br>Multiple devices share the signal as a wire-OR. The signal is asserted synchronous with PCLK for<br>one PCLK period. The signal deassertion period is determined by the RC time period provided by<br>the pull-up.                                                                                                                                                                               |

-----

\_\_\_\_\_

# SCSI Interface Pin Signals

.

| Table 2-9. | . SCSI Interface Pin Signals |  |

|------------|------------------------------|--|

|------------|------------------------------|--|

| Symbol       | Туре     | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCD[15:0]#   | in-n/o/d | SCSI Data [15:0] #. The SCSI data lines drive the ID during arbitration and selection and command and data information as well as status and messages. SCD[7:0] are used for 8-bit data transfers while SCD[15:8] are floated with their inputs disabled.                                                                                                                                                                                                                                                       |

| SCDPH#       | in-n/o/d | SCSI High Byte Parity #. This bit provides odd parity for SCD[15:8]#. SCDPH# is floated for 8-bit data transfers with its input disabled.                                                                                                                                                                                                                                                                                                                                                                       |

| SCDPL#       | in-n/o/d | SCSI Low Byte Parity #. This bit provides odd parity for SCD[7:0]#.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CD#          | ìn-n/o/d | <b>Command/Data #</b> . This control line is received when in Initiator mode or driven when<br>in Target mode. It indicates Command or Message phase when asserted, and Data<br>phase when deasserted. This control signal is used for 8 or 16-bit transfers.                                                                                                                                                                                                                                                   |

| 10#          | in-n/o/d | In/Out #. This control line is received when in Initiator mode or driven when in Targe mode. It indicates the In direction when asserted, and the Out direction when deas-<br>serted. This control signal is used for 8 or 16-bit transfers.                                                                                                                                                                                                                                                                    |

| MSG#         | in-n/o/d | <b>Message #</b> . This control line is received when in Initiator mode or driven when in Target mode. It indicates a Message phase when asserted, and a Command or Data phase when deasserted. This control signal is used for 8 or 16-bit transfers.                                                                                                                                                                                                                                                          |

| REQ#         | in-n/o/d | Request #. This control line is received by the device when in Initiator mode and<br>driven when in Target mode. A Target will assert REQ# to indicate a byte is ready or is<br>needed by the Target. This control signal is used for 8 or 16-bit transfers.                                                                                                                                                                                                                                                    |

| ACK#         | in-n/o/d | Acknowledge #. This control line is received by the device when in Target mode and<br>driven when in Initiator mode. An Initiator will assert ACK# to indicate a byte is ready<br>for or was received from the Target. This control signal is used for 8 or 16-bit<br>transfers.                                                                                                                                                                                                                                |

| RESET#       | in-o/d   | <b>Reset #</b> . This line is received and/or driven. It is interpreted as a hard reset and will clear all commands pending on the SCSI bus. This control signal is used for 8 or 16-bit transfers.                                                                                                                                                                                                                                                                                                             |

| SEL#         | in-o/d   | Select #. This line is driven after a successful arbitration to Select as an Initiator or<br>Reselect as a Target, and otherwise it is received. This control signal is used for 8 or<br>16-bit transfers.                                                                                                                                                                                                                                                                                                      |

| BSY#         | in-o/d   | <b>Busy #.</b> This line is driven by the Initiator as a handshake during arbitration, and received for the rest of the transfer. As a Target, it is driven also as a handshake during Arbitration, and then is driven for the rest of the transfer. This control signal is used for 8 or 16-bit transfers.                                                                                                                                                                                                     |

| ATN#         | in-n/o/d | Attention #. This line is driven as an Initiator when a special condition occurs. It is received by the Target. This control signal is also used for 16-bit transfers.                                                                                                                                                                                                                                                                                                                                          |

| DIFFDAT[3:0] | t/s      | Differential Control Data. These lines contain information which is latched by out-<br>side circuitry to provide control of differential drivers. The definition of these bits<br>depends on the value of DIFFADR[1:0]. This control signal is used for 8 or 16-bit<br>transfers. Note the DIFFDAT[3:0] outputs are floated when RST# is asserted.                                                                                                                                                              |

| DIFFADR(1:0] | t/s      | <b>Differential Control Address</b> . These lines determine the meaning of DIFFDAT[3:0]. This control signal is used for 8 or 16-bit transfers. Note the DIFFADR[1:0] outputs are floated when RST# is asserted.                                                                                                                                                                                                                                                                                                |

| DIFFSTRB#    | in-t/s   | <b>Differential Control Strobe #</b> . This signal clocks the data present on DIFFDAT[3:0] into the addressed latch specified by DIFFADR[1:0] on its rising edge. Both DIFFDAT[3:0] and DIFFADR[1:0] are stable for the duration of DIFFSTRB#. This control signal is used for 8 or 16 -bit transfers. Note DIFFSTRB# output is floated when RST# is asserted and its internal pull-up will keep DIFFSTRB# at a high level. DIFFSTRB# is also used for setting TESTBITEN status, used during component testing. |

-----

| Symbol  | Туре  | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

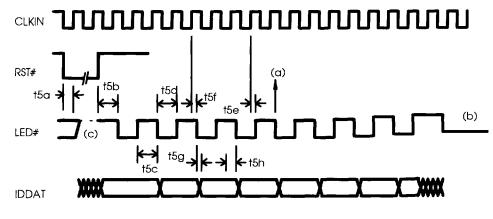

| LED#    | t/s   | LED#. Output provides three functions:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         |       | 1 To indicate (when asserted =0) that the AIC-7870 is actively connected to the<br>SCSI bus. LED asserted state is latched with the ORed result of active bits<br>SELINGO, SELDI and SELDO in the SSTAT0 register and deasserted by the<br>following SCSI bus free condition. LED# may be used to provide system status of<br>the AIC-7870 SCSI bus activity and may directly drive an indicator (LED) provid-<br>ing the current is limited to a maximum of 20 mÅ.                                                                                                                                                                             |

|         |       | 2 As a clock to (20 MHz) shift-in an external device ID value from input IDDAT, to replace the internal default Device ID value. This use of LED# is triggered as a result of RST# assertion. See IDDAT pin for details.                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         |       | 3 For diagnostic support or general purpose output control bit, see Device<br>SBLKCTL register. Note the LED# output is floated when RST# is asserted. After<br>RST# is deasserted the specified IDDAT clocking occurs, then LED# will be<br>asserted continuously until cleared by software/firmware, to provide an indication<br>that normal run mode has been entered. Should a PCI target access be<br>attempted to the AIC-7870 while the IDDAT shift-in process is active, a RETRY<br>response will be returned. Note the fourth IDDAT clock present on LED# internali<br>samples the input state of RAMPS# to store the MPORTMODE state. |

| STPWCTL | t/s   | SCSI Termination Power Down Control. Provides the capability to enable or dis-<br>able the external SCSI bus termination power source. The enable/disable polarity of<br>STPWCTL may be selected with the STPWLEVEL bit in the Configuration<br>DEVCONFIG register and the actual enable/disable state is selected with the<br>STPWEN bit in the Device SXFRCTL1 register. CHIPRST forces STPWCTL to the<br>selected disabled state and STPWEN to the inactive state. While RST# assertion<br>forces STPWCTL to be floated, and both STPWLEVEL and STPWEN to be inactive<br>STPWCTL may also be used for a general purpose output control bit.  |

| WIDEPS# | input | Wide Present#. When asserted (=0) indicates that a wide (16-bit) cable connector is present. WIDEPS# input contains an internal pull-up and only needs to be connected for 16-bit operation. See the AIC-7870 Device SBLKCTL register.                                                                                                                                                                                                                                                                                                                                                                                                          |

Table 2-9. SCSI Interface Pin Signals (Continued)

## SCSI Pin Signal Type Definition

Table 2-10. SCSI Pin Signal Type Definition

| Туре     | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|