Document Revision 5 December 1995

# AIC-8375B

Fast IDE Disk Controller IC

#### **ATA Interface Block**

- ▼ ATA Multiword DMA modes 0-2

- ▼ Fast IDE PIO modes 0-4

- ▼ IORDY for PIO flow control

- ▼ Automatic AT R/W command execution

- ▼ Automatic AT Task File updates

- ▼ 32-byte host FIFO

- ▼ LBA or CHS TASK File Modes

- Programmable IRQ automation to comply with different BIOS implementations

- Provides logic for daisy chaining two embedded disk drive controllers

- ▼ Hardware selectable PCMCIA 2.0

- ▼ Full BIOS compatibility

- ▼ On-Chip12 mA Host Drivers

- PCMCIA Attribute Memory stored in buffer memory

#### **Buffer Controller Block**

- ▼ 8 bit wide or 16 bit wide buffer data bus with parity

- ▼ DRAM support with up to 4 Mbyte addressing capability; up to 36 Mbyte/s (18 Mbyte/s PCMCIA) buffer bandwidth using page mode DRAM access

- ▼ SRAM support for up to 256 Kbyte direct addressing; up to 50 Mbyte/s (25 Mbyte/s PCMCIA) buffer bandwidth

- Automated Data Flow Management (ADFM) automates disk/host transfers.

- ▼ 2K page direct microprocessor access

- ▼ Variable Segmentation

- ▼ Write Cache Support

- ▼ Servo Split count out of buffer

#### **Other Features**

- ▼ 128-pin QFP and TQFP packages

- ▼ Automatic power-down modes

- ▼ High-speed, low-power CMOS

#### **EDAC Block**

- ▼ Optimized 168 bit ECC with Triple Burst on-the-fly (OTF) correction

- ▼ 65 bit single burst OTF correction in <1 sector time or 17 bit Double or Triple Burst OTF correction in <1 sector time</p>

- ▼ SW correction up to three 17-bit bursts

- ▼ Error detection of one 89-bit error, two 41-bit errors, or three 17-bit errors

- ▼ ECC seeding validating servo and head track position

- ▼ Fault tolerant sync mark detection with 2 byte sync

#### **Disk Controller Block**

- ▼ Enhanced Headerless Architecture (EDSA)

- ▼ 50 Mbits/sec, 100 Mbits/sec and 120 Mbits/ sec disk rate in single, dual, and byte-wide NRZ modes respectively

- ▼ 31 x 3 byte flexible high-speed RAMbased sequencer

- Defect skipping and/or embedded servo capabilities with Constant Density Recording (CDR)

- ▼ 32-byte disk FIFO for speed matching with the buffer manager

- ▼ Two-index timer

- ▼ Supports (1,7) and (2,7) RLL interfaces

- MR and PRML channel support

#### **Microcontroller Interface Block**

- Direct support for Intel or Motorola multiplexed or non-multiplexed interfaces

- Ready line for interfacing to faster microprocessors and for direct microprocessor access to the Buffer

- Programmable open drain interrupt output for host, disk, and buffer

- ▼ Address latch outputs for multiplexed microprocessor interface

- Direct buffer addressing in programmable 2K windows with 1K resolution on base address

Copyright© 1995 Adaptec, Inc. All rights reserved. The information contained in this document (including all revisions) is the confidential, trade secret and proprietary property of Adaptec, Inc. It may not be used, copied, distributed, or disclosed without the express written permission of Adaptec, Inc. Adaptec and the Adaptec logo are registered trademarks of Adaptec, Inc. All other trademarks used are owned by their respective owners. The information contained in this document is subject to change without notice.

# Table of Contents

| SECTIO                                                                                                             | N 1 - INT                                                                                                                    | RODUCTION                                                                                                                                                                                                                                                              | 1                                            |

|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 1.1                                                                                                                | Introdu                                                                                                                      | uction                                                                                                                                                                                                                                                                 | 1                                            |

| 1.2                                                                                                                | Genera                                                                                                                       | I Description and Features                                                                                                                                                                                                                                             | 1                                            |

|                                                                                                                    | 1.2.1                                                                                                                        | The Local Microprocessor Interface Block                                                                                                                                                                                                                               | 2                                            |

|                                                                                                                    | 1.2.2                                                                                                                        | The Host Interface Block                                                                                                                                                                                                                                               | 2                                            |

|                                                                                                                    | 1.2.3                                                                                                                        | The Buffer Control Block                                                                                                                                                                                                                                               | 3                                            |

|                                                                                                                    | 1.2.4                                                                                                                        | The Disk Control Block                                                                                                                                                                                                                                                 | 3                                            |

|                                                                                                                    | 1.2.5                                                                                                                        | The Disk ECC Block                                                                                                                                                                                                                                                     | 4                                            |

|                                                                                                                    | 1.2.6                                                                                                                        | Power Management                                                                                                                                                                                                                                                       | 4                                            |

|                                                                                                                    | 1.2.7                                                                                                                        | Headerless Architecture                                                                                                                                                                                                                                                | 4                                            |

|                                                                                                                    |                                                                                                                              |                                                                                                                                                                                                                                                                        |                                              |

| SECTION                                                                                                            | N 2 - PIN                                                                                                                    | DEFINITIONS                                                                                                                                                                                                                                                            | 5                                            |

| 2.1                                                                                                                | AIC-83                                                                                                                       | 375 Disk Interface Pins                                                                                                                                                                                                                                                | 7                                            |

| 2.2                                                                                                                | AIC-83                                                                                                                       | 375 Buffer Interface Pins                                                                                                                                                                                                                                              | 10                                           |

| 2.3                                                                                                                | AIC-83                                                                                                                       | 375 Host Interface Pins                                                                                                                                                                                                                                                | 15                                           |

| 2.4                                                                                                                | AIC-83                                                                                                                       | 375 Microprocessor Interface Pins                                                                                                                                                                                                                                      | 21                                           |

| 2.5                                                                                                                | AIC-83                                                                                                                       | 75 Power/Ground Pins                                                                                                                                                                                                                                                   | 24                                           |

|                                                                                                                    |                                                                                                                              |                                                                                                                                                                                                                                                                        |                                              |

|                                                                                                                    |                                                                                                                              |                                                                                                                                                                                                                                                                        |                                              |

| SECTION                                                                                                            | N 3 - REC                                                                                                                    | GISTER SUMMARY                                                                                                                                                                                                                                                         | 25                                           |

| SECTION<br>3.1                                                                                                     |                                                                                                                              | GISTER SUMMARY                                                                                                                                                                                                                                                         |                                              |

|                                                                                                                    | Device                                                                                                                       |                                                                                                                                                                                                                                                                        | 25                                           |

| 3.1                                                                                                                | Device<br>Disk Co                                                                                                            | Control Registers                                                                                                                                                                                                                                                      | 25                                           |

| 3.1<br>3.2                                                                                                         | Device<br>Disk Co                                                                                                            | Control Registers                                                                                                                                                                                                                                                      | 25<br>25<br>                                 |

| 3.1<br>3.2                                                                                                         | Device<br>Disk Co<br>ECC Co<br>3.3.1                                                                                         | Control Registers<br>ontrol Registers<br>ontrol Registers                                                                                                                                                                                                              | 25<br>25<br>28<br>28                         |

| 3.1<br>3.2<br>3.3                                                                                                  | Device<br>Disk Co<br>ECC Co<br>3.3.1<br>Host Co                                                                              | Control Registers<br>ontrol Registers<br>ontrol Registers<br>ECC Indirect Data Registers                                                                                                                                                                               |                                              |

| <ul><li>3.1</li><li>3.2</li><li>3.3</li><li>3.4</li></ul>                                                          | Device<br>Disk Co<br>ECC Co<br>3.3.1<br>Host Co<br>Buffer (                                                                  | Control Registers<br>ontrol Registers<br>ontrol Registers<br>ECC Indirect Data Registers<br>ontrol Registers                                                                                                                                                           |                                              |

| <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> </ul>                                        | Device<br>Disk Co<br>ECC Co<br>3.3.1<br>Host Co<br>Buffer O<br>Disk Se                                                       | Control Registers                                                                                                                                                                                                                                                      | 25<br>25<br>28<br>28<br>29<br>33<br>37       |

| <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> </ul>                           | Device<br>Disk Co<br>ECC Co<br>3.3.1<br>Host Co<br>Buffer O<br>Disk Se<br>PCMCI                                              | Control Registers                                                                                                                                                                                                                                                      | 25<br>25<br>28<br>28<br>29<br>33<br>37<br>37 |

| <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> <li>3.7</li> </ul>              | Device<br>Disk Co<br>ECC Co<br>3.3.1<br>Host Co<br>Buffer O<br>Disk Se<br>PCMCI                                              | Control Registers                                                                                                                                                                                                                                                      | 25<br>25<br>28<br>28<br>29<br>33<br>37<br>37 |

| <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> <li>3.7</li> <li>3.8</li> </ul> | Device<br>Disk Cd<br>ECC Cd<br>3.3.1<br>Host Cd<br>Buffer d<br>Disk Se<br>PCMCD<br>Host Ta                                   | Control Registers                                                                                                                                                                                                                                                      |                                              |

| <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> <li>3.7</li> <li>3.8</li> </ul> | Device<br>Disk Cd<br>ECC Cd<br>3.3.1<br>Host Cd<br>Buffer d<br>Disk Se<br>PCMCI<br>Host Ta                                   | Control Registers                                                                                                                                                                                                                                                      |                                              |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>SECTION                                                    | Device<br>Disk Cd<br>ECC Cd<br>3.3.1<br>Host Cd<br>Buffer d<br>Disk Se<br>PCMCI<br>Host Ta<br>N 4 - REC<br>Device            | Control Registers<br>ontrol Registers<br>ontrol Registers<br>ECC Indirect Data Registers<br>ontrol Registers<br>Control Registers<br>control Registers<br>equencer RAM Registers<br>IA Interface Registers<br>IA Interface Registers (AT Host)<br>GISTER RESET SUMMARY |                                              |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>SECTION<br>4.1                                             | Device<br>Disk Co<br>ECC Co<br>3.3.1<br>Host Co<br>Buffer O<br>Disk Se<br>PCMCI<br>Host Ta<br>N 4 - REC<br>Device<br>Disk Co | Control Registers                                                                                                                                                                                                                                                      |                                              |

i

| 4.4 | Host C | ontrol Registers                   | 42   |

|-----|--------|------------------------------------|------|

|     | 4.4.1  | Host Task File Registers (AT Host) | . 44 |

|     | 4.4.2  | PCMCIA Interface Registers         | . 44 |

| 4.5 | Buffer | Control Registers                  | . 45 |

| SECTION | 15 - REC | GISTER DESCRIPTIONS                            | 47  |

|---------|----------|------------------------------------------------|-----|

| 5.1     | Device   | Control Register Descriptions                  | 47  |

| 5.2     | Disk Bl  | ock Register Descriptions                      | 51  |

| 5.3     | ECC B    | lock Register Descriptions                     | 69  |

| 5.4     | Host Bl  | ock Register Descriptions                      | 74  |

| 5.5     | Buffer l | Block Register Descriptions                    | 107 |

| 5.6     | Disk Se  | quencer RAM Register Descriptions              | 128 |

| 5.7     | PCMCI    | A Interface Register Descriptions              | 129 |

|         | 5.7.1    | Card Information Structure (000h-1FFh, R, CIS) | 129 |

|         | 5.7.2    | PCMCIA Registers                               | 129 |

| 5.8     | AT Inte  | rface Register Descriptions                    | 132 |

|         | 5.8.1    | AT Task File/Command Block Registers           | 132 |

|         | 5.8.2    | AT Task File/Control Block Registers           | 136 |

|         |          |                                                |     |

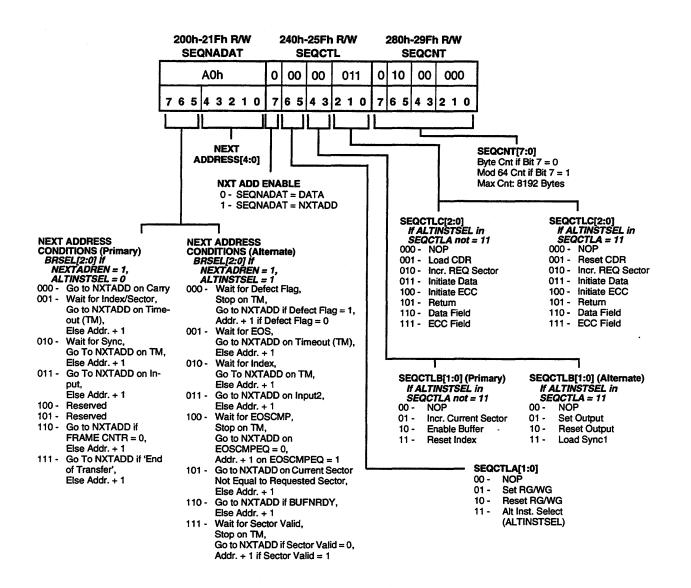

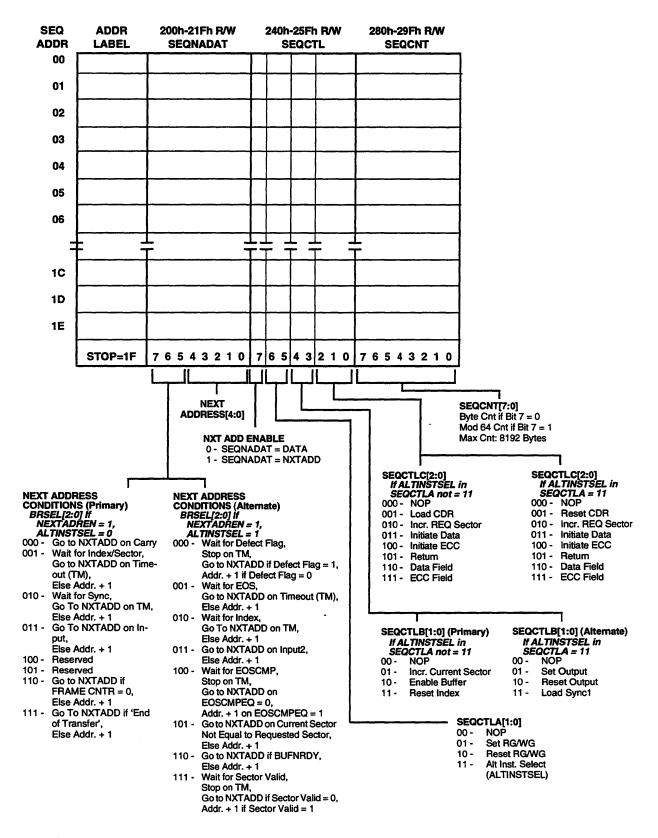

# SECTION 6 - THE DISK SEQUENCER MAP 139 6.1 Overview Of The Disk Sequencer Map 139 6.2 Sequencer Data/Next Address Byte (200h-21Fh, R/W, SEQNADAT) 140 6.2.1 Data Field 141 6.2.2 Next Address Field 141 6.3 Sequencer Control Byte (240h-25Fh, R/W, SEQCTL) 145 6.4 Sequencer Count Byte (280h-29Fh, R/W, SEQCNT) 148

| SECTION | 7 - PRELIMINARY ELECTRICAL SPECIFICATIONS | 151 |

|---------|-------------------------------------------|-----|

| 7.1     | Absolute Maximum Ratings                  | 151 |

| 7.2     | Operating Conditions                      | 151 |

| 7.3     | DC Characteristics                        | 152 |

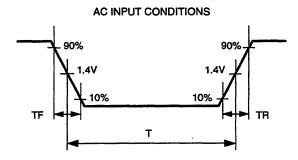

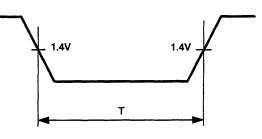

| SECTION | 8 - TIM | ING SPECIFICATIONS                | 155 |

|---------|---------|-----------------------------------|-----|

| 8.1     | General | Timing                            | 155 |

|         | 8.1.1   | AC Input/Output Timing Parameters | 155 |

|         | 8.1.2   | AC Input/Output Timing            | 155 |

| 8.2 | Microp  | processor Interface Timing                    | 156 |

|-----|---------|-----------------------------------------------|-----|

|     | 8.2.1   | Microprocessor Interface Timing Parameters    | 156 |

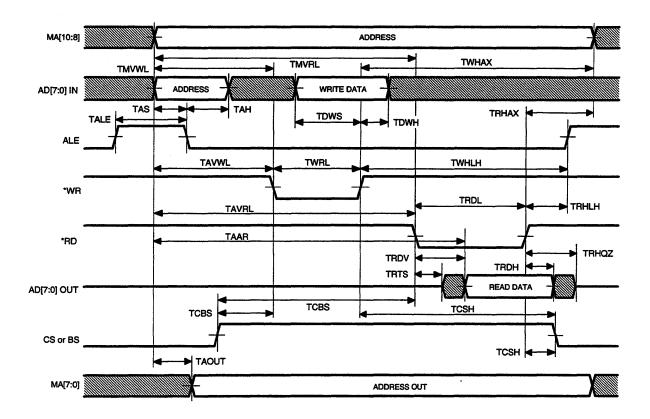

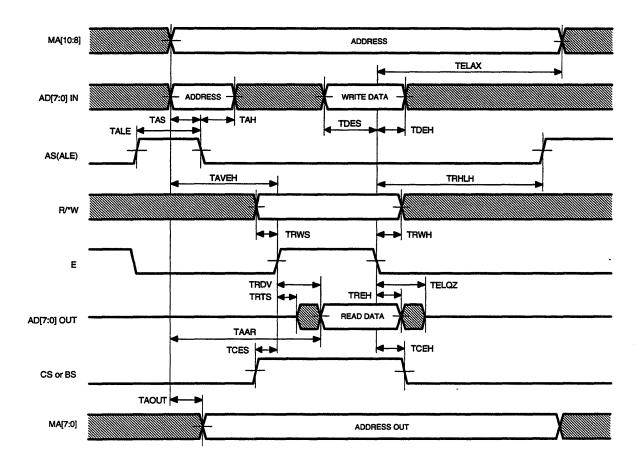

|     | 8.2.2   | Intel Multiplexed Mode                        | 158 |

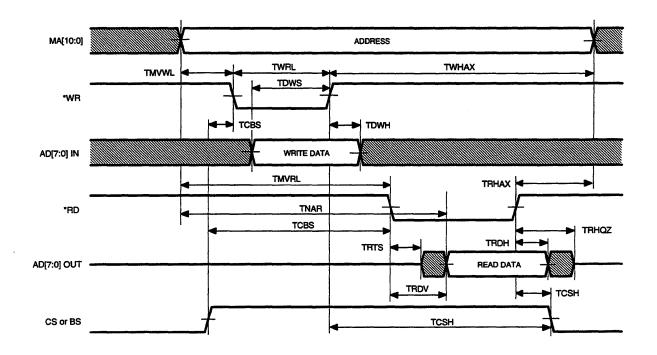

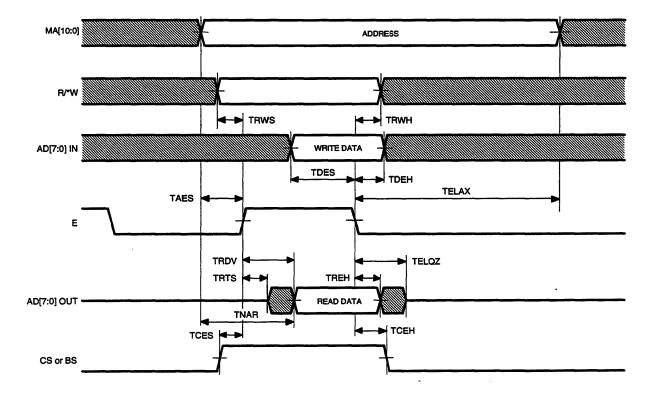

|     | 8.2.3   | Intel Non-Multiplexed Mode                    | 159 |

|     | 8.2.4   | Motorola Multiplexed Mode                     | 160 |

|     | 8.2.5   | Motorola Non-Multiplexed Mode                 | 161 |

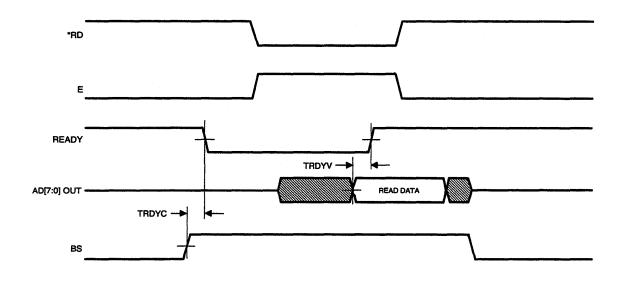

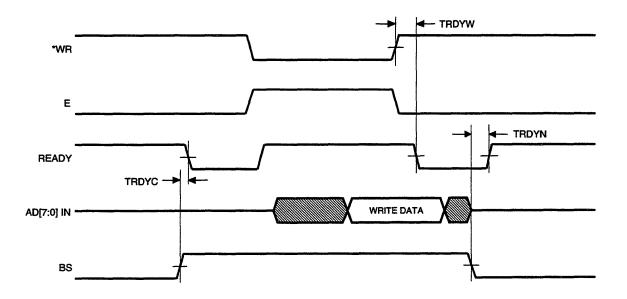

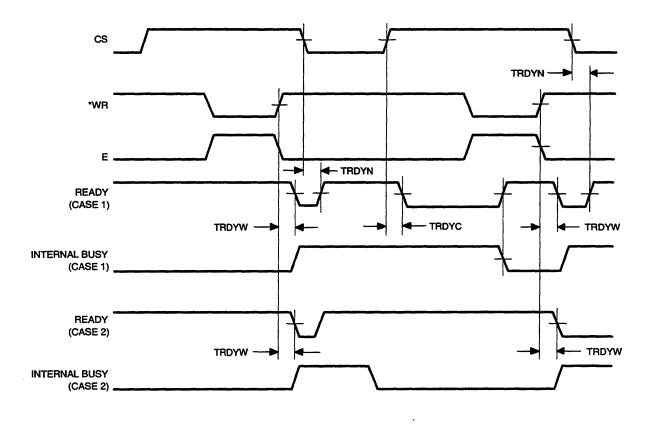

|     | 8.2.6   | Microprocessor Ready Line Operation           |     |

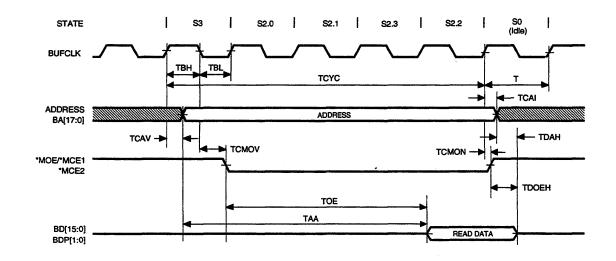

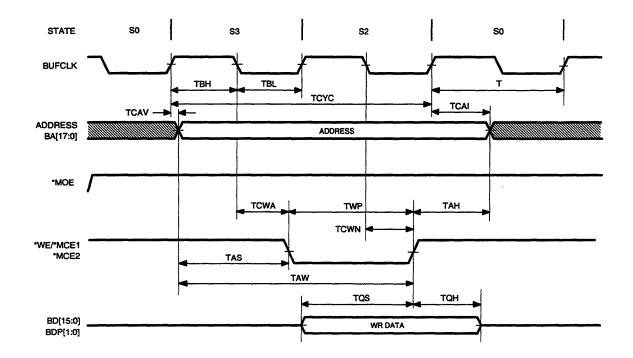

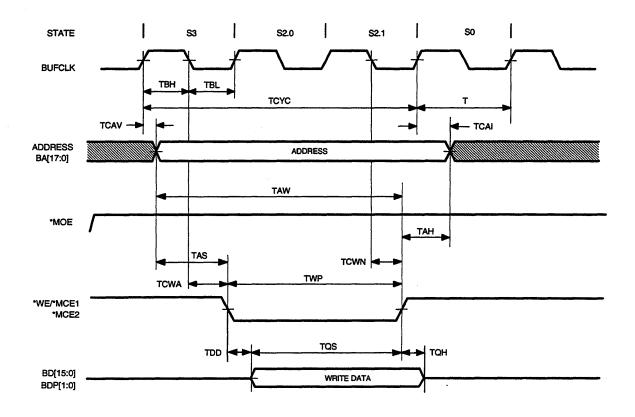

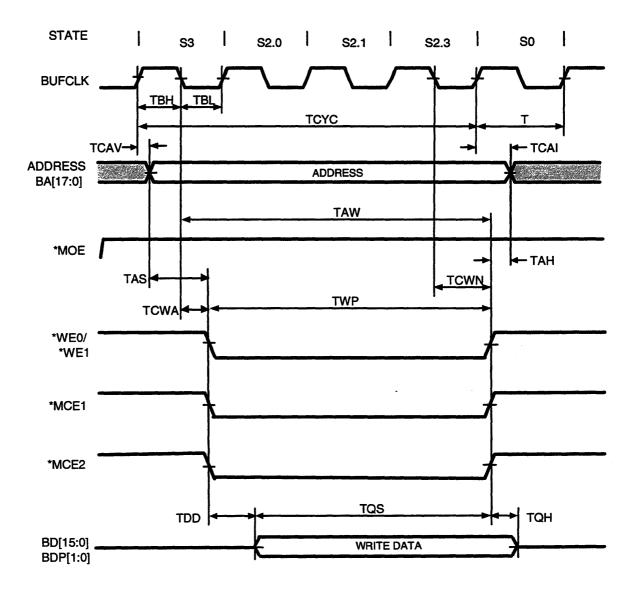

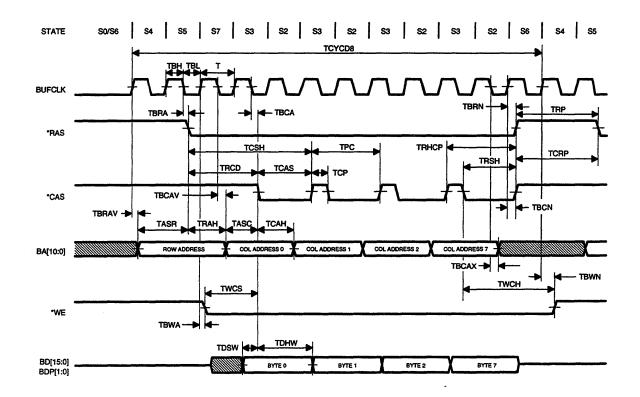

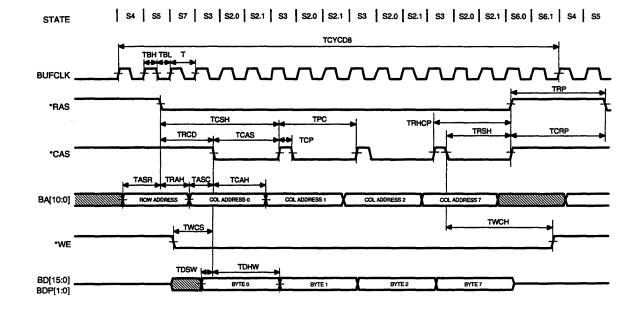

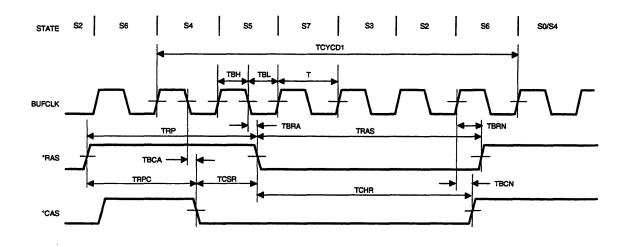

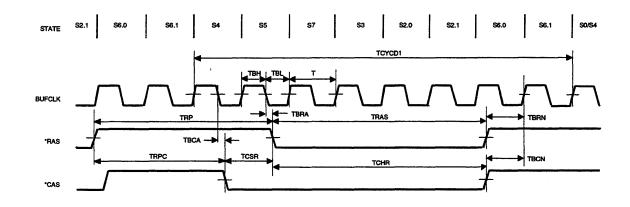

| 8.3 | Buffer  | Interface Timing                              |     |

|     | 8.3.1   | SRAM Timing Parameters                        |     |

|     | 8.3.2   | DRAM Timing Parameters                        |     |

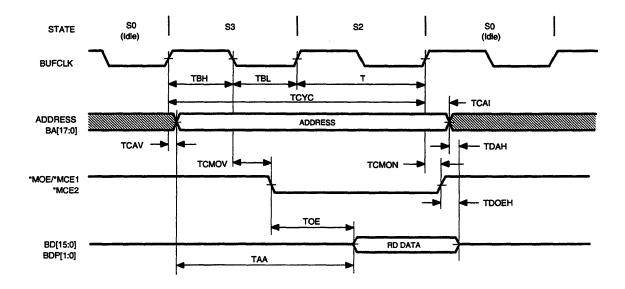

|     | 8.3.3   | SRAM Timing (Read, 2T Access)                 | 167 |

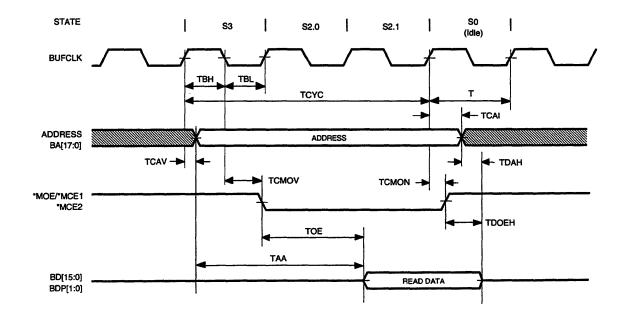

|     | 8.3.4   | SRAM Timing (Read, 3T Access)                 |     |

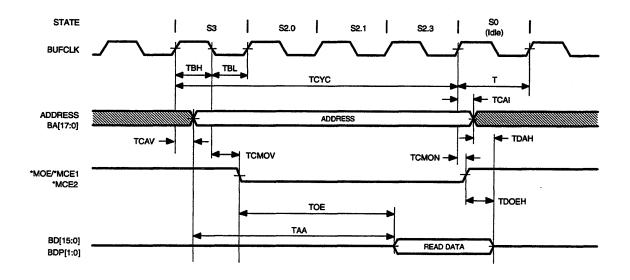

|     | 8.3.5   | SRAM Timing (Read, 4T Access)                 |     |

|     | 8.3.6   | SRAM Timing (Read, 5T Access)                 |     |

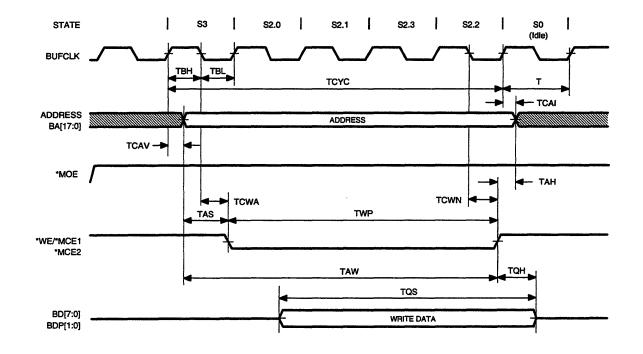

|     | 8.3.7   | SRAM Timing (Write, 2T Access)                | 169 |

|     | 8.3.8   | SRAM Timing (Write, 3T Access)                | 170 |

|     | 8.3.9   | SRAM Timing (Write, 4T Access)                | 171 |

|     | 8.3.10  | SRAM Timing (Write, 5T Access)                | 172 |

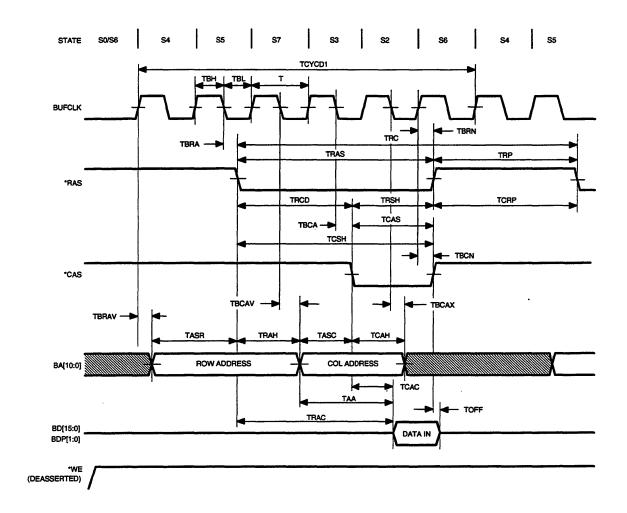

|     | 8.3.11  | DRAM Timing (No Wait State, One Byte Read)    |     |

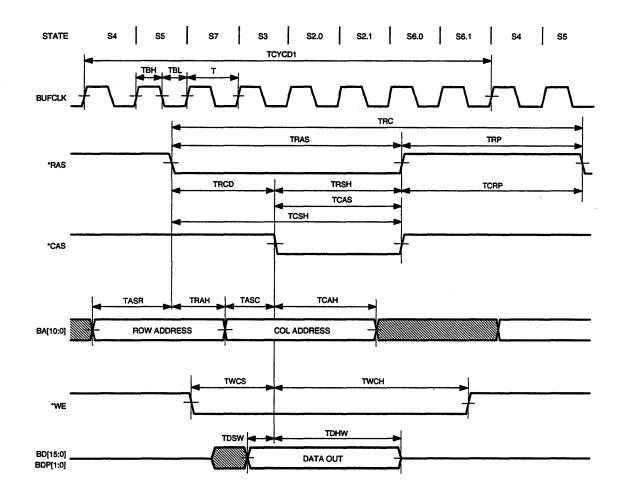

|     | 8.3.12  | DRAM Timing (Wait State, One Byte Read)       | 174 |

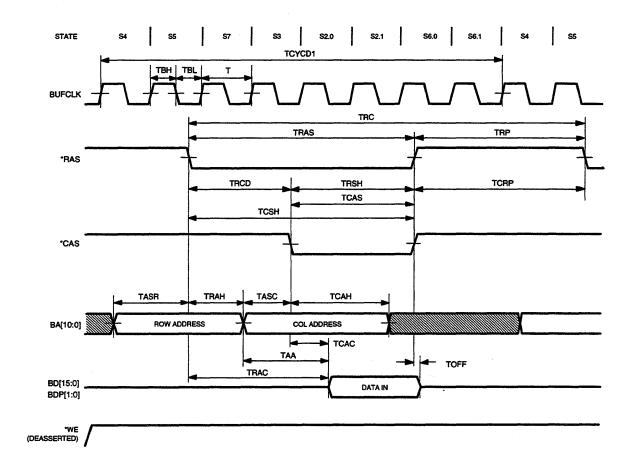

|     | 8.3.13  | DRAM Timing (No Wait State, One Byte Write)   | 175 |

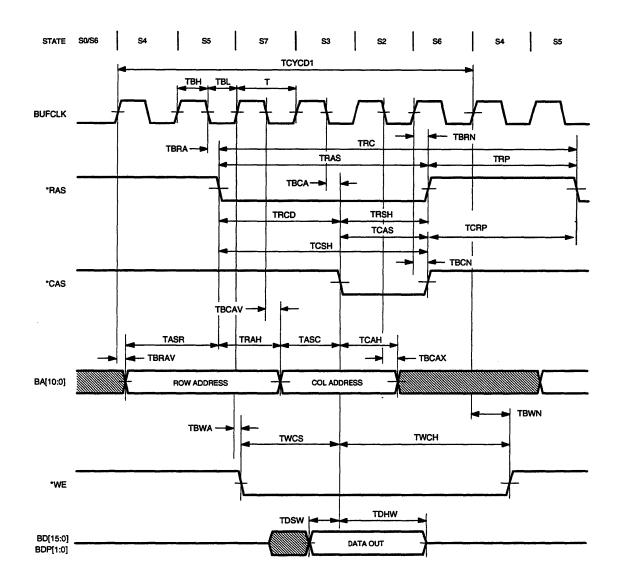

|     | 8.3.14  | DRAM Timing (Wait State, One Byte Write)      | 176 |

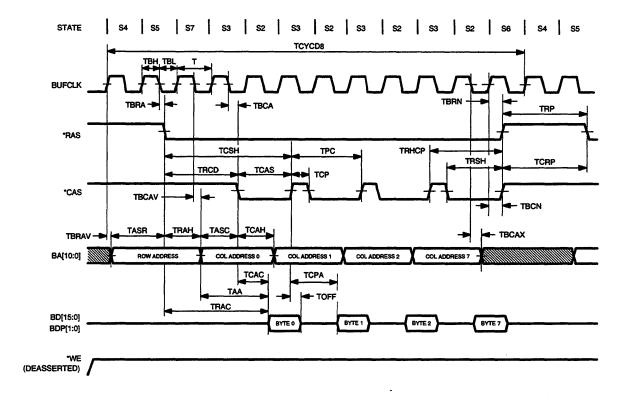

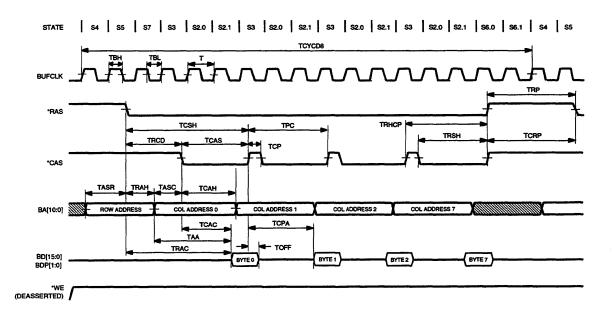

|     | 8.3.15  | DRAM Timing (Page Mode, No Wait State, Read)  | 177 |

|     | 8.3.16  | DRAM Timing (Page Mode, Wait State, Read)     | 177 |

|     | 8.3.17  | DRAM Timing (Page Mode, No Wait State, Write) | 178 |

|     | 8.3.18  | DRAM Timing (Page Mode, Wait State, Write)    | 179 |

|     | 8.3.19  | DRAM Timing (Refresh, No Wait State)          |     |

|     | 8.3.20  | DRAM Timing (Refresh, Wait State)             |     |

| 8.4 | Disk In | Iterface Timing                               |     |

|     | 8.4.1   | Disk Timing Parameters                        |     |

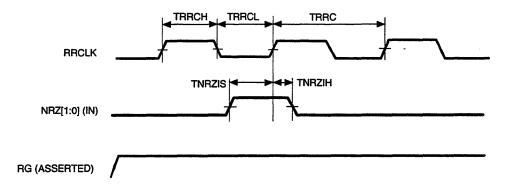

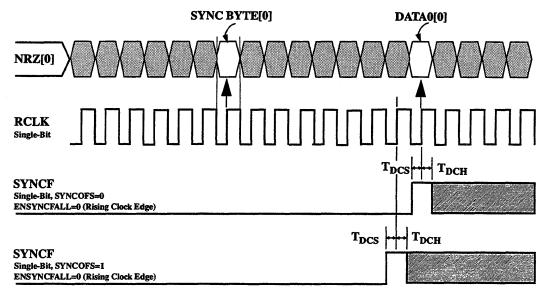

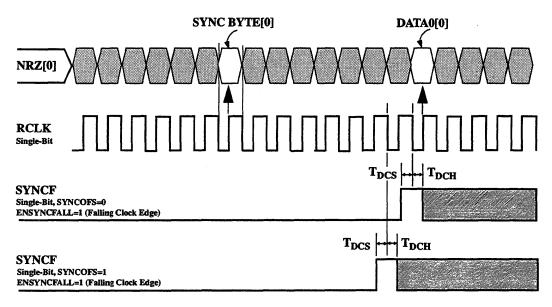

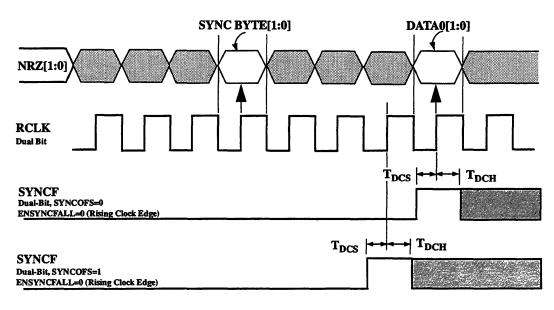

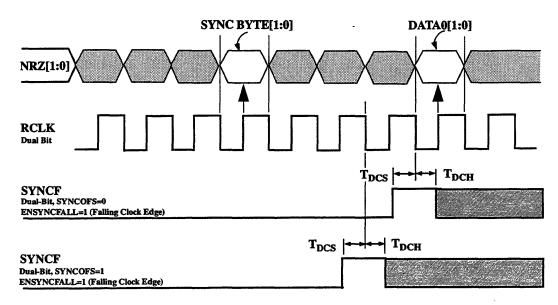

|     | 8.4.2   | Single- and Dual-Bit: Disk Read Timing        |     |

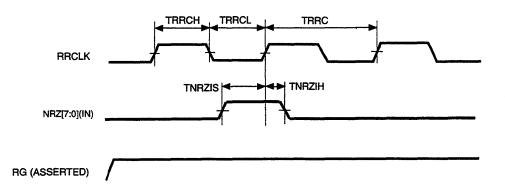

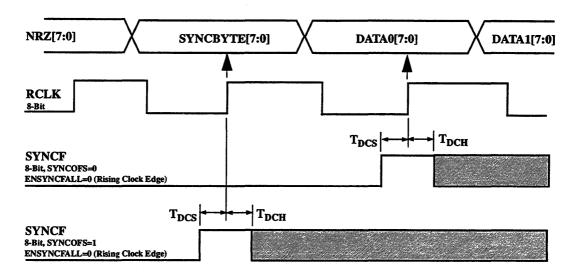

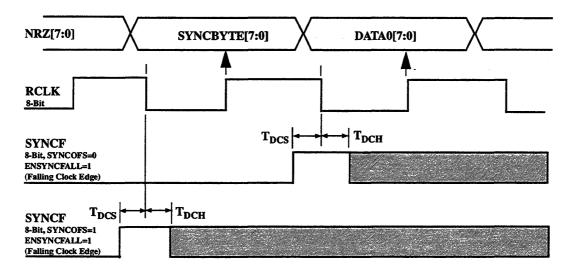

|     | 8.4.3   | Eight-Bit: Disk Read Timing                   |     |

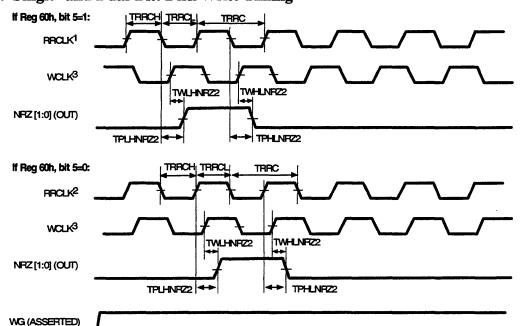

|     | 8.4.4   | Single- and Dual-Bit: Disk Write Timing       |     |

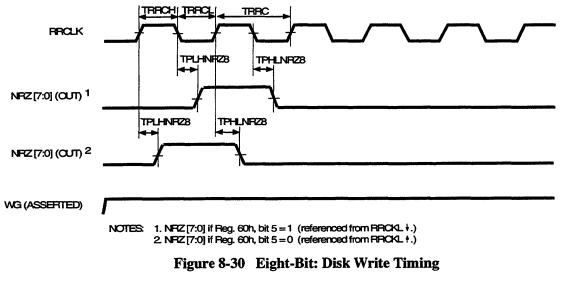

|     | 8.4.5   | Eight-Bit: Disk Write Timing                  |     |

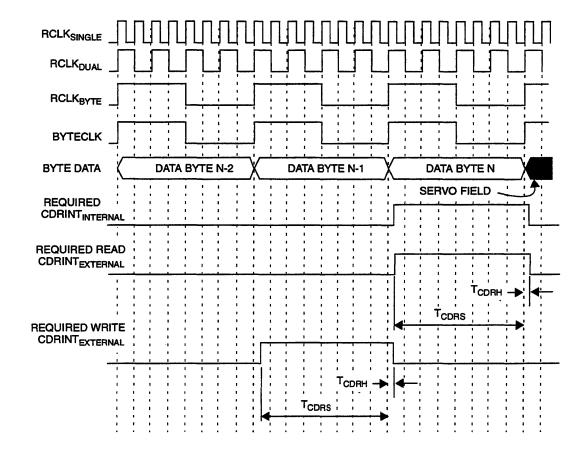

|     | 8.4.6   | Disk Control Timing                           |     |

|     | 8.4.7   | External Sync Found Timing                    | 184 |

| 8.5 | AT Hos  | st Interface Timing                           | 188 |

|     | 8.5.1   | AT Host Timing Parameters                     |     |

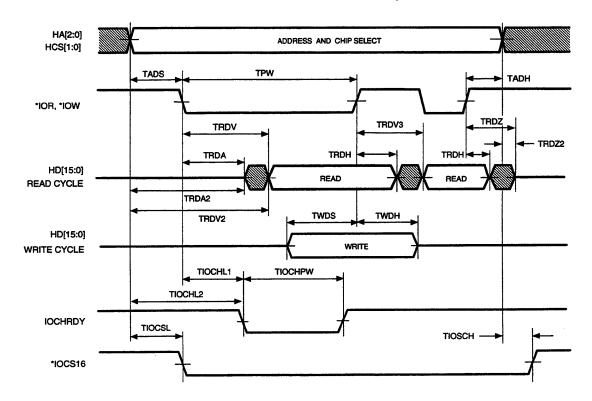

|    |       | 8.5.2    | AT PIO Timing                                                | 189 |

|----|-------|----------|--------------------------------------------------------------|-----|

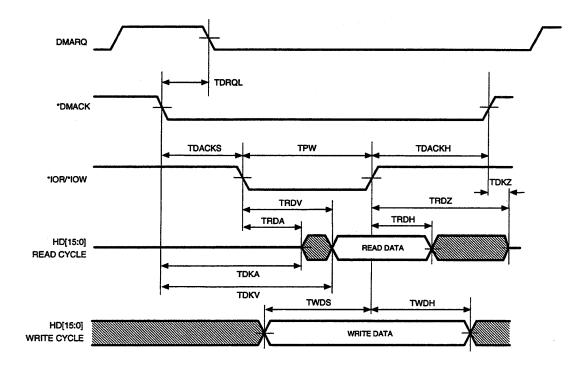

|    |       | 8.5.3    | AT Single-Word DMA Timing                                    | 190 |

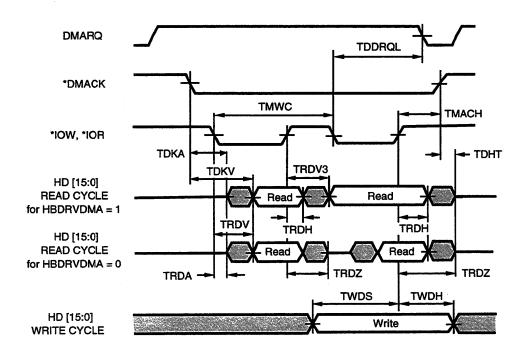

|    |       | 8.5.4    | AT Multi-Word DMA Timing                                     | 190 |

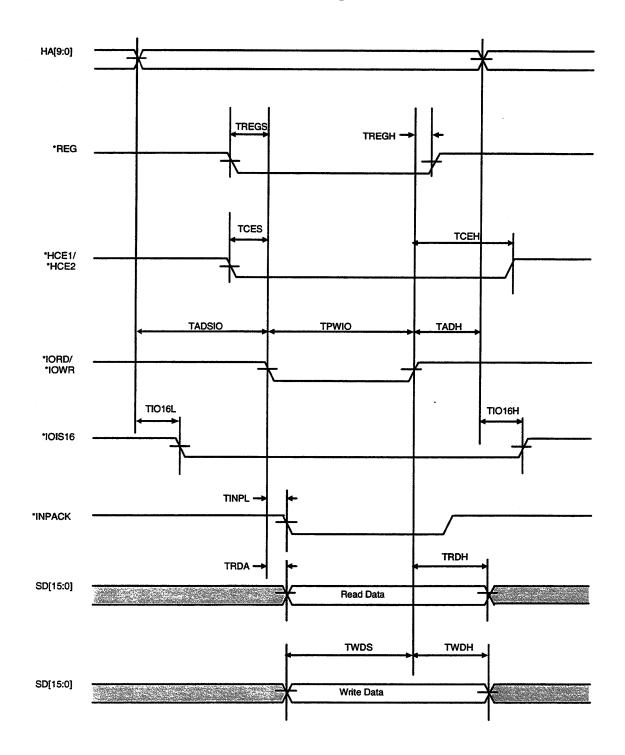

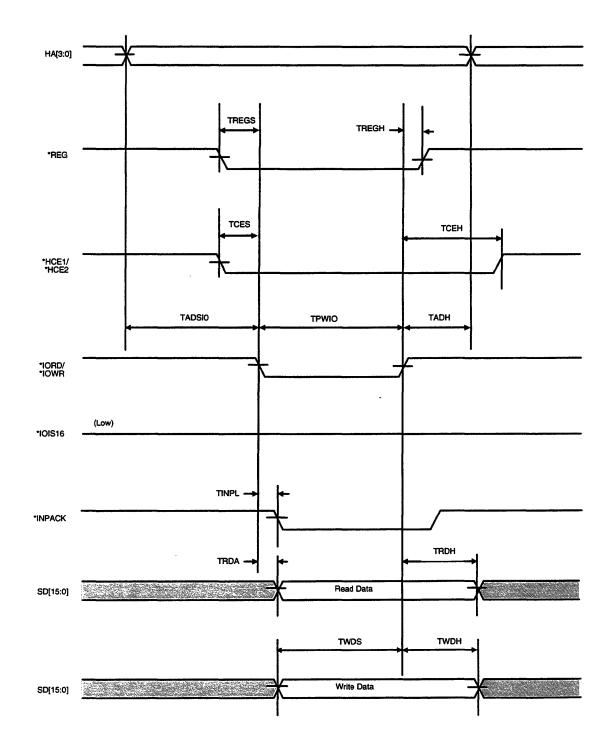

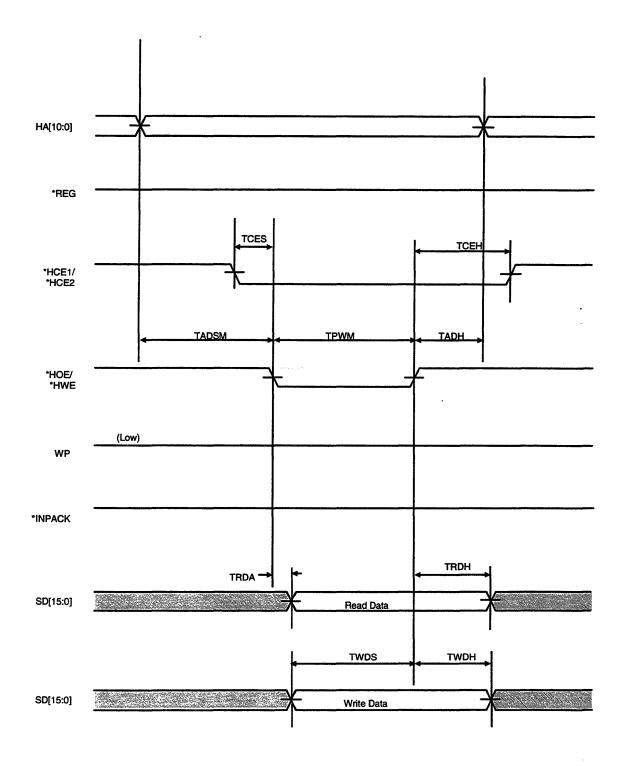

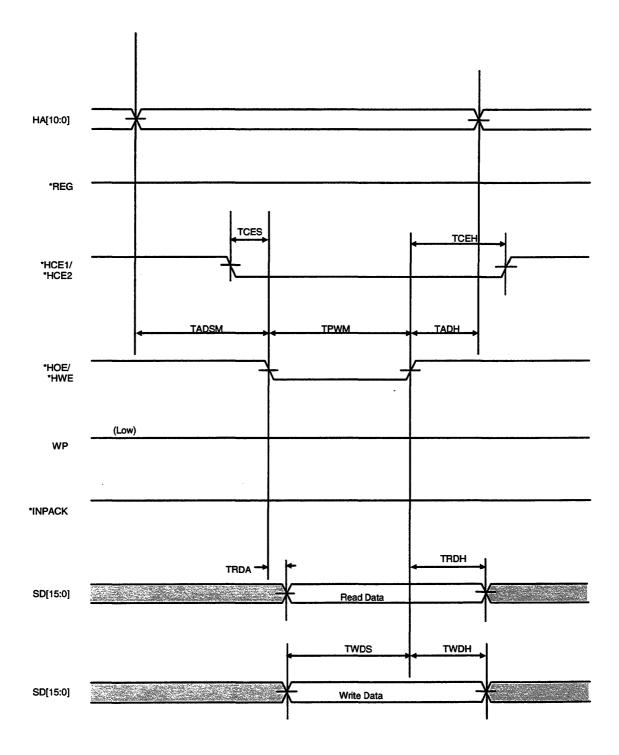

|    | 8.6   | PCMCI    | IA Host Interface Timing                                     | 191 |

|    |       | 8.6.1    | PCMCIA Host Timing Parameters                                | 191 |

|    |       | 8.6.2    | PCMCIA Attribute Memory Read/Write Timing                    | 192 |

|    |       | 8.6.3    | PCMCIA Primary/Secondary Input/Output Addressing Mode Timing | 193 |

|    |       | 8.6.4    | PCMCIA Block Mode Input/Output Addressing Mode Timing        | 194 |

|    |       | 8.6.5    | PCMCIA Memory Addressing Mode Timing                         | 195 |

|    |       |          |                                                              |     |

| SE | CTION | 9 - PAC  | CKAGING SPECIFICATIONS                                       | 197 |

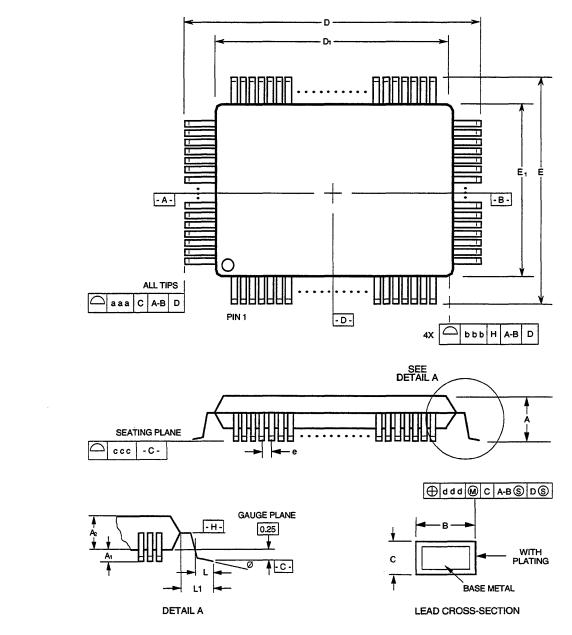

|    | 9.1   | AIC-83   | 75 MQFP Packaging Specifications                             | 197 |

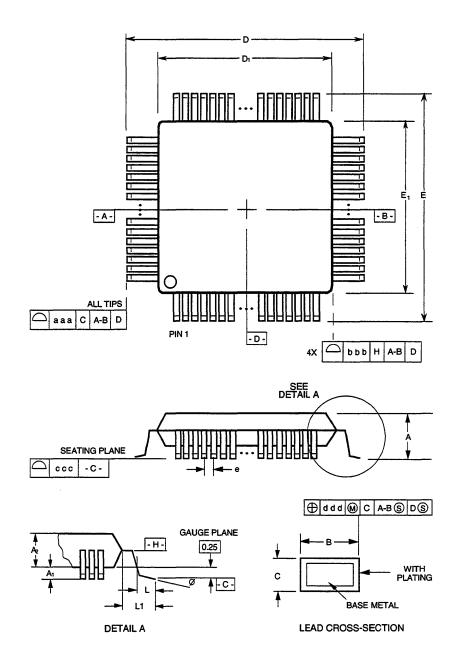

|    | 9.2   | AIC-83   | 75 TQFP Packaging Specifications                             | 199 |

|    |       |          |                                                              |     |

| AD | DEND  | UM - OF  | PERATIONAL CHARACTERISTICS                                   | 201 |

|    | A1.1  | Host Bl  | lock - No operational characteristics noted.                 | 201 |

|    | A1.2  | Buffer ] | Block - No operational characteristics noted.                | 201 |

|    | A1.3  |          | lock                                                         |     |

|    |       | A1.3.1   | Reset 2 Index Timeout Operational Characteristic             | 201 |

|    | A1.4  | Microp   | rocessor Block - No operational characteristics noted.       | 201 |

|    | A1.5  | ECC BI   | lock - No operational characteristics noted.                 | 201 |

|    |       |          |                                                              |     |

# List of Tables

| Table 2-1 | Disk Interface Pin Descriptions                                 | 7   |

|-----------|-----------------------------------------------------------------|-----|

| Table 2-2 | Buffer Interface Pin Descriptions                               | 10  |

| Table 2-3 | Host Interface Pin Descriptions                                 | 15  |

| Table 2-4 | Microprocessor Interface Pin Definitions                        | 21  |

| Table 2-5 | Power/Ground Pin Descriptions                                   | 24  |

| Table 5-1 | AT Task File/Command Registers (definition during CHS mode)     |     |

| Table 5-2 | AT Task File/Command Registers (definition during LBA mode)     | 132 |

| Table 5-3 | AT Task File/Control Block Registers                            | 136 |

| Table 6-1 | Relationship Between Byte Time and Read Reference Clock (RRCLK) |     |

| Table 6-2 | Disk Sequencer Data Sources                                     | 141 |

| Table 6-3 | Sequencer Program Flow Instructions                             | 141 |

| Table 9-1 | AIC-8375 MQFP Package Dimensions                                |     |

| Table 9-2 | AIC-8375 TQFP Package Dimensions                                |     |

.

# List of Figures

| Figure 1-1  | AIC-8375 Block Diagram                               | 2   |

|-------------|------------------------------------------------------|-----|

| Figure 2-1  | AIC-8375 MQFP Pin Assignments                        | 5   |

| Figure 2-2  | AIC-8375 TQFP Pin Assignments                        | 6   |

| Figure 6-1  | Sequencer Map Format                                 |     |

| Figure 6-2  | Blank Sequencer Map                                  | 149 |

| Figure 8-1  | AC Input/Output Timing                               |     |

| Figure 8-2  | Intel Multiplexed Mode                               | 158 |

| Figure 8-3  | Intel Non-Multiplexed Mode                           |     |

| Figure 8-4  | Motorola Multiplexed Mode                            |     |

| Figure 8-5  | Motorola Non-Multiplexed Mode                        |     |

| Figure 8-6  | Microprocessor Ready Timing (Buffer RAM Read Cycle)  |     |

| Figure 8-7  | Microprocessor Ready Timing (Buffer RAM Write Cycle) |     |

| Figure 8-8  | Microprocessor Ready Timing                          |     |

| Figure 8-9  | SRAM Timing (Read, 2T Access)                        |     |

| Figure 8-10 | SRAM Timing (Read, 3T Access)                        |     |

| Figure 8-11 | SRAM Timing (Read, 4T Access)                        |     |

| Figure 8-12 | SRAM Timing (Read, 5T Access)                        |     |

| Figure 8-13 | SRAM Timing (Write, 2T Access)                       |     |

| Figure 8-14 | SRAM Timing (Write, 3T Access)                       |     |

| Figure 8-15 | SRAM Timing (Write, 4T Access)                       |     |

| Figure 8-16 | SRAM Timing (Write, 5T Access)                       |     |

| Figure 8-17 | DRAM Timing (No Wait State, One Byte Read)           |     |

| Figure 8-18 | DRAM Timing (Wait State, One Byte Read)              |     |

| Figure 8-19 | DRAM Timing (No Wait State, One Byte Write)          |     |

| Figure 8-20 | DRAM Timing (Wait State, One Byte Write)             |     |

| Figure 8-21 | DRAM Timing (Page Mode, No Wait State, Read)         |     |

| Figure 8-22 | DRAM Timing (Page Mode, Wait State, Read)            |     |

| Figure 8-23 | DRAM Timing (Page Mode, No Wait State, Write)        |     |

| Figure 8-24 | DRAM Timing (Page Mode, Wait State, Write)           |     |

| Figure 8-25 | DRAM Timing (Refresh, No Wait State)                 |     |

| Figure 8-26 | DRAM Timing (Refresh, Wait State)                    |     |

| Figure 8-27 | Single- and Dual-Bit: Disk Read Timing               |     |

| Figure 8-28 | Eight-Bit: Disk Read Timing                          |     |

| Figure 8-29 | Single- and Dual-Bit: Disk Write Timing              |     |

| Figure 8-30 | Eight-Bit: Disk Write Timing                         |     |

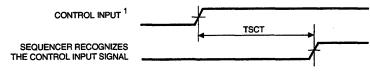

| Figure 8-31 | Disk Control Input Timing                |     |

|-------------|------------------------------------------|-----|

| Figure 8-32 | External Sync Found Timing               |     |

| Figure 8-33 | External CDR Interrupt Timing            |     |

| Figure 8-34 | AT PIO Timing                            |     |

| Figure 8-35 | AT Single-Word DMA Timing                |     |

| Figure 8-36 | AT Multi-Word DMA Timing                 |     |

| Figure 8-37 | PCMCIA Attribute Memory R/W Timing       |     |

| Figure 8-38 | PCMCIA Primary/Secondary I/O Mode Timing |     |

| Figure 8-39 | PCMCIA Block I/O Mode Timing             |     |

| Figure 8-40 | PCMCIA Memory Mode R/W Timing            | 195 |

| Figure 9-1  | 128 Pin MQFP Package Outline             |     |

| Figure 9-2  | 128 Pin TQFP Package Outline             |     |

# **REVISION NOTES** for AIC-8375B Data Sheet (PN 700191-011 Rev 5) - December 1995

In this document, all changes to **technical information** incorporated by document Rev 4 (interim release) and Rev 5 are indicated by a change bar in the left-hand margin. The sections and pages affected are listed in the table below. Included are all final AC characterization timing data for the rev B chip. (Superficial or non-technical edits are not indicated.)

Changes incoporated by Rev 5 only are noted with bold section and page numbers in the table below.

| Section<br>Updated | Pages<br>Affected | Change Description                                                                                                                                    |  |

|--------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Overali            |                   | Miscellaneous changes/corrections, and all AC characterization timing data have been incorporated as indicated.                                       |  |

| 3.3                | 28                | Reg. 9Fh (ECC Indirect Data (moto)) has been deleted. Register 9Eh is always used for ECC Indirect Data regardless of Swapmode bit for Motorola mode. |  |

| 4.3                | 41                | Reg. 9Fh has been deleted. See description for page 28 above.                                                                                         |  |

| 5.2                | 55                | Correction made to register 60h (Disk Control 0 Reg.) bit 5 (ENNRZFALL).                                                                              |  |

|                    | 66                | Changes made to register 7Bh (Disk Modulo 64 Counter).                                                                                                |  |

| 7.3                | 152 &153          | DC char data: Changes made to Sleep Mode and Power-Down mode data.                                                                                    |  |

| 8.2                | 156 &157          | AC char timing data: Changes made to microprocessor timing parameter data                                                                             |  |

| 8.3                | 164 & 166         | AC char timing data: Changes made to buffer timing parameter data.                                                                                    |  |

| 8.4                | 181               | AC char timing data: Changes made to disk timing parameter data.                                                                                      |  |

| 8.4                | 182               | Changes made to notes 6 and 7 clarifying Disk Write timing parameter data.                                                                            |  |

| 8.5                | 183               | Changes made to clarify Disk Write timing diagrams, Figures 8-29 and 8-30.                                                                            |  |

| 8.5                | 188               | AC char timing data: Changes made to AT host timing parameter data.                                                                                   |  |

| 9 new              | 197 - 200         | New package dimensioning information corrections and additions.                                                                                       |  |

| Addendum           | 201 - 204         | There are new buffer, disk, ECC, and microprocessor operational characteris-<br>tics described in the Addendum.                                       |  |

#### Changes incorporated into document Rev 4 and Rev 5:

#### **1.1 Introduction**

The Adaptec AIC-8375 is an automated single-chip disk controller designed for high performance, headerless ATA and PCMCIA drive applications. The AIC-8375 is a feature enhancement of the AIC-8371 which includes EDSA Headerless support, a fixed 168 bit ECC that supports triple burst on-the-fly hardware correction, PCMCIA interface support, and a 2K direct address range for the microprocessor. The AIC-8375 is pin compatible with the AIC-8371 in ATA mode.

The AIC-8375 is capable of executing full track read/write operations, at a maximum disk rate of up to 50 Mbits/sec in single NRZ mode, 100 Mbits/sec in dual NRZ mode, and 120 Mbits/sec in byte wide NRZ mode, with complete automation including full automation of the various sub functions such as error detection and correction, buffer data flow management, embedded servo or defect algorithms, and AT or PCMCIA interface management. The various functional blocks within the device work together automatically to ensure proper data flow management and data integrity. This automation provides the local microprocessor with more bandwidth to apply to other tasks such as servo control functions and cache management. Alternately, the improved bandwidth may be applied towards the use of a lower performance microprocessor to further increase the performance/price ratio.

Designed using high speed CMOS technology, the AIC-8375 provides a hierarchy of power down and automatic wake up modes for power sensitive applications.

#### **1.2 General Description and Features**

The AIC-8375 works in conjunction with a local microprocessor to perform the AT or PCMCIA interface control, buffer data flow management, disk format/read/write control, and error correction functions of an embedded disk drive controller. The microprocessor communicates with the AIC-8375 by reading from and writing to its various internal registers.

To the microprocessor, the registers of the AIC-8375 appear as unique memory or I/O locations that are randomly accessed and operated upon. By reading from and writing to the registers, the local microprocessor initiates operations and examines the status of the different functional blocks. Once an operation is started, successful completion or an error condition may cause the AIC-8375 to interrupt the local microprocessor, which then examines the status registers of the AIC-8375 and determines an appropriate course of action. The local microprocessor may also poll the device to ascertain successful completion or error conditions.

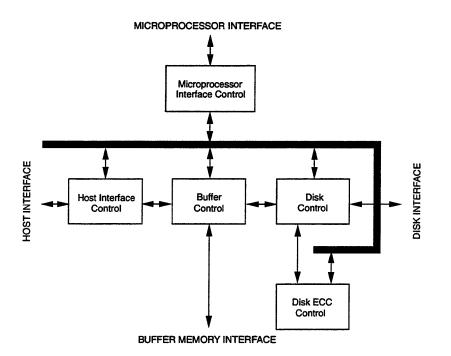

Figure 1-1 reveals the various blocks within the AIC-8375 along with their generalized interconnection. The blocks described in this figure will be referred to throughout this document.

Figure 1-1 AIC-8375 Block Diagram

#### **1.2.1 The Local Microprocessor Interface Block**

It is through the Local Microprocessor Interface Block that the local microprocessor communicates to the other control blocks within the device or to the buffer. The AIC-8375 supports Intel and Motorola type 8-bit multiplexed and non-multiplexed address/data busses. The AIC-8375 requires two chip selects, one for the internal register space and the other for directly addressing the buffer memory. Each chip select covers a 2K addressing range. The microprocessor interface block also supports a READY/DSACK line for interfacing to very fast microprocessors.

#### **1.2.2** The Host Interface Block

The AIC-8375 provides both an ATA and a PCMCIA interface to the host computer. Both provide a means for the host to access the Task File Registers used to control the transfer of data between host memory and the disk. The PCMCIA communication modes available are:

- 1. Primary/Secondary I/O Addressing Mode: This mode is compatible with existing IDE drives and ATA BIOSes. The primary addresses are 1F0h-1F7h and 3F6h-3F7h.

- 2. Block I/O Mode: This mode allows the host to locate the Task File Registers on a 16-Byte boundary in the host's I/O memory space. This allows multiple cards to coexist without I/O conflicts.

3. Attribute Memory: This is read by the host to determine information about the PCMCIA card and to change the card's configuration. It is not available in ATA mode. The Attribute Memory can be read by the host at any time the AIC-8375 is not in a busy state.

The AIC-8375 Attribute Memory consists of two parts:

*Card Information Structure*: This data structure contains readable tuple configuration data. This is a user-defined interface that supports up to 256 Bytes of information. The CIS is not writable by the host.

*Configuration Registers*: These registers return information about the current configuration. The host can write to these registers to change the current configuration (e.g., change from Memory to a Block I/O Addressing Mode).

4. Memory Mode: The Task File Registers are mapped into memory along with a 1KByte block of memory for data transfers. The PCMCIA specification refers to this memory as Common Memory.

The Host Interface Block can be programmed to execute various host read/write commands either completely automatically without any microprocessor intervention, semi-automatically with minimal microprocessor intervention, or manually with the aid of the microprocessor.

#### **1.2.3 The Buffer Control Block**

The Buffer Control block manages the flow of data into and out of the buffer. Significant automation is incorporated which allows buffer activity to take place automatically during read/write operations between the host and the disk. This automation works together with automation within the Host Control and Disk Control blocks to provide more bandwidth for the local microprocessor to perform non-data flow functions.

The buffer control circuitry keeps track of buffer full and empty conditions and automatically works with the Disk Control block to stop transfers to or from the disk when necessary. In addition, transfers to or from the host are automatically stopped or started based on buffer full or empty status.

#### **1.2.4 The Disk Control Block**

The AIC-8375 Disk Control block manages the flow of data between the disk and the buffer. It is capable of performing completely automated track read and write operations at a maximum data rate of 50 Mbits/sec in single NRZ mode, 100 Mbits/sec in dual NRZ mode, or 120 Mbits/sec in byte-wide NRZ mode. Many flexible features and elements of automation have been incorporated to complement the automation contributed by the Host and Buffer blocks.

The Disk Control block consists of the programmable 31 by 3 byte sequencer, CDR/data split logic, disk FIFO, fault tolerant sync detect logic, and other support logic.

#### **1.2.5 The Disk ECC Block**

The AIC-8375 supports a fixed 168 bit 3-way interleaved Reed-Solomon ECC. The code is capable of correcting up to three 17-bit bursts or one 65-bit burst in hardware. The Disk ECC block also supports up to 48 bits of seed data to the ECC generator to allow for greater data integrity in a headerless environment. The ECC will also detect up to three 17-bit bursts or one 89-bit burst errors. Software provides correction with burst limiting.

#### **1.2.6 Power Management**

Power management features are incorporated into each block of the AIC-8375. This allows the designer to tailor the amount of power management to the specific design as required. Other power management features include:

- Independent power management control for each block.

- ECC logic automatically powered down when not in use and powered up when needed.

- Disk sequencer and associated disk logic powered up when the sequencer is started.

- Weak pull-up structure on input pins to prevent undesirable power consumption due to floating CMOS inputs.

#### **1.2.7 Headerless Architecture**

The AIC-8375 supports an Enhanced Data Sector headerless architecture. This is an enhancement of the headerless architecture currently in production with the AIC-8371.

This architecture is based on the sequencer flushing then loading the CDR FIFO every data sector pulse. The chip does not require the servo microprocessor to suppress sector pulses. The microprocessor determines alignment with the media using EOS counts. Once on track and using the EOS count the microprocessor can set the servo CDR pointer to the CDR word for the sector following the EOS pulse. The microprocessor also invalidates the first CDR word of every sector that the microprocessor would like to skip (i.e. defective sectors, spare sectors and unrequested sectors). This architecture can support ZLR. The microprocessor loads the Sector Address register with the data sector number of the first sector to be read. The sequencer increments the sector address after successful transfer with the buffer of a sector. This allows the microprocessor the ability to know which sector had an error if an error occurs.

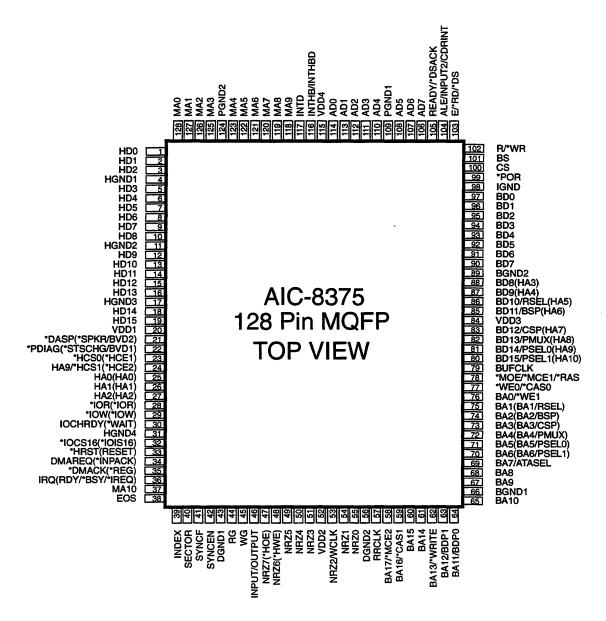

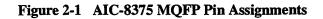

Figures 2-1 and 2-2 show the pinouts of the AIC-8375. Many signal pins have pullup resistors (refer to Section 7 for pull-up, hysteresis, and other values). Most pullups can be enabled/disabled via the Device Control registers (reg. 50h, R/W, bit 7 and reg. 51h, R/W, bits 7, 6, & 4) as described in Section 5 of this document.

Figure 2-2 AIC-8375 TQFP Pin Assignments

# 2.1 AIC-8375 Disk Interface Pins

Refer to Section 7 of this document for hysteresis and pull-up values.

| SYMBOL<br>(* = active low) | PIN #<br>(MQFP) | ТҮРЕ              | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------|-----------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EOS                        | 38              | I<br>(hysteresis) | END OF SERVO: This is a programmable input pin used to signal the end of a servo burst field. This input is edge sensitive with the polarity programmable via the ACTHIEOS bit (reg. 63h, R/W, bit 4).                                                                                                                                                                         |

| INDEX                      | 39              | I<br>(hysteresis) | INDEX: This is a programmable level edge sensitive input pin<br>used to signal the Index point on the track of a Disk Drive HDA.<br>The polarity is programmable via the ACTHIIDX bit (reg. 63h,<br>R/W, bit 5). The leading (asserting) edge of the Index signal will<br>set the INDEXPASS bit (reg. 65h, R/W, bit 5). This signal pin<br>can be tested in the Sequencer Map. |

| SECTOR                     | 40              | I<br>(hysteresis) | SECTOR: This is a programmable level edge sensitive input<br>used to signal hard sector marks (SECTOR). The Disk<br>Sequencer uses this as a branch condition, and it must be at least<br>2 BUFCLK periods in duration. The polarity is programmed<br>with the ACTHISEC bit (reg. 63h, R/W, bit 6). The Disk<br>Sequencer can be programmed to branch on this signal.          |

| SYNCFND                    | 41              | I<br>(hysteresis) | EXTERNAL SYNC FOUND: This is an active high input used<br>to indicate when the external Sync Detect logic has found the<br>sync byte. The polarity of this bit is programmable via the<br>ACTHISFND bit (reg. 63h, R/W, bit 7).                                                                                                                                                |

| SYNCEN                     | 42              | O<br>(4 mA)       | EXTERNAL SYNC DETECT ENABLE: This pin is an active high output used to enable an external sync detector. This pin is asserted via the "Wait For Sync Instruction" decode in the Sequencer Map.                                                                                                                                                                                 |

| RG                         | 44              | O<br>(4 mA)       | READ GATE: This is an active high output signal controlled by<br>the Disk Sequencer, and it is used to enable the external Disk<br>Drive Read circuitry.                                                                                                                                                                                                                       |

| WG                         | 45              | I/O<br>(4 mA)     | WRITE GATE: This is an active high output signal controlled by<br>the Disk Sequencer, and it is used to enable the external Disk<br>Drive Write circuitry. When it is high the appropriate NRZ pins<br>for the NRZ mode are driven.                                                                                                                                            |

|                            |                 | ,                 | This pin is an input during Host Standalone Test Mode only.                                                                                                                                                                                                                                                                                                                    |

#### **Table 2-1 Disk Interface Pin Descriptions**

| SYMBOL<br>(* = active low) | PIN #<br>(MQFP) | ТҮРЕ                                        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------|-----------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INPUT/OUTPUT               | 46              | I/O<br>(4 mA w/<br>pull-up &<br>hysteresis) | INPUT BRANCH / OUTPUT CONTROL: This pin can be pro-<br>grammed to be either an input or output of the disk sequencer. It<br>can be used by the disk sequencer for branching on external<br>events or for external control and status. If the ENOUPUT bit<br>(reg. 62h, R/W, bit 4) is set, this pin is configured as an output.<br>As an output, it is directly controlled via the Set and Reset OUT-<br>PUT control instructions in the disk sequencer. If ENOUTPUT<br>is cleared, this pin is used as a level sensitive input branch condi-<br>tion in the disk sequencer. |

| NRZ7<br>(*HOE)             | 47              | I/O<br>(8 mA w/<br>pull-up &<br>hysteresis) | DISK SERIAL NRZ I/O BIT 7/HOST OUTPUT ENABLE:<br><u>ATA MODE</u> - NRZ7: When WG is set this pin is bit 7 of the<br>active high serial NRZ output, but it is only valid when in 8-bit<br>NRZ Mode. When RG is set this pin is an input.<br><u>PCMCIA MODE</u> - *HOE: Refer to (*HOE) description in<br>Table 2-3.                                                                                                                                                                                                                                                           |

| NRZ6<br>(*HWE)             | 48              | I/O<br>(8 mA w/<br>pull-up &<br>hysteresis) | DISK SERIAL NRZ I/O BIT 6/HOST OUTPUT ENABLE:<br><u>ATA MODE</u> - NRZ6: When WG is set this pin is bit 6 of the<br>active high serial NRZ output, but it is only valid when in 8-bit<br>NRZ Mode. When RG is set this pin is an input.<br><u>PCMCIA MODE</u> - *HWE: Refer to (*HWE) description in<br>Table 2-3.                                                                                                                                                                                                                                                           |

| NRZ[5:3]                   | 49-51           | I/O<br>(4 mA w/<br>pull-up)                 | DISK NON RETURN TO ZERO [5:3]: These bits are used to<br>send or receive bits 5:3 of the NRZ data to or from the drive.<br>These bits are used only when the NRZSEL[1:0] bits (reg. 60h,<br>R/W, bits 3:2) are set to '10', selecting 8-bit NRZ mode. These<br>bits are driven while WG is asserted and receive data while RG<br>is asserted.                                                                                                                                                                                                                                |

| NRZ2/WCLK                  | 53              | I/O<br>(8 mA w/<br>pull-up)                 | DISK NON RETURN TO ZERO [2] / WRITE CLOCK: When<br>8-bit NRZ mode is selected (NRZSEL[1:0] = '10'), this pin is<br>configured as NRZ2 and is driven while WG is asserted and<br>receives data while RG is asserted. If 8-bit NRZ mode is not<br>selected, this pin is configured as the disk write clock output<br>which provides better setup and hold times for disk write opera-<br>tions than RRCLK. In this mode, a clock will always be present<br>on the pin regardless of the state of WG or RG.                                                                     |

| SYMBOL<br>(* = active low) | PIN #<br>(MQFP) | ТҮРЕ                        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------|-----------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NRZ[1:0]                   | 54, 55          | I/O<br>(8 mA w/<br>pull-up) | DISK NON RETURN TO ZERO [1:0]: These signal pins func-<br>tion as the two least significant bits of 8-bit NRZ data if 8-bit<br>NRZ mode is selected. If Dual bit NRZ mode is selected, these<br>two bits are used to send and receive data in bit-pairs to and from<br>the drive. If Single bit NRZ mode is selected, only NRZ0 is<br>used to input or output a serial NRZ bit stream (refer to reg. 60h,<br>R/W, bits 3:2). |

| RRCLK                      | 57              | Ι                           | READ / REFERENCE CLOCK: This pin is the input reference<br>clock for the Disk controller logic. NRZ data is synchronized to<br>it during reads and writes.                                                                                                                                                                                                                                                                   |

| Table 2-1 | Disk Int | erface Pin | Descriptions | (Continued) |

|-----------|----------|------------|--------------|-------------|

|-----------|----------|------------|--------------|-------------|

# 2.2 AIC-8375 Buffer Interface Pins

Refer to Section 7 of this document for hysteresis and pull-up values.

| SYMBOL<br>(* = active low) | PIN #<br>(MQFP) | ТҮРЕ                        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------|-----------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BA17/*MCE2                 | 58              | 0<br>(4 mA)                 | BUFFER ADDRESS [17] / *MEMORY CHIP SELECT 2: This<br>is an active high output pin used as address bit 17 in SRAM<br>mode (256K) or an active low Chip Select in a two SRAM con-<br>figuration. Dual SRAM mode is selected when the RAMSEL<br>[2:0] bits (reg. 100h, R/W, bits 5:3) are set to '100', '101', or '110'.                                                                                                                                                                                    |

| BA16/*CAS1                 | 59              | O<br>(8 mA)                 | BUFFER ADDRESS [16] /*COLUMN ADDRESS STROBE 1: This<br>is an active high output pin used as address bit 16 in SRAM<br>mode or an active low High Byte (bits 15:8) Column Address<br>Strobe in DRAM mode.                                                                                                                                                                                                                                                                                                 |

| BA[15:14]                  | 60, 61          | 0<br>(4 mA)                 | BUFFER ADDRESS [15:14]: These are active high output pins<br>for address bits [15:14] in SRAM mode. They are not used in<br>DRAM mode.                                                                                                                                                                                                                                                                                                                                                                   |

| BA13/*WRITE                | 62              | 0<br>(4 mA)                 | BUFFER ADDRESS [13] / *DRAM WRITE: This is the active<br>high SRAM address bit 13 in SRAM mode or the active low<br>write control for DRAM using early write mode access when in<br>DRAM Mode.                                                                                                                                                                                                                                                                                                           |

| BA12/BDP1                  | 63              | I/O<br>(4 mA w/<br>pull-up) | BUFFER ADDRESS [12] / BUFFER DATA PARITY 1: This is<br>the active high SRAM address bit 12 in SRAM mode or the<br>active high Buffer Data parity for BD[15:8] in DRAM mode.                                                                                                                                                                                                                                                                                                                              |

| BA11/BDP0                  | 64              | I/O<br>(4 mA w/<br>pull-up) | BUFFER ADDRESS [11] / BUFFER DATA PARITY 0: This is<br>the active high SRAM address bit 11 in SRAM mode or the<br>active high Buffer Data parity for BD[7:0] in DRAM mode.                                                                                                                                                                                                                                                                                                                               |

| BA[10:8]                   | 65,<br>67, 68   | 0<br>(4 mA)                 | BUFFER ADDRESS [10:8]: In SRAM mode, these pins are<br>buffer addresses [10:8]. In DRAM mode, they are used as the<br>row and column address lines.                                                                                                                                                                                                                                                                                                                                                      |

| BA7/ATASEL                 | 69              | I/O<br>(4 mA w/<br>pull-up) | BUFFER ADDRESS[7] / ATA/*PCMCIA CONFIG PIN:<br>At power on time (negation of *POR) this pin is automatically<br>checked. If it is a 1, ATA Mode is selected; if it is a 0, PCMCIA<br>Mode is selected (an external 6.8K pull-down resistor is used to<br>bias this pin low). During this reset time the output driver is dis-<br>abled; at all other times this pin is bit 7 of the Buffer Address. In<br>ATA Mode, the MPU Configuration pins are on BD[15:10]; in<br>PCMCIA Mode, they are on BA[6:1]. |

#### Table 2-2 Buffer Interface Pin Descriptions

| SYMBOL<br>(* = active low)                                          | PIN #<br>(MQFP) | ТҮРЕ                        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------------------------------------------------------|-----------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BA[6:1]<br>(BA[6:1]/<br>PSEL[1:0],<br>PMUX,<br>CSP<br>BSP,<br>RSEL) | 70-75           | I/O<br>(4 mA w/<br>pull-up) | ATA MODE -<br>BUFFER ADDRESS[6:1]: These are active high output pins<br>used to address the Buffer Memory.<br><u>PCMCIA MODE</u> -<br>BUFFER ADDRESS[6:1] / ATA/*PCMCIA CONFIG PIN:<br>At power on time these pins are the MPU Configuration pins<br>which are checked when *POR is negated. The output drivers<br>are disabled at this time. At all other times they are bits 6:1 of<br>the Buffer Address. Refer to the ATA pin definitions for<br>BD[15:10] to determine the MPU Configuration operation. An<br>external 6.8K pull-down resistor is used to bias each pin low at<br>power on time. |

| BA0/*WE1                                                            | 76              | O<br>(8 mA)                 | BUFFER ADDRESS [0] / *WRITE ENABLE 1: This is a multifunction output pin based on the type and width of RAM used.<br>In DRAM mode and in 8-bit SRAM mode, this pin is configured<br>as BA0. In 16-bit SRAM mode, it is configured as *WE1 and is<br>used as the SRAM Write Enable signal for BD[15:8] only.                                                                                                                                                                                                                                                                                           |

| *WE0/*CAS0                                                          | 77              | O<br>(8 mA)                 | *MEMORY WRITE ENABLE 0 / *COLUMN ADDRESS<br>STROBE 0: In DRAM mode, this pin is an active low output<br>used for the CAS function. In SRAM mode, it is configured as<br>the Write Enable signal to the SRAM bits 7:0. RAM SELECT<br>[2:0], (reg. 100h, R/W, bits 5:3) establishes the function of this<br>pin.                                                                                                                                                                                                                                                                                        |

| *MOE/*MCE1/<br>*RAS                                                 | 78              | O<br>(8 mA)                 | *MEMORY OUTPUT ENABLE / *MEMORY CHIP ENABLE 1 /<br>*ROW ADDRESS STROBE: In DRAM mode, this pin is an active low output used for the RAS function. In SRAM mode it is an active low output function of Output Enable (*MOE) or Chip Enable (*MCE1). RAM SELECT [2:0], (reg. 100h, R/W, bits 5:3) establishes the function of this pin.                                                                                                                                                                                                                                                                 |

| BUFCLK                                                              | 79              | Ι                           | BUFFER CLOCK: This input is the clock source for the Buffer Controller and Host Interface logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

#### Table 2-2 Buffer Interface Pin Descriptions (Continued)

•

| SYMBOL<br>(* = active low)             | PIN #<br>(MQFP) | ТҮРЕ                                        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------------------|-----------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BD[15:14] /<br>PSEL[1:0]<br>(HA[10:9]) | 80, 81          | I/O<br>(4 mA w/<br>pull-up &<br>hysteresis) | ATA MODE -<br>BUFFER DATA [15:14] / PROCESSOR SELECT: These pins<br>are dual function pins. On the rising (negating) edge of Power<br>On Reset (*POR), these pins are internally sampled. Based<br>upon the value of PSEL[1:0] (see AIC-8375 User's Guide) at<br>this sample time, the device will be configured to interface with<br>a specific microprocessor. At all other times, these pins function<br>as bits [15:14] of the Buffer Data bus. These pins incorporate<br>internal pullup resistors to bias the pins high. A 6.8K Ohm<br>external resistor tied to ground can be used to pull down these<br>pins. Without any external pulldown resistors, the default value<br>of PSEL[1:0] after *POR is '11'.<br><u>PCMCIA MODE</u> -<br>HOST ADDRESS[10:9]: These pins are active high inputs used |

| BD13/PMUX<br>(HA8)                     | 82              | I/O<br>(4 mA w/<br>pull-up &<br>hysteresis) | as bits 10:9 of the Host Address.<br><u>ATA MODE</u> -<br>BUFFER DATA [13] / PROCESSOR BUS MODE: This is a<br>dual function pin. On the rising (negating) edge of Power On<br>Reset (*POR) this pin is internally sampled. If it is found to be<br>high, the device is configured for multiplexed microprocessor<br>bus mode. If found to be low, the device is configured for non-<br>multiplexed microprocessor bus mode. At all other times, this<br>pin functions as bit 13 of the Buffer Data bus. This pin has an<br>internal pullup resistor to bias the pin high. A 6.8K Ohm pull-<br>down resistor is externally used to pull it down. Without an<br>external pulldown resistor, the default value of PMUX after<br>*POR is '1' (multiplexed mode).                                               |

|                                        |                 |                                             | PCMCIA MODE -<br>HOST ADDRESS[7]: This pin is an active high input used as<br>bit 8 of the Host Address.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SYMBOL<br>(* = active low) | PIN #<br>(MQFP) | ТҮРЕ                                        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------|-----------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BD12/CSP<br>(HA7)          | 83              | I/O<br>(4 mA w/<br>pull-up &<br>hysteresis) | ATA MODE -<br>BUFFER DATA [12] / CHIP SELECT POLARITY: This is a<br>dual function pin. On the rising (negating) edge of Power On<br>Reset (*POR) this pin is internally sampled. If found to be low,<br>the polarity of the Chip Select (CS) pin is inverted. If found to<br>be high, the polarity is not inverted. At all other times, this pin<br>functions as bit 12 of the Buffer Data bus. This pin has an inter<br>nal pullup resistor to bias the pin high. A 6.8K Ohm pulldown<br>resistor is externally used to pull it down.                                                                                                                                            |

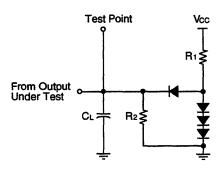

|                            |                 |                                             | <u>PCMCIA MODE</u> -<br>HOST ADDRESS[7]: This pin is an active high input used as<br>bit 7 of the Host Address.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |