# adaptec

| AHA-1740A/1742A/17<br>EISA-to-Fast SCSI Host | 744<br>Adapter |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

|----------------------------------------------|----------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Technical Reference Mar                      | nual           |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

|                                              |                |     | **************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

|                                              |                |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

|                                              |                |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

|                                              |                |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

|                                              |                |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

|                                              |                |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

|                                              |                |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

|                                              |                |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

|                                              |                |     | tool Delagange are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

|                                              |                |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

|                                              |                |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

|                                              |                |     | ***************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

|                                              |                |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

|                                              |                |     | ***************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

|                                              |                |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

|                                              |                | . • |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

|                                              |                |     | and the latest of the latest o |      |

|                                              |                |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

|                                              |                |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

|                                              |                |     | ***************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <br> |

| *                                            |                |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

## adaptec

AHA-1740A/1742A/1744 EISA-to-Fast SCSI Host Adapter

Technical Reference Manual

#### Copyright

© Copyright 1992 Adaptec, Inc. All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means; electronic, mechanical, photocopying, recording or otherwise, without the prior written consent of Adaptec, Inc., 691 South Milpitas Blvd., Milpitas, CA 95035.

#### **Trademarks**

EISA is a registered trademark of BCPR Services Inc.

Intel is a registered trademark, and 286, 386 are trademarks of Intel Corporation.

$\operatorname{IBM}$ , OS/2, PC AT, and Micro Channel are registered trademarks of International Business Machines Corporation.

MS-DOS, MS, Windows, Xenix, and Microsoft are registered trademarks of Microsoft Corporation.

Novell and NetWare are registered trademarks of Novell, Inc.

QEMM is a trademark of Quarterdeck Office Systems.

SCO is a trademark of the Santa Cruz Operation.

SYTOS and Sytos Plus are trademarks of Sytron Corporation.

QRAM, Move Em, and 386-Max are trademarks of Qualitas, Inc.

UNIX is a registered trademark of AT&T Bell Laboratories.

#### Changes

The material in this manual is for information only and is subject to change without notice. While reasonable efforts have been made in the preparation of this manual to assure its accuracy, Adaptec, Inc. assumes no liability resulting from errors or omissions in this manual, or from the use of the information contained herein.

Adaptec reserves the right to make changes in the product design without reservation and without notification to its users.

Additional information may be obtained from:

#### adaptec

Literature Department - MS/40 691 South Milpitas Blvd. Milpitas, CA 95035

#### **FCC Compliance Statement**

NOTE: This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15 of the FCC rules. These limits are designed to provide reasonable protection against harmful interference in residential installations. This equipment generates, uses, and can radiate radio frequency energy, and if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation.

If this equipment does cause interference to radio or television equipment reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

- Reorient or relocate the receiving antenna

- Move the equipment away from the receiver

- Plug the equipment into an outlet on a circuit different from that to which the receiver is powered

- If necessary, the user should consult the dealer or an experienced radio/television technician for additional suggestions

CAUTION: Only equipment certified to comply with Class B (computer input/output devices, terminals, printers, etc.) should be attached to this equipment, and must have shielded interface cables.

Finally, any change or modifications to the equipment by the user not expressly approved by the grantee or manufacturer could void the user's authority to operate such equipment.

Each AHA-1740A/1742A/1744 is equipped with an FCC compliance label which shows only the FCC Identification number. This device complies with part 15 of the FCC rules. Operation is subject to the following two conditions: (1) this device may not cause harmful interference and (2) this device must accept any interference received, including interference that may cause undesired operation.

iv

## **Table of Contents**

|    | Prelace                                                  |      |

|----|----------------------------------------------------------|------|

|    | Conventions                                              | X11  |

|    |                                                          |      |

|    |                                                          |      |

| Ch | apter One - Introduction                                 |      |

|    | Document Scope                                           | 1-1  |

|    | Purpose                                                  |      |

|    | AHA-1740A/1742A/1744 Product Features                    |      |

|    | EISA Features                                            |      |

|    | SCSI Features                                            |      |

|    | Board Features                                           |      |

|    | Configuration Diskette and Installation Guide (ASW-C174) | 1-4  |

|    | Product Specifications                                   | 1-5  |

|    | Extended Industry-Standard Architecture Interface        |      |

|    | Standard EISA Bus Electronic and Physical Interface      |      |

|    | SCSI Interface                                           |      |

|    | Electrical Interface for AHA-1740A/1742A                 |      |

|    | Electrical Interface for AHA-1744                        |      |

|    | Internal Connector                                       | 1-7  |

|    | External Connector                                       | 1-8  |

|    | Floppy Disk Interface                                    | 1-9  |

|    | Standard Electronic and Physical interface               |      |

|    | Connector                                                | 1-9  |

|    | Radiation Immunity                                       | 1-9  |

|    | Reference Documents                                      | 1-9  |

|    |                                                          |      |

| Cn | napter Two - Architecture                                |      |

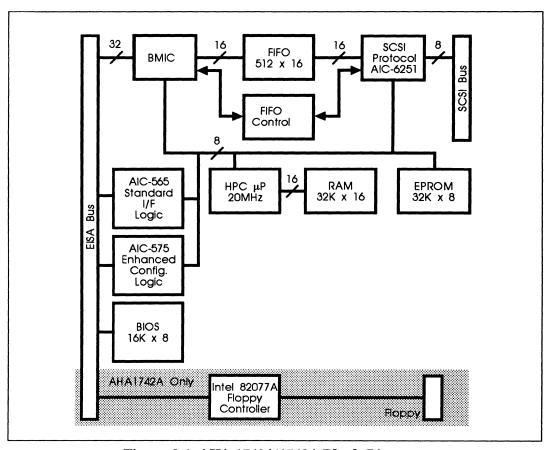

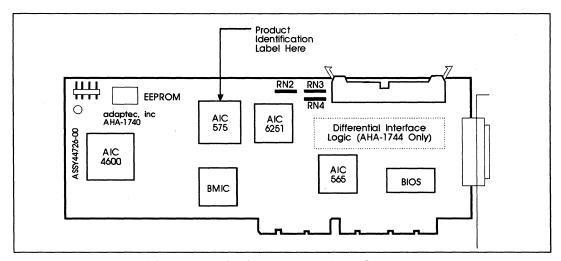

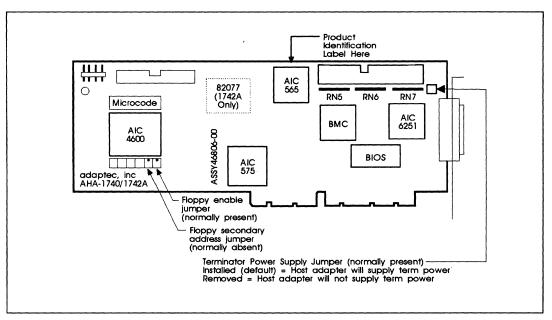

|    | Hardware                                                 | 2-1  |

|    | Bus Master DMA                                           | 2-2  |

|    | SCSI Interface and Protocol Chip (AIC-6251)              | 2-2  |

|    | 8- and 16-Bit Memory and Odd Byte Data Transfers         | 2-3  |

|    | Bus Auxiliary Interface Chip (AIC-565)                   | 2-3  |

|    | EISA Configuration Chip (AIC-575)                        | 2-4  |

|    | BMIC Bus Interface Chip (82355)                          | 2-4  |

|    | Floppy Disk Controller (AHA-1742A Only)                  | 2-4  |

|    | Standard Mode Firmware                                   | 2-5  |

|    | Mailboxes                                                | 2-5  |

|    | Command Control Block                                    | 2-6  |

|    | Command Descriptor Block                                 | 2-7  |

|    | Principles of Operation                                  | 2-8  |

|    | Task Queuing                                             |      |

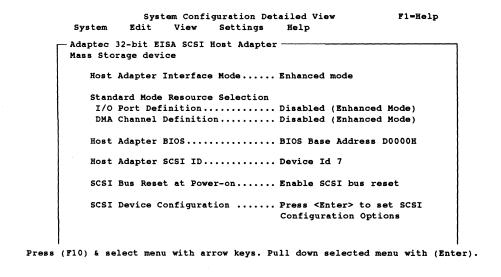

|    | Enhanced Mode Firmware                                   |      |

|    | Onboard BIOS Operation                                   |      |

|    | Power-Up Diagnostics                                     | 2-11 |

|    |                                                          |      |

|    | ASW-C174 Configuration Diskette                   | 2-12 |

|----|---------------------------------------------------|------|

|    |                                                   |      |

| Cn | apter Three - Installation                        |      |

|    | Unpacking and Inspection                          |      |

|    | Installation                                      |      |

|    | System Configuration Background for Standard Mode |      |

|    | Preparation                                       |      |

|    | Termination                                       |      |

|    | SCSI Addressing (ID)                              |      |

|    | SCSI Parity                                       |      |

|    | Hardware Installation                             |      |

|    | Checklist                                         |      |

|    | Terminators                                       |      |

|    | System Configuration                              |      |

|    | MCS Configuration                                 |      |

|    | Standard Mode SCSI Configuration                  |      |

|    | Enhanced Mode SCSI Configuration                  |      |

|    | Multiple Adapters Sharing Same SCSI Bus           |      |

|    | Phoenix Configuration                             |      |

|    | Floppy Disk Configuration                         |      |

|    | ADL Utility                                       |      |

|    | ADL Operation                                     |      |

|    | List of Adapters                                  |      |

|    | Main Menu                                         |      |

|    | Download Firmware (AHA-1740/1744 Only)            |      |

|    | Firmware Information (AHA-1740/1744/1740A/1742A)  |      |

|    | Low-level Format                                  | 3-18 |

| Ch | apter Four - Hardware Functional Description      |      |

|    | •                                                 | 4.1  |

|    | Hardware OverviewStandard Mode I/O Port Interface |      |

|    | I/O Port Interface Bit Definition                 |      |

|    | Control and Status Port                           |      |

|    | Command/Data Out and Data In Port                 |      |

|    | Interrupt Flag Port                               |      |

|    | Reset Functions                                   |      |

|    | Hard Reset Operations                             |      |

|    | SCSI Reset Operations                             |      |

|    | SCSI Soft Reset Option                            |      |

|    | SCSI Hard Reset Option                            |      |

|    | EISA Expansion Identifiers                        |      |

|    | Expansion Board ID Registers                      |      |

|    | Board Configuration Registers                     |      |

|    | I/O Port Register Standard Mode (Group 1)         |      |

|    | I/O Port Register Enhanced Mode (Group 2)         |      |

|    | Diskette Registers                                |      |

|    |                                                   |      |

| Digital Output Registers (Write 3F2)                         |      |

|--------------------------------------------------------------|------|

| Diskette Controller Registers (Read/write 3F4 and 3F5)       | 4-24 |

| Digital Input Register (Read 3F7)                            | 4-25 |

| Diskette Control Register (Write 3F7)                        | 4-25 |

| Firmware Download (AHA-1740/1744 Only)                       | 4-26 |

| Hardware Configuration Requirements                          | 4-27 |

| SCSI Configuration                                           | 4-27 |

| BIOS Driver Needs                                            | 4-28 |

| SCSI Subsystem Configuration                                 | 4-28 |

| Initialize SCSI Subsystem Command (Standard Mode)            | 4-28 |

| Initialize SCSI Subsystem Command (Enhanced Mode)            | 4-28 |

| Configuration Byte Description and Defaults                  | 4-29 |

| Chapter Five - Standard Mode Firmware Description            | 1    |

| Host Adapter Command Overview                                | 5-1  |

| No Operation (Operation Code 00)                             | 5-2  |

| Mailbox Initialization (Operation Code 01)                   | 5-2  |

| Start SCSI Command (Operation Code 02)                       | 5-3  |

| Start PC AT BIOS Command (Operation Code 03)                 |      |

| Adapter Inquiry (Operation Code 04)                          |      |

| Enable Mailbox Out Available Interrupt (Operation Code 05)   |      |

| Set Selection Time out (Operation Code 06)                   |      |

| Set Bus On Time (Operation Code 07)                          | 5-5  |

| Set Bus Off Time (Operation Code 08)                         |      |

| Set Transfer Speed (Operation Code 09)                       |      |

| Return Installed Devices (Operation Code 0A)                 |      |

| Return Configuration Data (Operation Code 0B)                |      |

| Enable Target Mode Command (Operation Code 0C)               |      |

| Return Setup Data (Operation Code 0D)                        |      |

| Initialize SCSI Subsystem (Operation Code 10)                |      |

| Return Firmware Checksum (Operation Code 11)                 |      |

| Write Adapter Channel 2 Buffer (Operation Code 1A)           |      |

| Read Adapter Channel 2 Buffer (Operation Code 1B)            |      |

| Write Adapter FIFO Buffer (Operation Code 1C)                |      |

| Read Adapter FIFO Buffer (Operation Code 1D)                 |      |

| Echo Command Data (Operation Code 1F)                        |      |

| Adapter Diagnostic (Operation Code 20)                       |      |

| Set Host Adapter Options (Operation Code 21)                 |      |

| Mailbox Overview                                             |      |

| Mailbox Out Definition                                       |      |

| Mailbox In Definition                                        |      |

| Command Block Definition                                     |      |

| Command Control Block Format                                 |      |

| Scatter/Gather List Definition                               |      |

| Description of Operation                                     |      |

| Execution of Initiator Mode Operations                       |      |

| Execution of Target Mode Operations With a Prepared CCB      |      |

| Execution of Target Mode Operations Without a Prepared CCB   |      |

| DMA Channel Initialization (with Host Adapter BIOS Disabled) | 5-31 |

| hapter Six - Enhanced Mode Firmware Descript            | tion         |

|---------------------------------------------------------|--------------|

| Introduction                                            | 6-1          |

| Control Block                                           |              |

| Command Word                                            | 6-4          |

| Flag Word 1                                             | 6-4          |

| Flag Word 2                                             |              |

| Data or Scatter/Gather List Pointer                     |              |

| Data or Scatter/Gather List Length                      | 6-11         |

| Status Block Pointer                                    |              |

| Chain Address                                           |              |

| Sense Information Pointer                               |              |

| Sense Length                                            |              |

| CDB Length                                              |              |

| Checksum of Data                                        |              |

| SCSI Command Descriptor Block                           |              |

| Status Block                                            |              |

| Status Word                                             | 6-14         |

| Host Adapter Status                                     | 6-17         |

| Target Status                                           | 6-17         |

| Residual Byte Count                                     |              |

| Residual Buffer Address                                 | <b>6-1</b> 8 |

| Additional Status Length                                | 6-19         |

| Sense Length                                            | 6-19         |

| Target Mode CDB                                         |              |

| Control Block Commands                                  |              |

| Download Firmware                                       | 6-21         |

| Initialize SCSI Subsystem                               | 6-23         |

| Initiator SCSI Command                                  |              |

| No Operation                                            | 6-27         |

| Read Host Adapter Inquiry Data                          |              |

| Read Sense Information                                  |              |

| Run Diagnostic Test                                     | 6-36         |

| Target SCSI Command                                     | 6-38         |

| Aborting Control Block Commands                         | 6-39         |

| Control Block is Queued for Operation                   | 6-40         |

| Associated Target for the Control Block is Disconnected | 6-40         |

| Control Block is Currently Active on the SCSI Bus       | 6-40         |

| Control Block in the Interrupt Queue                    | 6-40         |

| Asynchronous Event Notification                         | 6-41         |

| Asynchronous Event Conditions                           | 6-41         |

| SCSI Bus Reset                                          | 6-41         |

| Host Adapter Selected by Another Initiator              |              |

| Immediate Commands                                      | 6-42         |

| Reset                                                   |              |

| Reset Device                                            |              |

| Reset Host Adapter                                      | 6-45         |

| SCSI Bus Reset Handling                                       | 6-46              |

|---------------------------------------------------------------|-------------------|

|                                                               | 6-46              |

|                                                               | 6-47              |

|                                                               | 6-47              |

| reset initiated by finding Sooi Device.                       | V-1               |

| Chapter Seven - Onboard BIOS Inte                             | rface             |

| Introduction                                                  | 7-1               |

| Operation with the Standard Interface                         |                   |

|                                                               |                   |

|                                                               | 7-2               |

|                                                               | alled             |

| Enhanced Interface Operation                                  |                   |

|                                                               | 7-2               |

|                                                               |                   |

|                                                               | 7-2               |

|                                                               |                   |

| Interrupt 13h Interface Functionality                         |                   |

|                                                               | slation7-5        |

|                                                               | slation7-5        |

|                                                               | 7-6               |

| Hardware BIOS Commands                                        | 7-7               |

| Int 15h Functionality                                         | 7-9               |

| Differences Between Operating Modes                           | 7-9               |

| Multiple Adapter Support                                      |                   |

| Chapter Eight - Device Drivers  DOS Operation without Drivers | 8-1               |

|                                                               | 8-1               |

|                                                               | 8-1               |

| System Configuration                                          |                   |

| Low-Level Format                                              |                   |

| Installation and Initialization Under DOS                     |                   |

|                                                               |                   |

| Managers                                                      |                   |

|                                                               | 8-4               |

|                                                               | emory Managers8-5 |

|                                                               | 8-E               |

|                                                               | 8-6               |

| Unix/Xenix Manager                                            | 8-6               |

| Chapter Nine - SCSI Features                                  | <del></del>       |

| Initiator Mode SCSI Description                               | 9-1               |

|                                                               | 9-2               |

|                                                               | 9-2               |

| Lord Lawring Iwaa Operation                                   |                   |

|      | SCSI Messages                                         | 9-3         |

|------|-------------------------------------------------------|-------------|

|      | Target Mode SCSI Description                          |             |

|      | Initiator Conformance Level Requirements              | <b>9-</b> 3 |

|      | Synchronous Transfer Support                          | 9-4         |

|      | SCSI Target Operation in Processor Target Mode        |             |

|      | Incorrect Length Management for Target Mode Operation |             |

|      | Aborting Target Mode Commands                         |             |

|      | č č                                                   |             |

|      |                                                       |             |

| Cha  | pter Ten - Problem Determination                      |             |

|      |                                                       |             |

|      | Self Diagnostic Capability                            |             |

|      | Indicators                                            |             |

|      | Problems Detected During Operation                    | 10-2        |

|      | HA Status Error Indications and Corrective Actions    | 10-3        |

|      | SCSI Error Indications and Corrective Actions         | 10-5        |

|      | Problems Detected During Installation                 | 10-6        |

|      |                                                       |             |

|      |                                                       |             |

| Cha  | pter Eleven - Glossary                                |             |

|      | ·                                                     |             |

|      | Glossary of Terms                                     | 11-1        |

|      |                                                       |             |

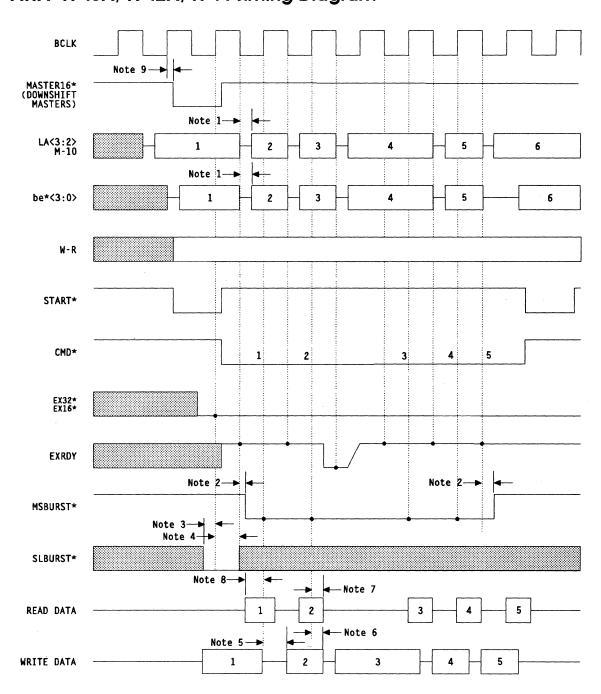

| Anne | endix A - Memory Cycle Timing Diagram                 |             |

| VPP. | ondix A - Momory Cycle Illining Diagram               |             |

|      | AHA-1740A/1742A/1744 Timing Diagram                   | A-1         |

|      |                                                       |             |

|      |                                                       |             |

| App  | endix B - Connector Pinout                            |             |

|      |                                                       |             |

|      | Internal Connector Pin Assignments                    | B-1         |

|      | External Connector Pin Assignments                    | B-3         |

|      |                                                       |             |

| App  | endix C - Register Reference                          |             |

|      | •                                                     |             |

|      | System Register Reference                             | C-1         |

|      |                                                       |             |

| Ann  | endix D - EISA Free-Form Data                         |             |

| APP. | CHAIN D - LIVA HEG-LOHH DUIG                          |             |

|      | SCSI Subsystem Data Structure                         | D-1         |

|      |                                                       |             |

#### **Preface**

This Technical Reference Manual provides technical information for Adaptec's AHA-1740A/1742A/1744 EISA-to-Fast SCSI Host Adapters. It is prepared for customer technical personnel requiring detailed information on the operation of the board at a register and command protocol level. Documentation of board schematics, integrated circuits, microcode and BIOS routines is not provided.

Programmers writing device drivers for specific perpherals are strongly advised to use the Advanced SCSI Programming Interface (ASPI) specification appropriate to the operating system chosen. This will allow flexibility across all boards complying with ASPI Manager modules and prevent obsolescence. Please contact Adaptec Corporate Communications for copies of ASPI specifications. Software managers are documented and sold separately.

Every effort has been made to ensure the technical accuracy of this reference manual. If you believe that inaccuracies exist, please communicate this information in writing to your local field applications support personnel or directly to the product manager.

## **Conventions**

The following typographic conventions are used throughout this Technical Reference Manual.

#### bold

Used for keystrokes (.. press the **Enter** key ..) and screen selection fields (.. select **Backup Device** and ..).

#### Helvetica

Used for operator entry that must be typed exactly as shown (.. device=c:\cdrom\cdrom.tsd..) and for screen messages (.. Enter Password ..).

#### Helvetica Italics

Used as a placeholder for text you must determine and type in (.. enter *nn* for number ..). Also used for program and file names in body text (.. the *autoexec.bat* file ..).

#### **Italics**

Used for emphasis (.. is *only* supported ..) and document reference (.. refer to Chapter Three, *Installation* ..).

#### ALL CAPITALS

Used for acronyms (..the SCSI device..).

## **Chapter One**

## Introduction

## **Document Scope**

This manual provides information on installation and defines the program interfaces of the AHA-1740A/1742A/1744 intelligent host adapters in EISA bus-based systems. Programming peripheral drivers directly to the hardware interface of the board is not recommended. The ASPI (Advanced SCSI Programming Interface) specifications provide a simpler and more flexible interface which is protected against changes, upgrades and obsolescence of the boards.

## **Purpose**

The Adaptec AHA-1740A/1742A/1744 provides a powerful multitasking interface between the Extended Industry Standard Architecture (EISA) bus and the Small Computer System Interface (SCSI) bus.

The AHA-1740A/1742A/1744 is a high-performance intelligent host adapter which supports a maximum asynchronous SCSI rate of 2.0 MBytes/second and a synchronous transfer rate of 10.0 MBytes/second. It supports multithreaded I/O operations, allowing simultaneous operations on multiple targets/LUNs. Disconnect/Reconnect support maximizes bus utilization for multiple target systems. Target mode operation allows the AHA-1740A/1742A/1744 to receive information from other host adapters. Scatter/Gather allows high performance even in systems with fragmented memory buffers.

The AHA-1740A/1742A/1744 provides a solution for system applications requiring very high performance, configuration flexibility, multithreaded I/O capability, and system redundancy. The Adaptec BIOS also allows the AHA-1740A/1742A/1744 to be used in place of a standard hard disk controller.

The AHA-1740A/1742A host adapter provides high-performance host adapter circuitry connected to the more common single-ended SCSI bus. The SCSI specification recommended maximum cable length for 5 MBytes/second synchronous data transfer is 6 Meters, or about 20 feet.

The AHA-1744 host adapter provides identical host adapter circuitry, but connects to a differential SCSI bus. The SCSI specification recommended maximum cable length for 5 MBytes/second synchronous data transfer is 25 Meters, or about 82 feet.

## AHA-1740A/1742A/1744 Product Features

#### **EISA Features**

The AHA-1740A/1742A/1744 is a full-performance EISA board offering the highest performance available across the bus. It takes advantage of first-party DMA operations, also known as bus mastering, which allow data transfers to proceed at high data rates without system processor intervention. The main EISA functions which come standard on the board include:

- Auto Configuration Support

- High-performance Bus Master transfers with burst cycles which provide a data rate of 33 MBytes/second

- 32-bit data path

- 32-bit address space

- Even or odd starting address and byte count handling