ALPHA MICROSYSTEM AM-300

SIX PORT SERIAL INPUT/OUTPUT BOARD DESCRIPTION

ALPHA MICROSYSTEMS 17881 SKYPARK NORTH SUITE F

c 1977 BY ALPHA MICROSYSTEM

DWS-00300-00 Rev. A00 10/18/78

## ALPHA MICROSYSTEMS AM-300 SIX PORT SERIAL INPUT/OUTPUT BOARD DESCRIPTION

#### I. Introduction

The Alpha Microsystem AM-300 Six Port Serial Input/Output Board has been designed to provide six full programmable RS232 I/O ports on a single printed circuit card.

The following is a summary of the AM-300 capability:

- S-100 bus compatible

- Six fully programmable RS232 I/O ports

- 16 selectable baud rates for each I/O port under software control. (max rate = 19,200 baud)

- Synchronous and Asynchronous operating modes for each port utilizing versatile Western Digital Corporation Asynchronous Synchronous Receiver/Transmitter (UC1671B)

- Five I/O ports utilized for data and control

- Multiple level interrupt compatibility

#### II. I/O Port Definitions

Five I/O ports are required by the AM-300. These are summarized in tables I and II. The I/O port address block is jumper selectable via a plug in header (Z33) and normally is configured for I/O address DECIMEN 248

F8/through FC (HEX).

Note that the first four I/O addresses are contained in the Western Digital Corporation UC1671B ASTRO. See the data sheet on the chip for a detailed explanation of the register contents.

In addition to the registers contained in the UC1671B, there are three other functions that must be considered:

A. MUX Control Register

See table II for description of control bits.

## B. Baud Rate Programming

The baud rate for a given serial I/O channel can be programmed as follows:

- 1. Set up the MUX Control Register with bit 3 set to a "1" and bits 0-2 set to address the appropriate channel.

- 2. Write to port X0 with bits 0-3 used to select the appropriate baud rate. The Western Digital Dual Baud Rate Clock Generator (BR1941L) is utilized to provide the programmable baud rates. See the BR1941L spec sheet for detailed baud rate codes.

## C. Interrupt Programming

Interrupts can be enabled by setting bit 4 of the MUX Control Register to a "1". Once set, any of the six channels can generate an interrupt to the CPU. A single line interrupt is used for all channels. To determine which channel has generated an interrupt, the following sequence must be programmed.

- 1. After receiving the interrupt, set up the MUX Control Register with bit 5 set to a "1" and bits 0-3 set to a "0".

- 2. Read port XO. The AM-300 will return the address of the channel that has generated the interrupt according to the following format:

| Bit 7 | MSB                 |

|-------|---------------------|

| Bit 6 |                     |

| Bit 5 | Interrupting        |

| Bit 4 | Channel Number      |

| Bit 3 | LSB                 |

|       |                     |

| Bit 2 | 1 = Read Interrupt  |

|       | 2 = Write Interrupt |

The channels have been prioritized such that I/O channel 1 has the highest priority and I/O channel 6 has the lowest.

#### III. RS232 Interface

Three edge connectors are provided at the top of the AM-300

to allow connection to RS232 compatible peripherals. Each connector contains interface signals for two I/O channels. The following RS232 signals are provided:

## Inputs: 1. BB Received Data

- 2. CB Clear to send

- 3. CC Data Set Ready

- 4. CF Carrier Detector

## Outputs: 1. CD Data Terminal Ready

- 2. BA Transmitted Data

- 3. CA Request to Send

- 4. Misc Miscellaneous

TABLE I

I/O PORT DEFINITIONS

| I/O Port<br>Address ⚠ | Input                     | Output                       | Comments         |

|-----------------------|---------------------------|------------------------------|------------------|

| XO                    | Control Register 1        | Control Register 1           | See UC1671B spec |

| X1                    | Control Register 2        | Control Register 2           | See UC1671B spec |

| X2                    | SYN and DLE Register      | Status Register              | See UC1671B spec |

| Х3                    | Receiver Holding Register | Transmitter Holding Register | See UC1671B spec |

| X4                    |                           | MUX Control Register         | See Table II     |

<sup>1</sup> the base I/O Port address (shown as 0) is jumper selectable to any block of eight I/O addresses.

## TABLE II MUX CONTROL REGISTER (X4)

| Bit | Function                | Comments                                                                                              |

|-----|-------------------------|-------------------------------------------------------------------------------------------------------|

| 0   | Multiplex Control Bit 0 | 3 bit code addressed                                                                                  |

| 1   | Multiplex Control Bit 1 | the appropriate RS232 channel. Legal addresses are 1-6.                                               |

| 2   | Multiplex Control Bit 2 | negat addresses are 1-0.                                                                              |

| 3   | Program Baud Rate       | Set to "l" to program addressed channel's baud rate. Set to "0" to program addressed channel's ASTRO. |

| 4   | Interrupt Enable        |                                                                                                       |

| 5   | Read Interrupt          | Set to "l" to enable reading of interrupt vector                                                      |

## SIO-6 CABLING

| SIO-6 CABLING A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 B1 B2 | SIGNAL NAME (CD)2 DTR2- (BA)2 TXD2 (CD)1 DTR1- (MISC)2 (CA)1 RTS1- (BB)1 RXD1 (CF)2 CARDET2- (CB)1 CTS1- (CB)2 CTS2- (CC)2 DSR2- N/C N/C | DB25 J2-5 J2-3 J1-5 N/C N/C J1-2 N/C N/C N/C J/C J/C J/C |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| B3                                                 | (BA)1 TXD1                                                                                                                               | J1-3                                                     |

| B4                                                 | (CA)2 RTS2                                                                                                                               | N/C                                                      |

| B5                                                 | (MISC)1                                                                                                                                  | N/C                                                      |

| B6                                                 | (CF)1 CARDET1-                                                                                                                           | N/C                                                      |

| B7                                                 | (BB)2 RXD2                                                                                                                               | J2-2                                                     |

| B8                                                 | (CC)1 DSR1-                                                                                                                              | J1-20                                                    |

| B9                                                 | (+5VP)                                                                                                                                   | N/C                                                      |

| B10                                                | (GND)                                                                                                                                    | J1+J2-7                                                  |

## ON SIO-6 CONNECTOR JUMPER

A1 TO A10 A3 TO B8 A5 TO A8 B4 TO A9 A7 TO B6 TO B9

ON DB 25 J1+J2 JUMPER:

PINS 5, 6, and 8

DATA SHEET

DUAL BAUD RATE CLOCK

## **FEATURES**

- 16 SELECTABLE BAUD RATE CLOCK FREQUENCIES

- DUAL SELECTABLE 16 X CLOCK OUTPUTS FOR FULL DUPLEX OPERATIONS

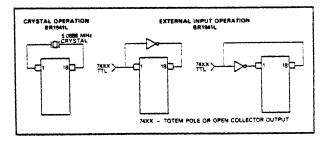

- OPERATES WITH CRYSTAL OSCILLATOR OR EXTERNALLY GENERATED FREQUENCY INPUT

- ROM MASKABLE FOR NON-STANDARD FRE-QUENCY SELECTIONS

- DIRECT UART/USRT AND TTL COMPATIBILITY

- OUTPUTS A 50% DUTY CYCLE CLOCK WITH 0.01% ACCURACY

- 18 PIN CERAMIC DIP PACKAGE

- 3 DIFFERENT FREQUENCY/DIVISOR PAIRS AVAILABLE

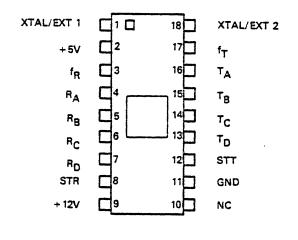

## PIN CONNECTIONS

## **GENERAL DESCRIPTION**

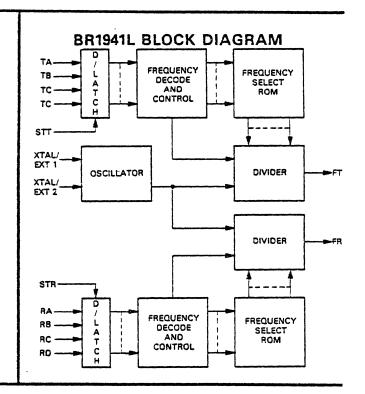

The BR1941L is a combination Baud Rate Clock Generator and Programmable Divider. It is manufactured in N-channel MOS using silicon gate technology. This device is capable of generating 16 externally selected clock rates whose frequency is determined by either a single crystal or an externally generated input clock. The BR1941L is a programmable counter capable of generating a division from 2 to (215-1).

The BR1941L is available programmed with the most used frequencies in data communication. Each fre-

quency is selectable by strobing or hard wiring each of the two sets of four Rate Select inputs. Other frequencies/division rates can be generated by reprogramming the internal ROM coding through a MOS mask change. Additionally, further clock division may be accomplished through cascading of devices. The frequency output is fed into the XTAL/EXT input on a subsequent device.

The BR1941L can be driven by an external crystal or by TTL logic. All pins are TTL compatible.

## PIN DESCRIPTION

| PIN NUMBER | SYMBOL               | NAME                           | FUNCTION                                                                                                                                                                            |  |  |  |

|------------|----------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1          | XTAL/EXT 1           | Crystal or<br>External Input 1 | This input receives one pin of the crystal package or one polarity of the external input.                                                                                           |  |  |  |

| 2          | Vcc                  | Power Supply                   | +5 volt Supply                                                                                                                                                                      |  |  |  |

| 3          | fR                   | Receiver Output<br>Frequency   | This output runs at a frequency selected by the Receiver Address inputs.                                                                                                            |  |  |  |

| 4-7        | RA,RB,RC,RD          | Receiver Address               | The logic level on these inputs as shown in Table 1, selects the receiver output frequency, f <sub>R</sub> .                                                                        |  |  |  |

| 8          | STR                  | Strobe-Receiver<br>Address     | A high-level input strobe loads the receiver address ( $R_A$ , $R_B$ , $R_C$ , $R_D$ ) into the receiver address register. This input may be strobed or hard wired to $\pm 5V$ .    |  |  |  |

| 9          | V <sub>DD</sub>      | Power Supply                   | + 12 voit Supply                                                                                                                                                                    |  |  |  |

| 10         | NC                   | No Connection                  |                                                                                                                                                                                     |  |  |  |

| 11         | GND                  | Ground                         | Ground                                                                                                                                                                              |  |  |  |

| 12         | STT                  | Strobe-Transmitter<br>Address  | A high-level input strobe loads the transmitter address ( $T_A$ , $T_B$ , $T_C$ , $T_D$ ) into the transmitter address register. This input may be strobed or hard wired to $+5V$ . |  |  |  |

| 13-16      | $T_D, T_C, T_B, T_A$ | Transmitter<br>Address         | The logic level on these inputs, as shown in Table 1, selects the transmitter output frequency, $f_T$ .                                                                             |  |  |  |

| 17         | fŢ                   | Transmitter Output Frequency   | This output runs at a frequency selected by the Transmitter Address inputs.                                                                                                         |  |  |  |

| 18         | XTAL/EXT 2           | Crystal or<br>External Input 2 | This input receives the other pin of the crystal package or the other polarity of the external input.                                                                               |  |  |  |

## **MAXIMUM GUARANTEED RATINGS**

| Operating Temperature Range                         | )°C to +70°C |

|-----------------------------------------------------|--------------|

| Positive Voltage on any Pin, with respect to ground | + 20.0V      |

| Negative Voltage on any Pin, with respect to ground | 0.3V         |

<sup>\*</sup>Stresses above those listed may cause permanent damage to the device. This is a stress rating only and Functional operation of the device at these or at any other condition above those indicated in the operational sections of this specification is not implied.

## **ELECTRICAL CHARACTERISTICS**

$(T_A = 0$ °C to 70°C,  $V_{CC} = +5V \pm 5\%$ ,  $V_{DD} = +12V \pm 5\%$ , unless otherwise noted)

| _ PARAMETER                                                                        | MIN.                  | TYP.     | MAX                    | UNIT     | COMMENTS                                             |

|------------------------------------------------------------------------------------|-----------------------|----------|------------------------|----------|------------------------------------------------------|

| DC CHARACTERISTICS                                                                 |                       |          |                        |          |                                                      |

| INPUT VOLTAGE LEVELS<br>Low-level, V <sub>IL</sub><br>High-level, V <sub>IH</sub>  | V <sub>CC</sub> - 1.5 |          | 0.8<br>V <sub>CC</sub> | <b>V</b> | excluding XTAL inputs                                |

| OUTPUT VOLTAGE LEVELS<br>Low-level, V <sub>OL</sub><br>High-level, V <sub>OH</sub> | V <sub>CC</sub> - 1.5 | 4.0      | 0.4                    | <b>V</b> | l <sub>OL</sub> = 3.2 mA<br>l <sub>OH</sub> = 100 μA |

| INPUT CURRENT<br>Low-level, I <sub>IL</sub>                                        |                       |          | 0.3                    | mA       | V <sub>IN</sub> = GND, excluding XTAL inputs         |

| INPUT CAPACITANCE All inputs, C <sub>IN</sub>                                      | 1                     | 5        | 10                     | pf       | V <sub>IN</sub> = GND, excluding XTAL inputs         |

| EXT INPUT LOAD                                                                     |                       | 4        | 5                      |          | Series 7400 unit loads                               |

| POWER SUPPLY CURRENT                                                               |                       |          |                        |          |                                                      |

| lcc<br>loo                                                                         |                       | 20<br>20 | 30<br>30               | mA<br>mA |                                                      |

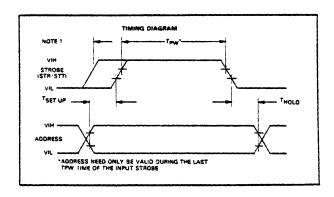

| AC CHARACTERISTICS                                                                 |                       |          |                        |          | T <sub>A</sub> = +25°C                               |

| CLOCK FREQUENCY                                                                    |                       | 5.0688   |                        | MHz      | XTAL, EXT                                            |

| PULSE WIDTH (T <sub>PW</sub> ) Clock                                               |                       |          |                        |          | 50% Duty Cycle ± 10%                                 |

| Receiver strobe                                                                    | 150                   |          | DC                     | ns       | See Note 1                                           |

| Transmitter strobe                                                                 | 150                   |          | DC                     | ns       | See Note 1                                           |

| INPUT SET-UP TIME (SET-UP) Address                                                 | 50                    |          |                        | ns       | See Note 1                                           |

| OUTPUT HOLD TIME (T <sub>HOLD</sub> ) Address                                      | 50                    |          |                        | ns       |                                                      |

NOTE 1: Input set-up time can be decreased to >0 ns by increasing the minimum strobe width by 50 ns to a total of 200 ns.

All inputs except XTAL/EXT have internal pull-up resistors.

#### **OPERATION**

#### STANDARD FREQUENCIES

Choose a Transmitter and receiver frequency from the table below. Program the corresponding address into TA-TD and RA-RD respectively using 200 nsec minimum strobe pulses or by hard wiring the strobe and address inputs.

#### **NON-STANDARD FREQUENCIES**

To accomplish non-standard frequencies do one of the following:

1. Choose a crystal that when divided by the BR1941 generates the desired frequency.

TABLE 1. CRYSTAL FREQUENCY = 5.0688 MHz

| Transmit/Receive<br>Address |   | Baud | Theoretical<br>Frequency | Actual<br>Frequency | Percent   | Duty<br>Cycle |       |       |         |

|-----------------------------|---|------|--------------------------|---------------------|-----------|---------------|-------|-------|---------|

| 0                           | С | 8    | A                        | Rate                | 16X Clock | 16X Clock     | Error | 9%    | Divisor |

| 0                           | 0 | 0    | G                        | 50                  | 0.8 KHz   | 08 KHz        |       | 50/50 | 6336    |

| 0                           | 0 | ٥    | 1                        | 75                  | 1 2       | 12            | _     | 50/50 | 4224    |

| C                           | 0 | 1    | 0                        | 110                 | 1.75      | 1 76          | _     | 50/50 | 2880    |

| 0                           | 0 | 1    | 1                        | 134 5               | 2.152     | 2.1523        | 0.016 | 50/50 | 2355    |

| 0                           | 1 | 0    | 0                        | 150                 | 2.4       | 2.4           |       | 50/50 | 2112    |

| 0                           | 1 | 0    | 1                        | 200                 | 48        | 4.8           |       | 50/50 | 1056    |

| 0                           | 1 | 1    | Q                        | 300                 | 9.6       | 9.6           | _     | 50/50 | 528     |

| 0                           | 1 | t    | 1                        | 600                 | 19 2      | 19.2          | -     | 50/50 | 264     |

| 1                           | ٥ | 0    | 0                        | 1200                | 28.8      | 28.8          |       | 50/50 | 178     |

| 1                           | 0 | G    | 1                        | 1800                | 32.0      | 32.081        | 0 253 | 50/50 | 158     |

| 1                           | 0 | 1    | 0                        | 2400                | 38.4      | 38.4          | -     | 50/50 | 132     |

| 1                           | 0 | 1    | 1                        | 3600                | 57 6      | 57.6          | _     | 50/50 | 88      |

| 1                           | 1 | 0    | 0                        | 4800                | 76.8      | 76.8          | -     | 50/50 | 66      |

| 1                           | 1 | 0    | 1                        | 7200                | 115.2     | 115.2         | -     | 50/50 | 44      |

| 1                           | 1 | 1    | 0                        | 9600                | 153.6     | 153 6         |       | 48/52 | 33      |

| 1                           | 1 | 1    | 1                        | 19,200              | 307.2     | 316.8         | 3.125 | 50/50 | 16      |

BR1941L

TABLE 3. CRYSTAL FREQUENCY = 4.9152 MHz

| Transmit/Receive<br>Address |   | Baud | Theoretical<br>Frequency | Actual<br>Frequency | Percent   | Duty<br>Cycle |       |       |         |

|-----------------------------|---|------|--------------------------|---------------------|-----------|---------------|-------|-------|---------|

| D                           | С | 8    | A                        | Rate                | 16X Clock | 16X Clock     | Error | 9%    | Divisor |

| 0                           | 0 | 0    | 0                        | 50                  | 0.8 KHz   | 0.8 KHz       | _     | 50/50 | 6144    |

| 0                           | 0 | 0    | 1                        | 75                  | 1.2       | 1.2           | -     | 50/50 | 4096    |

| 0                           | 0 | 1    | a                        | 110                 | 1 78      | 1.7598        | -0.01 | •     | 2793    |

| 0                           | 0 | 1    | 1                        | 134.5               | 2.152     | 2.152         | _     | 50/50 | 2284    |

| 0                           | 1 | 0    | 0                        | 150                 | 2.4       | 2.4           | _     | 50/50 | 2048    |

| 0                           | 1 | Q    | 1                        | 300                 | 4.8       | 48            |       | 50/50 | 1024    |

| 0                           | 1 | 1    | 0                        | 600                 | 9.6       | 9.6           | _     | 50/50 | 512     |

| 0                           | 1 | 1    | 1                        | 1200                | 19.2      | 19.2          | -     | 50/50 | 256     |

| 1                           | 0 | 0    | 0                        | 1800                | 28.8      | 28,7438       | -0.19 | •     | 171     |

| 1                           | 0 | 0    | 1                        | 2000                | 32.0      | 31.9168       | -0.26 | 50/50 | 154     |

| 1                           | 0 | 1    | 0                        | 2400                | 38.4      | 38.4          | _     | 50/50 | 128     |

| 1                           | Q | 1    | 1                        | 3600                | 57.6      | 57.8258       | 0.39  | •     | 85      |

| 1                           | 7 | 0    | 0                        | 4800                | 76.8      | 76.8          | -     | 50/50 | 64      |

| 7                           | 1 | 0    | 1                        | 7200                | 115.2     | 114 306       | -0.77 | •     | 43      |

| 1                           | 1 | 1    | 0                        | 9600                | 153.6     | 153.6         |       | 50/50 | 32      |

| 1                           | 1 | 1    | 1                        | 19.200              | 307.2     | 307.2         | -     | 50/50 | 16      |

<sup>\*</sup>When the duty cycle is not exactly 50% it is 50% = 10%

BR1941L-5

2. Cascade devices by using the frequency outputs as an input to the XTAL/EXT inputs of the subsequent BR1941.

3. Consult the factory for possible changes via ROM mask reprogramming.

#### CRYSTAL SPECIFICATIONS

User must specify termination (pin, wire, other) Frequency - 5.0688 MHz or 4.9152 MHZ at dut

Temperature range 0°C to 70°C

Series resistance 50

Series Resonant

Overall tolerance ±.01%

TABLE 2. CRYSTAL FREQUENCY = 5.0688 MHz

| Transmit/Receive<br>Address |   |   |   |        | Theoretical<br>Frequency | Actual<br>Frequency | Percent | Duty<br>Cycle |         |

|-----------------------------|---|---|---|--------|--------------------------|---------------------|---------|---------------|---------|

| ٥                           | C | 8 | A | Rate   | 32X Clock                | 32X Clock           | Error   | 3%            | Divisor |

| 0                           | 0 | 0 | 0 | 50     | 16 KHz                   | 1 6 KHz             | -       | 50/50         | 3168    |

| 0                           | 9 | 0 | 1 | 75     | 2.4                      | 2.4                 | -       | 50/50         | 2112    |

| 0                           | 0 | 1 | 0 | 110    | 3 52                     | 3 52                | -       | 50/50         | 1440    |

| 9                           | 0 | 1 | 1 | 134.5  | 4 3C4                    | 4 303               | 026     | 50/50         | 1173    |

| 0                           | 1 | 0 | C | 150    | 48                       | 48                  | -       | 50/50         | 1056    |

| 0                           | 1 | 0 | 1 | 200    | 6 4                      | 6.4                 | -       | 50/50         | 792     |

| 0                           | 1 | 1 | 0 | 300    | 96                       | 9.6                 |         | 50/50         | 528     |

| 0                           | 1 | 1 | 1 | 600    | 19.2                     | 19.2                |         | 50/50         | 264     |

| 1                           | 0 | 0 | 0 | 1200   | 38.4                     | 38.4                |         | 50/50         | 132     |

| 1                           | ò | 0 | 1 | 1800   | 57 6                     | 57 6                | -       | 50/50         | 88      |

| 1                           | 0 | 1 | 0 | 2400   | 76.8                     | 76.8                | -       | 50/50         | 66      |

| 1                           | 0 | 1 | 1 | 3600   | 115 2                    | 115.2               |         | 50/50         | 44      |

| 1.                          | 1 | 0 | G | 4800   | 153.6                    | 153.6               |         | •             | 33      |

| 1                           | 1 | 0 | 1 | 7200   | 230.4                    | 230.4               | _       | 50/50         | 22      |

| 1                           | 1 | 1 | 0 | 9600   | 307.2                    | 298.16              | 2.941   | •             | 17      |

| 1                           | 1 | 1 | 1 | 19,200 | 614.4                    | 633.6               | 3.125   | 50/50         | 8       |

\*When the duty cycle is not exactly 50% it is 50% ± 10% BR1941L-6

#### **CRYSTAL MANUFACTURERS (Partial List)**

Northern Engineering Laboratories 357 Beloit Street Burlington, Wisconsin 53105 (414) 763-3591

**Bulova Frequency Control Products** 61-20 Woodside Avenue Woodside, New York 11377 (212) 335-6000

CAL Crystal 1142 N. Gilbert Street Anaheim, California 92801 (Available in HC-18 small can) (815) 786-8411

CTS Knights Inc. 101 East Church Street Sandwich, Illinois 60548

(714) 991-1580

This is a preliminary specification with tentative device parameters and may be subject to change after final product character-

Information furnished by Western Digital Corporation is believed to be accurate and reliable. However, no responsibility is assumed by Western Digital Corporation for its use; nor any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Western Digital Corporation. Western Digital Corporation reserves the right to change said circuitry at any time without notice.

# WESTERN Ø DIGITAL

MOS/LSI UC1671B

ASYNCHRONOUS/SYNCHRONOUS RECEIVER/TRANSMITTER

WESTERN DIGITAL CORPORATION - 3128 HED HILL AVENUE P.O. BOX 2180 - NEWPORT BEACH: CALIFORNIA 926634.

(714) 557.3550 - TWX: 910-595.1139

## **FEATURES**

- SYNCHRONOUS AND ASYNCHRONOUS Full Duplex Operations

- SYNCHRONOUS MODE

Selectable 5-8 Bit Characters

Two Successive SYN Characters Sets

Synchronization

Programmable SYN and DLE Character

Stripping

Programmable SYN and DLE-SYN Fill

- ASYNCHRONOUS MODE

Selectable 5-8 Bit Characters

Line Break Detection and Generation

1-, 1½-, or 2-Stop Bit Selection

False Start Bit Detection

Automatic Serial Echo Mode

- BAUD RATE DC TO 1M BAUD/SEC

- 8 SELECTABLE CLOCK RATES

Accepts 1X Clock and Up To 4 Different

32X Baud Rate Clock Inputs

Up To 47% Distortion Allowance With

32X Clock

- SYSTEM COMPATIBILITY

Double Buffering of Data

8-Bit Bi-Directional Bus For Data,

Status, and Control Words

All Inputs and Outputs TTL Compatible

Up To 32 ASTROS Can Be Addressed On

Bus

On-Line Diagnostic Capability

TRANSMISSION ERROR DETECTION-PARITY

Overrun and Framing

PIN CONNECTIONS

| 1     |    |   |    | 1               |

|-------|----|---|----|-----------------|

| VBB   | 1  |   | 40 | OQ <sup>V</sup> |

| TACKI | 2  |   | 39 | RE              |

| CS    | 3  |   | 38 | RTS             |

| WE    | 4  |   | 37 | TDATA           |

| TACKO | 5  |   | 36 | CTS             |

| RPLY  | 6  |   | 35 | TXTC            |

| INTR  | 7  |   | 34 | IXRC            |

| DALØ  | 8  |   | 33 | R4              |

| DAL 1 | 9  |   | 32 | R3              |

| DAL2  | 10 |   | 31 | R2              |

| DAL3  | 11 |   | 30 | R1              |

| DAL4  | 12 |   | 29 | CARR            |

| DAL5  | 13 | - | 28 | DSR             |

| DAL6  | 14 |   | 27 | RDATA           |

| DAL7  | 15 |   | 26 | 1D3             |

| DTR   | 16 |   | 25 | 1 D4            |

| 107   | 17 |   | 24 | 105             |

| RING  | 18 |   | 23 | MR              |

| MISC  | 19 |   | 22 | 106             |

| ۷ss   | 20 |   | 21 | VCC             |

|       | L  |   |    | l               |

## **APPLICATIONS**

SYNCHRONOUS COMMUNICATIONS

ASYNCHRONOUS COMMUNICATIONS

SERIAL/PARALLEL COMMUNICATIONS

## GENERAL DESCRIPTION

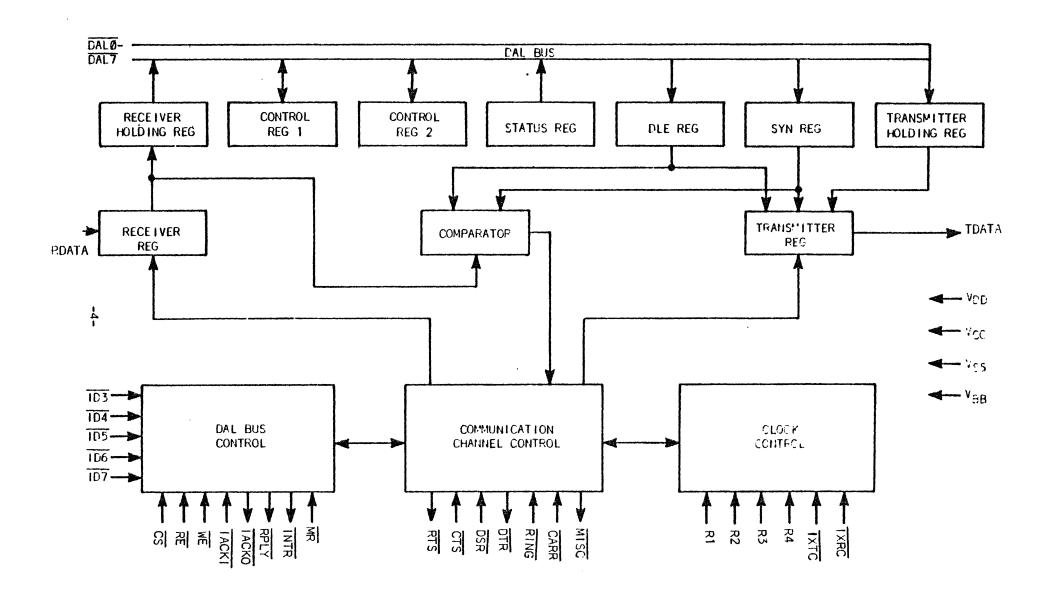

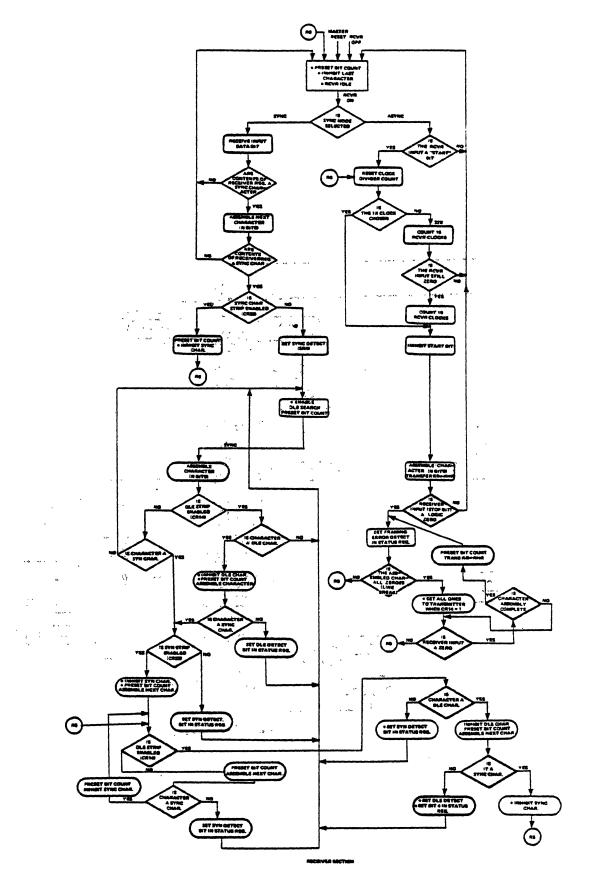

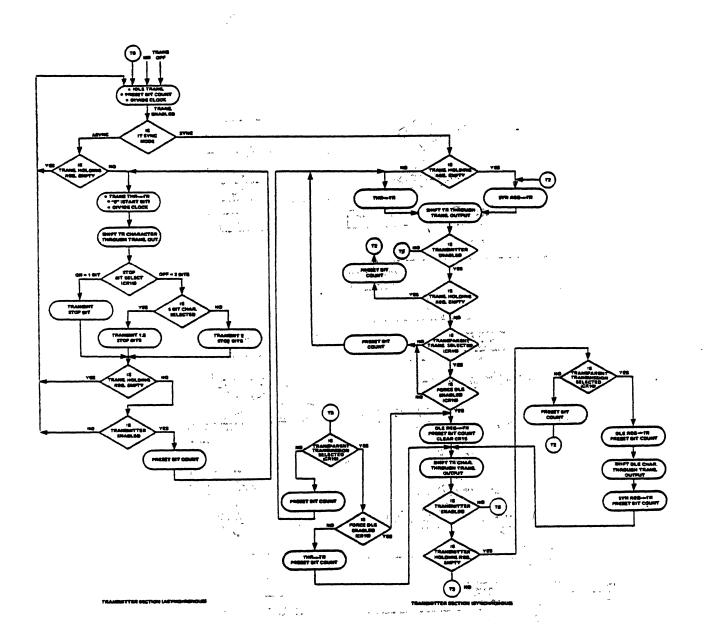

The UC1671B (ASTRO) is a MOS/LSI device which performs the functions of interfacing a serial data communication channel to a parallel digital system. The device is capable of full duplex communications (receiving and transmitting) with synchronous or asynchronous systems. The ASTRO is designed to operate on a multiplexed bus with other bus-oriented devices. Its operation is programmed by a processor or controller via the bus and all parallel data transfers with these machines are accomplished over the bus lines.

The ASTRO is fabricated in n-channel silicon gate MOS technology and is TTL compatible on all inputs and outputs.

## ORGANIZATION

The ASTRO block diagram is illustrated on Page 4. The primary sections include the receiver, the transmitter, control and bus interface.

- RECEIVER REGISTER This 8-bit shift register inputs the received data at a clock rate determined by the Control Register. The incoming data is assembled to the selected character length and then transferred to the Receiver Holding Register with logic zeroes filling out any unused high-order bit positions.

- RECEIVER HOLDING REGISTER This 8-bit parallel buffer register presents assembled receiver characters to the DAL bus lines when requested through a Read operation.

- COMPARATOR The 8-bit comparator is used in the Snychronous mode to compare the assembled contents of the Receiver Register and the SYN register or DLE register A match between the registers sets up stripping of the received character, when programmed, by preventing the data from being loaded into the Receiver Holding Register. A bit in the Status Register is set when stripping is performed. The comparator output also enables character synchronization of the Receiver on two successive matches with the SYN register.

- SYN REGISTER This 8-bit register is loaded from the DAL lines by a Write operation and holds the synchronization code used to establish receiver character synchronization. It serves as a fill character when no new data is available in the Transmitter Holding Register during transmission. This register cannot be read onto the DAL lines. It must be loaded with logic zeroes in all unused high-order bits.

- DLE REGISTER This 8-bit register is loaded from the DAL lines by a Write operation and holds the "DLE" character used in the Transparent mode of operation in which an idle transmit period is filled with the combination DLE-SYN pair of characters rather than a single SYN character. In addition the ASTRO may be programmed to force a single DLE character prior to any data character transmission while in the transmitter transparent mode.

- TRANSMITTER HOLDING REGISTER This 8-bit parallel buffer register holds parallel transmitted data transferred from the DAL lines by a Write operation. This data is transferred to the Transmitter Register when the transmitter section is enabled and the Transmitter Register is ready to send new data.

- TRANSMITTER REGISTER This 8-bit shift register is loaded from the Transmitter Holding Register, SYN register, or DLE register. The purpose of this register is to serialize data and present it to the transmitted Data output.

- CONTROL REGISTERS There are two 8-bit Control Registers which hold device programming signals such as mode selection, clock selection, interface signal control, and data format. Each of the Control Registers can be loaded from the DAL lines by a Write operation or read onto the DAL lines by a Read operation. The registers are cleared by a Master Reset.

- STATUS REGISTER This 8-bit register holds information on communication errors, interface data register status, match character conditions, and communication equipment status. This register may be read onto the DAL lines by a Read operation.

- DATA ACCESS LINES The DAL is an 8-bit bi-directional bus port over which all address, data, control, and status transfers occur. In addition to transferring data and control words the DAL lines also transfer information related to addressing of the device, reading and writing requests, and interrupting information.

## ASTRO OPEPATION

#### ASYNCHRONOUS MODE

Framing of asynchronous characters is provided by a Start bit (logic low) at the beginning of a character and a Stop bit (logic high) at the end of a character. Reception of a character is initiated on recognition of the first Start bit by a positive transition of the receiver clock, after a preceding Stop bit. The Start and Stop bits are stripped off while assembling the serial input into a parallel character.

The character assembly is completed by the reception of the Stop bit after reception of the last character bit. If this bit is a logic high, the character is determined to have correct framing and the ASTRO is prepared to receive the next character. If the Stop bit is a logic low the Framing Error Status flag is set and the Receiver assumes this bit to be the Start bit of the next character. Character assembly continues from this point if the input is still a logic low when sampled at the theoretical center of the assumed Start bit. As long as the Receive input is spacing, all zero characters are assembled and error flags and data received interrupts are generated so that line breaks can be determined. After a character of all zeroes is assembled along with a zero in the Stop bit location, the first received logic high is determined as a Stop bit and this resets the Receiver circuit to a Ready state for assembly of the next character.

In the Asynchronous mode the character transmission occurs when information contained in the Transmitter Holding Register is transferred to the Transmitter Register. Transmission is initiated by the insertion of a Start bit, followed by the serial output of the character least significant bit first with parity, if enabled, following the most significant bit; then the insertion of a I-, I.5-, or 2-bit length Stop condition. If the Transmitter Holding Register is full, the next character transmission starts after the transmission of the Stop bit of the present character in the Transmitter Register. Otherwise, the Mark (logic high) condition is continually transmitted until the Transmitter Holding Register is loaded.

In order to allow re-transmission of data received at a slightly faster character rate, means are provided for shortening the Stop bit length to allow transmission of characters to occur at the same rate as the reception of characters. The Stop bit is shortened by 1/16 of a bit period for 1-Stop bit selection and 3/16 of a bit period for 1.5-, or 2-Stop bit selection, if the next character is ready in the Transmitter Holding Register.

## SYNCHRONOUS MODE

Framing of characters is carried out by a special Synchronization Character Code (SYN) transmitted at the beginning of a block of characters. The Receiver, when enabled, searches for two continuous characters matching the bit pattern contained in the SYN register. During the time the Receiver is searching, data is not transferred to the Receiver Holding Register, status bits are not updated, and the Receiver interrupt is not activated. After the detection of the first SYN character, the Receiver assembles subsequent bits into characters whose length is determined by contents of the Control Register. If, after the first SYN character detection, a second SYN character is present, the Receiver enters the Synchronization mode until the Receiver Enable Bit is turned off. If a second successive SYN character is not found, the Receiver reverts back to the Search mode.

In the Synchronous mode a continuous stream of characters are transmitted once the Transmitter is enabled. If the Transmitter Holding Register is not loaded at the time the Transmitter Register has completed transmission of a character, this idle time will be filled by a transmission of the character contained in the SYN register in the Non-transparent mode, or the characters contained in the DLE and SYN registers respectively while in the Transparent mode of operation.

## DETAILED OPERATION

Receiver - The Receiver Data input is clocked into the Receiver Register by a IX Receiver Clock from a modem Data Set, or by a local 32X bit rate clock selected from one of four externally supplied clock inputs. When using the IX clock, the Receiver Data is sampled on the positive transition of the clock in both the Asynchronous and Synchronous modes. When using a 32X clock in the Asynchronous mode, the Receive Sampling Clock is phased to the Mark-To-Space transition of the Received Data Start bit and defines, through clock counts, the center of each received Data bit within  $\pm 0\%$ ,  $\pm 3\%$  at the positive transition 16 clock periods later.

In the Synchronous mode the Sampling Clock is phased to all Mark-To-Space transitions of the Received Data inputs when using a 32X clock. Each transition of the data causes an incremental correction of the Sampling Clock by I/32nd of a bit period. The Sampling Clock can be immediately phased to every Mark-To-Space Data transition by setting Bit 4 of Control Register I to a logic high, while the Receiver is disabled.

When the complete character has been shifted into the Receiver Register it is then transferred to the Receiver Holding Register; the unused, higher number bits are filled with zeroes. At this time the Receiver Status bits (Framing Error/Sync Detect, Parity Error/DLE Detect, Overrun Error, and Data Received) are updated in the Status Register and the Data Received interrupt is activated. Parity Error is set, if encountered while the Receiver parity check is enabled in the Control Register. Overrun Error is set if the Data Received status bit is not cleared through a Read operation by an external device when a new character is ready to be transferred to the Receiver Holding Register. This error flag indicates that a character has been lost, as new data is lost and the old data and its status flags are saved.

The characters assembled in the Receiver Register that match the contents of the SYN or DLE register are not loaded into the Receiver Holding Register, and the DR interrupt is not generated, if Bit 3 of Control Register 2 (CR23=SYN Strip) or Bit 4 of Control Register 1 (CR14=DLE Strip) are set respectively, the SYN-DET and DLE-DET status bits are set with the next non SYN or DLE character. When both CR23 and CR14 are set (Transparent mode), the DLE-SYN combination is stripped. The SYN comparison occurs only with the character received after the DLE character. If two successive DLE characters are received only the first DLE character is stripped. No parity check is made while in this mode.

Transmitter- Information is transferred to the Transmitter Holding Register by a Write operation. Information can be loaded into this register at any time, even when the Transmitter is not enabled. Transmission of data is initiated only when the Request To Send bit is set to a logic one in the Control Register and the Clear To Send input is a logic low. Information is normally transferred from the Transmitter Holding Register to the Transmitter Register when the latter has completed transmission of a character. However, information in the DLE register may be transferred prior to the information contained in the Transmitter Holding Register if the Force DLE signal condition is enabled (Bits 5 = Force DLE and 6 = TX Transparent of Control Register I set to a logic one). The control bit CRI5 must be set prior to loading of a new character in the transmitter holding register to insure forcing the DLE character prior to transmission of the data character. The Transmitter Register output passes through a flip-flop which delays the output by one clock period. When using the IX clock generated by the Modem Data Set, the output data changes state on the negative clock transition and the delay is one bit period. When using a local 32X clock the transmitter section selects one of the four selected rate inputs and divides the clock down to the baud rate. This clock is phased to the Transmitter Holding Register empty flag such that transmission of characters occurs within two clock times of the loading of the Transmitter Holding Register when the Transmitter Register is empty.

When the Transmitter is enabled, a Transmitter interrupt is generated each time the Transmitter Holding Register is empty. If the Transmitter Holding Register is empty when the Transmitter Register is ready for a new character the Transmitter enters an idle state. During this idle time a logic high will be presented to the Transmitted Data output in the Asynchronous mode or the contents of the SYN register will be presented in the Synchronous Non-transparent mode (CR16=0). In the Synchronous Transmit Transparent mode (enabled by Bit 6 of Control Register I=Logic I), the idle state will be filled by a DLE-SYN character transmission in that order. When entering the Transparent mode the DLE-SYN fill will not occur until the first forced DLE.

If the Transmitter section is disabled by a reset of the Request to Send, any partially transmitted character is completed before the transmitter section of the ASTRO is disabled. As soon as the CTS goes high the transmitted data output will go high.

When the Transmit parity is enabled, the selected Odd or Even parity bit is inserted into the last bit of the character in place of the last bit of the Transmitter Register. This limits transfer of character information to a maximum of seven bits plus parity or eight bits without parity. Parity cannot be enabled in the Synchronous Transparency mode.

## DEVICE PROGRAMMING

The two 8-bit Control Registers of the ASTRO determine the operative conditions of the ASTRO chip. The Control Register contents are shown in Figures 1 and 2.

| BiT | 7                            | 6                                                                                                             | 5                      | 4                                                                                                                                                                     | 3                                                                                                                                                                                   | Z                                                   | ı          | 3         |

|-----|------------------------------|---------------------------------------------------------------------------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------|-----------|

| SYM | NC/ASYNC                     | ASYNC                                                                                                         | ASYNC (TRANS. ENABLED) | ASYNC                                                                                                                                                                 | ASYNC                                                                                                                                                                               | SYNC, ASYNC                                         | SYNC/ASYNC | SMC/ASTIC |

|     | - LOOP MODE<br>- NORMAL MOSE | ) - MOM BREAK MODE  1 - BREAK MODE  SYNC  J - NON TRANSMITTER TRANSPARENT MODE  1 - TRANSMIT TRANSPARENT MODE | 0 - WISC OUT = 1       | C - NON ECHO NODE  I - AUTO ECHO NODE  SYNO (GR12 = 1)  C - DLE STRIPPING NOT ENABLED  I - CLE STRIPPING ENABLED  SYNG (GR12 = 0)  C - NISC OUT = 1  I - MISC OUT = 0 | O - NO PARITY EVABLED I - PARITY CHECK ENAULD ON RECEIVER PARITY CENERATION ENABLED ON TRANSMITTER  SYNC O - RECEIVER PARITY CHECK IS DISABLED I - RECEIVER PARITY CHECK IS ENABLED | ) - RECELVER<br>DISABLED<br>I - PECELVER<br>ENABLED |            | cur = c   |

## Control Register |

- $\underline{\text{Bit 7}}$  A logic Ø configures the ASTRO into an Internal Data and Control Loop mode and disables the Ring interrupt. In this diagnostic mode the following loops are connected internally:

- a. The Transmit Data is connected to the Receive Data with the TD pin held in a Mark condition and the input to the RD pin disregarded.

- b. With a IX clock selected, the Transmitter Clock also becomes the Receive Clock.

- c. The Data Terminal Ready (DTR) Control bit is connected to the Data Set Ready (DSR) input, with the DTR output pin held in an Off condition (logic high), and the DSR input pin in disregarded.

- d. The Request to Send Control bit is connected to the Clear To Send (CTS) and Carrier Detector inputs, with the RTS output pin held in an Off condition (logic high), and the CTS and Carrier Detector input pins are disregarded

- e. The Miscellaneous pin is held in an Off (logic high) condition.

A logic I on Bit 7 enables the Ring interrupt and returns the ASTRO to the normal full duplex configuration.

<u>Bit 6 - In the Asynchronous mode a logic I holds the Transmitted Data output in a Spacing (Logic O) condition, starting at the end of any current transmitted character, when the Transmitter is enabled. Normal Transmitter timing continues so that this Break condition can be timed out after the loading of new characters into the Transmitter Holding Register.</u>

In the <u>Synchronous</u> mode a logic I sets the Transmitter in a transparent transmission which implies that idle transmitter time will be filled by DLE-SYN character transmission and a DLE can be forced ahead of any character in the Transmitter Holding Register when CRI5 is a logic one in the sync mode.

Bit 5 - In the Asynchronous mode a logic I, with the Transmitter enabled, causes a single Stop bit to be transmitted. A logic  $\emptyset$  causes 2-Stop bit transmission for character lengths of 6, 7, or 8 bits and one-and-a-half Stop bits for a character length of 5 bits.

With the Transmitter disabled this bit controls the Miscellaneous output on Pin 19, which may be used for Make Busy on 103 Data Sets, Secondary Transmit on 202 Data Sets, or dialing on CBS Data Couplers.

In the <u>Synchronous</u> mode a logic I combined with a logic Ø on Bit 6 of Control Register I enables Transmit parity; if CRI5=0 or CRI6=I no parity is generated. When set to a logic I with Bit 6 also a logic I, the contents of the DLE register are transmitted prior to the next character loaded in the Transmitter Holding Register as part of the Transmit Transparent mode.

<u>Bit 4</u> - In the <u>Asynchronous</u> mode a logic I enables the Automatic Echo mode when the receiver section is enabled. In this mode the clocked regenerated data is presented to the Transmit Data output in place of normal transmission through the Transmitter Register. This serial method of echoing does not present any abnormal restrictions on the transmit speed of the terminal. Only the first character of a

Break condition of all zeroes (null character) is echoed when a Line Break condition is detected. For all subsequent null characters, with logic zero Stop bits, a steady Marking condition is transmitted until normal character reception resumes. Echoing does not start until a character has been received and the Transmitter is idle. The Transmitter does not have to be enabled during the Echo mode.

In the <u>Synchronous</u> mode a logic I, with the Receiver enabled, does not allow assembled Receiver data matching the DLE register contents to be transferred to the Receiver Holding Register; also, parity checking is disabled.

When the Receiver is not enabled this bit controls the Miscellaneous output on Pin 19, which may be used for New Sync on a 201 Data Set. When operating with a 32X clock and a disabled Receiver a logic I on this bit also causes the Receiver timing to synchronize on Mark-To-Space transitions.

Bit 3 - In the Asynchronous mode a logic I enables check of parity on received characters and generation of parity for transmitted characters.

In the <u>Synchronous mode a logic I bit enables</u> check of parity on received characters only. Note: Transmitter parity enable is controlled by CRI5.

Bit 2 - A logic I enables the ASTRO to receive data into the Receiver Holding Register, update Receiver Status Bits I, 2, 3, and 4, and to generate Data Peceived interrupts. A logic  $\emptyset$  disables the Receiver and clears the Receiver Status bits.

Bit I - Controls the Request To Send output on Pin 38 to control the CA circuit of the Data Set. The RTS output is inverted from the state of CRII. A logic I combined with a low logic Clear To Send input enables the Transmitter and allows THRE interrupts to be generated. A logic Ø disables the Transmitter and turns off the external Request to Send signal. Any character in the Transmitter Register will be completely transmitted before the Transmitter is turned off. The Request to Send output may be used for other functions such as "Make Busy" on 103 Data Sets.

Bit Ø - Controls the Data Terminal Ready output on Pin 16 to control the CD circuit of the Data Set. A logic I enables the Carrier and Data Set Ready interrupts. A logic Ø enables only the telephone line Ring interrupt. The DTR output is inverted from the state of CRIØ.

| 817 | 7                                                 | 6            | 5                                          | 4                                                     | 3                                                                                                                                                                           | 2                                         | i                                                                                                                              | 0   |

|-----|---------------------------------------------------|--------------|--------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----|

|     | SYNC/ASYNC                                        |              | MODE SELECT                                | SYNC/ASYNC                                            | ASYNC                                                                                                                                                                       | SYNC/ASYNC                                |                                                                                                                                |     |

|     | CHARACTER<br>Q0 = 8<br>Q1 = 7<br>10 = 6<br>11 = 5 | BITS<br>BITS | O - ASYNCHRONOUS MODE I - SYNCHRONOUS MODE | 1 - 000 PARITY<br>SELECT<br>O - EVEN PARITY<br>SELECT | I - RECEIVER CLOCK DETERMINED BY BITS 2-0 0 - RECEIVER CLK = RATE    SYNC (CRI6 = 0) 0 - NO SYN STRIP 1 - SYN STRIP  SYNC (CRI6 = 1) 0 - NO DLE-SYN STRIP 1 - DLE-SYN STRIP | 001 -<br>010 -<br>011 -<br>100 -<br>101 - | LECT  IX CLOCK  PATE   CLOCK  PATE   CLOCK  PATE 2 CLOCK  PATE 3 CLOCK  PATE 4 CLOCK  PATE 4 CLOCK  PATE 4 CLOCK  PATE 4 CLOCK | + 4 |

FIGURE 2 - CONTROL REGISTER 2

## Control Register 2

Control Register 2, unlike Control Register 1, cannot be changed at any time. This register should be changed only while both the receiver and transmitter sections of the ASTRO are in the idle state.

Bits 7-6 - These bits select the character length as follows:

| <u>Bits 7-6</u> | Character Length |

|-----------------|------------------|

| ØØ              | 8 bits           |

| ØI              | 7 bits           |

| ĪØ              | 6 bits           |

| 11              | 5 bits           |

When parity is enabled it must be considered as a bit when making character length selection, i.e. 5 character bits plus parity = 6 bits.

Bit 5 - A logic I selects the Synchronous Character mode. A logic  $\emptyset$  selects the Asynchronous Character mode.

Bit 4 - A logic I selects odd parity and a logic  $\emptyset$  selects even parity, when parity is enabled by CRI3 and/or CRI5.

Bit 3 - In the Asynchronous mode a logic  $\emptyset$  selects the rate 1-32X clock input (pin  $\overline{30}$ ) as the Receiver Clock rate and a logic I selects the same clock rate for the Receiver as selected by Bits 2- $\emptyset$  for the Transmitter. This bit must be a logic I for the IX clock selection by Bits 2- $\emptyset$ .

In the <u>Synchronous</u> mode a logic I causes all DLE-SYN combination characters in the Transparent mode when DLE strip CRI4 is a logic I, or all SYN characters in the Non-transparent mode to be stripped out and no Data Received interrupt to be generated. The SYN Detect status bit is set with reception of the next assembled character as it is transferred to the Receiver Holding Register.

$Bits 2-\emptyset$  - These bits select the Transmit and Receive clocks. The Input Clock to the Rate 4 pin may be divided down to form the 32X clock from a multiple clock as shown:

| Bits 2-Ø | Clock                                                           |  |  |  |  |  |

|----------|-----------------------------------------------------------------|--|--|--|--|--|

| ØØØ      | IX clock for Transmit and Receive (Pins 35 and 34 respectively) |  |  |  |  |  |

| ØØI      | 32X clock - Rate   input (pin 30)                               |  |  |  |  |  |

| ØIØ      | 32X clock - Rate 2 input (Pin 31)                               |  |  |  |  |  |

| ØII      | 32X clock - Rate 3 input (Pin 32)                               |  |  |  |  |  |

| IØØ      | 32X clock - Rate 4 input ÷ 1 (Pin 33)                           |  |  |  |  |  |

| 1Ø1      | 32X clock - Rate 4 input ÷ 2 (Pin 33)                           |  |  |  |  |  |

| 110      | 32X clock - Rate 4 input ÷ 4 (Pin 33)                           |  |  |  |  |  |

| 111      | 32X clock - Rate 4 input ÷ 8 (Pin 33)                           |  |  |  |  |  |

## Status Register

The data contained in the Status Register define Receiver and Transmitter data conditions and status of the Data Set. The Status word is shown in Figure 3, and defined below.

| 7                      | 6                     | 5                    | 4     | 3                                  | 2                 | 1                 | Ø                                            |

|------------------------|-----------------------|----------------------|-------|------------------------------------|-------------------|-------------------|----------------------------------------------|

| •Data<br>Set<br>Chance | •Data<br>Set<br>Ready | •Carrier<br>Detector | Error | •DLE<br>Detect<br>•Parity<br>Error | •Overrun<br>Error | •Da⊤a<br>Received | •Transmitter<br>Holdina<br>Penister<br>Emptv |

. 🕇

#### FIGURE 3 - STATUS REGISTER

- Bit 7 This bit is set to a logic I whenever there is a change in state of the Data Set Ready or Carrier Detector inputs while Data Terminal Ready (Bit  $\emptyset$  of Control Register I) is a logic I or the Ring Indicator is turned on, with DTR a logic  $\emptyset$ . This bit is cleared when the Status Register is read onto the Data Access Lines.

- $\underline{\text{Bit 6}}$  This bit is the logic complement of the Data Set Ready input on Pin 28. With  $\underline{\text{202-type}}$  Data Sets it can be used for Secondary Receive.

- Bit 5 This bit is the logic complement of the Carrier Detector input on Pin 29.

- Bit 4 In the Asynchronous mode a logic I indicates that received data contained a log  $\emptyset$  bit after the last data bit of the character in the stop bit slot, while the Receiver was enabled. This indicates a Framing error. This bit is set to a logic  $\emptyset$  if the proper logic I condition for the Stop bit was detected.

- In the <u>Synchronous</u> mode a logic I indicates that the contents of the Receiver Register matched the contents of the SYN Register. The condition of this bit remains for a full character assembly time. If SYN strip (CR23) is enabled this status bit is updated with the character received after the SYN character. In both modes the bit is cleared when the Receiver is disabled.

- Bit 3 When the DLE Strip is enabled (Bit 4 of Control Register I) the Receiver parity check is disabled and this bit is set to a logic I if the previous character to the presently assembled character matched the contents of the DLE register; otherwise it is cleared. The DLE DET remains for one character time and is reset on the next character transfer or on a Status Register Read. If DLE Strip is not enabled this bit is set to a logic I when the Receiver is enabled, Receiver parity (Bit 3 of Control Register I) is also enabled, and the last received character has a Parity error. A logic Ø on this bit indicates correct parity. This bit is cleared in either of the above modes when the Receiver is disabled.

- <u>Bit 2</u> A logic I indicates an Overrun error which occurs if the previous character in the Receiver Holding Register has not been read and Data Received is not reset, at the time a new character is to be transferred to the Receiver Holding Register. This bit is cleared when no Overrun condition is detected i.e. the next character transfer time or when the Receiver is disabled.

- <u>Bit I A logic I indicates that the Receiver Holding Register is loaded from the Receiver Register, if the Receiver is enabled.</u> It is cleared to a logic Ø when the Receiver Holding Register is read onto the Data Access Lines, or the Receiver is disabled.

- Bit  $\emptyset$  A logic I indicates that the Transmitter Holding Register does not contain a character while the Transmitter is enabled. It is set to a logic I when the contents of the Transmitter Holding Register is transferred to the Transmitter Register. It is cleared to a  $\emptyset$  bit when the Transmitter Holding Register is loaded from the DAL, or when the Transmitter is disabled.

## INPUT/OUTPUT OPERATIONS

All Data, Control, and Status words are transferred over the Data Access Lines (DAL  $\emptyset$ -7). Additional input lines provide controls for addressing a particular unit, and regulating all input and output operations. Other lines provide interrupt capability to indicate to a Controller that an input operation is requested by the ASTRO. All input/output terminology below is referenced to the Controller so that a Read or Input takes data from the ASTRO and places it on the DAL lines, while a Write or Output places data from the DAL lines into the ASTRO.

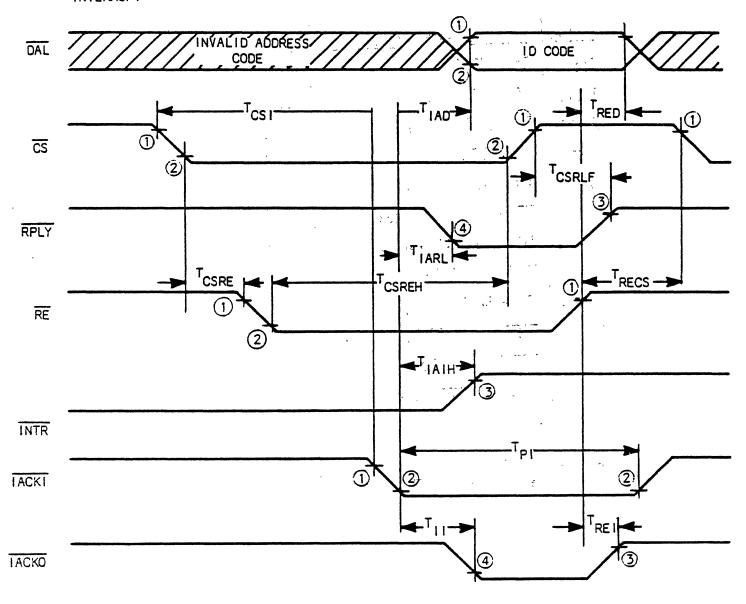

## Read

A Read operation is initiated by the placement of an <u>eight-bit address</u> on the DAL by the Controller. When the Chip Select signal goes to a logic low state, the ASTRO compares Bits 7-3 of the DAL with its hard-wired ID code (Pins 17, 22, 24, 25, and 26) and becomes selected on a Match condition. The ASTRO then sets its RPLY line low to acknowledge its readiness to transfer data. Bits 2-Ø of the address are used to select ASTRO registers to read from as follows:

| Bits 2-0 | Selected Register         |

|----------|---------------------------|

| ØØØ      | Control Register 1        |

| Ø1Ø      | Control Register 2        |

| 100      | Status Register           |

| 11Ø      | Receiver Holding Register |

When the Read Enable (RE) line is set to a logic low condition by the Controller the ASTRO gates the contents of the addressed register onto the DAL. The Read operation terminates, and the devices becomes unselected, when both the Chip Select and Read Enable return to a logic high condition. Reading of the Receiver Holding Register clears the DR Status bit. Bit Ø must be a logic low in read or write operations.

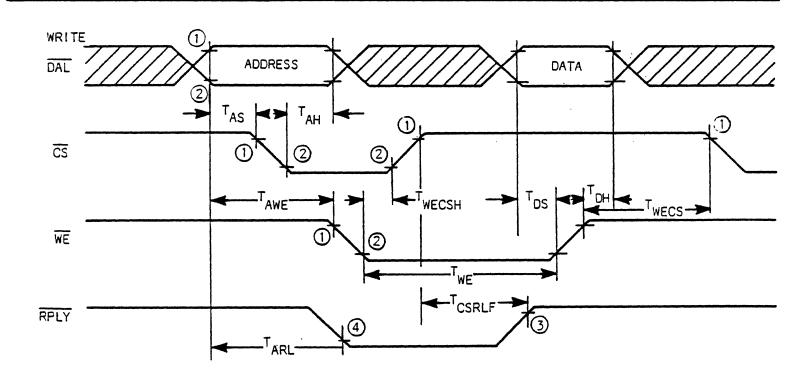

## Write

A Write operation is initiated by the placement of an eight-bit address or the DAL by the Controller. The ASTRO compares Bits 7-3 of the DAL with its 1D code when the Chip Select input goes to a logic low state. If a Match condition exists the device is selected and makes its RPLY line low to acknowledge its readiness to transfer data. Bits  $2-\emptyset$  of the address are used to select ASTRO registers to be written into as follows:

| Bits 2-0 | Selected Register            |

|----------|------------------------------|

| ØØØ      | Control Register 1           |

| Ø1Ø      | Control Register 2           |

| 100      | SYN and DLE Register         |

| 11Ø      | Transmitter Holding Register |

When the Write Enable (WE) line is set to a logic low condition by the Controller the ASTRO gates the data from the DAL into the addressed register. If data is written into the Transmitter Holding Register, the THRE Status bit is cleared to a logic zero.

The 100 address loads both the SYN and DLE registers. After writing into the SYN register the device is conditioned to write into the DLE if followed by another Write pulse with the 100 address. Any intervening Read or Write operation with

other addresses resets this condition such that the next 100 will address the SYN register.

## Interrupts

The following conditions generate interrupts:

- 1. <u>Data Received (DR)</u> Indicates transfer of a new character to the Receiver Holding Register while the Receiver is enabled.

- 2. Transmitter Holding Register Empty (THRE) Indicates that the THR register is empty while the Transmitter is enabled. The first interrupt occurs when the Transmitter becomes enabled if there is an empty THR, or after the character is transferred to the Transmitter Register making the THR empty.

- 3. Carrier On Indicates Carrier Detector input goes low when DTR is on.

- 4. Carrier Off Indicates Carrier Detector input goes high when DTR is on.

- 5. DSR On Indicates the Data Set Ready input goes low when DTR is on.

- 6. DSR Off Indicates the Data Set Ready input goes high when DTR is on.

- 7. Ring On Indicates the Ring Indicator input goes low when DTR is off.

Each time an Interrupt condition exists the INTR output from the ASTRO is made a logic low. The following interrupt procedure is then carried out even if the Interrupt condition is removed.

The Controller acknowledges the Interrupt request by setting the Chip Select (CS) and the Interrupt Acknowledge Input (IACKI) to the ASTRO to a Low state. On this transition all non-interrupting devices receiving the IACKI set their Interrupt Acknowlege Output (IACKO) low, enabling lower priority daisy-chained devices to respond to the Interrupt request. The highest priority device that is interrupting will then set its RPLY low. This device places its ID code on Bit Positions 7-3 of the DAL when a low RE signal is received. In addition Bit 2 is set to a logic one if any of the interrupt numbers I and 3-7 above occured, and remains a logic low if the THRE has caused the interrupt.

To reset the Interrupt condition (INTR) Chip Select (CS) and IACKI must be received by the ASTRO. A setup time must exist between CS and the RE or WE signals to allow chip selection prior to read/write operations and deselection control through the latter signals. The data is removed from the DAL when the RE signal returns to the logic high state.

## MAXIMUM RATINGS

$V_{DD}$  With Respect To  $V_{BB}$  (Ground) +20 to -0.3V Max Voltage To Any Input With Respect To  $V_{BB}$  +20 to -0.3V Operating Temperature  $0^{\circ}$ C to  $0^{\circ}$ C Storage Temperature -55°C to +125°C Power Dissipation

## OPERATING CHARACTERISTICS

$T_A$  =  $\emptyset^{O}C$  to  $7\emptyset^{O}C$ ,  $V_{DD}$  = +12. $\emptyset$ V  $\pm$  .6V,  $V_{BB}$  = -5. $\emptyset$   $\pm$  .25V,  $V_{SS}$  =  $\emptyset$ V,  $V_{CC}$  = +5V  $\pm$  .25V

| SYMEOL             | CHARACTERISTIC                    | MIN | TYP | MAX | UNITS      | CONDITIONS                         |

|--------------------|-----------------------------------|-----|-----|-----|------------|------------------------------------|

| 161                | Input Leakage                     |     |     | 10  | μА         | V <sub>IN</sub> = V <sub>DD</sub>  |

| LO                 | Output Leakage                    |     |     | 19  | Aμ         | V <sub>OUT</sub> = V <sub>DD</sub> |

| I <sub>BB</sub>    | V <sub>BB</sub> Supply Current    |     |     | 1   | mA         | V <sub>BB</sub> = -5V              |

| ICC <sub>AVE</sub> | V <sub>CC</sub> Supply Current    | •   |     | 80  | mA         |                                    |

| IDDAVE             | V <sub>DD</sub> Supply Current    |     |     | 10  | mA         |                                    |

| v <sub>IH</sub>    | input High Voltage                | 2.4 |     |     | ٧          |                                    |

| ٧١٢                | Input Low Voltage<br>(All Inputs) |     |     | .8  | <b>v</b> . |                                    |

| V <sub>OH</sub>    | Output High Voltage               | 2.8 |     |     | ٧          | $I_0 = -100  \mu A$                |

| V <sub>OL</sub>    | Output Low Voltage                |     |     | .4  | ٧          | I <sub>O</sub> = 1.6 mA            |

## AC CHARACTERISTICS

$T_A = \emptyset^{O}C$  to  $70^{O}C$ ,  $V_{DD} = +12.0V \pm 0.6V$ ,  $V_{BB} = -5.0V \pm 0.25V$ ,  $V_{CC} = +5.0 \pm .25V$ ,  $V_{SS} = \emptyset V_{MAX} = 20 pf$

| MAX     | , - 20 μ        | the second of the constant of |      |     |      | ,     | ı                      |

|---------|-----------------|-------------------------------|------|-----|------|-------|------------------------|

|         | SYMBOL          | CHARACTERISTIC                | MIN  | TYP | MAX  | UNITS | CONDITIONS             |

| ,       | TAS             | Address Set-Up Time           | Ø    | 1.4 |      | ns    |                        |

|         | TAH             | Address Hold Time             | 150  | -   | ,    | ns    |                        |

|         | TARL            | Address to RPLY Delay         |      | , · | 400  | ns    |                        |

|         | TCS             | CS Width                      | 250  |     |      | ns    |                        |

|         | TCSRLF          | CS to Reply OFF Delay         | Ø    |     | 250  | ns    | RL = 2.7 KΩ            |

| READ    |                 | `                             | , ve |     |      |       |                        |

|         | TARE            | Address and RE Spacing        | 250  |     |      | ns    |                        |

|         | TRECSH          | RE and CS Overlap             | 20   |     |      | ns    |                        |

|         | TRECS           | RE to CS Spacing              | 250  |     |      | ns    |                        |

|         | TRED            | RE to Data Out Delay          |      |     | 180  | ns    | C <sub>L</sub> = 20 pf |

| WRITE   | T <sub>RE</sub> | RE Width                      | 200  |     | 1000 | ns    |                        |

|         | TAWE            | Address to WE Spacing         | 250  |     |      | ns    |                        |

| *       | TWECSH          | WE and CS Overlap             | 20   |     |      | ns    |                        |

| ,       | TWE .           | WE Width                      | 200  |     | 1000 | ns    |                        |

|         | T <sub>DS</sub> | Data Set-Up Time              | 150  |     |      | ns    |                        |

| max I r | TDH             | Data Hold Time                | 100  |     |      | กร    |                        |

|         | TWECS           | WE to CS Spacing              | 250  |     |      | ns    |                        |

|         |                 |                               |      |     | i    |       | l                      |

$1 - V_{1H}(min) = 2.4V$

$2 = V_{1L}(max) = 0.8V$

$3 = V_{OH}(min) = 2.8V$

$4 - V_{OL}(max) = 0.4V$

NOTE I: ID DECODE is the major factor in TARE and TARL timing.

NOTE 2: If changing the Control Registers while processing data the WE pulse width must be contained within the Data Valid envelope to insure correct data processing.

## INTERRUPT

| SYMBOL | CHARACTERISTIC               | MIN | TYP | MAX | UNITS | CONDITIONS  |

|--------|------------------------------|-----|-----|-----|-------|-------------|

| TCSI   | CS to IACKI Delay            | ~ Ø |     |     | ns    |             |

| TCSRE  | CS to RE Delay               | 250 |     |     | ns    |             |

| TCSREH | CS and RE Overlap            | 20  | ē   |     | ns    |             |

| TRECS  | RE to CS Spacing             | 250 |     |     | ns    |             |

| Tpi    | TACKI Pulse Width            | 200 |     |     | ns    |             |

| TIAD   | IACKI to Valid ID Code Delay |     |     | 250 | ns    | See Note 1. |

| TRED   | RE OFF to DAL Open Delay     |     |     | 180 | ns    |             |

| TIARL  | IACKI to RPLY Delay          | '   |     | 250 | ns    |             |

| TCSRLF | CS to RPLY OFF Delay         | Ø   |     | 250 | ns    | RL = 2.7 KΩ |

| TIAIH  | TACKI ON to INTR OFF Delay   |     |     | 300 | ns    |             |

| T11    | TACKI to TACKO Delay         |     |     | 200 | ns    |             |

| TREI   | RE OFF to TACKO OFF Delay    |     |     | 250 | ns    |             |

|        | ` ~ ."                       |     |     |     |       |             |

|        | • •                          |     |     |     |       |             |

Note 1: If RE goes low after TACKI goes low, the delay will be from the falling edge of RE.

titi som et alle som et al

## INTERRUPT

NOTE 3: DALO must be a logic high during  $\overline{\text{CS}}$  to form an invalid address during Daisy Chain Interrupt Response.

•:1-

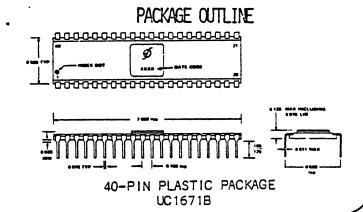

## PIN OUTS

The device is packaged in a 40-pin plastic cavity package. The interface signals are defined below with all input/output signals complemented to facilitate bussing and interfacing with TTL. The Data Set controls and Status signals are also complemented to allow for an inversion when converting to EIA RS232C levels. The names and symbols assigned to the Data Set interface signals follows EIA standard nomenclature.

| PIN NO.                | PIN NAME                    | SYMBOL                   | FUNCTION                                                                                                                                                                                                                                                  |

|------------------------|-----------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>21<br>40<br>20    | POWER SUPPLIES              | VBB<br>VCC<br>VDD<br>VSS | -5V<br>+5V<br>+12V<br>Ground                                                                                                                                                                                                                              |

| 23                     | MASTER RESET                | MR                       | <ul> <li>The Control and Status Registers<br/>and other controls are cleared<br/>when this input is low.</li> </ul>                                                                                                                                       |

| 8-15                   | DATA ACCESS LINES           | DALØ-DAL7                | <ul> <li>Eight-bit bi-directional bus used<br/>for transfer of data, control,<br/>status, and address information.</li> </ul>                                                                                                                             |

| 17,22,<br>24,25,<br>26 | SELECT CODE                 | 107-103                  | <ul> <li>Five input pins which when hard-<br/>wired assign the device a unique<br/>identification code used to<br/>select the device when addressing<br/>and used as an identification<br/>when responding to interrupts.</li> </ul>                      |

| 3                      | CHIP SELECT                 | CS                       | <ul> <li>The low logic transition of CS iden-<br/>tifies a valid address on the DAL bus<br/>during Read and Write operations.</li> </ul>                                                                                                                  |

| 39                     | READ ENABLE                 | RE                       | <ul> <li>This signal, when low, gates the<br/>contents of an addressed register<br/>from a selected ASTRO onto the<br/>DAL.</li> </ul>                                                                                                                    |

| 4                      | WRITE ENABLE                | WE                       | <ul> <li>This signal, when low, gates the<br/>contents of the DAL bus into the<br/>addressed register of a selected<br/>ASTRO.</li> </ul>                                                                                                                 |

| ~ <b>7</b>             | INTERRUPT                   | INTR                     | <ul> <li>This open drain output is made<br/>low when one of the communication<br/>interrupt conditions occur.</li> </ul>                                                                                                                                  |

| 2                      | INTERRUPT<br>ACKNOWLEDGE IN | TACKI                    | • This input becomes low when polling takes place on the bus by the Controller to determine the interrupting source. When this signal is received, the ASTRO places its ID code on the DAL if it is requesting interrupt, otherwise it makes TACKO a low. |

| PIN NO. | PIN NAME                  | SYMBOL        |   | FUNCTION                                                                                                                                                                                                                                                   |

|---------|---------------------------|---------------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|