Advanced Micro Computers A subsidiary of Advanced Micro Devices

Am95/3310 Communication I/O Expansion Board

**User's Manual**

059910089-001 \$10.00

|           | REVISION RECORD                                                    |            |

|-----------|--------------------------------------------------------------------|------------|

| REVISION  | DESCRIPTION                                                        |            |

| 01        | Preliminary Issue                                                  |            |

| (6/26/80) |                                                                    |            |

| Α         | Manual Released                                                    |            |

| (9/15/80) |                                                                    | ed (et a l |

| В         | Manual Updated to Support the Production Released Version A Board. |            |

| (4/15/81) |                                                                    |            |

| С         | Publication Number Changed And Manual Reprinted                    |            |

| (9/30/81) |                                                                    |            |

|           |                                                                    |            |

|           |                                                                    |            |

|           |                                                                    |            |

|           |                                                                    |            |

|           |                                                                    |            |

| 144       |                                                                    |            |

|           |                                                                    |            |

|           |                                                                    |            |

|           |                                                                    |            |

|           |                                                                    |            |

|           |                                                                    |            |

|           |                                                                    |            |

|           |                                                                    |            |

|           |                                                                    |            |

|           |                                                                    |            |

REVISION LETTERS I, O, Q AND X ARE NOT USED

© 1981 Advanced Micro Computers Printed in U.S.A.

Publication No.

059910089-001

Address comments concerning this manual to:

ADVANCED MICRO COMPUTERS

Publications Department

Publications Department 3340 Scott Boulevard Santa Clara, CA 95051

#### **PREFACE**

This manual provides general information, an installation and interface guide, programming information, principles of operation, and service information for the Advanced Micro Computers Am95/3310 Communication I/O Expansion Board. Additional information can be obtained from the following documents:

- Bell System Technical Reference

- Data Auxiliary Set 801C (Automatic Calling Unit)

- Interface Specification (PUB41601)

- Intel Multibus<sup>†</sup> Specification (9800683)

- The 8080A/9080A MOS Microprocessor Handbook

- Using the 8259A Programmable Interrupt Controller (AP-59)

In this manual both active-high (positive true) and active-low (negative true) signals appear in the text. To eliminate confusion and simplify presentation, the following convention is adhered to: whenever a signal is active-low (negative true), its mnemonic is followed by an asterisk (\*) (i.e., MEMR\* denotes an active-low signal). For a signal that is active-high, the asterisk is omitted (i.e., IORW denotes an active-high signal).

The information in this manual is believed to be accurate and complete at the time it was printed. However, AMC reserves the right to change specifications without notice. No responsibility is assumed for errors that might appear in this manual. No part of this manual may be copied or reproduced in any form without prior written permission from AMC.

<sup>†</sup>Multibus is a registered trademark of Intel Corporation.

# **TABLE OF CONTENTS**

| 1.   | General Information1-1                  |    | Am8255A Control Word Format3-10<br>Am8255A Port A and B Data3-10 |

|------|-----------------------------------------|----|------------------------------------------------------------------|

|      | Introduction1-1                         |    | Am8255A Port C Data3-10                                          |

|      | Physical Description1-1                 |    | Programmable Interval Timer                                      |

|      | Functional Description1-3               |    | Programming3-10                                                  |

|      |                                         |    | Am8253 Initialization3-12                                        |

|      | Specifications1-4                       |    | Am8253 Operation3-13                                             |

|      |                                         |    | Am8253 Counter Read3-13                                          |

| _    |                                         |    |                                                                  |

| 2.   | Installation and Interfacing2-1         |    | Am8253 Clock Frequency/                                          |

|      |                                         |    | Divide Ratio Selection3-14                                       |

|      | Introduction2-1                         |    | Synchronous Mode3-14                                             |

|      | Unpacking and Inspecition2-1            |    | Asynchronous Mode3-14                                            |

|      | Power Requirements2-1                   |    | Rate Generator/Interval                                          |

|      | Cooling Requirements2-1                 |    | Timer3-15                                                        |

|      | Bus Interface Requirements2-1           |    | Interrupt Timer3-16                                              |

|      | User Selectable Options2-2              |    | Programmable Interrupt Con-                                      |

|      | I/O Address Base2-2                     |    | troller3-16                                                      |

|      | Transfer Acknowledge (XACK*)2-2         |    | 8259A Interrupt Request                                          |

|      |                                         |    | Register (IRR)3-18                                               |

|      | System Interrupt Configu-               |    | 8259A In-Service Register                                        |

|      | ration2-2                               |    | (ISR)3-18                                                        |

|      | Serial I/O Clock Selection2-5           |    |                                                                  |

|      | Serial Interface2-5                     |    | 8259A Priority Resolver3-18                                      |

|      | Transmit/Receive Clock                  |    | 8259A Interrupt Mask                                             |

|      | Selection2-7                            |    | Register (IMR)3-18                                               |

|      | Serial I/O Port Current-Loop            |    | 8259A Read/Write Logic3-18                                       |

|      | Configuration2-9                        |    | 8259A Cascade Buffer/                                            |

|      | Parallel Interface Config-              |    | Comparator3-19                                                   |

|      | uration2-12                             |    | 8259A Data Bus Buffer3-19                                        |

|      | TTL Buffered I/02-12                    |    | 8259A Least-Significant                                          |

|      | RS232C Buffered                         |    | Address Bit ABO3-19                                              |

| T // | 02-13                                   |    | 8259A Addressing3-19                                             |

| 1/\  | U                                       |    | 8259A Initialization3-19                                         |

|      |                                         |    | 8259A Operation Command                                          |

| _    | 2 1 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 |    |                                                                  |

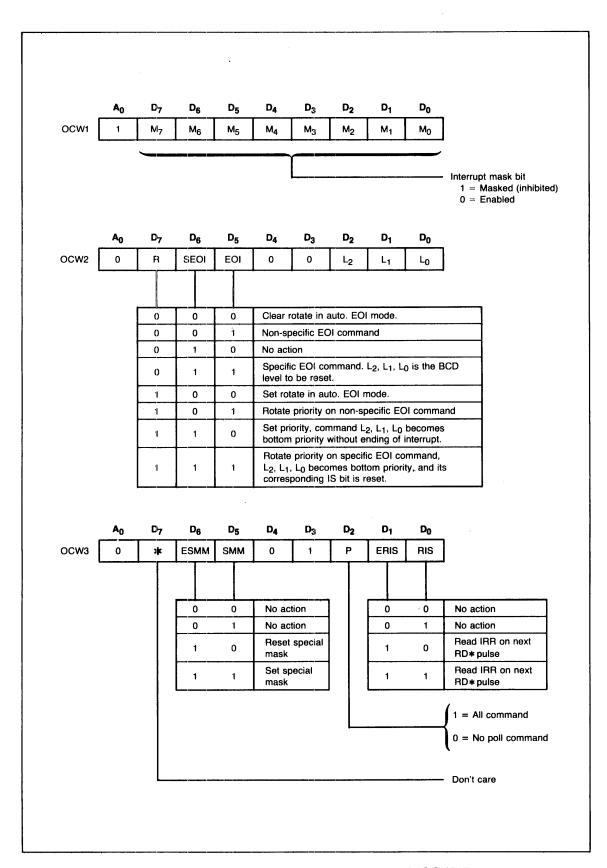

| 3    | • Operation and Programming3-1          |    | Word (OCWs)3-24                                                  |

|      | 0.1                                     |    | 8259A Operating Modes3-24                                        |

|      | Introduction3-1                         |    | End-Of-Interrupt and Spec-                                       |

|      | I/O Base Address Assignment3-1          |    | ific End-Of-Interrupt                                            |

|      | Address Assignments3-1                  |    | Commands3-27                                                     |

|      | Am95/3310 Initialization3-3             |    | 8259A Status Read3-27                                            |

|      | Serial I/O Interface Program-           |    |                                                                  |

|      | ming3-3                                 |    |                                                                  |

|      | Am9551 Addressing3-3                    | 4. | Theory of Operation4-1                                           |

|      | Am9551 Initialization3-4                |    |                                                                  |

|      | Mode Instruction Word3-4                |    | Introduction4-1                                                  |

|      | Command Instruction Word                |    | Bus Interface4-1                                                 |

|      | Format3-6                               |    | Data Buffers4-1                                                  |

|      |                                         |    | Address Buffers4-1                                               |

|      | Am9551 Status Read3-6                   |    | Board Selection4-1                                               |

|      | Am9551 Data Input/Output3-8             |    | Chin Coloct Logic                                                |

|      | Parallel I/O Interface Pro-             |    | Chip-Select Logic4-3                                             |

|      | gramming3-8                             |    | Board Read/Write Logic4-3                                        |

|      | Am8255A Initialization3-8               |    | Acknowledge Logic4-3                                             |

|      | Am8255A Addressing3-10                  |    | Board Clock Logic4-3                                             |

# **TABLE OF CONTENTS (Cont.)**

|          | Baud-Rate Generator/Timer                             | 3-8.                           | PIT Control Word Format3-12                              |

|----------|-------------------------------------------------------|--------------------------------|----------------------------------------------------------|

|          | Logic4-3                                              | 3-9.                           |                                                          |

|          | Interrupt Control Logic4-4                            |                                | Counter Register Latch3-14                               |

|          | Serial I/O Ports4-4                                   | 3-10.                          | 8259A Functional Block                                   |

|          | Current-Loop Circuits4-4                              |                                | Diagram3-17                                              |

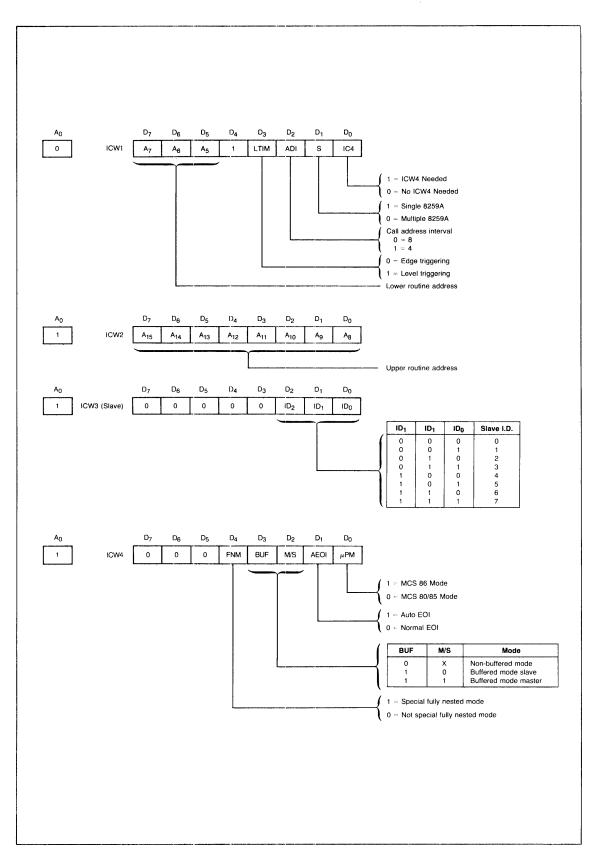

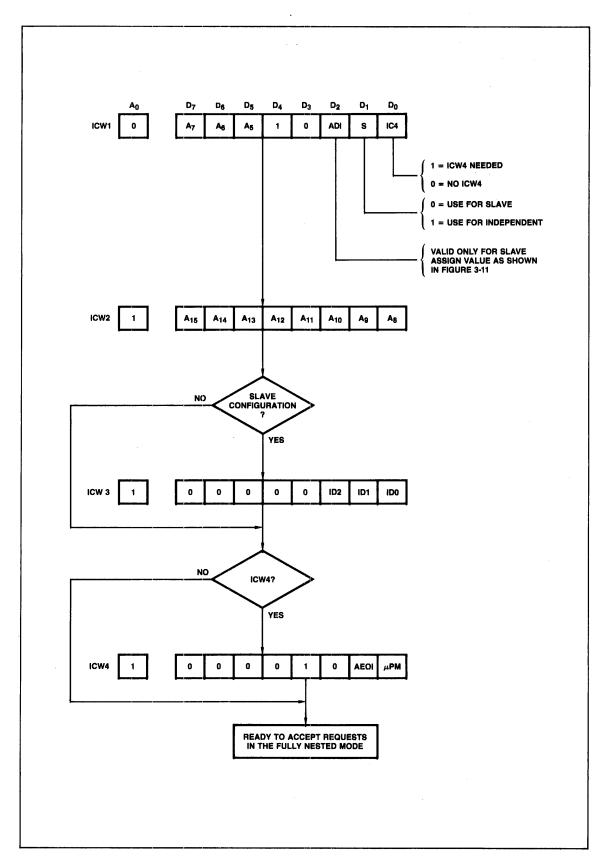

|          | Clock Connection4-4                                   | 3-11.                          | 8259A Initialization Com-                                |

|          | Parallel I/O Port4-5                                  |                                | mand Word (ICW) Format3-20                               |

|          |                                                       | 3-12.                          | Am95/3310 8259A Initi-                                   |

|          |                                                       | 2 12                           | alization Sequence3-23                                   |

|          |                                                       | 3-13.                          | 8259A Operation Command                                  |

| 5.       | Compies Information 5.1                               | <i>1</i> 1                     | Word (OCW) Format3-25                                    |

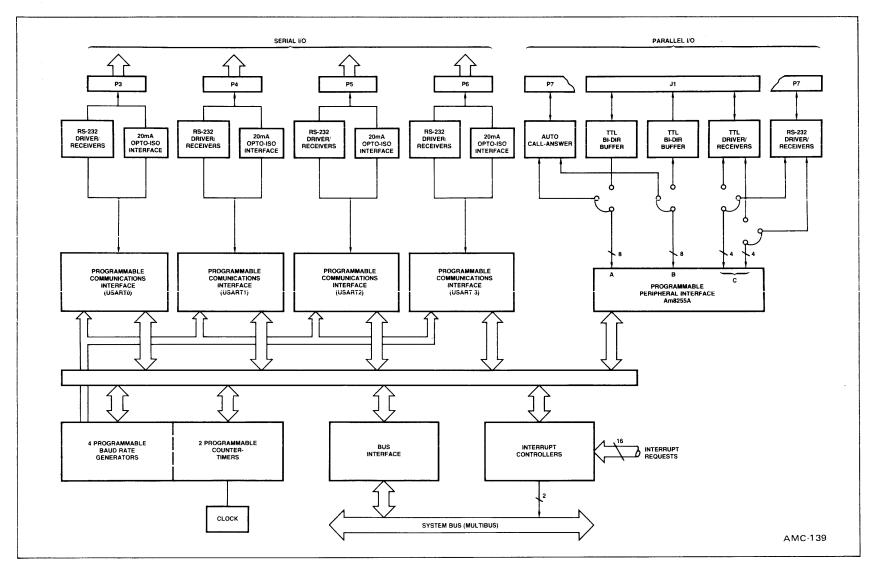

| J.       | Service Information5-1                                | 4-1.                           | Am95/3310 Communication                                  |

|          | Introduction5-1                                       |                                | Expansion Board Function                                 |

|          | Service and Repair Assistance5-1                      | 5-1.                           | Diagram4-2<br>Am95/3310 Components Loca-                 |

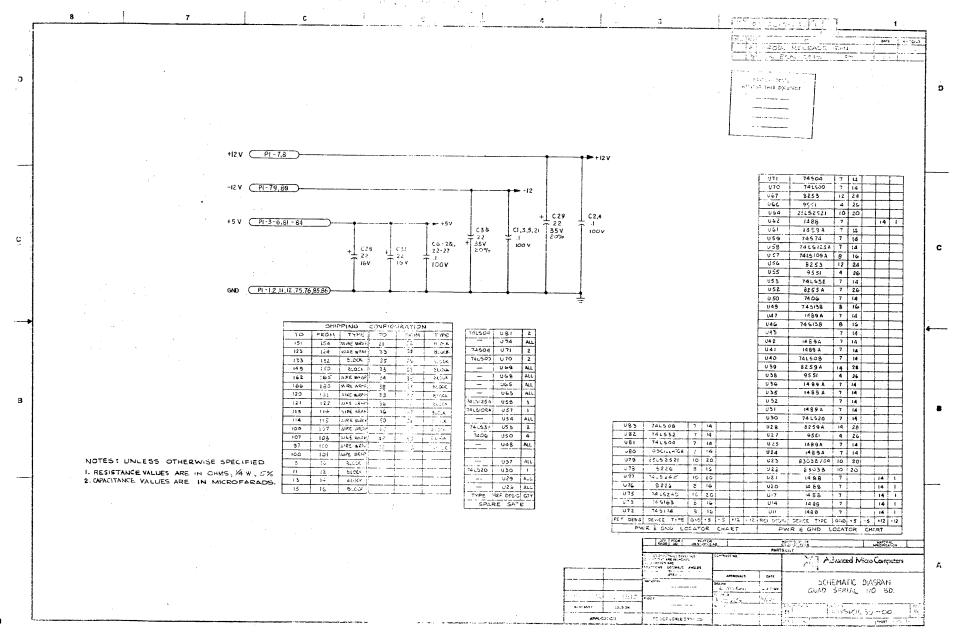

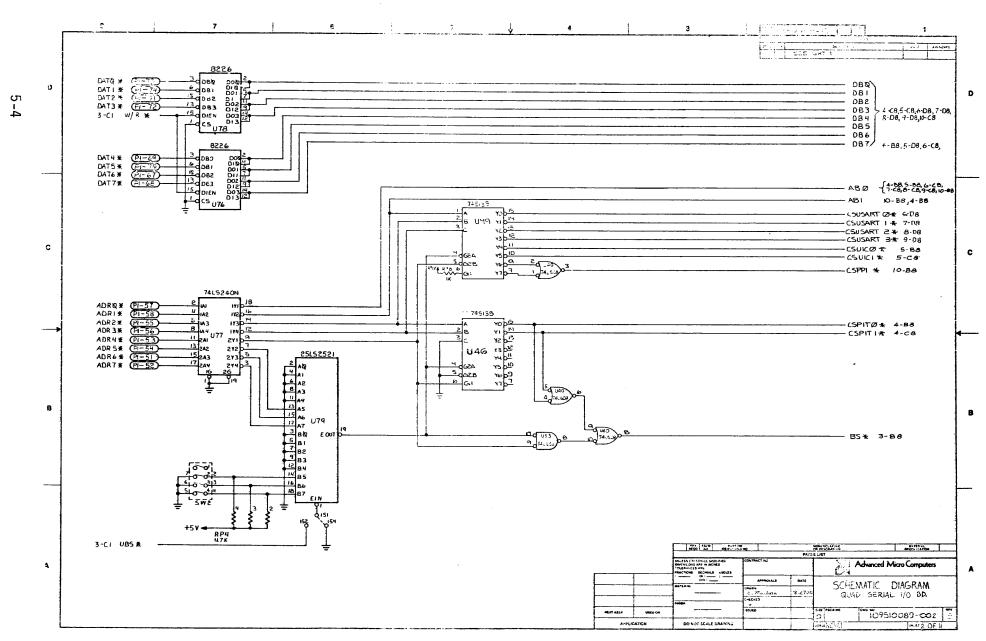

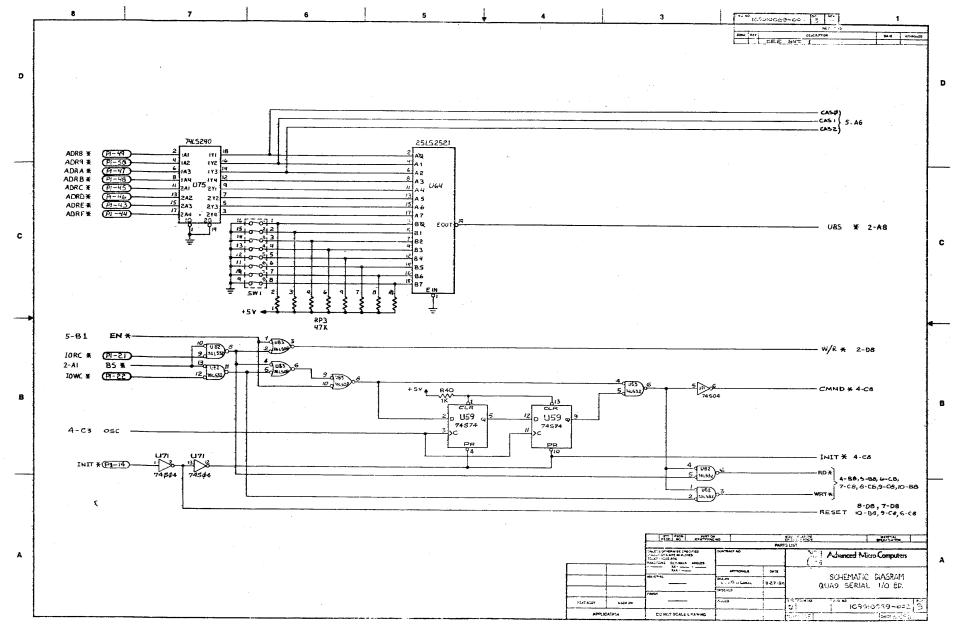

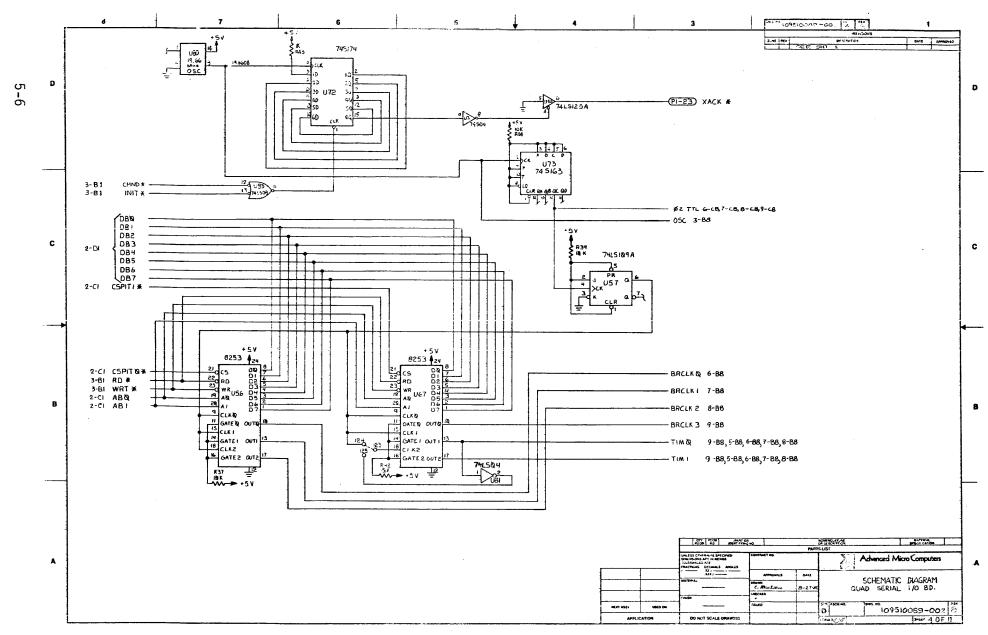

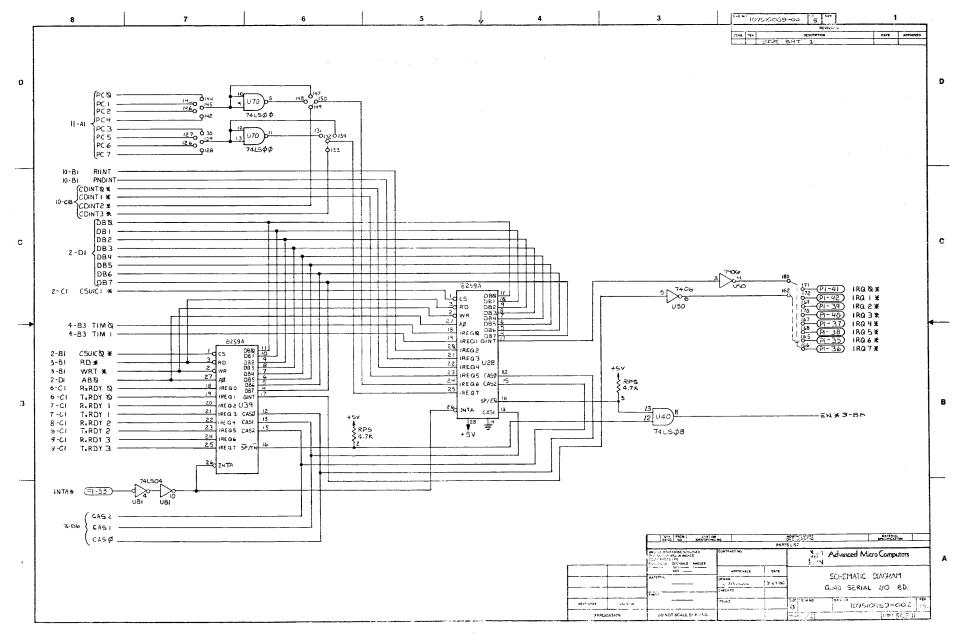

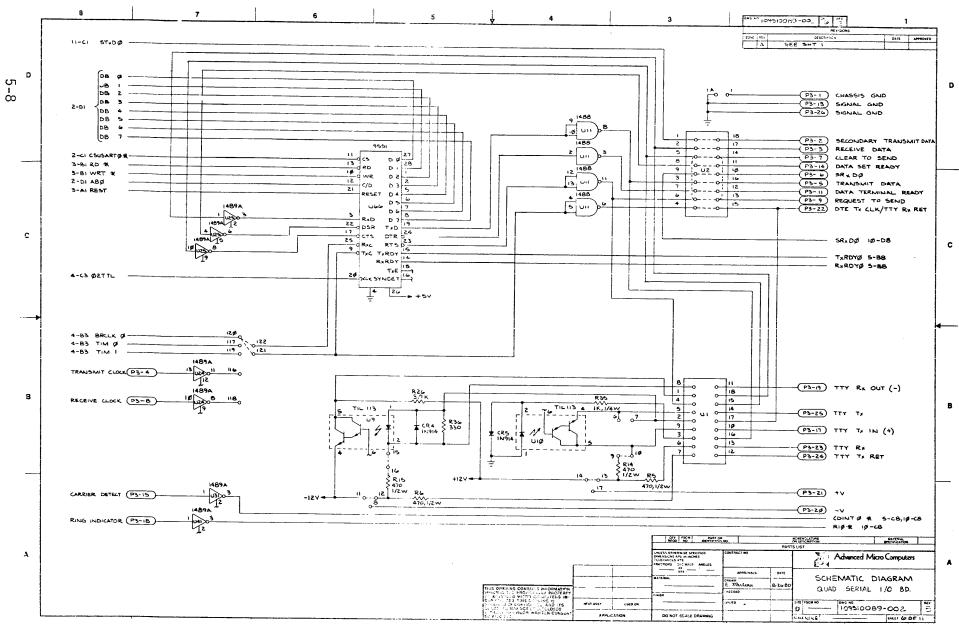

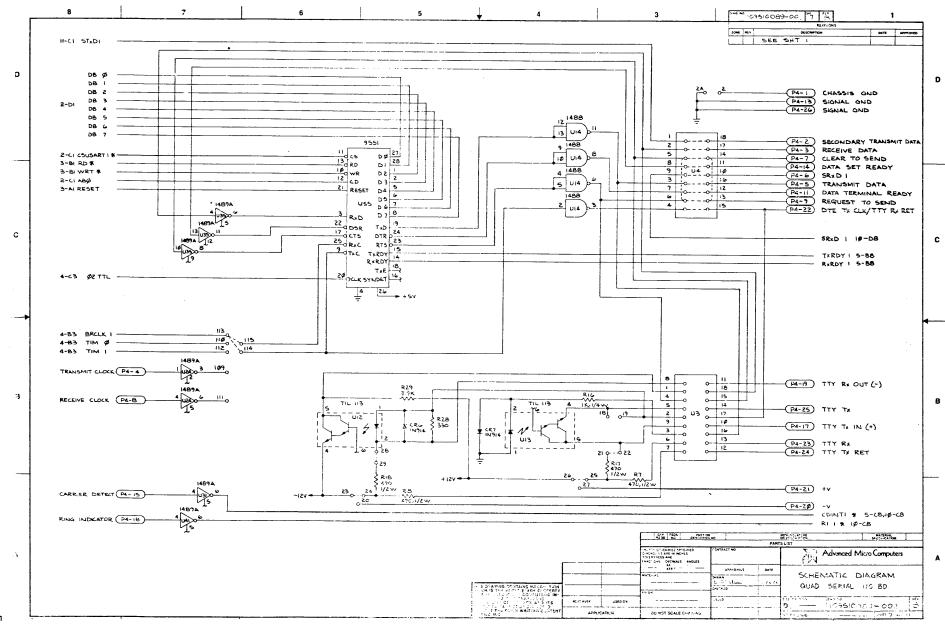

|          | Service Diagrams5-1                                   | J-1•                           | tion Diagram5-2                                          |

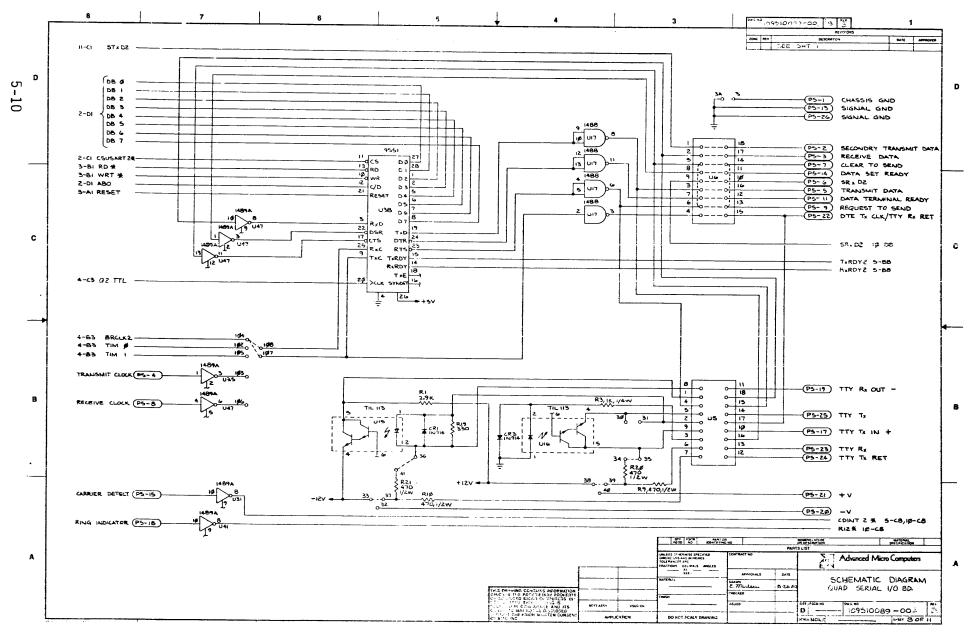

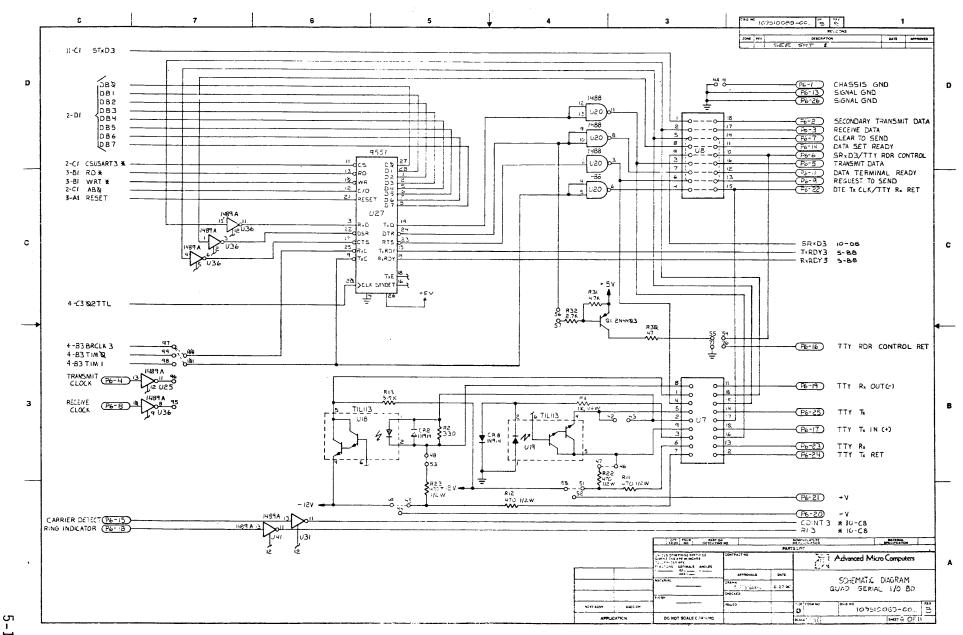

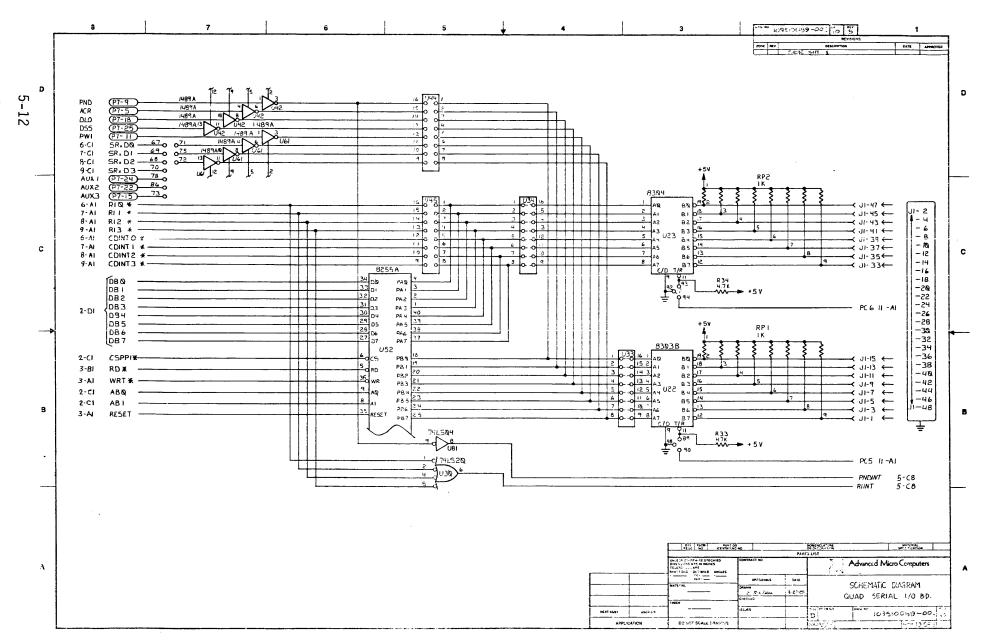

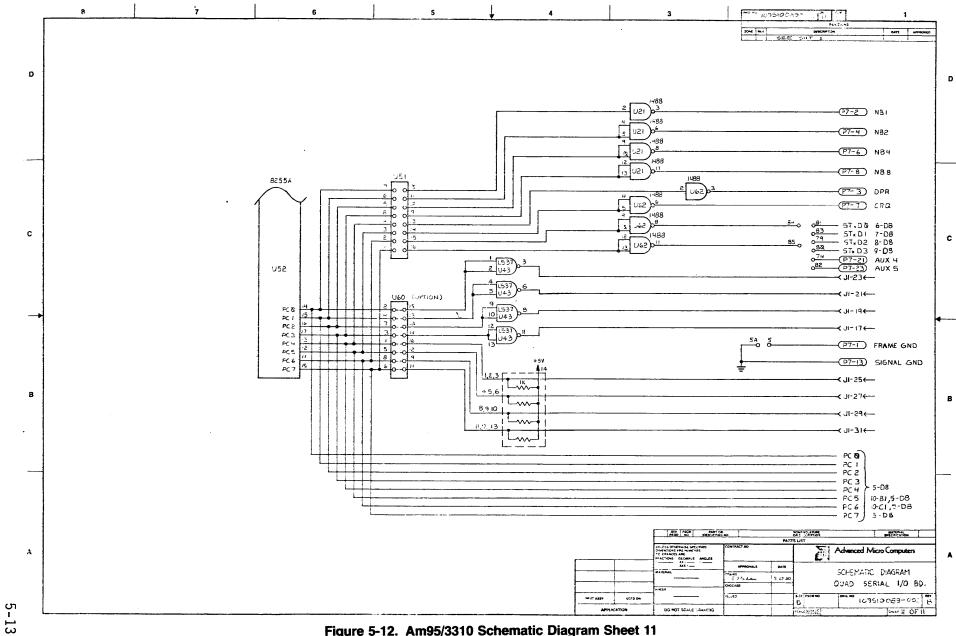

|          | Service Diagrams                                      | 5-2                            | Am95/3310 Schematic                                      |

|          |                                                       | Thru                           | Diagrams5-3                                              |

| FIGU     | IRES                                                  | 5-12.                          | Thru 5-13                                                |

|          |                                                       |                                | , , , , , , , , , , , , , , , , , , ,                    |

| 1-1.     |                                                       | TABLES                         | S                                                        |

|          | Diagram1-2                                            |                                |                                                          |

| 2-1.     | Basic Isolator Current-Loop                           | 1-1.                           | Specifications1-5                                        |

|          | Circuit2-9                                            | 2-1.                           | P1 Pin Assignments2-3                                    |

| 2-2.     | , , , , , , , , , , , , , , , , , , , ,               | 2-2.                           | P3-P6 Pin Assignment2-4                                  |

|          | Loop Circuit For Single                               | 2-3.                           | P7 Pin Assignment2-5                                     |

|          | Port2-10                                              | 2-4.                           | J1 Pin Assignment2-5                                     |

| 2-3.     | ` ' ' '                                               | 2-5.                           | I/O Address Boundary                                     |

|          | Loop Circuit For Single                               | 0.6                            | Selection2-7                                             |

| 2 /      | Port2-10                                              | 2-6.                           | Interrupt Selection2-7                                   |

| 2-4.     | •                                                     | 2-7.                           | Factory Installed TxC and                                |

| 3-1.     | Jumper Circuit For Port 02-11 Am9551 Synchronous Mode | 2-8.                           | RxC2-8                                                   |

| 3-1•     | Control Code3-5                                       | 2 <b>-</b> 0.<br>2 <b>-</b> 9. | Optional TxC and RxC Sources2-8 Current Loop Jumpers2-11 |

| 3-2.     |                                                       | 2-10.                          |                                                          |

| J – L. • | Control Code3-5                                       | 2-11.                          |                                                          |

| 3-3.     |                                                       | 2-12.                          | •                                                        |

|          | Word Format3-7                                        |                                | I/O Address Assignments3-2                               |

| 3-4.     |                                                       | 3-2.                           | PPI Interface Signals                                    |

| 3-5.     | Am8255A Operation Control                             |                                | (Factory Configuration)3-9                               |

|          | Word Format3-9                                        | 3-3.                           | PIT Count Value vs Rate Mult-                            |

| 3-6.     | PPI Port A and B Bit                                  |                                | iplier For Each Baud Rate3-15                            |

|          | Definitions3-11                                       | 3-4.                           | PIT Rate Generator Frequen-                              |

| 3-7.     | PPI Port C Bit Definitions                            |                                | cies and Timer Intervals3-16                             |

|          | If Auto Call Option Is                                | 3-5.                           | PIT Time Intervals vs Timer                              |

|          | Used3-11                                              |                                | Counts3-17                                               |

# CHAPTER 1 GENERAL INFORMATION

#### 1-1. INTRODUCTION

The Am95/3310 Communication I/O Expansion Board is designed to enhance AMC's MonoBoard products and Multibus compatible 8-bit and 16-bit microcomputer systems by providing an expansion of system serial and parallel communications, and a capability of being directly compatible with Bell 801 Automatic Calling Unit (ACU). The Am95/3310 programmable synchronous and asynchronous communications interface includes four serial I/O ports with jumper-selectable RS232C or current-loop buffering with optional Opto-isolation for TTY drivers/receivers, and independently programmable baud rate generator/timers. The programmable parallel interface has 24 software configurable parallel lines for supporting Bell 801 ACU or parallel I/O ports; sockets are provided for interchangeable line drivers/receivers, or terminators.

The 95/3310 interfaces directly to the Multibus and conforms with Multibus specifications in every respect. Major features are:

• Four Serial I/O Ports, RS232C Buffered

• 20 MA Current-Loop Interface for the four serial I/O ports (jumper block selectable) with sockets for Opto-isolators.

24 Line Parallel I/O Channel, RS232C or TTL Buffered

Multibus Compatible Interface

• Directly Compatible with Bell 801 ACU

16 Interrupt Request Lines with Programmable Priority

Processing Algorithm

- Sockets for interchangeable Line Drivers/Receivers in the Parallel Interface (8303 Octal Tri-State Inverting Bidirectional Transceivers or 8304 Octal Tri-State Bidirectional Transceivers)

- Six independently Programmable Baud-Rate Generators/ Timers

- 8 or 16-bit Multibus I/O Address Capability

- Switch-Selectable I/O Address Base Assignment

#### 1-2. PHYSICAL DESCRIPTION

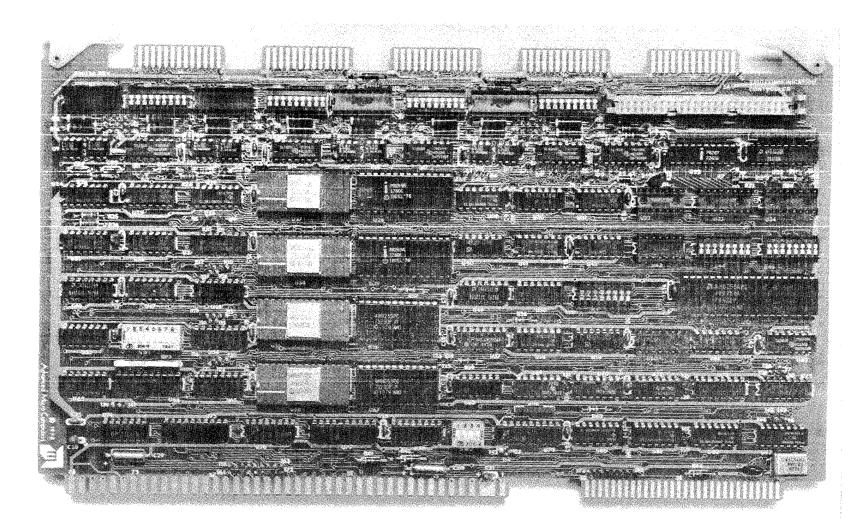

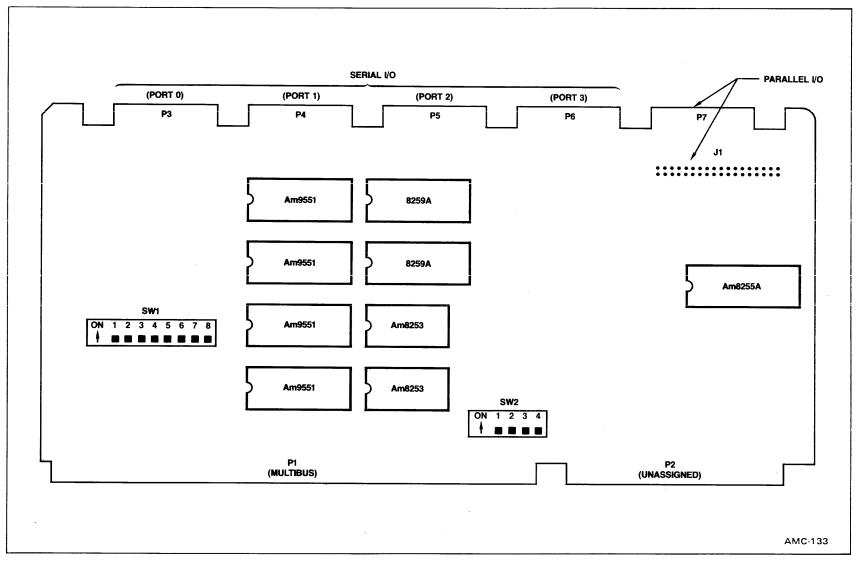

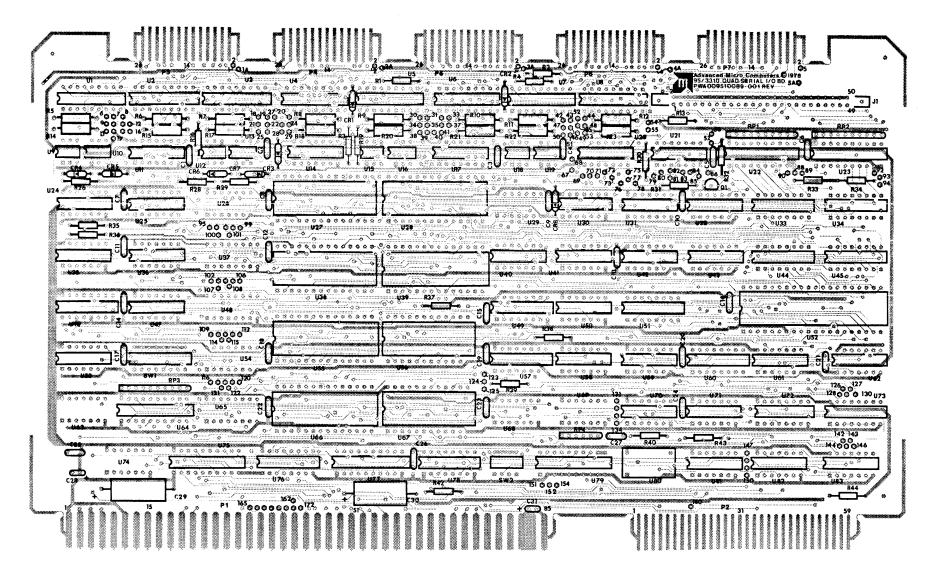

The Am95/3310 circuit components are mounted on a two layer printed circuit board as shown in Figure 1-1. Seven edge connectors and one flat cable connector provide bus and peripheral interfacing. Edge connector P1 interfaces to the Multibus which provides addresses, control signals, data transfers, and power requirements for board operation. P1 pin assignments are listed in table 2-1. Connector P2 is unassigned. Connectors P3 through P6 interface to the serial I/O ports (P3 interfaces Port 0, P4 interfaces Port 1, etc). Connectors P3

Figure 1-1. Am95/3310 Physical Block Diagram

through P6 pin assignments and signal names are listed in table 2-2. Connectors P7 and J1 interface to the parallel I/O ports. Connectors P7 and J1 pin assignments are listed in tables 2-3 and 2-4, respectively.

The Am95/3310 hardware consists of one Am8255A Programmable Peripheral Interface, two 8253 Programmable Interval Timers, two 8259A Universal Interrupt Controllers, four Am9551 Universal Synchronous/Asynchronous Receiver Transmitters, associated support circuitry, and Multibus interface circuitry.

On-board switches and jumpers establish address boundary, interrupt level, interval timer configuration, serial I/O clock selection, RS232C or current-loop operation, and parallel I/O port configuration.

#### 1-3. FUNCTIONAL DESCRIPTION

The Am95/3310 communicates with 8-bit or 16-bit CPUs via the Multibus (system-bus). Addresses on the system-bus are monitored for an address that matches the on-board switch settings; only an address that matches is decoded into board functions and chip-selects. Using I/O commands, a CPU can initialize, read from, or write to the Am95/3310. In return, the Am95/3310 supplies status and data.

Each of the serial I/O ports is RS232C plug compatible and controlled by an Am9551 USART (Universal Synchronous/Asynchronous Receiver/Transmitter). All of the serial I/O ports are wired for RS232 Data Communication Equipment (DCE) protocol. The USARTs can be individually programmed for both synchronous and asynchronous serial data transmission formats.

In the synchronous mode the following are programmable:

- Character length

- Sync character (or characters)

- Parity

In the asynchronous mode the following are programmable:

- Character length

- Baud rate factor (clock divide ratios of 1, 16, or 64)

- Stop bits

- Parity

In both the synchronous and asynchronous modes, each serial I/O port features half or full-duplex, double-buffered transmit and receive capability. In addition, USART error detection circuits can check for parity, overrun, and framing errors. The USART transmit and receive clock rates are derived from six independently programmable Baud rate/time generators.

Each serial I/O port supports input and output that require isolated current-loops. The Am95/3310 can supply 20mA to an external loop.

The parallel interface has 24 I/O lines which can be jumpered for either TTL or RS232C compatibility. It can be jumpered to interface automatic calling units similar to Bell 801C or for any general purpose or auxiliary functions.

Two Am8253 Programmable Interval Timer (PIT) chips provide six time/rate generators that can be independently programmed, to generate baud rate clocking for each USART. As shipped, four of the timers are used as baud rate clocks; the remaining two can be used for miscellaneous functions such as transmit and receive clocks or real-time interrupt.

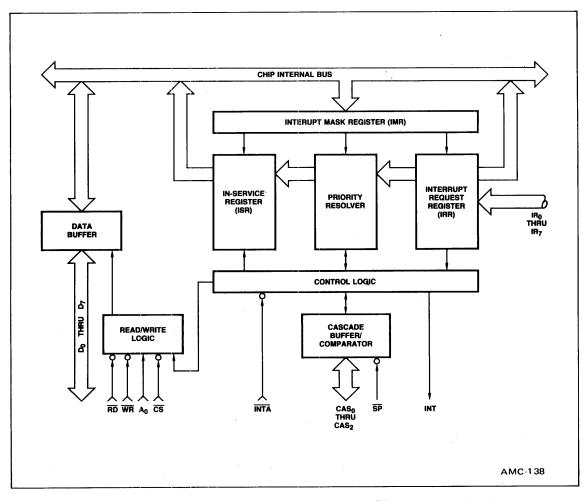

Two 8259A Universal Interrupt Controllers (PICs) manage up to 16 maskable interrupt request inputs, resolve priorities, and provide bus vectoring information for each interrupt. The PICs are set-up by the initialization routine to call the service routines at the proper location, and service the interrupts on either a fixed or rotating basis in either an interrupt or polled mode, allowing flexibility to establish interrupt service priorities. When an Am8259A receives an interrupt request, an interrupt output is issued onto the multibus. When the interrupt is acknowledged, the master Am8259A on the CPU board issues the CALL CODE and the interrupting slave Am8259A issues the appropriate 16-bit branching address. After an interrupt has been serviced, the software resets the corresponding bit-flag.

#### 1-4. SPECIFICATIONS

Physical, environmental, and technical specifications for the Am95/3310 board are listed in table 1-1.

#### TABLE 1-1. SPECIFICATIONS

#### PHYSICAL

#### Board Dimensions:

WIDTH 30.48 cm (12 inches) 17.15 cm (6.75 inches) 1.50 cm (0.60 inches) DEPTH THICKNESS

#### **ENVIRONMENTAL**

Operating Temperature: 0°C to 55°C

Relative Humidity:

Up to 90% without condensation

Storage Temperature: -40°C to 75°C

#### POWER

| VOLTAGE    | TYPICAL CURRENT | MAXIMUM CURRENT |

|------------|-----------------|-----------------|

| VCC = +5V  | 1.35A           | 1.90A           |

| VDD = +12V | 0.19A           | 0.27A           |

| VAA = -12V | 0.18A           | 0.25A           |

#### TECHNICAL

Interface:

RS232C or 20mA Current Loop or TTL

Number of Ports:

4 Serial and 3 Parallel

Transmission Type:

Synchronous or Asynchronous

Transmission Mode:

Full or Half-Duplex

Asynchronous Format:

5 to 8-bit Characters Break Character Generation 1, 1.5, or 2 Stop-bits False Start-bit Detector

Synchronous Format:

5 to 8-bit Characters 1 or 2 Sync Characters Automatic Sync Insertion

Serial Baud Rate: Serial I/O Address: Parallel I/O Address: Programmable See table 3-1 See table 3-1

Interrupt Controller

Address:

See table 3-1

Programmable Interval

Timers Addresses:

See table 3-1

#### TABLE 1-1. SPECIFICATIONS (Cont.)

TECHNICAL (continued):

I/0 Addressing: The USART, Interval Timer, Interrupt Controller, and Parallel Interface registers are configured as a block of 24 I/O address locations. The location of this block is jumper-selectable to begin at any 32-byte I/O address boundary (i.e. 00H, 20H, 40H,

.... EOH).

I/O Access

Time:

375 nanoseconds, typical

Compatible Connectors/Cable:

| INTERFACE                            | NO. OF<br>PINS | CENTERS<br>(INCHES) | CONNECTOR CONNECTOR    | PART NUMBER                                                        |

|--------------------------------------|----------------|---------------------|------------------------|--------------------------------------------------------------------|

| MULTIBUS                             | 86             | 0.156               | Solder                 | VPB01E43D00A1<br>MP-01560430BW4<br>2VH43AV5                        |

| Serial and 801C<br>Edge Connectors   | 26             | 0.1                 | Flat Crimp<br>Wirewrap | 609-2615<br>88106-1<br>3462-0001 Crimp<br>SD6726 Series<br>H311113 |

| Parallel I/O Flat<br>Cable Connector | 50             | 0.1                 |                        | ЗМ Δ3496                                                           |

#### Sample Baud Rate:

| FREQUENCY <sup>1</sup> (kHz, SOFTWARE |               | BAUD RATE (H   | z) <sup>2</sup> |  |

|---------------------------------------|---------------|----------------|-----------------|--|

| SELECTABLE)                           | SYNCHRONOUS   | S ASYNCHRONOUS |                 |  |

|                                       |               | ÷ 16           | ÷ 64            |  |

| 153.60<br>76.80                       |               | 9600<br>4800   | 2400<br>1200    |  |

| 38.40                                 | 38400         | 2400           | 600             |  |

| 19.20<br>9.60                         | 19200<br>9600 | 1200<br>600    | 300<br>150      |  |

| 4.80                                  | 4800          | 300            | 75              |  |

| 6.98                                  | 6980          |                | 110             |  |

NOTES: 1. Frequency selected by I/O writes of appropriate 16-bit frequency factor to Baud Rate Register.

Baud rates shown here are only a sample subset of possible 2. software programmable rates available. Any frequency from 18.75 Hz to 614.4 kHz may be generated utilizing on-board crystal oscillator and 16-bit Programmable Interval Timer (used here as frequency divider).

#### TABLE 1-1. SPECIFICATIONS (Cont.)

INTERVAL TIMER AND BAUD RATE GENERATOR

Input Frequency: 1.2288 MHz ±0.1% for 8253 PIT input;

0.814 microsecond period, nominal.

Output Frequencies:

| FUNCTION                           | SINGLE TIMER             |                          | DUAL TIMERS<br>(TWO TIMERS CASCADED) |                  |

|------------------------------------|--------------------------|--------------------------|--------------------------------------|------------------|

| FUNCTION                           | MINIMUM                  | MAXIMUM                  | MINIMUM                              | MAXIMUM          |

| Real-Time<br>Interrupt<br>Interval | 1.63<br>micro<br>seconds | 53.3<br>milli<br>seconds | 3.26<br>micro<br>seconds             | 58.22<br>minutes |

| Rate<br>Generator<br>(Frequency)   | 18.76 Hz                 | 613.4 kHz                | 0.00029 Hz                           | 306.7 kHz        |

#### INTERFACE COMPATIBILITY

Serial I/O: EIA Standard RS232C signals provided and supported:

Carrier Detect

Receive Data Ring Indicator

Clear to Send Data Set Ready

Secondary Receive Data

Data Terminal Ready

Secondary Transmit Data

Request to Send Receive Clock

Transmit Clock Transmit Data

Parallel I/0:

The board has three programmable bidirectional 8-bit I/O ports with TTL drivers and receivers controlled by an 8255A Programmable Peripheral Interface device or optionally can be configured to be Bell 801C compatible with RS232C

drivers and receivers.

System Bus: Compatible with Multibus

# CHAPTER 2 INSTALLATION AND INTERFACING

#### 2-1. INTRODUCTION

This chapter describes procedures for installing the Am95/3310 Communication Controller. These include unpacking and inspection, power and cooling requirements, bus interface requirements, jumper configurations, current-loop considerations, and device cabling.

## 2-2. UNPACKING AND INSPECTION

Inspect the shipping carton immediately upon receipt for evidence of mishandling during transit. If the shipping carton is severely damaged or water-stained, request that the carrier's agent be present when the carton is opened. If the carrier's agent is not present when the carton is opened and the contents of the carton are damaged, keep the carton and packing material for the agent's inspection.

Do not attempt to service a product damaged in shipment, this will void warranty. For any repairs or replacements, contact AMC Customer Service for further instructions. It is also suggested that salvageable shipping cartons and packing materials be saved for future use in the event the product must be shipped.

#### 2-3. POWER REQUIREMENTS

The Am95/3310 requires +5V, +12V, and -12V power supply inputs. The current required from these supplies are listed in table 1-1. Ensure that the power supply has sufficient current to accommodate the Am95/3310 requirements.

#### 2-4. COOLING REQUIREMENTS

The Am95/3310 must have adequate air circulation to prevent a temperature rise above 50°C (131°F).

## 2-5. BUS INTERFACE REQUIREMENTS

The Am95/3310 has seven edge connectors and one flat cable connector providing bus interfacing. Edge connector P1 (86-pin) pin assignments

are listed in table 2-1. P2 connector is unassigned. P3 through P6 (26-pin connectors) pin assignments are listed in table 2-2. P7 (26-pin) and J1 (50-pin) pin assignments are listed in table 2-3 and 2-4, respectively.

## 2-6. USER SELECTABLE OPTIONS

The Am95/3310 is shipped from the factory jumpered as required by the option(s) ordered. The address is set to respond to an 8-bit I/0 address starting at 80H. On-board jumpers can be used to select interval timer configuration, two group-type interrupt connections, serial I/0 clock selection, RS232C or current-loop operation, and parallel I/0 port configuration.

#### 2-7. I/O ADDRESS BASE

The block of 24 I/O addresses is switch-selectable to begin on any 32-byte I/O address boundary within an 8-bit or 16-bit I/O address space. As shipped from the factory, the Am95/3310 is assigned to an 8-bit I/O address space at 80H and will respond to addresses 80H through 97H. If some other address boundary is desired, change SW2 and SW1 settings as listed in table 2-5.

# 2-8. TRANSFER ACKNOWLEDGE (XACK\*)

XACK\* is issued 375 nanoseconds, typically, after the receipt of an I/O command. Best case XACK\* response is 350 nanoseconds; worst case is 400 nanoseconds. No jumpers are required.

#### 2-9. SYSTEM INTERRUPT CONFIGURATION

The Am95/3310 has an interrupt pad that can connect the two Programmable Interrupt Controllers (PICs) interrupt outputs to any of the eight Multibus interrupt lines, IRQ0\* through IRQ7\*. As shipped, interrupts from PICO and PIC1 are jumpered to IRQ6 and IRQ7, respectively. Table 2-6 lists source and destination jumpers.

TABLE 2-1. P1 PIN ASSIGNMENTS

| PIN*                                         | SIGNAL                                           | FUNCTION                                                                                                                                                                                                                                | PIN*                                         | SIGNAL                                                      | FUNCTION       |

|----------------------------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-------------------------------------------------------------|----------------|

| 1<br>2<br>3                                  | GND<br>GND<br>+5VDC                              | GROUND                                                                                                                                                                                                                                  | 44<br>45<br>46                               | ADRF*<br>ADRC*<br>ADRD*                                     |                |

| 4<br>5<br>6<br>7<br>8                        | +5VDC<br>+5VDC<br>+5VDC<br>+12VDC<br>+12VDC      | POWER INPUT                                                                                                                                                                                                                             | 47<br>48<br>49<br>50<br>51                   | ADRA*<br>ADRB*<br>ADR8*<br>ADR9*<br>ADR6                    | ADDRESS<br>BUS |

| 9<br>10<br>11<br>12<br>13                    | GND<br>GND                                       | GROUND                                                                                                                                                                                                                                  | 52<br>53<br>54<br>55<br>56                   | ADR7*<br>ADR4*<br>ADR5*<br>ADR2*<br>ADR3*                   |                |

| 14<br>15<br>16<br>17                         | INIT*                                            | SYSTEM INITIALIZE                                                                                                                                                                                                                       | 57<br>58<br>59<br>60                         | ADRO*<br>ADR1*                                              |                |

| 18<br>19<br>20<br>21<br>22                   | IORC*                                            | I/O READ COMMAND<br>I/O WRITE COMMAND                                                                                                                                                                                                   | 61<br>62<br>63<br>64<br>65                   |                                                             |                |

| 23<br>24<br>25<br>26<br>27<br>28<br>29       | XACK*                                            | TRANSFER ACKNOWLEDGE                                                                                                                                                                                                                    | 66<br>67<br>68<br>69<br>70<br>71<br>72       | DAT6*<br>DAT7*<br>DAT4*<br>DAT5*<br>DAT2*<br>DAT3*          | DATA<br>BUS    |

| 30<br>31<br>32<br>33<br>34                   | INTA*                                            | INTERRUPT ACKNOWLEDGE                                                                                                                                                                                                                   | 73<br>74<br>75<br>76                         | DATO*<br>DAT1*<br>GND<br>GND                                | GROUND         |

| 35<br>36<br>37<br>38<br>39<br>40<br>41<br>42 | IRQ6* IRQ7* IRQ4* IRQ5* IRQ2* IRQ3* IRQ0* IRQ01* | INTERRUPT REQUEST ON LEVEL 6 INTERRUPT REQUEST ON LEVEL 7 INTERRUPT REQUEST ON LEVEL 4 INTERRUPT REQUEST ON LEVEL 5 INTERRUPT REQUEST ON LEVEL 2 INTERRUPT REQUEST ON LEVEL 3 INTERRUPT REQUEST ON LEVEL 0 INTERRUPT REQUEST ON LEVEL 1 | 77<br>78<br>79<br>80<br>81<br>82<br>83<br>84 | -12VDC<br>-12VDC<br>+5VDC<br>+5VDC<br>+5VDC<br>+5VDC<br>GND | POWER INPUT    |

| 43                                           | ADRE*                                            | ADDRESS BUS                                                                                                                                                                                                                             | 85                                           | GND                                                         | GROUND         |

| All un                                       | assigned pi                                      | ns are reserved.                                                                                                                                                                                                                        |                                              | • • • • • • • • • • • • • • • • • • •                       |                |

TABLE 2-2. P3-P6 PIN ASSIGNMENTS

| PIN | SIGNAL                 | RS232C<br>PIN<br>NUMBER | PIN | SIGNAL                                                         | RS232C<br>PIN<br>NUMBER |

|-----|------------------------|-------------------------|-----|----------------------------------------------------------------|-------------------------|

| 1   | Chassis GND            | 1                       | 2   | Secondary Transmit<br>Data                                     | 14                      |

| 3   | Receive Data           | 2                       | 4   | DCE TxC (Transmit                                              | 15                      |

| 5   | Transmit Data          | 3                       | 6   | Clock)<br>Secondary Receive<br>Data/ TTY RDR<br>Control (Note) | 16                      |

| 7   | Clear to Send          | 4                       | 8   | DCE RxC (Receive Clock)                                        | 17                      |

| 9   | Request to Sent        | 5                       | 10  | Not Used                                                       | 18                      |

| 11  | Data Terminal<br>Ready | 6                       | 12  | Not Used                                                       | 19                      |

| 13  | Signal GND             | 7                       | 14  | Data Set Ready                                                 | 20                      |

| 15  | Carrier Detect         | 8                       | 16  | TTY RDR Control<br>RET (Note)                                  | 21                      |

| 17  | TTY Tx IN (+)          | 9                       | 18  | Ring Indicator                                                 | 22                      |

| 19  | TTY Rx OUT (-)         | 10                      | 20  | -V                                                             | 23                      |

| 21  | <b>+V</b>              | 11                      | 22  | DTE TxC/TTY Rx RET                                             | 24                      |

| 23` | TTY Rx                 | 12                      | 24  | TTY Tx RET                                                     | 25                      |

| 25  | TTY Tx                 | 13                      | 26  | Signal GND                                                     |                         |

Note: TTY RDR Control, TTY RDR Control RET are only for Serial I/O Port 3 (P6)

TABLE 2-3. P7 PIN ASSIGNMENTS

| PIN | SIGNAL                  | RS232C PIN<br>NUMBER | PIN | SIGNAL                | RS232C PIN<br>NUMBER |

|-----|-------------------------|----------------------|-----|-----------------------|----------------------|

| 1   | Frame GND               | 1                    | 2   | NB1                   | 14                   |

| 3   | Digit                   | 2                    | 4   | NB2                   | 15                   |

| 5   | Abandon Call<br>& Retry | 3                    | 6   | NB4                   | 16                   |

| 7   | Call Request            | 4                    | 8   | NB8                   | 17                   |

| 9   | Present Next<br>Digit   | 5                    | 10  |                       | 18                   |

| 11  | Power Indication        | 6                    | 12  |                       | 19                   |

| 13  | Signal GND              | 7                    | 14  |                       | 20                   |

| 15  | Auxiliary 3             | 8                    | 16  |                       | 21                   |

| 17  |                         | 9                    | 18  | Data Line<br>Occupied | 22                   |

| 19  |                         | 10                   | 20  |                       | 23                   |

| 21  | Auxiliary 4             | 11                   | 22  | Auxiliary 2           | 24                   |

| 23  | Auxiliary 5             | 12                   | 24  | Auxiliary 1           | 25                   |

| 25  | Data Set Status         | 13                   | 26  |                       |                      |

TABLE 2-4. J1 PIN ASSIGNMENTS

| PIN                                                                   | SIGNAL                                              | PIN                                                            | SIGNAL                                                                                  | PIN                                                              | SIGNAL        | PIN                                                                        | SIGNAL        |

|-----------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------|---------------|----------------------------------------------------------------------------|---------------|

| 1<br>3<br>5<br>7<br>9<br>11<br>13<br>15<br>17<br>19<br>21<br>23<br>25 | PB7 PB6 PB5 PB4 PB3 PB2 PB1 PB0 PC3 PC2 PC1 PC0 PC4 | 27<br>29<br>31<br>33<br>35<br>37<br>39<br>41<br>43<br>45<br>47 | PC5<br>PC6<br>PC7<br>PA7<br>PA6<br>PA5<br>PA4<br>PA3<br>PA2<br>PA1<br>PA0<br>Unassigned | 2<br>4<br>6<br>8<br>10<br>12<br>14<br>16<br>18<br>20<br>22<br>24 | Signal<br>GND | 26<br>28<br>30<br>32<br>34<br>36<br>38<br>40<br>42<br>44<br>46<br>48<br>50 | Signal<br>GND |

#### 2-10. SERIAL I/O CLOCK SELECTION

The two Am8253 Programmable Interval Timers (PITO and PIT1) provide six independent Baud-Rate clocks as follows:

| (TIMERS)   | (COUNTER) | (OUTPUT) | (DESCRIPTION)                                   |

|------------|-----------|----------|-------------------------------------------------|

| PITO (U56) | 0         | BRCLK0   | Baud-rate clock,Port 0.                         |

| PITO (U56) | 1         | BRCLK1   | Baud-rate clock,Port 1.                         |

| PITO (U56) | 2         | BRCLK2   | Baud-rate clock,Port 2.                         |

| PIT1 (U67) | 0         | BRCLK3   | Baud-rate clock,Port 3.                         |

| PIT1 (U67) | 1         | TIMO     | User available Auxi-<br>liary clock or timer 0. |

| PIT1 (U67) | 2         | TIM1     | User available Auxi-<br>liary clock or timer 1. |

These clocks may be at the same frequency or at different frequencies. Clock signals BRCLKO through BRCLK3, TIMO, and TIM1 can be programmed for any integer submultiple of the clock frequency range from 18.75 Hz to 614.4 KHz. When the two auxiliary timers are connected in series (jumper 123 connected to 125), the output from PIT 1, timer 1 (TIMO) provides clock input for PIT 1 timer 2 (TIM1). Series connection permits lower clock rates or longer time intervals. Thus, clock frequencies from 0.00029 Hz to 306.7 KHz can be realized.

#### 2-11. SERIAL INTERFACE

The four Am9551 USARTs used in the serial I/O circuits can be independently configured to function with data sets, data processing terminals, or optically-isolated current-loop devices. Each RS232 port is wired to look like an RS232C DCE (Data Communications Equipment). To implement this flexibility, the Am95/3310 is shipped with four universal headers. These headers must be installed in U1, U3, U5, and U7 for the respective channel to operate as a 20mA current-loop interface and in U2, U4, U6, and U8 for the respective channel to operate as an RS232C interface. To use the headers in standard RS232C or current-loop applications, clip the jumper connected between (This makes the header function as a straight adjacent header pins. across jumper.) When the RS232C interface is being used with a terminal that does not return CTS (Clear To Send) in response to RTS (Request To Send), the header must be configured differently. configure the header so that the RTS signal is turned around as the CTS signal, remove all adjacent inter-pin jumpers except the one between pins 5 and 6. (This configures the header so that all pins including 5 and 6 are connected straight across; in addition, pins 5 and 6 are shorted together.)

TABLE 2-5. I/O ADDRESS BOUNDARY SELECTION

| SWITCH SW1 †† (UPPER 8-BIT<br>ADDRESS FOR 16-BIT I/O ADDRESS<br>ONLY)                 | SWITCH SW2<br>(8-BIT I/O ADDRESS)                             | I/O ADDRESS<br>BOUNDARY<br>SELECTED                    |

|---------------------------------------------------------------------------------------|---------------------------------------------------------------|--------------------------------------------------------|

| 8 7 6 5 4 3 2 1  ADF ADE ADD ADC ADB ADA AD9 AD8  0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | AD7 AD6 AD5  0 0 0 0 0 1 0 1 0 0 1 1 1 0 0† 1 0 1 1 1 0 1 1 1 | 00H<br>20H<br>40H<br>60H<br>80H†<br>A0H<br>COH<br>E OH |

t As shipped = 80H where 1 = 0pen, 0 = Closed

**TABLE 2-6. INTERRUPT SELECTION**

| SOURCE OF INTERRUPT | JUMPER     | JUMPER                                               | DESTINATION                                                  |

|---------------------|------------|------------------------------------------------------|--------------------------------------------------------------|

| PICO<br>PIC1        | 162<br>180 | 171<br>172<br>169<br>170<br>167<br>168<br>165<br>166 | IRQ0<br>IRQ1<br>IRQ2<br>IRQ3<br>IRQ4<br>IRQ5<br>IRQ6<br>IRQ7 |

#### 2-12. TRANSMIT/RECEIVE CLOCK SELECTION

Jumpers are used to select the Transmit Clock (TxC) and Receive Clock (RxC) sources. Tables 2-7 and 2-8 list source, jumper and connection, signal name, and destination for TxC and RxC. As shipped, each baud rate generator is connected to it's respective channel's TxC or RxC.

These bits are ignored when configured as shipped. To configure the board to respond to a 16-bit address, remove jumper 151-154 and add jumper 151-152.

TABLE 2-7. FACTORY INSTALLED TxC and RxC

| FROM | JUMPER | JUMPER | T0    | SIGNAL | USART |

|------|--------|--------|-------|--------|-------|

| PITO | 120    | 121    | (TxC) | BRCLKO | 0     |

| PIT0 | 120    | 122    | (RxC) | BRCLKO | 0     |

| PIT0 | 113    | 114    | (TxC) | BRCLK1 | 1     |

| PIT0 | 113    | 115    | (RxC) | BRCLK1 | 1     |

| PIT0 | 104    | 107    | (TxC) | BRCLK2 | 2     |

| PIT0 | 104    | 108    | (RxC) | BRCLK2 | 2     |

| PIT1 | 97     | 100    | (RxC) | BRCLK3 | 3     |

| PIT1 | 97     | 101    | (TxC) | BRCLK3 | 3     |

TABLE 2-8. OPTIONAL TxC and RxC SOURCES

| USART | OPTIONAL SIGNAL                                             | JUMPER                   | JUMPER     | USART SIGNAL |

|-------|-------------------------------------------------------------|--------------------------|------------|--------------|

| 0     | TIMO<br>TIMI<br>DCE XMIT CLK, PORT O<br>DCE RCV CLK, PORT O | 117<br>119<br>116<br>118 | 122<br>121 | RxC<br>TxC   |

| 1     | TIMO<br>TIMI<br>DCE XMIT CLK, PORT 1<br>DCE RCV CLK, PORT 1 | 110<br>112<br>109<br>111 | 115<br>114 | RxC<br>TxC   |

| 2     | TIMO<br>TIM1<br>DCE XMIT CLK, PORT 2<br>DCE RCV CLK, PORT 2 | 102<br>105<br>103<br>106 | 108<br>107 | RxC<br>TxC   |

|       | TIMO<br>TIM1<br>DCE XMIT CLK, PORT 3<br>DCE RCV CLK, PORT 3 | 99<br>98<br>96<br>95     | 100<br>101 | R×C<br>T×C   |

#### 2-13. SERIAL I/O PORT CURRENT/LOOP CONFIGURATION

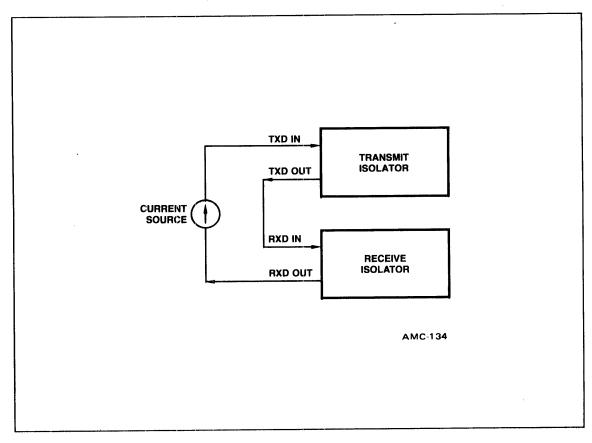

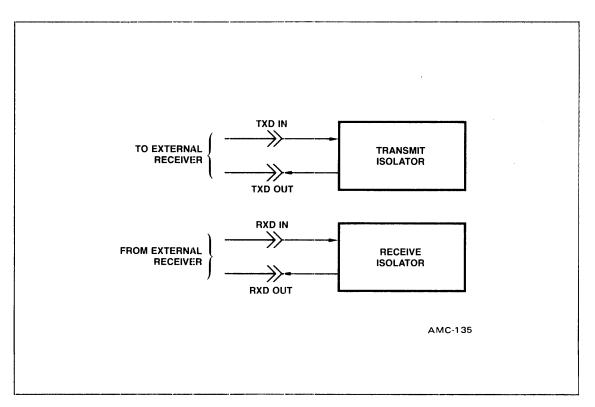

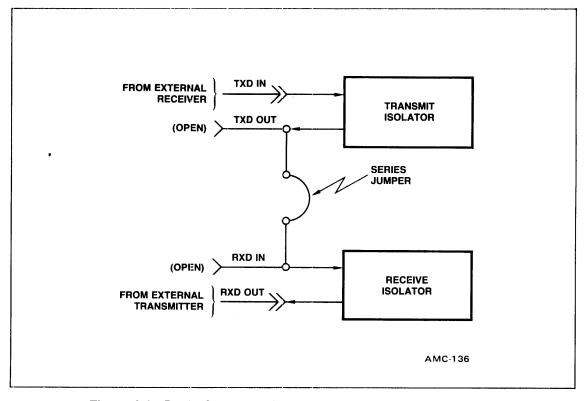

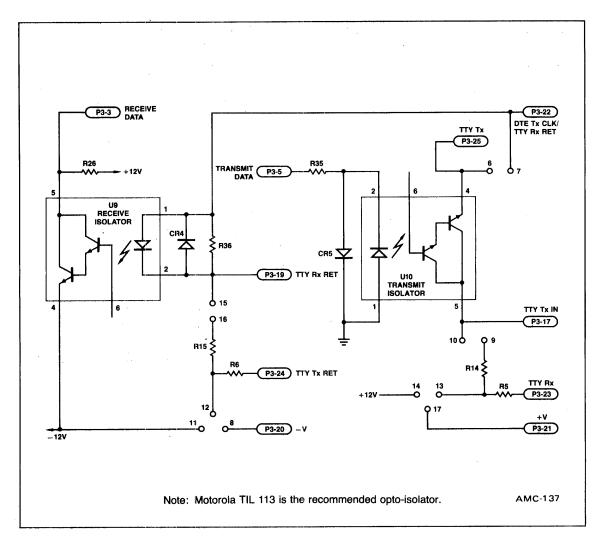

The four serial interface current-loop circuits can be jumpered for use with optically isolated current-loop devices. A block diagram of the basic current-loop circuit shown in figure 2-1 consists of a receive isolator, transmit isolator, and a current source. The current-loop circuitry in each serial I/O interface can be connected in one of two basic configurations: a separate (double) loop shown in figure 2-2 or a series (single) loop shown in figure 2-3. A simplified diagram of the jumpers used to configure port O is shown in figure 2-4. The voltage source, current sorce, and loop configuration jumpers are installed in port O as follows:

- Voltage Source to use the internal ±12 V source, connect jumpers between jumper pins 11-12 and 13-14. To use an external ±12 V source, connect jumpers between jumper pins 8-12 and 13-17.

- Current Source voltage for current source operation can be connected internally or externally. To connect the current source voltage internally, connect a jumper between jumper pins 9-10 and 15-16. To use a voltage source supplied by the external transmitter/receiver, no jumpers should be connected between jumper pins 9-10 and 15-16.

Figure 2-1. Basic Isolator Current-Loop Circuit

Figure 2-2. Basic Separate (or Double) Loop Circuit for Single Port

Figure 2-3. Basic Series (or Single) Loop Circuit for Single Port

Figure 2-4. Simplified Current Loop Jumper Circuit for Port 0

• Loop Configuration - a jumper must, or must not, be connected between jumper pins 6 and 7, depending on the current loop configuration being used. Leave jumper open for separate (double) loop and series (single) loop with internal current source configurations. Connect a jumper between jumper pins 6 and 7 for series (single) loop with external current source configurations.

Jumper connections for ports 1, 2, and 3 are the same as for port 0 except for jumper pin numbers. Table 2-9 shows the correspondence between port 0 jumpers and the jumpers for port 1, 2, and 3. The on-board (internal)  $\pm 12 \text{V}$  supply will provide 20mA (minimum) to a single or double current-loop with one receiver and one transmitter in the external loop. External voltage sources are recommended for single loops with more than one external element in each loop, or for double loops with more than two external element.

TABLE 2-9. CURRENT LOOP JUMPERS

| PORT | VOLTAGE        | SOURCE         | INTERNAL<br>CURRENT | SINGLE LOOP<br>WITH EXTERNAL |

|------|----------------|----------------|---------------------|------------------------------|

| PURI | INTERNAL       | EXTERNAL       | SOURCE              | CURRENT SOURCE               |

| 0    | 13-14<br>11-12 | 13-17<br>8-12  | 9-10<br>15-16       | 6- 7                         |

| 1    | 25-26<br>23-24 | 25-27<br>20-24 | 21-22<br>28-29      | 18-19                        |

| 2    | 38-39<br>33-37 | 40-39<br>32-37 | 34-35<br>36-41      | 30-31                        |

| 3    | 50-51<br>49-45 | 51-52<br>44-45 | 46-47<br>48-53      | 42-43                        |

#### 2-14. PARALLEL INTERFACE CONFIGURATION

An 8255A controls the parallel interface. The parallel interface can be configured as 24 TTL compatible inputs or outputs; Or, it can be configured as 16 RS232C buffered inputs and 8 RS232C buffered outputs. The RS232C buffered lines are compatible with a Bell 801C Automatic Calling Unit. As shipped, the Am95/3310 is configured to support The Bell 801C Automatic Calling Unit.

#### 2-15. TTL BUFFERED I/O

The Am95/3310 is shipped with the parallel port lines configured to support RS232C receiver/drivers. To configure the parallel port lines for TTL receiver/drivers, remove the headers from locations U44, U45, and U51; install the headers in locations U33, U34, and U60. In addition, sockets are provided for driver/receivers for ports PA, PB, and PC. The sockets for ports PA and PB (U23 and U22, respectively) must be loaded with user-supplied 8304 non-inverting 8-bit bidirectional data buffers or 8303B inverting buffers. Port PC (sockets V43 and V32) must be loaded with one of the various 4-bit driver/terminators shown in Table 2-10. As shipped, Ports PA and PB are jumpered for input by the jumpers between 92 and 93 on U23 and between 88 and 89 on U22; PA and PB can be used as outputs when these jumpers are removed. When jumpers are installed between 93 and 94 on U23 and between 89 and 90 on U22, port PC bits PC5 and PC6 control the direction of bidirectional transfers.

#### 2-16. RS232C BUFFERED I/O

The Am95/3310 is shipped from the factory configured with RS232C driver/receivers for the parallel port lines. To support the Bell 801CAutomatic Calling Unit. When the board configuration has been modified and RS232C support is desired, remove the headers from locations U33, U34, and U60. Reinstall the headers in locations U44, U45, and U51. Port B lines PBO through PB4 support PND (Present Next Digit), ACR (Abandon Call; Retry), DLO (Data Line Occupied), DDS (Data Set Status), and PWI (Power Indication) signals from the ACU. Carrier Detect Interrupts (CDINTO though CDINT3) and Ring Indicators (RIO through RI3) are supported with port PA. Port PC bits PCO through PC5 support the ACU number bit lines (NB1, NB2, NB4, and NB8), DPR, and CRQ signals. In addition, three bits of PB can be connected to any of the Secondary Receive Data (SRxDO through SRxD3) from the serial ports, or to auxiliary inputs (AUX1 through AUX3) using jumpers 67 through 73, 75, 78, and 86. Table 2-11 lists jumper connections when configuring PB for RS232C input. Port PC bits PC6 and PC7 can be connected to any of the Secondary Transmit Data lines (STxD0 through STxD3) of the serial ports with jumpers listed in table 2-12.

TABLE 2-10. PARALLEL I/O SOCKET DEVICES

| 7438 7437 7432 7426 7409 7408 7400 iSBC-901 BLC-901 iSBC-902 | CHARACTERISTIC  Driver,I,OC,48mA Driver,I,48mA Driver,NI,16mA Driver,NI,OC,16mA Driver,NI,OC,16mA Driver,NI,16mA Driver,I,0C,16mA Driver,I,16mA Terminator,220/330,Intel Terminator,220/330,National Pull-up,1K,Intel |  |  |  |

|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1SBC-902<br>BLC-902                                          | Pull-up,1K,Intel Pull-up,1K,National  NOTE: I=inverting NI=non-inverting OC=open collector                                                                                                                            |  |  |  |

TABLE 2-11. PARALLEL INPUT PORT

|        | SOURCE |        | DESTI  | NATION |

|--------|--------|--------|--------|--------|

| SIGNAL | FROM   | JUMPER | JUMPER | T0     |

| SRxD0  | P3- 6  | 67     | 71     | U44-11 |

| SRxD1  | P4- 6  | 69     | 75     | U44-10 |

| SRxD2  | P5- 6  | 68     | 72     | U44- 9 |

| SRxD3  | P6- 6  | 70     |        |        |

| AUX1   | P7-24  | 78     |        |        |

| AUX2   | P7-22  | 86     |        |        |

| AUX3   | P7-15  | 73     |        |        |

TABLE 2-12. PARALLEL OUTPUT PORT

| FROM   | VIA<br>JUMPER | то | SIGNAL<br>NAME | CONNECTOR     |

|--------|---------------|----|----------------|---------------|

| U62- 8 | 84            | 81 | STxD0          | P3- 2         |

| U62-11 | 85            | 83 | STxD1          | P <b>4-</b> 2 |

|        |               | 79 | STxD2          | P5- 2         |

|        |               | 80 | STxD3          | P6- 2         |

|        |               | 74 | AUX4           | P7-21         |

|        |               | 82 | AUX5           | P7-23         |

# CHAPTER 3 OPERATION AND PROGRAMMING

#### 3-1. INTRODUCTION

The Am95/3310 Communication Controller includes nine programmable device as follows:

- Four Am9551 Universal Synchronous/Asynchronous Receiver/ Transmitter \*USART) chips that control the four serial I/O ports.

- Two 8259A Programmable Interrupt Controller chips (PIC) that control the interrupt functions.

- One Am8255A Programmable Peripheral Interface chip (PPI) that controls the parallel I/O ports.

- Two Am8253 Programmable Interval Timer chips (PIT) that control frequency and timing functions.

#### 3-2. I/O BASE ADDRESS ASSIGNMENT

A CPU communicates with the Am95/3310 through a sequence of I/O Read and I/O Write commands. The I/O addresses used for these commands are relative to an I/O base address that is a multiple of 32. The only consideration to be taken in assigning the I/O address base is to ensure that no two boards in the system share the same block of I/O addresses. The block of 24 I/O addresses is jumper-selectable to begin on any 32-byte I/O address boundary (i.e. 0000H, 0020H, 0040H, etc.) The I/O address base is assigned at the factory as 80H through 97H.

#### 3-3. ADDRESS ASSIGNMENTS

The Am95/3310 is mapped into the CPU address space as 24 I/O addresses shown in table 3-1. The first 8 addresses (80H through 87H) are assigned to the four serial I/O ports 0 through 3. The next four addresses (88H through 8BH) in the sequence are assigned to the interrupt controllers. The parallel ports A, B, and C are assigned addresses 8CH through 8FH. The last 8 addresses (90H through 97H) are assigned to the two programmable interval timers.

TABLE 3-1. I/O ADDRESS ASSIGNMENTS

| EDGE CONNECTOR | DEVICE (PORT)                                                      | FUNCTION                                           | I/O ADDRESS                            |

|----------------|--------------------------------------------------------------------|----------------------------------------------------|----------------------------------------|

| Р3             | USART O, PORT O                                                    | Data                                               | 80H*                                   |

|                | (CSUSARTO*)                                                        | Control                                            | 81H                                    |

| P4             | USART 1, PORT 1                                                    | Data                                               | 82H                                    |

|                | (CSUSART1*)                                                        | Control                                            | 83H                                    |

| P5             | USART 2, PORT 2                                                    | Data                                               | 84H                                    |

|                | (CSUSART2*)                                                        | Control                                            | 85H                                    |

| P6             | USART 3, PORT 3                                                    | Data                                               | 86H                                    |

|                | (CSUSART3*)                                                        | Control                                            | 87H                                    |

|                | PIC 0                                                              | Command                                            | 88H                                    |

|                | (CSUICO*)                                                          | Data                                               | 89H                                    |

| J1/P7          | PIC 1<br>(CSUIC1*)<br>(PORT A)<br>PPI (PORT B)<br>(CSPPI*)(PORT C) | Command<br>Data<br>Data<br>Data<br>Data<br>Control | 8AH<br>8BH<br>8CH<br>8DH<br>8EH<br>8FH |

|                | PIT 0                                                              | BRCLK 0                                            | 90Н                                    |

|                | (CSPITO*)                                                          | BRCLK 1                                            | 91Н                                    |

|                | PIT 1<br>(CSPIT1*)                                                 | BRCLK 2<br>Control<br>BRCLK 3<br>TIM 0             | 92H<br>93H<br>9 <b>4</b> H<br>95H      |

|                |                                                                    | TIM 1<br>Control                                   | 96н<br>97н                             |

<sup>\*</sup> As shipped BASE ADDRESS = 80H

### 3-4. Am95/3310 INITIALIZATION

After the Am95/3310 has been installed, use the following steps to initialize the board:

- a. Disable system interrupts. For systems based on Am8080/Am8085 microprocessors, use DI instruction.

- b. Initialize 8259A chip.

- c. Select baud rate for the four serial I/O ports.

- d. Initialize 8253A chips.

- e. Initialize USARTs 0 through 3 for serial I/O ports 0 through 3, respectively.

- f. Initialize 8259A chips. Set up mode and interrupt mask bits as appropriate.

- g. Enable system interrupts. For systems based on Am8080 and Am8085 microprocessors, use EI instruction.

If appropriate subroutines have been written, the initialization procedure consists simply of calling subroutines.

### 3-5. SERIAL I/O INTERFACE PROGRAMMING

Each of the four serial I/O ports is controlled by an Am9551 USART. The USART converts parallel data to serial data format for half or full-duplex operation. The USART also converts serial input data to parallel data format. Operating modes are selected by a mode instruction and a command instruction word. When reset is activated, it forces the Am9551 into an idle mode in which data is neither transmitted nor received. Following reset, a new set of mode and command words must be output by the CPU to the USARTs before operations can resume. The USARTs should be reset after power is first applied.

#### 3-6. Am9551 ADDRESSING

Each Am9551 uses two consecutive addresses. The lower address is used to read or write data; the upper address is used to write mode and command words and to read the USART status. Refer to table 3-1.

#### 3-7. Am9551 INITIALIZATION

Each Am9551 is initialized as follows:

- a. Reset the USART to Mode instruction format by writing a command word with bit 6 (IR) set address 81H, 83H, 85H, or 87H.

- b. Write a Mode Control Word to address 81H, 83H, 85H, or 87H.

NOTE

After initialization, always check the status of the TxRDY bit prior to writing data or a new command word to the Am9551. The TxRDY bit must be true to prevent overwriting and subsequent loss of commands or data. The TxRDY is inactive until initialization has been completed.

Once initialized, it is not necessary for a command instruction to precede all data transactions--only those transmissions that require a change in the command instruction.

To change the Mode Control Word, the USART must receive a Reset Command. The next word written to the USART after a Reset Command is assumed to be a Mode Control Word. Similarly, for sync mode, the next word after a Mode Control Word is assumed to be one or two sync characters. All controls words written into the USARTs after Mode Control Word, are assumed to be command instructions. An individual USART can be reset by bit 6 in the Command Instruction Word, all four can be reset by a system reset.

#### 3-8. MODE INSTRUCTION WORD

The Mode Instruction Word defines the general characteristics of the USART and must follow a reset operation. Once the Mode Instruction Word has been written, Sync Characters or Command Instruction Words may be inserted. The Mode Instruction Word defines the following:

- Synchronous Mode

- Character length

- Parity enable

- Even/odd parity generation and check

- External sync detect (not supported by 95/3310)

- Single or double character sync

#### Asynchronous Mode

- Baud rate (multiplier x1, x16, x64)

- Character length

- Parity enable

- Even/odd parity generation and check

- Number of stop bits

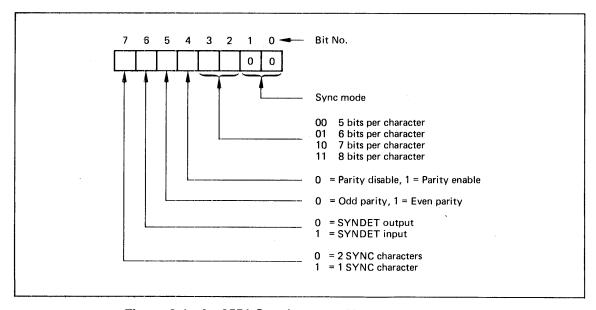

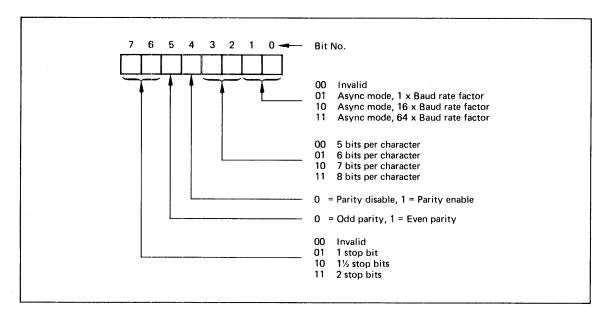

The mode instruction word formats for synchronous and asynchronous mode are shown in figures 3-1 and 3-2 respectively.

Figure 3-1. Am9551 Synchronous Mode Control Code

Figure 3-2. Am9551 Asynchronous Mode Control Code

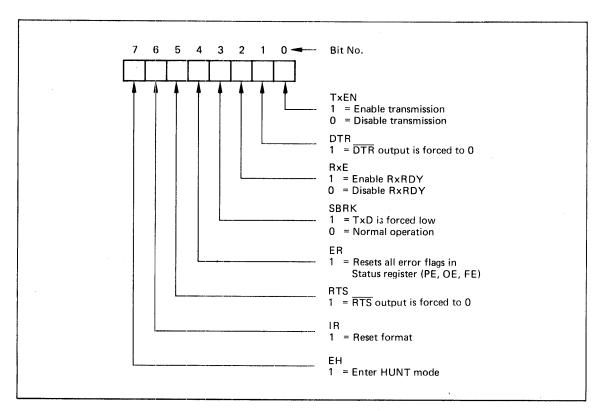

#### 3-9. COMMAND INSTRUCTION WORD FORMAT

The Command Instruction Word shown in figure 3-3 controls the operation of the addressed USART. A Command Instruction Word must follow the mode and/or sync words. Once the Command Instruction Word is written, data can be transmitted or received by USART. It is not necessary for a Command Instruction Word to precede all data transactions; only those transmissions that require a change in the Command Instruction Word.

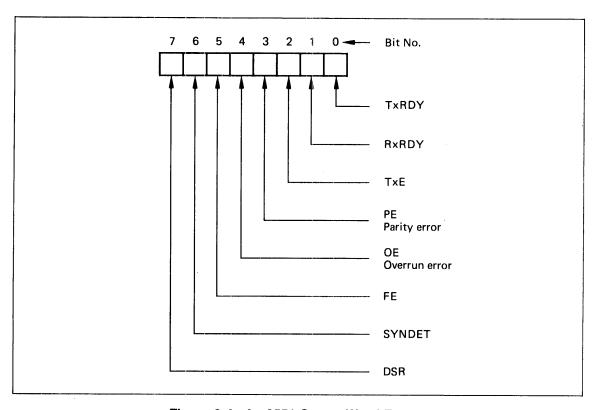

#### 3-10. Am9551 STATUS READ

The CPU can determine the status of a USART by issuing an I/O Read Command to address 81H, 83H, 85H, or 87H. The format of the status byte is shown in figure 3-4.

The definition of the status bits is as follows:

| TxRDY | Transmitter  | Ready   | indicat  | tes the | Am9551 | is | ready | to |

|-------|--------------|---------|----------|---------|--------|----|-------|----|

|       | accept a dat | a chara | acter or | command | •      |    |       |    |

- RxRDY Receiver Ready indicates the Am9551 has received a character on its serial input and is ready to transfer it to the CPU.

- TxE Transmitter Empty signals the processor that the transmit register is empty. TxE is not supported by the 95/3310.

- PE Parity Error indicates the character stored in the receive character buffer was received with an incorrect number of binary 1 bits.

- OE Overrun flag is set when a byte stored in the receiver character register is over written with a new byte before being transferred to the processor.

- FE Framing Error indicates the asynchronous mode byte stored in the receiver character buffer was received with incorrect character bit format.

- SYNDET When Sync Detect is set for internal sync detect, this bit indicates character sync has been achieved and the Am9551 is ready for data. SYNDET is not supported by the 95/3310.

- DSR Data Set Ready is set by the external Data Set Ready Signal to indicate the communications data set is ready.

Figure 3-3. Am9551 Command Instruction Word Format

Figure 3-4. Am9551 Status Word Format

# 3-11. Am9551 DATA INPUT/OUTPUT

A data receive or transmit operations requires a read or write, to the desired USART.

During normal transmit operation, each USART generates a Transmit Ready (TxRDY) signal that indicates that the USART is ready to accept a data character for transmission. TxRDY is automatically reset when a character is loaded into the USART.

Similarly, during normal receive operation, each USART generates a Receive Ready (RxRDY) signal that indicates that a character has been received. RxRDY is automatically reset when a character is read.

The TxRDY and RxRDY outputs of each USART chip are connected to a Programmable Interrupt Controller chip (PIC 0), which resolves priority in case of simultaneous inputs and generates an interrupt for the multibus.

## 3-12. PARALLEL I/O INTERFACE PROGRAMMING

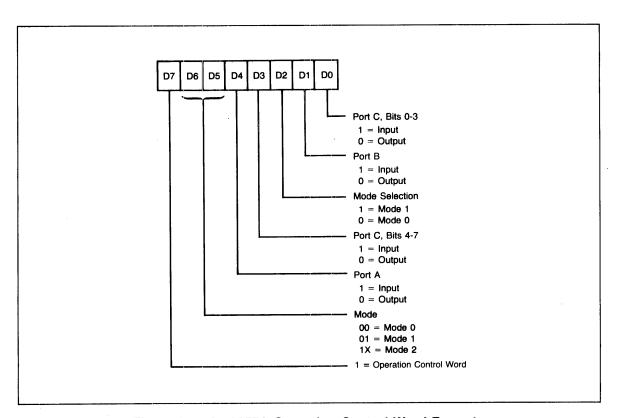

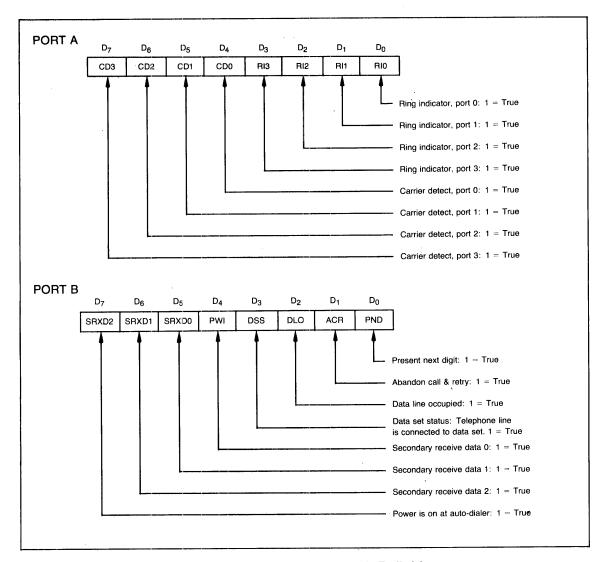

The PPI provides three 8-bit ports (A, B, and C). Each port can be configured as either input or output, and port C is used to control ports A and B in some modes. The operating modes of the ports are controlled by outputting either an operation control word or a bit set/reset control word. Signals interfaced to the PPI are listed in table 3-2.

Parallel I/O ports B and C can be configured to interface directly with a Bell 801 Automatic Calling Unit (ACU).

# 3-13. Am8255A INITIALIZATION

The PPI chip is initialized by writing 92H to 8FH. Notice in figure 3-5 that this initializes PPI as follows:

- Operation Control Word Active

- Mode 0 Selected

- Port A Input

- Port B Input

- Port C Output

TABLE 3-2. PPI INTERFACE SIGNALS (FACTORY CONFIGURATION)

|                                      | PORT B INPUTS                                                    | POI                                  | RT A INPUTS                                                                                             | PORT C OUTPUTS                       |                                                               |  |

|--------------------------------------|------------------------------------------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------|---------------------------------------------------------------|--|

| BIT                                  | SIGNAL                                                           | BIT                                  | SIGNAL                                                                                                  | BIT                                  | SIGNAL                                                        |  |

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | PND ACR DLO DSS PWI SRxDO, SRxD1 SRxD2, SRxD3 AUX1,AUX2, or AUX3 | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | RIO (PORT 0) RI1 (PORT 1) RI2 (PORT 2) RI3 (PORT 3) CDO (PORT 0) CD1 (PORT 1) CD2 (PORT 2) CD3 (PORT 3) | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | NB1 NB2 NB4 NB8 DPR CRQ STxD0,STxD1 STxD2,STxD3 AUX4, or AUX5 |  |

# NOTES:

- PND, R1, and CD signals are connected to the interrupt controllers.

- RI AND CD are from serial I/O ports, which do not support these signals.

- Multiple inputs (e.g. bits 5-7 of port B) are jumper wired (See tables 2-11 and 2-12).

Figure 3-5. Am8255A Operation Control Word Format

# 3-14. Am8255A ADDRESSING

The PPI uses four consecutive I/O addresses (8CH through 8FH) for transferring data, obtaining Port C status and for device control. Refer to table 3-1 for port addresses and functions.

# 3-15. Am8255A CONTROL WORD FORMAT

The control word shown in figure 3-5 defines the three operating modes of the ports; Modes 0, which is basic input/output; Mode 1, strobed input/output; and Mode 3, bidirectional bus. The modes for Ports A and B can be separately defined, while port C is divided into two 4-bit ports.

# 3-16. Am8255A PORT A AND B DATA

Data from Ports A and B are obtained by performing a I/O read of 8CH and 8DH, respectively. Bit definitions for Ports A and B (if Auto Call option is used) are given in Figure 3-6. If Auto Call option is not being used these bits come from parallel port connector J1.

# 3-17. Am8255A PORT C DATA

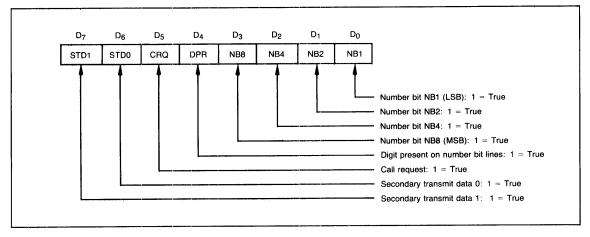

Data is written to Port C or a call is placed with the ACU by performing a write to 8EH. Bit definitions for Port C (if Auto Call option is used) are given in figure 3-7. If Auto Call option is not being used these bits come from the parallel port connector J1.

# 3-18. PROGRAMMABLE INTERVAL TIMER PROGRAMMING

The timing functions on-board are provided by two 8253 Programmable Interval Timers (PITs) driven by a 1.2288 MHz clock signal. Each PIT has three independent 16-bit interval timers. Four of the timers, PITO output 0 through 2 and PIT 1, output 0, are connected to the four USARTs transmit and receive clocks BRCLKO through BRCLK3. The remaining two (PIT1 outputs 1 and 2) can be programmed to generate separate clock signals or real-time interrupt intervals.

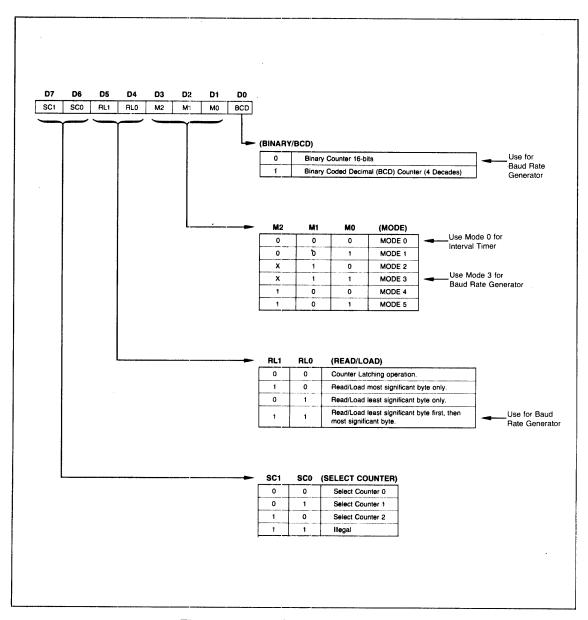

A set of control words must be sent by the CPU to initialize each PIT counter with the desired mode. The control words program the mode, loading sequence and selection of binary or BCD counting. Refer to figure 3-8 for PIT control word format.

Figure 3-6. PPI Port A and B Bit Definitions

Figure 3-7. PPI Port C Bit Definitions If Auto Call Option is Used

Figure 3-8. PIT Control Word Format

# 3-19. Am8253 INITIALIZATION

To initialize the Programmable interval timer for baud rate generation, perform the following:

a. Write mode control word for PIT 0 Counter 0 to 93H.

#### NOTE

All mode control words for PIT 0 are written to 93H, since the mode control word must specify which counter is being programmed. Refer to figure 3-8.

- b. Assuming mode control word has selected a 2-byte load, load least-significant byte of count into Counter 0 at 90H.

- c. Load most-significant byte of count into Counter 0 at 90H.

## NOTE

Be sure to enter the down-count in two bytes if the counter was programmed for a two-byte entry in the mode control word. Similarly, enter the down-count value in BCD if the counter was so programmed.

d. Repeat steps a, b, and c for PIT 0 Counters 1 and 2 and for PIT 1 Counter 0. Refer to table 3-1 for control addresses.

## 3-20. Am8253 OPERATION

The following paragraphs describe operating procedures for a counter read, clock frequency divide/ratio selection, and interrupt timer counter selection.

# 3-21. Am8253 Counter Read

For Mode 3 operation, there usually is no requirement to reset or read the counters; however, it is possible to do so at any time. If a count register is reloaded during counting in Mode 3, the new value is reflected immediately following the output transition of the current count. For Mode 0 (interrupt on terminal count), reloading during counting has the following results:

- a. Loading first byte stops current count.

- b. Loading second byte starts new count.

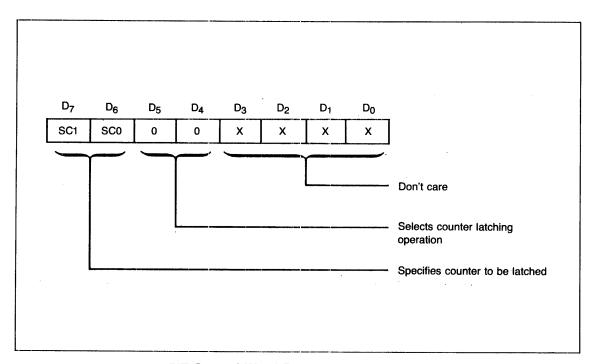

If desired, it is possible to read the count register during the down count. The recommended procedure is to write a mode control word (shown in figure 3-9) to latch the contents of the count register, this ensures that the count reading is accurate and stable. The latched value of the count can then be read.

#### NOTE

Be sure to read one or two bytes, whichever was specified in the initialization mode control word. For two bytes, read in the order specified.

Figure 3-9. PIT Control Word Format for Counter Register Latch

# 3-22. Am8253 Clock Frequency/Divide Ratio Selection

All of the modes for each counter are programmed by the system software using I/O operation. Each counter must be programmed with a down-count number, or count value N. When count value N is loaded into a PIT counter, it becomes the clock divisor. To derive N for either synchronous or asynchronous operation, use the procedures described in the following paragraphs.

3-23. Synchronous Mode - In the synchronous mode, the TxC and/or RxC rates equal the Baud rate. Therefore, the count value is determined by:

N = C/B

Where: N is the count value.

B is the desired Baud rate, and

C is 1.2288 MHz, the input clock frequency.

3-24. Asynchronous Mode - In the asynchronous mode, the TxC and/or RxC rates equal the Baud rate times of the following multipliers: X1, X16, or X64. Therefore, the count value is determined by:

N = C/BM

where: N is the count value,

B is the desired Baud rate,