# American National Standard

- for information systems -

- intelligent peripheral interface physical level

american national standards institute, inc. 1430 broadway, new york, new york 10018

# American National Standard for Information Systems -

# Intelligent Peripheral Interface – Physical Level

Secretariat

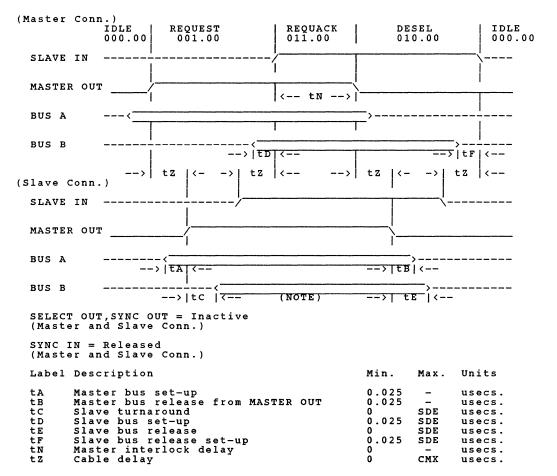

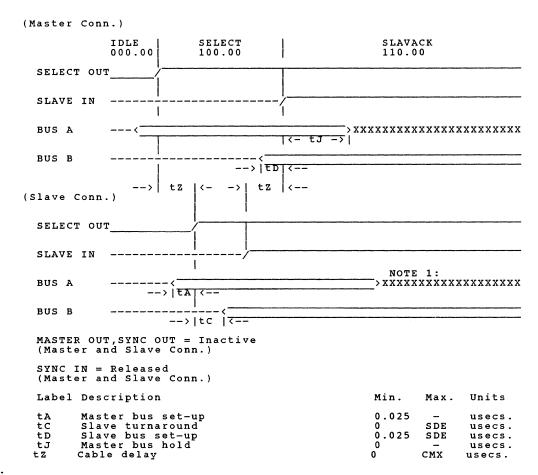

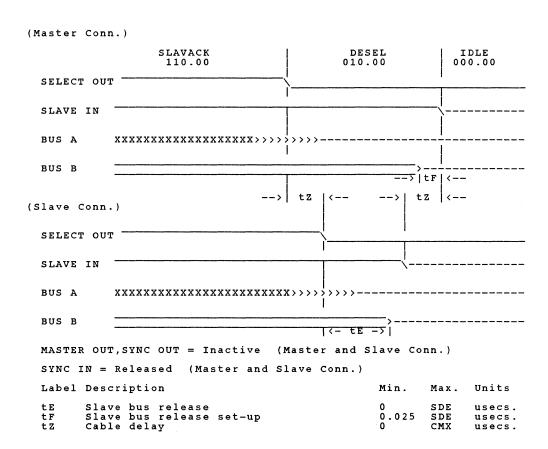

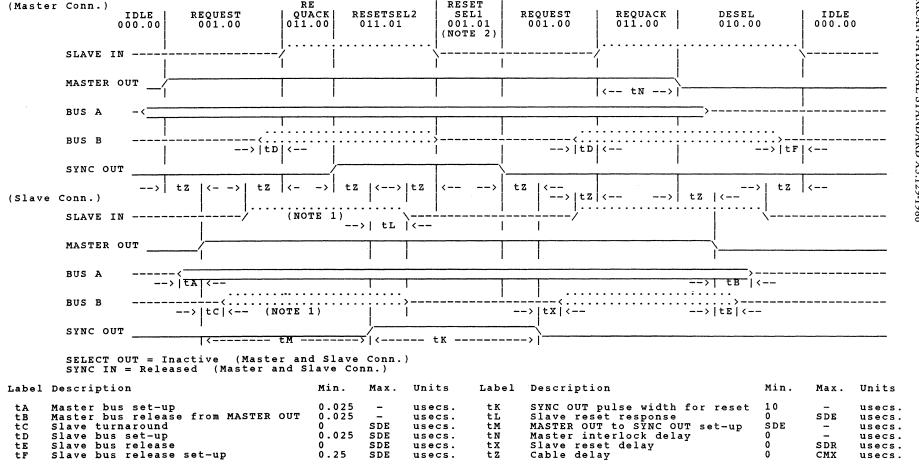

Computer and Business Equipment Manufacturers Association

Approved April 24, 1986

American National Standards Institute, Inc

### American National Standard

Approval of an American National Standard requires verification by ANSI that the requirements for due process, consensus, and other criteria for approval have been met by the standards developer.

Consensus is established when, in the judgment of the ANSI Board of Standards Review, substantial agreement has been reached by directly and materially affected interests. Substantial agreement means much more than a simple majority, but not necessarily unanimity. Consensus requires that all views and objections be considered, and that a concerted effort be made toward their resolution.

The use of American National Standards is completely voluntary; their existence does not in any respect preclude anyone, whether he has approved the standards or not, from manufacturing, marketing, purchasing, or using products, processes, or procedures not conforming to the standards.

The American National Standards Institute does not develop standards and will in no circumstances give an interpretation of any American National Standard. Moreover, no person shall have the right or authority to issue an interpretation of an American National Standard in the name of the American National Standards Institute. Requests for interpretations should be addressed to the secretariat or sponsor whose name appears on the title page of this standard.

CAUTION NOTICE: This American National Standard may be revised or withdrawn at any time. The procedures of the American National Standards Institute require that action be taken to reaffirm, revise, or withdraw this standard no later than five years from the date of approval. Purchasers of American National Standards may receive current information on all standards by calling or writing the American National Standards Institute.

Published by

American National Standards Institute 1430 Broadway, New York, New York 10018

Copyright © 1986 by American National Standards Institute, Inc All rights reserved.

No part of this publication may be reproduced in any form, in an electronic retrieval system or otherwise, without the prior written permission of the publisher.

Printed in the United States of America

PC2M886/20

### Foreword

(This Foreword is not part of American National Standard X3.129-1986.)

This standard is a definition of the physical portion of a family of standards called the Intelligent Peripheral Interface (IPI). It is a new high-performance, general-purpose parallel peripheral interface. This standard responds to an industry market need (expressed both by users and manufacturers) to limit the increasing costs in hosts associated with changes in peripherals. The intent of the IPI is to isolate the host (CPU), both hardware and software, from changes in peripherals by providing a "function-generic" command set to allow the connection of multiple types of peripherals (disks, printers, tapes, communications). To smooth the transition from the current methods to the generic approach, the IPI also supports device-specific command sets to aid in bridging the gap between the two approaches.

To accomplish this set of goals, the design of the IPI includes device-specific and device-generic command sets, both utilizing a common physical bus. The device-specific command set provides:

- (1) Device-oriented control

- (2) Physical Data Addressing

- (3) Timing Critical Operations

- (4) Lower Device Cost

The device-generic command set provides a higher level of functionality and portability. It includes:

- (1) Host/Device Independence

- (2) Logical Data Addressing

- (3) Timing Independence

- (4) Command Queuing Capability

A system is not restricted to the use of one level of command set or the other. It is possible that both levels of command sets will be utilized with a given system's architecture to balance such parameters as system performance, cost, and peripheral availability. It is also possible for the host to provide for migration from device-specific to device-generic levels while still retaining the same physical interface.

The development of an Intelligent Peripheral Interface (IPI) was begun after a preliminary investigation had been completed. The earliest proposals were made by participants of Task Group X3T9.3 in late 1978. At that time, the Task Group decided generic-oriented peripheral interfaces were not yet ready for standardization and that the group should concentrate on device-oriented interfaces and the system-oriented, high-speed serial interfaces. The group acknowledged the desirability of higher level intelligent commands by reserving code fields in American National Standard for Interface between Rigid Disk Drives and Their Host(s), ANSI X3.101-1983, during its April 1980 meeting.

The basic architecture of the resultant IPI was first proposed at the X3T9.3 August 1980 meeting. In addition to the 1978 proposal, complete company implementations were proposed by several manufacturers from August 1980 to August 1981. These proposals resulted from the initiative of the contributors and from wide-spread solicitation by the task group.

X3T9.3 agreed upon preliminary functional requirements during the October 1980 meeting, which included the following:

- (1) Parallel transfer

- (2) Command and Data Handshaking

- (3) Allowance for high-speed transfers without Handshaking

- (4) Minimum transfer rate to 5 Megaoctets per second

X3T9.3 began work on the IPI in 1981 in response to an emerging need for a higher performance peripheral interface. Coincidental with the need for higher performance was the availability of low-cost VLSI circuit technologies, allowing increased intelligence in the peripheral device. These needs were confirmed by large and active participation from all areas of the computer industry.

The fundamental characteristics that the group achieved included the following:

- (1) Single or dual octet transfers

- (2) Data rates of at least 10 megabytes per second

- (3) Cable lengths extending from 5 to 125 meters depending upon type of transmitter and cable type

- (4) Low-cost, commonly available components

- (5) High level of maintainability and availability

- (6) A multilevel command structure allowing different levels of intelligence in the peripherals

- (7) A definition that facilitates evolutionary changes in the levels with minimal impact on software and hardware components

- (8) Definitions supporting an extensive group of peripheral devices including disks, tape, communications equipment, printers, and the like, with a common choice of interface hardware and commands

Suggestions for improvement of this standard will be welcome. They should be sent to the Computer and Business Equipment Manufacturers Association, 311 First Street, NW, Suite 500, Washington, D.C. 20001.

This standard was processed and approved for submittal to ANSI by Accredited Standards Committee on Information Processing Systems, X3. Committee approval of the standard does not imply that all committee members voted for approval. At the time it approved this standard, the X3 Committee had the following members:

Edward Lohse, Chair Richard Gibson, Vice-Chair Catherine A. Kachurik, Administrative Secretary

Organization Represented

American Express

American Library Association American Nuclear Society

AMP Incorporated

Association for Computing Machinery

Association of the Institute for Certification of Computer Professionals AT&T Communications

AT&T Information Systems

Burroughs Corporation Control Data Corporation Name of Representative

D. L. Seigal Lucille Durfee (Alt) Paul Peters Geraldine C. Main D. R. Vondy (Alt) Patrick E. Lannan Edward Kelly (Alt) Kenneth Magel Jon A. Meads (Alt)

Thomas M. Kurihara Henry L. Marchese Richard Gibson (Alt) Herbert V. Bertine Paul D. Bartoli (Alt) Stanley Fenner Charles E. Cooper Keith Lucke (Alt) Organization Represented

Cooperating Users of Burroughs Equipment

**Data General Corporation**

Data Processing Management Association Digital Equipment Computer Users Society

Digital Equipment Corporation

Eastman Kodak

General Electric Company

General Services Administration

**GUIDE** International

Harris Corporation

Hewlett-Packard Honeywell Information Systems

**IBM** Corporation

**IEEE Computer Society**

Lawrence Berkeley Laboratory

Moore Business Forms National Bureau of Standards

National Communications System

NCR Corporation

Prime Computer, Inc

Railine Corporation Recognition Technology Users Association

Scientific Computer Systems

SHARE, Inc

Sperry Corporation

Texas Instruments, Inc

3M Company

Travelers Insurance Companies, Inc U.S. Department of Defense

VIM

VISA International

Wang Laboratories, Inc

Xerox Corporation

Name of Representative

Thomas Easterday Donald Miller (Alt) John Pilat Lyman Chapin (Alt) Christian G. Meyer William Hancock Charles Mustain (Alt) Gary S. Robinson

Delbert L. Shoemaker (Alt) Charleton C. Bard Gary Haines (Alt) William R. Kruesi Richard W. Signor (Alt) William C. Rinehuls Larry L. Jackson (Alt) Frank Kirshenbaum Thomas F. O'Leary, Jr (Alt) Walter G. Fredrickson Rajiv Sinha (Alt) Donald C. Loughry Thomas J. McNamara David M. Taylor (Alt) Mary Anne Gray Robert H. Follett (Alt) Sava I. Sherr Thomas M. Kurihara (Alt)

Thomas A. Varetoni (Alt)

David F. Stevens

John S. Colonias (Alt) Delmer H. Oddy Robert E. Rountree James Moulton (Alt) Marshall L. Cain George W. White (Alt) Thomas W. Kern A. Raymond Daniels (Alt) Joseph Schmidt John McHugh (Alt) R. A. Petrash Herbert F. Schantz G. W. Wetzel (Alt) James A Baker Carl Haberland (Alt) Thomas B. Steel Robert A. Rannie (Alt) Marvin W. Bass Jean G. Smith (Alt) Presley Smith Richard F. Trow, Jr (Alt) J. Wade Van Valkenburg R. C. Smith (Alt) Joseph T. Brophy Fred Virtue Belkis Leong-Hong (Alt) Chris Tanner Madeline Sparks (Alt) Jean T. McKenna Susan Crawford (Alt) Marsha Hayek Joseph St. Armand (Alt) John L. Wheeler

Subcommittee X3T9 on I/O interfaces, which reviewed this standard, had the following members:

Delbert L. Shoemaker, Chairman William E. Burr, Vice-Chairman

James R. Barnette

Steve Cooper

Duane Barney

Louis C. Domshy

Robert Dugan

Patrick Lannan

John B. Lohmeyer

John McCool

Gene Milligan

Ted Petrowich

Reinhard Knerr

Gary S. Robinson

Arnold J. Roccati

Floyd E. Ross

Mark Hammang (Alt)

Kris Kowal (Alt)

George Clark (Alt)

Roger Cormier (Alt)

Charles Brill (Alt)

Sunil Joshi (Alt)

Dennis Krob (Alt)

Robert B. Anthony (Alt)

Kirk Moulton (Alt)

Dennis Appelyard

Task Group X3T9.3 on Device Level Interfaces, which was responsible for the development of this standard, had the following participants:

Gary S. Robinson, Chair I. Dal Allan, Vice-Chair

|                                  | •              |              |                                  |

|----------------------------------|----------------|--------------|----------------------------------|

| J. Amstutz                       | S. Finch       | D. Mc Intyre | D. Roberts                       |

| <ul> <li>D. Appleyard</li> </ul> | R. Fish        | P. Mclean    | <ul> <li>A. Roccati</li> </ul>   |

| R. Barnes                        | M. Fitzpatrick | F. Meadows   | F. Ross                          |

| D. Barney                        | M. Gamerl      | J. Meyer     | L. Russell                       |

| R. Bender                        | R. Geller      | G. Milligan  | <ul> <li>A. Salthouse</li> </ul> |

| R. Bergey                        | S. Gersten     | P. Mizera    | W. Sanderson                     |

| F. Berkowitz                     | M. Glier       | D. Moczarny  | E. Sandoval                      |

| B. Bonner                        | W. Grace       | K. Moe       | K. Scharf                        |

| M. Bradac                        | B. Graham      | J. Monaco    | D. Schneider                     |

| C. Brill                         | E. Grivna      | R. Morris    | J. Schuessler                    |

| B. Brown                         | K. Hallam      | J. Mulligan  | R. Schultz                       |

| R. Brown                         | M. Hammang     | R. Notari    | D. Shoemaker                     |

| W. Burr                          | D. Hartig      | T. O'Connor  | E. Slater                        |

| E. Calkins                       | P. Hayden      | M. O'Donnell | J. Smith                         |

| E. Cieniawa                      | C. Hess        | J. Patton    | R. Snively                       |

| S. Cooper                        | C. Jarboe      | R. Peacock   | C. Stead                         |

| R. Davideit                      | S. Juhasz      | J. Peterson  | H. Stehle                        |

| R. Davis                         | K. Kong        | T. Petrowich | M. Stewart                       |

| R. Derr                          | A. Kononov     | P. Phillips  | H. Truestedt                     |

| S. Dick                          | T. Leland      | M. Poehler   | N. Vashi                         |

| R. Dillon                        | J. Lohmeyer    | D. Ray       | D. Voigt                         |

| R. Driscal                       | R. Lopez       | B. Reago     | C. Walker                        |

| T. Eiland                        | R. Matheson    | C. Ridgeway  | O. Weeden                        |

| D. Filpus                        | T. Mc Clendon  | W. Roberts   | D. Williams                      |

| D. Impub                         | 1. Me Cichaon  | W. Roberts   | L. Zorza                         |

|                                  |                |              | L. Zorza                         |

| Contents | SECTION                                                                                                                                                                               | PAGE |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|          | 1. Scope and Purpose.  1.1 Scope 1.2 Purpose 1.3 Description of Sections. 1.4 Editorial Conventions. 1.5 Physical Interface 1.6 Configuration Characteristics 1.7 Signal Nomenclature |      |

|          | 2. Referenced Publications          2.1 American National Standards          2.2 Other Standards                                                                                      |      |

|          | 3. Definitions                                                                                                                                                                        |      |

|          | 4. Physical Characteristics. 4.1 Configuration. 4.2 Connector Specification. 4.3 Cable Characteristics. 4.4 Electrical Characteristics. 4.5 Cable Interconnections.                   |      |

|          | 5. Protocol 5.1 Interface Description 5.2 Usage of Signals 5.3 States 5.4 Sequences 5.5 Bus Octet Definitions 5.6 Maintenance Mode 5.7 Other Maintenance Considerations               |      |

|          | 6. Logical Interface Environment                                                                                                                                                      | 72   |

|          | 7. Timing                                                                                                                                                                             |      |

|          | Tables Table 1 Signal Nomenclature                                                                                                                                                    |      |

|          | Table 11 Facility Address Mapping                                                                                                                                                     | 60   |

| SECTION   | PAGE                                                 |

|-----------|------------------------------------------------------|

| Table 13  | MM Signal Line Assignments                           |

| Table 14  | MM2 Scenario Summary                                 |

|           | Description of MM2 FDSR                              |

|           | Encoded MM2 Orders                                   |

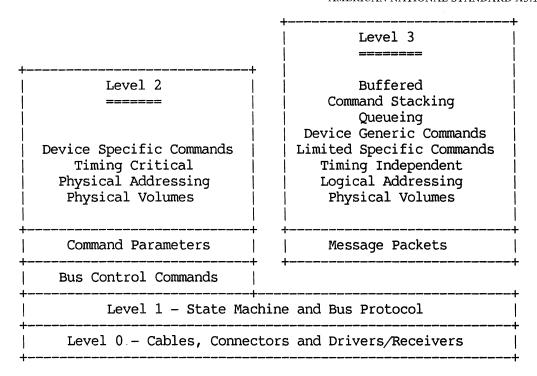

|           | Level Characteristics                                |

|           |                                                      |

| Figures   | M. C. C. C. V. F. I                                  |

| Figure 1  | Mainframe Configuration Example                      |

| Figure 2  | Minicomputer Configuration Example                   |

| Figure 3  | 2 × 25 Pin Header — Plug                             |

| Figure 4  | 2 × 25 Pin Header – Receptacle                       |

| Figure 5  | 50-Position Subminiature "D" Pin/Socket Contact      |

| Figure 6  | 50-Position Subminiature "D" Receptacle/Plug         |

| Figure 7  | 50-Position Subminiature "D" Connector               |

| Figure 8  | 48-Position Shielded Modular Connector — Panel Mount |

| •         | 48-Position Shielded Modular Connector – Cable Mount |

| -         | 48-Position Connector Crimp-Type Contact             |

|           | Configuration for Bidirectional Bus Signals          |

| Figure 12 | Configuration for Unidirectional Single-Ended        |

| F: 12     | Lines from Slave                                     |

| Figure 13 | Configuration for Unidirectional Single-Ended        |

| T: 14     | Lines from Master                                    |

|           | Interface Signal Summary                             |

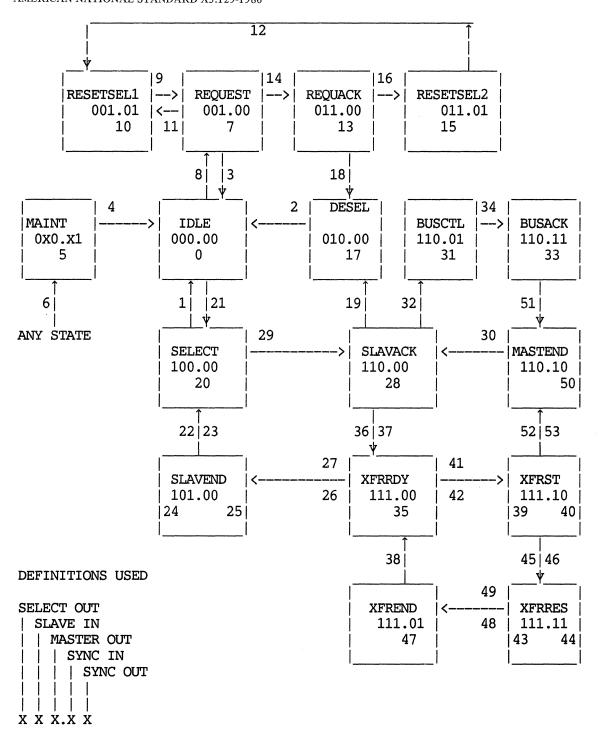

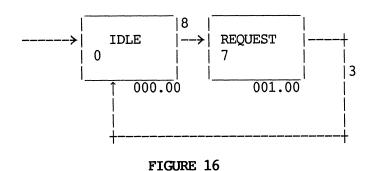

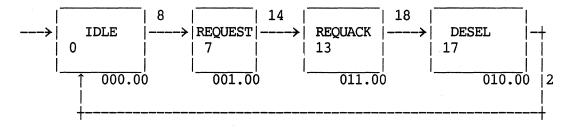

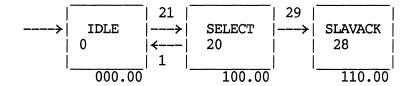

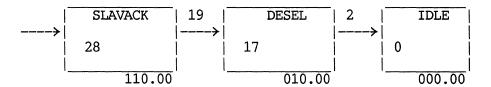

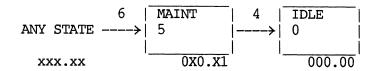

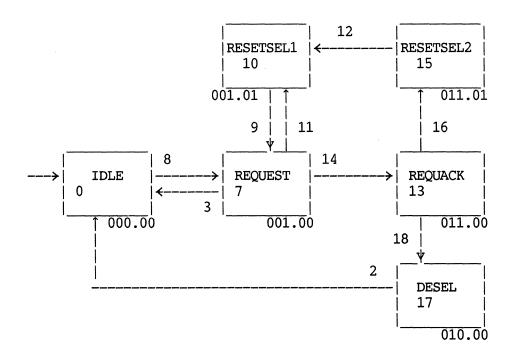

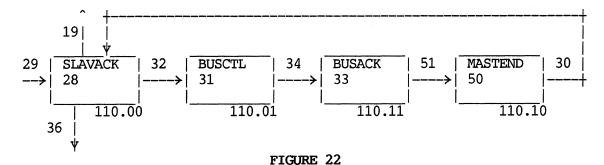

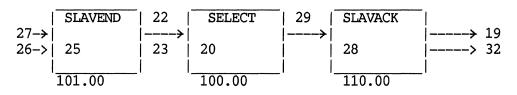

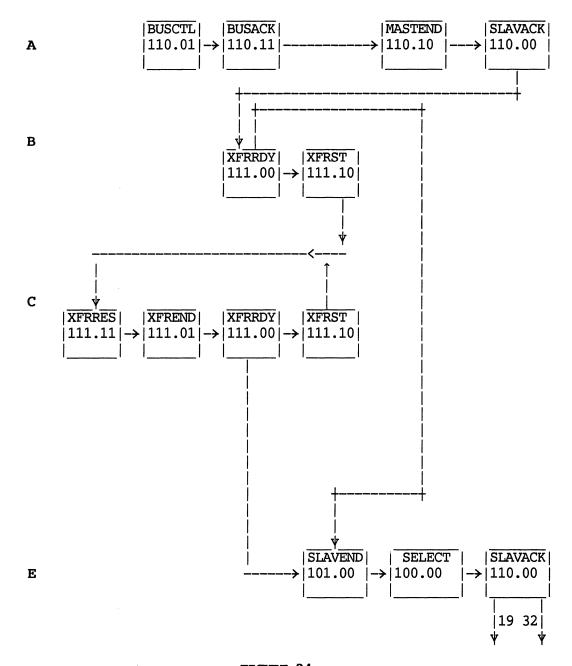

|           | Bus State Diagram                                    |

| -         | Request Interrupts Sequence                          |

| _         | Request Transfer Settings Sequence                   |

|           | Selection Sequence                                   |

|           | Normal Deselection Sequence                          |

|           | Master Reset Sequence                                |

|           | Selective Reset Sequence                             |

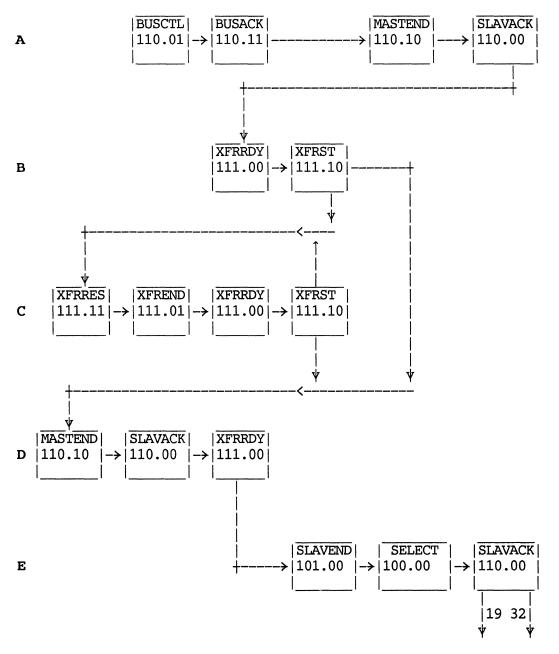

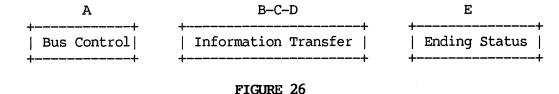

| -         | Bus Control Sequence                                 |

| -         | Ending Status Sequence                               |

|           | Slave-Initiated Ending of Information Transfer       |

|           | Master-Initiated Ending of Information Transfer      |

|           | Information Transfer Sequence                        |

|           | Bus A Selection Octet                                |

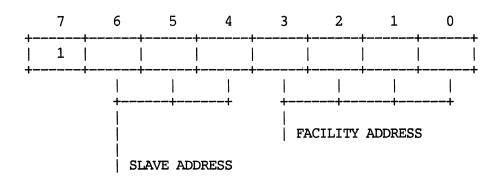

| -         | Bus A Facility Selection Octet                       |

| _         | Bus B Select Status Octet                            |

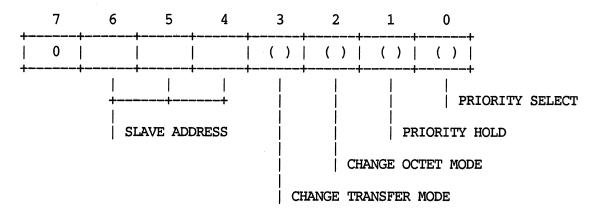

| -         | Bus A Control Octet                                  |

| -         | Bus B Bus Acknowledge Octet                          |

| _         | Bus A Master Status Octet                            |

| -         | Bus B Slave Status Octet                             |

|           | Request Interrupts Octet                             |

| -         | Request Facility Interrupts Octet                    |

|           | Request Transfer Settings Octet                      |

| -         | Selective Reset Control Octet                        |

|           |                                                      |

|           | Address Octet Response to Request Interrupts         |

|           | Slave Interrupts Octet                               |

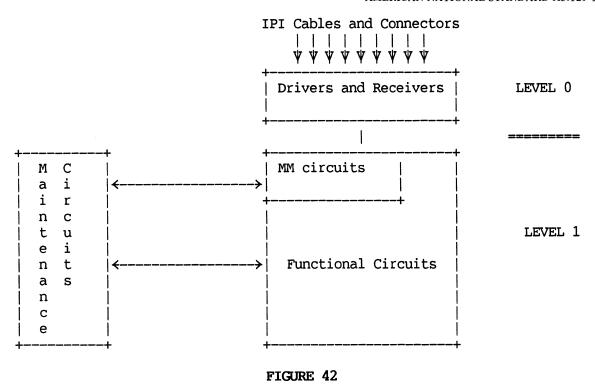

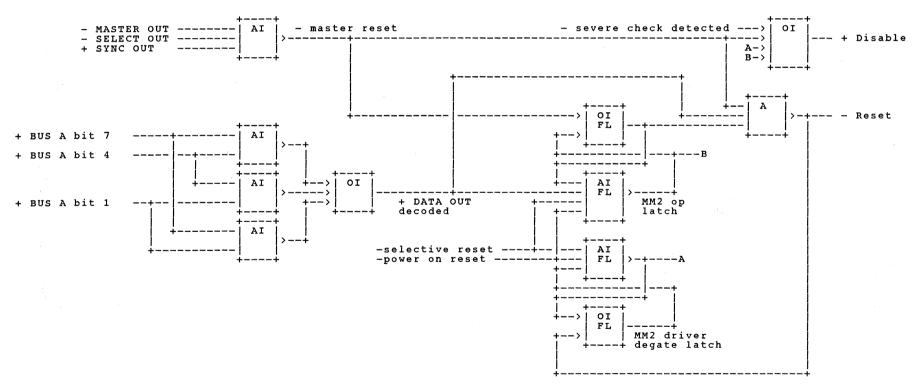

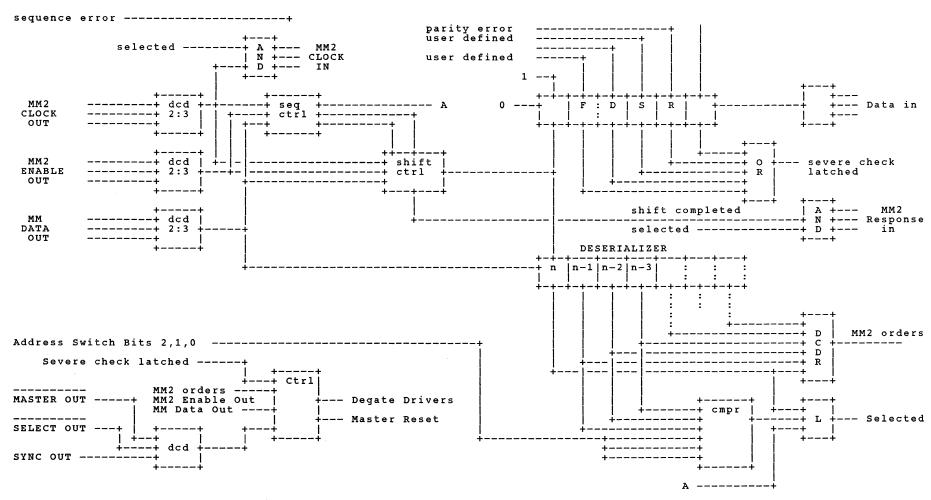

|           | Block Diagram of Maintenance Mode                    |

|           | IPI Levels                                           |

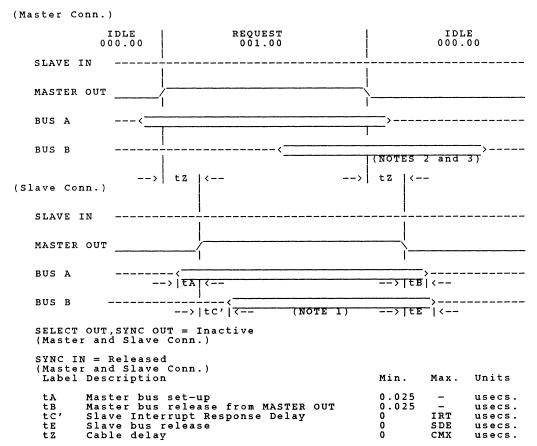

|           | Request Interrupts Sequence                          |

| riguit 44 | request interrupts bequerice//                       |

| SECTION | PAGE |

|---------|------|

|         |      |

|   | Figure 45 Request Transfer Settings/Slave Interrupts                      |    |

|---|---------------------------------------------------------------------------|----|

|   | (Optional)/Facility Interrupts (Optional) Sequence                        |    |

|   | Figure 46 Selection Sequence                                              |    |

|   | Figure 47 Normal Deselection Sequence                                     |    |

|   | Figure 49 Selective Reset Sequence                                        |    |

|   | Figure 50 Slave End without Information Transfer Sequence                 |    |

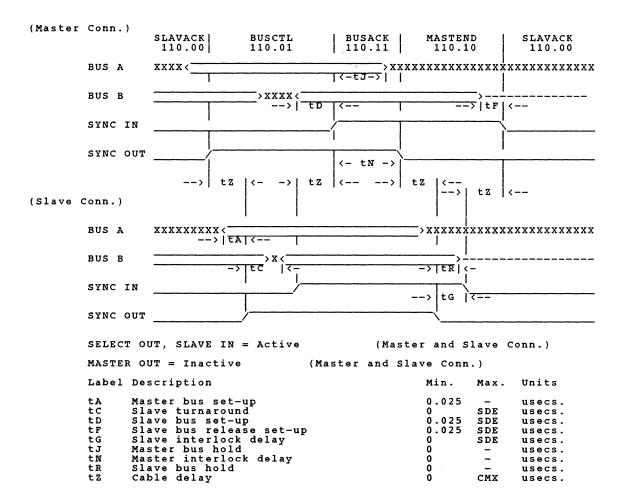

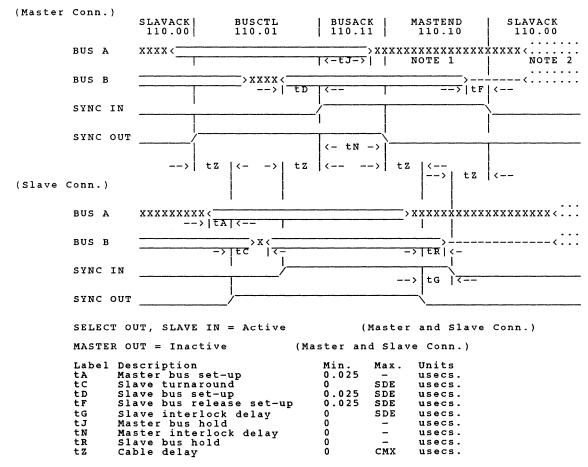

|   | Figure 51 Bus Control Sequence (Preceding Transfers In)                   |    |

|   | Figure 52 Bus Control Sequence (Preceding Transfers Out)                  |    |

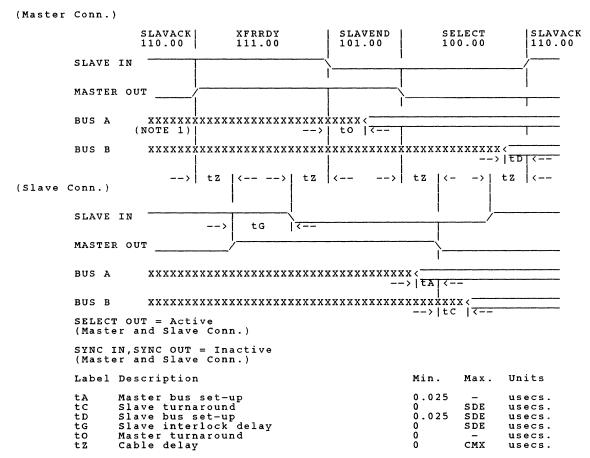

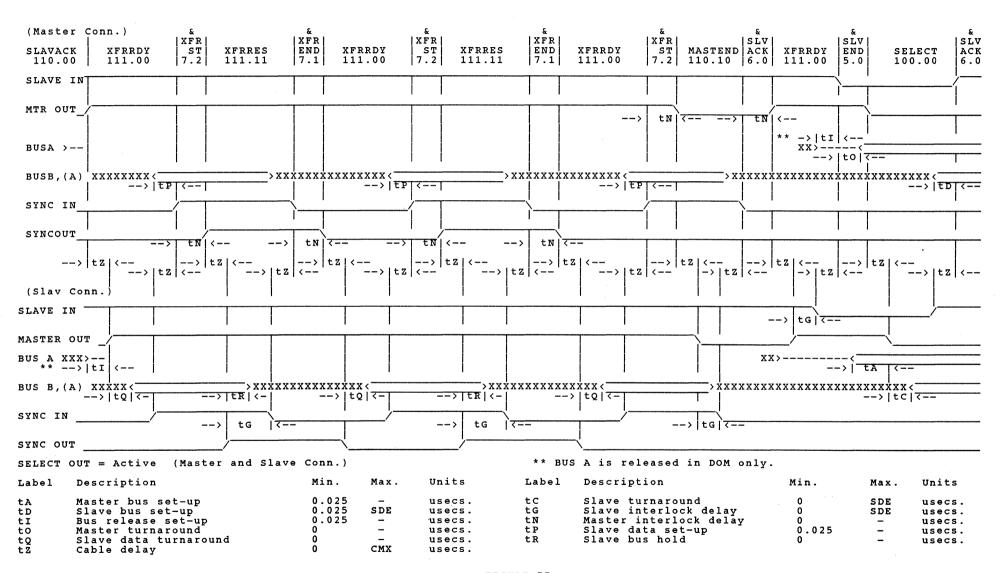

|   | Figure 53 Interlocked Input Sequence — Slave End                          |    |

|   | Figure 54 Interlocked Output Sequence — Slave End                         |    |

|   | Figure 55 Interlocked Input Sequence — Master End                         |    |

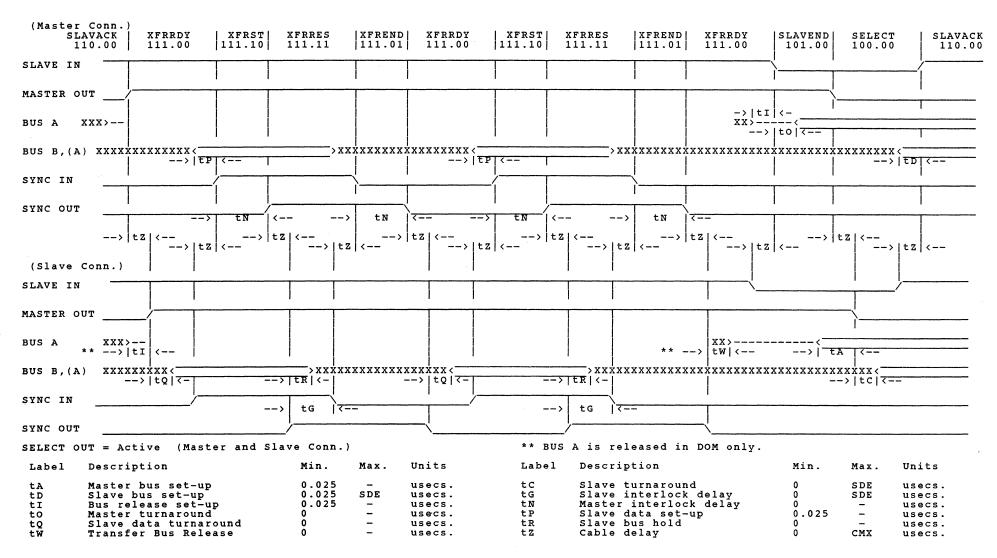

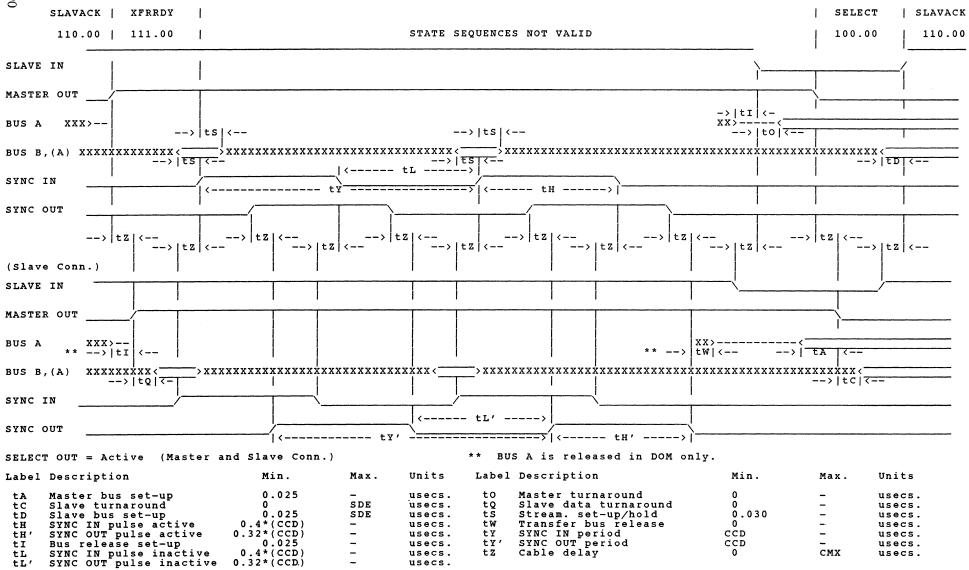

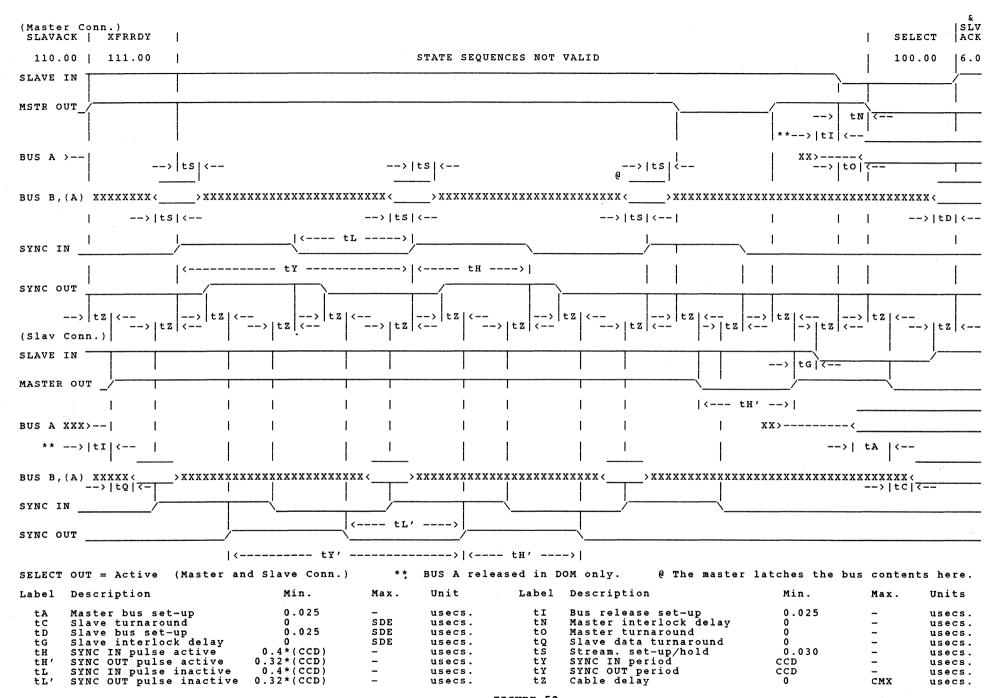

|   | Figure 57 Data Streaming Input Sequence — Slave End                       |    |

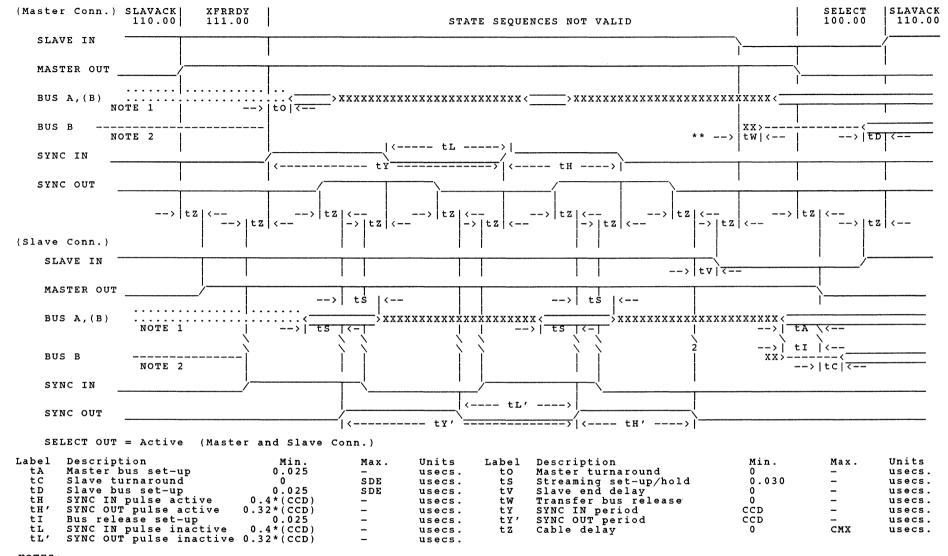

|   | Figure 58 Data Streaming Output Sequence — Slave End                      |    |

|   | Figure 59 Data Streaming Input Sequence – Master End                      |    |

|   | Figure 60 Data Streaming Output Sequence — Master End                     |    |

|   | Figure 61 Maintenance Mode 1                                              |    |

|   | Figure 62 Maintenance Mode 2                                              | 95 |

| Α | ppendixes  Appendix A Example of State Sequences for Information Transfer | 96 |

|   | Table A1 State Sequences for Information Transfer                         |    |

|   | Appendix B Specifications for 24-Conductor Shielded Cable                 | 97 |

|   | B1. Individual Coaxial Cables                                             |    |

|   | B2. Overall Cable Assembly                                                | 97 |

|   | Appendix C Specifications for 50-Conductor, Flat, Twisted-Pair Cable      | 98 |

|   | C1. Introduction                                                          |    |

|   | C2. Component Wire Description                                            |    |

|   | C3. Cable Description                                                     | 98 |

|   | Appendix D Specifications for 50-Conductor, Shielded, Twisted-Pair Cable  | 99 |

|   | D1. Introduction                                                          |    |

|   | D2. Inner Conductors                                                      |    |

|   | D3. Cable                                                                 | 99 |

|   | Appendix E 75-Meter Differential Driver/Receiver System                   | 00 |

|   | Appendix F Voltage Mode Differential Driver/Receiver System               | 01 |

|   | Figure F1 The Two Subsystem Arrangements with Parameter Labels            | 03 |

|   | Appendix G Maintenance Mode Logic Examples                                | 04 |

|   | Figures                                                                   |    |

|   | Figure G1 MM1 Block Diagram                                               |    |

|   | Appendix H Flat Cable Conductor/Subminiature "D"                          |    |

|   | Connector Pin Identification                                              | 06 |

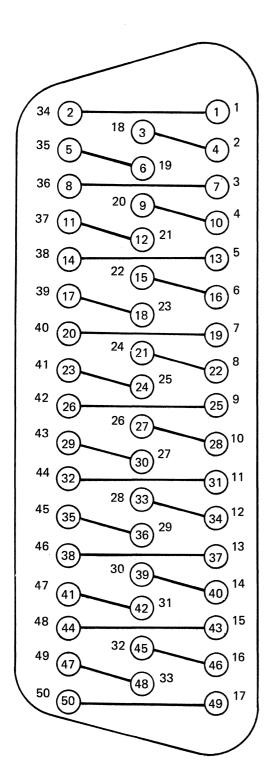

|   | Figure H1 Correspondence between Conductor Numbers and Pin Numbers 10     | 06 |

| , | 2.56.0 2.2. Concespondence over con conductor rumous and 1 in rumous It   | 50 |

|   |                                                                           |    |

## American National Standard for Information Systems -

# Intelligent Peripheral Interface – Physical Level

#### 1. Scope and Purpose

1.1 Scope. This American National Standard provides the mechanical, electrical and bus protocol requirements for a high-performance interface for peripheral devices attached to powerful computers.

The physical interface described in this document can be operated at rates up to 10 megabytes per second and over distances of up to 125 meters, depending upon circuit and cable implementation choices.

1.2 Purpose. The purpose of this standard is to facilitate the development and utilization of computer systems by providing a common interface at the physical level that provides for connection of peripherals (disks, tapes, printers, terminals, and the like) with diverse characteristics.

#### 1.3 Description of Sections

Section 1 contains the introductory material. Section 2 lists the publications referenced in this standard.

Section 3 provides a glossary.

Section 4 specifies the classes of electrical and mechanical connections defined by this standard. These specifications cover drivers, receivers, line termination, connectors, and cable parameters

Section 5 specifies control sequences required to implement master/slave interactions.

Section 6 describes the relationship between this standard and its companion standard, which covers logical use of the interface.

Section 7 provides detailed timing information.

**1.4 Editorial Conventions.** Certain terms used in this standard that are proper names of signals, state mnemonics, or similar terms are printed in

uppercase to avoid possible confusion with other uses of the same words; e.g., BUS A, SLAVE IN, SYNC OUT, DESEL, SLAVEND. Any lowercase uses of these words have the normal English meaning.

A number of conditions, sequence parameters, events, English text, states or similar terms are printed with the first letter of each word in uppercase and the rest lowercase; e.g., In, Out, Selective Reset, Bidirectional, Bus Control, Operation Response. Any lowercase uses of these words have the normal English meaning.

#### 1.5 Physical Interface

- **1.5.1 Purpose.** The purpose of the interface is to exchange information between connected machines, and meet the criteria of:

- (1) Content Independence. The operation of the interface is not affected by the contents of Information Transfers.

- (2) Speed Independence. The control of the interface is not timing critical in handling of the interface protocol.

- (3) Protocol Integrity. The integrity of the protocol sequences is ensured by requiring that each signal change be handshaked. No more than one signal is permitted to change at any time, except during optional Data Streaming transfers.

- **1.5.2 Characteristics.** The characteristics of the physical interface are as follows:

- (1) Master/slave mode of execution is used.

- (2) There is one master only.

- (3) Master selects slave.

- (4) A daisy-chained cable consisting of 24 signals is used.

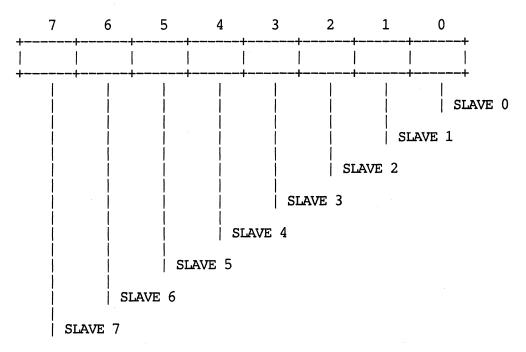

- (5) Up to 8 slaves are allowed, with up to 16 facilities per slave.

- (6) Bus Exchanges are used to frame Information Transfers and are executed only as interlocked and unidirectional.

- (7) Information Transfers occur using either the unidirectional configuration or in a 16-bit bidirectional configuration. The two can coexist on the same cable.

- (8) Information Transfers can be terminated in either direction by either the master or the slave.

- (9) Information Transfers are asynchronous and interlocked except during Data Streaming.

- (10) Except for Selection, a master can allocate control of interface functions to a dominant slave.

- **1.6 Configuration Characteristics.** The IPI has been designed to operate with three defined elements of a computer system; master, slave and facility.

- **1.6.1 Master.** The master manages the slaves and is responsible for control of the interface. It is the master's responsibility to operate the slaves according to their capabilities.

- 1.6.2 Slave. The slave is managed by the master and may or may not have intelligence, depending on the command set it is capable of executing. In an intelligent configuration, it can support a master that is oriented to generic device characteristics, such as a disk with 22 000 blocks of data, each 512 bytes long. In a device-oriented configuration, it can support a master oriented to specific device characteristics; e.g., a disk with 10 000 bytes/track, 7 tracks/cylinder, 500 cylinders/actuator. A facility is addressable through the slave.

- 1.6.3 Facility. The facility is addressable through the slave. It is the responsibility of the slave to manage the facility. A facility may or may not have generic functionality and may or may not be a device.

- **1.6.4 Multi-tier Structure.** Configurations of the IPI can be tiered in a hierarchical manner to provide a measure of compatibility between the different functional requirements of system utilization.

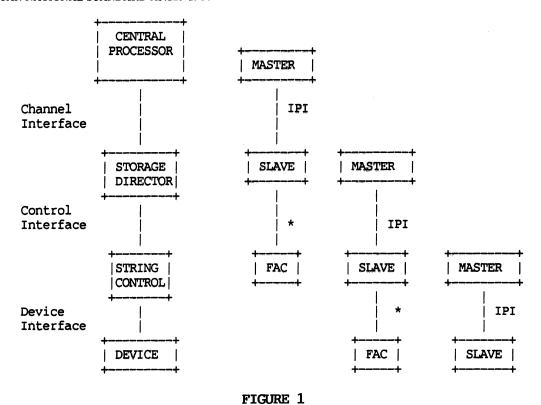

Figure 1 illustrates a mainframe configuration in which a Storage Director is both slave to the CPU and master to the String Control. The CPU can directly address the String Controls through the Storage Director.

The String Control is both slave to the Storage Director and master to the Devices. The Storage Director can directly address devices through the String Control.

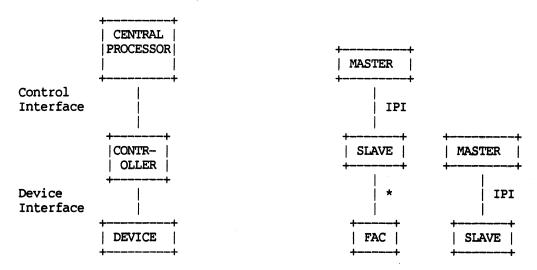

Figure 2 illustrates a minicomputer configuration in which the Controller is both

slave to the CPU and master to the Devices. The CPU can directly address devices through the Controller.

NOTE: The interface between slave and facility need not be IPI, but if it is, two separate IPI interfaces are needed to obtain 16 addresses.

1.7 Signal Nomenclature. The nomenclature used to define voltage levels, signal states, logical states, and their correlation to each other is defined in Table 1.

#### 2. Referenced Publications

**2.1** American National Standards. This standard is intended to be used in conjunction with the following American National Standards. When these standards are superseded by revisions approved by the American National Standards Institute, Inc, the revisions shall apply.

ANSI X3.130-1986, Information Systems — Intelligent Peripheral Interface — Device-Specific Command Sets for Magnetic Disk Drives

ANSI X3.132<sup>1</sup>, Information Systems — Intelligent Peripheral Interface — Device-Generic Command Set for Magnetic and Optical Disk

ANSI X3.147<sup>1</sup>, Information Systems — Intelligent Peripheral Interface — Device-Generic Command Set for Magnetic Tapes

**2.2 Other Standards.** This standard is also intended to be used in conjunction with EIA Standard for Electrical Characteristics of Generators and Receivers for Use in Balanced Digital Multipoint Systems, EIA RS-485-1983.

#### 3. Definitions

bidirectional. This term refers to the use of signal lines that may be asserted by either the master or a slave, but not concurrently.

bus acknowledge. In the optional configuration, where the master permits the slave to define the type of Information Transfer to be executed, Bus Acknowledge is the BUS B equivalent of Bus Control.

These standards are currently under development. Contact the Secretariat for the most recent information on the status and availability of these standards.

MAINFRAME CONFIGURATION EXAMPLE

\* This interface may or may not be IPI, but if it is, then the master/slave relationship is valid at that tier.

### FIGURE 2

#### MINICOMPUTER CONFIGURATION EXAMPLE

TABLE 1

SIGNAL NOMENCLATURE

|                          | _                                                                | <b>.</b>              |                       |   |                 |

|--------------------------|------------------------------------------------------------------|-----------------------|-----------------------|---|-----------------|

| <b>.</b>                 | L                                                                |                       | INTERFACE             | L |                 |

| TYPE OF<br>DRIVER        | VOLTAGE<br>  LEVEL                                               | SIGNAL<br>  CONDITION | LOGICAL<br>TRANSITION | 1 | GICAL<br>DITION |

|                          | LOW                                                              | ACTIVE                | ASSERT                | 1 | ONE             |

| THREE STATE              | HIGH                                                             | INACTIVE              | NEGATE                | 0 | ZERO            |

|                          | <br>  RELEASED<br>                                               | <br>  INACTIVE<br>    | DEGATE                | 0 | ZERO            |

| DIFFERENTIAL             | <br> <br>  HIGH                                                  | ACTIVE                | ASSERT                | 1 | ONE             |

| (Odd pin                 | LOW                                                              | INACTIVE              | NEGATE                | 0 | ZERO            |

| relative to<br>Even pin) | <br>  RELEASED<br>                                               | <br>  INACTIVE<br>    | DEGATE                | 0 | ZERO            |

| OPEN EMITTER             | HIGH                                                             | ACTIVE                | ASSERT                | 1 | ONE             |

| OPEN ENTITER             | LOW                                                              | INACTIVE              | NEGATE                | 0 | ZERO            |

|                          | RELEASED                                                         | INACTIVE              | DEGATE                | 0 | ZERO            |

|                          | والجبيد والبان ويون والمن والمن المنت مثاث والبي مردم والمن بدين |                       |                       |   | <b></b>         |

...........

NOTE: GATE is the action of ASSERTing or NEGATEing

bus control. This term refers to the Physical Interface Bus Control octet asserted on BUS A by the master during the Bus Control sequence. It is used to define the bus configuration for the subsequent Information Transfer.

bus exchange. This term refers to the Bus Control sequence (initiated by the master) and the Ending Status sequence (initiated by the slave), that are used to frame an Information Transfer (which may or may not have occurred). For every Bus Control sequence, there shall be an Ending Status sequence.

busy. This term describes a slave that is currently unable to process Bus Exchanges or Information Transfers.

data. This term refers to information transferred over the Physical Interface, other than that defined as Operation Commands and Operation Responses by the Logical Interface.

data streaming. This term refers to the transfer of information in a noninterlocked manner in order to achieve faster transfer rates.

dominant slave. This term describes a slave capable of assuming the role of the master for slave — slave Information Transfers.

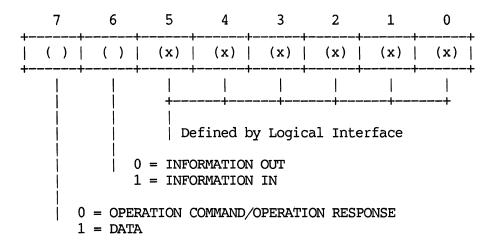

double octet mode (DOM). This term refers to a mode of Information Transfer that uses BUS A and BUS B in parallel in a bidirectional manner to transfer 16 bits concurrently.

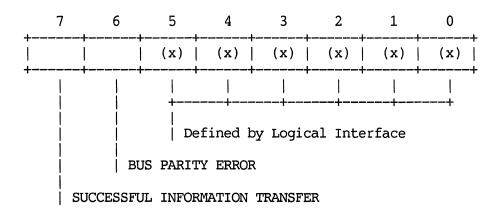

ending status. This term refers to the Physical Interface status octets presented by the master (optional) and the slave (mandatory) immediately following an Information Transfer.

facility. This term refers to the entity addressable by the master through the slave.

information transfer. This term refers to interchanges on the interface associated with the Logical Interface (i.e., Operation Commands, Operation Responses, and Data).

**interlocked.** This term refers to the handshake between master and slave of signals on the interface.

level 0. This term refers to the electrical and

mechanical characteristics of the Physical Interface.

**level 1.** This term refers to the bus states, sequences, and other rules (excepting electrical and mechanical characteristics of Level 0) that govern the use of the Physical Interface.

logical interface. This term refers collectively to all protocols higher than the Physical Interface specified in this standard.

maintenance mode. This term refers to the capability for a master to initiate analysis of the interface and restore operation after a failure condition.

mandatory. The functions labeled *mandatory* shall be included in all masters and slaves. They shall be implemented as defined in this standard.

master. This term refers to the entity in control of the interface.

master status. In the optional configuration, where the master permits the slave to define the type of Information Transfer to be executed, Master Status is the BUS A equivalent of Slave Status.

operation command. This term refers to a command issued by the master to initiate some specific operation that is outside the Physical Interface and is associated with a Logical Interface function.

operation response. This term refers to the response of a slave to an Operation Command. It is associated with the Logical Interface.

**optional.** This term describes features that are not required by the standard. However, if any feature defined by the standard is implemented, it shall be done as defined by the standard.

physical interface. This term denotes the mechanical, electrical, and interface protocols specified in this standard. In use, this term is the opposite of Logical Interface.

sequence. This term refers to a series of states that follow each other in a definite order to accomplish a function.

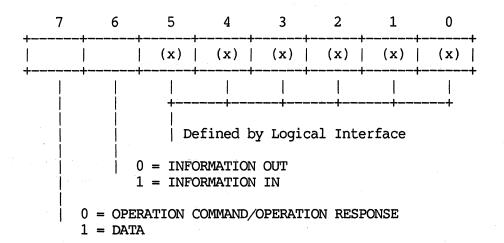

single octet mode (SOM). This term refers to a mode of Information Transfer that uses BUS A in a unidirectional manner to transfer 8 bits of information from master to slave, and BUS B in a unidirectional manner to transfer 8 bits of information from slave to master.

slave. This term refers to the addressable entity under control of, and directly connected to, the master.

slave status. This is the status asserted on BUS B by the slave at the completion of an Information Transfer (which may or may not have occurred).

**state.** This term is used to define the immediate condition of the interface, excluding transitions, as indicated by the control signals.

unidirectional. This term refers to the use of signal lines that are not asserted by both the master and slave (either concurrently or successively).

vendor unique. This term defines those features that can be defined as required by a vendor in a specific implementation. Caution should be exercised in defining and using such features since they are not necessarily standard between vendors.

#### 4. Physical Characteristics

This interface specification defines the configuration classes that cover all of the cable types and line driver/receiver types permitted by the proposed standard. The classes are defined in response to perceived market requirements for the wide range of applications within which this interface is expected to be used. The protocol and timing differences between classes are expected to be either absent or so small as to permit inexpensive, simple interconnection of different classes within a single system environment.

Table 2 represents the mechanical and electrical characteristics of all of the configuration alternatives, which are chosen by an implementor on the basis of required performance, cost considerations, or both. The connectors for each type of cable are specified

in 4.2 for both shielded and unshielded applications.

- **4.1** Configuration. A maximum of eight slaves shall be connected to the master. Typically, this would be by a daisy-chain signal cable configuration, but radial connection is permitted. Some precautions shall be taken to properly handle interface features, such as dominant slaves, if radial connections are used.

- **4.1.1** Alternatives. The configurations permitted by this standard are intended to permit selection of the most cost-effective alternative for different market environments.

#### **4.1.2** Intermix of Configurations

#### 4.1.2.1 Same Driver/Receiver Types.

The interconnection of different cable types using the same driver type is permitted within the restrictions of Table 6, provided that suitable techniques are used to maintain signal quality.

#### 4.1.2.2 Different Driver/Receiver Types.

The interconnection of configurations using different driver types requires that the master either be capable of operating with both, or there be an adapter that will exchange the signal types at the respective interfaces. The adapter, if any, is not defined in this standard.

- **4.1.3 Extension of Distance Limitations.** The use of repeaters/converters is not defined in this standard.

- **4.2 Connector Specification.** Three connector types shall be used with this interface. They are as follows:

- (1) A 2 · 25 pin header, plug-receptacle

- (2) A 50-pin connector

- (3) A 48-pin connector

#### 4.2.1 2 · 25 Pin Header, Plug-Receptacle. A

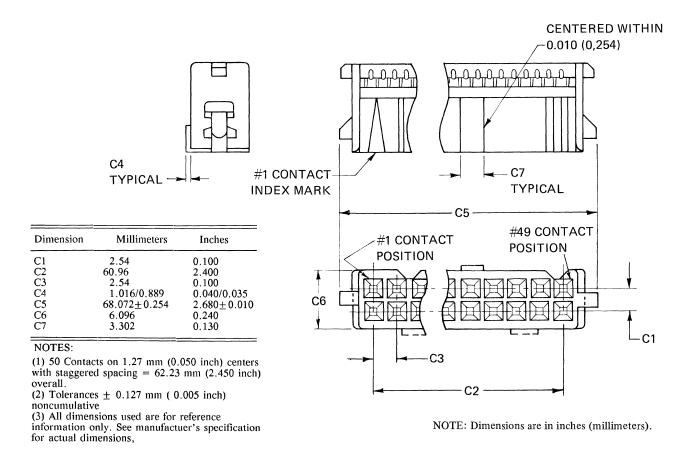

- 2 · 25 pin header assembly shall be used. See Figures 3 and 4 for the connector physical specifications. See Table 3 for the pin assignments and signal nomenclature.

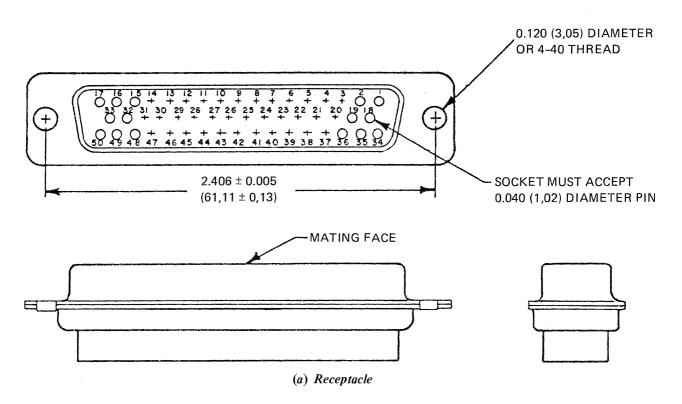

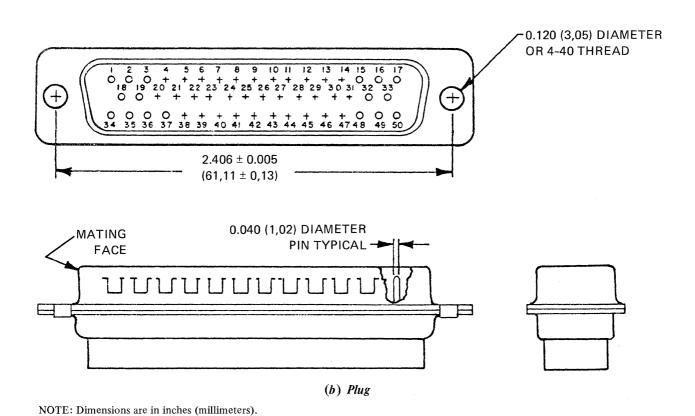

- **4.2.2 50-Pin Shielded Bulkhead Connector.** A three-row 50-pin shielded bulkhead subminature "D" connector shall be used. See Figures 5 through 7 for the connector physical specifications. Refer to Table 3 for the pin assignments and signal nomenclature.

NOTE: Cables with 50-pin connectors allow cables to be joined if a slave has to be removed from the interface for any reason (this is the rationale for requiring alternating retention hardware on opposite ends of the cable). However, it should be recognized that such abutments need to be limited in number so as to minimize signal degradation.

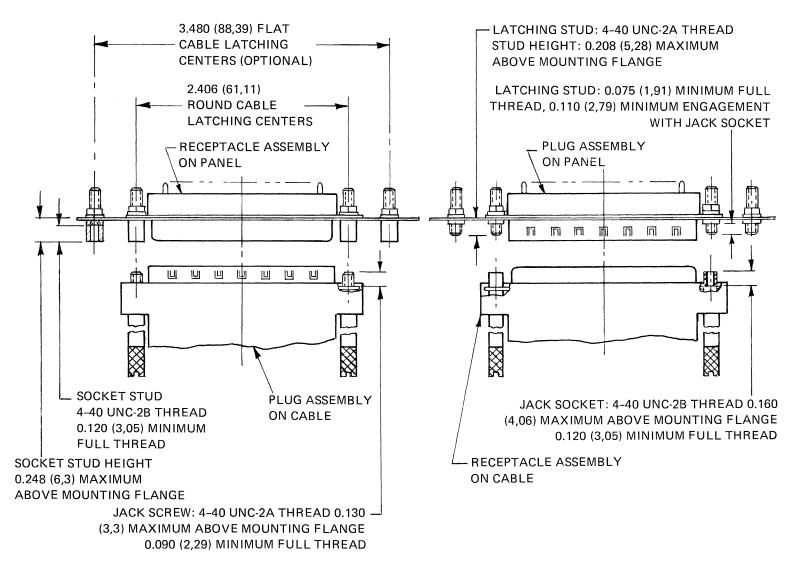

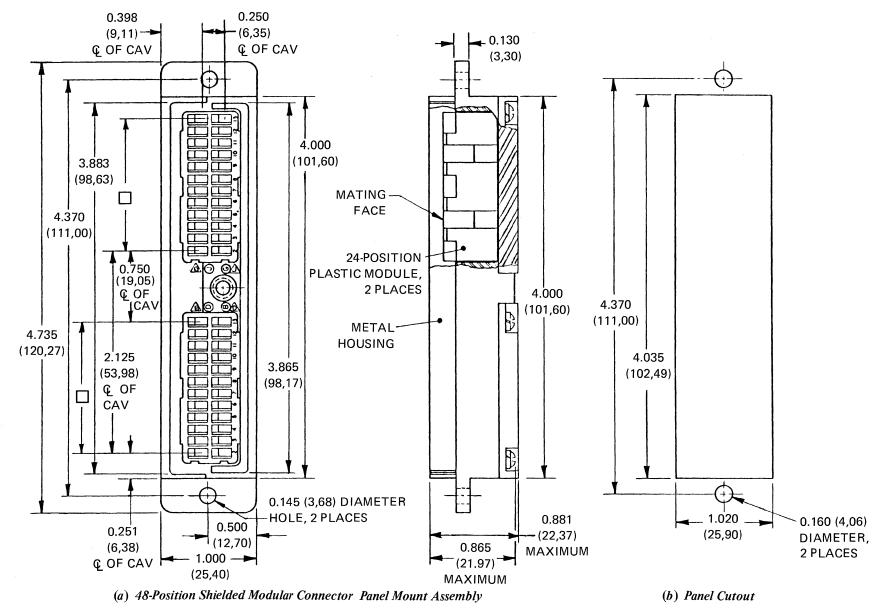

- 4.2.3 48-Pin Shielded Bulkhead Connector. A 48-pin shielded bulkhead coaxial connector shall be used. See Figures 8 through 10 for the connector physical specifications. See Table 4 for the pin assignments and signal nomenclature.

- 4.2.4 Connector Shells. The shells of the shielded connectors shall be plated with conductive material to ensure the integrity of the cable shield to chassis current path. The resistance of the cable shield to equipment chassis shall not exceed 5 milliohms, after a minimum of 500 cycles of mating and unmating.

- 4.2.5 Terminators. The terminators shall fit within the same dimensions as the cable end connectors, and shall be secured by the same retention method as are the cable connectors.

#### 4.3 Cable Characteristics

4.3.1 50-Conductor, 28-AWG Flat Cable. The cable shall consist of 50 conductors of 28 AWG capable of mass termination to all standard 50 mil insulation displacement connectors (IDC). The following electrical characteristics apply to the individual wires within the flat cable assembly:

Characteristic

impedance:  $100 \text{ ohms} \pm 10\%$

Signal

attenuation: 0.029 db max/ft at 5 MHz

Propagation

$1.4 \text{ ns/ft} \pm 10\%$ delay:

70 ohm max/1000 ft at 20°C dc Resistance:

4.3.2 50-Conductor, 28-AWG, Twisted-Pair Cable. The cable shall consist of 25 twisted pairs of conductors of 28 AWG. The cable may have an overall shield, suitable for terminating in a metal-shielded connector (see 4.2.2). The overall shield serves the purpose of a signal shield. The two wires of a pair shall be connected to the same signal, one to the positive and the other to the negative signal pin. The following electrical characteristics apply to the twisted pairs within the bulk cable assembly:

Characteristic

105 ohms + 6 ohms - 4 ohmsimpedance:

120 ohms  $\pm$  12 ohms (Voltage mode differential only)

Signal

attenuation: 0.029 db max/ft at 5 MHz

Propagation

delay:  $1.7 \text{ ns/ft} \pm 10\%$

dc Resistance: 70 ohms max/1000 ft at 20°C

NOTE: See 4.3.3 for conductor-to-conductor capacitance, pair-toshield delta capacitance, and pair-to-pair propagation delay delta.

4.3.3 50-Conductor, 26-AWG, Twisted-Pair Cable. The cable shall consist of 25 twisted pairs of conductors of 26 AWG. The cable may have an overall shield, suitable for terminating in a metal-shielded connector (see 4.2.2). The overall shield serves the purpose of a signal shield. The two wires of a pair shall be connected to the same signal, one to the positive and the other to the negative signal pin. The following electrical characteristics apply to the twisted pairs within the bulk cable assembly:

Characteristic

$106 \text{ ohms } \pm 10 \text{ ohms}$ impedance:

120 ohms  $\pm$  12 ohms (Voltage

mode differential only)

Signal

0.029 db max/ft at 5 MHz attenuation:

Propagation

delay:  $1.65 \text{ ns/ft} \pm 10\%$

43 ohms max/ft at 20°C dc Resistance:

Conductor-toconductor

> capacitance: 17 pf/ft max

Pair-to-shield

delta

capacitance: 0.8 pf/ft max

Pair-to-pair

propagation

delay delta: 0.15 ns/ft max

4.3.4 24-Conductor Coaxial Cable. The cable shall be a special-purpose, twin, parallel electrical cable. Each of these twin cables shall consist of 12 coaxial cables of 26-AWG signal wire and an associated shield and an overall shield. The overall shield shall be suitable for terminating in a metal-shielded connector (see 4.2.3). The following electrical characteristics apply to individual coaxial

Characteristic

cables:

95 ohms +6 ohms / -4 ohms impedance:

Signal attenuation (Increase in rise time measured between the 20% and 80% points of

the leading

0.025 ns max/ft edge):

Propagation delay (Measured at the 50% point of the

> leading edge): 1.22 < tPD < 1.27 ns/ft

45 ohms max/1000 ft at 20°C dc Resistance:

|                                                     |                           | =======             |                 | CINTUIT   |                                          |        |

|-----------------------------------------------------|---------------------------|---------------------|-----------------|-----------|------------------------------------------|--------|

| DRIVERS AND                                         | CABLE                     |                     | +<br> <br>+ MAX | MIN       | <br>  MAX STREAMING<br>  TRANSFER RATE** |        |

| RECEIVERS                                           | TYPE                      | ELECT<br>CHAR       | LENGTH          | ·         | SOM                                      | DOM    |

| THREE-STATE DRIVERS and TTL RECEIVERS W/ HYSTERESIS | <br>  FLAT<br>            | <br>  4.4.1<br>     | <br>  5m<br>    | - 200ns   | 5MBs                                     | 10MBs  |

| DIFFERENTIAL                                        | <br> <br>  TWISTED PAIR - | 4.4.2               | 50M             |           | Source                                   | TUMDS  |

| DIFFERENTIAL                                        | <br>                      | 4.4.3               | <br>  75м       |           |                                          |        |

| OPEN EMITTER                                        |                           | <br> <br> - 4.4.4 - | 65M             | <br> <br> |                                          |        |

| OFEN ENTITES                                        | COAX CABLE                | - 4.4.4 ·           | 125M            | 290ns     | 3.3MBs                                   | 6.7MBs |

TABLE 2

MECHANICAL AND ELECTRICAL CHARACTERISTICS

<sup>\*\*</sup> Interlocked transfer rates may exceed these rates over short distances

FIGURE 3 2 x 25 PIN HEADER - PLUG

<sup>\*</sup> See timing in Section 7 for a definition of CCD

TABLE 3

PIN ASSIGNMENTS FOR THREE STATE AND DIFFERENTIAL

| PIN             | GROUND<br>PIN   | THREE STATE DRIV     | ers/ receivers         | SIGNAL<br>PIN   | GROUND<br>PIN   |

|-----------------|-----------------|----------------------|------------------------|-----------------|-----------------|

| SIGNAL<br>PIN + | SIGNAL<br>PIN - | DIFFERENTIAL DRI     | VERS/RECEIVERS         | SIGNAL<br>PIN + | SIGNAL<br>PIN - |

|                 |                 | SIGNAL NAME          | SIGNAL SOURCE          |                 |                 |

| 1               | 2               | DC GROUND            |                        | 1               | 34              |

| 9               | 10              | ATTENTION IN         | SLAVE                  | 20              | 4               |

| 23              | 24              | SYNC OUT             | MASTER                 | 41              | 25              |

| 17              | 18              | SLAVE IN             | SLAVE                  | 39              | 23              |

| 43              | 44              | SYNC IN              | SLAVE                  | 15              | 48              |

| 35              | 36              | MASTER OUT           | MASTER                 | 45              | 29              |

| 29              | 30              | SELECT OUT           | MASTER                 | 43              | 27              |

| 45              | 46              | BUS B - BIT 0        | SLAVE(MASTER)          | 32              | 16              |

| 47              | 48              | 1                    |                        | 49              | 33              |

| 7               | 8               | 2                    |                        | 3               | 36              |

| 19              | 20              | 3                    |                        | 7               | 40              |

| 21              | 22              | 4                    |                        | 24              | 8               |

| 25              | 26              | 5                    |                        | 9               | 42              |

| 3               | 4               | 6                    | ļ                      | 18              | 2               |

| 5               | 6               | 7                    |                        | 35              | 19              |

| 49              | 50              | BUS B - PARITY       | SLAVE (MASTER)         | 17              | 50              |

| 37              | 38              | BUS A - BIT 0        | MASTER(SLAVE)          | 13              | 46              |

| 39              | 40              |                      | . ]                    | 30              | 14              |

| 15              | 16              |                      | !                      | 22              | 6               |

| 27              | 28              | ] ] 3                |                        | 26              | 10              |

| 31              | 32              |                      | ļ                      | 11              | 44              |

| 33              | 34              | 5                    |                        | 28              | 12              |

| 11              | 12              | 6                    | ļ                      | 37              | 21              |

| 13              | 14              | 7                    | <br>                   | 5<br>47         | 38              |

| 41              | 42              | BUS A - PARITY       | MASTER(SLAVE)          | 47              | 31              |

| 1               | !               |                      |                        | !               | !               |

| <br>  Head      | ler Pin Des     | signation (See Figur | e 3)                   | ,               |                 |

|                 |                 |                      | IEC 48B<br>Designation | Connector       |                 |

<sup>(1)</sup> The outer shield of the 50-conductor shielded cable is used to tie to the frame via the connector.

<sup>(2)</sup> When using the shielded bulkhead connector in a daisy-chain configuration, the master shall have a female panel connector per port, and each slave shall have both a female and a male panel connector per port. Line termination shall be provided at both ends of the cable.

<sup>(3)</sup> Each cable shall be manufactured with a male cable connector on one end and a female connector on the other end.

TABLE 4

PIN ASSIGNMENTS FOR OPEN EMITTER WITH 48 PIN COAXIAL CONNECTOR

| SIGNAL<br>PIN | DRAIN<br>WIRE | SIGNAL NAME  | SIGNAL SOURCE |

|---------------|---------------|--------------|---------------|

|               |               |              |               |

| G06           | G11           | ATTENTION IN | SLAVE         |

| D13           | D12           | SYNC OUT     | MASTER        |

| J02           | J03           | SLAVE IN     | SLAVE         |

| <b>J</b> 13   | J12           | SYNC IN      | SLAVE         |

| B06           | B11           | MASTER OUT   | MASTER        |

| D02           | D03           | SELECT OUT   | MASTER        |

| J04           | J05           | BUS B BIT 0  | SLAVE(MASTER) |

| G05           | G04           | 1            |               |

| J06           | J07           | 2            |               |

| G08           | G07           | 3            |               |

| J09           | J08           | 4            |               |

| G10           | G09           | 5            |               |

| J11           | J10           | 6            |               |

| G12           | G13           | 7            |               |

| G03           | G02           | BUS B PARITY | SLAVE(MASTER) |

| D04           | D05           | BUS A BIT 0  | MASTER(SLAVE) |

| <b>B</b> 05   | в04           | 1            |               |

| D06           | D07           | 2            |               |

| в08           | в07           | 3            |               |

| D09           | D08           | 4            |               |

| B10           | в09           | 5            |               |

| D11           | D10           |              |               |

| B12           | B13           | 7            |               |

| в03           | в02           | BUS A PARITY | MASTER(SLAVE) |

\_\_\_\_\_\_

- (1) The outer shield of the cable specified is used to tie to frame via the connector, and so provide the equivalent of the shield signal specified in Table 3.

- (2) When used in a daisy-chain configuration, each slave shall have panel connectors for a signal-In cable and a signal-Out cable per port. Each extreme end shall have line termination at the panel connectors. A master that has only a signal-Out connector shall have internal provision for line termination.

- (3) The connectors are hermaphroditic. The signal—In cable connector and the signal—Out panel (bulkhead) connector shall be light—colored. The signal—Out cable connector and the signal—In panel connector shall be dark—colored. Each cable shall be manufactured with a light—colored signal—In cable connector on one end and a dark—colored signal—Out cable connector on the other. Proper mating, including cable to cable shall be light to dark.

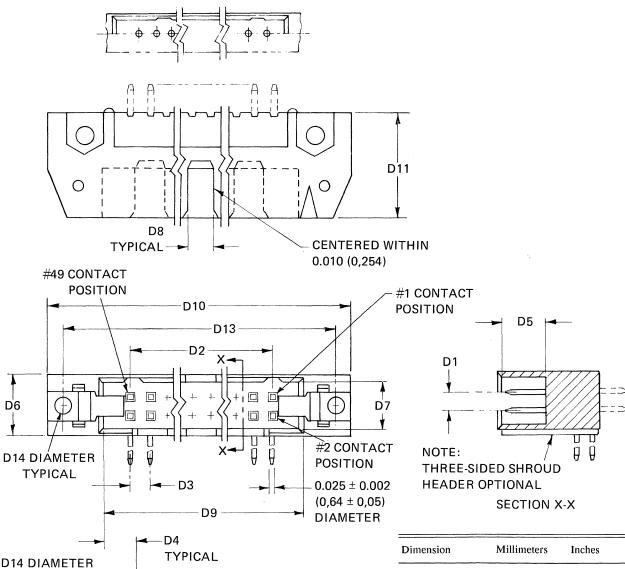

| D14 DIAMETER TYPICAL | TYPICAL |

|----------------------|---------|

| D15                  |         |

| 4                    | D12 →   |

NOTE: Dimensions are in inches (millimeters).

| Dimension | Millimeters       | Inches            |

|-----------|-------------------|-------------------|

| D1        | 2.54              | 0.100             |

| D2        | 60.96             | 2.400             |

| D3        | 2.54              | 0.100             |

| D4        | 4.83              | 0.190             |

| D5        | $6.10 \pm 0.25$   | $0.335 \pm 0.010$ |

| D6        | 82.80             | 3.260             |

| D7        | 6.35              | $0.250 \pm 0.010$ |

| D8        | 4.19              | $0.165 \pm 0.005$ |

| D9        | $68.83 \pm 0.038$ | $2.710 \pm 0.015$ |

| D10       | 9.14 Max          | 0.360 Max         |

| D11       | 13.94             | 0.549             |

| D12       | 72.64             | 2.060             |

| D13       | 78.74             | 3.100             |

- (1) 50 Contacts on 2.54 mm (0.100 inch) centers with staggered spacing = 60.96 mm (2.40 inch) overall.

- (2) Tolerances  $\pm$  0.127 mm ( 0.005 inch) noncumulative

- (3) All dimensions used are for reference information only. See manufactuer's specification for actual dimensions,

FIGURE 4

2 x 25 PIN HEADER - RECEPTACLE

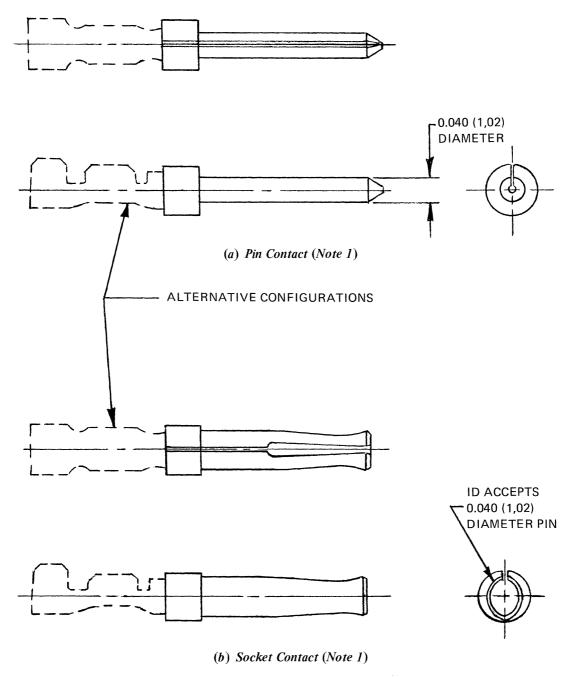

- Contact pictorials for reference only.

Dimensions are in inches (millimeters).

#### FIGURE 5

#### 50-POSITION SUBMINIATURE "D" PIN/SOCKET CONTACT

FIGURE 6

50-POSITION SUBMINIATURE "D" RECEPTACLE/PLUG

- (1) Recommended mounting clearance shall be in accordance with EIA 449-1983.

- (2) Receptacle assembly should have a conductive metal front shell.

- (3) Plug assembly should have a conductive metal front shell with grounding indents.

- (4) Cable end assembly should have a shielded stain relief system.

- (5) Connector assembly, on the panel side, can be rear or front mounted. Rear mounting shown for illustration only. Dimensions apply to rear or front mounting.

- (6) Dimensions are in inches (millimeters).

NOTES: (1) o denotes pin assignments for signal-in (dark) panel-mounted connector.

- (2)  $\triangle$  denotes pin assignments for signal-out (light) panel-mounted connector.

- (3)  $\Box = 11$  equal spaces at 0.125-1.375 (3.18-34.93).

- (4) All dimensions are in inches (millimeters). CAV = cavity.

FIGURE 8 48-POSITION SHIELDED MODULAR CONNECTOR - PANEL MOUNT

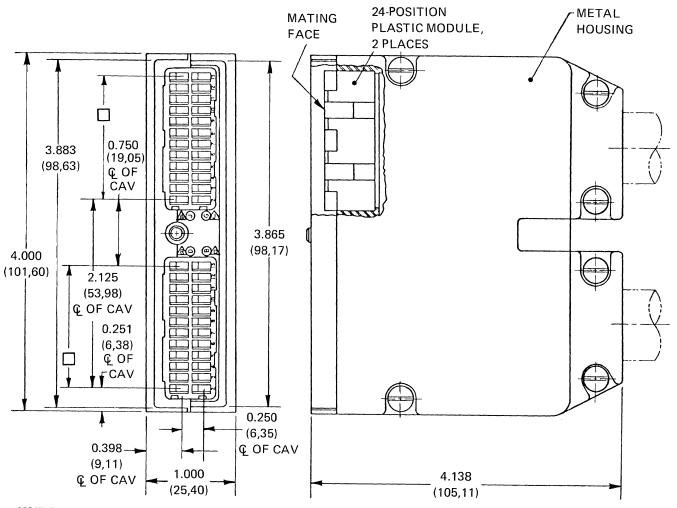

NOTES: (1)  $\circ$  denotes the pin assignments for the signal-out (dark) cable connector.

- (2) \( \triangle \) denotes the pin assignments for the signal-in (light) cable connector.

- (3) Each cable should have a signal-in connector on one end and a signal-out connector on the other end.

- (4)  $\Box = 11$  equal spaces at 0.125 1.375 (3,18-34,93).

- (5) All dimensions are in inches (millimeters). CAV = cavity.

FIGURE 9 48-POSITION SHIELDED MODULAR CONNECTOR - CABLE MOUNT

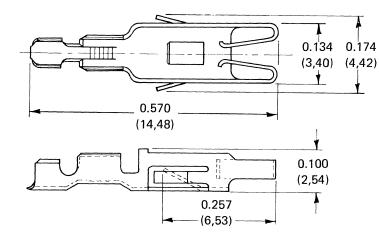

NOTES: (1) Crimp-type contact shown is for 30-26 AWG (0,050-0,13 mm<sup>2</sup>) and 24-22 AWG (0,2-0,4 mm<sup>2</sup>).

(2) All dimensions are in inches (millimeters).

FIGURE 10 48-POSITION CONNECTOR CRIMP-TYPE CONTACT

**4.4 Electrical Characteristics.** Bidirectional line transceivers are permitted on all signals; but when lines are used unidirectionally, transceivers shall be wired as unidirectional.

Upon completion of a Power On Reset, Slaves shall enable all drivers.

NOTE: If Slave-to-Slave Information Transfers are supported, MASTER OUT and SYNC OUT shall be bidirectional (see 5.4.9).

In all electrical configurations, the receiver as well as the driver shall tolerate, without damage, the situation in which up to nine drivers are active simultaneously in the same direction as well as the situation in which a line is shorted to dc ground. In the case of the ATTENTION IN signal, it is possible that up to eight slaves may be simultaneously signaling an Attention condition. The receiver output shall remain at logical active when any combination of the eight slaves is signaling attention. The ATTENTION IN signal shall not be driven to inactive.

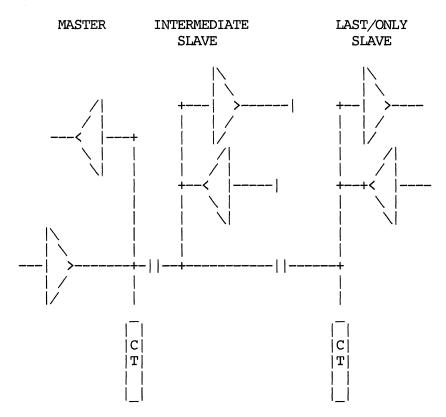

See Figure 11 for the configuration of bidirectional signal lines. See Figures 12 and 13 for the configuration of the unidirectional signal lines.

## **4.4.1** Three State Logic Drivers and Receivers with Hysteresis

4.4.1.1 Line Transceivers. The maximum Low-level output voltage shall be 0.5 volts. The minimum High-level output voltage shall be 2.4 volts. At the Low-level output voltage, the driver shall be capable of sinking 48 milliamperes, minimum. At the High-level output voltage, the driver shall be capable of sourcing 15 milliamperes, minimum. The maximum three-state output current with the line at the Low-level voltage shall be -1 milliamperes. Line drivers shall not be driven during power sequencing.

The maximum Low-level input voltage shall be 0.8 volts. The minimum High-level input voltage shall be 2.0 volts. At Low level, the input current shall be -1 milliamperes maximum. At High level, the input current shall be 80 microamperes, maximum. The hysteresis at the receiver inputs shall be 0.2 volts, minimum.

4.4.1.2 Line Drivers. The maximum Low-level output voltage shall be 0.5 volts. The minimum High-level output voltage shall be 2.4 volts. At the Low-level output voltage, the driver shall be capable of sinking 48 milliamperes, minimum. At the High-level output voltage, the driver shall be capable of sourcing 15 milliamperes, minimum. The maximum three-state output current

with the line at the Low-level voltage shall be -400 microamperes. Line drivers shall not be driven during power sequencing.

- 4.4.1.3 Line Receivers. The maximum Low-level input voltage shall be 0.8 volts. The minimum High-level input voltage shall be 2.0 volts. At Low level, the input current shall be -600 microamperes, maximum. At High level, the input current shall be 80 microamperes, maximum. The hysteresis at the receiver inputs shall be 0.2 volts, minimum.

- **4.4.1.4 Bus Terminators.** Each signal line shall be terminated at both ends of the cable by installing a 220-ohm resistor  $\pm$  2% from signal to + 5 volts and a 330-ohm resistor  $\pm$  2% from signal to ground.

- **4.4.1.5 Stubs.** A maximum stub length of 7 centimeters is allowed off of the mainline within any connected equipment. The mainline is defined as the continuous path between the terminators at each extreme end of the interface. The stub signals on the Printed Circuit Board shall maintain a characteristic impedance of 100-ohms  $\pm 20\%$ .

- **4.4.1.6 ATTENTION IN Signal.** The ATTENTION IN signal shall not be driven to inactive.

#### 4.4.2 Voltage Mode Differential

**Drivers/Receivers.** This class can support data transmission rates up to 10 Mbytes/s at up to 50 meters. The total length of all cable segments between master and slaves, all effective cable segments within the connected master and slaves, and all stubs shall be less than or equal to 50 meters.

The twisted pair leads always attach to an adjacent pair of connector pins as noted in Table 3.

- 4.4.2.1 Line Drivers. The differential driver shall meet the requirements of EIA RS-485-1983, which specifies the electrical characteristics of generators (drivers) and receivers for use in a balanced digital multipoint system.

- 4.4.2.2 Line Receivers. The differential receiver shall meet the requirements of EIA RS-485-1983, which specifies the electrical characteristics of generators (drivers) and receivers for use in a balanced digital multipoint system.

If the (+) signal lead is positive with respect to the (-) signal lead, the receiver output shall be logically active. The receiver output shall be inactive if the input differential signal is reversed.

Note: Terminator CT shall be at extreme ends of the cable.

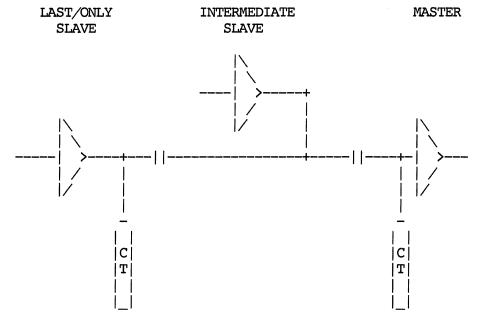

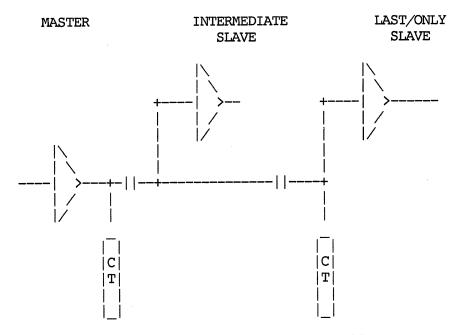

FIGURE 11

CONFIGURATION FOR BIDIRECTIONAL BUS SIGNALS

Note: Terminator CT shall be at extreme ends of the cable.

CONFIGURATION FOR UNIDIRECTIONAL SINGLE-ENDED LINES FROM SLAVE

FIGURE 12

Note: Terminator CT shall be at extreme ends of the cable.

FIGURE 13

CONFIGURATION FOR UNIDIRECTIONAL SINGLE-ENDED LINES FROM MASTER

- **4.4.2.3 Line Terminators.** Each signal line pair shall be terminated at both ends of the cable by installing a 150-ohm ( $\pm$  2%) resistor from signal pin (+) to signal pin (-).

- **4.4.2.4 Stubs.** A maximum stub length of 60 centimeters is allowed off of the mainline within any connected equipment. The mainline is defined as the continuous path between the terminators at each extreme end of the interface.

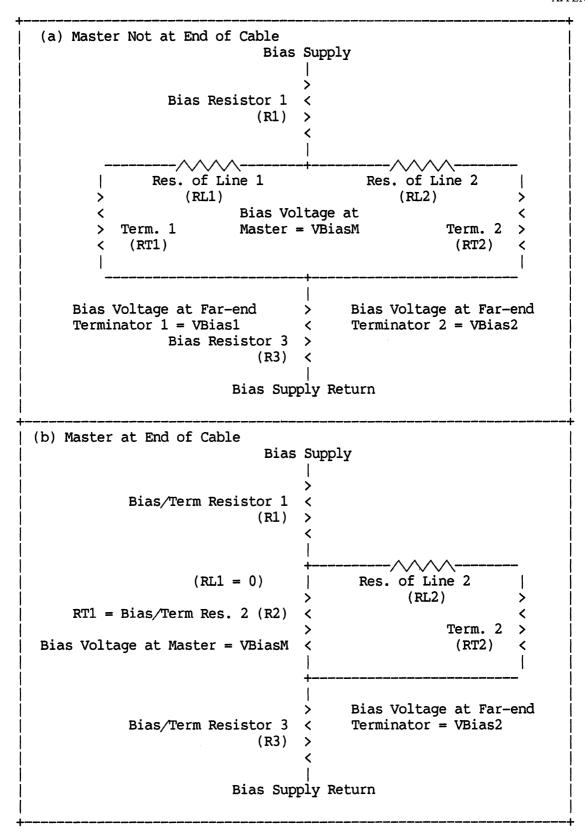

- 4.4.2.5 Line Bias. Each signal line pair shall be biased so as to establish a minimum 250-millivolt quiescent differential voltage. This is done in order to enforce an inactive state (zero) when the signal pair is released. The biasing network shall be of sufficiently high impedance to minimize disturbance of signal transmission.

- **4.4.2.6 Signal Level.** The minimum signal available to any master or slave differential receiver attached to the cabling system shall be at least 400 millivolts.

- **4.4.2.7 ATTENTION IN Signal.** The ATTENTION IN signal shall not be driven to inactive.

- 4.4.3 Current Mode Differential Drivers/Receivers. The driver approximates a constant current source. The current is steered to the leads of the twisted-pair transmission line by the appropriate logic levels at the input terminals. The output current can be switched off (released) for multidriver operation. The driver can either be a single current source that is steered into one or the other of the twisted-pair leads or a dual current source to ensure nearly equal and opposite currents in the twisted-pair leads. Either type can be intermixed on the interface, provided that they individually meet the criteria outlined in this standard.

The twisted-pair leads always attach to adjacent connector pins (as noted in Table 3).

4.4.3.1 Line Drivers. When all other drivers are inhibited, a driver's constant current source shall be capable of developing a differential signal across the twisted-pair leads of between 125 millivolts and 1.1 volts at a receiver that is separated from the driver by the maximum allowable cable resistance. The differential signal value should apply with the duty cycle between 30 percent and 60 percent at 5 megahertz and with the lines properly terminated. If the data input becomes inactive, the output signal is reversed resulting in a minimum of -125 millivolts as measured from the

- (+) signal relative to the (—) signal twisted-pair lead. When the driver is inhibited, the current source is disconnected from the outputs so that the output current and voltage will allow the receiver to detect signals from the other drivers on the line. The common mode range of the driver shall be at least +3 volts or at least -3 volts.

- 4.4.3.2 Line Receivers. The two receiver are connected to the twisted-pair (+) and (-) signal leads; so that the receiver may sense signals on the interface line pair. The receiver sensitivity shall be such that the receiver output is stable with a differential signal of 25 millivolts or more. Common mode range of the receiver shall be at least +3 volts or at least -3 volts.

If the (+) signal lead is positive with respect to the (-) signal lead, the receiver output shall be logically active. The receiver output shall be inactive if the input differential signal is reversed.

4.4.3.3 Line Termination. Each twisted-pair conductor line is terminated to DC ground at both extreme ends of the twisted-pair transmission line with a 51-ohm ( $\pm$  2%) resistor. The lines are biased at the master to ensure that the case in which the lines are undriven can be reliably interpreted and also to prevent receiver oscillation.

If the drivers used require two voltage supplies, the biasing network shall consist of a resistor from the (—) signal lead to a positive supply and a resistor from the (+) signal lead to a negative supply. If a single voltage supply driver is used, a single resistor will suffice. If the resistors are used, the resistor values shall be small enough to place the (—) signal a minimum of 60 millivolts above DC ground and the (+) signal at least 60 millivolts below ground. If a single resistor is used its value shall ensure that the (+) signal is a minimum of 120 millivolts more negative than the (—) signal with all drivers inhibited.

NOTE: Since the biasing subtracts from the operating noise margins, the resistor values shall also be large enough so that the normal operating differential signal does not fall below the 125-millivolt minimum specified in 4.4.3.1. This range shall be ensured regardless of where on the cable the measurement is taken, including the extreme end, which is separated from the biasing network by the maximum cable resistance. The values apply after the lines fully stabilize.

**4.4.3.4 Stub/Interconnect Lengths.** A maximum stub length of 12 centimeters is allowed

off of the mainline within any connected equipment. The mainline is defined as the continuous path between the terminators at each extreme end of the interface.

A maximum etched mainline interconnect length of 12 centimeters is allowed at any one place within any connected equipment. The etched interconnects and stubs are controlled so that the two conductors associated with a twisted pair are routed together. The interconnect and stubs shall maintain an effective resistance of no greater than the 28 AWG wire specified in 4.3.2. It is recommended that etched interconnects be avoided whenever possible, especially at intermediate points on the interface where the cable goes through a slave. Etched interconnects add significantly to differential noise as well as increasing the exposure to losing the entire interface whenever a connector fault occurs within a slave.

- **4.4.3.5 ATTENTION IN Signal.** The ATTENTION IN signal shall not be driven to inactive.

- 4.4.4 Open Emitter Drivers/Receivers

- **4.4.4.1 Line Drivers.** The maximum Low-level output voltage shall be 0.15 volts. The minimum High-level output voltage shall be 2.4 volts. At High level, the driver output shall source 100 milliamperes, minimum. Line driver outputs shall be Low or released during power sequencing, except for ATTENTION IN, which shall be released.

- 4.4.4.2 Line Receivers. The maximum Low-level input voltage shall be 0.7 volts. The minimum High-level input voltage shall be 1.7 volts. At Low level, the input current shall be -400 microamperes, maximum. At High level (5.0 volts), the input current shall be 420 microamperes, maximum.

- **4.4.4.3 Line Termination.** Each signal shall be terminated by installing a 95-ohm ( $\pm$  2%) resistor from signal to ground at the extreme ends of the cable.

- 4.4.4.4 Stub Lengths. A signal In bulkhead connector shall be used with an interconnection to a signal Out bulkhead connector. A maximum stub length of 15 centimeters is allowed off of the mainline within any connected equipment. The mainline is defined as the continuous path between the terminators at each extreme end of the interface. The interconnection shall maintain an effective 26 AWG with an impedance of 95 ohms, +6 ohms, -4 ohms.

- 4.4.4.5 Intermixed Cable Configurations. It is allowable to intermix twisted-pair cables and coaxial cables in the same daisy chain. Twisted pair may be used internal to a slave to complete the signal path between the signal In connector and the signal Out connector. The internal length of this path shall be kept to a minimum and shall be included in the calculation of maximum cable length.

- **4.4.4.6 ATTENTION IN Signal.** The ATTENTION IN signal shall not be driven to inactive.

#### 4.5 Cable Interconnections

- **4.5.1 Stub Lengths.** Table 5 represents the valid stub lengths for electrical and cable combinations.

- 4.5.2 Maximum Cable Lengths and Allowable Cable/Driver Combinations. The maximum cable lengths with the various cabling/driver configuration choices are shown in Table 6.

- **4.5.3 Cable and Connector Configurations.** The cable and connector combinations permitted by the standard are described in Table 7.

- 4.5.4 Configurations. Figures 11 through 13 illustrate cabling alternatives for configurations that have a master at one end of the cable, a slave at the other, with intermediate slaves. Other electrically valid configurations may be used, even if they are not shown in the figures.

TABLE 5

STUB LENGTHS (Centimeters) FOR ELECTRICAL/CABLE COMBINATIONS

| +                                       | 4.3.1         | 4.3.2             | 4.3.3             | 4.3.4         |

|-----------------------------------------|---------------|-------------------|-------------------|---------------|

|                                         | FLAT<br>CABLE | 28 AWG<br>TWISTED | 26 AWG<br>TWISTED | COAXIAL CABLE |

| 4.4.1 Three State                       | 7             | N/A               | N/A               | N/A           |

| 4.4.2 Differential (Voltage Mode Class) | N/A           | 60                | 60                | <br>  N/A<br> |

| 4.4.3 Differential (Current Mode Class) | N/A           | 12                | 12                | N/A           |

| 4.4.4 Open Emitter                      | N/A           | N/A               | 15                | 15            |

31

TABLE 6

MAXIMUM CABLE LENGTHS (Meters) FOR VARIOUS DRIVER OPTIONS

|                                                    | 4.3.1         | 4.3.2             | 4.3.3                                   | 4.3.4                                  |

|----------------------------------------------------|---------------|-------------------|-----------------------------------------|----------------------------------------|

|                                                    | FLAT<br>CABLE | 28 AWG<br>TWISTED | <br>  26 AWG<br>  TWISTED<br>  PR CABLE | COAXIAL<br>  CABLE                     |

| <br>  4.4.1 Three State<br>                        | 5             | N/A               | <br>  N/A<br>                           | N/A                                    |

| <br>  4.4.2 Differential<br>  (Voltage Mode Class) | N/A           | 50                | 50 less<br> length of<br>  4.3.2        | N/A                                    |

| <br>  4.4.3 Differential<br>  (Current Mode Class) | N/A           | 50                | 75 less<br> 1.5*(lngth<br>  of 4.3.2)   | , ,                                    |

| <br>  4.4.4 Open Emitter<br>                       | N/A           | N/A               | <br>  65<br>                            | 125 less  <br>2*(length  <br>of 4.3.3) |

NOTE: The values shown in this table represent the maximum accumulated length that is valid with a particular electrical class. An implementation may permit two cable types to coexist, for example, an internal cable that interconnects multiple devices within a cabinet and an external cable that exits the cabinet. The formula shown is used to calculate the total for one type, less the actual sum of the lengths in the other type referenced, for example, the maximum length for an installation of Open Emitter and Coaxial Cable is 125 meters, less twice the actual length of the twisted-pair cable internal to the cabinet.

TABLE 7

CABLE AND CONNECTOR COMBINATIONS

| <del>+</del><br>                            | 4.3.1         | 4.3.2                         | 4.3.3                         | 4.3.4            |

|---------------------------------------------|---------------|-------------------------------|-------------------------------|------------------|

|                                             | FLAT<br>CABLE | 28-AWG<br>TWISTED<br>PR CABLE | 26-AWG<br>TWISTED<br>PR CABLE | COAXIAL<br>CABLE |

| 4.4.1 50 Pin Header                         | х             | <br>  x<br>                   | Х                             | N/A              |

| 4.4.2 50 Pin Shielded<br>Bulkhead Connector | N/A           | <br>  X<br>                   | x                             | N/A              |

| 4.4.3 48 Pin Shielded<br>Bulkhead Connector | N/A           | <br>  N/A<br>                 | N/A                           | x                |

#### 5. Protocol

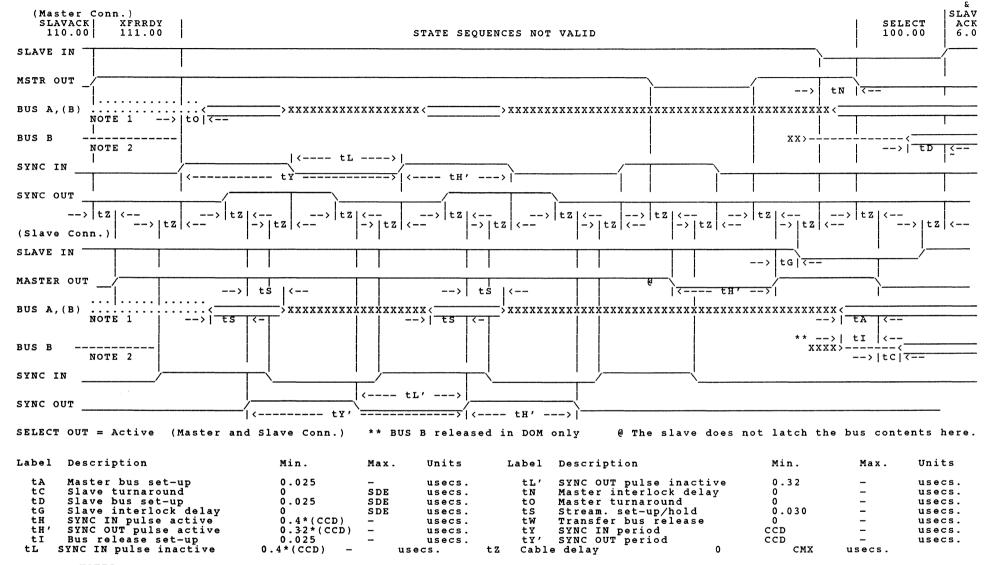

This section provides signal definitions, state, sequence, octet, and Maintenance Mode descriptions. The terms "In" and "Out" are always used in reference to the master. Relative signal timing and tolerance is defined in Section 7.

#### 5.1 Interface Description

- **5.1.1 Bus Usage.** The following apply to the use of BUS A and BUS B

- (1) The uses of BUS A and BUS B are structured to optimize operations between Bus Exchanges and Information Transfers.

- (2) The Bus Control sequence is initiated by the master and is associated with control of the Physical Interface. The Ending Status sequence is initiated by the slave and is associated with reporting the status of the Bus Exchange or the preceding Information Transfer.

- (3) During Bus Exchanges BUS A is unidirectional Out from the master for Bus Control and Master Status (optional), and BUS B is unidirectional In to the master for Bus Acknowledge (optional) and Slave Status.

- (4) Information Transfer is the term used to indicate the various types of information (Data, Operation Command, or Operation Response) that are transparently transferred across the Physical Interface.

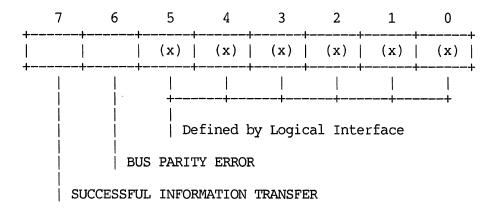

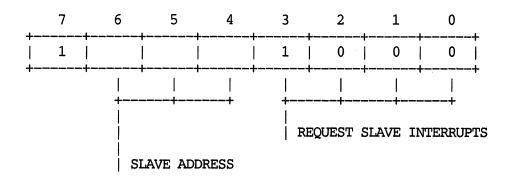

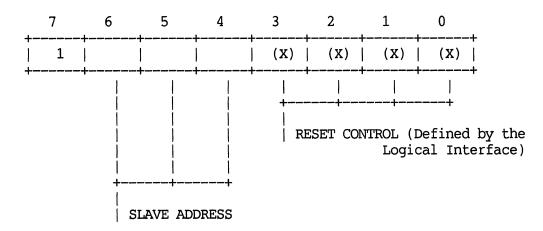

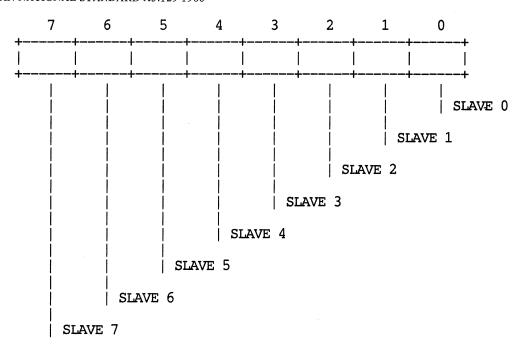

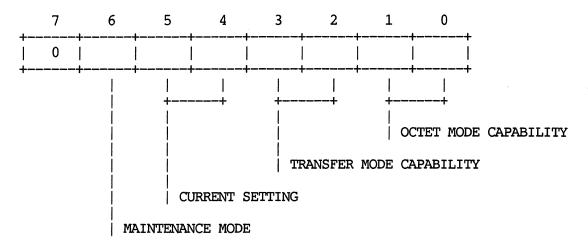

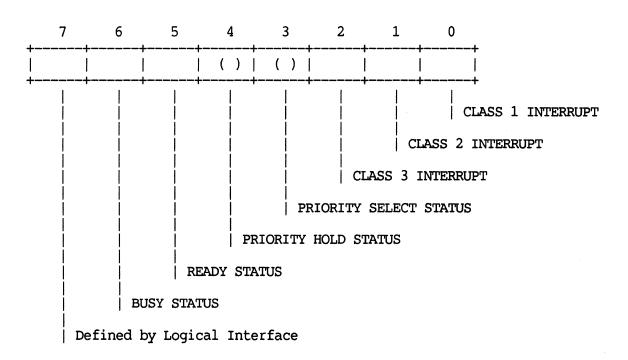

- (5) Bus Exchanges are defined as framing (bracketing) Information Transfers. The differentiation between Bus Exchanges and Information Transfers allows a simple state machine to control Bus Exchanges; for example, the timing-independent Bus Exchanges can be interpreted by a general-purpose microprocessor.