## Service Processor Module

#### General:

The Service Processor Module (SPM) attaches to the system bus and provides various service functions for the system. These functions include system console interfaces, front panel interface, real time clock, system clock interrupt source, power supply controls, floppy disk controller, system wide interrupt dispatcher, various system monitor functions (power, temperature), and system diagnostic capabilities.

#### Hardware:

The Service Processor Module is a special purpose computer consisting of two boards, the main board, which plugs into the CSS bus backplane, and the real world interface board, which contains all connectors for the serial ports, the power supply control connectors, and the temperature sensor connectors. The real world interface board is connected to the main board via a third 96pin din connector at the bottom of the main board. The real world interface board resides behind the CSS backplane in the interface slot behind the Service Processor Main board. The SPM contains the following elements:

- \* 68020 processor operating at 10Mhz (1/2 the system clock rate)

- \* 32 or 64 or 128 kbytes of EPROM organized bytewise.

- \* 256 kbytes of static RAM organized as 64 k x 32 bits

(8 32k x 8 RAM chips)

floppy disk controller (WD37C65)

- \* (RWI) Z8030 SCCs (2) for 4 console ports

- \* Z8036 CIO for internal timing

- \* (RWI) additional Z8036 CIOs (2) for various input/output bits

- \* Real time clock and calendar chip (MK48T12) (also contains 2K bytes of RAM for nonvolatile storage) and battery

- \* (RWI) RS232 drivers and receivers

- \* A/D converter chip for voltage and a temperature sensor

- \* (RWI) a second A/D converter for system temperature sensors

- \* (RWI) relays for power supply controls

CSS bus interface

state machine and queuing registers for interrupt dispatcher

\* Clock controller for switching between a local CPU clock and the CSS bus clock

Mapping RAM (16 x 8 RAM for mapping the entire systems address space in 1/4 Gbyte segments into the 68020s address space).

all sections marked with a (RWI) are located on the real world interface

#### Power:

Part of the SPM is powered separately from the rest of the system (all sections marked with an \*). This separate power supply must be capable of supplying +5V at 3.5 A and +12V at .25 A and -12V at .25 A. This power supply is ored with the main power supply, so that, after the main power is on, the SPM can continue to function, even in the event of a failure of the separate SPM power supply.

## Physical:

The Service Processor consists of two physical PC boards. The main board is a standard size CSS board which resides in the CSS cardcage. The real world interface board contains the serial port drivers and receivers, the serial controller chips (SCCs), an Analog to Digital converter chip for sensing temperatures, a parallel I/O chip (CIO) and relays and optoisolated input receivers for controlling power supplies and all necessary connectors to support these funcions.

The real world interface board receives power from the main board and is powered whenever the SPMs CPU is powered, i.e. even when the system's main power is turned off (see above).

# 68020 Processor:

The SPMs CPU is a 12.5 MHz 68020 which operates either from the CSS bus system clock divided by two (10 MHz) or its own 10 MHz clock source. (See below for clock select information).

## Address Decoding:

The address bits of the 68020 are numbered Add.00 to Add.31 with Add.00 as the least significant bit and Add.31 the most significant bit. Add.31 is used to differentiate between CSS bus accesses and local board acesses. Add.31 = 0 means the CPU is accessing a local resource. The local resources are further decoded as follows:

Add.31 30 29 28 27 26 25 24

| 0      | х      | х      | х      | 0      | 0      | 0      | 0      | 0      | EPROM (or SRAM)                       |  |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------------------------------|--|

| 0      | х      | х      | х.     | 0      | 0      | 0      | 1      | 1      | SRAM (or EPROM)                       |  |

| 0      | х      | х      | х      | 0      | 0      | 1      | 0      | 2      | Z-bus Peripherals                     |  |

| 0      | х      | х      | х      | 0      | 0      | 1      | 1      | 3      | Real Time Clock & NV RAM              |  |

| 0      | х      | х      | х      | 0      | 1      | 0      | 0      | 4      | reserved                              |  |

| 0      | х      | х      | х      | 0      | 1      | 0      | 1      | 5      | Clock control                         |  |

| 0      | х      | х      | х      | 0      | 1      | 1      | 0      | 6      | reserved                              |  |

| 0      | х      | х      | х      | 0      | 1      | 1      | 1      | 7      | Status and Control Registers          |  |

| 0<br>0 | У<br>х | У<br>х | У<br>х | 1<br>1 | 0<br>0 | 0<br>0 | 0<br>1 | 8<br>9 | Map RAM location (yyy)<br>Floppy disc |  |

| 0      | х      | х      | х      | 1      | 0      | 1      | 0      | А      | reserved                              |  |

| 0      | х      | х      | х      | 1      | 0      | 1      | 1      | В      | Interrupt Dispatcher Idle Que         |  |

| 0      | х      | х      | х      | 1      | 1      | 0      | 0      | С      | Interrupt Dispatcher Queue            |  |

| 0      | х      | х      | х      | 1      | 1      | 0      | 1      | D      | Interrupt Dispatcher Pointer          |  |

| 0      | X      | x      | х      | 1      | 1      | 1      | 0      | E      | Interrupt Dispatcher Misc.            |  |

| 0      | х      | х      | х      | 1      | 1      | 1      | 1      | F      | reserved                              |  |

x are not decoded and are don't cares.

#### EPROM:

The EPROM is 8 bits wide and can be read by the processor on data bits 24 to 31. There are 2 sockets for the EPROM, one or both can be populated with either 27256s (32k x 8 each), or 27512s (64k x 8 each) or 271001s (128k x 8 each). Address bits Add.00 to Add.15 or Add.16 or Add.17 are used to address the EPROM. The decoding of the high bit is controlled by the Promsize field in control register 2. This allows the two EPROM chips to be contiguous regardless of their size. (See Control register 2 desciption for details).

## SRAM:

The SRAM is 32 bits wide and consists of 8 or 4  $32k \times 8$  static RAM chips for  $64k \times 32$  or  $32k \times 32$  bits of memory. It is addressed with address bits Add.02 to Add.17.

Z - Bus Peripherals

Add.11 10 9 8

There are 7 peripherals attached to the Z - bus. 2 of them are located on the main board, and 5 are on the auxiliary board. When the Z-bus is selected (Add.31 = 0 and Add.27 to Add.24 = 2), Add.11 to Add.08 are further decoded as follows:

| 0<br>0<br>0 | -           | 0<br>0<br>1 | 0<br>1<br>0 | $\begin{array}{r} 0\\ 1\\ 2\\ 3 - 7\end{array}$ | reserved<br>Local Analog to Digital Converter<br>Local CIO<br>reserved for local devices |

|-------------|-------------|-------------|-------------|-------------------------------------------------|------------------------------------------------------------------------------------------|

| -           | 0<br>0<br>0 | -           | 0<br>1<br>0 | 8<br>9<br>A                                     | Auxiliary SCC 0<br>Auxiliary SCC 1<br>Auxiliary CIO 0                                    |

| 1 | 0 | 1 | 1 | В     | Auxiliary Analog to Digital Converter |

|---|---|---|---|-------|---------------------------------------|

| 1 | 1 | 0 | 0 | С     | Auxiliary CIO 1                       |

| 1 | 1 | 0 | 1 | D     | Auxiliary Temperature mux             |

|   |   |   |   | E – F | reserved for auxiliary devices        |

#### Local Analog to Digital Converter:

The local A/D converter is an MC14442 and a REF02 voltage reference. It is used to measure the temperature on the Service Processor (i.e. the cardcage) and the 6 voltages present on the SPM (i.e. +5V main, +5V aux., +12V main, +12V aux., -12V main, and -12V aux.).

Local CIO:

The local CIO is a Zilog 8036, it is used for various timing functions including the CSS bus timeout and the main System clock interrupt.

Auxiliary Z-Bus Peripherals

The Auxiliary Z-bus peripherals are covered as part of the Real World Interface board (see separate spec)

Real Time Clock:

The real time clock is a MK48T12 chip. This chip has a built in crystal oscillator and a lithium battery. In addition to a real time clock, it has 2K bytes of nonvolatile RAM. This RAM can be used to keep configuration information. The service processor does not have any switches.

Clock Control:

The Clock control port is a single bit port which is written with data bit 0. Data.00 = 0 means the CPU is using its onboard 10 MHz clock, Data.00 = 1 means the CPU is using the CSS bus clock divided by two as its clock source. When switching from one clock source to the other, approximately 1 us after the write to the clock control port, the hardware will issue a reset to the CPU, hold the reset for approximately 500 us, and switch clocks during the reset. This is required to meet the timing specifications of the 68020. In the process, the entire board will be reset, so any VLSI chips will have to be reinitialized. The memory, however, will keep its data valid. If the main power is turned on, the state of the clock bit (i.e. which clock is being used)

can be read in the status register. If the CSS bus clock is not running (e.g. the CSS bus is powered down), the hardware will not select the CSS clock. If the CSS bus clock is selected and fails, the clock select mechanism will switch to the local clock.

Status and Control Registers:

There are 3 Status registers and 3 control registers. The status registers are read by the CPU, and the control registers are written by the CPU. When the Status/Control is selected (Add.31 = 0 and Add.27 to Add.24 = 7), Add.07 to Add.05 are further decoded as follows:

Add.07 06 05

|   | 0<br>0<br>1 | 0<br>1<br>0 | 0<br>2<br>4 | Read<br>Read<br>Read | Write control register 0 readback<br>Write control register 1 readback<br>Write control register 2 readback |

|---|-------------|-------------|-------------|----------------------|-------------------------------------------------------------------------------------------------------------|

|   | 1           | 1           | 6           | Read                 | reserved                                                                                                    |

|   | 0           | 0           | 8           | Read                 | CSS command register                                                                                        |

| 1 | 0           | 1           | А           | Read                 | Status register                                                                                             |

|   | 1           |             |             | Read                 | CSS Error information register                                                                              |

| 1 | 1           | 1           | Ε           | Read                 | Dispatcher Error Register                                                                                   |

| 0 | 0           | 0           | 0           | Write                | Write control register 0                                                                                    |

| 0 | 0           | 1           | 2           | Write                | Write control register 1                                                                                    |

| 0 | 1           | 0           | 4           | Write                |                                                                                                             |

|   |             |             |             | Write                | reserved for other control bits                                                                             |

## CSS Command Register:

The CSS command register is a 32 bit register which allows the local CPU to read the value written to the SPM via a CSS write to address 0xXXXX AAYY by any other CSS module. X are don"t care and AA will be captured by the SPM and can be read in the Status register. YY must be of the form 100X XXXX. The SPM only decodes the top three bits of the least significant byte of CSS address. When another module writes to an address of the form described above on the SPM, the 68020 receives an interrupt informing it that CSS command has been received. The 68020 will read the CSS command register and the status register to determine the data of the command.

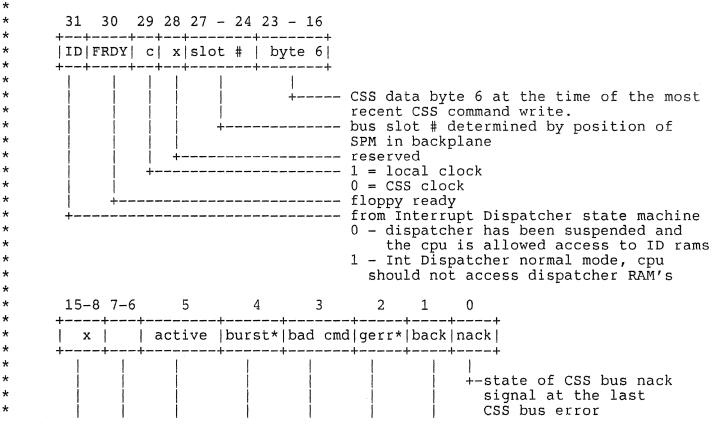

# Status Register:

The Status register is a 32 bit register, data bits 00 to 31 can be read by the 68020. The bits mean the following:

| data.00<br>data.01 |      | CSS bus nak at last CSS error (active high)<br>CSS bus ack at last CSS error (active high)                                                                         |

|--------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| data.02            | -    | CSS bus granterror at last CSS error (active low)                                                                                                                  |

| data.03            | =    | Protocol violation (if = 1, there is<br>a violation, e. g. bad parity or illegal<br>type, if = 0, there is no violation, but<br>another error, e. g. missing ack.) |

| data.04            | =    | reserved                                                                                                                                                           |

| data.05            | =    | CSS bus active at last CSS error                                                                                                                                   |

| data.06 to (       | )7 = | reserved                                                                                                                                                           |

| data.08 to 1       | L5 = | CSS data byte 6 at last CSS command write                                                                                                                          |

| data.16 to | 19 = | Source slot of the originator of the last<br>CSS command write                                                                                                                                                                                                       |

|------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| data.20 to | 23 = | reserved                                                                                                                                                                                                                                                             |

| data.24 to | 27 = | The SPM's own slot id as read from the backplane                                                                                                                                                                                                                     |

| data.28    | =    | Idle full. If 0, indicates that the dispatcher idle queue is full.                                                                                                                                                                                                   |

| data.29    | =    | <pre>status of clock (if = 1, clock is local,<br/>if = 0, clock is CSS clock divided by 2)</pre>                                                                                                                                                                     |

| data.30    | =    | Floppy ready (active low)                                                                                                                                                                                                                                            |

| data.31    | =    | CPU dispatcher access allowed (if = 0,<br>the interrupt dispatcher has suspended its<br>dispatching function and the CPU is allowed<br>to access the interrupt dispatcher RAMs. If<br>= 1, the dispatcher is running normally and<br>cannot be accessed by the CPU.) |

# CSS Error information register:

When the SPM detects an error on the CSS bus, the hardware will interrupt the 68020. The 68020 will read the CSS error information register to determine the nature of the error. The conditions which cause such an error are: bad data parity, bad type parity, destination error, source error, invalid type, bus nack, or granterror. All error conditions will latch in valid data for the CSS error information register as follows:

| data.00 to 07 | = bus data parity 0 to / (bit $x = 0$ means     |

|---------------|-------------------------------------------------|

|               | parity error on byte x)                         |

| data.08 to 13 | = bus type 0 to 5                               |

|               | <pre>= source error (bit = 1 means error)</pre> |

| data.15       | = destination error (bit = 1 means error)       |

|               | = bus source 0 to 3                             |

|               | = bus destination 0 to 3                        |

|               | <pre>= bus type parity (bit = 0 is error)</pre> |

| data.25 to 26 |                                                 |

| data.27 to 31 | = CSS data bits $57$ and $40$ to $43$ .         |

Additional error information is captured in the Status register (see above). When a bus error condition has been latched in the error register, no new error conditions can be latched until after the bus error register has been read by the 68020.

## Dispatcher Error Register:

When the Interrupt Dispatcher detects an error, it will suspend its operation and latch error information in this register. This register is a 32 bit register with the meaning of the bits as follows:

data.00 to 06 I/O bus source slot (only valid if

|                                         |      | data.07 = 1, don't care otherwise)                                                                                                                                                           |

|-----------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| data.07                                 |      | I/O bus interrupt. When this bit is a 1,<br>the interrupt came from an I/O bus module<br>attached to the CSS bus module. If this<br>bit is a 0, the interrupt came from a<br>CSS bus module. |

| data.08 to                              | o 11 | CSS bus source slot                                                                                                                                                                          |

| data.12 to                              | o 15 | CSS bus destination slot                                                                                                                                                                     |

| data.16 to                              | o 17 | Interrupt Priority                                                                                                                                                                           |

| data.18 to                              | o 19 | reserved                                                                                                                                                                                     |

| data.20 to                              | o 22 | error code:                                                                                                                                                                                  |

| 22 21 20                                | 0    |                                                                                                                                                                                              |

|                                         | 1    | reserved for hardware failure<br>Interrupt acknowledge received without<br>pending interrupt                                                                                                 |

| 0 1 0                                   | 0    | Request error (timeout or error on attempted<br>Interrupt level request)                                                                                                                     |

| 0 1 3                                   | 1    | Receive error (new interrupt arrived, but queue is full)                                                                                                                                     |

| 1 0 0                                   |      | reserved for hardware failure                                                                                                                                                                |

|                                         | 1    | Interrupt acknowlegde response error (timeout or error on attempted acknowledge response)                                                                                                    |

| 1 1                                     |      | same as 010.                                                                                                                                                                                 |

| $\begin{array}{ccc}1&1\\1&1\end{array}$ |      | same as 011.                                                                                                                                                                                 |

| data.23                                 |      | Directed Interrupt.                                                                                                                                                                          |

|                                         |      |                                                                                                                                                                                              |

data.24 to 31 Interrupt Vector number

When the Dispatcher detects an error, it will assert a level 1 autovector interrupt at the 68020. The interrupt service routine must assert the cpu.disp.req\* bit to gain access to the dispatcher, remove the cause of the error, and reenable the dispacher by deasserting the cpu.disp.req\* bit. Removing the cause is recommended as follows:

| ving the cause is recommended as forrows:       |

|-------------------------------------------------|

| error code recommended action                   |

| 001 assert, then deassert forc.res.ack*.        |

| 010 or 110 identify the intended target of the  |

| error interrupt and remove this slot            |

| number from the CFIG RAM. Examine the           |

| pointers for directed interrupts pending        |

| for this slot number and compute their          |

| difference. Decrement the counters for          |

| these directed interrupts by these differences. |

| Set the pointers to be equal. This has          |

| the effect of flushing all directed interrupts  |

| pending for the target on which the attmpted    |

| request failed.                                 |

| 104000 101100.                                  |

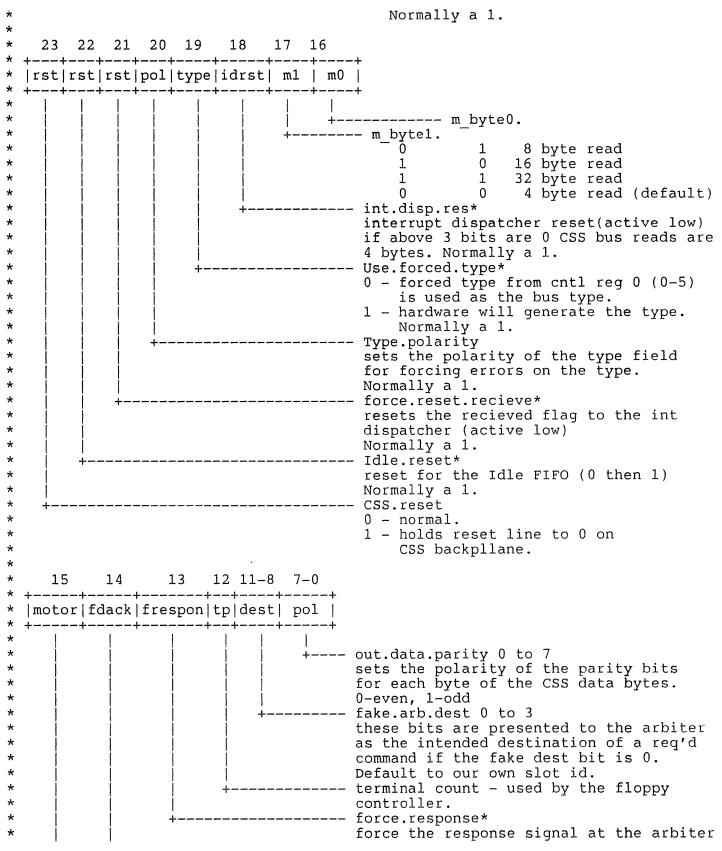

011 or 111 assert, then deassert forc.res.recv\*. Write Control Register 0: The Control register 0 is a 32 bit register with the meaning of the bits as follows: data.00 to 05 = Forced type (this is used instead of the hardware generated type, if Use.forced.type is active (see control register 1)). data.06 to 07 = forced address bits 00 and 01. When 'use.forced.type' is active, these two bits are used as the low address bits (CSS data bits 70 and 71). data.08 to 11 = slot id for use of the interrupt dispatcher. data.12 to 15 = slot id for use of the CSS backplane .(This is the value which is used as the SPMs slot id for comparison with the destination of a CSS bus command from another module. if the destination address on the bus matches this field, the SPM will assume that it is being adressed). data.16 to 19 = out.src 0 to 3. This is the source id which the SPM will use as the source when it is issueing a command on the CSS bus. data.20 to 23 = out.src 0 to 3\*. This is the complement of the source id. (It is separately settable in order to facilitate the forcing of errors). data.24 = forc.ack.nak\*, when asserted (=0), forces a single (50ns) occurrence of busack, if diag.any.type is false (=1) or a single occurrence of busnack, if diag.any.type is true = forc.grant.err\*, when asserted (=0), forces a data.25 single occurrence of granterr. This and the preceeding signal are edge sensitive; i.e. the true going (transition form 1 to 0) edge causes the descibed action. = forc.bad.dest\*, when asserted, forces a mismatch data.26 between dest(0...3) and dest(0...3)\* on any CSS bus access. data.27 = freeze = 1 and css.res.ready\* = 1 together cause the bus.freeze\* to be true (=0). = inhibit\*, when asserted (=0), causes the CSS data.28 bus error capturing to be inhibited. data.29 to 31 = reserved Write Control Register 1: Write Control Register 1 is a 32 bit register with the meaning of the bits as follows: data.00 to 07 = out data.parity 0 to 7. These bits set the polarity of the parity bits for each byte of the CSS data bytes. (0 = parity even, 1 = parityodd. This is used to force data parity errors). data.08 to 11 = fake.arb.dest 0 to 3. These bits are presented to the arbiter as the intended destination of a requested command if the use.fake.dest\* bit

|               |   | is on (= 0).                                                                                |

|---------------|---|---------------------------------------------------------------------------------------------|

| data.12       | = | terminal count - used by the floppy controller.                                             |

| data.13       | = | force.response*. this bit is used to force                                                  |

|               |   | the response signal at the arbiter when                                                     |

| ,             |   | arbiter request is asserted. It is used for                                                 |

|               |   | memory emulation.                                                                           |

| data.14       | = | fdack*. used by the floppy controller.                                                      |

| data.15       | = | floppy.motor*. Used by the floppy controller.<br>These two bits are used to indicate to the |

| data.16 to 17 | = |                                                                                             |

|               |   | hardware what type of reads are to be done<br>when the CSS bus is selected for a read.      |

|               |   | data.17 16 CSS reads performed:                                                             |

|               |   | 0  0  4  byte                                                                               |

|               |   | 0 1 8 byte                                                                                  |

|               |   | 1 0 16 byte                                                                                 |

|               |   | 1 	 1 	 32 	 byte                                                                           |

| data.18       | = | int.disp.res*. This signal, when asserted,                                                  |

|               |   | resets the interrupt dispatcher, if the                                                     |

|               |   | CSS bus clock is active.                                                                    |

| data.19       |   | Use.forced.type*. When this bit is a 0, the                                                 |

|               |   | forced type from control register 0, bits 0 to                                              |

|               |   | 5 is used as the bus type. If the bit is 1,                                                 |

|               |   | the hardware will generate the bus type                                                     |

|               |   | according to the access being performed. (This                                              |

|               |   | bit must be 1 for proper operation of the                                                   |

| 1-1-20        |   | interrupt dispatcher).                                                                      |

| data.20       | = | Type.polarity. This bit sets the polarity of the type field (normally = 1).                 |

| data.21       |   | force.reset.receive*. This bit resets the                                                   |

| uaca.21       |   | received flag to the interrupt dispatcher.                                                  |

|               |   | It must be used when the dispatcher has caused                                              |

|               |   | an error during the reception of an interrupt.                                              |

| data.22       | = | Idle.reset*. This is the reset for the Idle                                                 |

|               |   | FIFO. It must be written with a 0, then a 1,                                                |

|               |   | for proper operation of the interrupt                                                       |

|               |   | dispatcher. It can be used during operation                                                 |

|               |   | of the dispatcher, if the CPU wishes to clear                                               |

|               |   | the idle FIFO.                                                                              |

| data.23       | = | CSS.reset*. This bit, when 0, holds the reset                                               |

|               |   | line on the CSS backplane at 0. It must be                                                  |

|               |   | asserted (= 0) during main power up, and = 1                                                |

| data.24       |   | during normal operation. cpu.disp.req*. When 0, this bit indicates to the                   |

| uala.24       |   | interrupt dispatcher statemachine that the 6802(                                            |

|               |   | wishes to access the dispatcher RAMs. The state                                             |

|               |   | machine will suspend normal dispatcher operatior                                            |

|               |   | and turn on (set = 0) bit 31 in the status                                                  |

|               |   | register. When 1, the interrupt dispatcher                                                  |

|               |   | resumes its dispatching function.                                                           |

| data.25       | = | diag.frc.int.rec*. When 0, this bit indicates                                               |

|               |   | to the hardware that it is to decode a CSS CPU                                              |

|               |   | interrupt request level as a CSS command and                                                |

|               |   | treat it as such. This bit is used for                                                      |

|               |   | diagnosing the interrupt dispatcher only, it                                                |

|               |   | is normally = 1.                                                                            |

| data.26       | = | diag.any.type*. When 0, this bit indicates to                                               |

|               |   |                                                                                             |

| the hardware that it is to accept any CSS bus   |

|-------------------------------------------------|

| action as a valid response to a SPM initiated   |

| read request. It is only used for diagnostic    |

| purposes and is normally = 1. If there is a     |

| response, the response data will be latched     |

| in the CSS command register and the CSS command |

| interrupt will be asserted.                     |

| = use fake dest*. When this bit is 0, the       |

- data.27 = use.fake.dest\*. When this bit is 0, the destination at the arbiter is forced to be bits 08 to 11 of control register 1. If this bit is a 1, the destination at the arbiter is the same as the destination which will be used on the CSS bus with the requested CSS bus transaction. This bit is normally 1.

- data.28 = force.modify\*. When 0, this bit forces a modify

cycle on the CSS bus as long as it is asserted

(= 0). This bit is normally 1.

- data.29 = cpu.res.ready\*. This bit resets all pals associated with CSS activity. It also resets the ready count. If asserted (=0), all CSS interrupt sources are disabled. It is recommended, that this bit be = 0, when switching to the CSS clock.

- = cpu.inc.ready\*. This bit increments the ready data.30 count in the arbiter for the SPM. It must be used after the SPM receives a CSS command addressed to it which caused a 68020 interrupt to increment the ready count for the SPM. The SPM only has a single register for receiving commands, so the ready count is either 0 or 1. This bit and the cpu.res.ready\* are eqde sensitive, i.e. a transition from a 1 to a 0 causes the assertion of the corresponding bit on the arbiter for one CSS bus cycle. A transition from a 0 to a 1 has no effect. data.31 = forc.res.ack\*. This bit is used with dispatcher error handling, see above.

Write Control Register 2

This is a 8 bit register writeable with data bits 24 to 31. Their meaning is as follows: data.24 = prom.at.1. When 0, the EPROM is located at starting address 0x0000 0000. When this bit is 1, the EPROM starting address is 0x0100 0000. data.25 to 26 = promsiz.0 and promsiz.1. These two bits are used to indicate the size of the EPROM chips to be used: 0 = EPROMs are 27256s (32k x 8) 0 = EPROMs are 27512s (64k x 8)  $1 \ 0 = EPROMs \ are \ 27010s \ (128k \ x \ 8)$ 1 = reserved - do not use.data.27 to 30 = LED.0 to LED.3. When a bit is 0, the LED is on, when the bit is 1, the LED is off. LED.0, 2, and 3 are red, LED.1 is green. = bd.reset\*. When 0 this bit holds the hardware data.31 of the SPM, with the exception of the 68020

in reset. On power up or when the 68020 has been reset, this bit will be 0. To allow operation of the board, the CPU must write this bit with a 1.

## Map RAM:

The map RAM consists of two 16 x 4 RAM chips which are used as an 8 x 8 RAM. It is addressed with address bits add.28 to 30. When address bit add.31 = 1, the SPM is performing a CSS access, and the map RAM is read. CPU Address bits 28 to 30 select one of eight locations in the map RAM. The top four bits of the map RAM output give the destination (i.e. the slot id of the board being accessed) and the bottom four bits are mapped to address bits bus data 44 to bus data 47 for the CSS bus. The lower 28 bits of the 68020s address are directly mapped to address bits bus\_data\_40 to 43 and bus\_data\_50 to 77 in the conventional manner. The map RAM is written when add.31 = 0 and add.24 to 27 = 8.

It is written with data.24 to 31 at the location selected by add.28, 29, and 30. Before accessing the CSS bus, the 68020 must initialize the map RAM.

# Floppy Disc Controller:

The floppy disc controller is a WD37C65 single chip controller. It controls a single 5 1/4 in floppy drive.

#### Interrupt Dispatcher CPU Access:

The CPU has four decoded address ranges for accessing the various RAMs present in the interrupt dispatcher. This allows the CPU to initialize the interrupt dispatcher and full diagnostic capabitily for analyzing any dispatcher malfunctions.

## Interrupt Dispatcher Idle Queue:

This is a 16 deep by 4 wide FIFO. It is written with data bits 24 to 27. If there are valid data in the Idle FIFO, the interrupt dispatcher will consider the data slot ids of CPUs which are preferred to receive the next interrupt request. When an interrupt is requested from the CPU corresponding to the first entry on the FIFO, that entry is taken off the FIFO. The SPMs 68020 will normally use this FIFO to indicate to the interrupt dispatcher, which CSS CPUs are idle.

#### Interrupt Dispatcher Queue:

The main queue is a 4k x 32 bit RAM which contains all the information attached to an interrupt as it is defined on the CSS bus (see the interrupt dispatcher description for details). It is adressed with add.02 to 13. It does not need to be intialized, however it is recommended that it is initialized with a known value for diagnostic reasons.

#### Interrupt Dispatcher Pointer:

There are two pointer RAMs, each 256 x 7 bits, called the incoming pointer RAM and the outgoing pointer RAM. These pointer RAMs allow the main queue to function as multiple FIFOs. The pointer RAMs are accessed together with add.02 to 09. Data.24 to 30 are for the incoming pointer, data.16 to 22 for the outgoing pointer. The ponters must be initialized in such a way that at all address locations, the incoming pointer equals the outgoing pointer (e.g. all 0).

Interrupt Dispatcher Miscellaneous RAMs:

There are three other RAMs in the interrupt dispatcher, they are the counter RAM, the service pending RAM, and the CPU configuration RAM. They are all simultaneously addressed as a 32 bit port, with different data bits going to the different RAMs as follows:

| name      | size    | address  | data     |

|-----------|---------|----------|----------|

| counter   | 8 x 10  | 02 to 04 | 00 to 09 |

| serv.pend | 128 x 1 | 02 to 08 | 15       |

| config.   | 16 x 5  | 02 to 05 | 24 to 28 |

The counter must be initialized to all 1s, the service pending must be initialized to all 0s, and the configuration RAM must be initialized with all slot ids of CPUs present in the CSS backplane which are available for receiving interrupts as follows:

| addı | cess |    |     | data | a (24 | to | 27) | data.28 |

|------|------|----|-----|------|-------|----|-----|---------|

| CPU  | slot | id | n   | CPU  | slot  | id | 1   | Х       |

| CPU  | slot | id | 1   | CPU  | slot  | id | 2   | Х       |

|      | •    |    |     |      | •     |    |     |         |

| CPU  | slot | id | n-1 | Cpu  | slot  | id | n   | Х       |

|      | n+1  |    |     | CPU  | slot  | id | 1   | Х       |

|      | •    |    |     |      | •     |    |     |         |

|      | 16   |    |     | CPU  | slot  | id | 1   | Х       |

X = 1 means the CPU slot number at this address can be the target of any interrupt, X = 0 means the CPU slot number at this address must be the Service Module itself.

# Interrupt Dispatcher:

The action of dispatching an interrupt consists basically of three parts:

1.) Receive an interrupt request. The interrupting device issues a CSS write to address FFFF FFA0 on the SPM.

2.) Request a CPU interrupt service. The SPM issues a CSS write to a CSS CPU at address FFFF FFFC with data = xyxx xxxx where x = don't care and y = 1ppp where ppp is the requested CPU interrupt priority level.

3.) Acknowledge an interrupt. The requested CSS CPU issues a read to the SPM at address FFFF FFYY where YY = 00pp p100 where ppp is the CPU interrupt priority level which is acknowledged. The SPM responds to the read with the interrupt data corresponding to the interrupt pending at the priority level which is being acknowledged.

## General Description:

The Interrupt dispatcher hardware consists of the following:

Incoming interrupt register (32 bits)

Pointer RAM (two 256 x 8 RAMs with latches and +1 adders for pointing into the main queue RAM and over- and underflow comparators (full and empty indicators)).

Main queue RAM (2 2k x 32 RAMs, one for up to 22 queues of length 64 for 2 levels of directed interrupts for up to 11 CPUs, one for 4 queues of length 128 for 4 levels of nondirected interrupts.

Interrupts present counter RAM (8 x 10 RAM keeps a count of the number of interrupts present at each interrupt level). Attached to it is a latch with a priority encoder which indicates the level of the highest priority interrupt present.

Interrupt service request state machine

CPU configuration RAM (16 x 5 RAM initialized by 68020 with all CPUs physically present at initial power up or reset)

Service pending RAM (128 x 1 RAM. Only up to 66 bits are actually used, one for each of 6 CPU levels one for each of up to 11 CPUs).

Interrupt information register (32 bits to be read by CPU in response to an Interrupt acknowlege read request).

## Functional Description:

1.) Receive an Interrupt Request.

When an Interrupt request(CSS write to address FFFF FFA0) is received by the SPM, the interrupt information is written to the incoming register. If the incoming register is full, the SPM will be not ready and therefore will not be issued any CSS writes. The receive logic will look at the CSS priority level, the directed/nondirected bit, and if directed, the CPU number, select the appropriate queue in the main queue RAM, and if the pointer RAM indicates not full, write the interrupt information into the main queue RAM into the proper queue. It will increment the incoming pointers in the pointer RAM and the count in the proper location in the counter RAM. The proper queue in the main queue RAM is selected by the CSS interrupt priority level (2 bits) and the CPU number (4 bits) and the Directed/Nondirected bit.

2.) Request a CPU Interrupt Service.

The Interrupt service request state machine will cycle thru the CPU numbers given by the CPU configuration RAM. At each CPU number, it will look at the output of the interrupt present indicator. If the highest interrupt present is a CPU level 5 or 6 (a directed interrupt) it will access the pointer RAM to determine if this level 5 or 6 is pending for this CPU number. If yes, it will attempt to issue the service request (see below). If this level 5 or 6 is pending for a different CPU the state machine will disable CPU levels 5 and 6 from the interrupt present indicator priority encoder and determine which is the highest CPU level interrupt present from CPU levels 4 and below. If there is one present, it will attempt to issue the service request. Attempting the service request means the state machine will access the Service pending RAM with the CPU interrupt level and the CPU number and test the service pending bit. if the bit is already set, an interrupt service is already pending at that CPU level on that CPU and no further service requests can be made. In this case, no service request will be made and the state machine will look at the next CPU number. If the bit is reset, no service request is pending, the bit will be set and the service request will be issued to the given CPU (write to FFFF FFFC with the level as data). The appropriate location in the counter RAM will be written with the decremented number of interrupts present at that level, and the level latch will be written. After issueing the service request, the state machine will look at the next CPU number.

3.) Acknowledge an interrupt.

When the SPM receives an interrupt acknowledge read request, the acknowledge logic will access the service pending RAM with the acknowledging CPU number and CPU level and reset the service pending bit. Using the CPU number and level information it accesses the main queue RAM, and latches the interrupt information into the interrupt information register ready to send to the acknowledging CPU. It will also increment the outgoing pointers in the pointer RAM.

## Arbitration

All three processes will access most of the elements of the dispatch

logic. It is therefore necessary to arbitrate among the three functions of the interrupt dispatcher. At any time, there can only be one of acknowledge response or interrupt request pending, because both of these actions are caused by a CSS bus transaction from another CSS bus board. The SPM will be not ready until the condition has been taken care of. Normally, the CPU service request state machine will always be running, attempting to request service for any interrupts which are present in the SPM. When one of the above functions is requested, the state machine will complete its current CPU service request attempt and then allow the requested function (ack response or interrupt request).

Timing

All timings assume a 50ns bus clock.

To receive an interrupt request into the incoming register takes one bus cycle (50ns). To receive an interrupt request into the main queue RAM takes 5 bus cycles (250ns).

The Service request state machine runs at 1 x bus cycle (50ns/tick). The following are projections based on a preliminary version of the state machine code and are subject to change: If there are interrupts present at all CPU levels in the main queue RAM, an interrupt service can be requested every 6 ticks (300ns). This is the maximum rate at which interrupt service can be requested. Since interrupt requests need to be received, and service requests need to be acknowledged, this rate can only be sustained for short bursts. The maximum sustained rate is one interrupt dispatched every 800ns (250ns to receive the request, 300ns to request service, 250ns to respond to the acknowledge)

The longest delay occurs when there is only one directed interrupt present in the main queue RAM and no other interrupts present. It takes 300ns x (n-1) + 300ns max., where n is the number of CPUs in the system, that is 3.3us for an 11 CPU system. It will take 300ns x (n-1/2) + 300ns average, or 1.8us for an 11 CPU system.

The acknowledge response takes 250ns (5 bus cycles).

All these times, if they are taken for a single transaction, must have the typical CSS bus latency added to it (150ns when there is no other bus traffic).

#### Clock Interrupts

The SPM is the source for system wide clock interrupts. Every 20ms, an interrupt will be requested from each CPU. This will be done by the SPM with a directed interrupt request for the given CPU via a interrupt request write to the SPM itself.

CSS Bus Access:

CSS Bus Commands by other Modules Addressed to the SPM:

For the purpose of recognizing and responding to CSS bus commands, the SPM decodes only three CSS bus address bits, bus.data75, 76, and 77. They are decoded as follows:

| bus.data.77 | 76 | 75 | read/wr | recognized                           |

|-------------|----|----|---------|--------------------------------------|

| 0           | 0  | 0  | write   | Command Register                     |

| 0           | 1  | 0  | -       | -                                    |

| -           | 1  | 1  |         | -<br>Interrupt Deguest (Dispetatory) |

| 0           | 1  | T  | write   | Interrupt Request (Dispatcher)       |

| 1           | 0  | 0  | read    | Interrupt Acknowledge (Dispatcher)   |

| 1           | 0  | 1  | -       | -                                    |

| 1           | 1  | 0  | -       | -                                    |

| 1           | 1  | 1  | write   | Interrupt Vector                     |

| 1           | 1  | 1  | read    | Status Register (Board ID only)      |

The Command Register is a general purpose 32 bit register which can be written by any other module. When this register is written by another module, the SPMs 68020 is interrupted. In response to such an interrupt, the 68020 will read the Command register, and force an increment ready count to the CSS bus arbiter.

The Interrupt Request Register is a 32 bit register. It is the input register for the interrupt dispatcher. Any other module may write to this register. When another module writes to the Interrupt Request Register, the hardware sets a bit to indicate to the dispatcher statemachine that an interrupt has been requested. The dispatcher will read the register into the appropriate queue and increment ready for the CSS bus arbiter. The meaning of the bits in the Interrupt Request Register is as follows:

| bus.data.00 to 07 | Interrupt Vector number                                                                                                                                                              |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bus.data.10 to 11 | Interrupt Priority                                                                                                                                                                   |

| bus.data.12 to 16 | reserved                                                                                                                                                                             |

| bus.data.17       | Directed Interrupt. When this bit is on,<br>the interrupt must be sent to the<br>specified destination slot. If this bit<br>is off, the interrupt may be sent to any<br>CSS bus CPU. |

| bus.data.20 to 23 | CSS bus source slot                                                                                                                                                                  |

| bus.data.24 to 27 | CSS bus destination slot (only used if<br>bus.data.17 = 1, ignored otherwise)                                                                                                        |

| bus.data.30 to 36 | 1/O bus source slot (only used if<br>bus.data.37 = 1, ignored otherwise)                                                                                                             |

| bus.data.37       | I/O bus interrupt. When this bit is a 1,                                                                                                                                             |

the interrupt came from an I/O bus module attached to the CSS bus module. If this bit is a 0, the interrupt came from a CSS bus module.

The Interrupt Acknowledge location is a range of addresses which can be read by any other CSS bus module. It is normally used by a CSS bus processing module after it has reveived an interrupt level request to acknowledge this request. Address bits bus.data.72 to 74 are further decoded to determine the interrupt level which is being acknowledged:

| bus.data.74 | 73 | 72 | acknowledge level |

|-------------|----|----|-------------------|

| •           | •  | •  |                   |

| 0           | 0  | 0  | -                 |

| 0           | 0  | 1  | 1                 |

| 0           | 1  | 0  | 2                 |

| 0           | 1  | 1  | 3                 |

| 1           | 0  | 0  | 4                 |

| 1           | 0  | 1  | 5                 |

| 1           | 1  | 0  | 6                 |

| 1           | 1  | 1  | -                 |

When a read to the Interrupt Acknowledge location is received, a bit is set for the dispatcher state machine and it will read the interrupt information from the appropriate queue and respond to the read with this information in the format given above. It will also take other actions to indicate to itself that this interrupt has been acknowledged. If a CSS bus module reads an interrupt acknowledge location without having first received an interrupt level request, this will disrupt the normal function of the interrupt dispatcher. This should be done for diagnostic purposes only.

The Interrupt Vector Register is not a physical register. In normal mode, a CSS write to this location causes a level 3 auto vector. For diagnostic purposes only, this is a feature which allows the SPMs 68020 to test the function of the interrupt dispatcher. (See the description of the diag.frc.int.rec\* bit in the Control register 1 for more).

The Status Register allows any other CSS bus module to read the SPMs board id.

CSS Bus Commands Initiated by the SPM:

There are two sources of SPM initiated CSS bus commands, the interrupt dispatcher and the SPMs 68020.

The interrupt dispatcher can initiate CSS writes and CSS read responses. When the dispatcher wishes to request an interrupt level, it will request the CSS bus for a write. The format of this write is as outlined above.

The SPMs CPU can initiate CSS read requests and CSS writes as well as any other CSS command including invalid commands. Normal reads and

writes, e.g. to a memory module, are transparent to the SPMs CPU. It needs only to select the system bus (address bit 31 = 1) and the map RAM will map the high order address bits as descibed above. The low order address bits are used directly. All CSS bus writes are one or 2 or 3 or 4 byte writes. The type field is automatically encoded from the size field of the 68020. All CSS bus reads are 4 or 8 or 16 or 32 byte reads. If none of the 8.byte, 16.byte, or 32.byte read bits are set in the control register, the normal default CSS bus read is a 4 byte read. If one of the control bits is set, the all CSS bus reads intitiated while the bit is set will be of the length given by the bit. For example if the 32.byte.read bit is set, a read by the SPMs 68020 - of necessity 4 bytes - with address bits 2, 3, and 4 = 0,will cause a 32 byte CSS bus read. The next 7 reads by the 68020, if not all of address bits 2, 3, and 4 are 0, are assumed to be part of the 32 byte CSS bus read and will give the data obtained during the 32 byte read response back to the 68020 in the order given by the address bits 2, 3, and 4. The 16.byte and 8.byte CSS reads operate in a similar manner. To do CSS bus accesses other than reads or writes, the SPM can set the CSS type field directly. See the forced type field in control register 0 and the Use.forced.type bit in control register 1. While the Use.forced.type bit is asserted (=0), any CSS bus access will use the forced type as the CSS bus type.

68020 Interrupt Levels

There are 7 interrupt levels on the 68020. The processor on the Service Module uses 6 of them as follows:

| Level | 1 | = | Interrupt Dispatcher Error     | Auto vector         |

|-------|---|---|--------------------------------|---------------------|

| Level | 2 | = | CSS Bus Command Write          | Auto vector         |

| Level | 3 | = | CSS Interrupt received         | Auto vector         |

| Level | 4 | = | Local Timer (CIO)              | Programmable vector |

| Level | 5 | = | Real World Interface Interrupt | Programmable vector |

| Level | 6 | = | Floppy Controller              | Auto vector         |

| Level | 7 | = | CSS Bus Error                  | Auto vector         |

## LEDs

There are 10 LEDs on the front panel of the Service Module The meaning of the LEDs is as follows:

LED 1) (red) Software LED 0. Udes as fault indicator

LED 2) (green) Software LED 1. Used as go indicator.

LED 3) (red) Software LED 2. Uncomitted.

LED 4) (red) Software LED 3. Uncomitted.

LED 5) (red) 68020 Address Strobe.

LED 6) (red) CSS Bus Active.

LED 7) (red) CSS Clock present.

LED 8) (red) Interrupt present in Dispatcher not yet dispatched

LED 9) (red) Interrupt present in Dispatcher not yet dispatched and interrupt pending on same level for the same Interrupt target (PM).

LED 10) (red) CSS bus Ready.

APPENDIX 1:

Translation table for CSS data bits to local address and data bits:

,

|      | CSS                                          |      | local                                                                                |

|------|----------------------------------------------|------|--------------------------------------------------------------------------------------|

| byte | bit                                          | byte | bit                                                                                  |

| 0    | 00<br>01<br>02<br>03<br>04<br>05<br>06<br>07 | 0    | data 24<br>data 25<br>data 26<br>data 27<br>data 28<br>data 29<br>data 30<br>data 31 |

| 1    | 10<br>11<br>12<br>13<br>14<br>15<br>16<br>17 | 1    | data 16<br>data 17<br>data 18<br>data 19<br>data 20<br>data 21<br>data 22<br>data 23 |

| 2    | 20<br>21<br>22<br>23<br>24<br>25<br>26<br>27 | 2    | data 08<br>data 09<br>data 10<br>data 11<br>data 22<br>data 23<br>data 24<br>data 25 |

| 3    | 30<br>31<br>32<br>33<br>34<br>35<br>36<br>37 | 3    | data 00<br>data 01<br>data 02<br>data 03<br>data 04<br>data 05<br>data 06<br>data 07 |

|      | 40<br>41                                     |      | addr 24<br>addr 25                                                                   |

| 4 | 42<br>43<br>44<br>45<br>46<br>47             | 0 | addr 26<br>addr 27<br>addr 28<br>addr 29<br>addr 30<br>addr 31                       |

|---|----------------------------------------------|---|--------------------------------------------------------------------------------------|

| 5 | 50<br>51<br>52<br>53<br>54<br>55<br>56<br>57 | 1 | addr 16<br>addr 17<br>addr 18<br>addr 19<br>addr 20<br>addr 21<br>addr 22<br>addr 23 |

| 6 | 60<br>61<br>62<br>63<br>64<br>65<br>66<br>67 | 2 | addr 08<br>addr 09<br>addr 10<br>addr 11<br>addr 12<br>addr 13<br>addr 14<br>addr 15 |

| 7 | 70<br>71<br>72<br>73<br>74<br>75<br>76<br>77 | 3 | addr 00<br>addr 01<br>addr 02<br>addr 03<br>addr 04<br>addr 05<br>addr 06<br>addr 07 |

| /*                | ·*************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                  |                  |                        |             |             |             |             |             |             |             |             |             | *           |             |             |             |             |             |             |             |             |                |                      |                                           |                                                       |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|------------------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|----------------|----------------------|-------------------------------------------|-------------------------------------------------------|--|

| *                 | Service Processor Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                  |                  |                        |             |             |             |             |             |             |             |             |             |             |             |             |             |             |             |             |             |             |                |                      |                                           |                                                       |  |

| * * * *           | <ul> <li>The Service Processor Module (SPM) attaches to the system bus and</li> <li>provides various service functions for the system. These functions</li> <li>include system console interfaces, front panel interface, real time</li> <li>clock, system clock interrupt service, power supply controls, floppy</li> </ul>                                                                                                                                                                                                                                                                                                                                                                       |                  |                  |                        |             |             |             |             |             |             |             |             |             |             |             |             |             |             |             |             |             |             |                |                      |                                           |                                                       |  |

| * * * * * * * * * | disk controller, system wide interrupt dispatcher, various system<br>monitor functions (power, temperature), and system diagnostic capabil-<br>ities. The SPM consists of two boards, the main board which plugs into the CSS<br>bus backplane, and the real world interface board which contains all<br>connectors for the serial ports, the power supply control connectors,<br>and the temperature sensor connectors. The real world interface board<br>is connected to the main board via a third 96pin din connector at the<br>bottom of the main board. The real world interface board resides behind<br>the CSS backplane in the interface slot behind the Service Processor<br>Main board. |                  |                  |                        |             |             |             |             |             |             |             |             |             |             | ./          |             |             |             |             |             |             |             |                |                      |                                           |                                                       |  |

| *<br>**           | `*************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                  |                  |                        |             |             |             |             |             |             |             |             |             |             |             |             |             |             |             |             |             |             |                |                      |                                           |                                                       |  |

| *<br>*_           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |                  | -                      |             |             |             |             |             |             |             |             |             |             |             |             |             |             |             |             |             |             |                |                      |                                           |                                                       |  |

| * *               | 0<br>0<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | x<br>x<br>x      | x<br>x<br>x      | x<br>x<br>x            | 0<br>0<br>0 | 0<br>0<br>1 | 0<br>1<br>1 | 0<br>1<br>1 | 0<br>1<br>1 | 0<br>1<br>1 | 0<br>1<br>1 | 0<br>1<br>1 | 00<br>11<br>11 | 0000<br>1111<br>1111 | 0000<br>1111<br>1111                      | Eprom<br>- 512k <<br>- 1M                             |  |

| *<br>*<br>*       | 0<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | x<br>x           | x<br>x           | x<br>x                 | 0<br>0      | 0<br>0      | 0<br>0      | 0<br>0      | 0<br>1      | 0<br>1      | 0<br>1      | 0<br>1      | 0<br>1      | 0<br>1      | 1<br>1      | 0<br>1      | 00<br>11       | 0000<br>1111         | 0000                                      | Spare                                                 |  |

| *<br>*            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | (<br>x           | )x(<br>x         | )10(<br>)103<br>x<br>x | 3ff<br>0    | 113<br>0    | E<br>O      | 1<br>1      | 0<br>0      | 0<br>0      | 0<br>0      | 0<br>0      | 0<br>0      | 0<br>0      | 0<br>1      | 00<br>11       | 0000<br>1111         | 0000<br>1111                              | Sram (256k)                                           |  |

| *                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | х                | x<br>x           | х                      | 0<br>0      |             |             |             |             |             |             |             |             |             |             |             |             |             |             |             |             |             |                | 0000<br>1111         |                                           | Spare                                                 |  |

| *<br>*<br>*       | 0<br>0<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | x<br>x<br>x      | x<br>x<br>x      | x<br>x                 | 0<br>0      | 0<br>0      |             | 0           | 0           | 0           |             | 0           | 0           | 0<br>0<br>0 | 0           | 0           | 0           | 0           | 0           |             | 0           | 0           | 01             | 0000                 | 0000                                      | reserved<br>local A/D conv<br>local CIO               |  |

| *<br>*            | 0<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | x<br>x           | х                | x<br>x                 | 0           | 0           |             |             |             |             |             |             |             | 0<br>0      |             |             |             |             |             | 0<br>0      |             |             |                |                      |                                           | reserved for<br>local devices                         |  |

| * * *             | 0<br>0<br>0<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | x<br>x<br>x<br>x | x<br>x<br>x<br>x | x<br>x                 | 0<br>0<br>0 | 0<br>0<br>0 | 1<br>1      | 0<br>0      | 0<br>0      | 0<br>0      | 0<br>0      |             | 0<br>0      | 1<br>1      | 0<br>0      | 01<br>10       | 0000<br>0000         | $\begin{array}{c} 0000\\ 0000\end{array}$ | aux. SCC 0<br>aux. SCC 1<br>aux. CIO<br>aux. A/D conv |  |

| * 0<br>* 0<br>*                                                    | х                                                                       | х                                                                            | x                                                                  | 0                                       | 0                                                   |             |                                                     |                            |                                 | 0<br>0                          |                            |                                                | 0<br>0                     |                            |                                 |                                                | 0<br>0      |                                         | 0<br>0                                              | 1<br>1                                    | 1<br>1                                  | 00<br>11                                           | 0000<br>0000                                                         | 0000<br>0000                                                         | reserved for<br>aux. devices                                                                                                                                                                  |

|--------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------|-----------------------------------------------------|-------------|-----------------------------------------------------|----------------------------|---------------------------------|---------------------------------|----------------------------|------------------------------------------------|----------------------------|----------------------------|---------------------------------|------------------------------------------------|-------------|-----------------------------------------|-----------------------------------------------------|-------------------------------------------|-----------------------------------------|----------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|