# microelectronics

FIRST, SECOND, AND FUTURE GENERATIONS

## The Story of Microelectronics...

## First, second, and future generations

by M. S. Parks

COPYRIGHT 1966 North American Aviation, Inc.

North American Aviation Anaheim, California

PUBLICATION NO. P3-75/317 PRINTED IN U.S.A.

#### Credits

All text and Appendices I and III were written by Martha Smith Parks; Appendices II, IV and V are from previously published Autonetics documents. The following made special contributions to the production of the book: David Kirby, art direction; Kenneth Hodges, cover design; and George Johnson, photography.

#### A cknowledgments

The author expresses appreciation for the valuable time and helpful suggestions given during interviews with many knowledgeable members of Autonetics' technical and management staff, including: J. W. Adkison, H. Almond, D. B. Anderson, K. D. Anderson, H. E. Allen, P. L. Anthony, Dr. H. Bender, Dr. C. E. Bergman, R. Berman, R. K. Booher, J. Boros, Dr. G. V. Browning, R. F. Burns, F. L. Chiaretta, H. D. Childers, W. V. Conover, J. V. Cross, D. G. Cummings, W. F. DeBoice, J. G. Doidge, P. H. Eisenberg, C. H. Fa, Dr. G. Galli, J. R. Gibbard, W. E. Grant, J. D. Guttenplan, P. J. Hagon, W. H. Hammers, J. E. Hill, E. F. Hogan, J. R. Howell, H. F. Jones, L. G. Karagianis, C. V. Kovac, T. J. LaChapelle, Dr. J. J. Licari, A. C. Lowell, Dr. L. L. Lowry, A. H. Marshall, Dr. H. C. Mattraw, J. W. McMurray, D. Medellin, Dr. T. Mitsutomi, C. D. Morris, Dr. F. L. Morritz, C. H. Petersen, R. C. Platzek, Dr. G. R. Pulliam, L. E. Reid, S. D. Robertson, D. D. Robinson, G. M. Sallus, H. S. Scheffler, T. K. Shuler, J. W. Slemmons, G. H. Smith, R. J. Theibert, B. Van Houten, J. E. Varga, and B. M. Wade.

The author is especially indebted to the engineers and scientists who made rigorous technical checks of particular portions of this book: two tables, "Typical Micro-Resistor Characteristics" and "Typical Micro-Capacitor Characteristics," J. E. Varga; chart, "A Typical Appraisal of Microelectronics Techniques for a 1-Megacycle Computer," A. C. Lowell; dielectric isolation, T. J. LaChapelle; microelectronics joining, J. W. Slemmons; Central Microelectronics Laboratory activities, F. Jones; multilayer boards evolution, J. Boros and P. L. Anthony; Appendix I, F. L. Chiaretta, G. Galli, and T. J. LaChapelle; and Appendix III, P. H. Eisenberg.

### Contents

| P | a | a | e |

|---|---|---|---|

| * | a | 9 | C |

| The Best Compromise for the Best System                         | . 2   |

|-----------------------------------------------------------------|-------|

| Reliability, Maintainability, Availability                      | . 3   |

| Physical Advantages of Microelectronics                         | . 6   |

| How It All Began: The Search for Increasing Smallness           | . 6   |

| First-Generation Microelectronics                               | . 10  |

| Digital Applications                                            | . 13  |

| Radio-Frequency Applications                                    | . 13  |

| Linear Applications                                             | . 14  |

| Second-Generation Microelectronics                              | . 17  |

| MOS Technology                                                  | . 17  |

| Improvements to First-Generation Devices and Their Packaging    | . 20  |

| Joining                                                         | 23    |

| A Major Microelectronic Systems Organization                    |       |

| and What It Is Doing Today                                      | . 26  |

| Researcher                                                      | . 27  |

| Developer                                                       | . 33  |

| Designer                                                        | . 43  |

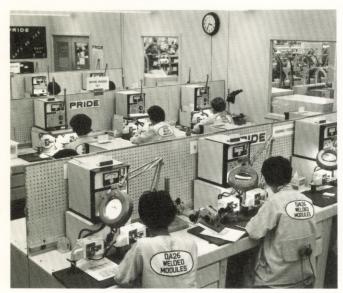

| Producer                                                        | . 51  |

| Purchaser                                                       | . 73  |

| User                                                            | . 79  |

| A Glimpse at the Future                                         | . 86  |

| Some Autonetics Breakthroughs                                   | . 86  |

| Special Devices                                                 | . 90  |

| Interconnection and Packaging                                   | . 93  |

| Conclusion                                                      | . 96  |

| Appendix I. How Semiconductors and Semiconductor Devices "Work" | . 97  |

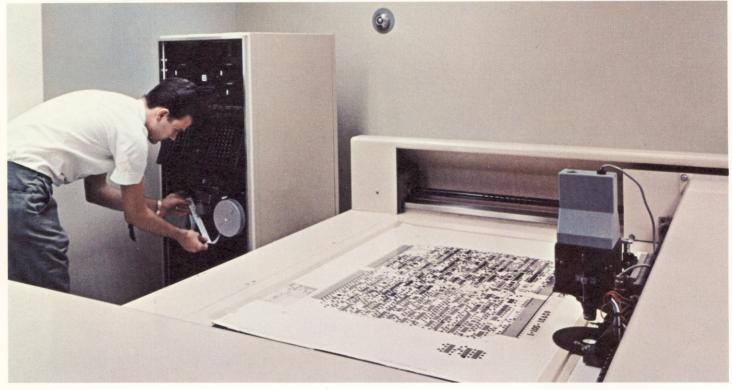

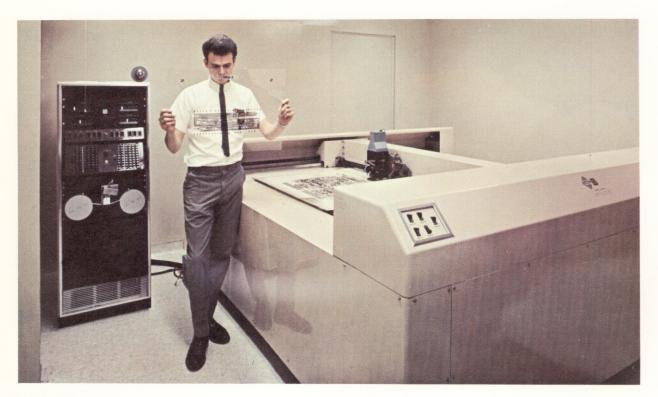

| Appendix II. Automated MOS Mask Preparation                     | . 105 |

| Appendix III. Components Reliability Assurance                  | . 109 |

| Appendix IV. Available Autonetics Technical Publications        |       |

| on Microelectronics                                             |       |

| Appendix V. Microelectronics Glossary                           | . 123 |

## The Story of Microelectronics... First, second, and future generations

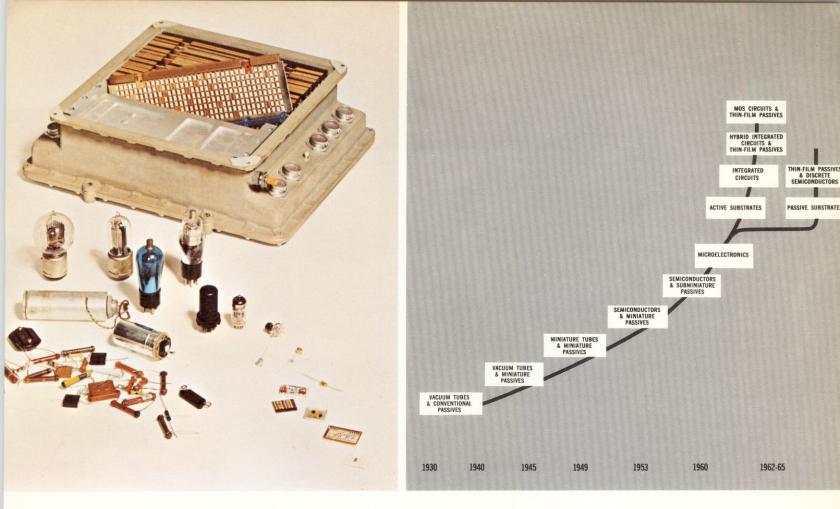

Microelectronics is looked upon as a revolutionary technology that has literally exploded on the scientific horizon. Actually, microelectronics' history has been one of evolution, rather than revolution, and this "sudden" technology has been increasingly with us over a period of more than 30 years ... presently acknowledged benefits to systems reliability, performance, and economy are the hard-won culmination of three decades of effort by dedicated scientists and engineers.

Evolution of microelectronics, from its early beginnings to the present, makes a stimulating story. Developments and improvements still evolving from the laboratories are even more exciting. Projection of the continuing evolution into the future promises startling and profitable new marvels. ☐ Microelectronics is generally hailed as answer to all electronic users' prayers. Galloping in on its attractive white stallion—cost effectiveness—this technological prodigy promises everything to everybody. But the question is, does it keep its promises? ☐ Whether or not it does in each case, depends upon many interrelated factors. But for the majority of applications—for defense, industry, and space microelectronics deserves all the praise and consideration one can give it.

$\Box$  In modern military avionics, for example, microelectronics is increasingly indispensable. A prime instance is its contribution to the control center of most airborne systems — the digital computer — with its numerous functions, such as navigation, fire control, display control, performance monitoring, autopilot steering, automatic radar control, air data processing, pre-mission checkout, communications control, and fuel management. This functional complexity, ever on the increase, *demands* smaller, lighter-weight, vastly more reliable means of systems implementation — in other words, microelectronics, unrivalled in all these respects.

□ For commercial aircraft applications, benefits of microelectronics are fast becoming equally essential. In this area, advantages stem from two trends :

1. The first trend is higher speeds, and greater traffic variety and density, requiring much more accurate and responsive air traffic control both by equipment in the aircraft and by equipment on the ground.

In the speed regime of the supersonic transport, both flight-management functions and ground control operations will require an ability to process data at a much higher rate.

2. The second significant trend is toward cheaper and much more reliable electronic equipment—cheaper to produce and cheaper to maintain. Benefits will be compounded for commercial applications, in that reduced costs and increased reliability of the electronic equipment will permit it to be used in places not previously feasible for economic or flight-safety reasons. (For example, it is now practical to consider microelectronics for performance monitoring of most aircraft subsystems, so that more economical maintenance programs can be devised. Correspondingly, increased reliability and reduced size make feasible the use of microelectronic radar, communications equipment, flight controls, and navigation devices coordinated through a central microelectronic computer—which also maintains a continuous check on performance of other elements of the aircraft, as well as of itself.)

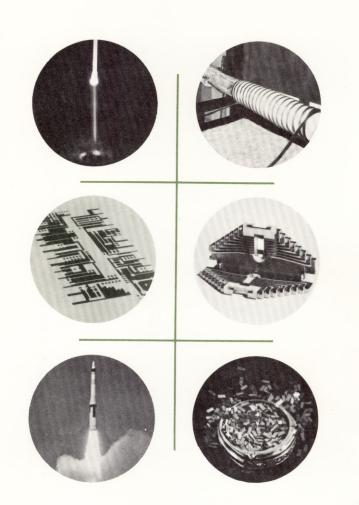

For the long voyages of space, microelectronics' appropriateness is obvious. In space, there is no second chance — no turning around midcourse when an electronic circuit goes bad, no convenient wayside service stations. For space, *reliability must be reliable* — and no other technique offers the inherent reliability of microelectronics. To this vital benefit add the reliability-enhancing potential for redundancy offered by microelectronics, plus the payloadand range-increasing advantages of its light weight, small size, and low power—and the attractiveness of microelectronics is assured.

#### The best compromise for the best system

$\Box$  To plan, or to buy, the best-performing, most reliable system — for the least amount of money the system designer or purchaser must compromise or "trade off" some degree of one desirable feature to arrive at the essential degree of another. The most effective system is eventually reached through a sequence and combination of such "tradeoffs."

$\Box$  In making the important decision of whether or not microelectronics has anything to offer this combination, it is necessary to consider its effect on and by a number of urgent factors:

- Objective How long, how often, in what environment will the system be used?

- Budget and Schedule How much money can you spend, and when do you need the system "ready to run"?

- Reliability If something goes wrong, can you replace it? If something goes wrong, will it be catastrophic to your "Objective"? (The obvious interdependence of this factor with those of "Objective" and "Logistics" dramatically point up the necessity for tradeoff.)

- Logistics How skilled will the available maintenance people be? How much room will you have for spares? How far do spares have to come to reach you from "home base"?

Physical Requirements – How much room will you have for the system? How heavy can you allow it to be? How much power supply will you be able to carry aboard for it? How much heat can you dissipate?

□ With microelectronics, as with any other system parameter, great care must be taken during tradeoffs, not only to *keep the necessary levels* of performance, accuracy, reliability, etc, but equally to *avoid "over-specifying*" too-excellent performance, too-high reliability, or greater accuracy than is actually required for the application. These things all demand the spending of money and, because of tradeoff interdependence, their "over-specification" can make required, interrelated parameters suffer needlessly.

☐ For space, for defense, and for commerce and industry, microelectronics does, indeed, have much to offer. In every case, however, careful thought must be given to whether its benefits outweigh its cost penalty to the program involved. To be truly meaningful, any evaluation of cost effectiveness must include consideration not only of the initial purchase price, but of all the related and subsequent costs... for reliability improvement, personnel training, maintenance operations, and spares.

#### Reliability, maintainability, availability

□ Reliability, maintainability, and availability are so closely interrelated that it is almost impossible to consider them as separate tradeoff factors.

$\Box$  By definition, if a system is *reliable*, it can be relied upon for satisfactory performance and it is, therefore, *available* — when, as often, and for as long as needed. By the same token, if equipment is highly *maintainable*, it is easily and economically kept reliable and available. All three of these interrelated factors of reliability, maintainability, and availability are, in turn, as already stated, closely tied in with total cost effectiveness — compounded not of initial expenditures alone, but of costs throughout the program.

$\Box$  In reliable systems, less maintenance is required. Consequently, logistics costs are greatly reduced. Fewer spares are needed, less elaborate maintenance facilities and equipment are demanded, fewer and less skilled maintenance personnel are required, and less maintenance training is necessary. Again, the result is — increased cost effectiveness.

□ In making the systems tradeoff decision for microelectronics, these factors are all of prime importance, because microelectronics is of uniquely high reliability.

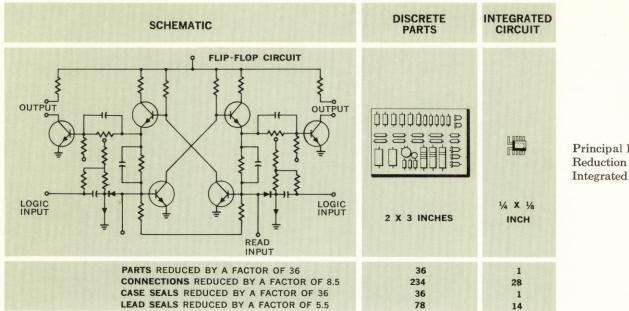

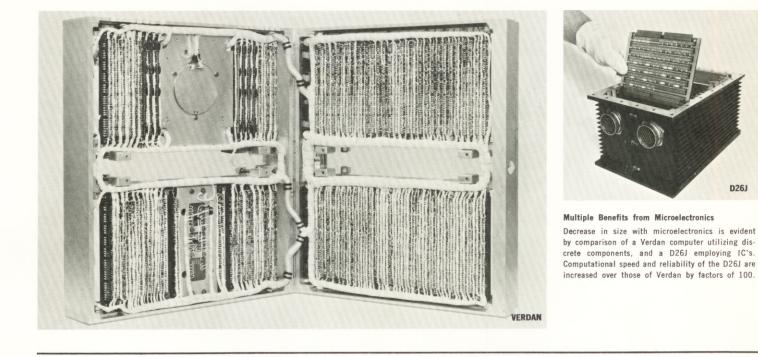

Principal Failure-Mode Reduction with Integrated Circuits

First of all, its inherent reliability is not matched even remotely by that of any other type of circuitry. This fact is graphically illustrated by the accompanying chart, which compares a computer circuit using discrete components, and a functionally identical one using semiconductor integrated circuits (IC's). The chart points up the drastic reduction in failure modes achievable with this particular type of microelectronics; the reliability improvement illustrated is not limited to IC's, however, but is one of the chief advantages of microelectronics, in general. The significant buildup of reliability is reflected in equally significant lowering of maintenance and logistics requirements, with heightened overall system cost effectiveness.

Primary factors in microelectronics' inherent reliability advantage are the smaller number of interconnections it requires, innate resistance to shock and vibration, and often reduced thermal stress.

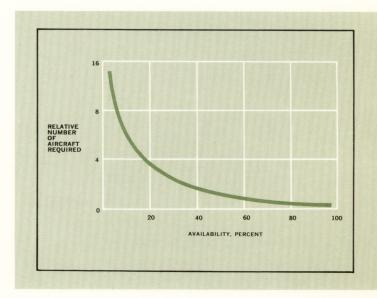

☐ Maintenance is simplified and maintenance costs are lowered by microelectronics' potential for throwaway and replacement of faulty units to the individual circuit level (with promising new developments, even to the subsystem level). □ Availability is also enhanced by microelectronics. (Military aircraft are taken as an example here, although the same kind of thinking applies to any major air- or space-borne system operation.) The fewer aircraft required for a given mission, the lower the total cost-of-ownership. Microelectronics can lower the number of aircraft required per mission and, thus, the total cost-of-ownership, in two ways:

Aircraft Availability

☐ First, microelectronics can permit on-board selfcheck and almost immediate replacement of faulty units upon return to base. From an avionics standpoint, this should increase availability of aircraft from present-day figures of 40 to 50 percent to approximately 95 percent; should cut number of aircraft required per mission by approximately one-half; and should bring about savings of billions of defense budget dollars.

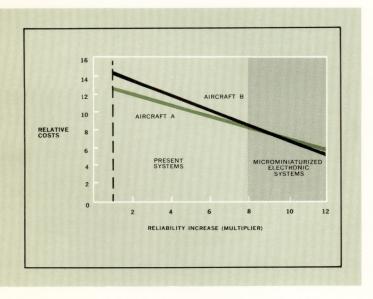

Tactical Aircraft Avionics Maintenance and Operating Costs

Second, microelectronics' benefit of reduced size permits redundancy – with resulting increased reliability and, consequently, reduced number of aircraft required per mission. (Detailed studies of tactical avionic systems indicate probabilities of reliable system operation as high as 0.98 obtainable in future systems with microelectronic equipment.) Two studies of typical aircraft (conducted by the Autonetics Division of North American Aviation, Inc.) have demonstrated how significantly microelectronics can reduce total cost-of-ownership by increasing reliability of mission success. Results of the studies are plotted in the chart at left, which shows reliability increase vs relative costs of systems maintenance and operation for the two types of aircraft.

□ As the chart indicates, the two studies revealed a common trend, with an approximately 2-to-1 reduction in maintenance and operating costs, and an order-of-magnitude or better increase in reliability with state-of-the-art microelectronics. Cost comparisons are relative numbers on the chart, and data from each study are normalized to cover the same number of aircraft for approximately 10 years.

#### ANCIENT INFANT - THE CRYSTAL DIODE

Batch production processes for high-device-density microelectronics promise lower component costs, with resulting lowered production costs and heightened reliability. These developments will be reflected in less demanding logistics requirements and even greater overall cost effectiveness.

#### Physical advantages of microelectronics

☐ The most obvious offerings of microelectronics are the "physical" ones of small size and light weight. Because of these characteristics, more room is left for fuel and payload. Equipment can be more complex, yielding greater accuracy and/or flexibility for contact with target or achievement of destination. Lighter weight and increased fuel allowance permit significantly longer range. Redundancy made possible through microelectronics' weight and space savings increases reliability, cuts maintenance, raises availability—reduces program costs.

Other physical advantages of microelectronics include reduced power and heat-dissipation requirements, with a resulting elimination of the need for heavy, cumbersome cooling systems and power supplies.

## How it all began: the search for increasing smallness

□ The wonders of microelectronics did not happen overnight, and the story of how these wonders evolved is not only interesting, but provides a background for full understanding of their behavior today and tomorrow.

□ Before World War II and the debut of the airplane as a major defense machine, electronic hardware was mostly land-based, big, and heavy... and its chief requirement, next to meeting widetolerance specs for performance, was for all-weather ruggedness.

□ The most sophisticated airborne electronics was limited to intercoms, communications radio, the simplest of radio compasses, and power supplies for these. To meet the scientific advances of the enemy, however, our Government soon realized the urgent need for electronics progress — and, almost overnight it seemed, there poured from Government and industry laboratories a stream of electronic marvels ... target search-and-track radar, airborne television, missile and drone radio control, radio and radar guidance systems, radio and radar altimeters, and bomb laying and armament control systems.

Billy Mitchell's predictions paled beside the actual burgeoning use of the airplane — and with this acceleration came the need for smaller, lighter electronics — and the need for "miniaturization."

First to feel the impact of miniaturization was the vacuum tube - at the time (early 1940's), the heart, brains, and soul of electronics. Although tubes of consistent performance and versatility had been developed - no vacuum tube was, at the beginning of World War II, sufficiently uncumbersome to meet the new requirements. Manufacturers responded to the new requirements by developing smaller and smaller glass and metal tubes - at first, simply smaller vertical replicas of their predecessors called "miniature" tubes ... later, "subminiature" devices departing from conventional configurations, as with the so-called "acorn tubes," sized and shaped just as their name would indicate. Always, the new tubes were, in function and in basic structure, simply smaller and smaller duplicates of the big tubes they were to replace. Definite limits of design and manufacture obviously restricted the eventual reduction in size achievable by this method.

□ Parallel with the race to shrink vacuum tubes, other components were miniaturized and subminia-

turized — including resistors, capacitors, connectors, inductors, and transformers. Fortunately, frequencies at which the wartime radar, television, and pulse circuits operated were extremely high, and components for these applications were readily compatible with the small-size, low-weight demands of airborne usage.

□ Research went on apace. And, with all the concentrated effort and talent poured into the search for increasing smallness, the embryonic beginnings of true microelectronics were bound to take place and did — with the development of "semiconductor" devices—first, germanium and silicon diodes, soon followed by the transistor.

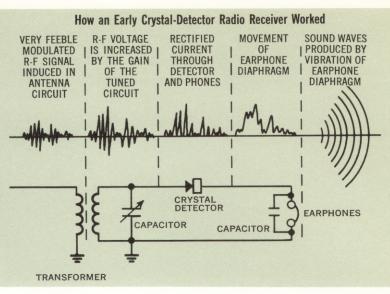

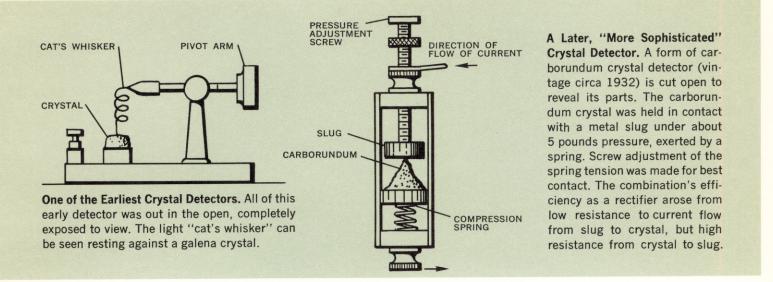

□ Actually, use of semiconductor devices is as old as radio. The "crystal detector" in early wireless sets was a semiconductor unit. The thin wire "cat's whisker" was moved over the semiconductor (carborundum or galena) crystal's surface until it located a "sensitive" spot (i.e., a spot where the conducting and rectifying properties of the crystal were best). A current then flowed through the earphones in proportion to the audio modulation of the signal's radio-frequency carrier, and the operator "heard music."

The "rectifying" property of semiconductors that is, their ability to conduct current better in one direction than in the other – was first extensively exploited in germanium and silicon diodes during the 1940's. Long before that, though – between 1920 and 1930 – copper oxide and selenium rectifiers had come into general use in power supplies, to convert a-c line voltage into d-c voltage to operate vacuum tubes; they were high-power, low-frequency devices, however, and had little or no potentiality for miniaturization. The devices needed were low-power, highfrequency units that could be small in size and low in weight, and that had characteristics compatible with the operating parameters of the pulse and microwave circuitry in widespread use in airborne equipment.

Germanium and silicon diodes were the first practical replacements for vacuum tubes to meet these requirements that were not simply miniature or subminiature replicas of tubes. Capable of being made many times smaller than the smallest vacuum tube, the semiconductor diodes were just as effective, and were inherently more rugged and reliable since they had fewer parts. They had generally a higher ratio of forward to back conductance (and, thus, were better rectifiers), needed no heater (filament) power, operated on lower voltages and so required smaller power supplies, and had longer life than vacuum tube diodes.

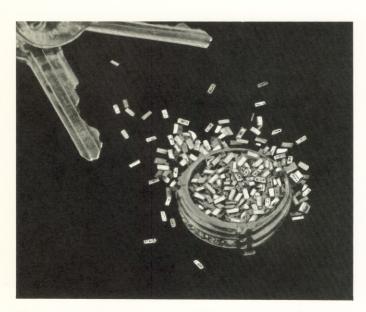

$\Box$  No matter how far reduced in size, vacuum tubes continued to be measured in inches — semiconductor diodes could be fabricated to perform the same functions as vacuum tubes, better and more dependably than vacuum tubes and, at the same time, were no bigger than match heads!

□ When semiconductor triodes—"transistors"—were added to the semiconductor family in the late '40's, they were eagerly welcomed. Transistors offered all the advantages of crystal diodes compared to vacuum tubes. Like the diodes, they were small, compact, and robust; operated with extremely low voltages; needed no cathode or filament heating power; and

**Microelectronics Evolution**

were capable of performing all the functions hitherto performed only by vacuum triodes — except more reliably than the latter.

Certain problems had to be overcome in designing transistor circuits without inherent instability, and in eliminating spurious noise signals which existed in the transistor at a much higher level than in the vacuum tube. Trouble was encountered, too, in producing transistors with uniform characteristics from sample to sample. With time, these problems were all solved to a satisfactory extent, however, and today the transistor replaces all but the highestpower or special-purpose vacuum tubes in airborne applications.

□ With transistors and crystal diodes supplanting their large vacuum tube counterparts, and with the miniaturization of their companions—resistors, capacitors, reactors, transformers, and potentiometers —circuit devices actually took up less space than the wires and cables to interconnect them !

The next innovation was naturally, then, the

printed or etched circuit – with all wiring, except the highest-power leads and cabling, consisting of lines of a conducting metal (copper, gold, silver) deposited on the surface of a "circuit board" fabricated of an insulating material. The terms "printed circuit" and "etched circuit" came from the chemical process used to transfer the interconnecting conductors onto the board. Special miniature connectors were designed for mounting on the boards and for cable terminations, and special flat multiconductor cables were developed for space-saving interconnection between boards. As skill in design and fabrication grew with experience, techniques were developed for depositing, not only wiring between circuit devices, but some of the "passive" devices themselves as integral parts of the circuit-first, resistors and capacitors, then reactors and transformers. Later, "active" elements like transistors were fabricated as integral parts of the monolithic "integrated circuit."

These techniques became "first-generation microelectronics"...

#### First-generation microelectronics

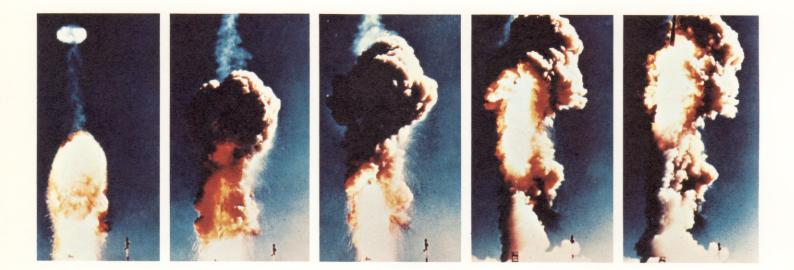

□ "Birth" is usually described as the occasion upon which an entity makes its first appearance in the big, outside world, and actually begins to live. Microelectronics first saw the light of day in many areas of application. For all practical purposes, however, the birth of microelectronics took place with its use throughout Minuteman II in 1962 — for this was the first time microelectronics began to "live" — in its overall mechanization of an entire defense weapon system.

☐ The microelectronics picture changes daily and, today, portions of so-called "second-generation microelectronics" are already fast reaching the operational stage — or birth into the big world outside the laboratory — but first-generation techniques are far from becoming obsolete. Indeed, firstgeneration technology possesses advantages for some applications that will probably never be offset by anything offered by later developments. First-generation microelectronics is in daily, world-wide use for heightened reliability, enhanced performance, lowered cost, smaller volume and weight, and increased range and payload... in the electronic guid-

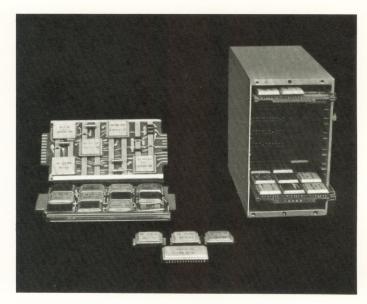

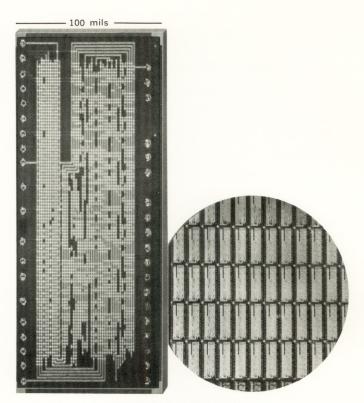

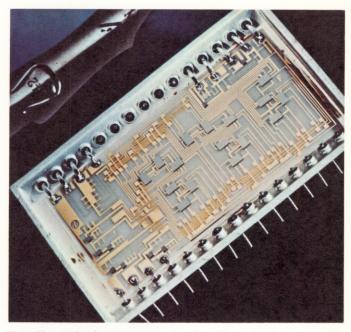

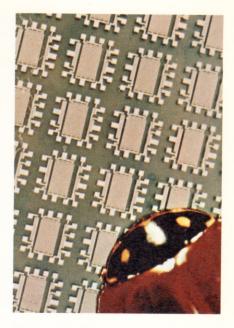

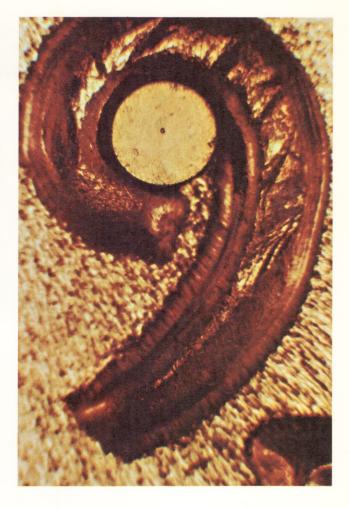

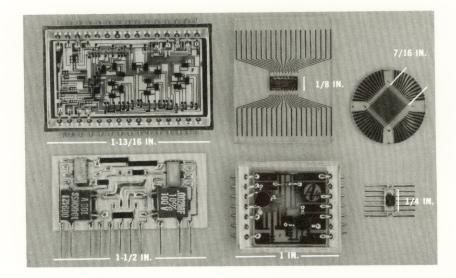

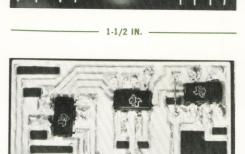

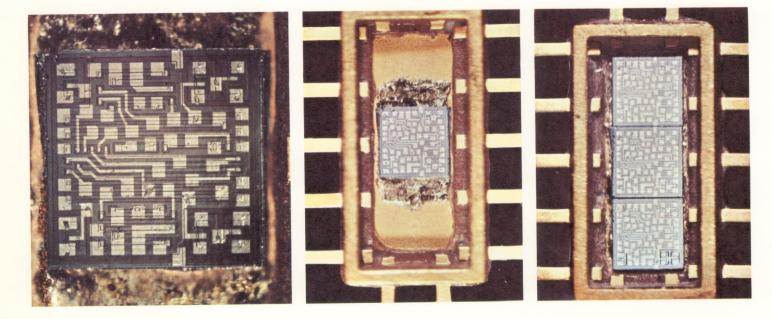

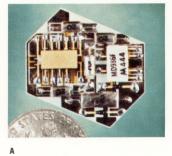

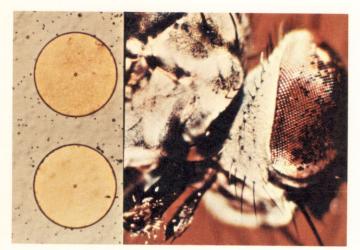

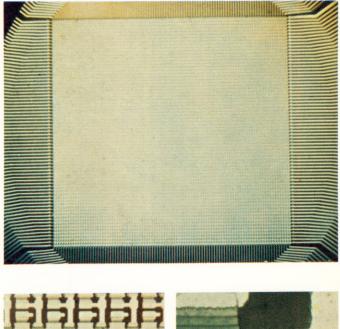

1960: 2000 TRANSISTORS AND CONDUCTORS ON EACH WAFER TO FORM MANY CIRCUITS LIKE THE ONE SHOWN, CENTER, HERE

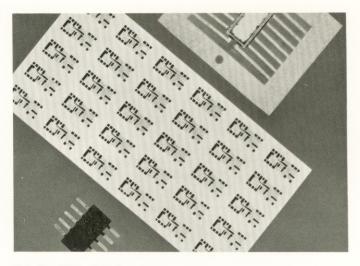

Microelectronics economy has been steadily improved through advances in batch fabrication. Costs are just about the same to process an area of silicon regardless of what kind of, or how many, elements are put on it. One of the first steps in microelectronics cost cutting was taken in the early '60's, when astute manufacturers began to deposit passive elements (conductors and resistors) on the same silicon wafer along with the active diodes and transistors. ance, control, communication, and data-processing systems of industry, science, NASA, the Army, Navy, and Air Force... and will continue to be for quite some time.

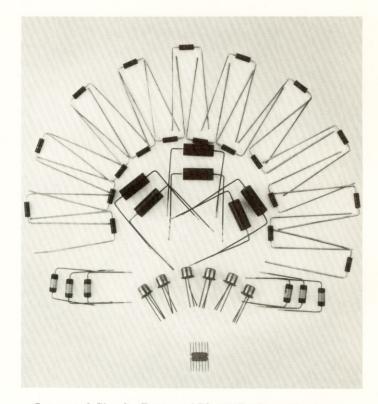

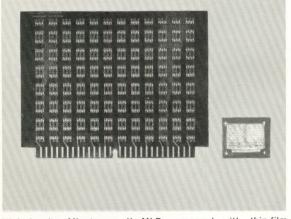

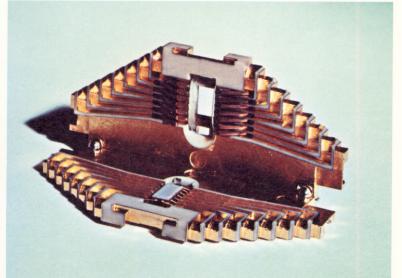

Integrated Circuit (Bottom of Photo) Performs the Same Circuit Function as the 38 Discrete Components Shown Above It

First-generation microelectronics includes – in addition to discrete transistors and diodes, potentiometers, transformers and inductors, subminiature cables and cable connectors, and boards for mounting these and other devices – three basic types of microcircuit technology, classifiable by physical structure and method of fabrication. These are the ceramic printed circuit (CPC) or "thick-film" circuitry; "thin-film" circuitry; and semiconductor integrated circuits (IC's) or, as they are sometimes called, microelectronic integrated circuits (MIC's). These three types are still in widespread use in their original forms and are, also, being brought forth from the laboratories in vastly improved "11/2generation" versions for revamping of present, and development of new, systems.

#### THE TYPES OF FIRST-GENERATION MICROELECTRONICS CLASSIFIED BY "STRUCTURAL" DIFFERENCES

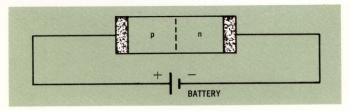

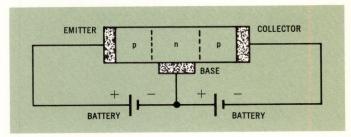

According to basic structure, first-generation microelectronics circuitry is of three types. In one of these — the "integrated" circuit—both active and passive devices are formed by diffusing small amounts of chemicals with certain electrical characteristics down *into* a block of "host" material. In a second type — resistors, capacitors, and conductors are formed by depositing chemical materials *onto* the surface of a substrate to form a "thin-film" circuit. The third type also employs a substrate, but resistors and conductors only are screened onto its surface, and all other devices are discrete; this type of microelectronics is the "thick-film" or "ceramic printed" circuit.

#### **Semiconductor Integrated Circuits**

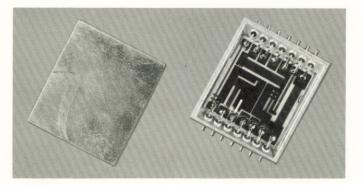

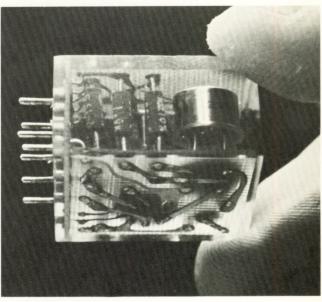

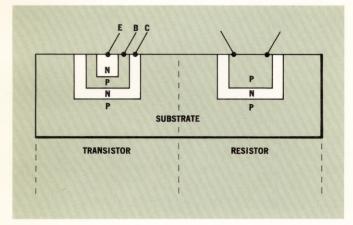

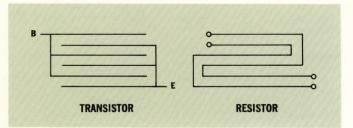

In the fabrication of integrated circuits (IC's)—transistors, resistors, diodes and other devices are diffused into a minute block of semiconductor material.

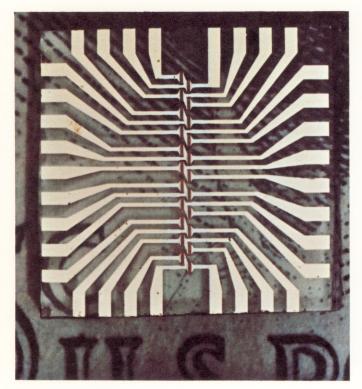

Interconnections of the diffused electronic component parts are made by vacuum depositing metal on an insulating oxide coating over the semiconductor surface. Then, by etching, the metal layer is formed into a pattern of conductors as required, to complete the circuit.

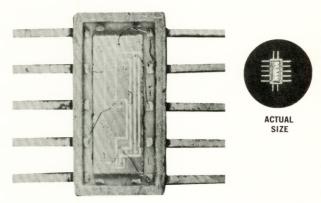

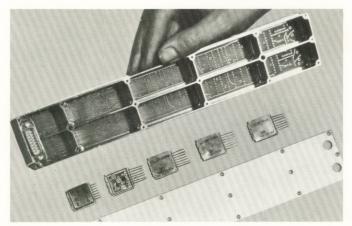

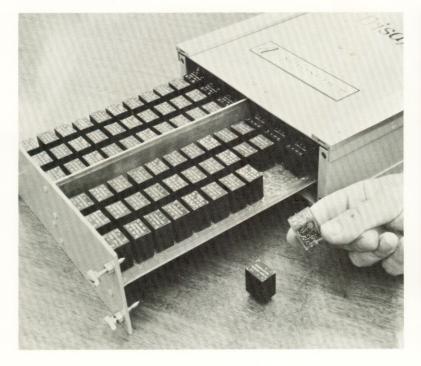

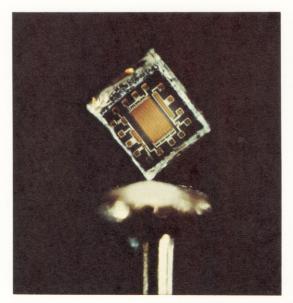

Many identical and separate circuits are formed in a single IC semiconductor wafer. The wafer is cut into individual chips—one circuit per chip—and each chip is mounted in a package. Terminals leading outside the package are attached, and the package is sealed.

The technology of "hybrid" integrated circuit packaging is also important in microelectronics. With this technique, individual chips of silicon are attached to a single header and interconnected by wire bonding, as opposed to the monolithic structure in which all of the devices are dif-

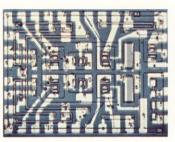

#### **Thin-Film Circuits**

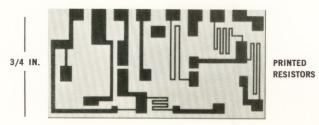

In one of the two major types of "thin-film" process — the "photo-etch" process — thin layers of resistive and conductive materials are chemically deposited on a ceramic or glass substrate. Unwanted portions of the overlays are then etched away by a photo process, leaving a film which forms a complex network of resistors and conductors. More than 70 resistors — ranging in individual value from 10 ohms to 1 megohm, and with a precision of 0.01% — can be deposited on a single substrate little more than an inch square.

With the "vacuum deposition" thin-film process, resistive and conductive materials are vaporized in a vacuum, then deposited on the substrate through a mask. The resulting pattern forms the conductors and passive components in the circuit. In subsequent operations, insulating layers are deposited on the substrate and covered by additional film to form an interconnected resistor-capacitor network.

fused into a single chip of silicon and interconnected by vapor-deposited metal. The hybrid technique occasionally employs vapor-deposited resistors, but primarily makes use of separate chips of silicon into which are diffused the active and passive devices.

#### Ceramic Printed (Thick-Film) Circuits

One of the earliest forms of microelectronics was the screened or ceramic printed circuit process. With this method, microcircuits are made by a technique adapted from silk screening.

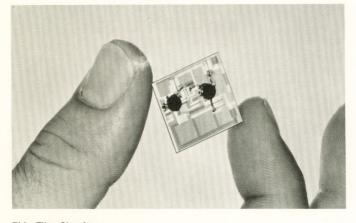

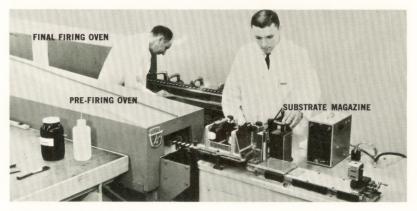

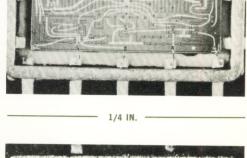

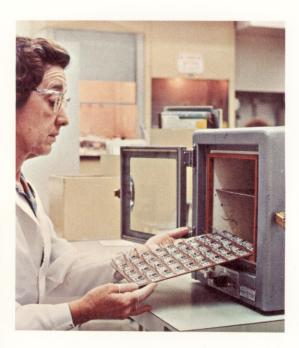

In ceramic printed circuit (CPC) fabrication, the circuit pattern is printed on a high-resolution metal screen. In separate operations, the conductor and resistor materials are pressed through the screen onto a tiny (as small as  $\frac{1}{4}$ -inch square), wafer-thin substrate of alumina or other ceramic.

When both conductor and resistor patterns have been printed, the wafer is placed, first, in a low-temperature oven which dries the pattern, and, then, in a high-temperature furnace which fires the resistor and conductor patterns in place on the substrate. Next, the conductors are dip-soldered, and additional components, such as transistors, diodes, and capacitors, are soldered, welded, or bonded to the substrate. In a final step, the substrate is placed in a special jig and encapsulated.

#### Typical Micro-Resistor Characteristics

| PARAMETER                                                            | MONOLITHIC<br>SILICON<br>DIFFUSED | SILICON<br>ON<br>SAPPHIRE | CHROMIUM               | NICHROME               | TANTALUM                                                            | TIN OXIDE                  | CERMET                 | TITANIUM          |

|----------------------------------------------------------------------|-----------------------------------|---------------------------|------------------------|------------------------|---------------------------------------------------------------------|----------------------------|------------------------|-------------------|

| Sheet resistance,<br>ohms/square                                     | 2.5-300 (4)                       | 2.5-300                   | 300-800 <sup>(7)</sup> | 20-1200 <sup>(5)</sup> | 25-1000 <sup>(16)</sup>                                             | 80-4000 (6)                | 100-50,000             | 5-100 (10, 9, 15) |

| Temperature coefficient of<br>resistance,<br>ppm/degree Centigrade   | 500-2000 <sup>(4)</sup>           | 500-2000                  | 100-600 <sup>(1)</sup> | ±100 <sup>(5)</sup>    | 0-1000 (3)                                                          | 0 to - 1500 <sup>(6)</sup> |                        |                   |

| Power dissipation,<br>milliwatts/mil                                 | 0.01                              | 0.02                      | 0.01                   | 0.01                   | 0.01                                                                | 0.02                       | 0.03 (13)              | 0.01 (15)         |

| Resistance tolerance,<br>percent:<br>As fabricated<br>After trimming | ±10 <sup>(4)</sup>                | ±10                       | 5<br>0.1               | 5<br>< 0.1             | $ \begin{array}{c} \pm 10  {}^{(16)}_{(17)} \\ < 0.1  \end{array} $ | 5 <sup>(6)</sup><br>0.1    | $\pm 15_{(13)}^{(13)}$ | ±10<br>0.1        |

| Resistance ratio tolerance,<br>% before trimming                     | ±3 <sup>(4)</sup>                 | <u>+</u> 3                | 1                      | 1                      | 5                                                                   | 1                          | 5                      | 5                 |

| Distributed capacitance,<br>picofarads/square mil                    | 0.1                               | None                      | None                   | None                   | None                                                                | None                       | None                   | None              |

Typical Micro-Capacitor Characteristics

| PARAMETER                                                           | MONOLITHIC SILICON |                                    | THIN-FILM                                |                                                  |                                |  |

|---------------------------------------------------------------------|--------------------|------------------------------------|------------------------------------------|--------------------------------------------------|--------------------------------|--|

|                                                                     | DIFFUSED           | THERMALLY GROWN<br>SILICON DIOXIDE | SILICON MONOXIDE                         | TANTALUM PENTOXIDE                               | TITANIUM DIOXIDE               |  |

| Capacitance (C),<br>picofarads/square mil                           | 0.2-0.1 (4)        | 0.25-0.4 (4)                       | 0.1(4)                                   | 0.7 (17)                                         | 0.5 <sup>(15)</sup>            |  |

| Working voltage,<br>d-c volts                                       | 6-20 (4)           | 50 <sup>(4)</sup>                  | 50 (14)                                  | 50 <sup>(17)</sup>                               | 25                             |  |

| Dissipation factor:<br>@ 1 kilocycle/sec<br>@ 1 megacycle/sec       | 0.001-0.010 (4)    | 0.001<br>0.7 (4)                   | $0.015_{(12)}^{(12)}\\0.8_{(12)}^{(12)}$ | $0.01_{(12)}^{(17)(12)}\\0.25_{(12)}^{(17)(12)}$ | 0.005 <sup>(15)</sup><br>> 0.2 |  |

| Temperature coefficient of<br>capacitance,<br>ppm/degree Centigrade | 100 (16)           | 30                                 | 110 <sup>(14)</sup>                      | 250 <sup>(17)</sup>                              | 400 (10)                       |  |

| Voltage dependence                                                  | V-1/2 (4)          | None                               | None                                     | None                                             | None                           |  |

| Polarization                                                        | Yes                | None                               | None                                     | None                                             | None                           |  |

| Shunt capacitance,<br>percent of (C)                                | 10-80(4)           | 10-50(4)                           | INTRACONNECTION ONLY                     |                                                  |                                |  |

| Leakage current @ 5 volts,<br>amperes/picofarad                     | 10-9               | 10-9                               | 10-8 (5)                                 | 10-10 (5) (12)                                   | 10-8(15)                       |  |

References (parenthetical superscripts in table refer to reference numbers in following list):

- Belser, R. B. and Hicklin, W. H., Temperature Coefficients of Resistance of Metallic Films in the Temperature Range 25-600 C, J. Applied Physics, <u>30</u>, 313, March 1959

Carroll, W. N., Thin-Film Microcircuit Networks, Proc. of the Agard Conference, Oslo, July 24, 1961

Clark, R. S. and Orr, C. D., Reactively Sputtered Tantalum Resistors and Capacitors for Semiconductor Networks, Proc. 1965 Electronic Components Conference, Washington, May 5, 1965

Dicken, H., Resistors and Capacitors for Integrated Circuits, Motorola Integrated Circuit Design Course, July 1963

Elarde V. D. et al. A New Material: Moldable Precision Coramic

- Elarde, V. D., et al, A New Material: Moldable Precision Ceramic, Proc. 1964 Electronic Components Conference, Washington, May 5 1064

- Proc. 19 5. 1964

- 6. Federal Telephone and Radio Corporation, Reference Data for Radio Engineers, Third Edition

- 7. Fowler, A. O., Aging Characteristics of Vapor Deposited Chromium Film Resistors, Proc. 1963 Electronic Components Conference, Washington, May 7, 1963

- 8. Huber, F., Thin Films of Titanium and Titanium Oxide for Micro-miniaturization, Proc. 1964 Electronic Components Conference, Washington, May 5, 1964

- 9. Keonjian, E., Microelectronics, Theory, Design and Fabrication, McGraw Hill Book Co., 1963, New York

A question often asked of the large-scale aerospace systems designer is: "Why do you use different types of microelectronics in your various equipments? Would it not be much more economical, as well as give the best performance, to decide upon one best type, and then to use that type throughout all your systems and subsystems?" The answer is straightforward: No single type of first-or secondgeneration microelectronics is best for all types of

- Lakshmanan, T. K., et al, Sputtered Titanium Oxide Films for Microcircuit Applications, Proc. 1964 Electronic Components Con-ference, Washington, May 5, 1964

- 11. Madland, G. R. and Kornfeld, W., Thin-Film Components and Technology, Motorola Integrated Circuit Design Course, July 1963

- Nowak, W. B. and O'Conner, J. J., Silicon Oxide Micromodule Capacitors, Proc. 1965 Electronic Components Conference, Wash-ington, May 5, 1965

- 13. Place, T. M. to Varga, J. E., private communication, North Ameri-can Aviation, Inc./Autonetics Division, Anaheim, California, can Aviation, October 1965

- Schenkel, F. W., Thin-Film Capacitor Parameter Studies, Proc. 1964 Electronic Components Conference, Washington, May 5, 1964

- Shockley, W. L., et al, Automatic Sputtering of Tantalum Films for Resistor and Capacitor Fabrication, Proc. 1964 Electronic Components Conference, Washington, May 5, 1964

- Sikina, T., et al, Integrated Tantalum-Silicon Microcircuits, Proc. 1963 Electronics Components Conference, Washington, May 7, 1963

- 17. Stone, H. A., Jr., A System of Tantalum Film Microcircuitry, Proc. of the Agard Conference, Oslo, July 24, 1961

applications. Each offers certain advantages, and each has certain limitations, for the various kinds of using systems. Different microelectronics techniques are employed singly or in combination, to best fulfill the performance, reliability, and cost requirements of each application.

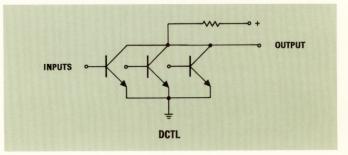

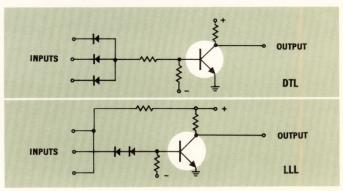

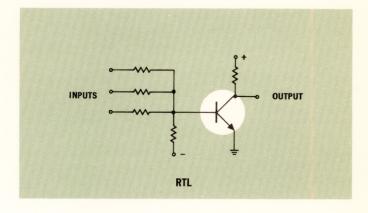

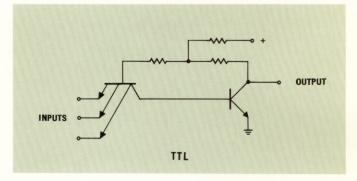

From this standpoint, microelectronics falls, again, into three classifications: digital, radiofrequency, and linear.

#### **Digital Applications**

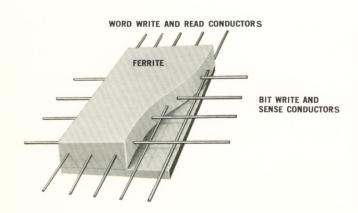

Digital systems include computers and other data processors. Circuit functions in these systems are pulse-driven, on-off operations, and are largely repetitive and low-power. Few capacitors are used, and those employed are small in both electronic (mostly below 2000 picofarads) and physical size. Semiconductor integrated circuits prove ideal for most digital applications.

☐ The major challenge to microelectronics in digital systems has been to devise a method for interconnecting the logic functions. In this type of circuitry, it is typically necessary for each logic element to "look at" a number of other logic elements, with the result that an enormous quantity of interconnecting leads must be provided between elements. The determining factor on the "smallness" of digital microelectronics thus becomes the ability to interconnect in as small a volume as possible. The volume is not limited by the volume of the microelectronic devices themselveswhich, in digital circuitry, are generally low-profile units—but by the board area required to interconnect them adequately. Techniques developed to solve this problem of device interconnection are as ingenious as the microelectronic devices themselves, and require the solving of three-dimensional problems in design. (See "The *Big* Problem of *Little* Room—for Interconnections," page 15.)

#### **Radio-Frequency Applications**

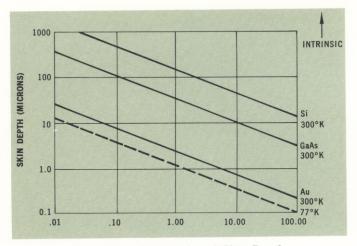

□ In r-f applications (radio, television, and radar systems), capacitors are still mostly less than 2000 picofarads in value and, thus, physically small, but a much larger number of them is needed than in digital applications. Also in contrast to digital systems, r-f microelectronics requires transformers and inductors and, for gain adjustment of the amplifier-type circuitry common to r-f applications, must have provisions for high-precision resistors. Distributed and stray capacitances must be kept to a minimum. To satisfy all these prerequisites, thin-film techniques

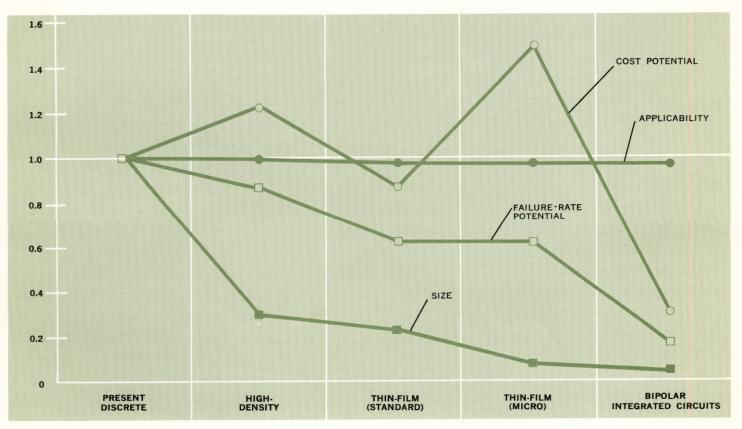

A Typical Appraisal of First-Generation Microelectronics Techniques for a 1-Megacycle Computer

#### IS THERE A "BEST" TYPE OF MICROELECTRONICS?

Not only must microelectronics be traded off as an entity with other system design factors — but, within the technology, tradeoffs must be made with regard to choice of the type of microelectronics best suited for a particular application. In this microelectronics type tradeoff, as in system parameter tradeoff, the factors of performance, cost, producibility, etc, must be weighed to make a final decision.

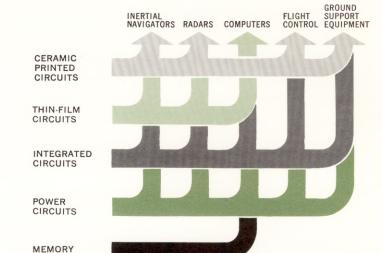

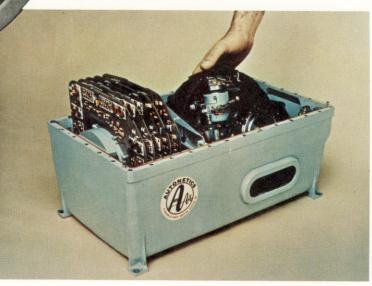

The Autonetics division of North American Aviation, Inc. recognized the feasibility of combining various microelectronics techniques and devices as far back as the late '50's. Continuing development work and actual application since that time has reinforced the conviction that no single approach is best for all kinds of systems. Various techniques are employed, depending upon the performance, reliability, and cost requirements of the system involved. As a multiproduct manufacturer, Autonetics finds applications for all types of microelectronics, using them in a variety of circuitry — both analog and digital — for inertial navigators, radars, computers, flight control, and ground support equipment.

now offer the best solution. To date, integrated circuit technology has not progressed as rapidly in the r-f field as in the digital, because of the difficulty of fabricating high-speed transistors; however, second-generation semiconductor materials, a novel technique for device isolation, and new economical batch-production processes for field-effect devices are solving this problem, and future r-f systems will be able to exploit the many benefits of integrated circuitry.

#### Linear Applications

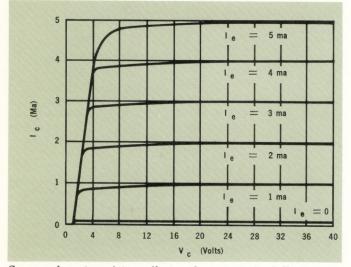

□ Linear circuits are used in those electromechanical control systems (such as systems for navigation and flight control) which interface with transducers such as gyro pickoffs, accelerometers, velocity meters, servo motors, torquing coils, and voice coils. The circuitry often consists of amplifier circuits; frequency of operation covers the range from dc to 100 kc, with 5 kc being typically the highest frequency.

Because of the low frequencies used in linear electronics, capacitors are big both electrically and physically. (Most of the capacitors in a typical set of

#### Autonetics' Systems Usage of Various Microelectronics Techniques:

linear microelectronics are greater than 1000 picofarads.) This electrical size "difficulty" is compounded by the fact that large numbers of the capacitors are required for coupling and bypass functions.

□ The necessity for linear microelectronics to interface with electromechanical transducers requires power levels to be relatively high, and the microelectronics technology employed must provide compatible mounting methods for power-dissipating transistors and resistors.

Despite these problems, semiconductor IC's have been effectively applied to fill about 70 percent of the circuit requirements in typical electromechanical control systems. Standardized semiconductor IC's have been designed for use with adapting circuits employing discrete and thin-film components. Through revisions in system techniques relating to grounding, power supplies, impedance level, and information format, the need for large capacitors and inductive elements has been greatly reduced. The power-dissipation problem is lessened by operating power amplifiers in the highly efficient switching mode.

#### THE BIG PROBLEM OF LITTLE ROOM—FOR INTERCONNECTIONS

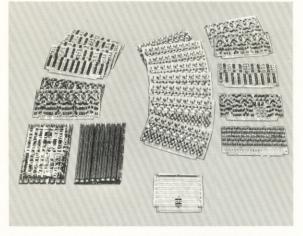

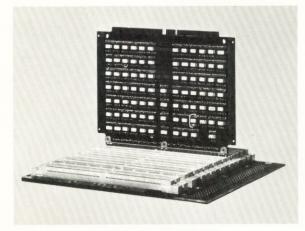

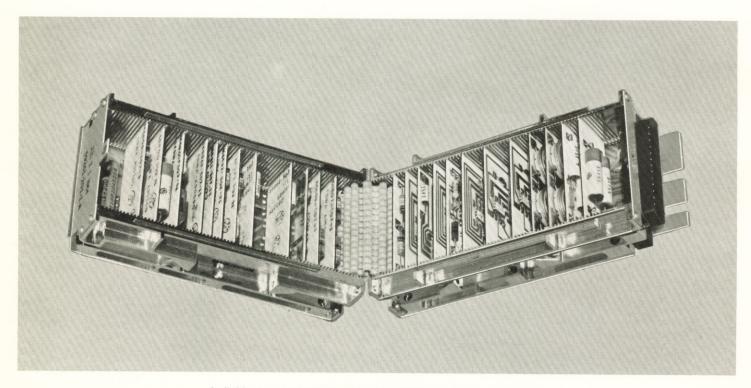

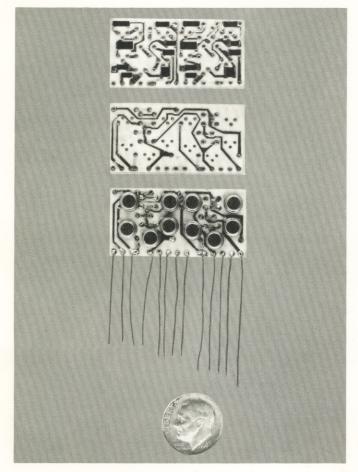

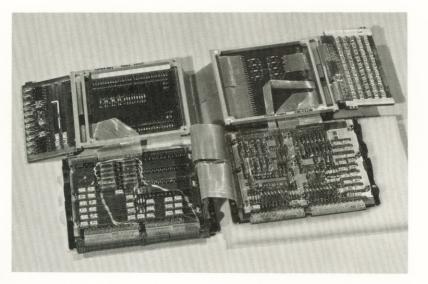

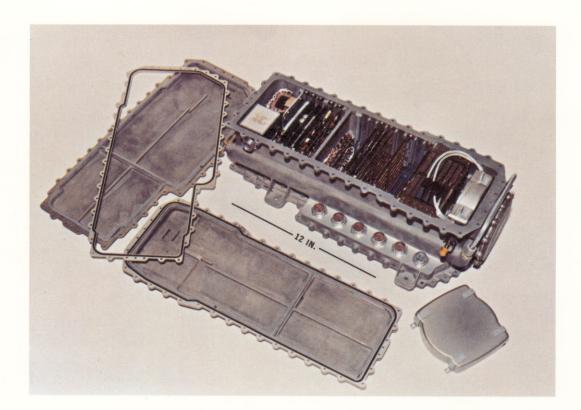

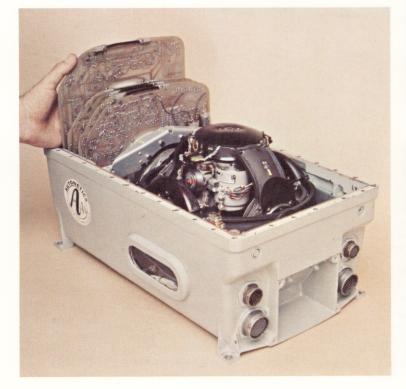

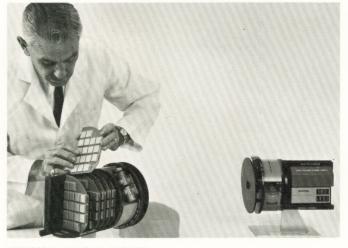

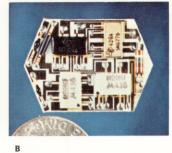

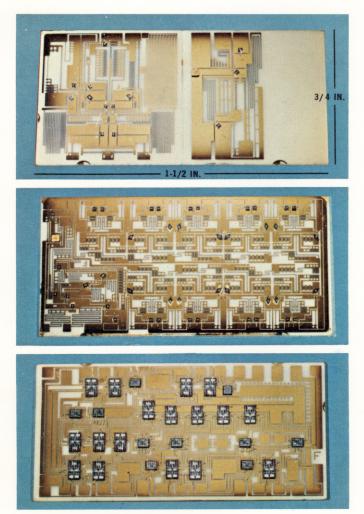

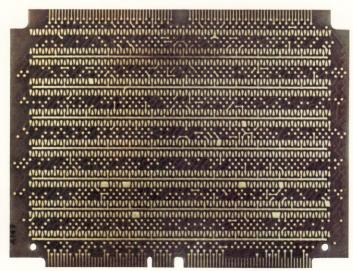

A single Minuteman II MLB (bottom) is the equivalent of as many as 19 conventional circuit boards, plus 19 connectors, and a substantial amount of wire harness

Minuteman II MLB and MIB

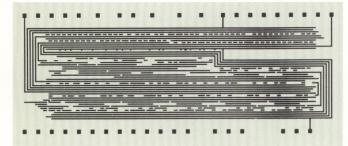

High-density Minuteman II MLB compared with thin-film microconductor MLB under development

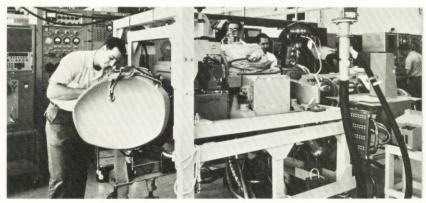

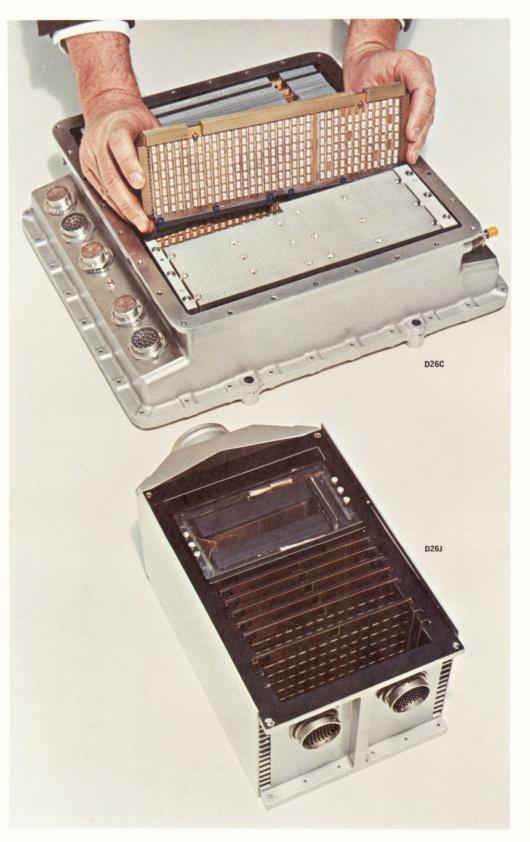

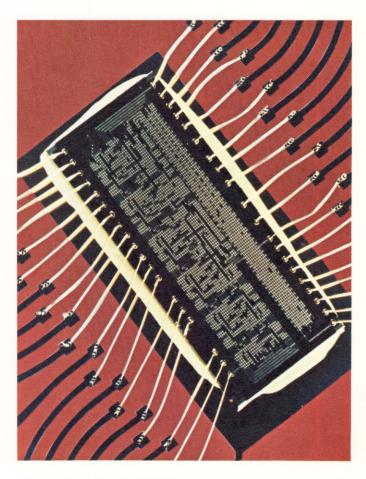

With microelectronic devices becoming ever smaller and smaller, the interconnecting leads and cabling for the devices soon became actually heavier and bigger than the devices themselves. In answer to the practical impossibility of jamming the required number of leads onto a single layer of etched circuitry Autonetics took the logical step of designing a multilayer board consisting of a number of layers laminated together.

Interconnection techniques developed for early and late models of Minuteman I's N10 computer electronics are contrasted in the photograph below. The conventional wire harness involved complex hand wiring and soldering operations requiring approximately 3000 hours of assembly time. The contoured multilayer "master interconnect" board (MIB) was designed to curve around the N10 toroid and to replace the bulky harness. The pioneering multilayer board—into which were "plugged" the computer's individual etched circuit boards containing discrete electronic components—was made up of 13 layers of standard-size printed wiring and used the inherently reliable plated through-hole interconnection method.

Comparison of contoured MIB designed for Minuteman I with conventional wire harness used in the missile

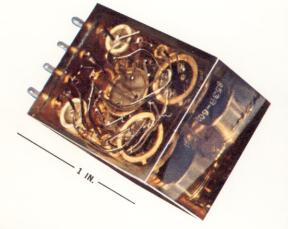

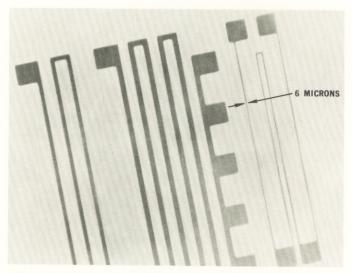

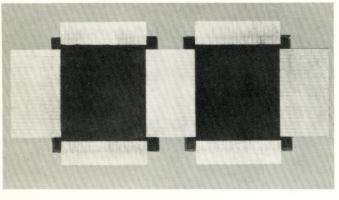

For Minuteman II's D37 computer a 10-layer highdensity circuit board has been developed to take care of such new microelectronic devices as semiconductor integrated circuits; interconnections between planes in the board are made through 30-mil-diameter plated through-holes. A master-interconnect board to accommodate the high-density multilayer circuit boards (MLB's) has been developed concurrently.

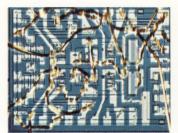

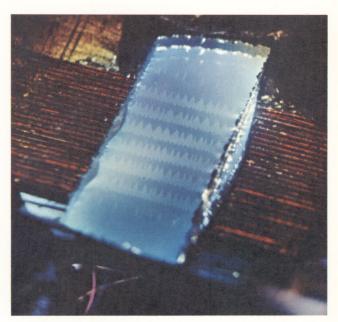

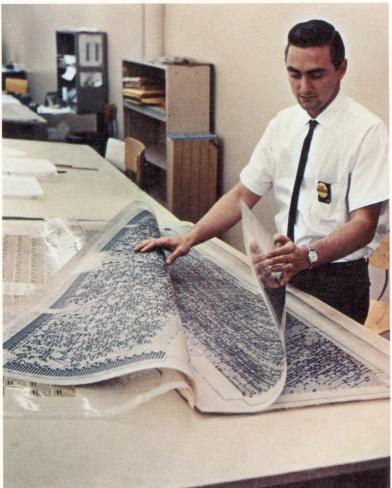

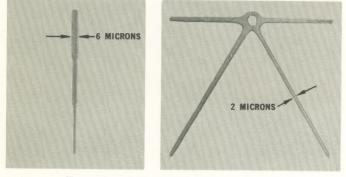

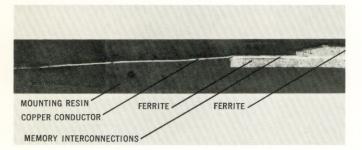

Even the high-density MLB's for Minuteman II will be out-paced by the thin-film multilayer boards now in the advanced development stage at Autonetics. Conductor patterns for these boards are obtained by photolithographic and etching techniques. The thin-film conductor and insulation networks are applied by vacuum deposition of conductive and insulating materials in accordance with a master pattern. Circuitry line-widths as small as 2 mils have been achieved.

#### DIFFERENT APPLICATIONS - DIFFERENT MICROELECTRONICS

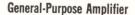

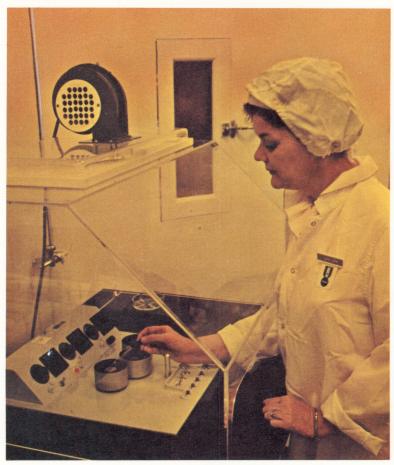

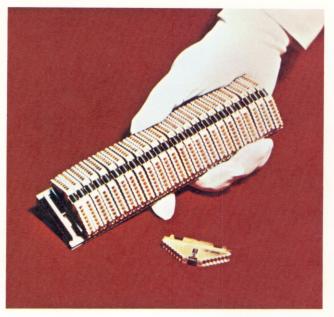

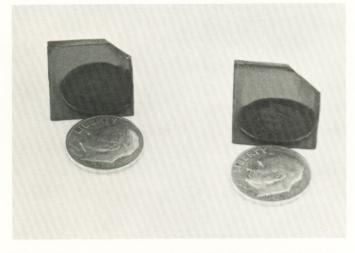

The quantity of semiconductor integrated circuits (IC's) in this wedding ring can form as much as 95% of the electronics for advanced computers.

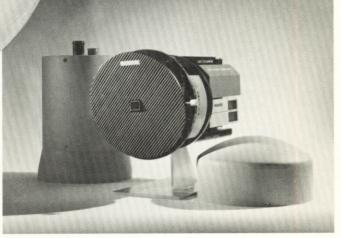

Thin-film circuits—mounted on interconnection boards—yield low-profile microelectronics packaging for radars.

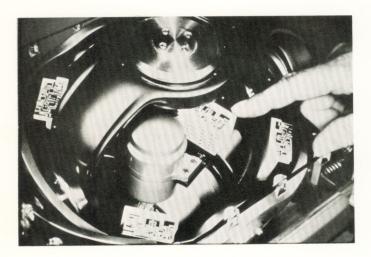

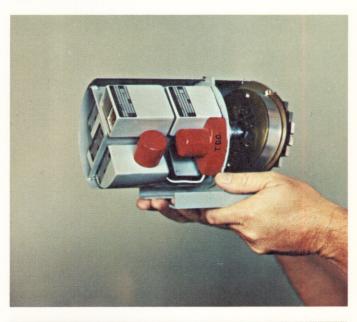

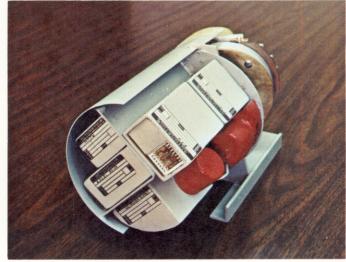

Individual ceramic printed circuits (CPC's) fit into tracks on the inner walls of this inertial autonavigator module.

#### Second-generation microelectronics

☐ The evolution of microelectronics has been given impetus by a changing motivation. At first, major emphasis was placed on size reduction; later, reliability was the chief selling-point, followed then by the suitability of microelectronics for digitalization. Today, new materials and processes are bringing cost reduction to take its place among significant microelectronics benefits — along with even higher reliability and lower weight, cube, and power.

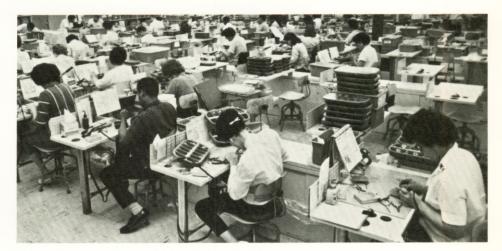

☐ The first-generation step that integrated separate circuit elements into a complete-circuit unit is now being followed by the second-generation step of integrating hundreds of circuits into a single monolithic unit. Economical ways have been found to quantity-develop low-usage semiconductor integrated circuits for linear systems. More efficient and reliable methods of microelectronics joining are cutting production hours and dollars. At the same time, still widely applicable first-generation devices are undergoing constant second-generation evolution, improving both physically and functionally.

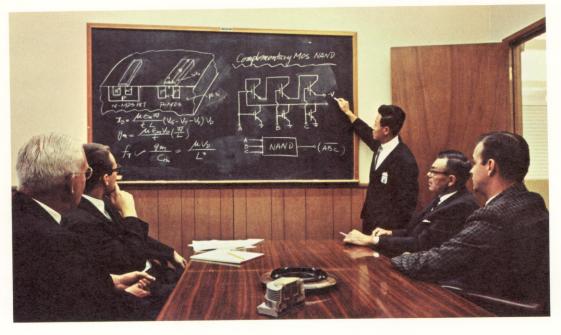

#### MOS Technology

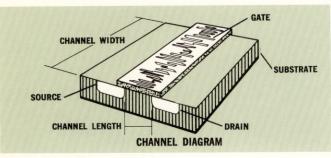

One of the most dramatic second-generation achievements is the transformation of metal-oxidesemiconductor (MOS) technology from a laboratory curiosity into usable microelectronic devices.

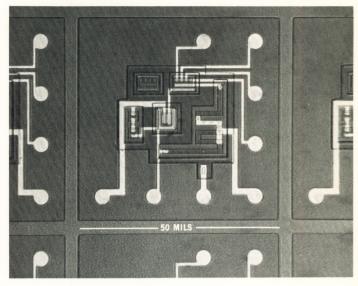

□ Looking through a microscope at a "conventional" integrated circuit, it seems almost impossible to imagine being able to get a greater number of separate individual devices into a single monolithic chip. But the proud ability of the bipolar IC to carry up to 2000 separate elements promises to become "old hat," with the laboratory emergence of field-effect MOS and its potential device density of as high as 100,000 elements in the same area. 1960

200 Logic Gates 2000 Active Elements

Yield: 2% To 5% CONVENTIONAL IC

#### 1965

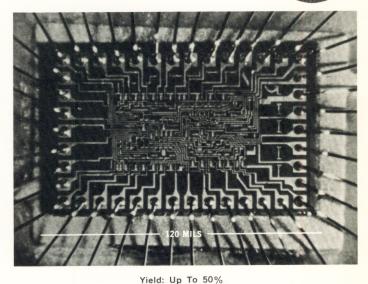

100 Functional Circuits 50,000 Active Elements

MOS DEVICE

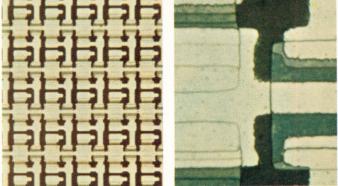

□ With MOS, functional complexity of circuitry can be increased as much as 30 to 50 times over that of the most complex double-diffused IC—either without increasing, or often actually decreasing, the space required and, at the same time, with an increase in yield.

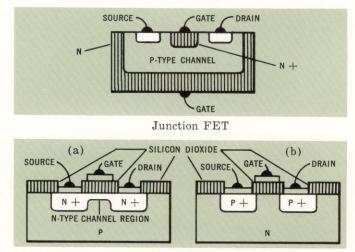

□ Specific examples of MOS "magic": A typical MOS logic NAND occupies only 9 sq mils, in contrast to 300 sq mils for a double-diffused integrated circuit NAND. A single MOS chip can replace as many as 100 functions of conventional doublediffused IC's, or as many as 1000 discrete components. □ What exactly is a "MOS" device? Actually, it is a new type of semiconductor IC. Like the conventional IC, the MOS unit uses silicon as a substrate, into which its circuits are "written" by diffusion. MOS devices, however, furnish their own natural inter-element insulation. There is, thus, no need for elaborate isolation schemes, and the circuit complexity and number of circuits possible per chip are promising by-products.

Unlike conventional IC's, a MOS device operates through the control of an electric field, rather than of a biased junction between portions of the device. (See Appendix I.)

□ Although patents for field-effect devices were issued as long ago as 1930, MOS FET's (metal-oxidesemiconductor field-effect transistors) were not manufactured until the middle 1960's, due chiefly to the difficulty of developing silicon of sufficient purity for the field effect to "work." Even when, around 1955, techniques were perfected for producing silicon of the necessary quality, MOS FET's still had to await the later development of planar techniques and improvement of material-processing skills.

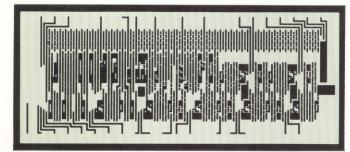

☐ The promise of MOS FET is not simply for reduced size and increased device density; systems designers have been and can certainly continue living

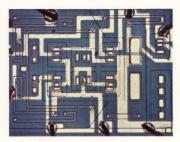

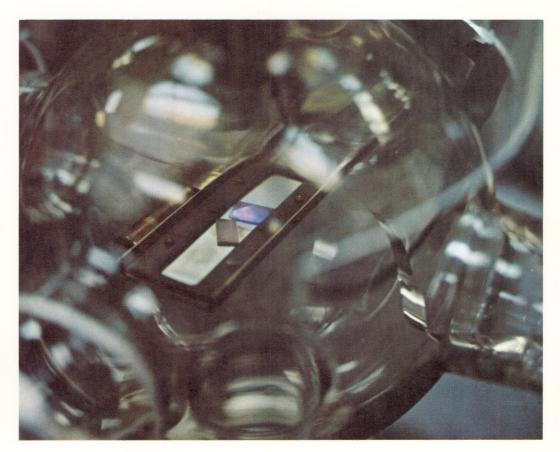

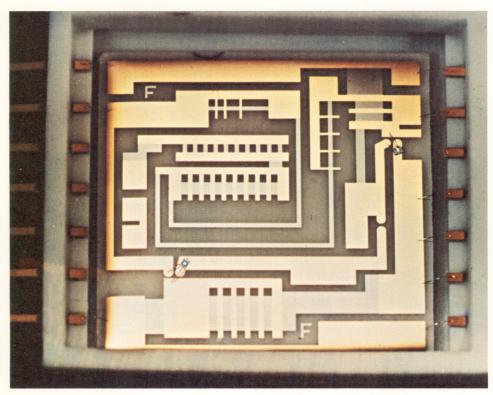

MOS Digital Circuitry

Autonetics' logic designers have decreased the size of a functioning group of circuits by a factor of 50, while increasing the effective parts count by a factor of 2, to give an overall two-order-of-magnitude increase in component density. On the 100-by-200-mil silicon chip shown here are approximately 800 effective discrete components. With computerized layout, the period from start of logical design and layout to the time of first unit availability for test is greatly reduced. (Note the regularity of the MOS shown here, resulting from computerized layout, in contrast to the manually designed MOS on page 17.)

happily with the density limits of conventional IC's. MOS' main offering is cost reduction, which it brings about in a number of ways. First of all, increased yield of MOS batch-fabrication processes teamed with the enormously increased device density per chip — add up to a potential 10-fold cut in production costs. Going beyond production to actual operation "in the field," cost savings are many times multiplied by logistics economies. Permissible density and complexity of MOS chips make the new technology suitable to perform subsystem\*—indeed,

$<sup>^{*}</sup>A$  "subsystem" as used here would be a full arithmetic unit, for example, while "system" would denote an entire computer made up of a number of subsystems."

even entire system—functions. Future logistics engineers will be able to isolate and replace malfunctioning elements to at least the subsystem level, and requirements for maintenance personnel skill and training, for handbook documentation, and for amount and complexity of ground checkout equipment will all be lowered accordingly. All of these logistics simplifications will underline the cost effectiveness of the MOS-mechanized hardware.

□ In addition to these primary economic advantages, MOS offers the already mentioned extremely small geometry, plus the characteristics of high input impedance and self-isolation of individual devices (no separate diffusion step is required for isolation). Furthermore, its principle of operation (as a majority-carrier device) makes MOS potentially more tolerant of the effects of radiation than other forms of microelectronic circuitry.

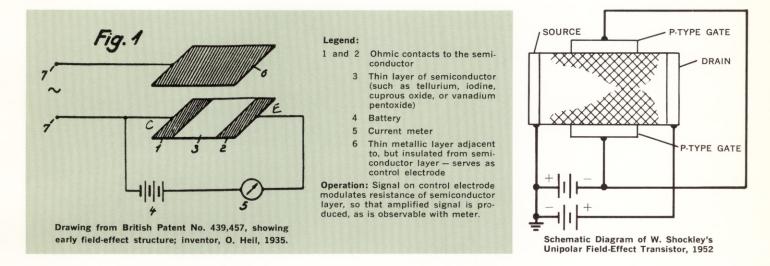

#### FIELD-EFFECT TRANSISTORS GO BACK TO THE 1930'S

First attempts to develop active field-effect devices are revealed by an amazingly early series of patents granted to J. E. Lilienfeld, including U. S. Patent No. 1745175, issued in 1930, and No. 1877140 and 1900018, both issued in 1932.

In 1935, a British patent was granted to Oskar Heil of Berlin, Germany, for "Improvements in or Relating to Electrical Amplifiers and Other Control Arrangements and Devices." Study of the inventor's original patent reveals the device to be describable in today's microelectronics language as a "unipolar fieldeffect transistor with insulated gate."

Following World War II, studies were carried out at Bell Telephone Laboratories under the direction of W. Shockley, leading to the discovery of the transistor effect by Bardeen and Brattain in 1948. In 1952, a paper was published by Shockley describing a unipolar field-effect transistor; this paper has become a basic reference for subsequent FET development. In the paper, Shockley described a unipolar field-effect transistor with a control electrode consisting of a reverse-biased junction. Later, C. Dacey and I. M. Ross actually built and tested such transistors, and, in 1955, made a detailed analysis of their performance limits.

Manufacture of MOS FET's has only recently become economically feasible, since only recently has there been devised a practical method of reducing surface impurities to a sufficient degree for the field-effect principle to be usable. Until as late as 1954, it was impossible to develop silicon of sufficient purity for even the conventional "non-field-effect" transistors, except by a complicated 20- to 30-step refining procedure. The MOS field-effect transistor was impossible to make until planar techniques became practical, and even then stability was still a problem not to be solved until the mid-1960's, with development of a controllable process for batch-fabrication of stable, producible, uniform MOS devices.

#### Improvements to First-Generation Devices and Their Packaging

□ Less dramatic than MOS, but extremely important to growth of the microelectronics art, are such second-generation improvements to first-generation devices and their packaging as dielectric isolation in integrated circuitry, conductive through-holes for ceramic printed circuits, a thin-film hybrid approach to high-density interconnection, compound semiconductor devices, and volume-development of IC's for linear system applications.

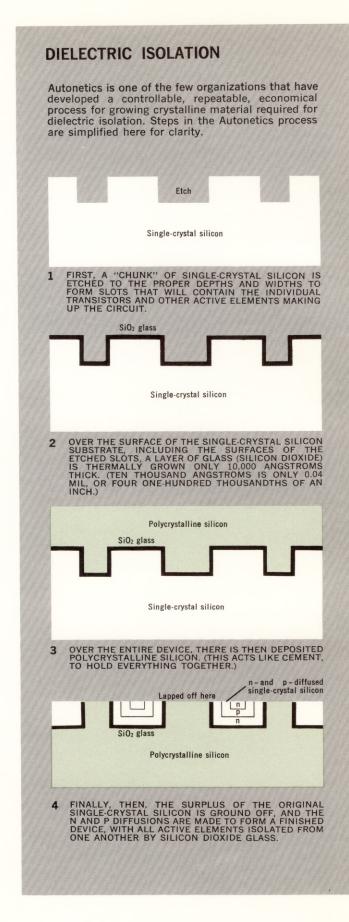

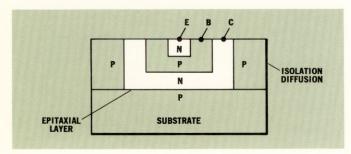

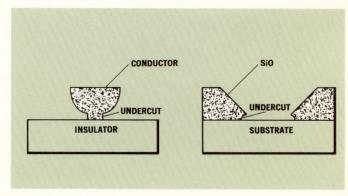

#### Dielectric Isolation

First-generation semiconductor IC's insulate between active elements by means of voltages on the elements that cause them to act, relative to one another, like reverse-biased diodes. Current cannot flow between the "diodes" due to this back-biasing, and the practical result is that each active element is isolated from all others on the substrate-within limits. The "diodes" have breakdown voltages just as capacitors do, and these voltages are quite low. Also, when subjected to some types of radiation, the IC semiconductor materials can exhibit changes which completely nullify the ability of the device to perform as an integrated circuit, and this effect is irreversible. Finally, stray capacitances in the device seriously stunt the frequency range over which it can operate.

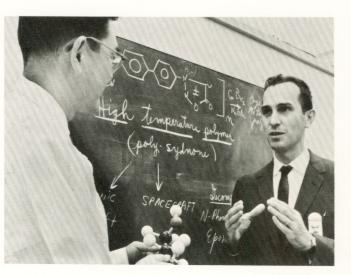

☐ The so-called "Poly"\* or "dielectric isolation" technique actually coats each active element with a completely-surrounding layer of glass insulation. Between each two of these glass-coated islands, insulation strength is in the neighborhood of 1000 volts.

<sup>&</sup>lt;sup>°</sup>The glass-insulated elements are mechanically supported in a polycrystalline silicon wafer-hence, the term "Poly process" for this Autonetics invention.

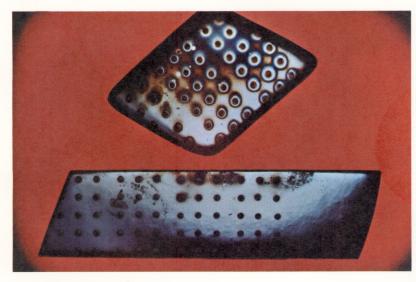

#### Ceramic Printed Circuit Advances

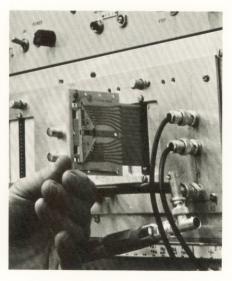

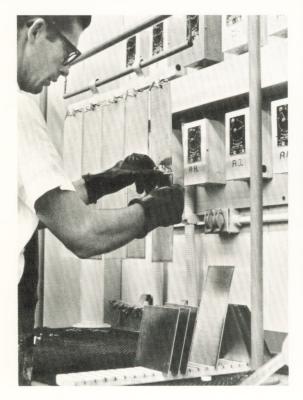

□ Recent enhancement of the CPC technology has resulted in techniques for drilling holes in the substrate and screening conductive material *through* the hole to form a conductive "through-hole." This provides a greater degree of design freedom, since both sides of the substrate can be utilized and interconnected, and crossovers can be easily provided.

☐ The through-hole method permits the use of axiallead micro parts, as well as radial-lead devices. The CPC or "thick-film" technology was originally developed as a *circuit* package technique, but the advent of the through-hole broadens its application into the *module* area.

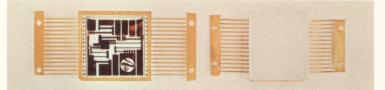

Through-Hole Ceramic Printed Circuits

#### Thin-Film Hybrid Packaging

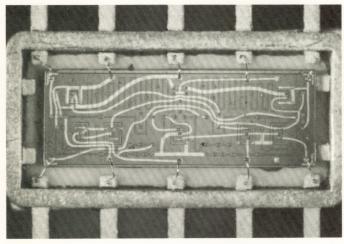

□ Interconnection density is vastly multiplied by a thin-film hybrid approach, in which solid-state active devices are bonded to thin-film passive circuitry.

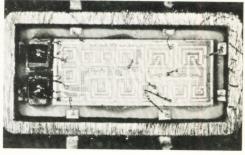

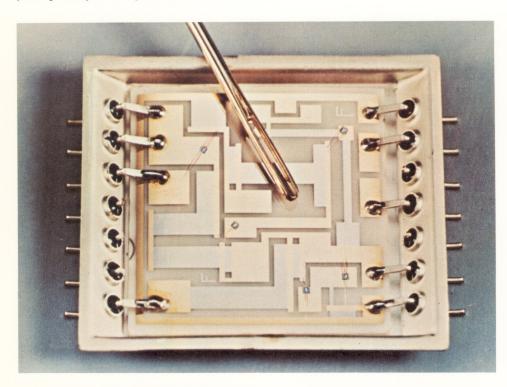

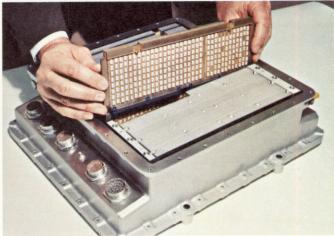

□ In the advanced thin-film hybrid "interconnection board" shown in the next illustration, uncased semiconductor integrated circuits are bonded to a thinfilm conductor network. The unit shown contains 23 solid-state devices, which, because they are uncased, require only 265 bonds in contrast to the 795 bonds that would be needed for individually cased devices. Also, since all 23 devices are enclosed in the single interconnection board package, only one hermetic seal is required, in contrast to the 23 separate ones demanded by conventional, individually packaged IC's.

Thin-film hybrid interconnection board containing uncased active devices bonded to passive thin-film circuitry. Unit shown is a 7-bit counter.

#### Compound Semiconductor Devices

□ Numbers of required interconnections and separate bonds are vastly diminished by the containment of as many as six different bipolar integrated circuits on a single silicon chip. Bond and interconnection requirements are reduced, and only one hermetic seal is necessary for the multifunction package. Furthermore, the simplified fabrication process, with its smaller number of steps, smaller amount of bonding and interconnection, and reduced human handling, promotes reliability and lowers costs.

#### Volume Development of Custom Designs

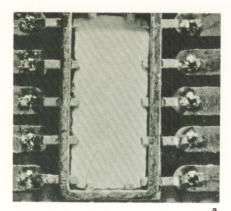

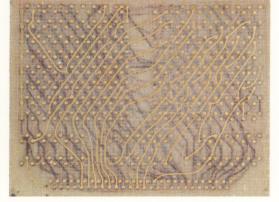

☐ Thanks to such developments as the "master dice" technique, the seemingly mutually exclusive operations of quantity production and low linear-circuit usage are becoming as compatible as the proverbial thieves.

□ In linear systems, many different kinds of circuits are required, but, as mentioned above, usage of each of the individual kinds is extremely low. In contrast to the circuit-type-repetition characterizing a digital computer, "high usage" in a linear system is on the order of 20 of the same kind of circuit, and "average usage" is more like from two to ten. The spending of large amounts of development money on each type of these low-usage circuits would be hard to justify, but batch methods like "master dice" processing provide low-cost, fast-turnaround means for developing many varieties of low-usage linear circuits simultaneously.

$\Box$  With master dice, for example, "custom" circuits can actually be "volume developed." A number of basic bipolar semiconductor integrated circuits are built to make up a set of "standard dice," each die containing transistors, diodes, and resistors, but no interconnections between these elements. During development, the active elements can be interconnected in various ways to form custom circuits. When the circuit design thus achieved is finalized, identical master dice are used by suppliers to produce the IC in the necessary quantity, the only difference being that, in the production model, interconnections are *deposited* on the substrate rather than being made up of actual wires.

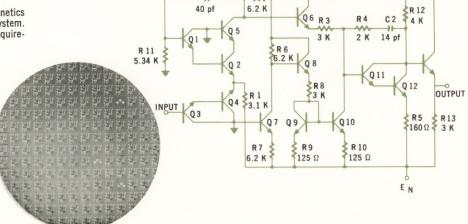

#### "MASTER DICE" TECHNIQUE

The "master dice" technique is an engineering tool for breadboarding and developing custom semiconductor integrated circuits. The process is the brainchild of Autonetics' linear system design engineers and serves as an answer to the high cost of IC development for their kinds of applications.

UNWIRED MASTER DIE

THE SAME MASTER DIE BREAD-BOARDED AS A PREAMPLIFIER

50

13/4 IN.

PRODUCTION MODEL OF SAME MASTER DIE WITH DEPOSITED INTERCONNECTIONS AND WITH BONDED LEADS FOR ATTACH-MENT TO PACKAGE TERMINALS

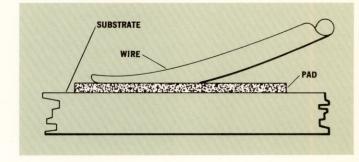

#### Joining

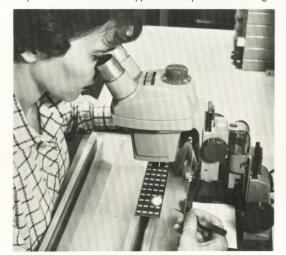

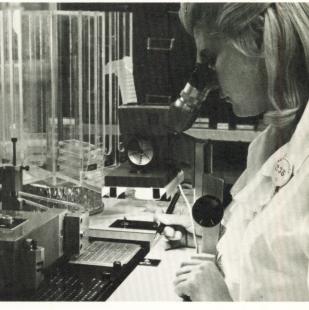

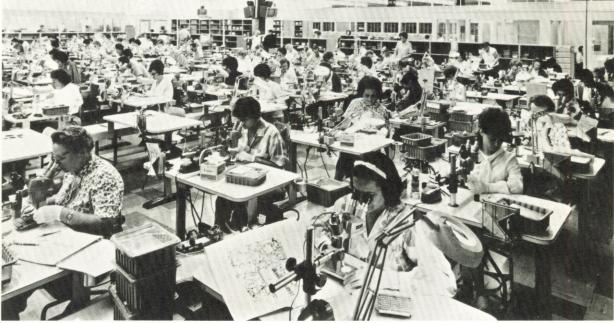

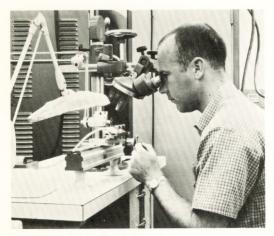

Since the advent of true microelectronics on the Minuteman II Program, the joining technology has undergone a burgeoning growth. New packaging concepts have required the development of new inter/intraconnection techniques. Increasing circuit densities have required "high-resolution" joining methods. Working tools have grown ever smaller, and working areas have become truly microscopic. Just as there is no universally best type of microcircuitry, there is no universally best type of joining, and many techniques have been developed, and are still being developed, to interconnect the devices into systems. All of these techniques have the estimable aim of avoiding degradation of the circuits, devices, and subsystems which they connect-by being reliable, producible, inspectable, and repairable. Some of the techniques are in everyday use-others require further development before attaining the degree of perfection and resulting reliability necessary for widespread application outside the laboratory.

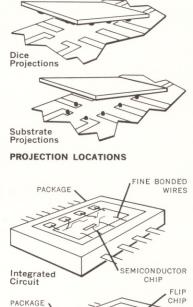

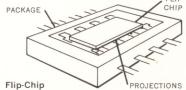

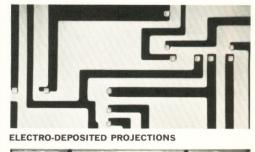

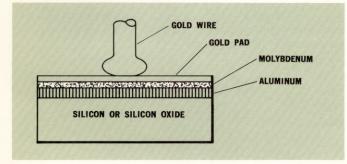

□ One method deserving special note here is registrative or "flip-chip" bonding, because of its marked potential for improving reliability, reducing assembly time, and lowering production costs.

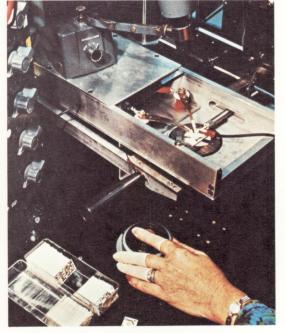

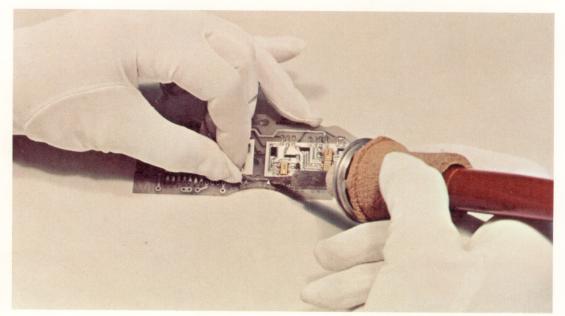

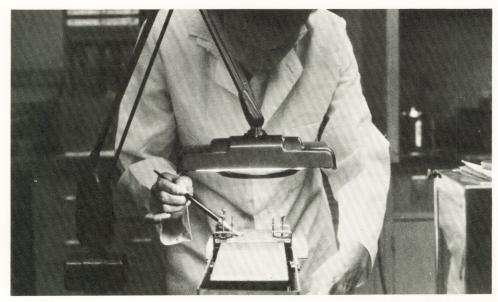

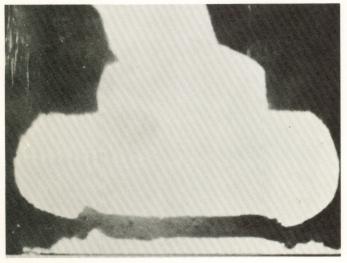

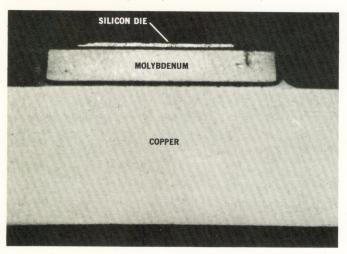

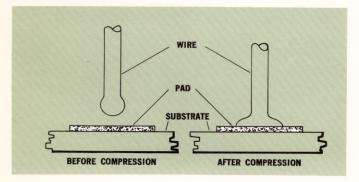

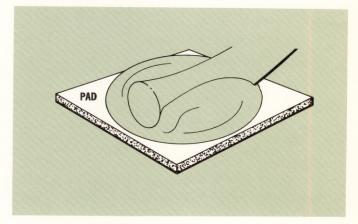

□ "Flip-chip" bonding is a technique for *inverted* joining of a device chip to a matching substrate conductor pattern. The device chip is fabricated to contain, in addition to active, passive, or other "working" networks, a pattern of metal contact pads; the pad pattern on the substrate is an exact mirror image of the pattern on the device chip.

□ To interconnect the device chip to the substrate, the chip is *flipped* (hence, the name of the process) and, while it is face down on the substrate, its contact pads, projecting slightly from the surface, are brought into precise register with the mating contacts on the device chip. Heat and pressure (or other

An Autonetics document-controlled assembly-line soldering process has produced more than 250 billion solder-joint-hours of performance for missile systems without a single reported failure of a solder joint.

forms of energy) are then applied, and the pad areas are joined together. The joining techniques which can be used are many—including microsoldering, ultrasonic bonding, and thermocompression bonding. Each has advantages in certain areas requiring cost and reliability tradeoffs.

□ For mounting integrated circuits within conventional packages, flip-chip bonding eliminates individual wire connections from the IC to the outgoing leads of the package and greatly heightens reliability of the device. It is also used to bond uncased microelectronic devices to microminiature interconnection boards such as the ones described on page 94.

#### MICROELECTRONICS JOINING

#### JOINING TECHNIQUES

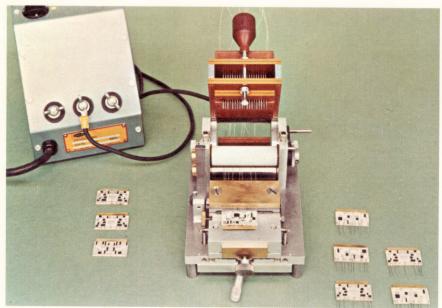

#### SOLDERING Hand-bit Manual operation in which a miniature soldering iron is used in fabrication of printed circuit boards, "cord-wood" modules, etc. Dip Automatic operation in which circuit boards are dipped into molten solder. Basic processes have been modified to allow use with CPC's. Resistance Semiautomatic or automatic operation in which components are individually soldered by direct or indirect I<sup>2</sup>R heating between two electrodes. Automated version has been used to fabricate ceramic printed circuits for Minuteman. Flow or Wave Automatic operation in which printed circuit boards with discrete components are passed on a con-veyor belt through a "wave" of molten solder. WELDING **Cross-wire** Welding by discharge of a capacitor bank through the materials to be joined. Semiautomatic equipment has been developed. Series Use of resistance welding techniques to attach IC (parallel gap) and discrete microcomponent leads to various other circuitry. Electron Welding by impingement of a high-energy electron beam beam onto joining area to produce a microfusion weld. Small beam diameter (0.0005 to 0.001 inch) permits high weld density. Laser Use of heat produced by focused beam of coherent light to melt the joining members and form a weld. Now limited to pulse-type operation at low repetition rate. THERMOCOM-Coalescence of two materials, of which at least one is ductile, by diffusion between the members being joined. Small gold, copper, silver, aluminum, platinum, and tin lead wires and ribbons have PRESSION (TC) BONDING been successfully TC-bonded directly to various semiconductor materials or to an intermediate vapor-deposited metallic conductor film. The gold wire-to-aluminum vapor-deposited circuitry com-bination is most predominantly used for bonding to surfaces of IC's and many transistor devices. Two basic types of TC bonding are "wedge" and "nailhead." Wedge Process in which a wedge-shaped tool is used to plastically deform a small-diameter wire into intimate contact with the semiconductor or metallic conductor. Nailhead Process in which a ball is formed in a hydrogen flame at the end of a small-diameter wire. The ball is then deformed into intimate contact with the bonding surface. ULTRASONIC Process in which ultrasonic energy is used to break up surface oxides, bringing the bonding BONDING surfaces into intimate contact and producing a metallurgical joint. Process in which bonding is accomplished by an electrical pulse passed between two electrodes SERIES (MICRO- GAP) BONDING which are shorted by one of the joining members.

#### NAILHEAD THERMOCOMPRESSION BONDING EQUIPMENT AND BOND

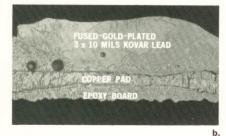

- Cross-section of bond between 1-mil gold wire and vapor-deposited aluminum on silicon.

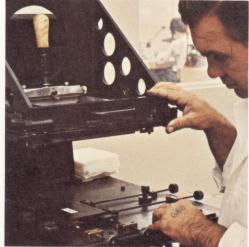

- b. Example of a nailhead thermocompression bonding attachment. Circled area includes the heated tungsten carbide bonding capillary, flame-off nozzle, and a flat package containing a semiconductor integrated circuit.

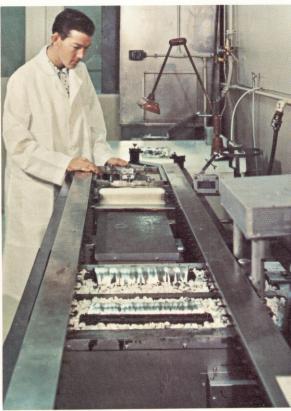

FLOW SOLDERING

Conveyor system moves board through a wave of solder.

#### LASER WELDS

- a. Leads of a dummy IC package have been welded to conductor pads on a glass epoxy circuit board, using a 1-joule ruby laser.

- **b.** Microsection of the 3 by 10 mils Kovar lead welded to copper circuitry.

RESISTANCE SOLDERING

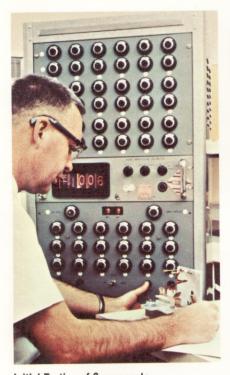

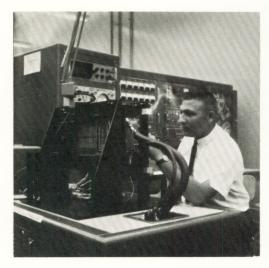

- a. Resistance soldering equipment.

- Resistance soldering of integrated circuits on multilayer board.

#### **CROSS-WIRE WELD**

Microphotograph shows nickel wire (20-mils diameter) welded to a nickel ribbon (10 by 30 mils).

ULTRASONIC BONDING

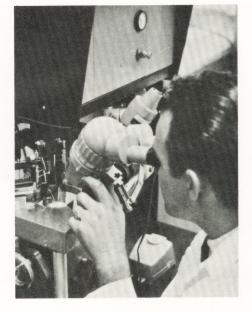

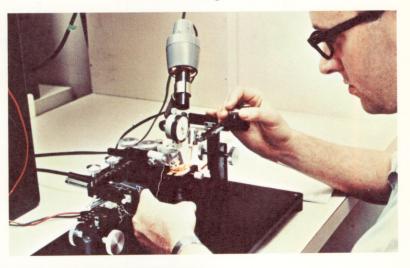

Ten-mil aluminum wire is being bonded to a power transistor.

#### **REGISTRATIVE (FLIP-CHIP) BONDING**

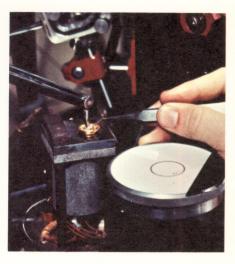

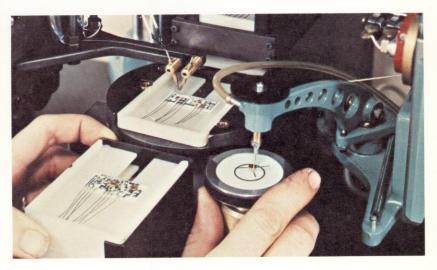

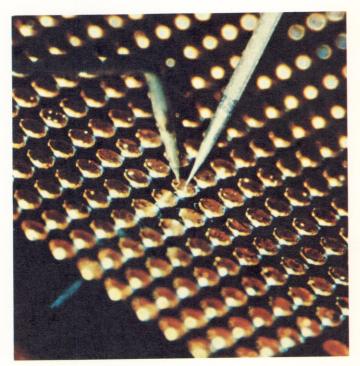

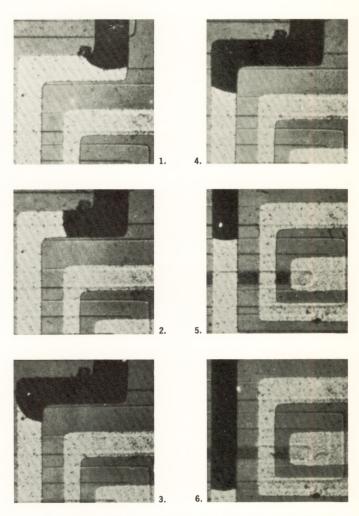

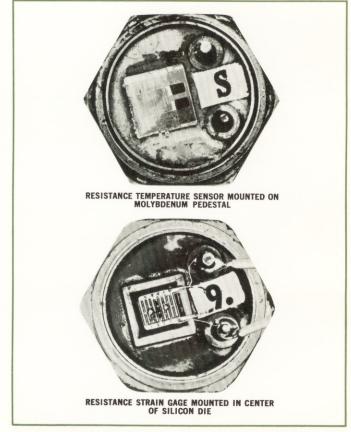

Packaging and assembly costs discovered during a microelectronics cost analysis at Autonetics have led to development of a semiautomatic flip-chip bonding machine. It was found during the analysis that the greater part of microelectronics production costs were those of packaging and assembly. Rapid handling of bonding operations by the machine have cut costs by 90%.

LABORATORY FLIP-CHIP BONDER

COMPARISON OF THE CONVENTIONAL METHOD FOR CONNECTING IC TO PACK-AGE AND THE FLIP-CHIP TECHNIQUE

SEMIAUTOMATIC FLIP-CHIP BONDING MACHINE DEVELOPED BY AUTONETICS

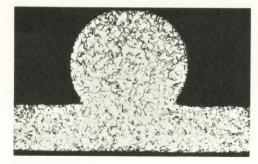

CONICAL GOLD PROJECTIONS FLIP-CHIP BONDED BY THERMOCOMPRESSION TO GOLD THIN-FILM IC INTRACONNECTS

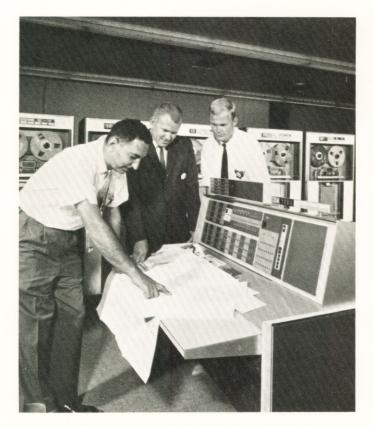

#### A major microelectronic systems organization and what it is doing today

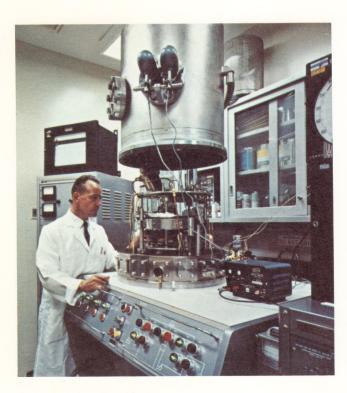

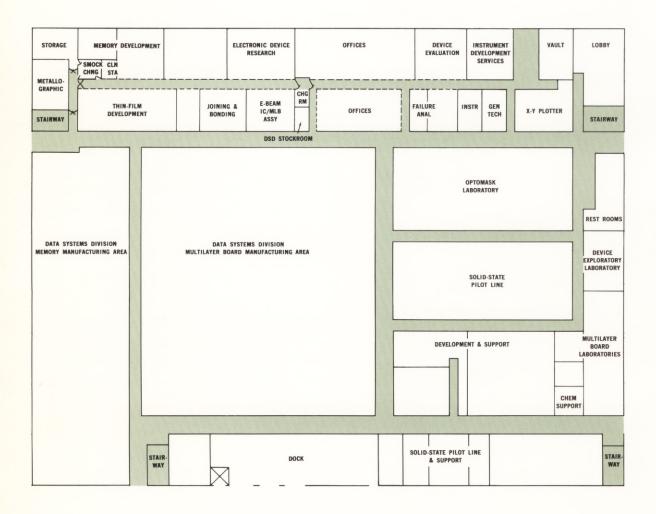

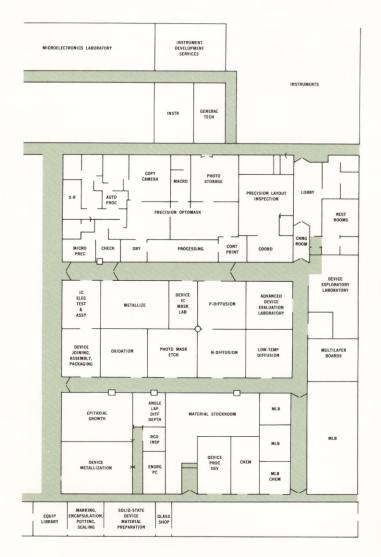

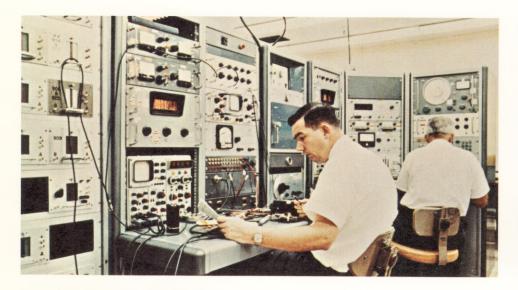

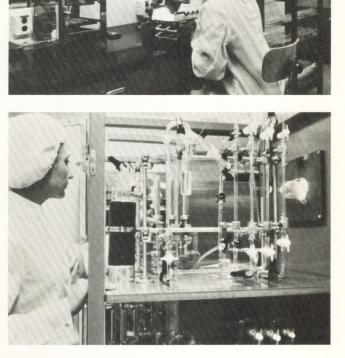

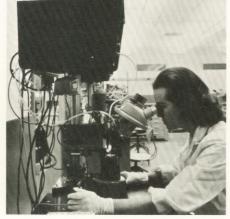

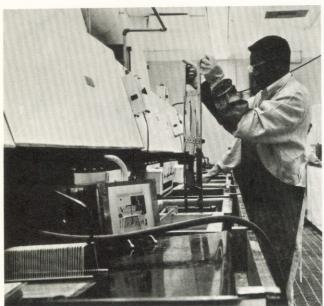

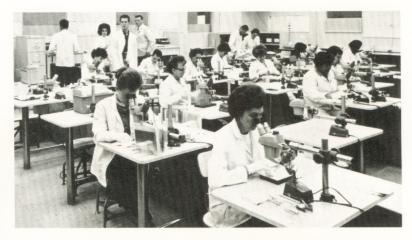

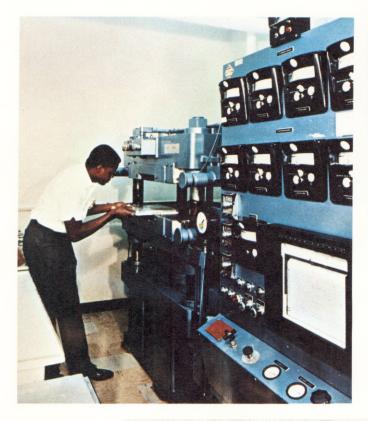

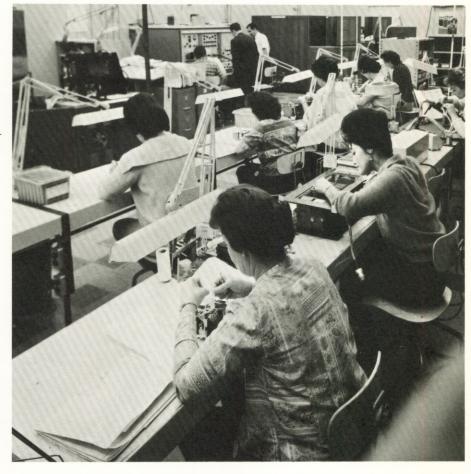

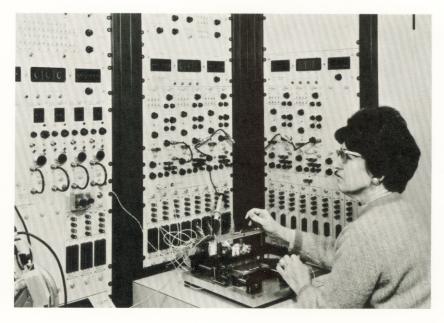

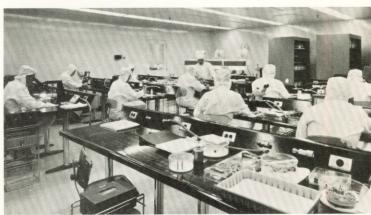

To the visitor from "outside," the microelectronics shops and laboratories of North American Aviation's Autonetics Division seem a bewildering mixture of alphabet soup and technological complexity. The Division is one of this nation's largest and most experienced aerospace systems designers and manufacturers-as well as the most extensive systems user of microelectronics. Its scientists have brought forth an impressive number of microelectronics breakthroughs, including (alphabetically speaking): POLY, SOS, YIG, and many others. It would be strange if Autonetics' scientific staff did not produce such progeny-having at their immediate disposal, as they do, one of the most complete facilities in the world for microelectronics research, development, and pilot-line production.

□ To a degree unparalleled by any other technology, microelectronics is an interdisciplinary blend of sciences—physics, chemistry, and electronics. Autonetics is uniquely qualified for microelectronics by impressive strength in materials research, plus the complementary capability to translate research findings into equipment performance.

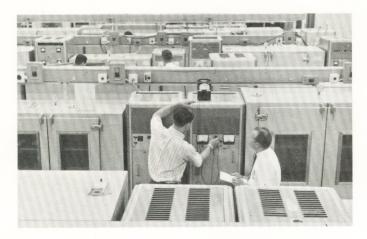

One of the things that make Autonetics remarkable in the microelectronics industry, and noted by visitors to the 290-acre complex in Anaheim, California, is the diffusion of microelectronics activities throughout the Company.

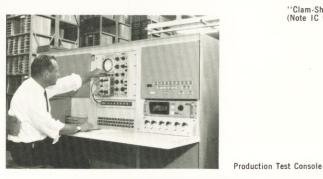

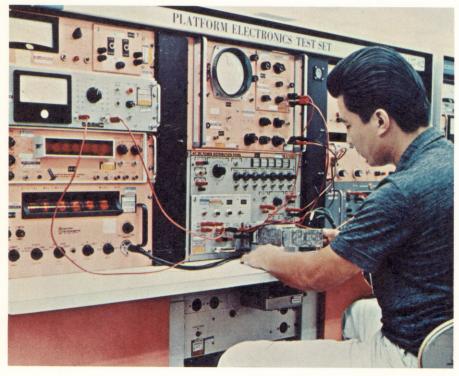

Coordinated purpose and focus are given by an Advanced Electronics Department comprised of three sections — Microelectronics Engineering, Materials and Processes Laboratories, and the Central Microelectronics Laboratory. Advanced Electronics has its own assigned research and development tasks in the areas of microelectronics interconnection techniques, joining methods, semiconductor diffusion processes, and microelectronic circuitry and memory design. At the same time, the department has the responsibility for making producible any promising microelectronics development of Autonetics' product divisions and Research Center, designing a pilot-line production process for it, and writing detailed specifications for its manufacture by the Company or its suppliers.

□ While held within the reasonable boundaries of Company objectives by the firm yet flexible reins of the centralized Advanced Electronics Department, the product divisions are free to pursue the intriguing lines of development indicated by their product lines' special requirements. To this "directly applicable" research of the product divisions, is added the "purer" research of the Research Center in its own superbly equipped building near the Company's headquarters. The parent NAA Kindelberger Science Center stands ready for consultation and guidance in the conduct of any of Autonetics' research projects.

□ Autonetics' leadership in microelectronics stems from the multiplicity of its roles in this technology—as researcher, developer, designer, producer, purchaser, and user in systems. This multiplicity of roles is borne out by the collection of words and pictures presented in the next section of this book.

## Researcher...

All of Autonetics' systems hardware achievements are born from the solid background of a comprehensive research program. In no technological area is this more meaningful than in the area of microelectronics. The materials, processes, and devices of microelectronics all have their origins in research and it is from the brilliant conceptions of research that the improved systems for defense, industry, and exploration are ultimately begotten.

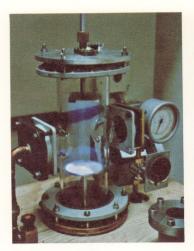

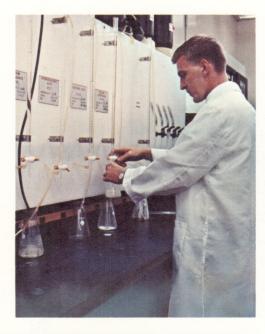

#### **Crystal Growth Facilities**

Facilities exist in the Research Center for growing a wide range of crystals from many different materials and in a variety of forms. The facilities include those for the following crystal-growth techniques: Verneuil, hydrothermal, Czochralski, Bridgman, and chemical vapor-deposition. A variety of techniques is required because of individual technique limitations with respect to crystal form and tolerable temperature. Each technique is able to produce crystals only of certain structure (thin-film, long-rod, bulk or large-crystal), and melting temperatures of raw materials are prohibitive for some processes.

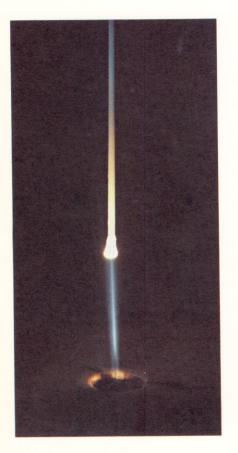

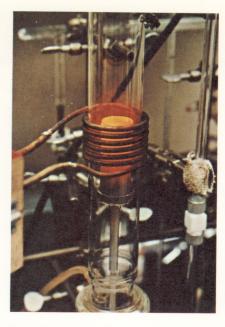

#### Verneuil

Source powder is fed down through an oxyhydrogen flame and onto a growing ruby boule in a flame fusion (Verneuil process) furnace.

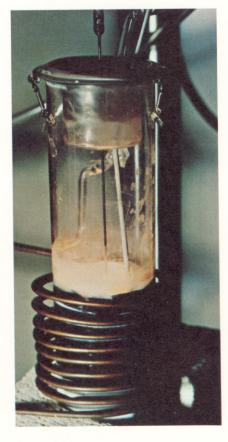

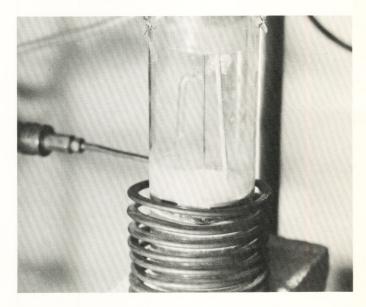

#### Czochralski

In an inert atmosphere, a rare-earth fluoride crystal is pulled from Czochralski melt. The crucible is radio-frequency heated.

#### **Chemical Vapor-Deposition**

Chemical vapor-deposition is used for homoepitaxial growth of single-crystal magnesium oxide on a substrate of magnesium oxide.

#### Some Epitaxial Achievements

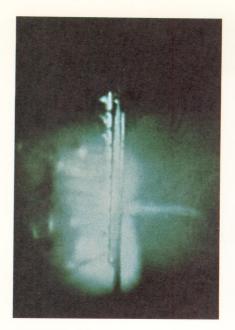

#### Laser Implications

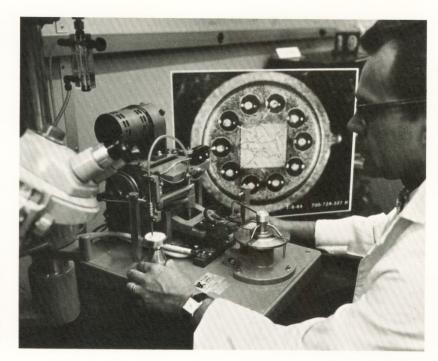

Chemical vapor-deposition of single-crystal germanium on gallium arsenide, and also of singlecrystal gallium phosphide on gallium arsenide, has been accomplished in the Research Center's epitaxial laboratory. Such heterojunctions are of interest because of their injection laser possibilities, as well as their photo-responsive properties. Viewed here through an infrared snooperscope, is an array of ten gallium arsenide injection lasers operating in liquid nitrogen. The array is fabricated from a single-crystal slice of gallium arsenide, grooved to allow independent operation of the ten devices.

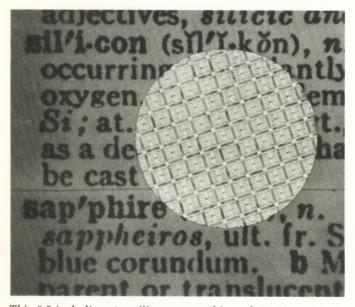

#### **Deposition Breakthrough**

With chemical vapor-deposition, the Research Center has achieved the first reported instance of single-crystal silicon deposition upon an insulating surface (sapphire). The deposited silicon is greater than three-quarters of an inch in diameter, and is of the quality required for fabrication of diodes and transistors.

#### **Thin-Film Transistors**

A ladybug examines an array of insulated-gate, field-effect transistors arranged in a grid on single-crystal silicon-on-sapphire. Each of these majority-carrier triodes is less than a micron thick, is completely compatible with passive thin-film elements, has excellent amplification ability, and is highly radiation-resistant.

#### Silicon-on-Sapphire Memories

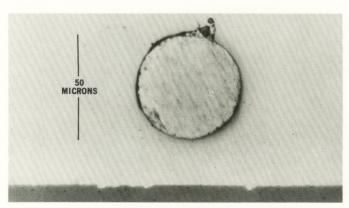

Bit density of over 25,000 bits per square inch characterizes a fixed-program memory fabricated from a silicon-on-sapphire diode array. (See page 92 for description of the memory.)

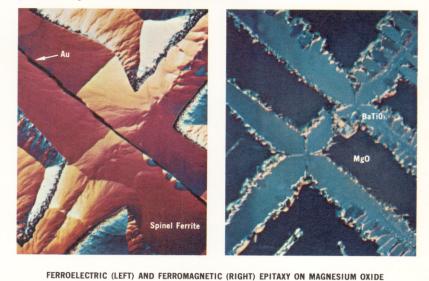

#### Single-Crystal Magnetic Materials

Autonetics' interest in computer application of magnetic effects goes back to 1960. Both metallic and oxide thin-film studies have been performed. It has been demonstrated that epitaxial single-crystal films of magnetic oxides that are particularly well suited for memory elements may be grown. Elementary bit capability of epitaxial ferrites and yttrium iron garnet on magnesium oxide has been demonstrated.

#### **Thin-Film Deposition**

Autonetics' laboratories have for several years employed both plasma techniques (glow discharge) and electron-beam techniques (both plasma and filament cathodes) to achieve organic and inorganic thin films which are pinhole-free, continuous, controllable in thickness, and either insulating or semiconducting. The films may be extremely thin (around 50 angstroms), and are ideally suited for fabrication of high-value capacitors, as well as protective oxide coatings.

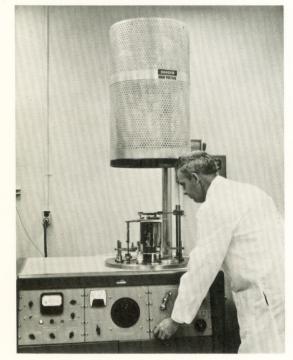

Glow-Discharge Method

Electron-Beam Method

#### Thin Films as Optical Interconnections

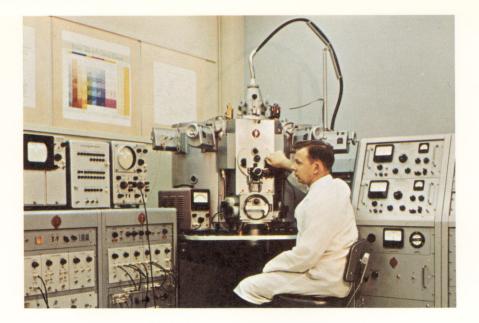

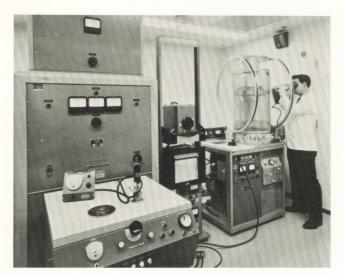

Complex equipment is used to investigate application of thin-film dielectric structures as waveguides to transmit optical signals between light-emitting and light-detecting devices. (Such high-speed coupling is of particular interest for digital computer circuitry.) The equipment includes a vacuum system, complete with microcircuit jig; an electron-beam gun; an electrobalance; a thin-film monitor; and an optical pyrometer.

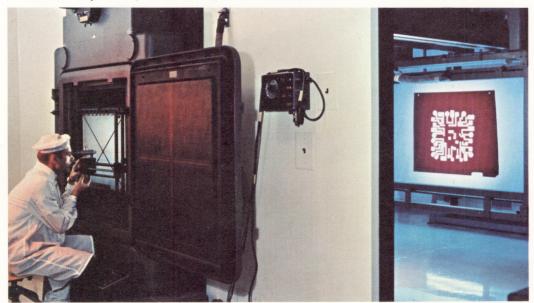

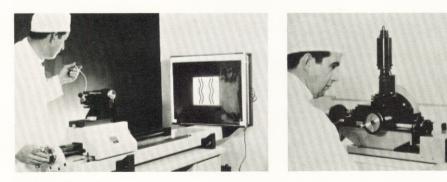

#### **Microphotolithography**

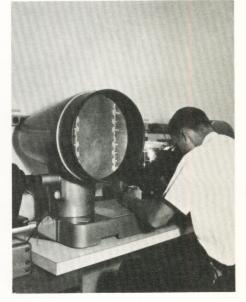

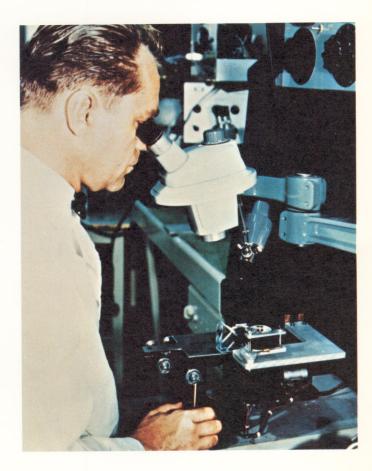

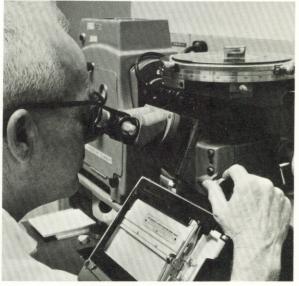

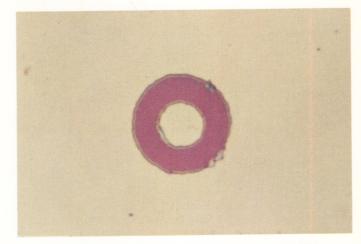

With this optical mask alinement equipment, the image of an entire pattern can be alined, projected, and printed on a photosensitized material with ultra-high precision ( $\pm 1$  micron), to help achieve such devices as the planar annular varactor.

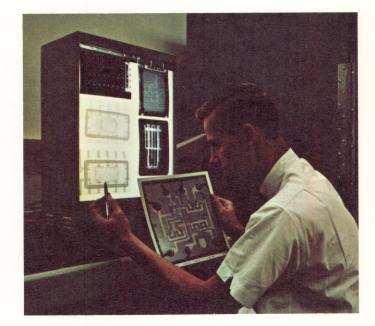

**Planar Annular Varactors**