PRODUCT SPECIFICATION S-Memory Processor A 2201 6760 Released 1/9/76

#### **B1700** HARDWARE SPECIFICATIONS

#### DISTRIBUTION

| DE | TR | 0 | Ι | T |

|----|----|---|---|---|

|----|----|---|---|---|

D. Kosinski - CPM

R. Stackhouse - CPM

D. Bookwalter - CPM

C. Chamberlain - Tech Pub

J. Raker - Int'1

T. Allison - Int'1 (2)

R. Gould - Int'1

H. Hayde - Int'1

J. Holton - Int'1

C. Nash - Int'1

E. Seif - Int'1

H. Nelson - BM&SS

J. Shifman - CSG

E. Rindels - BMG

W. Cunningham - BMG

E. Paulsen - TIO

#### **PLYMOUTH**

D. Calkins

#### **DOWN INGTOWN**

J. Berta

#### PAOLI

G. Smolnik

#### McLEAN

L. Guell

A. Kosla

#### **PASADENA**

D. Gale

J. Malson

#### MISSION VIEJO

T. Gibson

#### WESTLAKE

H. Smith

J. Dowling

#### LIEGE

J. Wery

A. Beaujean

#### **GENNEVIELIERS**

A. Isola

#### **MIDDLESEX**

W. Marshall

#### CUMBERNAULD

D. Wright

SANTA BARBARA

R. Bunker

Manufacturing (2) Quality Assurance

TIO (2)

SENEFFE J. Jeanty

Software (30)

W. Keenan (5)

Hardware - J. Vigil

J. Trost

GLENROTHES

B. Slattery

## S. Bhagwan (2)

#### F. E. TRAINING DEV. GROUP

M. McCoy

3374 Rio Hondo Avenue

El Monte, California 91731

#### PATENT ATTORNEY

Mr. D. Bruce Prout Christie, Parker & Hale 201 South Lake Avenue Pasadena, California 91101

#### TIREMAN

F. Williams

## Burroughs Corporation

BUSINESS MACHINES GROUP SMALL SYSTEMS PLANT

B1700 S-MEMORY PROCESSOR

## PRODUCT SPECIFICATION

#### REVISIONS

| REV<br>LTR | REVISION<br>ISSUE DATE | PAGES REVISED ADDED DELETED OR CHANGE OF CLASSIFICATION                                                                                                                                                                                                                                                                                                                            | PREPARED BY | APPROVED BY            |

|------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------------------|

| F          | 1-8-76                 | Revised document primarily to reflect addition of S-Processor-2. Preface: Added information on S-Processor-2 Rel Specs: Added PS #2209 7968, SDS #2210 0143. Sec 2.0: Added M&E 2208 3141, 2208 3158, 2212 8276. Sec 3.1.11: Added PERR. Sec 3.3.10: Added reference to S-Proc-2.                                                                                                  | WFK         | Hole<br>Male<br>1-8-16 |

|            |                        | Added note on M-op fetch. Added note on addressing non-present memory.  Sec 3.3.12: Added reference to S-Proc-2.  Sec 3.3.14: Revised, expanded U-Register information.  Sec 3.3.15: Revised eigth paragraph (bus interrupt). Added paragraph on C-Reg-                                                                                                                            |             |                        |

|            | ·                      | ister bit reset.  Sec 3.3.16, 3.3.17: Deleted references to MOVE, MOVE SCRATCHPAD.  Sec 3.3.19, 3.3.20: Expanded to include operations from control panel.  Sec 3.4.1: Exception (4) expanded to include SUM, DIFF; Exception (5) revised; Exception (6) deleted; Exception (7) renumbered to (6).  Sec 3.4.19, 3.4.20, 3.4.21: Added notes reference reset of bits in C-Register. | e           |                        |

|            |                        | Sec 3.5: Deleted (branch taken) after BIAS.  Reorganized and copy edited entire document for entry into Product Specification data base. New section sequence is as follows. Asterisks indicate revisions referred to above.  Was Preface  1.0* 1.1*                                                                                                                               | AAM         | Al helknum<br>1/8/75   |

|            |                        | 2.0<br>1.2*<br>1.3<br>1.0<br>2.0<br>3.0<br>3.1<br>3.3.10<br>3.1.1*                                                                                                                                                                                                                                                                                                                 |             |                        |

"THE INFORMATION CONTAINED IN THIS DOCUMENT IS CONFIDENTIAL AND PROPRIETARY TO BURROUGHS CORPORATION AND IS NOT TO BE DISCLOSED TO ANYONE OUTSIDE OF BURROUGHS CORPORATION WITHOUT THE PRIOR WRITTEN RELEASE FROM THE PATENT DIVISION OF BURROUGHS CORPORATION"

## Burroughs Corporation

BUSINESS MACHINES GROUP SMALL SYSTEMS PLANT

B1700 S-MEMORY PROCESSOR

## PRODUCT SPECIFICATION

#### REVISIONS

| REV<br>LTR | REVISION<br>ISSUE DATE |                                          | ADDED DELETED OR<br>CLASSIFICATION | PREPARED BY | APPROVED BY |

|------------|------------------------|------------------------------------------|------------------------------------|-------------|-------------|

| F          | 1-8-76                 | Was                                      | Is                                 |             |             |

| 1          | Cont.                  | 3.3.11                                   | 3.1.2                              |             |             |

|            |                        | 3.3.9                                    | 3.1.3                              | 1           |             |

|            |                        | 3.3.8                                    | 3.1.4                              |             |             |

|            |                        |                                          | 3.1.5                              |             |             |

|            |                        | 3.3.1                                    | 3.1.6                              |             |             |

|            |                        | 3.3.2                                    | 3.1.7                              |             |             |

|            |                        | 3.3.3                                    |                                    |             |             |

|            | ٠                      | 3.3.4                                    | 3.1.8                              |             | •           |

|            |                        | 3.3.5                                    | 3.1.9                              |             |             |

| ·          |                        | 3.3.6                                    | 3.1.10                             |             |             |

|            |                        | 3.1.9                                    | 3.1.11                             | 1           |             |

|            |                        | 3.3.7                                    | 3.1.12                             |             |             |

| l l        |                        | 3.3.15                                   | 3.1.13*                            | l           |             |

|            |                        |                                          | 3.1.13.1                           |             |             |

|            |                        | 0 0 10 0 0 10                            | 3.1.13.2                           | ,           |             |

|            |                        | 3.3.12, 3.3.13                           | 3.1.14*                            |             |             |

|            |                        | 3.3.14                                   | 3.1.15*                            | 1           |             |

|            |                        | 3.3.16                                   | 3.1.16*                            | 1           |             |

|            |                        | 3.3.17                                   | 3.1.17*                            |             |             |

| l i        |                        | 3.3.18                                   | 3.1.18                             |             |             |

|            |                        | 3.3.19                                   | 3.1.19*                            |             |             |

|            |                        | 3.3.20                                   | 3.1.20*                            | 1           |             |

|            |                        | 3.1                                      | 3.2                                | <u>'</u>    |             |

|            |                        | 3.1.1                                    | 3.2.1                              |             |             |

|            |                        | 3.1.2                                    | 3.2.2                              |             |             |

|            |                        | 3.1.3                                    | 3.2.3                              |             |             |

|            | •                      | 3.1.4                                    | 3.2.4                              |             |             |

|            |                        | 3.1.5                                    | 3.2.5                              |             |             |

|            |                        | 3.1.6                                    | 3.2.6                              |             |             |

|            |                        | 3.1.7                                    | 3.2.7                              | 1           | į           |

|            |                        | 3.1.8                                    | 3.2.8                              |             |             |

|            |                        | 3.1.10, 3.1.11                           | 3.2.9*                             |             |             |

|            |                        | 3.2                                      | 3.3                                | }           |             |

|            |                        |                                          | 3.4 and 3.5 remain                 |             |             |

|            |                        | unchanged.                               |                                    |             |             |

|            |                        |                                          |                                    |             |             |

|            |                        |                                          |                                    | 1           |             |

|            |                        |                                          |                                    |             |             |

| •          |                        |                                          |                                    |             |             |

| j          |                        |                                          |                                    |             |             |

|            |                        |                                          |                                    | 1           |             |

|            |                        | en e |                                    | 1           | ]           |

"THE INFORMATION CONTAINED IN THIS DOCUMENT IS CONFIDENTIAL AND PROPRIETARY TO BURROUGHS CORPORATION AND IS NOT TO BE DISCLOSED TO ANYONE OUTSIDE OF BURROUGHS CORPORATION WITHOUT THE PRIOR WRITTEN RELEASE FROM THE PATENT DIVISION OF BURROUGHS CORPORATION"

.

# TABLE OF CONTENTS:

| 1 0      | THEROPHETION              | •  |

|----------|---------------------------|----|

| 1.0      | INTRODUCTION              | 1  |

| 1.1      | PURPOSE                   | 1  |

| 1.2      | PRODUCT IDENTIFICATION    | 1  |

| 1.3      | RELATED SPECIFICATIONS    | 2  |

| 2.0      | GENERAL DESCRIPTION       | 3  |

| 3.0      | PRODUCT DESCRIPTION       | 8  |

| 3.1      | PROCESSOR REGISTERS       | 8  |

| 3.1.1    | MAR(A)                    | 8  |

| 3.1.2    | M                         | 9  |

| 3.1.3    | A STACK                   | 9  |

| 3.1.4    | TAS                       | 10 |

| 3.1.5    | X AND Y                   | 10 |

| 3.1.6    | L                         | 10 |

| 3.1.7    | <b>T</b>                  | 11 |

| 3.1.8    | FA                        | 11 |

| 3.1.9    | FB                        | 12 |

| 3.1.10   | SCRATCHPAD                | 12 |

| 3.1.11   | FLCN                      | 13 |

| 3.1.12   | BR AND LR                 | 13 |

| 3.1.13   | C                         | 13 |

| 3.1.13.1 | CP (CYF, CPU, CPL)        | 13 |

| 3-1-13-2 | CA+ CB+ CC+ CD            | 14 |

| 3.1.14   | MAXS, MAXM                | 16 |

| 3.1.15   | U                         | 16 |

| 3.1.16   | DATA                      | 16 |

| 3-1-17   | CMND                      | 17 |

| 3.1.18   | NULL                      | 17 |

| 3.1.19   | READ                      | 17 |

| 3.1.20   | WRIT                      | 17 |

| 3.2      | 24-BIT FUNCTION BOX       | 18 |

| 3.2.1    | SUM                       | 19 |

| 3.2.2    | DIFF                      | 19 |

| 3.2.3    | XANY, XORY, XEDY          | 20 |

| 3.2.4    | CMPX, CMPY                | 20 |

| 3.2.5    | MSKX.MSKY                 | 20 |

| 3.2.6    | BICN                      | 20 |

| 3.2.7    | XYCN                      | 21 |

| 3.2.8    | XYST                      | 22 |

| 3.2.9    | INCN. PERR                | 23 |

| 3.3      | 4-BIT FUNCTION BOX        | 23 |

| 3.4      | M-INSTRUCTIONS            | 24 |

| 3.4.1    | REGISTER MOVE             | 24 |

| 3.4.2    | SCRATCHPAD MOVE           | 25 |

| 3.4.3    | SWAP F WITH DOUBLEPAD WOR |    |

| 3.4.4    | MOVE 8-BIT LITERAL        | 26 |

| 3.4.5    | MOVE 24-BIT LITERAL       | 27 |

| 3.4.6    | READ/WRITE MEMORY         | 27 |

| 3.4.7    | COUNT FAZEL               | 28 |

| 3.4.8    | SCRATCHPAD RELATE FA      | 29 |

| 3.4.9    | EXTRACT FROM REGISTER T   | 29 |

| 2010/    | CHINACT LAUR HEULUICH I   | 27 |

| 3.4.10 | SHIFT/ROTATE REGISTER T LEFT         | 30 |

|--------|--------------------------------------|----|

| 3.4.11 | SHIFT/ROTATE REGISTER X/Y LEFT/RIGHT | 31 |

| 3.4.12 | SHIFT REGISTERS XY LEFT/RIGHT        | 31 |

| 3.4.13 | NORHALIZE X                          | 32 |

| 3.4.14 | CALL                                 | 32 |

| 3.4.15 | BRANCH                               | 33 |

| 3.4.16 | BIAS                                 | 33 |

| 3.4.17 | SET CYF                              | 34 |

| 3.4.18 | 4-BIT MANIPULATE                     | 34 |

| 3.4.19 | BIT TEST BRANCH FALSE                | 35 |

| 3.4.20 | BIT TEST BRANCH TRUE                 | 35 |

| 3.4.21 | SKIP WHEN                            | 36 |

| 3.4.22 | CASSETTE CONTROL                     | 37 |

| 3.4.23 | HALT                                 | 37 |

| 3.4.24 | NO OPERATION                         | 38 |

| 3.4.25 | NO OPERATION                         | 38 |

| 3.5    | M-INSTRUCTION FIMING                 | 39 |

|        |                                      |    |

|        |                                      |    |

|        |                                      |    |

|        |                                      |    |

|        |                                      |    |

COMPANY CONFIDENTIAL S-MEMORY PROCESSOR P.S. #2201 6760

#### 1.0 INTRODUCTION

#### 1.1 PURPOSE

This specification defines the functional requirements of two S-Memory Processors intended for general purpose data processing. Environmental conditions, safety conditions, reliability parameters, power requirements, etc., are specified in P.S. #1913 1739, B1700 CENTRAL SYSTEMS.

Both processors have I/O bus interfaces for communication with the I/O subsystem, control panel interfaces for communication with the control panel, and memory-to-processor interfaces for communication with main memory (B1700 S-Memory).

S-Memory-Processor-1 can address up to 64K bytes (512K bits) of memory. S-Memory-Processor-2 can address up to 128K bytes (1024K bits).

Both processors are capable of operating with 2MHz as well as 4MHz clocks.

An appropriate processor adapter, either 2MHz or 4MHz, is required with S-Processor-1; S-Processor-2 requires no adapter but only a field adjustment of the clock rate.

#### 1.2 PRODUCT IDENTIFICATION

| 2205 | 0967 | S-MEMORY PROCESSOR-1     |      |

|------|------|--------------------------|------|

| 2208 | 3141 | S-PROCESSOR-1 ADAPTER, 2 | 2MHz |

| 2208 | 3158 | S-PROCESSOR-1 ADAPTER.   | MHZ  |

| 2212 | 8276 | S-MEMORY PROCESSOR-2     |      |

COMPANY CONFIDENTIAL S-MEMORY PROCESSOR P.S. #2201 6760

#### 1.3 RELATED SPECIFICATIONS

| P.S.      | #     | NAME                                 |

|-----------|-------|--------------------------------------|

|           | • •   |                                      |

| 1904      | 5681  | B1700 SYSTEM INDEX                   |

| 1913      | 1739  | B1700 CENTRAL SYSTEM                 |

| 2204      | 8623  | B1700 I/O BUS SUBSYSTEM              |

| 1913      | 1754  | B1700 MEMORY SUBSYSTEM               |

| 2205      | 7376  | B1700 S-MEMORY STORAGE CARD          |

| 2209      | 7968  | B1700 CONTROL PANEL                  |

| S . D . S | 5 - # | NA ME                                |

|           |       | •••                                  |

| 2204      | 8656  | B1700 S-MEMORY/S-PROCESSOR INTERFACE |

| 2210      | 0143  | B1700 CONTROL PANEL INTERFACE        |

COMPANY CONFIDENTIAL S-MEMORY PROCESSOR P.S. #2201 6760

#### 2.0 GENERAL DESCRIPTION

The S-Memory Processor (or S-Processor) provides the combinatorial and arithmetic portion of the system along with other registers and hard storage that are appropriate for efficient operation.

The S-Processor provides hardware sensitivity to a set of low-level micro-functions which are used in a program string to fetch and execute instructions. This micro-program is contained in main memory (B1700 S-Memory).

Included in the S-Processor are registers and pseudo registers which are addressable by the individual micro-operators.

The registers are normally addressed by a 4-bit group (row) number and a 2-bit select (column) number as shown in Table 1.

Some of the registers listed, such as the Pseudo Sum Register, can serve only as source registers while others are capable of serving both as source and destination registers. Also, some of the registers listed are actually subregisters which, although parts of larger registers, can be individually addressed and manipulated.

Table 2 summarizes the various conditions available by addressing particular pseudo source registers and actual registers; Figure 1 lists the micro-instructions and their variants; and Figure 2 is a diagram of the major registers.

Only the MAR(A), M, C, U, ML, and MIR registers are reset by a control panel CLEAR signal.

COMPANY CONFIDENTIAL S-MEMORY PROCESSOR P.S. #2201 6760

TABLE 1: M-PROCESSOR REGISTER SELECTION

|        |    |     |            | SELECT NUMB | ER   |      |

|--------|----|-----|------------|-------------|------|------|

|        |    |     | 0          | 1           | 2    | 3    |

|        | 0  | 1   | TA         | FU          | X    | SUM  |

|        | 1  | 1   | <b>T</b> B | FT          | Y    | CMPX |

|        | 2  | 4   | TC         | FLC         | Ţ    | CMPY |

|        | 3  | 1   | TD         | FLD         | L    | XANY |

|        | 4  | i   | TE         | FLE         | A    | XEOY |

|        | 5  | 1   | TF         | FLF         | M    | MSKX |

|        | 6  | 1   | CA         | BICN        | BR   | MSKY |

|        | 7  | !   | СВ         | FLCN        | LR   | XORY |

| GROUP  | 8  | 1   | LA         | TOPMS       | FA   | DIFF |

| NUMBER | 9  | . 1 | LB         | UNASSIGNED  | FΒ   | MAXS |

|        | 10 | 1   | LC         | UNASSIGNED  | FL   | MAXM |

|        | 11 | 1   | LD         | PERR        | TAS  | U    |

|        | 12 | i   | LE         | XYCN        | CP   | MBR* |

|        | 13 | 1   | LF         | XYST        | MSM* | DATA |

|        | 14 | ł   | CC         | INCHE       | READ | CMND |

|        | 15 | 1   | CD         | CPU         | WRIT | NULL |

TOPM, PERR, INCN, MSM, AND MBR are not physically present in the B1700 S-Memory Processor-1 or -2. When any of them is addressed as a source, a binary value of zero is returned. When addressed as destination, the data is lost. (See P.S. #1913 1747, M-MEMORY PRUCESSOR, for meaning in the B1700 M-Memory Processors.)

COMPANY CONFIDENTIAL S-MEMORY PROCESSOR P.S. #2201 6760

# TABLE 2: SUMMARY OF REGISTER CONDITIONS

I LSUY I CYF I CYD I CYL I BICN: 1 MSBX 1 X=Y 1 X<Y 1 X>Y 1 XYCN: XYST: I LSUX I INT I Y neq 0 I X neq 0 I 1 FL=SFL 1 FL>SFL 1 FL<SFL 1 FL neq 0 1 FLCN: I CONTROL PANEL I TIMER I I/O BUS I CONTROL PNL I CC: | STATE LAMP | INTERRUPT | INTERRUPT | | FLIP-FLOP | I MEMORY I MEMORY RSVD I MEMORY RSVD I MEMORY RSVD CD: 1 READ DATA I WRT/SWAP ADDR 1 READ ADDR 1 WRT/SWAP ADDR 1 I PAR. ERR. I DUT OF BOUNDS I DUT OF BNDS I DUT OF BOUNDS I | INTERRUPT | OVERRIDE | INTERRUPT | INTERRUPT 2 3

Satura

|            | _                            | _        |          |      |            |       |                 | _      |      |            |         |            |            |              |               | _    |      | _                     |             |                                                  |                                                  |              |              |              |                                                  |              |                  |                       |                     |              |                            |

|------------|------------------------------|----------|----------|------|------------|-------|-----------------|--------|------|------------|---------|------------|------------|--------------|---------------|------|------|-----------------------|-------------|--------------------------------------------------|--------------------------------------------------|--------------|--------------|--------------|--------------------------------------------------|--------------|------------------|-----------------------|---------------------|--------------|----------------------------|

|            | MICRO NAME                   | 15       | MC<br>14 | . 13 | 12         | 11    | , M.C.          |        | 8    | 7          | 6 ,     | Ε<br>5,    | 4          | 3            | _ A<br>2      | F    |      | VARIANTS              | 000         | 001                                              | 010                                              | 11           | 100          | 101          | 11.0                                             | 111          |                  |                       |                     |              |                            |

| 10         | REGISTER MOVE                | 0        | ٥        | 0    | ī          |       | 1 GRO           |        |      | REG        | 1<br>CT | REG        | 2<br>CT    |              | EG 2          |      |      | VALUATION             | 000         | 001                                              | 010                                              |              | i 100        | 101          | 110                                              | i            | 1                |                       | RF GIST             | TER SEI      | ISCT                       |

| 2 C        | SCRATCHPAD MOVE              | 0        | 0        |      | 0          | REGI  | STER            | GROU   | P    | RE         | G       |            | DPW        | DOUB         |               | D W  |      | MOV DIR:              | P+R<br>LEFT |                                                  |                                                  | •            | <del> </del> |              | •                                                | <del>i</del> | REGISTE<br>GROUP | R O                   | 1                   | 2            | 3                          |

| 3 C        | 4 BIT                        | 0        | ó        | -    | 1          | REGIS | STER (          | GROUP  | >,   | REG<br>SEL | MANI    | PULA       | TE         |              | T MA          | NIP  | •    | MANIP.                |             | ANI                                              |                                                  | EOR          | INC          | INC          | DEC                                              | DEC          | 1                | TA                    | FU<br>FT<br>FLC     | Y            | SUM<br>CMPX<br>CMPY        |

| 4C         | BIT TEST REL<br>BRANCH FALSE | 0        | 1 .      | 0    | 0          | REG   | ISTER           | GROU   | JP,  | REG<br>SEL | TE5T    | BIT        | DSP        | REL          | ATIVE         | BR   | ANCH | DSP SIGN :            | +           | -                                                |                                                  | 1            | ,            |              |                                                  |              | 3                | TO                    | FLD                 | L<br>MAR(A)  | YANY                       |

| <b>5</b> C | BIT TEST REL<br>BRANCH TRUE  | 0        | 1        | 0    | -          | REGI  | STER            | GRO    | JP   | REG<br>SEL | TEST    | BIT ,      | DSP        | RELA         | TIVE          | BRA  | NCH  | DSP SIGN :            | +           | -                                                | 1                                                | +            |              | <del> </del> | 1                                                | !            | 5<br>6<br>7      | CA                    | FLF<br>BICK<br>FLCN | M BR         | MSKX<br>MSKY<br>XORY       |

| 6 C        | SKIP WHEN                    | 0        | 1        | 1    | 0          | REGI  | STER<br>F SOR   | GROU   | P    | REG        | 5KIF    |            | т          |              | T TE          |      |      | SKIP TEST             |             | ALL                                              |                                                  | ALL<br>/ CLR | ANY/         | ALL/         | EQL /                                            | ALL /        |                  | LA<br>LB              | RES.                | FA           | DIFF                       |

| 7C         | READ/WRITE<br>MEMORY         | 0        | 1        | . 1  |            | R/W   | COUN            | T FA   | FL ; | DATA       | REG     | TW         |            | DATA         | TRA           | NSF  | ER   | R/W VAR:              | READ<br>NOP |                                                  | T .                                              | FAT          | FA+          | FA +         | CCK /                                            | FAI          |                  | FP                    | ::::                | TAS          | MAXM                       |

| 80         | MOVE B BIT                   | 1        | 0        | 0    | 0          | REGI  | STER (          | GROUP  |      |            |         |            |            | BIT          |               |      |      | REG SEL               | ¥           | Y                                                | F+1                                              | FL           |              |              | FLI                                              | FL           | 12<br>13<br>14   | LE<br>LF<br>CC        | XYST<br>RES.        | RES.<br>READ | CMND                       |

| 90         | MOVE 24 BIT<br>LITERAL       | 1        | 0        | ٥    | 1          | REC   | GISTER<br>EL SE | R GROU |      |            |         |            |            | NFICAL       |               |      | -    | TW SIGN.              | -           | <del>                                     </del> | 1                                                | 1            | 1            |              | 1                                                | <del></del>  | 15               | C D                   | CPU                 | WRIT         | NULL                       |

| 10 C       | SHIFT/ROTATE<br>T REG        | <b> </b> | 0        | 1    | 0          |       | NK REC          | GISTER |      |            | REG     | S/R        |            | FT SH        |               | ROTA | TE.  | 5/R VAR               | SHFT        | ROT                                              | <del>r                                    </del> | +            |              |              | 1                                                | ;            |                  |                       |                     |              |                            |

| HC         | EXTRACT FROM                 | 1        | 0        | 1    | ı          |       | SHT E           | BIT PO |      | ER         | SNK     | REG        | E          | XTRAC        |               | FIE  | LD   | SINK REG              | ×           | Y                                                | īΤ                                               | -            |              | i            | <del>:</del>                                     | 1            |                  |                       |                     |              |                            |

| IZ3C       | BRANCH<br>RELATIVE           | 1        | ı        | 0    | DSP<br>SGN |       |                 |        |      | E DIS      |         |            | NT         |              |               |      | _    | DSP SIGN:             | +           | +-                                               |                                                  |              |              |              | <del>                                     </del> |              | INDIV            |                       |                     |              | OME 4-BIT                  |

| 14.5C      | CALL<br>RELATIVE             | 1        | 1        |      | DSP<br>SGN |       | RE              | LATI   | VE C | ALLI       | ED A    | DDRE       | .55 t      | MAGI         | VITU          | DE   |      | DSP SIGN:             | +           | -                                                |                                                  |              | 1            |              |                                                  | 1            | NOTE:            |                       |                     |              | BELOW:                     |

|            |                              |          |          |      |            |       |                 |        |      |            |         |            |            |              |               |      |      |                       |             | :                                                | i                                                |              |              |              | 1                                                |              | ACCOR            | RE N<br>RDING<br>ENTI | TO T                | ERED H       | HERE<br>RDWARE             |

|            |                              |          |          |      |            |       |                 |        |      |            |         |            |            |              |               |      |      |                       |             |                                                  |                                                  |              |              |              | 1                                                |              | LA               | LB I                  | LCIL                | D LE         |                            |

| 4 D        | SHIFT/ROTATE<br>X OR Y       | 0        | 0        | 0    | 0          | 0     | i               | 0      | 0    | 5/R D      |         |            |            |              |               |      |      | X/Y VAR:<br>5/R, DIR: | X<br>SFT+   | Y                                                | - ROT                                            | - ROT →      |              |              | Ī                                                |              | MSB<br>23        |                       | Ľ                   |              | LSB<br>00                  |

| 50         | SHIFTARA                     | ٥        | 0        | 0    | 0          | 0     | ı               | 0      | T    | S/R,E      |         |            |            | OR RI        |               |      | D Y  | S/R, DIR              | SFT-        |                                                  |                                                  | RES.         | 1            |              |                                                  |              | BIT# B           | ICN                   | XYCN                | XYST         | FLCN                       |

| 6 D        | COUNT FA/FL                  | 0        | 0        | 0    | 0          | 0     | ı               | 1      | 0    | COUN       | T FA    |            |            | NUO:         | T 5C<br>SNITL |      | ₹ _  | COUNT FA/             | NØP         |                                                  |                                                  | FA t         |              | FA ŧ         | FL+                                              | FA +         | 0 0              | /L :                  | ×>×                 | x + 0        | FL + O<br>FL < SFL         |

| 7 D        | EXCHANGE DPW                 | 0        | 0        | 0    | 0          | 0     | 1               | 1      | 1    |            | INK     | DPW<br>E55 |            |              | OURC          |      | w    |                       |             |                                                  | İ                                                |              |              |              |                                                  |              |                  | UY I                  | X= Y<br>M5BX        | INT OR       | FL>SFL<br>FL=SFL           |

| 80         | SCRATCHPAD<br>RELATE FA      | 0        | 0        | 0    | 0          | 1     | 0               | 0      | 0    | /          | /       |            | D5P<br>SGN |              | T HA          |      |      | DSP SIGN:             | +           | -                                                |                                                  |              |              |              |                                                  |              | CCO C            | CI CC                 | 1 Y 1 C             | OR MOR       | RE OF:                     |

| <b>9</b> D | MONITOR                      | ō        | 0        | 0    | 0          | 1     | 0               | 0      | '    | LIT        | ERAL    | . 000      | URR        | ENC          | E IDE         | ENTI | FIER |                       |             |                                                  |                                                  | 1            |              |              | 1                                                |              |                  |                       |                     |              |                            |

|            |                              |          |          |      |            |       |                 |        |      |            |         |            |            |              |               |      |      |                       |             | i                                                | ì                                                |              |              |              |                                                  |              |                  |                       |                     |              |                            |

| 2 E        | CASSETTE<br>CONTROL          | 0        | 0        | 0    | 0          | 0     | 0               | 0      | ٥    | 0          | 0       | ı          | ٥          | CASS<br>MANI | ETTE<br>P VAR |      | 5/   | CASSETTE<br>MANIP:    |             |                                                  | ® STOP                                           | NUNDEF       | UNDEF        | UNDEF        | UNDER                                            | UNDEF        | CC & CD          |                       |                     |              |                            |

| 3E         | BIAS                         | ٥        | 0        | 0    | 0          | 0     | 0.              | 0      | 0    | 0          | 0       | 1          | 1          | V.           | BIA5          | TS   | TST  | TEST FLG:             | TST/        | TES                                              | 5                                                | FS           | NØP          | FCP          | NØP                                              | UNDEF        | CC0 C0           | NSOLE                 | ERVIC               | E REQU       | TERRUPT .<br>JEST INTERPT. |

|            | i i                          |          |          |      |            |       |                 |        |      |            |         |            |            |              |               |      |      |                       |             |                                                  | 1                                                |              |              |              | :                                                |              | CC2 RE           | AL TIM                | AG (DIS             | K (100 MS    | ) INTERPT.                 |

|            |                              |          |          |      |            |       |                 |        |      |            |         |            |            |              |               |      |      |                       |             |                                                  |                                                  |              |              |              | 1                                                |              | CD1 RE           |                       |                     |              |                            |

| 6 E        | CARRY FF MANIPULATE          | 0        | 0        | 0    | 0          | 0     | 0               | 0      | 0    | 0          | 1       | 1          | 0          |              | CYL           | CYF  | CYF  |                       |             |                                                  |                                                  |              |              |              |                                                  |              | CD2 RE           | SERV                  | E.D                 |              |                            |

| IF         | HALT                         | 0        | 0        | 0    | 0          | 0     | 0               | 0      | 0    | 0          | 0 -     | 0          | 0          | 0            | 0             | 0    | 1    |                       |             | •                                                |                                                  |              |              |              |                                                  |              | CD3 MI           |                       |                     | DATA         |                            |

|            |                              |          |          |      |            |       |                 |        |      |            | •       |            |            |              |               |      |      |                       |             |                                                  |                                                  |              |              |              |                                                  |              |                  |                       |                     |              |                            |

| 3 F        | NORMALIZE X                  | 0        | 0        | 0    | 0          | 0     | 0               | 0      | 0    | 0          | 0       | 0          | ۰          | 0            | 0             | 1    | ı    |                       |             |                                                  |                                                  |              |              |              |                                                  |              |                  |                       |                     |              |                            |

| ZERO       | NO OPERATION                 | °_       | 0        | 0    | 0          | 0     | •               | •      | •    | 0          | 0       | 0          | 0          | 0            | •             | •    | 0    |                       |             |                                                  |                                                  |              |              |              |                                                  |              |                  |                       |                     |              |                            |

|            |                              |          |          |      |            |       |                 |        |      |            |         |            |            |              |               |      |      |                       |             |                                                  |                                                  |              |              |              |                                                  |              |                  |                       |                     |              | •                          |

FIGURE 1 S-PROCESSOR MICRO-INSTRUCTIONS AND VARIANTS

COMPANY CONFIDENTIAL S-MEMORY PROCESSOR P.S. #2201 6760

- 3.0 PRODUCT DESCRIPTION

- 3.1 PROCESSOR REGISTERS

#### 3.1.1 MAR(A)

The MAR(A) Register is a micro-program address register capable of addressing micro-operators located in S-Memory. When used in this manner the lower-order 4 bits are ignored and the operator is fetched and stored in the M Register, bypassing the rotator (field isolation unit). IThe MAR(A) Register is comprised of 19 bits in S-Processor-1 and 20 bits in S-Processor-2.1

Binary increments from 0 through 4095 (multiplied by 16) may be added to or subtracted from MAR(A) by means of a high-speed carry adder that facilitates micro-program branching. MAR(A) is automatically incremented by binary 16 during run mode. Wrap-around can occur and is permitted.

Note: The fetch of an M-op from the last (highest addressed) 16 bits of installed S-Memory is not permitted since the automatic fetch of the next M-op will in some cases address portions of memory that are not present which, in turn, may result in parity errors. In addition, the maximum allowable S-Memory is subject to change.

The MAR(A) Register addresses 16-bit micro-operators in S-Memory by assuming them to be located at bit boundary addresses exactly divisible by 16. These addresses are obtainable by ignoring the rightmost 4 bits of the register.

The MAR(A) Register is addressable as a source and as a sink. When addressed as a source, all bits are produced. However, the rightmost 4 bits are masked to zeros. When addressed as a sink, the rightmost 4 bits of the source are moved to the rightmost 4 bits of the MAR(A) Register, but are not significant.

The MAR(A) Register also serves to address S-Memory for the READ/WRITE micro-operator. In this case the address of the next micro-operator is temporarily stored in a scratchpad holding register and the address in FA is moved to the

COMPANY CONFIDENTIAL S-MEMORY PROCESSOR P.S. #2201 6760

MAR(A) Register. The most significant bits of FA are ignored. The least significant bits are not ignored and are used to address memory at any bit location. The data is passed through the rotator.

Note: When addressing S-Memory via the READ/WRITE micro-operator, data returned from non-present memory locations will be zeros with odd parity if the address in MAR(A) is in-bounds, and zeros with wrong parity if the address in MAR(A) is out-of-bounds. In addition, if maximum S-Memory is installed, data and parity from the extremes of memory (lowest addressed portion if addressed in the forward direction and highest addressed portion if addressed in the backward direction) will be bit-ORed with the zeros and odd parity bits, obtained because of the out-of-bounds condition. This, in some cases, may result in parity error.

#### 3.1.2 M

The M Register (micro-register) is a 16-bit register used to hold the active micro-instruction (M-instruction or micro-operator or M-op). The state of this register is decoded to enable the different control signals within the processor to perform the operations called for by the M-Op. The M Register is broken into 4 fields for decoding that are structured such that 60 distinct M-ops can be decoded.

The M Register is addressable as a source and as a sink (destination). When used as a sink register, the source is bit-ORed with the upcoming M-op. Exception: In TAPE mode, the source is not bit-ORed with the upcoming M-op.

#### 3-1-3 A STACK

The A Stack is 16 words deep by 24 bits wide, does not have automatic hard overflow, and operates as a push-down stack with a last-in, first-out type of structure. Using this stack, the microcoded routines operate in the normal software call-return type of programming. This allows for a highly shared microcode structure and reduces the associated memory requirements. Although the A Stack is not intended to be used as an operand stack, it has purposely been made 24 bits wide to allow limited

COMPANY CONFIDENTIAL S-MEMORY PROCESSOR P.S. #2201 6760

capabilities for operand storage.

wrap around of the TAS pointer is provided. That is, 32 consecutive pushes will cause the TAS pointer to contain its original contents.

#### 3.1.4 TAS

The TAS (Top of Stack) Register is a 24-bit register which is the top of the A Stack. The TAS Register is addressable as a source and as a sink. References to TAS result in the stack being automatically pushed or popped.

#### 3.1.5 X AND Y

The X Register and the Y Register are 24-bit general purpose registers used primarily to hold and to act as a source for the two operands of the arithmetic and combinatorial unit. Each register is addressable as a source and as a sink.

Both registers, along with the L Register and the T Register, are capable of read/write operations with main memory.

Both registers are capable of the SHIFT/ROTATE operation. The X Register is capable of the NORMALIZE operation.

#### 3.1.6 L

The L Register is a 24-bit general purpose register used typically to hold logical flags for the micro-program code. The L Register, as well as each 4-bit group of L (denoted as LA, LB, LC, LD, LE, and LF) is addressable as a source and as a sink.

Since the L Register is addressable in 4-bit groups, its contents are available for analysis and alteration via the 4-bit function box. MANIPULATE, SKIP and BIT-TEST-BRANCH instructions can operate on L data.

The L Register is one of 4 registers (X, Y, L, and T) capable of read/write operations with main memory.

T

COMPANY CONFIDENTIAL S-MEMORY PROCESSOR P.S. #2201 6760

3.1.7

The T Register is a 24-bit general purpose register used primarily for the interpretation of S-Language instructions. The T Register, as well as each 4-bit group of T denoted as TA, TB, TC, TD, TE, and TF, is addressable as a source and as a sink.

Since the T Register is addressable in 4-bit groups, its contents are available for analysis and alteration via the 4-bit function box. MANIPULATE, SKIP and BIT-TEST-BRANCH instructions can operate on T data.

The T Register is one of 4 registers (X, Y, L, and T) capable of read/write operations with main memory.

The T Register is also capable of the SHIFT/ROTATE and EXTRACT operations.

3.1.8 FA

The FA Register (Field Address) is a 24-bit register used primarily to hold an absolute bit address for main memory. It has the capability of directly addressing any bit in the memory starting at any point.

The FA Register is addressable as a source and as a sink.

The FA Register is capable of being counted up or down by a literal in a micro-instruction or by the value contained in CPL in order to facilitate iteration through a memory field. It can be incremented or decremented by a value in a left scratchpad word. It also has the capability of being loaded, stored, or swapped along with FB into a double scratchpad word.

Neither overflow nor underflow of FA is detected. The value of FA may go through its maximum value or its minimum value and wrap around.

COMPANY CONFIDENTIAL S-MEMORY PROCESSOR P.S. #2201 6760

3.1.9 FB

The FB Register is a 24-bit register which can be functionally divided into three portions: a 4-bit FU (Field Unit) Register, a 4-bit FT (Field Type) Register, and a 16-bit FL (Field Length) Register.

The FB Register, as well as each 4-bit portion of FB (denoted as FU, FT, FLC, FLD, FLE, and FLF) is addressable as a source and as a sink. In addition, the 16-bit portion comprised of FLC, FLD, FLE, and FLF and denoted as FL is also addressable as source and as a sink.

The FU Register holds the length of the unit which makes up a field in memory. The FT Register holds field type information while the FL Register holds the total length of the field. FL is capable of describing fields up to 65,636 bits and can be adjusted up or down by a literal in a micro-instruction or by the value contained in CPL in order to facilitate iteration through a memory field.

Note: Overflow of FL is not detected. The value of FL will go through its maximum value and wrap around. Underflow of FL is detected and will not wrap around. The value of zero is left in FL.

Since the FB Register is addressable in 4-bit groups, its contents are available for analysis and alteration via the 4-bit function box. MANIPULATE, SKIP and BIT-TEST-BRANCH instructions can operate on FB data.

FB has the capability of being swapped along with FA into a double scratchpad memory word.

FU and FL along with corresponding portions of the first cell of scratchpad are used to set the various conditions of FLCN (see Section 3.1.11, FLCN) and the various conditions of the CP register (see Section 3.4.16, BIAS).

#### 3.1.10 SCRATCHPAD

A scratchpad memory of sixteen 48-bit words is provided to hold field descriptors during the iteration of operands. Some cells may be used to hold S-Language stack pointers

COMPANY CONFIDENTIAL S-MEMORY PROCESSOR P.S. #2201 6760

and other processor registers which are under constant manipulation.

The FU and FL portion of the FB Register and like portions of the first cell of the scratchpad are used to set the various conditions of FLCN (see Section 3.1.11, FLCN) and the various conditions of the CP register (see Section 3.4.16, BIAS).

#### 3.1.11 FLCN

FLCN (field length condition) is a 4-bit pseudo register that holds the result of a static comparison of the FL portion of the FB register and the corresponding portion of the first scratchpad word. It is addressable as a source only.

FLCN: | FL=SFL | FL>SFL | FL<SFL | FL neq 0 |

#### 3.1.12 BR AND LR

The LR and BR Registers are both 24-bit registers, addressable as sources and destinations.

#### 3.1.13 C

The C (control) Register is a 24-bit register which is not addressable is an entity but which is functionally divided into one 8-bit section and four 4-bit sections.

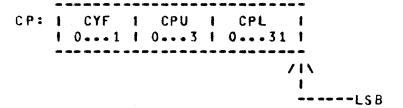

#### 3-1-13-1 CP (CYF, CPU, CPL)

The 8-bit section, addressed as CP, is comprised of the arithmetic unit carry flip-flop (CYF), the 2-bit unit control for the arithmetic unit (CPU) and the 5-bit variable data length control (CPL). CPU is addressable as a sink only.

COMPANY CONFIDENTIAL S-MEMORY PROCESSOR P.S. #2201 6760

#### 3.1.13.2

CA. CB. CC. CD

The remaining 16-bits of the C Register are addressable in 4-bit groups as CA, CB, CC and CD. Their contents are available for analysis and alteration via the 4-bit function box. MANIPULATE, SKIP and BIT-TEST-BRANCH instructions are applicable.

The 4-bit groups designated as CA and CB have no special functional assignment and are available as general purpose 4-bit storage registers.

The two 4-bit registers designated as CC and CD are used for the storage of various processor states and conditions as shown below:

| CC: | ı | S | TA | TE | L | . A 1 | <br>1 | I | NT | ER | RI | JP T | • | I | IT! | ER | RU | PT | 1 | <br>P | TROL<br>NL<br>RRUP |       | 1 1             |

|-----|---|---|----|----|---|-------|-------|---|----|----|----|------|---|---|-----|----|----|----|---|-------|--------------------|-------|-----------------|

| ·   |   |   |    |    |   | -     |       |   |    |    |    |      |   |   |     |    |    |    |   |       |                    | <br>/ | '1\<br>1<br>.SB |

COMPANY CONFIDENTIAL S-MEMORY PROCESSOR P.S. #2201 6760

| co: | 1 | MEMORY<br>READ DATA<br>PAR ERROR<br>INTERRUPT | 4 | RESERVED | 1 1 | RESERVED | 1<br>1<br>1 | RESERVED I        |

|-----|---|-----------------------------------------------|---|----------|-----|----------|-------------|-------------------|

|     | - |                                               | - |          | -   |          | -           | /1\<br> <br>  LSB |

The control panel state lamp flip-flop when true will cause the STATE lamp to light.

The timer interrupt signal is developed from the primary power frequency, field adjustable for either 50Hz or 60Hz. The interrupt signal is received and is used to set the appropriate CC bit once every 100 milliseconds.

The I/O Bus interrupt level is derived from the various I/O controls connected to the processor's I/O Bus. The level is the result of a service request by one or more controls and is used to set the interrupt bit every clock time.

The control panel interrupt level is derived from the on position of the control panel's INTERRUPT switch. The level from the switch is used to set the interrupt bit every clock time.

The memory read data parity error interrupt is set as a result of a parity error signal received from the interface to main memory.

No reaction occurs as a result of any interrupt until the micro-program tests the interrupt bit.

A micro-instruction or the control panel CLEAR pushbutton is capable of resetting a bit in the C Register. The bit being reset will be false for at least one clock period following the reset regardless of the continued existence of the condition to set the bit (e.g., control panel or service request interrupts). Any test micro-operator executed in this clock period will find the bit false. If the condition does not continue to exist beyond the reset time, a failure to set the bit may occur (e.g., timer interrupt).

COMPANY CONFIDENTIAL S-MEMORY PROCESSOR P.S. #2201 6760

3.1.14

MAXS. MAXM

MAXS is a 24-bit pseudo register that can be field-adjusted to give the actual size of the main memory installed in the system. It is addressable as a source only. MAXS has 4K-byte resolution. The least significant 15 bits and the most significant 5 (S-Processor-1) or 4 (S-Processor-2) bits of the register are always zeroes. MAXM, also a 24-bit pseudo register, always has a value of zero for the S-Processors.

3.1.15

U

The U Register is a 16-bit register used primarily to accumulate the bit-by-bit input from the control panel's tape cassette. The U Register is addressable as a source register only.

In RUN mode, if data is not yet available in the register, the micro-operator will be delayed. Data not accepted in time will be lost.

In TAPE mode, the register's contents are automatically moved to the M Register for execution except when executing micro-operators that reference the U Register as a source. In these cases the source data is moved directly from the U Register to the destination and will not be treated as an instruction to be executed. The next instruction from the tape will follow this data. For MOVE 24-BIT LITERAL, the 8 bits of the literal in the M Register are also moved to the destination. For CONDITIONAL BRANCH, the A Register may be changed but the next micro-operator read from the tape will also be executed.

Note: In RUN mode, the U Register may not be addressed after the issuance of a CASSETTE STOP micro.

3.1.16

DATA

DATA is a 24-bit pseudo register that can act as a source or as a destination. It is used to transfer data to and from the I/O Bus. When it is used as a source, the

COMPANY CONFIDENTIAL S-MEMORY PROCESSOR P.S. #2201 6760

processor. generates the RC (RESPONSE COMPLETE) signal to the interface and accepts the 24-bits of data from the bus. When used as a destination, the processor generates the RC signal to the interface and the data from the designated source to the bus.

3.1.17 CMND

CMND (Command) is a 24-bit pseudo register that can act as a destination only. It is used to transfer commands to devices on the I/O Bus. The processor generates the CA signal to the interface and moves the data (or the command) from the designated source to the bus.

3-1-18 NULL

NULL is a 24-bit pseudo register that can act as a source and as a destination. When addressed as a source, all zeros are supplied to the destination. When addressed as a destination, the source data is not accepted. However, NULL is useful as a destination in order to pop the TAS Register without affecting other registers.

3-1-19 READ

READ is a 24-bit pseudo register that is not permitted to be addressed either as a source or as a destination in the S-Processors. It is used in conjunction with a memory read operation from the control panel. (See P.S. #1913 1747 for meaning in the M-Processors.)

3-1-20 WRIT

WRIT is not permitted to be addressed as a source or as a destination, but is used in conjunction with a memory write operation from the control panel.

COMPANY CONFIDENTIAL S-MEMORY PROCESSOR P.S. #2201 6760

#### 3.2 24-BIT FUNCTION BOX

The 24-bit "function box" is composed of a 24-bit arithmetic unit and a 24-bit combinatorial unit. It has as data inputs the contents of the X and Y Registers and the carry flip-flop (CYF). It also uses the CPU and CPL portions of the C Register.

All results from the combinatorial section are generated immediately and are continuously available to the micro-programmer. A move to one of the input registers or an alteration of a value in the CP portion of the CR egister immediately generates a new result. The results are available to the next micro-instruction and are accessed by moving the contents of a result register to a destination register or by testing one of the 4-bit condition registers.

The results are most of the commonly used functions between two operands. These include the And, Or, Exclusive-Or, sum, carry-out, difference, and borrow functions and the set of equal-to, greater-than, and less-than relationals. The results of the unary operations of complementation and masking are also available.

The results of the arithmetic unit are under control of the CPU and the CPL Registers as follows.

| CPU | UNIT TYPE      | POSSIBLE CPL VALUES | DATA TYPE    |

|-----|----------------|---------------------|--------------|

| 00  | 1-bit operands | 1 to 24             | Binary       |

| 00  | 4-bit operands | 4,8,12,16,20,or 24  | 4-bit binary |

| 10  | Undefined      |                     |              |

11 Undefined

For valid arithmetic operations, the operand length (as specified by CPL) must be an exact multiple of the length of the unit specified by CPU.

The contents of each of the registers described in the following subsections are immediately available to the micro-programmer.

COMPANY CONFIDENTIAL S-MEMORY PROCESSOR P.S. #2201 6760

3.2.1

SUM

SUM is a pseudo register equal to the sum of the X, Y, and CYF Registers (X + Y + CYF). Zero bits in the more significant bit positions of the 24-bit result are produced when the length as determined by CPL (5-bit variable data length control) is less than 24. Results are not defined for CPL values 25 through 31. The carry-out level is generated from the bit position of the output specified by CPL. If CPL = 0, the carry-out level is equal to CYF. If CPL = 1, the carry-out level is generated from the rightmost bit of X, Y and CYF. See Section 3.1.13.1, CP (CYF, CPU, CPL).

If CPU (2-bit arithmetic unit control) = 00, the binary sum is produced. See Section 3.1.13.1, CP (CYF, CPU, CPL).

If CPU = 01, the decimal sum is produced by considering the X and Y inputs to be comprised of six 4-bit units. Results are not defined for non-Binary Coded Decimal (BCD) units. CPL must be a multiple of four.

If CPU = 10 or 11, the sum is undefined.

3.2.2

DIFF

DIFF is a pseudo register equal to the difference of the X-Y-, and CYF Registers (X - Y - CYF). Zero bits appear in the more significant bit positions of the 24-bit result when the length as determined by CPL is less than 24. Results are not defined for CPL values 25 through 31. The borrow-out level, generated from the static comparison of all 24-bits of X & Y-, is true if X < Y or if X = Y and CYF is true.

If CPU = 00, the binary difference is produced.

If CPU = 01, the decimal difference is produced by considering the X & Y inputs to be comprised of six 4-bit units. Results are not defined for non-BCD units. CPL must be a multiple of four.

If CPU = 10 or 11, the difference is undefined.

COMPANY CONFIDENTIAL S-MEMORY PROCESSOR P.S. #2201 6760

A negative result is in 2's complement form in the binary case and in 10's complement form in the decimal case.

#### 3.2.3 XANY, XORY, XEDY

XANY (X and Y), XORY (X or Y), and XEOY (X exclusive-or Y) are 24-bit pseudo registers that hold the results of the specified logical functions. Zero bits are produced in the more significant bit positions of the 24-bit result when the length as determined by CPL is less than 24. Results are not defined for CPL values 25 through 31.

#### 3.2.4 CMPX, CMPY

CMPX (complement of X) and CMPY (complement of Y) re 24-bit pseudo registers that hold the 1's complement of the specified registers. Zero bits are produced in the more significant positions of the 24-bit result hen the length as determined by CPL is less than 24. CR values 25 through 31 have undefined results.

#### 3.2.5 MSKX, MSKY

MSKX, (mask of X) and MSKY (mask of Y) are 24-bit pseudo registers that hold the mask of the appropriate register (X or Y). Beginning with LSB of X or Y, the number of bit positions included in the mask is determined by the value of CPL. Zero bits are produced in the more significant bit positions of the 24-bit result when the length as determined by CPL is less that 24. Results are not defined for CPL values 25 through 31.

#### 3.2.6 BICN

BICN (binary conditions) is a 4-bit pseudo register that holds the following binary conditions, considered as a 4-bit group, and addressable as a source only:

COMPANY CONFIDENTIAL S-MEMORY PROCESSOR P.S. #2201 6760

NOTE: CYF is also addressed by the SET CYF M-Instruction as well as being available in the (8-bit) group

addressed as CP.

BICN: I LSUY I CYF I CYD I CYL I

I I I Carry Out Level

I Borrow-Out Level

Carry Flip-Flop

Least Significant Unit of Y

The carry-out level is a function of X, Y, CPL, and CPU. See Section 3.2.1, SUM. The borrow-out level is a function of X, Y, and CYF. See Section 3.2.2, DIFF.

LSUY is true if the least significant unit of Y is equal to 1 and CPU = 00, or if the least significant unit of Y is equal to 1001 and CPU = 00.

#### 3.2.7 XYCN

XYCN (XY condition) is a 4-bit pseudo register that holds the following relational conditions, considered as a 4-bit group and addressable as a source only:

XYCN: 1 MSBX 1 X=Y 1 X<Y 1 X>Y 1

MSBX is true if the bit in X referenced by CPL is 1. CPL = references the rightmost bit of X while CPL = 24references the leftmost bit. MSBX = 0 if CPL = 0.

The relational results are based on the binary value of all 24-bits of X and Y.

COMPANY CONFIDENTIAL S-MEMORY PROCESSOR P.S. #2201 6760

#### 3.2.8

XYST

XYST (XY states) is a 4-bit pseudo register that holds the following relational conditions, considered as a 4-bit group and addressable as a source only:

LSUX is true when the least significant unit of X is equal to 1 and CPU = 00, or when the least significant unit of X is equal to 1001 and CPU = is not equal to 00.

The relational results are based on the binary value of all 24 bits of X or Y.

INI is true if any of the following conditions as reflected in (INCN) CC, and CD are true. (See Section 3.2.9, INCN and 3.1.13.2, CA, CB, CC, CD.)

X

| 1.   | Timer Interrupt         | cc(1)  |

|------|-------------------------|--------|

| 2.   | Bus I/O Interrupt       | CC (2) |

| `3 • | Control Panel Interrupt | cc (3) |

4. Memory Parity Error Interrupt CD(0)

software His

COMPANY CONFIDENTIAL S-MEMORY PROCESSOR P.S. #2201 6760

#### 3.2.9 INCN: PERR

INCN (interrupt conditions) and PERR (Parity error) are 4-bit pseudo registers which are not physically present in the S-Processors. When either is addressed as a source, a binary value of zero is yielded; when addressed as destinations, the data is lost.

#### 3.3 4-BIT FUNCTION BOX

The 4-bit function box (4-bit arithmetic and combinatorial section of the processor) can accept, as one of its inputs, the contents of any of the following 4-bit registers and pseudo registers.

| TA | <b>T</b> B | TC  | TD  | TE  | TF  |

|----|------------|-----|-----|-----|-----|

| LA | LB         | LC  | LD  | LE  | LF  |

| FU | FT         | FLC | FLO | FLE | FLF |

| CA | СВ         | CC  | CO  |     |     |

| CA | CB         | CC  | CD  |     |     |

Outputs include the result of most of the commonly used functions between two operands; for example: Set. And. Or. Exclusive-Or. Binary Sum and Difference (both modulo 16). Outputs are directed back to the source register.

The sum and difference output can be tested for overflow and underflow respectively and, based on the test, a skip of one instruction can be made.

The 4-bit function box also provides for the selective testing of one of the bits of a four-bit group and relative branching based on the result of the test. A skip of one instruction based on the result of testing on a combination of up to four bits in the group is also provided.

BICN, XYCN, XYST, and FLCN are not actually registers but can be sourced as if they were. They can be changed only as a result of changing the condition which they reflect.

COMPANY CONFIDENTIAL S-MEMORY PROCESSOR P.S. #2201 6760

3.4 M-INSTRUCTIONS

3.4.1 REGISTER MOVE

FORMAT: 1 OP 1 SOURCE 1 SOURCE 1 DESTINATION 1 DESTINATION 1 FORMAT: 1 CODE 1 REGISTER 1 REGISTER 1 REGISTER 1 GROUP # 1 GROUP # 1 GROUP # 1 GROUP # 1 O --- 15 1 O --- 3 1 O --- 15 1

Move the contents of the source register to the destination register. If the source register is smaller than the destination register, data are right justified with left (most significant) zero bits supplied. If the source register is larger than the destination register, data are truncated from the left.

The contents of the source register are unchanged unless it is also the destination register.

## Exceptions:

- 1. When M is used as a destination register in run or step mode, the operation is changed to a bit-OR which modifies the next micro-operation. It does not modify the instruction as stored in the memory. In tape mode, no bit-OR takes place.

- 2. CPU, HRIT, READ, and CMND are excluded as source registers.

- BICN, FLCN, XYCN, XYST, INCN, READ, WRIT, SUM, CMPX, CMPY, XANY, XEOY, MSKX, MSKY, XORY, DIFF, MAXS, MAXM, and U are excluded as destination registers.

- 4. When DATA, SUM, or DIFF is designated as a source, CMND and DATA are excluded as destinations.

- 5. U is excluded as a source in STEP mode but is permitted as a source in RUN or TAPE mode. When U is used as a source, TAS, MAR(A) and M registers are excluded as destinations.

COMPANY CONFIDENTIAL S-MEMORY PROCESSOR P.S. #2201 6760

6. When A, M, CP, or DATA is designated as a source, all 4-bit registers are prohibited as destinations.

#### 3.4.2 SCRATCHPAD MOVE

FORMAT: | CODE | GRP # | SLCT# | O TO SCRTCHPD | WORD | WO

Move the contents of the register (SCRATCHPAD) to SCRATCHPAD (register). If the move is between registers of unequal lengths, the data is right justified with left (most significant) zero bits supplied or with data truncated from the left, whichever is appropriate.

The contents of the source register are unchanged.

## Exceptions:

- 1. When M is used as a destination register, the operation is changed to a bit-DR which modifies the next micro-operation. It does not modify the instruction as stored in the memory.

- CPU, WRIT, READ, and CMND are excluded as source registers.

- 3. BICN, FLCN, XYCN, XYST, INCN, READ, WRIT, SUM, CMPX, CMPY, XANY, XORY, XEOY, MSKX, MSKY, DIFF, MAXS, MAXM and U are excluded as destination registers.

- 4. M as a source results in a transfer of 24 zeroes.

- 5. U is excluded as a source in STEP mode.

COMPANY CONFIDENTIAL S-MEMORY PROCESSOR P.S. #2201 6760

3.4.3

WAP F WITH DOUBLEPAD WORD

Move the contents of the FA and FB registers to a holding register. Move the contents of the left and right word of the source scratchpad word to the FA and FB Register respectively. Move the contents of the holding register to the left and right word of the destination scratchpad word.

3.4.4

NAM 8-BIT LITERAL

FORMAT: 4 CUDE 1 REGISTER 1 1 1000 1 GROUP # 1 0...255 1 1 0...15 1

Move the 8-bit literal given in the instruction to the destination register. If the move is between registers of unequal lengths, the data is right justified with left (most significant) zero bits supplied. The register select number is assumed to be 2.

Exceptions:

READ and WRIT are excluded as destination registers.

COMPANY CONFIDENTIAL S-MEMORY PROCESSOR P.S. #2201 6760

#### 3.4.5

24-BIT LITERAL

I OP 1 DESTINATION 1 24-BIT LITERAL 1 FORMAT: I CODE I REGISTER I O...MAX 1 1001 | GROUP # 1 0 . . . 15 1

Move the 24-bit literal given in the instruction to the destination register. If the move is between registers of unequal lengths, the literal is truncated from the left. The register select number is assumed to be 2.

## Exceptions:

M, CP, READ, and WRIT are excluded as destination registers.

#### 3.4.6

READ/HRITE MEMORY

# 1 OP # DIRECTION | COUNT # RGSTR # # FIELD # MEMORY | FORMAT: | CODE | O to RGSTR | VRNTS | OO = X | DIRECTION | | FIELD | | 1 0111 1 1 TO MEMORY | 0...7 | 01 = Y | 1 0 - POSITIVE | LENGTH | 1 10 = T 1 1 - NEGATIVE 1 0 ... 26 1 1 1 11 = L 1

> Move the register's (memory's) contents to the memory (register). If the value of the memory field length is less than 24, the data from memory is right justified with left (most significant) zero bits supplied while the data from the register is truncated from the left.

The contents of the source is unchanged.

Register FA contains the bit address of the memory field while the memory field direction sign and memory field length is given in the instruction.

COMPANY CONFIDENTIAL S-MEMORY PROCESSOR P.S. #2201 6760

If the value of the memory field length as given in the instruction is zero, the value in CPL is used.

Memory field length values (or CPL values if MFL = 0) of 25 and 26 are truncated to the value 24. When used on a write operation, the value 25 and 26 cause odd and even parity respectively to be written into memory regardless of the parity of the read data.

For a description of the count variants, see Section 3.4.7, COUNT FA/FL.

## 3.4.7 COUNT FA/FL

|         | 1 | OP   |      | 1 | COUNT    | 1 | LITE | RAL | 1 |

|---------|---|------|------|---|----------|---|------|-----|---|

| FORMAT: | 1 | CODE |      | 1 | VARIANTS | 1 | 0    | 31  | 1 |

|         | 1 | 0000 | 0110 | 1 | 0 7      | 1 |      |     | 1 |

|         | - |      |      |   |          |   |      |     | - |

Increment (decrement) binarily the designated register(s) by the value of the literal contained in the instruction or by the value of CPL if the value of the literal is zero.

Neither overflow nor underflow of FA is detected. The value of FA may go through its maximum value or its minimum value and wrap around.

Overflow of FL is not detected. The value of FL will go through its maximum value and wrap around. Underflow of FL is detected and will not wrap around. The value of zero is left in FL.

Literal values (or CPL values if LIT = 0) of 25 through 31 are truncated to the value 24.

BURROUGHS CORPORATION COMPANY CONFIDENTIAL COMPUTER SYSTEMS GROUP S-MEMORY PROCESSOR SANTA BARBARA PLANT

P.S. #2201 6760

#### Count variants are as follows:

V = 000 No count 001 Count FA Up 010 Count FL Up 011 Count FA Up and FL Down 100 Count FA Down and FL Up 101 Count FA Down 110 Count FL Down 111 Count FA Down and FL Down

#### 3.4.8 SCRATCHPAD RELATE FA

I OP I RESERVED I SIGN OFF I LEFT SCRATCHPAD I CODE I I SPAD WORD I WORD ADDRESS I 0000 1000 I 000 I 0-POSITIVE I 0...15 I 1-NEGATIVE I I FORMAT: 1 CODE

Replace the contents of the FA Register by the binary sum of the FA Register and specified scratchpad register.

Neither overflow nor underflow of FA is detected. The value of FA may go through its maximum value or its minimum value and wrap around.

#### 3.4.9 EXTRACT FROM REGISTER T

-----1 OP 1 ROTATE 1 DESTINATION 1 EXTRACT 1 1 1 01 - Y 1 10 - T 1 i i ii - L i

Rotate Register 7 left by the number of bits specified and then extract from the right the number of bits specified. Move this result to the destination register supplying left most (most significant) zero bits if the extract

COMPANY CONFIDENTIAL S-MEMORY PROCESSOR P.S. #2201 6760

count is less than 24.

The contents of the source register are unchanged unless it is also the destination register.

A rotate value of 24 is equivalent to 0.

#### 3.4.10 SHIFT/ROTATE REGISTER T LEFT

|         | 1 | ΩP   | i | DSTNATN | 1 | DSTNATN | ı | S/R | VARIANT | ŧ | S/R       | ł |

|---------|---|------|---|---------|---|---------|---|-----|---------|---|-----------|---|

| FORMAT: | 1 | CODE | 1 | REGISTR | 1 | REGISTR | 1 | 0 - | SHIFT   | 1 | BIT COUNT | i |

|         | ŧ | 1010 | 1 | GROUP # | 1 | SELECT# | ı | 1 - | ROTATE  | 1 | 024       | 1 |

|         | 1 |      | 1 | 015     | ı | 0 2     | ı |     |         | į |           | ı |

|         |   |      |   |         |   |         |   |     |         |   |           |   |

SHIFT (ROTATE) Register T left by the number of bits specified and then move the 24-bit result to the destination register. If the move is between registers of equal lengths, the data is right justified with data truncated from the left.

The contents of the source register are unchanged unless the source register is also the destination register.

Zero fill on the right and truncation on the left occurs for the SHIFT operation.

If the value of the SHIFT/ROTATE count as given in the instruction is zero, the value given in CPL is used.

## Exceptions:

- 1. When M is used as a destination register, the operation is changed to a bit-or which modifies the next micro-operation. It does not modify the instruction as stored in the memory.

- BICN, FLCN, XYCN, XYST, INCN, READ, and WRIT.

COMPANY CONFIDENTIAL S-MEMORY PROCESSOR P.S. #2201 6760

#### 3.4.11

#### SHIFT/ROTATE REGISTER X/Y LEFT/RIGHT

1 OP | 1 S/R | L/R | X/Y | S/R | FORMAT: 1 CODE | VARIANT | VARIANT | VARIANT | BIT | 1 0000 0100 | 0-SHIFT | 0-LEFT | 0-X REG | COUNT | 1 1-ROTATE | 1-RIGHT | 1-Y REG | 0...24 |

SHIFT (ROTATE) Register X or Register Y left (right) by the number of bits specified.

Zero fill on the right and truncation on the left occurs for the left shift. Zero fill on the left and truncation on the right occurs for the right shift.

#### 3-4-12

#### SHIFT REGISTERS XY LEFT/RIGHT

FORMAT: | CODE | SHIFT | L/R | SHIFT | BIT | O000 0101 | O | O-LEFT | COUNT | O00001 |

ONCY

SHIFT the concatenated X and Y registers left (right) by one bit. The register X is the leftmost (more significant) half of the concatenated 48-bit XY register.

# ONU

Zero fill on the right and truncation on the left occurs for the left shift. Zero fill on the left and truncation on the right occurs for the right shift.

If the value of the shift count as given in the instruction is not 1, an undefined result will occur.

COP OUT

COMPANY CONFIDENTIAL S-MEMORY PROCESSOR P.S. #2201 6760

3.4.13

NORMALIZE X

SHIFT the X Register left while counting FL down, until FL=0 or until the bit in X referenced by  $C^{PL}=1$ . Zeros are shifted into the rightmost end of X.

CPL = 1 references the rightmost bit of X while CPL = 24 references the leftmost bit of X. CPL is undefined.

3-4-14