Burroughs

a i i

FIELD ENGINEERING

# TECHNICAL MANUAL

INTRODUCTION AND OPERATION

FUNCTIONAL DETAIL

> CIRCUIT DETAIL

ADJUSTMENTS

MAINTENANCE PROCEDURES

INSTALLATION PROCEDURES

RELIABILITY IMPROVEMENT NOTICES

> OPTIONAL FEATURES

# COPYRIGHT © 1972 BURROUGHS CORPORATION DETROIT, MICHIGAN 48232 AA38664672

Burroughs believes that the information described in this manual is accurate and reliable, and much care has been taken in its preparation. However, no responsibility, financial or otherwise, is accepted for any consequences arising out of the use of this material. The information contained herein is subject to change. Revisions may be issued to advise of such changes and/or additions.

# INDEX

# Page No.

# INTRODUCTION AND OPERATION – SECTION I

| Control Operations         |      |      |     |      |      |   |   |   |  | 5 |

|----------------------------|------|------|-----|------|------|---|---|---|--|---|

| Control to Disk Cartridge  | Int  | terf | ace | Le   | evel | s |   |   |  | 3 |

| Disk Pack Control Mnemo    | onic | G    | los | sary | 7.   |   |   |   |  | 6 |

| General Operation          | •    |      |     |      |      |   |   |   |  | 1 |

| Initializing the Cartridge |      |      |     |      |      |   |   |   |  | 3 |

| Operations                 |      |      |     |      |      |   |   |   |  | 1 |

| Pause Operation            |      |      |     |      |      |   |   |   |  | 3 |

| Read Burroughs Format      |      |      |     |      |      |   |   |   |  | 2 |

| Read/Write Immediate .     |      |      |     |      |      |   |   |   |  | 3 |

| Read/Write Index           |      |      |     | •    | •    | • |   | • |  | 2 |

| Standard Burroughs Form    | nat  |      | •   | •    |      |   |   |   |  | 1 |

| Test Operation             |      |      |     |      |      |   | • |   |  | 3 |

| Write Burroughs Format     |      |      |     |      |      |   |   |   |  | 2 |

# FUNCTIONAL DETAIL – SECTION II

| Basic Data Flov | W  |     |     |  |  |   | • |   | • | • | 5  |

|-----------------|----|-----|-----|--|--|---|---|---|---|---|----|

| Detailed Flow   |    |     |     |  |  |   |   |   |   |   | 21 |

| General Buffer  | Сс | ont | rol |  |  | • |   | • |   |   | 13 |

| I/O Descriptor  | 5  |     |     |  |  |   |   | • |   |   | 1  |

| Test OP .       |    |     |     |  |  |   |   |   |   |   | 1  |

| Pause OP.       |    |     |     |  |  |   |   |   |   | • | 1  |

| Read OP.        |    |     |     |  |  |   |   |   |   |   | 1  |

| Write OP.       |    |     |     |  |  |   |   |   |   | • | 2  |

| Logic Description .    |     |      |     |     |            |    |    |    |   |   |   | 16 |

|------------------------|-----|------|-----|-----|------------|----|----|----|---|---|---|----|

| Operation              |     |      |     |     |            |    |    |    |   |   |   | 6  |

| Registers and Logic De | scr | ipti | ion |     |            |    |    |    |   |   |   | 4  |

| Result Information .   |     |      |     |     |            |    |    |    |   |   |   | 2  |

| a                      |     |      | •   |     |            | •  | •  | •  | • | • | • | 6  |

| MAINTENANCE PRO        | CE  | DU   | RE  | S - | <u>– S</u> | EC | TI | ON | v |   |   |    |

| Confidence Routine .   |     |      |     |     |            |    |    | •  | • |   |   | 1  |

| Hardware Testpoints    |     |      |     |     |            |    |    |    |   |   |   | 8  |

| How to Load Cartridge  | Τe  | est  |     |     |            |    |    |    |   |   |   | 1  |

| I/O Debug Routine .    |     |      |     |     |            |    |    | •  |   |   |   | 3  |

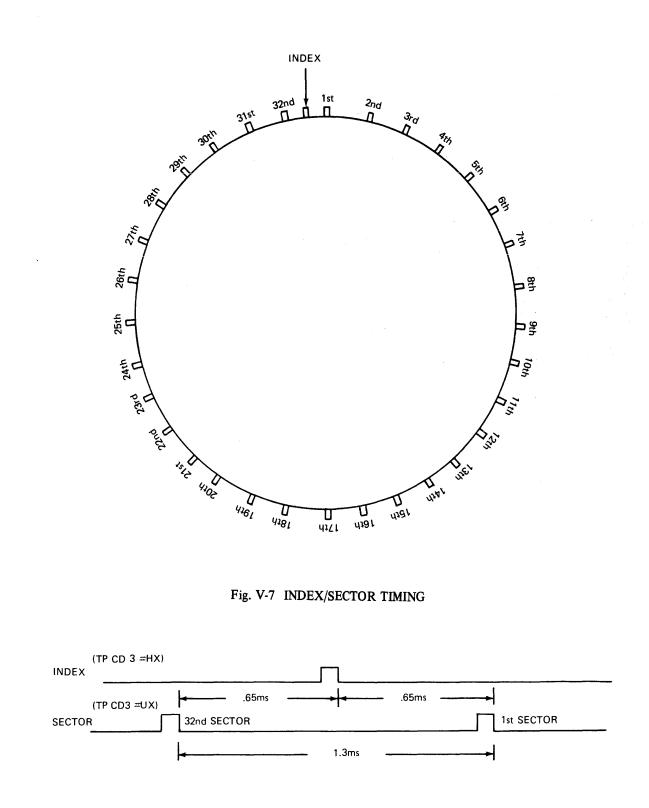

| Index Sector Timing.   |     |      |     |     |            |    |    |    |   |   |   | 15 |

| Interface Testpoints . |     |      |     |     |            |    |    |    |   |   |   | 13 |

| Test Procedures        |     |      |     |     |            |    |    |    |   |   |   | 6  |

| Run Instructions . '.  |     | •    | •   | •   | •          |    | •  |    |   |   | • | 1  |

# INSTALLATION PROCEDURES - SECTION VI

| Electrical Installation |  | ٢. |   |   |   |  | 2 |

|-------------------------|--|----|---|---|---|--|---|

| Logic Preparation .     |  |    |   |   |   |  |   |

| Peripheral to I/O Adap  |  |    |   |   |   |  |   |

| Physical Installation . |  |    | • | • | • |  | 1 |

# Page No.

#### INTRODUCTION

The Disk Cartridge Control provides for the attachment of the B9480-2 Dual Disk Cartridge Drive to the B1700. It operates as a  $1 \times 2$  or a  $1 \times 4$  Exchange depending upon whether 1 or 2 dual drives are attached. See Figure I-1.

Fig. I-1 CONFIGURATION

#### **GENERAL OPERATION**

The Disk Cartridge Control provides for six basic read/write operations. In addition to a normal read or write, the control may perform a Read Index, Read Immediate, Write Index or Write Immediate. Most of the data transfers between control and disk will be via the normal read and write operation codes with the other codes used primarily for initialization of the disk.

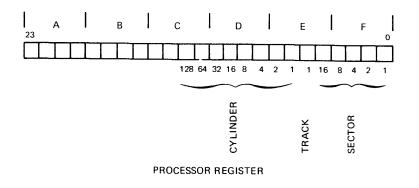

The Disk Cartridge Control operates in the sector mode only using the Burroughs Standard format for the data. The disk sector or area to be read or written is specified by a fourteen bit (expandable) File Address. The addresses range binarily from 0 through 12991 for the cartridge used on this control. There are 32 sectors per track and two tracks per cylinder, one on the upper surface of the disk and one on the lower surface.

Each platter has a total of 203 cylinders of which 200 may be used with the other three used as spares. It is a function of the software to recognize which cylinders are spare and not address those cylinders.

#### STANDARD BURROUGHS FORMAT

The Control will read/write standard Burroughs format except when a read/write immediate or <u>read/write index</u> is commanded. Standard Burroughs format is shown in Figure I-2 along with the times associated with each portion for the 2200 BPI disk.

| stor                              | in the second | ADDRESS – 2 Bytes                       | The State of the S | Y K           | Sec                   |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------------|

| PREAMBLE<br>33 Bytes<br>170.28 us | 1 Byte<br>00011110                                                                                              | Cylinder Track Sector<br>0-202 0-1 0-31 | DATA<br>180 Bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | LPC<br>1 Byte | POSTAMBLE<br>25 Bytes |

| 5 Lat                             | 5.16 us                                                                                                         | 10.32 us                                | 928.8 us                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5.16 us       | 130.28 us             |

#### Fig. I-2 STANDARD BURROUGHS FORMAT

#### **OPERATIONS**

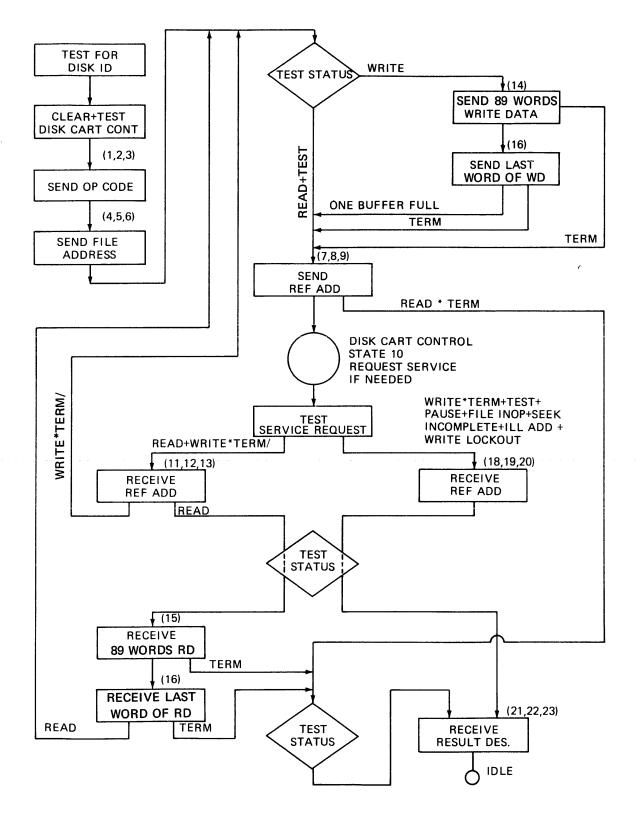

The following paragraphs are intended to give a brief description of the six disk read/write operations along with the Test and Pause Operations. A detailed flow is provided in Section II of this manual along with a description of the various OP Codes and the Result Descriptor returned at the end of the operations.

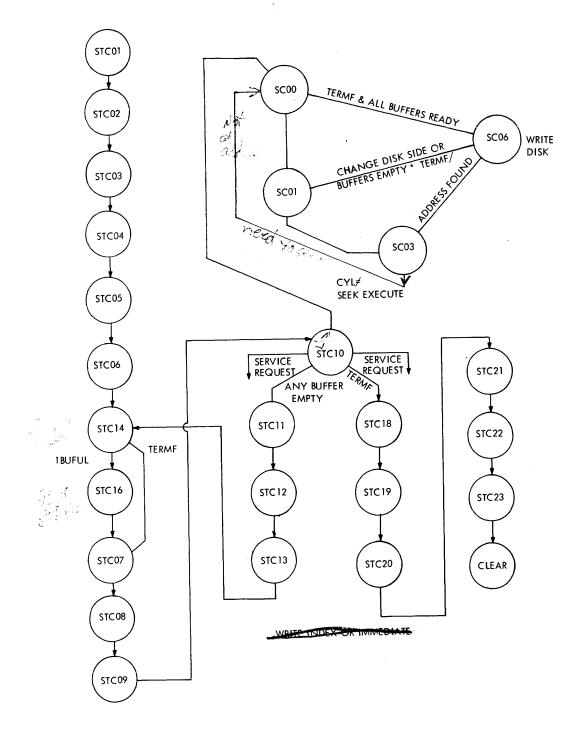

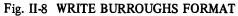

# WRITE BURROUGHS FORMAT

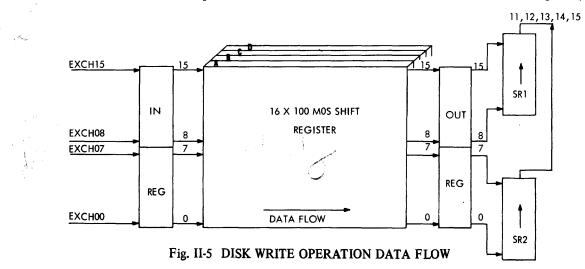

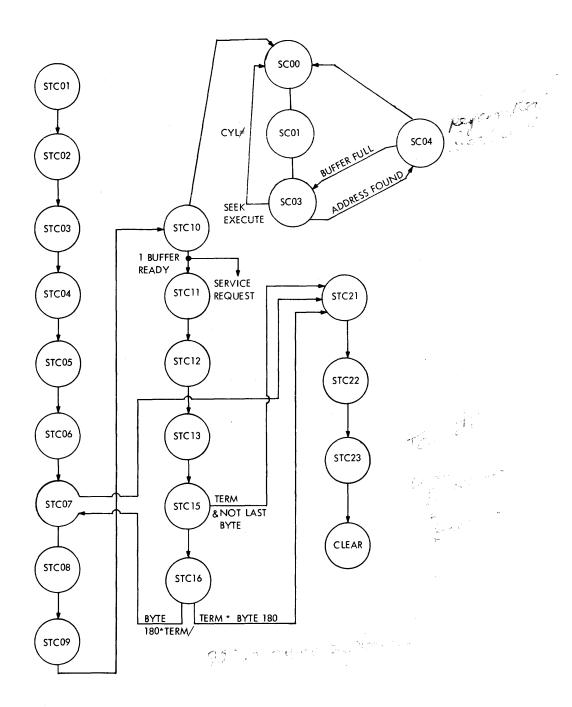

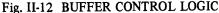

The Write Burroughs Format OP-Code is intended for normal storage of information on the disk. The Processor first must send the OP Code to the Control where it is stored in the OP Register. Having received the OP Code, the Control will advance to a status where it can receive the File Address from the processor. With the File Addressed stored, the processor then proceeds to send the data to the Control. Data is not immediately written onto disk but rather stored in one of the four 16 x 100 MOS Shift Registers. It should be noted that the data transfer occurs for two bytes (16 bits) at a time rather than the standard one byte per transfer which is used in most controls. If the processor reaches an end address ehreby it determines that all the data has been transferred, it will send a Terminate Command. The Terminate Command will allow the disk to proceed in the operation. If the Terminate Command is not received prior to filling a buffer the disk will proceed with the write operation and the processor must recognize this with the status count which is returned at every data transfer time during Phase B of the cycle.

Assuming one buffer is filled or a Terminate received, the control proceeds to receive the three Reference Address Bytes which it stores in an Address Memory. At this point several actions can occur. If a Terminate had not been received, the control will set a Service Request and proceed to send the Reference Address back to the processor when the processor has recognized the service request. This can be done as the disk has four of the MOS Shift Registers and only one is full at this time. While the Control allowed the service request to be generated and allows more data to be received, it also proceeds to start the writing of the previous buffer load onto disk.

Before the actual write occurs however, the Control determines by reading addresses from the disk that the cylinder address read from the disk compares with the cylinder address which has been placed in the File Address Register. If the cylinder address compares, the Control waits for sector coincidence at which time the write can begin. The write operation actually writes the address back onto the disk along with the sync pattern and the data. The Control also will generate a Longitudinal Parity Character to be written at the end of the 180 bytes of data.

The Longitudinal Parity Character (LPC) is an odd sum of the bits. If the cylinder address did not compare the Control would initiate a seek and terminate the operation by storing a Result Descriptor. It would be a function of the Processor to wait for the seek to complete itself and re-initiate the same write command in order to cause the data to be written. The Control will continue writing data on disk until a Terminate Command is received.

#### **READ BURROUGHS FORMAT**

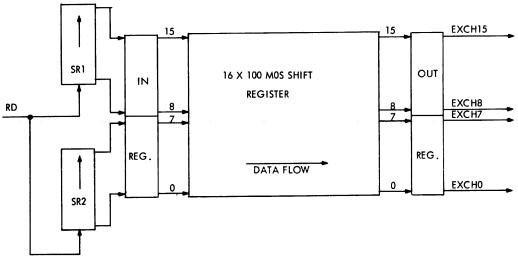

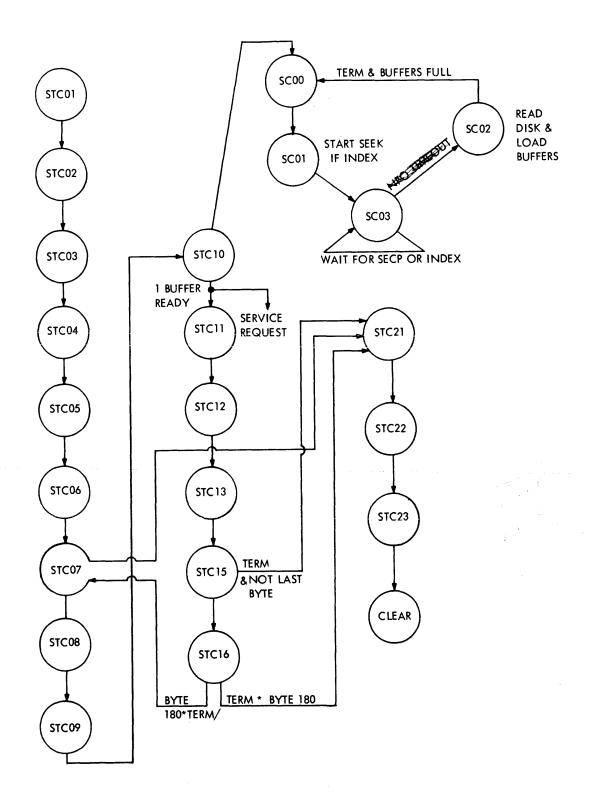

The Read Burroughs Format OP-Code is intended for normal reading of information from the disk. Like the Write OP, the control first receives the OP Code and File Address from the Processor which are stored in their respective registers. Having received the File Address, the disk control will receive the three Reference Address Bytes and store them in Address Memory. It is at this point the actual disk operations begin with the Control determining in the same manner that the cylinder address in the File Address Register compares with the cylinder address being read from the disk. If they do not compare the operation is terminated and a seek is executed prior to storage of the Result Descriptor. If the cylinder addresses do compare then sector coincidence is sought at which time data may be read from disk and stored in the  $16 \times 100$  MOS Shift Register. When one of the buffers ( $16 \times 100$  MOS Shift Registers) is full, a Service Request is generated by the control.

The Processor having recognized the service request, will transfer in the reference address bytes and begin reading the data from the buffer two bytes at a time. While the processor is emptying the buffer, the control is continuing the read and filling the other three MOS Shift Registers. While the buffer is being unloaded the processor may determine that it has received all the data required and send a Terminate Command, at which time the operation is completed and a result descriptor stored. If the buffer is emptied and a terminate is not received, the control will receive the Reference Address back from the Processor and store it in Address Memory. The control proceeds back to a point where it can determine if another buffer is full and generate a service request to empty the buffer. In any event the read will continue until a Terminate Command is received.

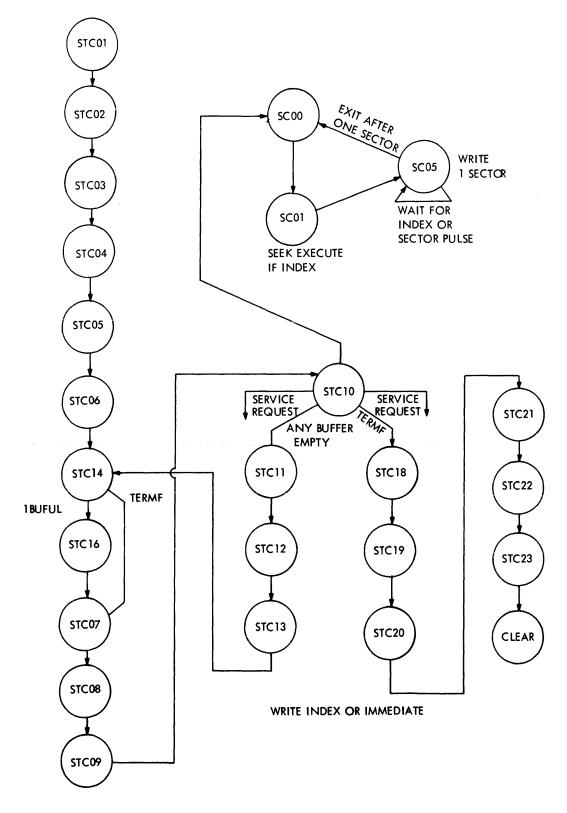

#### **READ/WRITE INDEX**

The Read and Write Index commands will perform in a similar manner as the Read/Write Burroughs format. Major differences are that the read/write does not occur for a specific sector but for the first sector following the index pulse received from the disk. Read/Write Index does imply a seek in that a cylinder address is given. The second major difference is on the data transfers. The read will read all data from the sector including preamble and store the information in Processor memory and the write must receive all data from the memory including preamble.

#### **READ/WRITE IMMEDIATE**

Read/Write Immediate performs similar to the Read/Write Index operations except that a seek is not implied. Reading or Writing will occur immediately following the first sector pulse received from the disk.

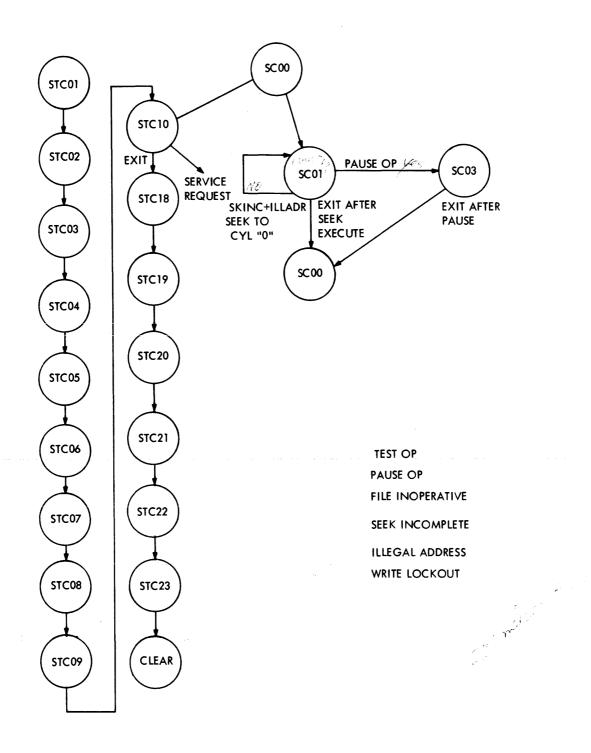

#### TEST OPERATION

The Test Operation is performed to test various status conditions of the disk which may normally be checked with the read/write operations also. The Test Operation in addition to checking the disk status such as not ready, seeking, position not settled to give a few examples also will return a control I/D to the Processor. The Processor can use the Control I/D to determine what type of control is on a specific channel such as Card Reader Control, Line Printer Control or Disk Control to mention a few.

#### PAUSE OPERATION

The Pause Operation is used primarily as a convenience to the Processor for the I/O operations. To give an example assume that the disk has just completed a read operation and has stored a Result Descriptor. Before that same OP Code can be performed again (software controlled and not a hardware restriction) the processor must be assured that the data has been handled. The software can do this by handling the data and clearing the result descriptor which was stored. If the processor therefore finds the Result Descriptor not cleared, rather than issuing the Read Command again, it sends a pause command to the disk. After the disk has been in a pause for the period of time required, it sends a Result Descriptor to the processor. Due to the soft I/O Driver the Result Descriptor is not stored; however, the SR serves as a reminder to the Processor that it is waiting to perform an active operation.

#### INITIALIZING THE CARTRIDGE

A new cartridge does not have any sector addresses written on the disk. Before Standard Burroughs Format can be written on the disk, it must be initialized by having the sector addresses written on the cartridge.

The initialization procedure is performed by using the various Read/Write commands. The Read/Write Index commands have been specifically developed for the initialization procedure.

#### CONTROL TO DISK CARTRIDGE INTERFACE LEVELS (REFER TO FIGURE I-3)

Logical "1" is signified by a voltage level between 0 and 0.5 volts; logical "0" by a voltage level between +3 and +5 volts.

#### CYLINDER ADDRESS

Cylinder Address is transmitted on eight lines. These lines are strobed into an 8-bit address register by the Cylinder Seek Execute pulse to be internally decoded. Each cylinder is addressed by the following binary notation:

|               | Decimal<br>Cylinder | Binary<br>Address |

|---------------|---------------------|-------------------|

|               | 000                 | 00 000 000        |

|               | 001                 | 00 000 001        |

|               | 002                 | 00 000 010        |

| 200 Cylinders |                     |                   |

| -             | 198                 | 11 000 110        |

|               | 199                 | 11 000 111        |

| 3 Spares      | 200                 | 11 001 000        |

|               | 201                 | 11 001 001        |

|               | 202                 | 11 001 010        |

## CYLINDER SEEK EXECUTE

This line provides a pulse that strobes the address information into the 8-bit address register in the file unit. This pulse initiates the Cylinder Seek Action.

#### HEAD SELECT

This line selects the top disk surface when in the "true" state and the bottom disk surface when in the "false" state.

| DISK<br>CARTRIDGE<br>DRIVE | CYLINDER ADDRESS<br>8-LINES<br>HEAD SELECT<br>CYLINDER SEEK EXECUTE<br>WRITE ENABLE<br>READ ENABLE<br>WRITE DATA<br>UNIT SELECT<br>FILE OPERATIONAL<br>POSITION SETTLED<br>READ DATA<br>DATA CLOCK<br>INDEX<br>SECTOR<br>ILLEGAL ADDRESS<br>SEEK INCOMPLETE | (LEVEL)<br>(PULSE)<br>(LEVEL)<br>(LEVEL)<br>(LEVEL)<br>(LEVEL)<br>(LEVEL)<br>(LEVEL)<br>(PULSE)<br>(PULSE)<br>(LEVEL)<br>(LEVEL) | DISK<br>CARTRIDGE<br>CONTROL |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------|

|                            |                                                                                                                                                                                                                                                             |                                                                                                                                  |                              |

Fig. I-3 CONTROL TO DISK CARTRIDGE INTERFACE

#### WRITE DATA

The Write Data line carries the serial-by-bit NRZ write data from the control.

## WRITE ENABLE

This line turns on the write amplifiers and edge erase. The line must go "false" after the write operation has been completed.

#### **READ ENABLE**

This line enables the read discriminator circuits. When the line is in the "true" state, the discriminator output will be placed on the Read Data and Clock lines.

1

#### WRITE LOCKOUT

This line indicates to the control that the Write Lockout plug has been pushed up in the Disk Cartridge, will disable writes.

#### FILE OPERATIONAL

This line indicates to the control that the Disk Drive is ready for operation. When the Drive has achieved operational speed, all interlocks and safety circuits are satisfied, and the line goes to a "true" level.

#### POSITION SETTLED

This line supplies a level to the control indicating that the heads are positioned and stabilized. The Drive is then ready to accept read or write commands.

#### READ DATA

The Read Data line transmits serial-bt-bit NRZ read data to the controller. The level of this line is maintained for the entire bit period.

#### CLOCK

This line transmits the 1.55 MHz write or read clock for the data. The clock output is used by the controller to strobe the data.

#### **INDEX**

The Index line supplies a pulse for the index reference point on the disk. The index pulse is used to synchronize Read/ Write Index Operations.

#### SECTOR

This line supplies a pulse at the beginning of each sector.

#### **ILLEGAL ADDRESS**

This line supplies a level when the cylinder address is greater than 202 during a Cylinder Seek Execute command. A valid address and a new Cylinder Seek Execute Pulse will reset the Illegal Address Line.

#### SEEK INCOMPLETE

This line supplies a true level 200 milliseconds after the Cylinder Seek Execute Pulse "if" The Seek Complete line indicates that an address has not been executed. This line will be reset by the next Seek Execute Pulse.

# UNIT SELECT

Unit Select consists of one line. When in the "true" state the functions applicable to access, control, and data transmission of one drive is selected. When in the "false" state the functions applicable to access, control and data transmission of the other drive is selected.

#### CONTROL OPERATIONS

The Disk Cartridge Control responses to four commands: Read, Write, Test and Pause. These operations are detailed in Section II.

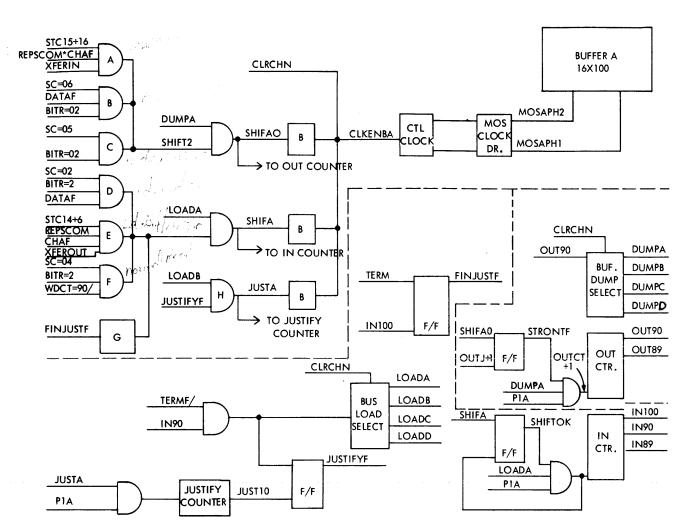

The control will transfer 16 bits of data at a time between the processor and the control. Data in the control is stored in four 100 x 16 buffers. These buffers may be loading while another buffer is unloading or vice versa. This allows the processor to communicate with the disk control at a rate up to 1.55 megabits per second.

# PERIPHERAL OPERATION

The B9480-2 consists of two separate disk cartridge drives with a common power supply. The operation of the two drives are independent of each other. The Disk Cartridge Control may communicate with one drive at a time.

| Storage (Full Track)<br>(180 Byte Format) | 2,457 M Bytes<br>2,304 M Bytes |

|-------------------------------------------|--------------------------------|

| Áverage Access Time                       | 90 M Sec                       |

| Disk Surfaces                             | 2                              |

| Tracks Per Inch                           | 100                            |

| Rotation Rate                             | 1500                           |

| Number of Cylinders                       | 200+3 Spare                    |

| Number of Tracks per Cylinder             | 2                              |

| Number of Sectors per Track               | 32                             |

| Sector Data Size                          | 180 Bytes                      |

| Transfer Rate (Bits/sec)                  | 1.55 MHz                       |

| Bits per Inch                             | 2200                           |

# Fig. I-4 B9480-2 DISK DRIVE CHARACTERISTICS

# DISK PACK CONTROL MNEMONIC GLOSSARY

| ADDRF   | ADDRESS FLIP-FLOP is set when a sync pattern is detected from the Disk Pack to indicate "Address                                                                                                             |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADF     | Mode".<br>ADDRESS FLIP-FLOP is set when the Control is entering the operation required to determine the Disk-OP<br>and find the correct address.                                                             |

| ASEL    | A SELECT is true when the address unit portion selects either Unit 0 or Unit 1 which are both on Disk Pack<br>Drive "A".                                                                                     |

| BITR=n  | BIT RING is a counter which is used to count the number of bits accumulated in the Shift Register for a disk read operation or the number of bits shifted from the Shift Register to disk for the disk write |

| DIVOTD  | operation.<br>BLANK COUNTED is used during preamble time to insert a 22 64 uses delay after Based Enable has been                                                                                            |

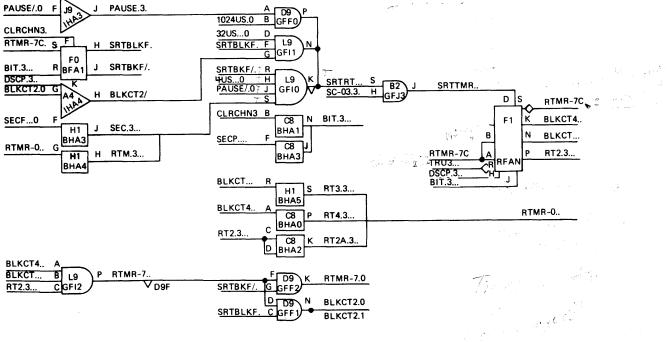

| BLKCTR  | BLANK COUNTER is used during preamble time to insert a 32-64 usec delay after Read Enable has been sent to the Disk Pack.                                                                                    |

| BSEL    | "B" SELECT is true when the unit portion of the Disk address is selecting either Unit 2 or Unit 3 which are                                                                                                  |

|         | located on Disk Pack Drive "B".                                                                                                                                                                              |

| BUFCT   | BUFFER COUNTER is a counter which indicates which of the four MOS Buffers in the Disk Control are to                                                                                                         |

|         | be either loaded or emptied depending upon the operation being performed.                                                                                                                                    |

| BUFCT=n | BUFFER COUNTER EQUAL "N" where N=A, B, C or D.                                                                                                                                                               |

| BUFFUL  | BUFFER FULL LEVEL is a level indicating all four buffers are full.                                                                                                                                           |

| BUFFULF | BUFFER FULL FLIP-FLOP is a flip-flop set as a result of Buffer Full Level. (BUFFUL)                                                                                                                          |

| BUFRDY  | BUFFER READY is a level indicating at least one of the four buffers contain information.                                                                                                                     |

| BUFSEMP | BUFFERS EMPTY is a level indicating all four of the MOS Buffers are empty.                                                                                                                                   |

| CCERR   | CYCLIC CHECK ERROR is true during a Disk Read operation if the Cyclic Check Character is not correct                                                                                                         |

|         | at the end of the sector being read.                                                                                                                                                                         |

| CCR     | CYCLIC CHECK REGISTER is a register used to accumulate a character which will be written at the end                                                                                                          |

|         | of each sector. The character written, referred to as cyclic check character, will be a longitudinal parity                                                                                                  |

|         | character. During a read operation the control will accumulate the character and compare it to the CCR                                                                                                       |

|         | character written on the disk. If the two characters do not compare, a parity error has occurred.                                                                                                            |

|         |                                                                                                                                                                                                              |

| CHAF            | CHANNEL ACTIVE FLIP-FLOP is set when a command is on the Exchange lines and the channel number                                                                                                       |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | corresponds to that of the Disk Pack Control indicating that the control is "active".                                                                                                                |

| CHANHI<br>CLEAR | CHANNEL HIGH is true if the command at Command Active time (CA) is for the Disk Pack Control.<br>CLEAR when true will cause the Disk Pack Control to reset all registers, counters and miscellaneous |

| ULLAK           | flip-flops.                                                                                                                                                                                          |

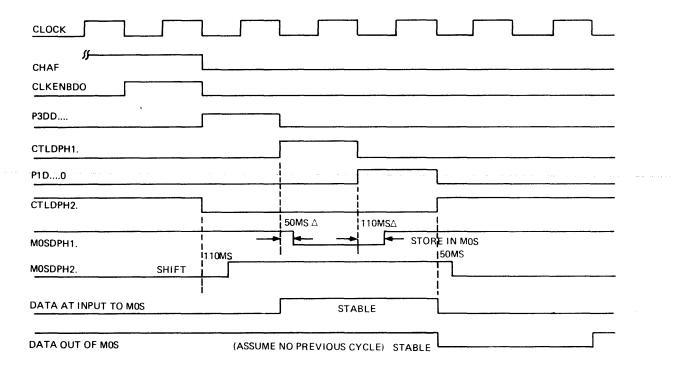

| CLKENBn         | CLOCK ENABLE BUFFER N comes true to enable the Shift Register Clock in order shift the MOS Buffer.                                                                                                   |

| O LINDI (BII    | N=one of the four buffers (A,B,C or D).                                                                                                                                                              |

| CLRCHAN         | CLEAR CHANNEL is a flip-flop which sets to allow the Disk Pack Control to reset all flip-flops, counters                                                                                             |

|                 | and registers. CLRCHAN is a reset of a system CLEAR                                                                                                                                                  |

| CNTLMSK         | CONTROL MASK is returend during a Test Service Request command from the processor indicating the Disk                                                                                                |

|                 | Control Service Request Flip-Flop is set. The Control Mask is a bit returned which corresponds with the                                                                                              |

|                 | channel number of the Disk Pack Control.                                                                                                                                                             |

| CNTOUT          | COUNT OUT is set to enable the Out Counter to count the number of 16 bit words being read from one of the four MOS Buffers.                                                                          |

| COMACT          | COMMAND ACTIVE is a one clock period pulse received from the Processor when a command is placed                                                                                                      |

| COMACI          | on the Exchange. (Note: COMACT corresponds to CA in the I/O Sub-System Technical Manual descrip-                                                                                                     |

|                 | tion)                                                                                                                                                                                                |

| COMCODEL        | COMMAND CODE LATCHES are the latches which are used to store the command received from the                                                                                                           |

|                 | processor at command active time.                                                                                                                                                                    |

| COMP1           | COMPARE ONE is true when the number of buffers emptied is equal to the number of buffers that was                                                                                                    |

|                 | loaded.                                                                                                                                                                                              |

| COMPF           | COMPARE FLIP-FLOP is set when COMP1 (See above) is true and a terminate command has been received                                                                                                    |

| COMP            | indicating the end of the operation.                                                                                                                                                                 |

| COMP≠           | COMPARE NOT EQUAL is true when the CCR accumulated on a Disk Read operation is not the correct                                                                                                       |

| COMP.A          | bit configuration.<br>COMPARE"A" and COMPARE "B" are two comparitors used to compare the address received from the                                                                                   |

| COMP.B          | processor to the address being read from the disk in order to indicate when the disk read/write can begin.                                                                                           |

|                 | They are also used to compare for a CCR error.                                                                                                                                                       |

| COMP=           | COMPARE EQUAL is true when the address received from disk is equal to the address obtained from the                                                                                                  |

|                 | Processor.                                                                                                                                                                                           |

| CONV            | CONTROL VARIANT is true when the command from the Processor is one of the control variants                                                                                                           |

|                 | commands.                                                                                                                                                                                            |

| COUNTL          | COUNT LEVEL is true to enable the "In Counter" which counts the number of words being stored in                                                                                                      |

|                 | one of the four MOS Buffers.                                                                                                                                                                         |

| CTLNPH2         | CTL "N" Phase Two is the output of the Shift Register Clock Logic which indicates the logic is in the                                                                                                |

| CYL8-1F         | initialized state. "N" is equal to one of the four buffers A,B,C or D.<br>CYLINDER FLIP-FLOPS is that part of the File Address Register which stores the cylinder portion of the                     |

|                 | address received from the Processor.                                                                                                                                                                 |

| CYL=F=          | CYLINDER EQUAL FLIP-FLOP is true when the cylinder address received from the disk is equal to the                                                                                                    |

|                 | cylinder address contained in the cylinder portion of the File Address Register.                                                                                                                     |

| DATAF           | DATA FLIP-FLOP is set when an address compare occurs which will take the control out of the "Address                                                                                                 |

|                 | Mode" and place it in the "DATA MODE".                                                                                                                                                               |

| DPBUF           | DUMP BUFFER is true to allow the shift of data from the buffer designated either placing data on the disk                                                                                            |

|                 | or sending information to the Processor.                                                                                                                                                             |

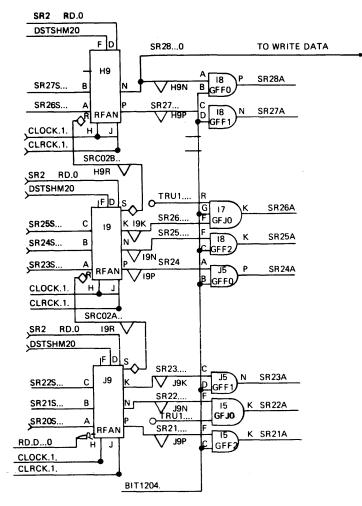

| DPCNTR          | DUMP COUNTER counts the number of buffers which have been "dumped" (emptied).                                                                                                                        |

| DPEF            | DISK PARITY ERROR FLIP-FLOP is set to report in the Result Descriptor that a parity error has occurred<br>on the Disk Read operation.                                                                |

| DTOT1F          | DISK TIME OUT FLIP-FLOPS are set as a result of the Index Pulse from the disk and are used to prevent                                                                                                |

| DTOT2F          | the Control from "hanging up" if the correct disk address cannot be found in one to two revolutions of the                                                                                           |

|                 | disk after the seek has been completed.                                                                                                                                                              |

| DUMPN           | DUMP BUFFER "N" where N=A,B,C or D and is used to address the buffer which is to be/being unloaded.                                                                                                  |

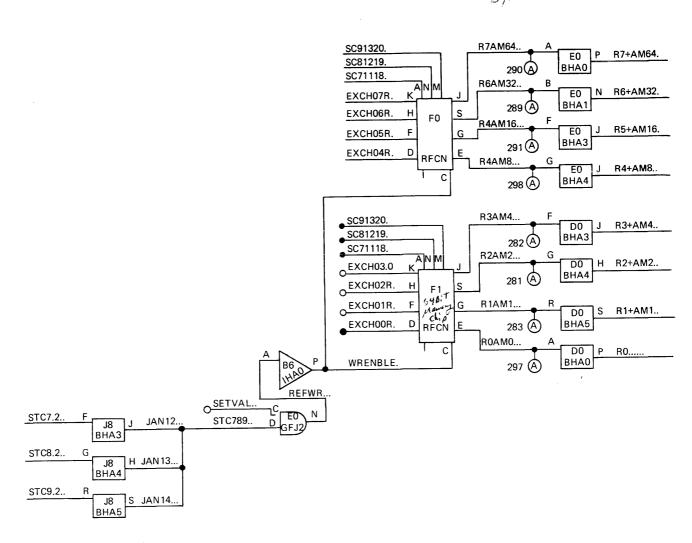

| EXCHnn          | EXCHANGE where nn=00-23 are the twenty-four exchange lines between the control and processor.                                                                                                        |

| EXCEPT.         | EXCEPTION is set to cause the exception bit in the Result Descriptor to be on if an error condition is                                                                                               |

|                 | detected or if the unit is not ready (See Result Descriptor).                                                                                                                                        |

|                 |                                                                                                                                                                                                      |

| EXITF                                                                                                               | EXIT FLIP-FLOP is set to indicate the end of a disk operation either as a result of an error or all buffers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FAR+1                                                                                                               | empty and a terminate command received.<br>FILE ADDRESS REGISTER PLUS ONE is true to upcount the register by one at the end of an operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| FINJSTF                                                                                                             | to keep the File Address in sync with the address being written on disk or read from disk.<br>FINISH JUSTIFY FLIP-FLOP is set as a result of a terminate received while loading a buffer and will                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| FINJSTN                                                                                                             | cause the data in the buffer to be right justified.<br>FINISH JUSTIFY BUFFER "N" is true to cause a justification of the appropriate buffer as a result of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| FL.OPL                                                                                                              | (FINJSTF).<br>FILE OPERATION LEVEL is true to indicate that the disk is ready for operation. This means that power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| FSFF                                                                                                                | is on, all interlocks are closed and a pack is inserted in the device.<br>FIRST SECTOR FLIP-FLOP is used on a disk write operation to upcount only the sector portion of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| HDSET                                                                                                               | file address in order to write the correct sector address on disk while writing the preamble.<br>HEAD SETTLED is true when a continuous sector write causes the disk to cross from the top of the disk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| HEADF                                                                                                               | to the bottom and indicates only an address search is to occur and not a seek.<br>HEAD FLIP-FLOP is a portion of the File Address Register and when reset indicates the address is on the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| HEADFF                                                                                                              | top side of the disk and when reset indicates the address is on the bottom side of the disk.<br>HEAD FLIP-FLOP "F" is used in conjunction with HEADF in the incrementing of an address where a<br>crossover from the bottom of a disk to the top (next track) is required. In this case the seek will only<br>require a movement of one track and the control will wait for the seek to complete and continue the<br>operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ILL.ADD                                                                                                             | ILLEGAL ADDRESS is true when the cylinder address is greater than 202 during a seek execute to the disk. A valid address and a new seek execute will reset the Illegal Address line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| INCT+1                                                                                                              | IN COUNTER PLUS ONE is used to count the characters (two characters at a time) that are stored in the MOS SHIFT BUFFER. These characters may be received either from the disk or the processor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| INXDF                                                                                                               | INDEX FLIP-FLOP is set during a Write Immediate or Write Index command at SC=05. On the Write Index it is set when an Index Pulse and a Sector Pulse have been received from the disk. On the Write Immediate it is set with the first sector pulse from the disk. In either of the above cases it indicates that the write is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| a an                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| INXF                                                                                                                | to start.<br>INDEX FLIP-FLOP is set with the reception of an Index Pulse from the disk. The position settle signal must also be true.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| INXF                                                                                                                | to start.<br>INDEX FLIP-FLOP is set with the reception of an Index Pulse from the disk. The position settle signal must also be true.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |