# B 1800/B 1700 DISK PACK CONTROL II

# **TECHNICAL MANUAL**

#### FIELD ENGINEERING PROPRIETARY DATA

The information contained in this document is proprietary to Burroughs Corporation. The information or this document is not to be reproduced, shown, or disclosed outside Burroughs Corporation without written permission of the Patent Division.

This material is furnished for Burroughs Field Engineering Personnel, and is not furnished to customers except under special License Agreement.

THIS DOCUMENT IS THE PROPERTY OF AND SHALL BE RETURNED TO BURROUGHS CORPORATION, BURROUGHS PLACE, DETROIT, MICHIGAN 48232.

FUNCTION

AND OPERATION

MAINTENANCE TECHNIQUES

THEORY

OF OPERATION

1

2

3

5

Burroughs believes that the information described in this manual is accurate and reliable, and much care has been taken in its preparation. However, no responsibility, financial or otherwise, is accepted for any consequences arising out of the use of this material. The information contained herein is subject to change. Revisions may be issued to advise of such changes and/or additions.

Correspondence regarding this document should be addressed directly to Burroughs Corporation, P.O. Box 4040, El Monte, California 91734, Attn: Publications Department, TIO-West.

# B 1800/B 1700 Disk Pack Control II

# LIST OF EFFECTIVE PAGES

| Page          | Issue      | Page           | Issue    |

|---------------|------------|----------------|----------|

| Title         | . Original | 5-9            | Original |

| ü'            | . Original | 5-10           | Blank    |

| iii           | . Original | 5-11 thru 5-15 | Original |

| iv            | . Blank    | 5-16           | Blank    |

| v thru viii   | . Original | 5-17 thru 5-33 | Original |

| 1-1 thru 1-18 | . Original | 5-34           | Blank    |

| 4-1 thru 4-5  | . Original | 5-35 thru 5-41 | Original |

| 4-6           | . Blank    | 5-42           | Blank    |

| 5-1 thru 5-7  | . Original | 5-43 thru 5-45 | Original |

| 5-8           | . Blank    | 5-46           | Blank    |

î

.

ſ

# TABLE OF CONTENTS

| Section |                                                                      | Page       |

|---------|----------------------------------------------------------------------|------------|

| 1       | FUNCTION AND OPERATION                                               |            |

|         |                                                                      | 1-1        |

|         |                                                                      | 1-1        |

|         |                                                                      | 1-1        |

|         |                                                                      | 1-2        |

|         |                                                                      | 1-2        |

|         |                                                                      | 1-2        |

|         |                                                                      | 1-2        |

|         |                                                                      | 1-2        |

|         |                                                                      | 1-3        |

|         |                                                                      | 1-3        |

|         |                                                                      | 1-6        |

|         |                                                                      | 1-6        |

|         | *                                                                    | 1-0        |

|         | •                                                                    | 1-0<br>1-9 |

|         | Initialize Operator                                                  |            |

|         | *                                                                    |            |

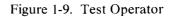

|         | Test Operator                                                        |            |

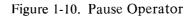

|         | Pause Operator                                                       |            |

|         | Stop Operator                                                        |            |

|         | Result Status (Result Descriptor)                                    |            |

|         | Operation Complete                                                   |            |

|         | Exception Condition                                                  |            |

|         | Not Ready                                                            |            |

|         | Read Parity Error                                                    |            |

|         | DPE/Drive Failure                                                    |            |

|         | Write Lockout                                                        |            |

|         | Slip Occurred                                                        |            |

|         | Unit Identification                                                  |            |

|         | Address Parity Error                                                 |            |

|         | Sector Address Error (type 225 only)                                 |            |

|         | Timeout                                                              |            |

|         | I/O Subsystem Configuration                                          |            |

|         | Seeking                                                              |            |

|         | Seek Status Flip-Flop Set                                            |            |

|         | Transmission Error                                                   | -18        |

|         | Control Type                                                         | -18        |

|         | Special Flags                                                        | -18        |

| 4       | MAINTENANCE TECHNIQUES                                               |            |

|         |                                                                      | 4-1        |

|         |                                                                      | 4-1        |

|         |                                                                      | 4-1        |

|         | Type 206 Drives – Notes $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ |            |

ŕ

v

# TABLE OF CONTENTS (Cont)

# Section

٠

| 5 | THEORY OF OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   | Logic Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | Input Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   | Output Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

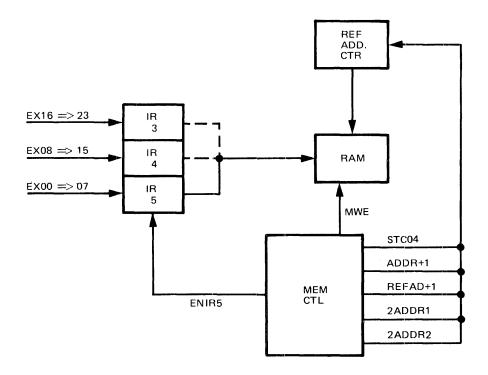

|   | RAM Storage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

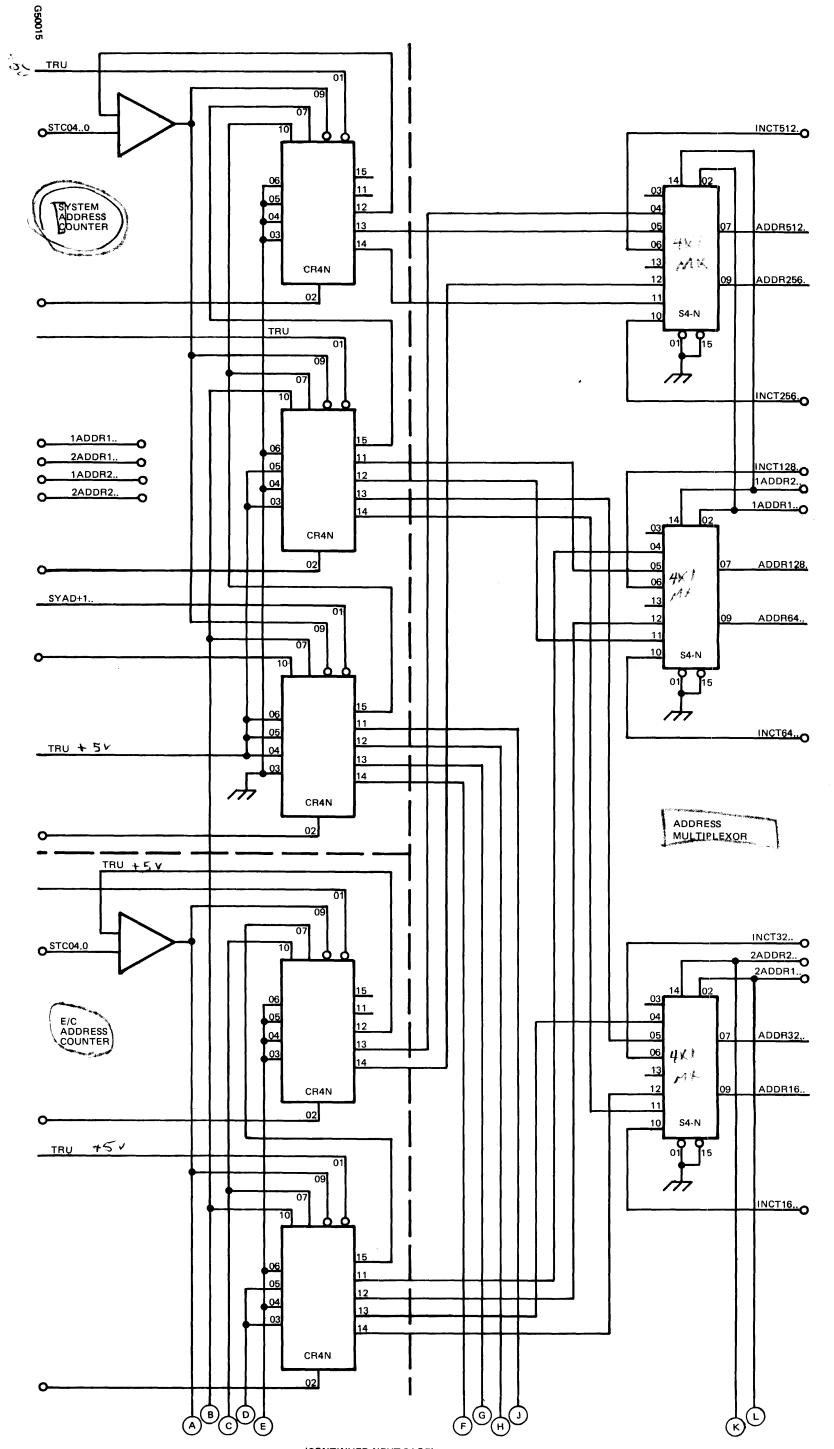

|   | RAM Address Counters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   | Memory Request Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

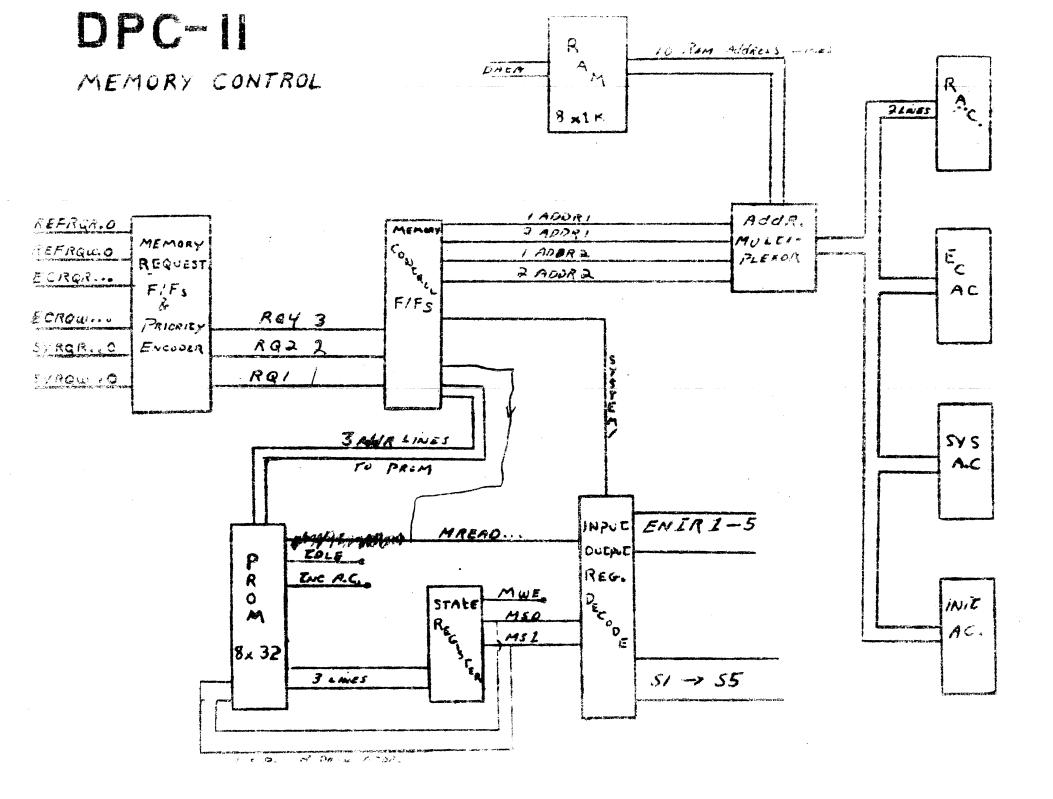

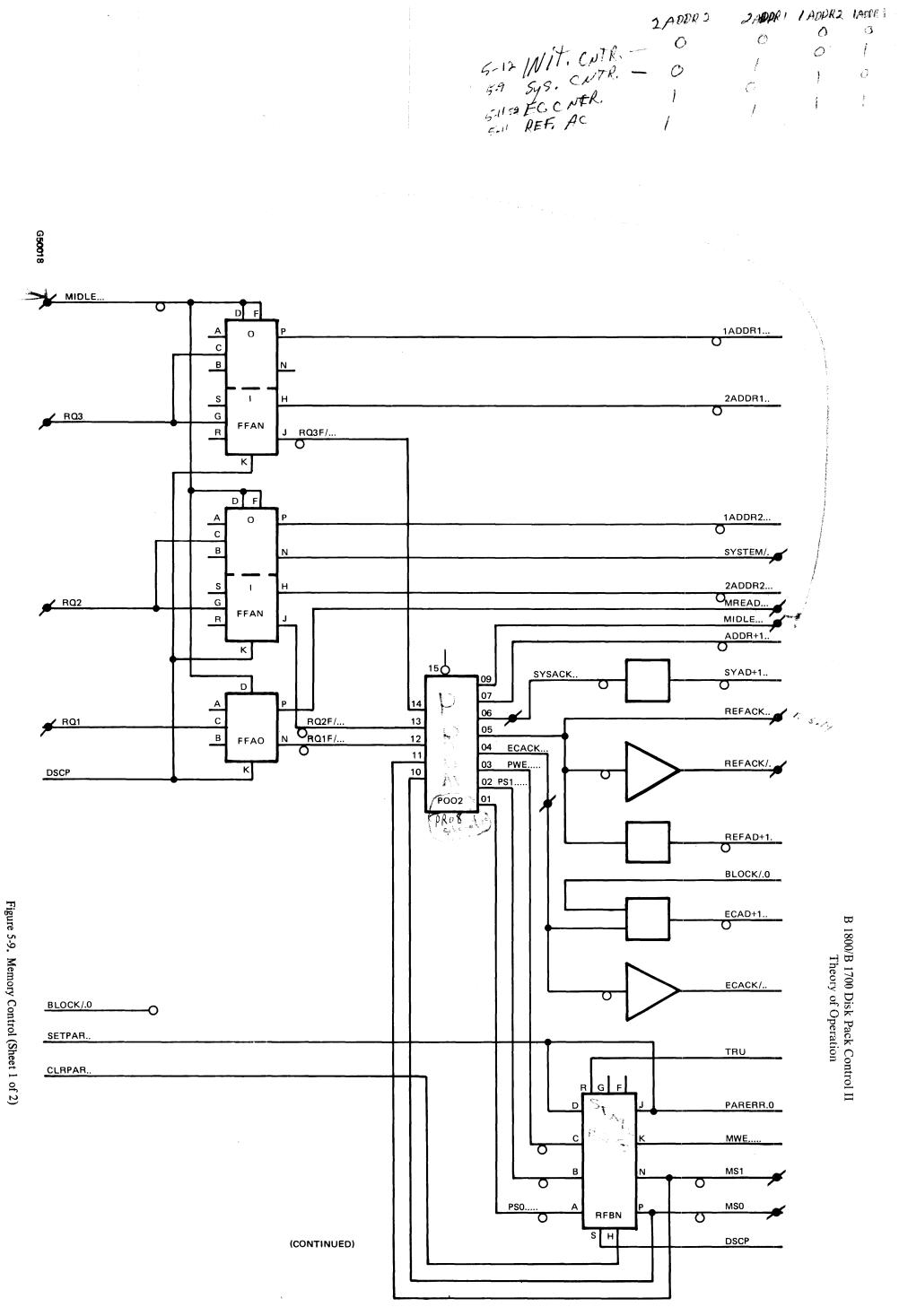

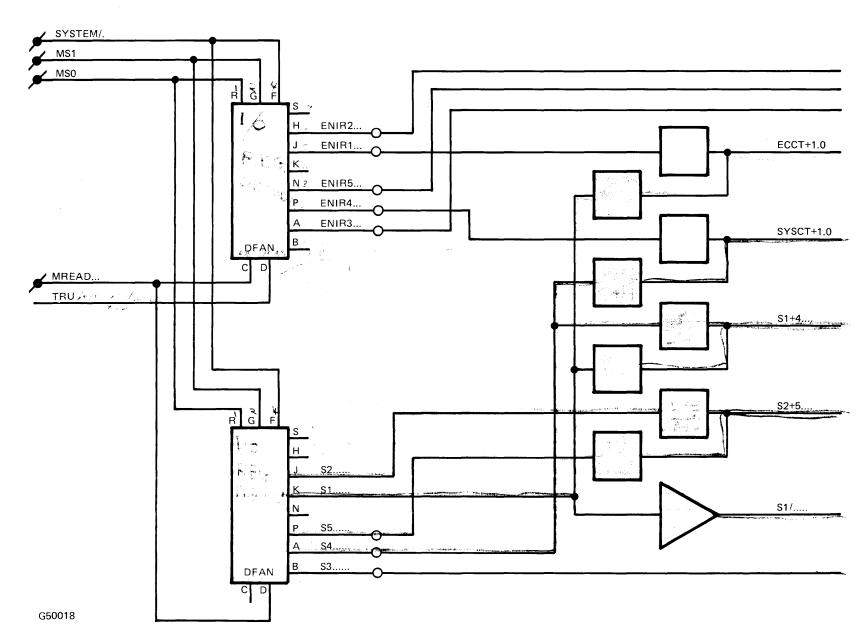

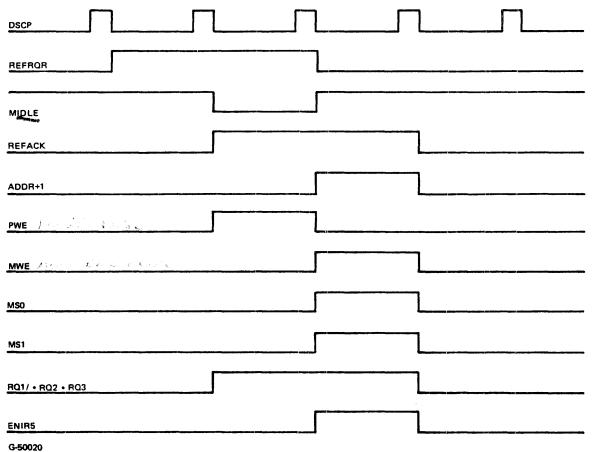

|   | Memory Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   | General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

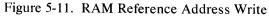

|   | Reference Address Write         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . |

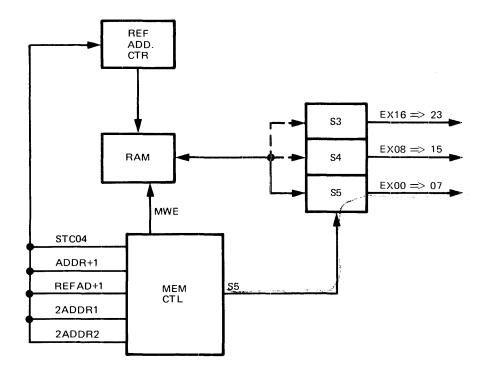

|   | Reference Address Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   | Electronic Control (EC) Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | System Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   | System Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   | Electronic Control Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

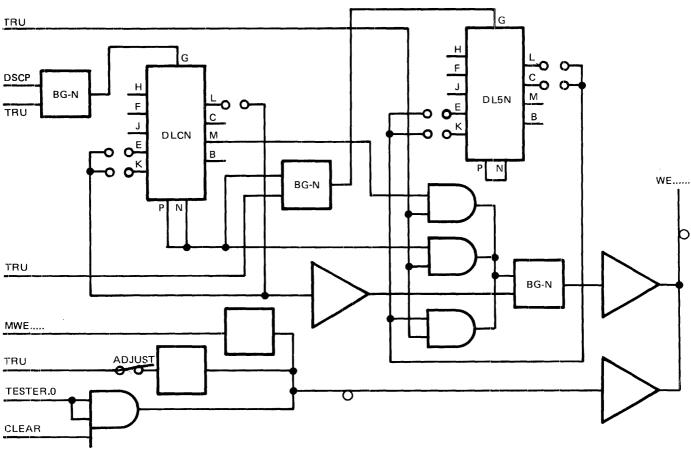

|   | Memory Write Enable Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

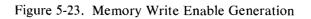

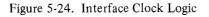

|   | Interface Clock Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

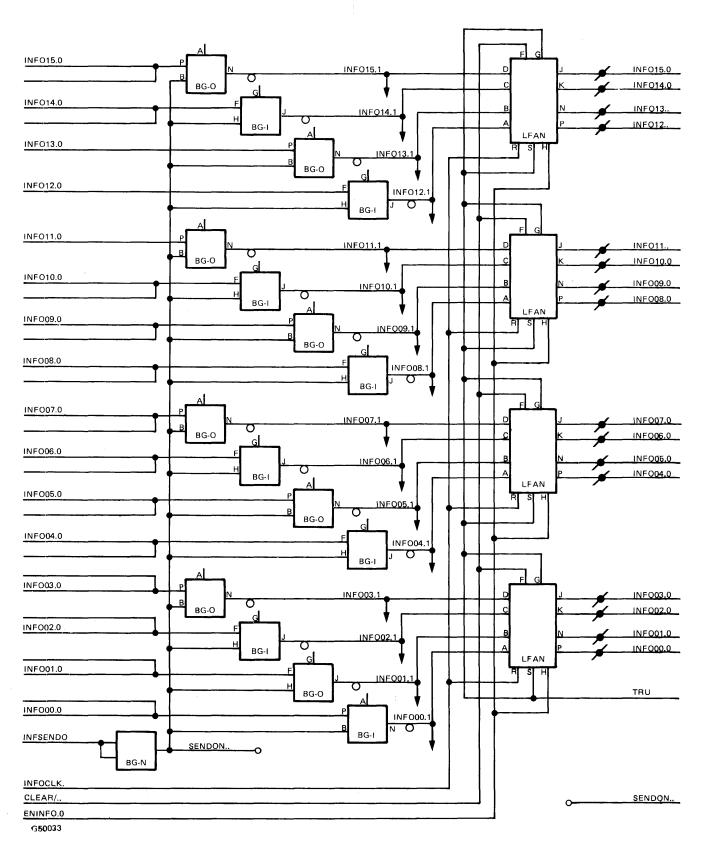

|   | Interface Drivers and Receivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | Status Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   | General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   | STC01, 02, 03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | STC04, 05, 06                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | STC07, 08, 09                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | STC10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | STC11, 12, 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | STC14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | STC15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | STC18, 19, 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | STC21, 22, 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | Sequence Decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   | Parity Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   | File Address Register    5-38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | System and EC Counters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   | Buffers Full Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   | Operation Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   | Command and Command Variant Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | Diagnostic Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   | Control Flip-Flops                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

# B 1800/B 1700 Disk Pack Control II

# LIST OF ILLUSTRATIONS

| 1-1       Disk Pack Subsystem       1-1         1-2       DPC I/O Descriptor       1-2         1-3       Type 225 Disk Pack Track Format       1-2         1-4       Type 206 Disk Pack Track Format       1-3         1-5       Read Operator       1-2 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-3       Type 225 Disk Pack Track Format       1-4         1-4       Type 206 Disk Pack Track Format       1-5                                                                                                                                          |

| 1-3       Type 225 Disk Pack Track Format       1-4         1-4       Type 206 Disk Pack Track Format       1-5                                                                                                                                          |

| 1-4         Type 206 Disk Pack Track Format         1-5                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                          |

| 1-6 Write Operator                                                                                                                                                                                                                                       |

| 1-7 Initialize Operator                                                                                                                                                                                                                                  |

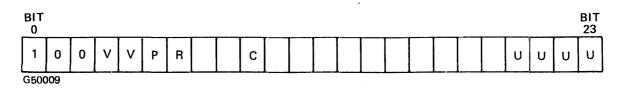

| 1-8 Relocate Operator                                                                                                                                                                                                                                    |

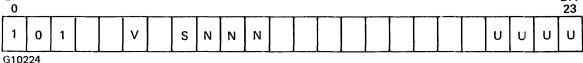

| 1-9 Test Operator                                                                                                                                                                                                                                        |

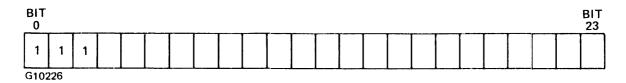

| 1-10 Pause Operator                                                                                                                                                                                                                                      |

| 1-11 Stop Operator                                                                                                                                                                                                                                       |

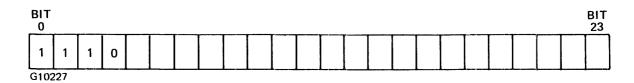

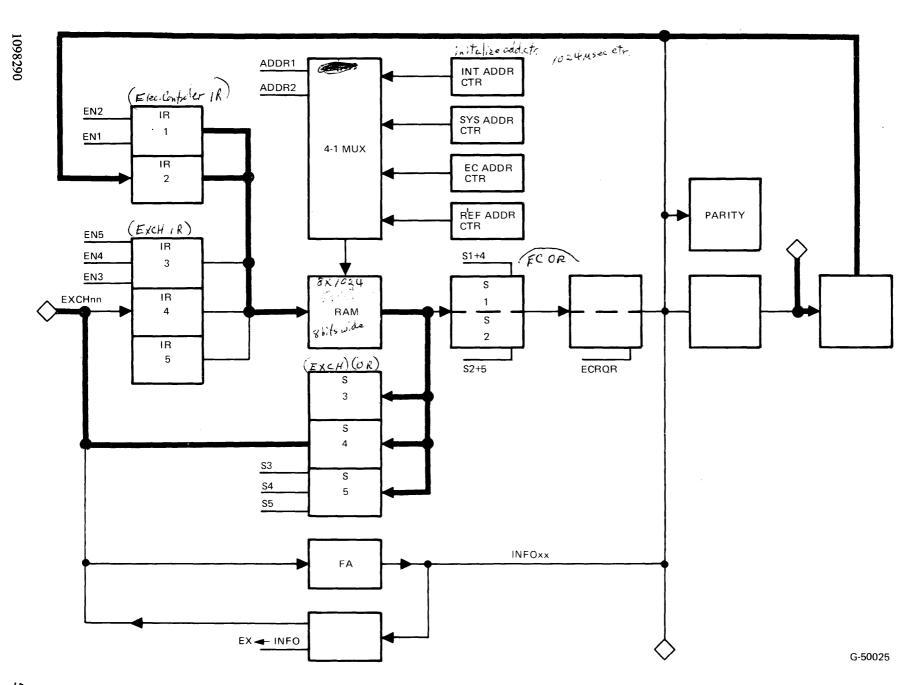

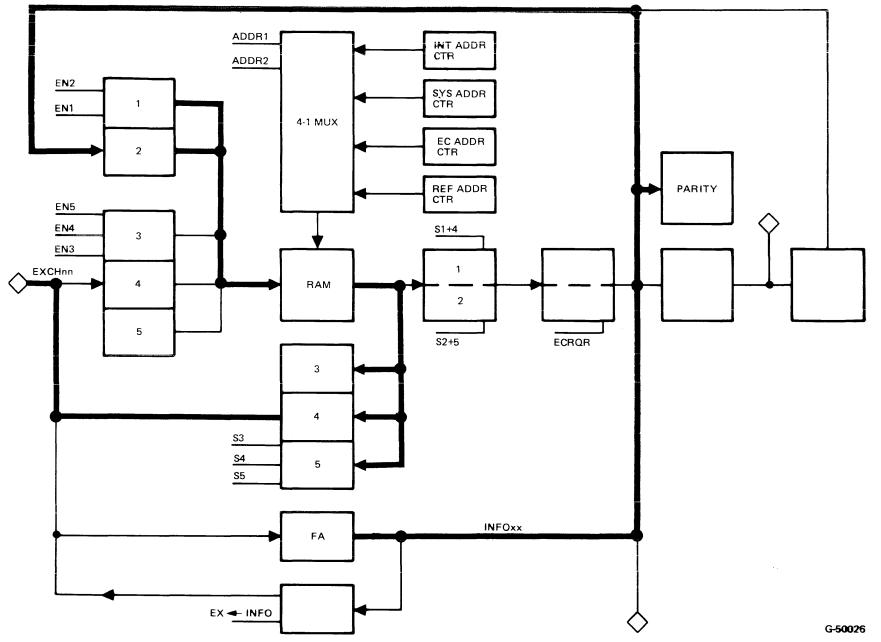

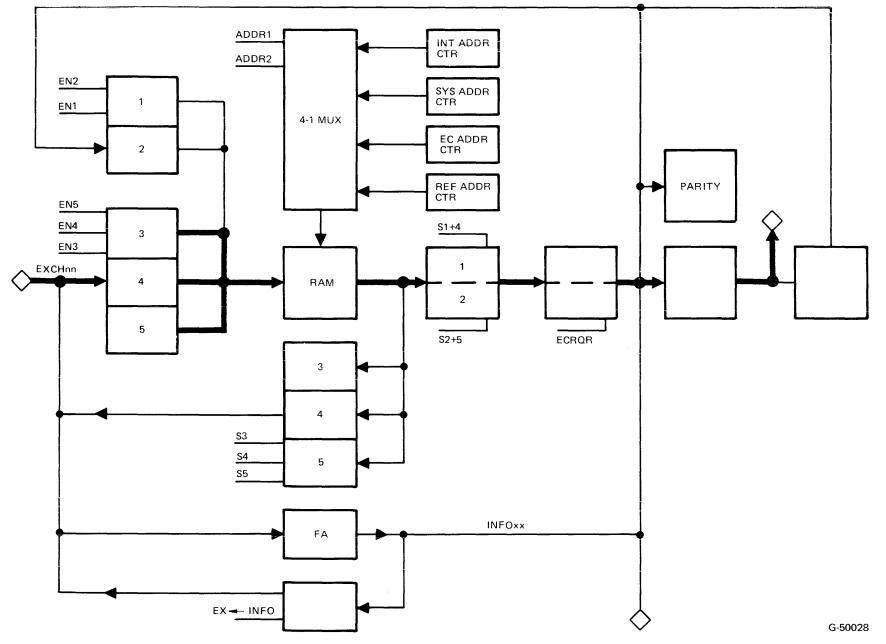

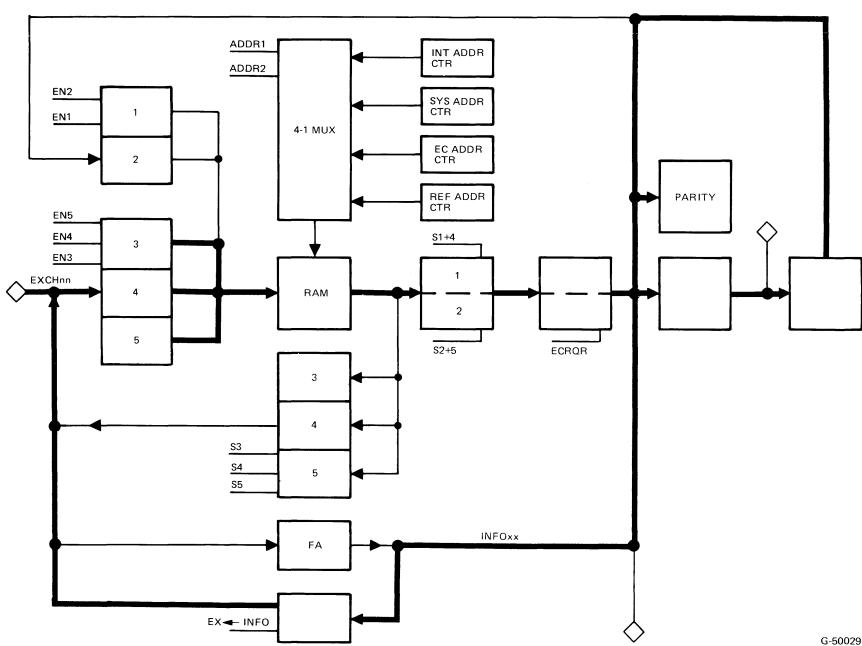

| 5-1 Electronic Control Input Register (ECIR)                                                                                                                                                                                                             |

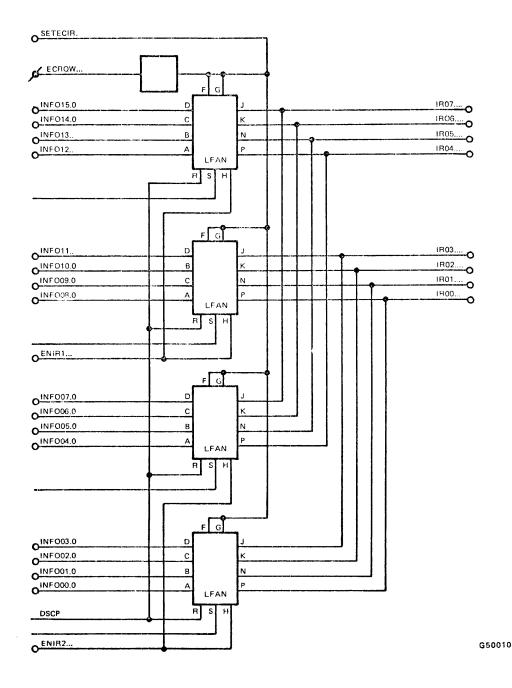

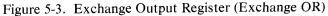

| 5-2 Exchange Input Register (Exchange IR)                                                                                                                                                                                                                |

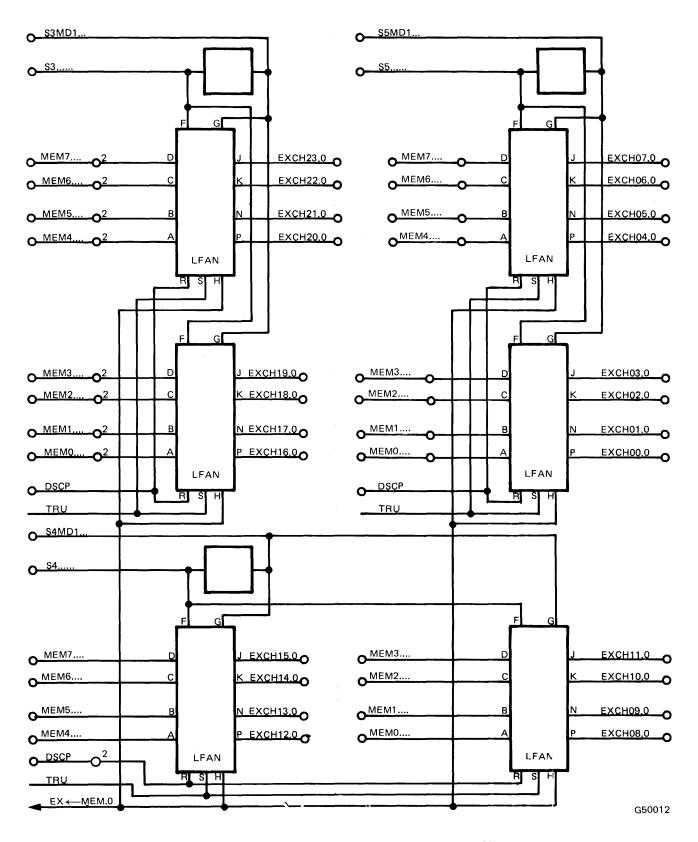

| 5-3 Exchange Output Register (Exchange OR)                                                                                                                                                                                                               |

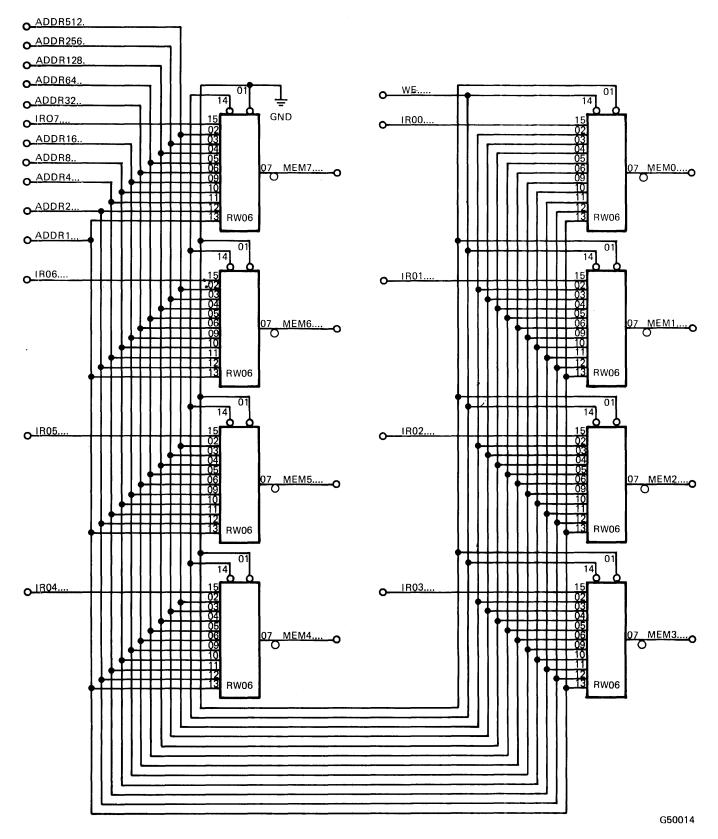

| 5-4 Electronic Control Output Registers 1 and 2 (ECOR1, ECOR2)                                                                                                                                                                                           |

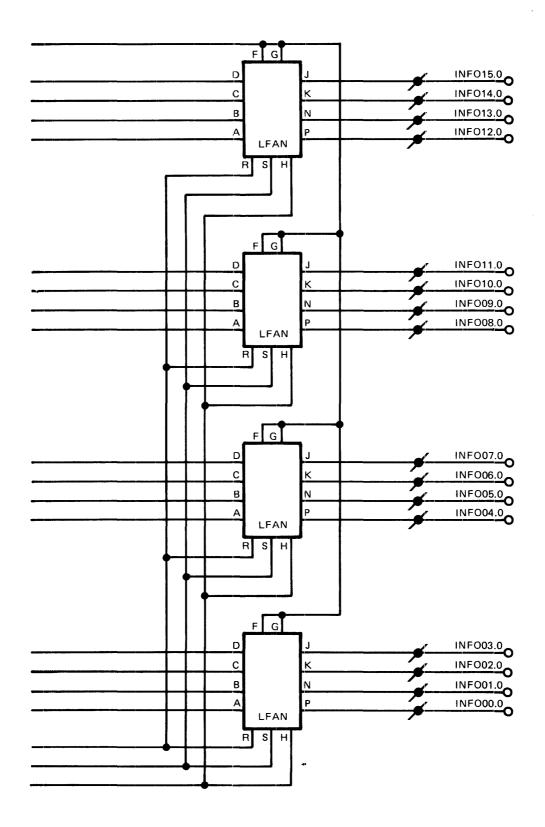

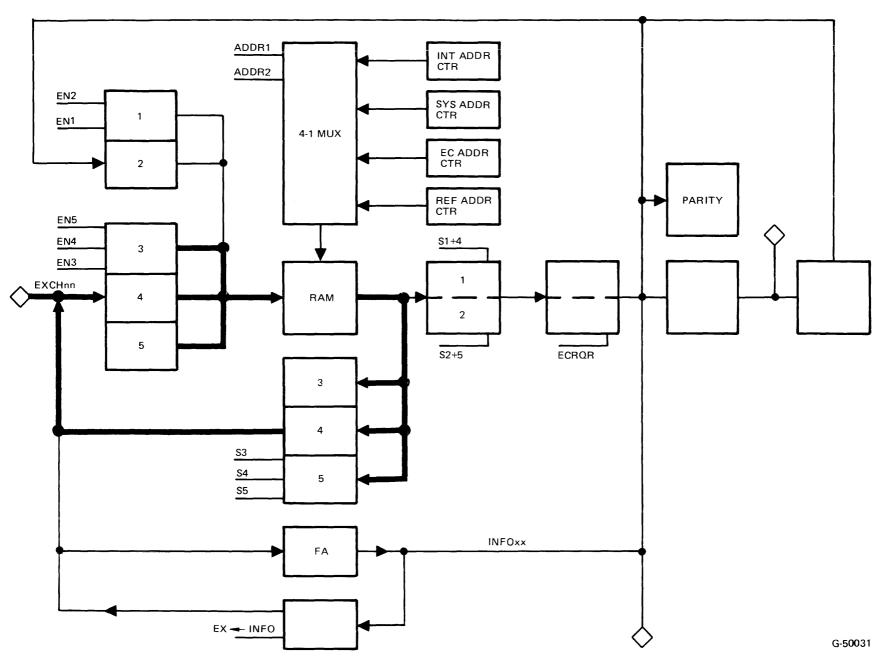

| 5-5 RAM Storage DPC-II                                                                                                                                                                                                                                   |

| 5-6 System, Electronic Control, and Reference Address Counters (2 Sheets)                                                                                                                                                                                |

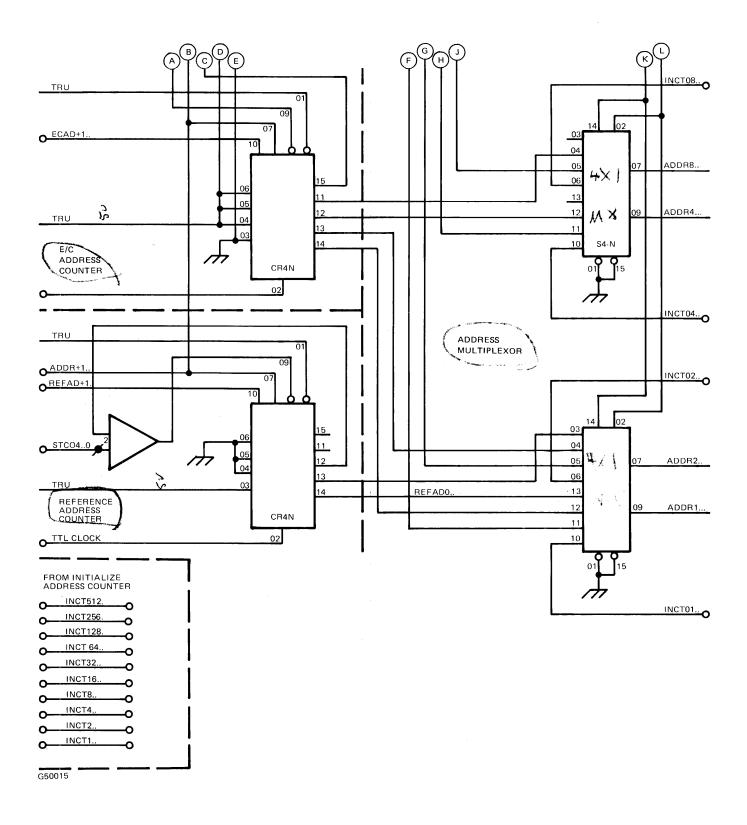

| 5-7 Initialize Address Counter                                                                                                                                                                                                                           |

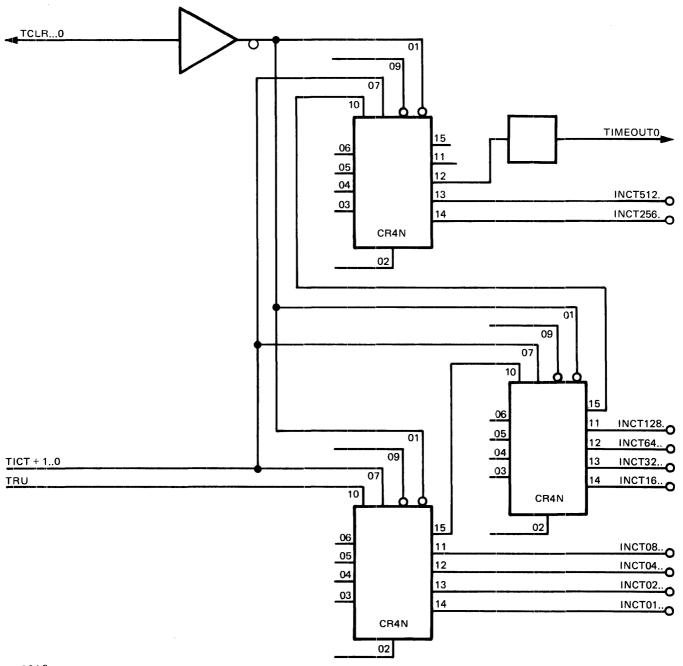

| 5-8 Memory Request Flip-Flops and Priority Encoder                                                                                                                                                                                                       |

| 5-9 Memory Control (2 Sheets)                                                                                                                                                                                                                            |

| 5-10 Reference Address Write Data Flow Diagram                                                                                                                                                                                                           |

| 5-11 RAM Reference Address Write                                                                                                                                                                                                                         |

| 5-12 Reference Address Read Data Flow Diagram                                                                                                                                                                                                            |

| 5-13 RAM Reference Address Read                                                                                                                                                                                                                          |

| 5-14 RAM EC Write                                                                                                                                                                                                                                        |

| 5-15 RAM System Read                                                                                                                                                                                                                                     |

| 5-16 Read Data Path                                                                                                                                                                                                                                      |

| 5-17 Diagnostic Read Data Path                                                                                                                                                                                                                           |

| 5-18 RAM System Write                                                                                                                                                                                                                                    |

| 5-19 Write Data Path                                                                                                                                                                                                                                     |

| 5-20 Diagnostic Write Data Path                                                                                                                                                                                                                          |

| 5-21 RAM EC Read                                                                                                                                                                                                                                         |

| 5-22 Diagnostic RAM Test Data Path                                                                                                                                                                                                                       |

| 5-23 Memory Write Enable Generation                                                                                                                                                                                                                      |

| 5-24 Interface Clock Logic                                                                                                                                                                                                                               |

| 5-25 Interface Drivers and Receivers                                                                                                                                                                                                                     |

| 5-26 Disk Pack Control-II Flow (Detailed)                                                                                                                                                                                                                |

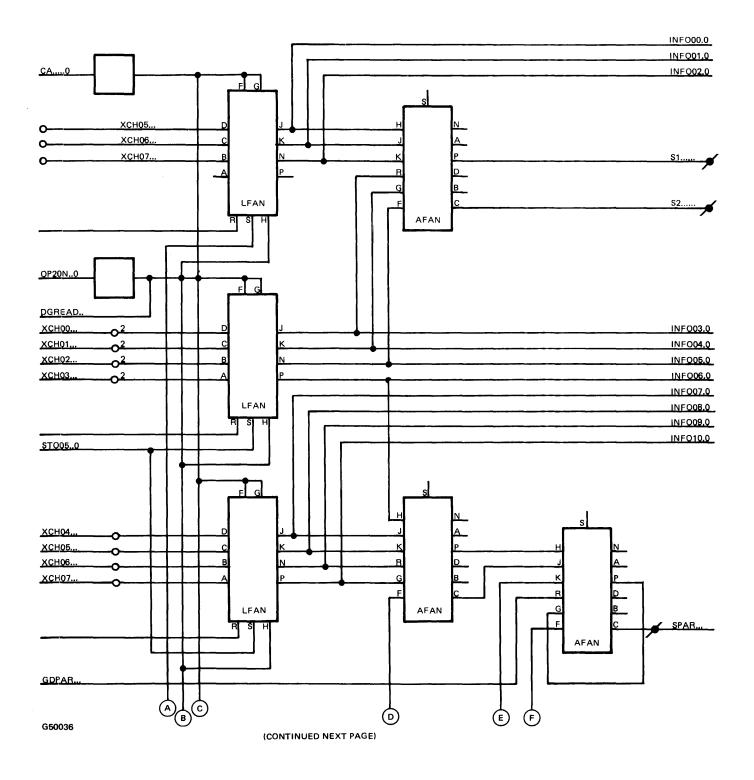

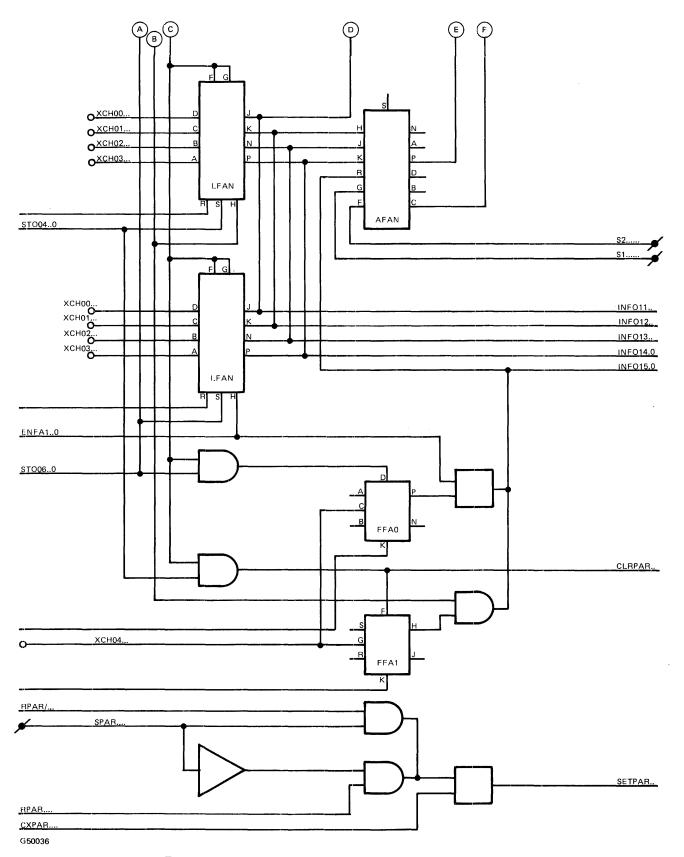

| 5-27 Parity Logic and File Address Register (2 Sheets)                                                                                                                                                                                                   |

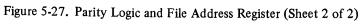

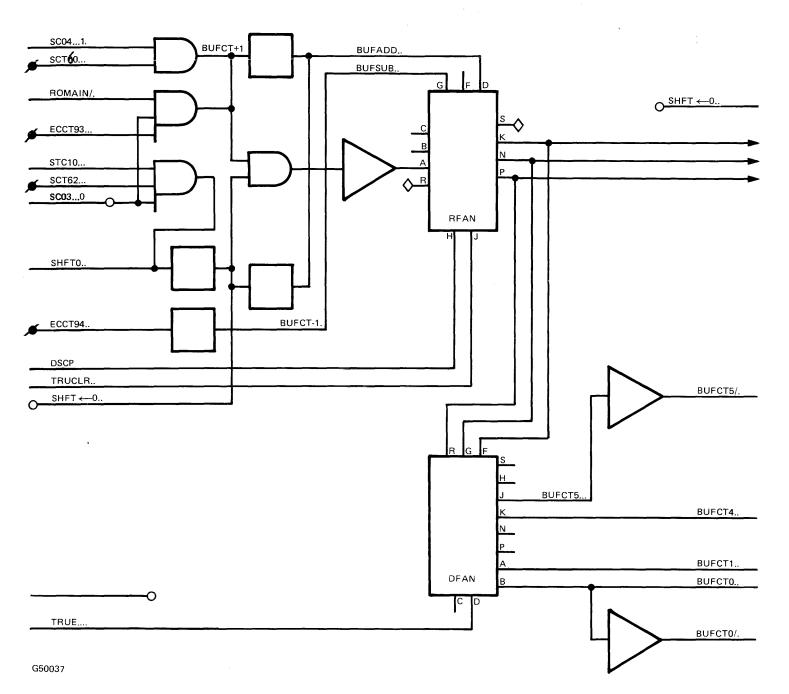

| 5-28 System, Buffer Full, and EC Counters (2 Sheets)                                                                                                                                                                                                     |

÷

7

.

₩. 1

# LIST OF TABLES

# Table

.

1

| 1-1 | DPEC 16-Bit Result Descriptor                         |

|-----|-------------------------------------------------------|

| 1-2 | DPC 24-Bit Result Descriptor                          |

| 4-1 | Relationship of DPEC and DPC Extended Status Results  |

| 4-2 | Diagnostic Read Bit Functions (Type 225 DPEC)         |

| 4-3 | Diagnostic Read Bit Functions (Type 206 DPEC)         |

| 4-4 | Control Messages (Type 206 Drive; Bits 39 through 62) |

| 5-1 | Logic Blocks in DPC-II                                |

.

# **SECTION 1**

# **FUNCTION AND OPERATION**

#### INTRODUCTION

The B 1800/B 1700 Disk Pack Control II (DPC-II) is part of the B 1800/B 1700 Disk Pack Subsystem. This subsystem also includes a disk pack electronics controller (DPEC) and one to eight disk pack drives (DPD), as diagrammed in figure 1-1.

Figure 1-1. Disk Pack Subsystem

#### DISK PACK CONTROL II

## GENERAL INFORMATION

ź

The B 1800/B 1700 Disk Pack Control II consists of two B 1700-size logic cards. These logic cards must be installed in a two-card location in an I/O base or I/O base extension.

The DPC-II performs the following functions:

- a. Provides an interface between the central processor and the DPEC

- b. Provides data storage for three sectors of disk pack information

- c. Decodes and interprets the operation (OP) code from the central processor to the DPEC

- d. Assembles a result descriptor based on information received from the DPEC

The DPC-II receives the I/O descriptor operators that are fetched by the I/O driver from main memory, interprets the operation specified by the descriptor operator and its variants, and initiates the required action in the DPEC. At the completion of the operation, the DPC generates a result descriptor using information received from the DPEC. The I/O driver stores the result descriptor in the result status (RS) field of the I/O descriptor. The I/O driver also returns an interrupt message if requested.

# **I/O DESCRIPTOR**

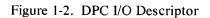

The I/O descriptor consists of seven 24-bit fields as shown in figure 1-2. The following is a detailed description of the functions and usage of each field.

| E  | ENDING ADDRESS.                                            |

|----|------------------------------------------------------------|

| RS | <b>RESULT STATUS (ALSO LOCATION OF RESULT DESCRIPTOR).</b> |

| L  | LINK ADDRESS.                                              |

| OP | OP, VARIANTS AND UNIT NUMBER.                              |

| Α  | START ADDRESS OF DATA                                      |

| В  | END PLUS ONE, ADDRESS OF DATA.                             |

| С  | START ADDRESS OF DATA (FILE ADDRESS).                      |

|    |                                                            |

## E Field

G50005

After an operation, the I/O driver stores the final incremented A address in the E field. The address in this field points to the memory location where the next bit of data normally would be stored. For read, write, and search operations, the E field address is normally equal to the B address unless the operation is terminated because of a "not-ready", address error, time-out, command transmission error, write lock-out (write operation only), or the end of the search table or entry (search operation only). The E field is not defined after a test operation or stop operation.

During some operations, the E field is used by the I/O driver to save the incremented A address between buffer loads to the DPC.

## <u>RS Field</u>

After completion of an operation and after the actual ending address has been stored in the E field, the I/O driver exchanges the result status information in the result status field with the interrupt control information.

Prior to and during an operation, the first 15 bits of the RS field are used to store temporary flags for the I/O driver. The last nine bits are used to indicate dynamic interrupt information.

#### L Field

After storing the result status information and after returning any requested interrupt message, the I/O driver normally fetches the Link address from the L field. The Link address is a 24-bit address pointing to the RS field of the next I/O descriptor to be executed.

#### **OP** Code, Variant(s) and Unit Number

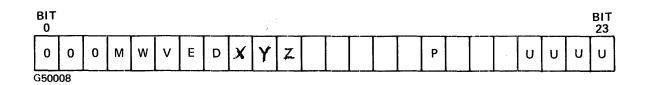

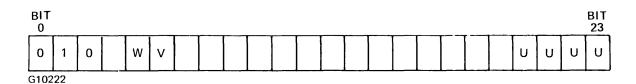

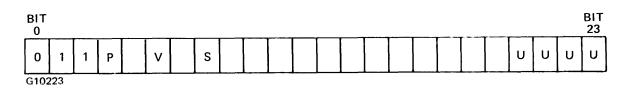

The OP code, variant(s) and unit number are contained in a 24-bit field. The leftmost three bits are used to designate the majority of operator codes; the rightmost four bits are used to designate the unit. (Operator codes extending beyond three bits are indicated by 111 in the first three bit positions.) The remaining bits are then used for variants (explained under the description of the individual operators). All bits remaining unassigned are reserved bits; they must be zeros.

#### A and B Fields

For most operators, the A and B fields are 24-bit fields containing the beginning and ending memory bit addresses, respectively, for a given operation. These addresses normally define the number of bits to be transferred. If the value in A equals the value in B, no data is transferred. For the Test descriptor, the A-field and B-field addresses are not used.

#### **C** Field (File Address)

Ĵ

The File Address, a binary sequential address contained in a 24-bit field, is used to designate a particular sector on a disk pack as the starting point for all operations except Test and Stop.

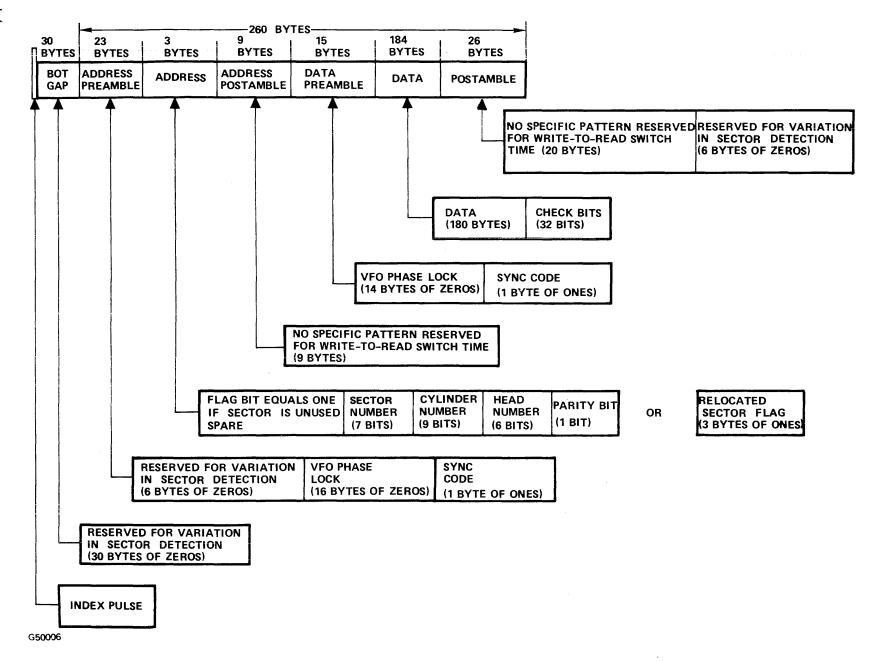

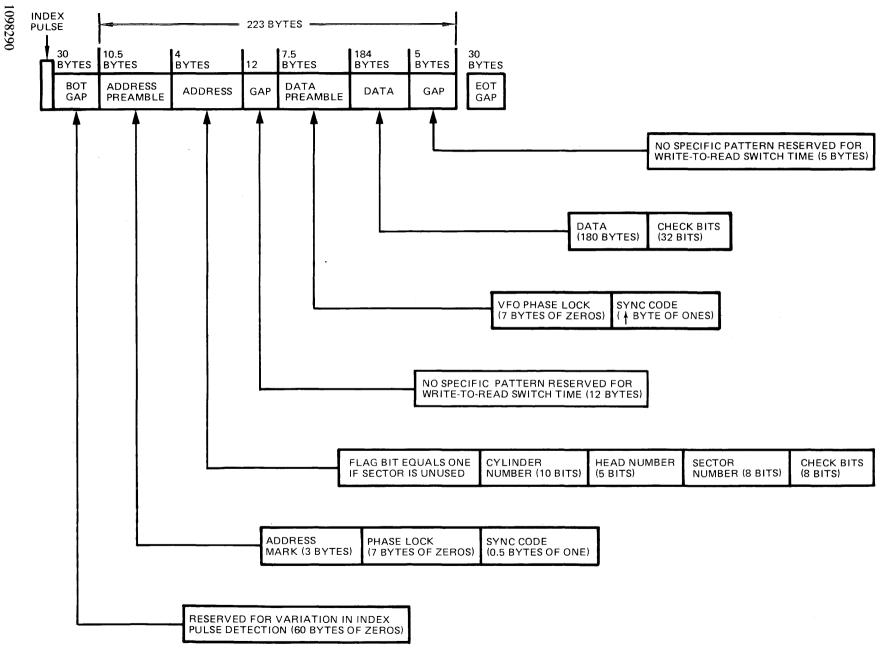

For full-capacity type 225 disk pack drives, the maximum binary file address is 485,169 corresponding to a maximum capacity of 87,330,600 eight-bit bytes for each removable disk pack. For half-capacity type 225 disk pack drives, the corresponding figures are 242,584, and 43,665,300 bytes, respectively. The disk cartridge track format for a type 225 disk drive is shown in figure 1-3.

For type 206 disk pack drives, the maximum binary file address is 362,229, corresponding to a maximum capacity of 65,201,400 eight-bit bytes per removable disk pack. For half-capacity type 206 (type 205) disk pack drives, the corresponding figures are 181,114, and 32,600,700 bytes, respectively. The disk cartridge track format for a type 206 disk drive is shown in figure 1-4.

For type 225 disk drives, the binary sequential file address corresponds to contiguous or adjacent sectors (excluding spares and sectors which have been relocated) that begin on head 0, cylinder 0 and continue through the pack by head and cylinder (in that order). On each surface (except the first) there are sixty sectors. The order of the sectors following index is 0, 1, 2, ..., 57, 58, 59. On the first surface (head 0) five spare sectors occupy the positions normally occupied by sectors 55 through 59. These spare sectors are not addressable in the address continuum (unless they have been assigned by relocation).

For type 206 disk drives, the binary sequential file address corresponds to interlaced sectors (excluding spares and sectors which have been relocated) that begin on head 0, cylinder 0 and continue through the pack by head and cylinder (in that order). On each surface except the fifth one, there are 90 sectors. The order of the sectors following index is 45, 0, 46, 1, 47, 2, ..., 89, 44. On the fifth surface (head 4) five spare sectors occupy the position normally occupied by sectors 85 through 89. These spare sectors are not addressable in the address continuum (unless they have been assigned by relocation).

For type 205/206 disk drives, a reserved cylinder is used for maintenance purposes. Sectors on this reserved cylinder are addressed with addresses 362,230 through 362,679.

4

# **I/O OPERATORS**

The following are all I/O operators for DPC-II:

- a. Read

- b. Write

- c. Initialize

- d. Relocate

- e. Test

- f. Pause

- g. Stop

Each I/O operator consists of a 24-bit field. The first three-bit positions (leftmost three-bit positions as displayed on the console) are reserved for the type of operation. The last four-bit positions are reserved for unit number; remaining positions are reserved for variants.

#### **Read Operator**

The read operator (refer to figure 1-5) provides the capability to read data from the disk pack, starting at the given file address (C field), into ascending memory locations that begin at the location specified by the A address and end at the location specified by the B address (minus one). A complete segment does not need to be stored but can be parity-checked. The DPEC transmits a total of 90 sixteen-bit data words and two error-code words to the DPC for each sector read. In addition, one 16-bit result status word reflecting the accumulation status of the entire operation up to that point is transmitted immediately following error-code words for each sector. Only data bits are stored, unless otherwise specified by variant E - 1 or M = 1.

Figure 1-5. Read Operator

Functions of the Read operator variants follow:

| Variant     |                                                                                                                                                      | Control Function                                                                                                                                                                                                                                                                                                                                                               |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MEDP = 0E00 | Read data as described under "Read Operator," above. The Read operator and VXYZ variants are sent to the DPEC. VXYZ variants are decoded as follows: |                                                                                                                                                                                                                                                                                                                                                                                |  |

|             | VXYZ = 0000                                                                                                                                          | Normal Read                                                                                                                                                                                                                                                                                                                                                                    |  |

|             | VXYZ = 10Y0                                                                                                                                          | Enable strobe; Y denotes direction, $0 = -$ ,<br>1 = +, type 206 only.                                                                                                                                                                                                                                                                                                         |  |

|             | VXYZ = 0X01                                                                                                                                          | Enable offset; X denotes direction, $0 = -$ ,<br>1 = +, types 206 and 225 DL2 only                                                                                                                                                                                                                                                                                             |  |

|             | VXYZ = 1XY1                                                                                                                                          | Enable strobe and offset; XY denotes direction, type 206 only                                                                                                                                                                                                                                                                                                                  |  |

|             | V = 1                                                                                                                                                | Disable automatic restore after a seek error,<br>type 225 only                                                                                                                                                                                                                                                                                                                 |  |

|             | Y = 1                                                                                                                                                | Not permitted on type 225 (See $D = 1$ , following)                                                                                                                                                                                                                                                                                                                            |  |

|             | XZ = 10                                                                                                                                              | Not defined                                                                                                                                                                                                                                                                                                                                                                    |  |

|             | VY = 01                                                                                                                                              | Not defined                                                                                                                                                                                                                                                                                                                                                                    |  |

| MEDP = 0E01 | variants are sent to the DPE<br>equal to 001 through 101 indic<br>sector is designated, only on<br>permitted if the specified spar                   | titled Read Operator). The verify operator and the VXYZ<br>C. XYZ equal to 000 indicates normal sectors while XYZ<br>cates the spare sector on the designated cylinder. If a spare<br>e sector is read. Designation of a spare sector is not<br>re sector has been assigned. Variant MD must equal 00. For<br>t equal 0. For type 225, V equal to 1 disables automatic         |  |

| E = 1       | addition to the data bits, can r                                                                                                                     | r "Read Operator," where P can be equal to 0 or 1 but, in<br>eturn the 32-bit error check code and the 16-bit result word<br>ent read. Return the final DPC result for the operation with<br>iant MD must equal 00.                                                                                                                                                            |  |

| M = 1       | and the postamble as record<br>result from the DPEC. If the<br>returned then contains all "or<br>operation at this time. The p                       | ess (and whenever possible) the data, the data check bits,<br>ed at the designated segment. In addition return the 16-bit<br>sector is relocated, the sync code and the address field<br>nes." Neither parity error nor wrong address terminates the<br>osition of the sector is obtained in the DPEC by counting<br>ants except WV must equal 0. For type 206, variant V must |  |

2 7

1

| Variant | Control Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D = 1   | Read extended status data from the DPEC. The DPC treats this operation identically to a read operation except for data length. Presently, data transfer from DPEC is terminated by DPEC after 64 bits occur. The data transfer from the control, if not terminated earlier by the system, is terminated after 264 bytes. The excess data is not defined. For type 225 DL2, the normal read operation (with Y equal to 1 variant) is sent to the DPEC. For type 206, the diagnostic read operation with the Y variant equal to 1 is sent to the DPEC. All other variants (except W) must equal 0. This $D = 1$ operation is not permitted for type 225 DL1 drive. |