# B 1870/B 1860 Systems

## **REFERENCE MANUAL**

PRICED ITEM

Burroughs believes that the information described in this manual is accurate and reliable, and much care has been taken in its preparation. However, no responsibility, financial or otherwise, is accepted for any consequences arising out of the use of this material. The information contained herein is subject to change. Revisions may be issued to advise of such changes and/or additions.

Correspondence regarding this document should be addressed directly to Burroughs Corporation, P. O. Box 4040, El Monte, California 91734, Attn: Publications Department, TIO – West.

### TABLE OF CONTENTS

| Section | I                                                | Page       |

|---------|--------------------------------------------------|------------|

|         | PREFACE                                          | xv         |

|         | INTRODUCTION                                     | xvii       |

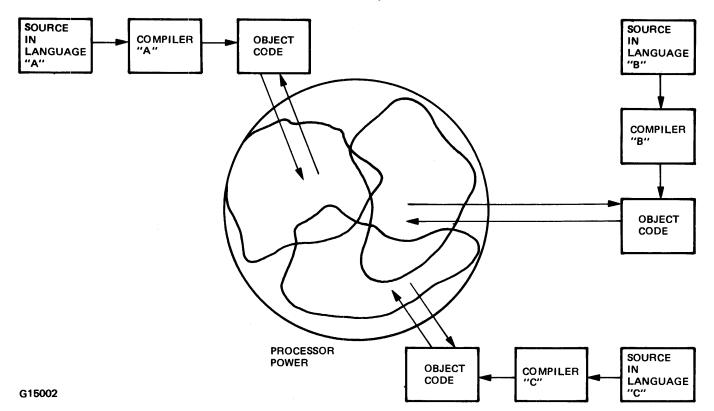

| 1       | CONCEPTS                                         |            |

|         | Overview                                         | 1-1        |

|         | Design Philosophy                                | 1-2        |

|         | Bit Addressability and the Defined-Field Concept | 1-3        |

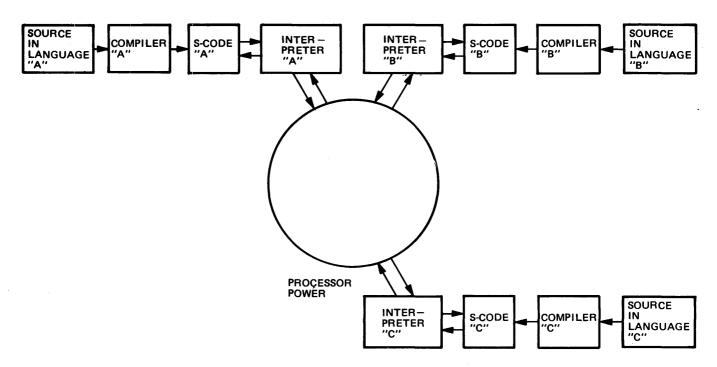

|         | The Concept of Interpretation                    | 1-4        |

|         | The Concept of Nanoprogramming                   | 1-8        |

|         |                                                  |            |

| 2       | SYSTEM ELEMENTS                                  | <b>~</b> 1 |

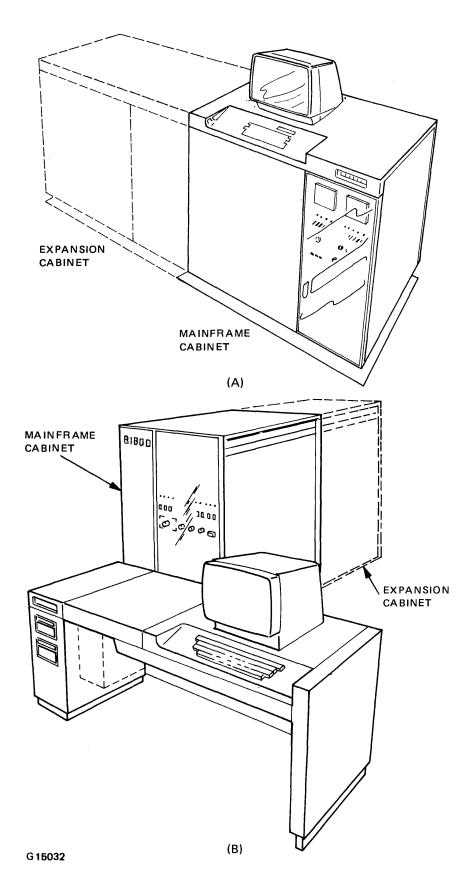

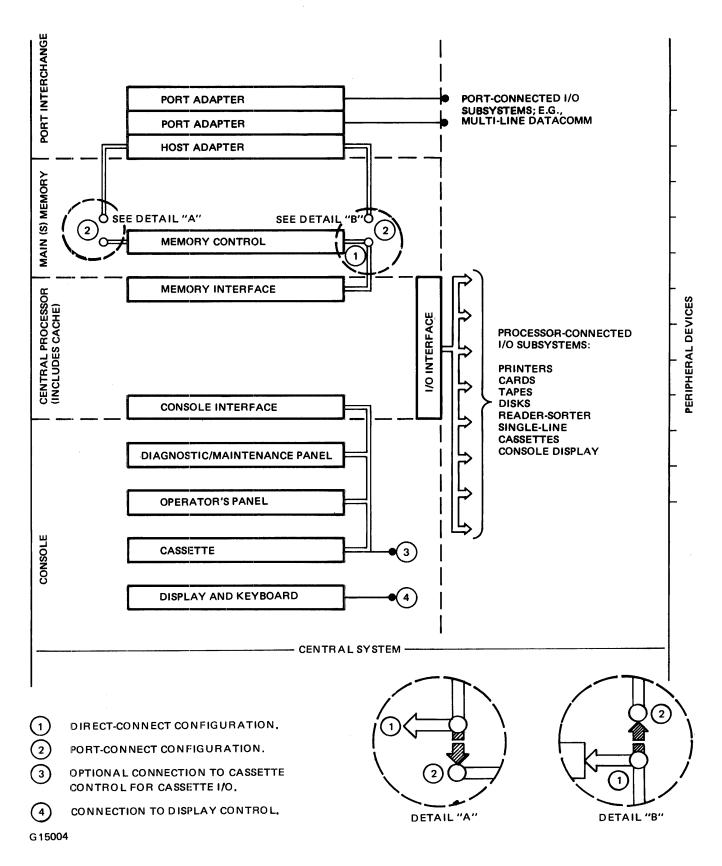

|         | Physical Configuration                           | 2-1        |

|         | Functional Configuration                         | 2-1        |

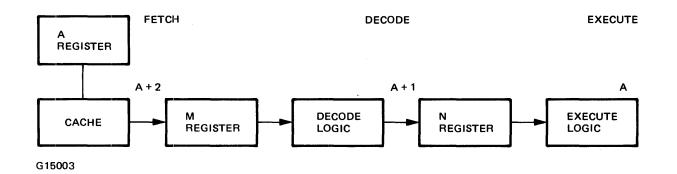

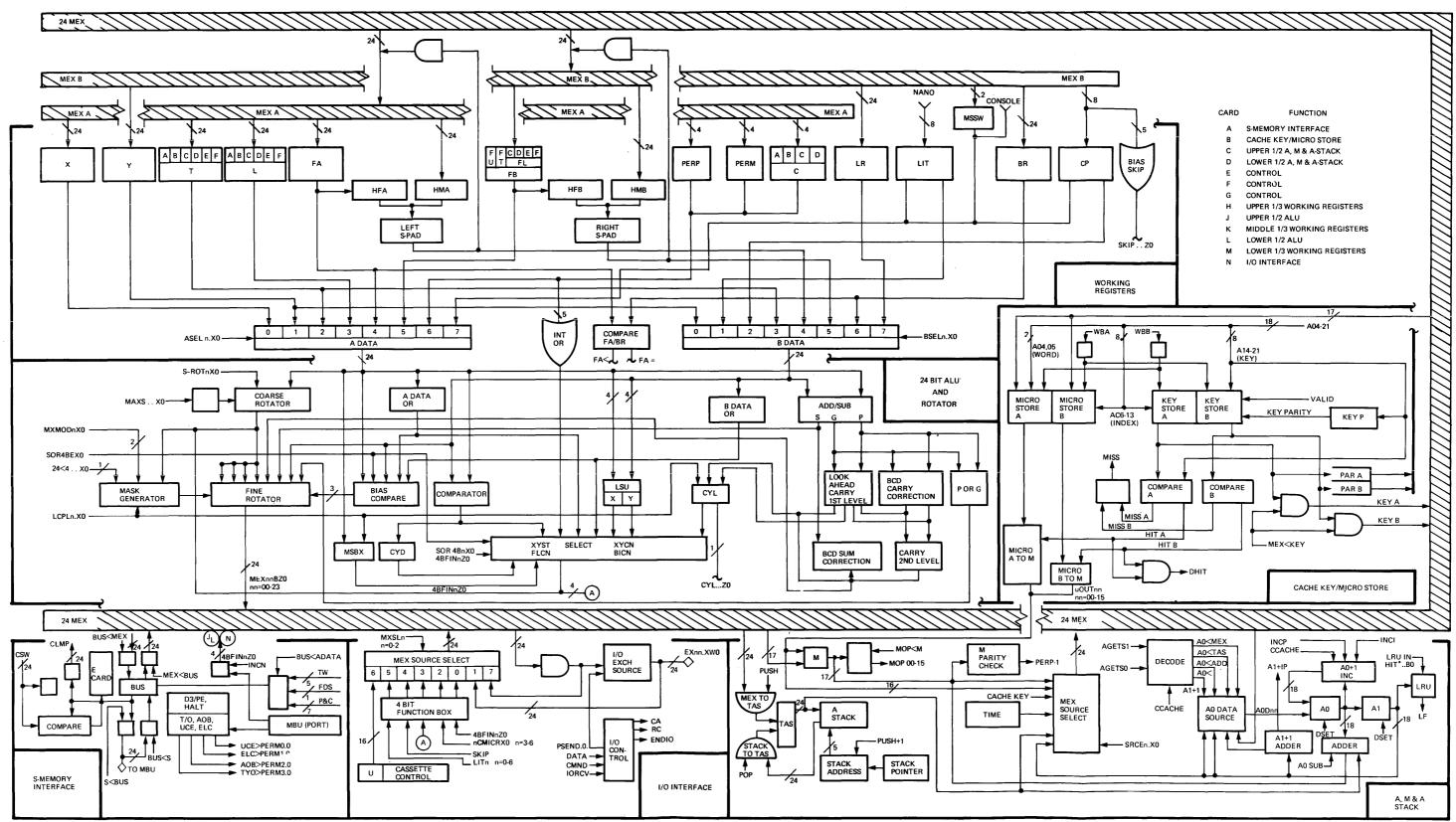

|         | Central Processor                                | 2-1        |

|         | Data Paths                                       | 2-4        |

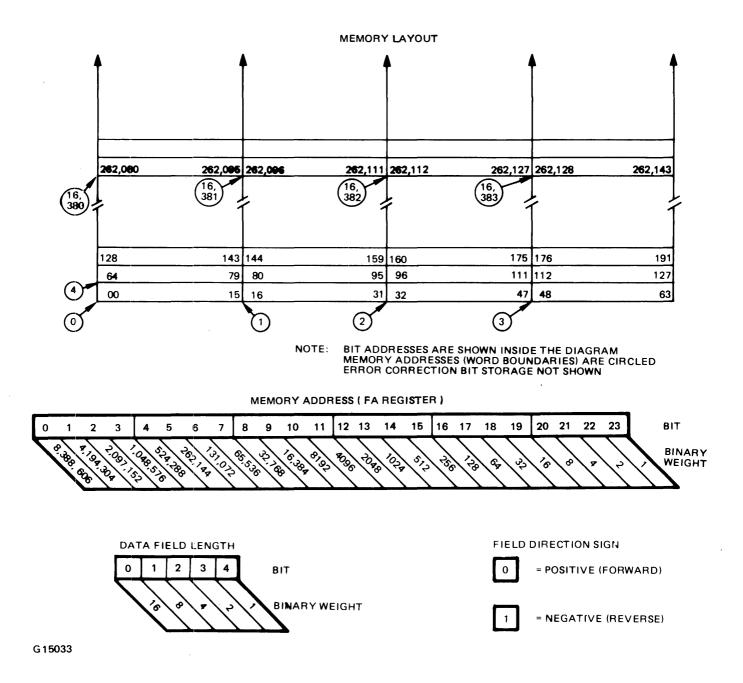

|         | Main Memory (S Memory)                           | 2-4        |

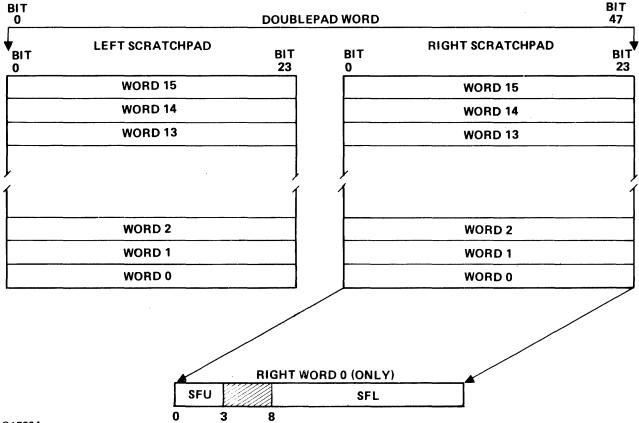

|         | Scratchpad                                       | 2-8        |

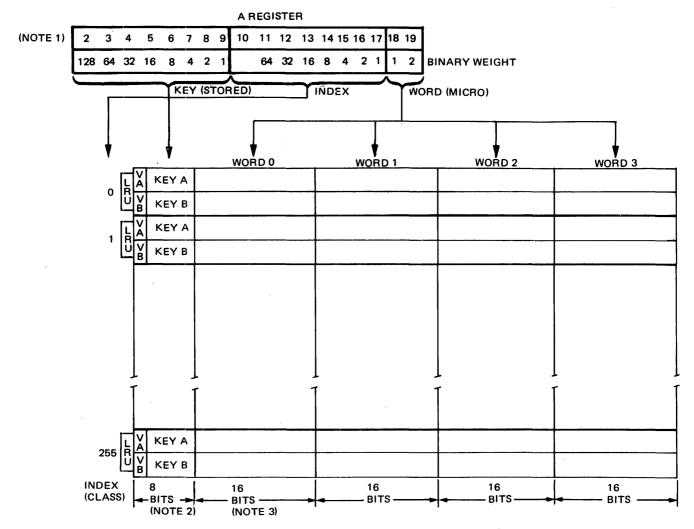

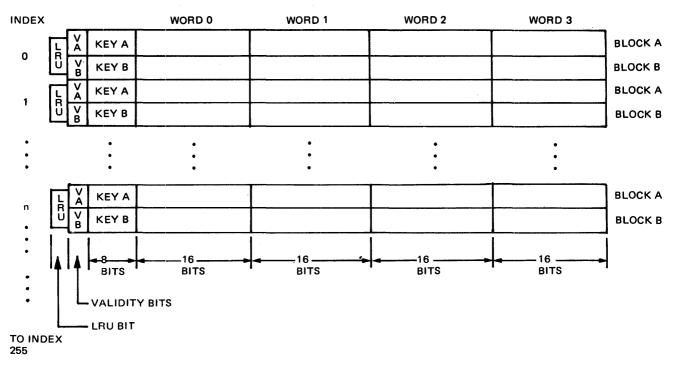

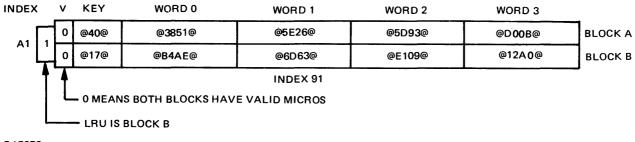

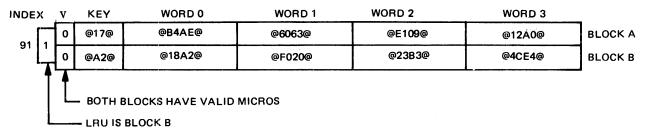

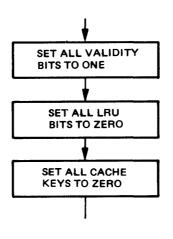

|         | Cache Memory                                     | 2-8        |

|         |                                                  | 2-13       |

|         |                                                  | 2-13       |

|         |                                                  | 2-13       |

|         |                                                  | 2-13       |

|         | -,                                               | 2-14       |

|         |                                                  | 2-15       |

|         | Initiation                                       | 2-15       |

|         |                                                  | 2-15       |

|         |                                                  | 2-15       |

|         |                                                  | 2-15       |

|         |                                                  | 2-16       |

|         |                                                  | 2-17       |

|         |                                                  | 2-19       |

|         | Service Request                                  |            |

|         | Data Transfer                                    | 2-21       |

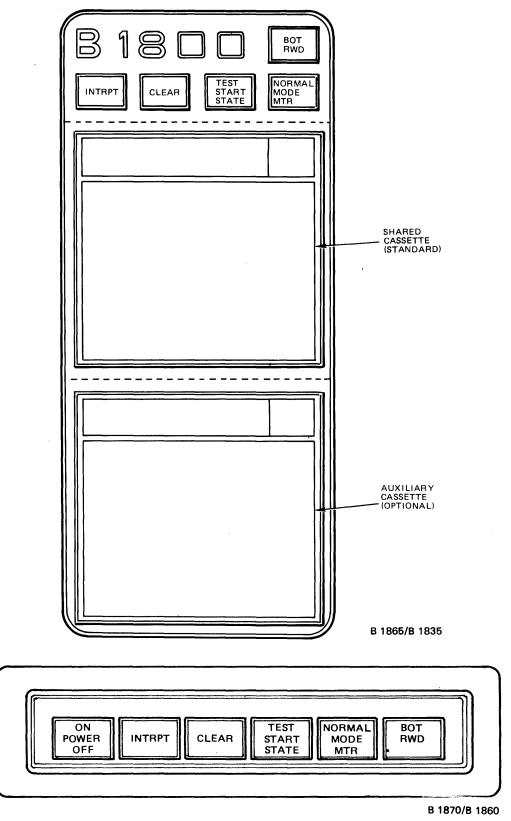

| 3       | B 1800 CONTROL PANELS                            |            |

| 3       | Introduction                                     | 3-1        |

|         | Operator's Panels.                               | 3-1        |

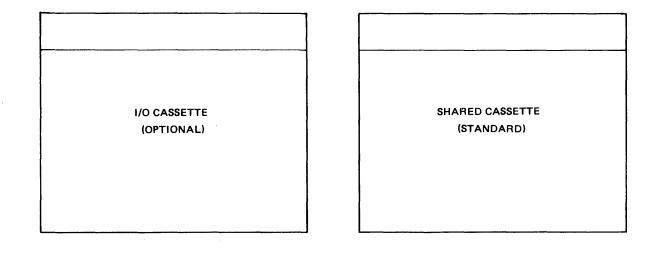

|         | Cassette Tape Drive                              | 3-1        |

|         |                                                  | 3-1        |

|         | RWD/BOT Pushbutton/Indicator                     | 3-1        |

|         | INTRPT Pushbutton/Indicator                      | 3-1        |

|         | Mode Pushbutton, NORMAL/MTR Indicator            | 3-3        |

|         | CLEAR Pushbutton                                 | 3-3        |

|         | START Pushbutton, TEST STATE Indicator           | 3-3        |

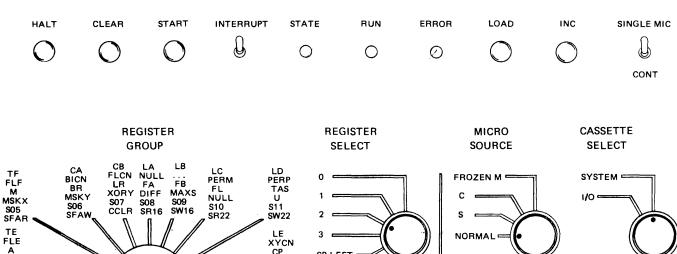

|         | Diagnostic and Maintenance Panel                 | 3-3        |

|         |                                                  | 3-3        |

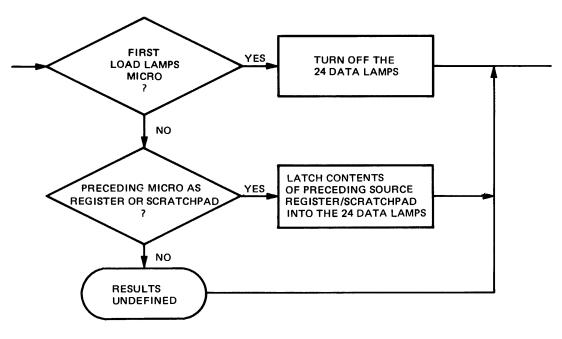

|         | Data Lamps.                                      | 3-3        |

|         | STATE                                            | 3-3        |

|         | RUN                                              | 3-5        |

|         | ERROR                                            | 3-5        |

|         | OVER TEMP                                        | 3-5        |

|         |                                                  | 5-5        |

| Section | 1                                           | Page       |

|---------|---------------------------------------------|------------|

|         | Toggle Switches                             | 3-5        |

|         | Data Switches                               | 3-5        |

|         | INTERRUPT                                   | 3-5        |

|         | SINGLE MIC/CONT                             | 3-5        |

|         | Rotary Switches                             | 3-6        |

|         | REGISTER GROUP, REGISTER SELECT             | 3-6        |

|         |                                             | 3-7        |

|         |                                             | 3-7        |

|         |                                             | 3-7        |

|         | HALT                                        | 3-7        |

|         | CLEAR                                       | 3-7        |

|         | START                                       | 3-7        |

|         |                                             | 3-8        |

|         |                                             | 3-9        |

|         | Register Group/Register Select Capabilities | 3-9        |

|         |                                             | 5-7        |

| 4       | REGISTERS                                   | 4 1        |

|         | General Purpose Registers                   | 4-1        |

|         | $\underbrace{V}_{-}$                        | 4-1        |

|         | $\mathbb{T}$                                | 4-1        |

|         | X and Y                                     | 4-2        |

|         | TAS and $\checkmark$ Stack                  | 4-2        |

|         | Addressing and Execution Registers          | 4-2        |

|         | F                                           | 4-2        |

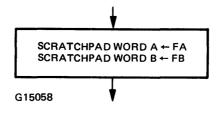

|         | FA                                          | 4-2        |

|         | FB                                          | 4-3        |

|         | Ý FU                                        | 4-3        |

|         | FT                                          | 4-3        |

|         | FL                                          | 4-3        |

|         | М                                           | 4-4        |

|         | × A                                         | 4-4        |

|         | BR and LR                                   | 4-5        |

|         | U                                           | 4-5        |

|         | MAXS                                        | 4-5        |

|         | $\mathbf{C}$                                | 4-6        |

|         | <b>C</b> DU                                 | 4-6        |

|         | CPU                                         | 4-6        |

|         | Arithmetic and Logical Registers            | 4-6        |

|         |                                             | 4-6        |

|         | 24-Bit Function Box                         | 4-7        |

|         |                                             | 4-7        |

|         |                                             | 4-7        |

|         | • DIFF                                      | 4-7        |

|         |                                             |            |

|         | • <i>CMPX</i> , CMPY                        | 4-7<br>4-7 |

|         | MSKX, MSKY                                  |            |

|         | BICN                                        | 4-7        |

|         | XYST                                        | 4-8        |

|         | • 4-Bit Function Box                        | 4-9        |

|         | Interrupt and Processor Status Registers    | 4-9        |

|         | CA and CB                                   | 4-9        |

|         | CC and CD                                   | 4-9        |

|         | INCN                                        | 4-10       |

| Section   | J                                              | Page |

|-----------|------------------------------------------------|------|

|           | - PÉRP                                         | 4-10 |

|           |                                                | -    |

|           |                                                | 4-11 |

|           |                                                | 4-11 |

| م<br>مورن | $\mathbf{c}$                                   | 4-11 |

|           | •                                              | 4-12 |

|           |                                                | 4-12 |

|           | CMND                                           |      |

|           | DATA                                           |      |

|           | / FLCN                                         |      |

|           | />NULL                                         |      |

|           | CSW                                            | 4-13 |

|           |                                                | 4-13 |

|           |                                                |      |

| 5         | MICROINSTRUCTIONS                              |      |

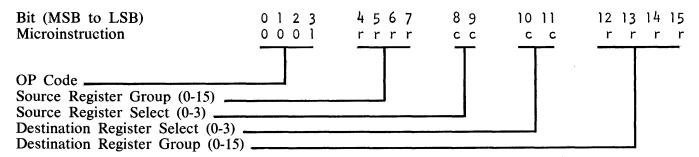

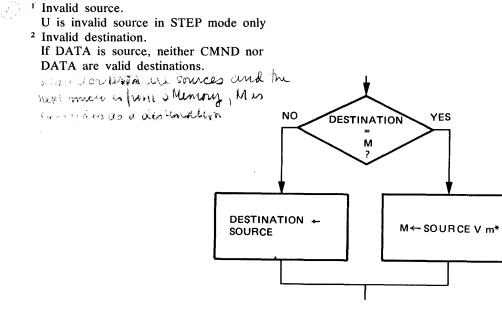

|           | 1C Register Move.                              | 5-2  |

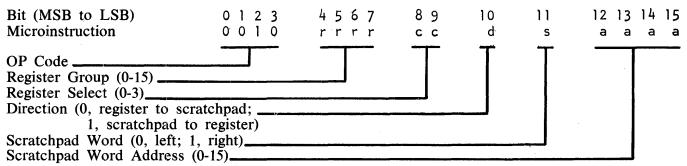

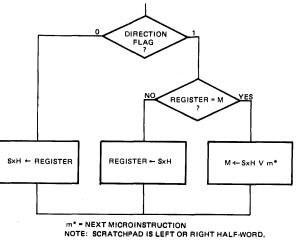

|           | 2C Scratchpad Move                             | 5-3  |

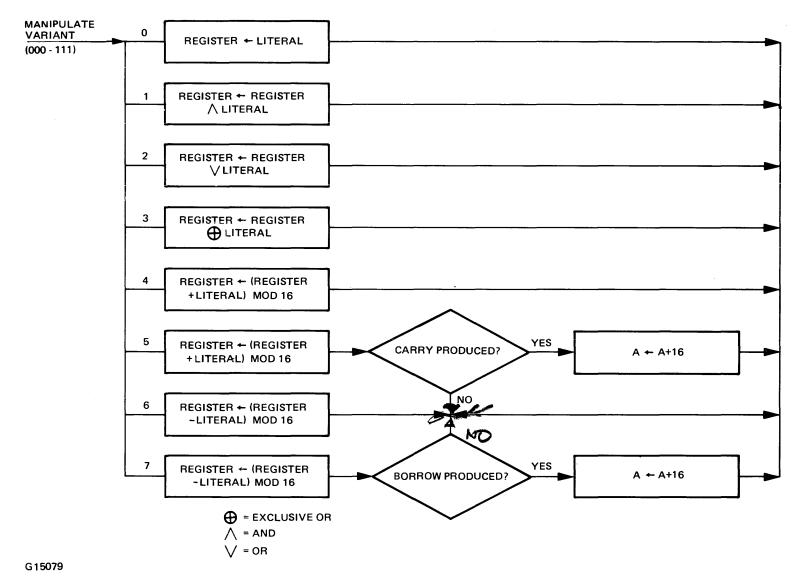

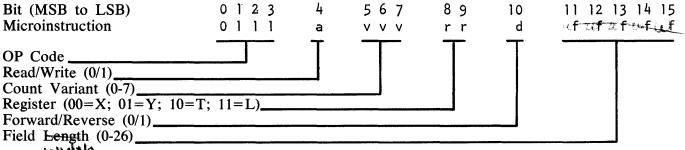

|           | 3C 4-Bit Manipulate.                           | 5-4  |

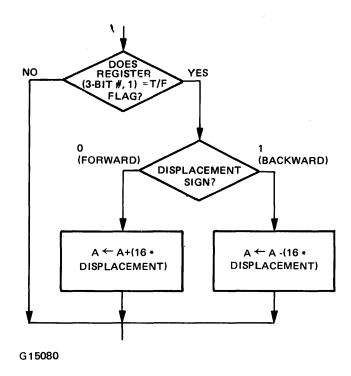

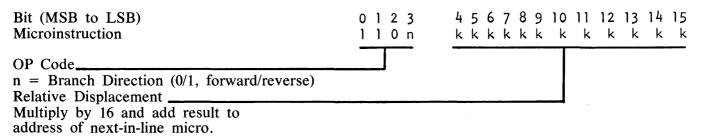

|           | 4C, 5C Bit Test Branch Relative                | 5-6  |

|           | 6C Skip When                                   | 5-8  |

|           | 7C Read/Write Memory                           |      |

|           |                                                |      |

|           | 8C Move 8-Bit Literal                          |      |

|           |                                                | 5-14 |

|           | 10C Shift/Rotate T                             |      |

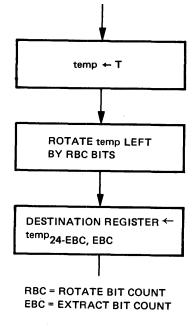

|           | 11C Extract from T                             |      |

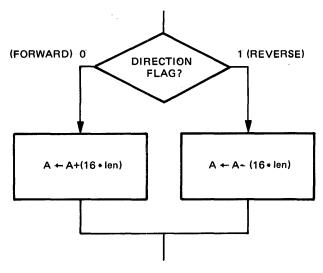

|           | 12C, 13C Branch Relative Forward, Reverse      |      |

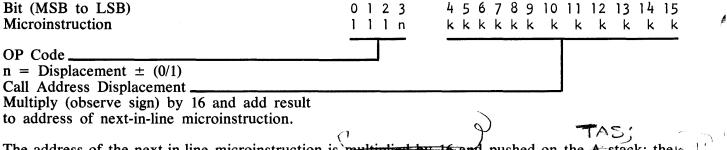

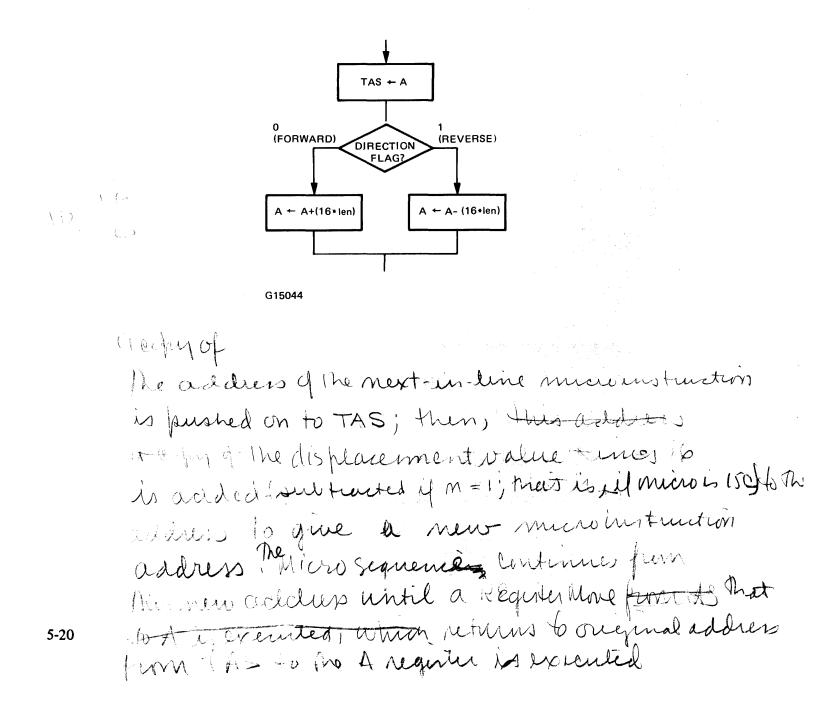

|           | 14C, 15C Call Relative Forward, Reverse        | 5-20 |

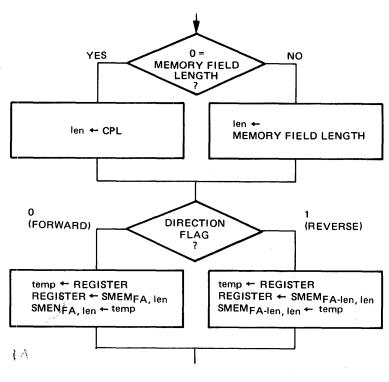

|           | 2D Swap Memory                                 | 5-21 |

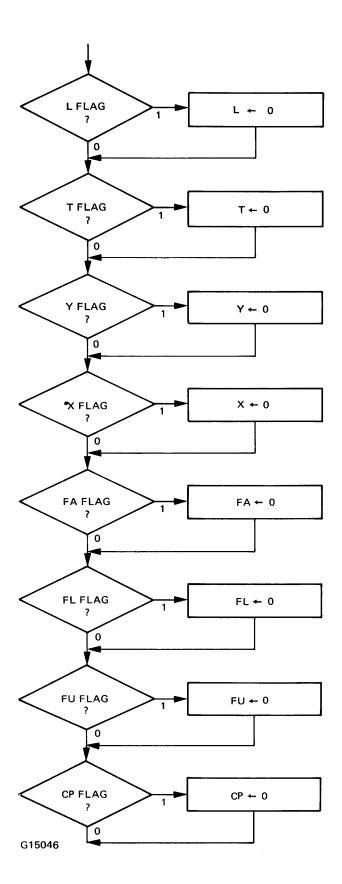

|           | 3D Clear Registers                             | 5-22 |

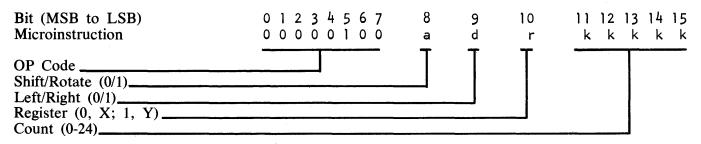

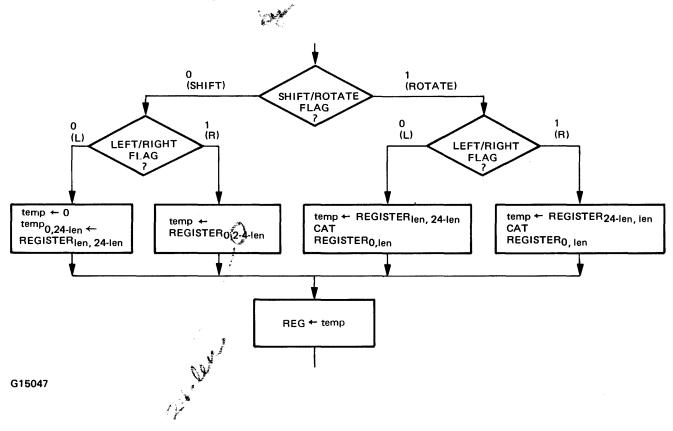

|           | 4D Shift/Rotate X or Y                         |      |

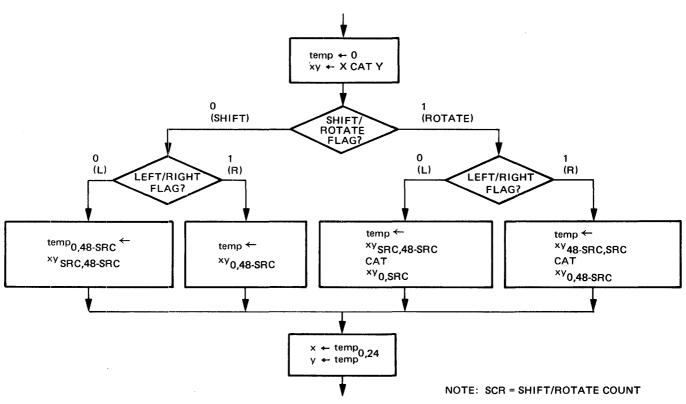

|           | 5D Shift/Rotate X Concatenated with Y          |      |

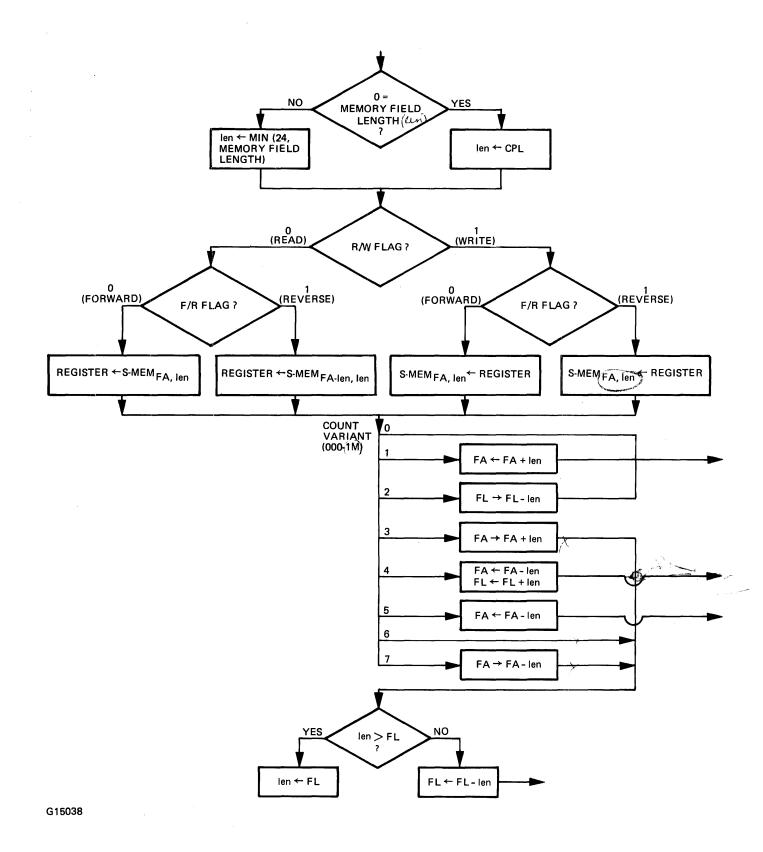

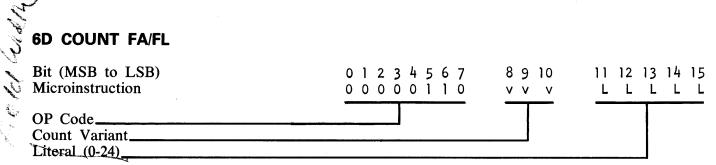

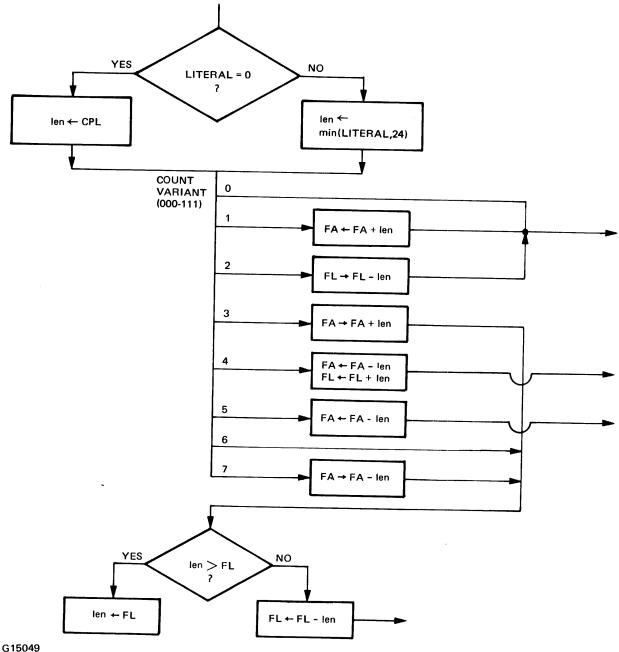

|           | 6D Count FA/FL                                 | 5-26 |

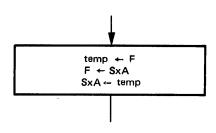

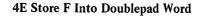

|           | 7D Exchange F with Doublepad Word              |      |

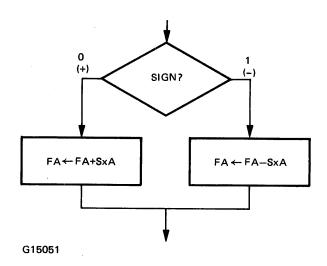

|           | 8D Scratchpad Relate FA                        |      |

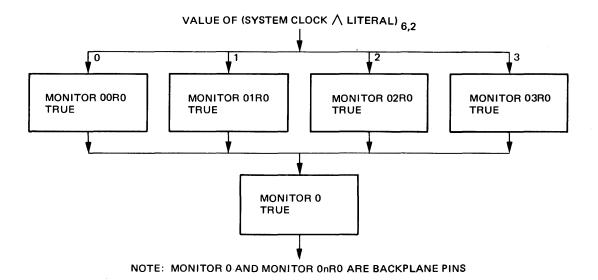

|           | 9D Monitor                                     |      |

|           | 10D Nano Move                                  |      |

|           |                                                |      |

|           | 11D Diagnostic Read/Write Memory               |      |

|           |                                                | 5-36 |

|           |                                                | 5-38 |

|           |                                                | 5-40 |

|           | 4                                              | 5-42 |

|           | -                                              | 5-42 |

|           |                                                | 5-42 |

|           |                                                | 5-44 |

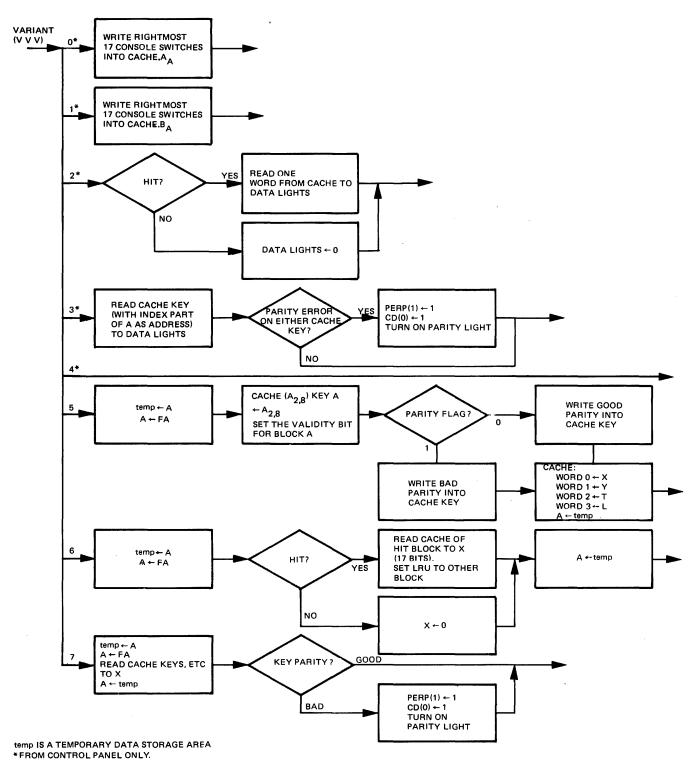

|           | V=0: Write From Console One Word Into Block A  | 5-44 |

|           | V=1: Write From Console One Word Into Block B. | 5-44 |

|           | V=2: Read One Word From Cache to Data Lights   | 5-44 |

|           |                                                | 5-44 |

|           |                                                | 5-45 |

|           |                                                | 5-45 |

|           |                                                | 5-45 |

|           | 0                                              | 5-45 |

|           | 1F Halt                                        |      |

|           | 11 11411                                       | )-4/ |

v

| Section |                                                                                                | Page         |

|---------|------------------------------------------------------------------------------------------------|--------------|

|         |                                                                                                | 5-47<br>5-48 |

|         |                                                                                                | 5-48         |

|         |                                                                                                | 5-48         |

|         |                                                                                                | 5-50         |

|         |                                                                                                | 5-51         |

|         | 0 No Operation                                                                                 | 5-51         |

| 6       | I/O SUBSYSTEMS AND DEVICE CONTROLS                                                             |              |

|         | Display Console Subsystem                                                                      | 6-1          |

|         | Introduction                                                                                   | 6-1          |

|         | Operations                                                                                     | 6-2          |

|         | Read                                                                                           | 6-3          |

|         | Write                                                                                          | 6-4          |

|         | Test                                                                                           | 6-4          |

|         | Result Descriptor                                                                              | 6-5          |

|         | Not Ready                                                                                      | 6-5          |

|         |                                                                                                | 6-5          |

|         |                                                                                                | 6-5          |

|         | Mode                                                                                           | 6-5          |

|         |                                                                                                | 6-6          |

|         |                                                                                                | 6-6          |

|         | Card Subsystems    80-Column Card Reader Control    80                                         | 6-6          |

|         |                                                                                                | 6-6          |

|         |                                                                                                | 6-6          |

|         | Operations                                                                                     | 6-7          |

|         | Definitions of Variants                                                                        | 6-7          |

|         | Read                                                                                           |              |

|         |                                                                                                | 6-7          |

|         |                                                                                                | 6-7          |

|         | Stop                                                                                           | 6-7          |

|         | Result Descriptor                                                                              | 6-7          |

|         | 80-Column Card Punch Control                                                                   | 6-8          |

|         |                                                                                                | 6-8          |

|         | Operations                                                                                     | 6-8          |

|         | Definitions of Variants                                                                        | 6-8          |

|         | Write (Punch) $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 6-9          |

|         | Test                                                                                           | 6-9          |

|         | Pause                                                                                          | 6-9          |

|         | Stop                                                                                           | 6-9          |

|         | Result Descriptor                                                                              | 6-9          |

|         | Not Ready                                                                                      | 6-9          |

|         | Power Off                                                                                      | 6-10         |

|         | Stop                                                                                           | 6-10         |

|         | Feed Failure                                                                                   | 6-10         |

|         | Card Jam                                                                                       | 6-10         |

|         |                                                                                                | 6-10         |

|         | Memory Parity Error                                                                            | 6-10         |

|         |                                                                                                | 6-10         |

| ·       |                                                                                                | 6-10         |

|         |                                                                                                | 6-10         |

|         |                                                                                                | 6-11         |

|         |                                                                                                | 6-11         |

|         |                                                                                                | 6-11         |

.

1

#### Section

|                                          | 5-11         |

|------------------------------------------|--------------|

|                                          | 5-11         |

|                                          | 5-12         |

|                                          | 5-12         |

|                                          | 5-13         |

|                                          | 5-13         |

|                                          | 5-13         |

| Punch, Print, and Read                   | 5-13         |

|                                          | 5-13         |

| Stop                                     | 6-13         |

| Pause                                    | 5-13         |

| Result Descriptor                        | 5-14         |

|                                          | 5-14         |

|                                          | 5-15         |

|                                          | 5-15         |

|                                          | 6-15         |

|                                          | 5-15         |

|                                          | 6-15         |

|                                          | 6-15         |

| Second Operation Complete Bit            | 6-15         |

| 96-Column Card Read-Punch-Print Control. | 5-15         |

|                                          | 5-15         |

|                                          | 5-15<br>5-16 |

| Definitions of Variants                  |              |

|                                          |              |

| Result Descriptor                        |              |

| Not Ready                                | 5-17<br>5-17 |

|                                          | 5-17<br>6-17 |

|                                          |              |

|                                          | 6-18         |

|                                          | 5-18         |

| <u>F</u>                                 | 6-18         |

|                                          | 5-18         |

|                                          | 5-18         |

|                                          | 5-18         |

|                                          | 5-19         |

| Operations                               |              |

| Definitions of Variants                  |              |

|                                          | 5-25         |

|                                          | 6-25         |

|                                          | 5-25         |

|                                          | 6-25         |

| Pause                                    | 5-25         |

| Result Descriptor                        | 5-25         |

|                                          | 5-26         |

| Not Ready                                | 6-26         |

|                                          | 6-27         |

|                                          | 5-27         |

|                                          | 5-27         |

|                                          | 5-27         |

|                                          | 5-27         |

|                                          | 5-27         |

|                                          | 5-28         |

Page

Page

#### Section

`

| Magnetic Tape Cassette Subsystem       |      |

|----------------------------------------|------|

| Introduction                           |      |

| Operations                             |      |

| Definitions of Variants                |      |

| Read                                   | 6-30 |

| Space-to-EOF                           | 6-30 |

|                                        | 6-30 |

| Rewind                                 |      |

| Test                                   |      |

| Lock                                   |      |

| Stop                                   |      |

| Pause                                  |      |

| Result Descriptor                      |      |

| I/O Descriptor Initiation              |      |

| Magnetic Tape Subsystems               |      |

|                                        |      |

|                                        |      |

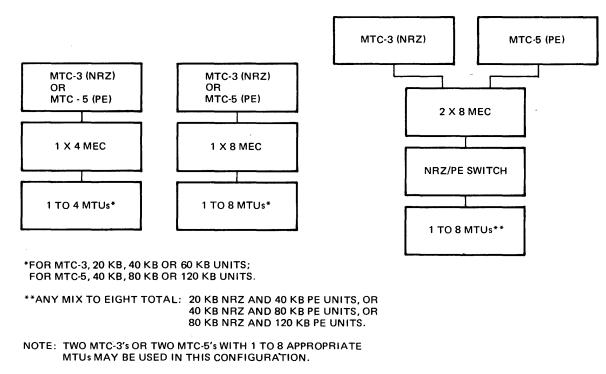

| NRZ Tape Subsystem (MTC-3)             |      |

| Introduction                           |      |

| Operations                             |      |

|                                        | 6-37 |

|                                        | 6-38 |

| Space                                  |      |

| Write                                  |      |

| Rewind                                 |      |

| Test                                   |      |

| Lock                                   |      |

| Stop                                   | 6-39 |

| Pause                                  | 6-39 |

| Result Descriptor (Non-Test Operators) | 6-40 |

| Exception Condition                    | 6-40 |

| Not Ready                              | 6-40 |

| Data Error                             | 6-40 |

| Access Error                           | 6-41 |

|                                        | 6-41 |

|                                        | 6-41 |

| Beginning of Tape (BOT)                |      |

|                                        | 6-41 |

| End of File Tape Mark Detected         |      |

| Rewinding                              |      |

|                                        | 6-42 |

| CRC Correction Possible                |      |

|                                        |      |

| PE Tape Subsystem (MTC-5)              |      |

|                                        |      |

|                                        |      |

|                                        |      |

| D 1                                    |      |

|                                        |      |

| Space                                  |      |

| Write                                  |      |

| Rewind                                 |      |

| - ·                                    | 6-44 |

| Lock                                   | 6-44 |

#### Section

| Stop.       6-44         Pause       6-44         Result Descriptor       6-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Result Descriptor 6-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Exception Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Not Ready                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Data Error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| End of Tape (EOT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Beginning of Tape (BOT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Tape Mark Detected    6-40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Rewinding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Timeout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Tape Format         6-40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Transmission Error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Diagnostic Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Channel Address (AAAA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

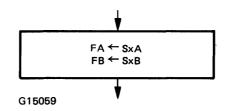

| Diagnostic Variant (VVVV) $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $6-4'$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Industry Compatible Mini-Disk Subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

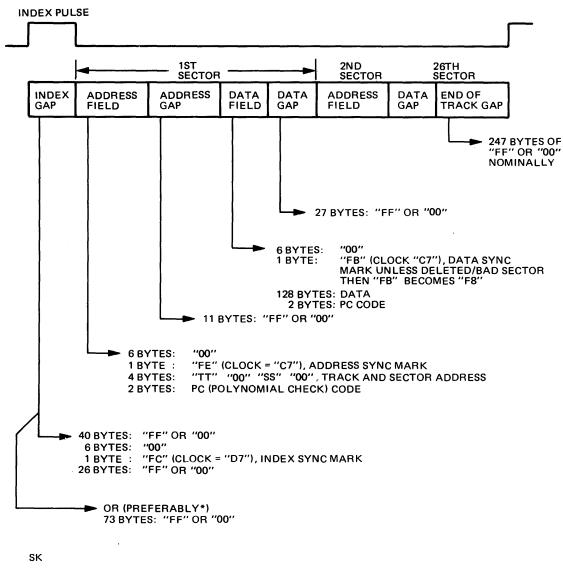

| Format and Disk Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Definitions of Variants                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Read Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Write Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Restore                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Initialize                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Read Absolute                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Result Descriptor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Exception Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Not Ready                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Data PC (Polynomial Check) Error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Write Fault         6.000         2.101         6.000         2.101         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000 |

| Track Seek Error $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Sector Search Error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Timeout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Special Sector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |