INTRODUCTION

PRINCIPLES OF OPERATION

# FIELD ENGINEERING TECHNICAL MANUAL

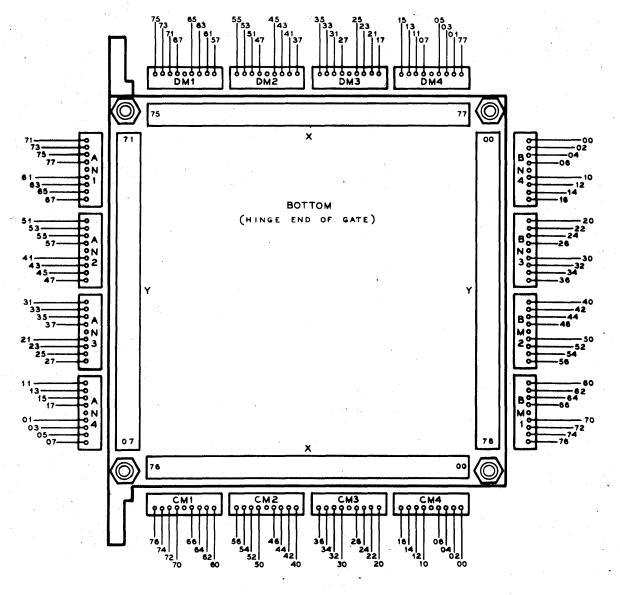

# Burroughs B 461 HI-SPEED CORE MEMORY

FUNCTIONAL DESCRIPTION-

**FUNCTIONAL**

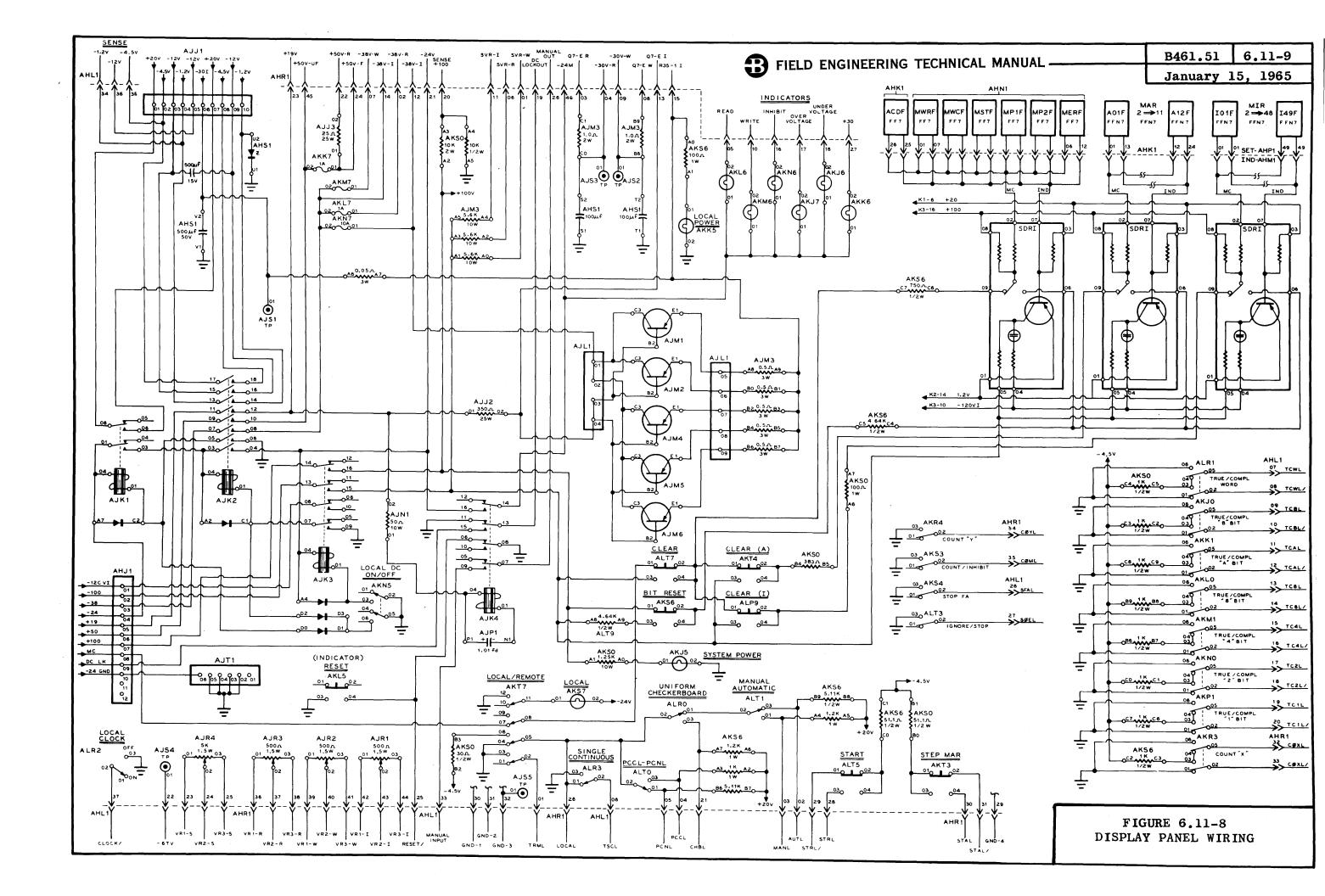

DESCRIPTION-ELECTRONIC

MECHANICAL

ASSEMBLY-DISASSEMBLY-ADJUSTMENTS

MAINTENANCE PROCEDURES AND AIDS

INSTALLATION PROCEDURES

> OPTIONAL FEATURES

| B461.51     | 1.0-1    |

|-------------|----------|

| <br>January | 15, 1965 |

# INDEX - SECTION I

#### **1** INTRODUCTION

| 1.1 | General Description      | January | 15, | 19 <b>6</b> 5 |

|-----|--------------------------|---------|-----|---------------|

| 1.2 | Equipment Specifications | January | 15, | 1 <b>96</b> 5 |

| 1.3 | Communication            | January | 15, | 19 <b>6</b> 5 |

| 1.4 | Power & Power Control    | January | 15, | 1965          |

| 1.5 | Off-Line Functions       | January | 15, | 19 <b>6</b> 5 |

| 1.6 | Glossary of Terms        | January | 15, | 1965          |

| B461.51 |     | 1. | 1- | 1 |  |

|---------|-----|----|----|---|--|

| January | 15, | 1  | 96 | 5 |  |

#### 1.1 GENERAL DESCRIPTION

The B461 Memory Unit is a high speed, random-access Memory using ferromagnetic cores as a storage media. The Memory is a self-contained Unit including Power Regulators, Current Drivers, Sense Amplifiers, Timing Circuits, and Information and Address Registers.

All circuitry in the B461 is of the solid state type with gating characteristics conforming to the B5500.

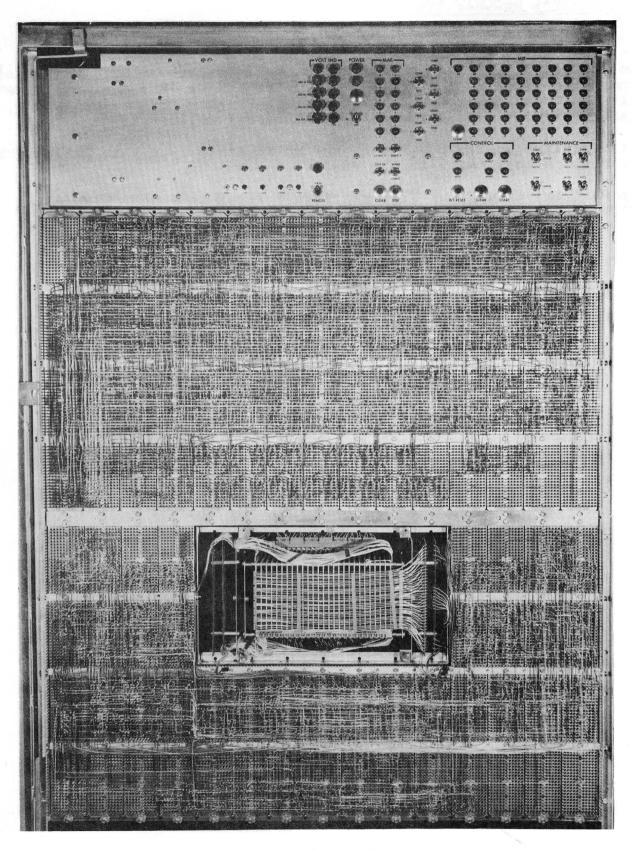

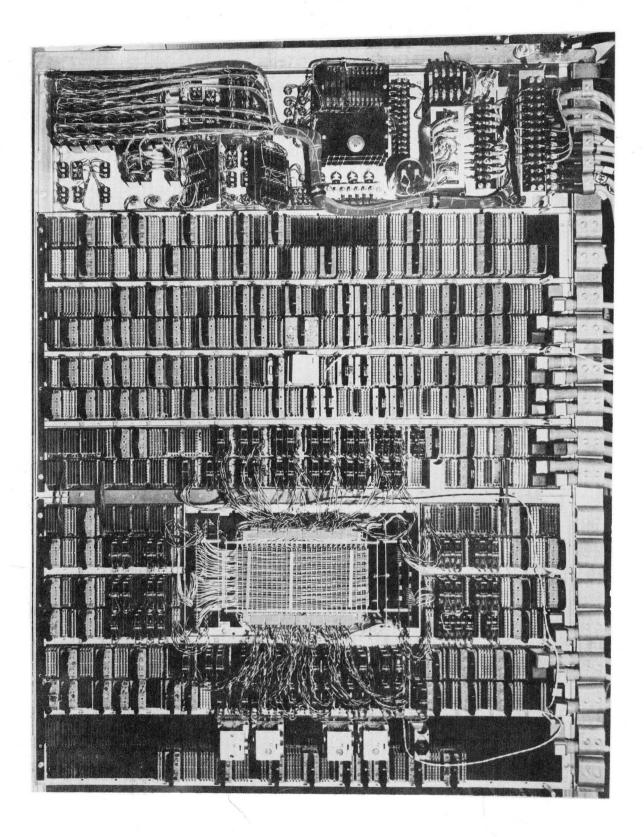

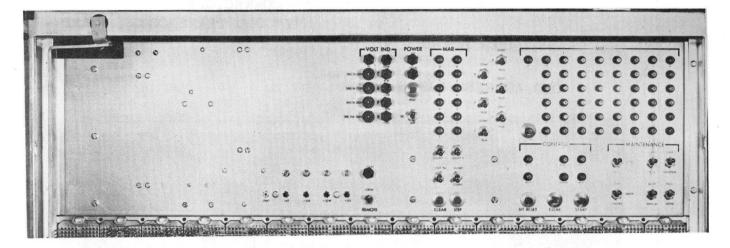

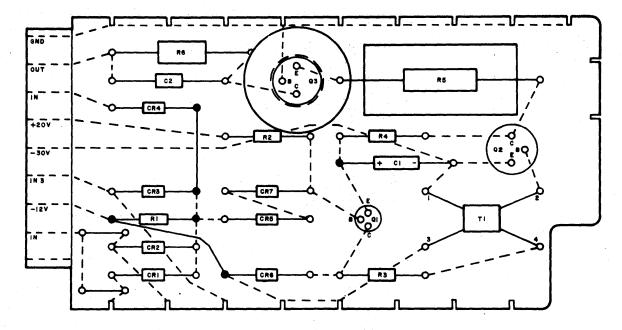

Figure 1.1-1 is a Front View and Figure 1.1-2 is a Rear View of a B461 Memory Module.

See Pages 1.1-2 & 1.1-3.

FIGURE 1.1-1 MEMORY MODULE - FRONT VIEW (WIRING SIDE)

FIGURE 1.1-2 MEMORY MODULE - REAR VIEW (PACKAGE SIDE)

Printed in U.S.A.

FIELD ENGINEERING TECHNICAL MANUAL -

| B461.51 |     | 1.2-1 |

|---------|-----|-------|

| January | 15, | 1965  |

#### **1.2 EQUIPMENT SPECIFICATIONS**

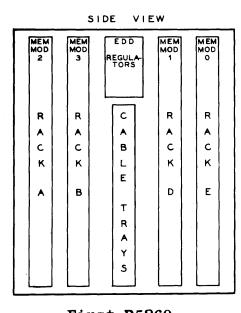

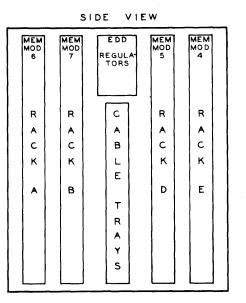

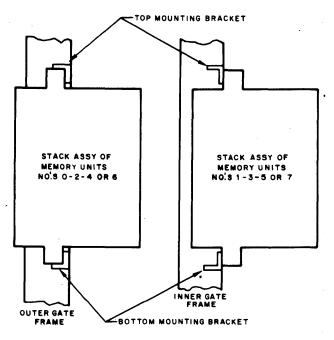

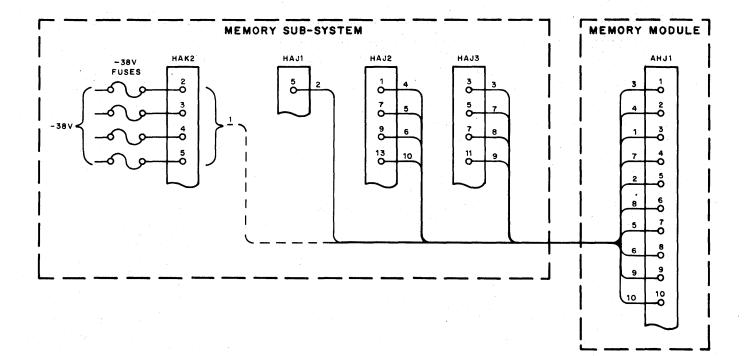

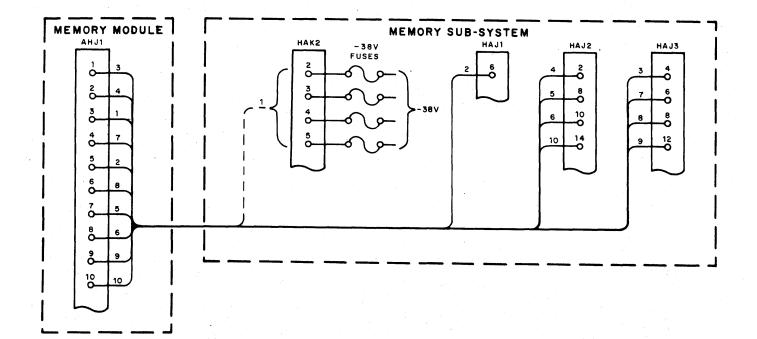

The B461 Memory is mounted in the B5260 Cabinet of the B5500. The B5260 can contain four B461 Memory Modules. If more than four B461 Memory Modules are needed on a B5500, then a second B5260 Memory Sub-System is installed which can also contain four B461 Modules.

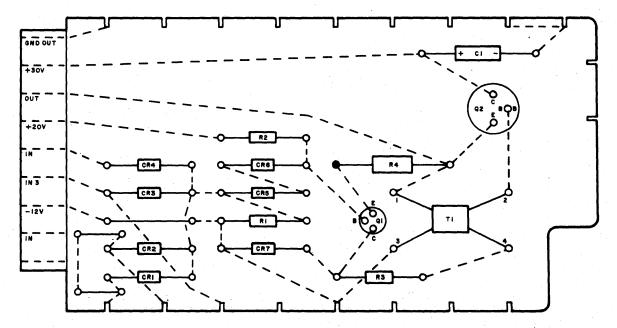

Figure 1.2-1 is an illustration of the B461 Modules in a B5260 Memory Sub-System with the locations of each of the Modules.

First B5260

Second B5260

FIGURE 1.2-1 B5260 MEMORY SUB-SYSTEM

The only difference between the two Sub-Systems is the numbering of the B461 Modules; 0 thru 3 in the first B5260, and 4 thru 7 in the second B5260.

#### Information Capacity

Each B461 Memory Module has a capacity of 4096 words. Each B5260 Sub-System can then contain 16,384 words and a maximum size Memory System with two B5260 units can consist of 32,768 words of core storage. Each word consists of 49 bits; 48 Information bits and 1 Parity bit.

#### Speed

The B461 has a Memory cycle time, READ or WRITE of four microseconds. The READ access time is two microseconds and the WRITE access time is one microsecond. FIELD ENGINEERING TECHNICAL MANUAL -----

| B461.51 | 1   | .3-1 |

|---------|-----|------|

| January | 15, | 1965 |

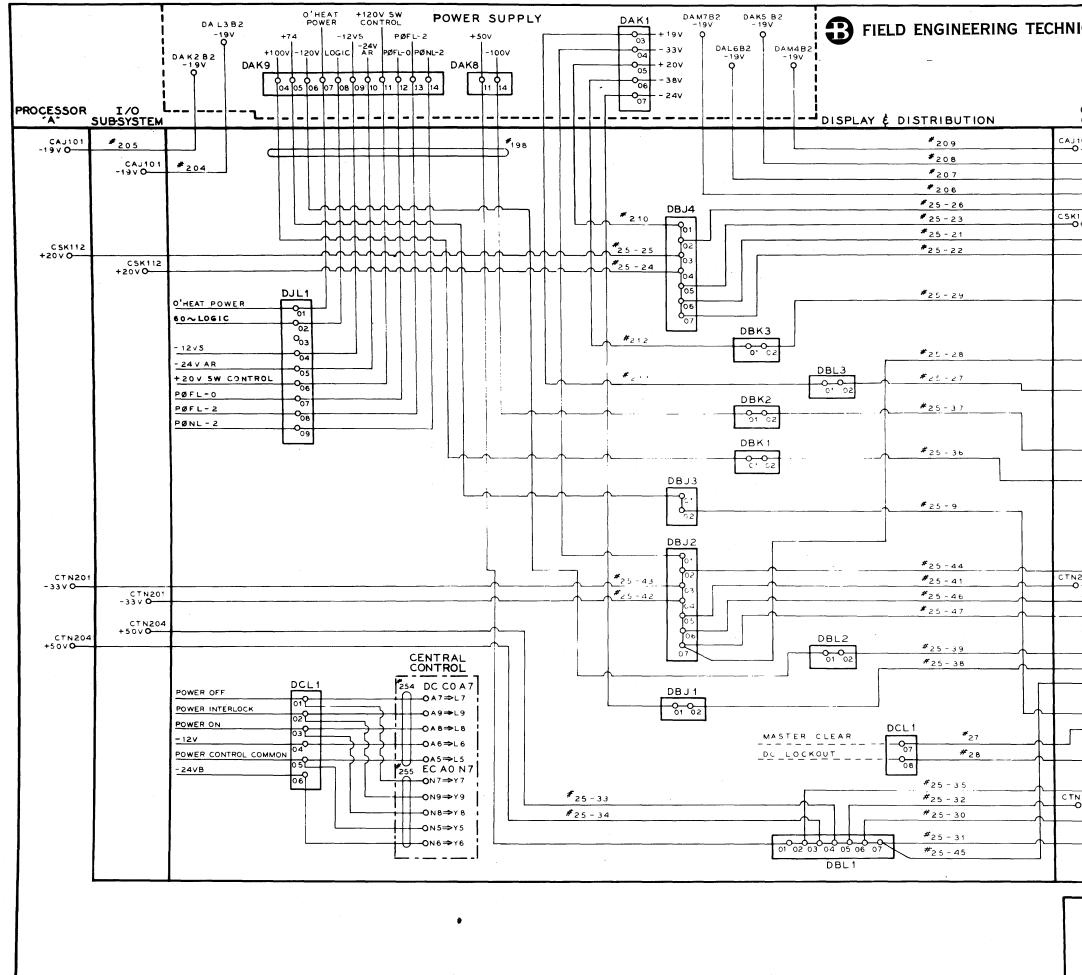

# 1.3 COMMUNICATION

Communication with a B461 by a Requesting Unit, Processor or I/O, is via the Memory Exchange portion of Central Control. Each B461 on a System is individually cabled from Central Control for all Information and Control Lines to and from the Module. The following is a list of the Communication Lines for any particular Memory Module.

Control Lines To Memory

| 1. | 1         | line  | Clock                                  |

|----|-----------|-------|----------------------------------------|

| 2. | 1         | line  | Write Level (WOOD-C)                   |

| 3. | 1         | line  | Start Memory (A00S-C)                  |

| 4. | 12        | lines | Address (A01S-C thru A12S-C)           |

| 5. | <b>48</b> | lines | Write Information (WO1S-C thru W48S-C) |

| 6. | 1         | line  | Single Pulse Status (SPUL/)            |

| 7. | 1         | line  | Master Clear                           |

#### Control Lines From Memory

| 1. | l line Cable Interlock (CINL/)                        |

|----|-------------------------------------------------------|

| 2. | l line Memory Parity Error (MERF)                     |

| 3. | 4 lines Memory Timing                                 |

|    | a. 1 line Read Obtained Line (MWCF)                   |

|    | b. l line Memory Cycle Finished Not (MCFS/)           |

|    | c. 2 lines Read Access Obtained Lines (RAØD & RAØS/)  |

| 4. | 49 lines Read Information (IO1F/ thru I48F/ and I48F) |

| 5. | l line Memory Not Available (MNAL)                    |

|    |                                                       |

FIELD ENGINEERING TECHNICAL MANUAL -

| B461.51 | 1.4-1    |  |

|---------|----------|--|

| January | 15, 1965 |  |

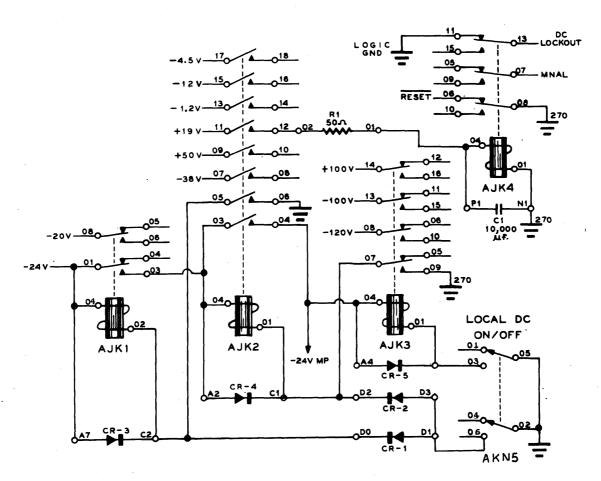

#### 1.4 POWER & POWER CONTROL

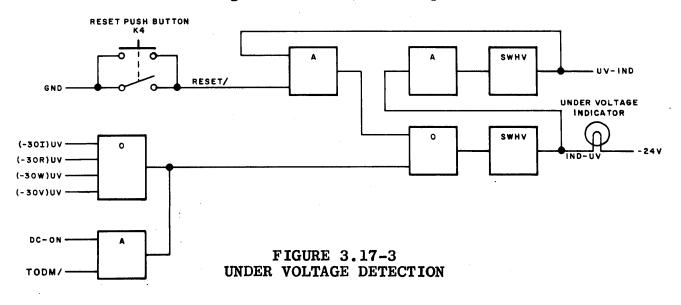

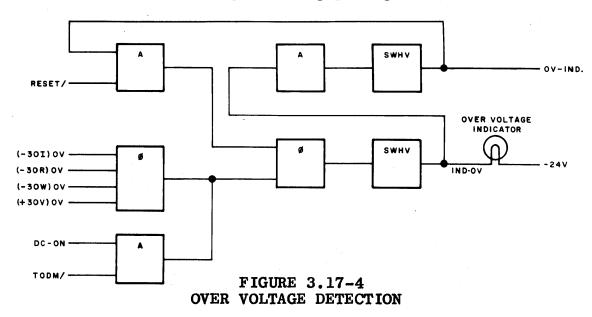

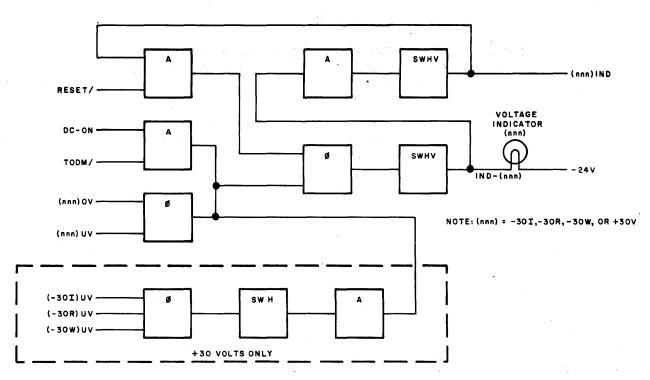

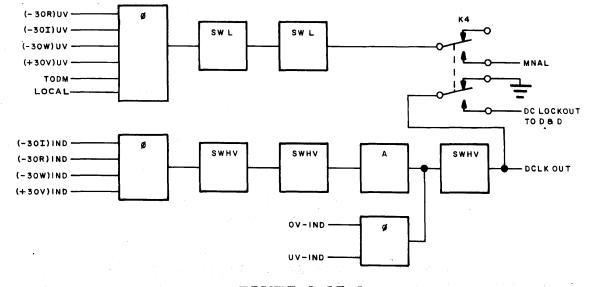

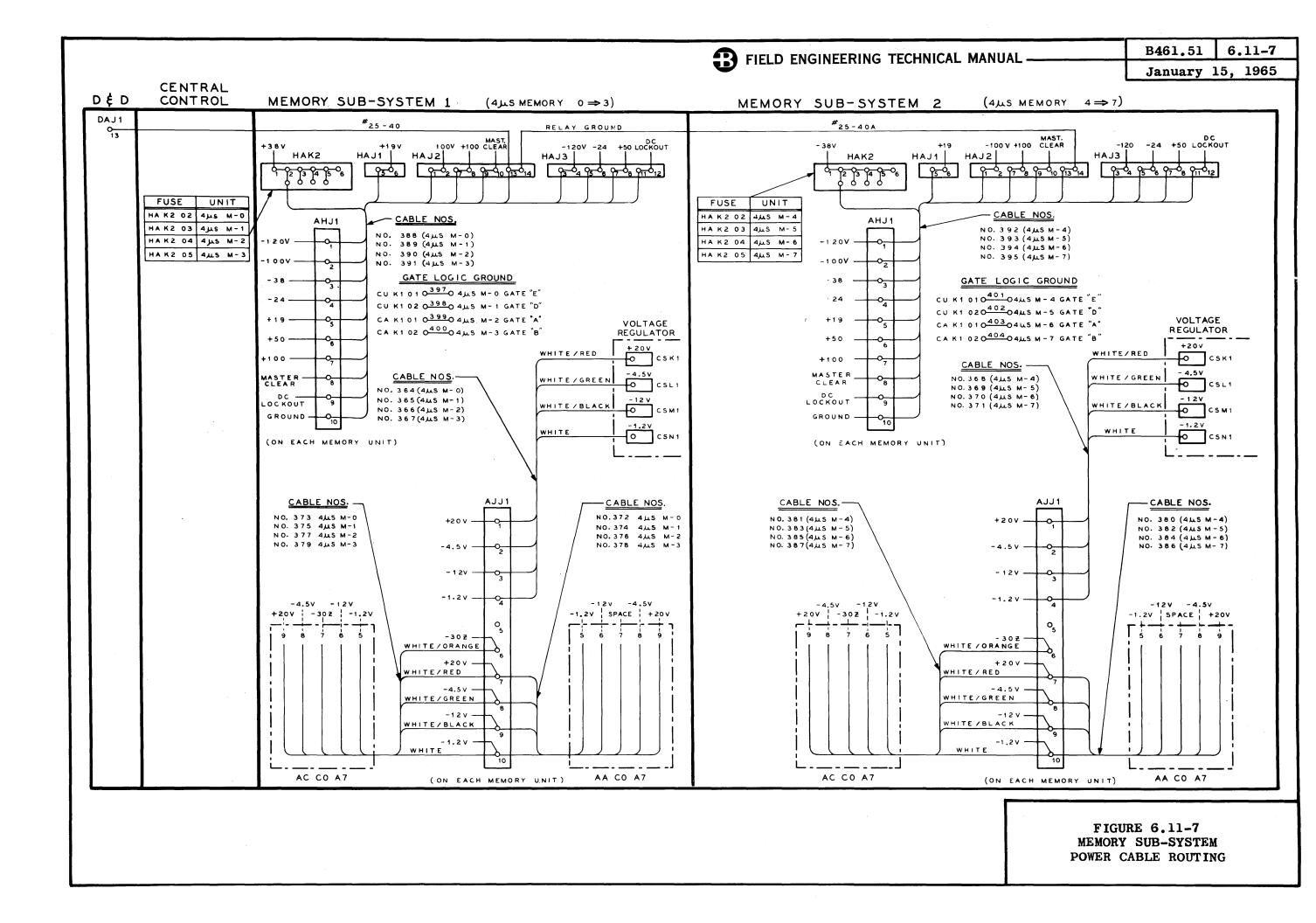

All power required by a B461 Memory Module is obtained from the B5500 Power Supply. This power is delivered to the B5260 Memory Sub-System, then distributed to the Memory Modules. Power sequencing is controlled by the B5500 and each Memory Module. Over and Under Voltage Sensing circuitry is provided in each Memory Module and Thermal protection in each Memory Sub-System.

The following is a list of the Power and Power Control lines to a Memory Sub-System.

- 11 lines DC Power Input

- 1 line Logic Ground

- 1 line -24 Volt Ground

- 1 line Excess Current Sensing

- 3 lines Voltage Sensing

- 1 line DC Lockout Sensing

- 1 line Temperature Sensing

FIELD ENGINEERING TECHNICAL MANUAL -----

| B461.51 | 1.5-1    |

|---------|----------|

| January | 15, 1965 |

#### 1.5 OFF-LINE FUNCTIONS

Off-line functions are accomplished within each individual Module and are used for maintenance and testing of the Memory. The testing of a Memory is divided into three categories:

- 1. Manual

- 2. Automatic

- 3. Checkerboard

These three modes of testing will be explained in Section 6 of this manual.

An additional Off-line maintenance feature is that DC Power can be turned ON and OFF in a particular Module without affecting the remainder of the System.

# B FIELD ENGINEERING TECHNICAL MANUAL -----

| B461.51 |     | 1. | 6- | 1 |  |

|---------|-----|----|----|---|--|

| January | 15, | 1  | 96 | 5 |  |

# 1.6 GLOSSARY OF TERMS

|                  | an a                        |

|------------------|-----------------------------------------------------------------|

| Aøøs             | Memory Start from Central Control                               |

| A01S thru A12S   | Address Lines from Central Control                              |

| A+1D             | Address Register Plus One Driver                                |

| A+1L             | Address Register Plus One Level                                 |

| A+1S/            | Address Register Plus One Not Switch                            |

| A+1S             | Address Register Plus One Switch                                |

| ACDF             | Address Counter Delay Flip-Flop                                 |

| A01F thru A12F   | Address Register Flip-Flops                                     |

| AX1S thru AX6S   | Address X Switches                                              |

| AX1S/ thru AX6S/ | Address X Not Switches                                          |

| AYIS thru AY6S   | Address Y Switches                                              |

| AYIS/ thru AY6S/ | Address Y Not Switches                                          |

| CAG001           | AX1S · AX2S · C $\emptyset$ XL · (A+1D)                         |

|                  | $AX1S \cdot AX2S \cdot AX3S \cdot AX4S \cdot CØXL \cdot (A+1D)$ |

| CAG003           |                                                                 |

|                  | CØYD · AYIS · AY2S · AY3S · AY4S                                |

|                  | AX1S · AX2S · AX3S · AX4S · AX5S · AX6S ·                       |

|                  | AYIS · AY2S · AY3S · AY4S · AY5S · AY6S                         |

| CAG006           | PC3S · TRMS/ · MANS/                                            |

| CAG007           | MSTL • MP1F/ • MP2F/ • MSTF • MANS/                             |

| CAG008           | MP1F · MP2F · MSTF · MANS/                                      |

| CCP-1 thru CCP-6 | Local Clock Driver Output                                       |

| 1CLP-1           | Local Clock Oscillator Output 1                                 |

| 1CLP-2           | Local Clock Oscillator Output 2                                 |

|                  | Local 1 Megacycle Pulse                                         |

|                  | Count Y Driver                                                  |

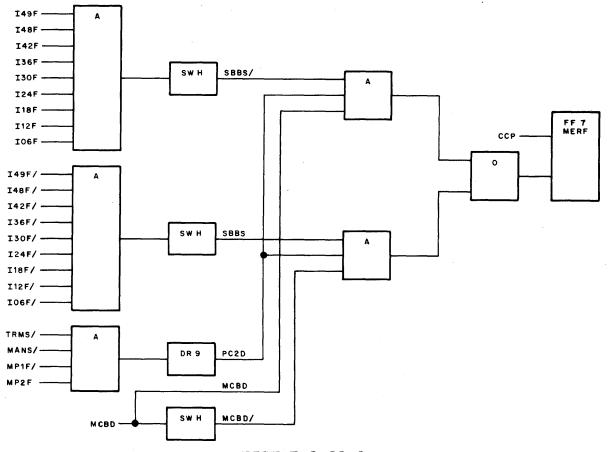

| CTUS             | Continue Switch                                                 |

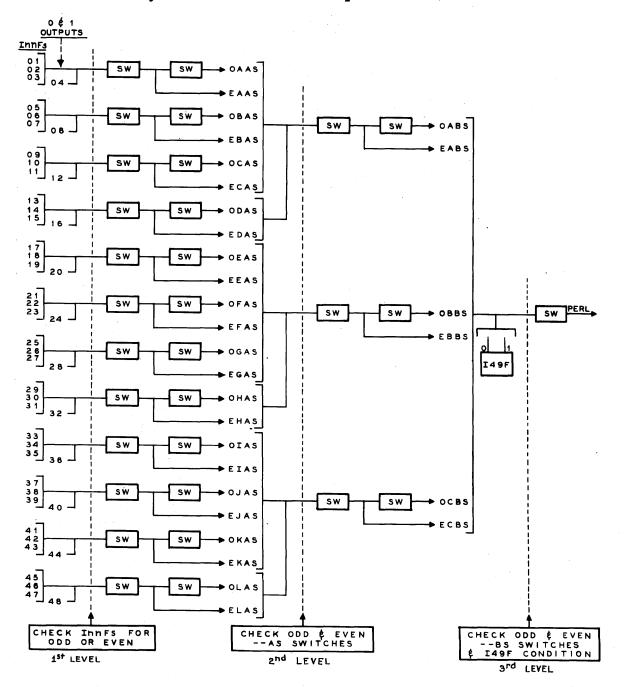

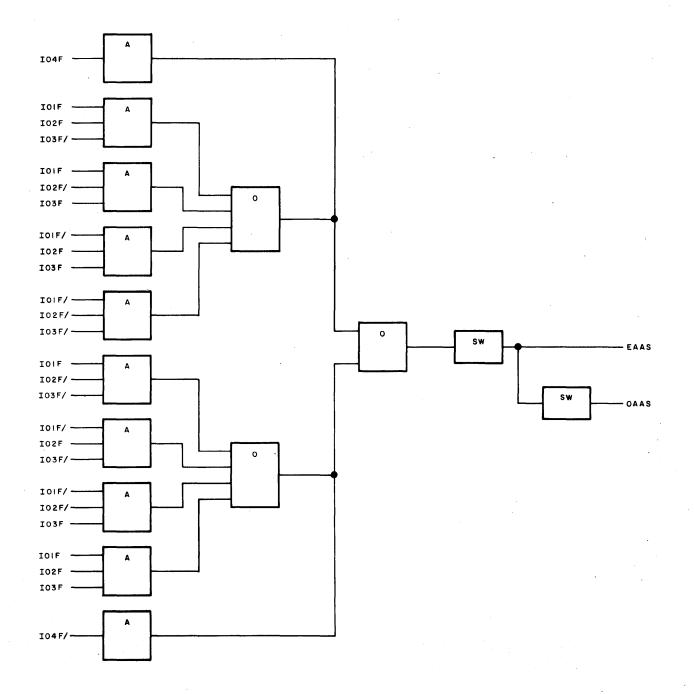

| ØAAS             | Parity Odd I01F thru I04F Switch                                |

| EAAS             | Parity Even IO1F thru IO4F Switch                               |

| ØBAS             | Parity Odd I05F thru I08F Switch                                |

| EBAS             | Parity Even IO5F thru IO8F Switch                               |

| ØCAS             | Parity Odd 109F thru 112F Switch                                |

| ECAS             | Parity Even IO9F thru I12F Switch                               |

| ØDAS             | Parity Odd I13F thru I16F Switch                                |

| EDAS             | Parity Even I13F thru I16 F Switch                              |

|                  |                                                                 |

| ØEAS I20F Switch                               |

|------------------------------------------------|

| EEAS I20F Switch                               |

| ØFAS I24F Switch                               |

| EFAS I24F Switch                               |

| ØGAS I28F Switch                               |

| EGAS 128F Switch                               |

| ØHAS I32F Switch                               |

| EHAS 132F Switch                               |

| ØIAS I36F Switch                               |

| EIAS I36F Switch                               |

| ØJAS I40F Switch                               |

| EJAS I40F Switch                               |

| ØKAS I44F Switch                               |

| EKAS I44F Switch                               |

| ØLAS I48F Switch                               |

| ELAS I48F Switch                               |

| ØABS Darity Odd AA thru DA Switch              |

| EABS Darity Even AA thru DA Switch             |

| ØBBS HA Switch                                 |

| EBBS HA Switch                                 |

| ØCBS LA Switch                                 |

| ECBS LA Switch                                 |

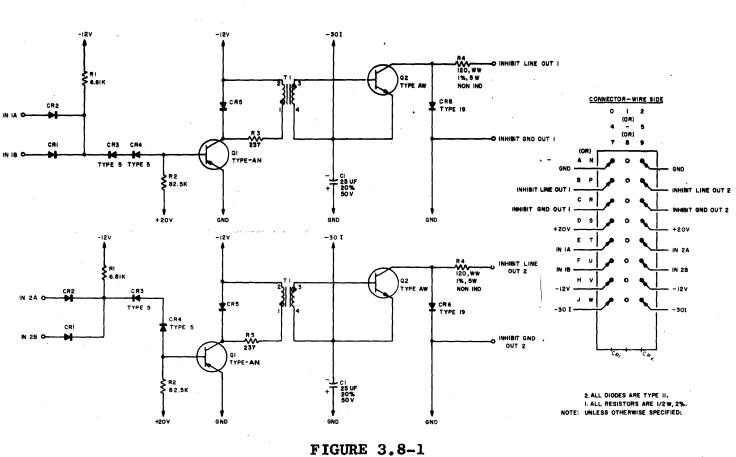

| IO1D thru I49D Inhibit Drivers                 |

| I01F thru I49F Information Register Flip-Flops |

| MACD Memory Address Register Clear Driver      |

| MANS/ Manual Not Switch                        |

| MC1D Maintenance Control 1 Bit Driver          |

| MC2D Bit Driver                                |

| MC4D 4 Bit Driver                              |

| MC8D 8 Bit Driver                              |

| MCAD A Bit Driver                              |

| MCBD Baintenance Control B Bit Driver          |

| MC1S/ Maintenance Control 1 Bit Not Switch     |

| MC2S/ Maintenance Control 2 Bit Not Switch     |

| MC4S/ Maintenance Control 4 Bit Not Switch     |

| MC8S/ 8 Maintenance Control 8 Bit Not Switch   |

| MCAS/ Maintenance Control A Bit Not Switch     |

|                                                |

| FIELD ENGINEERING TECHNICAL MANUAL | B <b>461.51</b> | 1.6-3   |

|------------------------------------|-----------------|---------|

|                                    | January 1       | 5, 1965 |

|        | Maintenance Control B Bit Not Switch       |

|--------|--------------------------------------------|

|        | Memory Cycle Finished Not Switch           |

| MERF   |                                            |

| MICD-1 | Memory Information Register Clear Driver 1 |

| MICD-2 | Memory Information Register Clear Driver 2 |

| MICM   | Memory Information Clear Multi             |

| MIHD   | Memory Inhibit Driver                      |

| MIHM   | Memory Inhibit Multi                       |

| MIHS/  | Memory Inhibit Not Switch                  |

| MISD   | Memory Input Strobe Driver (Remote Write)  |

| MP1F   | Memory Pulse Counter 1 Flip-Flop           |

| MP2F   | Memory Pulse Counter 2 Flip-Flop           |

| MR2M   | Memory Read 2 Multi                        |

| MRWP   | Memory Read to Write Delay Pulse           |

| MS1M   | Memory Switch 1 Multi                      |

| MSTD   | Memory Start Driver                        |

| MSTF   | Memory Start Flip-Flop                     |

| MSTL   | Memory Start Level                         |

| MSTS   | Memory Start Switch                        |

| MSTS/  | Memory Start Not Switch                    |

| MW2M   | Memory Write 2 Multi                       |

| Mw2S   | Memory Write 2 Multi Switch                |

| MWCF   | Maintenance Worst Case Flip-Flop           |

| MWRF   | Memory Write Flip-Flop                     |

| P03S   | Pulse Counter Equals 0 or 3 Switch         |

| PC2D   | Pulse Counter Equals 2 Driver              |

| PC1S   | Checkerboard Control Logic 1 Switch        |

| PC2S   | Checkerboard Control Logic 2 Switch        |

| PC3S   | Checkerboard Control Logic 3 Switch        |

| PC4S   | Checkerboard Control Logic 4 Switch        |

| PERL   | Parity Error Level                         |

| RAØD   | Read Access Obtained Driver                |

| RAØS/  | Read Access Obtained Not Switch            |

| RISD-1 | Read Information Strobe Driver 1           |

|        | Read Information Strobe Driver 2           |

|        | Read Information Strobe Driver 3           |

|        |                                            |

| RISD-4 Read Information Strobe Driver 4  |

|------------------------------------------|

| RSPD-1 Reset Single Pulse Driver 1       |

| RSPD-2 Reset Single Pulse Driver 2       |

| SIBS Sense 1 Bits Switch                 |

| S1BS/ Sense 1 Bits Not Switch            |

| S2BS Sense 2 Bit Switch                  |

| S2BS/                                    |

| S4BS Sense 4 Bits Switch                 |

| S4BS/ Sense 4 Bits Not Switch            |

| S8BS                                     |

| S8BS/Sense 8 Bits Not Switch             |

| SABS Sense A Bits Switch                 |

| SABS/ Sense A Bits Not Switch            |

| SBBS Sense B Bits Switch                 |

| SBBS/Sense B Bits Not Switch             |

| S01P thru S49P Sense Amplifiers          |

| SPUS Single Pulse Switch                 |

| STTP Strobe Timing Pulse                 |

| TRMS/ Remote Not Switch                  |

| WISD-1 Write Information Strobe Driver 1 |

| WISD-2 Write Information Strobe Driver 2 |

| XROD thru XR7D X Axis Read Driver        |

| XWOD thru XW7D X Axis Write Driver       |

| X00S thru X70S X Axis Switch Output      |

| X00G thru X70G X Axis Switch Return      |

| YROD thru YR7D Y Axis Read Driver        |

| YWOD thru YW7D Y Axis Write Driver       |

| YOOS thru Y70S Y Axis Switch Output      |

| YOOG thru Y70G Y Axis Switch Return      |

| FIELD ENGINEERING TECHNICAL MANUAL | B461.51 2.0-1    |

|------------------------------------|------------------|

|                                    | January 15, 1965 |

# INDEX - SECTION 2

# 2. PRINCIPLES OF OPERATION

| 2.1 | On-Line Operation  | January | 15, | 1965 |

|-----|--------------------|---------|-----|------|

| 2.2 | Off-Line Operation | January | 15, | 1965 |

| B461.5  | 1   | 2.1-1 |

|---------|-----|-------|

| January | 15, | 1965  |

#### 2.1 ON-LINE OPERATION

The B461 Core Memory is designed to operate with the B5500. All interconnecting lines conform to the requirements of the B5220 Central Control for Timing and Information flow. The following is a list of the inter-connecting lines between Central Control and the Core Memory.

Central Control to Core Memory

- 1. AnnS 12 lines labeled A01S thru A12S, Address lines to the Address Register in Memory.

- 2. A00S 1 line, Memory Start Pulse to initiate a Memory cycle.

- 3. WOOD 1 line, occurs at the same time as AOOS, used to indicate a Memory Write Operation.

- 4. SPUL/ 1 line, indicates that the System Clock Control switch in D & D is in the NORMAL position.

- 5. WnnS 48 lines labeled WOIS thru W48S, Write Information to the Memory Information Register.

CORE MEMORY to Central Control

- 1. InnF 49 lines labeled IO1F/ thru I48F/ and I48F, Memory Read Information from the Memory Information Register to Central Control.

- 2. MCFS/ 1 line labeled MT4F/ in Central Control, used to clear the Cross-point Flip-flop and Memory cycle Flip-flop at the end of a Memory access.

- 3. MWCF 1 line labeled MRØF in Central Control, gates the Read Information lines from Central Control to Processor.

- 4. RAØD 1 line labeled MT2F in Central Control, develops MT2F to the Processor to indicate Read Information is in the Memory Information Register.

- 5. RAØS/ 1 line labeled MT2F/ in Central Control, develops MT2S to the I/O Channels to indicate that the Read Information is in the Memory Information Register.

- 6. MERF 1 line labeled MPEF in Central Control, indicates a Parity Error in Memory during a Memory Read access.

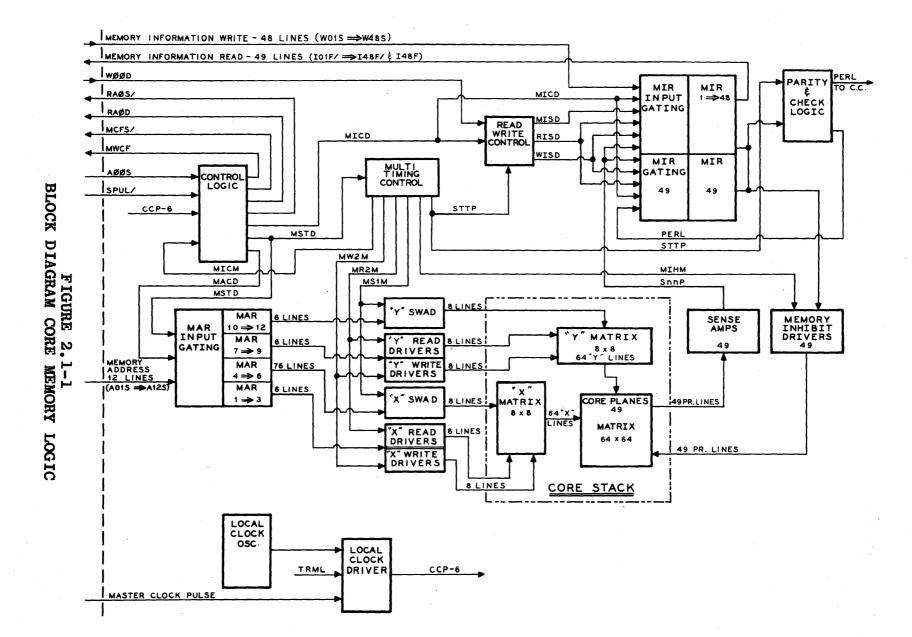

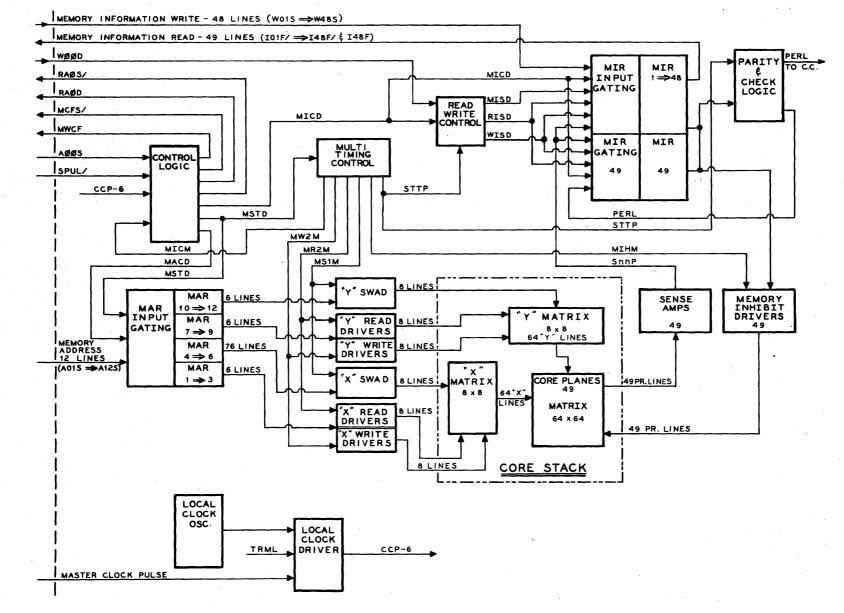

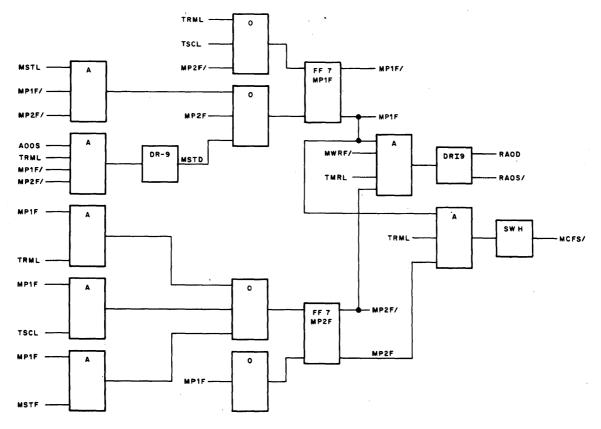

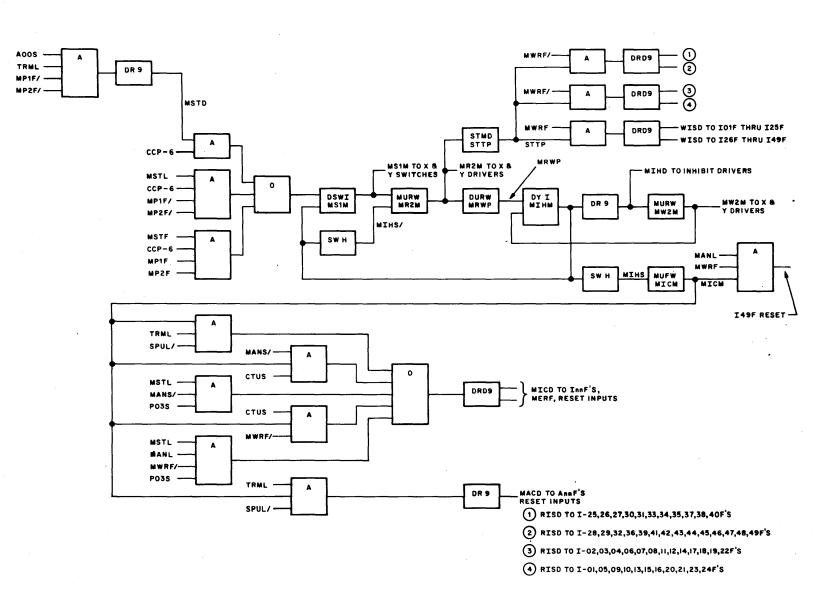

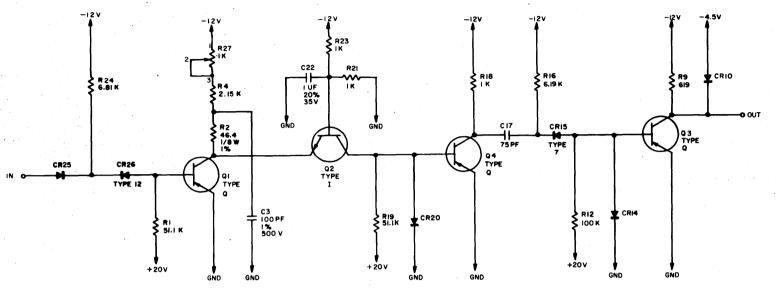

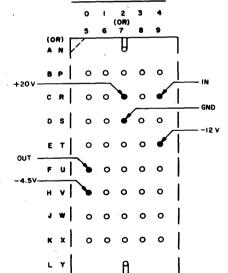

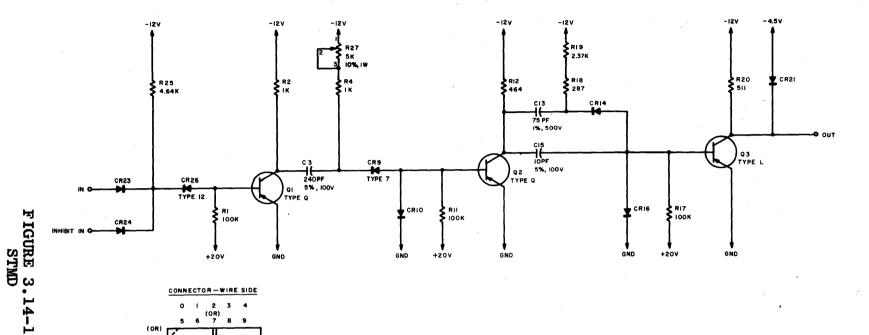

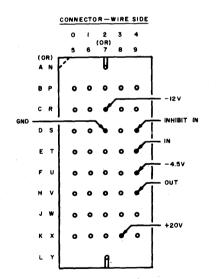

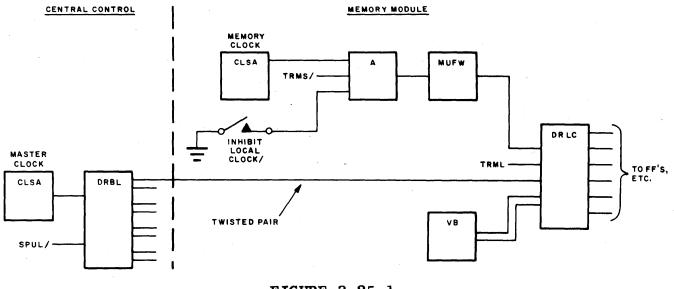

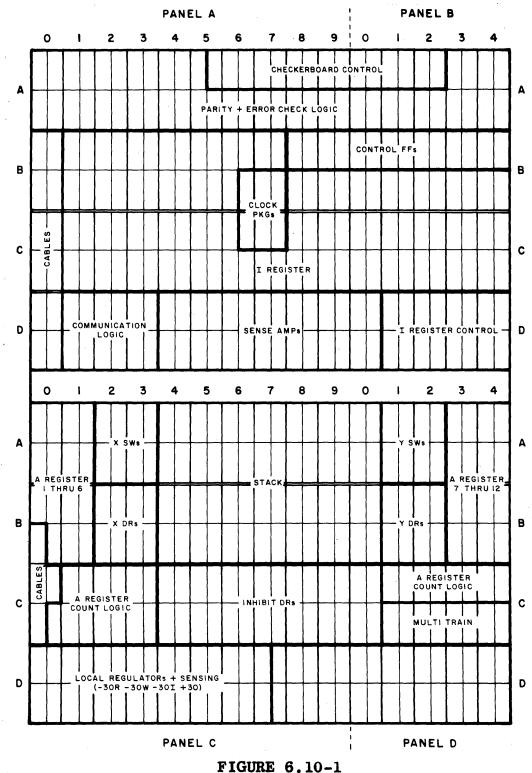

The various Logical Units of the Memory Module, as indicated in Figure 2.1-1, are the Logical Units of the Memory Module used during an On-Line operation. These Units serve the following functions:

2.1-2

FIELD ENGINEERING TECHNICAL MANUAL

| B461.51 |     | 2.1-3 |  |

|---------|-----|-------|--|

| January | 15, | 1965  |  |

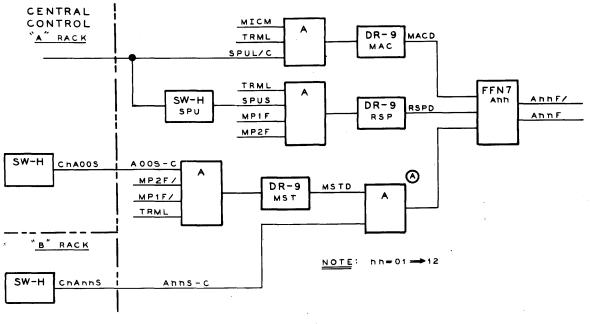

- 1. Control Logic Controls all Memory functions which depend upon the System Clock. It also develops the Control levels that go to Central Control.

- 2. Multi Timing Control Initiated by MSTD from the Control Logic; but once initiated, continues on its own, completely independent of the System Clock. This circuit is used to control all Addressing and Information lines to and from the Core Stack.

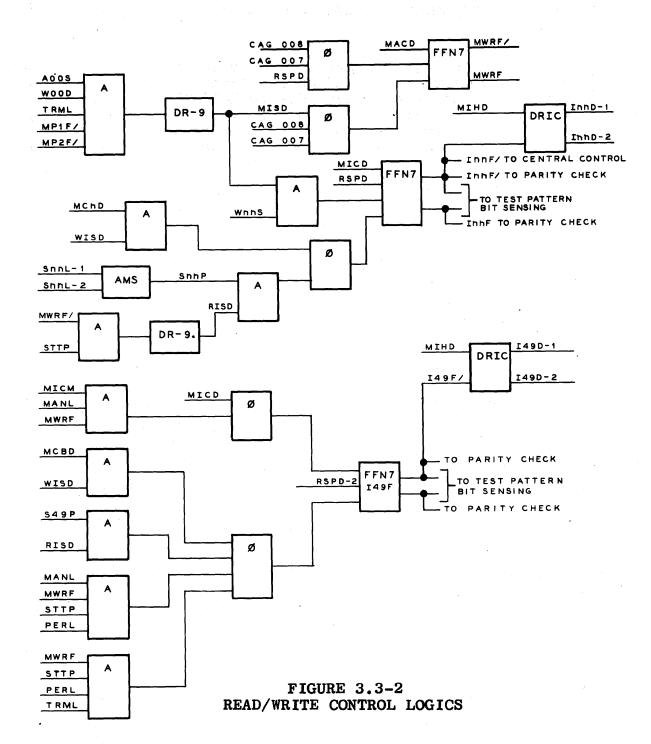

- 3. Read/Write Control Retains the fact that a Memory Access is a Read or Write. Controls the flow of Information for either a Read or a Write operation.

- 4. MIR & Parity MIR is a temporary storage for Information going to or from the Core Stack. The Parity circuitry uses the Information in the Information Register (MIR) to generate the correct Parity during a Write Access and to check for correct Parity during a Memory Read Access.

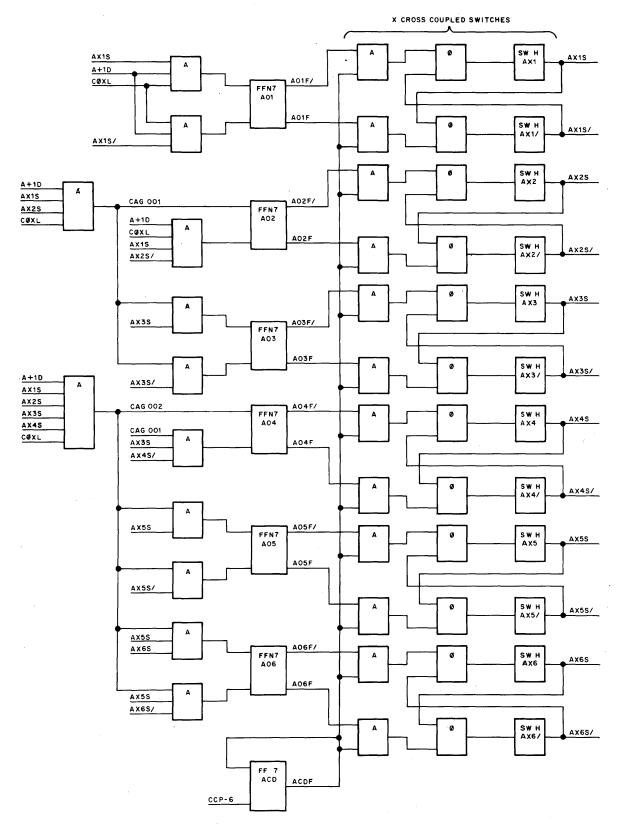

- 5. Address The Addressing portion of Figure 2.1-1 consists of the Address Register, the Address switches, and the Read/Write Drivers. The Address Register contains the Core Address being accessed and in turn will determine the Address switch and Read/ Write Driver to be used. The Address switch and Read/Write Driver outputs go to the "X" and "Y" Transformer Matrices to select one of the Transformers which will in turn select one of the 64 "X" lines and "Y" lines to the Core Stack.

#### Information Flow

The flow of Information during a Memory Write Access is from Central Control via the Memory Information Write lines to MIR 1 thru 48. While this Information is in MIR, the correct Parity is generated by the Parity generation circuitry and set into MIR 49. During the Write phase of the Memory Access, the information is transferred into the Core Stack via the 49 Inhibit Drivers.

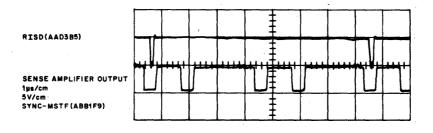

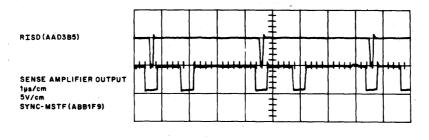

The flow of Information during a Memory Read Access is from the Core Stack to MIR via the 49 Sense Amps. The outputs of the Sense Amps are strobed into MIR with the Strobe Timing Pulse (STTP). While the Information is in MIR, the Parity circuitry checks the 49 bits for correct Parity. If the Parity is in error, then the Error Flip-Flop (MERF) is set to indicate this condition to Central Control.

After Parity is checked, the Information in MIR is transferred to Central Control via the Memory Information Read lines. Only bits 1 thru 48 are transferred to and from the Memory Module. Bit 49 is the Parity bit and its status (ON or OFF) is determined in the Memory and remains in the Memory Module.

#### Central Control Operation

The function of Memory Exchange in Central Control is to logically con-

Printed in U.S.A.

nect a Memory Module with an Accessing Unit (Processor or I/O). The Control and Information lines will be gated through Memory Exchange between the Accessing Unit and the Memory Module.

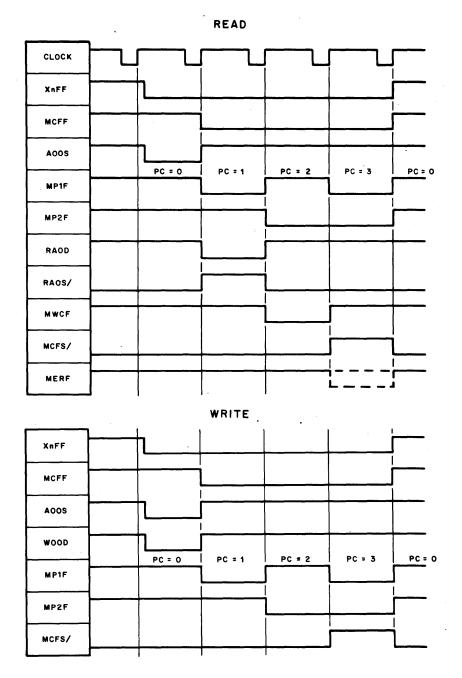

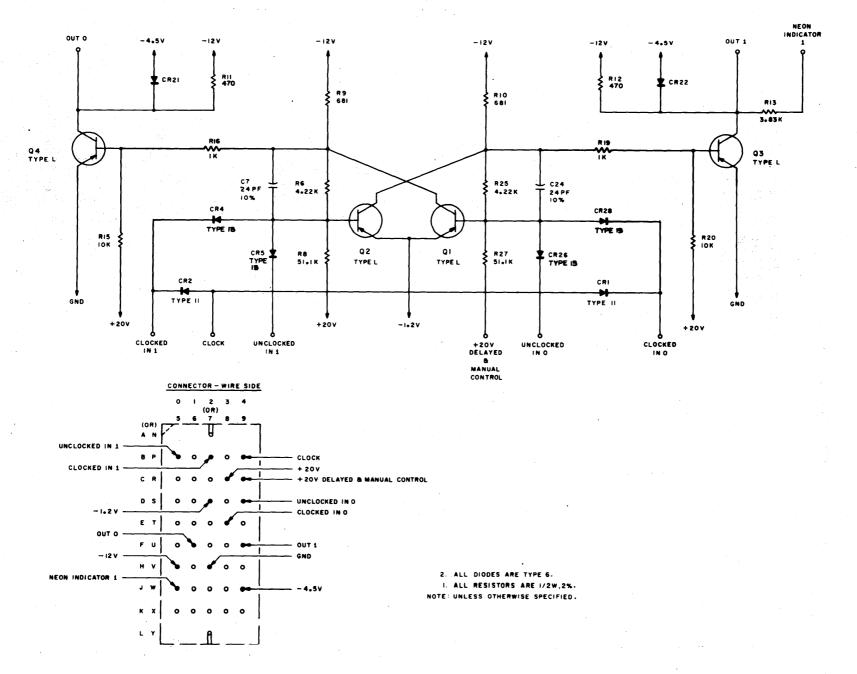

When the Processor or I/O requests a Memory Access and that access can be accomplished, the Cross-point Flip-Flop in Central Control is set (Unclocked). See Figure 2.1-2.

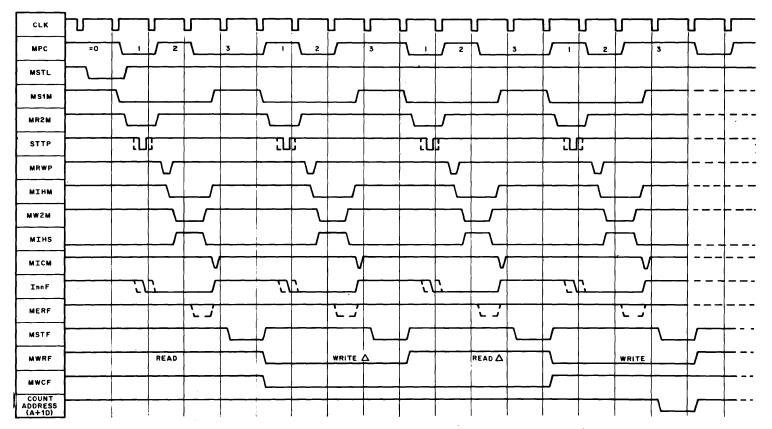

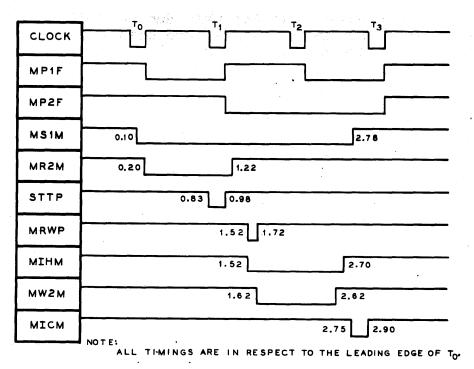

FIGURE 2.1-2 MEMORY TO CENTRAL CONTROL TIMING

With the Cross-point set, level A00S (Memory Start) is developed in Central Control and sent to the Memory Module. If the operation is a

| A | FIELD ENGINEERING TECHNICAL MANUAL | B461.51   | 2.1-5    |

|---|------------------------------------|-----------|----------|

| U |                                    | January 1 | .5, 1965 |

Memory Write, then the Memory Write Level(WOOD) is also sent to the Memory Module. A00S will initiate the Memory operation in the Memory Module, and WOOD will allow the Information to be written to be set into the Information Register and set the Memory Write Flip-Flop (MWRF).

In the Memory Module, the Pulse Counter is counted with each Clock Pulse from 0 to 3 and back to 0. Its purpose is to determine when the Logical levels will be TRUE to keep the Logical operation of the Memory and Central Control in sync with the Multi Timing to the Core Stack.

The Logical levels RAOD, RAOS/ and MCFS/ are developed from the Pulse Counter to gate the Processor or I/O and the Central Control during a Memory Access. The terms RAOD, RAOS/, MWCF and MERF are used only during a Memory Read operation. The only term used during a Write operation is MCFS/. Its use is to indicate to Central Control that a Memory operation is completed, clearing the Memory Cross-point and Memory cycle flip-flop.

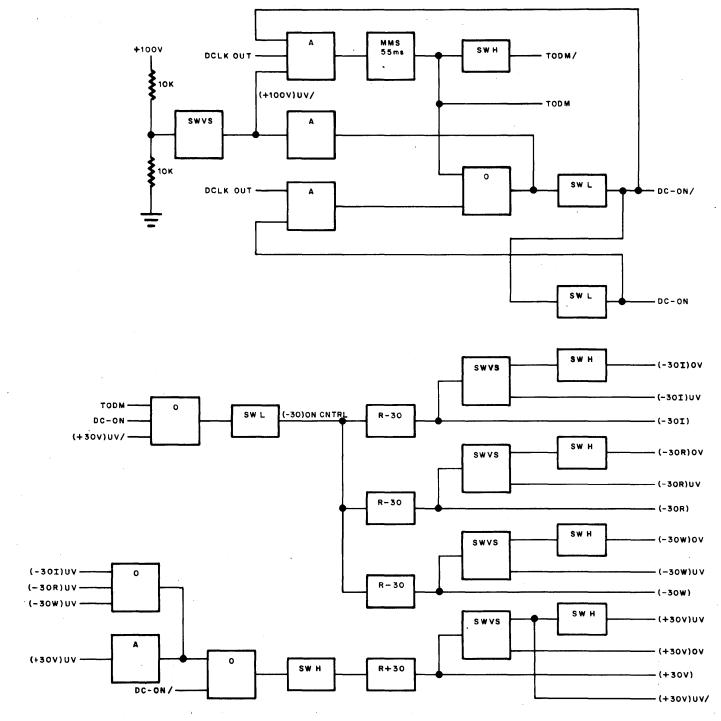

#### Memory Operation

The functions which occur in the Memory Module during a Memory operation are controlled by the Memory Pulse Counter and the Multi Timing circuitry. The Pulse Counter controls those functions which use the 1 meg. Clock instead of the Multis for their timing. The Multi timing, initiated by the 1 meg. Clock, is completely asynchronous in its operation.

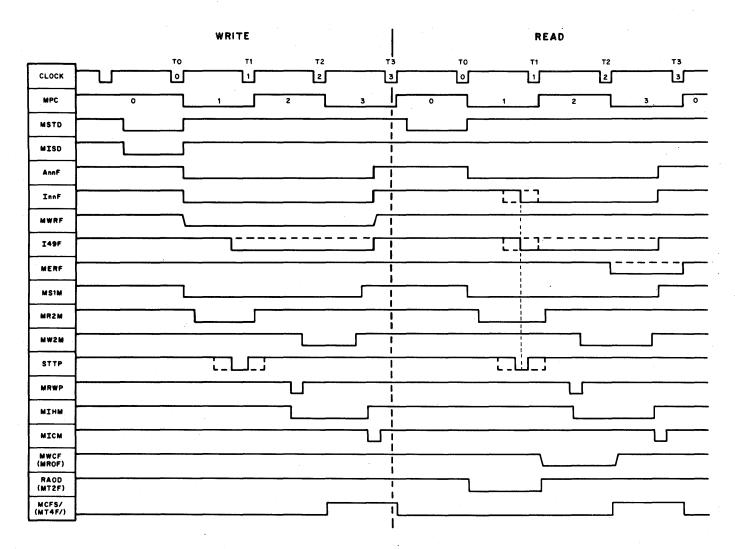

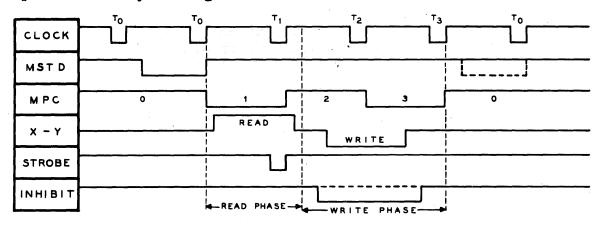

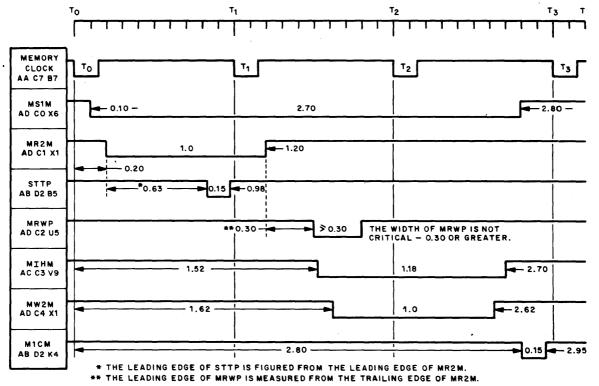

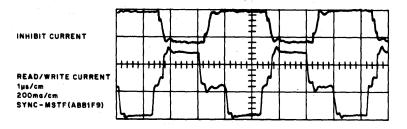

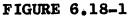

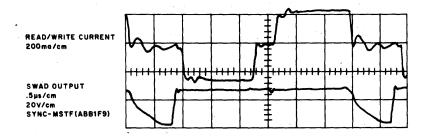

Referencing Figure 2.1-3, the Memory operation is started when MSTD (Memory Start Driver) is TRUE. MSTD with the  $T_0$  Clock Pulse will set the Address Register(AnnF) and initiate the Multi Timing by triggering MS1M (Memory Switch 1 Multi). This Multi will be TRUE for the entire Memory cycle, approximately 3 microseconds. Occurring with MSTD is the level MISD (Memory Input Strobe Driver) for a Write operation only. MISD will set the Information Register (InnF) to the information to be written and set the Memory Write Flip-Flop (MWRF).

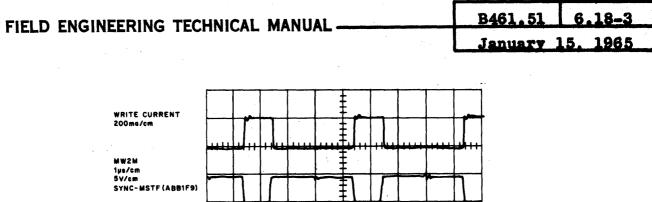

The next occurrence is in the Multi Timing. MS1M sets MR2M (Memory Read 2 Multi). With MS1M and MR2M both TRUE, a destructive Read of the Stack is done. At Strobe Time (STTP), bit 49 in the Information Register will be set (or not set) to generate the correct Parity in the Information Register. The Clock Pulse  $T_1$  occurs during the Read portion of the Memory cycle and its only function for a Write operation is to count the Pulse Counter to two. While the Pulse Counter is at a value of two, the Read out is terminated with the time out of MR2M which in turn sets MRWP (Memory Read to Write Delay Pulse). MRWP in turn, triggers MIHM (Memory Inhibit Multi). MIHM turns on the Inhibit Drivers that are associated with those bits in the Information Register that are in the "zero" state. MIHM also turns on the Memory Write 2 Multi (MW2M) to drive Write current in the "X" and "Y" lines in the Core Stack.

During the Write portion of the Memory cycle, the T2 Clock Pulse will count the Pulse Counter to Three. With the Pulse Counter equal to three, the level MCFS/ (Memory Cycle Finished Not Switch) goes FALSE.

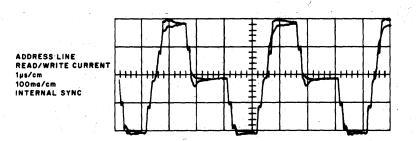

FIGURE 2.1-3 REMOTE MEMORY TIMING

This FALSE level, with the T3 Clock Pulse, indicates to Central Control that the Memory operation is complete. The T3 Clock Pulse will count the Pulse Counter back to zero, and with MCFS/ FALSE, the same Clock Pulse will clear the Cross-point and Memory cycle Flip-Flops in Central Control. In the Multi Timing, at approximately the same time as T3, MS1M and MW2M and MIHM will time out. MIHM timing out will set MICM (Memory Information Register Clear Multi) which will result in clearing the Memory Module.

In a Memory Read operation, the actions of the Pulse Counter and Multi Timing are identical to the Memory Write operation. During a Read operation, the level MISD remains FALSE. This results in the Information Register and MWRF remaining in the "Zero" state. When STTP occurs during the Read phase of the operation, the information being read from the Stack is set into the Information Register, including the Parity bit I49F. The Parity circuit will check the information in the Information Register and if a Parity Error exists (even number of bits ON in the Information Register), MERF (Memory Error Flip-Flop) will be set with T<sub>2</sub> Clock Pulse.

| B FIELD ENGINEERING TECHNICAL MANUAL | B461.51   | 2.1-7   |

|--------------------------------------|-----------|---------|

|                                      | January 1 | 5, 1965 |

Other differences between a Read and a Write operation are in the Logical levels sent to the Central Control. During a Memory Read operation (indicated by MWRF in the "zero" state), the RAOD level will be TRUE when the Pulse Counter is equal to one. This allows the accessing Unit (Processor or I/O) to prepare to accept the Read information from Memory at Clock Pulse T2. MWCF is TRUE when the Pulse Counter equals two. This indicates to Central Control that the Read information can now be transferred to the Processor. MCFS/ serves the same purpose in a Memory Read Operation as it did in a Memory Write operation, clearing the flip-flops in Central Control at  $T_3$ .

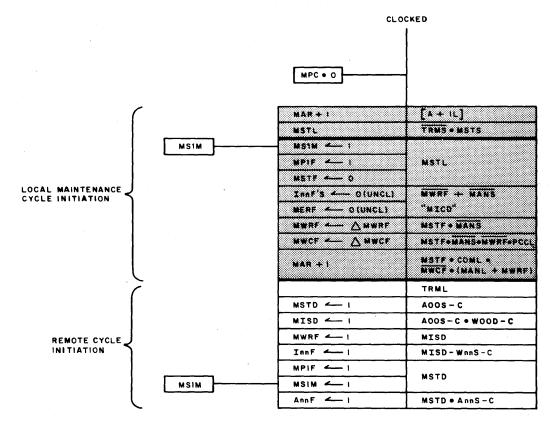

#### **Clocked Flow**

The Core Memory flow charts are separated into two groups, Clocked and Unclocked. The description of these flows will cover the two groups separately. The described actions will be identified as to their respective MPC values (Memory Pulse Counter).

#### MPC = 0

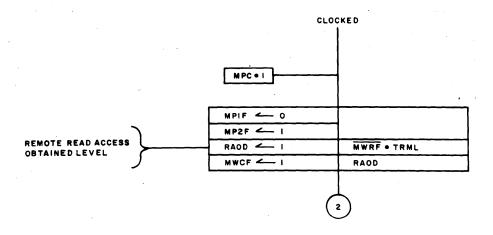

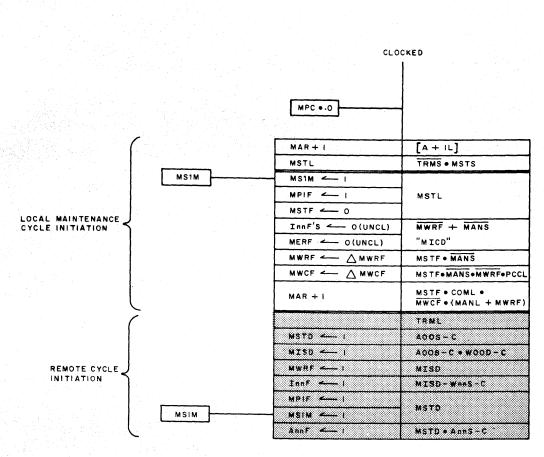

All actions occurring at this MPC count require the Memory Module to be in Remote (TRML). Reference Figure 2.1-4.

FIGURE 2.1-4 MPC = 0 FLOW  $MSTD \leftarrow 1$  (Unclocked)

With the Start Pulse from Central Control (AOOS-C), the Memory Start Driver will go TRUE to start the Memory operation.

MISD -1 (Unclocked)

If the Memory operation is a Memory Write, then the Memory Input Strobe Driver will go TRUE at the start of the Memory cycle (A00S-C • W00D-C).

#### MWRF - 1

Set the Memory Write flip-flop if this is a Memory Write operation as indicated by MISD being TRUE.

#### InnF - 1

Set the information to be written into the Information Register as specified by the Write Information lines (MISD  $\cdot$  WnnS-C). The nn in this case are the values of 01 thru 48.

$MP1F \leftarrow 1$ ,  $MS1M \leftarrow 1$

Set MPlF to give the Pulse Counter a value of "one" in preparation for the next sequence operation. With MSTD, set the MSlM multi to initiate the Multi Timing to the Core Stack.

#### AnnF — 1

Set the Address of the Core Stack into the Memory Address Register at the start of the operation (MSTD  $\cdot$  AnnS-C). AnnS-C are the 12 Address lines from Central Control.

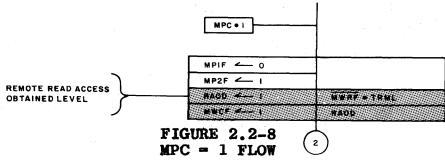

#### MPC = 1

For the flow chart of this MPC value, refer to Figure 2.1-5.

FIGURE 2.1-5 MPC = 1 FLOW

| B FIELD ENGINEERING TECHNICAL MANUAL | B461.51   | 2.1-9    |

|--------------------------------------|-----------|----------|

|                                      | January 1 | .5, 1965 |

Unconditionally increase the value of the Pulse Counter by "one" (MPIF to 0 and MP2F to 1).

RAOD - 1

While the Pulse Counter is at a value of "one", allow the Remote Read Access Obtained Level to be TRUE to Central Control if the Memory operation is a Read and the Memory Module is in REMOTE (MWRF/  $\cdot$  TRML).

#### MWCF — 1

With RAOD, the operation is a Read. Set MWCF.

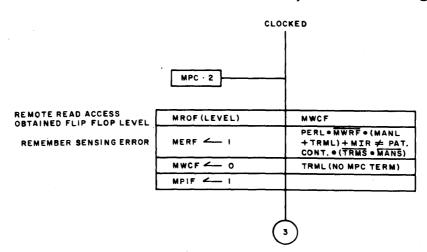

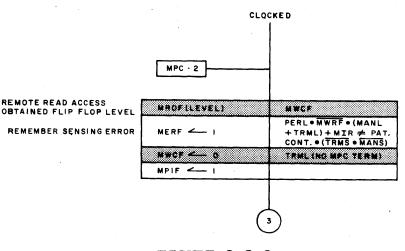

#### MPC = 2

For the actions listed for this MPC value, refer to Figure 2.1-6.

FIGURE 2.1-6MPC = 2 FLOW

MROF (Level)

With MWCF set, the MROF level is developed in Central Control to gate the Information lines from Central Control to the Processor. If the Accessing Unit is an I/O channel, then this level will not effect Central Control.

#### MERF - 1

There are two conditions by which MERF can be set. The one that is used when in a REMOTE operation is the term PERL • MWRF/ • (MANL + TRML). PERL will be TRUE if an even number of bits are ON in the Information Register indicating a Parity Error during a Read operation (MWRF/).

If the Memory is being operated in REMOTE or MANUAL (TRML + MANL), then set the Memory Error Flip-Flop (MERF to 1).  $MWCF \longleftarrow 0$

Set MWCF to zero when in REMOTE (TRML).

MP1F -1

Unconditionally set MPIF to one at MPC = 2 to increase the Pulse Counter to a value of three.

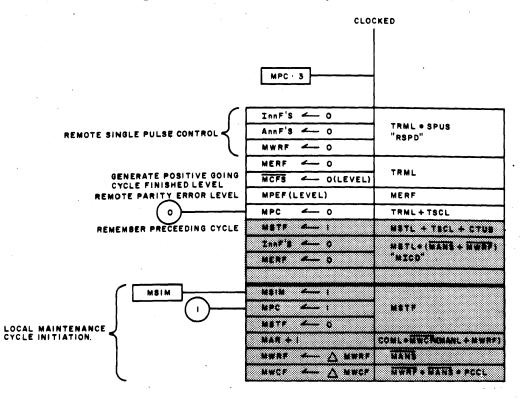

MPC = 3

For all actions occurring at this MPC count, refer to Figure 2.1-7.

FIGURE 2.1-7MPC = 3 FLOW

InnFs  $\leftarrow 0$ , AnnFs  $\leftarrow 0$ , MWRF  $\leftarrow 0$

When terminating a Memory operation, it is necessary to clear the Memory Module in order to have all flip-flops in the "zero" state at the start of some future Memory operation. If the System Clock is in single or double pulse, then the clearing of some of the Module will be done with a Clock pulse via the Remote Single Pulse Driver (RSPD). RSPD = TRML • SPUS, the Memory Module in Remote and the System Clock not in the Normal Mode. If this condition exists, then clear the Information Register (InnFs), the Address Register (AnnFs), and the Memory Write Flipflop (MWRF). FIELD ENGINEERING TECHNICAL MANUAL

| B461.51 | 2.  | 1-11 |  |

|---------|-----|------|--|

| January | 15, | 1965 |  |

#### MERF -0, MCFS/-0

When operating in REMOTE, unconditionally set the Error Flipflop to zero; and with MPC = 3, the MCFS/ level goes FALSE to Central Control. This level will result in the controlling flipflops in Central Control being cleared.

MPEF (Level)

If a Memory Parity Error existed in the Read operation, then MERF will be ON. With MERF in the "one" state, develop the Memory Parity Error Level (MPEF) in Central Control.

#### $MPC \leftarrow 0$

When in REMOTE, and at MPC = 3, unconditionally set the Memory Pulse Counter to zero. This results in the termination of the Memory operation. At MPC = 0, a Memory Start is needed from Central Control for any more actions to take place. Refer to Figure 2.1-4.

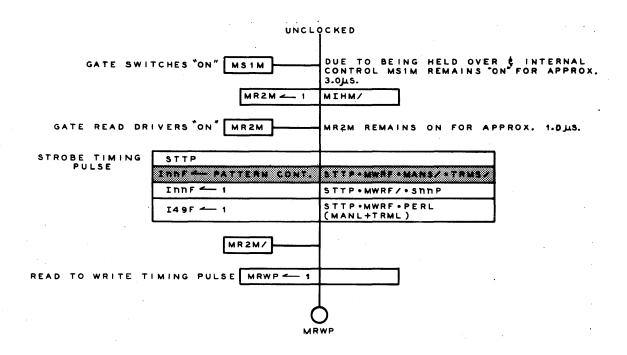

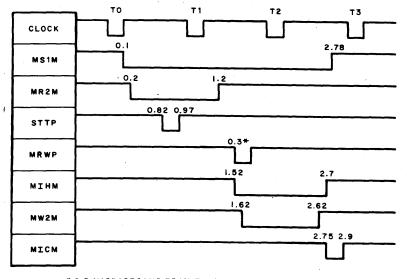

#### Unclocked Flow

The Unclocked flow is primarily concerned with the Multi Timing and those functions which are a result of the multis. The Multi Timing circuitry is initiated by MSTD and a Clock pulse at MPC = 0, (see Figure 2.1-4) by setting the MSIM multi. Once MSIM is set, the multi train will continue to completion, completely independent of the System Clock as described below.

#### NOTE

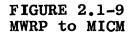

All timings given in this section of the Manual are approximations only. For exact timings of the Multis, refer to Section 5 of this Manual.

#### MS1M

MS1M is turned ON at the start of a Memory operation and remains ON for the entire Memory operation, approximately 3 microseconds. MS1M enables the Address switches selected by the Address in the Address Register. Refer to Figure 2.1-8.

MR2M ~ 1

MR2M is turned ON by MS1M if the Inhibit multi is OFF (MIHM/). MR2M is on for approximately 1.0 microsecond and enables the "X" and "Y" Read drivers to drive Read current in the Core Stack.

#### MR2M

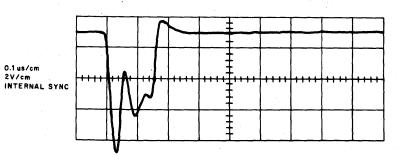

While MR2M is TRUE, the Strobe Pulse will occur approximately 630 nanoseconds after the Leading Edge of MR2M. The Strobe Pulse (STTP) will gate several functions during the Read phase of the Memory operation.

FIGURE 2.1-8 MS1M to MRWP

#### InnF — 1

If this is a Memory Read operation (MWRF/), set the Read information into the Information Register at Strobe time (STTP). The information to be placed in the Register is from the Sense Amps (SnnP).

#### **I49F** ← 1

If a Parity Error exists in the MIR Register (PERL), set bit 49 of the Information Register at Strobe Time for a Memory Write operation (STTP • MWRF). By this action, the correct Parity is set into the Information Register during a Memory Write operation.

#### MR2M/

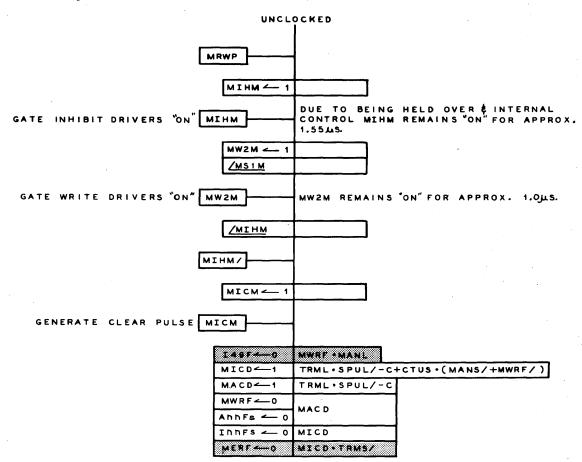

Approximately 300 nanoseconds after the time out of MR2M, the MRWP delay will be set. This is for a 300 nanosecond delay between the Read and Write portions of a Memory operation. The remainder of this description will reference Figure 2.1-9.

#### MRWP

When MRWP is set, the Inhibit Multi (MIHM) is set to gate on the Inhibit Drivers. Which Inhibit Drivers will drive current through the Stack depends upon the Information in the MIR Register.

| ß | B FIELD ENGINEERING TECHNICAL MANUAL | B461.51   | 2.1-13 |

|---|--------------------------------------|-----------|--------|

| U |                                      | January 1 |        |

#### MIHM

The Inhibit Multi will be on for approximately 1.55 microseconds. During the time it is set, it will hold-over MS1M to prevent MS1M from timing out. The Inhibit multi will also set the Write Multi (MW2M  $\leftarrow$  1) to drive the Write current in the Core Stack. MW2M will remain on for approximately 1.0 microsecond.

#### MW2M

To prevent the Inhibit Multi from timing out, MW2M will hold-over the Inhibit Multi (MIHM/).

#### MIHM/

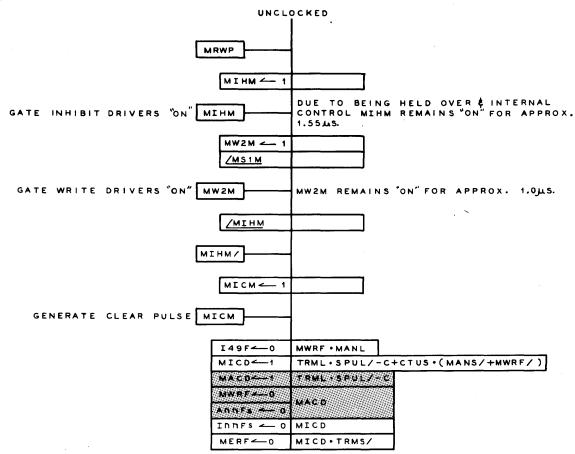

The Inhibit Multi will time out at the termination of the Write phase of the Memory operation. When it times out, the Memory Information Clear Multi (MICM) is set to generate a Clear Pulse in the Memory Module.

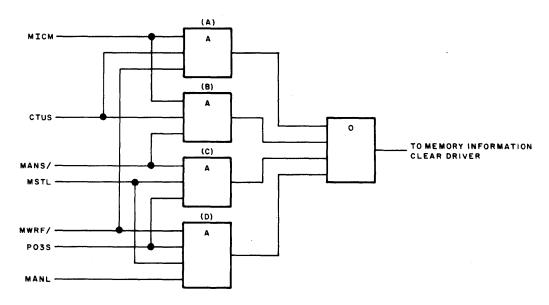

#### MICM

With MICM TRUE, the following actions will occur in REMOTE:

MICD -1

This driver will have a TRUE output if the Memory Module is in REMOTE and the System Clock switch is in the NORMAL position (TRML • SPUL/-C). If the System Clock Mode switch is in single or double pulse, then MACD and MICD will go TRUE with the Pulse Counter equal to three. See Figure 2.1-7.

$MWRF \leftarrow 0$ ,  $AnnFs \leftarrow 0$

Clear the Address Register and the Memory Write Flip-Flop with the MACD level.

InnFs — 0

Clear the Information Register with the MICD level.

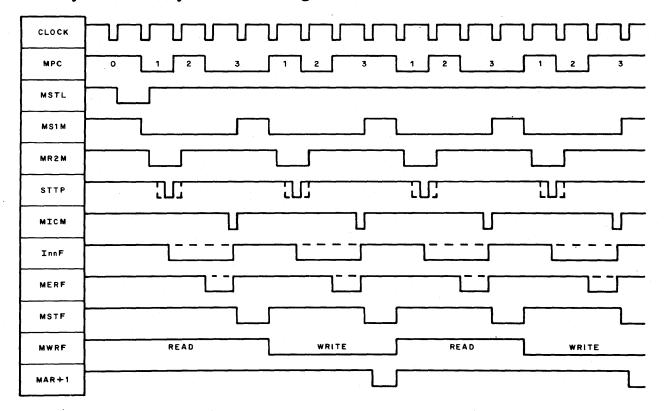

Figure 2.1-10 is a Timing Diagram of the Multi Timing previously described with the times indicated for each of the Multis. All times indicated are taken from the Leading Edge of  $T_0$ .

NOTE

The Times used here are only approximations. The user of this manual is cautioned to use only the timings indicated in Section 5 for adjusting a Memory Module.

\* 0.3 MICROSECOND FROM TRAILING EDGE OF MR2M, TRAILING EDGE OF MRWP NOT CRITICAL.

FIGURE 2.1-10 MULTI TIMING

FIELD ENGINEERING TECHNICAL MANUAL

| B461.51     |     | 2.2-1 | - |

|-------------|-----|-------|---|

| <br>January | 15, | 1965  | - |

#### 2.2 OFF-LINE OPERATION

The B461 Core Memory is designed to operate Off-Line as well as On-Line. The Off-Line Mode of operation is used primarily for testing of the Memory Module.

With the Off-Line Mode of operation, the Information recorded can be manually inserted in the Information Register, or generated within the Memory Module. All Information manually inserted is tested for the proper Parity and all Information generated is tested for specific combinations of bits as determined by the Pattern Control circuitry.

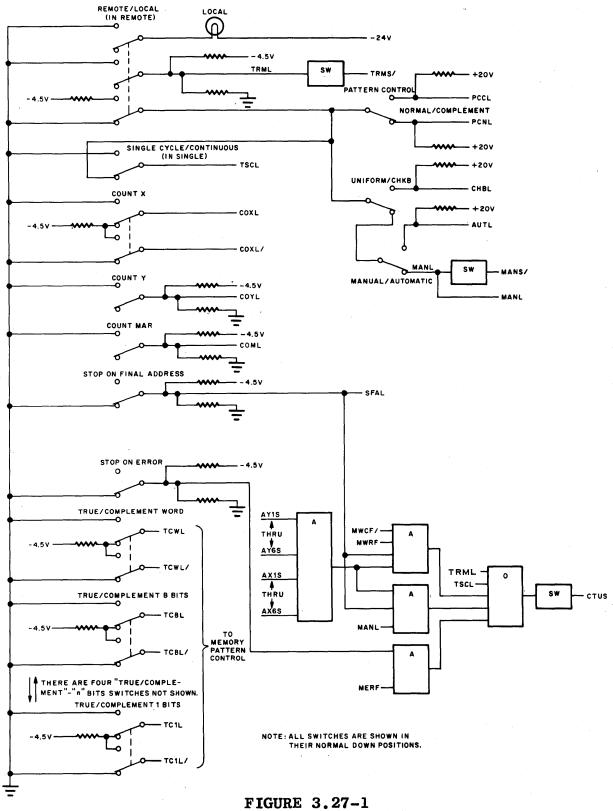

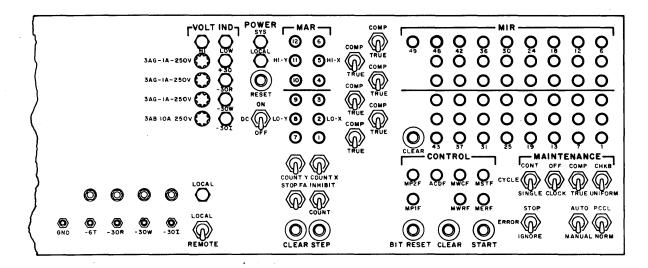

The Memory Maintenance switches are the prime control in the Off-Line Mode of operation. These switches determine the Information to be recorded and the type of operation to be done. For a detailed description of the Maintenance switches, refer to Section 3.27 of this Manual.

The various types of operations which can be done are as follows:

- 1. Single Cycle/Continuous Continuous allows the Memory Module to initiate successive Memory cycles. Single cycle will allow only one Memory cycle to be executed.

- 2. Manual/Auto In the Manual position, the Information to be recorded is manually inserted into the Information Register and tested for the correct Parity (ODD). In the Automatic position, the Information to be recorded is determined by and checked for the combination of bits specified by the Pattern Control circuitry.

- 3. Pattern Normal/Pattern Complement In Pattern Normal (PCNL), the testing of the Module is accomplished with two Memory cycles at each Address. In Pattern Complement (PCCL), the testing is accomplished with four Memory cycles at each Address. The PCCL Mode of operation is also referred to as "Worst Case".

- 4. Uniform/Checkerboard This Mode of operation will only determine the type of Information pattern to be developed. When in Checkerboard, this will force the Automatic Mode of operation. For a description of the Checkerboard patterns developed, refer to Section 6.8 of this Manual.

When operating the Memory Module in Off-Line, the Address Register instead of being Set and Reset, is counted up by one. A certain amount of control can be exercised over this counting. Via the Maintenance switches, one can count only the "X" portion of the Address Register, count only the "Y" portion of the Address Register, or inhibit all counting of the Address Register. This Register can also be manually counted by use of the STEP MAR switch.

Two other conditions that have not been previously mentioned that can be used in an Off-Line operation are as follows:

- 1. STOP ON ERROR This will stop the operation if an Error condition exists and the IGNORE/STOP switch is in the STOP position.

- 2. STOP ON FINAL ADDRESS This switch will stop the Memory opera-

tion when the Address Register is equal to 7777.

The STOP ON ERROR and STOP ON FINAL ADDRESS will stop a Continuous operation with the Pulse Counter equal to three. The Stop due to a Single cycle operation will stop with the Pulse Counter equal to zero.

#### Multi Timing

The Multi Timing for an Off-Line operation is the same as the timing in an On-Line operation. For this reason, only the portions of Memory Timing that are unique to an Off-Line operation will be discussed at this time.

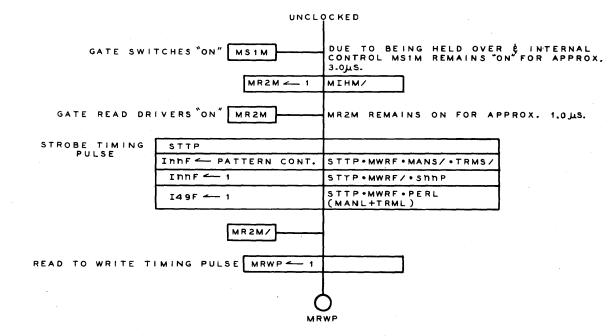

Referencing Figure 2.2-1, only the occurrences at Strobe Time (STTP) vary for the Read portion of a Memory cycle. These differences are:

FIGURE 2.2-1 MULTI TIMING (MS1M to MRWP)

1. InnF — PATTERN CONTROL - The Information Register is set to the configuration specified by the Pattern Control circuitry if the following condition exists:

STTP • MWRF • MANS/ • TRMS/

This logic states that at Strobe Time (STTP) and the Memory cycle is a Write (MWRF); when in Local (TRMS/), set the Information to the Pattern Control if this is not a Manual operation (MANS/). This is a set of 49 bits of the Information Register.

2. I49F ← 1 - If the condition of STTP • MWRF • PERL • (MANL + TRML) exists, then set the correct Parity into the Information Register for a Memory Write operation. In an Off-Line operation, the term TRML is FALSE. This action is then enabled by the term MANL. If I49F is to be set, the PERL level will be TRUE to indicate an even number of bits exist in the Information Register.

| B FIELD ENGINEERING TECHNICAL MANUAL | B461.51   | 2.2-3   |

|--------------------------------------|-----------|---------|

|                                      | January 1 | 5. 1965 |

Referencing Figure 2.2-2, the only differences in the Off-Line operation are at MICM time. The terminations of a Memory cycle are as follows:

FIGURE 2.2-2 MULTI TIMING (MRWP TO MICM)

- I49F ~ 0 Clear the 49th bit (Parity bit) of the Information Register if this is a Manual Write operation (MWRF • MANL). This action allows the correct Parity to be generated each time a Memory Write operation is executed in Manual.

- 2. MICD 1 If the condition of CTUS (MANS/ + MWRF/) exists, then allow MICD to be developed. The gating for MICD states that the operation is continuous (CTUS) and this is either an Auto operation (MANS/), or, a Memory Read operation is being completed (MWRF/). If the operation is a Manual Write, then MICD will not be developed and the Information Register will not be cleared. This allows the contents of the Information Register to be rerecorded, possibly at the next Address in succession.

- 3. MACD ← 1 This level is Inhibited by the term TRML which is FALSE when in Local for the Off-Line operations. See shaded portion of Figure 2.2-2.

- 4. InnFs 0 If MICD is TRUE, then clear the Information Register.

5. MERF - 0 - Clear the Error Flip-Flop with MICD whenever the Memory Module is in LOCAL.

#### Clocked Control

When operating in LOCAL (Off-Line), certain actions require the one meg. Clock. These actions will vary depending upon the setting of the Maintenance switches.

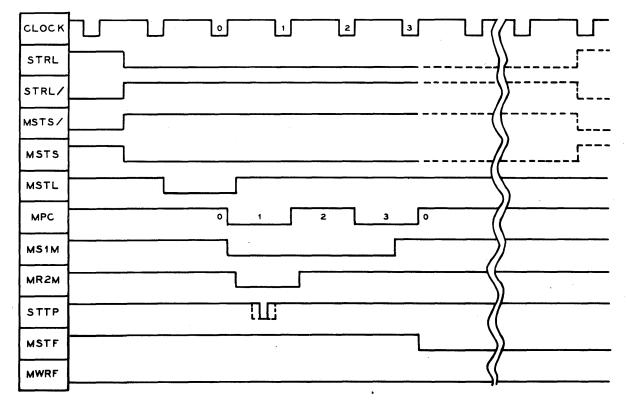

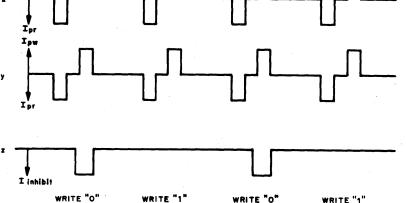

Figure 2.2-3 is a Timing diagram of a Manual, Write, Single cycle operation. This operation will record the contents of the Information Register and stop at the end of the Memory cycle.

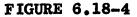

FIGURE 2.2-3 MANUAL - WRITE - SINGLE CYCLE TIMING

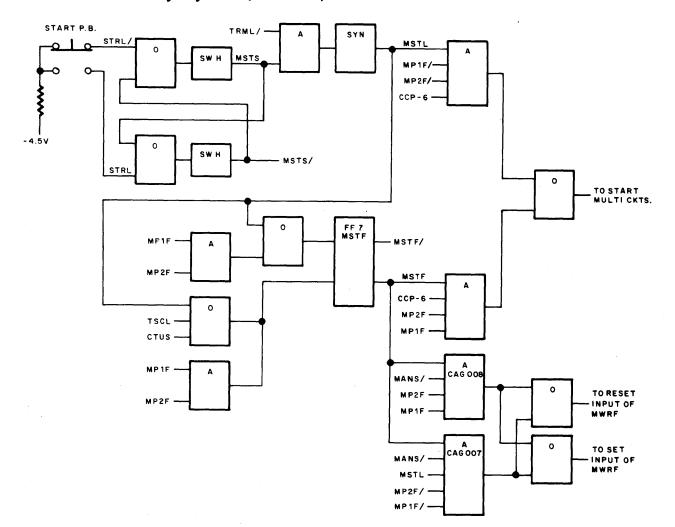

The terms STRL and STRL/ are derived from the START button on the Maintenance Panel, developing the MSTS and MSTS/ levels.

MSTL = MSTS • TRMS/

The term MSTS in turn develops MSTL (Memory Start Level) which initiates the Memory cycle by setting the MPC to 1 and triggering MS1M to initiate the Multi Timing. The MSTL level can only be developed when the Memory Module is in LOCAL due to the term TRMS/.

The only action to occur at Strobe Time (STTP) is the generation of the correct Parity in the Information Register. When the operation is terminated, the MPC is set to zero and the Memory Start Flip-Flop is

| B FIELD ENGINEERING TECHNICAL MANUAL | B461.51   | 2.2-5   |

|--------------------------------------|-----------|---------|

|                                      | January 1 | 5, 1965 |

set (MSTF).

If a second Memory cycle is to be initiated, the START button must be depressed to again develop MSTL which will count the Address Register plus one with MSTF set.

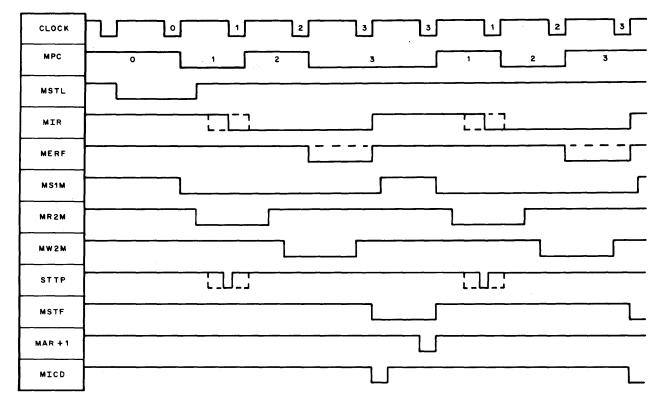

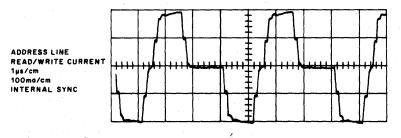

A Manual Read Continuous operation is also initiated by MSTL. See Figure 2.2-4.

FIGURE 2.2-4 MANUAL READ CONTINUOUS TIMING

At Strobe Time (STTP), the Read information is placed into the Information Register and checked for correct Parity. If a Parity Error should exist, then the Error Flip-Flop (MERF) will be set with Clock Pulse 2. MICD is used to clear the Information Register and to reset MERF if it is set.

MPC = 3 for two Clock Pulses. The first Clock Pulse that occurs when the Memory Pulse Counter is equal to three will set MSTF. The second Clock Pulse will find MSTF = 1 and MPC = 3 resulting in MSTF being Reset and MPC set to 1. MSIM is triggered to start another Memory cycle, and the Address Register is incremented by 1 (MAR + 1).

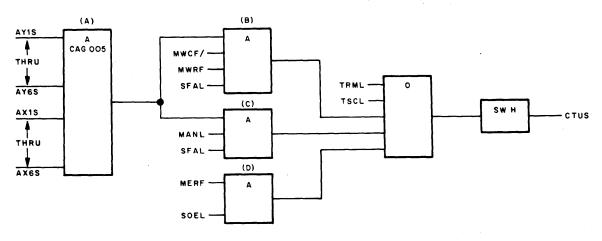

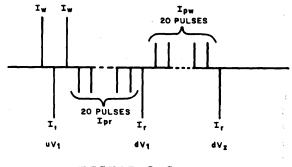

The Memory Module can also be operated automatically by placing the MANUAL/AUTO switch in AUTO, or by placing the UNIFORM/CHECKERBOARD switch in CHECKERBOARD. When in Auto or Checkerboard, the operation is the same, the only difference is in the pattern generated. For the pattern developed by the UNIFORM/CHECKERBOARD switch, refer to Section 3.28 of this Manual. Only the MANUAL/AUTO switch will be considered With the MANUAL/AUTO switch in the Auto position, the Memory operation will consist of two or four Memory cycles before counting the Address Register. The two or four cycle operation is determined by the Pattern Normal/Pattern Complement (PCNL-PCCL) switch on the Maintenance Panel. With the switch in the PCNL (Pattern Control Normal) position, the Auto operation is a two cycle operation, first a Read cycle followed by a Write cycle. See Figure 2.2-5.

#### FIGURE 2.2-5 CONTINUOUS AUTO PCNL TIMING

During the Write cycle, the Information Register is set with the configuration indicated by the Pattern Control circuitry. During the Read cycle, the information is checked for the configuration indicated by the Pattern Control circuitry. The configuration of bits indicated may or may not contain a Parity Error, but the Parity Error is disregarded. The Address Register is counted only after the Write cycle (MAR + 1).

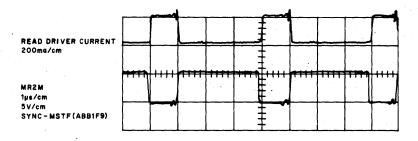

If the PCNL-PCCL switch is in the PCCL position, also referred to as "worst case" operation, the Auto operation is a four cycle access at each Address. See Figure 2.2-6.

The first Memory cycle is a Read. The information read must agree with the Pattern Control switch settings or MERF is set. At the end of this Read operation, the Memory Worst Case Flip-Flop (MWCF) is set.

| A | FIELD ENGINEERING TECHNICAL MANUAL | B461.51   | 2,2-7  |

|---|------------------------------------|-----------|--------|

| U |                                    | January ] | 5 1965 |

## FIGURE 2.2-6 PCCL AUTOMATIC

The second Memory cycle is a Memory Write of the complement of the pattern indicated by the Pattern Control switches.

The third Memory cycle is a Memory Read to check for this complement pattern. If any bits are in the wrong state, then set the Error Flip-Flop (MERF). At the termination of the third Memory cycle, reset MWCF.

With MWCF OFF, the fourth Memory cycle will now Write the true pattern indicated by the Pattern Control switches. At the end of the fourth Memory cycle, the condition of MWCF is OFF, MWRF is ON, and MSTF exists. With this condition, the Address Register is counted up one (MAR + 1) and the four cycles are repeated for the next Address.

#### **Clocked Flows**

The following write up will be primarily concerned with the Off-Line functions indicated on the Clocked portion of the flow chart.

#### MPC = 0

For actions occurring at MPC = 0, refer to Figure 2.2-7.

FIGURE 2.2-7MPC = 0 FLOW

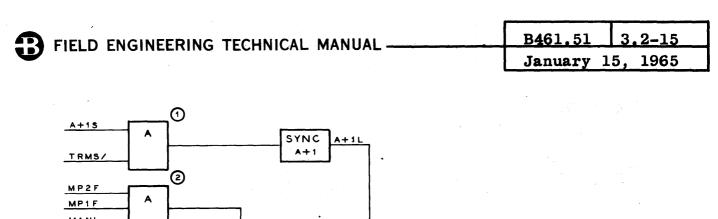

### (A + 1L)

2.2 - 8

By depressing the STEP MAR switch on the Maintenance Panel, the Address Register is incremented by one (MAR + 1). This action does not require the Pulse Counter to be at a count of zero, but it does require that the Memory Module be in LOCAL. (A + 1L =  $A + 1S \cdot TRMS/$ ) A + 1S is the level developed from the STEP MAR switch.

#### TRMS/ • MSTS

With the Memory Module in LOCAL (TRMS/) and depressing the START switch (MSTS), the Memory Start Level (MSTL) is developed.

#### MSTL

When MSTL is TRUE with a Clock Pulse; initiate the Multi Timing (MSIM - 1), set the Pulse Counter to one (MPIF - 1), and reset the Memory Start Flip-Flop (MSTF - 0). MSTF will be set if a previous Memory cycle had stopped due to a Single Cycle operation.

MSTL will also enable all of the actions listed below the double line shown in Figure 2.2-7.

## MWRF/ + MANS/ "MICD"

If this is not a Write cycle (MWRF/), or if this is an Auto op-

| A | FIELD ENGINEERING TECHNICAL MANUAL | B461.51   | 2.2-9   |

|---|------------------------------------|-----------|---------|

| U |                                    | January 1 | 5, 1965 |

eration instead of a Manual operation (MANS), then the MICD level is developed. MICD in turn will clear the Information Register (InnFs -0) and reset the Error Flip-Flop (MERF -0). Both of these actions are Unclocked but are shown here because they require the Pulse Counter equal to zero.

MSTF • MANS/

If the Memory Start Flip-Flop is ON and this is an Auto operation (MSTF  $\cdot$  MANS/), then complement the Write Flip-Flop (MWRF  $\leftarrow \Delta$  MWRF). This action will alternate the Read and Write operations when operating in Auto.

MSTF • MANS/ • MWRF/ • PCCL

If the Memory Start Flip-Flop is ON (MSTF) and this is not a MANual operation (MANS/) and the previous Memory cycle was a Memory Read with the Pattern Control switch in the "worst case" position (MWRF/  $\cdot$  PCCL), then complement the "worst case" flip-flop (MWCF  $-\Delta$  MWCF). With MWCF ON, the complement of the bit configuration indicated by the Pattern Control circuitry will be written and read in Memory.

$MSTF \cdot COML \cdot MWCF / \cdot (MANL + MWRF)$

With the Memory Start Flip-Flop set and the COUNT/INHIBIT switch in the COUNT position (COML) and the "worst case" flip-flop OFF (MWCF/), the Address Register will be incremented by one (MAR + 1) if this is a Manual operation or if the Write Flip-Flop is set (MANL + MWRF). This allows the Address Register to be counted after each Memory cycle when operating in Manual, or if in Auto, only at the end of the Write cycle. The combination of MWCF/ and MWRF will count up the Address Register only after the fourth Memory cycle when doing a PCCL operation. See Figure 2.2-6.

All of the actions shown in the shaded portion of Figure 2.2-7 cannot occur when in LOCAL due to the REMOTE level (TRML) being FALSE.

#### MPC = 1

The only action to occur at the Pulse count of one is the unconditional setting of the Pulse Counter to two (MP1F - 0, MP2F - 1). See Figure 2.2-8.

# MPC = 2

#### For the actions which occur at MPC = 2, refer to Figure 2.2-9.

FIGURE 2.2-9 MPC = 2 FLOW

PERL • MWRF/ • (MANL + TRML) + (MIR  $\neq$  PAT. CONT.) • (TRMS/ • MANS/)

With either of the two conditions TRUE, then the Error Flip-Flop will be set (MERF - 1). The first of the two OR terms; PERL • MWRF/ • (MANL + TRML) is used when a Parity Error is present during a Memory Read cycle (PERL • MWRF/) with the Memory being operated in Manual or Remote (MANL + TRML).

The second OR term (MIR  $\neq$  PATTERN CONTROL) • (TRMS/ • MANS/) is used if the configuration of bits in the Information Register does not coincide with the configuration indicated by the Pattern Control circuitry and the Memory is being operated in Local and not in Manual (TRMS/ • MANS/).

Unconditionally set the Pulse Counter to three (MPIF -1).

## MPC = 3

Before going into the actions listed under MPC = 3, the levels TSCL and CTUS should be understood. TSCL is the Test Single Cycle Level and it will be TRUE if the SINGLE/CONTINUOUS switch is in the SINGLE position. This will result in the Pulse Counter being set to zero and the Start Flip-Flop set to one. With these actions, the Memory Module will be at MPC = 0 and MSTF = 1 to enable the logic in Figure 2.2-7 when the START button is depressed.

The mnemonic CTUS is the Continue Level used in a LOCAL operation to allow one Memory cycle to immediately follow a previous Memory cycle. CTUS is made up of the following logic: B FIELD ENGINEERING TECHNICAL MANUAL \_\_\_\_\_\_ B461.51 2.2-11 January 15, 1965

| -0/- | CTUS                            |                             |

|------|---------------------------------|-----------------------------|

| -I-  | + TRML                          | REMOTE                      |

|      | + TSCL                          | TEST SINGLE CYCLE           |

|      | + MWCF/ • MWRF • CAG 005 • SFAL | STOP-FINAL-ADDRESS & AUTO   |

|      | + MANL · CAG 005 · SFAL         | STOP-FINAL-ADDRESS & MANUAL |

|      | + MERF • SOEL                   | STOP-ERROR & ERROR EXISTS   |

If all of the above inputs are FALSE, then CTUS will be TRUE through a switch to enable the Continuous operation.

Examining the inputs from top to bottom:

- 1. The LOCAL/REMOTE switch must be in LOCAL to make TRML a FALSE level.

- 2. TSCL will be FALSE if the SINGLE/CONTINUOUS switch is in the CON-TINUOUS position.

- 3. CAG 005 = AX1S · AX2S · AX3S · AX4S · AX5S · AX6S · AY1S · AY2S · AY3S · AY4S · AY5S · AY6S

The third input is used in AUTO (or CHECKERBOARD) to STOP-FINAL-ADDRESS. With the condition of MWCF/  $\cdot$  MWRF, the AUTO operation will be at the end of either the two or four cycle operation for any particular Address. If this Address is 7777, then the output of CAG 005 will be TRUE. The inputs to CAG 005 are from the cross-coupled switches of the Address Register. With the STOP-FINAL-ADDRESS switch in the STOP FA position, then SFAL level will be TRUE to inhibit a CONTINUOUS operation when MAR = 7777.

- 4. The fourth input (+ MANL CAG 005 SFAL) is the STOP FA for a Manual operation.

- 5. The fifth input will be TRUE to inhibit a CONTINUOUS operation if there is an Error as indicated by MERF, and the STOP ERROR/ IGNORE ERROR switch is in the STOP position as indicated by SOEL.

If all of the inputs to CTUS are FALSE, then the output of the CTUS switch will be TRUE to allow a CONTINUOUS operation. If any one of the inputs are TRUE, then CTUS will be FALSE and a CONTINUOUS operation will be stopped with the Pulse Counter equal to three.

For the actions which occur at MPC = 3, refer to Figure 2.2-10. The portions of this Figure which are shaded can occur only when in the REMOTE position and have been discussed in Section 2.1.

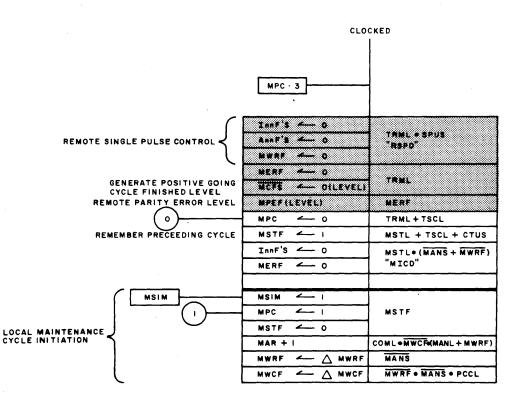

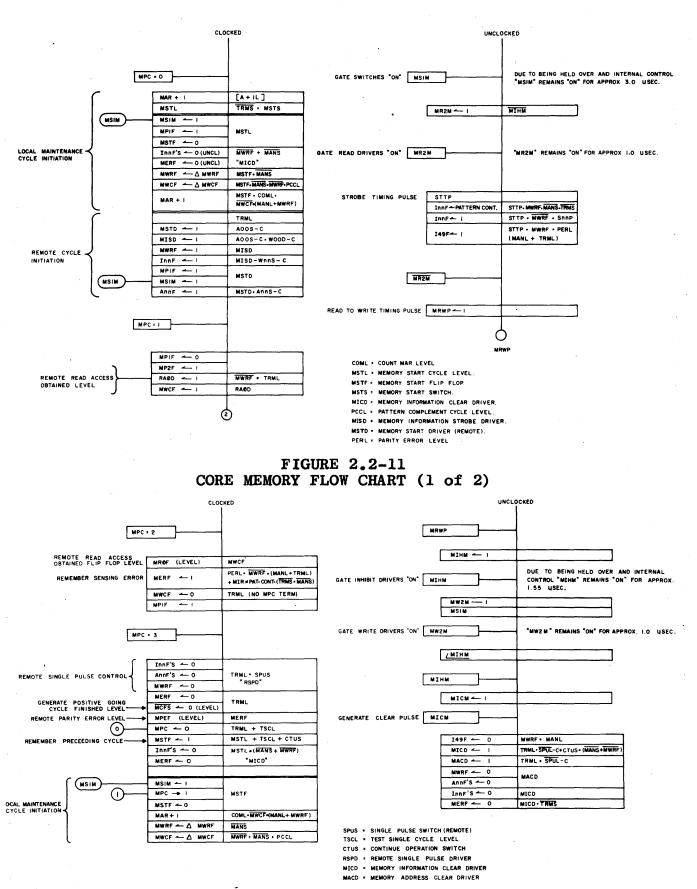

FIGURE 2.2-10 MPC = 3 FLOW

#### TRML + TSCL

If the Memory Module is in REMOTE (TRML) or if it is in SINGLE CYCLE (TSCL), then set the Pulse Counter to zero, MPC -0.

#### MSTL + TSCL + CTUS

If the Memory Start Level is TRUE from the Start switch (MSTL) or, if this is a SINGLE CYCLE operation (TSCL) or, if the CON-TINUOUS level is TRUE (CTUS); then set the Start Flip-Flop to one (MSTF -1) to remember a previous operation.

MSTL • (MANS/ + MWRF/) "MICD"

The level MICD, Memory Information Clear Driver, will be TRUE with the MSTL level and either MANS/ (no Manual operation) or MWRF/ (a Memory Read operation). MICD in turn is used to clear the Information Register (InnFs -0), and to reset the Error Flip-Flop (MERF -0).

#### MSTF

With MSTF set at MPC = 3(this is the second Clock Pulse at MPC = 3); another Memory cycle will be initiated by setting MSIM  $\leftarrow 1$  to initiate the Multi Timing. Also, the Pulse Counter is set to one (MPC  $\leftarrow 1$ ), and the Memory Start Flip-Flop is reset (MSTF  $\leftarrow 0$ ). The Pulse Counter is set to zero instead of one because the actions to initiate a Memory cycle are now done at MPC = 3 instead of at MPC = 0.

With MSTF set to one, all of the actions listed below the double

FIELD ENGINEERING TECHNICAL MANUAL -

| B461.51 |   | 2  | 2-13 |  |

|---------|---|----|------|--|

| January | 1 | 5, | 1965 |  |

line shown in Figure 2.2-10 can occur.

$COML \cdot MWCF/ \cdot (MANL + MWRF)$

With the above conditions, the Address Register will be incremented by one (MAR + 1). The above term states that the COUNT/ INHIBIT switch is in the COUNT position (COML) and the "worst case" flip-flop is OFF (MWCF/) and, this is either a Manual operation (MANL) or, the Write flip-flop is set (MWRF). When operating in AUTO, MANL is FALSE. The combination of MWCF/ and MWRF indicates the end of a two or four cycle Memory operation. See Figures 2.2-5 and 2.2-6.

MANS/

If this is not a Manual operation, then complement the Write flip-flop (MWRF  $\leftarrow -\Delta$  MWRF).

MWRF/ • MANS/ • PCCL

If the operation is the "worst case" (PCCL), and not a Manual operation (MANS/), then complement the "worst case" flip-flop (MWCF  $\leftarrow \Delta$  MWCF) at the completion of each Memory Read cycle. The complementing of MWCF allows for the Writing and Reading of the true and complement form of the configuration of bits as indicated by the Pattern Control circuitry.

The previous discussion of the Flow Charts showed only the portions of the flows involved. Figures 2.2-11 and 2.2-12 display the entire flows for the Core Memory.

The columns at the left are the Clocked portion of the flow subdivided by MPC values. The columns at the right display the Unclocked portion of the flow and is subdivided by the individual Multis and the actions that they perform.

SEE PAGE 2.2-14 FOR FIGURES 2.2-11 & 2.2-12.

FIGURE 2.2-12 CORE MEMORY FLOW CHART (2 of 2) B FIELD ENGINEERING TECHNICAL MANUAL -

| B461.51 | 3.  | .0-1 |

|---------|-----|------|

| January | 15, | 1965 |

~

# INDEX - SECTION 3

# 3 FUNCTIONAL DESCRIPTION - ELECTRONIC

| 3.   | l Core Stack                            | January | 15, | 1965 |

|------|-----------------------------------------|---------|-----|------|

| 3.2  | 2 Addressing                            | January | 15, | 1965 |

| 3.3  | 3 Read/Write Control                    | January | 15, | 1965 |

| 3.4  | 4 Memory Cycle Timing                   | January | 15, | 1965 |

| 3.   | 5 Parity                                | January | 15, | 1965 |

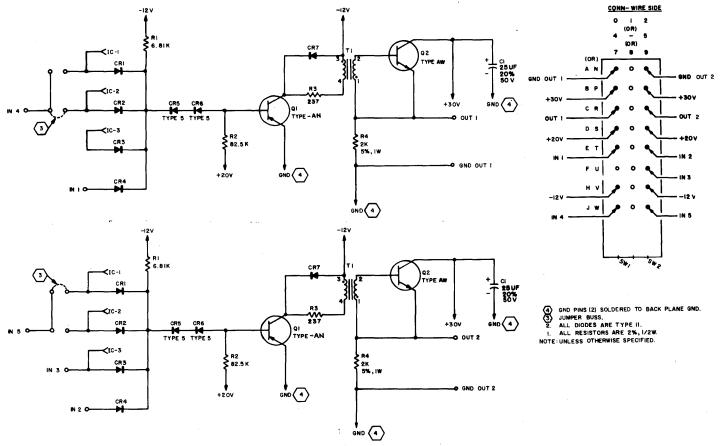

| 3.0  | 6 Read/Write Current Driver (DRAC)      | January | 15, | 1965 |

| 3.7  | 7 Memory Address Switch (SWAD)          | January | 15, | 1965 |

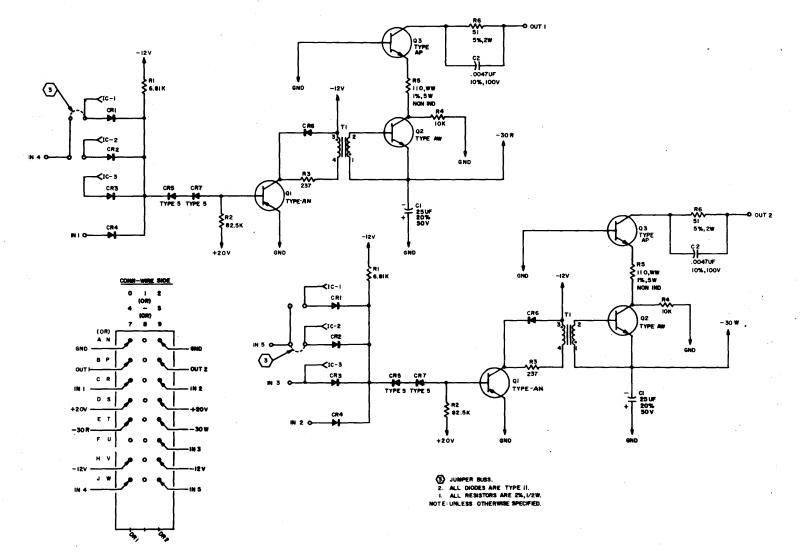

| 3.8  | 3 Inhibit Current Driver (DRIC)         | January | 15, | 1965 |

| 3.9  | 9 Sense Amplifier (AMS)                 | January | 15, | 1965 |

| 3.10 | No Delay Flip-Flop (FFN7)               | January | 15, | 1965 |

| 3.1  | Read Switch 1 Multi - DSW1 (MS1M)       | January | 15, | 1965 |

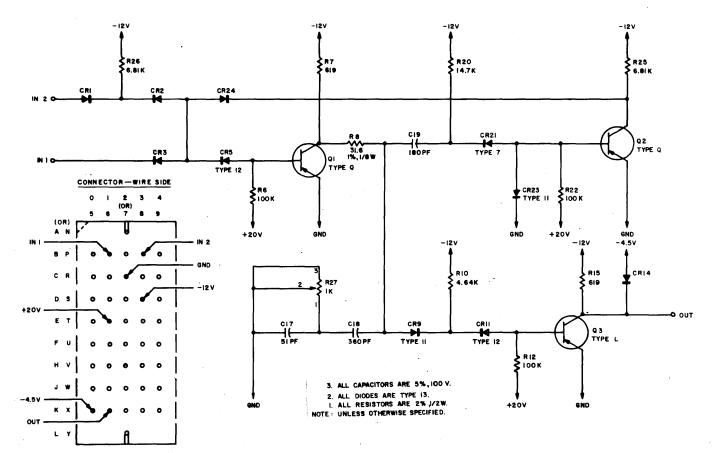

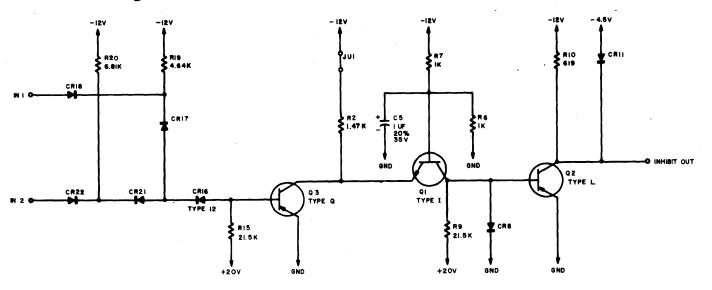

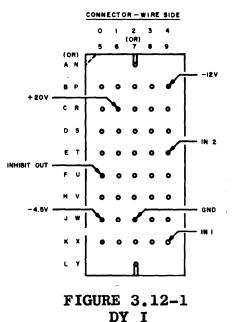

| 3.12 | 2 Inhibit Delay - DY I (MIHM)           | January | 15, | 1965 |

| 3.13 | B Read/Write Delay - DURW (MRWP)        | January | 15, | 1965 |

| 3.14 | 4 Strobe Multi - STMD                   | January | 15, | 1965 |

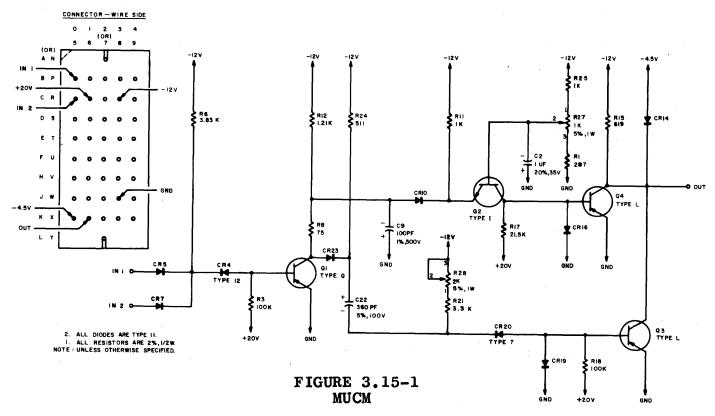

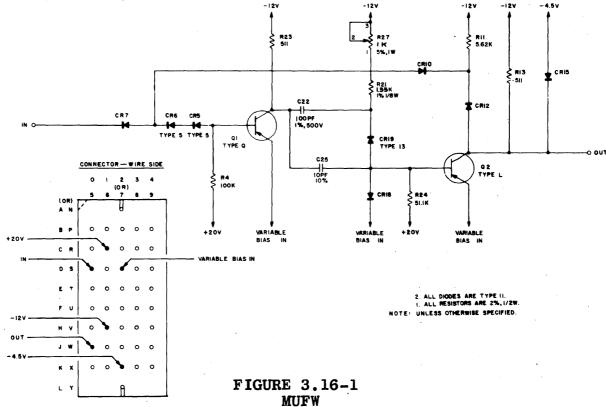

| 3.15 | 5 Read/Write Multi - MURW (MR2M & MW2M) | January | 15, | 1965 |

| 3.16 | 6 Multi F W -(MUFW)                     | January | 15, | 1965 |

| 3.17 | Power Control                           | January | 15, | 1965 |

| 3.18 | 3 -15V Regulator                        | January | 15, | 1965 |

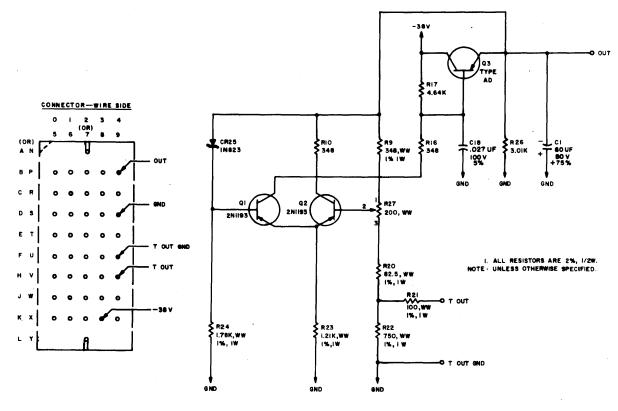

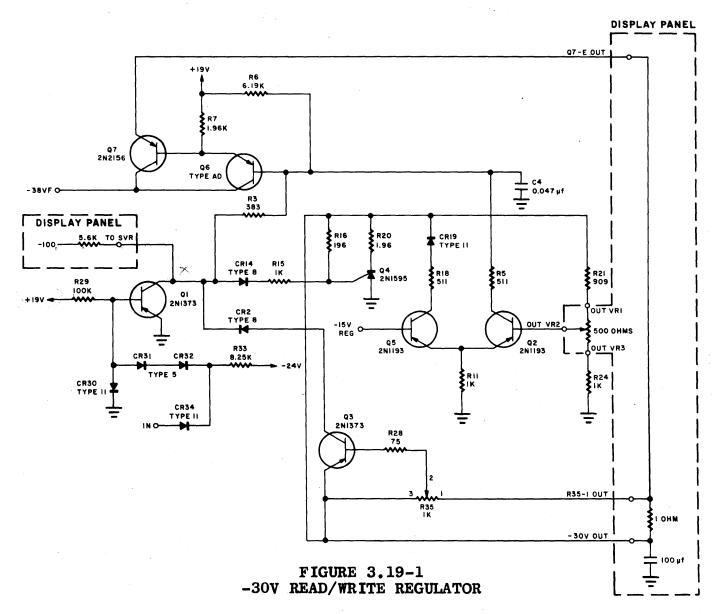

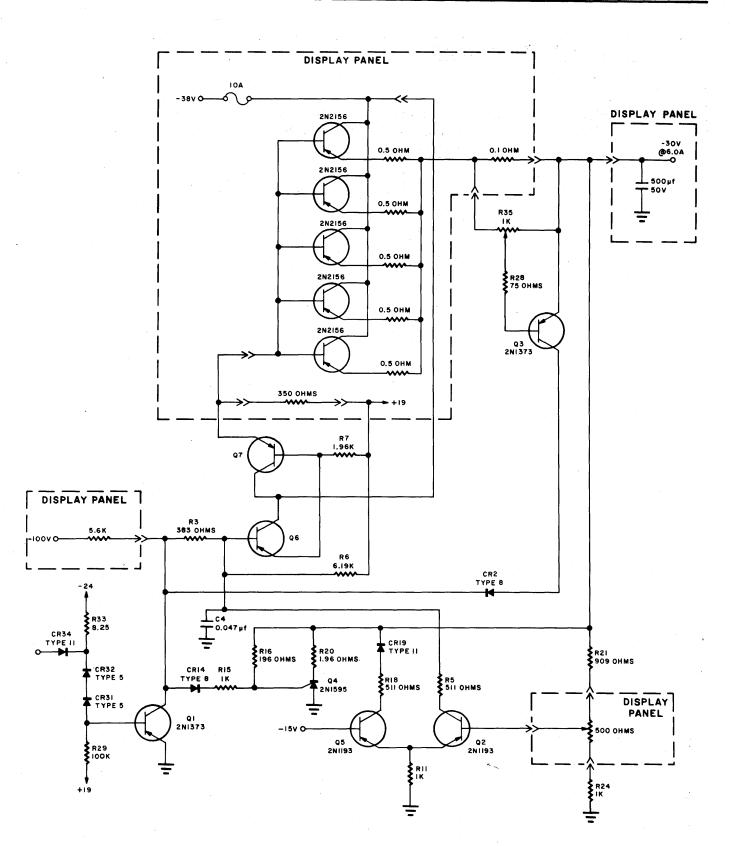

| 3.19 | -30V Read/Write Regulator (250ma)       | January | 15, | 1965 |

| 3.20 |                                         | -       |     |      |

| 3.2  | 0                                       | Ţ       | •   |      |

| 3.22 |                                         | •       | •   |      |

| 3.23 |                                         | •       | •   |      |

| 3.24 |                                         | •       |     |      |

| 3.25 | 5 Clock & Clock Control                 | January | 15, | 1965 |

| 3.20 | -                                       |         | •   |      |

| 3.27 | Maintenance Control Switches            | January | 15, | 1965 |

| 3.28 |                                         | •       | •   |      |

| 3.29 | Maintenance Start Logic                 | January | 15, | 1965 |

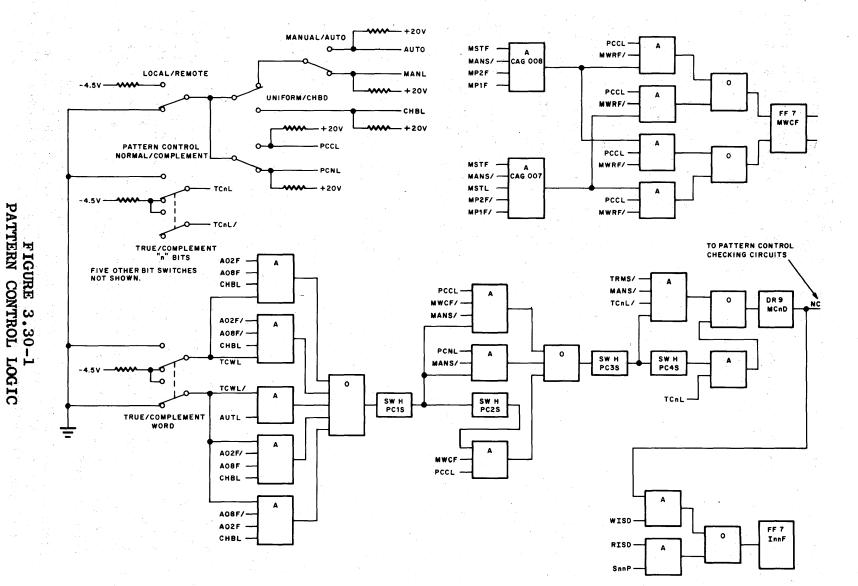

| 3.30 | Pattern Control Logic                   | January | 15, | 1965 |

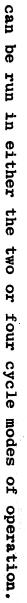

| 3.31 | Pattern Control Checking Circuits       | January | 15, | 1965 |

| 3.32 |                                         | •       | •   |      |

| 3.33 | Test Clear Circuits                     | January | 15, | 1965 |

|      |                                         |         |     |      |

| A | FIELD ENGINEERING TECHNICAL MANUAL | B461.51   | 3.1-1    |

|---|------------------------------------|-----------|----------|

| V |                                    | January 1 | .5, 1965 |

## 3.1 CORE STACK

Storage in the B461 Core Memory is based on the principle of magnetizing a toroid core in one direction to record the storage of a binary "one" and in the opposite direction to record a "zero".

The ferro-magnetic material used in the construction of the core has a nearly rectangular hysteresis loop. Since the entire operation of storage in a core is based on the hysteresis loop, an understanding of the magnetic characteristics of a ferro-magnetic material is essential.

#### Ferro-Magnetism

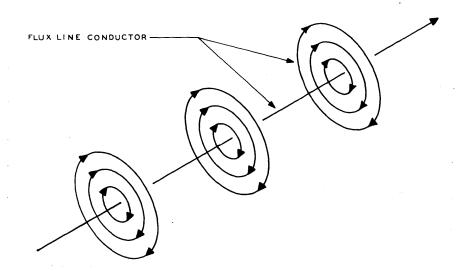

A current flowing through a conductor will cause a magnetic field to be built up around the conductor. The magnetic lines of force are concentric and lying in a plane which is perpendicular to the plane of the conductor. See Figure 3.1-1.

FIGURE 3.1-1 MAGNETIC FIELD

An easy method of determining the direction of the magnetic lines of force is to imagine grasping the conductor with the right hand so that the thumb points in the direction of the current flow. The fingers will then encircle the conductor in the direction of the flux lines.

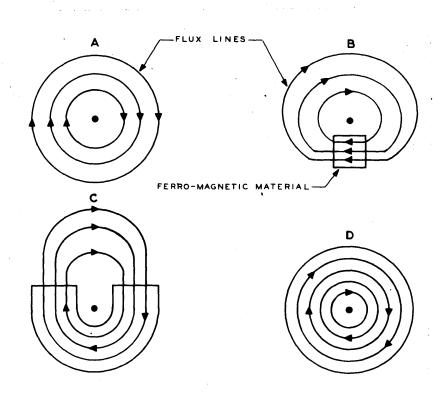

When a ferro-magnetic material is introduced into the magnetic field, the field becomes distorted in the manner shown in Figure 3.1-2B. This is because the material offers a low resistance path in comparison to the space that surrounds the inductor. The magnetic field will pass through the ferro-magnetic material following the contour of the material as illustrated in Figure 3.1-2C.

FIGURE 3.1-2 FIELD DISTORTION

When the ferro-magnetic material is fashioned into the form of a closed ring, the magnetic field set up by a magnetizing current is wholly confined to the interior of the ring. No lines of magnetic induction pass through the surface of this material to the space outside the ring. See Figure 3.1-2D. The magnetic intensity (H) in the material of the ring is equal to the product of this magnetization current and the number of turns in the magnetizing winding, divided by the mean circumference of the ring.

| H = Ni/c | H = Magnetic Intensity         |

|----------|--------------------------------|

|          | N = Number of Turns            |

|          | i = Current in the Winding     |

|          | c = Mean Circumference of Ring |

Note that the magnetic intensity does not depend on the type of material of which the ring is formed.

The magnetic flux density (B) within the ring is the product of the magnetic intensity (H) and the permeability  $(\mu)$  of the ring material.

| B = | Нµ | B | - | Magnetic Flux Density        |

|-----|----|---|---|------------------------------|

|     |    | H | - | Magnetic Intensity           |

|     |    | μ | - | Permeability of the Material |

|     |    |   |   |                              |

The flux density (B) is not a linear function of the magnetic intensity. This is because the permeability of a material is not a constant value. Permeability depends on the type of material, the temperature

| B461.51 | 3   | 3.1-3 |  |

|---------|-----|-------|--|

| January | 15, | 1965  |  |

of the material, and on how much the material has been previously magnetized.

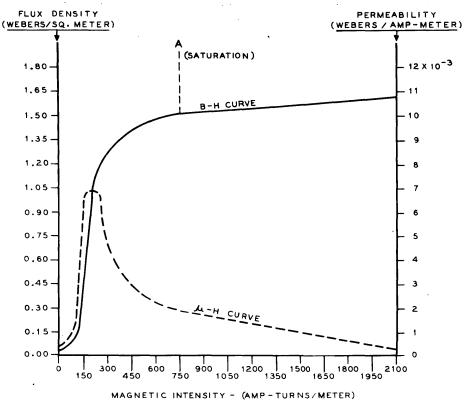

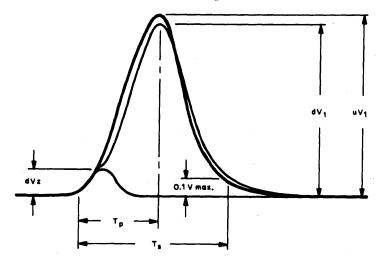

## FIGURE 3.1-3 TYPICAL MAGNETIZATION CURVE

Figure 3.1-3 shows the relationship between B, H, and  $\mu$  for a typical ferro-magnetic material. Notice that beyond point A, even though H is increasing, B remains almost constant. This is the magnetic saturation of the material and is due to the permeability ( $\mu$ ) decreasing at the rate that H is increasing.

## Hysteresis

Figure 3.1-3 shows the relationship between the B and H only if the material is initially unmagnetized and H is always increasing.

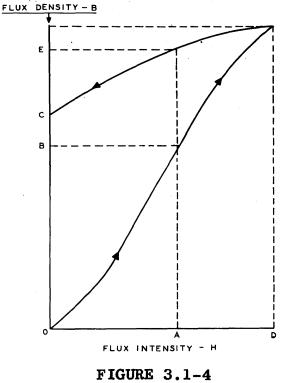

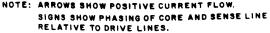

The magnetization curve shown in Figure 3.1-4 expresses the relationship of B and H for the following conditions.

- The magnetization current is increased from zero until the magnetic intensity (H) is equal to value A. The flux density (B) for this value of H is given to point B.

- 2. The magnetization current is increased from 0 until the value of H is D, and then decreased until the value of H is A. Now the flux density for the H value of A is given to point E.

- 3. The magnetization current is decreased to 0. The value of H falls from point A to 0. The flux density has a value of C

B-H CURVE

The flux density in the material is shown to depend not only on H, but also on the degree that the material has been previously magnetized. This behavior of the material, which causes the curve for a decreasing value of H to depart from the curve for an increasing value of H, is called Hysteresis.

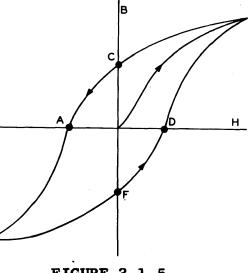

When H is increased from 0 to some maxinum value in the opposite direction, then decreased to 0; increased to the same maximum value in the opposite direction, then decreased to 0; the flux density reverses in the manner shown in Figure 3.1-5. This closed magnetization curve is called a hysteresis loop. Points C and F indicate the flux density that remains in the material after H is decreased to 0. These points are usually labeled +Br and -Br and are called the magnetic retentivity of the material. Points A and D show the amount of H required to reduce B to 0 after the material has been magnetized in the opposite direction. This is called the Coercive Force.

FIGURE 3.1-5 HYSTERESIS LOOP

## Square Hysteresis Loop

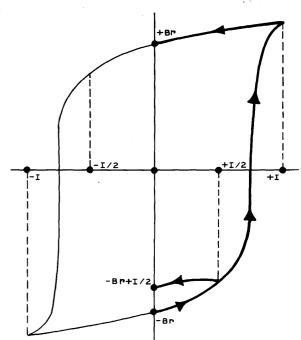

Ferrite cores are made of special materials that will produce a hysteresis loop which is almost square. This square-loop characteristic allows the ferrite to act as a bi-stable storage element. If the

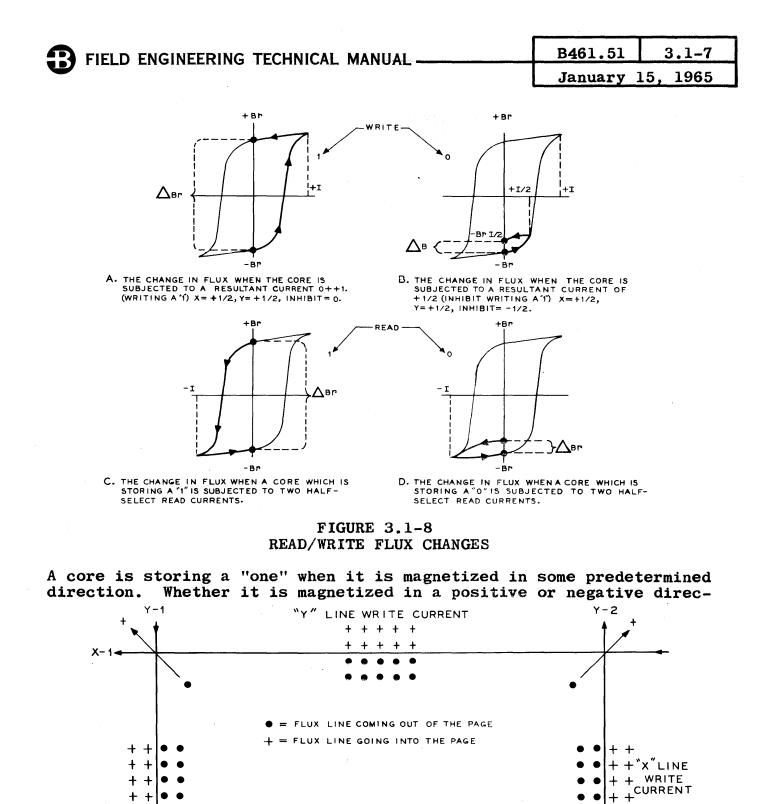

ferrite core whose hysteresis loop is shown in Figure 3.1-6 is magnetized in the negative direction (-Br), and we pulse the winding with a current value of +I/2, the flux density in the core will be changed from -Br to -BrI/2. As illustrated, the change in residual flux is very small, and the core is still highly magnetized in the negative direction. However, if we pulse the winding with a current value of +I, the core will rapidly switch from -Br to +Br and will now be highly magnetized in the positive direction.

The square loop discriminates against small values of current in the windings. There is no appreciable change in flux density unless the winding current reaches a value which will cause an H value beyond the knee of the curve. The H current value of + or - I/2 is referred to as a half-select current; and an H current value of + or - I is referred to as a full select current.

FIGURE 3.1-6 SQUARE LOOP

#### **Temperature Effect**

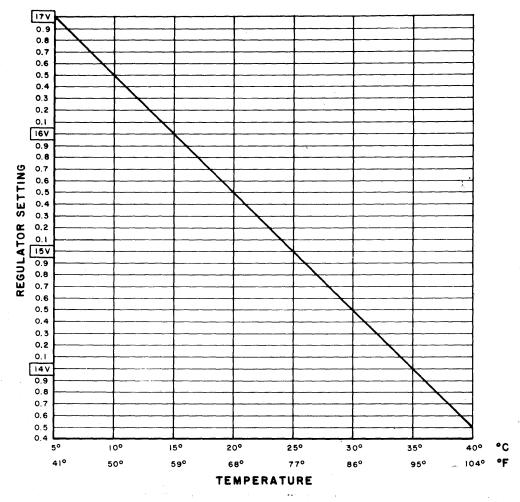

The permeability of a ferro-magnetic material decreases as the temperature increases. The flux density (B) is the product of the flux intensity (H) and the permeability ( $\mu$ ); therefore, if the permeability decreases, then the shape of the material's hysteresis loop will be changed. This temperature problem demands that the core storage system be operated within a specified range of temperatures.

A core's hysteresis loop tends to become less square as the temperature of the material increases. This means that a winding current of I/2 will cause a larger change in the flux density of the core. To insure that the change in flux density will remain the same within the range of operating temperatures, the core winding drive current is decreased as the temperature is increased.

## Core Windings

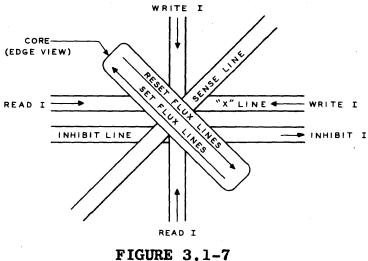

Each of the cores in the Memory are threaded by four wires, each wire serving as a one-turn winding. See Figure 3.1-7. In order to understand the function of the windings, assume that the core is magnetized in the negative direction and that the X and Y windings have a current flow that tends to establish a flux density in the positive direction.

To write a binary "one" into the core, that is to switch the state of the core from -Br to +Br, both the X and Y currents must occur at the same time and have a combined value which will cause a sufficient magnetizing force to switch the polarity of the core's flux density.

CORE WINDING

If the current flowing through each individual winding is equal to I/2, then the combined value is I. This means that the core will switch states when both currents are present; but, if only one of the currents is present, there is very little effect on the flux density of the core (See Figure 3.1-8A and B), and the core is half-selected.

As shown in Figure 3.1-7, the Inhibit winding current flow when present, will oppose that of the Write currents in the X and Y lines. When all three currents are present, the resulting effect on the core is +I/2 since the -I/2 due to the Inhibit winding current will cancel one of the Write +I/2 currents. See Figure 3.1-8B. The Inhibit-winding Driver is gated by the Information Register and is used to prevent the writing of a binary "one" into the core.

During the Read phase of a Memory cycle, the direction of current flow in the X and Y lines is reversed. If the core is in the "ones" state, coincident currents in the X and Y windings will cause the core to switch its magnetic state. This is shown in Figure 3.1-8C. This rapid change in the flux density of the core will cause a current to be induced into the Sense winding. This is a Read out of a binary "one".

If the core has been originally in the "O" state, the coincident Read currents would merely drive the core further into saturation. As shown in Figure 3.1-8D, there will be very little change in the flux density and little current induced into the Sense winding.

FIGURE 3.1-9 ALTERNATE LINE WRITE CURRENTS

+ + +

+ + +

+

+

$\bullet$  + +

Printed in U.S.A.

X-2-

+

+ +

tion will depend on the direction of the Write currents flowing in the X and Y lines. Notice in Figure 3.1-9 that due to the alternate X and Y line Write currents, two of the cores are magnetized in the positive direction and two are magnetized in the negative direction. It does not make any difference in what direction a core is magnetized, since during the Read out of the information, the X and Y line current is reversed.

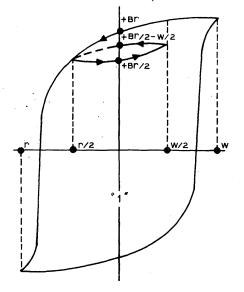

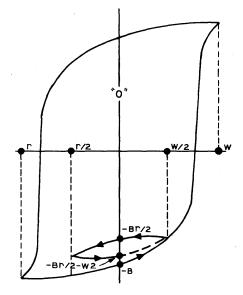

## Noise

Figure 3.1-10 shows a typical hysteresis loop. Because of the curved portions of the loop, a half-select current will disturb the magnetic state of the core. A core is subjected to half-select currents each time another core on the same X or Y line is selected for a Read or Write operation.

When a core that is storing a "one" is subjected to a half-select Read current, the state of the core is changed from +B to +Br/2. Similarly, a core that is storing a "zer0" will be changed from -B to -Br/2. When the information is written back into the selected core, the half-selected cores are subjected to a half-select Write current. This half-select Write current goes from +Br/2 to +Br/2-w/2 and from -Br/2 to -Br/2-w/2 respectively.

A. THE CHANGES IN FLUX OF A CORE STORING A '1' WHEN IT IS SUBJECTED TO A HALF-SELECT READ (P/2) FOLLOWED BY A HALF-SELECT WRITE (W/2).

B. THE CHANGES IN FLUX DENSITY OF A CORE STOR-ING A "O" WHEN IT IS SUBJECTED TO A ( $\Gamma/2$ ) FOL-LOWED BY A HALF-SELECT WRITE (W/2).

÷ч

# FIGURE 3.1-10 HALF-SELECT FLUX CHANGES

When half-select currents are applied alternately in the Read and Write directions, the core will transverse a minor hysteresis loop as shown in Figure 3.1-10.

Previously, only the selected core's contribution to the Sense line

|   | FIELD ENGINEERING                                           | TECHNICAL | MANIIAL | B461.51 | 3.1-9    |

|---|-------------------------------------------------------------|-----------|---------|---------|----------|

| U | L I has been how - has a 12 % of 12 % has been 12 & 12 % of |           |         | January | 15, 1965 |

current has been considered. However, the same Sense line passes through every core in a plane. Unavoidably, each of the cores threaded by the selected X and Y lines receives a half-select Read current which also contributes to the Sense line current. In a 64 x 64 matrix, 63 cores along the X line and 63 cores along the Y line would receive a half-select current. This accumulation of induced currents from the half-selected cores can amount to an induced current which is much greater than that due to the selected core, thereby causing a Read error if the accumulated half-select induced currents are out of phase with the induced current from the co-selected core.

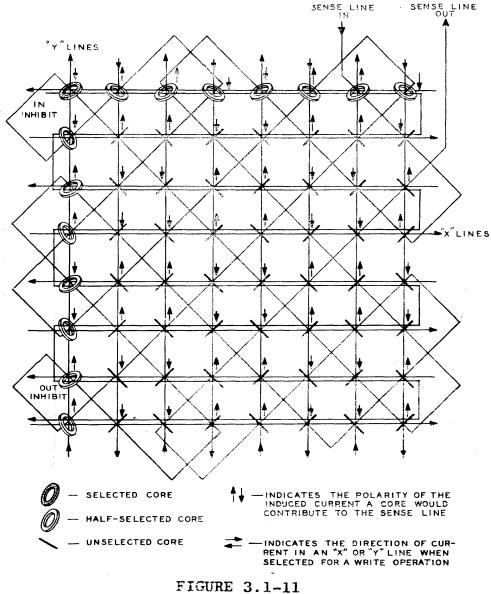

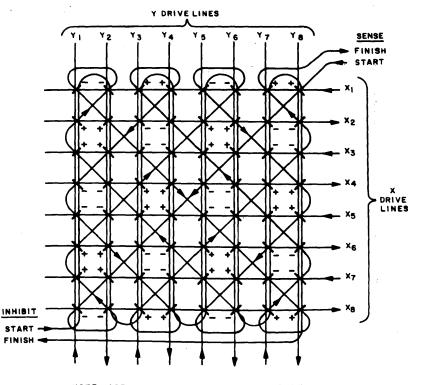

To minimize this undesirable current flow, the Sense winding is arranged through the cores in a checkerboard pattern so that half of the cores will produce a negative-going pulse in the Sense line, and the other half will produce a positive pulse in the line. See Figure 3.1-11.

8 x 8 CORE PLANE

When all cores contain the same information (1 or 0), the positive induced current which is contributed by one half of the half-selected cores, will be cancelled by the negative induced current from the other half of the half-select cores.

In actual practice, there is not a complete cancellation of the halfselect signals. This is because it is not possible to manufacture cores that all exhibit exactly the same magnetic characteristics. This is also due to the physical layout of the Sense line. There will be two half-select cores left unopposed.

There are 63 half-select cores on each selected line. Of these cores, 32 are contributing a pulse of one polarity and 31 are contributing a pulse of the opposite polarity. This leaves one core on each line that is unopposed. Both of these cores are contributing a pulse that is out of phase with the pulse from the selected core. The resultant signal in the Sense line is the contribution of the selected core, minus the two unopposed half-select cores contribution, plus or minus the difference noise from the remaining half-selected cores.

- $R = S-2hs \pm dn$

- R = Resultant Signal

- S = Signal due to the selected core

- hs = Signal due to the two unopposed half-selected cores

- dn = The difference noise signal due to

31 half-selected cores not complete ly cancelling the other 31 half selected cores

The worst pattern of storage information would be to have all the cores producing positive-going currents in one state and the other half in the opposite state. In this case, the term dn takes on a maximum value. The reason for this is that at the time that they are both subjected to a half-select Read current, the change in flux density of a core storing a "one" is not equal to the change in flux density of a core storing a "zero".

The cores storing zeros have been subjected to one more half-select current than the cores storing ones. This additional half-select current was applied at the time that the cores storing "ones" were fully selected. Because of this additional half-select current, the residual flux density of a core storing a "one" is not equal to the residual flux density of a core storing a "zero".

One of the factors that determines the permeability of a material is the degree that it has been previously magnetized. Since a core storing a "one" is not magnetized to the same degree as a core storing a "zero", the changes in flux density as the result of the half-select Read will not be the same.

| FIELD ENGINEERING TECHNICAL MANUAL | B461.51 | 3.1-11   |  |

|------------------------------------|---------|----------|--|

|                                    | January | 15, 1965 |  |

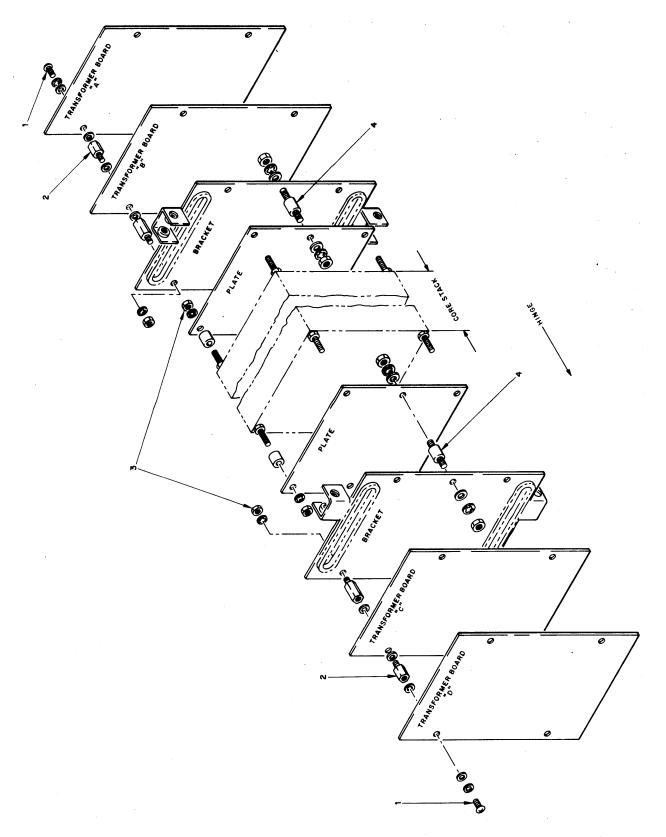

## Stack Construction

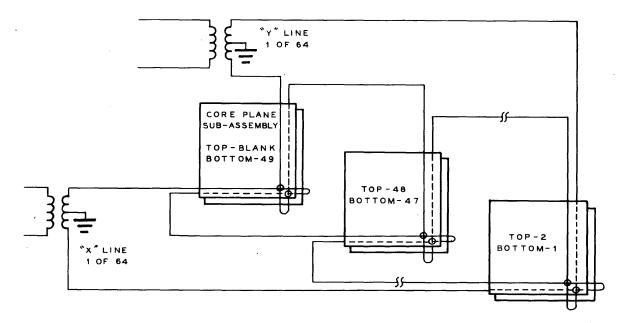

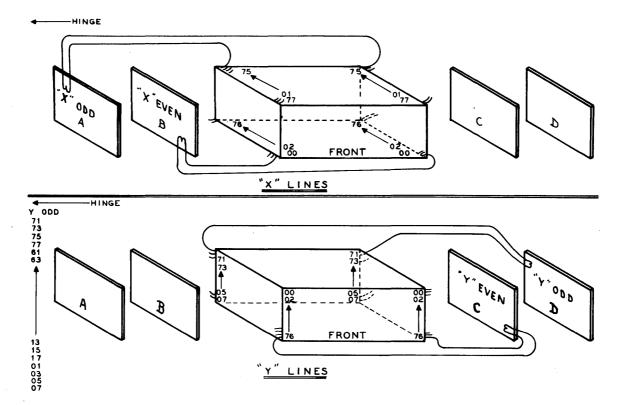

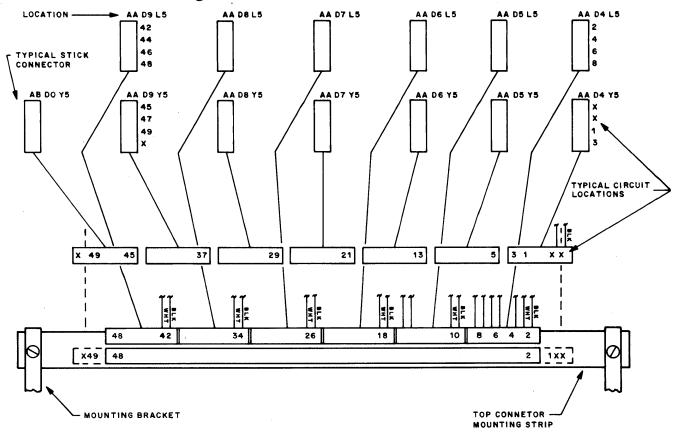

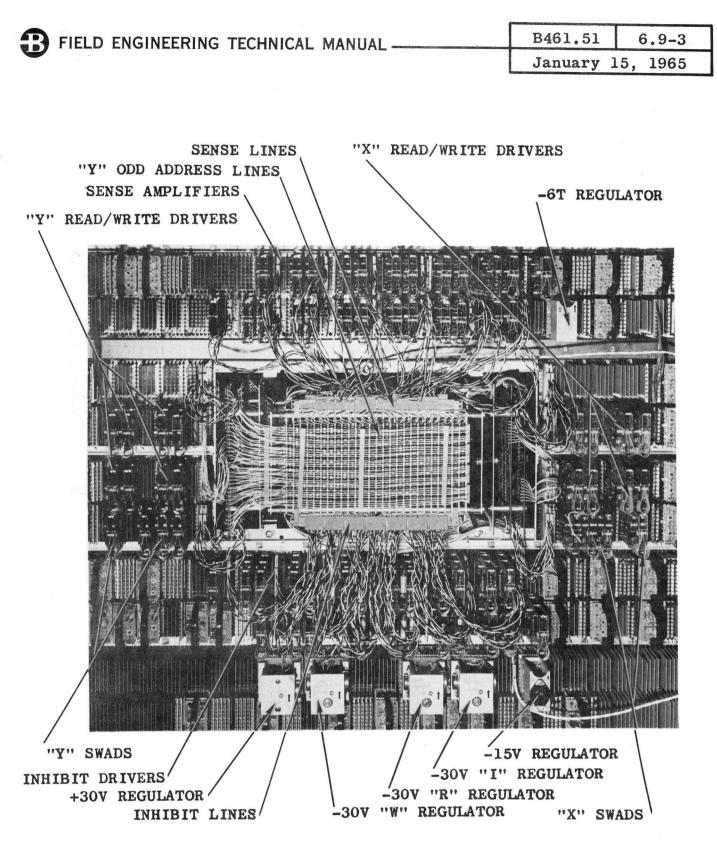

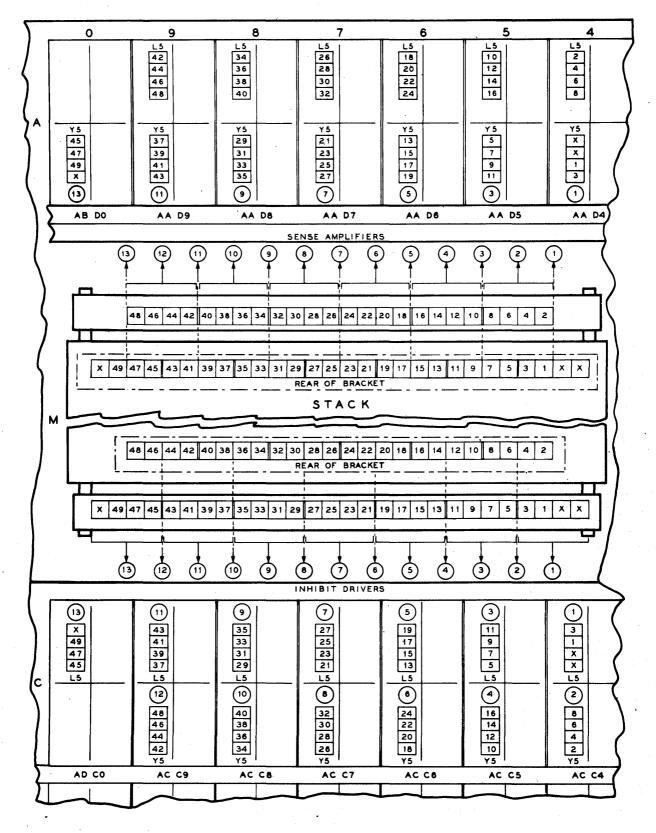

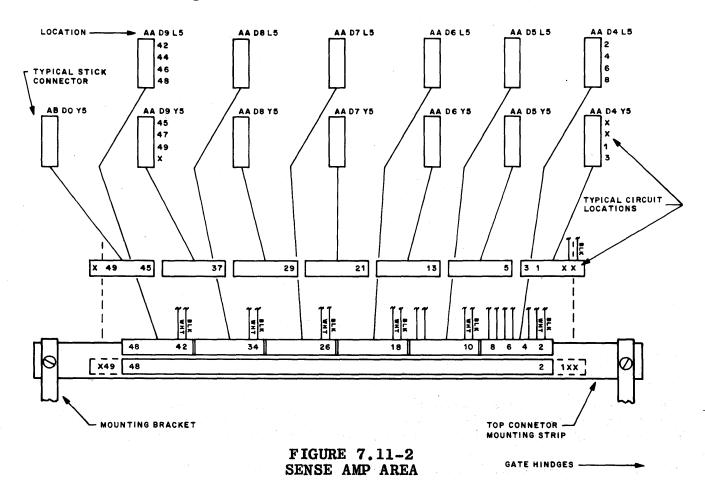

All the cores for the Memory are mounted into a unit referred to as the Core Stack. The Core Stack is sub-divided into planes. Each plane corresponds to one bit of information in each of the words. As there are 48 Information bits and one Parity bit in a word, the stack consists of 49 planes, plus one blank plane for a total of 50 planes. Each plane has its own Sense and Inhibit windings to make a total of 49 Sense and 49 Inhibit windings, one for each bit in a word.

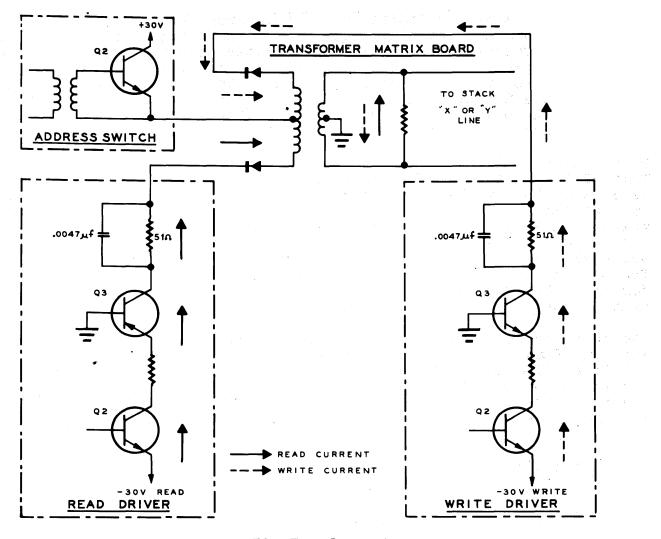

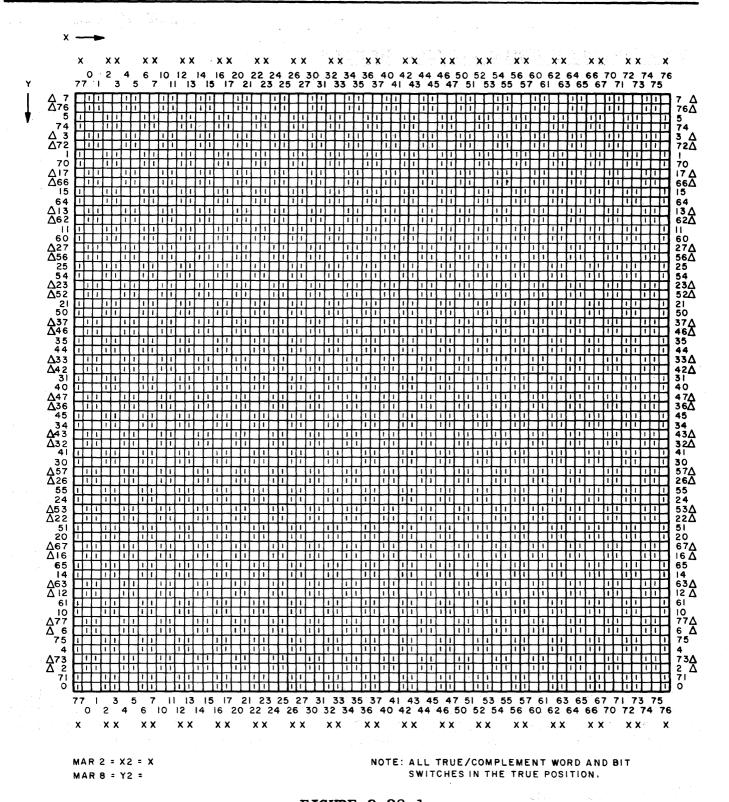

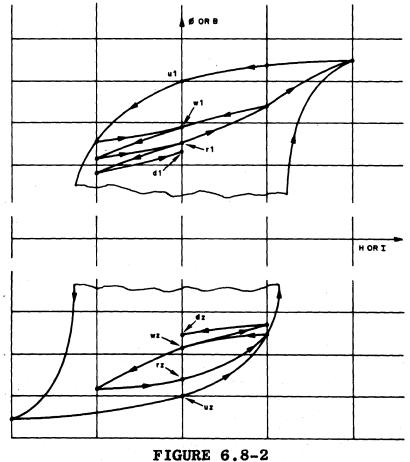

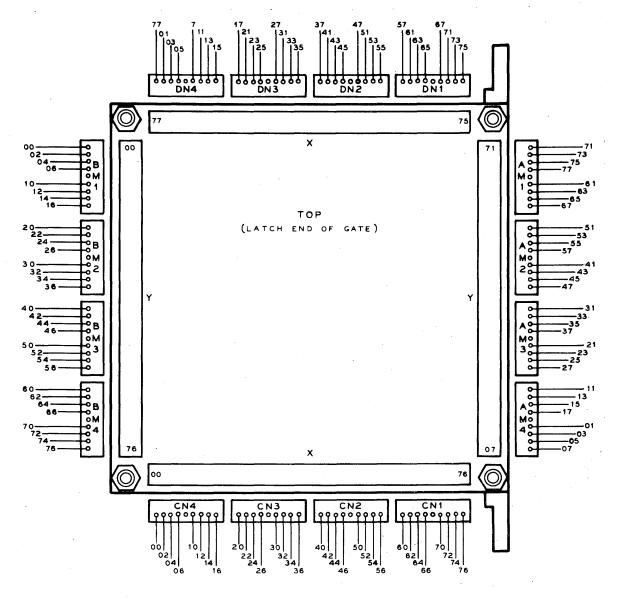

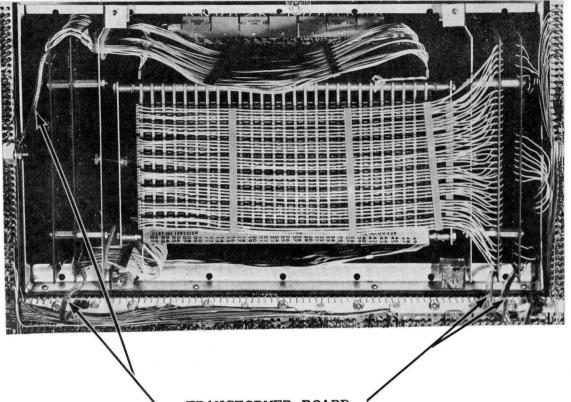

Every time a Memory cycle is initiated, one core in each plane is selected to access all 49 bits of a word. This is accomplished by the X and Y lines. There are 4096 cores in each plane arranged in a 64 x 64 Matrix, or, each plane is accessed by 64 X lines and 64 Y lines. Any one X line will intersect any one Y line only once in each plane; (refer to Figure 3.1-12), but the X and Y lines are wired to all planes in the Stack. By driving current into one X line and one Y line, both currents being in coincidence, one core will be selected in each plane; a total of 49 cores for an entire word.

FIGURE 3.1-12 X - Y LINE INTERSECTION

Each X and Y line originates from one side of the secondary of a transformer, loops through the entire stack, and returns to the other side of the same transformer secondary. See Figure 3.1-12. There is one transformer for each of the X lines and each of the Y lines. By driving current through the transformer primary in one direction for a Read, and the other direction for a write, the current in the secondary will also change direction. This in turn will drive current in the X or Y line in one of two directions, depending upon Read or Write.

For a detailed description of the transformer operation, refer to Section 3.2 of this manual.

| B FIELD ENGINEERING TECHNICAL | B461.51   | 3.2-1   |

|-------------------------------|-----------|---------|

|                               | January 1 | 5, 1965 |

# 3.2 ADDRESSING

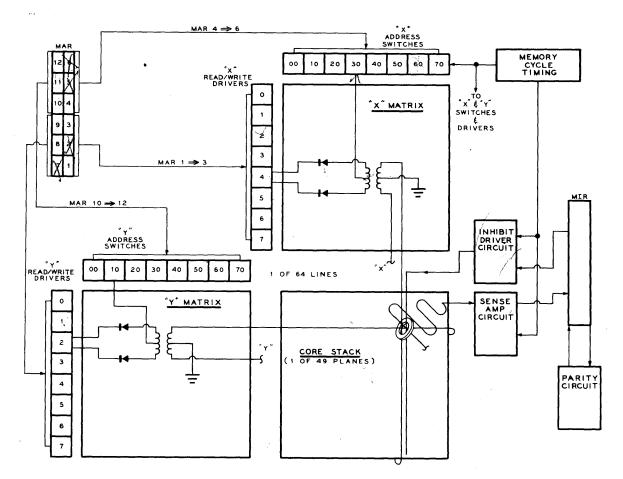

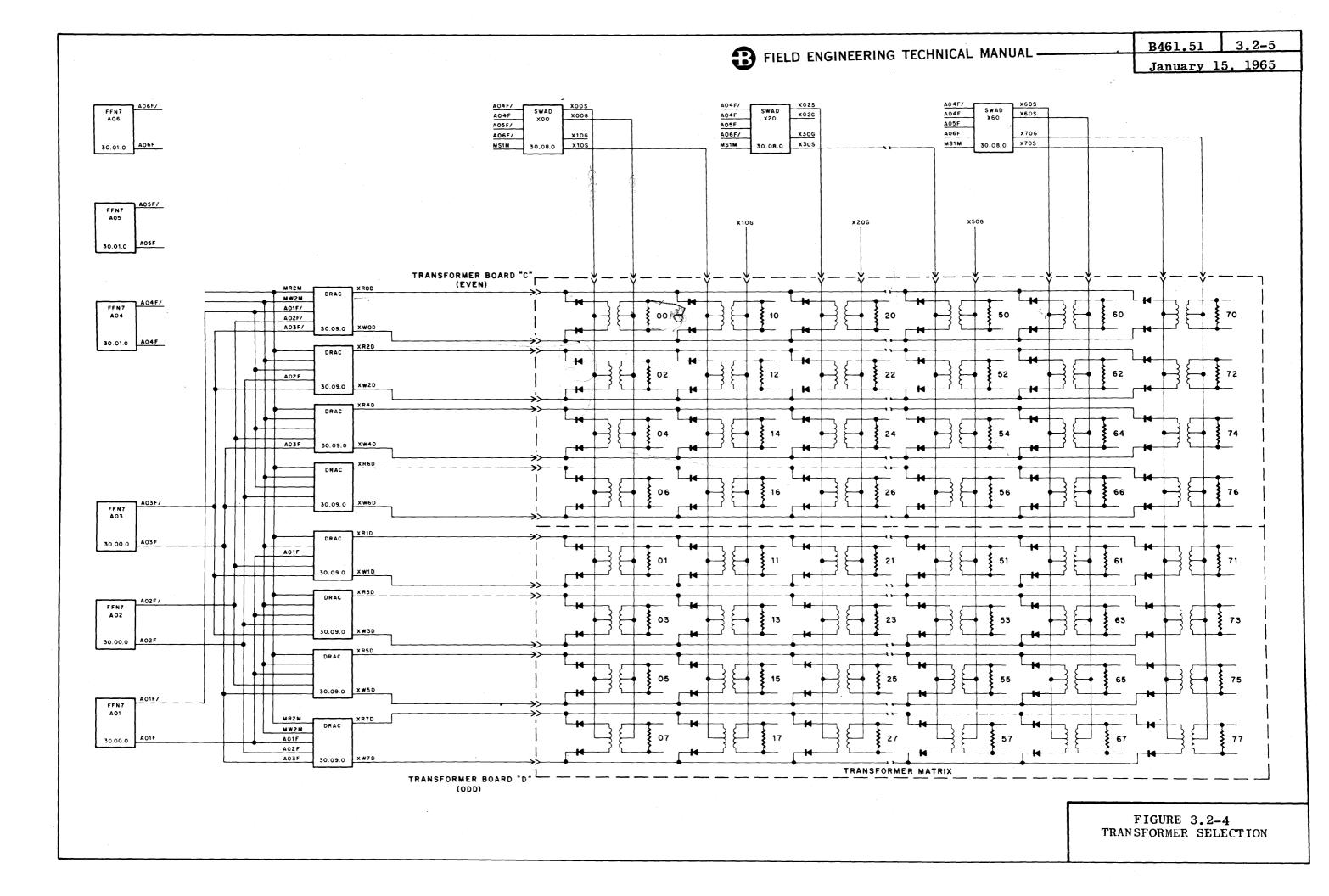

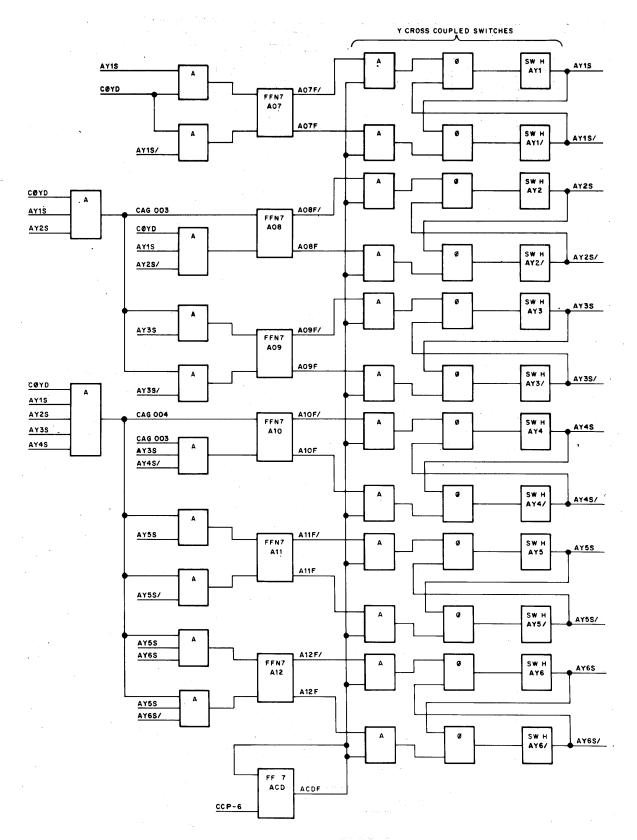

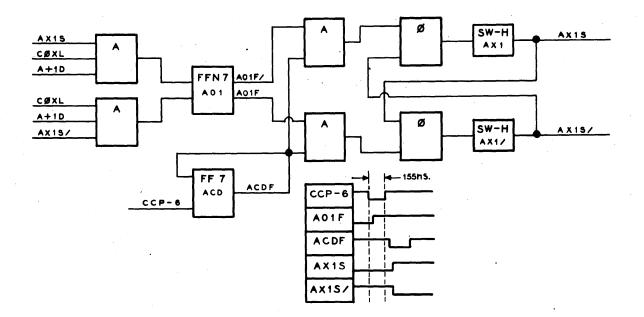

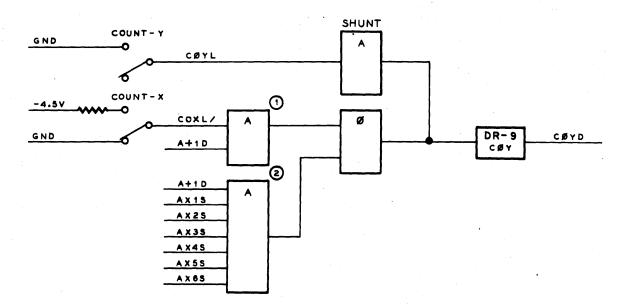

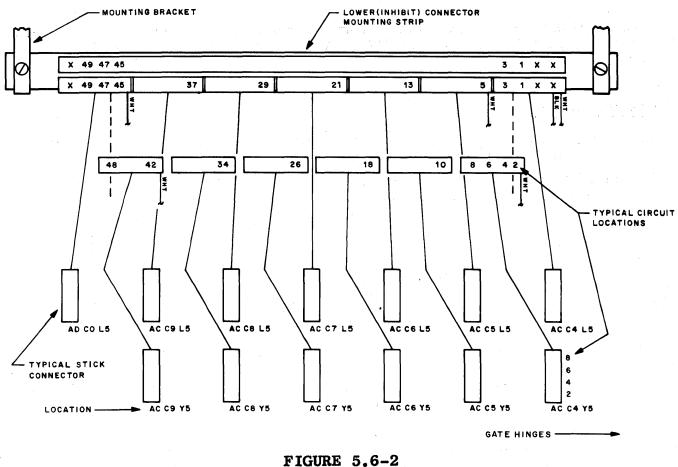

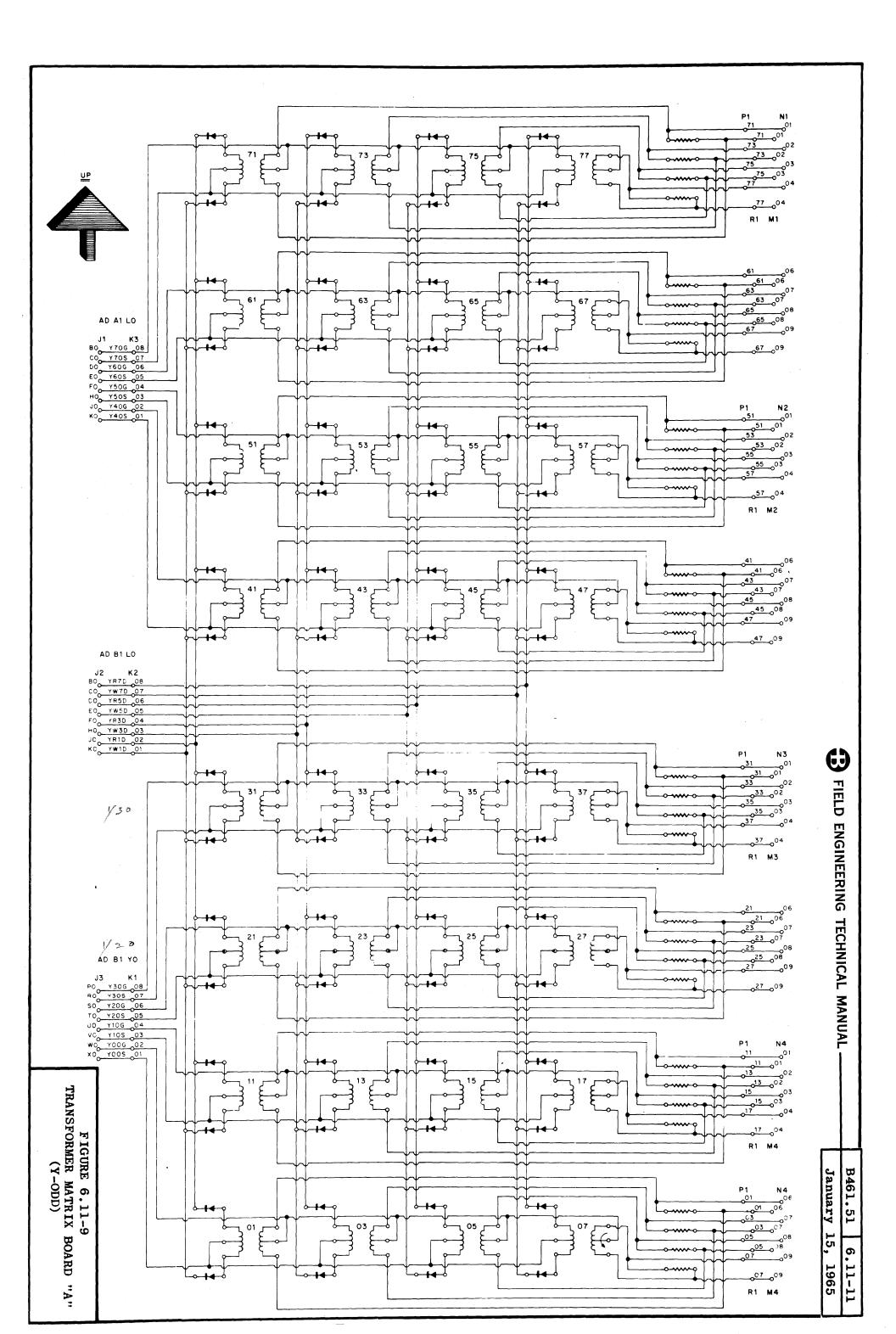

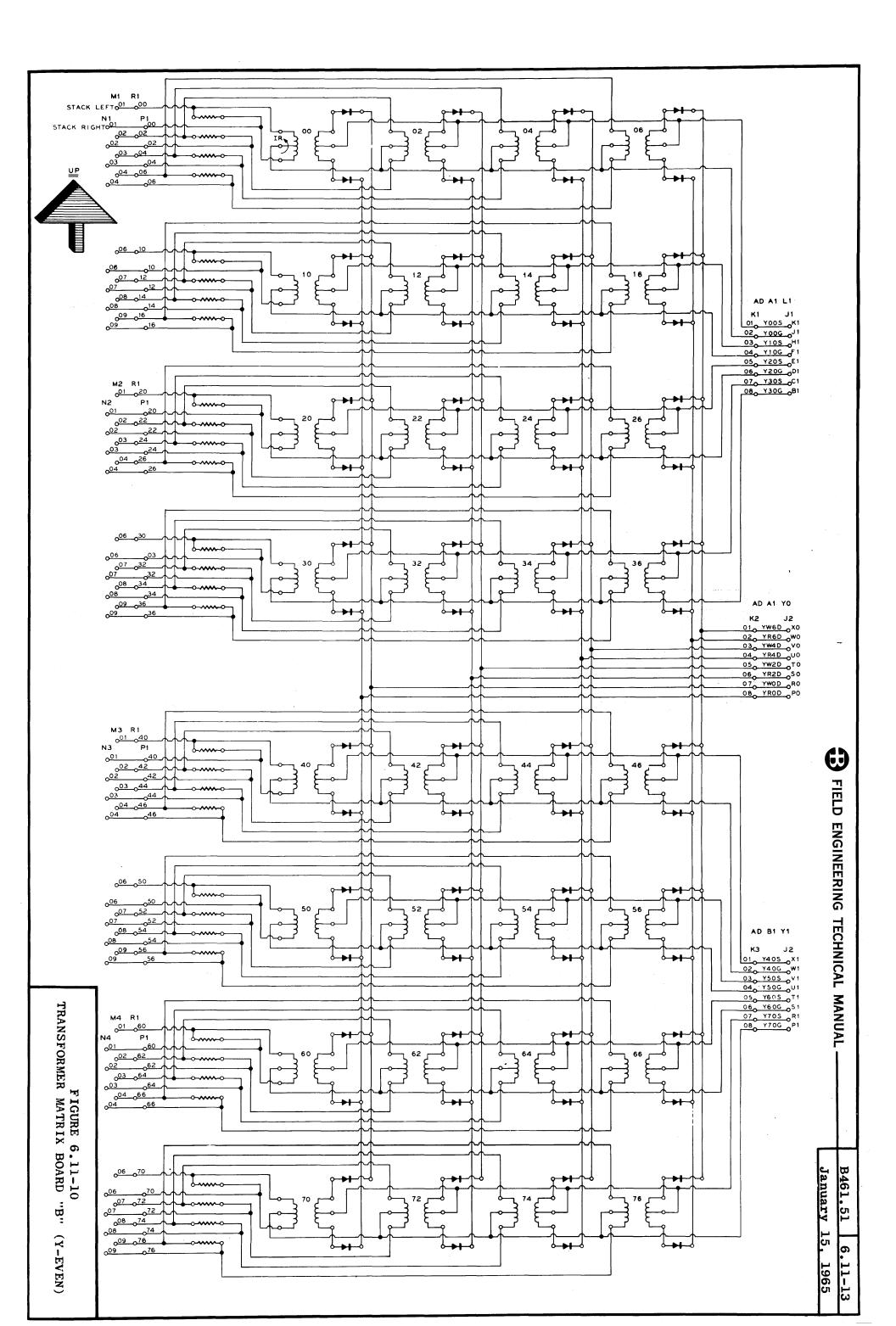

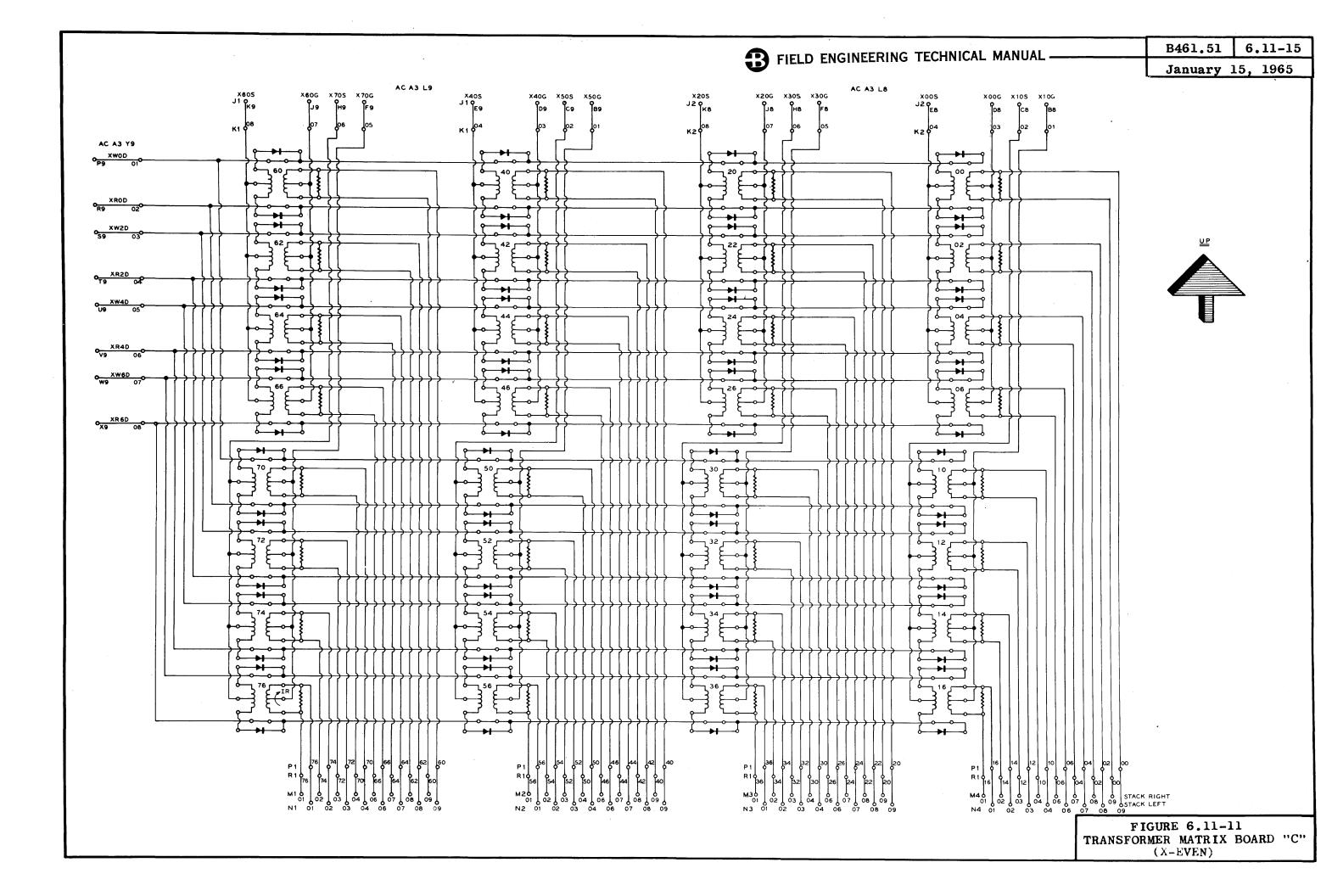

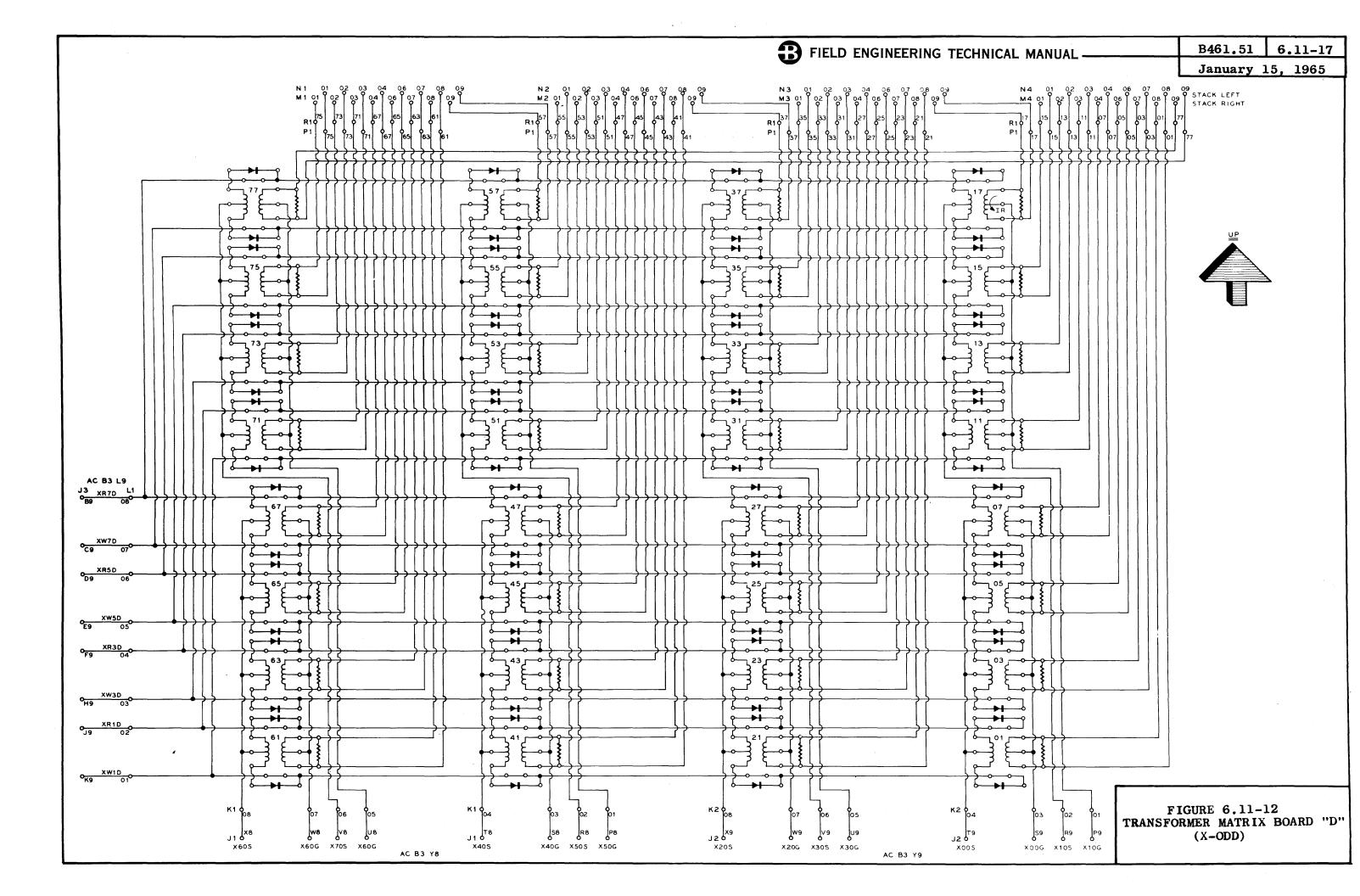

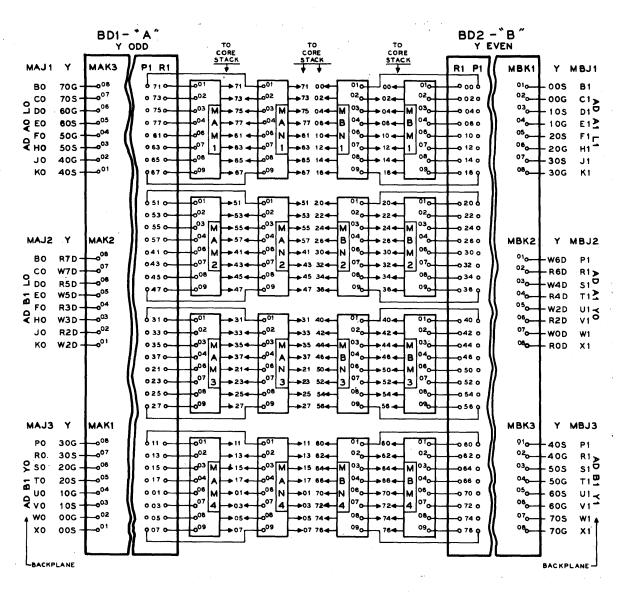

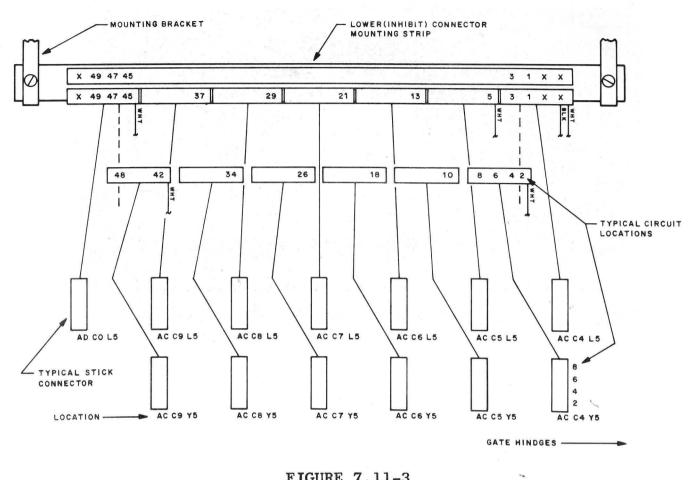

Addressing is the function of selecting a particular "X" line and "Y" line to access one of the 4096 words in the Core Stack. Figure 3.2-1 is a diagram of the Logical Units of the Core Memory.

FIGURE 3.2-1 LOGICAL UNITS

The Addressing portion of this diagram consists of the Address Register (MAR), "X" and "Y" switches, "X" and "Y" Read/Write drivers, the "X" and "Y" Transformer Matrices, and the "X" and "Y" lines to the Stack. The Memory Timing circuits go to the "X" and "Y" Address switches and Read/Write drivers as an enabling level to indicate when they are turned ON.

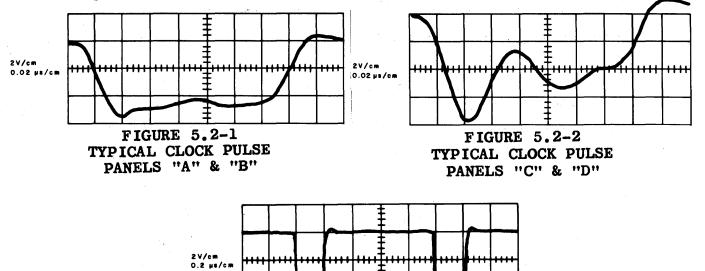

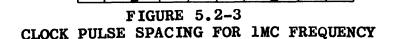

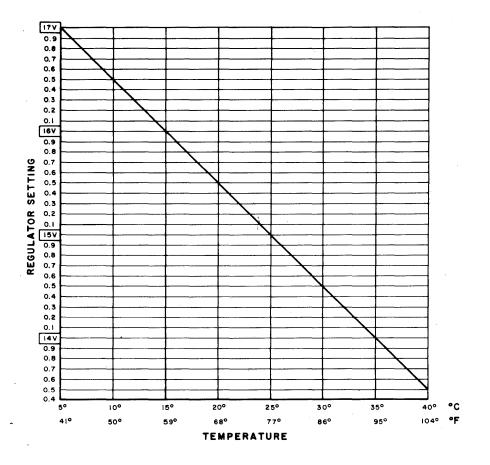

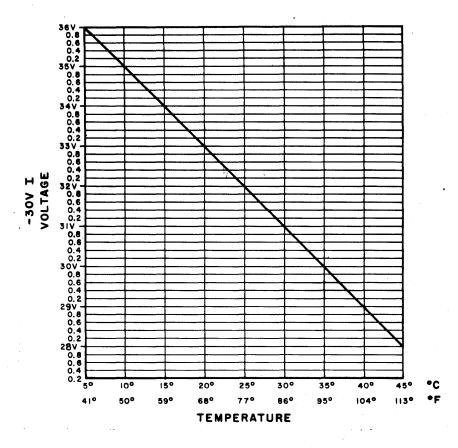

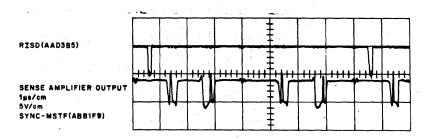

"X" and "Y" line selection is under control of the Address Register which can be of any octal value of 0000 thru 7777. For decoding purposes, the Address Register can be divided into four sections. Refer to Figure 3.2-2.