## FIELD ENGINEERING TECHNICAL MANUAL

INTRODUCTION

PRINCIPLES OF OPERATION

FUNCTIONAL DESCRIPTION-ELECTRONIC

FUNCTIONAL DESCRIPTION-MECHANICAL

# Burroughs B 471 DISK FILE ELECTRONICS UNIT

B

ASSEMBLY-DISASSEMBLY-ADJUSTMENTS

MAINTENANCE PROCEDURES AND AIDS

INSTALLATION PROCEDURES

> OPTIONAL FEATURES

PROPERTY OF AND TO BE RETURNED TO

## Burroughs

PRINTED IN U.S.A.

7-1-64

B 471.51

| FIELD ENGINEERING TECHNICAL MANUAL | B471.51  | 1.0-1   |

|------------------------------------|----------|---------|

| $\mathbf{\Psi}$                    | February | 1, 1965 |

## INDEX - SECTION I

## 1 INTRODUCTION

| 1.1 | General Description      | July | 1, | 1964          |

|-----|--------------------------|------|----|---------------|

| 1.2 | Equipment Specifications | July | 1, | 1964          |

| 1.3 | Physical Description     | Dec. | 1, | 19 <b>6</b> 4 |

| 1.4 | Glossary                 | Feb. | 1, | 1965          |

| 3 | FIELD ENGINEERIN                  | TECHNICAL | MANUAL | F       | B471,51 | 1.1-1 |

|---|-----------------------------------|-----------|--------|---------|---------|-------|

| U | FIELD ENGINEERING TECHNICAL MANUA |           | 1      | July 15 | 1965    |       |

#### 1.1 GENERAL DESCRIPTION

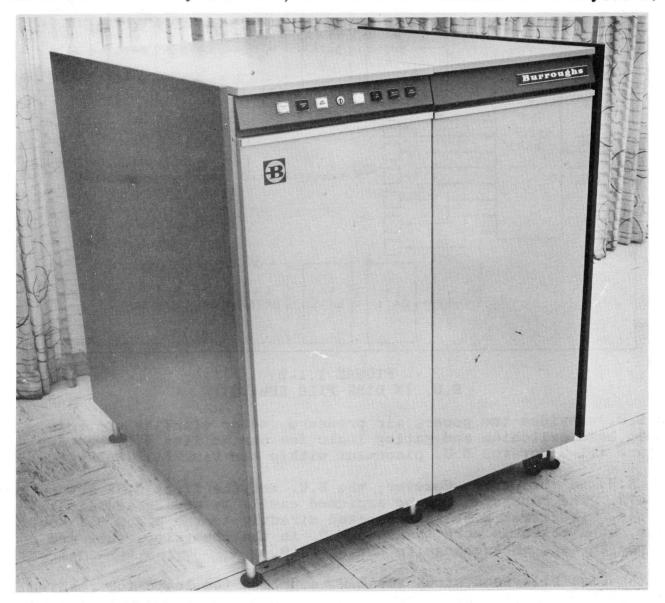

Figure 1.1-1 shows the Disk File Electronics Unit (E.U.) with one Disk File Storage Unit (S.U.). One E.U. can control from one to five S.U.'s, while up to ten E.U.'s may be connected to one Disk File Control Unit (D.F.C.U.). A maximum Disk File Subsystem will consist of one D.F.C.U., 10 E.U.'s, and 50 S.U.'s. Only one Disk File Subsystem can be controlled by the B200; the B5500 can control two Subsystems.

FIGURE 1.1-1 E.U. IN DISK FILE SUBSYSTEM

FIGURE 1.1-2 E.U. IN DISK FILE SUBSYSTEM

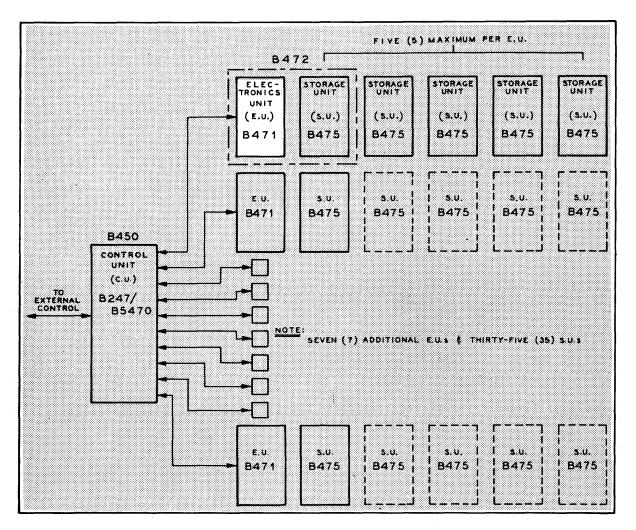

An E.U. provides the power, air pressure, motor starting controls, basic head switching and gating logic for one to five S.U.'s. See Figure 1.1-2 for the E.U. placement within the Disk File Subsystem.

The E.U. is the B471. However, the E.U. and the first S.U. are called a B472. The Subsystem can be expanded easily by adding additional S.U.'s. The first E.U. is connected directly to the D.F.C.U.; however, when there is more than one E.U. in the Subsystem, they are connected through an Exchange to the D.F.C.U.

In the Disk File Subsystem, the E.U. supplies the logic for reading and writing. Before an operation may take place, a segment (record) must be located on the disk. Each segment has an address which is read and compared with the desired address. When the correct segment address is found, the operation proceeds.

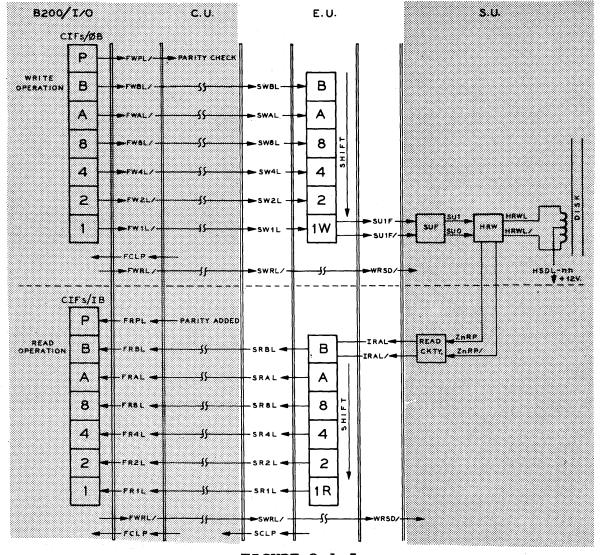

A write operation transfers characters from the Processor to the D.F.C.U., to the E.U., and finally to a disk in the S.U. The E.U. accepts a six-bit character from the D.F.C.U. parallel by bit, then

| M | FIELD ENGINEERING TECHNICAL M | B471.51 | 1.1-3 |

|---|-------------------------------|---------|-------|

| Y | FIELD ENGINEERING TECHNICKE   | July 1, | 1964  |

passes the character to the Module serially by bit since data is written serially on the disk.

In a read operation, the serial by bit information read from the disk is accumulated into a character in the E.U. and then sent to the D.F.C.U. and on to the Processor.

| ß | FIELD ENGINEERING TECHNICAL MANUAL | B471.51 | 1.2-1 |

|---|------------------------------------|---------|-------|

| Y |                                    | July 1, | 1964  |

#### 1.2 EQUIPMENT SPECIFICATIONS

Height ..... 53 inches Width ..... 23 inches Length ..... 45 inches Weight ..... 450 pounds

POWER REQUIREMENTS

208VAC or 230VAC from two phases and neutral. Maximum current, 63 amps for five S.U.'s.

Maximum cable length to D.F.C.U. - 50 feet.

FIELD ENGINEERING TECHNICAL MANUAL -----

| B471.51 |    | 1.3-1 |  |

|---------|----|-------|--|

| July    | 1, | 1964  |  |

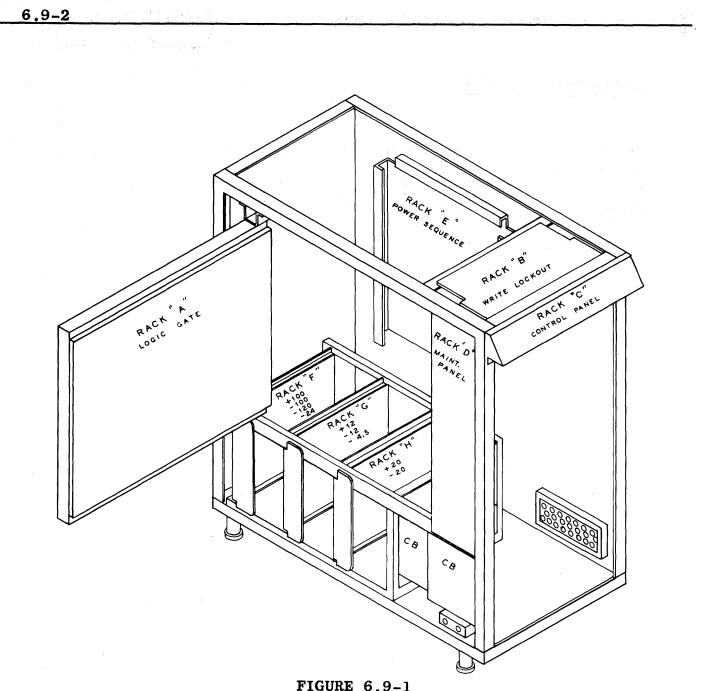

1.3 PHYSICAL DESCRIPTION

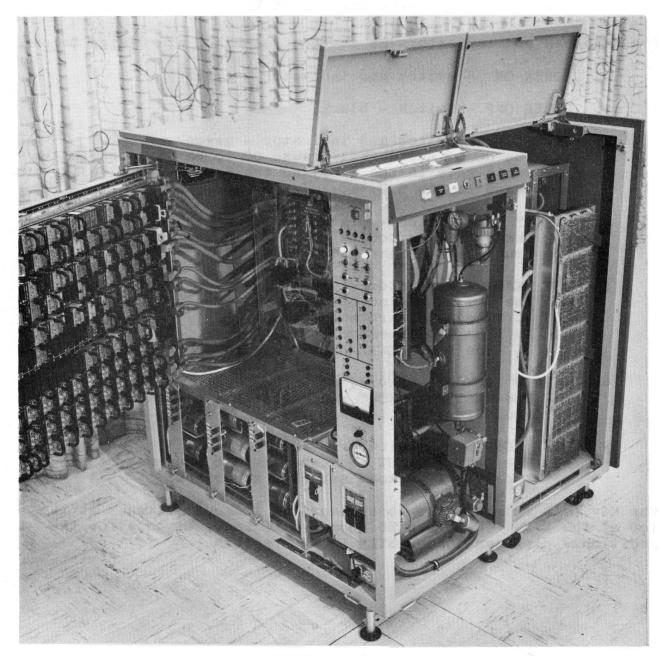

The Electronics Unit supplies the power and power controls for the Storage Units as well as providing the read/write logic. All operator controls are located on the front of the E.U. Figure 1.3-1 shows the left side of the E.U. The logic gate contains control logic for the E.U. and S.U.'s. The Maintenance Panel to the right allows the engineer quick access to information on the status of the E.U. and associated S.U.'s.

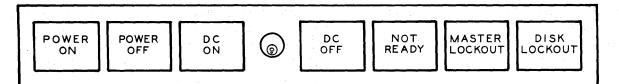

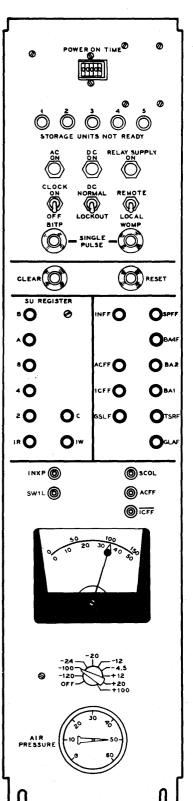

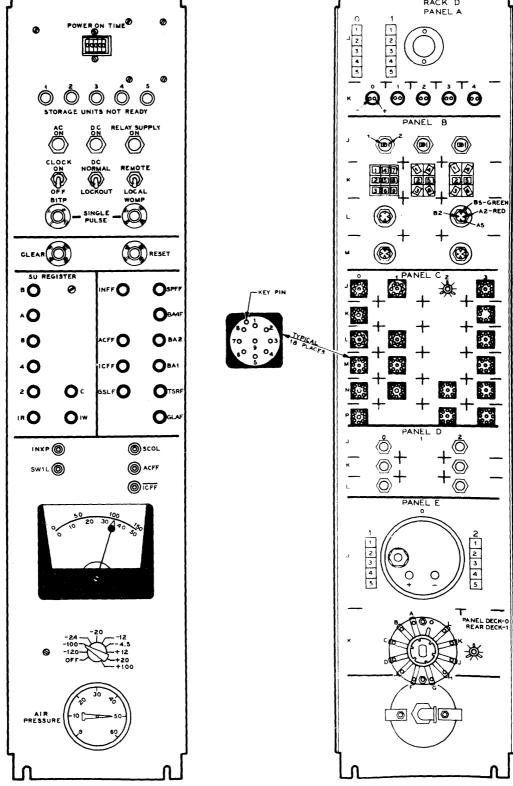

FIGURE 1.3-1 COMPONENT LAYOUT - E.U. The Control Panel on the E.U. (Figure 1.3-2) provides the operator controls for the E.U. and its Modules.

FIGURE 1.3-2 E.U. CONTROL PANEL

The switches and indicators on the Control Panel are listed below:

- 1. POWER ON switch and indicator green

- 2. POWER OFF switch black

- 3. DC ON switch and indicator green

- a. The DC ON switch will cause DC to be supplied to the logic gate in the E.U. and the S.U.'s and also fly the heads in the S.U.'s.

- 4. DC OFF switch black

a. The DC OFF switch retracts the heads and removes DC from the E.U. and the S.U.'s.

- 5. NOT READY indicator white

- a. The NOT READY indicator is lit when:

- 1. The heads are not flying.

- 2. The air pressure is not normal.

- 3. The E.U. LOCAL/REMOTE switch is in LOCAL.

- 6. MASTER LOCKOUT indicator red

a. The MASTER LOCKOUT indicator is lit when the MASTER LOCKOUT switch is thrown.

- 7. DISK LOCKOUT indicator red

a. The DISK LOCKOUT indicator is lit when any of the individual Lockout switches are thrown.

The Key Lock releases the cover over the Lockout switches at the top of the E.U. There are 20 separate Lockout switches for the individual disks and one MASTER LOCKOUT switch.

| M |                   | TECHNICAL | MANITAT | B471.51  | 1.3-3   |

|---|-------------------|-----------|---------|----------|---------|

| Ð | FIELD ENGINEERING | TECHNICAL |         | December | 1, 1964 |

The Maintenance Panel (Figure 1.3-3) has the following:

- 1. A POWER ON meter.

- 2. Five NOT READY indicators for the S.U.'s.

- 3. The AC ON and DC ON indicators which parallel POWER ON and DC ON on the Control Panel.

- 4. RELAY SUPPLY ON indicator.

- 5. The LOCAL/REMOTE switch.

- 6. DC LOCKOUT switch.

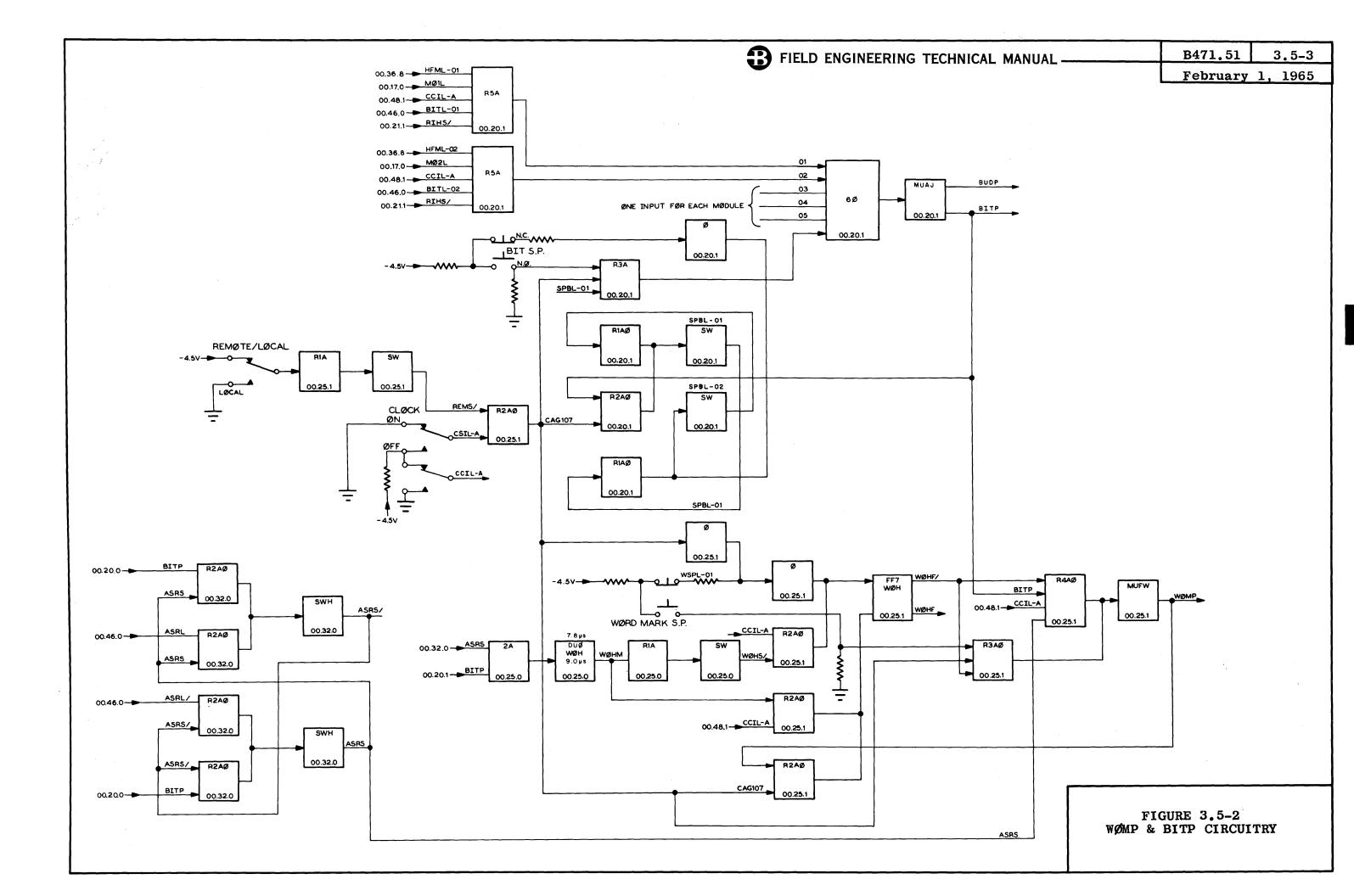

- 7. A CLOCK switch which must be on for normal operation. It is off for single pulsing with the BITP and WØMP buttons.

- 8. Indicators for flip-flops in the E.U.

- 9. Test points.

- 10. A voltmeter for monitoring the power supplies.

- 11. An AIR PRESSURE meter.

FIGURE 1.3-3 MAINTENANCE PANEL

Figure 1.3-4 shows a B471 and one B475 viewed from the front with the skins removed to show the physical location of many of the components.

Note the Winchester type connector mounted just above and behind the compressor. This is the connector for the logic cable from the associated D.F.C.U.

|                                                     |                                                                                                                | B471.51 1.4-1                             |

|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------|

|                                                     | GINEERING TECHNICAL MANUAL                                                                                     | B471.51 1.4-1<br>February 1, 1965         |

|                                                     |                                                                                                                |                                           |

| 1.4 GLOSSAR                                         | <u>Y</u>                                                                                                       |                                           |

| ACFF                                                | Action FF is on during a disk file acc<br>second revolution cross-over.                                        | ess except during a                       |

| ASRL<br>ASRL/                                       | Address Read Levels from the Storage M                                                                         | odule.                                    |

| ASRS<br>ASRS/                                       | Cross-coupled switches set by the Addr<br>BITP time. The outputs of the switche<br>when ICFF is off.           | ess Read Levels at<br>s are set into SUBF |

| BA1F<br>BA2F<br>BA4F                                | Address Count FFs. Normally only coun<br>indicates a Maintenance Segment addres                                | t to three. BA4F<br>s.                    |

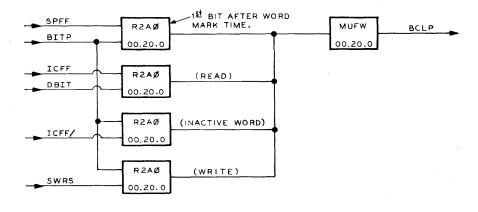

| BCLP                                                | Output of the Bit Clock Multi. Pulse seconds. Input is BITP or DBIT.                                           | width 150 nano-                           |

| BITL-01<br>BITL-02<br>BITL-03<br>BITL-04<br>BITL-05 | Bit pulse levels from the five possibl                                                                         | e modules.                                |

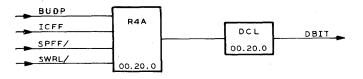

| BITP                                                | Delayed output of the Bit Pulse Multi.<br>nanoseconds. Input is BITL-nn. Produ<br>250 nanoseconds after input. |                                           |

| BSPL                                                | Bit Single Pulse Level. Effectively,<br>of the Bit Single Pulse switch to BITM                                 |                                           |

| BUDP                                                | Undelayed output of Bit Pulse Multi.<br>nanoseconds. Input is BITL-nn.                                         | Pulse width is 250                        |

| CBAS                                                | Count Address Count Switch. Negative count-up of BAnFs.                                                        | output causes a                           |

| CCEL-C                                              | Continuous Clock Enable Level. Makes when Clock Switch is ON.                                                  | CCIL-A negative                           |

| CCIL-A                                              | Continuous Clock Inhibit Level. Ground is OFF.                                                                 | d when Clock Switch                       |

| CSIL-A                                              | Clock Single Inhibit Level. Ground wh<br>ON. (This should be SCIL, See SCEL,)                                  | en Clock Switch is                        |

| CSUS                                                | Clears SUlFR, SU2F, SU4F and SU8F.                                                                             |                                           |

| 1.4-2                                        | n en 1997).<br>1919 - Charles Martin, and an an Antonio and an anna a                                                                                                                  |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                              |                                                                                                                                                                                                                                                |

| CS1L/<br>CS2L/                               | Characters per Segment Levels.<br>Both ground for 96 characters per segment.<br>1 negative and 2 ground for 240 characters per segment.<br>1 ground and 2 negative for 480 characters per segment.                                             |

| DBIT                                         | Delayed Bit Pulse from an adjustable multi. Output is a negative pulse 675 nanoseconds after BUDP. Used to fire BCLP while reading an active word.                                                                                             |

| DFSL/                                        | Disk Face Select Level. Negative to select a clock head<br>on the lower face of a disktracks 00=>49. Must be<br>opposite of DFSS.                                                                                                              |

| DFSS                                         | Disk Face Select Switch. Negative to select a clock<br>head on the upper face of a disktracks 50=>99. Must<br>be opposite of DFSL/.                                                                                                            |

| DISC-01/<br>DISC-02/<br>DISC-03/<br>DISC-04/ | Disk Select Levels. Ground to select disk "n" in each<br>Storage Module. Only one line ground at one time.<br>Derived from the decoded outputs of the Disk Switches.                                                                           |

| DIXP                                         | Delayed Index Pulse from DIXM. DIXM is 600 microseconds<br>and is set during second revolution cross-over. In case<br>the cross-over results in a Not Ready condition (non-<br>existent disk), DIXP resets INFF and produces one more<br>SCLP. |

| D01L/<br>D02L/<br>D04L/<br>D08L/<br>D16L/    | Disk Switch Levels inverted from Disk File Control address levels.                                                                                                                                                                             |

| ECCS                                         | Enable Character Clock Switch. If a BITP was missed,<br>ECCS ensures that SCLP cannot occur out of sync due to<br>the set of SUCF by the BITP that occurs at WØMP.                                                                             |

| FWLS-OR1<br>FWLS-OR2<br>FWLS-OR3             | File Write Lockout decoding.                                                                                                                                                                                                                   |

| GLAF                                         | Gain Latch FF latches the Gain Select circuit.                                                                                                                                                                                                 |

| GSLF                                         | Gain Select FF is set to the state of TSRF at each<br>Word Mark (SPFF).                                                                                                                                                                        |

| GSSL                                         | Gain Select Switch Level is negative to select low gain in the Module read amplifiers.                                                                                                                                                         |

|                                                      | GINEERING TECHNICAL MANUAL                                                                                                                       | B471.51     | 1.4-3    |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------|

|                                                      |                                                                                                                                                  | February    | 1, 1965  |

|                                                      |                                                                                                                                                  |             |          |

| HFML-01/                                             | Storage Module Ready Levels are positi                                                                                                           | ve when:    |          |

| HFML-02/                                             | a. Unit is Ready (disks up to speed,                                                                                                             | no touch ci | rcuits   |

| HFML-03/<br>HFML-04/                                 | triggered, air pressure up, heat e                                                                                                               |             |          |

| HFML-05/                                             | b. Unit is in LOCAL and not designate                                                                                                            | d.          |          |

| HSDL-00<br>thru<br>HSDL-99                           | Head Select Drive Level is positive to<br>Only one line can be positive at a tim                                                                 |             | ck "nn". |

| HSTL-00/<br>HSTL-10/<br>HSTL-20/<br>thru<br>HSTL-90/ | Head Select Tens Levels.                                                                                                                         |             |          |

| HSUL-00/                                             |                                                                                                                                                  |             | 2 2<br>P |

| thru<br>HSUL-09/                                     | Head Select Units Levels,                                                                                                                        |             |          |

| ICFF                                                 | Interlace Control FF is set during the reset during the inactive word or "idl                                                                    |             |          |

| INFF                                                 | Index FF is set during first and secon<br>overs. Its purpose is to "blank out"<br>segments and to index the continuation<br>on the correct word. | the mainten | ance     |

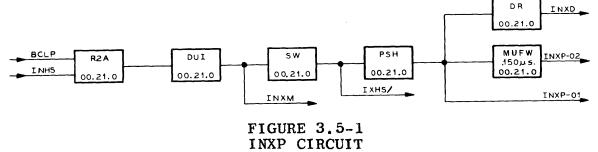

| INHS                                                 | Index Holdover Switch. The output lev<br>the holdover of IXHM and is used to pr<br>INXP in a second rveolution cross-over                        | oduce the p |          |

| INXP                                                 | Index Pulse. The output of the Index<br>when it times out. IXHM = BCLP • INHS.                                                                   | Holdover Mu | lti      |

| IRAL<br>IRAL/                                        | Information Read Levels from the Stora                                                                                                           | ge Module,  |          |

| IRAS<br>IRAS/                                        | Cross-coupled switches set by the Info<br>by BCLPs (DBIT). The switch outputs a<br>when ICFF is on.                                              |             |          |

| LØSW-01/<br>thru<br>LØSW-20/                         | Write Lockout Switches 1 through 20 fo<br>possible 20 disks. Ground level when                                                                   |             |          |

| MLØS/                                                | Master Lockout Switch. Ground level w<br>is locked out.                                                                                          | hen the who | le file  |

| MO1L                                                 |                                                                                                                                                  |             |          |

| MO2L                                                 | Module Designate Levels derived from t                                                                                                           | he five Dis | k        |

| MO3L<br>MO4L                                         | Switch Levels.                                                                                                                                   |             |          |

MO5L

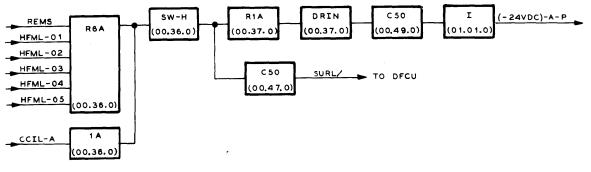

RDHM Read Delay Holdover Multi. 32 microsecond multi is set to inhibit BITPs during a second revolution cross-over when clock tracks are being changed. REMS / Remote Level. Ground when the LOCAL-REMOTE switch is in REMOTE. RIHS Read Inhibit Holdover Switch. Controlled by RDHM. Segment Address Read Level. Ground level to D.F.C.U. SARL/ after the Address Count FFs indicate an address has been read. SCEL-A Single Clock Enable Level. Negative when the Clock switch is off to enable the use of the single pulse button. SCLP Storage Clock Pulse (Character Clock) is a negative pulse for each character. Is also sent to D.F.C.U. to generate clock pulses. SCØL/ Segment Coincidence Level is ground from D.F.C.U. when address coincidence has been found. SCØS SCØL/ switched for gating logic in the E.U. Normally a ground level to enable a DC ON cycle in the SEQ-LOC-OUT E.U. When the DC Lockout switch is thrown, the ground level is removed inhibiting DC ON. SPBL-01 The output levels of two cross-coupled switches which, when in Single Pulse Mode, will provide a negative SPBL-02 pulse from SPBL-01 to produce one BITP for each depression of the single pulse button. Set by WØMP and cleared by the next BITP SPFF Space FF. (second space bit). Is the first "flag" bit for each word. SRAL Storage Read A Level. Negative level to D.F.C.U. when SUAF is set at Character Clock time (SCLP). SRBL SR8L Storage Read Levels. Negative level to D.F.C.U. when SR4L associated FF is set. SR2L SR1L SR1L-IND/ Storage Ready "n" Level Indicators. When ground, the SR2L-IND/ associated indicator will light. They correspond to SR3L-IND/ HFML-nn/ inputs. SR4L-IND/ SR5L-IND/

FIELD ENGINEERING TECHNICAL MANUAL -

| B471.51  |   | 1.4-5 |  |

|----------|---|-------|--|

| February | 1 | 1965  |  |

SSUD Shift SUnFs Driver,

SUIFR Storage Unit 1 Read FF.

SUIFW Storage Unit 1 Write FF.

SU2F SU4F

SU8F Storage Unit "n" FFs.

SUAF SUBF

- SUCF Storage Unit Character FF. This FF is set to indicate character time; that is, a complete character. It generates an SCLP.

- SUID Storage Unit Input Strobe. The character to be written is set into the SUnFs.

- SURL/ Storage Unit Ready Level. Ground level through a relay contact from SURS/. SURS/ is derived from HFML-nn, Clock On and REMOTE.

SW1L SW2L

SW4LStorage Write Levels. Negative level will cause theSW8Lappropriate SUnF to be set by SUID.SWAL

SWBL

TD1L

TD5L

- SWLL Storage Write Lockout Level. Negative level to D.F.C.U. when an attempt is made to write to a locked out disk.

- TD2L<br/>TD3LThreshold Detect Levels. Negative pulses from a Module<br/>set the gain control circuit for low gain.

- TSRF Threshold Store FF. Set by TDnL from a designated Module.

T01L/ T02L/ T04L/ T08L/ T10L/ T10L/ T20L/ T40L/ T01L/ T02L/ T40L/

| WICD                           | Write Information Control Level. Negative during the active word to enable information to be written on the selected track.                                                     |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WØHF                           | Word Mark FF. Set by the Word Mark Multi. Reset by<br>WØHS/ (WØHM after time out). Used to inhibit the<br>generation of WØMPs by flux changes when an address is<br>being read. |

| wØHM                           | Word Mark Multi. The multi has 7.8 microseconds duration<br>and is fired and held over by any flux changes read from<br>the address track.                                      |

| WØHS/                          | Word Mark Switch. The switched cutput of WØHM.                                                                                                                                  |

| WØMD                           | Word Mark Driver. The negative output is the Word Mark pulse to the D.F.C.U.                                                                                                    |

| WØMP                           | Word Mark Pulse. Generated by a flux change in the address track corresponding to the beginning of each word.                                                                   |

| WRSD/                          | Write Storage Level. When positive, indicates a write operation is to be performed.                                                                                             |

| WSPL-01                        | Word Single Pulse Level. The output of the Word Single Pulse switch.                                                                                                            |

| Z <b>Ø1L/</b><br>Z <b>Ø2L/</b> | Zone 1 and 2 Levels from the D.F.C.U. These are decoded to form three levelsZ $01L-01/$ , Z $02L-01/$ and Z $03L-01/$ which are used to select the correct zone.                |

| B FIELD ENGINEERING TECHNICAL MANUAL | B471.51  | 2.0-1   |

|--------------------------------------|----------|---------|

| •                                    | February | 1, 1965 |

## INDEX - SECTION II

### 2 PRINCIPLES OF OPERATION

| 2.1 | Electronics | Unit | Feb. | 1, | 1965         |

|-----|-------------|------|------|----|--------------|

| 2.2 | Disk Format |      | Dec. | 1, | 19 <b>64</b> |

| B471.5 | 1   | 2.1 - 1 |

|--------|-----|---------|

| July   | 15, | 1965    |

#### 2.1 ELECTRONICS UNIT

#### GENERAL OPERATION

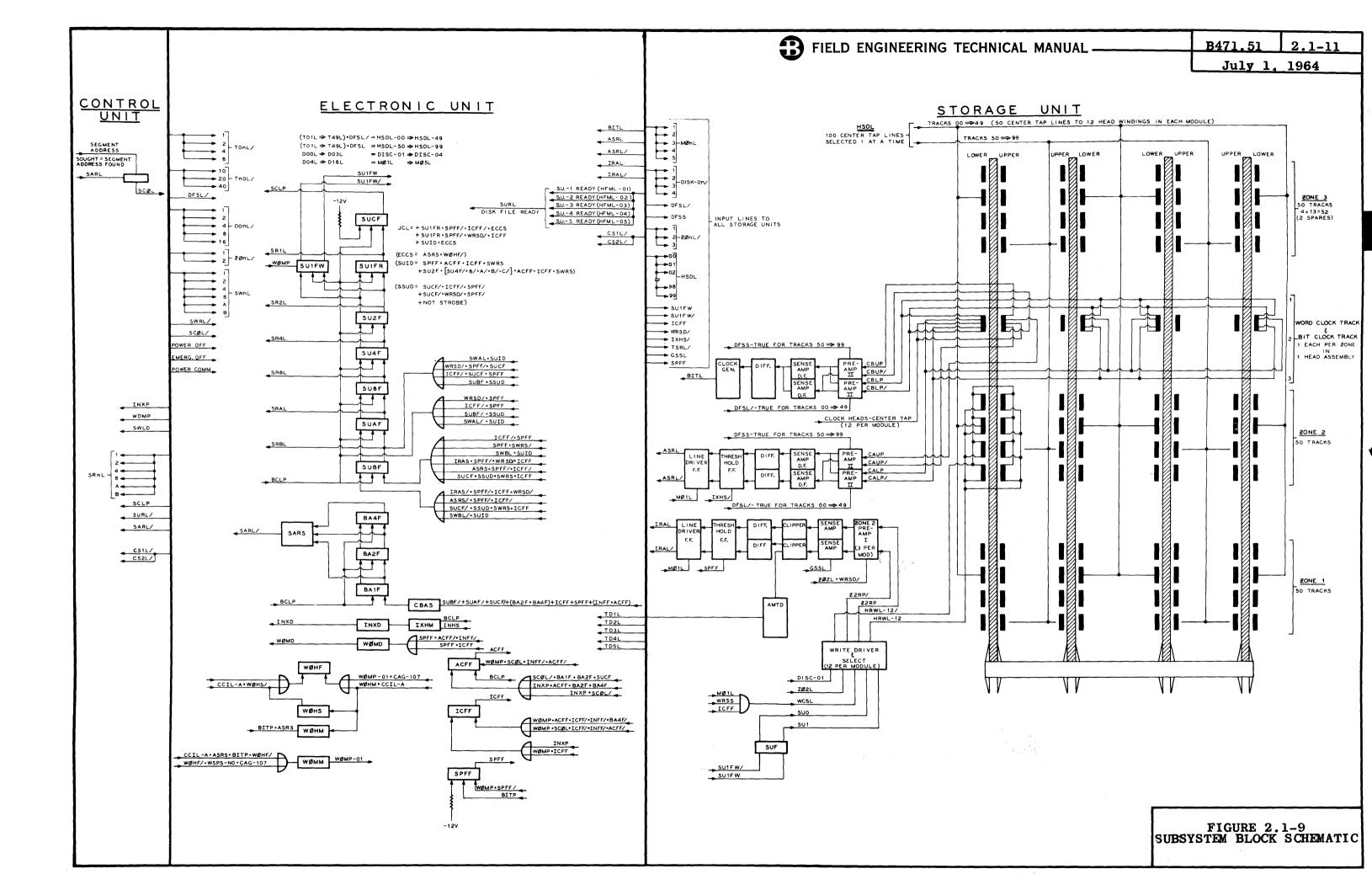

The Disk File Subsystem provides the B200 and B5500 systems with a very large capacity storage device with rapid access to any record. In the Subsystem the Electronics Unit provides the local logical control of up to five Storage Modules.

To write on a disk, first a specified area is identified by its unique address and then the six-bit BCL characters are written serially by bit in that area. The B5500 can write in the binary mode if required. All characters may be written.

To read from the disk, the area to be read must first be located by head selection and address comparison. Then the serial bit information is assembled into characters which are transferred to the Processor one at a time.

Head selection entails the selection of the Module, disk, face, zone and track. Each information track is found in three zones so three heads are designated. Each zone has unique clock tracks and an address will be read for each segment in the selected zone. Once the required segment is located, the read or write operation begins. The E.U. provides logic for head selection, clocking, information read and information write.

#### HEAD SELECTION

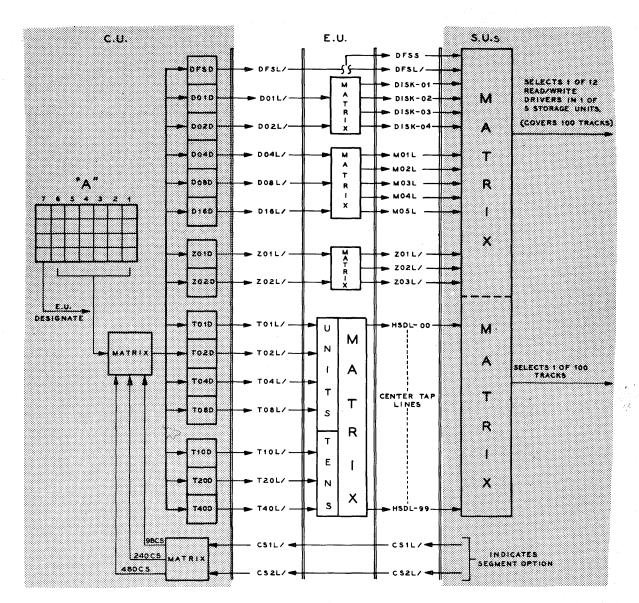

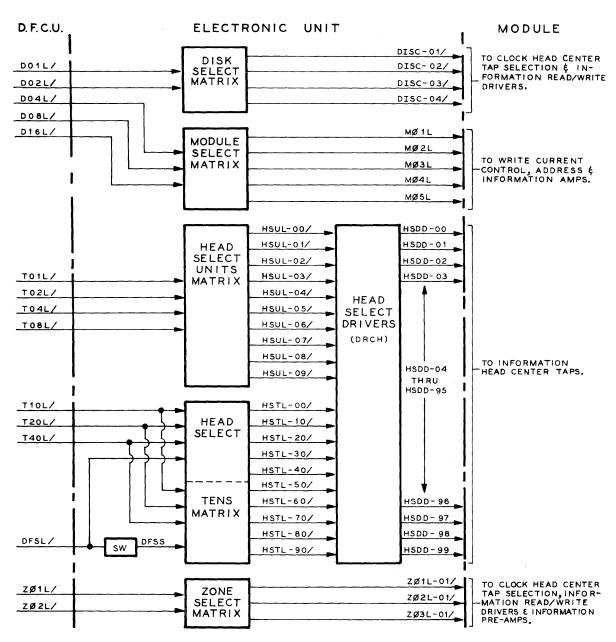

An address is shifted into the A Register in the D.F.C.U. by the Processor. This is the unique address of one segment; 96, 240 or 480 characters on one side of one disk, in one Module, in one E.U. The decoded output levels of A Register are sent to the E.U. which further decodes them into head select lines to the Module and disk face. The levels from the D.F.C.U. are: (Refer to Figure 2.1-1.)

- 1. The DnnL's which select one Module of five and one of four disks in that Module.

- 2. Disk Face Select Level (DFSL/) to select the lower or upper face.

- 3. The ZnnL's which select the 100 heads in one zone (both sides of the disk).

- 4. The TnnL's which select one of 50 tracks in each zone.

The E.U. decodes the fifty TnnL's and DFSL/ into 100 center tap levels called HSDL's to enable the center taps of the information heads.

2.1 - 2

FIGURE 2.1-1 E.U. IN THE DISK FILE SUBSYSTEM

Each HSDL enables 12 heads; one head in each zone of one face of each disk. With the 480 option, the information head enabled in zone 1 can read and write segments 0 - 11. The corresponding head in zone 2 can read and write segments 12 - 27 and the enabled head in zone 3 can read and write segments 28 - 49. The opposite face on the disk will have segments 50 - 99. Refer to Figure 2.1-2.

The ZnnL's and Disk-nn will select the 100 heads in one zone of one disk (both faces). These levels will also enable the center taps of the four clock heads for that zone of the disk (both faces). The desired face is selected by DFSL/ and DFSS.

| B471.51  |    | 2.1-3 |

|----------|----|-------|

| December | 1, | 1964  |

|      | 480 OPTION 2  |        | 240 OPTION |           | <b>96</b> OI | PTION      |                   |

|------|---------------|--------|------------|-----------|--------------|------------|-------------------|

| ZONE | CW/CCW FACE   |        | ONE FACE   | DIS       | К 1          | DISK 2     |                   |

| L    |               |        |            | CW FACE   | CCW FACE     | CW FACE    | CCW FACE          |

| 1    | 0->11         | 50-⇒61 | 0->23      | 0 -> 59   | 250→309      | 750 -> 809 | 500 -> 559        |

| 2    | 12-27         | 62-+77 | 24 -> 55   | 60 -> 139 | 310->389     | 810 -> 889 | 560 -> 639        |

| з    | 28-249 78-299 |        | 56 - 99    | 140 249   | 390-++499    | 890 -> 399 | <b>64</b> 0 → 749 |

FIGURE 2.1-2 SEGMENT ADDRESSES BY OPTION

#### ADDRESS SEARCH

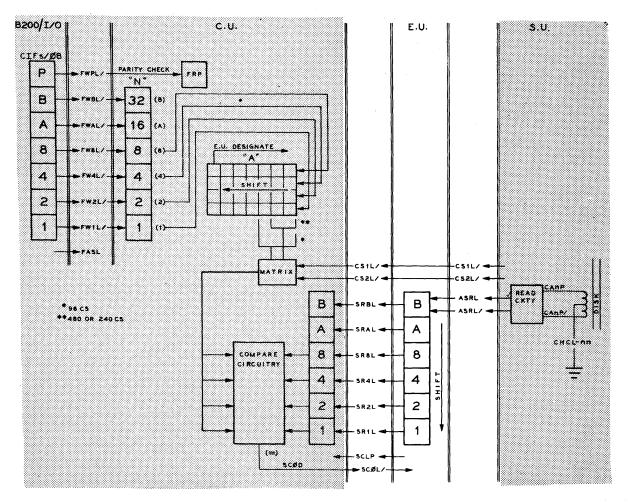

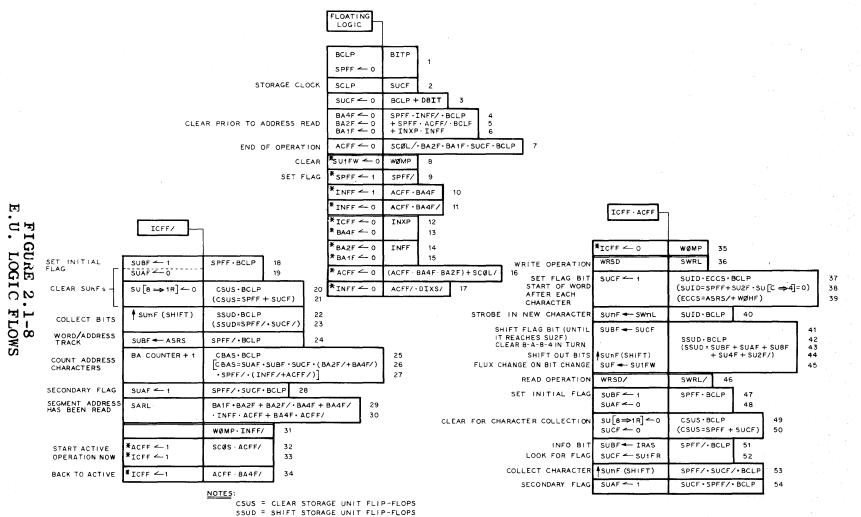

The selected Word Mark clock head reads three digit addresses from the Word Mark track and sends them serially by bit, serially by digit, to the E.U. From the point of view of timing, these addresses are read during the word time preceding the first word of the segment. When an address is read by the Word Mark clock head, a new segment will pass under the selected information head after the next Word Mark. The segment address is sent back to the D.F.C.U. to be compared with the address in the A Register. If the segment address compares, Segment Coincidence Level (SCØL/) is sent to the E.U. to indicate that the segment has been found. The E.U. will now go into an active read or write operation. Figure 2.1-3 shows the block diagram of the Address Search operation.

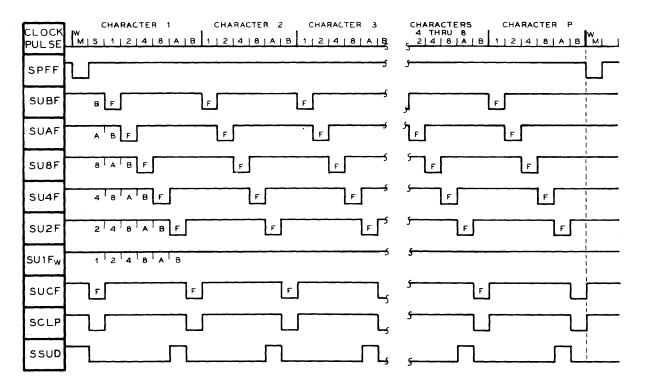

The selected Bit clock track in the S.U. will generate clock pulses which are sent to the E.U. The E.U. uses these Bit pulses for all clocking purposes. Information and addresses are handled in similar ways by the E.U.; that is, either information levels or address levels are strobed into the Stack-Up Register (SUnF's) by Bit pulses. When a complete character has been assembled, it is sent to the D.F.C.U. parallel by bit.

The Word Mark track generates Word Mark pulses (WØMP) as well as segment addresses. The Bit track generates timing for writing or reading one bit at a time. Each zone has its own Word Mark and bit tracks since, to maintain a reasonably constant packing density in all three zones, the frequency must vary. There are a total of six clock tracks on each disk face located between zone 2 and zone 3.

Refer to Figure 2.1-8 for the E.U. logical flow diagram,

The Interlace Control Flip-Flop (ICFF) is the control to determine active and inactive words. ICFF is off until segment coincidence is found. After SCØL to the E.U., ICFF is complemented by each WØMP until the write or read operation is completed. When ICFF is off, the Word Mark track (ASRL) is scanned for an address (inactive word). When ICFF is on, reading or writing is being done during the active word.

The S.U. Register is comprised of seven flip-flops -1, 2, 4, 8, A, B, C. The function during write is to receive a character at a time from

FIGURE 2.1-3 INFORMATION FLOW - ADDRESS SEARCH

the D.F.C.U. and send it serially by bit to the S.U. During read, the bits are stacked up in the S.U. Register until the character is complete and then it is sent to the D.F.C.U.

Address Read Level, ASRL, will produce a WØMP (Word Mark Pulse) with the following logic:

$WOMP = ASRS \cdot WOHF / \cdot BITP$

ASRS is also the segment address input to the E.U. after WØMP has been recognized and WØHF inhibits WØMP being generated by address information.

WØMP triggers the Space Flip-Flop (SPFF). SPFF signifies the beginning of a word, either active or inactive.

SPFF = WØMP • SPFF/

| FIELD ENGINEERING TECHNICAL MANUAL | B471.51  | 2.1-5   |

|------------------------------------|----------|---------|

|                                    | December | 1, 1964 |

The address bits read from the Word Mark track are shifted into SUBF. Refer to Figure 2.1-4. Notice that SPFF starts the operation by clearing the S.U. Register and placing a flag bit in SUBF. The flag bit is circulated through the SUNF's and each time it shifts into SUCF, an SCLP is sent to the D.F.C.U. to indicate a complete character has been stacked up.

#### SCLP = SUCF

FIGURE 2.1-4 ADDRESS DIGIT ACCUMULATION

Reading continues after this transfer so that the next bit will again set or reset SUBF. Since the flag bit must precede the character, SUAF is set.

SUBF = ASRS · SPFF/ · ICFF/ SUAF = ICFF/ · SPFF/ · SUCF

Three address characters will be read for a normal address. The A and B bits will always be ones to indicate an address digit. (Since the numeric part of the digit is in binary code, the A and B bits must be used to indicate a zero.) Each address character causes a count up of the BA Flip-flops. BAnF's serve as a counter for the number of address characters read. Address coincidence cannot be made until three characters have been compared. The addresses of the maintenance segments have more than three digits; therefore, BA4F will be set to indicate a maintenance function.

When three characters have been read, Segment Address Read Level (SARL) is sent to the D.F.C.U. to indicate a complete address.

SARL = BA1F • BA2F

If segment coincidence is found, then two SCLP's later, SCØL is sent to the E.U. to initiate action on the next WØMP.

With SCØL true, the next WØMP sets ICFF and ACFF (Action). ACFF will remain set during the Read or Write operation unless there is a change of track. ICFF is complemented with each WØMP for the inactive words interlaced with the active words.

FIGURE 2.1-5 READ/WRITE INFORMATION FLOW

| A | FIELD ENGINEERING TECHNICAL MANUAL | B471.51 | 2.1-7  |

|---|------------------------------------|---------|--------|

| U |                                    | July 15 | , 1965 |

#### INFORMATION WRITE

Refer to Figure 2.1-5 for the READ/WRITE Information Flow.

The level SWRL from the D.F.C.U. will denote a Write operation. SWRL/ indicates a Read operation. With SWRL, ACFF • ICFF true, WRSD/ will be false to the S.U. for a Write operation.

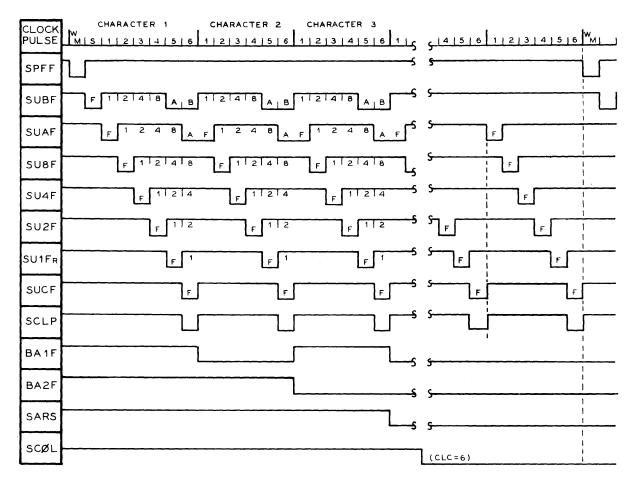

During a Write operation, the S.U. Register will receive a character at a time from the D.F.C.U. Each bit pulse shifts the character through the Register. SUlFw replaces SUlFr during a Write operation. The output of SUlFw will condition the Bit flip-flop in the S.U. to write a one or a zero on the disk. Refer to the timing diagram, Figure 2.1-6.

#### FIGURE 2.1-6 WRITE TIMING

With SPFF, ACFF, ICFF and a Write operation, the first character from the D.F.C.U. is strobed into the S.U. Register and a flag bit is set into SUCF by Storage Unit Input Strobe Driver (SUID).

SUID = SPFF • ACFF • ICFF • SWRS SUNF - SWNL'S = SUID • BCLP SUCF = SUID • BCLP

With the S.U. Register loaded, the next BITP will write the state of SUIFw on the disk. The next BCLP will shift the S.U. Register; SUCF to SUBF, SUBF to SUAF, etc.

SSUD = SUID/

The flag bit is also shifted through the S.U. Register. When it reaches SU2F, the last bit of the character is in SULFw being written on the disk. The next BCLP will strobe in the next character from D.F.C.U. and set a new flag bit in SUCF.

$SUID = SU2F \cdot SU4F / \cdot SU8F / \cdot SUAF / \cdot SUBF / \cdot SUCF /$

The Write operation will continue until from 1 to 10 segments have been written when the B200 Processor is connected. The B5500 is capable of writing from 1 to 63 segments with one instruction.

#### INFORMATION READ

The Read operation is similar to the Address Search operation previously discussed. Instead of ASRL, the Information Read Level, IRAL, which is conditioned by the information track, is strobed into SUBF.

#### FIGURE 2.1-7 READ TIMING

The Information Read Timing Chart, Figure 2.1-7, starts with the flag bit set into SUBF and the remaining flip-flops being cleared. SUlFr replaces SUlFw for Read. The first BCLP after SPFF has been reset will place the first information bit into SUBF and will shift the S.U. Register.

SUBF = IRAS • SPFF/ • WRSD/ • ICFF

|   | FIELD ENGINEERING TECHNICAL MANUAL | B471.51  | 2.1-9   |

|---|------------------------------------|----------|---------|

| U |                                    | December | 1. 1964 |

Since the information was written on the disk with word interlace, it must be read in a similar manner. ICFF is set to read the information word and then reset to allow reading of the address track.

As each bit is read off the disk, the S.U. Register is shifted. When the flag bit reaches SUCF, a complete character has been assembled in the S.U. Register and SUCF gates the character to the D.F.C.U.

$SRnL = SUnF \cdot SUCF$

The Read operation will continue until the number of segments specified have been read.

\* = UNCLOCKED

CBAS = COUNT ADDRESS CHARACTERS SUID = STORAGE UNIT FLIP-FLOP INPUT STROBE

ECCS = ENABLE CHARACTER CLOCK

N

01

FIELD ENGINEERING TECHNICAL MANUAL ------

| B471.51  |    | 2.2-1 |

|----------|----|-------|

| December | 1, | 1964  |

#### 2.2 DISK FORMAT

Information on the disk is organized in words and segments. One word consists of 8 characters plus a longitudinal parity character. There is a two bit space between words so that a word time is a total of 56 bit pulses. During a write or read operation an active word is followed by an inactive word. Interlace is controlled by ICFF. The words from two segments are interlaced to allow the address track to be scanned during the inactive word. The bit frequency on the disk varies from 1 mc in zone 1 to approximately 1.8 mc in zone 3.

The segment layout for a track in zone 1 using the 480 option is as follows:

|   |                                          |       |       |       |        |        |            | -        |

|---|------------------------------------------|-------|-------|-------|--------|--------|------------|----------|

|   |                                          | 4 4 7 |       |       |        |        | MS DEAD    | /        |

|   | 0 - 0                                    | 1 + / | 2 + 8 | 3 + 9 | 4 + 10 | 5 + 11 | ILLOS BACE |          |

|   |                                          |       |       |       |        | 1      | 1+2 SPACE  | 1        |

| • | أنتي مستبر المسبرة لتبري الأنابي التراجع |       |       |       |        |        |            | <b>a</b> |

Each word of segment 0 is followed by a word of segment 6, completely interlacing the two segments. The following diagram depicts this word interlace:

| WORD    | 59 | WORD | 60 | WORD | 60 | WORD | 1 | WORD 1 | WORD 2 |

|---------|----|------|----|------|----|------|---|--------|--------|

| <br>SEG | 6  | SEG  | 0  | SEG  | 6  | SEG  | 1 | SEG 7  | SEG 1  |

The address for each segment is written in the word mark track during the word time preceding the first word of that segment. The following diagram illustrates this:

NOTE

The address digits are in REVERSE order.

| WØMP    | 1       | 100     | 700    | 1 1    | ]      |

|---------|---------|---------|--------|--------|--------|

| WORD 59 | WORD 60 | WORD 60 | WORD 1 | WORD 1 | WORD 2 |

| SEG 6   | SEG 0   | SEG 6   | SEG 1  | SEG 7  | SEG 1  |

It takes two revolutions of the disk to completely read or write one track. On each revolution a dead space is encountered which is a physical reference on the disk. One maintenance segment can be operated on in each revolution. The first revolution may read segments 0 through 5 or MS1, and the second revolution will read segments 6 through 11 or MS2.

Preceding the dead space on each track are the two maintenance segments which are available to the engineer for checking purposes. The maintenance segments are 96 characters long regardless of the S.U. option.

Printed in U.S.A.

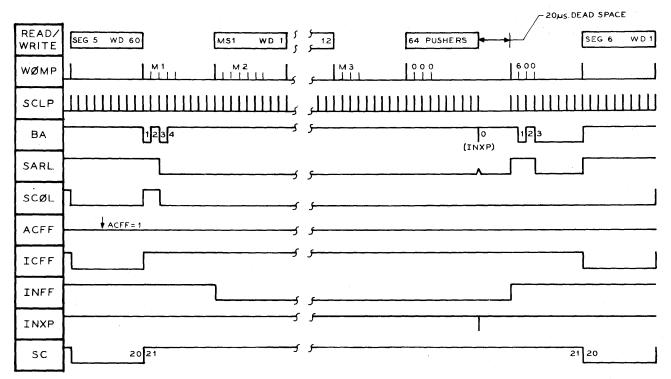

When a read or write operation is in progress, the dead space and maintenance segments must be taken into account. Refer to Figure 2.2-1 for first revolution crossover. The figure reflects the 480 option, though the action is similar for the 240 and 96 options.

#### FIGURE 2.2-1 FIRST REVOLUTION CROSSOVER

Assume the operation has proceeded through the last word of segment 5 (the 6th segment). The next WØMP signals the start of an inactive word during which the address for Maintenance Segment 1 will be read. The address consists of four binary 10's. The 4 character address results in BA4F being set. INFF will be set by the next WØMP to inhibit further action during the maintenance segments and dead space. BA4F is cleared by INXP, which is generated by the absence of BITPs.

#### INFF = WOMP . ACFF . BA4F

Notice that ACFF remains set to indicate further action is required on this track. INFF is reset by the first WØMP after dead space so that ICFF will not be set until the second word after the dead space. This second word is the first word of segment 6.

$$ICFF = WOMP \cdot INFF/$$

SCLP pulses occur each time SUCF is set with the flag bit. The flag bit circulates until cleared by WØMP; therefore SCLP pulses are produced up to the dead space. Sixty four extra bit pulses occur after the last word of MS2 and before the dead space occurs. They are called "pusher" pulses and create SCLPs for the pseudo word time during which is read the address of the first segment after the dead space.

| FIELD ENGINEERING TECHNICAL MANUAL | B471.51  | 2.2-3   |

|------------------------------------|----------|---------|

|                                    | December | 1, 1964 |

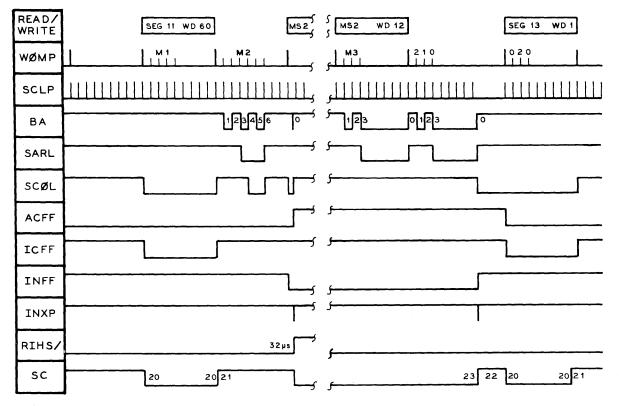

The crossover on the second revolution involves the selection of another information head and different clock tracks. The "A" Register in the DFCU is counted up as each segment is completed. After two revolutions on one track, the address in the "A" Register will activate new head select lines. The new address may be on another disk face or disk, so dead space is used to ensure the logic stays in sync.

FIGURE 2.2-2 SECOND REVOLUTION CROSSOVER

Refer to Figure 2.2-2. After the last word of the last segment on the track the six digit (all binary 12's) MS2 address is read during the inactive word. The 6 digit address will set BA4F. BA2F to indicate a change of track. INFF is set by WØMP and, with BA4F and BA2F, enables a simulated INXP to be generated. This INXP will reset ACFF and the "A" Register counts up the segment address and a new head is selected. DIXM is fired by INXP. BITPs are inhibited by RIHS/ to prevent extraneous pulses occurring during the clock track change.

#### RIHS/ = RDHM (32 microseconds) • IXHS/ • DIXM

With INFF on, no further action can take place until it is reset by INXP. This will occur when the newly selected head reads into dead space. SCØL from the DFCU will permit the first WØMP after dead space to set ACFF and ICFF, and the operation will continue in sequence on the new track.

| B471.51      | 3  | .0-1 |

|--------------|----|------|

| <br>February | 1, | 1965 |

## INDEX - SECTION III

## **3 FUNCTIONAL DESCRIPTION - ELECTRONIC**

| 3.1 | Disk File Electronics and Storage Units Power<br>Sequencing | Feb. | 1, | 1965         |

|-----|-------------------------------------------------------------|------|----|--------------|

| 3.2 | Cabling                                                     | July | 1, | 19 <b>64</b> |

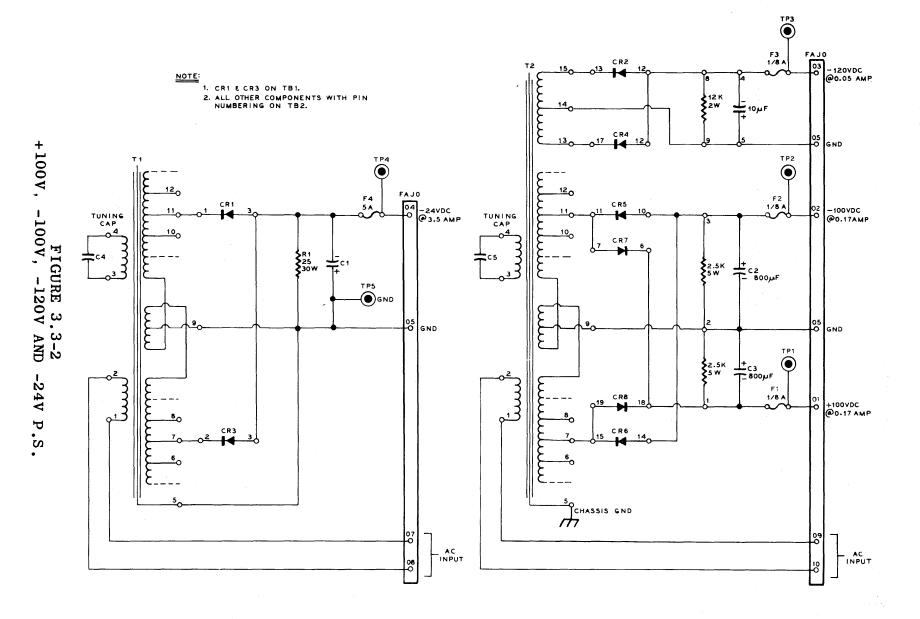

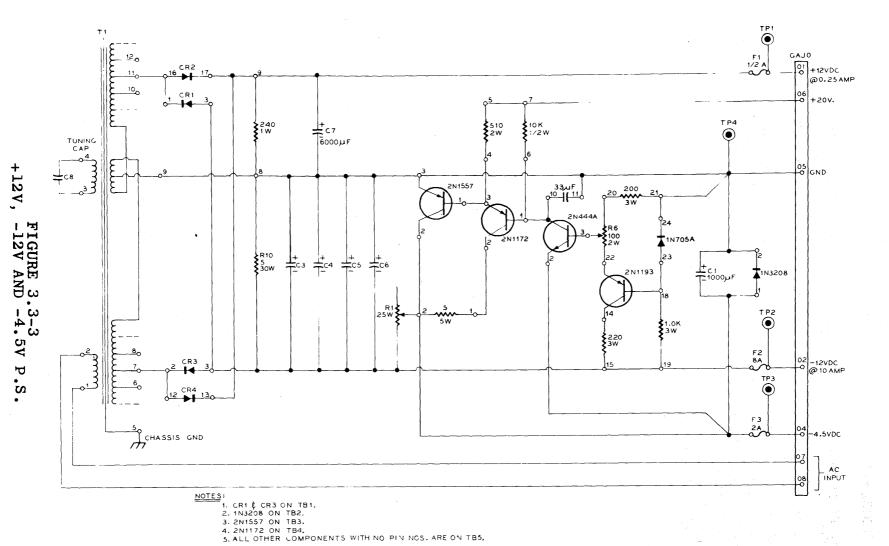

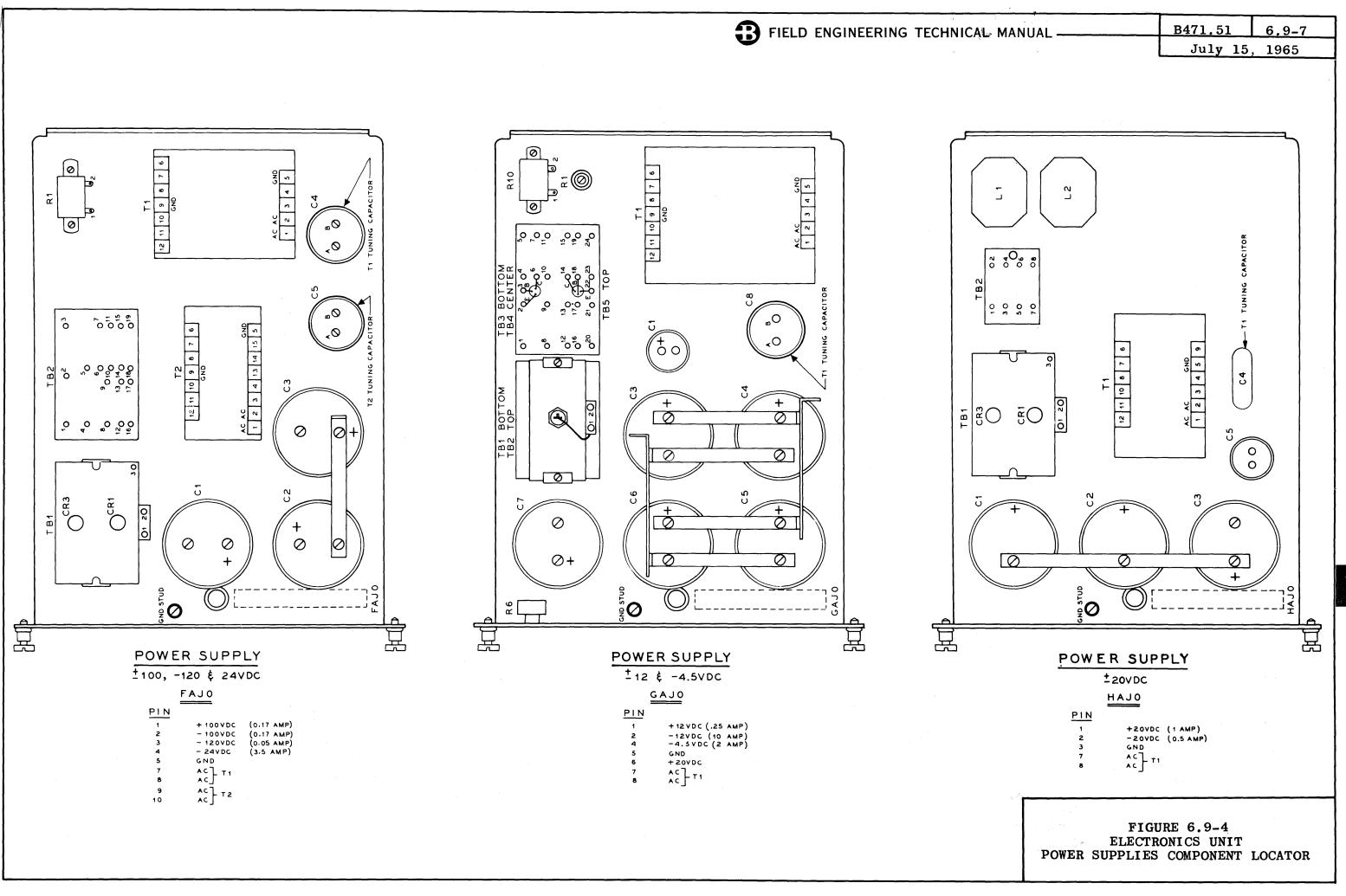

| 3.3 | Power Supplies                                              | Feb. | 1, | 1965         |

| 3.4 | Addressing                                                  | July | 1, | 1964         |

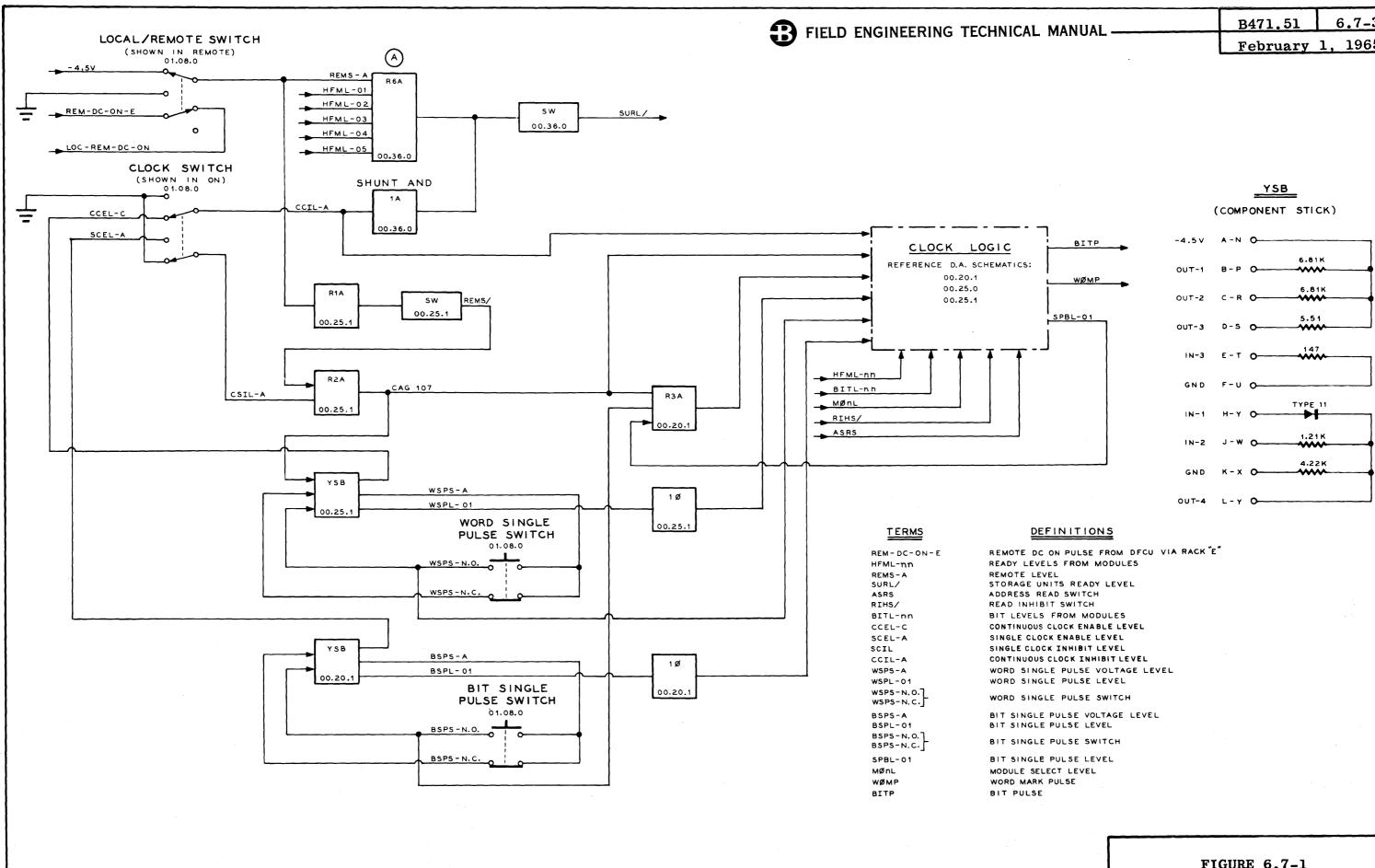

| 3.5 | Clocking                                                    | Feb. | 1, | 1965         |

| 3.6 | Ready Circuits                                              | July | 1, | 1964         |

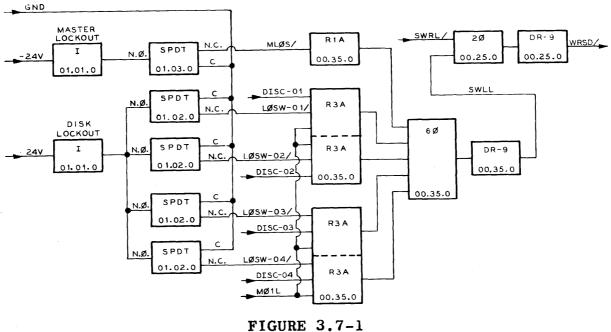

| 3.7 | Write Lockout                                               | July | 1, | 19 <b>64</b> |

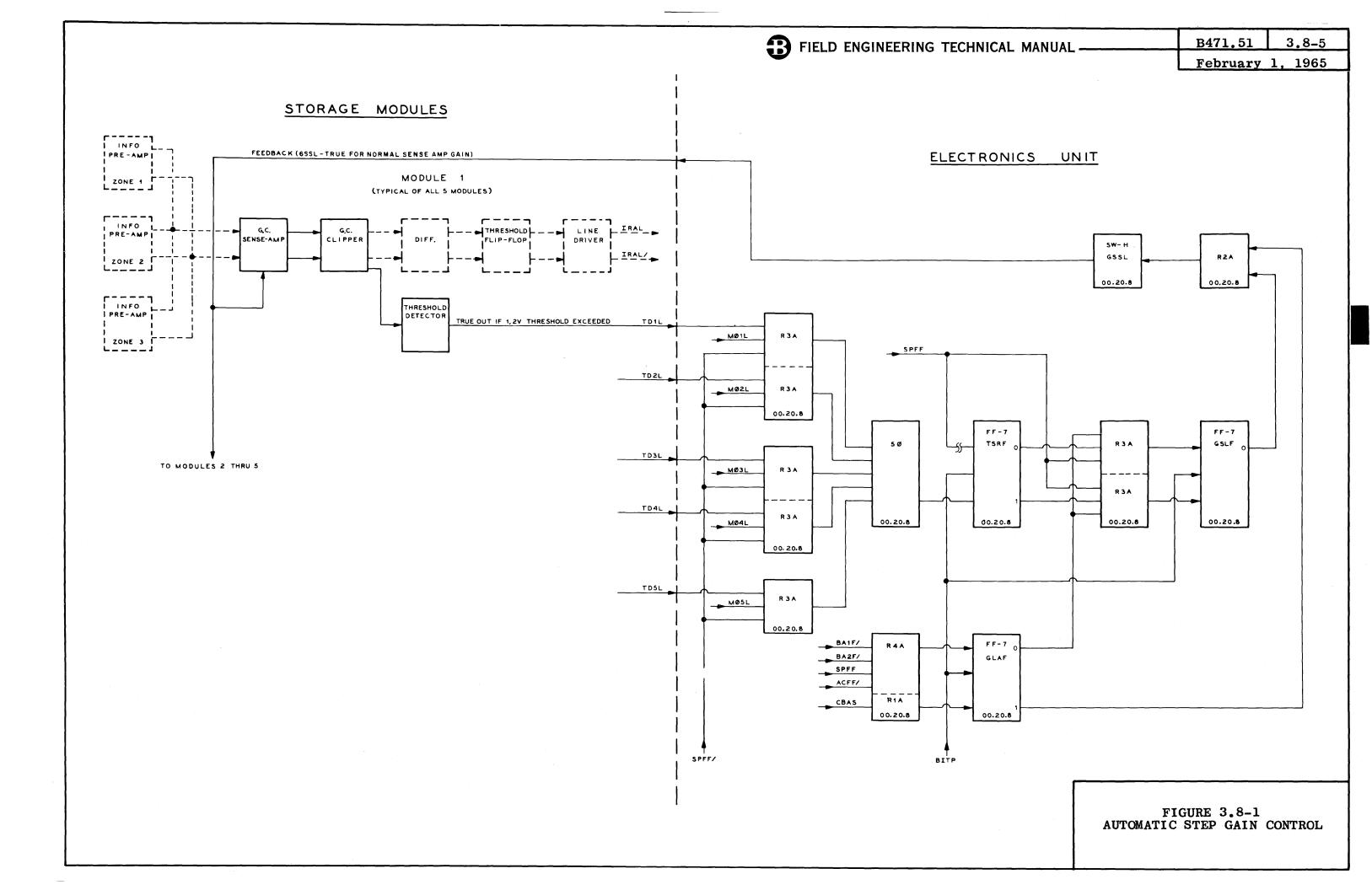

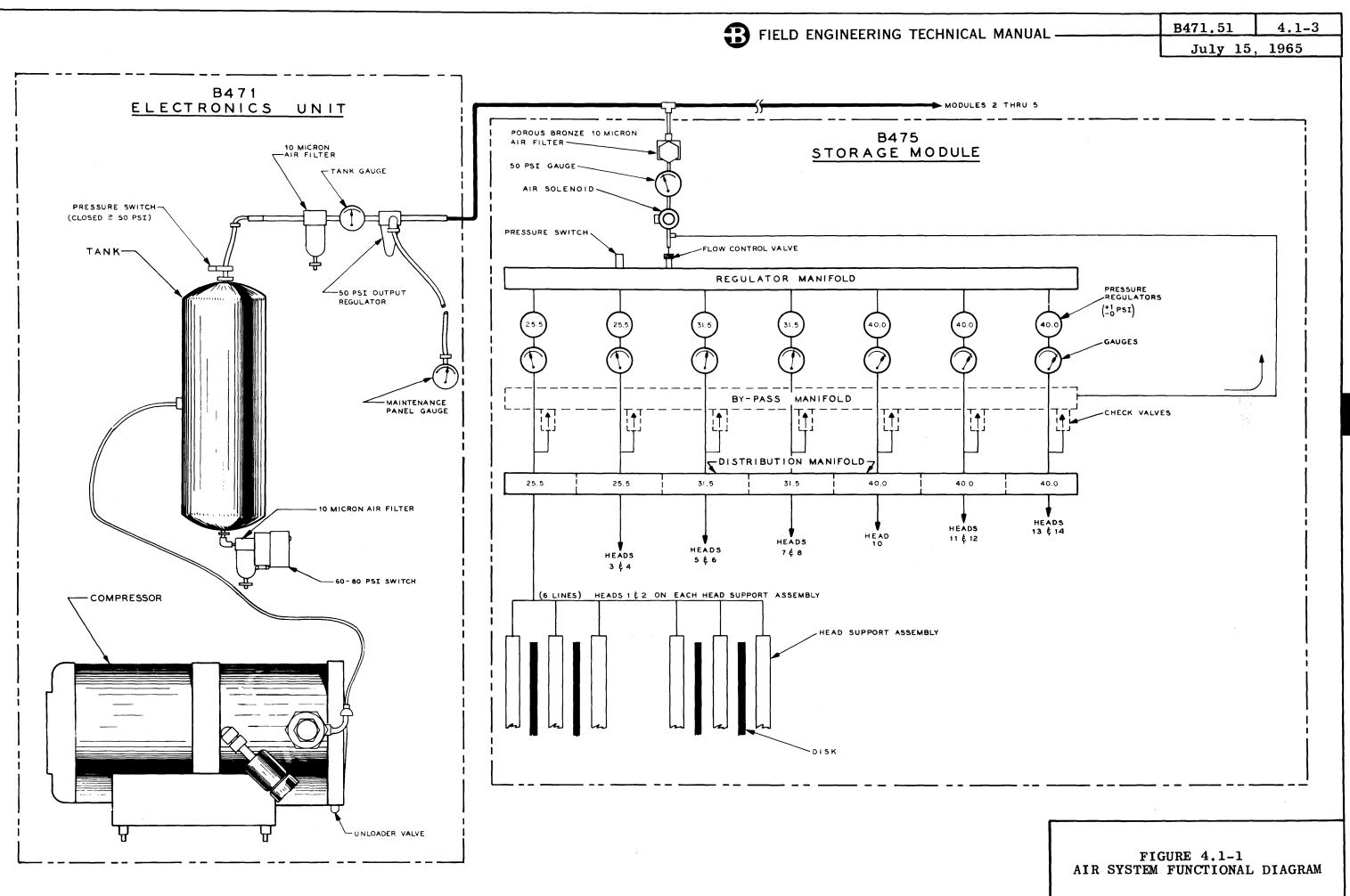

| 3.8 | Read Signal Automatic Step Gain Control                     | Feb. | 1, | 1965         |

| Γ | B471.51 | 3.1-1  |

|---|---------|--------|

| Ι | July 15 | , 1965 |

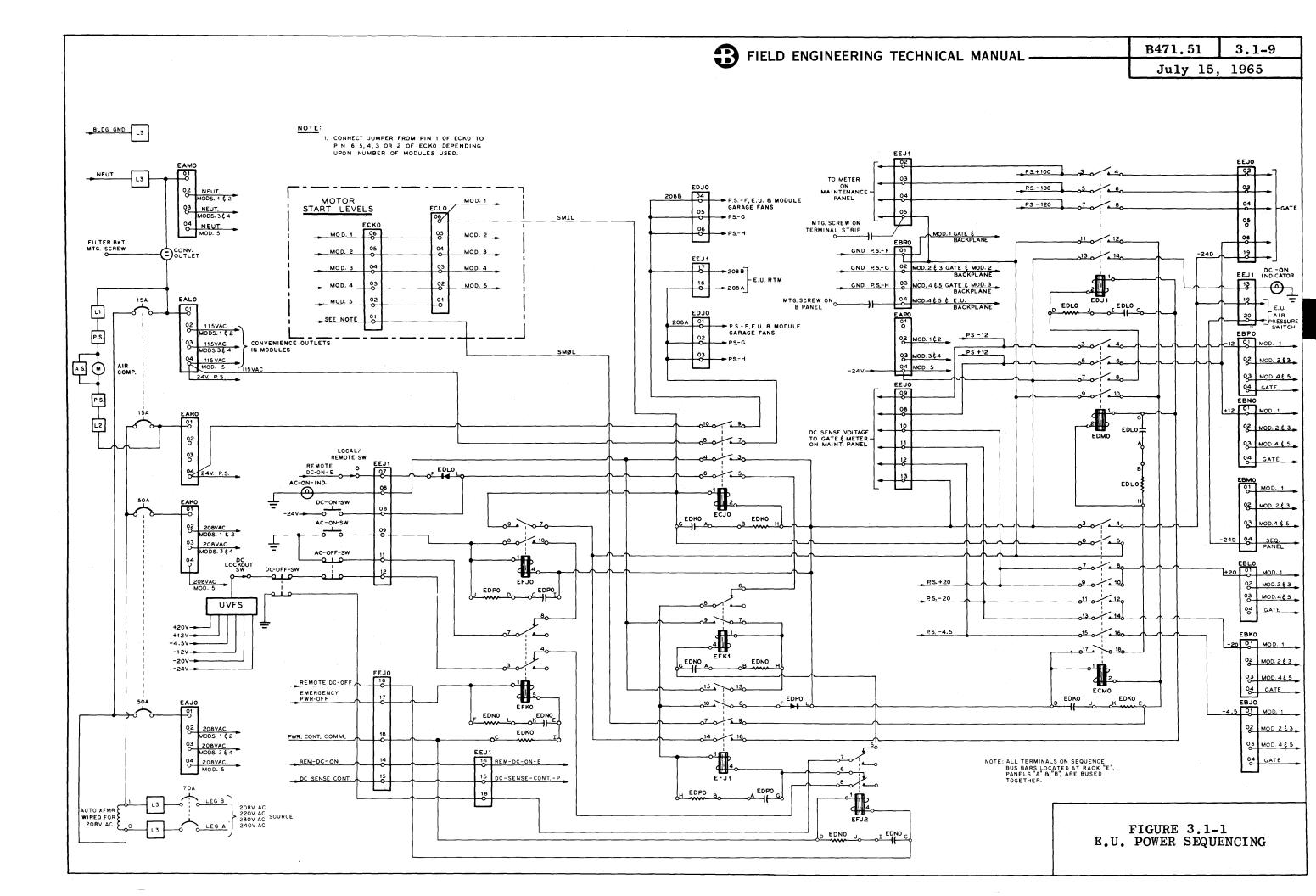

#### 3.1 DISK FILE ELECTRONICS AND STORAGE UNITS POWER SEQUENCING

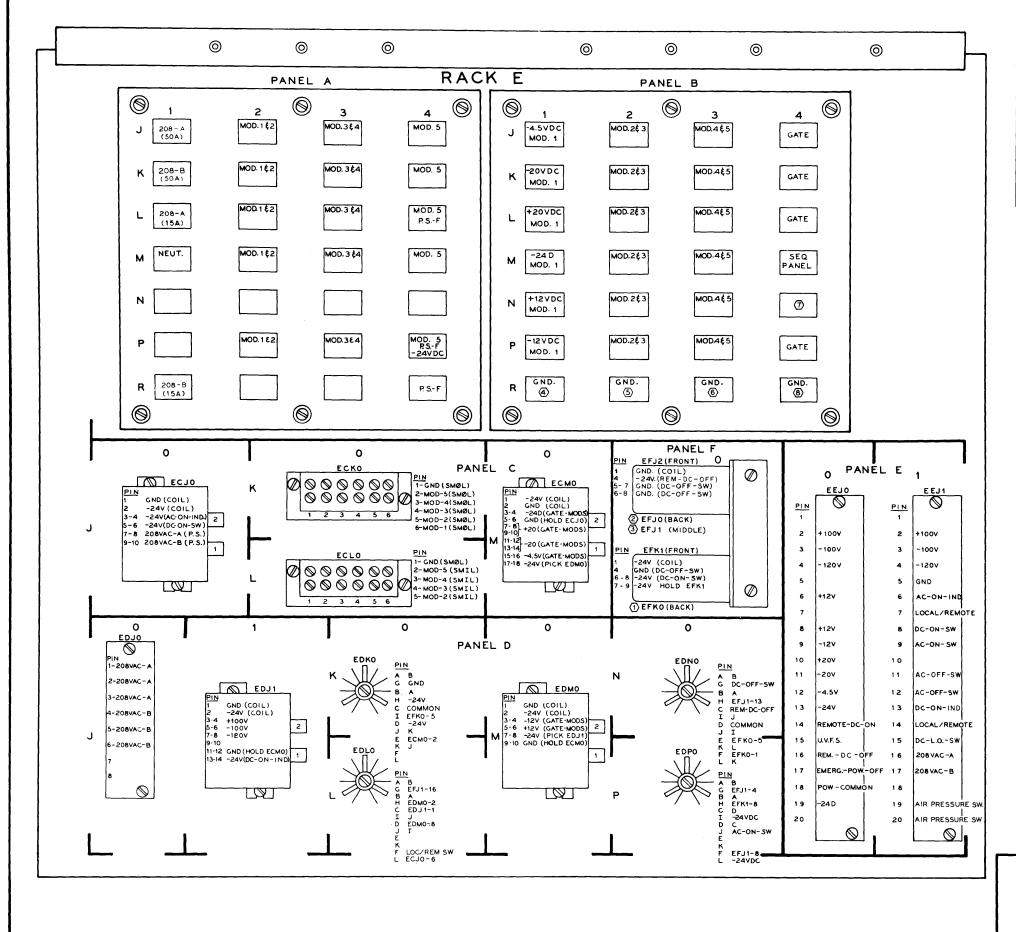

#### Reference Figure 3.1-1.

Power for an Electronics Unit and its associated Storage Modules is supplied from the E.U. power supplies. Disk drive motors in the Storage Modules start in consecutive sequence from the first Module. Successive Modules can only start after the motor in the preceeding Module is up to speed. No DC voltages can be applied to the E.U. gate or the Modules until the disk drive motors in all Modules associated with that E.U. are up to normal running speed. If the Motor Run Switch of a Module is in the Off position, that Module's motor will not start and the sequence continues with the next Module in line.

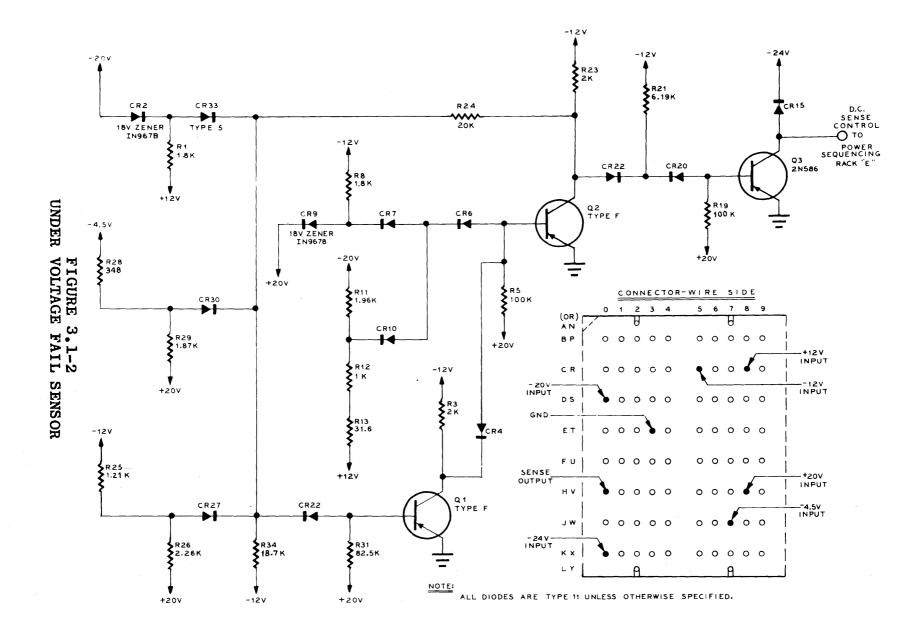

#### UNDER VOLTAGE FAIL SENSOR

Each E.U. has a voltage fail sensor which monitors the DC output voltages of the power supplies. When the supplies are correct, a ground level is supplied to the power sequencing which allows a normal DC On cycle. If any DC voltage falls below normal, DC power will cycle off as in a normal DC Off cycle. Ref. Fig. 3.1-2 for detailed schematic.

#### ELECTRONICS UNIT DC LOCKOUT SWITCH

Each E.U. has a lockout switch which disables the DC On sequence. With DC locked out, AC may be applied but no DC voltages will be supplied to the Modules and E.U. gate.

#### ELECTRONICS LOCAL-REMOTE SWITCH

Each E.U. has a Local-Remote switch. In the Remote position the -24V to start the DC On cycle may come from either the associated Disk File Control or the DC On switch on the E.U. control panel. If the switch is in the Local position, the -24V must come from the DC On switch on the E.U. control panel only.

#### MODULE MOTOR RUN SWITCH

Each Module has a motor run switch which, if on, enables the pick of its motor power relay when SMIL (Start Motor Input Level) from the preceeding Module is present. If off, it disables the pick of the motor power relay and transfers SMIL to the next Module as SMOL (Start Motor Output Level).

#### ELECTRONICS UNIT POWER SEQUENCING PANEL

Inputs

208VAC Leg A 208VAC Leg B Main line voltage inputs. AC Neutral Remote-DC-ON Remote-DC-OFF Remote power control lines from asso-Emergency-Power-Off ciated Disk File Control cabinet. Pwr-Cont-Comm AC-ON-IND AC-ON AC-OFF DC-ON-IND Power control levels from switches and DC-ON indicators on E.U. Control Panel and DC-OFF Under-Voltage Fail Sensor. LOC-REM-DC-ON DC-Sense-Control SEQ-LOC-OUT Power Supply Voltages +100V, -100V, -120V, -24V, GND(Rack F) Power Supply Voltages (Rack G) -12V, +12V, -4.5V, GND Power Supply Voltages (Rack H) +20V, -20V, GNDSMOL Ground level from last storage module in a file to E.U. power sequencing panel. -24D Return from Air Compressor Pressure Switch.

Outputs

Electronics Gate and Modules:

-4.5V -20V +20V +12V -12V -24D

Modules:

208VAC

Legs A and B to disk drive motors and heat exchange fans (2 per module), garage fans (3 per module) and Running Time Meter.

| <b>B</b> FIELD ENGINEERING TECHNIC                                                                                                                                        | AL MANUAL                                                                                                            | B471.51                     | 3.1-3            |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------|--|

|                                                                                                                                                                           |                                                                                                                      | July 15                     | , 1965           |  |

| 115VAC                                                                                                                                                                    | 208VAC Leg A for convenience outlets.                                                                                |                             |                  |  |

| SMIL                                                                                                                                                                      | Ground level to Motor Run Switch in first module.                                                                    |                             |                  |  |

|                                                                                                                                                                           |                                                                                                                      |                             |                  |  |

| Electronics Unit Maintenance                                                                                                                                              | Panel:                                                                                                               |                             |                  |  |

| +100V<br>-100V<br>-120V                                                                                                                                                   | Indicator drivers.                                                                                                   |                             |                  |  |

| 208VAC Legs A and B<br>115VAC (Leg A 208VAC)<br>115VAC (Leg B 208VAC)                                                                                                     | Running Time Meter.<br>Convenience outlets a<br>E.U. fans (2 per unit                                                |                             | ressor.          |  |

| All voltages metered at E.U.                                                                                                                                              | panel.                                                                                                               |                             |                  |  |

|                                                                                                                                                                           |                                                                                                                      |                             |                  |  |

| POWER ON SEQUENCE                                                                                                                                                         |                                                                                                                      |                             |                  |  |

| Conditions:                                                                                                                                                               |                                                                                                                      |                             |                  |  |

| 70 Amp. Circuit Breaker On.<br>E.U. Local-Remote switch in Local or Remote position.<br>E.U. DC Lockout switch off.<br>Motor Run switches in all Modules in Run position. |                                                                                                                      |                             |                  |  |

| AC-ON-Cycle                                                                                                                                                               |                                                                                                                      |                             |                  |  |

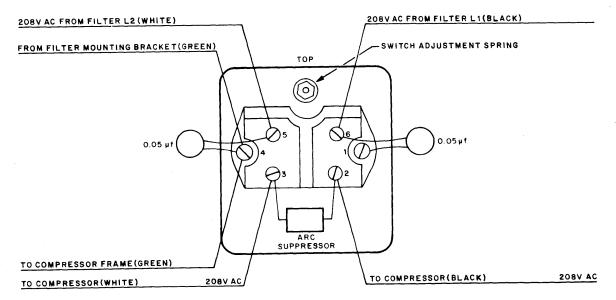

| AC Circuit Breaker "ON"<br>(15 Amp.)                                                                                                                                      | 208VAC Legs A and B t<br>supply in E.U. and ai<br>Leg A to contact 8 EC<br>outlets in E.U. and m<br>contact 10 ECJO. | r compresso<br>CJO, conveni | r motor.<br>ence |  |

| -24V Power Supply                                                                                                                                                         | Supplies relay contro<br>and modules.                                                                                | ol voltage t                | o E.U.           |  |

| AC Circuit Breaker "ON"<br>(50 Amp.)                                                                                                                                      | 208VAC Legs A and B t<br>relay contacts in all                                                                       | -                           | er               |  |

| AC-On-Switch "ON"<br>EFJO contacts 8-10                                                                                                                                   | Pick EFJO (ground pin<br>Hold EFJO (ground pin<br>through NC contacts 7<br>AC-Off-Switch).                           | l coil cir                  | cuit             |  |

| contacts 7-9                                                                                                                                                              | SMIL to first Module<br>Motor Run Switch. Pi<br>Relay and starts disk                                                | .cks Motor P                | ower             |  |

|                                                                                                                                                                           | Pick ECJO (ground pin                                                                                                | ı l coil cir                | cuit).           |  |

3.1 - 4

ECJ0 contacts 5-6

Enable pick and hold EFJl circuit. (Close line from DC-On and Local-Remote switch to pin 1 EFJl coil and contact 10 EFJl through NC contacts 6-8 EFK1.)

contacts 3-4 AC-On-Indicator lit (-24V to indicator).

contacts 7-8 208VAC Legs A and B to DC Power Supplies, Running Time Meter, and E.U. and module garage fans.

When all module disk drive motors are up to speed, SMOL from last module in sequence supplies ground level to contact 7 EFJ1 and enables pick of ECM0.

DC-ON-Cycle

DC-ON-Switch "ON" or Remote DC "ON" Pick EFJ1 (-24V to pin 1 coil circuit through contacts 5-6 ECJ0 and 6-8 EFK1). Ground to pin 4 coil EFJ1 supplied from Under-Voltage Fail Sensor (ground when Power Supply voltages normal) through NC DC-Off-Switch, NC DC-Lockout-Switch, NC AC-Off-Switch, NC contacts 3-4 EFK0, and NC contacts 6-8 EFJ2.

(Ground pin

EFJ1 contacts 14-16 Enable pick EDMO and EDJ1. (Gr 1 coil circuit on both relays.)

> contacts 7-9 Pick ECMO (ground pin 2 coil circuit with SMOL from last module when module motors up to speed).

contacts 8-10 Hold EFJ1 (-24V to pin 1 coil circuit).

contacts 13-15 Pick EFK1 (-24V to pin 1 coil circuit through contacts 3-4 ECJO). Ground to pin 4 EFK1 coil circuit supplied through NC contacts 5-7 EFJ2 and NC DC-Off-Switch.

EFK1 contacts 7-9 Hold EFK1 (-24V to pin 1 coil circuit through contacts 3-4 ECJ0).

contacts 6-8 Open -24V line from DC-On-Switch to pin 1 coil circuit EFJ1.

ECMO contacts 17-18 Pick EDMO (-24V to pin 2 coil circuit).

contacts 15-16 -4.5V to E.U. gate and modules.

| R | FIELD | ENGINEERING | TECHNICAL | MANUAL - |

|---|-------|-------------|-----------|----------|

|   |       |             |           |          |

| B471.5 | 1   | 3.1-5 |

|--------|-----|-------|

| July   | 15, | 1965  |

|      | contacts | 13-14<br>11-12 | -20V to E.U. gate and Modules.                                                  |

|------|----------|----------------|---------------------------------------------------------------------------------|

|      | contacts | 7-8<br>9-10    | +20V to E.U. gate and Modules.                                                  |

|      | contacts | 5-6            | Hold ECJO (ground pin l coil circuit).                                          |

|      | contacts | 3-4            | -24D to E.U. gate and Modules when Air<br>Compressor Pressure Switch is closed. |

| EDMO | contacts | 9-10           | Hold ECMO (ground pin 2 coil circuit).                                          |

|      | contacts | 7-8            | Pick EDJ1 (-24V to pin 2 coil circuit).                                         |

|      | contacts | 5-6            | +12V to E.U. gate and Modules.                                                  |

|      | contacts | 3-4            | -12V to E.U. gate and Modules.                                                  |

| EDJ1 | contacts | 13-14          | DC-On-Indicator lit (-24V to indicator).                                        |

|      | contacts | 11-12          | Hold ECMO (ground pin 2 coil circuit).                                          |

|      |          |                |                                                                                 |

|      | contacts | 7-8            | -120V to Maintenance Panel.                                                     |

|      | contacts | 5-6            | -100V to Maintenance Panel.                                                     |

|      | contacts | 3-4            | +100V to Maintenance Panel.                                                     |

Relays EFJO, ECJO, EFJ1, EFK1, ECMO and EDJ1 are energized, EFKO and EFJ2 are de-energized. Module motors all running and power supply voltages normal.

DC-OFF-Cycle (Local)

Depress DC-Off-Switch Drop EFJ1 (remove ground from pin 4 coil circuit through NC contacts 3-4 EFK0 and 8-6 EFJ2).

Drop EFK1 (remove ground from pin 4 coil circuit through NC contacts 5-7 EFJ2).

Open EFJ1 contacts 14-16

Drop EDJ1 (remove ground from pin 1 coil circuit).

Drop EDMO (remove ground from pin 1 coil circuit).

contacts 7-9 Remove SMOL ground to pin 2 coil circuit ECMO. ECMO will hold until EDJ1 and EDMO drop.

Printed in U.S.A.

| contacts 8-10                   | Open hold EFJl line (remove -24V from pin l coil circuit).                                |

|---------------------------------|-------------------------------------------------------------------------------------------|

| contacts 13-15                  | Open pick EFKl line (-24V to pin l EFKl coil circuit).                                    |

| Open EFK1 contacts 7-9          | Open hold EFK1 line (remove -24V pin l coil circuit).                                     |

| close contacts 6-8              | Enable pick EFJl line.                                                                    |

| Open EDJ1 contacts 13-14        | DC-On-Indicator off (remove -24V from indicator).                                         |

| contacts 11-12                  | Open one hold ECMO line (remove ground from pin 2 coil circuit).                          |

| contacts 7-8                    | Remove -120V from Maintenance Panel.                                                      |

| contacts 5-6                    | Remove -100V from Maintenance Panel.                                                      |

| contacts 3-4                    | Remove +100V from Maintenance Panel.                                                      |

| Open EDMO contacts 9-10         | Drop ECMO (remove ground from pin 2<br>coil circuit). Last hold ECMO in DC-<br>Off-Cycle. |

| contacts 7-8                    | Open pick EDJ1 line (remove -24V from pin 2 coil circuit).                                |

| contacts 5-6                    | Remove +12V from E.U. gate and Modules.                                                   |

| contacts 3-4                    | Remove -12V from E.U. gate and Modules.                                                   |

| <b>Open ECMO contacts 17-18</b> | Open pick EDMO line (remove -24V from pin 2 coil circuit).                                |

| contacts 15-16                  | Remove -4.5V from E.U. gate and Mod-ules.                                                 |

| contacts 13-14<br>11-12         | Remove -20V from E.U. gate and Modules.                                                   |

| contacts 7-8<br>9-10            | Remove +20V from E.U. gate and Modules.                                                   |

| contacts 5-6                    | Open hold ECJO line (remove ground from pin 1 coil circuit).                              |

| contacts 3-4                    | Remove -24D from E.U. gate, Air Pres-<br>sure Switch and Modules.                         |

3.1-6

FIELD ENGINEERING TECHNICAL MANUAL -----

| B471.5 | 1   | 3.1-7 |

|--------|-----|-------|

| July   | 15, | 1965  |

## AC-OFF-Cycle (Local)

Depress AC-Off-Switch

Drop EFJ0 (open hold EFJ0 line and remove ground from pin 1 coil circuit, through NC contacts 7-8 EFK0). Start normal DC-Off-Cycle by dropping EFJ1 (AC-Off-Switch and DC-Off-Switch in series). See "Drop EFJ1" in DC-Off-Cycle (Local).

Open EFJO contacts 8-10

contacts 7-9

Open ECJO contacts 5-6

contacts 3-4

contacts 7-8 9-10 Open hold EFJO line (remove ground from pin 1 coil circuit).

Open pick ECJO. Drop ECJO only when ECMO (last relay to drop in DC-Off-Cycle) removes ground from pin 1 coil circuit ECJO; Module motors will stop due to loss of ground level (SMIL) to motor power relays.

Open pick EFJl line from DC-On-Switch to pin l coil circuit EFJl.

AC-On-Indicator off (remove -24V to indicator).

Open hold EFK1 line (remove -24V from contact 9 EFK1). Open pick EFK1 line (remove -24V from contact 15 EFJ1).

DC power supplies off (remove 208VAC Legs A and B to power supply racks F, G and H).

Running Time Meter and E.U. fans off. (Remove 208VAC Legs A and B to RTM and Leg B to fans.)

Pick EFJ2 (-24V pulse from Processor to

Drop EFJ1 (remove ground from pin 4

DC-OFF-Cycle (Remote)

Remote DC-Off pulse from D.F.C.U.

Open EFJ2 contacts 8-10

coil circuit). contacts 5-7 Drop EFK1 (remove ground from pin 4

pin 4 coil circuit).

coil circuit).

Dropping EFJ1 and EFK1 starts normal DC-Off-Cycle. Refer to "Open EFJ1" in DC-Off-Cycle (Local) for further details. Note that the AC On condition is not affected and the Module motors continue to run. Emergency-Power-Off-Cycle

| Emergency-Power-Off pulse<br>from Processor | Pick EFKO (-24V pulse from Processor to pin 1 coil circuit).                                                                                                                          |

|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Open EFKO contacts 3-4                      | Drop EFJ1 (remove ground from pin 1<br>coil circuit through contacts 8-6<br>EFJ2, NC AC-OFF-Switch, NC DC-OFF-Switch<br>and DC Lockout-Switch from the Under<br>Voltage Fail Sensor). |

| contacts 7-8                                | Drop EFJO (open hold EFJO line from<br>NC AC-OFF-Switch to contact 10 EFJO).                                                                                                          |

Dropping EFJ1 and EFJ0 starts AC and DC Off-Cycles. Refer to "Open EFJ1" in DC-Off-Cycle (Local) and "Open EFJ0" in AC-Off-Cycle (Local) for further details.

FIELD ENGINEERING TECHNICAL MANUAL

B471.51 3.1-11 July 1, 1964

| B FIELD ENGINEERING TECHN   | ICAL MANUAL B471.51 3.2-                  |

|-----------------------------|-------------------------------------------|

| PIELD ENGINEERING TECHNI    | July 1, 1964                              |

|                             |                                           |

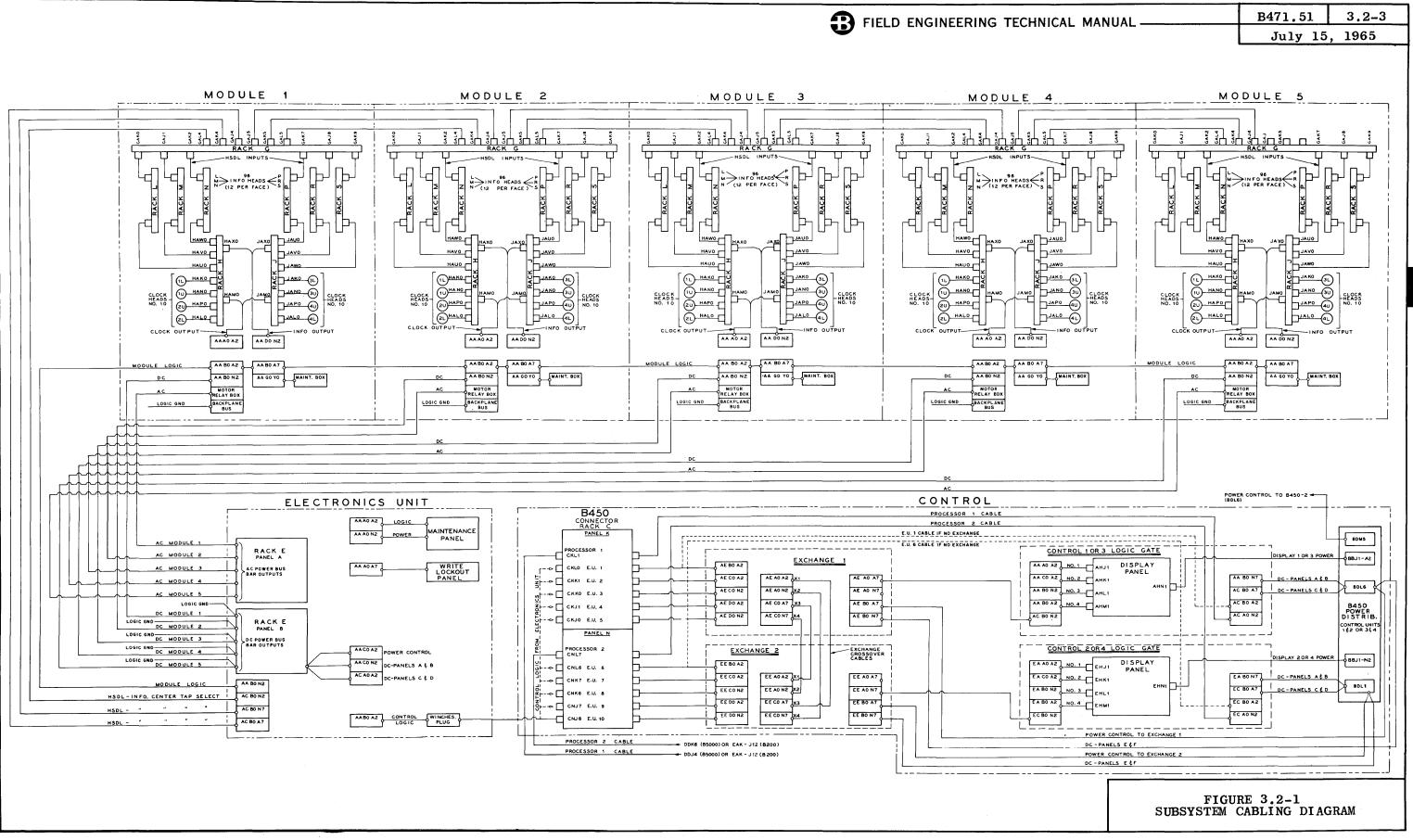

| 3.2 CABLING                 |                                           |

|                             | • a.                                      |

| All the lines in the logic  | and power cables associated with an Elec- |

|                             | in cross-reference tables. The following  |

|                             | th table references. Refer to Figure 3.2. |

| for sub-system cabling diag | ;ram.                                     |

| · · ·                       |                                           |

| LOGIC CABLES INTER-UNIT     |                                           |

|                             |                                           |

| Table 3.2-1.                |                                           |

| ACBON7GAK4                  | Information center tap select cables      |

| ACBON2GAL4                  | from E.U. logic gate to center tap        |

| ACBOA7GAJ4                  | distribution board in Module 1.           |

| Table 3.2-2.                |                                           |

| B450 Panel K                | E.U. logic gate to Control.               |

| AAB0A2 - (C.U. 1  or  3)    | E.U. logic gate to control.               |

| B450 Panel N                |                                           |

| (C.U. 2 or 4)               |                                           |

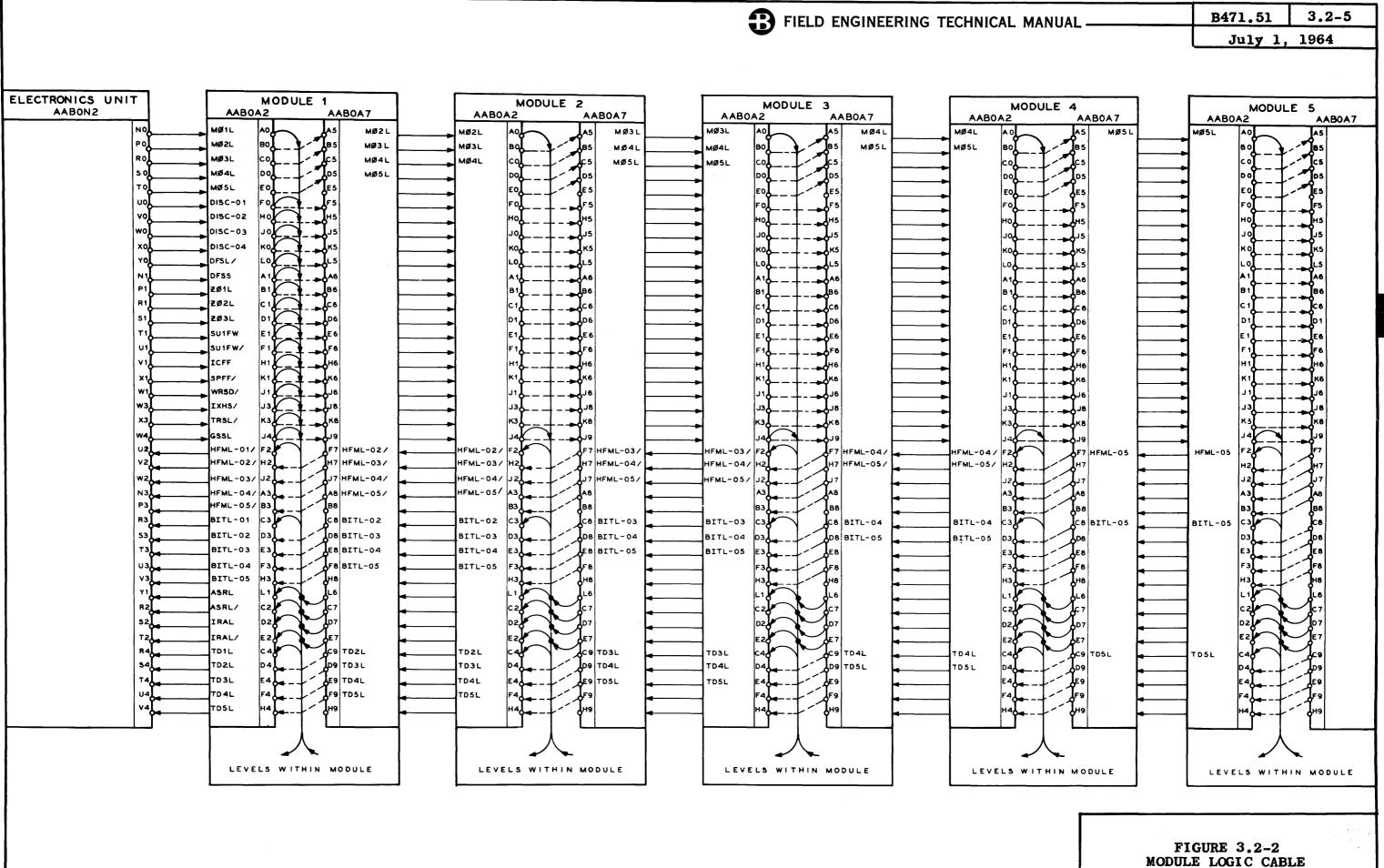

| Figure 3.2-2.               | ـــــــــــــــــــــــــــــــــــــ     |

| -                           |                                           |

| AABUN2AABUA2 (Module 1      | ) E.U. logic gate to first Module.        |

| LOGIC CABLES INTERNAL       |                                           |

|                             |                                           |

| Table 3.2-3.                |                                           |

| AAAOA2Maintenance Pane      | E.U. logic gate to Maintenance Panel.     |

|                             | Switch and indicator levels.              |

| Table 3.2-4.                |                                           |

| Table 3.2-4.                |                                           |

| AAAOA7Write Lockout         | E.U. logic gate to Write Lockout Panel    |

| Panel                       | Switch levels.                            |

|                             |                                           |

| POWER CABLES INTER-UNIT     | : 1                                       |

| Table 3.2-5.                |                                           |

| Rack E Motor power rel      | ay AC power cables from E.U. sequence     |

| Panel A in Modules 1        | panel to each Module.                     |

| through 5                   |                                           |

| Table 3.2-6.                |                                           |

|                             |                                           |

| Rack E AABON2 (Modules      | DC power cables from E.U. sequence par    |

| Panel B 1 through 5)        | to each Module.                           |

|                             |                                           |

Printed in U.S.A.

3.2-2

July 1, 1964

POWER CABLES INTERNAL

Table 3.2-7.

AAAON2----Maintenance Panel Maintenance Panel power cable.

Table 3.2-8.

Rack E \_\_\_\_AACOA2 Panel B

Power control cable.

Table 3.2-9.

Rack E \_\_\_\_AACON2 Panel B

DC - Panels A and B.

Table 3.2-10.

Rack E \_\_\_\_ACA0A2 Panel B

DC - Panels C and D.

| B471.51 | 3.2-7 |

|---------|-------|

| July 1, | 1964  |

| *E.U.      |        |         |      |            |            |         |      |        |            |         |      |

|------------|--------|---------|------|------------|------------|---------|------|--------|------------|---------|------|

| E.U.       | **MOD. |         | MOD. | *E.U.      | **<br>MOD. |         | MOD. | *E.U.  | **<br>MOD. |         | MOD. |

| ACBOA7     | GAJ5   | LEVEL   | GAJ4 | ACBON2     | GAL5       | LEVEL   | GAL4 | ACBON7 | GAK5       | LEVEL   | GAK4 |

| A5         | 19     | HSDL-90 | 1    | NO         | 19         | HSDL-08 | 1    | 19     | N 5        | HSDL-13 | 1    |

| B5         | 18     | HSDL-88 | 2    | PO         | 18         | HSDL-06 | 2    | 18     | P5         | HSDL-11 | 2    |

| C5         | 17     | HSDL-74 | 3    | RO         | 17         | HSDL-12 | 3    | 17     | R5         | HSDL-33 | 3    |

| D5         | 16     | HSDL-98 | 4    | SO         | 16         | HSDL-00 | 4    | 16     | \$5        | HSDL-05 | 4    |

| E5         | 15     | HSDL-96 | 5    | то         | 15         | HSDL-26 | 5    | 15     | T5         | HSDL-03 | 5    |

| F5         | 14     | HSDL-89 | 6    | vo         | 14         | HSDL-16 | 6    | 14     | U5         | HSDL-29 | 6    |

| H5         | 13     | HSDL-67 | 7    | vo         | 13         | HSDL-32 | 7    | 13     | ¥5         | HSDL-45 | 7    |

| J 5        | 12     | HSDL-69 | 8    | WO         | 12         | HSDL-34 | 8    | 12     | ₩5         | HSDL-47 | 8    |

| <b>K</b> 5 | 11     | HSDL-85 | 9    | xo         | 11         | HSDL-20 | 9    | 11     | X5         | HSDL-25 | 9    |

| A6         | 10     | HSDL-59 | 10   | Nl         | 10         | HSDL-40 | 10   | 10     | N6         | HSDL-60 | 10   |

| B6         | 9      | HSDL-61 | 11   | P1         | 9          | HSDL-42 | 11   | 9      | P6         | HSDL-54 | 11   |

| C6         | 8      | HSDL-81 | 12   | Rl         | 8          | HSDL-24 | 12   | 8      | R6         | HSDL-52 | 12   |

| D6         | 7      | HSDL-51 | 13   | <b>S</b> 1 | 7          | HSDL-48 | 13   | 7      | S6         | HSDL-64 | 13   |

| E6         | 6      | HSDL-53 | 14   | Tl         | 6          | HSDL-23 | 14   | 6      | T6         | HSDL-78 | 14   |

| F6         | 5      | HSDL-77 | 15   | U1         | 5          | HSDL-39 | 15   | 5      | U6         | HSDL-80 | 15   |

| H6         | 4      | HSDL-99 | 16   | V1         | 4          | HSDL-17 | 16   | 4      | V6         | HSDL-68 | 16   |

| J6         | 3      | HSDL-97 | 17   | W1         | 3          | HSDL-15 | 17   | 3      | <b>W</b> 6 | HSDL-86 | 17   |

| ۸7         | 2      | GND-03  | 18   | N2         | 2          | GND-01  | 18   | 2      | N7         | GND-02  | 18   |

| B7         | 1      | GND-03  | 19   | P2         | 1          | GND-01  | 19   | 1      | P7         | GND-02  | 19   |

| <b>A8</b>  | 37     | HSDL-72 | 20   | N3         | 37         | HSDL-10 | 20   | 37     | N8         | HSDL-35 | 20   |

| B8         | 36     | HSDL-94 | 21   | P3         | 36         | HSDL-04 | 21   | 36     | P8         | HSDL-09 | 21   |

| C8         | 35     | HSDL-92 | 22   | R3         | 35         | HSDL-02 | 22   | 35     | R8         | HSDL-07 | 22   |

| D8         | 34     | HSDL-91 | 23   | <b>S</b> 3 | 34         | HSDL-14 | 23   | 34     | <b>S</b> 8 | HSDL-31 | 23   |

| E8         | 33     | HSDL-71 | 24   | тз         | 33         | HSDL-28 | 24   | 33     | Т8         | HSDL-01 | 24   |

| F8         | 32     | HSDL-73 | 25   | U3         | 32         | HSDL-30 | 25   | 32     | U8         | HSDL-43 | 25   |

| H8         | 31     | HSDL-87 | 26   | V3         | 31         | HSDL-18 | 26   | 31     | V8         | HSDL-27 | 26   |

| <b>J</b> 8 | 30     | HSDL-63 | 27   | W3         | 30         | HSDL-36 | 27   | 30     | W8         | HSDL-49 | 27   |

| K8         | 29     | HSDL-65 | 28   | ХЗ         | 29         | HSDL-38 | 28   | 29     | X8         | HSDL-58 | 28   |

| <b>A</b> 9 | 28     | HSDL-83 | 29   | N4         | 28         | HSDL-22 | 29   | 28     | N9         | HSDL-56 | 29   |

| B9         | 27     | HSDL-55 | 30   | P4         | 27         | HSDL-44 | 30   | 27     | P9         | HSDL-62 | 30   |

| C9         | 26     | HSDL-57 | 31   | R4         | 26         | HSDL-46 | 31   | 26     | R9         | HSDL-50 | 31   |

| D9         | 25     | HSDL-79 | 32   | S4         | 25         | HSDL-41 | 32   | 25     | <b>S</b> 9 | HSDL-76 | 32   |

| <b>E</b> 9 | 24     | HSDL-95 | 33   | T4         | 24         | HSDL-21 | 33   | 24     | Т9         | HSDL-66 | 33   |

| F9         | 23     | HSDL-93 | 34   | U4         | 23         | HSDL-19 | 34   | 23     | U9         | HSDL-82 | 34   |

| <b>J</b> 9 | 22     | HSDL-75 | 35   | ₩4         | 22         | HSDL-37 | 35   | 22     | <b>W</b> 9 | HSDL-84 | 35   |

| 10         | 21     | SPARE-2 | 36   | X4         | 21         | SPARE-1 | 36   | 21     | <b>X</b> 9 | HSDL-70 | 36   |

| L9         |        |         |      |            |            |         |      |        |            |         |      |

TABLE 3.2-1

\*3 Center Tap Cables from E.U. to 1st Module.

ACBOA7

ACBUN2-ACBUN7 Quad Connectors in E.U. Logic Gate

\*\* 3 Center Tap Cables from a Module to the next Module. GAJ 5 GAL5 GAK5 Connectors - Rack G Storage Module.

ELECTRONICS UNIT

**B**0

FO

4

14

10

18

CS1L/

CS2L/

4

14

10

18

E.U. 1 thru 5 ACBOA2 E.U. 1 ONLY AABOA2 WINCHESTER AEBOA2 - E.U. 1 & 6 PANEL K LEVEL AECOA2 - E.U. 2 & 7 E.U. 1 thru 10 E.U. 1 thru 10 AED0A2 - E.U. 4 & 9 E.U. 6 thru 10 AECON2 - E.U. 3 & 8 PANEL N AEDON2 - E.U. 5 & 10 PIN NO. SIGNAL GND PIN SIGNAL GND PIN A2 N2 **E4** 104 111 REM-POW-ON 104 111 E4 T4 H4 115 121 REM-PWR-OFF 115 121 H4 ٧4 KS 82 87 EMERG-PWR-OFF 82 87 ΚЗ ΧЗ **B4** 93 PWR-CONT-COMM 100 100 93 **B4 P4** СЗ 65 60 DFSL/ 65 60 CЗ RЗ D01L/ HЗ 75 71 75 71 НЗ ¥3 L3 84 79 D02L/ 84 79 L3 ¥З C4 95 90 D04L/ 95 90 C4 R4 F4 107 102 107 102 F4 D08L/ U4 113 K4 117 D16L/ 117 113 K4 X4 DO 2 7 Z01L/ 7 2 DO S0JO 16 12 Z02L/ 12 WO 16 JU **B**1 25 21 SW1L 25 21 **B**1 **P1** Fl 33 29 33 29 Fl U1 SW2L LO 23 27 SW4L 23 27 LO YU D1 31 **S1** 35 31 35 SW8L Dl J2 57 53 57 ₩2 SWAL 53 J2 D3 62 S3 66 SWBL 66 62 D3 J3 76 72 SWRL/ 76 72 J3 WЗ **14** 85 80 SCØL/ 85 80 **A4** NЗ C0 5 T01L/ 5 1 1 CO Rû HO T02L/ V0 15 11 15 11 HO **A**1 24 20 T04L/ 24 20 **A**1 N1 **E**1 32 28 T08L/ 32 28 E1 **T**1 T10L/ 36 **K1** 40 36 **4**0 K1 X1 D2 48 T20L/ 48 44 44 D2 **S2** H2 56 52 T40L/ 52 **V**2 56 H2 D4 97 92 INXP 97 92 D4 **S4 J**1 39 43 WDMP **3**9 43 **W1 J**1 L4 120 114 SWLL 120 114 L4 ¥4 **A**0 3 8 SR1L 3 8 NO AO E0 13 17 SR2L 13 17 EO TO KO 22 22 26 XO 26 SR4L KO Rl Cl 30 34 SR8L 30 34 Cl Hl 38 42 SRAL 38 42 H1 **V1** 46 Ll 50 SRBL 50 Ll ¥1 46 E2 SCLP 58 54 58 54 E2 T2 63 67 SURL/ 67 A3 AЗ 63 NЗ 73 77 SARL/ 73 77 EЗ тз E3

**TABLE 3.2-2**

B450

EXCHANGE 1 or 2

BO

FO

PO

UO

c

## B471.51 3.2-9 July 1, 1964

TABLE 3.2-3

|            | IADLE     | 3.2-3             |     |  |  |

|------------|-----------|-------------------|-----|--|--|

| AAA0A2     | LEVEL     | MAINTENANCE PANEL |     |  |  |

| PIN        |           | LOCATION          | PIN |  |  |

| EO         | SR5L-IND/ | DAKO (IND)        | 2   |  |  |

| DU         | SR4L-IND/ | DAK1 (IND)        | 2   |  |  |

| Cυ         | SR3L-IND/ | DAK2 (IND)        | 2   |  |  |

| <b>B</b> 0 | SR2L-IND/ | DAK3 (IND)        | 2   |  |  |

| <b>A</b> 0 | SR1L-IND/ | DAK4 (IND)        | 2   |  |  |

| E2         | SCHOS     | DDJO (JT)         | 1   |  |  |

| Ll         | INXP-01   | DDJ2 (JT)         | 1   |  |  |

| F2         | ACFF      | DDKO (JT)         | 1   |  |  |

| C2         | WØMP-01   | DDK2 (JT)         | 1   |  |  |

| H2         | ICFF-2A/  | DDLO (JT)         | 1   |  |  |

| D2         | BITP-D    | DDL2 (JT)         | 1   |  |  |

| El         | SPFF-IND  | DCJOA2 (DRI)      | 7   |  |  |

| K1         | BA2F-IND  | DCLOA2 (DRI)      | 7   |  |  |

| J1         | BA1F-IND  | DCMOA2 (DRI)      | 7   |  |  |

| D1         | INFF-IND  | DCJ1A2 (DRI)      | 7   |  |  |

| Fl         | ACFF-IND  | DCL1A2 (DRI)      | 7   |  |  |

| Hl         | ICFF-IND  | DCM1A2 (DRI)      | 7   |  |  |

| F4         | SPFF-MC   | DCJOA2 (DRI)      | 2   |  |  |

| L4         | BA2F-MC   | DCLOA2 (DRI)      | Ż   |  |  |

| K4         | BA1F-MC   | DCMOA2 (DRI)      | 2   |  |  |

| E4         | INFF-MC   | DCJ1A2 (DRI)      | 2   |  |  |

| H4         | ACFF-MC   | DCL1A2 (DRI)      | 2   |  |  |

| J4         | ICFF-MC   | DCM1A2 (DRI)      | 2   |  |  |

| C1         | SUCF-IND  | DCN2A2 (DRI)      | 7   |  |  |

| B1         | SULFW-IND | DCP2A2 (DRI)      | 7   |  |  |

| FO         | SUBF-IND  | DCJ3A2 (DRI)      | 7   |  |  |

| HO         | SUAF-IND  | DCK3A2 (DRI)      | 7   |  |  |

| <b>J</b> 0 | SU8F-IND  | DCL3A2 (DRI)      | 7   |  |  |