# Burroughs B 5370 POWER SUPPLY AND REGULATORS

TECHNICAL MANUAL

March 29, 1965

6.13

#### B 5370.51

#### TABLE OF CONTENTS

#### SUBJECT TITLE DATE PREVENTIVE l. 1.1 Daily (Not Applicable)..... November 15, 1963 1.2 November 15, 1963 Weekly..... 1.3 Monthly..... November 15, 1963 1.4 Quarterly..... November 15, 1963 1.5 Semi-Annually..... November 15, 1963 1.6 Annually..... November 15, 1963 2. TROUBLESHOOTING 2.1 Precautions..... November 15, 1963 2.2 AC Circuits..... November 15, 1963 2.3 DC Power Supplies..... November 15, 1963 2.1 Voltage Regulators..... November 15, 1963 2.5 Voltage Sensing..... November 15, 1963 2.6 Power Control Relays..... November 15, 1963 2.7 RIN Index..... March 29, 1965 3. ADJUSTMENTS 3.1 Voltage Regulator..... May 25, 1964 3.2 Calibration Procedure for Meter Check Circuit .... November 15, 1963 4. ASSEMBLY & DISASSEMBLY 4.1 Power Supply..... November 15, 1963 November 15, 1963 և.2 Voltage Regulators..... 5. INSTALLATION 5.1 November 15, 1963 Introduction..... November 15, 1963 Primary Power Connections..... Cabling and Power Supply to D & D..... November 15, 1963 November 15, 1963 Power On-Off..... Regulator Connections and Check Out..... November 15, 1963 System Power Application and Voltage Sensing Verification..... November 15, 1963 5.7 FCN Installation..... November 15, 1963 5.8 Installation Check List..... November 15, 1963 6. CIRCUIT ANALYSIS 6.1 General..... November 15, 1963 6.2 November 15, Unregulated Supplies..... 1963 6.3 +20V Electrical Switch..... November 15, 1963 6.4 November 15, 1963 +100V Electrical Switch..... 6.5 November 15, 1963 AC Meter..... Elapsed Time Meter..... November 15, 6.6 1963 Meter Check Switch..... November 15, 1963 6.7 6.8 Meter Check Circuit..... November 15, 1963 6.9 Power Off Switch..... November 15, 1963 6.10 November 15, 1963 Power Control..... November 15, 1963 6.11 Power On..... 6.12 November 15, 1963 Power Off.....

Undervoltage Inhibit.....

i

November 15, 1963

March 29, 1965

## TABLE OF CONTENTS (Continued)

| SUBJECT | TITLE                                 | DATE         | •      |

|---------|---------------------------------------|--------------|--------|

| 6.14    | Pre-Stop (PGDL) 1 Megacycle Clock In  |              |        |

| 1       | Central Control                       | November 15, |        |

| 6.15    | +20V Switch Control Level             | November 15, |        |

| 6.16    | -20V B                                | November 15, |        |

| 6.17    | Power Interlock (Peripheral Units)    | November 15, |        |

| 6.18    | Cover Interlock                       | November 15, |        |

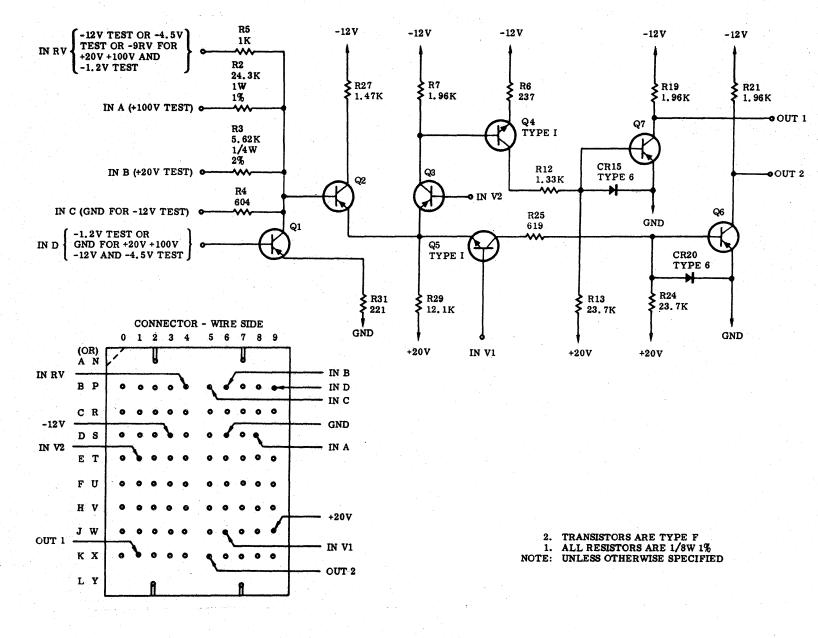

| 6.19    | Voltage Sensing                       | November 15, |        |

| 6.20    | Voltage Sensing Package               | November 15, |        |

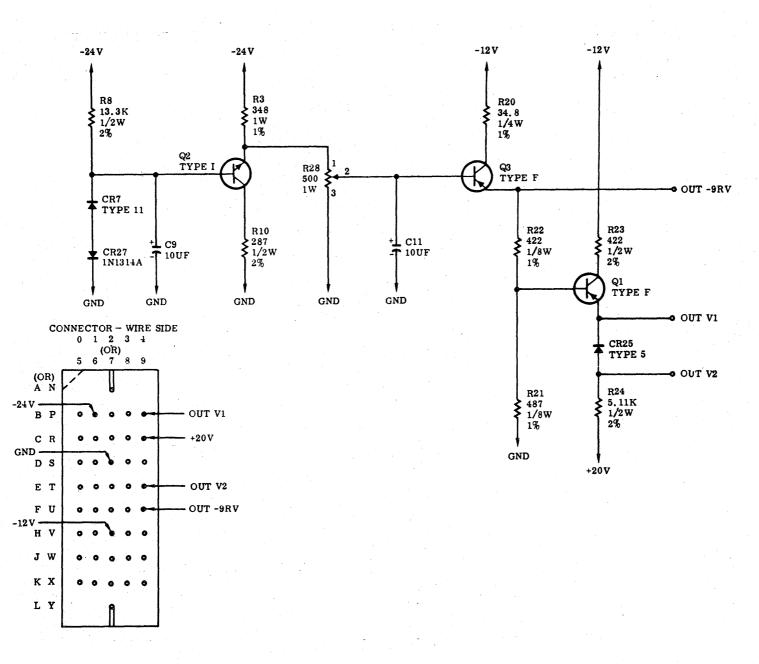

| 6.21    | Voltage Reference Package             | November 15, |        |

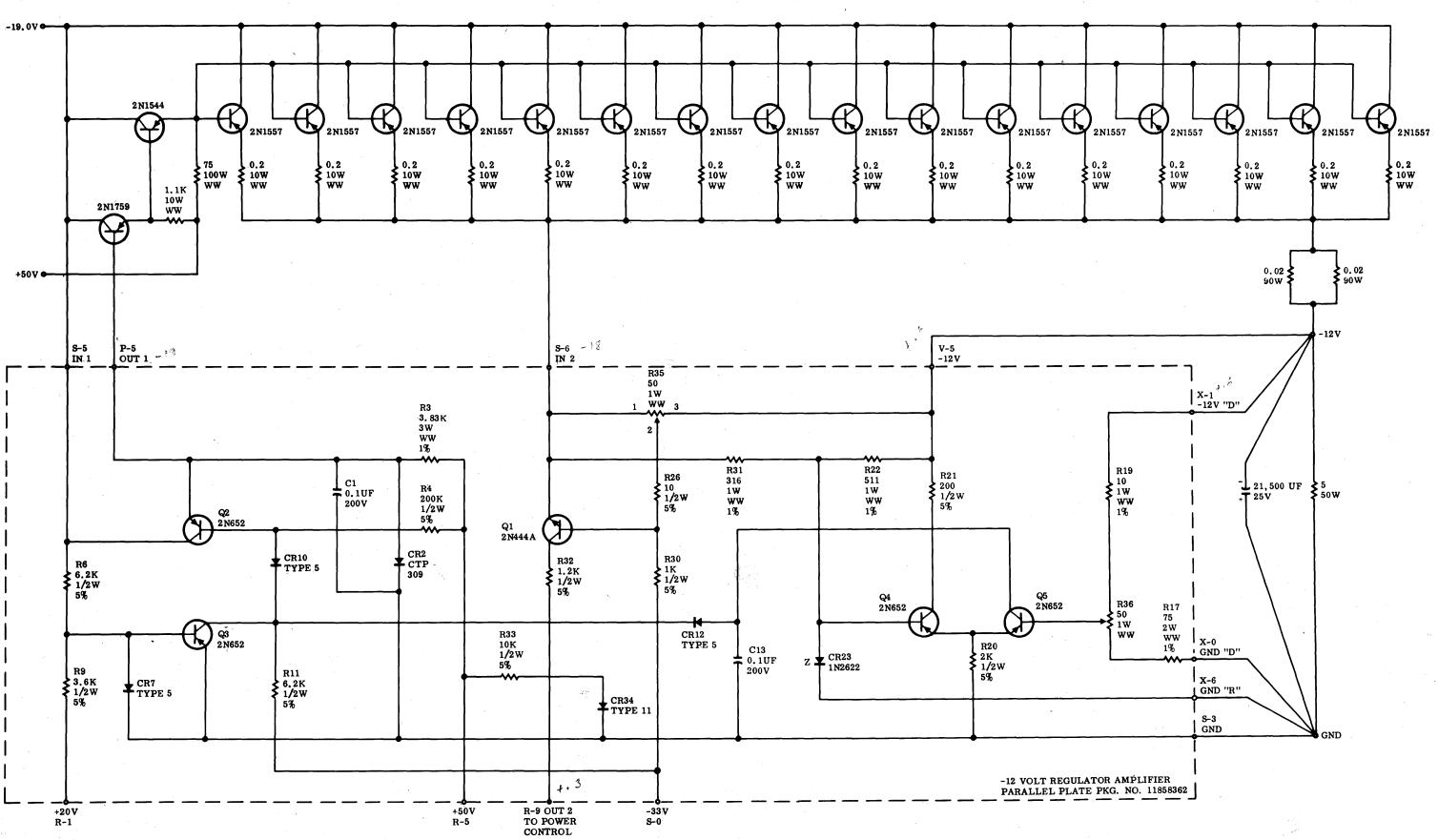

| 6.22    | -12V Regulator                        | November 15, |        |

| 6.23    | B 5000 Parallel Plate Packages        | November 15, |        |

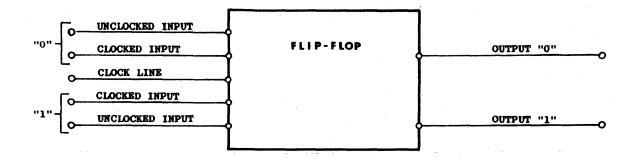

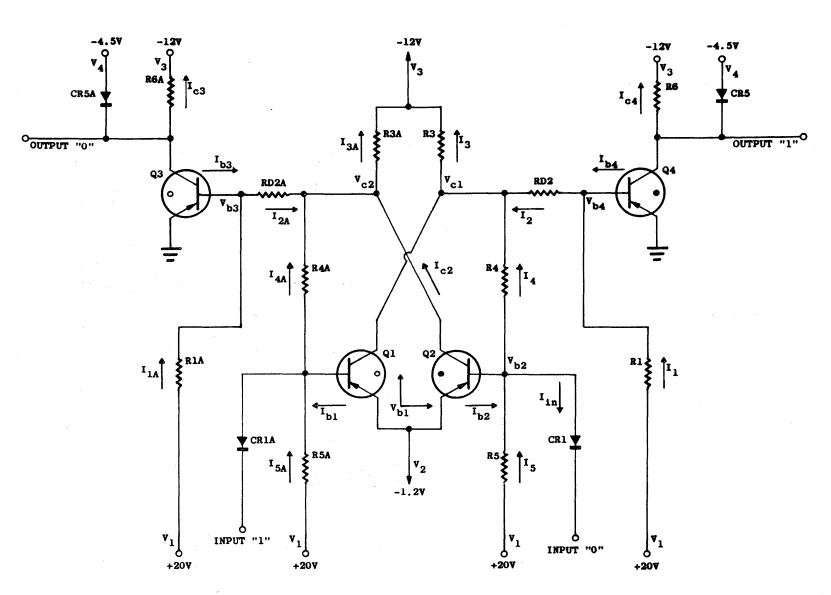

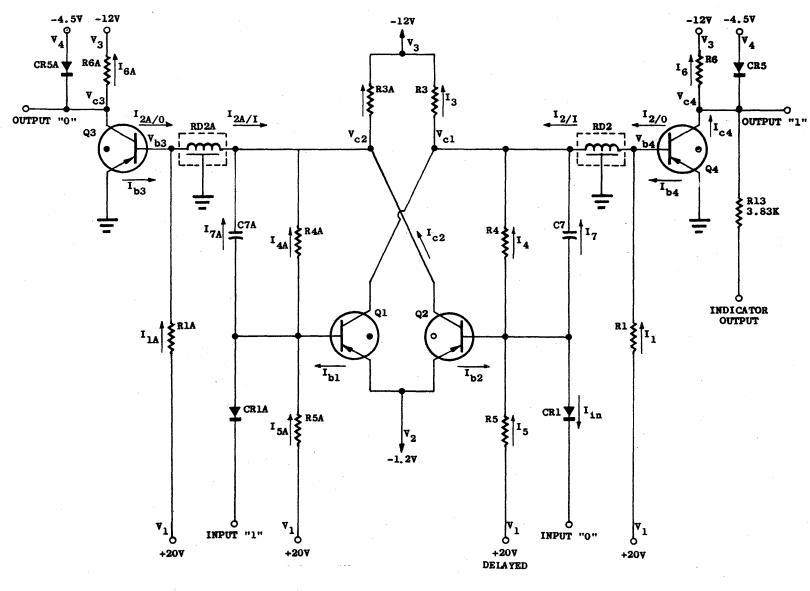

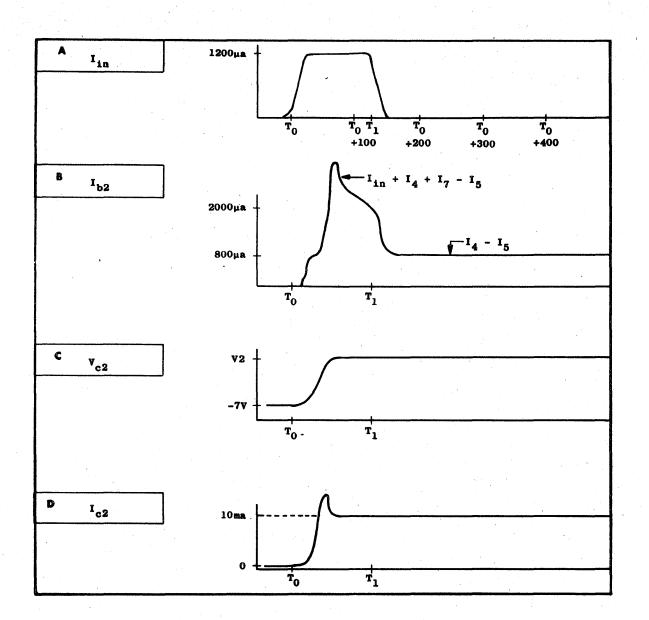

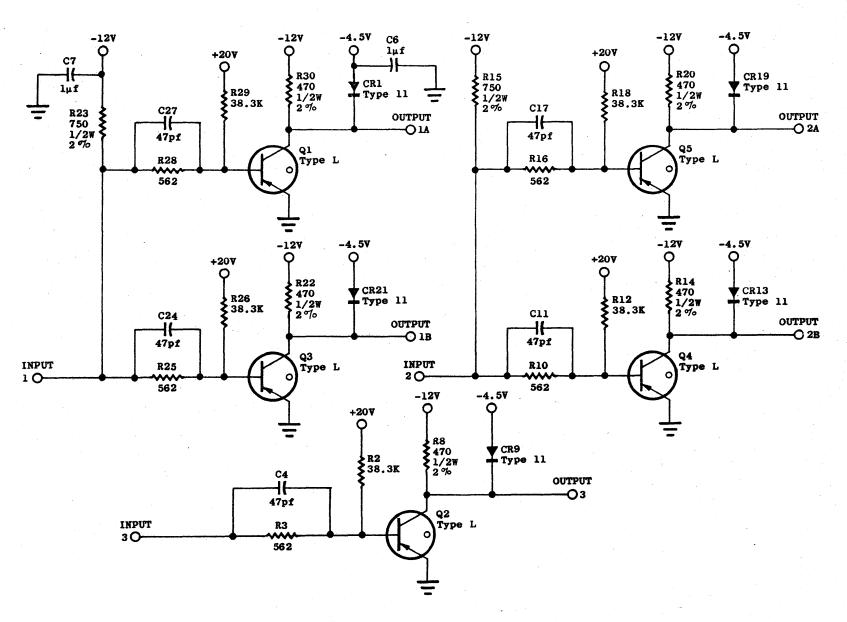

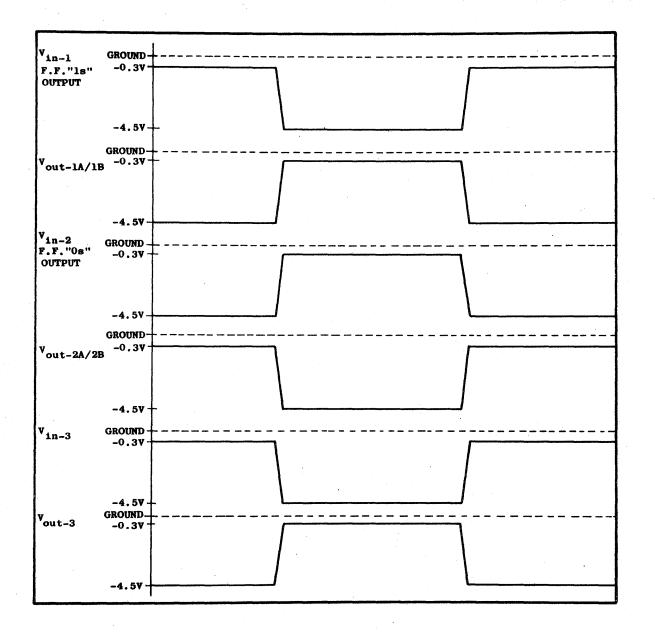

| 6.24    | Flip-flop 20-70                       | November 15, |        |

| 6.25    | Switch I                              | November 15, |        |

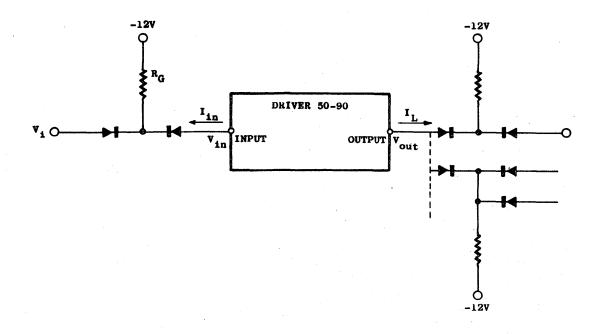

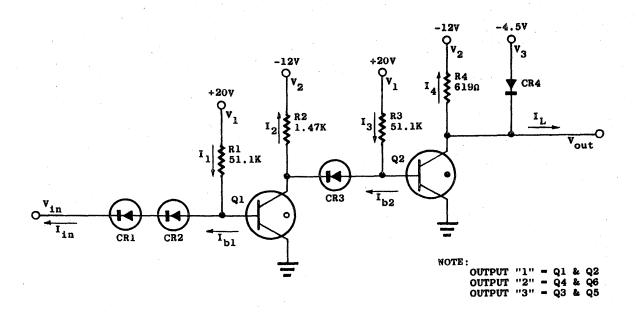

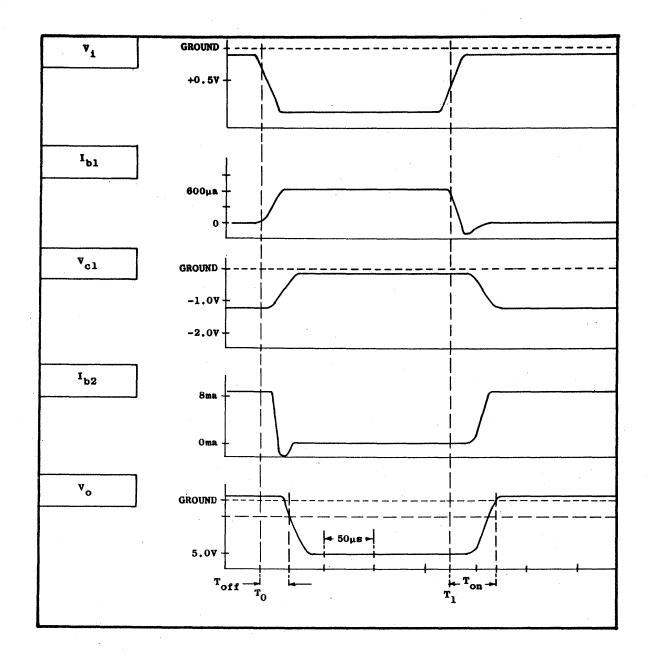

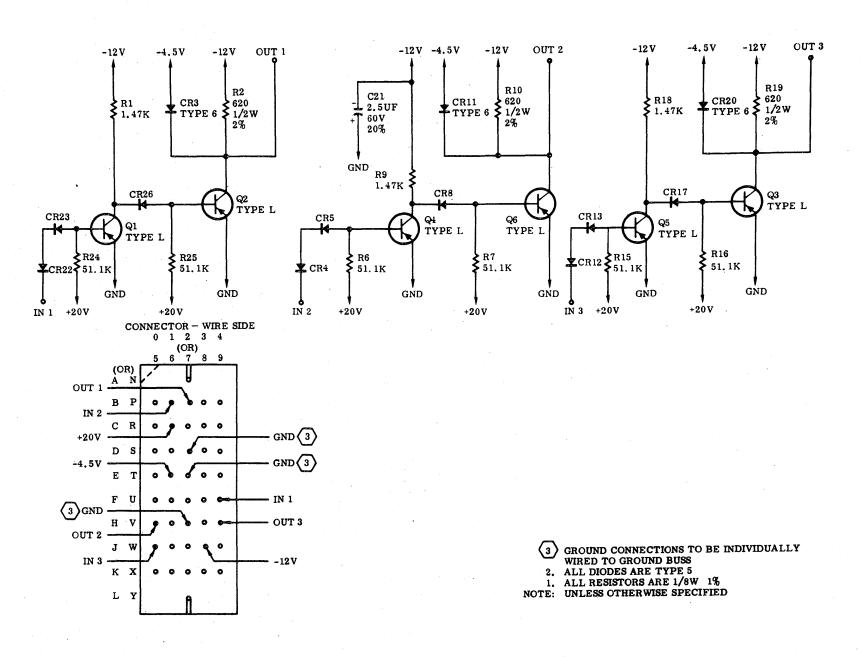

| 6.26    | Driver 50-90                          | November 15, |        |

| 6.27    | Delay "A"                             | November 15, |        |

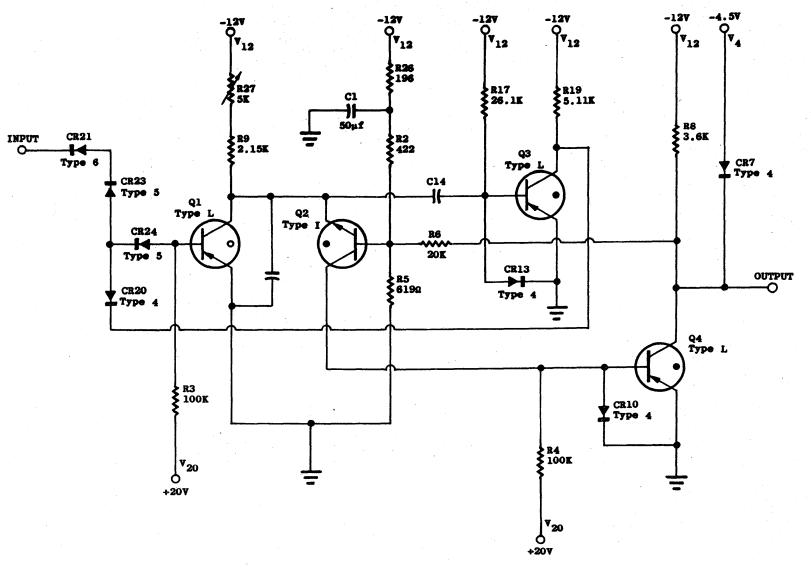

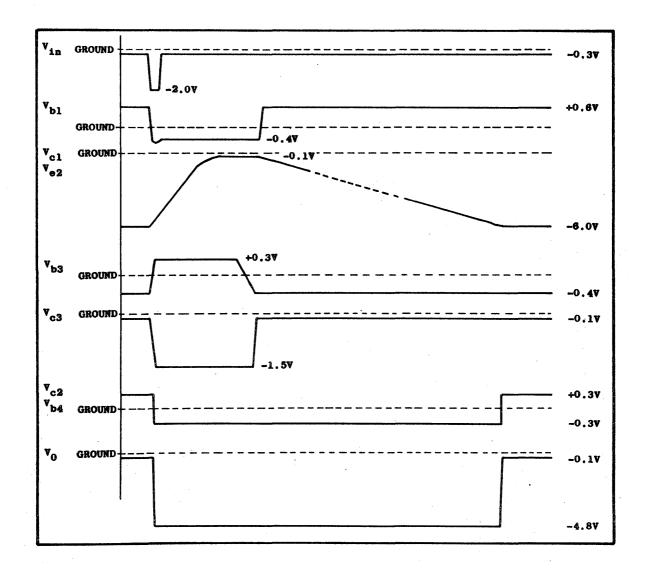

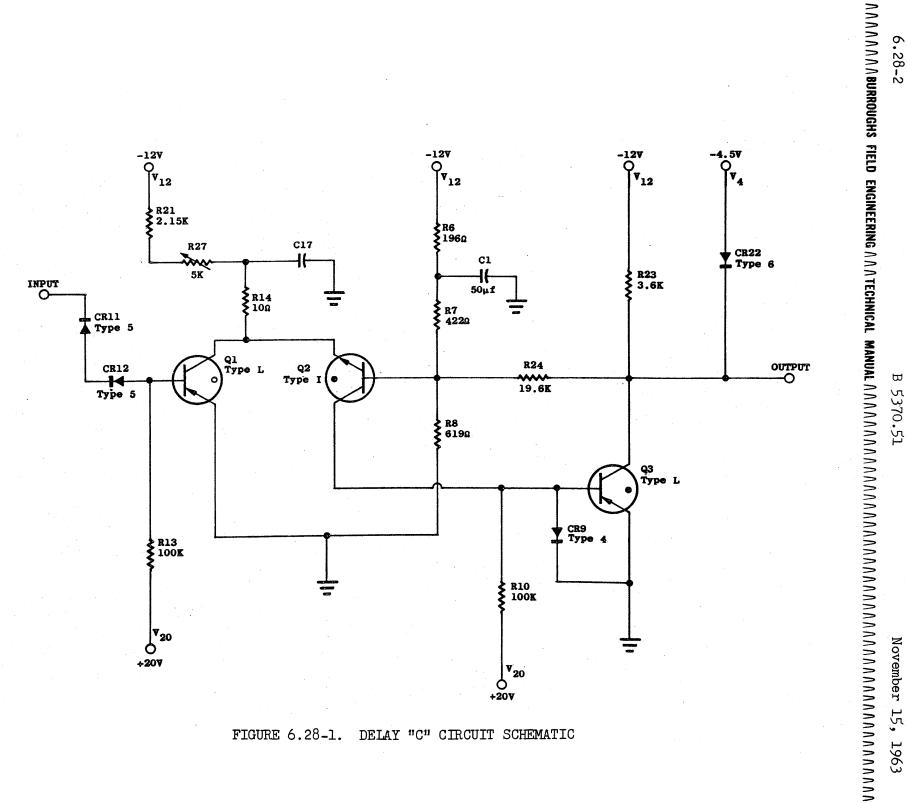

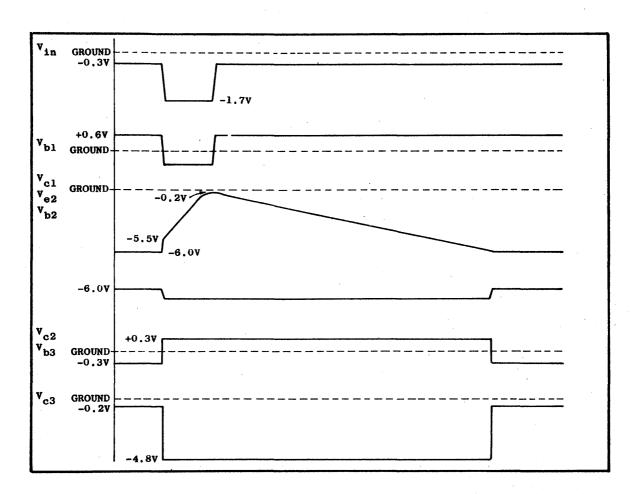

| 6.28    | Delay "C"                             | November 15, |        |

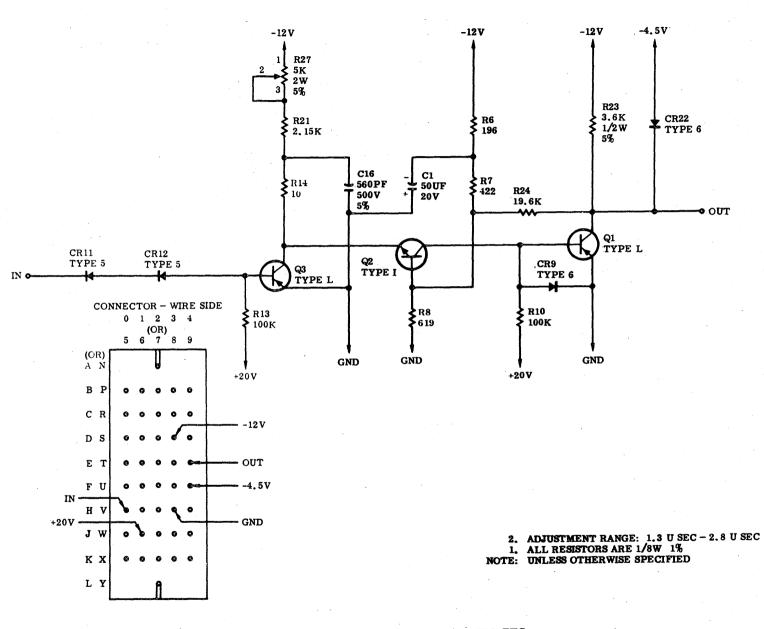

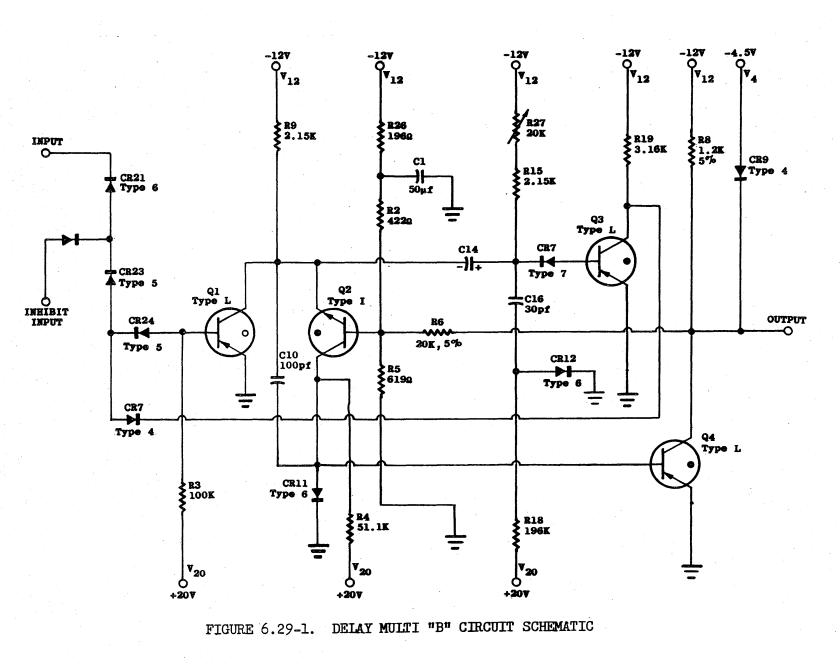

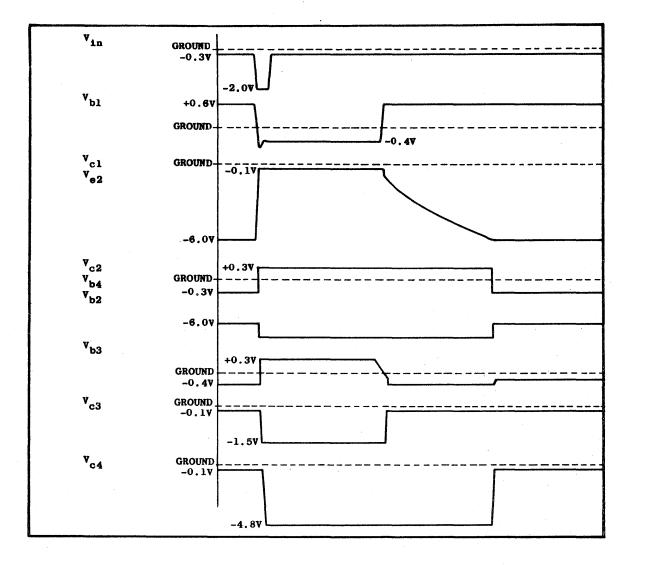

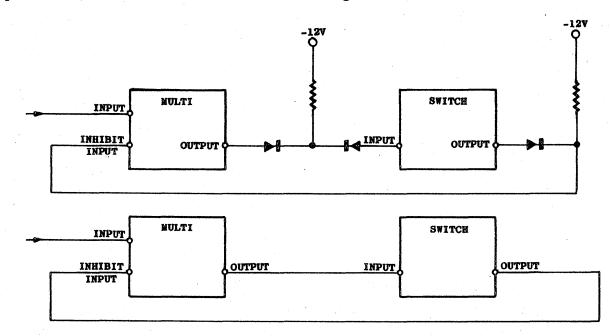

| 6.29    | Multi                                 | November 15, | 1963   |

| 6.30    | Compressor                            | November 15, | 1963   |

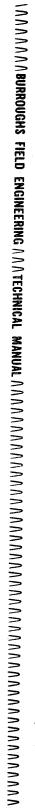

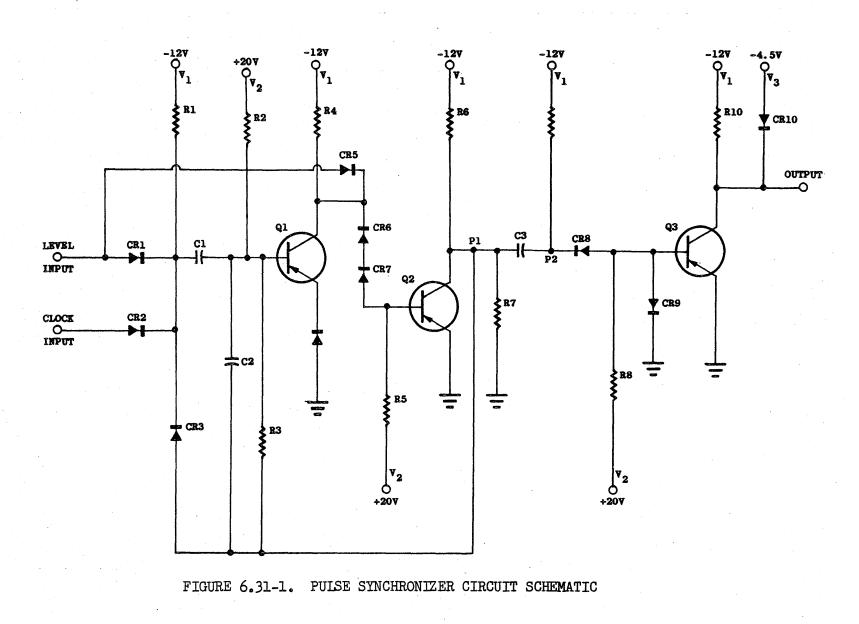

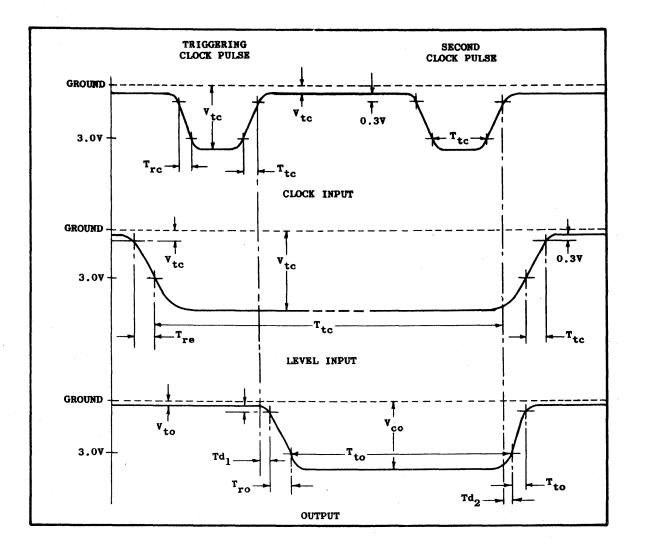

| 6.31    | Pulse Synchronizer                    | November 15, | 1963   |

| 6.32    | Clock Oscillator & Squaring Amplifier | November 15, | 1963   |

| 6.33    | Blocking Oscillator & Line Driver     | November 15, | 1963   |

| 6.34    | Direct-Coupled Local Clock Driver and |              |        |

|         | Variable Bias                         | November 15, | 1963   |

| 6.35    | Double Driver 90                      | November 15, |        |

| 6.36    | Inverter Driver 90                    | November 15, |        |

| 6.37    | Flip-Flop Amplifier                   | November 15, |        |

|         |                                       |              | _/ _ / |

| 7.      | FUNCTIONAL DESCRIPTION                |              | 7.0(0) |

| 7.1     | General                               | November 15, |        |

| 7.2     | Classification of DC Supplies         | November 15, |        |

| 7.3     | +20V Electrical Switch                | November 15, | 1963   |

| 7.4     | +100V Electrical Switch               | November 15, |        |

| 7.5     | AC Circuits                           | November 15, |        |

| 7.6     | Elapsed Time Indicator                | November 15, |        |

| 7.7     | Meter Check Switch                    | November 15, | 1963   |

| 7.8     | Meter Check Circuit                   | November 15, | 1963   |

| 7.9     | Control Relays                        | November 15, | 1963   |

| 7.10    | Voltage Sensing                       | November 15, | 1963   |

| 7.11    | Voltage Sensing Package               | November 15, | 1963   |

| 7.12    | Voltage Reference Package             | November 15, | 1963   |

| 7.13    | -12V Regulator                        | November 15, | 1963   |

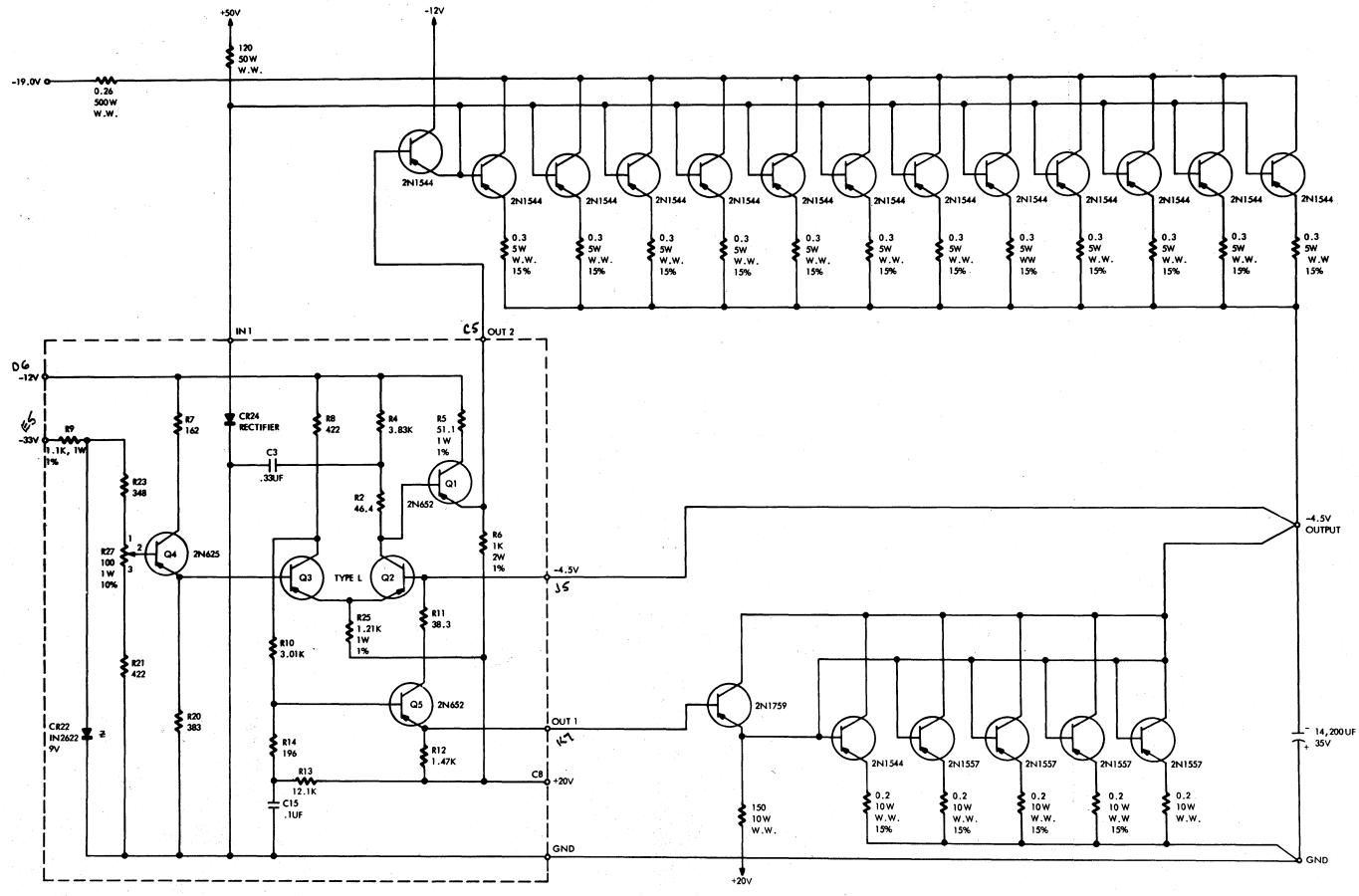

| 7.14    | -4.5V Regulator                       | November 15, | 1963   |

| 7.15    | -1.2V Regulator                       | November 15, | 1963   |

| 7.16    | Power Off Circuit                     | November 15, |        |

|         |                                       |              |        |

ii

τ-τ・τ

L NOILDES

PREVENTIVE MAINTENANCE

YJIAU L.I

۱

Not Applicable.

1.2-1

#### 1.2 WEEKLY

Monitor all AC and DC voltages from the Power Supply meters.

Check fan operation.

November 15, 1963

τς.ογες α

τ-ε.τ

T.3 MONTHLY

1. Inspect the air filters and replace if necessary.

2. Clean fan screens.

1.4-1

#### 1.4 QUARTERLY

- 1. Verify voltage sensing. Refer to Section 5.6 for procedure.

- 2. Monitor the voltage regulator outputs according to Section 5.5. Use a precision voltmeter.

- 3. Check terminals for tightness.

1.5-1

#### 1.5 SEMI-ANNUALLY

- 1. Scope all DC supplies for ripple. For ripple specifications, see Table 5.6-1.

- 2. Check the DC meter and the ammeter for proper adjustment. See Section 3 for adjustment procedure.

- 3. Visually check all capacitors for any leakage and replace if necessary.

- 4. Lubricate Rotron Muffin fans with Anderol L-826 using special oil injector.

Oil injector .... Part No. 11838588 Oil ..... Part No. 11838596

#### PROCEDURE

The exhaust fans are lubricated by inserting the Oil Injector needle through a selfsealing rubber cap, located in the center of the motor hub.

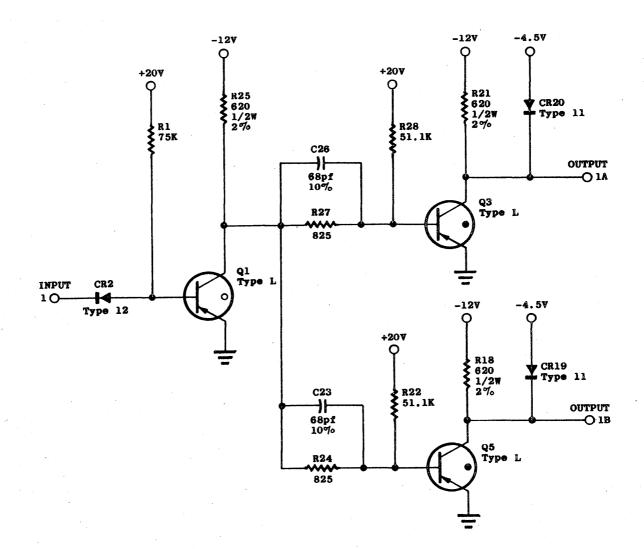

#### NOTE

On most units, a Gold Seal label is mounted over the rubber plug. This series of fans is called the Gold Seal series.

There are 8 fans in the Power Supply. Five are located at the top of the cabinet, and three directly above the transformers. These three are accessible by removing two screws and swinging the assembly down. The assembly is hinged to allow this access.

- 1. Fan grill, remove and clean as necessary.

- 2. Remove air from Oil Injector by holding the needle up, and pressing on the plunger.

- 3. Place Oil Injector needle at the center of circle marked on the Gold label (on the 034 series, place the needle approximately 1/8" from the edge of the rubber cap).

- 4. Position the needle at an angle of approximately 45 degrees to the center of the rubber cap.

- 5. Pierce the label and the concealed self-sealing rubber cap located under the label.

- 6. Insert the needle approximately 1/4" deep.

- 7. Depress the plunger of the Oil Injector to allow approximately 1/16" of oil to escape. Rotating the fan will relieve air pressure and allow oil to flow into the oil chamber.

1.6-1

#### 1.6 ANNUALLY

- 1. Visually check the Surge Suppressors for any trace of overloads.

- 2. General visual inspection of all components and wire for overloads, overheating, or any other general damage.

2.1-1

### SECTION 2

### TROUBLESHOOTING

#### 2.1 PRECAUTIONS

- 1. Do not use a battery-buzzer for continuity checking. The buzzer current exceeds the maximum current rating for diodes and transistors in the system.

- 2. Do not use the first two low scales (X1 or X10) on the Triplett ohmmeter for continuity checking. For these scales, the meter current exceeds the maximum current rating for diodes and transistors in the system.

- 3. Do not remove packages or diode sticks when Power is UP.

- 4. Care must be taken when using Scope or Jumper Clip Leads to prevent touching adjacent pins. Use Minigator Clips with insulators or the Wire Wrap Pin Probe Tip (Part No. 11838547).

- 5. Use extreme caution when working on the plug-in side of the panels. Avoid hitting packages when moving the scope.

- 6. Do not attempt to force a TRUE level with -12V. In all cases, the desired effect can be obtained either by the use of a ground clip, or by taping off one or more diodes.

- 7. A ground jumper may be used to force a FALSE level.

NOTE

Connect clip to the point to be grounded prior to making ground connection.

- 8. Do not pull Cable Plugs with POWER ON at either end of the cable.

- 9. Only soldering irons that have an isolation transformer may be used.

- 10. Scope ground to prevent ground loops and noise interference use only the ground clip on the scope probe. Attach it to a suitable ground as near as possible to the point being observed.

#### 2.2 AC CIRCUITS

The convenience outlets, the -24V and the 120V Supplies, are controlled by the primary wall breaker.

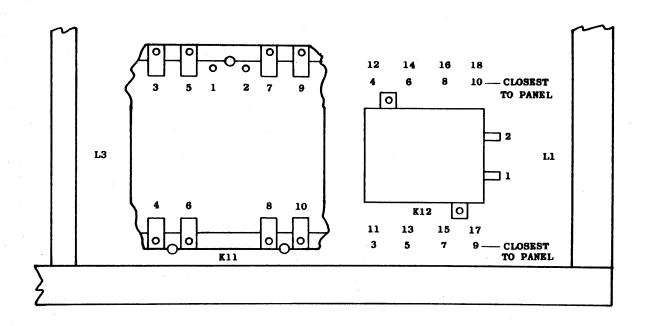

The AC Input to the DC Power Supplies is controlled by Kll and Kl2 contactors.

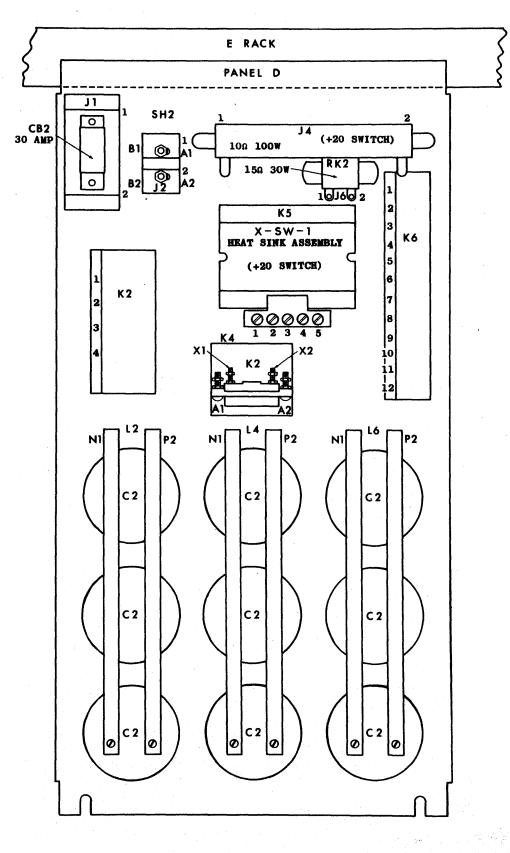

FIGURE 2.2-1. AC CONTROL CONTACTORS

2.3-1

#### 2.3 DC POWER SUPPLIES

The DC Power Supplies are all of the constant voltage type. The transformers have associated tuning capacitors. See Section  $\mu$  for the physical layout of Power Supply components.

The SP (Surge Suppressors) in the secondary are selenium type rectifiers. These are active for high surge currents and can possibly short. They are used to protect the diode rectifiers.

There are two supplies whose outputs are controlled by electronic switches. They are the +20V and +100V supplies.

When troubleshooting these voltages, the Power Supply monitoring system will show that the voltages are present even though they are not being delivered to the system.

If the +20V electronic switch is open, the power regulators of the system will not operate. If it is shorted, the DC LOCKOUT switch on the Display and Distribution Panel will not turn the power regulators off.

If the +100V electronic switch circuit is open, the undervoltage sensing will indicate +100V undervoltage. If it is shorted, the system Flip-flops will be in random on-off conditions when power is applied. If the +100V switch is working properly, they should come on cleared.

2.4-1

#### 2.4 VOLTAGE REGULATORS

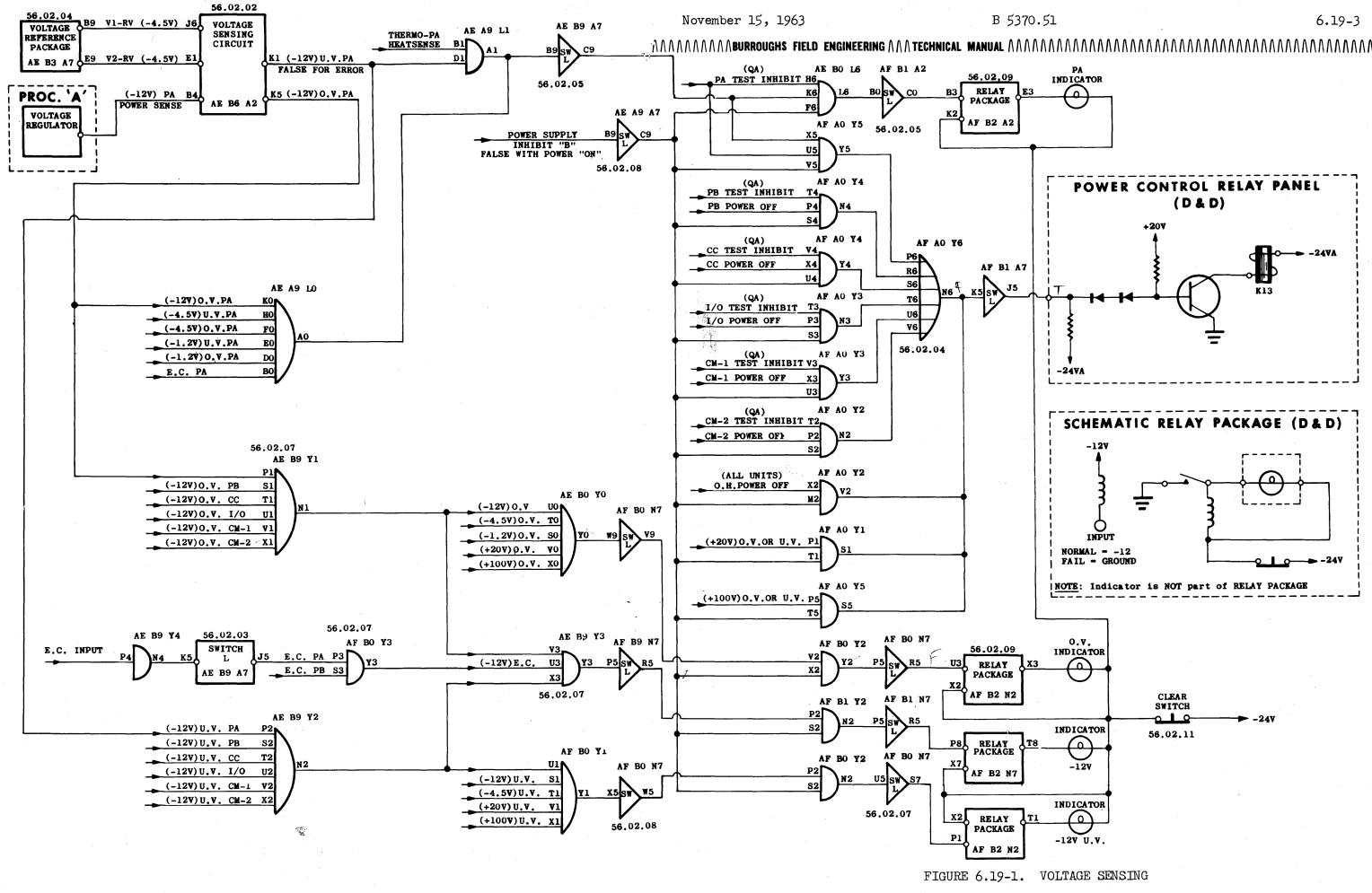

The -12V regulator controls the -4.5V and -1.2V regulators. The -4.5V and -1.2V regulators cannot operate until -12V is present.

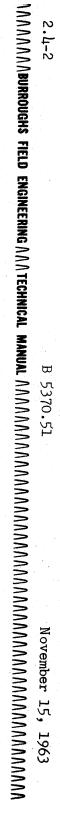

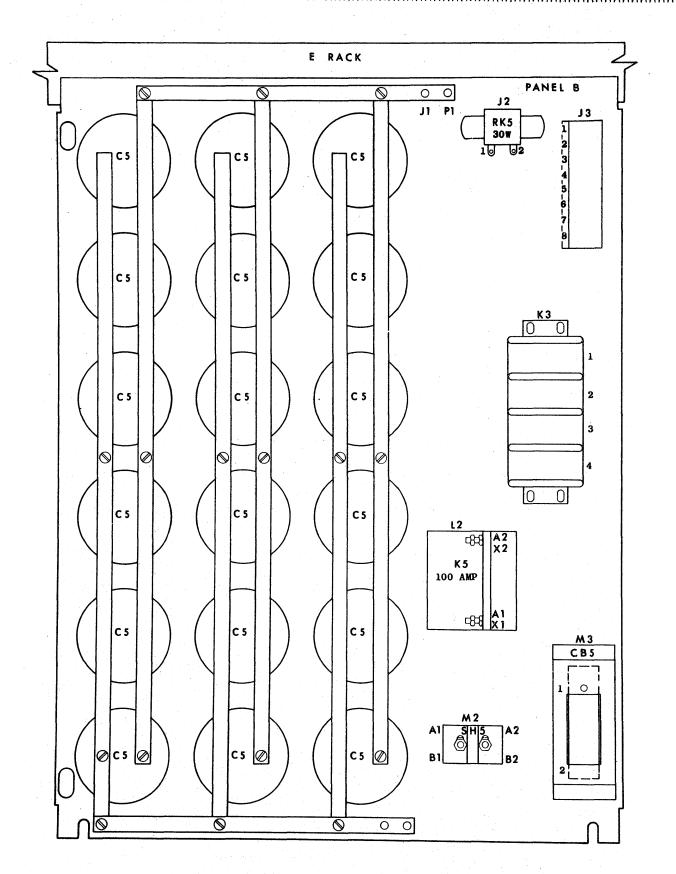

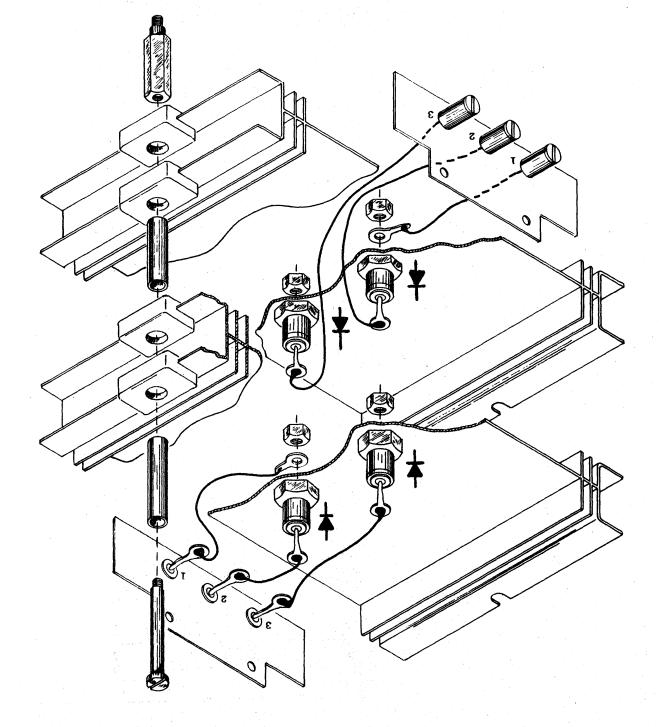

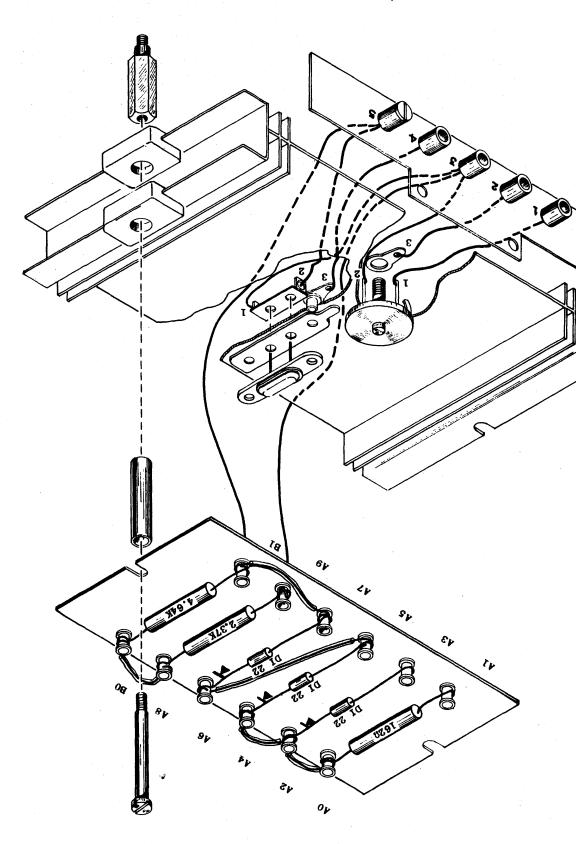

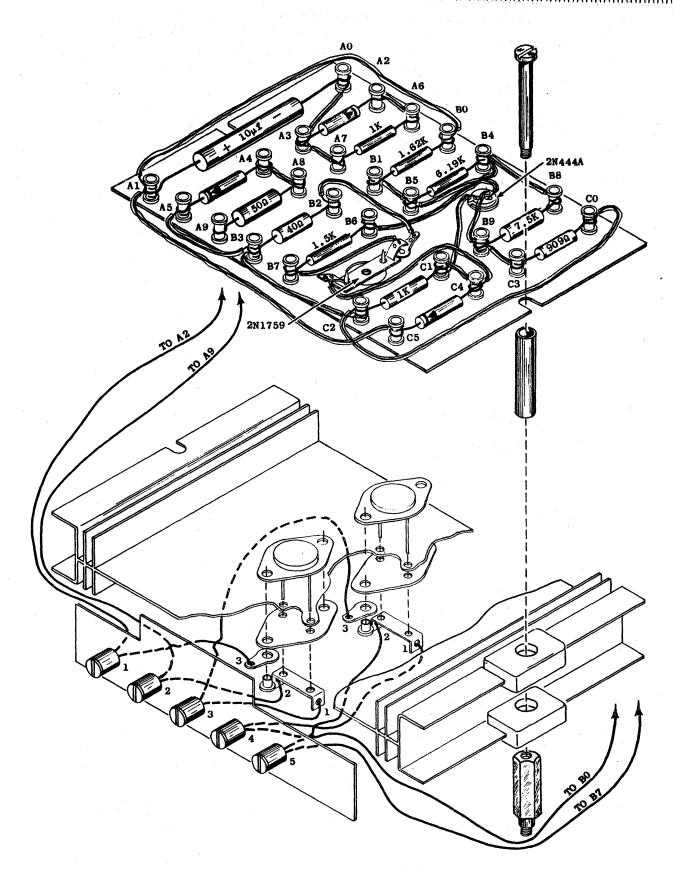

It is possible for the -12V regulator to operate with one or more of the output transistors open, depending on load requirement. Each heatsink assembly contains three (3) power transistors with common collector and base connections. See Figure 2.4-1.

If an output transistor opens, it can be located by checking the voltage drop across the 0.2 ohm emitter resistor while the regulator is operating.

The regulator will not shut down due to an open output transistor unless the current load becomes too high for the remaining transistors. When this occurs, one of the remaining transistors will short, and an overvoltage condition will be displayed by the voltage sensing panel.

If an output transistor shorts, the output of the regulator will go from -12V to -19V. A -12 overvoltage will be indicated, and the power supply will shut down. The voltage sensing panel will also indicate in which cabinet the failure occurred. With power off, disable the voltage sensing for the cabinet indicated on the voltage sensing panel.

Refer to Table 3.1-1 for the Inhibit points. Disconnect the emitter terminals of one heatsink. Refer to Figures 2.4-1 and 2.4-2.

Apply power and monitor the output of the -12V regulator if it is still at -19V. Shut power down and reconnect the emitter terminals. Continue this procedure until the shorted heatsink assembly is located. When the proper heatsink assembly is located, the output of the regulator should read -12V. Remove the heatsink and locate the shorted transistor. Another cause of -12V overvoltage is the loss of one of the control voltages on the regulator. These are the -33V and +50V. Do not leave the -19V from the regulator on the system for longer than necessary.

If a failure occurs in the -4.5V regulator or the -1.2V regulator, the same procedure can be used as described for the -12V regulator.

#### NOTE

If the -12V regulator fails in Central Control (no output), there will be no voltage sensing available. The voltage sensing circuits are supplied operating voltages from Central Control. Power could be applied and the system would look normal, except there would be no +100V for Flip-flop clear.

FIGURE 2.4-1 HEATSINK CONNECTION

2.4-3

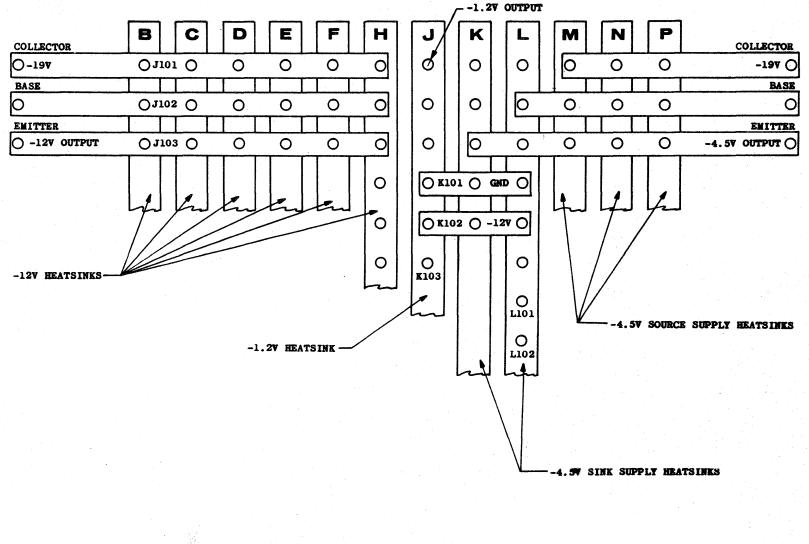

### FIGURE 2.4-2. VOLTAGE REGULATOR LOCATOR

2.5-1

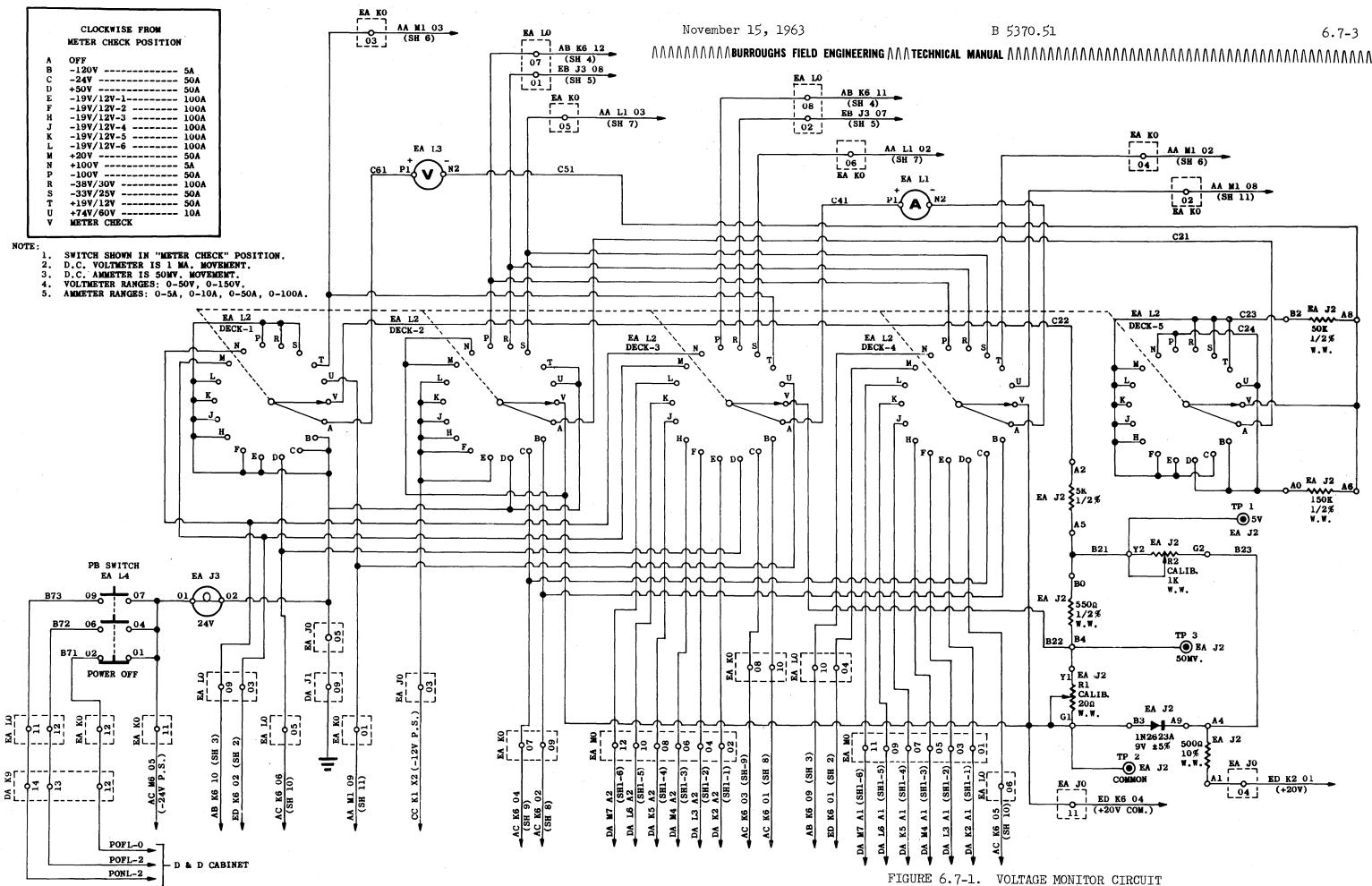

#### 2.5 VOLTAGE SENSING

The Voltage Sensing circuits can be checked by comparing the operation of one to another. If the voltage regulator outputs are at the proper value and a fail condition is still displayed, disable sensing for that unit. Refer to Table 3.1-1.

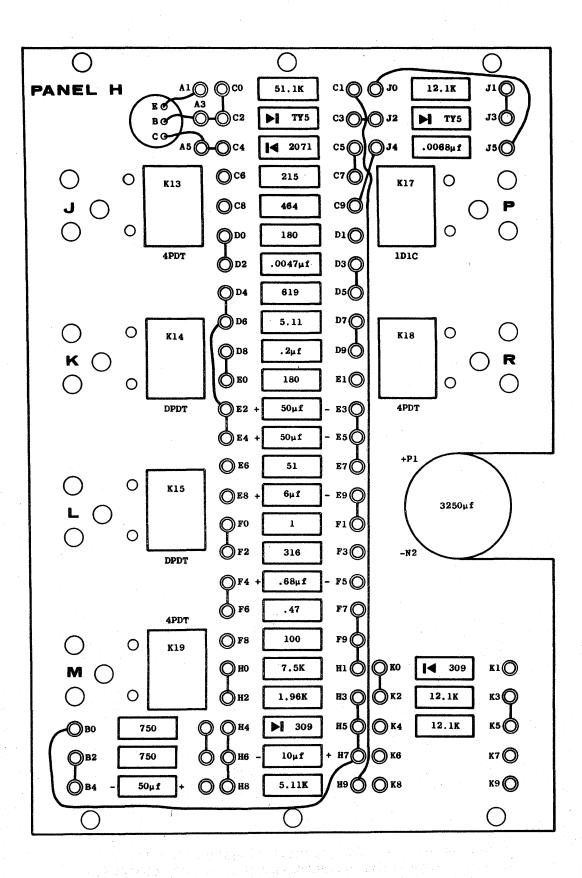

After sensing is disabled, apply power and compare the failing circuit to an operating one. See Figure 2.5-1 for Sensing Package Layout.

November 15, 1963

| ŀ | <b>.</b> |   |         |                                                        | PANE                      | L — F     | l                                                                  |                                                                       |                                                    |   |                                                                           |   |   |                    | <u> </u> |                   |   |                   |   | PANEL             | - E |                   |                | <u> </u> |   |                                                   |   | - <u></u> |                                         |                                   |

|---|----------|---|---------|--------------------------------------------------------|---------------------------|-----------|--------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------|---|---------------------------------------------------------------------------|---|---|--------------------|----------|-------------------|---|-------------------|---|-------------------|-----|-------------------|----------------|----------|---|---------------------------------------------------|---|-----------|-----------------------------------------|-----------------------------------|

|   | 4        | • |         | 3                                                      | 2                         | 2         | ٩                                                                  | l                                                                     | C                                                  | ) | 9                                                                         | ) | 8 | B                  | 7        |                   | 6 | 5                 | 5 | 5                 | 4   |                   | 3              | 3        | 2 | 2                                                 | 1 |           | 0                                       | )                                 |

|   |          |   |         |                                                        |                           |           |                                                                    |                                                                       |                                                    |   | SW-L<br>1. PA<br>FAIL<br>2. PB<br>FAIL<br>3. CC<br>FAIL<br>4. I/O<br>FAIL |   |   | •95C<br>-4.5<br>CC |          | VSC<br>-4.5<br>PB |   | VSC<br>-4.5<br>PA |   | vsc<br>-1.2<br>CC |     | VSC<br>-1.2<br>PA | - <b>V</b><br> |          |   | C50<br>FROM<br>AH-S1<br>ON CC<br>DISPLAY<br>PANEL |   |           | C50<br>POWER<br>FROM<br>CC<br>REGULATOR | C 50<br>PA<br>SENSE<br>&<br>POWER |

| А |          |   |         |                                                        |                           |           |                                                                    |                                                                       |                                                    |   | 4. 1/0<br>FAIL<br>5. O.H.<br>POWER<br>SUPPLY                              |   |   |                    |          |                   |   |                   |   |                   |     |                   |                |          |   | CABLE<br>NO. 64                                   |   |           | CABLE<br>NO. 140                        | CABLE<br>NO. 62                   |

|   | ·        |   | <u></u> |                                                        |                           |           |                                                                    |                                                                       |                                                    |   | SW-L<br>1. CM-1                                                           |   |   | VSC                |          | VSC               |   | ¥8C               |   | ¥8C               |     | VSC               |                |          |   | C50                                               |   |           |                                         | C50                               |

|   |          |   |         |                                                        |                           |           |                                                                    |                                                                       |                                                    |   | FAIL<br>2. CM-2<br>FAIL<br>3. O.H.<br>FAIL<br>4. BC<br>CM-1               |   |   | -4.5<br>CM-2       |          | -4.5<br>CM-1      |   | -4.5<br>I/O       |   | -1.2<br>I/0       |     | -1.2<br>PB        |                |          |   | I/O 2<br>SENSE<br>&<br>Power                      |   |           |                                         | I/O 1<br>SENSE<br>&<br>POWER      |

|   |          |   |         |                                                        |                           |           |                                                                    |                                                                       |                                                    |   | 5. EC<br>CM-2                                                             |   |   |                    |          |                   |   |                   |   |                   |     |                   |                |          |   | CABLE<br>NO. 65-2                                 |   |           |                                         | CABLE<br>NO. 65-1                 |

|   | ,        |   |         | CONJECTORS<br>TO                                       | KPK<br>CM-1               | KPK<br>PA | SW-L<br>1. CM-1                                                    | SW-L<br>1. I/O                                                        |                                                    |   | SW-L<br>1. INH.                                                           |   |   | VSC                |          | VSC               |   | VSC               |   | VSC               |     | ▼ SC              | VRP            |          |   | C50                                               |   |           |                                         | C50                               |

|   |          |   |         | CONNECTORS<br>TO<br>INDICATORS<br>&<br>CLEAR<br>BUTTON | CM-2<br>POWER<br>OVERHEAT | PB<br>CC  | RELAY<br>2. CM-2<br>RELAY<br>3. O.H.<br>RELAY<br>4. POWER<br>RELAY | 1. I/O<br>RELAY<br>2. PA<br>RELAY<br>3. PB<br>RELAY<br>4. CC<br>RELAY |                                                    |   | LEVEL<br>2. EC<br>1/0<br>3. EC CC<br>4. EC PB<br>5. EC PA                 |   |   | -12<br>CC          |          | -12<br>PB         |   | -12<br>PA         |   | -1.2<br>CM-1      |     | +20               |                |          |   | I/O 4<br>SENSE<br>&<br>POWER                      |   |           |                                         | I/O 3<br>SENSE<br>&<br>POWER      |

| Б |          |   |         |                                                        |                           |           |                                                                    |                                                                       |                                                    |   |                                                                           |   |   |                    |          |                   |   |                   |   |                   |     |                   |                |          |   | CABLE<br>NO. 65-4                                 |   |           |                                         | CABLE<br>NO. 65-3                 |

| В |          |   |         |                                                        | КРК<br>12                 | KPK<br>EC | SW-L                                                               |                                                                       | SW-L<br>1. EC                                      |   | S₩-L<br>1. +20¥                                                           |   |   | vsc                | <u>├</u> | ¥8C               |   | VSC               |   | VSC               |     | <b>∀</b> SC       |                | VRP      |   | .C50                                              |   |           |                                         | C50                               |

|   |          |   |         |                                                        | -1.2<br>-4.5              | UV<br>OV  | 1. +20<br>RELAY<br>212<br>RELAY<br>31.2<br>RELAY                   |                                                                       | 1. EC<br>RELAY<br>2. OV<br>RELAY<br>3. UV<br>RELAY |   | OV/UV                                                                     |   |   | -12<br>CM-2        |          | -12<br>CM-1       |   | -12<br>I/0        |   | -1.2<br>CM-2      |     | +100              |                |          |   | SPECIAL<br>D/D<br>VOLTAGES                        |   |           |                                         | PB<br>SENSE<br>&<br>POWER         |

|   |          |   |         |                                                        | +100                      | +20       | 4. 4.5<br>RELAY<br>5. +100<br>RELAY                                |                                                                       |                                                    |   | 212<br>FAIL<br>31.2<br>FAIL<br>44.5<br>FAIL<br>5. +100V<br>OV/UV          |   |   |                    |          |                   |   |                   |   |                   |     |                   |                |          |   | NOT<br>SENSING<br>LEVELS<br>CABLE<br>NO. 66       |   |           |                                         | CABLE<br>NO. 63                   |

# в 5370.51

## FIGURE 2.5-1. SENSING PACKAGE LAYOUT (PACKAGE SIDE)

#### 2.6 POWER CONTROL RELAYS

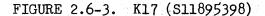

The Power Control Panel Relays are shown in the following figures.

#### COIL CHARACTERISTICS

COIL RESISTANCE: 300 OHMS ± 10 PERCENT @ 25° C. OPERATING CURRENT: .080 AMPS NOMINAL. OPERATING VOLTAGE: 12V DC.

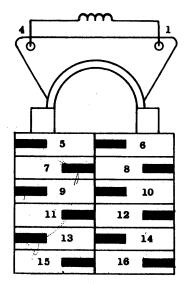

FIGURE 2.6-1. K13, 18, 19 (S-52066-21)

#### COIL CHARACTERISTICS

COIL RESISTANCE: 500 OHMS ± 10 PERCENT @ 25° C. OPERATING CURRENT: .048 AMPS NOMINAL. OPERATING VOLTAGE: 24V DC.

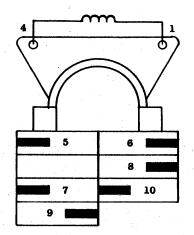

FIGURE 2.6-2. K14 and K15 (S-11895380)

Printed in U.S.A.

2.6-1

The Power ON-OFF sequencing is controlled by relays located in the D and D cabinet. Refer to Figure 2.6-4 for component layout.

POWER ON CYCLE

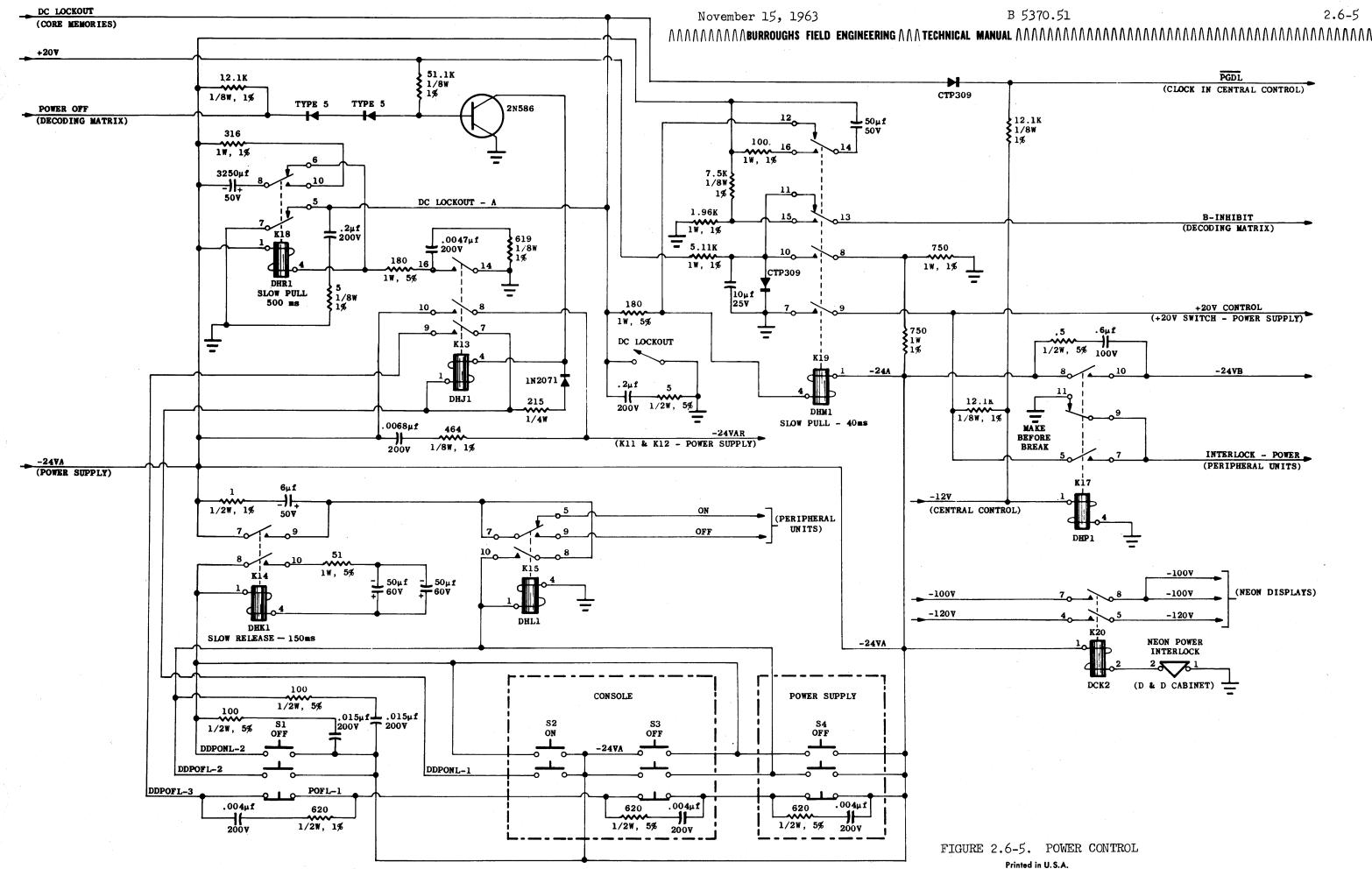

Refer to Figure 2.6-5 for Power Control Schematic.

1. Pushing the ON button will pick K13 (DHJ1), which will then latch in.

a. The -24VA-R line should go from open to -24V.

2. K18 (DHR1) should pick approximately 400 ms later than K13 (DHJ1).

a. PGDL' should go from -0.3V to -12V.

b. DC Lockout to core memory should go from ground to -24V.

3. K19 (DHM1) should drop out.

a. +20V control line should go to -1.5V.

- b. Inhibit-B line should remain true for approximately 20 ms.

- c. The Power Interlock line will go to -12V if K17 (DHP1) is picked.

- 4. Kl4 (DHK1) is also picked by pushing the ON button. It should drop out approximately 150 ms after release of the ON button.

November 15, 1963

### B 5370.51

2.6-3

FIGURE 2.6-4. RELAY PANEL D & D

November 15, 1963

- a. While Kl4 (DHK1) is picked, the peripheral unit ON bus should have -24V on it.

- 5. Applying -12V to K17 (DHP1) will cause it to pick.

- a. The Power Interlock line should go from ground to the same level as the +20V control line. (Ground, if K19 (DHM1) is picked; -12V if K19 (DHM1) is dropped out).

- b. The -24V-B line should go from open to -24V.

#### POWER OFF CYCLE

Refer to Figure 2.6-5 for Power Control Schematic.

- 1. Pushing the OFF button will cause K13 (DHJ1) to drop out.

- a. The -24VA-R line will go from -24V to open.

- 2. K18 (DHR1) will drop out.

- a. PGDL' will go from -12V to -0.3V.

- b. DC Lockout to core memories will go to ground.

- 3. K19 (DHM1) will pick approximately 35 ms after DC Lockout becomes grounded.

- a. Inhibit-B will go to approximately -5V.

- b. The +20V control line will go to ground.

- c. The Power Interlock line will go to ground if K17 (DHP1) is picked.

- 4. K14 (DHK1) and K15 (DHL1) should both pick and remain picked for approximately 150 ms after the OFF button is released.

- a. The peripheral unit OFF bus should go from open to -24V and remain as long as K14 (DHK1) is picked.

- 5. Removing the -12V from K17 (DHP1) causes it to drop out.

- a. The Power Interlock level becomes grounded.

- 6. K2O (DCK2) Neon Power Interlock. This relay is controlled by the neon interlock switch located on the D & D cabinet.

NOTE

When measuring the -20V, special attention should be given the reading because -100V is also present thru the neon drivers. It may appear that -120V is present when it is not.

March 29, 1965

### B 5370.51

2.7-1

### 2.7 RIN INDEX

RIN INDEX FOR THE B 5370 POWER SUPPLY AND REGULATORS (11831450)

| RIN NO. | INSTAL.<br>TIME IN<br>HOURS | PRE-<br>REQUISITE | UNITS<br>EFFECTED        | DESCRIPTION                                                                                           |

|---------|-----------------------------|-------------------|--------------------------|-------------------------------------------------------------------------------------------------------|

| 5002    | 1.0                         | -                 | 102 🗢 143                | Improve reliability of the +20V switch.                                                               |

| 5007    | 0.5                         |                   | 102 🖚 143                | Replacement of the AC input box cover.                                                                |

| 5008    | 1.0                         |                   | 10 <b>2 → 1</b> 43       | Replacement of the Kl2 relay to improve reliability.                                                  |

| 5011    | 1.0                         |                   | 102 🖚 143                | Addition of a resistor to reduce transient surge current in the $-24V$ supply.                        |

| 5024    | 1.0                         |                   | 10 <b>2 →</b> 143        | Replace end panel washers with the pro-<br>per size.                                                  |

| 5034    | 2.0                         |                   | 102 <del>-&gt;</del> 143 | Improve heat dissipation of the 30 watt<br>resistors by removing insulation from<br>leads.            |

| 5035    | 1.0                         |                   | 102 🗢 143                | Installation of spacers to high wattage resistors mounts, in order to provide better air circulation. |

|         |                             |                   |                          |                                                                                                       |

|         |                             |                   |                          |                                                                                                       |

|         |                             |                   |                          |                                                                                                       |

|         |                             |                   |                          |                                                                                                       |

|         |                             |                   |                          |                                                                                                       |

|         |                             |                   |                          |                                                                                                       |

|         |                             |                   |                          |                                                                                                       |

3.1-1

#### SECTION 3

#### ADJUSTMENTS

#### 3.1 VOLTAGE REGULATOR

The Voltage Regulators are adjustable in each cabinet.

#### PROCEDURE

To make adjustments on the voltage regulator, perform the following steps:

- 1. Connect a precision voltmeter to terminal CSM1 of the voltage regulator. Check for -12V.

- 2. Adjust R36 on the -12V regulator parallel plate package until the output is -12V.

- 3. Connect the precision voltmeter to terminal CSL1 of the voltage regulator. Check for -4.5V.

- 4. Adjust R27 on the -4.5V regulator parallel plate package until the output is -4.5V.

- 5. Connect the precision voltmeter to terminal CSN1 of the voltage regulator. Check for -1.2V.

- 6. Adjust R27 on the -1.2V regulator parallel plate package until the output is -1.2V.

#### -12V EXCESS CURRENT ADJUSTMENT

The overcurrent potentiometer should be adjusted so that the sensing threshold is 10 to 15 percent above the desired operating range of the regulator.

In order to determine the threshold setting for the overcurrent potentiometer, it is desirable to inhibit the power failure sensing so that the indicator lights will come on without power going down. This can be done by grounding the test inhibit line for the cabinet of interest. Refer to Table 3.1-1. This line is located on the Power Sensing Panel in the D and D cabinet.

With the potentiometer R35 all the way clockwise, begin turning it counterclockwise until the AMP light comes on. The threshold setting will then be equal to the -12V load current at the time of setting.

To achieve the 10 to 15 percent margin for operation, set the threshold at nominal load and then back potentiometer R35 off (clockwise) by the proper amount. Potentiometer R35 is designed so that the threshold changes approximately 5 amps per turn.

| and the second |                          |

|------------------------------------------------------------------------------------------------------------------|--------------------------|

| UNIT                                                                                                             | TEST INHIBIT PIN (D & D) |

| PA                                                                                                               | AFAO U5                  |

| PB                                                                                                               | AFAO T4                  |

| CC                                                                                                               | AFAO V4                  |

| I/0                                                                                                              | AFAO T3                  |

| CM-1                                                                                                             | AFAO V3                  |

| CM-2                                                                                                             | AFAO T2                  |

| · · · · · · · · · · · · · · · · · · ·                                                                            |                          |

#### TABLE 3.1-1. TEST INHIBIT

In order to lower the range of potentiometer R35 and increase its sensitivity at low normal loads, it is recommended that one of the two parallel .02 ohm resistors in the output of the -12V regulator be disconnected. This may be done for nominal load less than 40 amps. The sensitivity of potentiometer R35 is then increased to about 2.5 amps per turn and the minimum threshold lowered to about 15 amps.

3.2-1

### 3.2 CALIBRATION PROCEDURE FOR METER CHECK CIRCUIT

- 1. Remove hole plug located below test points on the meter panel.

- 2. Pre-set Rl and R2 fully counterclockwise.

- 3. Rotate meter selector switch to "Meter Check" position.

- 4. Apply POWER to the system.

- 5. Adjust Rl clockwise for 5.0 ± .05 volts at TPl (1) to common TP2 (-).

- 6. Adjust R2 clockwise for 50.0 ± .5 millivolts at TP3 (+) to common TP2 (-).

- 7. Recheck voltage at TP1. If it is not 5.0 ± .05 volts, repeat steps 5, 6, 7 and 8. If the voltage is correct, calibration is complete and both the Ammeter and Voltmeter should indicate full scale deflection. Accuracy of both meters should be 2 percent or better.

- 8. Insert hole plugs.

4.1-1

**SECTION 4**

### ASSEMBLY AND DISASSEMBLY

4.1 POWER SUPPLY

#### INTRODUCTION

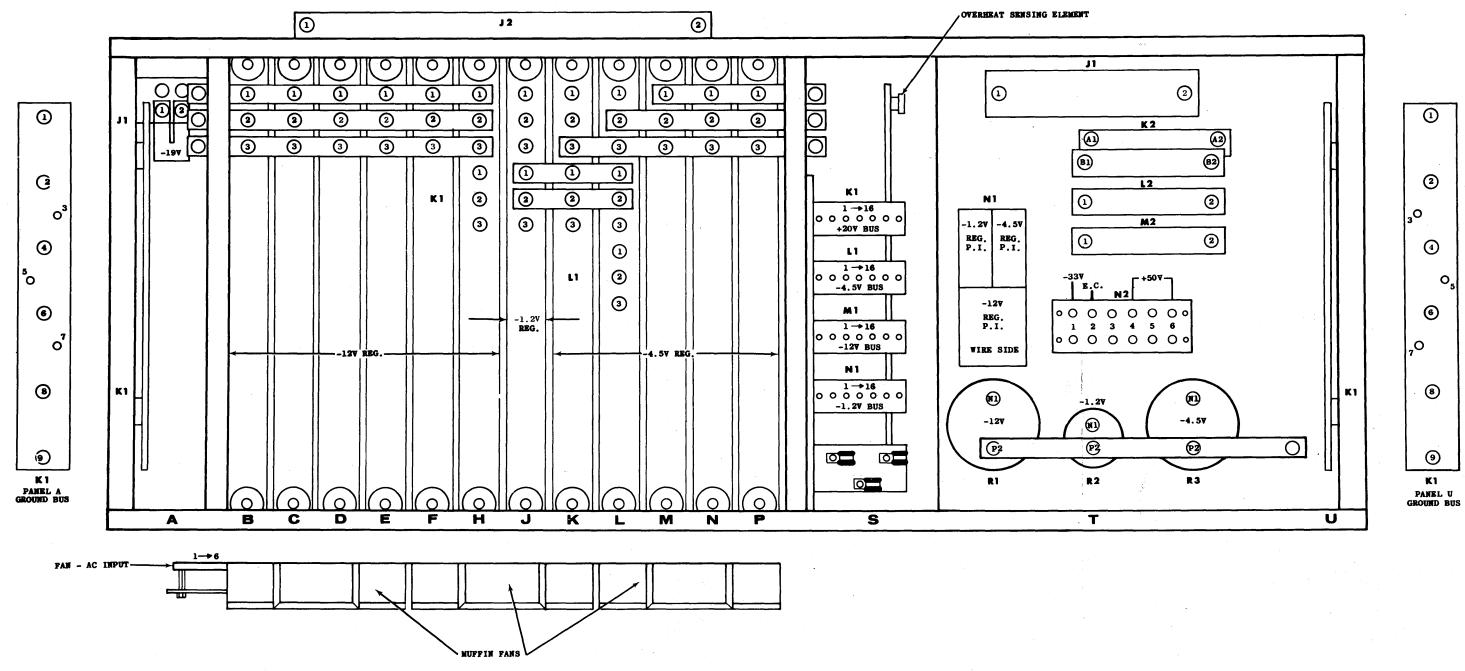

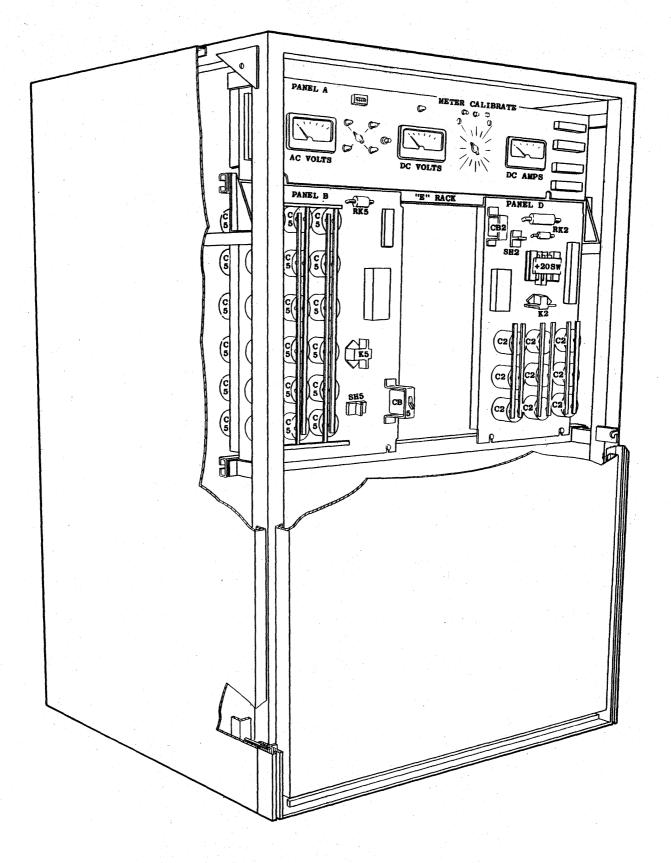

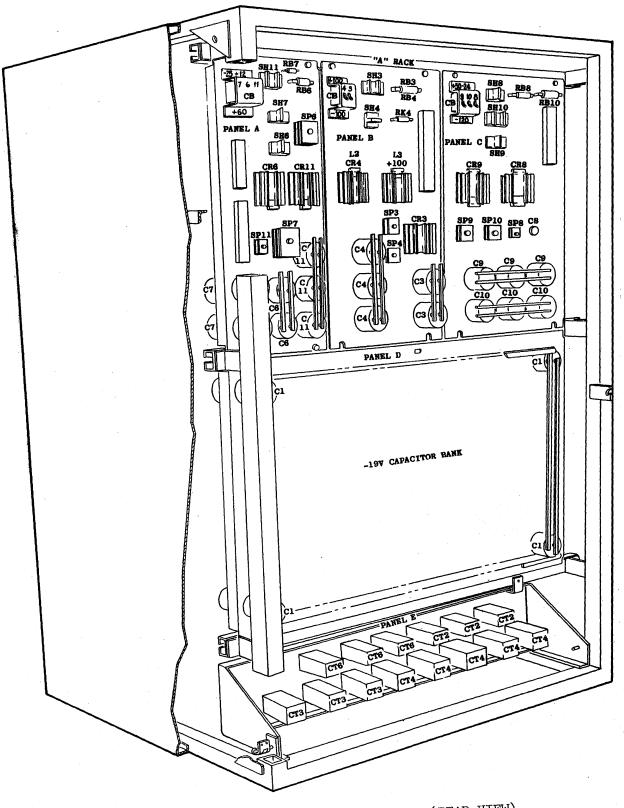

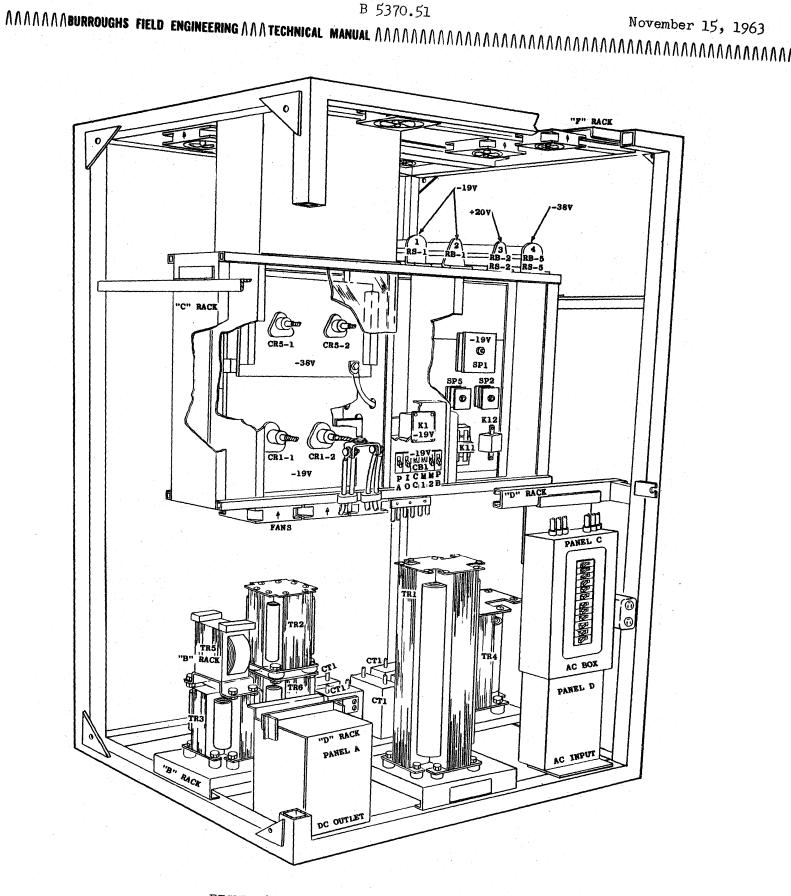

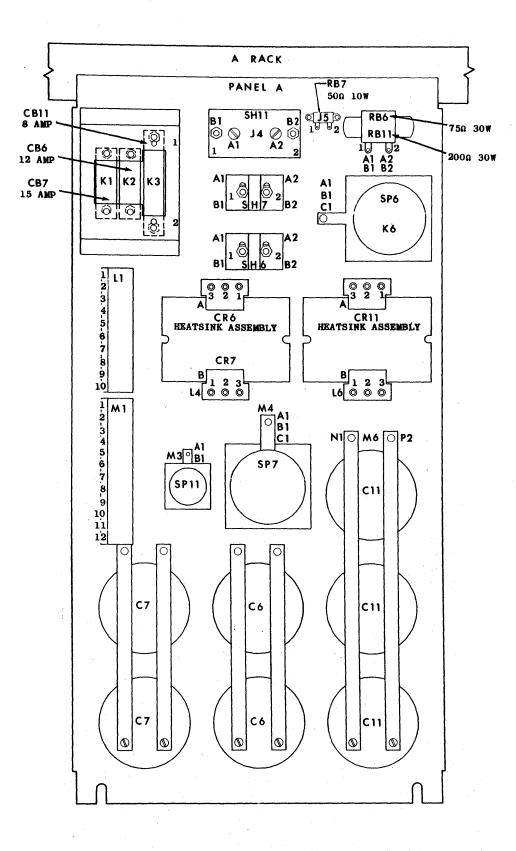

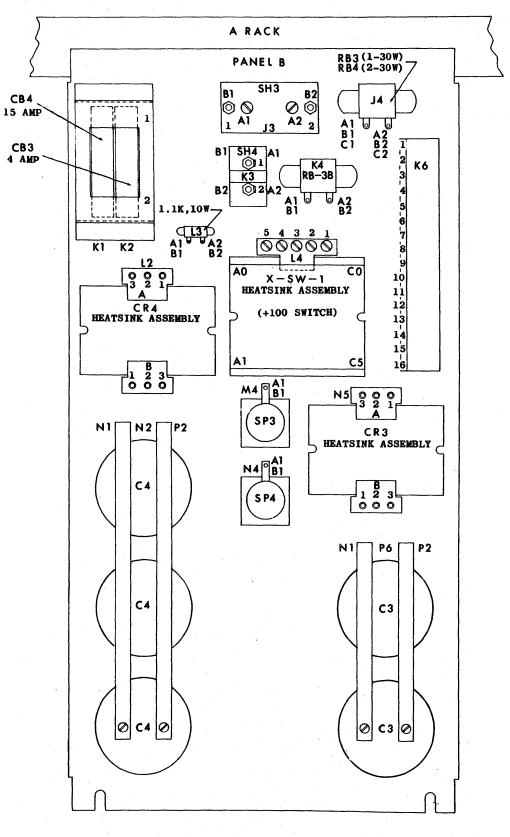

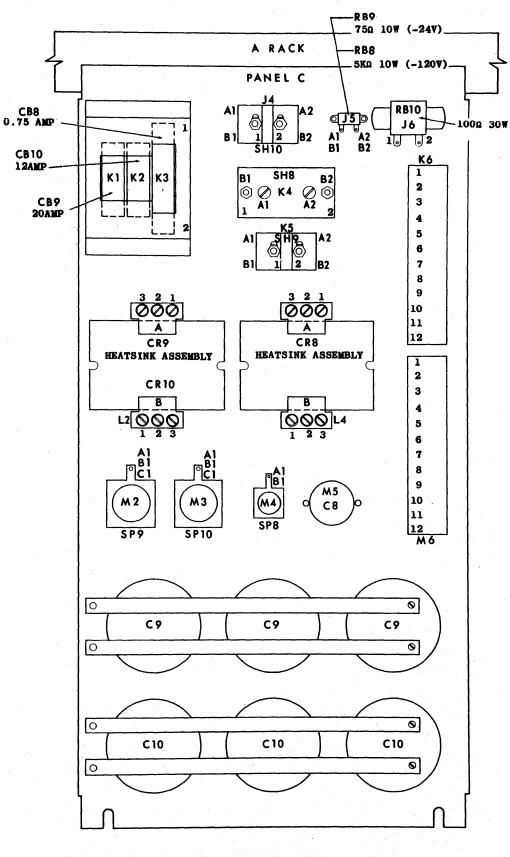

This section of the manual contains illustrations of each DC Power Supply by panel.

Layouts of the Heatsink Assemblies used within the Power Supply are also illustrated.

FIGURE 4.1-1. POWER SUPPLY (FRONT VIEW)

# в 5370.51

4.1-3

FIGURE 4.1-2. POWER SUPPLY (REAR VIEW)

FIGURE 4.1-3. POWER SUPPLY (INTERIOR)

4.1-5

FIGURE 4.1-4 PANEL LAYOUT (-33V, +19V, +74V)

4.1-6

FIGURE 4.1-5. PANEL LAYOUT (+100V, -100V)

4.1-7

FIGURE 4.1-6. PANEL LAYOUT (+50V, -24V, -120V)

j.

### B 5370.51

4.1-8

FIGURE 4.1-7. PANEL LAYOUT (-38V)

FIGURE 4.1-8. PANEL LAYOUT (+20V)

τς.ογες ε November 15, 1963

FIGURE h.l-9. COMMON HEATSINK ASSEMBLY

ττ-τ.4

FIGURE 4.1-10. +20 ELECTRIC SWITCH

FIGURE 4.1-11. +100 ELECTRIC SWITCH

4.2-1

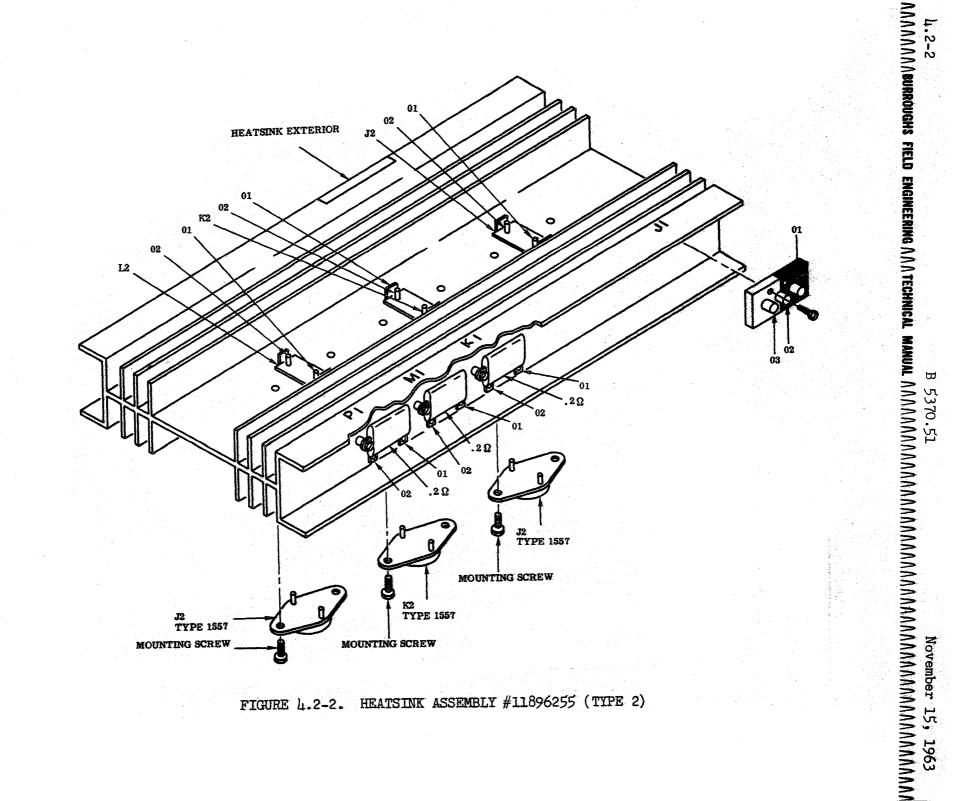

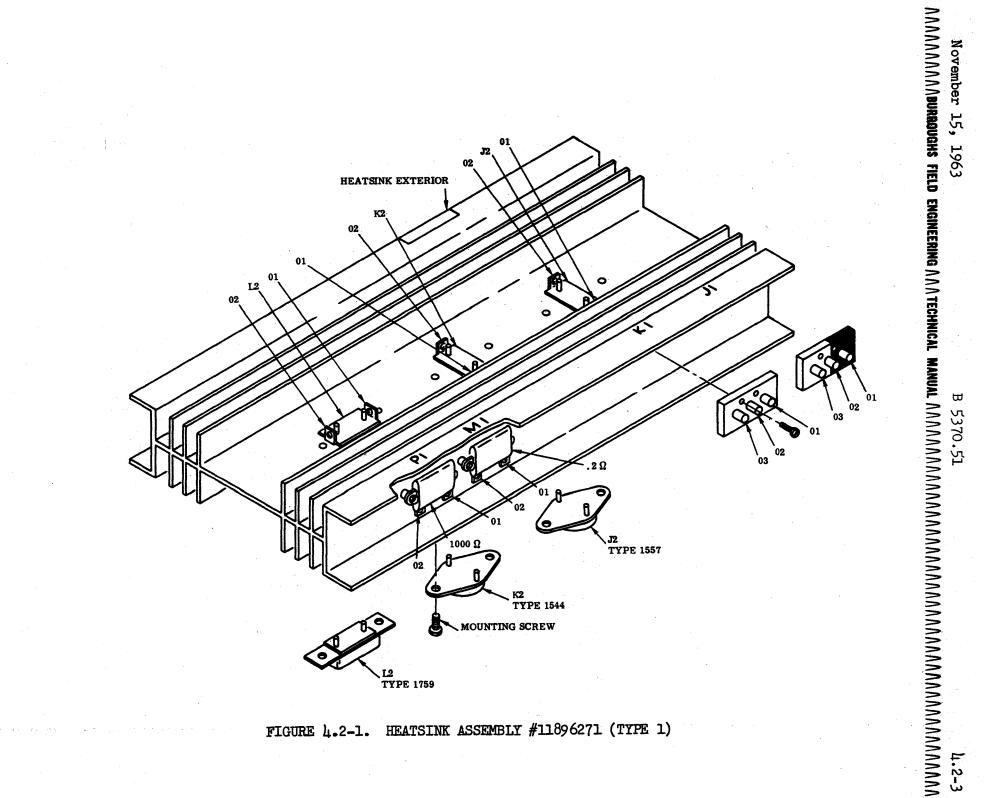

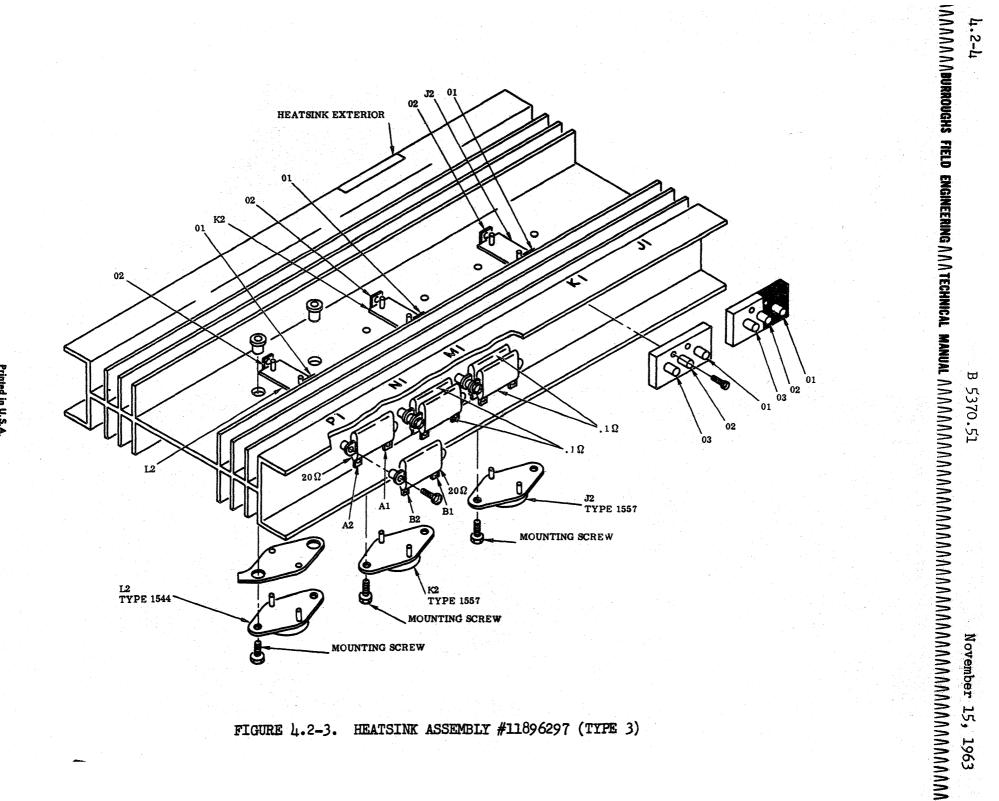

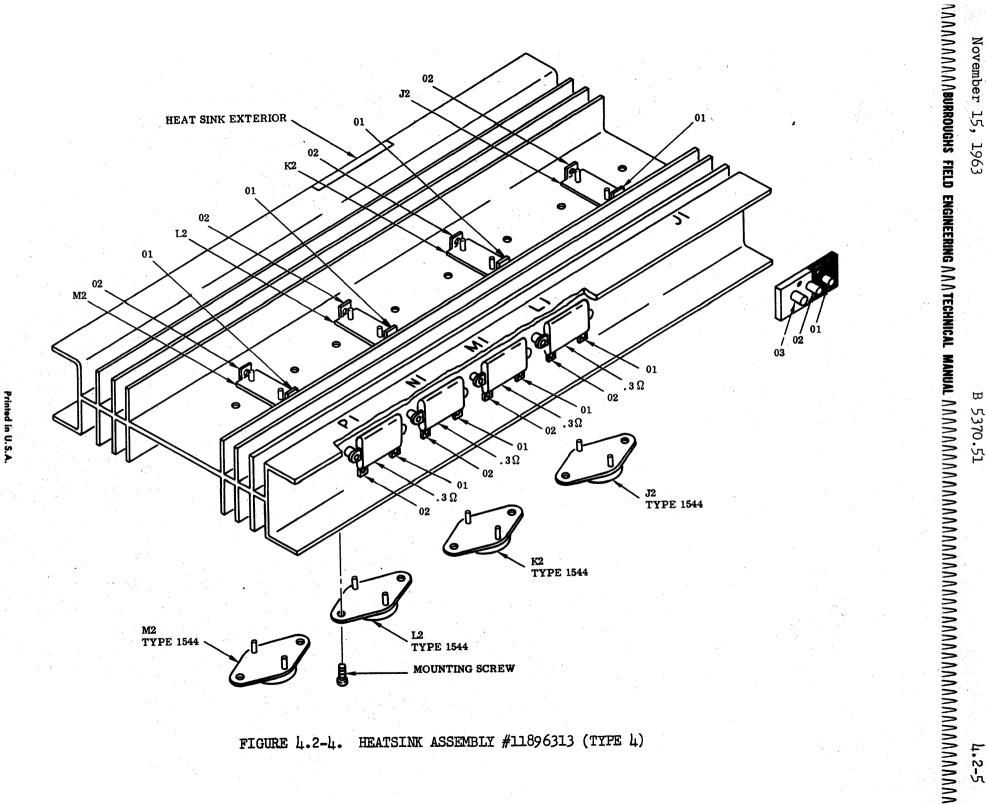

# 4.2 VOLTAGE REGULATORS

# INTRODUCTION

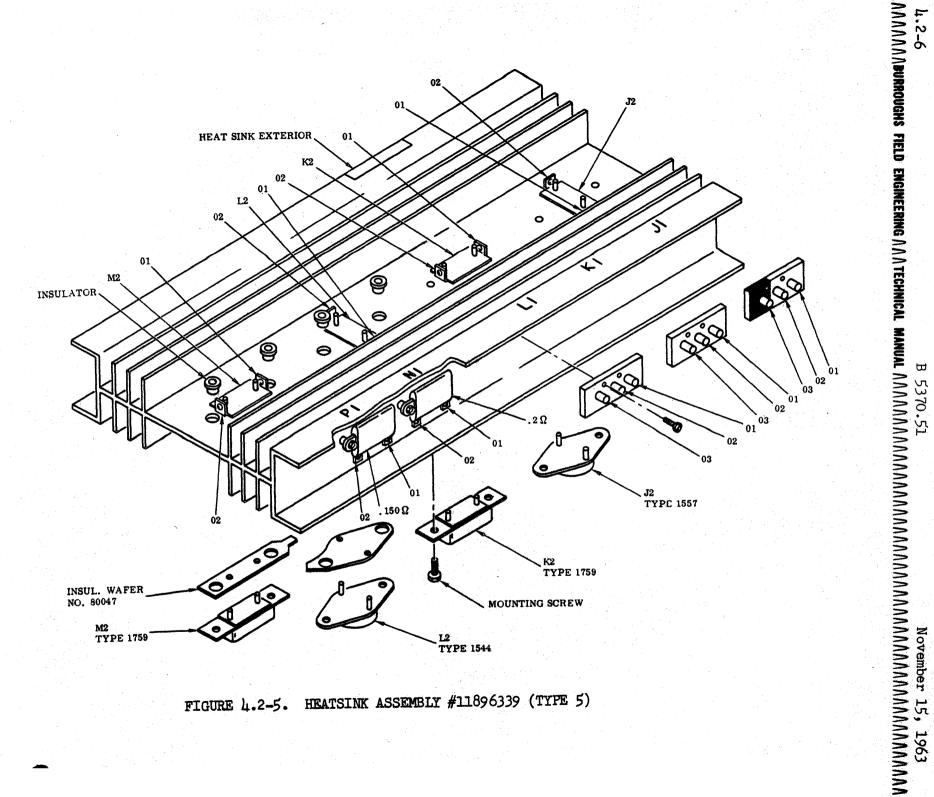

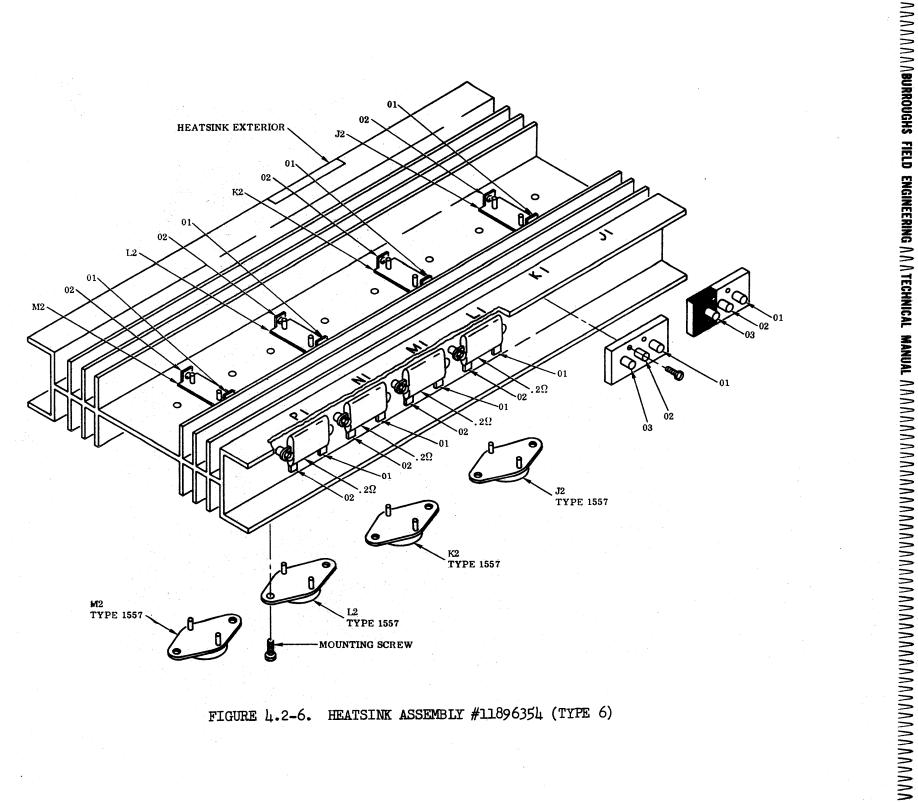

The Power Regulator Unit Heatsink Assemblies are illustrated in this section of the manual.

HEATSINK ASSEMBLY #11896313 (TYPE 4) FIGURE 4.2-4.

5370.51

Β

FIGURE 4.2-6. HEATSINK ASSEMBLY #11896354 (TYPE 6)

November 15, 1963

Β

5370.51

4.2-7

5.1-1

# 5.1 INTRODUCTION

The installation procedures described, pertain to the B 5000 Power Supply and the associated controls (from the remainder of the system) necessary to operate the Power Supply for check-out.

The Voltage Regulator and Sensing circuit check-out will also be described. Site preparation such as power, floor space and floor load requirements are assumed completed according to the Pre-Installation Planning Manual and customer specifications. The unpacking and physical placement of the system is assumed completed.

5.2-1

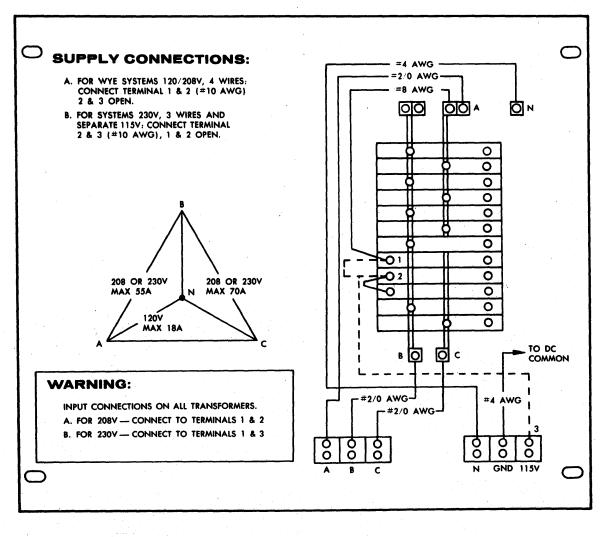

## 5.2 PRIMARY POWER CONNECTIONS

The 3 wire AC input, neutral, and building ground lines from the Main Power Disconnect are connected to the Power Supply.

For Primary Power Connections, See Figure 5.2-1.

FIGURE 5.2-1. AC POWER CABLE CONNECTION

5.3-1

#### 5.3 CABLING AND POWER SUPPLY TO D & D

SINGLE CONDUCTOR CABLES

Connect the Single Conductor Cables listed in Table 5.3-1 between the Power Supply and the D & D Unit.

Install the Cables in the sequence listed in Table 5.3-1.

| CABLE NO. | POWER SUPPLY | DISPLAY &<br>DISTRIBUTION | WIRE SIZE | FUNCTION    | ASSEMBLY NO. |

|-----------|--------------|---------------------------|-----------|-------------|--------------|

| 200       | DAJ1 13      | DAJ1 02                   | #4/0      | GND         | 11891629     |

| 201       | DAJ1 14      | DAJ1 01                   | #4/0      | GND         | 11891629     |

| 202       | DAJ1 15      | DAJ1 01                   | #4/0      | GND         | 11891629     |

| 203       | DAK1 06      | DAJ1 13                   | #0        | +20 GND     | 11891611     |

| 210       | DAK1 05      | DBL4 01                   | #0        | +20         | 11891611     |

| 211       | DAK8 12      | DBL3 01                   | #4        | +19         | 11891595     |

| 212       | DAK1 07      | DBK3 01                   | #0        | -38         | 11891611     |

| 213       | DAK8 13      | DBT2 01                   | #4        | -33         | 11891595     |

| 216       |              | DF GND                    | #4        | CABINET GND | 11891595     |

TABLE 5.3-1. SINGLE CONDUCTOR CABLES

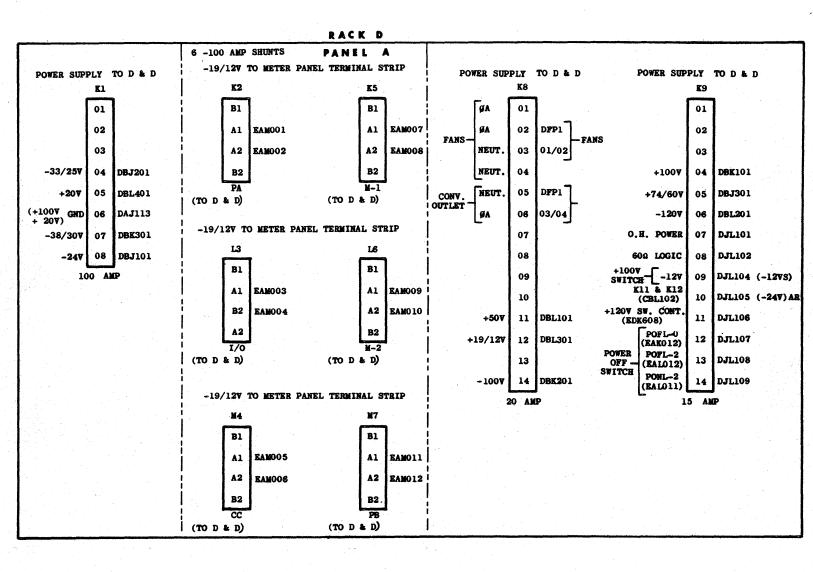

See Figure 5.3-1 for Distribution Box Layout.

CABLING - MINUS 19 VOLTS

The -19V cables (1 minimum, 6 maximum) from the Power Supply to the other units of the system (for example, Processor, I/O Control, etc.) are routed through Display and Distribution, but are not physically connected to it.

Perform the following steps to install the -19V cables.

- 1. Trip the -19V output circuit breakers in the Power Supply.

- 2. Insulate the regulator end of each cable until it is ready to be connected to its respective regulator.

Refer to Table 5.5-1, Regulator Power for Regulator Cabling.

#### MULTIPLE WIRE CABLE

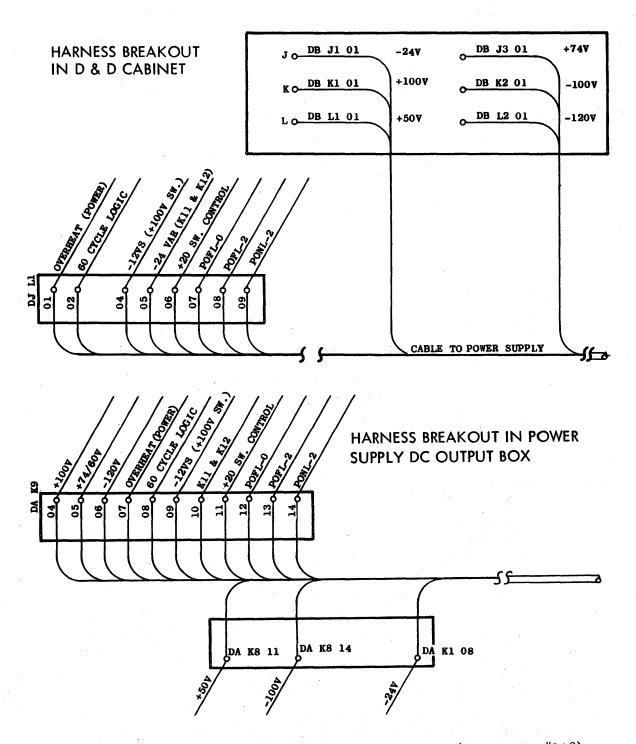

Cable #198 is the only multiple wire cable connected between the Power Supply Unit and the Display and Distribution Unit. This cable carries several low current voltages and miscellaneous control signals. Connect the harness breakouts as indicated in Figure 5.3-2.

FIGURE 5.3-1. DC DISTRIBUTION BOX

Printed in U.S.A.

5.3-2 B 5370.51 November 15, 1963

5.3-3

FIGURE 5.3-2. POWER SUPPLY TO D & D CONNECTIONS (FOR CABLE #198)

### CONVENIENCE AND FAN POWER CABLES

Install Cable #224 from PS DAK8 05/06 to D & D DFPl 03/04 and from PS DAK8 02/03 to D & D DFPl 01/02. Cable #224 is the Fan Power Cable and convenience outlet power cable.

November 15, 1963

## B 5370.51

## 5.4 POWER ON-OFF

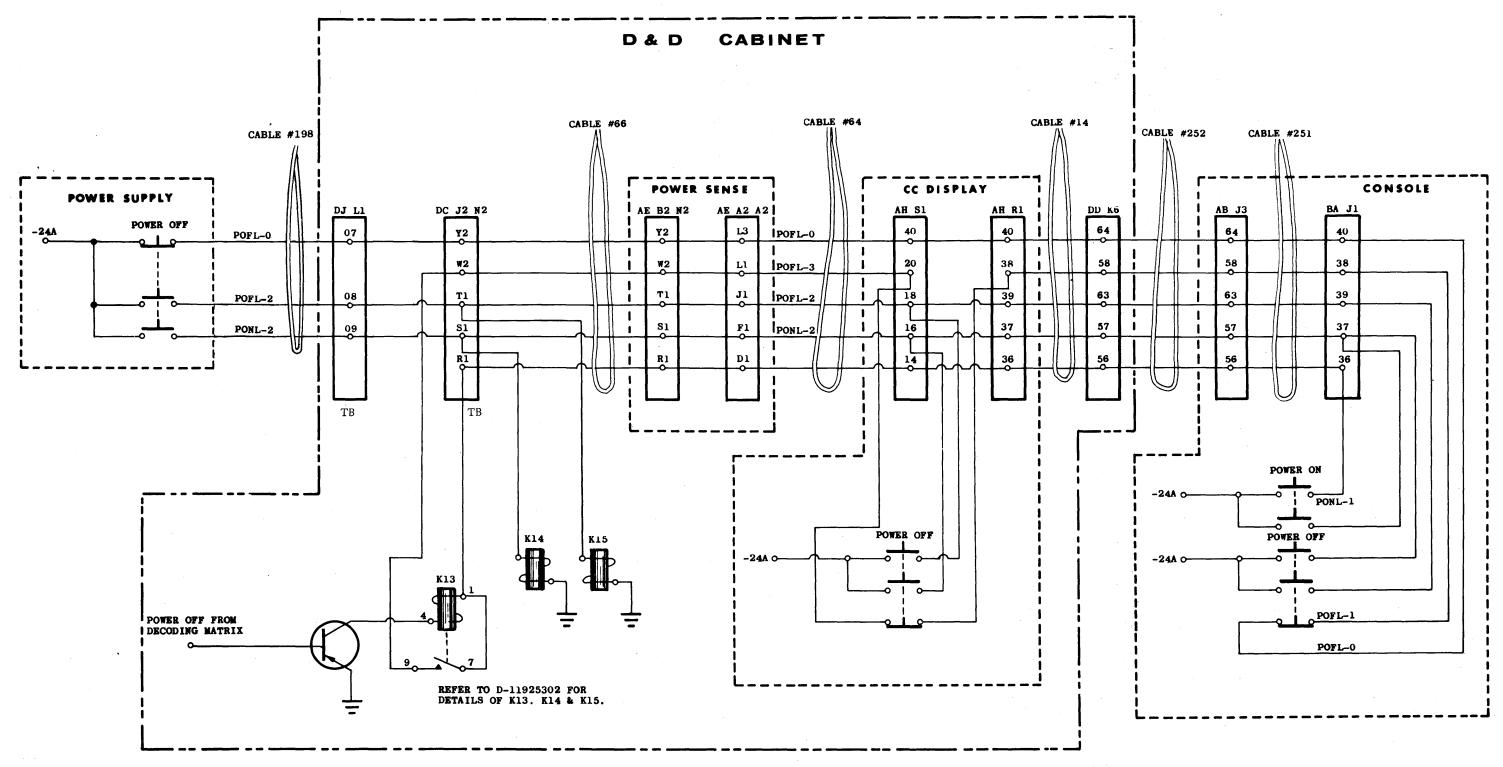

Before the Power Supply can be operated, the Console and Display and Distribution units must be cabled according to Figure 5.4-1 Power On-Off Cabling Requirements.

Only one POWER ON button exists. It is located on the Console.

There are three POWER OFF switches located on the Power Supply, the Console, and the Central Control Panel of D & D. The operation of each of these circuits will be checked.

When the above cabling has been accomplished, perform the following steps:

- 1. Turn all of the Power Supply Output circuit breakers ON, except the -19V circuit breakers.

- 2. Close the primary wall breaker and monitor the AC voltage from the Power Supply meter.

- 3. Check the -24V indicator on the Power Supply Cabinet. It should be ON.

- 4. Put the DC Lockout Switch (located on the CC Display and Distribution Panel) in the DC on position.

- 5. Depress the POWER ON button on the Console.

- 6. Calibrate the Voltmeter and Ammeter on the Power Supply. See Section 3 for procedure.

- 7. Monitor all DC Supplies from the Power Supply meters.

#### NOTE

The +20V and +100V will indicate normal on the voltage monitor. However, the monitoring is accomplished on the supply side of the electronic switch. It does not indicate that the electronic switch is functioning properly. The +100 switch will not operate until -12V is available from CC.

8. Turn off the Power Supply from all positions. After Power Off check, leave Power OFF.

5.4-1

November 15, 1963

5.4-3

FIGURE 5.4-1. POWER ON-OFF CABLING REQUIREMENTS

# 5.5 REGULATOR CONNECTIONS AND CHECK OUT

The +50V, +20V, -19V, and -33V Cables must be connected to the regulators. See Table 5.5-1 for connections from PS and D & D to each regulator. See Figure 2.4-2 for pictorial of Voltage Regulator.

| CABLE NO. | FUNCTION     | FROM UNIT | CONNECTOR | TO UNIT | CONNECTOR<br>(ON REG.) | VIA TRAY   |

|-----------|--------------|-----------|-----------|---------|------------------------|------------|

| 204       | -19V         | PS        | DAL3B2    | I/0-55  | CAJ101                 | 2R         |

| 205       | -19 <b>V</b> | PS        | DAK2B2    | PA      | CAJ101                 | 2R         |

| 206       | -19V         | PS        | DAM7B2    | PB      | CAJ101                 | 2R         |

| 207       | -19V         | PS        | DAL6B2    | M-SS2   | CAJ101                 | 2R         |

| 208       | -19V         | PS        | DAK5B2    | M-SS1   | CAJ101                 | 2R         |

| 209       | -19V         | PS        | DAM4B2    | CC      | CAJ101                 | 2R         |

| 25 - 41   | -33V         | D & D     | DBJ205    | CC      | CTN201                 | 1R         |

| 25 - 42   | -33V         | D & D     | DBJ204    | I/0-88  | CTN201                 | 1R         |

| 25 - 43   | -33V         | D & D     | DBJ203    | DP-A    | CTN201                 | 2 <b>F</b> |

| 25 - 44   | -33V         | D & D     | DBJ 20 2  | DP-B    | CTN 201                | 2F         |

| 25 - 46   | -33V         | D & D     | DBJ206    | M-SS1   | CTN 201                | 2 <b>F</b> |

| 25 - 47   | -33V         | D & D     | DBJ207    | M-SS2   | CTN 201                | 2F         |

| 25 - 30   | +50V         | D & D     | DBL106    | M-SS1   | CTN 204                | 2F         |

| 25 - 31   | +50 V        | D & D     | DBL107    | M-SS2   | CTN204                 | 2F         |

| 25 - 32   | +50V         | D & D     | DBL105    | CC      | CTN 204                | 1F         |

| 25 - 33   | +50V         | D & D     | DBL104    | I/0-SS  | CTN204                 | 17         |

| 25 - 34   | +50V         | D & D     | DBL103    | DP-A    | CTN 204                | 2F         |

| 25 - 35   | +50V         | D & D     | DBL102    | DP-B    | CTN204                 | 2F         |

| 25 - 21   | +20V         | D & D     | DBL406    | M-SS1   | CSK112                 | 2F         |

| 25 - 22   | +20V         | D & D     | DBL407    | M-SS2   | CSK112                 | 2F         |

| 25 - 23   | +20V         | D & D     | DBL405    | СС      | CSK112                 | lF         |

| 25 - 24   | +20V         | D & D     | DBL404    | 1/0-SS  | CSK112                 | 1F         |

| 25 - 25   | +20V         | D & D     | DBL403    | DP-A    | CSK112                 | 2F         |

| 25 - 26   | +20▼         |           | DBL402    | DP-B    | CSK112                 | 2F         |

TABLE 5.5-1. REGULATOR POWER CONNECTIONS

Turn power ON and measure the outputs of all regulators in the system. Use a precision meter.

The regulator output terminals are -12V (CSM1), -4.5V (CSL1), and -1.2V (CSN1). Refer to Figure 2.4-2. These terminals are located on the regulator. The regulator outputs should measure their true values. If not, adjust the following potentiometers.

- 1. Adjust R36 on the -12V Regulator Amplifier package until the -12V regulator output reads -12V. DO NOT ADJUST R35 ON THE -12V PACKAGE.

- 2. Adjust R27 on the -4.5V Regulator Package. Adjust R27 on the -1.2V Regulator Package.

5.5-1

5.6-1

### 5.6 SYSTEM POWER APPLICATION AND VOLTAGE SENSING VERIFICATION

Apply all power. When all units of the system have power applied, perform the following procedure for under and over voltage detection.

- 1. Install a temporary ground wire to package AFBLA7, Pin K5 on the Sensing Panel of D & D. The ground wire will allow power to remain on, and only the power fail indicators will light for the following check:

- a. Vary all regulator voltages ±10 percent.

Monitor each voltage with a precision meter. Refer to Figure 2.4-2 for terminals.

DO NOT VARY THE EXCESS CURRENT POTENTIOMETER (R35) ON THE -12V REGULATOR PACKAGE. This potentiometer is factory set. If adjustment is necessary, see Section 3 for proper procedure.

The ±10 percent voltage variation should light the proper indicators for each cabinet, voltage condition, and the voltage that failed. Once all regulators have been checked, insure that all voltages are returned to their proper value.

- 2. Remove the ground wire at AFBLA7, Pin K5 of D & D.

- 3. Vary one of the regulator voltages to a FAIL condition. The Power Supply should completely shut down except for the -24V Supply.

- a. Adjust the potentiometer to approximately its original position and apply power.

- b. Reset the regulator voltage to its proper value. Refer to Section 5.5 for proper procedure.

#### DC VOLTAGE RIPPLE

Scope all DC voltages for ripple. Maximum allowable ripple is indicated in Table 5.6-1.

Scope at the input terminals of the D & D Cabinet.

Scope the -19V at one of the regulator units.

### DC LOCKOUT

Turn the DC Lockout to the lockout position. The regulator units in the system should shut down. The +20V and +100V output to the system should also shut down.

NOTE

ALL OTHER VOLTAGES WILL BE PRESENT IN D & D

|       | POWER SUPPLY |               | QUA           | LIFYING                      |                                                                     |                         |                |                                                     |

|-------|--------------|---------------|---------------|------------------------------|---------------------------------------------------------------------|-------------------------|----------------|-----------------------------------------------------|

|       |              | DESCRIPT      | <b>FION</b>   | MAX. DC                      | VOLTAGE VOLTAGE V <sub>pp</sub> @ FUL<br>C. @ FULL @ FULL LOAD @ NO |                         | MAX. RIPPLE    |                                                     |

| CLASS | NO.          | DC<br>VOLTAGE | DC<br>CURRENT | VOLTAGE<br>© NO EXT.<br>LOAD |                                                                     | LOAD @ NOM.<br>LINE ±3% | REMARKS        |                                                     |

| 3     | 9            | -24V          | 18A           | 27.0                         | 23.5                                                                | 25.5                    | 3.5            | @ -120V LOADED 80%                                  |

| 3     | 8            | -120V         | 0.75A         | 129.0                        | 118.0                                                               | 124.0                   | SEE<br>REMARKS | € -24V LOADED 80%<br>ADJUST CF8 SO<br>V PEAK ≪ 140V |

| 1     | 2            | +20V          | 30A           | 22.5                         | 19.5                                                                | 21.5                    | 1.0            | @ +50V LOADED 80%                                   |

| 1     | 10           | +50V          | 12A           | 55.0                         | 49.0                                                                | 52.0                    | 3.5            | @ +20V LOADED 80%                                   |

| 2     | 5            | -38/30V       | 90A           | 42.0                         | 36.5                                                                | 38.5                    | 2.2            |                                                     |

| 1     | 3            | +100V         | 4A            | 106.0                        | 99.0                                                                | 103.0                   | 2,2            | @ -100V LOADED 80%                                  |

| 1     | 4            | -100V         | 14A           | 108.0                        | 99.0                                                                | 103.0                   | 3.5            | @ +100V LOADED 80%                                  |

| 2     | 11           | +74/60V       | 8A            | 78.0                         | 72.0                                                                | 75.0                    | 3.5            | @ +19/12V & -33/25V<br>LOADED 80%                   |

| 2     | 6            | +19/12V       | 1 <b>4A</b>   | 22.0                         | 18.2                                                                | 20.0                    | 2.0            | € +74/60V & -33/25V<br>LOADED 80%                   |

| 2     | 7            | -33/25V       | 12A           | 36.0                         | 31.5                                                                | 33.5                    | 3.5            | @ +74/60V & +19/12V<br>LOADED 80%                   |

| 2     | 1            | -19/12V       | 500A          | 21.0                         | 18.2                                                                | 20.0                    | 1.5            |                                                     |

TABLE 5.6-1. POWER SUPPLY RIPPLE

### 5.7 FCN INSTALLATION

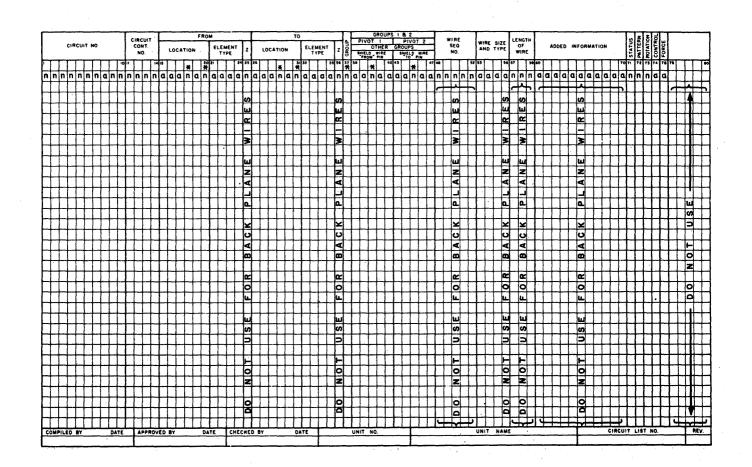

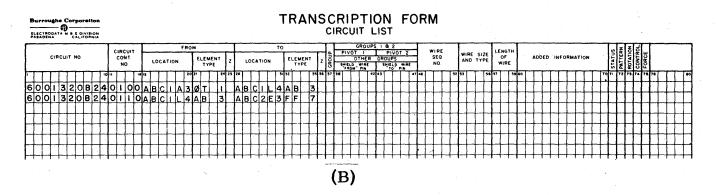

The purpose of this section is to recommend a procedure to expedite wiring changes when installing FCN's and to explain the new "B" size Circuit List Transcription Form (EDD 1760).

### EXPEDITING FCN INSTALLATION

In order to eliminate clerical errors, the circuit list change sheets are not modified from the original engineering instructions. Therefore, the add/delete sequence indicated on the change sheet is not always the most convenient. The following procedure is recommended to expedite wiring changes:

- 1. Remove all access wires (code 6 in column 71).

- 2. Remove all level "2" deletes (code 1 in column 71). Levels are encoded in column 25.

- 3. Remove all level "1" deletes (code 1 in column 71).

- 4. Add all level "1" adds (code 4 in column 71).

- 5. Add all level "1" to level "2" adds (code 4 in column 71).

- 6. Add all level "2" adds (code 4 in column 71).

- 7. Add all access wires (code 6 in column 71).

When making wire changes which require a wire to be removed and then replaced on the same pin, (status 6, column 71) do not rewrap previously wrapped wire. If length permits, clip off the previously wrapped part and then wrap. If length does not permit clipping, replace the wire.

CIRCUIT LIST TRANSCRIPTION FORM (EDD 1760)

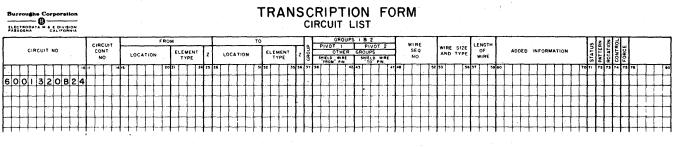

- 1. The circuit list will consist of a B size sheet as shown one-half scale in Figure 5.7-1.

- 2. The Circuit List Transcription Form EDD 1760, is a hand prepared document. It is a vellum 17 inches wide and 11 inches in length. The working area of the document is comprised of 34 horizontal rows, each row contains 80 character positions. One (1) character is the maximum allowed in any one character position.

- 3. The 80 character positions are divided into 21 vertical column increments, each increment is separated by a thick vertical partitioning line (Figure 5.7-1).

- 4. The usage of the 80 character positions is as follows:

5.7-1

### CHARACTER POSITIONS EXPLANATION

1 🔿 10

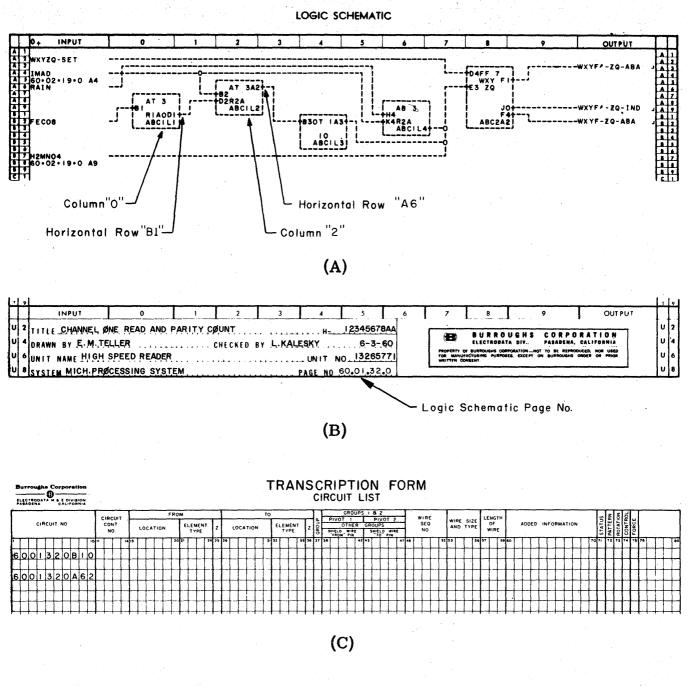

Circuit Number (Single Origin)

A circuit number is derived from the location of the circuit origin on the logic schematic and is comprised of the page number, horizontal row and vertical column of the logic schematic from which the circuit originates. It is thus possible to read the circuit number directly from the schematic.

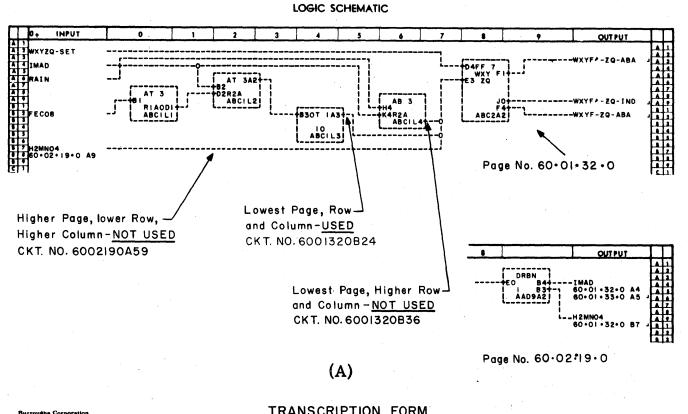

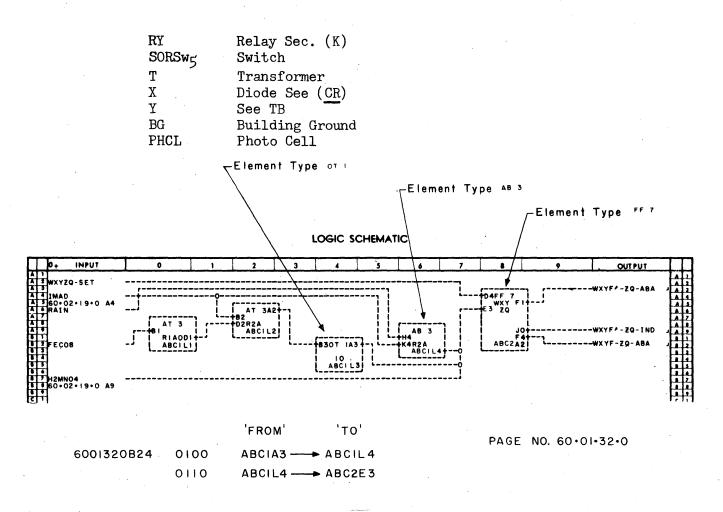

The illustration (Figure 5.7-2A and 5.7-2B) shows how the circuit numbers of single origin circuits are determined on the logic schematic and transcribed onto the transcription form (Figure 5.7-2C).

Circuit Number (Multiple Origins)

The circuit number of a circuit with multiple origins (if on the same page) is derived from the origin within the circuit which has the lowest horizontal row number and vertical column number on the logic schematic. If the origins are on more than one page, the circuit number is derived from the lowest page number.

The illustration (Figure 5.7-3) shows a circuit with three origins, and how the circuit number is depicted and transcribed.

$11 \Rightarrow 14$  Circuit Continuity Number

Each wire within a circuit is identified by a continuity number. A continuity number is comprised of four (4) numeric characters. All continuity numbers are assigned in a numerical sequence which allows for the future insertion of additional wires.

The continuity field indicates the order in which the individual wires within a circuit appear on the circuit list.

5.7-3

#

# FIGURE 5.7-1. CIRCUIT LIST TRANSCRIPTION FORM, EDD 1760

a - denotes use of alpha character

n - denotes use of numeric character

\* - denotes that an alpha character may be used for Non Back Plane wires

FIGURE 5.7-2. DETERMINATION AND TRANSCRIPTION OF THE ORIGIN OF SINGLE CIRCUIT

5.7-5

**(B)**

# FIGURE 5.7-3. DETERMINATION AND TRANSCRIPTION OF CIRCUIT NUMBER FROM A CIRCUIT WITH MULTIPLE ORIGINS

# POSITIONS EXPLANATION

15 ⇒ 20

CHARACTER

Location (FROM)

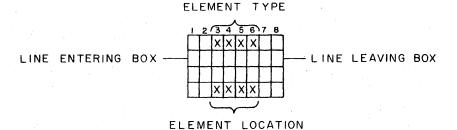

The location of an Element is depicted in character positions 3 thru 6 on the bottom row of an element box, Figure 5.7-4, and is comprised of the Rack (3), Panel (4), Connector Block Row (5) and Connector Block Column (6). The 'From' or 'To' pin designations are depicted in character positions 1 and 2 for a line entering an element box or character positions 7 and 8 for a line leaving an element box. Figure 5.7-5 gives examples of the above.

FIGURE 5.7-4. ELEMENT LOCATION AND TYPE DESIGNATION Element Type (FROM)

The Element Type is depicted in character positions 3 thru 6 on the top row of an element box (Figure 5.7-4). The Element Type transcription for 'From' pins appears in Vertical Columns 21 thru 24 and for 'To' pins, in Vertical Columns 32 thru 35, (Figure 5.7-5B). These character positions contain abbreviations which indicate the type of elements connected together. Most of the abbreviations may be found in the Design Automation Element representation book. The following list contains additional abbreviations that may appear in these columns:

| Р                         | Plug                               |

|---------------------------|------------------------------------|

| J                         | Jack                               |

| TB or Y                   | Terminal Bd.                       |

| C                         | Capacitor (also used as connector) |

| DS                        | Buzzer or bell                     |

| HS                        | Heat Sink                          |

| $\mathbf{L}_{\mathbb{C}}$ | Choke                              |

| M                         | Meter                              |

| NE                        | Neon                               |

21 ⇒ 24

5.7-7

**(A)**

FIGURE 5.7-5. 'FROM' AND 'TO' PIN LOCATIONS

$\Lambda\Lambda\Lambda\Lambda\Lambda\Lambda$

#### CHARACTER POSITIONS EXPLANATION

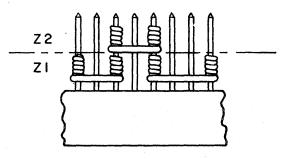

25

"Z" (FROM)

The 'Z' Level (Figure 5.7-6) depicts the physical location of the wire wrap on a connector block pin. Two wire wraps are permitted to one pin. The 'Z' Level is applicable to Back Plane wires only. Vertical Character Position 25 is used to designate the 'From' pin 'Z' Level, and Vertical Character Position 36 is used to designate the 'To' pin 'Z' Level. The ground strip pins are allowed one (1) wrap only; the level is assigned as Z1 automatically.

FIGURE 5.7-6. 'Z' LEVELS

| 26 🔿 31 | Same as 15 ⇒ | 20 except this is | the "TO" location. |

|---------|--------------|-------------------|--------------------|

| 32 🗢 35 | Same as 21 ⇒ | 24 except this is | the "TO" location. |

| 37      | Group        |                   |                    |

Group denotes the type of connection and method of wiring used. Five Groups exist. The character used to denote the Group is transcribed into Vertical Column 37.

The five Groups refer to connections as defined below:

- (0) Between two pins not on a wire wrap frame.

- (1) Between two pins on the same wire wrap frame (machine installation).

- (2) Between two pins on the same wire wrap frame (manual installation).

- (3) Between two pins on the same frame non-wire wrap connection such as current loops, etc.

(4) Manual calculation of Gardner-Denver installed wires which cannot be handled through the normal Back Plane processing, specifically ground wires along the 'M' or 'R' pin columns of a connector block. The cards for these wires are entered directly into the Circuit List. No wire entered through the normal Back Plane processing may carry this group number. At present this group is special for the B 5000 System.

5.7-9

(5) Between two pins of different frames of the same rack (Inter-Frame Jumpers and Cables).

38 ⇒ 47 Gardner Denver Wire Wrap Information

If the wire is a twisted pair, columns 38 thru 42 are used to identify the return "FROM" pins. If the wire is a twisted pair, columns 43 thru 47 are used to identify the return "TO" pins.

$48 \Rightarrow 52$  Wire Sequence Number

The Wire Sequence Number indicates the order in which wires are installed on frames and is applicable to Back Plane wires only.

$53 \Rightarrow 56$  Wire Size and Type

Gage size 12 ⇒ 36 Type - TW - Thin Wall BS - Buss TP - Twisted Pair CX - Coaxial Cable SD - Solid Wire

$57 \Rightarrow 59$  Length of Wire

Gardner Denver Wire Wrap Information

The length of wires between "FROM" and "TO" pins is measured in increments of two tenths of an inch, which is the approximate physical distance between two wire wrap pins. A figure of 24 in character positions  $57 \Rightarrow 59$  indicates the length of wire in terms of 24 wire wrap pins resulting in  $24 \times .2$ " or 4.8 inches.

$60 \Rightarrow 70$  Added Information

Used for Engineering Project Information or specific information on a given connector.

| 71                                                         | Status              |                                                                                                                                    |  |  |

|------------------------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|

| a an trainighteach<br>An trainighteach<br>An trainighteach | STATUS<br>CODE NAME | DESCRIPTION                                                                                                                        |  |  |

|                                                            | l Wire              | Physically remove this wire from the equipment. (Also delete from C/L).                                                            |  |  |

|                                                            | 4 Wire<br>Add       | Physically add this wire to the equipment. (Also add to C/L).                                                                      |  |  |

|                                                            | 5 Clerical          | Delete this wire from the C/L only.<br>This change does not affect the<br>wiring in any way.                                       |  |  |

|                                                            | 6 Access<br>Wire    | This wire must be removed with the<br>deletes and added with the adds to<br>facilitate adding or deleting a wire<br>underneath it. |  |  |

|                                                            | 8 Clerical<br>Add   | Add this wire to the C/L only. This code will always have a matching wire listed under code 5.                                     |  |  |

| 2                                                          | Pattern             |                                                                                                                                    |  |  |

|                                                            | Gardner Denver Wire | Wrap Patterns for wires.                                                                                                           |  |  |

| 73                                                         | Garnder Denver Wire | Wrap Routing for wires.                                                                                                            |  |  |

| 74                                                         | Control             |                                                                                                                                    |  |  |

|                                                            | a. A "blank" denote | es that the wire is under Schematic Control.                                                                                       |  |  |

|                                                            | "P" must be car     | hat the wire is under Project control. A<br>ried on all wires whose pins are not on the<br>ay be carried on other schematic wires. |  |  |

|                                                            |                     | a wire produced by the Program whose front<br>not from the schematic but from a "TO" pin<br>ntrol wire.                            |  |  |

| 75                                                         | Force               | Force                                                                                                                              |  |  |

|                                                            | The letter UEU erro | aring in column 75 indicates that a wire has                                                                                       |  |  |

|                                                            |                     | se the routing assigned automatically is                                                                                           |  |  |

### 5.8 INSTALLATION CHECK LIST

- 1. Remove packing and locate cabinets. Section 5.1-1 of D & D Manual.

- 2. Bolt cabinets (Processor, I/O, D & D, CC and Core Memory) together. Level and install trim.

NOTE

The process of bolting these cabinets together will necessitate swinging gates open. Where a unit has gates on both sides, open both sides as there is a slight possibility of unbalance with only one side open when the unit is free standing. On units with only one gate, bolt the side with no gate first and then swing the gate to bolt the other side.

- 3. As the process of adjusting the heads on the drum may be lengthy, it is suggested that the Drum Cabinet be placed in position and wired up first so that the head adjustment can go on concurrently with the hook up on the system. Refer to Section 3.3-1 of the Drum Memory Technical Manual. Prior to applying power, refer to Section 5 of the B 430 Manual.

- 4. While electricians are hooking up primary power to Power Supply, install convenience and fan cables in the main frame cabinets. Refer to Figure 5.2-3, Detail B, of the D & D Manual. Install the ground straps between the cabinets. Refer to Section 5.3-1 of the D & D Technical Manual.

- 5. Install ground cables from D & D to Individual Cabinet Regulators.

- 6. Install power cables (DC and AC) from Power Supply Cabinet to D & D (where required by special conduit, it may be necessary to cut off and relug certain cables at the D & D panel). Refer to Section 5.3-1 of Power Supply Technical Manual.

- 7. Connect inter-unit cables. Refer to B 5000 System Special Instruction. Document All891660.

- 8. Lay out all peripheral unit cables. Do not hook up the D & D end until after power checkout on main frame units.

- 9. Make resistance checks in Core Memory according to the B 460 Manual, Section 5.4-1.

- 10. Check out power as described in Power Supply Manual, Section 5.

- 11. Check out maintenance panel functions (unit checks).

- 12. Hook up peripheral equipment and check LOCAL and REMOTE operation of each. Manpower permitting, the LOCAL check of peripheral equipment may have been accomplished concurrently with other operations.

- 13. Check all multis and record settings.

- 14. Run system tests.

- 15. Place MCP on Drum and run test ALGOL and/or test COBOL programs.

6.1 - 1

SECTION 6

### CIRCUIT ANALYSIS

#### 6.1 GENERAL

#### INTRODUCTION

The B 5000 System Power Supply provides all DC voltages required for proper operation of the system, and 115V AC for the Convenience Outlets and Fan Motor Power.

The voltages are distributed through the Display and Distributions Cabinet to the Central Processors, Central Control, Core Memories and the Input/Output which are the Main cabinets of the system; and also to the Control Console.

All power is supplied through the Distribution Panel in the D & D Unit EXCEPT -19V which comes from the Power Supply via the D & D Cabinet to the cabinets with regulator units.

The peripheral units not receiving power from the Main Supply for example, the Drum Memories, Readers, Punches, Printer, Magnetic Tapes, etc., will be dealt with separately and connected electrically for optimum phase balance according to the Pre-Installation Planning Manual.

The raw voltages of the System Supply are developed from transformers of the constant voltage type, and are used as inputs to voltage regulators, drive voltage sensing and shut-down circuits, and energize Control Relays. The raw supplies are also used directly without external regulation within the B 5000 system.

The voltage regulators (B 5000 Regulator Power Unit) develop the regulated voltages -1.2V, -4.5V and -12V. The regulator units are physically separate and each unit provides its own three (3) regulated voltages. There are six (6) of these power units in a maximum system configuration, one in each of the Main cabinets except the Display and Distribution cabinet, Drum cabinet and the Power Supply cabinet. Each of the three voltages, provided by the power unit of each cabinet, is sensed for over and under voltage within the Display and Distribution cabinet set. The status is shown by indicator lights.

Excess Current is also sensed from the power unit (-12V Regulator), and indicated on the Power Maintenance Panel located in the Display and Distribution cabinet. In addition, the +20V and +100V Supplies are sensed only in the Display and Distribution cabinet and indicated on the Power Maintenance Panel.

Overheat in the cabinets, and excess current drawn from a power unit (-12V Regulator) and the other FAIL conditions provide automatic shut-down of the system Power Supply.

Voltage is controlled by DC relays. The relays sequence the supplies ON and OFF, provide delays, control peripheral units and Core Memories, and serve inhibit functions.

November 15, 1963

The operation of the fans in each cabinet, and power for the running of the Elapsed Time Meter is under the control of the relay contactors. Also under power control, but not directly associated with the contactors, is a manual switch to remove DC power from Core Memories and the Regulator Units.

November 15, 1963 6.2-3

# B 5370.51

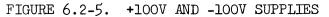

# FIGURE 6.2-1. -24V AND -120V SUPPLY

FIGURE 6.2-2. -19/12V SUPPLY

November 15, 1963

$\Lambda\Lambda\Lambda\Lambda\Lambda\Lambda\Lambda\Lambda\Lambda\Lambda$

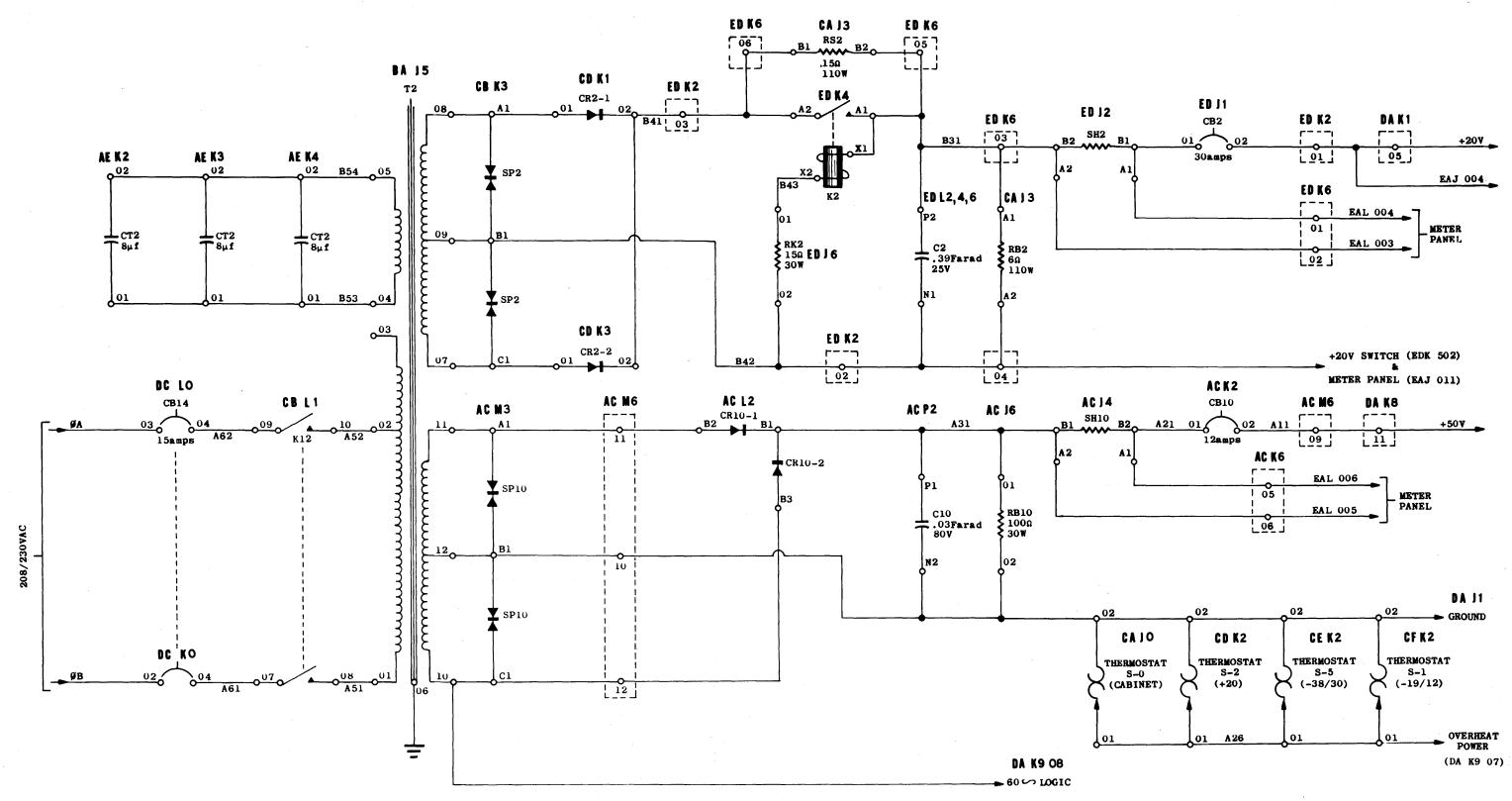

# FIGURE 6.2-3. +20V AND +50V SUPPLIES

Printed in U.S.A.

6.2-1

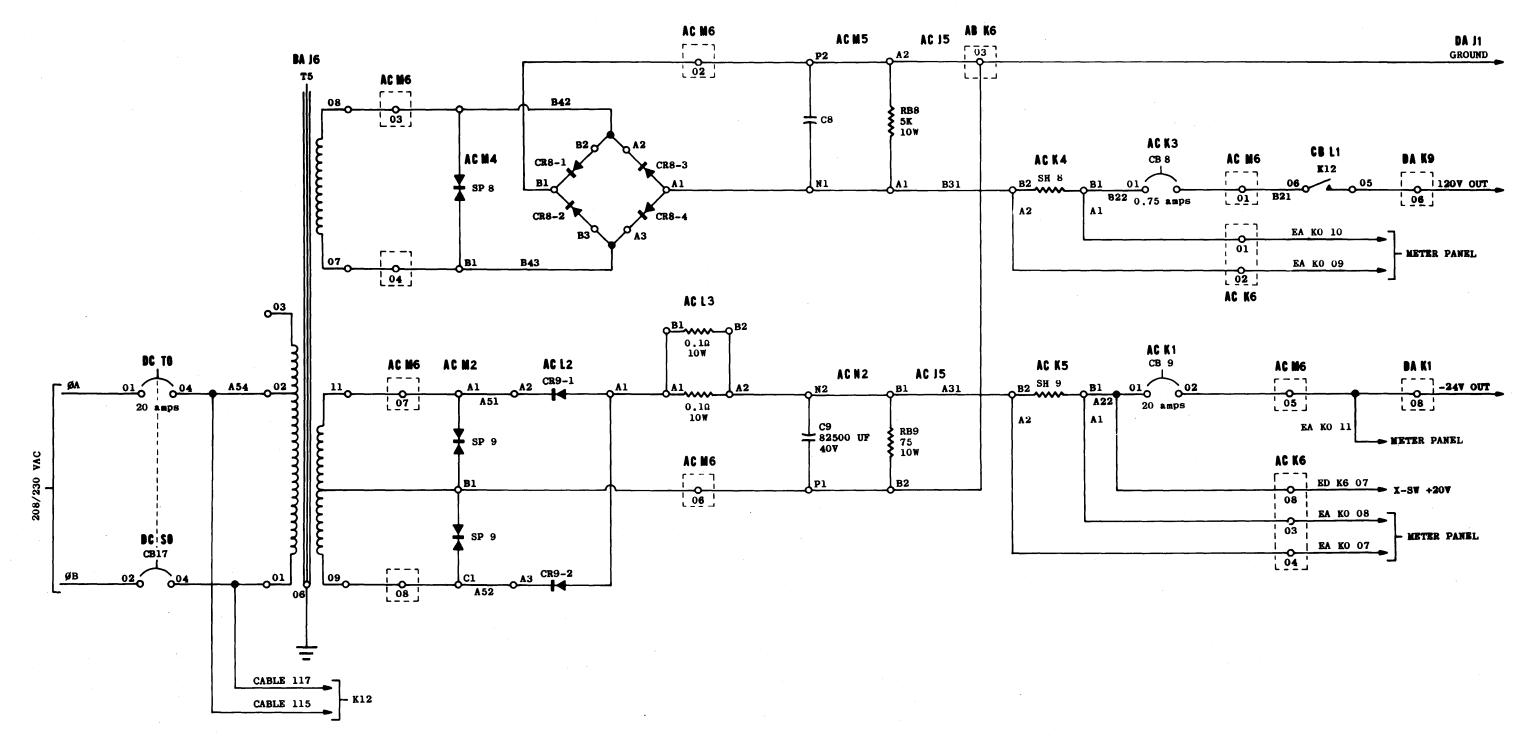

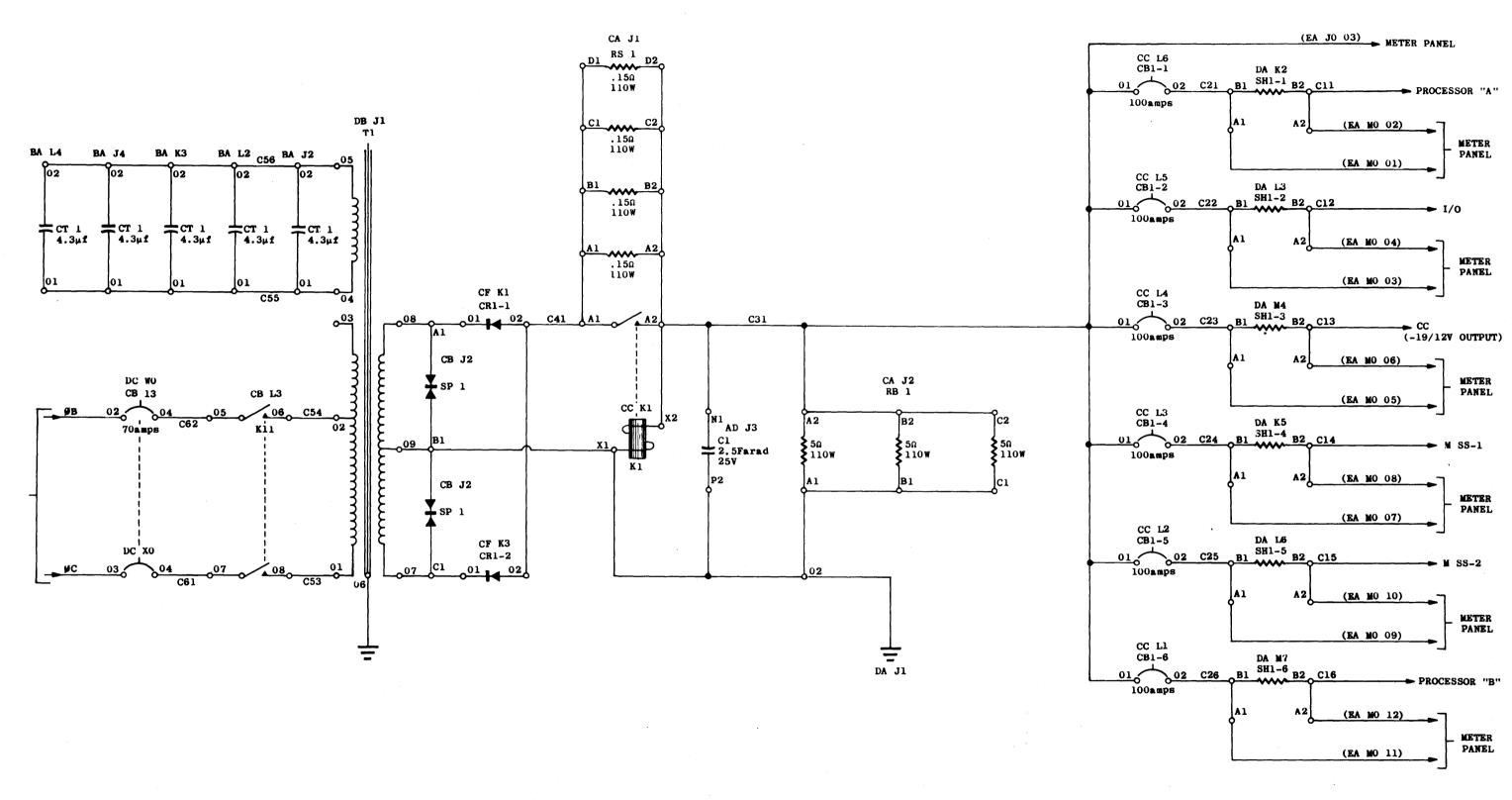

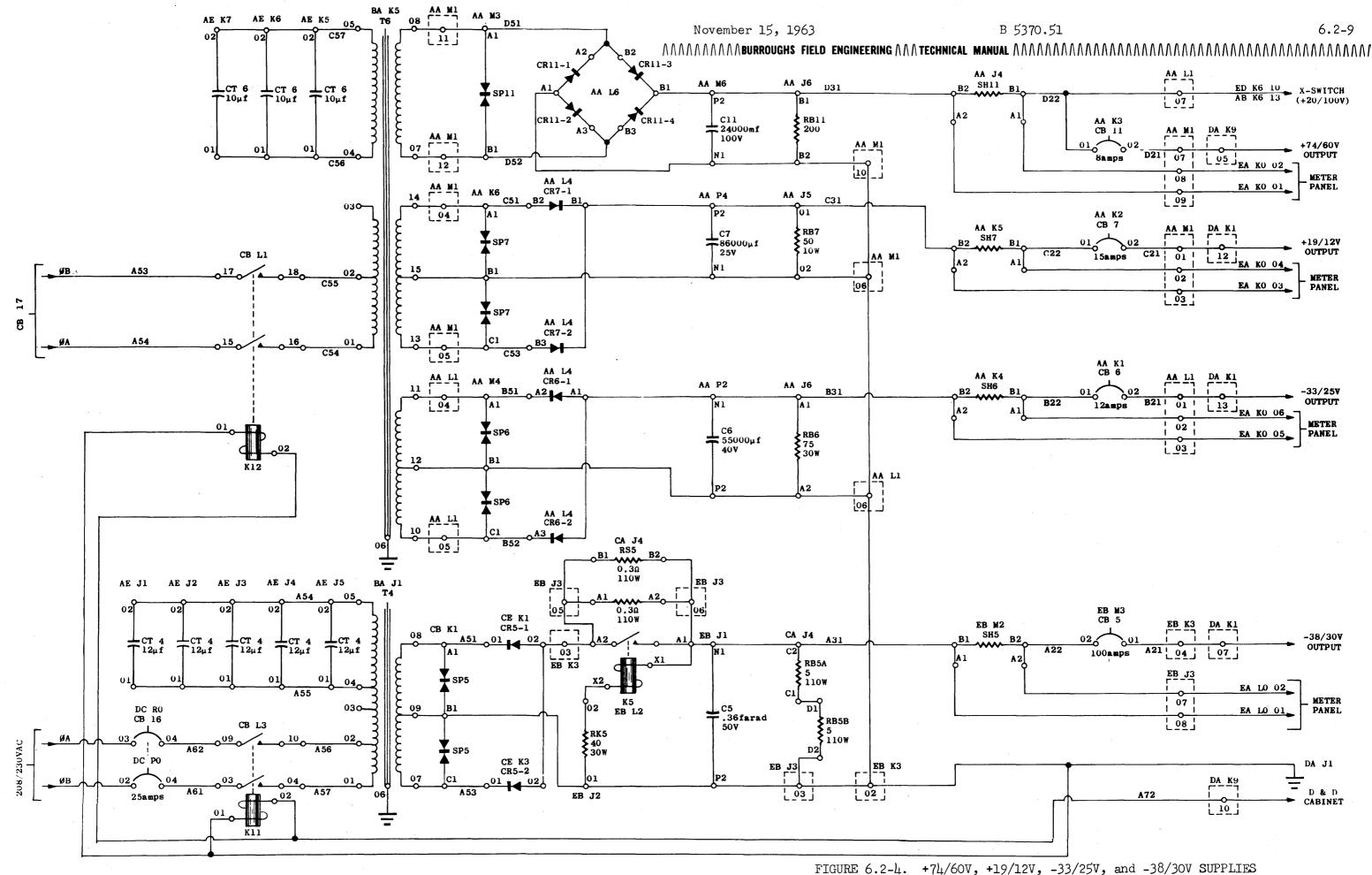

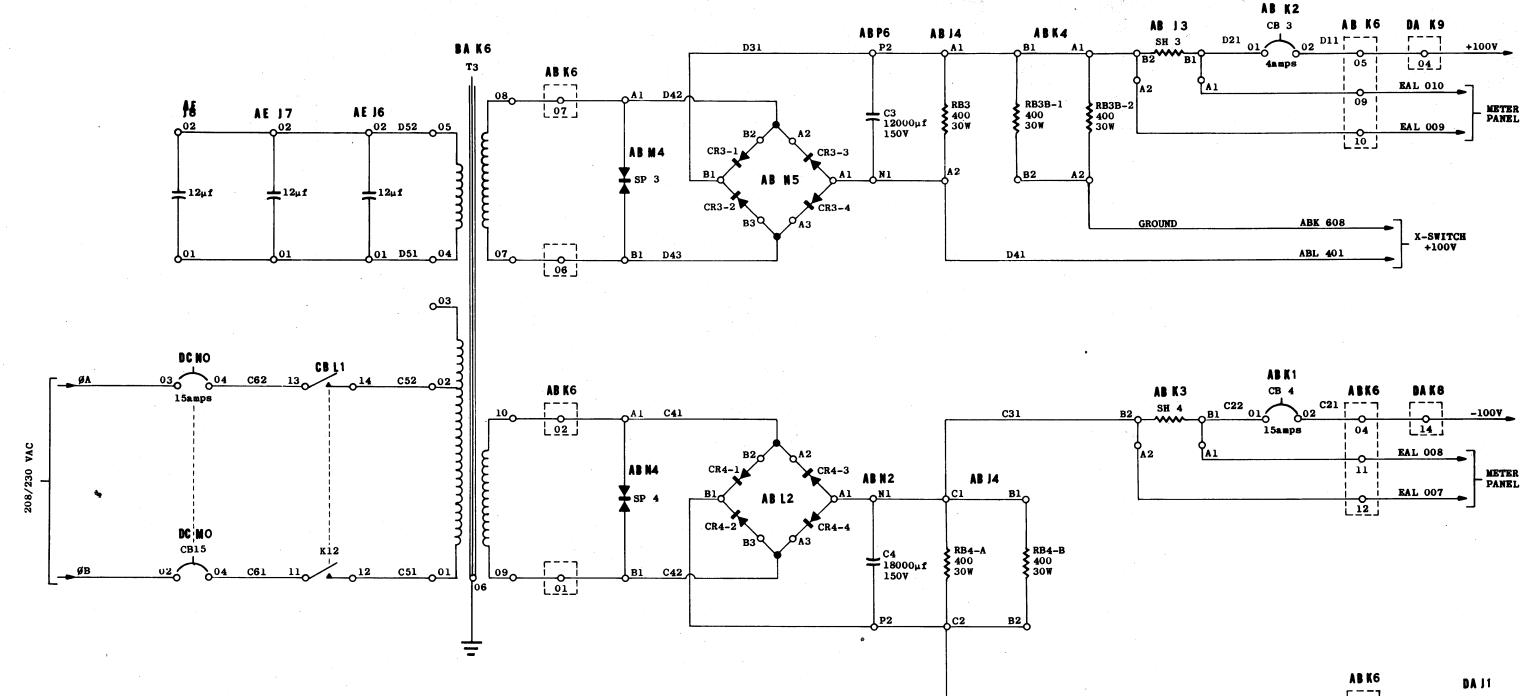

## 6.2 UNREGULATED SUPPLIES

There are six (6) Power Transformers supplying eleven (11) separate raw voltages:  $\pm 19V$ ,  $\pm 20V$ , -24V-A, -33V, -38V,  $\pm 50V$ ,  $\pm 74V$ ,  $\pm 100V$ , and -120V. These transformers are supplied from the input line voltage.

The primary windings of all the transformers except transformer 5 are controlled through contacts of power control relays. Transformer 5 provides -24V-A (control voltage) for power sequencing and -120 neon voltage as soon as primary power is applied. Refer to Figure 6.2-1. The -120 neon voltage is only available in the Power Supply unit until K12 is picked. Also, at this time, 115V, 60 cycle power is supplied to the convenience outlets. Each transformer primary is protected by a circuit breaker.

#### CIRCUIT DESCRIPTION

Refer to Figures 6.2-2, 3, 4, and 5.

Transformers 1, 2, 3,  $\mu$  and 6 are of the constant voltage type. These transformers stabilize line input fluctuations from ±13 percent to approximately ±1 percent, and are used with supplies requiring this regulation.

When supplies require the use of the complete secondary tranformer winding, bridge rectifiers are used. Circuits of this type are  $+7\mu$ V, -120V, and the  $\pm 100$ V supplies. Other circuits requiring only partial use of their transformer secondaries use the two full wave diode rectifier circuits.

The Surge Suppressors (SP) across the transformer secondary windings are of the selinium stack type and are used to suppress the starting surge, due to the large amount of capacitance. They have no function during normal supply operation.

The relays K1, K2 and K5 are used to shunt the current limiting series resistor circuits which prevent the filter capacitors from drawing an excess of current which could damage the rectifier circuits at the onset of power. As the capacitors charge, the relays pick and shunt the current around the limiting resistors.

The fans in each unit, which are tied in parallel across the 115V AC line, are used to cool the individual unit cabinets.

The Elapsed Time Meter indicates the time in hours that the DC Power has been available to the system.

November 15, 1963

в 5370.51

6.2-11

|   | AB K6 | DA J1<br>GROUND |

|---|-------|-----------------|

| : |       |                 |

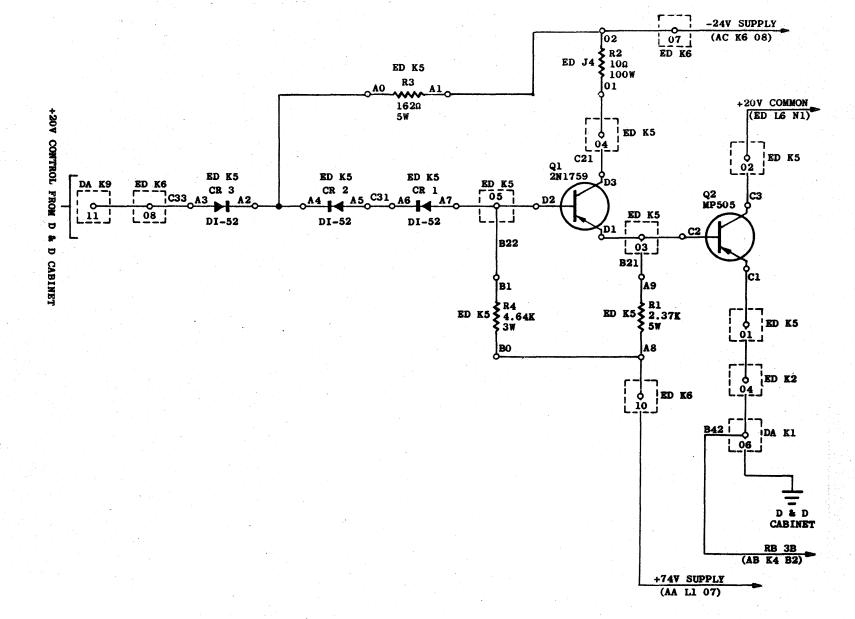

#### 6.3 +20 VOLT ELECTRICAL SWITCH

#### INTRODUCTION

The +20V Electrical Switch is a circuit which provides the means of controlling the +20V Power Supply. This circuit is used to insure that the +20V power is supplied to the transistor circuit prior to the negative voltages. In this way, damage to circuit components is prevented.

This circuit also provides a means of removing the negative potentials from the circuitry, prior to removal of the bias voltage when power is lost due to a power failure, or during power shut down.

#### CIRCUIT DESCRIPTION

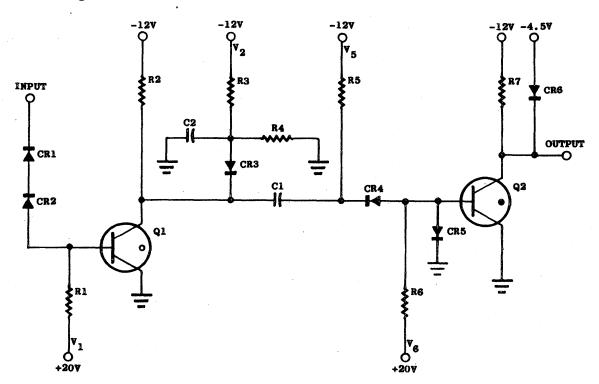

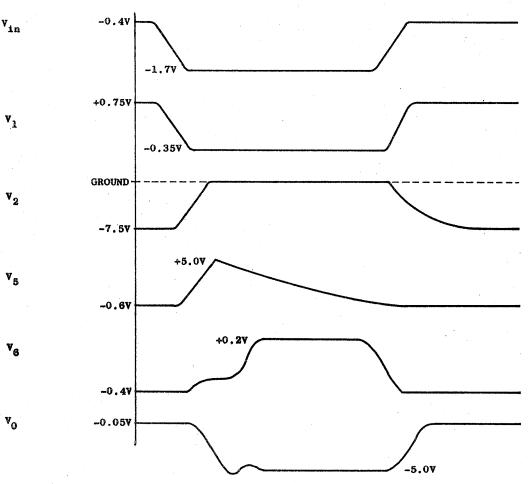

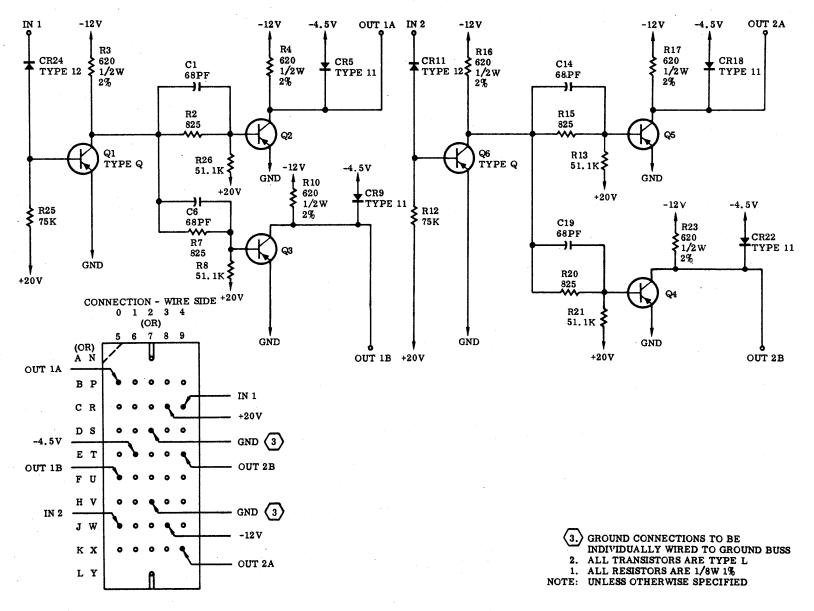

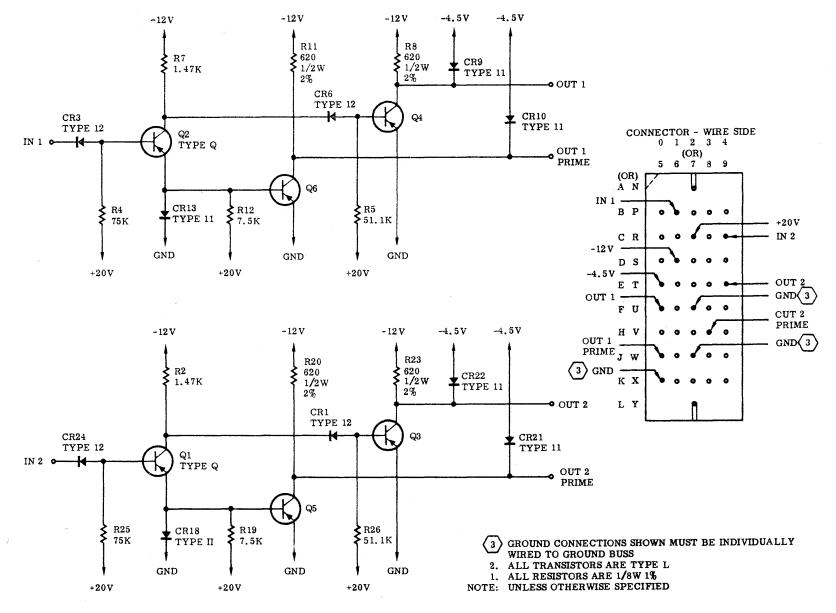

Refer to Figure 6.3-1.

In the quiescent state, the emitter follower transistor Ql has a ground input at DA K9 11 and Q2 is cut off. (This is for Power OFF state.)

The collector voltage of Q2 is from the +20V Supply Common and, depending on whether the transistor Q2 is cut off or saturated, this +20 Common is completed or open, thereby acting as a switch. The +74V and the -24V are bias voltages used in this switch. The -24V is used on the collector of Q1 rather than -12V which is not available prior to the +20V switch. The -24V is available with the wall circuit breaker ON.

The input at DA K9 11 (+20 Control from D & D cabinet), is the input from Control Relay K19 in the Display and Distribution cabinet. When the power fails in any manner, the +20V Supply is the first supply that starts down. All other voltages follow in sequence.

During normal operation -12V is supplied thru a 12.1K resistance to DA K9 11. Negative 24V is available with the wall circuit breaker on. This back biases the diode CR3, allowing base drive current to flow through diodes CR2 and CR1. With the emitter of Q1 tied to +74V, transistor Q1 is saturated. With Q1 on, negative drive current is supplied to the base of Q2 turning it on through the forward biased base emitter junction to ground. With the transistor Q2 on, the +20V Common circuit is complete and +20V is available to the system.

During a power failure or shut down, DA K9 11 is false (ground), shunting the Q1 base drive current, and allowing +74V through resistor R4 to take Q1 to less conduction. With Q1 conducting less, +74V through resistor R1 cuts off Q2, opening the +20V common. This drops the +20V Supply and subsequent voltage will follow.

Printed in U.S.A.

FIGURE 6.3-1. +20V ELECTRICAL SWITCH B 5370.51

November 15, 1963

6.3-2

6.4-1

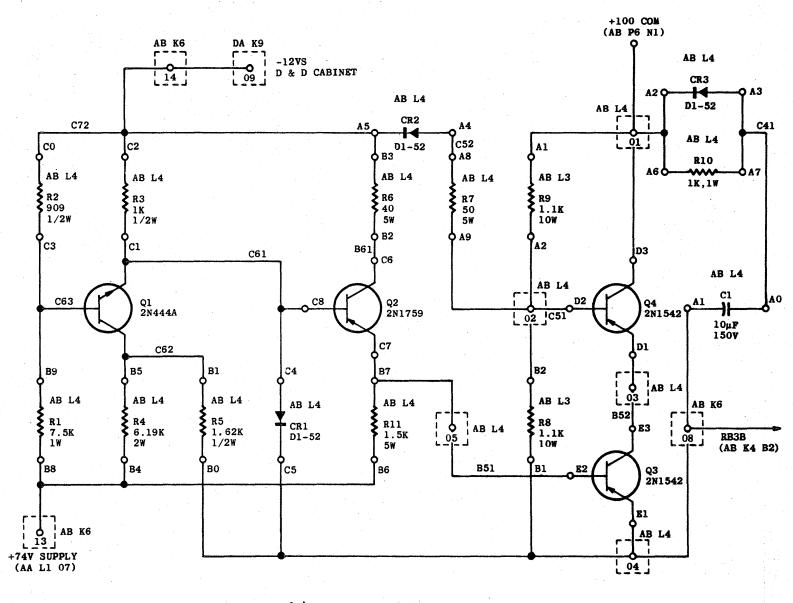

# 6.4 +100 VOLT ELECTRICAL SWITCH

#### INTRODUCTION

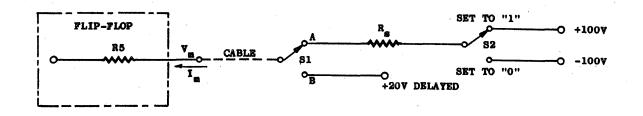

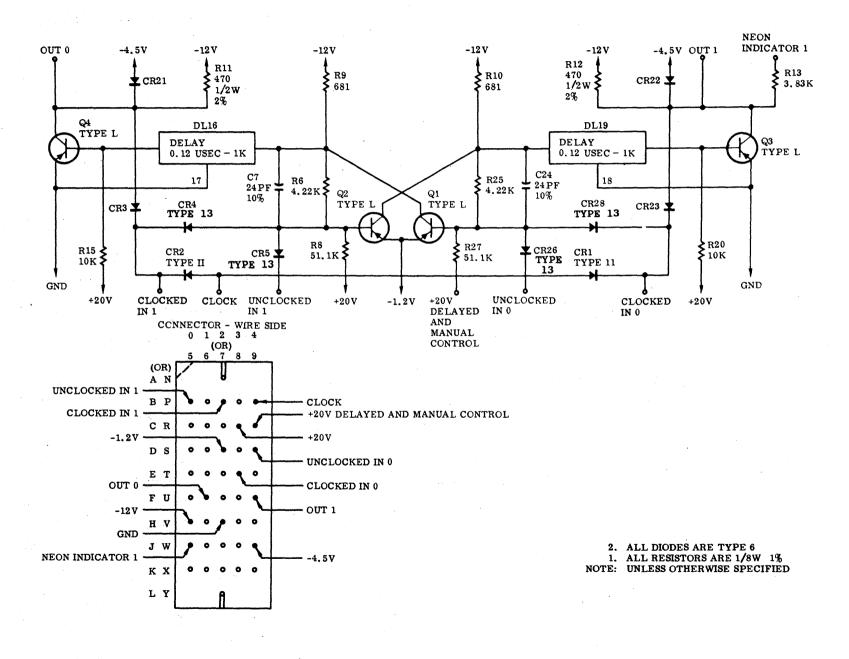

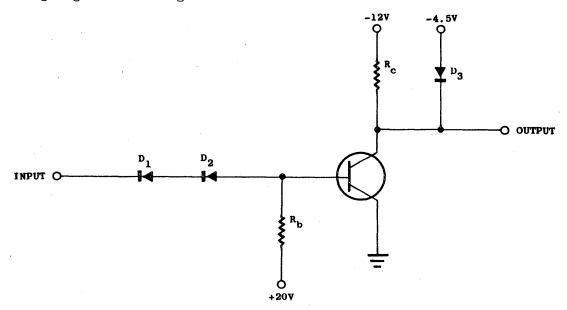

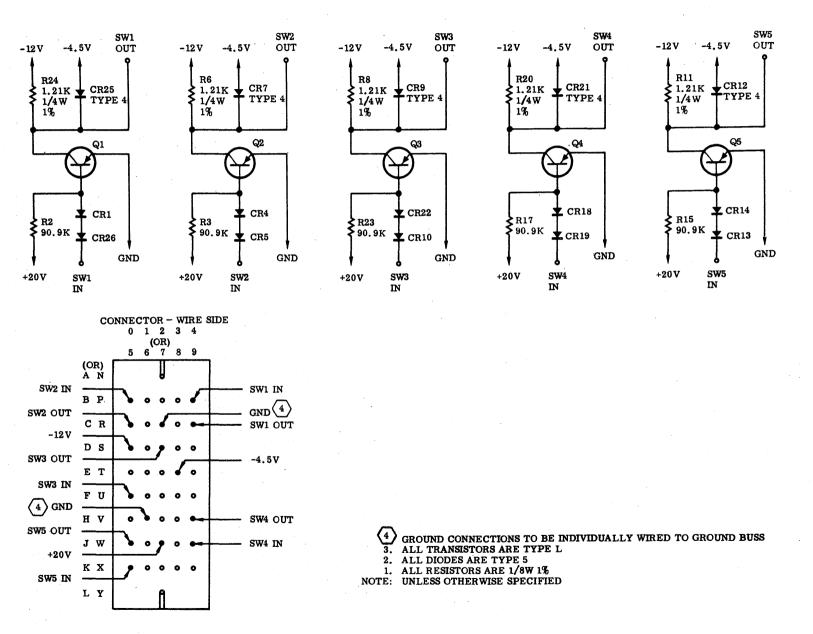

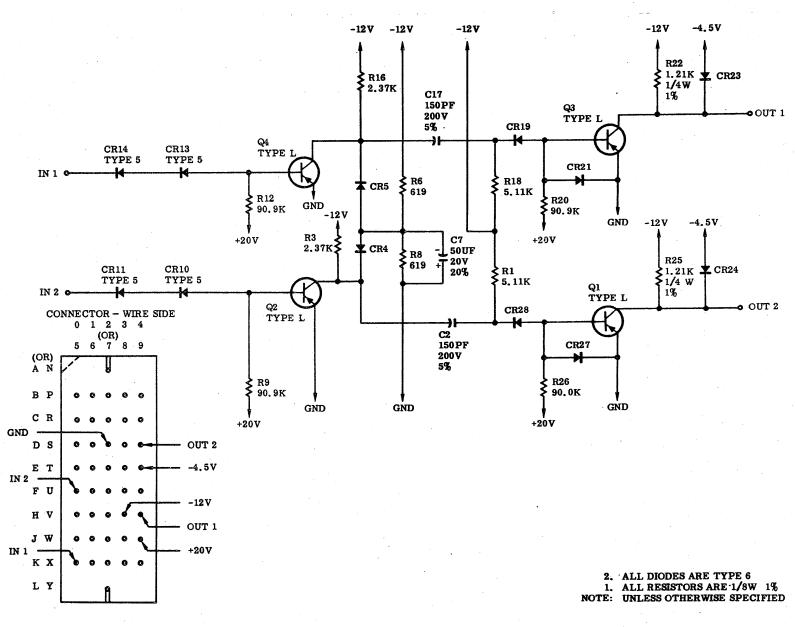

The +100V Electrical Switch provides a means of controlling the +100V Power Supply. The switch circuit is used to insure that all other voltages are present on the system prior to the +100V. The +100V is used to develop the +20V delayed to clear all flip-flops when power is applied.

# CIRCUIT DESCRIPTION

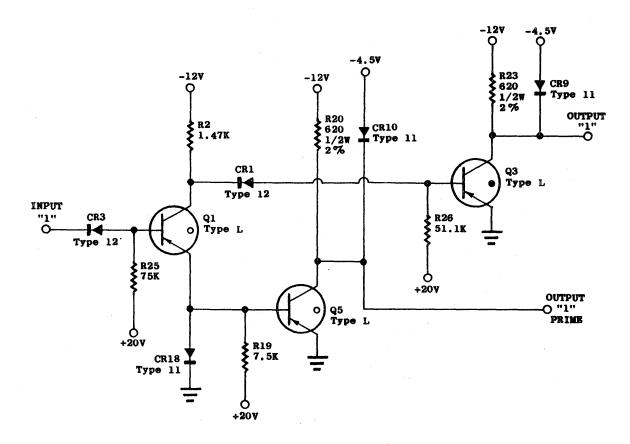

Refer to Figure 6.4-1.

In the quiescent state Ql is in saturation due to the input at DA K9 09 being at ground. The emitter follower, Q2, is conducting enough to hold its emitter at approximately +0.9V. Q3 will be cut off due to Q2. Q4 will also be cut off due to Q3 being at cut off. The +100V Supply will not have a ground reference due to Q3 and Q4. When the circuit goes from the quiescent state to operating state, Q1 senses the change from ground to -12V at DA K9 09. When the emitter of Q1 reaches approximately -9V, Q1 will cut off. At this time, Q2 will be biased on to almost full drive. Q3 will remain off until Q3 receives full drive current. At that time, Q3 will switch to saturation. When Q3 switches, Q4 will also switch to saturation due to the collector emitter circuit of Q3 and Q4. Q4 receives its base drive from the -12V thru CR2. This action causes the collector of Q4 to reference the +100 common line to near ground.

The capacitor and diode circuit in the collector of Q4 allows Q3 and Q4 to turn off at a very low collector voltage. During turnoff transistion, the current normally supplied by Q3 and Q4 comes out of C1 thru CR3. The voltage +100 common decays toward -100V as C1 becomes charged. To lower the surge current of Q3 and Q4 during turn on transistion, the amount of current going into C1 is limited by R10. C1 charges on an RC time constant at this time.

FIGURE 6.4-1. +100V ELECTRICAL SWITCH

6 .4-2 Β 5370.51 November 15, 1963

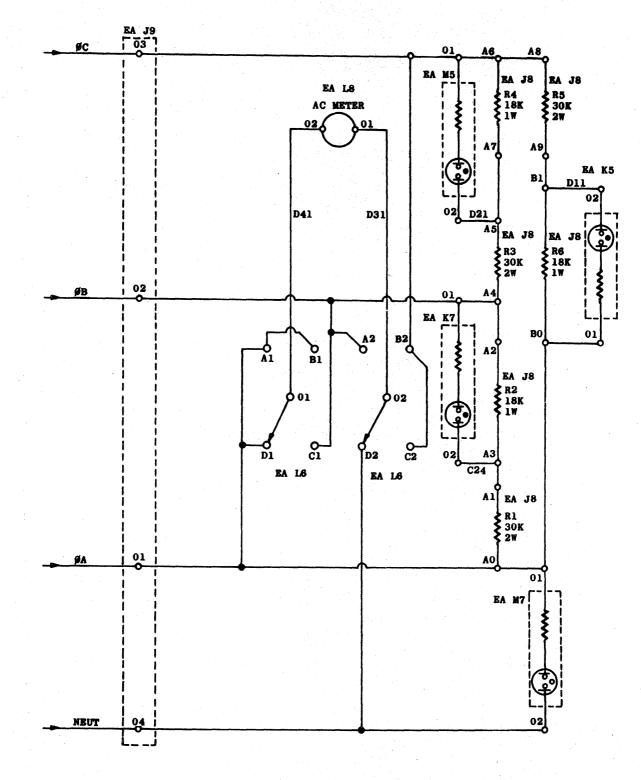

# 6.5 AC METER

#### INTRODUCTION

The AC Meter indicates the voltage across any two legs of the input lines. It is controlled through a four position, two layer, rotary switch and provides monitoring of the three phase  $(3\emptyset)$  AC input.

There are four neon indicators located on the Power Supply cabinet, adjacent to the AC Meter. When lit, they indicate Power ON. There is one light for each of the following combinations: ØAB, ØBC, ØAC and ØAN.

## CIRCUIT DESCRIPTION

Refer to Figure 6.5-1, AC Monitoring Circuit.

In the following explanation, only one position of the AC Meter switch and the accompanying light will be considered. The other three positions and circuits are similar.

With the rotary switch in the position shown in the figure, the AC Meter is monitoring the potential across phases A and N (neutral). The circuit runs from  $\emptyset$ A to D1, O1 or the rotary switch, through the meter, O2, D2 to neutral: the meter will read the voltage between these two legs.

Also across these two legs is the neon and its resistor EA M7. When this light is ON, it indicates there is power across these two phases.

Printed in U.S.A.

# 6.6 ELAPSED TIME METER

#### INTRODUCTION

The Elapsed Time Meter indicates in hours the time that DC power is available to the system. This meter is located on the system Power Supply cabinet.

## CIRCUIT OPERATION

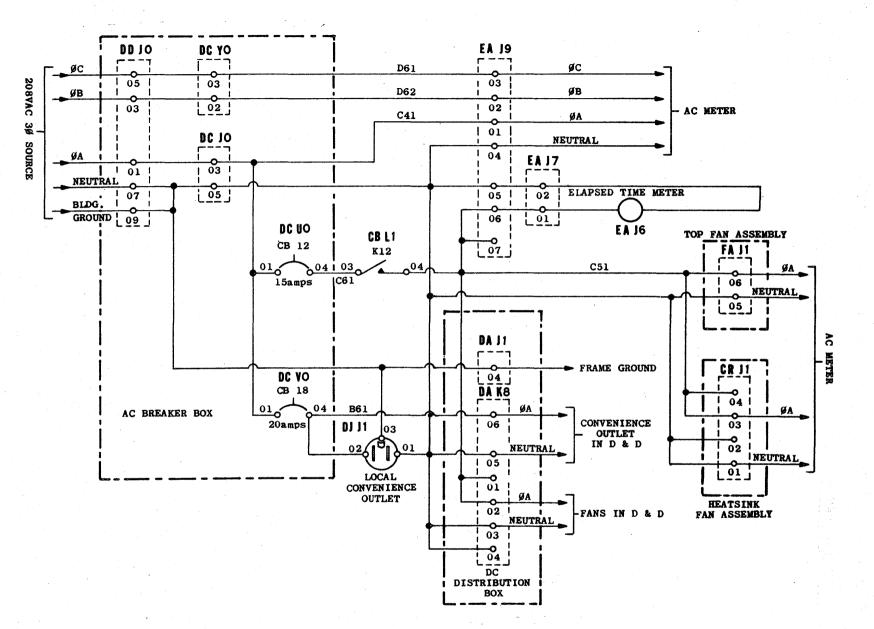

Refer to Figure 6.6-1.

The meter is connected between  $\emptyset$ A and Neutral of the input power line. The meter is protected by a 15 amp. circuit breaker, and is controlled through the 03, 04 contacts of power contactor K12. The contactor is energized and its contacts close any time power is applied to the system. Also shown in the figure is the distribution of the  $\emptyset$ A and Neutral, for use with system fans and convenience outlets.

Printed in U.S.A.

Β 5370.51

November 15, 1963

6.6-2

#### 6.7 METER CHECK SWITCH

#### INTRODUCTION

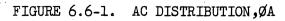

The Meter Check switch is a five deck rotary wafer switch located on the Power Supply Indicator Panel. The Meter Check switch is used to individually monitor the voltage and amperage of the DC supplies.

The voltmeter is 1 millamperes movement and ranges 0-50V. The ammeter is 150 millivolt movement and ranges 0-5A, 0-10A, 0-50A, and 0-100A.

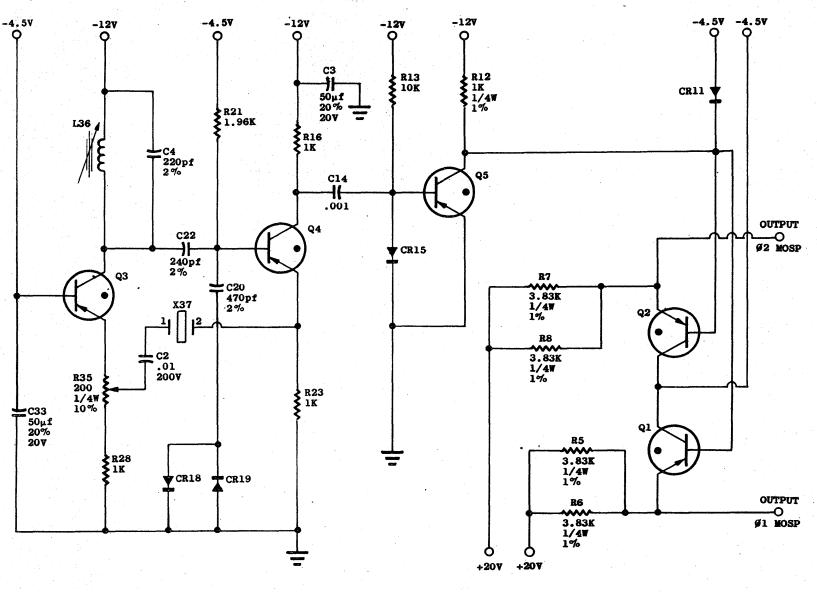

The Meter Check switch is used in conjunction with a voltmeter and an ammeter to select and monitor a given DC Supply.