### L9000 ADJUSTMENTS

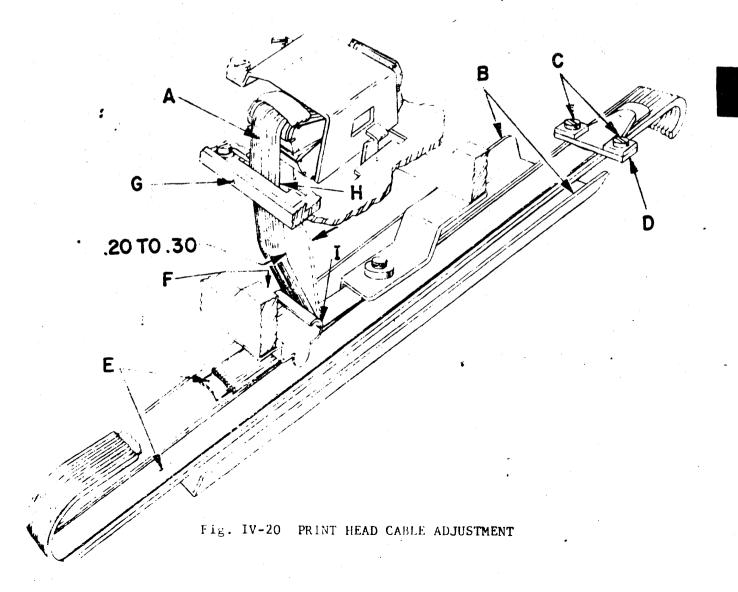

# PRINT HEAD CABLE ADJUSTMENT

With upper carrier assembly G, Fig. IV-20, advanced and print head cable A visually centered with retractor E and channel B there should be .20" to .30" total free play in cable A approximately mid-way between points H and I.

NOTE: With the cable in its normal relaxed position, but bowed toward wall F of the lower carrier assembly, there should be no rubbing of the cable with wall F when the upper carrier assy is advanced or retracted.

To Adjust:

Loosen both screws C on clamp D and with cable A positioned as required, gently pull cable at clamp end snugly against retractor E to remove any excessive slack. Tighten screws C.

### Reason:

To avoid tension and prevent rubbing at the flexing portion of the cable.

Page 18

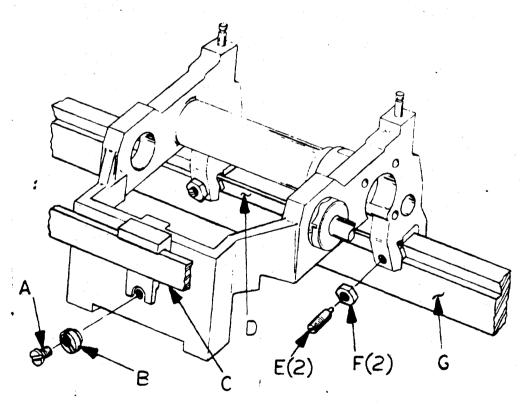

CARRIER ASSEMBLY

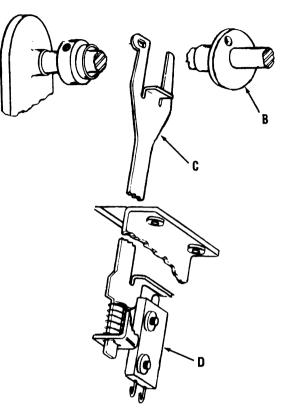

With the carrier assembly positioned on rails C and G of Fig. IV-21:

A) There should be clearance not to exceed .002" between eccentric B and rail C.

B) There should be clearance not to exceed .0015" between link D and high points of rail G.

To Adjust:

A) Loosen screw A, rotate eccentric B as required. Tighten screw A.

B) Turn both screws E as required. Tighten both nuts F.

NOTE: Check for free carrier travel across entire length of rails C and G.

Fig. IV-21 CARRIER ASSEMBLY ADJUSTMENT

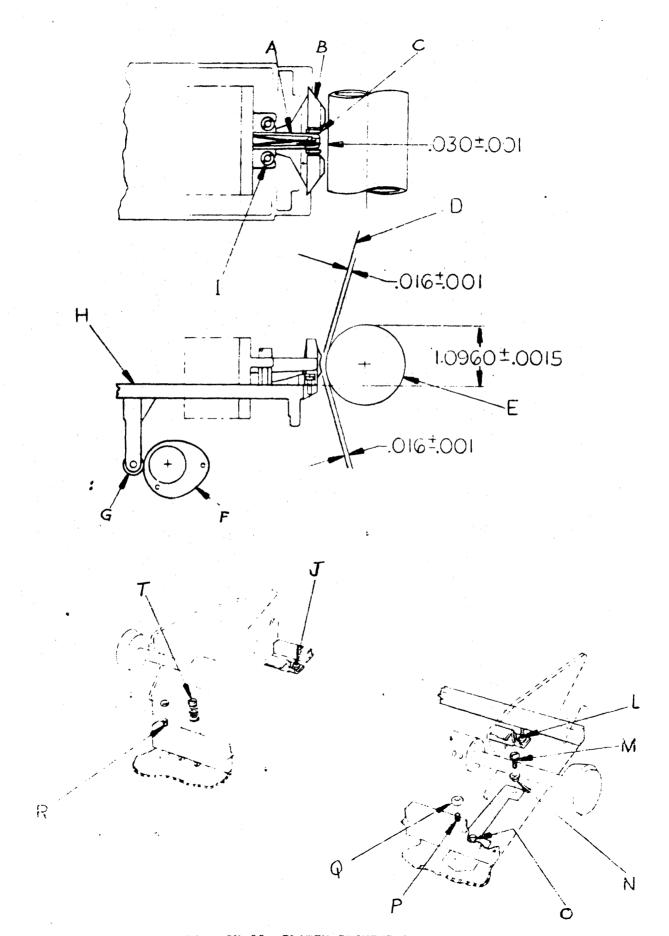

# PLATEN-PRINT HEAD

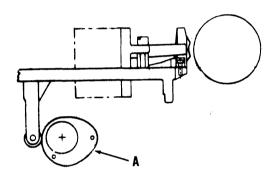

With upper carrier assembly H advanced, Fig. IV-22, roller G limiting on cam F, and with the carrier in any print position, there should be:

- A. 1.0960" +.0015" between top of platen E and top of upper carrier casting H.

- B. .016" + .001" clearance between platen E and the four sled faces D.

- C. .030" <u>+</u> .001" clearance between print head nose A and platen E, and the print head nose should be central to ribbon guide posts C within .006".

To Adjust:

The carriage must be securely tied down with screws T.

- 1. With carrier H in its leftmost position, adjust platen E to its proper height using screw R, then adjust the platen to sled B gap using screw J.

- With carrier H in its right most position, adjust platen E to its proper height using screw P, then adjust the platen to sled gap using eccentric N. Tighten screws M and O and bring up screw L just enough to support the rear of the carriage.

- 3. Recheck adjustments. Fine tune, if necessary, to meet the requirements of tests A and B. Tighten locknuts Q.

- 4. Perform CARRIAGE DRIVE BELT TENSION ADJUSTMENT (60 CPS) as outlined elsewhere in this section.

- 5. Perform CARRIAGE TIMING ADJUSTMENT (60 CPS) as outlined elsewhere in this section.

- 6. Loosen nuts I, position print head A as required. Tighten nuts I with 7 to 8 in. 1bs of torque each.

Reason:

To achieve optimum print quality within a limited pin travel, over a .020" maximum document thickness differential.

Fig. IV-22 PLATEN-PRINTHEAD ADJUSTMENTS

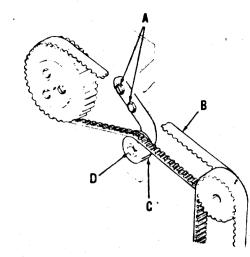

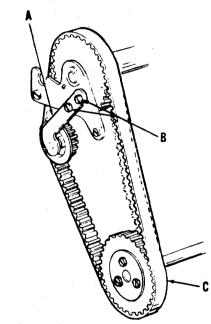

CARRIAGE DRIVE BELT TENSION (60 CPS)

With a 16 oz. load applied at the center of the long span of belt B, Fig. IV-23 belt B should deflect .2".

To Adjust:

Loosen screws A and position idler C as required. Tighten screws A.

Reason:

To provide proper belt tension.

Fig. IV-23 60 CPS CARRIAGE DRIVE BELT TENSION ADJUSTMENT

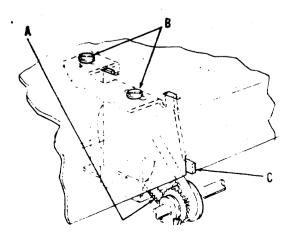

PRINT SHAFT BELT TENSION (60 CPS)

With a force of 16 oz. applied at the center of the long span of belt C, Fig. IV-24, belt C should be deflected .120" to .140".

To Adjust:

Loosen screws B and locate idler pulley bracket A as required. Tighten screws B.

Reason:

To prevent belt slippage and minimize belt noise and bearing wear.

PULSE GENERATOR BELT TENSION (60 CPS)

There should be 8 oz. tension in belt A, Fig. IV-25.

To Adjust:

Loosen screws B. While applying a 16 oz.  $\pm$  1 oz. load to tab C, tighten screws B.

Reason:

To ensure minimum bearing wear and proper pulse generator operation.

Fig. IV-24 60 CPS PRINT SHAFT BELT TENSION

Fig. IV-25 30 CPS PULSE GENERATOR BELT TENSION

#### 1060/09

### Page 22

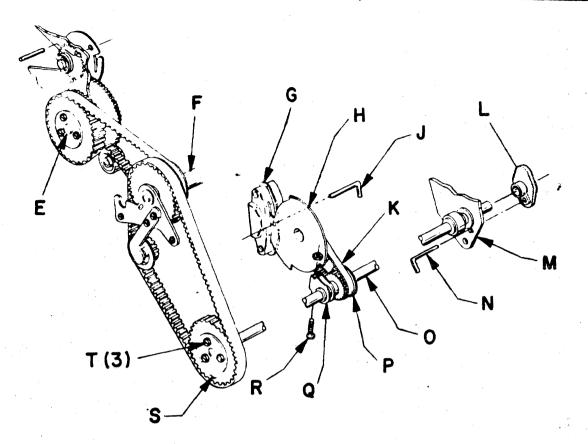

PRINT TIMING ADJUSTMENT (60 CPS)

NOTE: The PRINT SHAFT BELT TENSION (60 CPS) and the PULSE GENERATOR BELT TENSION (60 CPS) adjustments must be completed prior to performing this adjustment.

Print shaft F and jack shaft 0, Fig. IV-26, should be synchronized with pulse generator disc H.

To Adjust:

Loosen three (3) screws T in pulley S, and one (1) screw R on clamp Q. Insert timing pin N in hole in side frame M. Rotate jackshaft O until timing pin N enters the hole in cam L. Rotate pulley P until the hole in disc H is aligned with the slot in plate G. Insert timing pin J and tighten screw R on clamp Q. Manually trip latch FF, Fig. IV-26, and rotate clutch driver BB counter clockwise until clutch dog CC drops into notch on clutch driver BB. Apply clockwise torque to clutch driver BB to ensure that clutch stop DD is in contact with pawl EE. Tighten screws T in pulley S. Remove all timing pins and restore insert/retract clutch to the latched position.

Rotate jackshaft O to see that belt K tracks in the approximate center of pulley P. If not, again insert timing pins N and J and reposition pulley P along jackshaft O as required. Remove all timing pins.

Reason:

To provide proper printer timing.

# Fig. IV-26 PRINT TIMING ADJUSTMENTS

### Burroughs-L8000 Technical Manual

CARRIAGE TIMING

NOTE: The following adjustments must be completed prior to performing this adjustment:

PLATEN-PRINT HEAD ADJUSTMENT, PRINT SHAFT BELT TENSION ADJUSTMENT, CARRIAGE DRIVE BELT TENSION ADJUSTMENT, PULSE GENERATOR BELT TENSION ADJUSTMENT AND PRINTER TIMING (60 CPS) ADJUSTMENT

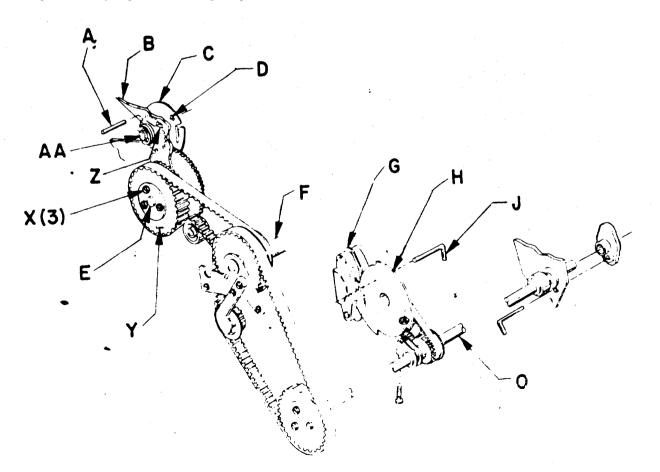

The carriage drive jackshaft E, Fig. IV-27 should be synchronized with the print shaft F and jackshaft O.

To Adjust:

Manually turn the carriage drive jackshaft E counter clockwise to actuate the carriage drive to place the forms spacing camshaft AA in the "zero" position. The "zero" position is set by inserting pin A (.093" dia.) through hole Z of side-frame B and through the corresponding hole D in forms spacing clutch release cam C. The axis of the .093" dia. pin A must be square with the surface of side frame B. Loosen (3) screws X in pulley Y to free pulley from drive hub. Rotate jackshaft ) until the holes in disc H and plate G are in alignment. Insert timing pin J. Tighten three screws X in pulley Y. Remove timing pin J and timing fix-ture.

Reason:

To provide proper carriage synchronization.

Page 24

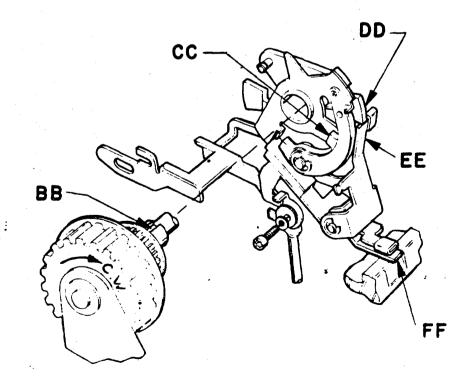

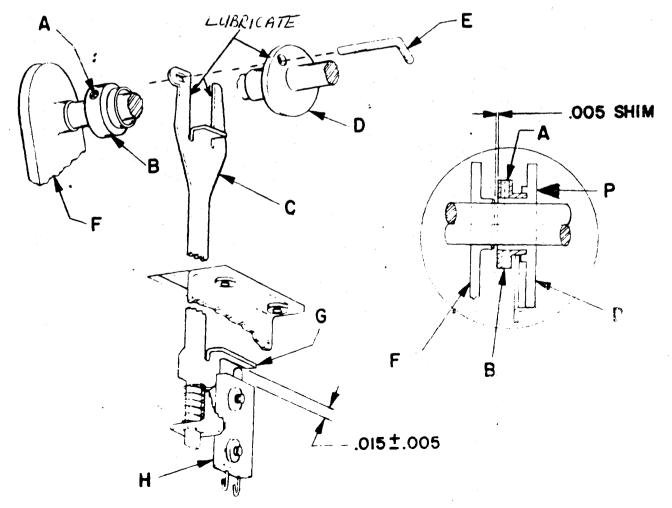

# STATE SWITCH TIMING AND LUBRICATION

The State switch cam "D", Fig. IV-28, should be synchronized with the "insert/retract" clutch. To Adjust:

Loosen setscrew A in hub B as shown in Fig. IV-28. Ensure that the "insert/retract" clutch is latched with the print head in the inserted position. When the print head is fully inserted, slide C should be in the full down position. This position is set by placing aligning pin E (.093" dia) in the hole in cam D and rotating the cam until pin E enters the slot in slot slide C. While holding pin E perpendicular to the face of cam D, a .005" shim should be inserted between hub B and bearing F. With a force P applied to cam face to push the cam and hub against the shim, tighten set screw A to  $9\pm1$  in. Ibs torque. Remove pin E.

With slide C still in the full down position, there should be .015+.005" clearance between tab G on slide C and the top of switch H. Bend tab G as required.

Reason:

To provide proper state switch timing and cam hub running clearance.

Lubricate the points indicated in Fig. IV-28 with a small amount of Alvania No. 1 grease (1624 9369).

### Fig. IV-28 STATE SWITCH TIMING ADJUSTMENT

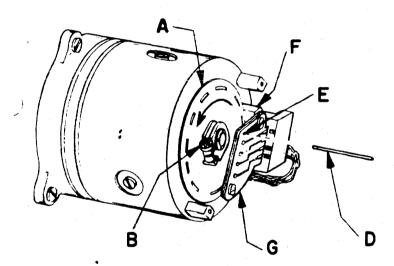

# CARRIER POSITION READOUT (60 CPS)

The Readout disc assembly A, Fig. IV-29, should be centered in the lamp and sensor assembly slot C within .005". Slot C is formed by housing F and printed wiring board assembly G. With the Carrier Position Escape Mechanism latched, any one of the twelve slots in the readout disc should be centered on the LED and photo-transistor axis.

### To Adjust:

Loosen screw B. Insert timing pin D (.046" dia.) in timing hole E. Rotate 'readout disc assembly A (in direction shown by arrow) until the timing pin can enter one of the twelve slots in the disc assembly. Continue rotating readout disc until the slot limits on the timing pin. Holding this contact point, position readout disc assembly A within the lamp and sensor assembly slot C to provide the center-ed condition shown. (Equal within .005"). Tighten screw B and remove timing pin D.

### Reason:

To provide proper readout disc operation.

Fig. IV-29 CARRIER POSITION READOUT ADJUSTMENT

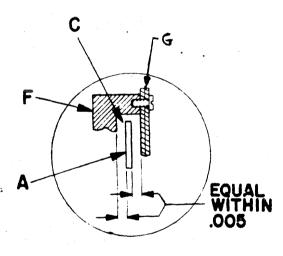

### RIBBON DRIVE LUBRICATION

Remove the ribbon cartridge. Remove the three screws holding the cover plate over the stepper motor gear assembly and remove plate.

Lubricate gears A and B, Fig. IV-30, with a small amount of Alvania No. 1 grease (1624 9369). Replace cover plate, screws and ribbon.

$1 \cap T$

L9000 - 60 CHARACTER PER SECOND

The 60 CPS printer used on the L9000 series machines is an enhancement to the existing L8000 product line. The 60 CPS printer currently utilizes a seven pin solenoid activated print head capable of producing five legible copies of printing and one original at a maximum speed of 60 characters per second. Unlike the L8000 there is no red ribbon capability on the L9000's. This section describes the functional detail of the 60 CPS console via the universal front end.

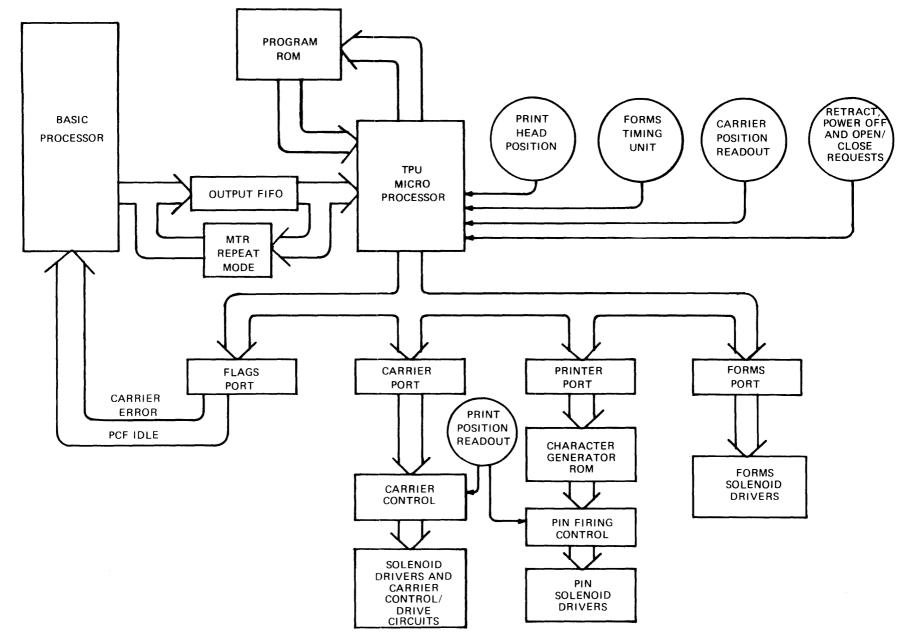

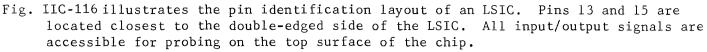

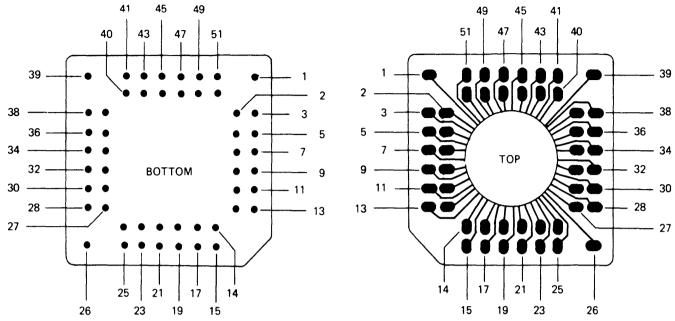

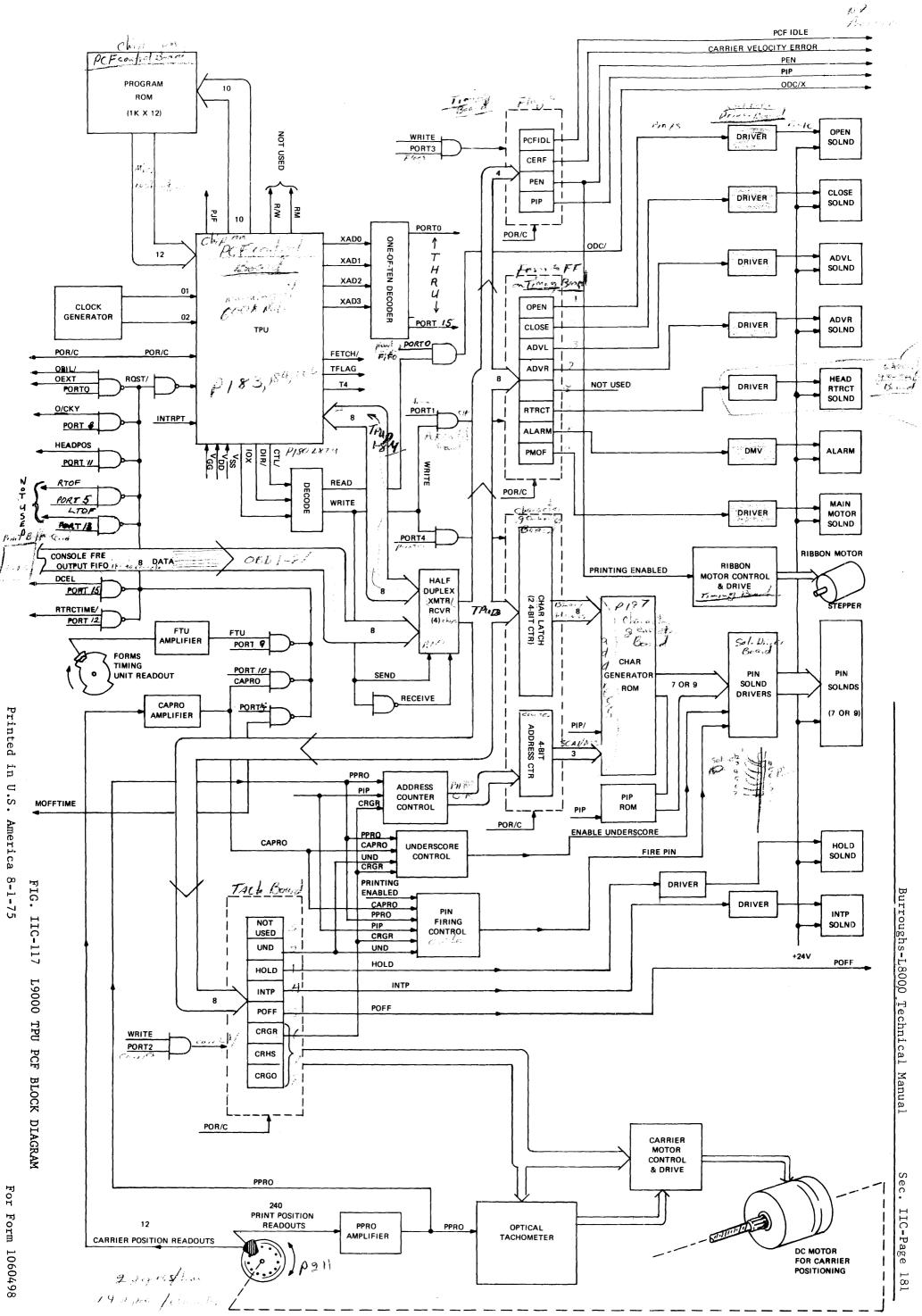

The Printer-Carrier-Forms (PCF) logic of L9000 60 CPS machines is different than that of either the 20 CPS or 30 CPS L8000 style machines. The 60 CPS PCF logic uses a TPU (Terminal Processor Unit) micro processor consisting of a TPU LSIC and 1K of 12-bit Program ROM and associated logic to control the PCF functions of the console.

From a mechanical standpoint the print ball, with its tilt and rotate bands and associated motors or decoder, has been replaced by a seven pin solenoid actuated print head mounted on the carrier.

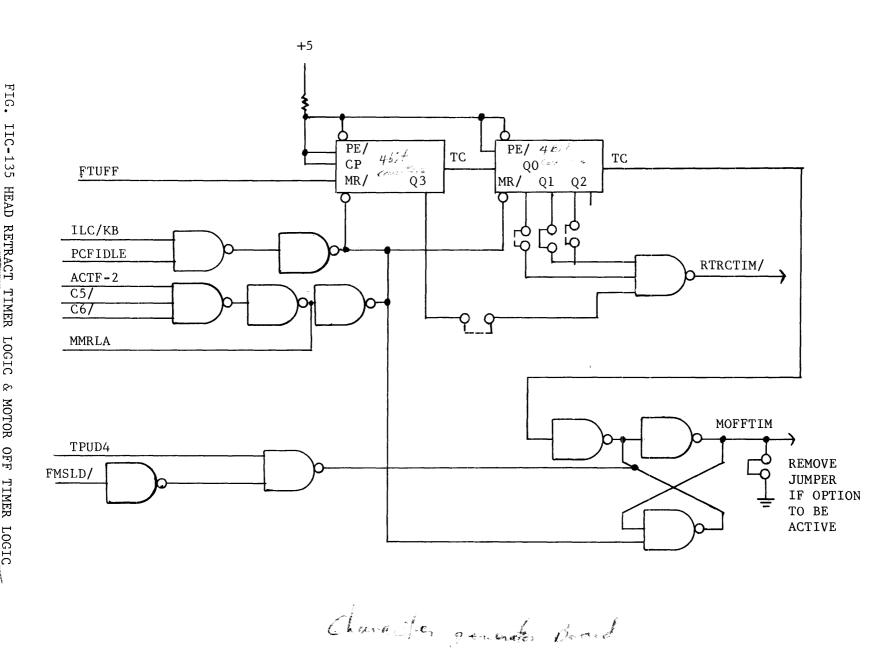

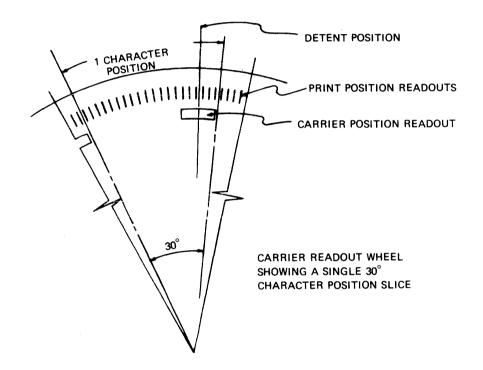

There is an operational difference between the L9000 60 CPS printer and the L8000 ball printer. The 60 CPS pin printer prints in between detent positions, where as the L8000 ball printer escapes and then prints on the detent position after escapement. Considering the following code sequence: PRTRT, A; PRTLT, B

The ball printer will print the characters BA in contiguous print positions; whereas, the 60 CPS L9000 pin printer, executing the same code sequence, will first print the A as the print head moves to the right. The character B will print right on top of the A as the print head moves to the left.

Firmware takes into consideration the overprint mentioned in the above example to insure this will not occur. Existing L8000 firmware sets are compatible with the L9000 hardware.

Unlike the L8000 ball printer firmware, the L9000 firmware has the capability of printing bi-directionally, i.e., printing is possible in both directions, left and" right on the same line. This is accomplished by the L9000 character generator logic which is capable of formatting the correct dot pattern for each character irrespective of the direction of carrier movement.

When the carrier moves to the right, printing of each character occurs serially from left to right. When the carrier moves to the left, printing of each character occurs serially from right to left.

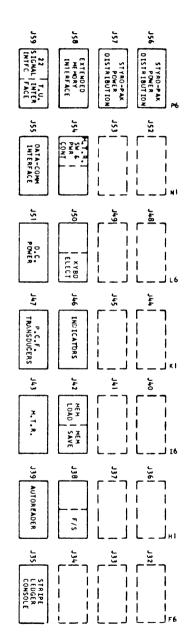

L9000 CARD ASSIGNMENTS.

The card assignments for the 60 CPS machine are shown in Fig. IIC-91. The various machine styles will have different combinations of the console mechanism and controls depending on machine configurations, e.g., 15", 26"with or without MMR. The console interface requirements for the 60 CPS printer are the same and the 60 CPS Printer-Carrier-Forms logic and mechanics are the same for MMR as well as non-MMR machines.

MMR, however, shares the use of the forms control mechanism in its ledger handling operations. There is a certain amount of interaction between the console and MMR operations which firmware takes into consideration to control either one or the other.

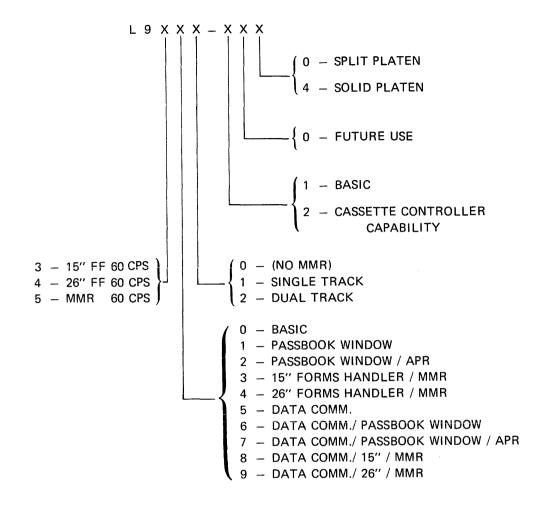

The L9000 configuration chart, Fig. IIC-92, illustrates the various combinations of features in each of the L9000 series machine styles including MMR.

F.E. Dist. AH

For Library Binder 46 For Form 1060498

Printed in U.S. America 8-1-75

# FIG. IIC-91 CARD LOCATION DIGRAM

וד

I

51

σ 0

ω ⋗

|                             | _           |

|-----------------------------|-------------|

|                             | P8          |

|                             | *5          |

| MEMORY LOADER LOGIC         | R2          |

|                             | وړل         |

| SEE NOTE I                  | 26          |

| SEE NOTE I                  |             |

| SEE NOTE 1                  |             |

| SEE NOTE 1                  | ].,         |

| SEE NOTE 1                  | ].4         |

| SEE NOTE 1                  |             |

| SEE NOTE I                  |             |

| SEE NOTE I                  | -1          |

| SEE NOTE I                  | =           |

| SEE NOTE I                  |             |

| SEE NOTE I                  | ""<br>      |

| SEE NOTE 1                  | ="          |

|                             |             |

|                             | -1**        |

|                             | =''         |

| SEE NOTE 1                  | <u>_</u>    |

| SEE NOTE 1                  | <u>-</u>    |

| POWER CONTROL 2             | - *8        |

| POWER CONTROL 1             | K5          |

| TAPE TO IR                  | X 2         |

| CONSOLE FLAGS IA            | ور 🗌        |

| CONSOLE FLAGS 2             | 16          |

| IND STORAGE & CONTROL       |             |

| IND STORAGE & CONTROL       |             |

| DATA SAVE TIMING            | 17          |

| DATA SAVE CONTROL           |             |

| FRE-1                       | $\Box_{n}$  |

| FRE-2                       | н8          |

| FRE-EXT (STRIPE 2) OPTICNAL | Н           |

| COMMAND REG                 | _н2         |

| DEVICE STATUS               |             |

| DECODE/MISC                 |             |

| F/S CONTROL (CPTIONAL)      |             |

| FORMS STATE CONTROL         |             |

| LPR-MC-TIMEOUT COUNTERS     | - 60        |

| LEDGER COUNTER              | F7<br>F4    |

|                             | #* <b>4</b> |

| 1 | CUTPUT/PARITY CHK                        | 26  |

|---|------------------------------------------|-----|

|   | CONTROL/REFRESH                          | 23  |

|   | INPUT PARITY GEN                         | 20  |

|   | ADDRESS DRIVERS                          | P7  |

|   | ADDRESS DR IVERS                         |     |

| 1 | CLOCK GENERATOR                          |     |

|   | TE ING/PIBBON DR 60 CPS                  | N8  |

|   | PROCESSOR SELF SCAN                      | N5  |

|   | PROCESSOR S/M S                          | N2  |

|   | PROCESSOR S/M 6                          | 119 |

| F | PRCCESSOR 3 REG                          | -   |

| Ц | PROCESSOR 1 CROM                         | -13 |

| F | PROCESSOR 2                              | но  |

| L | SYNC PROCESSOR INTERFACE                 | 17  |

| - | FUNCTION GENERATOR                       | 1.4 |

| Г | FRE-I                                    | 1.1 |

| Ц | F RE - 2                                 | -8  |

|   | PCF CONTROL 60 CHS                       | K5  |

|   | CHARACTER GENERATUP'SEE NOTE 2)          | K2  |

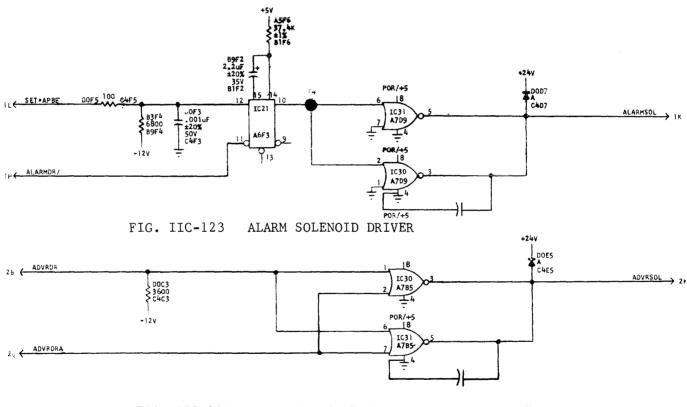

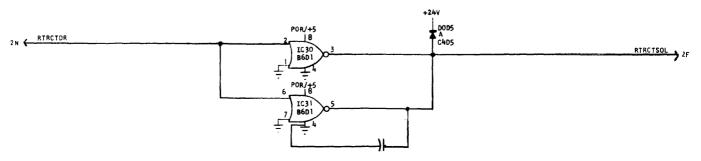

|   | SULENDID CHIVER 60 CHS                   | ورا |

| 1 | CARRIER TACHOMETER                       | 16  |

|   | CA-RIER_CRIVER                           | 13  |

|   | MOD 2 INDICATOR DRIVER                   | 10  |

|   | MOD 2 INDICATOR DRIVER                   | 17  |

|   | DATA SAVE R.'W                           | 114 |

|   | SL CLOCK/AUTO READER                     | 11  |

|   | R/W LOGIC (STRIPE 1)                     | н8  |

|   | R/W LOGIC (STRIPE 2) OPTIONAL            | н5  |

|   | INPUT TO R/W                             | H2  |

|   | LEDGER READ WRITE (STRIPE 1)             | 69  |

|   | LEGGER READ/WRITE (STRIPE 2)<br>OPTIONAL | 66  |

|   |                                          | G3  |

|   | FORMS STATE DECODES                      | GO  |

|   | S/L CONTROL CKTS                         | F7  |

|   | SL SOLOR CELL CKTS                       | F4  |

LA

ł

FIG. IIC-92 L9000 STYLE CONFIGURATOR

L9000 (60 CPS) CONSOLE PRINTER CARRIER FORMS.

The L9000 (60 CPS) Console Printer Carrier Forms mechanism, like the L8000 (20 CPS and 30 CPS) console mechanism, is controlled by the basic processor through a set of codes which specifies the control and its parameter, and the characters to be printed. These codes are loaded by the basic processor into an output buffer, where they are retrieved and interpreted by the TPU microprocessor to perform the specified oper-ation. Fig. IIC-93 is a generalized block diagram of the L9000 PCF mechanism.

Printer Carrier Forms Code Set

The code set for the control of the L9000 printer carrier forms consists of 8-bit codes, which can be divided into three groups: control codes, print codes, and no-op codes.

Control Codes The control codes are used to control printing format, forms handling, carrier positioning, as well as print head retraction and engagement. These control codes appear in ASCII 0 and 1, and are described in Fig. IIC-94.

Page 148

Burroughs-L8000 Technical Manual

| CONTRO                   | L CODES                                  |                        |                                                                                                                                                                                                         | CONTRO            | L CODES           |                               |                                                                                                                                                                                                             |

|--------------------------|------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CODE                     | NAME                                     | CONTROL<br>FUNCTION    | REMARKS                                                                                                                                                                                                 | CODE              | NAME              | CONTROL<br>FUNCTION           | REMARKS                                                                                                                                                                                                     |

| 0-1                      | PIP                                      | PRINT-IN-PLACE         | MODIFY THE NEXT PERIOD OR COMMA<br>TO PRINT IN BETWEEN PRINT POSITIONS.                                                                                                                                 | 1-2               | PMOF              | AC MOTOR OFF                  | RETRACTS THE PRINTHEAD (IF IT HAS<br>NOT BEEN RETRACTED) AND WAITS<br>UNTIL P-C~F IS IN THE IDLE STATE,<br>THEN TURNS THE AC MOTOR OFF.                                                                     |

| 0-4<br>0-5<br>0-6<br>0-7 | PRTLT<br>PRTRT<br>PRTLT<br>PRTRT         | PRINT<br>DIRECTION     | PRINT TO THE LEFT<br>PRINT TO THE RIGHT<br>PRINT TO THE LEFT<br>PRINT TO THE RIGHT                                                                                                                      | 1-3               | ENGG              | ENGAGE<br>PRINTHEAD           | CLOSES THE PLATEN (IF IT IS OPEN)<br>AND THEN ENGAGE THE PRINTHEAD<br>AGAINST THE PLATEN ROLLER READY                                                                                                       |

| 0-8<br>0-9<br>0-A        | OPN<br>Clos<br>O/C                       | PLATEN<br>OPEN/CLOSE   | OPEN PLATEN<br>CLOSE PLATEN<br>Complement platen                                                                                                                                                        | 1-4               | RTRCT             | RETRACT                       | FOR PRINTING.<br>WILL RETRACT THE PRINTHEAD.                                                                                                                                                                |

|                          |                                          |                        | IF THE PRINTHEAD IS ENGAGED<br>AGAINST THE PLATEN, AN OPEN<br>PLATEN OPERATION IS ALWAYS<br>PRECEDED BY A HARDWARE<br>INITIATED HEAD RETRACT                                                            | 1-5               | BKSP              | HORIZONTAL<br>SPACING         | WILL POSITION ONE SPACE OPPOSITE<br>THE DIRECTION PRESENTLY SPECIFIED.<br>DOES NOT CHANGE SPECIFIED<br>DIRECTION, EXCEPT TO ACCOMPLISH<br>BACKSPACE.                                                        |

| 0-C<br>0-D               | O-C SHLT CARRIER<br>O-D SHRT POSITIONING |                        | MOVE CARRIER N POSITIONS TO THE<br>LEFT (SHLT) OR RIGHT (SHRT).<br>N IS THE 8-BIT BINARY NUMBER IN<br>THE OUTPUT FIFO IMMEDIATELY<br>FOLLOWING SHLT OR SHRT.<br>N = 0 NO MOVEMENT<br>N = 1 ONE POSITION | 1-6               | ENUND             | ENABLE<br>UNDERLINE           | WILL MODIFY SUBSEQUENT PRINT<br>CHARACTERS (INCLUDING SPACES)<br>BY UNDERLINING THEM. THIS IS IN<br>EFFECT UNTIL SUCH TIME A DSUND<br>CODE IS RECEIVED.                                                     |

|                          |                                          |                        | ETC.<br>SHLT SETS PRINT DIRECTION TO THE<br>LEFT. SHRT SETS PRINT DIRECTION<br>TO THE RIGHT                                                                                                             | 1-7               | DSUND             | DISABLE<br>UNDERLINE          | WILL DISABLE UNDERLINING OF PRINT<br>CHARACTERS CAUSED OF THE<br>CODE. HAS NO EFFECT ON THE UNDER-<br>SCORE CODE (5-F)                                                                                      |

| 0-E<br>0-F               | L NL T<br>L NR T                         | CARRIER<br>POSITIONING | UNASSIGNED CODE<br>NOT USED BY L9000                                                                                                                                                                    | 1-8<br>1-9<br>1-A | ALT<br>ART<br>ARL | VERTICAL<br>FORMS<br>MOVEMENT | ADVANCE LEFT PLATEN (ALT), ADVANCE<br>RIGHT PLATEN (ART), OR BOTH RIGHT<br>AND LEFT PLATENS (ARL) N LINES. N<br>IS THE 8-BIT BINARY NUMBER IN THE<br>OUTPUT FIFO IMMEDIATELY FOLLOWING<br>THE ADVANCE CODE. |

| 1-0                      | ALARM                                    | ALARM                  | SOUNDS AUDIBLE ALARM                                                                                                                                                                                    |                   |                   |                               | THE ADVANCE CODE.                                                                                                                                                                                           |

| 1-1                      | POFF                                     | POWER OFF              | RETRACTS THE PRINTHEAD (IF IT HAS<br>NOT BEEN RETRACTED) AND WAITS<br>UNTIL P-C-F IS IN THE IDLE STATE,<br>THEN CAUSES MACHINE TO GO ON<br>STANDBY POWER.                                               | 1 - C<br>1 - D    | SKHDL<br>SKHDR    | VERTICAL<br>FORMS<br>MOVEMENT | ADVANCE LEFT (SKHDL) OR RIGHT<br>(SKHDR) PLATEN TO TOP OF FORM.<br>IN PRESENT L9000 DESIGN, WILL<br>ADVANCE SPECIFIED PLATEN ONE<br>LINE.                                                                   |

|                          |                                          |                        |                                                                                                                                                                                                         | 1-E<br>1-F        | INLT<br>INRT      | CARRIER<br>MOVEMENT           | MOVES CARRIER TO LEFT (INLT) OR<br>RIGHT (INRT)BUMPER AT ESCAPE<br>VELOCITY (6"/SEC). INLT SETS<br>PRINT DIRECTION TO THE RIGHT. INRT<br>SETS PRINT DIRECTION TO THE LEFT.                                  |

all colors and on Alsiah Phillips

FIG. IIC-94 L9000 CONTROL CODES

Burroughs-L8000 Technical Manual

.

Sec. IIC-Page 149

Print Codes and No-op Codes

The print codes and No-op codes used in the L9000 are shown in Fig. IIC-95. Unlike the L8000 machines the ASCII print codes do not require any conversion into tilt or rotate coding as the L9000 pin printer contains no tilt or rotate mechanics. Instead, the ASCII print code, under TPU microprocessor control, is fed into a character generator ROM which formats the character as the print head moves across the platen.

The No-Op codes, as shown in Fig. IIC-95, may be classified into 2 types.

Regular No-ops.

0-0, 0 B, 1-B and all ASCII stick 8 and 9 codes are regular no-ops that time out within 300 microseconds after they are loaded into the output buffer by the basic processor. After this maximum time delay, the TPU microprocessor is ready to service the next code (if any) in the output buffer.

No-ops with Delay.

0-2 and 0-3 are no-ops that provide a delay of 100-150 MS before the TPU microprocessor returns to service the next code (if any) in the output buffer.

The P-C-F idle status bit will indicate "busy" during the delay when any of these no-ops codes are processed by the TPU microprocessor.

P-C-F INITIALIZATION

The P-C-F control program in the TPUmicroprocessor will be initialized to the idle state by any one of the following:

- A. Machine full operational power is turned on.

- B. The manual reset button is depressed, or a "No memory card" error occurs.

- C. A "Reset Port and Clear Buffers" IOCTL command is issued to the console port.

The initialization will turn the AC motor on, retract the printhead, open the carriage, and set the print direction to the right. Any other forms or carrier movement must be initiated programmatically.

Initialization will also clear the carrier velocity error flag.

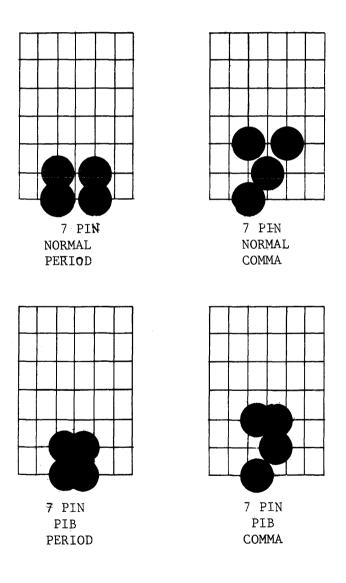

PRINT-IN-PLACE

All codes, except 2-0, that are preceded by the PIP control code 0-1, will print one of two symbols: PIP Comma, or PIP Period.

Specific code assignments are shown as follows:

| CODES                | SYMBOLS |

|----------------------|---------|

| 2-B, 2-C<br>2-F, 3-C | COMMA   |

| 2-7, 2-E<br>3-E      | PERIOD  |

| B8<br>B7<br>B<br>I | 6 —<br>B5 |    |    |    |    | 0<br>0<br>0        | 0<br>0<br>1      | 0<br>0<br>1<br>0 | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>0 | 0<br>1<br>0<br>1 | 0<br>1<br>1<br>0 |       |

|--------------------|-----------|----|----|----|----|--------------------|------------------|------------------|------------------|------------------|------------------|------------------|-------|

| TS                 | в4        | B3 | B2 | Bl |    | 0                  | 1                | 2                | 3                | 4                | 5                | 6                | 7     |

|                    | 0         | 0  | 0  | 0  | 0  | NO-OP              | ALARM            | SPACE            | 0                | @                | Р                | `                | р     |

|                    | 0         | 0  | 0  | 1  | 1  | PIP                | POFF             | 1                | 1                | Α                | Q                | а                | P     |

|                    | 0         | 0  | 1  | 0  | 2  | NO-OP <sup>2</sup> | MOF              | i í              | 2                | В                | R                | Ь                | r     |

|                    | 0         | 0  | 1  | 1  | 3  | NO-OP <sup>2</sup> | ENGG             | #                | 3                | C                | S                | с                | S     |

|                    | 0         | 1  | 0  | 0  | 4  | PRTLT              | RTRCT            | \$               | 4                | D                | т                | d                | t     |

|                    | 0         | 1  | 0  | 1  | 5  | PRTRT              | BKSP             | %                | 5                | Ε                | U                | e                | u     |

|                    | 0         | 1  | 1  | 0  | 6  | PRTLT              | ENUND            | ૩                | 6                | F                | v                | f                | v     |

|                    | 0         | 1  | 1  | 1  | 7  | PRTRT              | DSUND            | 1                | 7                | G                | W                | g                | W     |

|                    | 1         | 0  | 0  | 0  | 8  | OPN                | ALT <sup>1</sup> | (                | 8                | Н                | x                | h                | x     |

|                    | ۱         | 0  | 0  | 1  | 9  | CLOS               | art <sup>1</sup> | )                | 9                | I                | Y                | 1                | у     |

|                    | 1         | 0  | 1  | 0  | 10 | 0/C                | ARL <sup>1</sup> | *                | :                | J                | Z                | j                | z     |

|                    | 1         | 0  | 1  | 1  | 11 | NO-0P              | NO-OP            | +                | .3               | К                | <u>ر</u> ۲       | k                | {     |

|                    | 1         | 1  | 0  | 0  | 12 | SHLT               | SKHDL            | ,                | <                | L                | $\mathbf{N}$     | 1                |       |

|                    | 1         | 1  | 0  | 1  | 13 | SHRT               | SKHDR            | -                | =                | М                | ]                | m                | }     |

|                    | 1         | 1  | 1  | 0  | 14 | LNLT               | INLT             | •                | >                | N                | ^                | n                | ~     |

|                    | 1         | 1  | 1  | 1  | 15 | LNRT               | INRT             | 1                | ?                | 0                |                  | 0                | BLANK |

1 - MUST BE FOLLOWED BY A COUNT

2 - NO-OP WITH DELAY OF 50-100 ms

FIG. IIC-95 L9000 94 CHARACTER INTERNAL CODES

The space code (2-0) will cause a space to be "printed-in-place," instead of a PIP punctuation.

All other codes will be mapped into either a comma or period.

The print-in-place punctuation is printed while the print-head is moving over a detent position (between character positions). This requires that the printhead be in a state of continuous motion both prior to and after the PIP punctuation if printed. The type of carrier motion on either or both sides of the PIP punctuation can be either a carrier positioning sequence, a printable character, a space code, or any combination of these. They must all be in the same direction (right or left) as the PIP printing.

If the PIP control code is issued when the printhead is not in a state of motion, or, if a command is not immediately issued after the PIP punctuation to keep the printhead in a state of continuous motion, certain carrier maneuvers are to be performed by hardware to ensure that the above mentioned requirement is met. Essentially, the printhead has to be backspaced once, before being moved forward to print the PIP punctuation. After the PIP punctuation is printed, the printhead will move one space beyond, before being backspaced to its intended detent position.

Attempts to print the PIP punctuation on either the left-most or right-most detent position will result in a carrier error condition.

UNDERLINE.

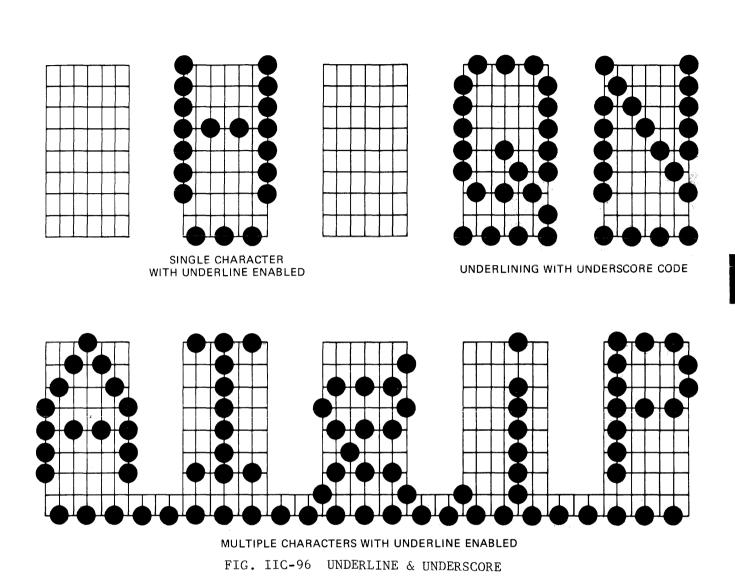

The underline function shown in Fig. IIC-96 can be done only by a printhead that has 9 needles. This may be done by one of two ways:

The underscore code (ASCII 5-F) is loaded into the output buffer, and then used to address the character generator ROM to print a 4-dot underscore. Note that this method is not valid for certain non-domestic character generator ROM's whose 5-F code does not address the underscore character.

An enable underline code, ENUND, (1-6) is issued, which will modify subsequent print characters (including the space code, 2-0) by underlining them. This will be in effect for all subsequent print characters until a disable underline code, DSUND (1-7) is issued. It will have no effect on the BKSP code, 1-5.

This mode of underscore operation required only one pass of the printhead motion at the same time as the characters to be underlined, are being printed. This is a 5 dot/character underline, except for the first and last character of a print field.

Both types of underline operations should not be attempted simultaneously, because each of their dot constructions does not coincide with the other. Doing so will result in firing the 9th head solenoid in consecutive print positions.

Therefore, firmware should replace the underscore code with a space code in print fields where underline has been enabled by the ENUND code (1-6). In this case, the 4-dot underscore will be replaced by the 5-dot underline, modifying the space character.

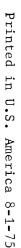

AC MOTOR ON/OFF CONTROL OPTION.

On-off control of the AC motor is an optional feature, and not part of standard construction.

With this option installed, the AC motor can be turned off programmatically by the motor off control code (MOF). There is also an optional motor off timer, such that if the printer-carrier-forms are idle continuously for approximately 13 seconds, the AC motor will automatically turn off.

The printhead is always retracted by hardware logic before the motor is turned off.

Any code, including no-op codes, will turn the motor back on, except the 0-0, 1-1, or 1-2 codes.

In striped ledger machines, a ledger line advance command to the striped ledger port will also turn the motor back on.

Printed in U.S. America 8-1-75

The O/CKY line to the TPU processor, when activated, will also turn the motor on.

# CAUTION

After the AC motor is turned off, the TPU processor control program is in its idle loop. If the head engage clutch is activated to trip the printhead state switch, the control program will react by turning on the AC motor to attempt to perform a head retraction. Anyone servicing the mechanical parts in that vicinity must take extra precaution to prevent injury.

PRINTHEAD ENGAGEMENT AND RETRACTION.

The printhead is retracted by the following:

A RTRCT code (1-4).

The printer-carrier-forms are idle for a time period of 1.6 seconds. This time period is field alterable in increments of 400 ms starting at a minimum of 400 ms, up to a maximum of 6 seconds.

The printhead is always retracted prior to AC motor off or power off.

An open platen operation is always preceded by a head retraction to avoid mechanical interference.

The printhead is engaged by the following:

An ENGG code (1-3)

Any code in sticks 2 through 7 (except the space code, 2-0) or any codes in sticks 10 through 15, will close the carriage, and engage the printhead against the platen to print the underline.

# INTERFACE WITH MMR.

MMR shares the use of the forms control mechanism in its ledger handling operations. There are certain interaction between the console and MMR operation that firmware has to take into consideration to control one or the other.

FIRMWARE INTERLOCKING OF CONSOLE AND STRIPED LEDGER.

Firmware should not perform any striped ledger operation until the "Console Printer, Forms and Carrier Quiet and Print Buffer Empty" condition is indicated by the console. Once ledger command execution begins, the "Console/SL Interlock Required" flag will be set to 1 and firmware should not perform any print buffer operations that might cause mechanical interference between the console and ledger mechanism until the console/SL interlock required flag is reset to 0. With the flag "Console/SL Interlock Required" =1, the following console operations can be performed:

- a. Power off, audible alarm, all indicators.

- b. Carrier positioning.

- c. Advance left platen on a split platen console.

- d. Print to the left of the left ledger margin.

Note that in case of a console carrier stall or overspeed condition, the flag "Console Printer, Forms and Carrier Quiet and Print Buffer Empty" will be in a state to inhibit SL operations until the stall or overspeed condition is cleared.

CONSOLE OPERATIONS WHEN A MMR JAM CONDITION EXISTS

The console operations that can be performed while a S.L. jam condition is present are:

- a. Power Off; Audible Alarm; All Indicators.

- b. Open or close platen.

- c. Carrier positioning.

- d. Advance left platen on a split platen console.

- e. Print to the left of the left ledger margin.

STRIPED LEDGER STATUS ON CONSOLE PORT

Two striped ledger status bits will be included as the console port device status:

- a. Ledger positioned: This bit is 1 if and only if the ledger positioned transducer at the gripper jaws indicates a ledger is positioned.

- b. Console/SL interlock required: This bit, when set, indicates that certain console operations should not be performed programmatically in order to avoid mechanical interference between SL and console mechanisms.

Those console operations that should not be performed when this bit is 1 are listed below:

Printing on the ledger.

Open or close the platen.

Advance right platen on a split platen machine or advance left platen on a solid platen machine.

All console operations not listed above may be performed when this bit is 1.

INTERFACE WITH APR.

The APR is part of the console port. It shares the universal front end with the console device control.

The APR Address is IOAR=10000

The processor can control the enabling and inhibiting of the console output FIFO extend line that goes into the TPU microprocessor, by issuing proper IOCTL commands to the APR control logic. APR uses the console port output FIFO in the serial output mode. Consequently, when APR is output active, APR logic can inhibit erroneous operation of the P-C-F control logic by inhibiting the FIFO extend line to the TPU microprocessor. This P-C-F inhibit applies only to P-C-F operations initiated by control codes and print codes passing through the FIFO. Other P-C-F operations that are not issued through the FIFO, can still be performed, such as:

a. Alarm IOCTL

b. Power off IOCTL

c. O/CKY line remains active

d. The timer that controls head retraction and AC motor off remains active.

The keyboard can remain enabled. APR has its own input FIFO and does not inhibit keyboard operation.

FRONT END STATUS BYTE.

The front end status bytes are defined in the L8000 I/O and device control logic. They are listed below, with those unique to the console further defined.

NOTE

Any front end status bit that is set (condition present) will appear as a zero in the AR, whereas device status bits will appear as a one in the AR if the condition is present.

TROUBLE.

This bit will be a one if any of the following conditions occur:

a. Out-of-paper detected.b. Carrier velocity error.c. Invalid keyboard entry flag set.

XFF.

This flip-flop will be set when the ready switch is depressed. It is reset via an IOCTL command to the console port. A minimum of at least two milliseconds should be allowed for contact bounce before resetting XFF. Refer to the L8000 I/O and device control logic for a description of the following bits:

a. Trouble.

- b. Input buffer extend (at least one byte in the input FIFO).

- c. Output buffer empty.

- d. Output buffer almost empty.

- e. Input buffer full.

- f. Input buffer almost full.

CONSOLE FLAGS.

Flags and status bits for the console device control consist of three bytes of device status as defined in the L8000 I/O logic. These status bytes are read when addressing the console device control, address 00000. The first device status byte contains console device control general status bits. The second device status byte contains TCl700 window machine flags. The third device status byte contains processor-oriented flags. The device status bytes are defined below.

If a particular option that is the source of a status bit is not present in a machine, then that bit will always be 0 (except in the DC140, PCF IDLE=1.)

Figs. IIC-97, 98 and 99 list the device status bits.

| BIT | B8                                                  | B7           | B6                                                                                               | B5                                              | B4   | B3   | В2        | B1    |                         |  |  |

|-----|-----------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------|------|------|-----------|-------|-------------------------|--|--|

| AR  |                                                     | ZON          | E                                                                                                |                                                 | NUM  | ERIC |           |       |                         |  |  |

|     | Z8F                                                 | Z4F          | Z2                                                                                               | ZlF                                             | N8F  | N4F  | N2F       | N1F   |                         |  |  |

|     | CVER                                                | OPD          | 0                                                                                                | 0                                               | PCFI | IKE  | LP        | C/SLI | DEVICE STATUS<br>BYTE 1 |  |  |

|     | B1=C/S<br>B2=LP<br>B3=IKE<br>B4=PCF<br>B5=0<br>B6=0 | LEDG<br>INVA | CONSOLE/STRIPED LEDGER<br>LEDGER POSITIONED<br>INVALID KEYBOARD ENTRY<br>PRINTER-CARRIER-FORMS D |                                                 |      |      | RLOCK REQ | UIRED |                         |  |  |

|     | B7=OPD<br>B8=CVE                                    |              |                                                                                                  | OUT-OF-PAPER DETECTED<br>CARRIER VELOCITY ERROR |      |      |           |       |                         |  |  |

FIG. IIC-97 DEVICE STATUS BYTE 1 BIT ASSIGNMENTS

| BIT                                                                                                                                                     | B8 B7 B                                                                                                       |                                            | B6                                   | B5                                                                              | B4                                         | B3             | B2    | B1         |                         |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------|--------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------|----------------|-------|------------|-------------------------|--|--|--|--|

| AR                                                                                                                                                      |                                                                                                               | ZONE                                       |                                      |                                                                                 |                                            | NUME           | RIC   |            |                         |  |  |  |  |

|                                                                                                                                                         | SVOL                                                                                                          | TBL                                        | TAL                                  | 0                                                                               | 0                                          | PBLL           | PSOF  | PBFL       | DEVICE STATUS<br>BYTE 2 |  |  |  |  |

|                                                                                                                                                         | B2=P<br>B3=P<br>B4=N<br>B5=N<br>B6=T<br>B7=T                                                                  | SOF<br>BLL<br>OT USE<br>OT USE<br>AL<br>BL | PA<br>PA<br>D AI<br>D AI<br>TE<br>TE | SSBOOK<br>SSBOOK<br>SSBOOK<br>WAYS Z<br>WAYS Z<br>CLLER A<br>CLLER B<br>IPERVIS | SPAC<br>LAST<br>ERO<br>ERO<br>LOCK<br>LOCK | E OVER<br>LINE | FOLD  |            |                         |  |  |  |  |

|                                                                                                                                                         | B8=SVOL SUPERVISORY OVERRIDE LOCK<br>FIG. IIC-98 DEVICE STATUS BYTE 2 BIT ASSIGNMENTS<br>WINDOW MACHINE FLAGS |                                            |                                      |                                                                                 |                                            |                |       |            |                         |  |  |  |  |

| BIT                                                                                                                                                     | в8                                                                                                            | В7                                         | B6                                   | B5                                                                              | B4                                         | B 3            | В2    | B1         |                         |  |  |  |  |

| AR                                                                                                                                                      |                                                                                                               | ZON                                        | ΝE                                   |                                                                                 |                                            | NUM            | ERIC  |            |                         |  |  |  |  |

|                                                                                                                                                         | LLVF                                                                                                          | r ø                                        | Ø                                    | BTEN                                                                            | 0                                          | MRPE           | NMC   | BTON       | DEVICE STATUS<br>BYTE 3 |  |  |  |  |

| B1=BTONBATTERY ONB2=NMCNO MEMORY CARDB3=MRPEMEMORY READ PARITY ERRORB4=0B5=BTENB5=BTENBATTERY ENABLEDB6=NOT USEDB7=NOT USEDB8=LLVFLOW LINE VOLTAGE FLAG |                                                                                                               |                                            |                                      |                                                                                 |                                            |                |       |            |                         |  |  |  |  |

|                                                                                                                                                         |                                                                                                               | FIG.                                       | IIC <b>-</b> 99                      | DEVI                                                                            | CE SI                                      | ATUS B         | YTE 3 | BIT ASSIGN | MENTS                   |  |  |  |  |

DEVICE STATUS BYTE 1.

CONSOLE/STRIPED LEDGER INTERLOCK REQUIRED (B1 IN AR)

This bit, when set, indicates that certain console operations should not be performed programmatically in order to avoid mechanical interference between SL and console mechanisms. Those console operations that should not be performed when this bit is 1 are:

a. Printing on the ledger.

b. Open or close platen.

c. Advance right platen on a split platen machine or advance left platen on a solid platen machine.

All other console operations may be performed when this bit is 1.

LEDGER POSITIONED (B2 IN AR):

This bit is 1 if and only if the ledger position transducer at the gripper jaws indicates a ledger is present.

INVALID KEYBOARD ENTRY (B3 IN AR):

This flag is a l if a keyboard depression has occurred while the keyboard was inhibited. It can also be set by an IOCTL command from the processor. It can be reset by an IOCTL command from the processor or by initializing the console port.

FIG. IIC-100 defines the IOCTL commands for setting and resetting this flag, as well as other console device IOCTL commands.

PRINTER-CARRIER-FORMS IDLE (B4 IN AR)

This bit is set when the console printer, carrier, and forms are idle and the console output buffer is empty. The console output buffer will appear empty to the TPU microprocessor if the command to inhibit console output buffer is issued prior to any APR operations. This signal is also hard-wired to the MMR.

Note that if the console output buffer is not empty, the PCF IDLE bit will be 0. Therefore, any no-op, PIP, PRTLT, PRTRT, ENUND, or DSUND codes, that are sent to the output buffer will cause the PCF IDLE bit to be 0, until the TPU micro-processor can retrieve and finish processing them.

OUT-OF-PAPER (B7 IN AR)

This bit is a direct function of the out-of-paper detector. If set (1), it indicates the out-of-paper detector is active (no paper). If reset (0), then the out-of-paper detector is not active (paper present). No programmatic set/ reset of this bit is available.

CARRIER VELOCITY ERROR (B8 IN AR)

This bit is set under any of the following conditions:

Carrier overspeed is detected by hardware when the hold solenoid is about to be de-energized.

Carrier underspeed

The printhead cannot be engaged due to a malfunction, when printing is initiated.

The carrier velocity error bit can be reset by initializing the consol port. If the carrier velocity error bit is set, the PCF IDLE bit will be 0, no further printer-carrier-forms operations can occur, except sounding the audible alarm via an IOCTL command to the Universal Front End.

Printed in U.S. America 8-1-75

UP.

| BIT   | в8  | B7        | вб       | в5 | в4                        | В3         | B2 | Bl |               |                               | D<br>C<br>1 |

|-------|-----|-----------|----------|----|---------------------------|------------|----|----|---------------|-------------------------------|-------------|

|       | 8F  | ZON<br>4F |          | ١F |                           | NUME<br>4F |    |    | HE X          |                               | 4<br>0      |

|       | 0   | <b>.</b>  | 0        | 0  | 1                         | 0          | 0  | 1  | 0-9           | RESET XFF (READY SWITCH)      | Y           |

|       | 0   | 0         | 0        | 1  | νη <sub>γιχο</sub> . και. |            | 0  | 1  | <b>1-</b> D   | SET OUTBUFF INHTBIT FF        | N           |

|       | 0   | 0         | 0        | 1  | 0                         | 1          | 0  | م  | 1-5           | RESET OUTBUFF INHIBIT FF      | N           |

|       | 0   | 0         | 1        | 1  | 0                         | 0          | 0  | 1  | 3-1           | IOC31 (AUDIBLE ALARM BYPASS)  | N           |

|       | 0   | 0         | 1        | 1  | 1                         | 1          | 0  | ſ  | 3-D           | SET GEN FF (POWER OFF BYPASS) | Y           |

|       | 0   | 0         | 0        | 1  | 0                         | 0          | 0  | 1  | 1-1           | RESET OUTBUFF CALL FF         | N           |

|       | 0   | 0         | 0        | 1  | 1                         | 0          | 0  | 1  | 1-9           | SET OUTBUFF CALL FF           | N           |

|       | 0   | 0         | 1        | 1  | 1                         | 1          | 0  | 0  | 3-C           | SELECT INDICATOR GROUP "S"    | Y           |

| fer . | 0   | 1         | 0        | 0  | 1                         | 1          | 0  | 0  | 4-C           | SELECT INDICATOR GROUP "A"    | Y           |

|       | 0   | 1         | 0        | 1  | 1                         | 1          | 0  | 0  | 5-C           | SELECT INDICATOR GROUP "B"    | N           |

|       | 0   | 1         | 1        | 0  | 1                         | 1          | 0  | 0  | 6-C           | SELECT INDICATOR GROUP "C"    | N           |

|       | 0   | 1         | <b>l</b> | 1  |                           | ]          | 0  | 0  | 7 <i>-</i> -C | SELECT INDICATOR GROUP "D"    | Y           |

|       | 0   | 0         | 0        | 0  | 0                         | 0          | 1  | 1  | 0-3           | KEYBOARD ENABLE               | Y           |

|       | 0   | 0         | 1        | 0  | 0                         | 0          | 1  | 1  | 2-3           | LOADER ENABLE                 | Y           |

|       | . O | 1         | 0        | 0  | 0                         | 0          |    | T  | 4-3           | SET INVALID KEYBOARD ENTRY FF | N           |

|       | 0   | 1         | 1        | 0  | 0                         | 0          | 1  | 1  | 6-3           | RESET INVALID KYBD ENTRY FF   | N           |

|       | 1   | 0         | 0        | 0  | 0                         | 0          | 1  | 1  | 8-3           | SET BATTERY ENABLE FF         | Y           |

|       | 1   | 0         | 1        | 0  | 0                         | 0          | 1  | 1  | A-3           | SET KEYBOARD INHIBIT          | N           |

(SEVERAL OF THESE COMMANDS ARE DEFINED IN THE UNIVERSAL FRONT END SPECIFICATION, AS ARE ADDITIONAL FRONT END-SENSITIVE CODES.)

FIG. IIC-100 L8000 CONSOLE DEVICE CONTROL IOCTL COMMANDS

DEVICE STATUS BYTE 2.

This byte is the second device status byte and is made available after reading the first device status byte. It consists of the window machine flags for the TCl700. If the window machine option is not installed, all bits will be zero. The bit designations are listed below:

- a. Passbook first line (Bl in AR).

- b. Passbook space over fold (B2 in AR).

- c. Passbook last line (B3 in AR).

- d. Teller A lock (B6 in AR).

- e. Teller B lock (B7 in AR).

- f. Supervisory override lock (B8 in AR).

DEVICE STATUS BYTE 3.

This status byte is reserved for processor-oriented flags. It is made available after reading device status byte 2.

In the standby power or battery mode the console will have all power removed except for the device status byte 3 flags. To make status byte 3 available in the battery mode, the processor must set IOAR to 0 and do three read microinstructions, disregarding the data loaded into the AR as a result of these three read's. The next slow read command (must be a slow read, 1-0, because TR will be high - fast read will not load AR) will load device status byte 3 into the AR. Neither the "No Memory Card" nor "Parity Error" flag will be reset by reading device status byte 3 when in the battery mode. If set, these two flags will remain set (battery mode only).

BATTERY ON FLAG (B1 IN AR).

This flag is reset by hardware when power is turned on from a full power off condition. The flag will be set if an under-voltage condition occurs such that it may be necessary to perform a memory dump operation.

Firmware can cause the machine to go to either full power off or standby power when this flag is set. If memory dump is not addressed (DSAF=O) a modified IOCTL instruction, 971F, will cause a transfer to the standby power mode. The same modified IOCTL instruction will cause a full power off condition if memory dump is addressed.

NO MEMORY CARD FLAG (B2 IN AR).

(Normal operation: Memory dump is not addressed: DSAF=0.)

This flag is reset by hardware when power is turned on from a full power off condition. It is set if an attempt is made to access (read or write) an area of memory for which there is no printed circuit board present. When "No Memory Card" is detected, the machine is initialized to FFFF. "No Memory Card" flag is reset when the processor does a read of device status byte 3. (INTIO will not reset this flag.)

Refer to "L8000 Firmware Control of Data Save Hardware" for no memory card errors when data save is addressed.

MEMORY READ PARITY ERROR FLAG (B3 IN AR).

The memory control circuits generate odd parity when data is written into the R/W memory. The parity bit is a ninth bit associated with each 8-bit memory location and is not accessible to the processor logic. The memory control circuits check parity when a R/W memory location is read. If a memory parity error occurs, the "Memory Read Parity Error" flag will be set.

There are two conditions that will cause the memory parity error flag to be set. They are:

- a. A parity error is detected when a valid R/W memory location is read and a ligitimate parity error occurs.

- b. A parity error is detected when reading a R/W memory location that is physically not present, although the printed circuit board that contains a position for that location is present. (e.g., on a 2048-byte R/W PCB, only 1024 bytes are assembled and an attempt is made to read a location in the missing 1024 bytes.)

The "Memory Read Parity Error" flag will be reset when power is turned on from a full power off condition. It will also be reset when the processor does a read of device status byte 3. (INTIO will not reset this flag.)

The Memory Read Parity Error flag can be interrogated by firmware when data save is not addressed, by a 3F (SKIP) instruction, as follows:

(DSAF=0)

•

PARITY ERROR FLAG=1

3-F TXRC D-N BRU P-Q PARITY ERROR FLAG=0 Z-N

If the parity error flag is set, it can only be reset by firmware by reading device status byte 3. The skip micro does not reset it.

If memory dump is addressed (DSAF=1), the 3F skip microinstruction will test the no memory card flag.

BATTERY ENABLE FLAG (B5 in AR).

This flag is reset by hardware when power is turned on from a full power off condition. It can only be set by programmatically issuing the appropriate IOCTL command to the console port 0. It should be set by the processor following a successful memory load, after which any DC undervoltage condition will cause hardware to switch in the battery. If "Battery Enable" is not set, a DC undervoltage condition will cause the machine to go to a full power off state. Fig. IIC-100 defines the IOCTL to set this flag.

LOW LINE VOLTAGE FLAG (B8 IN AR).

This flag is sampled by firmware when the power control circuits detect a D.C. undervoltage condition and initialize the machine. As a result of sampling the flag, firmware decides if a memory dump operation is required, or if the machine should go to the standby power mode.

CHARACTER GENERATOR ROMS.

There is provision made in the L9000 character generator hardware to accomodate two character generator ROM's: One that is addressed by print codes in ASCII columns 2 through 7, and another one that is addressed by print codes in ASCII columns 10 through 15.

There is another hardware configuration available wherein bit 8 of the print codes will be ignored, so that codes in ASCII columns 10 through 15 will be mapped into those in columns 2 through 7, thereby controlling printing from only one character generator ROM.

There is no hardware provision, however, to map ASCII columns 6 or 7 codes onto columns 4 or 5. These codes will directly address the character generator, and whatever is defined in the character generator ROM at that location will be printed. Note that this implies that, if such mapping is desired, a printer code translation table must be employed by firmware.

CONSOLE MTR FUNCTIONS.

Console MTR functions for the L9000 are identical to those defined for the L8/TC.

### L9000 LOGIC CIRCUITS

The following describes the basic logic elements as well as the packaging used for each logic element. The basic logic element is the NAND gate. There are also a number of unique logic elements used to control specific PCF functions. These include Flip-flops, DMV's, binary counter and shift register devices as well as some unique LSIC and ROM chips. The individual devices are explained in detail here to provide a better understanding of how each device operates.

### L9000 LOGIC LEVELS

The L9000 PCF logic deals primarily with two state devices. The two physical states on each signal line can be referred to as the high state and low state. Generally, the high state will be the active state and the low state will be the inactive state. There are exceptions when the low state will be the active state.

The L9000 PCF logic uses both positive logic and Negative MOS logic. The TPU LSIC and the two Micro Program ROMs use Negative MOS logic levels. It is only necessary to think of these outputs as active low. Reference to input or output signals for the negative active devices will be referred to as big or low which indicates that the voltage level is either high or low.

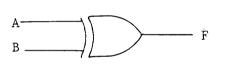

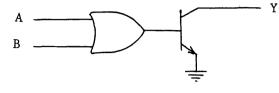

#### NAND GATE

The symbol shown in Fig. IIC-101 represents one version of the NAND function. From the accompanying truth table it can be seen that any low input clamps the output high. The output goes low, its active condition, only when all inputs are high.

|   | INPU | JT           | OUTPUT |

|---|------|--------------|--------|

| A | В    | С            | F      |

| L | L    | L            | Н      |

| L | L    | Н            | Н      |

| L | Н    | L            | Н      |

| L | Н    | Н            | Н      |

| н | L    | $\mathbf{L}$ | Н      |

| Н | L    | Н            | Н      |

| Н | Н    | L            | Н      |

| H | Н    | Н            | L      |

FIG. IIC-101 NAND GATE

### 2 INPUT EXCLUSIVE OR

The symbol shown in Fig.IIC-102 represents the EXCLUSIVE OR function. As seen in the accompanying truth table the output is high, active condition, only when the two inputs are dissimilar. If both inputs are high or low at the same time, the output of the EXCLUSIVE OR will be low.

INPUT А В F = |A(H)| and B(L) or B(H)| and A(L)|L L L L Н Н Н L Н Н Н L

# FIG. IIC-102 EXCLUSIVE OR

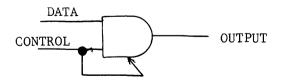

### TRI-STATE BUFFER

Fig. IIC-103 indicates the symbol for a TRI-STATE BUFFER. As shown in the truth table, three states

| DATA | CONTROL | OUTPUT         |

|------|---------|----------------|

| H    | Н       | Н              |

| L    | Н       | L              |

| L    | L       | HIGH IMPEDANCE |

| Н    | L       | HIGH IMPEDANCE |

FIG. IIC-103 TRI-STATE BUFFER

are possible. The state of the data input, either high or low, will be reflected on the output whenever the control input is high. With the control input low, and, irrespective of the state of the data input, the output line will appear as a high impedance to the next input device. This high impedance is in the megohms and is effectively an open to subsequent logic.

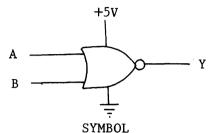

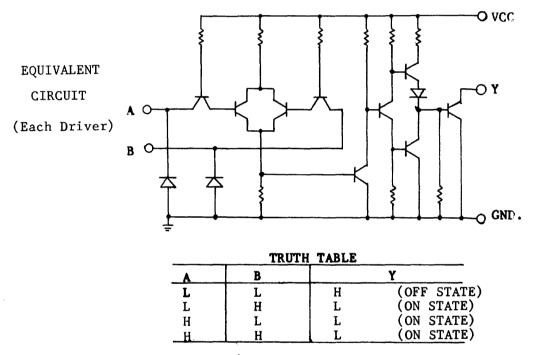

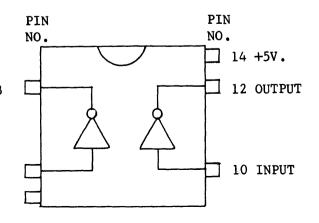

# POSITIVE NOR PERIPHERAL DRIVER

FIG.IIC-104 indicates the symbol for a POSITIVE NOR PERIPHERAL DRIVER. It is a NOR gate with a driver transistor attached. The Emitter is grounded and the collector is open receiving collector voltage from the load to which it is attached. The POSITIVE NOR PERIPHERAL DRIVER provides fast and positive switching.

EQUIVALENT CIRCUIT

H= HIGH LEVEL LOW = LOW LEVEL

FIG. IIC-104 DUAL POSITIVE-NOR PERIPHERAL DRIVER

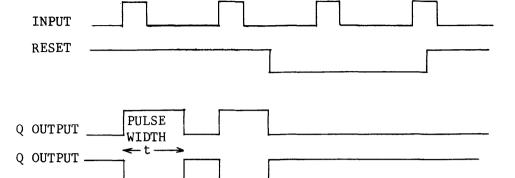

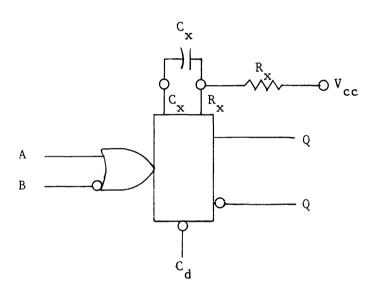

# DUAL RETRIGGERABLE RESETTABLE MONOSTABLE MULTIVIBRATOR

The multivibrator shown in Fig.IIC-105 provides an output pulse whose duration and accuracy is a function of the externally mounted timing components (capacitor Cx and resistor Rx).

Reset Operation - An overriding active LOW level is provided on each oneshot. By applying a LOW to the reset, any timing cycle can be terminated or any new cycle inhibited until the LOW reset input is removed. Trigger inputs will not produce spikes in the output when the reset is held LOW.

| PIN N | o's  |    | OPERATION |  |  |  |

|-------|------|----|-----------|--|--|--|

| В     | A    | Cd | OTENATION |  |  |  |

| H→ L  | L    | Н  | TRIGGER   |  |  |  |

| Н     | L→ H | Н  | TRIGGER   |  |  |  |

| x     | x    | L  | RESET     |  |  |  |

$H \longrightarrow L = HIGH TO LOW VOLTAGE LEVEL TRANSITION.$

$L \rightarrow H = LOW$  TO HIGH VOLTAGE LEVEL TRANSITION.

H = HIGH VOLTAGE LEVEL

L = LOW VOLTAGE LEVEL

(1/2 OF DIVICE SHOWN)

X = DO NOT CARE

FIG. IIC-105 LOGIC DIAGRAM AND TRIGGERING TRUTH TABLE

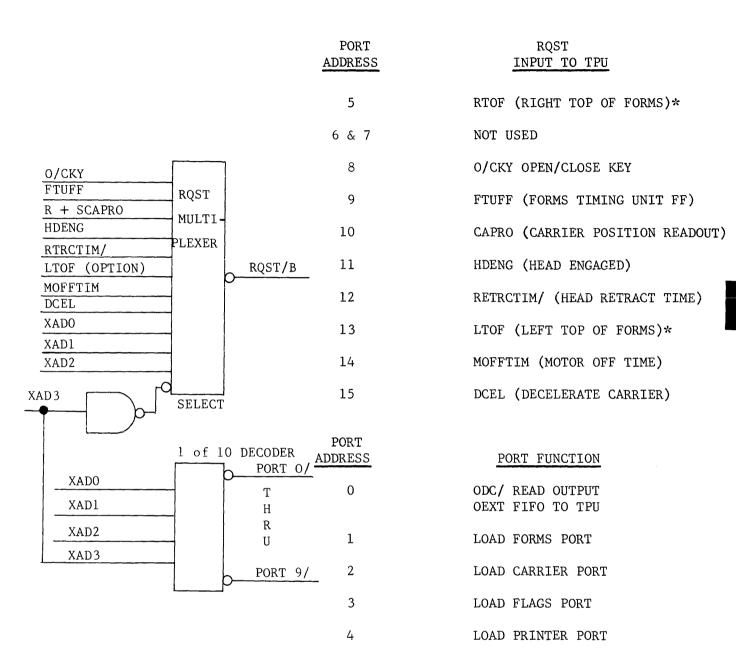

ONE OF TEN DECODER

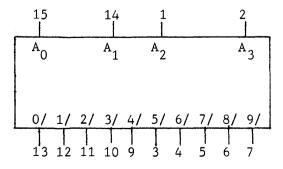

The ONE OF TEN DECODER IC is shown in Fig. IIC-106. The device accepts four inputs  $(A_0 - A_3)$  and provides ten mutually exclusive outputs. This device is used to generate the port addresses by decoding the 4 input addresses (XADO - XAD3). The active output of the decoder is a low logic level as shown in the truth table.

|     | A <sub>0</sub> | A <sub>1</sub> | А <sub>2</sub> | А <sub>3</sub> | 0/ | 1/ | 2/ | 3/  | 4/                                                           | 5/  | 6/   | 7/  | 8/  | 9/ |

|-----|----------------|----------------|----------------|----------------|----|----|----|-----|--------------------------------------------------------------|-----|------|-----|-----|----|

| 0   | L              | L              | L              | L              | L  | н  | Н  | Н   | н                                                            | Н   | Н    | Н   | Н   | Н  |

| 1   | н              | L              | L              | L              | Ĥ  | L  | H  | Н   | Н                                                            | H   | H    | H   | Н   | Н  |

| 2   | L              | Н              | L              | L              | Н  | H  | L  | H   | Н                                                            | H   | H    | Н   | H   | Н  |

| 3   | н              | H              | L              | L              | Н  | Н  | Н  | L   | Н                                                            | H   | H    | H   | Н   | Н  |

| 4   | L              | L              | H              | L              | Н  | Н  | Н  | Н   | L                                                            | Н   | H    | Η   | Н   | Н  |

| 5   | н              | L              | H              | L              | Н  | H  | H  | H   | н                                                            | L   | H    | Н   | H   | Н  |

| 6   | L              | Н              | H              | L              | Н  | H  | H  | H   | Н                                                            | H   | L    | H   | H   | H  |

| 7   | н              | Н              | Н              | L              | н  | Н  | Н  | Н   | Ĥ                                                            | Н   | Н    | L   | Н   | Н  |

| 8   | L              | L              | L              | Н              | Н  | Н  | H  | Н   | Н                                                            | Н   | Н    | Η   | L   | Н  |

| 9   | н              | L              | L              | Ĥ              | Н  | Н  | Н  | Н   | Н                                                            | H   | Н    | Н   | Н   | L  |

| 10  | L              | Н              | L              | Н              | Н  | H  | Н  | Н   | Н                                                            | Н   | Н    | Н   | Н   | Н  |

| 11  | н              | Н              | L              | Н              | Н  | H  | Н  | Н   | Н                                                            | Н   | Н    | H   | H   | Н  |

| 12  | L              | L              | Н              | H              | Н  | Н  | H  | Н   | Н                                                            | Н   | H    | Η   | H   | Н  |

| 13  | н              | L              | H              | H              | Н  | H  | H  | H   | Н                                                            | Η   | H    | Н   | Н   | Н  |

| 14  | L              | Н              | Н              | Н              | Н  | Н  | Н  | Η   | Н                                                            | Н   | Н    | Н   | Н   | Н  |

| 15  | н              | Н              | Н              | Н              | Н  | Н  | H  | Н   | Н                                                            | Н   | Н    | Н   | Н   | Н  |

| 1 A | ddre           | ss             | Inp            | ut A           | 2  |    |    | 9 ( | Outj                                                         | put | 4/   |     |     |    |

|     | ddre           |                |                |                |    |    | 10 | ) ( | Out                                                          | put | 3/   |     |     |    |

|     | utpu           |                |                |                | 5  |    | 1: | 1 ( | Out                                                          | put | 2/   |     |     |    |

| 4 0 | utpu           | t 6            | /              |                |    |    | 1  | 2 ( | Out                                                          | put | 1/   |     |     |    |

| 50  | utpu           | t 7            | /              |                |    |    | 1  | 3 ( | Out                                                          | put | 0/   |     |     |    |

| 60  | utpu           | t 8            | /              |                |    |    | 14 | 4   | A <sub>,</sub> dd:                                           | res | s Iı | npu | t A | 1  |

| 70  | utpu           | t 9            | /              |                |    |    | 1. |     | Address Input A <sub>1</sub><br>Address Input A <sub>0</sub> |     |      |     |     |    |

| 8 G | roun           | d              |                |                |    |    |    |     |                                                              |     |      |     |     | -  |

|     |                |                |                |                |    |    |    |     |                                                              |     |      |     |     |    |

FIG. IIC-106 ONE OF TEN DECODER

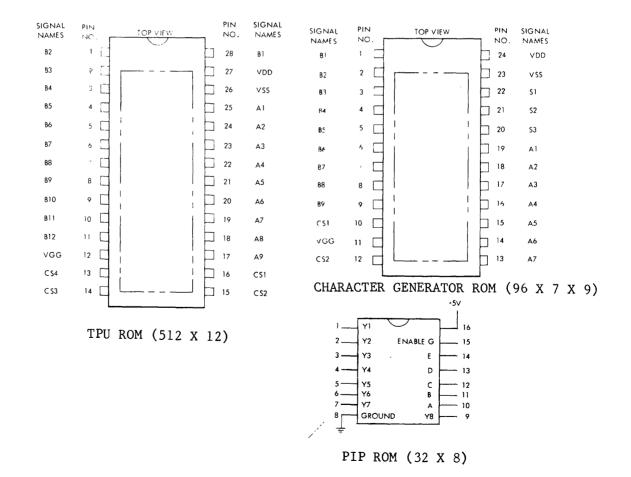

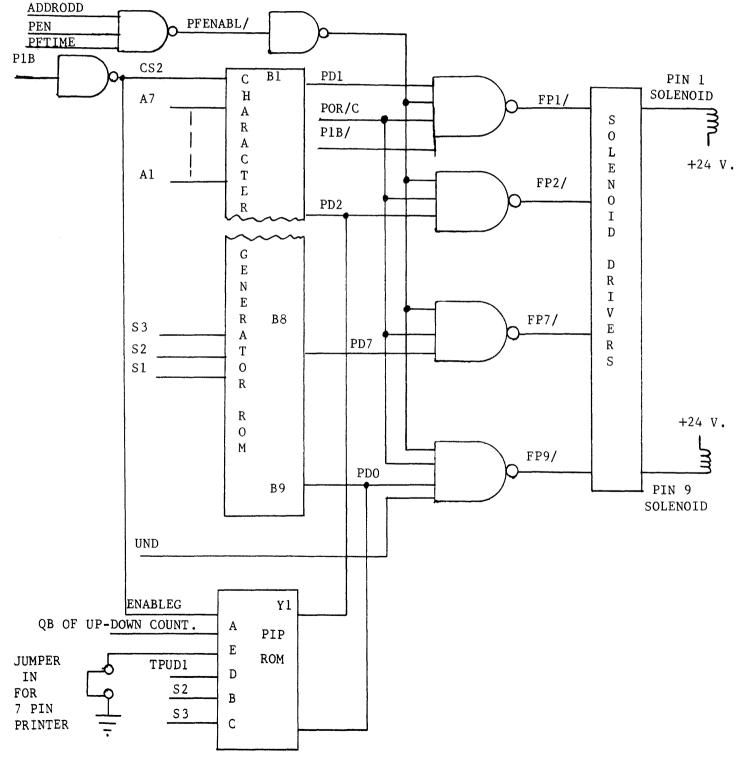

ROM CHIPS

There are three different type MOS ROMs used in the L9000 TPU Micro processor logic. These are the two TPU Micro Program ROMs, the Character Generator ROMs and the PIP ROM. The chip configuration for these three ROMs is shown in Fig. IIC-107.

The ROM chips as well as the TPU LSIC inputs and outputs are all Negative MOS Logic Levels. With Negative MOS Logic Levels a 0 is a more positive voltage (+5 volts) and a 1 is a more negative voltage (0 volts).

The TPU Micro Program ROMs consist of 512 characters of 12 bit wide data (B1-B12) and is referred to as a 512 X 12 ROM. The active state of the ROM inputs and outputs is 0 volts and is said to be low active.

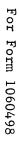

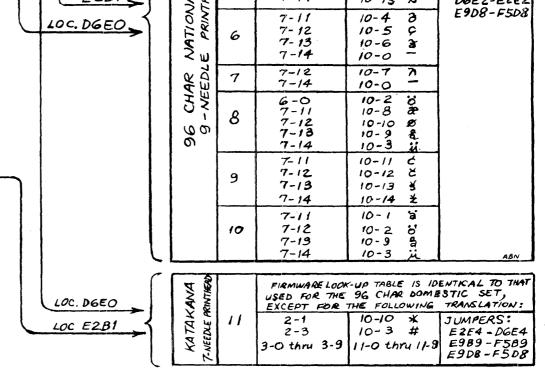

The Character Generator ROMs are 96 X 7 X 9 which means that there are a total of 96 9 bit characters (B1-B9 outputs) which are counted out in serial fashion by counting the S1-S2 scanning line inputs from 1 to 7 for each 8 bit address into the chip (A1-A7).

The PIP ROM is a 32 X 8 ROM. It contains 32 characters of 8 bit data selected by the 8 address line inputs enabled by the ENABLE signal.

FIG. IIC-107

L9000 ROMS

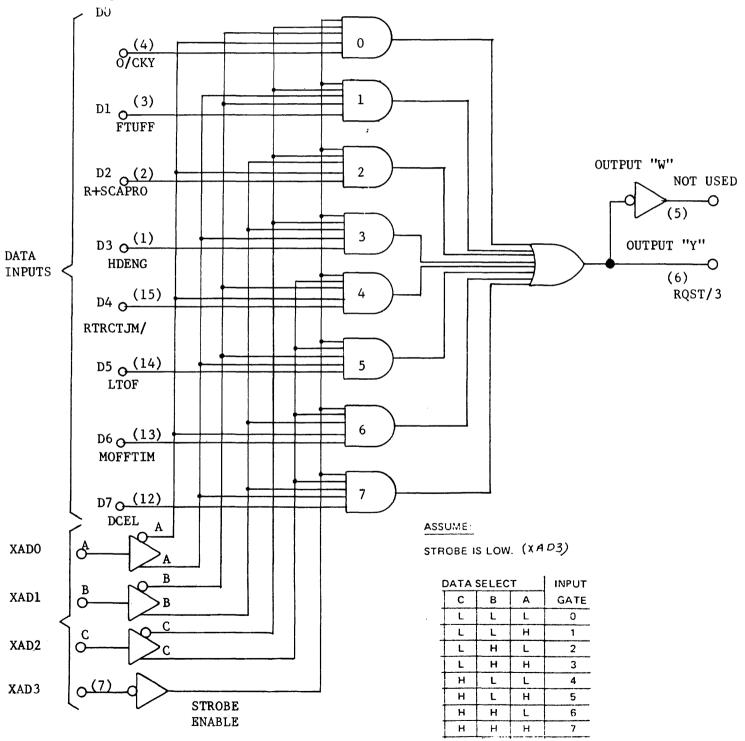

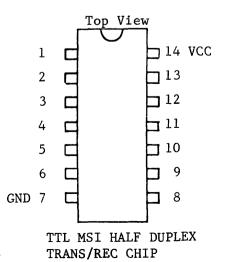

### DATA SELECTOR MULTIPLEXER

The Data Selector Multiplexer shown in Fig.IIC-108 is used to reflect the status of various PCF functions to the TPU Microprocessor as defined by the data input signals. As seen in the accompanying truth table the data select inputs A, B, and C will determine which input gate 0-7 will be selected. The A, B, and C data select inputs are the TPU Microprocessor address lines XAD0-XAD3 respectively. XAD3/ is the strobe enable signal and must be low to enable data selection. The output of the chip RQST/-B will be set to the same condition as the data input to the selected input gate.

FIG. IIC-108 DATA SELECTOR MULTIPLEXER

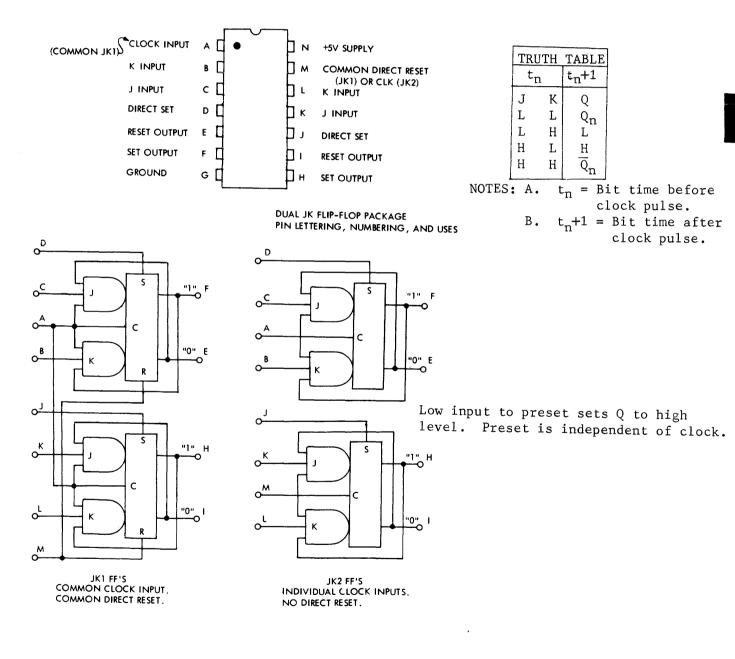

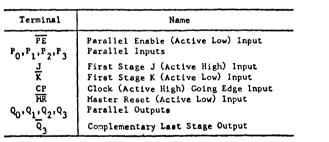

## JK FLIP-FLOPS

There are two types of JK Flip-flops used in the L9000. They are designated JKl or JK2. Fig.IIC-109 shows the layout of the two types. The JKl chip has two flip-flops sharing a common clock input and a common direct reset input. The JK2 chip has a seperate clock input for both flip-flops but no direct reset for either.

Both the JKl and JK2 flip-flops function as shown in the accompanying truth table.

Fig. IIC-109 J-K FLIP-FLOPS

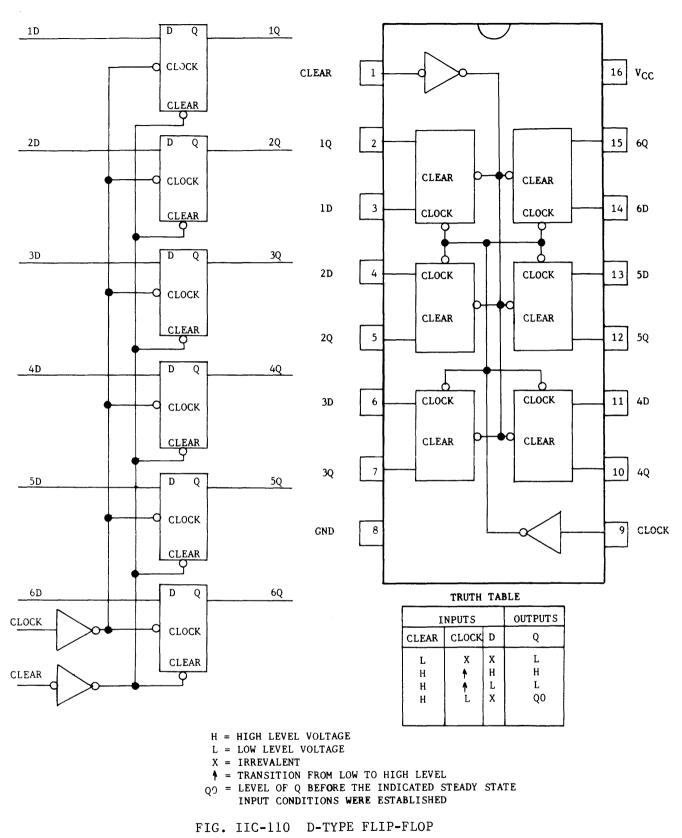

D-TYPE FLIP FLOP

The D-Type Flip flop shown in Fig.IIC-110 consists of six flip flops with a common clock input and a common clear line. Input data is transferred from the D inputs to the Q outputs on the positive-going edge of the clock pulse.

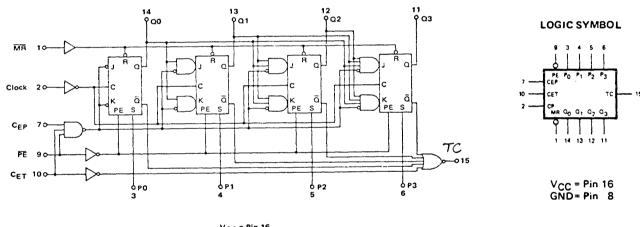

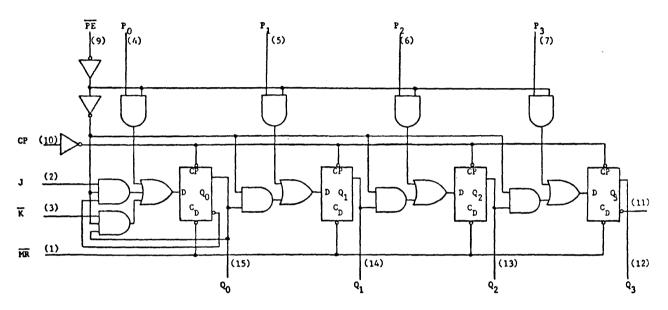

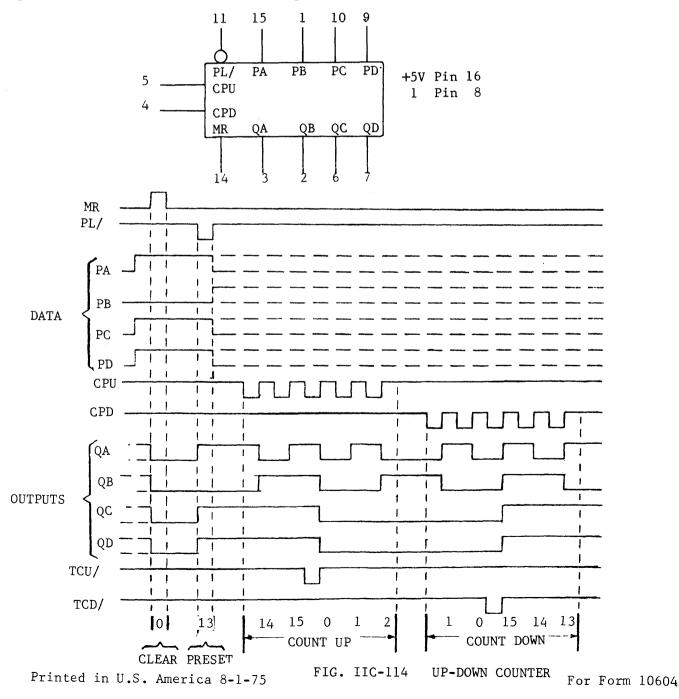

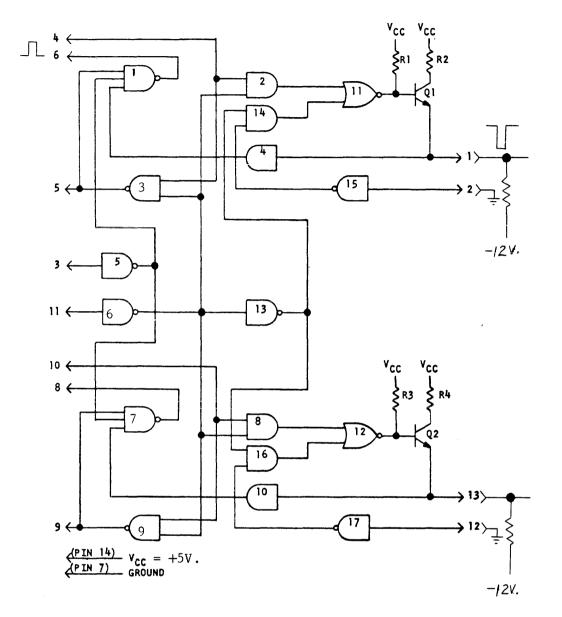

## FOUR BIT BINARY COUNTER

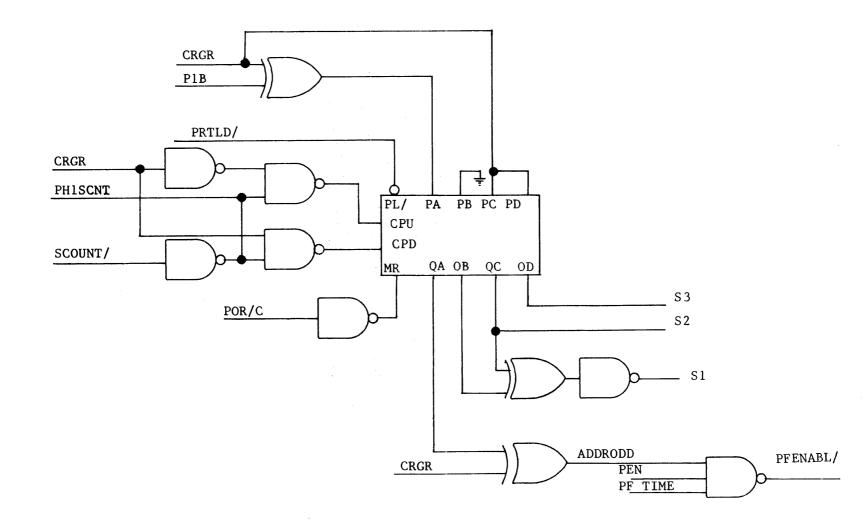

The four Bit Binary Counter is shown in Fig.IIC-111 and has two modes of operation in the L9000. The counter may be operated as a straight binary counter counting from 0 to a maximum count of 15 (TC output). The counter may also be preset via its PE/ line to a specific count which appears on the PO-P3 lines.

In most instances in the L9000 this counter will first be preset to a specific count, then counted up to a desired count. Several Counters may be cascaded to achieve counts greater than 15 where required. This is done by hooking the TC output of one stage to the CET input of the next stage to clock the second stage once for every 15 counts in the first stage.

Referring to Fig.IIC-111 when the MR/ line goes low all four Flip-flops will be reset. To allow operation of the counter, MR/ must be high. Each Flip-flop has a binary weight as shown in the schematic respresentation.

When PE/ goes low, the Flip-flops will be preset to a count between 0-15 by the condition on the PO-P3 inputs. In the count up mode, counting will begin from 0 or the preset value. The first counter Flip-flop is enabled and compliments on each clock pulse. As each Flip-flop sets, the next one is enabled to set as shown in the timing diagram.

V<sub>CC</sub> = Pin 16 GND = Pin 8

> CONNECTION DIAGRAMS DIP (TOP VIEW)

|     | MOL     | DE SELECT | FION             |                      |                                                       |                               |

|-----|---------|-----------|------------------|----------------------|-------------------------------------------------------|-------------------------------|

| PE  | CEP     | CET       | MODE             | PIN NAMES            |                                                       |                               |

| L   | L       | L         | Preset           | PE<br>P0, P1, P2, P3 | Parallel Enable (Active LOW) Input<br>Parallel Inputs |                               |

| L   | н       | H<br>L    | Preset<br>Preset | CEP                  | Count Enable Parallel Input                           | 3 0 0 0 14                    |

| L   | н       | н         | Preset           | CET                  | Count Enable Trickle Input                            | 4 0 P1 01 13                  |

| н   | L       | L         | No Change        | CP                   | Clock (Active HIGH Going Edge) Input                  | 5 P2 02 12                    |

| н   | L       | н         | No Change        | MR-                  | Master Reset (Active LOW) Input                       |                               |

| н   | н       | L         | No Change        | $Q_0, Q_1, Q_2, Q_3$ | Parallel Outputs                                      | • <b>[</b> ]•3 •3 <b>[</b> ]" |

| н   | н       | н         | Count            | TC                   | Terminal Count Outputs                                |                               |

| (MR | = HIGH) |           |                  |                      |                                                       |                               |

FIG. IIC-111 FOUR BIT BINARY COUNTER

### FOUR BIT SHIFT REGISTER