Burroughs believes that the information described in this manual is accurate and reliable, and much care has been taken in its preparation. However, no responsibility, financial or otherwise, is accepted for any consequences arising out of the use of this material. The information contained herein is subject to change. Revisions may be issued to advise of such changes and/or additions.

Correspondence regarding this document should be addressed directly to Burroughs Corporation, P.O. Box 4040, El Monte, California 91734, Attn: Publications Department, TIO-West.

# LIST OF EFFECTIVE PAGES

| Page          |   |   |   |   |   |   |   |   |   |   | Issue    | Page          |   |  |  |  |  |  | Issue    |

|---------------|---|---|---|---|---|---|---|---|---|---|----------|---------------|---|--|--|--|--|--|----------|

| Title         |   |   |   |   |   |   |   |   |   |   | Original | 3-1 thru 3-37 |   |  |  |  |  |  | Original |

| ii            |   |   |   |   |   |   |   |   |   |   | Original | 3-38          |   |  |  |  |  |  | Blank    |

| iii           |   |   |   |   |   |   |   |   |   |   | Original | 4-1 thru 4-7  |   |  |  |  |  |  | Original |

| iv            |   |   |   |   |   |   |   |   |   |   | Blank    | 4-8           |   |  |  |  |  |  | Blank    |

| vthruvii.     |   |   |   |   |   |   |   |   |   |   | Original | 5-1 thru 5-3  | • |  |  |  |  |  | Original |

| viii          |   |   |   |   |   |   |   |   |   |   | Blank    | 5-4           |   |  |  |  |  |  | Blank    |

| 1-1 thru 1-11 |   |   |   |   |   |   |   |   |   |   | Original | A-1 thru A-7  |   |  |  |  |  |  | Original |

| 1-12          |   |   |   |   |   |   |   |   |   |   | Blank    | A-8           |   |  |  |  |  |  | Blank    |

| 2-1 thru 2-6  | • | • | • | • | • | • | • | • | • | • | Original |               |   |  |  |  |  |  |          |

# TABLE OF CONTENTS

| Section | Title                                                | Page         | Section | Title                                                     | Page       |

|---------|------------------------------------------------------|--------------|---------|-----------------------------------------------------------|------------|

|         | PREFACE                                              | vii          |         |                                                           | 2.4        |

| 1       | FUNCTION AND OPERATION                               | 1-1          |         | Domestic Installations                                    | 2-4<br>2-4 |

| 1       | INTRODUCTION                                         | 1-1          |         | System Checkout                                           |            |

|         | GENERAL DESCRIPTION                                  | 1-1          | 3       | DOCUMENTATION AND                                         | 3-1        |

|         | DPEC OPERATION CODES                                 | 1-6          |         | COMPONENTS                                                |            |

|         | INSTRUCTION FORMAT                                   | 1-9          |         | INFORMATION                                               | 3-1        |

|         | RESULT DESCRIPTOR                                    | 1-9          |         | RELATED DOCUMENTS                                         | 3-1<br>3-1 |

|         | INFORMATION                                          |              |         | PRINTED CIRCUIT CARDS<br>Card Backplane Pin And Connector | 3-1        |

|         | Extended Result Descriptor Feature                   | 1-9          |         | Pad Identification                                        | 5-1        |

|         | PHYSICAL REQUIREMENTS                                | 1-10         |         | Cable Connector Cards                                     | 3-2        |

|         | Construction                                         | 1-10         |         | Q, R, S, and P Cards                                      | 3-2        |

|         | Control Panel                                        | 1-10         |         | F Card                                                    | 3-2        |

|         | Dimensions                                           | 1-10         |         | DPEC MODE DEFINITIONS                                     | 3-2        |

|         | FUNCTIONAL REQUIREMENTS                              | 1-11<br>1-11 |         | DPEC FLOW CHART DESCRIPTION                               | 3-3        |

|         | Compatibility<br>Chained I/O (DPC) Conditional Seeks | 1-11         | 4       | MAINTENANCE                                               | 4-1        |

|         | Error Detection                                      | 1-11         | 4       | INTRODUCTION                                              | 4-1        |

|         | Operational Procedure                                | 1-11         |         |                                                           |            |

|         | •                                                    |              |         | USE OF MAINTENANCE CONTROL                                | 4-1        |

| 2       | INSTALLATION                                         | 2-1          |         | PANEL                                                     |            |

|         | INTRODUCTION                                         | 2-1          |         | Switch Functions (Local Mode Only)                        | 4-1        |

|         | PRE-INSTALLATION                                     | 2-1          |         | Indicator Functions                                       | 4-3        |

|         | REQUIREMENTS                                         | <b>a</b> 1   |         | Maintenance Memory Loading                                | 4-3<br>4-3 |

|         | Physical Site Requirements                           | 2-1<br>2-1   |         | Memory Address Counter Indicators                         | 4-3        |

|         | Maintenance Clearances<br>Floor Loading              | 2-1<br>2-1   |         | P CARD PLUG-ON INDICATOR<br>TROUBLESHOOTING AIDS          | 4-4        |

|         | I/O Cable Information (B 1700 to                     | 2-1          |         | Local Maintenance Aids                                    | 4-4        |

|         | DPEC)                                                | 2-1          |         | Block Diagrams                                            | 4-4        |

|         | Drive Cable Information (DPEC to                     | 2-1          |         | Flow Charts                                               | 4-5        |

|         | 206)                                                 |              |         | B 1700 Disk Pack Subsystem Test                           | 4-5        |

|         | Power Requirements                                   | 2-1          |         | Routine                                                   |            |

|         | Circuit Breaker Information                          | 2-1          |         | Extended Result Descriptor                                | 4-5        |

|         | Equipment Grounding                                  | 2-1          |         | Local                                                     | 4-5        |

|         | Drive Power Sequencing                               | 2-3          |         | Remote                                                    | 4-5        |

|         | Environment                                          | 2-3          |         | Using the E Log                                           | 4-5        |

|         | Operating Environment                                | 2-3          |         | LOGIC LEVELS                                              | 4-6        |

|         | Shipment and Storage Environment                     | 2-3          |         | True                                                      | 4-6        |

|         | Unpacking Instructions                               | 2-3          |         | False                                                     | 4-6        |

|         | INSTALLATION PROCEDURE                               | 2-3          | 5       | SUBASSEMBLY MAINTENANCE                                   | 5-1        |

|         | Panel Removal                                        | 2-3          | 5       | ADJUSTMENTS                                               |            |

|         | AC Input Power                                       | 2-3          |         | INTRODUCTION                                              | 5-1        |

|         | Cables                                               | 2-3<br>2-3   |         | 10 MEGAHERTZ CLOCK                                        | 5-1        |

|         | DC Common Cable                                      | 2-3<br>2-3   |         | ADJUSTMENT                                                |            |

|         | AC Ground Cable<br>Signal Cable                      | 2-3          |         | POWER SUPPLY ADJUSTMENTS                                  | 5-1        |

|         | I/O Cable                                            | 2-3          |         | Overload Protection                                       | 5-1        |

|         | Drive Installation                                   | 2-4          |         | Overvoltage Protection                                    | 5-1        |

|         | SPECIAL INSTALLATION                                 | 2-4          |         | +5.0 Volts Supply                                         | 5-1        |

|         | INSTRUCTIONS                                         | 4 T          |         | High/Low Input Voltage Adjustment                         | 5-1        |

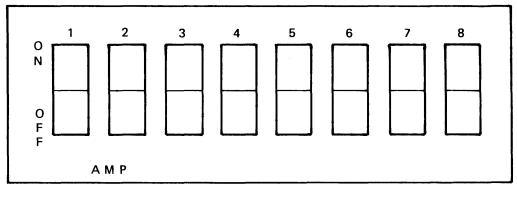

|         | Normal Three Phase Operation                         | 2-4          |         | DRIVE PRESENT AND FORMAT                                  | 5-1        |

|         | Single Phase Operation                               | 2-4          |         | OPTION ADJUSTMENTS                                        |            |

|         | International Installations                          | 2-4          | А       | GLOSSARY OF TERMS                                         | A-1        |

v

# LIST OF ILLUSTRATIONS

| Figure | Title                                  | Page | Figure | Title P                                          | age   |

|--------|----------------------------------------|------|--------|--------------------------------------------------|-------|

| 1-1    | 206 Disk Pack Electronic Controller    | 1-2  | 3-2    | Card Backplane Pin Locating Scheme               | 3-3   |

| 1-2    | Internal Front View of 206 DPEC        | 1-3  | 3-3    | Cable Connector Type Card                        | 3-4   |

| 1-3    | Internal Rear View of 206 DPEC         | 1-4  | 3-4    | Detailed DPEC Flow Chart                         | 3-6   |

| 1-4    | Interface Lines, DPEC to DPC ground.   | 1-5  | 3-5    | Read and Write and Verify Operation              | 3-20  |

| 1-5    | 206 Track Format                       | 1-8  | 3-6    | Initialize Operation                             | 3-33  |

| 2-1    | Cabling Diagram                        | 2-2  | 4-1    | Maintenance Control Panel                        | 4-2   |

| 2-2    | DPEC Power Supply Schematic            | 2-5  | 4-2    | P-Card Plug-on Indicator                         | 4-4   |

| 2-3    | Single Phase Input Power Connection    | 2-6  | 4-3    | Example of an E Log                              | 4-7   |

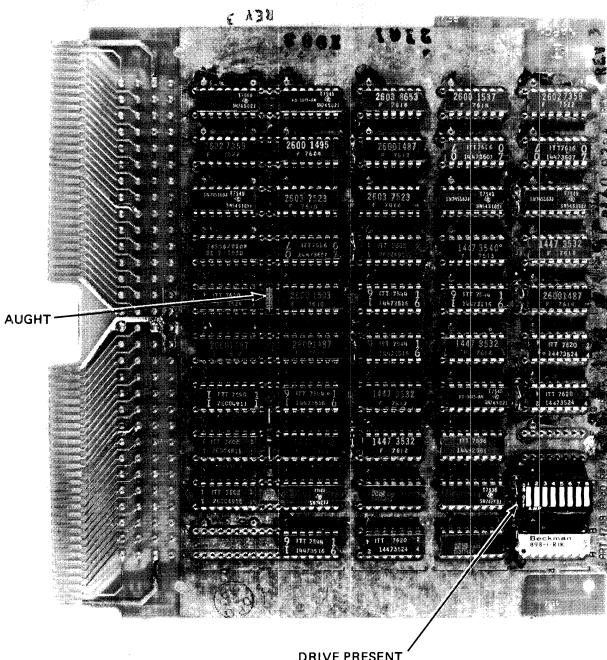

| 3-1    | Integrated Circuit Leg to Card         | 3-1  | 5-1    | H-Card                                           | 5-1   |

|        | Backplane Correlation (Backplane View) |      | 5-2    | Drive Present Integrated Circuit Switch Assembly | y 5-3 |

# LIST OF TABLES

| Table | Title                               | Page | Table | Title                          | Page |

|-------|-------------------------------------|------|-------|--------------------------------|------|

| 1-1   | Edge Connector Wiring               | 1-1  | 3-1   | Mode Functions                 | 3-2  |

| 1-2   | DPEC 206 Operation Codes            | 1-7  | 3-2   | Main Mode Jump Conditions      | 3-36 |

| 1-3   | DPEC 206 Instruction Format         | 1-9  | 4-1   | Maintenance Memory Loading     | 4-3  |

| 1-4   | Result Descriptor Information Lines | 1-9  |       | Descriptions                   |      |

| 1-5   | 206 Extended Result Descriptor      | 1-10 | 4-2   | 206 Extended Result Descriptor | 4-5  |

|       | Information in a Local Mode         |      |       | (Remote)                       |      |

# PREFACE

The 206 Disk Pack Electronic Controller (206 DPEC) technical manual provides installation, operation, and maintenance information to the field engineer. In addition, three standard appendices are included:

- a. Appendix A. Glossary of Terms.

- b. Appendix B. LINs.

- c. Appendix C. RINs.

# SECTION 1 FUNCTION AND OPERATION

# INTRODUCTION

This section contains a general description of the B 9499-3 Disk Pack Electronic Controller (206 DPEC). It includes explanations of the operation codes, result descriptor information, and miscellaneous functional requirements.

# **GENERAL DESCRIPTION**

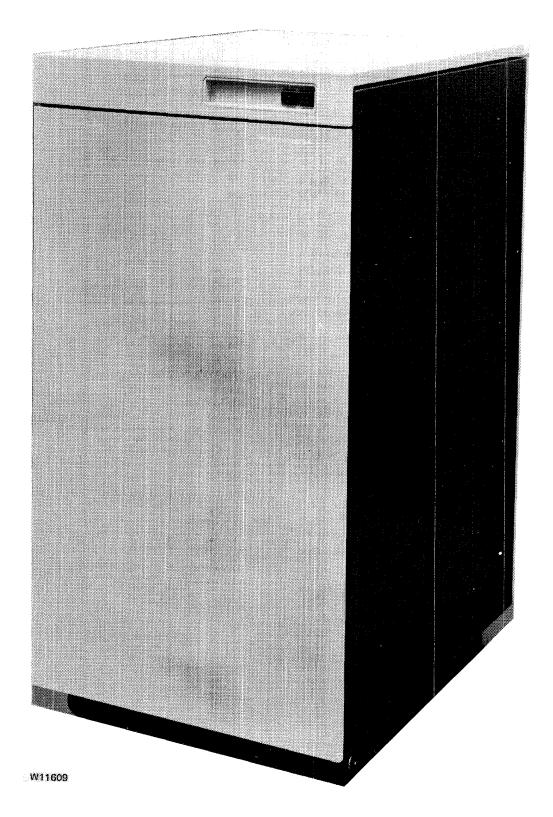

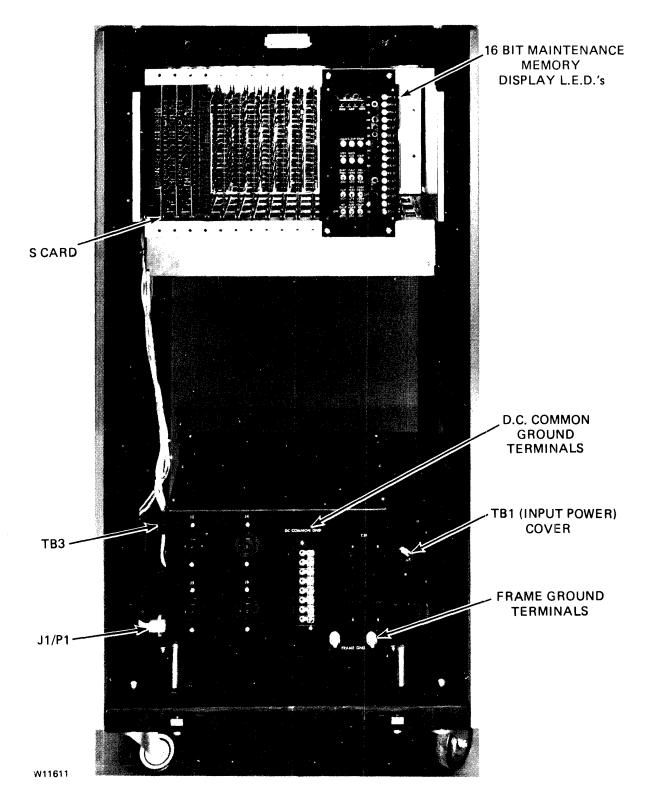

The 206 DPEC is a hard-wired controller that includes all the hardware for synchronizing the interfaces between the B1700 Disk Pack Control (DPC) and the 206 Disk Pack Drive (DPD) (see figures 1-1 through 1-3).

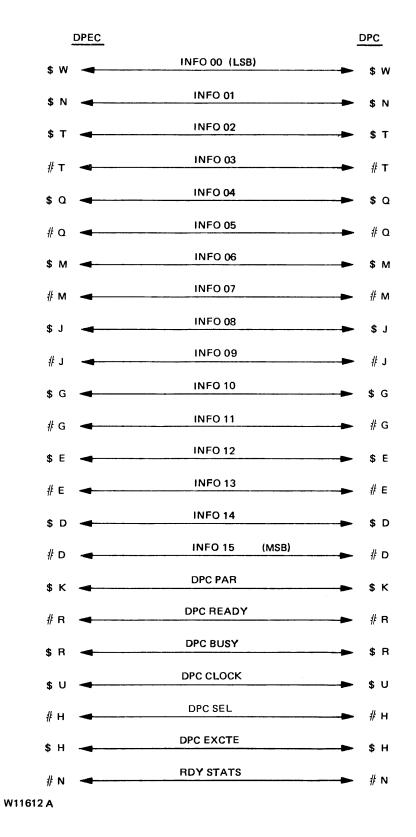

The controller is designed for a maximum configuration of one by eight spindles of disk pack drives. All DPEC's are capable of one by eight operation with no modifications. Standard 25-wire interface (parallel) is used between the DPC (host system) and the DPEC (see figure 1-4).

The DPEC acts upon I/O instructions from the DPC, performs the operation specified by the I/O descriptor and, upon completion, generates a result descriptor containing the operation completed and any error status information.

A 6-wire interface is used between the DPEC and the DPD. The interface lines consist of two bidirectional data lines (positive and negative), two clock lines (positive and negative), a controller message line, and a drive message line (refer to table 1-1).

| Table 1 | -1. Edge | Connector | Wiring |

|---------|----------|-----------|--------|

|---------|----------|-----------|--------|

| Signal<br>Description | Spindle<br>Number | Card Edge<br>Signal Lead | Connector Pin<br>Ground Lead |

|-----------------------|-------------------|--------------------------|------------------------------|

| СМ                    | 1                 | \$D                      | \$C                          |

| DATA<br>POSITIVE      | 1                 | \$E                      | \$F                          |

| DATA<br>NEGATIVE      | 1                 | \$G                      | \$F                          |

#### Table 1-1. Edge Connector Wiring (Cont)

| Tuble 1           | Li Duge C |             |               |

|-------------------|-----------|-------------|---------------|

| Signal            | Spindle   | Card Edge   | Connector Pin |

| Description       | Number    | Signal Lead | Ground Lead   |

| CLOCK<br>POSITIVE | 1         | \$H         | \$I           |

| CLOCK<br>NEGATIVE | 1         | \$J         | <b>\$I</b>    |

| DM                | 1         | \$K         | \$L           |

| DM                | 2         | \$M         | <b>\$L</b>    |

| CLOCK<br>NEGATIVE | 2         | \$N         | \$P           |

| CLOCK<br>POSITIVE | 2         | \$Q         | \$P           |

| DATA<br>NEGATIVE  | 2         | \$R         | \$S           |

| DATA<br>POSITIVE  | 2         | \$Т         | \$S           |

| СМ                | 2         | <b>\$U</b>  | \$V           |

| СМ                | 3         | # D         | #C            |

| DATA<br>POSITIVE  | 3         | # E         | # F           |

| DATA<br>NEGATIVE  | 3         | #G          | #F            |

| CLOCK<br>POSITIVE | 3         | #н          | # I           |

| CLOCK<br>NEGATIVE | 3         | # J         | # I           |

| DM                | 3         | #K          | #L            |

| DM                | 4         | #M          | #L            |

| CLOCK<br>NEGATIVE | 4         | #N          | #P            |

| CLOCK<br>POSITIVE | 4         | #Q          | #P            |

| DATA<br>NEGATIVE  | 4         | # R         | # s           |

| DATA<br>POSITIVE  | 4         | #т          | # S           |

| СМ                | 4         | #U          | # v           |

Figure 1-1. 206 Disk Pack Electronic Controller

Figure 1-2. Internal Front View of 206 DPEC

Figure 1-3. Internal Rear View of 206 DPEC

Figure 1-4. Interface Lines, DPEC to DPC ground.

## **DPEC OPERATION CODES**

The following discussion provides a description of the operation codes used in the disk pack subsystem. Table 1-2 contains a list of the DPEC operation codes.

a. READ (000)

Read data from the disk pack starting at the beginning address specified by the initiate words and continue reading each full sector until the select line drops, informing the DPEC that the operation is terminated. No partial sector reads are permitted.

The DPEC will send 90 data words and two error code words to the DPC followed by the result descriptor in each sector read. The final result descriptor will be a composite of all previous sectors read.

b. READ MAINTENANCE (001) Unconditional Seek

Read all data bits from the designated sector, through the error protection code (EPC), by dead reckoning beginning at the index mark. Data integrity is not guaranteed.

c. READ EXTENDED STATUS (001 and N2 variant set)

A read maintenance operation code with the N2 variant set is used to clear a TRY DIAG-NOSTICS condition. In local, the READ EXTENDED STATUS operation code is used to read the four extended result descriptor registers.

d. WRITE (010)

Write data on the disk pack starting at the beginning addresss specified by the initiate words and continue writing each full sector until the select line drops informing the DPEC that the operation is terminated. No partial sector writes are permitted.

The DPEC will accept 90 data words plus two dummy words. The DPEC will strip the dummy words and write the 32 check bits (Fire code) on disk. A result descriptor is sent to the DPC at the termination of the write operation.

e. INITIALIZE (011)

Write all bits according to the format shown in figure 1-5, starting after the index pulse on the specified track (head) for the entire track of pack. Spare sectors are also initialized. One data transfer takes place between the DPC and DPEC during an initialization period. The DPEC will fill the data field and write the check bits for the pattern specified by the S variant.

If the operation is terminated by the DPC (SELECT FALSE) during an initialize, the DPEC will complete the initialize to the end of the existing full track. The result descriptor will be returned at the termination of the initialize whether the DPC or DPEC caused the termination.

f. RELOCATE (100) Specified data

One data transfer takes place between the DPC and the DPEC. The DPEC writes the actual formatted address in the designated spare sector and writes the specified data pattern on a repeating basis to fill the data field. On completion of this operation, the DPEC returns a result descriptor to the DPC.

g. RELOCATE (101) Address data

No data transfer takes place between the DPC and the DPEC. The DPEC writes the actual formatted address in the designated spare sector and writes the sync byte and address repeatedly to fill the data field. On completion of this operation, the DPEC returns a result descriptor to the DPC.

During a normal read or write operation, the DPEC will perform all necessary and required operations to read the relocated sectors and then return to the previous address plus one to ensure the continuity of data transfer.

h. VERIFY (110)

The verify operation is a normal read if the N1, N2 or N3 variants are all zeros (LOW TRUE). If the N N N variants are specified, the following applies:

| NNN<br>Variant | Read<br>Spare<br>Sector | Head | Sector |

|----------------|-------------------------|------|--------|

| 001            | 1                       | 4    | 85     |

| 010            | 2                       | 4    | 86     |

| 011            | 3                       | 4    | 87     |

| 100            | 4                       | 4    | 88     |

| 101            | 5                       | 4    | 89     |

The test pattern for verification is keyed data: sync byte plus cylinder, head, and sector information, if the S variant is not set on the initialization. If the S variant is set, then the data is specified by the processor. i. TEST OP (111)

The DPEC will return a result descriptor for the unit specified in the test operation.

| OP1 | OP2 | OP3 | NO  | N1  | N2  | N3 | OP DECODE                          |

|-----|-----|-----|-----|-----|-----|----|------------------------------------|

| 0   | 0   | 0   | PLO | OF  | E/L | Ι  | READ                               |

| 0   | 0   | 1   | -   | -   | D   | -  | READ MAINTENANCE OR READ<br>ERD    |

| 0   | 1   | 0   | -   | -   | -   | -  | WRITE                              |

| 0   | 1   | 1   | -   | -   | S   | Р  | INITIALIZE                         |

| 1   | 0   | 0   | -   | . N | Ν   | Ν  | RELOCATE 1. DATA<br>SPECIFIED.     |

| 1   | 0   | 1   | -   | N   | N   | N  | RELOCATE 2. DATA=ADDRESS<br>FIELD. |

| 1   | 1   | 0   | -   | Ν   | Ν   | Ν  | VERIFY                             |

| 1   | 1   | 1   | -   | -   | С   | W  | TESTOP                             |

#### Table 1-2. DPEC 206 Operation Codes

The following are variants of the above codes.

| NNN* | = | (Binary 1 to 5) Spare Sector No. |

|------|---|----------------------------------|

| С    | = | 1, Clear Seek Status Flip-Flops  |

| Р    | = | 0, Single Track. Initialize      |

| Р    | = | 1, Full Pack Initialize          |

| w    | = | 0, Normal Test Op                |

| W    | = | 1, Remote Power Down             |

| PLO  | = | 1, Enable Early/Late Strobe      |

| PLO  | - | 0, Disable Early/Late Strobe     |

| E/L  | - | 0, Early Strobe                  |

| E/L  | = | 1, Late Strobe                   |

| S    |   | 1, Specified Data                |

| S    | = | 0, Address Data                  |

| OF   | = | 0, Normal                        |

| OF   | = | 1, Offset                        |

| D    | = | 0, Read Maintenance              |

| D    |   | 1, Read Extended Status          |

| I    | = | 0, Offset Away from Spindle      |

I = 1, Offset Toward Spindle

\*The binary values of the N variants are N1 = 1, N2 = 2, N3 = 4.

.

| INDĒX A      |                    |                          |                  |                  |                |                |                |                |

|--------------|--------------------|--------------------------|------------------|------------------|----------------|----------------|----------------|----------------|

| вот дар      | AD                 | DRESS PREAMBLE - 10.5 BY | res              |                  |                | SECTOR         | DDRESS         |                |

| 60 BYTES     | 3 BYTES<br>ADDRESS | 7 BYTES<br>BINARY        | 5 BYTE<br>BINARY | S<br>P<br>A<br>R | 1<br>MSB       | О ВІТЅ СҮ      | LINDER         |                |

| BINARY ZEROS | MARK               | ZEROS                    | ONES             | E                | 2 <sup>9</sup> | 2 <sup>8</sup> | 2 <sup>7</sup> | 2 <sup>6</sup> |

|              | PLO<br>SYNC        | PHASE LOCK<br>SYNC       | FRAME<br>DIGIT   |                  |                |                |                |                |

#### SECTOR ADDRESS CONTINUED - 4 BYTES

| 10 BITS CYLINDER (CONTINUED) |                |                |                |                |                |          | 5    | BITS HEA       | 8 BITS SECTOR  |                |                |                |                |                |

|------------------------------|----------------|----------------|----------------|----------------|----------------|----------|------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

|                              |                |                |                |                | LSB            |          |      | MSB            |                | LSB            | MSB            |                |                |                |

| 2 <sup>5</sup>               | 2 <sup>4</sup> | 2 <sup>3</sup> | 2 <sup>2</sup> | 2 <sup>1</sup> | 2 <sup>0</sup> | S        | s    | 2 <sup>2</sup> | 2 <sup>1</sup> | 2 <sup>0</sup> | 2 <sup>7</sup> | 2 <sup>6</sup> | 2 <sup>5</sup> | 2 <sup>4</sup> |

|                              |                |                |                |                |                |          |      | •              |                |                | ·····          |                | В              |                |

|                              |                |                |                |                | DA             | TA PREAN | ABLE | DATA           | FIELD          |                | 6              | ND OF          |                |                |

| SECTOR ADDRESS (CONTINUED)          |                |                | 19             | .5 BYTE              |                             |    | RECORD               | EOT GAP           |                              |                            |             |

|-------------------------------------|----------------|----------------|----------------|----------------------|-----------------------------|----|----------------------|-------------------|------------------------------|----------------------------|-------------|

| 8 1                                 | BITS SECT      | OR (CON        | IT.)<br>LSB    | 8<br>BITS<br>EPC     | 19 BYTES<br>BINARY<br>ZEROS |    | .5<br>BYTE<br>BINARY | 180 BYTES<br>DATA | 4 BYTES<br>ERROR<br>PROTECT- | 5 BYTES<br>BINARY<br>ZEROS | 30<br>BYTES |

| 2 <sup>2</sup>                      | 2 <sup>3</sup> | 2 <sup>1</sup> | 2 <sup>0</sup> |                      |                             | ×4 | ONES                 |                   | ION CODE<br>(EPC)            |                            |             |

| 8 BITS = 1 BYTE<br>2 BYTES = 1 WORD |                |                |                | SWITCH<br>TIME<br>PI | PHASE<br>LOCK<br>LO         | 1  |                      | IROUGH B IS RE    | EPEATED 89 T                 | IMES                       |             |

TRACK FORMAT, 90 SECTORS/TRACK (20, 160 BYTES/TRACK), INTERLACE FORMAT

W11613

Figure 1-5. 206 Track Format

#### **INSTRUCTION FORMAT**

Each instruction format contains three data words. The first data word consists of the operation code, "N" variants, unit designations, and the five least significant bits of the file address. The second data word consists of the 14 most significant bits of the file address and two spare bits. The third data word consists of the data information used during initialize, write, and relocate operations. Refer to table 1-3.

Table 1-3 DPFC 206 Instruction Format

| Table 1-3. | DPEC     | 206 Instruct     | ion | Format           |

|------------|----------|------------------|-----|------------------|

| INFO NN    | First Da | ata Word         | Ini | tiate Phase      |

| (LSB)      | 1        | OP1              | 9   | N1               |

|            | 2        | OP2              | 10  | N2               |

|            | 3        | OP3              | 11  | N3               |

|            | 4        | NO               | 12  | B2*0             |

|            | 5        | U1               | 13  | B2*1             |

|            | 6        | U2               | 14  | B2*2             |

|            | 7        | U4               | 15  | B2*3             |

|            | 8        | U8               | 16  | B2*4(MSB)        |

| INFO NN    |          | nd Data<br>Vord  | In  | itiate Phase     |

| (LSB)      | 1        | B2*5             | 9   | B2*13            |

|            | 2        | B2*6             | 10  | B2*14            |

|            | 3        | B2*7             | 11  | B2*15            |

|            | 4        | B2*8             | 12  | B2*16            |

|            | 5        | B2*9             | 13  | B2*17            |

|            | 6        | B2*10            | 14  | B2*18            |

|            | 7        | B2*11            | 15  | SPARE            |

|            | 8        | B2*12            | 16  | SPARE (MSB)      |

| INFO NN    | Third    | Data Word        | Ini | tiate Phase      |

| (LSB)      |          | D Word,<br>Bit 1 | 9   | B Word,<br>Bit 1 |

|            |          | D Word,<br>Bit 2 | 10  | B Word,<br>Bit 2 |

|            |          | D Word,<br>Bit 4 | 11  | B Word,<br>Bit 4 |

|            |          | D Word,<br>Bit 8 | 12  | B Word,<br>Bit 8 |

|            |          | C Word,<br>Bit 1 | 13  | A Word,<br>Bit 1 |

|            | 6        | C Word,<br>Bit 2 | 14  | A Word,<br>Bit 2 |

|            | 7        | C Word,<br>Bit 4 | 15  | A Word,<br>Bit 4 |

|            | 8        | C Word,<br>Bit 8 | 16  | A Word,<br>Bit 8 |

#### NOTE

The first and second data words of the file address bits are identified as B2\*0 (least significant bit) through B2\*18 (most significant bit). For example, 2\*3 indicates that 2 is to be raised to the third power, 2x2x2 = 8.

At the completion of an operation code, a result descriptor will be returned to the DPC. (In a local mode, the result descriptor will be displayed on the maintenance plug-on package on the F card.) Table 1-4 lists the definitions of the result descriptor bits.

| Table | 1-4. | Result | Descriptor | Information | Lines |

|-------|------|--------|------------|-------------|-------|

|-------|------|--------|------------|-------------|-------|

#### Bit Description

- 00 Read Data Error. Indicates an error in the data field or the Fire code bytes.

- 01 Write Lockout. Indicates the spindle is in a Read-Only mode or the DPEC failed to send a Write Enable CM during a write operation.

- 02 Seek Status Flip-Flop Set. Indicates the previous seek operation has not been serviced by the DPC (conditional seek capability).

- 03 Spindle Not Ready. Indicates the positioner is not settled, and a seek is in progress.

- 04 Spindle Off Line. Indicates the spindle is in an off condition and will not accept any commands.

- 05 Spindle Unsafe. Indicates the spindle is unsafe for use.

- 06 Data Sync Code Error. Indicates the data sync character was not detected.

- 07 Address Parity Error, EPL Error, or Sync Code Error. Indicates one of the following:

- a. The address was not found.

- b. The read data address Error Protection Logic (EPL) code is not in agreement with the actual EPL.

- c. The address sync character was not detected.

- 08 Seek Timeout. Indicates that the DPD was unable to complete a seek within 700 milliseconds after being told to do so.

- 09 Drive not present. Indicates that the DPD is not present.

- 10 NA

- 11 NA

- 12 NA

- 13 NA

- 14 Transmission Parity Error or Illegal Command. Indicates a parity error exists between the DPC and DPEC.

- 15 Operation Not Completed. Try diagnostics. Indicates that an exception condition (fault) occurred in the subsystem and that the data is corrupt. A Read Extended Status command is required to clear the condition.

#### **Extended Result Descriptor Feature**

The 206 DPEC contains the ability to store up to 64 bits of extended result descriptor (ERD) information in addition to the normal 16 bits of result descriptor information. Table 1-5 contains a list of the 64 bits of ERD that are used. Refer to section 4 of this volume for details on using the ERD capability.

#### NOTE

The information in table 1-5 is listed in the order that will be read on the maintenance display plug-on indicator on the F card when in a LOCAL mode. (In REMOTE, the contents of each word are inverted. For example, in the E log, ERD bit 1 is cylinder 512, ERD bit 17 is sector 32, ERD bit 33 is DPEC blower failure, and ERD bit 49 is spindle address error.)

#### Table 1-5. 206 Extended Result Descriptor Information in a Local Mode

| EI  | RD Word 1                   | 3  | ERD Word 2                |

|-----|-----------------------------|----|---------------------------|

| 1   | Sector 64                   |    | 1 N3 Variant bit          |

| 2   | P Head 1                    |    | 2 N2 Variant bit          |

| 3   | Head 2                      |    | 3 N1 Variant bit          |

| 4   | Head 4                      |    | 4 N0 Variant bit          |

| 5   | 5 Spare                     |    | 5 Unit 2*0                |

| e   | Spare                       |    | 6 Unit 2*1                |

| 7   | Cylinder 1                  |    | 7 Unit 2*2                |

| 8   | Cylinder 2                  | :  | 8 OP Code 3               |

| 9   | O Cylinder 4                |    | 9 OP Code 2               |

| 10  | O Cylinder 8                | 1  | 0 OP Code 1               |

| 11  | Cylinder 16                 | 1  | 1 Sector 1                |

| 12  | Cylinder 32                 | 1  | 2 Sector 2                |

| 13  | Cylinder 64                 | 1  | 3 Sector 4                |

| 14  | Cylinder 128                | 1  | 4 Sector 8                |

| 15  | Cylinder 256                | 1  | 5 Sector 16               |

| 16  | Cylinder 512                | 1  | 6 Sector 32               |

| ERI | D Word 3                    | ER | D Word 4                  |

| 1   | Illegal Cylinder            | 1  | Spare                     |

| 2   | Illegal Head                | 2  | Bad DM response           |

| 3   | CM or Offline when seeking  | 3  | RPM less than 3420        |

| 4   | Wr Protect and Wr<br>Enable | 4  | Temp critical             |

| 5   | Write data missing          | 5  | Temp warning              |

| 6   | Maintenance mode            | 6  | DC power failure          |

| 7   | Spare                       | 7  | Head select fault         |

| 8   | Spare                       | 8  | No write current changes  |

| 9   | Spare                       | 9  | Write current, no Wr gate |

| 10  | Model 206 Drive             | 10 | Spare                     |

| Variant bit                | 9    | Write  | bit              | 9   | Address information or             |

|----------------------------|------|--------|------------------|-----|------------------------------------|

| Variant bit<br>Variant bit | 10   | Mark   | Bit              | 10  | Spare<br>Address information or    |

| it 2*0                     |      |        |                  |     | Spare                              |

| it 2*1                     |      |        |                  | 11  | Address information or Find index  |

| it 2*2<br>Code 3           |      |        |                  | 12  | Address information or Send status |

| Code 2                     |      |        |                  | 13  | Address information or Re-zero     |

| Code 1                     |      |        |                  |     |                                    |

| tor 1                      |      |        |                  | 14  | Address information or Power down  |

| tor 2<br>tor 4             |      |        |                  | 15  | Address information or Power up    |

| tor 8                      |      |        |                  | 16  | Address information or             |

| tor 16                     |      |        |                  |     | PLO late                           |

| tor, 32                    |      |        |                  |     |                                    |

| 14                         | РНү  | 'SIC/  | AL REQUIRE       | MEN | ITS                                |

| M response                 | Cons | struct | ion              |     |                                    |

| less than 3420             | ) Th | e cor  | troller is const |     | d as a free-standing               |

|                            | unit | and is | s snipped with t | oth | side panels attached.              |

ERD Word 3

(CM Error)

Address information or

Address information or

3

4

5

6

7

8

End bit

Spare

Write enable

Parity even (1-23)

Address information or Set maintenance mode

Address information or Reset maintenance mode

Head or cylinder or

Address or Control

Parity even (1-5)

Address mark

PLO early

Offset in

Offset on

message

Continue

Read bit

1

2

3

4

5

6

7

8

**ERD Word 4**

(CM error)

as a free-standing nit and is shipped with both side panels attached. The unit is designed to attach to a 206 disk pack drive unit.

#### **Control Panel**

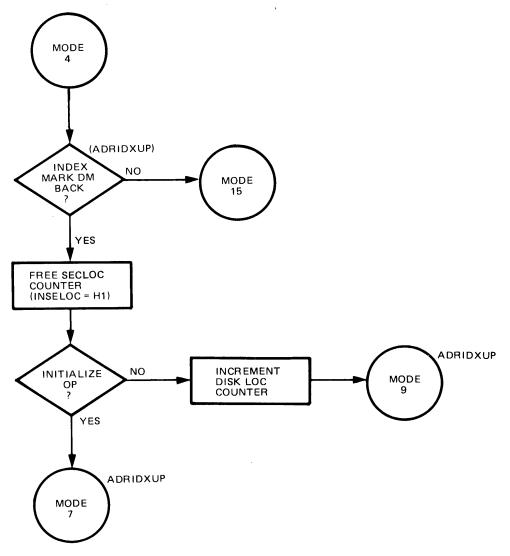

A control panel incorporated on the indicator panel provides the following controls and indicators:

| POWER:  | ON/OFF switch and indicator.        |

|---------|-------------------------------------|

| REMOTE: | ONLINE/OFFLINE switch and indicator |

#### **Dimensions**

The following are the dimensions for a 1 x 8 configuration, including front door, rear door, and side panels.

| Dimensions                   | Inches | Cm   |  |

|------------------------------|--------|------|--|

| Height                       | 44     | 112  |  |

| Width, including side panels | 21.5   | 53.5 |  |

| Depth, including doors       | 30     | 76.3 |  |

\* When a CM error is detected in a local mode, the last CM message that was sent to the drive will be displayed in ERD registers three and four in the following manner:

11

12

13

14

15

16

Carriage hit end stop

Seek incomplete

Offset during seek

Off track and Wr enable

Offset during Wr enable

Spindle address error

11

12

13

14

15

16

CM error\*

Index Mark Missing

**Missing Address mark**

DPEC blower failure

Missing R/W clock

Read data not received

| Weights                                               | Pounds                 | Kg                     |

|-------------------------------------------------------|------------------------|------------------------|

| Installed Weight                                      | 220                    | 100                    |

| Shipping Weights<br>(not including I/O cables)        |                        |                        |

| Packaged for local<br>shipment,<br>polyethylene cover | 225                    | 102                    |

| Packaged for air shipment                             | 250-260<br>(estimated) | 113-118<br>(estimated) |

When I/O cables are included in the shipping weight, use the following increments:

| P/N       | Description           | Pounds | Kg   |

|-----------|-----------------------|--------|------|

| 1145 7645 | I/O Cable,<br>25 ft.  | 17     | 7.7  |

| 1147 8369 | I/O Cable,<br>35 ft.  | 20     | 9.0  |

| 1147 8377 | I/O Cable,<br>50 ft.  | 32     | 14.5 |

| 2105 8788 | I/O Cable,<br>100 ft. | 64     | 29.0 |

## FUNCTIONAL REQUIREMENTS

#### Compatibility

The DPEC is compatible with the BX 387 disk pack drive controller, standard 90 sector interlaced format.

#### Chained I/O (DPC) Conditional Seeks

The DPEC is capable of operating with a chained I/O from the central processor unit (CPU). With chained or linked I/O, the DPEC will internally determine if a seek (positioner change) is required. If a seek is required, the DPEC performs the seek and

informs the CPU (DPC) that a specific spindle is seeking. By the use of a seek status flip-flop, once a seek has been initiated, the DPEC will not again perform a seek to that specific spindle until a read or write is received for that same cylinder. However, it will accept and perform operations on other spindles.

#### **Error Detection**

The DPEC will generate the Fire code and perform the error detection for all data transfers. (Error correction will be done by CPU.)

#### **Operational Procedure**

The front panel of the DPEC contains two pushbutton switches. See figures 1-1 and 1-2.

The switch on the left is the POWER ON/POWER OFF switch. Pressing the switch once causes the DPEC to be powered on and the ON portion of the switch to be illuminated. There is approximately a 30 second delay after the power ON button is pressed before the DPEC is operational.

Pressing the POWER button a second time will cause the DPEC to power off, and the OFF portion of the POWER button will become illuminated. In a similar manner, the REMOTE switch is used to place the DPEC in the ONLINE (remote) or OF-FLINE (local) mode.

For system operation, the DPEC must be in the ONLINE mode and OFFLINE for local operation.

The mode of the DPEC (ONLINE or OFFLINE) will be indicated by having either the upper or lower portion of the REMOTE button illuminated. To transfer the DPEC to the opposite mode, press the REMOTE button.

# SECTION 2 INSTALLATION

# INTRODUCTION

This section contains the information necessary to install the B 9499-3 Disk Pack Electronics Controller (206 DPEC).

# **PRE-INSTALLATION REQUIREMENTS**

The following paragraphs explain how the 206 disk pack drives are connected to the 206 DPEC. See figure 2-1.

# **Physical Site Requirements**

# Maintenance Clearances

| Front | 36 inches | 90 cm |

|-------|-----------|-------|

| Rear  | 36 inches | 90 cm |

| Sides | None      | None  |

# Floor Loading

| Front  | 50 pounds | (100 pounds total) |

|--------|-----------|--------------------|

| Wheels | each      | 45.4 kg            |

| Rear   | 60 pounds | (120 pounds total) |

| wheels | each      | 54.5 kg            |

## I/O Cable Information (B 1700 to DPEC)

| 25 feet  | 1145 | 7645 |

|----------|------|------|

| 35 feet  | 1147 | 8369 |

| 50 feet  | 1147 | 8377 |

| 100 feet | 2105 | 8788 |

## Drive Cable Information (DPEC to 206)

The 1 x 4 cable kit, 2781 0068, is available for use with the 206 DPEC and 206 DPD. The 1 x 4 kit consists of the following:

One 1 x 4 signal cable.

Two 3.0 foot dc common cables

Two 4.5 foot dc common cables

One 3.0 foot ac frame ground cable

One 4.5 foot ac frame ground cable

Depending on the system configuration, the following quantities of the kit can be ordered from Group III Distribution. One kit can be ordered for a  $1 \times 2$  configuration, one for a  $1 \times 4$  configuration, two for a  $1 \times 6$  configuration, and two for a  $1 \times 8$ configuration.

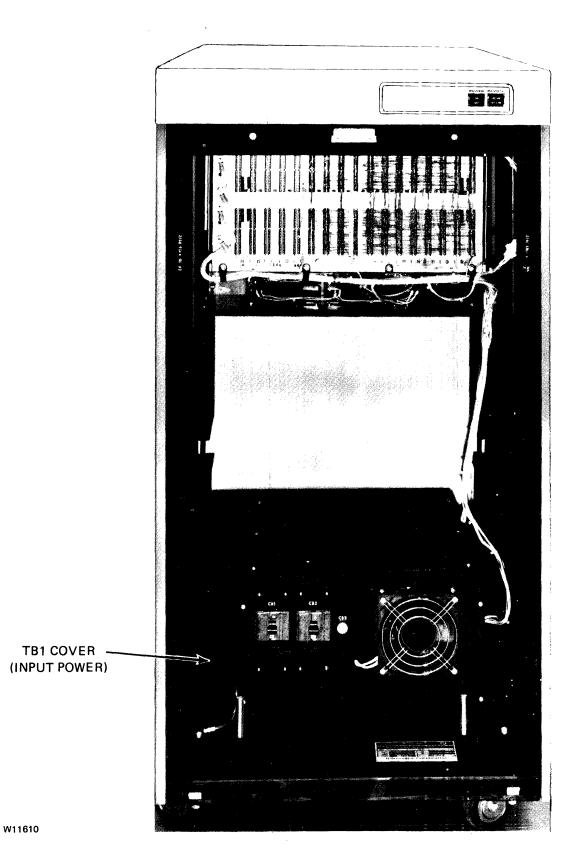

# **Power Requirements**

Input power is wired directly to the DPEC by the building electrician, through the access hole adjacent to terminal block TB1 on the left side of the power supply. Refer to section 5 of this volume for adjustments to the power supply to compensate for variations in input power.

| Voltage 20                                                    | 08 to 240V +5%, -10%           |

|---------------------------------------------------------------|--------------------------------|

| Frequency 50                                                  | $1 \pm 1$ Hz or $60 \pm 1$ Hz  |

| Power (208V three phase)                                      | 1 x 4 1 x 8<br>3.7 KVA 7.5 KVA |

| Current (208V three phase)                                    |                                |

| Line 1                                                        | 4A 12A                         |

| Line 2                                                        | 8A 12A                         |

| Line 3                                                        | 6A 10A                         |

| Power (240V single phase std. Int'l.)                         | 3.7 KVA 7.5 KVA                |

| Current (240V single phase std Int'l)                         | 18A 34A                        |

| Power factor                                                  | 0.8 0.8                        |

| Power consumption (DPEC only)                                 | 300W 300W                      |

| Heat dissipation (DPEC only)                                  | 1024 1024<br>BTU/Hr BTU/Hr     |

| Air flow at a density<br>of 0.075 lb/cubic foo<br>(DPEC only) |                                |

# **Circuit Breaker Information**

The DPEC and the power distribution subsystem in the DPEC are protected by time delay circuit breakers (20 amperes) that are rated at 1.75 times the current value of the 1 x 8 configuration, single phase, for a period of one minute.

# Equipment Grounding

A separate equipment ground wire is required in addition to the neutral service connection. Additionally, a frame ground lug is also provided for connection to the DPD. To meet U.L. requirements, the building ground wire that is furnished by the input power cable must be connected directly to the DPEC frame ground lug. A jumper wire is connected between the frame ground lug and TP1-5 in the terminal box.

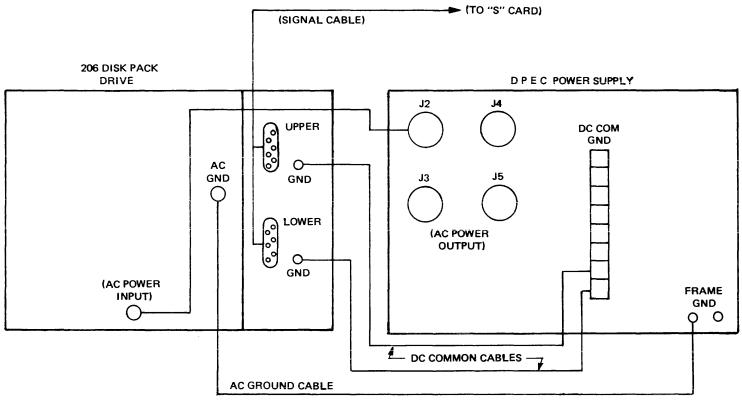

W11614

Figure 2-1. Cabling Diagram

A separate dc common lug is provided for connection to the DPD. The dc common wire is connected to the frame ground wire at a single point in the controller.

#### **Drive Power Sequencing**

AC power is distributed by the controller to the associated disk pack drives. Power-on and power-off of the disk pack drives are controlled by sequenced logic in the controller and disk pack drives.

The 206 DPEC will provide power-on sequencing to all attached units when the front panel RUN/ STOP switch on the drive is activated. The sequencing will commence approximately 25 seconds after the DPEC is ready. Each unit will be commanded to power on at 8- second intervals. After this initial power-on sequence, all future power-on cycles will be done on the appropriate drive through use of the RUN/STOP switch.

#### Environment

#### **Operating Environment**

| Temperature       | 60 to 100 degrees F (16 to 38 degrees C) |

|-------------------|------------------------------------------|

| Relative humidity | 10 to 90 percent                         |

|                   | <b>—</b> •                               |

Shipment and Storage Environment

| Temperature       | 50 to 160 degrees F  |

|-------------------|----------------------|

|                   | (45 to 71 degrees C) |

| Relative humidity | up to 95 percent     |

#### **Unpacking Instructions**

All DPEC's shipped via air carrier will be in a packing crate. The crate consists of a pallet with cushion supports, tri-wall top, front, rear, and side cardboard panels. The DPEC is in a polyethylene bag. Edge protectors are used between the DPEC and the crate. The complete packing crate is then wrapped with two metal packing straps.

The following procedure is to be used to remove the DPEC from its packing crate.

- a. Remove the metal packing straps.

- b. Remove the crate cover.

- c. Remove the edge protectors from inside the crate.

- d. Carefully lift off the cardboard sleeve.

- e. Lift the DPEC off the shipping pallet.

#### WARNING

To prevent injury, at least two field engineers must assist in removing the DPEC from the pallet.

## **INSTALLATION PROCEDURE**

#### Panel Removal

To remove any DPEC panel, two bolts must be loosened under the appropriate panel. Once these bolts are loose, lifting the panel approximately onequarter inch will allow the top of the panel to be pulled away from the DPEC frame and the panel can be removed.

The maintenance plug-on packages will be located inside the DPEC beside the power supply.

An I/O cable and T & F documentation package will also be shipped with the DPEC.

#### **AC Input Power**

AC input power is wired directly to the DPEC by an electrician. A 2.5-inch by 10-inch access hole for ac input power is provided below TB1 on the left side of the power supply. Refer to the TB1 cover or the power supply schematic for details

#### NOTE

To meet U.L. requirements, the fifth wire (green/building ground) in the input power cable to the DPEC must not be connected to TB1-5. It must be connected to the frame ground lug on the DPEC chassis. A wire is then connected from the frame ground lug to TB1-5.

AC power for all disk pack drive units is obtained from the back of the DPEC power supply. The receptacles on the DPEC are labeled J2, J3, J4, and J5.

There are three circuit breakers on the front of the DPEC power supply: CB1, CB2, and CB3. CB1 is used to protect J2 and J3. CB2 is used to protect J4 and J5. CB3 is used to protect the DPEC power supply.

#### Cables

#### DC Common Cable

A dc common ground cable is placed between each disk pack drive spindle and the dc common ground terminal on the rear of the DPEC power supply.

#### AC Ground Cable

An ac ground cable is placed between the AC GND terminal on each disk pack drive ac panel and the FRAME GND terminal on the rear of the DPEC power supply.

#### Signal Cable

A signal cable is placed from the "S" card (in the DPEC) for up to four disk pack drive spindles. A

second signal cable connected to the "R" card is required for spindles 5 through 8.

#### I/O Cable

The processor I/O cable is attached to the "Q" card in the DPEC.

#### **Drive Installation**

Regardless of the configuration used, the voltage at receptacles J2, J3, J4 and J5 must be measured before inserting the disk pack drive line cords. Refer to the B 9484-5 Disk Pack Drive technical manual Volume I, form number 1084324 for the correct input voltage requirements to prevent serious damage to the drive.

# SPECIAL INSTALLATION INSTRUCTIONS

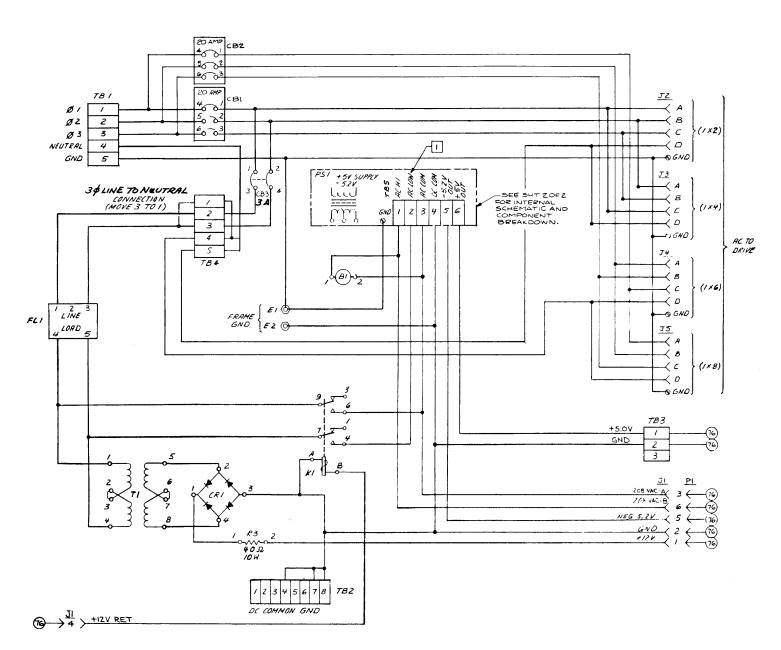

See figure 2-2, DPEC power supply schematic.

#### **Normal Three Phase Operation**

The standard power that is intended for use with the 206 DPEC is three phase power that provides 208 to 240 volts (+5 percent, 10 percent) phase to phase, four or five wire. The 206 DPEC is wired for this configuration when it is shipped from the factory. Refer to the HIGH/LOW INPUT VOLTAGE adjustment in section 5 for the input voltage that exceeds 225 volts, phase to phase.

#### **Single Phase Operation**

The DPEC is capable of single phase operation if modifications are made on the DPEC power supply (see figure 2-3).

The maximum number of drawers that can be used is four. The drive units must be wired for line-to-line operation.

#### CAUTION

Under no circumstances may the voltage applied to FL1 (in the DPEC power supply) between lugs 1 and 3 exceed 250 volts ac.

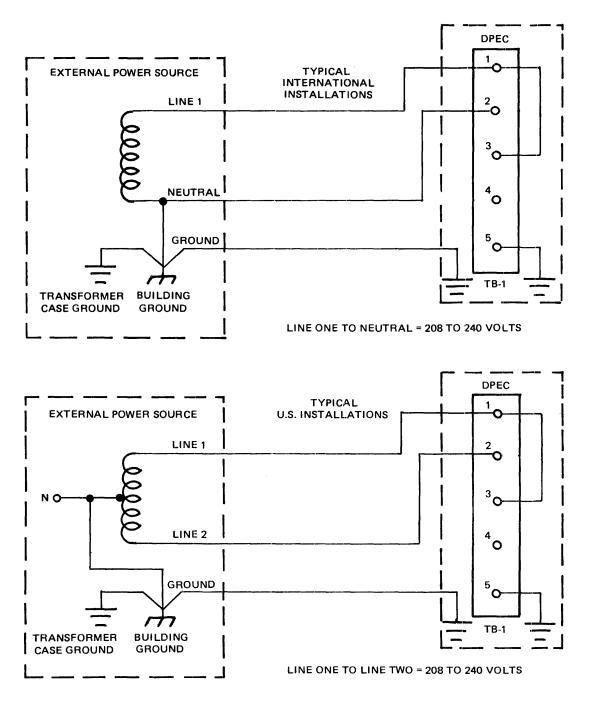

#### **International Installations**

Only receptacles J2 and J5 on the DPEC are used. (Line to Neutral=208 to 240 volts.)

a. Connect a jumper wire from TB1-1 to TB1-3.

- b. Connect the line lead to TB1-1.

- c. Connect the neutral lead to TB1-2.

- d. Connect the building ground lead to the frame ground screw provided.

NOTE

There is no connection to TB1-4. Do not use DPEC power receptacles J3 or J4. Do not make any modifications to the TB4 terminal strip in the DPEC power supply.

#### **Domestic Installations**

Only receptacles J2 and J5 on the DPEC are used. (Line to Line=208 to 240 volts, Line to Neutral=110 Volts.)

- a. Connect a jumper wire from TB1-1 to TB1-3.

- b. Connect line one to TB1-1.

- c. Connect line two to TB1-2.

- d. Connect the building ground lead to the frame ground screw.

#### CAUTION

Do not connect the neutral lead to any TB1 terminal.

#### NOTE

There is no conection to TB1-4. Do not use DPEC receptacles J3 or J4. Do not make any modifications to the TB4 terminal strip in the DPEC power supply.

#### NOTE

To meet U.L. requirements, the building ground lead in the input power cable must not be connected to TB1-5. This lead must be connected directly to the frame ground lug on the DPEC chassis. Another wire is then connected from the frame ground lug to TB1-5.

#### System Checkout

Revision AG (P/N CT 2211-0175) of the B 1700 disk pack subsystem test routine can be used to check out the disk pack subsystem. This revision is supplied with the DPC. Refer to section 4 for details.

W11615A

,

Figure 2-2. DPEC Power Supply Schematic

2-5

....

NOTE TO MEET U.L. REQUIREMENTS, THE GREEN (OR BUILDING GROUND) WIRE IN THE INPUT POWER CABLE TO THE DPEC MUST NOT BE CONNECTED TO TB1-5. IT MUST BE CON-NECTED DIRECTLY TO THE FRAME GROUND LUG ON THE DPEC CHASSIS. A WIRE IS THEN CONNECTED FROM THE FRAME GROUND LUG TO TB1-5.

W11616 A

Figure 2-3. Single Phase Input Power Connection

# SECTION 3 DOCUMENTATION AND COMPONENTS

#### INFORMATION

This section contains material relating to the documentation, component location, and flow charts for the 206 DPEC.

#### **RELATED DOCUMENTS**

The following is a list of books and documents related to the operation and maintenance of the 206 DPEC.

- a. B 9499-3 Disk Pack Electronic Controller Theory of Operation, form no. 1095650.

- b. B 9484-5 206 Disk Pack Drive Function and Operation, form no. 1104189.

- c. B 9484-5 206 Disk Pack Drive Theory of Operation, form no. 1084332.

- d. B 1800/B 1700 Disk Pack Control II, form number 1098290.

- e. Test and Field Document, P/N 2161 1660.

- f. B 9499-3 DPEC Illustrated Parts Catalog, form no. 1104189.

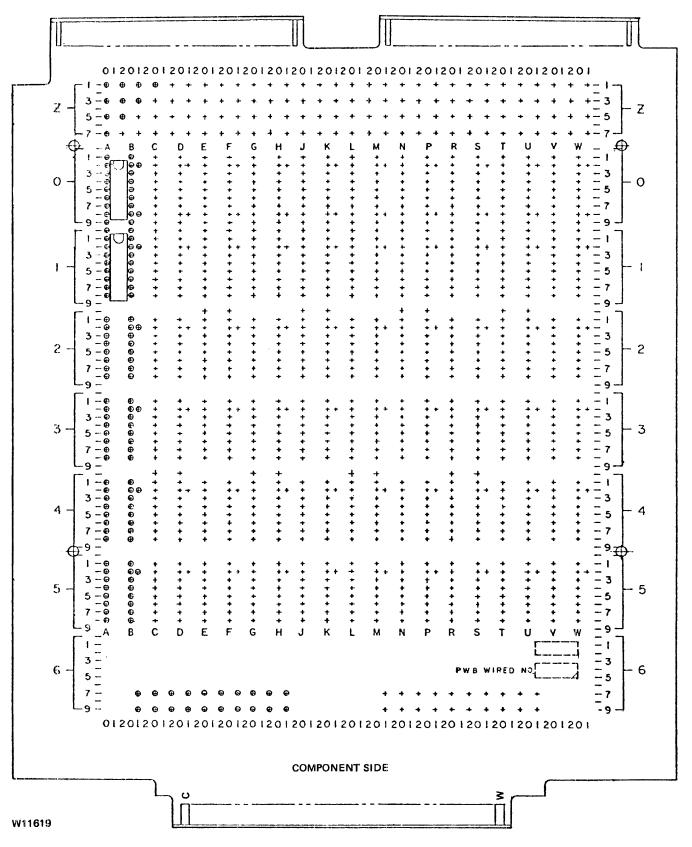

#### PRINTED CIRCUIT CARDS

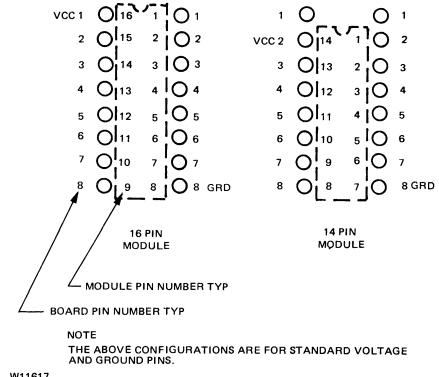

The printed circuit cards used in the DPEC are double sided boards into which 860 gold-plated socket terminals can be installed. Printed circuit wiring is used to distribute power and ground planes to the matrix terminals, and the socket terminals are configured to accept 14-pin or 16-pin dual in-line (DIL) integrated circuit packages. All of the integrated circuit modules, terminator resistors, decoupling capacitors, and potentiometers which comprise a card are pluggable; no solder is used to mount these components to the boards.

All connections on the card assembly backplane are wire wrapped. Two connections can be made on each card assembly backplane terminal.

A particular integrated circuit (IC) can be located by using the coordinate markings that appear on both sides of the cards. The IC locations will be listed on the schematics as two letters followed by a number: AB4, LM3, VW0, etc.

Figure 3-1 will be helpful in locating a particular integrated circuit leg for troubleshooting purposes.

The ground plane is the complete etching surface on the backplane or wiring side (#) of the card.

The +5.0 volts plane is the complete etching surface on the component side (\$) of the card.

W11617

#### 3-1. Integrated Circuit Leg to Card Backplane Correlation (Backplane View)

# Card Backplane Pin And Connector Pad Identification

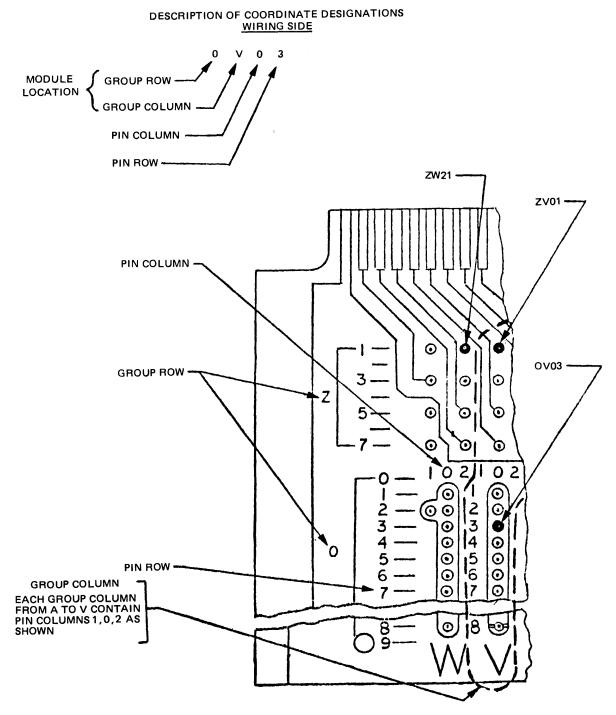

Figure 3-2 illustrates the method used in the DPEC to locate a particular backplane pin on the card. Group row "Z" will be used to make connections to the card connector pads. All cards will have a top and a bottom section of backplane connector pads.

#### **Cable Connector Cards**

There are five cards in the DPEC that have connector pads at both ends of the card. The following discussion refers to only the cable connector ends of these cards.

#### Ω, R, S, and P Cards

The Q, R, S, and P cards contain 40-edge connector pads, 20 pads on each side. The pads on the component side will be identified with a letter between "C" and "W" and will be preceded by a "\$" symbol. The pads on the wiring side will be preceded by a " " symbol.

All connector pad pins for both sides of the card will be located in group row 6 on the wiring or backplane side of the card. The coordinate method of pin identification is used in this row of pins. See figures 3-2 and 3-3.

#### F Card

The F card has a conventional card cage backplane connector pad array on both ends of the card. The maintenance control plug-on package is attached to this card. The plug-on package connector pad pins will be in group rows 6 and 7. See figure 3-2 for the coordinate designations.

Each DPEC is shipped with a set of Test and Field documents (T & F) which reflect the configuration of that particular DPEC. In some cases, a supplemental T & F document may also be included.

The following material will be found in the T & F package:

- a. DPEC block diagrams.

- b. Flow chart.

- c. Schematics for the cards and the power supply.

- d. Card assembly parts lists.

- e. Switch panel parts list.

- f. Power supply parts list and specifications.

- g. Backplane wiring list, signal name.

- h. Card wiring list.

## DPEC MODE DEFINITIONS

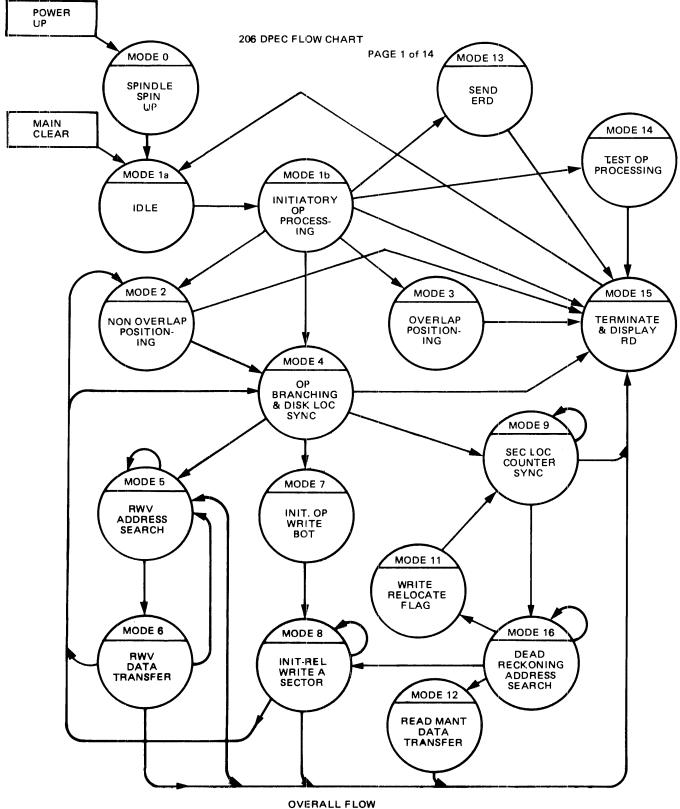

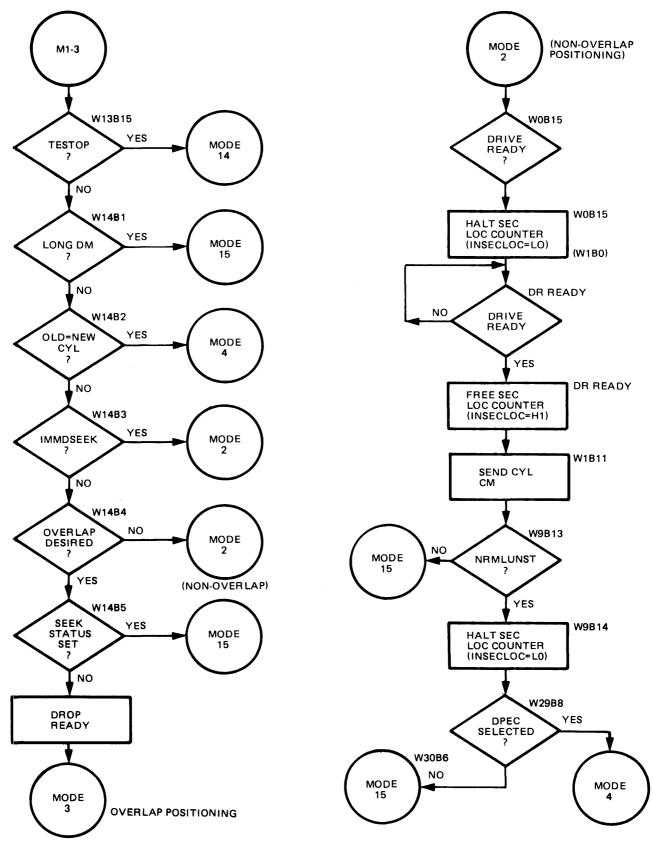

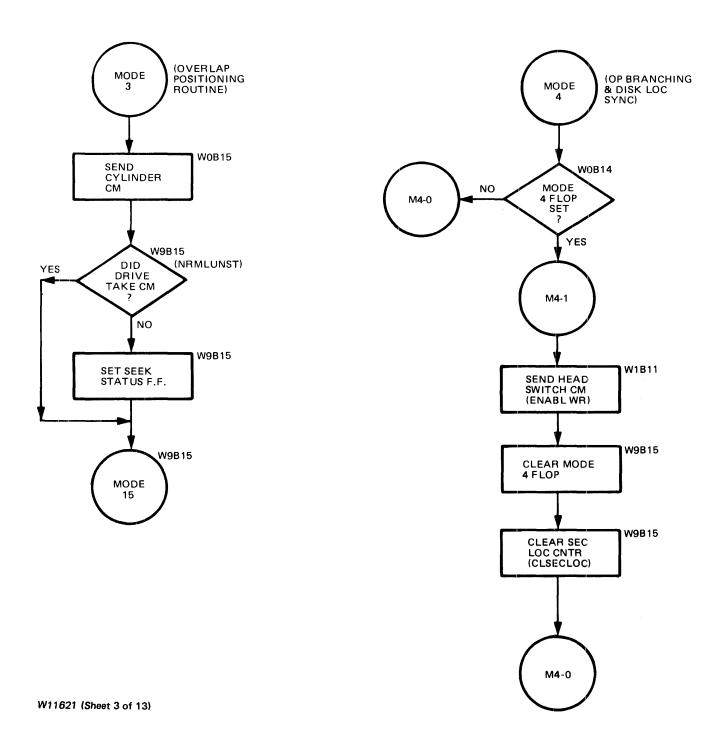

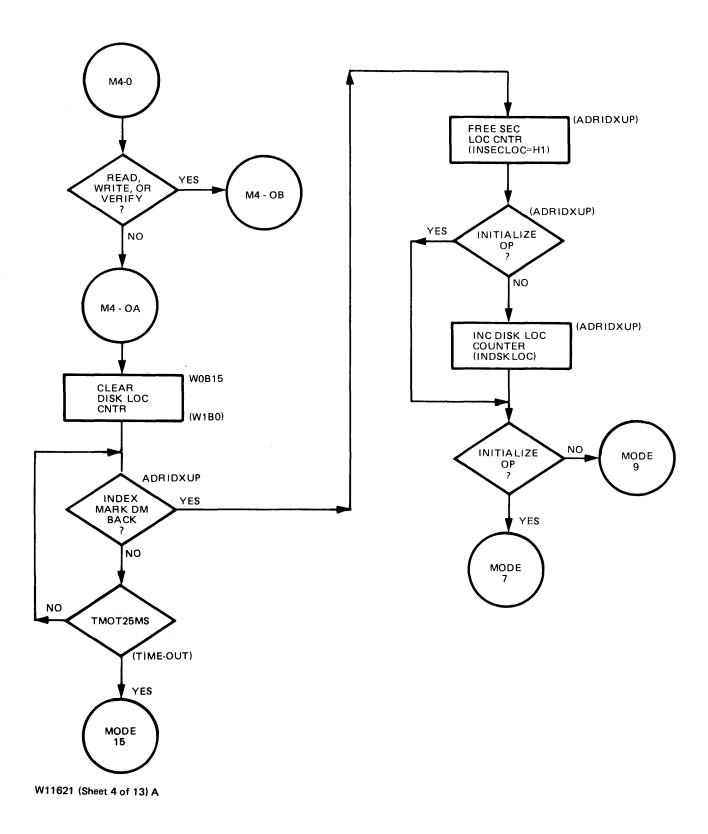

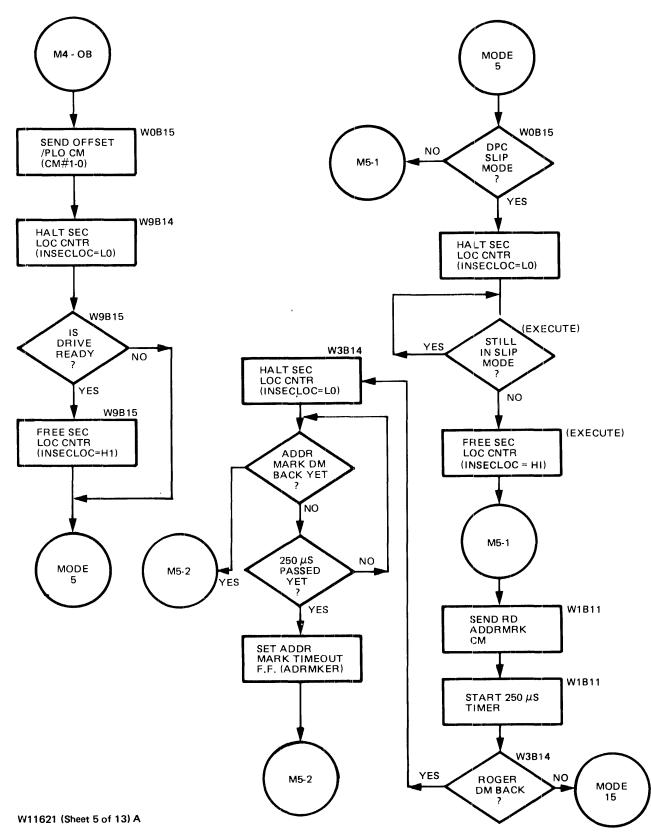

The 206 DPEC operates in 16 modes. Table 3-1 lists the basic function of each mode.

#### Table 3-1. Mode Functions

#### Mode

- Function

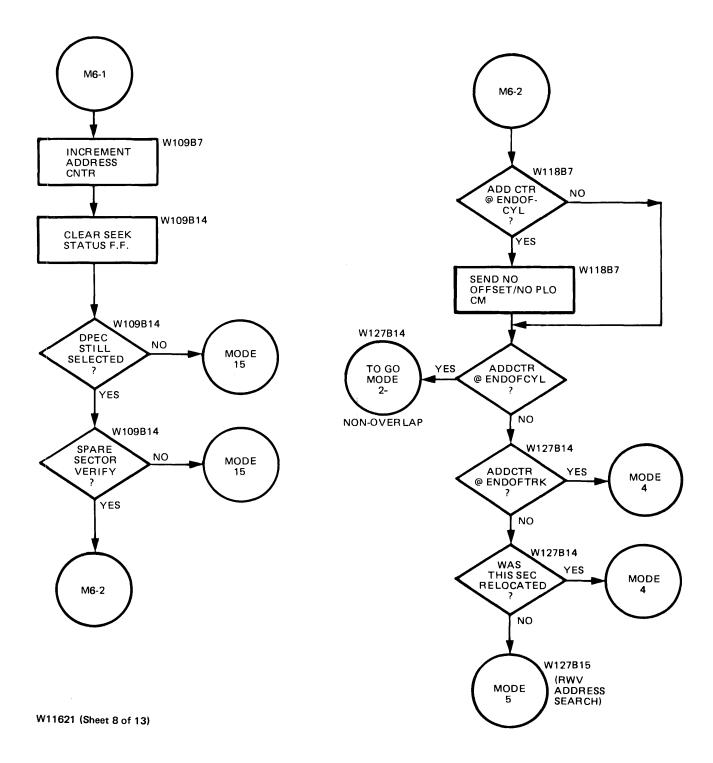

- 0 Spindle spin up sequence.

- 1 Idle halt and initiatory OP processing.

- 2 Non overlap positioning routine.

- 3 Overlap positioning routine.

- 4 Op branching and disk location sync.

- 5 Read, write or verify address search.

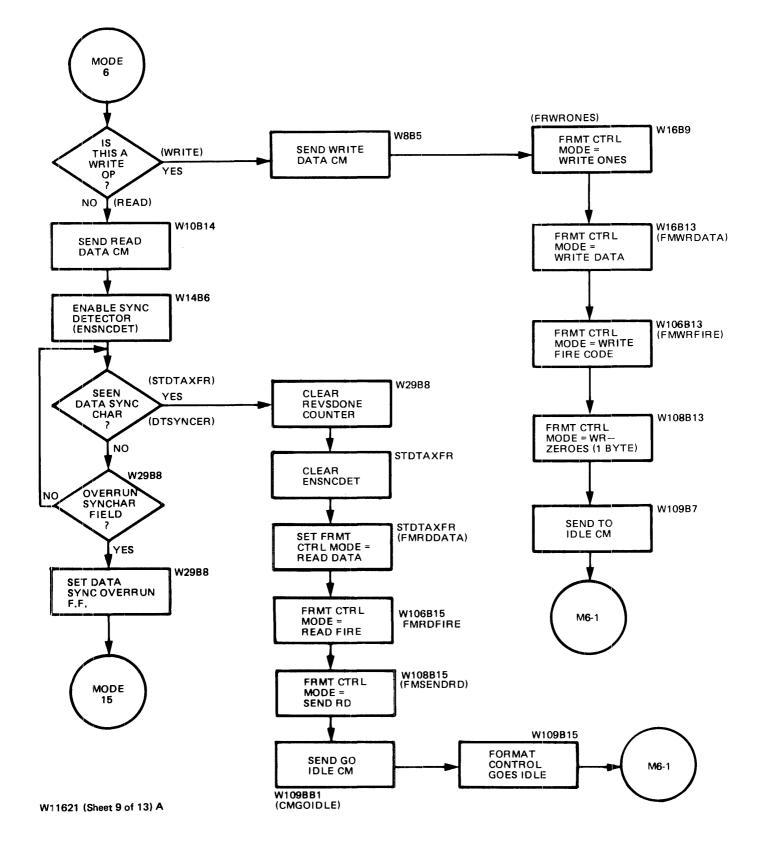

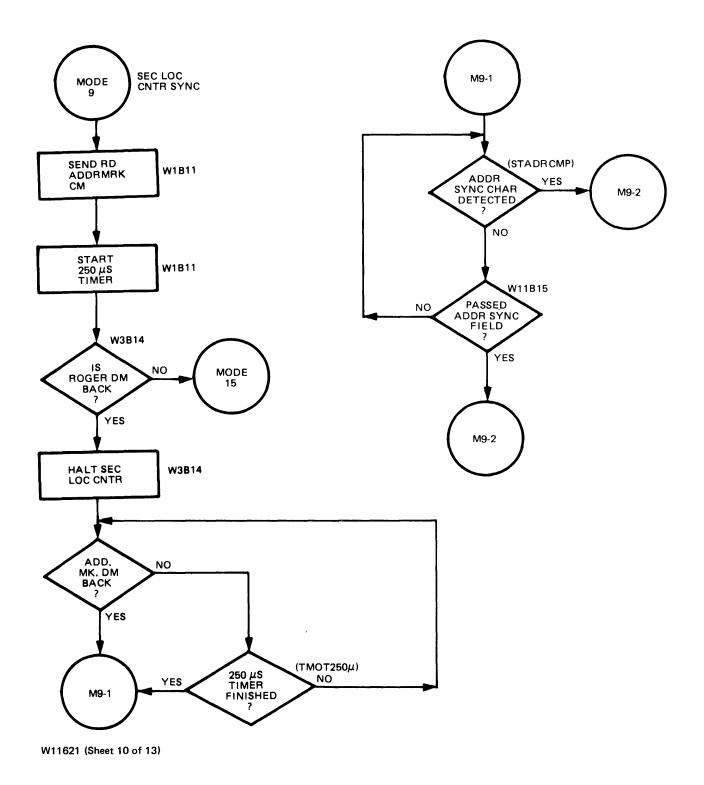

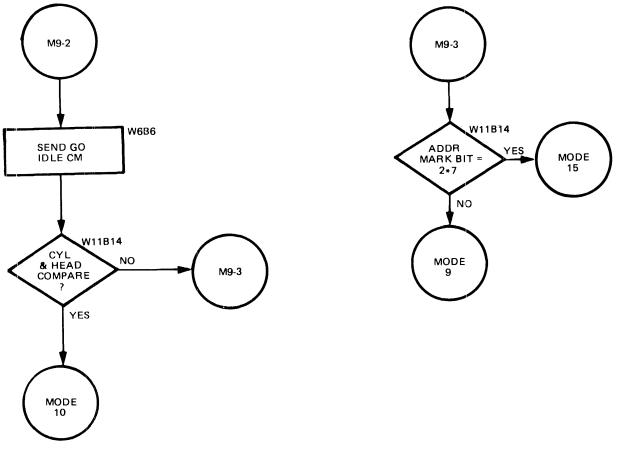

- 6 Read, write or verify data transfer.

- 7 Initialize operation and index mark search routine.

- 8 Initialize and relocate writing operation.

- 9 Sector location counter sync routine.

- 10 Dead reckoning address search (relocate and read maintenance)

- 11 Write relocate flag routine.

- 12 Read maintenance data transfer.

- 13 Send ERD routine.

- 14 Test operation processing

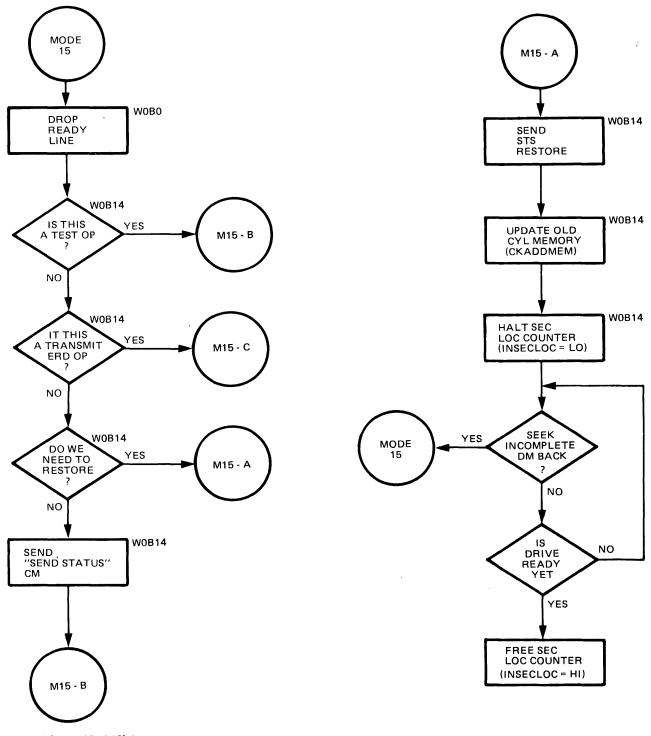

- 15 Terminate and display result descriptor.

W11618A

Figure 3-2. Card Backplane Pin Locating Scheme

Figure 3-3. Cable Connector Type Card

#### DPEC FLOW CHART DESCRIPTION

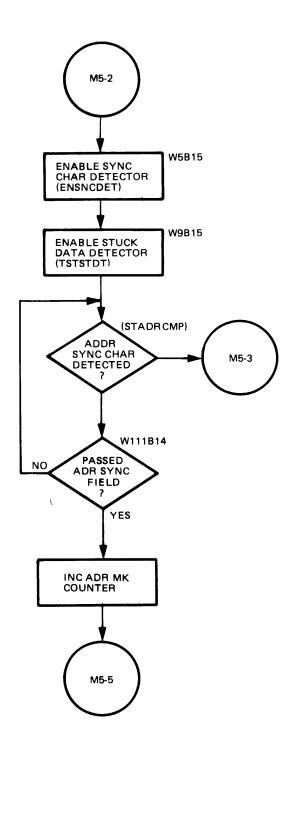

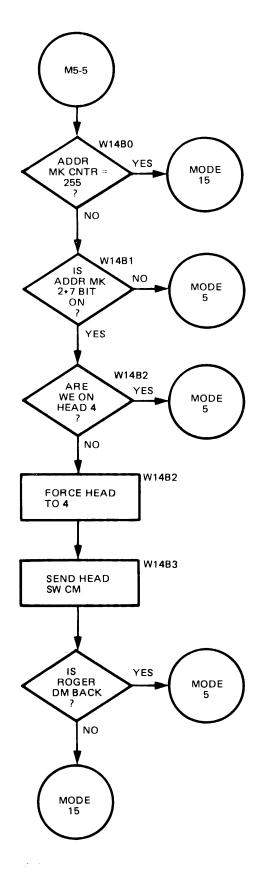

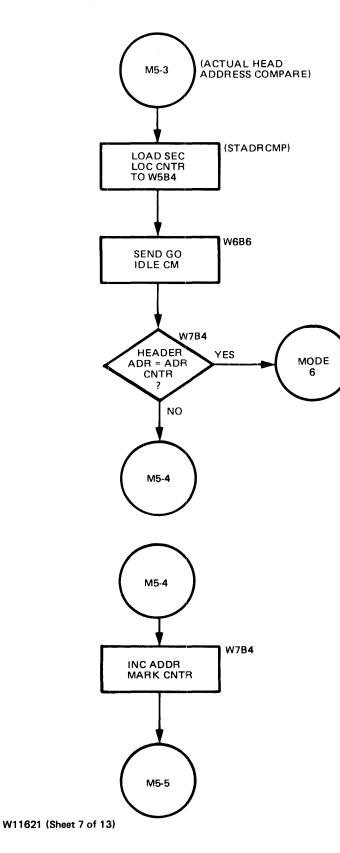

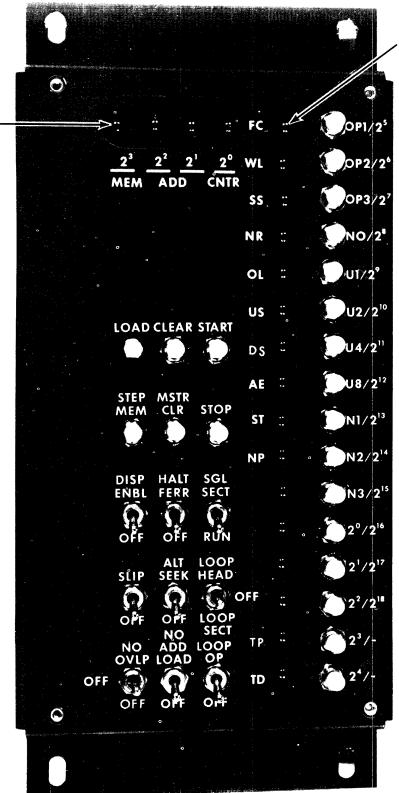

The following paragraphs describe the use of the 206 DPEC detailed flow chart (see figure 3-4). The flow chart is for reference use only, refer to the flow chart in the T & F documentation package for the current revision.

The first page of the flow chart is an overall flow diagram which can be used as a guide in determining which modes can be accessed from any other mode. There is also a brief description of the operations that will take place at that particular mode.

The top half of the second page of the flow chart contains a guide to the use of the flow chart.

The abbreviations used are as follows:

| Abbreviation | Meaning |

|--------------|---------|

|--------------|---------|

|           | -                                                  |

|-----------|----------------------------------------------------|

| HEAD      | Header name                                        |

| DO        | Operation to be performed                          |

| MAKE      | Make some particular thing happen                  |

| TEST      | Condition to be tested.                            |

| GO TO     | Name of header desired.                            |

| CMNT      | Text of the comment                                |

| SYMBL     | Symbol                                             |

| EXEC TIME | Execution time                                     |

| P         | Page number in schematics                          |

| YSSYM     | Operation to be performed if test result is "yes." |

| NOSYM     | Operation to be performed if test result is "no."  |

The actual flow chart begins on the third page. The left margin will contain the mode that the DPEC is in where the actions in that section are to take place.

There are four columns on the right side of the page. When a TEST condition is being performed, the first column will contain the mode to go to if the result of the TEST was a "yes." The second column on the right will contain the mode to go to if the result of the TEST was a "no." Other terms used during the TEST condition are NEXT, SKIP 1, AND BACK 1. NEXT indicates that the following line is to be performed, SKIP 1 indicates the next line is to be skipped and the following line performed. BACK 1 is self explanatory.

Term names in parentheses are used to identify a term that is instrumental in the PERFORM statement preceding it.

When a DO, MAKE, or TEST statement is being performed, the third column on the right will contain the time when the statement will be performed. In some cases, the GO TO MODE statement can contain a location within a certain mode, for example, M5-4. This means that the operation will be performed at part 4 time of mode 5. It may be necessary to locate this new mode by searching the left margin on another page within the flow chart.

Unless otherwise specified, when a comment contains the phrase "GO TO MODE 'n' '', the SEC-TOR LOCATION COUNTER is cleared and the MAIN MODE COUNTER is set to the number indicated.

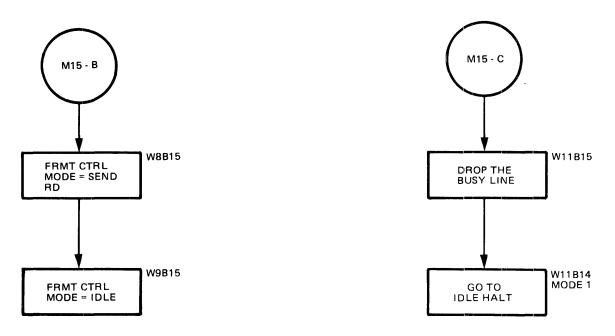

Figure 3-5 is a simplified flow chart of the 206 DPEC covering the READ, WRITE, or VERIFY operation codes. This flow chart is intended only as a quick reference. When detailed descriptions and timing information are required, refer to the detailed flow chart of figure 3-5.

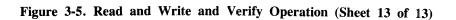

Figure 3-6 is a simplified flow chart of an INITIALIZE operation. It begins at Mode 4 because there are no significant differences, prior to that mode, when compared to the READ, WRITE, or VERIFY simplified flow chart.

The following table (table 3-2) illustrates the main mode jump conditions.

The first column lists the MODE that is being entered.

Column 2 is the FINAL TERM name and the schematic where the term can be found.

Column 3 contains the PARTIAL TERMS (default names) needed to derive the final term.

Column 4 has SUB PARTIAL TERMS, where applicable, and the page numbers.

Column 5, FROM MODE, lists the modes that the DPEC may be in prior to entering a particular mode.

Column 6 contains the conditions needed to produce the "GO TO MODE" term.

The final column, 7, contains the SOURCE PIN and PAGE DPEC to the opposite mode, press the REMOTE button. NUMBER for the PARTIAL TERM names.

W11620 (Sheet 1 of 14) A

|               | DW CHA                                     | BLOC                                           | CK 1               | TE X1                          | ſ                                   |                      |                           |                         |      |                      |                  |                     | G              | o <b>t</b> o <b>i</b> | GOT                  | 02 |                      |                | R           | PAG                     |

|---------------|--------------------------------------------|------------------------------------------------|--------------------|--------------------------------|-------------------------------------|----------------------|---------------------------|-------------------------|------|----------------------|------------------|---------------------|----------------|-----------------------|----------------------|----|----------------------|----------------|-------------|-------------------------|

|               | HEAD<br>DO<br>MAKE<br>TEST<br>GOTO<br>CMNT | HE AC<br>OPER<br>Some<br>Cont<br>NAME<br>TE X1 |                    | NAM<br>ION<br>RTI<br>ION<br>HE | TO<br>TO<br>CUL<br>TO<br>ADE<br>E C | BE<br>AR<br>BE<br>CM | PER<br>THI<br>TESI<br>ENT | FOR<br>NG<br>TED<br>RED | HAP  | PEN                  | *                |                     | S<br>S<br>Y    | YMBL<br>YMBL<br>Ssym  | NOS                  | YN | EXE<br>EXE<br>TES    |                | E<br>E<br>E | P                       |

|               | CMNT                                       | MODE                                           |                    |                                | IRU<br>(HRU                         | 9 /                  | ARE                       |                         |      | NDE<br>D M           | 0 T<br>D 1 0     | HRU                 | MD I<br>RU I   | E9;<br>4D15           |                      |    |                      |                | P 46        |                         |

| `             | CMNT                                       | 1.                                             | THE.               | CLE                            | EARI                                | N G<br>I N           | OF<br>Mod                 | SEC                     | TOR  |                      | CAT              | ION                 | C 0 (          | JNTE                  | ED O<br>R, A<br>MENT | ND |                      | 5E):           |             |                         |

|               | HEAD                                       | >>>>                                           | >>>>               | >>>>                           | ····                                | ST                   | RT                        | 0E                      | FLO  | W C                  | HAR              | T <-                | <<<            |                       |                      |    |                      |                |             |                         |

|               | TEST<br>DO                                 | IS /<br>PWR                                    | NC P<br>RES        | POWE                           |                                     |                      | ET?                       | RE                      | _ DI | PEC                  |                  |                     | N  <br>M       | EXT<br>DEO            | SAM                  | E  | PWRI                 | RSYNC          | )           | Р77<br>Р42<br>Р71       |

| >>>>><br>MDE0 | >>>>><br>HEAD                              | MDE                                            | )                  | IDEC                           | ) M                                 | DEC                  | ) N                       | DEO                     | M    | DEO                  | M                | DEO                 |                |                       |                      |    |                      |                |             | P50                     |

|               | CMNT<br>CMNT                               | WE (<br>Powe<br>Main<br>Inse                   | ER F               | RESE<br>DDE                    | = 0                                 | AST                  | IS A<br>UNIT              | BOU                     | T 2' | 5 SI<br>= 0          | ET<br>ECO<br>• S | ONL'<br>NDS<br>EC I | r -<br>Loc     | CNT                   | R =                  | 0  |                      |                |             | P71<br>P51              |

| SPIN          | HEAD<br>TEST<br>DO<br>CMNT<br>DO<br>TEST   | DRIN                                           |                    | THEF<br>SF                     | ιε <b>?</b><br>ι =                  | н                    | •                         |                         | 1    | (DR<br>(i<br>F<br>NE | TH<br>CM_<br>BIT | ERE<br>SEL<br>TI    | <b>}</b><br>ЧЕ |                       |                      |    | W181<br>W281<br>W281 | 1<br>1         |             | <b>P7</b><br>P55<br>P55 |

| SP_1          | TEST<br>CMNT<br>DO<br>DO<br>DO             |                                                | VE P<br>D PV<br>RT | RES<br>R-1<br>8-5              | ENT<br>IP C                         | AN<br>M 1<br>ND      |                           | ONE<br>RIV              | RED  | ON<br>CST            | ( MD<br>8 T      | EO)<br>Inr          |                |                       |                      |    |                      | 15<br>15<br>15 |             |                         |

|               | CHNT                                       | SEC                                            | L00                | C                              | ITR                                 | TO                   | STA                       | Y 0                     | FF   | UNT                  | IL               | TIM                 | ER F           | INI                   | SHES                 |    |                      |                |             |                         |

|               | TEST<br>Do                                 | 8-9<br>FREE                                    | SEC<br>Se          | TIN<br>EC L                    | IER<br>OC                           | FINCOL               | II SH<br>IN TE            | ED?<br>R                | CIN  | CTH                  | 0 T 8<br>L 0 C   | SEC<br>=HI          | ) NE           | EXT                   | SAM                  | Ε  | THO                  | I BSEC         |             | P 37<br>P 51            |

| SP_2          | 00<br>00<br>00                             | MAKE<br>SWI<br>INCE                            | ГСН                | TO                             | LOC                                 | AL.                  | CLO                       |                         |      | (SW)                 | _LŌ              | SEL<br>CAL<br>TCT   | )              |                       |                      |    | W681<br>W681<br>W681 | 5              |             | P55<br>P55<br>P57       |

|               | TEST<br>Do<br>gcto                         | CLE                                            | AR S               | SEC                            | LOC                                 | CN                   | ITR                       |                         | 4    | CUN<br>CCL:<br>QUEI  | SEC              | 2 * 3<br>1 0 C      | )              | 2_3<br>PIN            | NEX                  | T  | W881<br>W881<br>W881 | .5             |             | P4<br>P52<br>•          |

| SP_3          | CMNT<br>DO<br>DO<br>GOTO                   | CLE                                            |                    | SEC                            | LOC<br>DC                           |                      | ITR<br>INTF               | R                       | CIN  | (CL<br>Seci          | SEC              |                     | )              | PSE<br>DE1            | QUEN                 | CE | W981<br>W981<br>W981 | 5              |             | P 52<br>P 54            |

| W11620        | ) (Sheet 2                                 | of 14)                                         |                    |                                |                                     |                      |                           |                         | •••• |                      |                  |                     |                |                       |                      |    |                      |                |             |                         |

Figure 3-4. Detailed DPEC Flow Chart (Sheet 2 of 14)

| »>>>:<br>NDE1 | HEAD<br>CMNT                 | MDE1 MDE1 MDE1 MDE1 MDE1 MDE1 MDE1 <<<<<<<br>IDLE HALT - INITIATORY OP PROCESSING - MODE 1<br>WE GET HERE EITHER FROM THE MODE 0 SEQUENCE OR<br>FROM A MAIN CLEAR OR FROM FINISHING AN OP.                            |                                                                                                                                                        |

|---------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | TEST                         | DPEC SELECTED YET? (SELECT) NEXT SAME                                                                                                                                                                                 | SELECT P45                                                                                                                                             |

|               | DC<br>DC<br>CMNT<br>DO<br>DO | FREE SEC LOC COUNTER (INSECLOC=HI)<br>LATCH INITIATE WORD 1 (CK WORD1)<br>ADDR DECODR NOVES INTO STATE 1 AT FRONT EDGE OF<br>SEND FIRST CK DPC (CK DPC)<br>RAISE THE READY LINE (READY)                               | SELECT         P51           W0B11         P4+8           W0B11         P4+6           W0B12-14         P66           W0B15         P56                |

|               |                              | LATCH INITIATE WORD 2 INTO A.D. (W1B11)<br>ADDR DECODR NOVES INTO STATE 2 AT FRONT EDGE OF<br>THEN STEPS AT 5MHZ RATE.<br>DRIVE THERE (DM BUF) NEXT NEXT<br>SEND SECOND CK_DPC (CK_DPC)<br>RAISE THE BUSY LINE (BUSY) | W1811     P8       W1811     P7       W1811     P7       W1812-14     P66       W1815     P56                                                          |

|               | TËST<br>DO<br>DD<br>Cmnt     | IS OP A TRANSMIT ERD? (SEND_ERD) MD13 NEXT<br>DRIVE THERE NEXT SKIP4<br>SWITCH TO DRIVE CLOCK (SW TO DR)<br>SEND SELECT CM TO DRIVE (CM_SEL)<br>DM_RCVD GOES LOW AT W281<br>CM_BUFF GOES LOW AT W282                  | W280         P67           P55         P55           W281         P55           W281         P55           W281         P23           W282         P22 |

| N             | TEST                         | XMINPERR OR TRY DIAG (XMPER+TD) MD15 NEXT                                                                                                                                                                             | W2B14 P49                                                                                                                                              |

|               | TEST<br>DO                   | RDM+INIT+REL+OVRLAPDS/ (IMMDSEEK) NEXT SKIP1<br>CLEAR SEEK STATUS FF (CKSKSTAT)                                                                                                                                       | W2815 P45<br>W2815 P55                                                                                                                                 |

|               | CMNT<br>D 0                  | ADDR DECODER FINISHED (ADSTATEO) AT<br>LOAD ADDRESS COUNTER (LOAD_AC) AT                                                                                                                                              | W387 TIME. P7<br>W4813 TIME. P9                                                                                                                        |

|               | CMNT<br>TEST<br>CMNT         | INITIAL SHORT DM S/B BACK BY W431 TIME.<br>DRIVE OFFLINE OR NOT READY? MD15 NEXT<br>WE MUST TEST THE DRIVE FOR SPINDLE ADDRESS<br>AND ALSO FOR WRITE LOCKOUT IN THE CASE OF<br>A WRITING OP (WR/INIT/OR RELOC).       | W581 P49                                                                                                                                               |

|               | 00                           | WR + INIT + RELOC OP? (NEEDTOWR) NEXT M1_2<br>SEND WR EN/SPNDL ADDR CM (ENABL_WR) CM_LOAD AT<br>THE TEST FOR TESTOP M1_3                                                                                              | ₩5815 P45<br>₩5815 P60+62                                                                                                                              |

| N1_2          | 00                           | SEND SPNDL ADDR ONLY CM (CM#2-1) CM_LOAD AT                                                                                                                                                                           | W5815 P62                                                                                                                                              |

|               | CMNT                         | SECOND DM SHOULD BE BACK BY WI3BIO TIME                                                                                                                                                                               | W13810 P23                                                                                                                                             |

| M1_3          | TEST<br>TEST<br>TEST         | IS THIS OP A TESTOP? (TESTOP) MO14 NEXT<br>DOES OLD CYL = NEW CYL? (OLD=NEW) MDE4 NEXT<br>RDM+INIT+REL+OVRLAPDS/ (IMMDSEEK) MDE2 NEXT                                                                                 | W13815 P67<br>W1482 P10<br>W1483 P45                                                                                                                   |

|               | CMNT                         | ONLY OPS READ, WRITE, AND VERIFY<br>Remain at this point in the flow.                                                                                                                                                 | P65+67                                                                                                                                                 |