Burroughs believes that the information described in this manual is accurate and reliable, and much care has been taken in its preparation. However, no responsibility, financial or otherwise, is accepted for any consequences arising out of the use of this material. The information contained herein is subject to change. Revisions may be issued to advise of such changes and/or additions.

Correspondence regarding this document should be addressed directly to Burroughs Corporation, P.O. Box 4040, El Monte, California 91734, Attn: Publications Department, TIO-West.

# LIST OF EFFECTIVE PAGES

| Page | Issue             | Page      | Issue             |

|------|-------------------|-----------|-------------------|

| ii   | Blank<br>Original | v thru vi | Original<br>Blank |

## TABLE OF CONTENTS

Section

| 1 | BASIC PRINCIPLES                                     |

|---|------------------------------------------------------|

|   | Introduction                                         |

|   | General Description                                  |

|   | Block Diagrams                                       |

|   | System Block Diagram                                 |

|   | Logic Overview                                       |

|   | Processor Interface                                  |

|   | Maintenance Block                                    |

|   | OP and Variant REG, Unit REG/Counter                 |

|   | Address Decoder                                      |

|   | Address Counter, Register, and EPC Generator         |

|   | Auxiliary Address Logic and Address Compare Register |

|   | PSP Buffers and Register                             |

|   | Read Operation                                       |

|   | Write Operation                                      |

|   | Fire Code Logic                                      |

|   | Main Serial Multiplexer                              |

|   | Main Clock and Data Sync Logic                       |

|   | Sync Char Logic                                      |

|   | CM Logic                                             |

|   | DM Logic                                             |

|   | Drive Interface                                      |

|   | RD and ERD Logic                                     |

|   | Main Mode Logic                                      |

|   | Sector Location Counter and Decoder                  |

|   | Seek Status Logic                                    |

|   | Timer Logic                                          |

|   | Format Control Logic                                 |

|   | CM Message                                           |

|   | DM Message                                           |

|   | DPEC-DPC Control and Status Interface Lines          |

|   | DPEC-DPC Interface Operation                         |

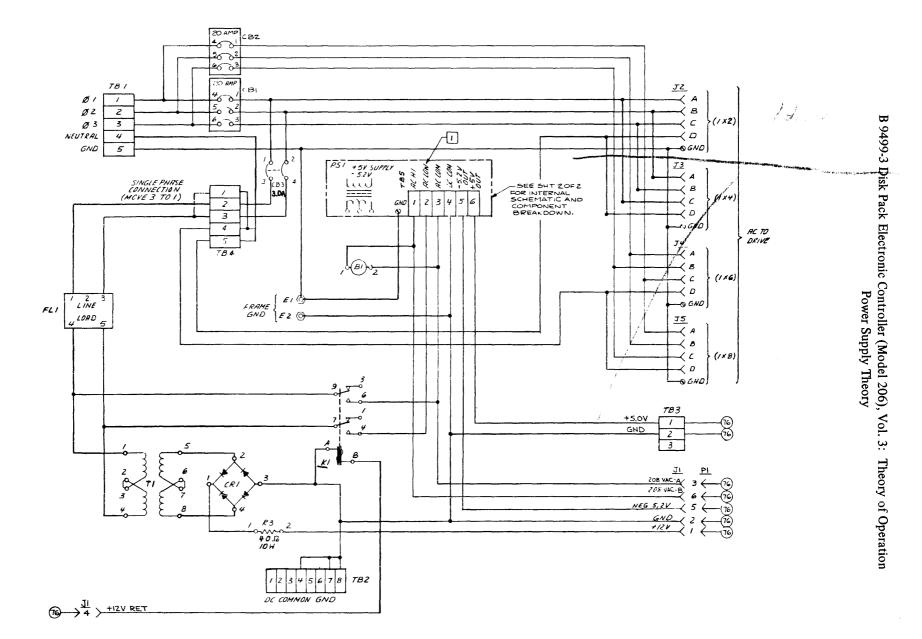

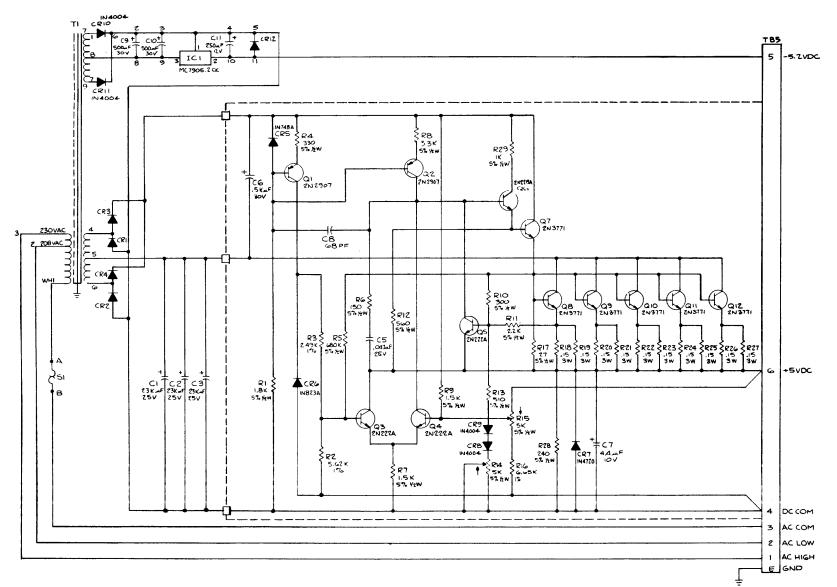

| 2 | POWER SUPPLY THEORY                                  |

|   | Introduction                                         |

|   | Power Supply                                         |

## LIST OF ILLUSTRATIONS

#### Figure Page 1-2 1-1 . . . 1-2 System Block Diagram 1-2 1-3 1-3 Logic Overview . . . . . 1-4 Processor Interface . . . 1-4 . . . . . . . . . . . . . . . . . . . . . . . . .

v

Page

# LIST OF ILLUSTRATIONS (Cont)

### Figure

### Page

Page

| 1.5  | Maintenance Block                                    |

|------|------------------------------------------------------|

| 1-5  |                                                      |

| 1-6  | OP and VARIANT Reg, Unit Reg/Counter                 |

| 1-7  | Address Decoder                                      |

| 1-8  | Address Counter, Register and EPC Generator          |

| 1-9  | Auxiliary Address Logic and Address Compare Register |

| 1-10 | PSP Buffers and Register                             |

| 1-11 | Fire Code Logic                                      |

| 1-12 | Main Serial Multiplexer                              |

| 1-13 | Main Clock and Data Sync Logic                       |

| 1-14 | Sync Char Logic                                      |

| 1-15 | CM Logic                                             |

| 1-16 | DM Logic                                             |

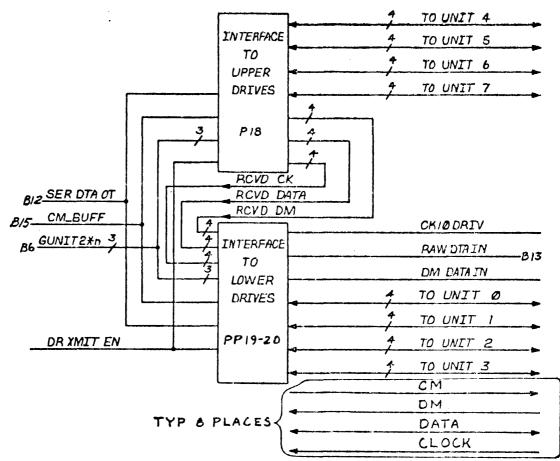

| 1-17 | Drive Interface                                      |

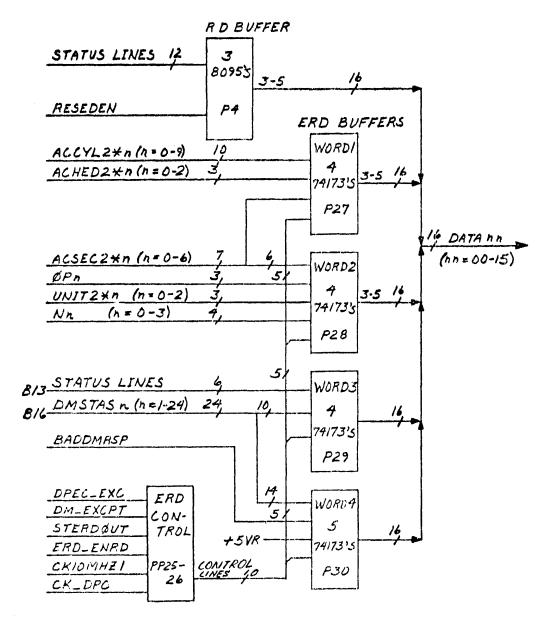

| 1-18 | RD and ERD Logic                                     |

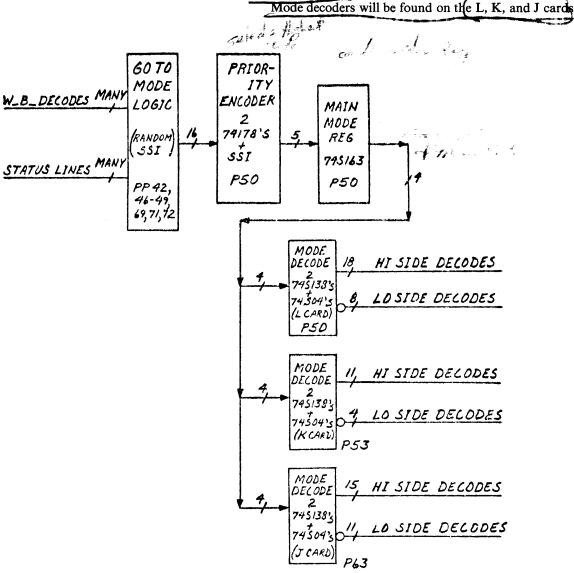

| 1-19 | Main Mode Logic                                      |

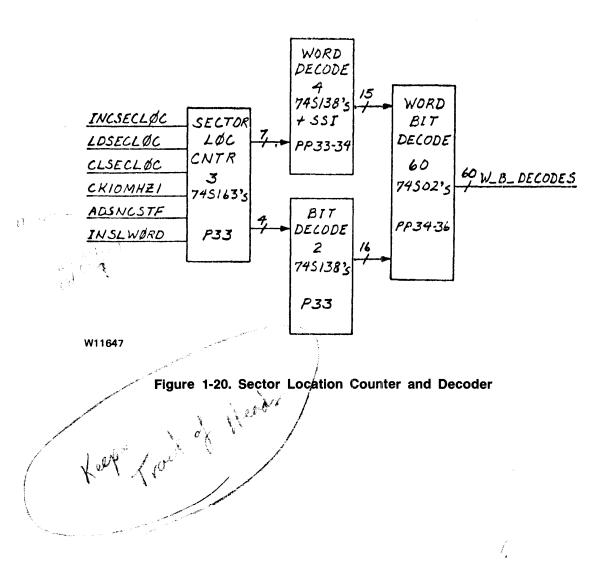

| 1-20 | Sector Location Counter and Decoder                  |

| 1-21 | Seek Status Logic                                    |

| 1-22 | Timer Logic                                          |

| 1-23 | Format Control Logic                                 |

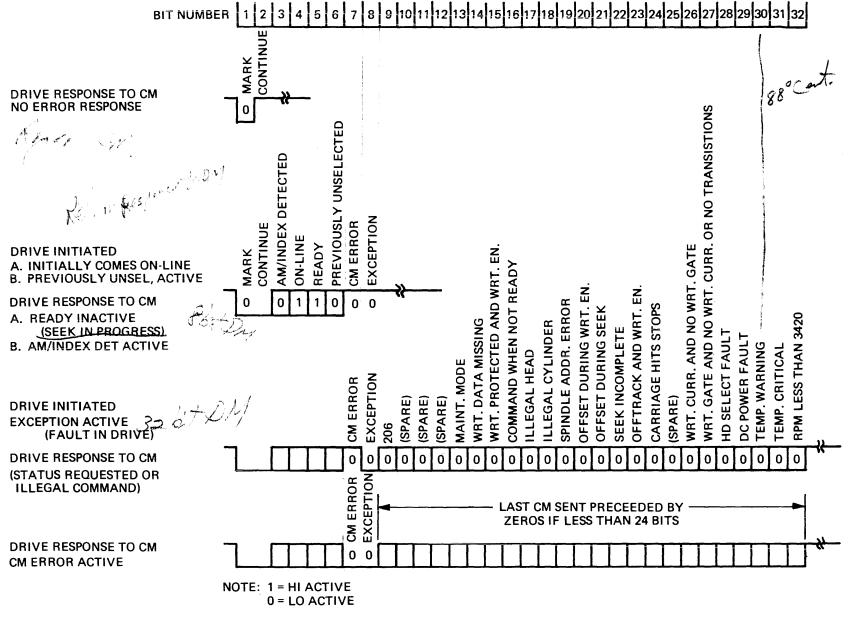

| 1-24 | Controller Message (CM) to Drive                     |

| 1-25 | Drive Message (DM) From Drive                        |

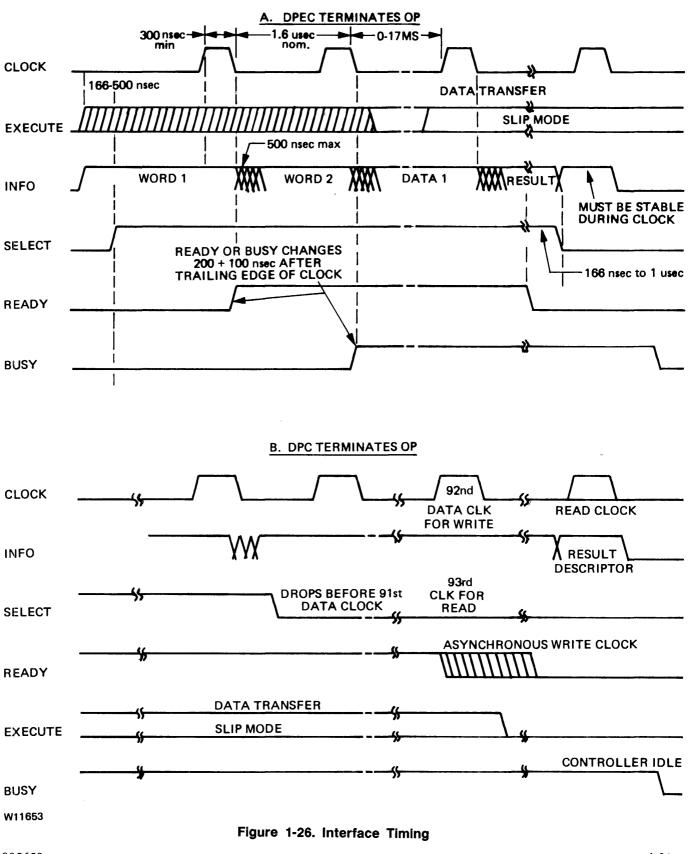

| 1-26 | Interface Timing                                     |

| 2-1  | Power Supply Schematic                               |

| 2-2  | Internal Power Supply Schematic                      |

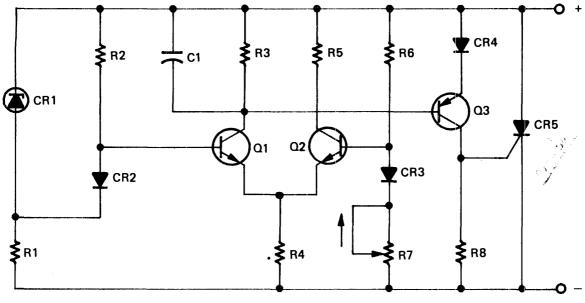

| 2-3  | Overvoltage Protection Schematic                     |

|      |                                                      |

# LIST OF TABLES

## Table

| 1-1 | Controller Message Bits        | 23 |

|-----|--------------------------------|----|

| 1-2 | 206 DPEC Control Messages      | 25 |

| 1-3 | Drive Message Bits             | 27 |

| 1-4 | SELECT, READY, and BUSY Status | 30 |

## **1. BASIC PRINCIPLES**

### INTRODUCTION

This manual provides reference documentation which describes the normal operation, sequences, and circuitry of the model 206 Disk Pack Electronic Controller (DPEC). The following is a list of related literature:

> Model 206 Disk Pack Electronic Controller Function and Operation, form number 1084365.

> Model 206 DPEC Illustrated Parts Catalog, form number 1104189.

Model 206 DPEC Test and Field Documentation.

Model 206 Disk Pack Drive Function and Operation, form number 1084324.

Model 206 Disk Pack Drive Theory of Operation, form number 1084332.

### **GENERAL DESCRIPTION**

The 206 DPEC is a hard-wired controller that includes all the hardware for synchronizing the interfaces between the B 1700 Disk Pack Control (DPC) and the 206 Disk Pack Drive (DPD).

The controller is designed for a maximum configuration of one by eight spindles of disk pack drives. All DPEC's are capable of one by eight operation with no modifications. Standard 25-wire interface (parallel) is used between the DPC (host system) and the DPEC.

The DPEC acts upon I/O instructions from the B 1700 host system, performs the operation specified by the I/O descriptor and, upon completion, generates a result descriptor containing the operation completed and any error status information.

### **BLOCK DIAGRAMS**

The following paragraphs and figures describe and illustrate the block diagrams of the sections of the DPEC. Figure 1-1 contains an introduction to the block diagram legend and an index.

### NOTE

In the following discussions both TRUE and FALSE, as well as LOW and HIGH, are being used. Because of the logic symbology used with the DPEC, a LOW level signal (approximately 0.0 volt) must not be considered as being either a TRUE or FALSE level unless the source of the signal is known.

When referring to the schematic diagrams, any time a signal name is followed by a slash, the active level of that signal will be a LOW. If the signal name has no slash, it is to be considered a HIGH active signal.

When using the block diagrams, it must be remembered that "signals are shown HIGH active regardless of their actual sense" (state). If the actual sense of the signal is required, refer to the schematics in the test and field documents.

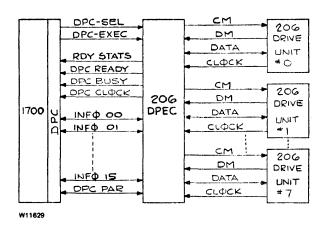

### SYSTEM BLOCK DIAGRAM

Figure 1-2, block diagram B2, is the B 1700, 206 DPEC, and 206 disk pack drive interface.

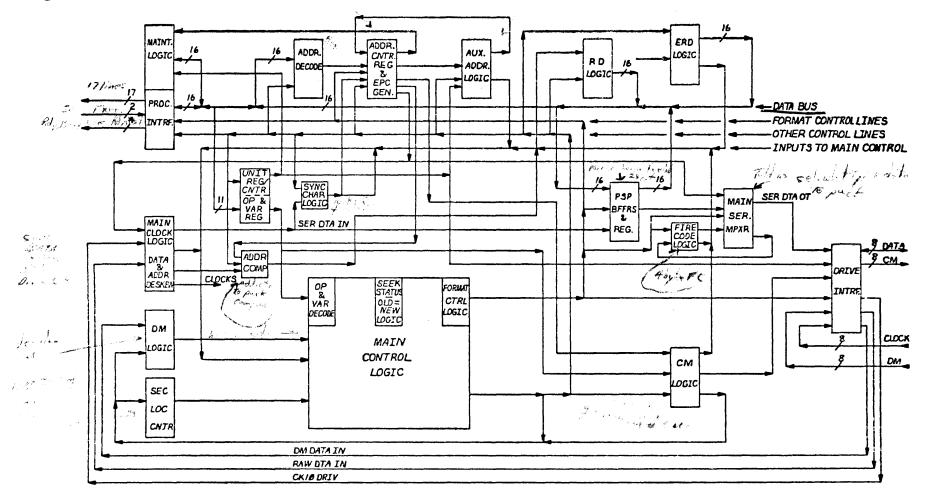

### LOGIC OVERVIEW

Figure 1-3, block diagram B3, is an overall view of the DPEC logic. The individual blocks contained in this diagram will be discussed in the following paragraphs.

|    | DEV. |

|----|------|

| IN | DEX  |

| PAGE NO.                                                                         | TITLE OF BLOCK DIAGRAM                                                                                                                                                                                                                                                                                 |

|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PAGE NO.<br>B1<br>B2<br>B3<br>B4<br>B5<br>B6<br>B7<br>B8<br>B9<br>B10<br>B11     | INDEX AND NOTES<br>1700-DPEC-206 DRIVE SYSTEM<br>206 DPEC OVERALL DIAGRAM<br>PROCESSOR INTERFACE<br>MAINTENANCE BLOCK<br>OP, VARIANT, UNIT REGISTERS<br>ADDRESS DECUDER<br>ADDR CNTR, REGISTER, EPC GENERATOR<br>AUXILIARY ADDRESS LOGIC, ADDR COMP REG<br>PSP BUFFERS AND REGISTER<br>FIRE CODE LOGIC |

| B12<br>B13<br>B14<br>B15<br>B16<br>B17<br>B18<br>B19<br>B20<br>B21<br>B22<br>B23 | MAIN SERIAL MPXR<br>MAIN CLOCK-DATA SYNC<br>SYNC CHAR LOGIC<br>CM LOGIC<br>DM LOGIC<br>DRIVE INTERFACE<br>RD AND ERD LOGIC<br>MAIN MODE LOGIC<br>SECTOR LOC CNTR AND DECODE<br>OLD CYL-SEEK STATUS<br>TIMER LOGIC<br>FORMAT CONTROL                                                                    |

### NOTES:

- 1. In this set of block diagrams, signals are almost always shown high active regardless of their actual sense.

- 2. Groups of signals are often shown as a single line with a diagonal cross hatch and a number indicating the number of signals referred to. Signal names are also written in a shorthand form. For example, DA TANN (nn=00-15),16, represents sixteen wires whose names are DA TA 00 through DA TA 15.

- 3. The page numbers written inside blocks (e.g. P39, or P78) refer to the schematic page(s) where this logic block is shown in detail. Occasionally reference is made at the right or left margin to interconnecting block diagram pages (e.g. B1 or B19).

Figure 1-1. Block Diagram Legend and Index

Figure 1-2. System Block Diagram

W11630

B 9499-3 Disk Pack Electronic Controller (Model 206), Vol. 3: Theory of Operation Basic Principles

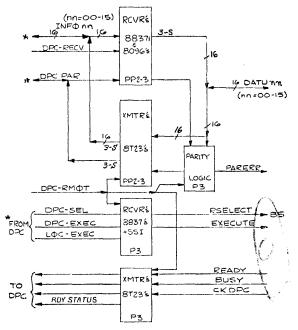

### **PROCESSOR INTERFACE**

This block diagram illustrates the receivers and transmitters used for the actual communication between the DPEC and the DPC (see figure 1-4). The interface lines are parallel lines INFO 00 through INFO 15, DPC PAR, DPC SEL, DPC EXEC, DPC READY, DPC BUSY, RDY STATUS, and DPC CLOCK.

Data coming from the DPC to the DPEC is received by four DM8837 and three DM8096 circuits and used as part of the 16 lines driving a common internal bus. There are eight sources driving this bus. The internal bus lines are designated DATA 00 through DATA 15.

Two 74180 integrated circuits are used to check the parity on the data lines.

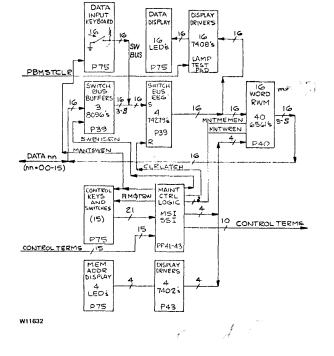

### MAINTENANCE BLOCK

Each DPEC contains maintenance control facilities to simulate a DPC when the DPEC is in a local mode (see

figure 1-5). All local operations on the DPEC are performed using the maintenance control panel mounted on the card in location F. All information is entered using 16 vertical pushbuttons. The switches are used to place information on the switch bus lines through the switch bus register. The display drivers are then used to illuminate the appropriate LEDs on the data display. The outputs from the switch bus register latches are also used as input information to the read/write memory integrated circuits that form the maintenance memory. The maintenance memory has a capacity of 256 bits, and is divided into 16 words of 16 bits each. Four memory address display LEDs and display drivers are used to indicate which one of the 16 maintenance memory words is being accessed.

When the DPEC is in local mode, 15 control switches are enabled. These switches are used to control the maintenance logic. (Refer to the 206 DPEC Function and Operation manual, form number 1084365, section 4.)

W11631

<

e<sup>rt</sup>

1 - y

Figure 1-5. Maintenance Block

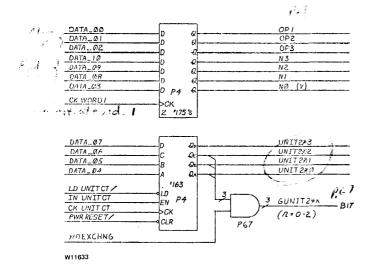

### Figure 1-6. OP and VARIANT Reg, Unit Reg/Counter

### OP AND VARIANT REG, UNIT REG/COUNTER

A series of D-type flip-flops are used to store data bus information for the appropriate OP code and VARIANT information which is available on the bus at clock word 1 time (CK WORD 1) (see figure 1-6).

Unit designation information (UNIT 2\*n) is obtained from the internal data bus lines through a synchronous 4-bit counter. The outputs from the counter are unit designations 0 (FIRST SPINDLE) through unit designation 7 (EIGHTH SPINDLE).

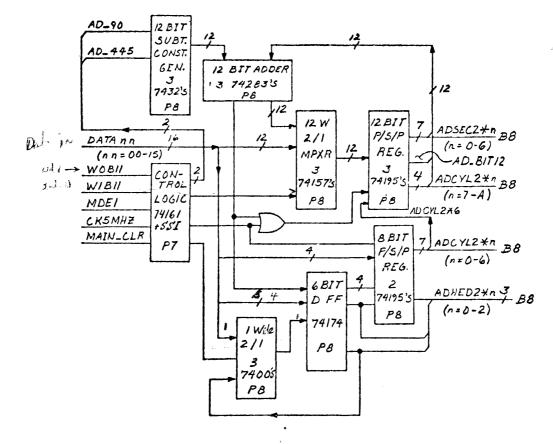

### ADDRESS DECODER

The 16 parallel lines of address data are loaded into three 74157 integrated circuits. The cylinder, head, and sector will be calculated by a division process (see figure 1-7). During the time that the control logic has the AD445 term TRUE, the address decode circuitry will be determining the cylinder address. During the time AD90 is TRUE, the address decode circuitry will be determining the proper head address. Any remainder, after the head division process has been performed, will be the sector number.

The five 74195 registers will provide the final cylinder, head, and sector information as decoded from the input data.

Figure 1-7. Address Decoder

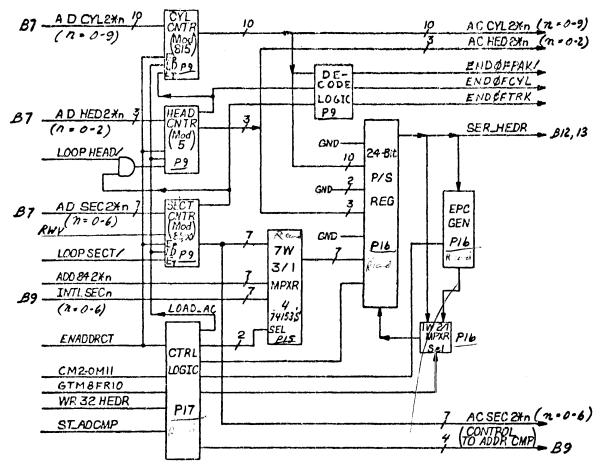

# ADDRESS COUNTER, REGISTER, AND EPC GENERATOR

The address counter is used primarily to isolate the address decoder output logic until it is ready to be used to supply serial header information to other sections of the DPEC (see figure 1-8).

A 24-bit parallel-to-serial register is used to convert the parallel address counter data (AC) to the serial header (SER HEDR) data.  $\rho \neq w dr$  The SER HEDR information is also used as an input to generate the address error protection code (EPC character). When the pack is initialized, the address EPC character will be written at the end of the address portion of each sector.

The seven word, three-to-one multiplexer (consisting of four 75153 integrated circuits) is used to provide the sector interlace that is used on the model 206 disk pack drive.

Figure 1-8. Address Counter, Register and EPC Generator

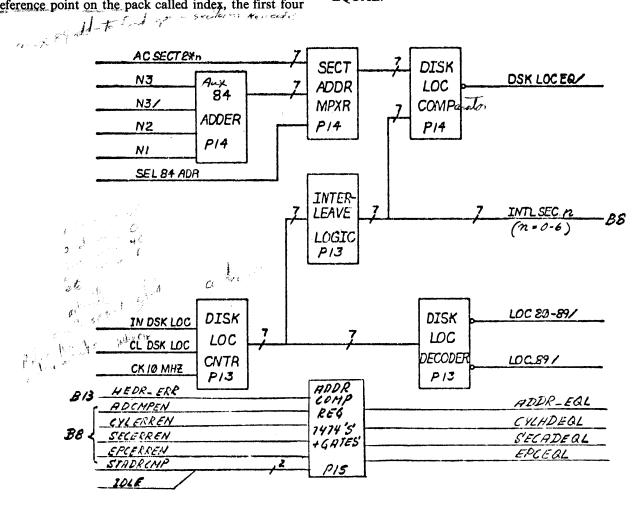

# AUXILIARY ADDRESS LOGIC AND ADDRESS COMPARE REGISTER

The 84-adder is used when addressing a spare sector on any track on head 4 (see figure 1-9). The value of the N variant (1-5) is added to the 84-adder to address the appropriate spare sector.

The sector address multiplexer is used to select either spare sector information (84-adder) or address counter sector information (AC SECT 2\*n). The term SEL 84 ADR will determine which is used.

The output of the disk location counter (DISK LOC CNTR) will be sequential sector information. The IN-TERLEAVE LOGIC will be used primarily during the initialize operation. This logic will be used to provide the proper sequence of sectors required for the interleave pattern that must be written on the disk pack. The model\_ 206 disk pack uses an interlaced format. Beginning at a reference point on the pack called index, the first four sectors will be numbered 45, 0, 46, and 1. The last four sectors, prior to returning to index, will be numbered 88, 43, 89, and 44. (Refer to the 206 DPEC Function and Operation manual, form number 1084365.)

When the desired sector address (AC SEC 2\*n or 84 ADDER) and INTERLEAVE sector number are equal, the term DSK LOC EQ will be TRUE, indicating the desired sector on the pack has been located.

The disk location decoder is used to sample the disk location counter and produce the term LOC 89/ when the final sector count for a particular track is reached. (LOC 80-89/ will be TRUE when the last five sectors are being read. It is a test point, not a logic term.)

The address compare register is a series of four 7474 D flip-flops used to latch conditions of ADDRESS EQUAL, CYLINDER/HEAD EQUAL, SECTOR EQUAL, and EPC (ERROR PROTECTION CODE) EQUAL.

W11636

Figure 1-9. Auxiliary Address Logic and Address Compare Register

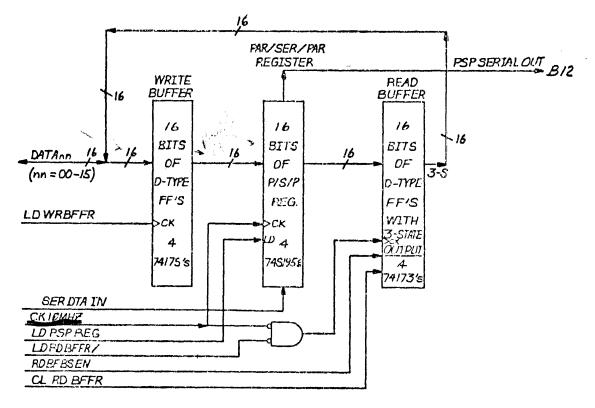

### PSP BUFFERS AND REGISTER

### READ OPERATION

Serial data from the drive (SERDTAIN) is loaded into the 16-bit parallel-serial-parallel register at LDPSPREG time. This information is then available to the read buffer, which consists of four D-type flip-flops. The read buffer is a tri-state output device. The tri-states are high, low, or high impedance. The high impedance state is necessary to isolate the read buffer from the internal bus lines (see figure 1-10).

### WRITE OPERATION

The 16-bit write buffer contains a series of D-type flipflops used to transfer the internal data bus information into the parallel-serial-parallel register. The parallel data input is clocked into the write buffer at LDWRBFFR (load write buffer) time. The serial output from the parallel-serial-parallel register (PSPSEROT) will be clocked by the 10 megahertz clock (CK10MHz).

Figure 1-10. PSP Buffers and Register

# 32bit

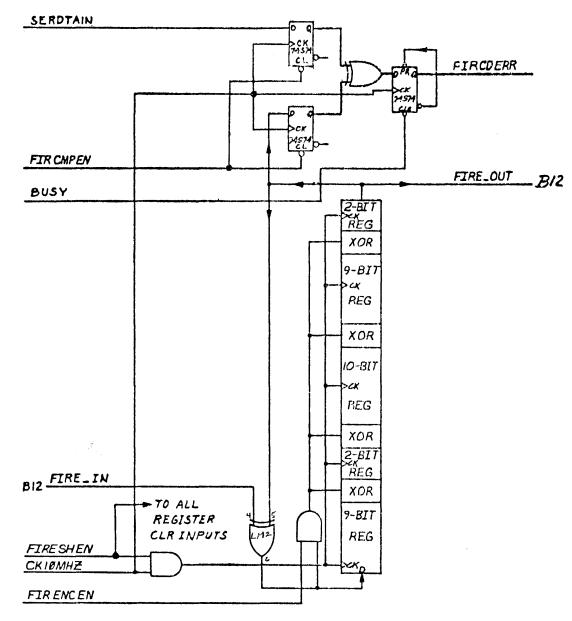

FIRE CODE LOGIC

A series of three 8-bit parallel load shift registers, two quadruple D-type flip-flops, and four exclusive OR circuits form the Fire code generation circuit (see figure 1-11).

Serial data (FIRE IN) is used as the input to the Fire code generator to produce the actual Fire code characters that are written at the end of each sector of data on a pack. Three flip-flops and an exclusive OR are used to check the Fire code that is read from a sector (SRDTDLYD) and it is compared with the FIRE OUT signal from the Fire code generator. If the two signals are the same, no Fire code error exists. If any of the 180 bytes are found to be incorrect, the Fire code characters will not compare, and the term FIRCDERR will be TRUE, indicating a Fire code error has been detected.

Figure 1-11. Fire Code Logic

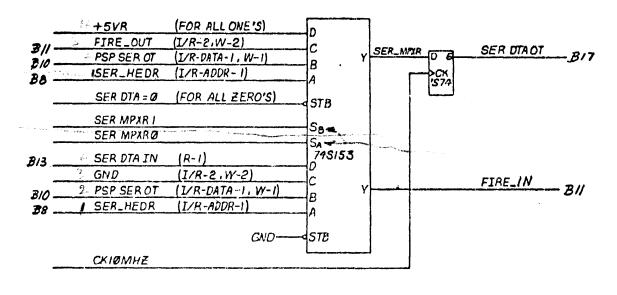

### MAIN SERIAL MULTIPLEXER

The outputs from the main serial multiplexer are FIRE IN and SER DTAOT (see figure 1-12). Depending on the combination of input strobe and select polarities, various input lines will be displayed at the outputs of the multiplexer.

The SER DTAOT output can contain SER HEDR, PSP SEROT, FIRE OUT, or an all "1's" pattern. The term SER DTA=0 is required as a strobe to obtain an output. The combination of SERMPXR0 and SERMPXR1 will determine which one of the inputs will be seen at the output. When SER DTA=0 is LOW, and both SERMPXR0 and SERMPXR1 are LOW, the SERDTAOT will contain SER HEDR information. When SERMPXR0 is HIGH and SERMPXR1 is LOW, PSPSEROT will be seen at the output. When both SERMPXR0 and SERMPXR1 are HIGH, all "1's" will be seen at the output because +5VR is applied to the 1C-3 input at RS0-3. The 10 megahertz clock is used to clock the SER DTAOT.

The FIRE IN output can contain SER HEDR, PSP SEROT, all "0's" or SRDTDLYD. The SERMPXR0 and SERMPXR1 terms will be used to select the inputs that will be used.

**DEFINITIONS:**

1. -1 REFERS TO THE 180-BYTE DATA FIELD TIME.

2. -2 REFERS TO THE 4-BYTE FIRE CODE TIME.

3. R\_REFERS TO READ AND VERIFY OPS.

4. W\_REFERS TO WRITE OP.

5. I/R - INITIALIZE AND RELOCATE OPS.

6. DATA AND ADDR SPECIFY WHAT IS TO BE WRITTEN.

Figure 1-12. Main Serial Multiplexer

### MAIN CLOCK AND DATA SYNC LOGIC

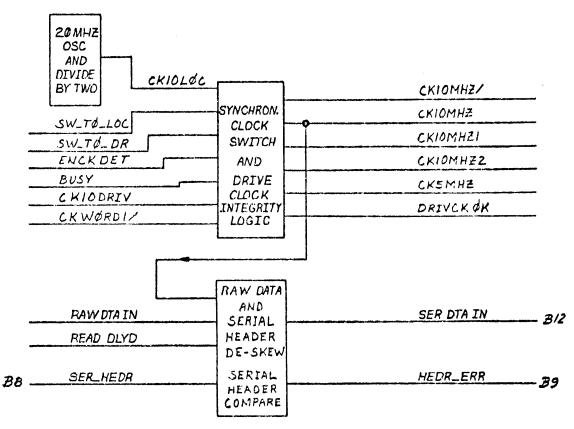

The basic clock frequency generated in the DPEC is 20 megahertz. This frequency is then divided by 2 to produce a symmetrical 10 megahertz clock (see figure 1-13).

The drive clock integrity logic is used to ensure that the 10 megahertz clock from the disk pack drive is within nominal tolerances. The terms DRIVCKOK and DRIV-CKOK/will be monitored to verify that this condition is maintained.

Three pairs of matched 7440 buffers are used to distribute the 10 megahertz DPEC clock throughout the DPEC. Three 74S74 flip-flops and an exclusive OR are used to deskew the serial header compare information.

RAWDTAIN (data from the disk pack drive) is clocked and compared to clocked SER HEDR information by the 74S86 exclusive OR. If both RAWDTAIN and SER HEDR are in sequence, the term HDR ERR (header error) will be LOW, indicating that no error condition exists.

After being processed by two 74S74 flip-flops, RAWD-TAIN becomes SERDTAIN. This processing is performed to eliminate any noise spikes on the data lines.

Figure 1-13. Main Clock and Data Sync Logic

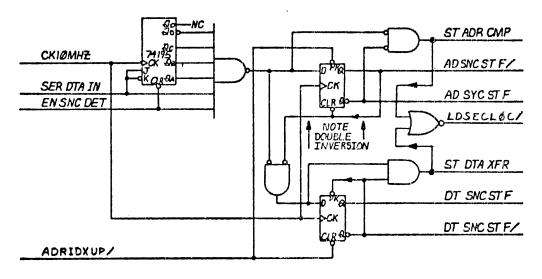

### SYNC CHAR LOGIC

A 74195 shift register integrated circuit is used to detect the 4-bit character preceding the address header (see figure 1-14). SERDTAIN is used as the JK input to the shift register and is clocked by the 10 megahertz clock. The term ENSNCDET (enable sync detect) will also be required to enable this circuit. Immediately after this condition takes place, STADRCMP (start address compare) will be TRUE. On the following clock pulse, AD-SNCSTF will be TRUE, indicating that the address sync start flip-flop has been reset. (The note on the schematics and block diagrams "NOTE DOUBLE INVERSION"

refers to the use of the reset state of a flip-flop, indicating a TRUE condition. A LOW TRUE into the flip-flop produces a LOW TRUE output from the set side of the flip-flop.)

The second time a 4-bit sync character is detected, the DTSNCSTF flip-flop will be set, indicating that the data sync character has been detected. STDAXFR will also go TRUE at this time, indicating the start of data transfer.

The term LDSECLOC/(load sector location counter, LOW TRUE) will be generated at the start address compare time.

W11641

ŝ.

Figure 1-14. Sync Char Logic

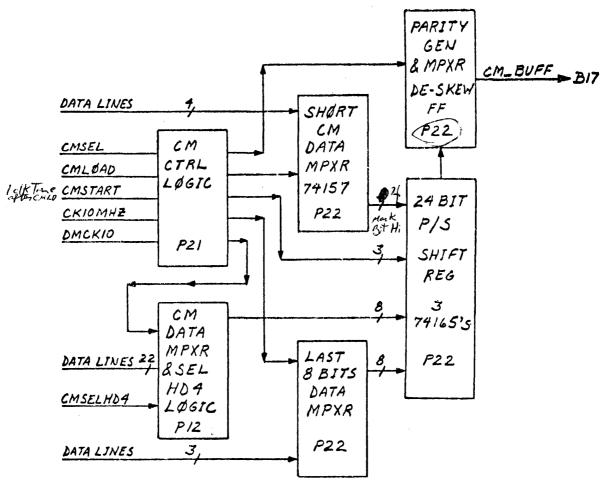

### CM LOGIC

The controller message (CM) data multiplexer and selectors (four 74153 integrated circuits) are used to select ACHED, ACCYL, PLO, and UNIT terms to produce eight CML lines (09-16). These eight lines will furnish one-third of the inputs to the 24-bit parallel-to-serial shift register (see figure 1-15).

The terms CM R/W/ (read), CM R/W (write), and CM ADD M/ (address mark) are used as inputs to the SHORT CM DATA multiplexer. These terms plus CMODE 01 and OFFSETEN will be used as inputs to the 74165 shift register to produce the first eight bits of the CM message.

The outputs from the CM data multiplexer (CML09-CML16) are used as inputs to the second eight bits of the 24-bit shift register.

The final eight bits of the CM message will be obtained from the last 8-bits data multiplexer. These bits will contain the high-order address counter cylinder information and enable write data.

The three shift registers are in series, and their output is used as the D input to the CM parity generator.

The CM BUF output is obtained from the deskew flipflop. The D input to this flip-flop is either CM SEL, the 24-bit shift register output, or the parity generator output.

Figure 1-15. CM Logic

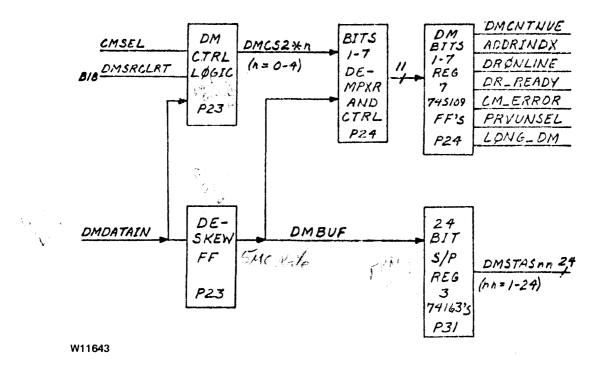

DM LOGIC

The 206 disk pack drive communicates with the 206 DPEC by sending a serial drive message (DM). A DM can only be sent while the controller has the drive selected (CM is HIGH). Unless this condition is met, the drive status is stacked in an unselected drive and sent when the drive is selected (see figure 1-16).

The eight DM lines coming from the maximum of eight 206 spindles are gated by the unit designation level on one of two drive interface cards. The term DMDA- TAIN is sent to the DM control logic and the deskew flip-flop network.

The deskew flip-flop produces terms called DMBUF and DMBUF/ that are at a 5 megahertz rate. These two terms will be used to gate the first seven bits of DM data and to gate the 24-bit serial-to-parallel register.

The first seven bits of the DM are stored in seven 74S109 JK flip-flops that are clocked by the term DM CLK.

The remaining 24 bits of the DM are obtained from three 74164 serial-to-parallel registers.

Figure 1-16. DM Logic

### DRIVE INTERFACE

Two interface cards are used to accommodate the eight spindles that can be used with the 206 DPEC. The S card is the drive-to-DPEC interface for spindles 0 through 3 and the R card, the interface between spindles 4 through 7 and the DPEC (see figure 1-17).

Four 75107 receiver integrated circuits are used on each card to receive the positive and negative data and clock information from the respective spindles. The data outputs from the receivers are used as inputs to a 74S51 multiplexer to produce RAWDTAIN. The clock outputs from the receivers are used as inputs to 74S151 multiplexers to produce the CK10DRV output, which is the 10 megahertz clock from the drive.

The GUNIT terms (2\*0 through 2\*2) are used to gate both the clock and data multiplexers.

DM data from the eight possible spindles is sent to four 8T24 receiver integrated circuits on the two interface cards. The outputs are the DRnDM terms, where n represents the drive number, from 0 through 7. All the DRnDM terms are used as inputs to a 74S251 multiplexer that uses the GUNIT terms to select the desired input. The output from the multiplexer is DMDATAIN.

Figure 1-17. Drive Interface

### RD AND ERD LOGIC

Three 8095 tri-state buffer integrated circuits are used to accept the 12 result descriptor (RD) status lines. The term RESDESEN/ (result descriptor enable) is used to enable the buffers. The outputs from these buffers are

used as inputs to the internal DPEC data bus lines (see figure 1-18).

Seventeen 74173 D-type registers are used to store the 64 bits of ERD (extended result descriptor) information.

The terms ERDFFB/ and ERDFFC/ are used for output controls of the register, and ERD XFEREN/ and STOBAD/ are used as the data and enable inputs.

Figure 1-18. RD and ERD Logic

### MAIN MODE LOGIC

The function of the "go to mode logic" is to generate a series of terms that will have a GOTOMDEn (where n is any mode from 1 to 15) format (see figure 1-19). Refer to figure 3-2 in the DPEC Function and Operation manual, form number 1084365, for additional information. The priority encoder block includes two 74148 integrated circuits that form a 16-bit to 6-bit decoder.

The mode decoders consist of a pair of 74S138 3-to-8 decoders and several 74S04 inverters. The output from the mode decoders will be the actual mode lines <u>MDE0</u> through MD15.

Figure 1-19. Main Mode Logic

### SECTOR LOCATION COUNTER AND DECODER

The sector location counter is composed of three 74S163 counters (see figure 1-20).

The terms ADSNCSTF/ and ADSNCSTF (from the sync start logic) will be used to force word 5, bit 4 and

word 17, bit 0 values into the counter. The first term will be TRUE at address sync time (W5B4), and the second term will be TRUE at data sync time (W17B0).

Two of the 74S163 integrated circuits are used to generate the word terms, and the third is used to generate the bit terms.

muchos seen No ----

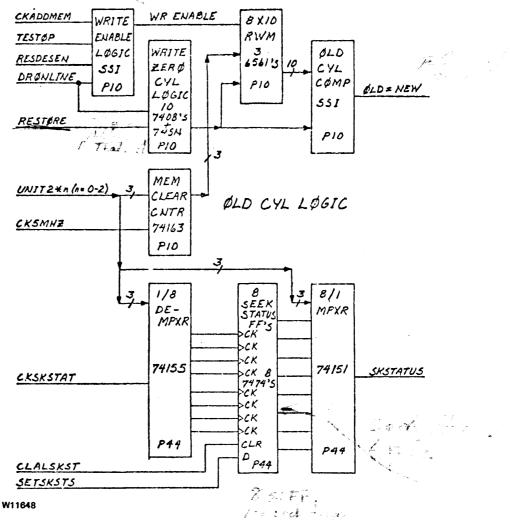

### SEEK STATUS LOGIC

The basic function of the seek status logic is to prevent the system from accessing a spindle that has not performed a data transfer. Once a seek operation has been initiated, the overlapping seek function allows the DPEC to satisfy other DPC service requests and not wait for the first seek operation to be completed (see figure 1-21).

When the seek status flip-flop is set for one spindle, the DPEC will not allow the DPC to address any other cylinder on that spindle until a data transfer has taken place. If the term old = new/is LOW (TRUE), the operation is completed. If the term old = new/ is HIGH (FALSE), the operation is not performed and a positioner not settled result descriptor is reported.

The write enable logic is used to allow writing address information into the 6561 memory integrated circuits.

The memory integrated circuits are used to store the old cylinder address. Eight exclusive OR circuits are used to compare the old cylinder address to the new cylinder address.

The write zero cylinder logic is used to clear, or set the memory integrated circuits to all "0's". This will be done at PWRRSYNC time, at RESTORE time, or if DRONLINE goes FALSE.

The memory clear counter (74163) is part of the write zero cylinder logic.

The 1-to-8 demultiplexer is used to furnish a clock pulse to the appropriate seek status flip-flop. At SE-TSKSTS time, all eight seek status flip-flops will have a TRUE at their D inputs. However, only the flip-flop that receives a clock pulse will be set.

Any time a unit is selected, the 8-to-1 multiplexer is interrogated to determine if the seek status flip-flop is set for that unit.

Figure 1-21. Seek Status Logic

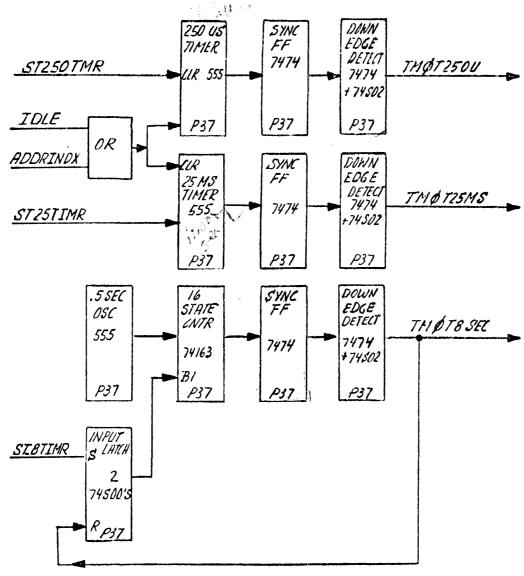

g t 5 Times 5 inD TIMER LOGIC

The timer logic consists of three timer circuits (see figure 1-22). A 250 microsecond timer is used to detect the absence of address marks. A 25 millisecond timer is used to detect the absence of index marks. If either of these timers is allowed to time out, a fault condition exists. An 8-second timer is used during the power-on sequence, to ensure that not more than one spindle is allowed to power on at a time.

The three timer circuits consist of a basic timer or oscillator, a synchronous flip-flop, and a down edge detect flip-flop.

Figure 1-22. Timer Logic

B 9499-3 Disk Pack Electronic Controller (Model 206), Vol. 3: Theory of Operation Basic Principles

Controls Alldata. flow in DPEC

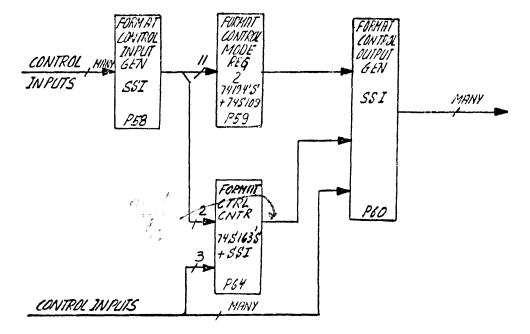

### FORMAT CONTROL LOGIC

The format control input generator consists of a series of gates that convert mode and word/bit terms into format terms (see figure 1-23).

The format control mode registers are used to process the format terms that will be used by the data stream control logic.

The format control counter uses the FMWRONES/ term as a load term. The primary functions of the counter are to furnish the RAWCKDPC (raw clock to the DPC) and to load the read buffer in the parallel-serial-parallel register.

The format control output generator is used to convert mode and write terms to CM mode terms that will be used by the CM control logic.

Refer to figure 1-5 in the 206 DPEC Function and Operation manual, form number 1084365, for the illustration of the track format used with the 206 DPEC and the 206 disk pack drive.

W11650

Figure 1-23. Format Control Logic

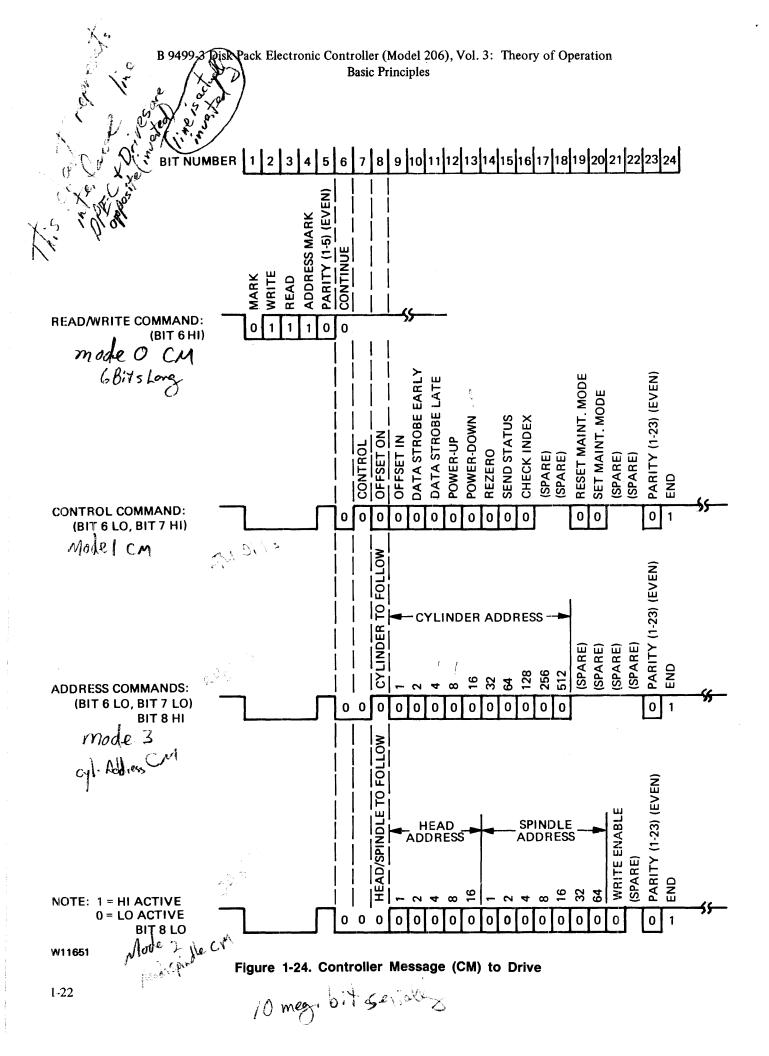

# Control and bit times uerde 2 werd and bit times CM MESSAGE

The controller message (CM) is used to allow the controller to select a drive, power on or power off the drive, position the head carriage to the proper cylinder, select a head, perform a read or write operation, make head offset and data strobe adjustments, and receive drive status. Figure 1-24 illustrates the controller messages, and table 1-1 lists the definitions of the CM bits.

The CM is either 6 bits or 24 bits long. The mark bit (bit 1) being LOW indicates the beginning of a message. The write, read, and address mark bits are HIGH active. The parity and continue bits are LOW active. The remaining bits in a 24-bit message are also LOW active.

a. 6-bit message. A read or write command has the continue bit (bit 6) set HIGH (inactive). When

this bit is HIGH, no further message is to follow.

b. 24-bit message. When the continue bit is LOW (active), the CM will contain 24 bits. If bit 7 is LOW (active), the message is an address command. If bit 7 is HIGH (inactive), the message is a control command. Bit 8 is used to describe the information that will follow. Each bit has a period of two clock pulses.

Table 1-2 contains the bit configurations for the various CM messages within the DPEC.

Column 1 contains the CM number, column 2 the CM message name, and the output bit configuration is shown in column 3. The legend at the bottom of the table lists the active state of the bits used. Unless otherwise stated, the bits shown in table 1-2 are LOW active levels.

### B 9499-3 Disk Pack Electronic Controller (Model 206), Vol. 3: Theory of Operation Basic Principles

# Invested

## Table 1-1. Controller Message Bits

| Bit | Name                 | Function                                                                                                                                                                                         | Bit | Name                | Function                                                                                                                         |

|-----|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------|----------------------------------------------------------------------------------------------------------------------------------|

| 1   | Mark<br>Write        | When LOW, indicates the beginning<br>of a message.<br>When HIGH, indicates a write mode.                                                                                                         | 11  | Data Strobe<br>Late | When LOW, indicates read data is<br>detected using the early strobe. Used<br>to recover data errors. Action starts<br>at bit 24. |

|     |                      | Write starts if no errors were detected<br>when bit 6 is received and write<br>enable (bit 21) is previously set.<br>When LOW, write stops immediately.                                          | 12  | Power On            | When LOW, initiates a drive power on.<br>Action starts at bit 24.                                                                |

| 3   | Read                 | When HIGH, indicates a read mode.<br>Read starts if no errors were detected                                                                                                                      | 13  | Power Off           | When LOW, initiates a drive to power off. Action starts at bit 24.                                                               |

| Λ   | Address Mark         | when bit 6 is received.                                                                                                                                                                          | 14  | Rezero              | When LOW, initiates a head retraction<br>into the outer guard band, on the pack                                                  |

| 4   | Audress Mark         | When HIGH, indicates a search for<br>address mark (AM) if in read mode or<br>write AM if in the write mode.                                                                                      |     |                     | and forward to cylinder zero. Action starts at bit 24.                                                                           |

|     |                      | Action starts if no errors are detected<br>when bit 6 is received. Search for<br>AM is reset by AM detection. Write<br>AM is reset after writing three bytes                                     | 15  | Send Status         | When LOW, sets the drive exception<br>bit and initiates a 32-bit status drive<br>message (DM). Action starts at bit 24.          |

| 5   | Duriter              | of no flux transitions.                                                                                                                                                                          | 16  | Check Index         | When LOW, specifies a drive message<br>will be sent at the next index mark                                                       |

| 3   | Parity               | Provides an even number of LOW<br>states for bits 1 through 4. If a par-<br>ity error exists, operations indicated<br>by the previous bits are processed.<br>An 8-bit DM with bit 6 active (par- |     |                     | detection. Index is not normally<br>reported. Any drive error will stop<br>the index mark search. Action starts<br>at bit 24.    |

|     |                      | ity error) is generated.                                                                                                                                                                         | 17  | Spare               |                                                                                                                                  |

| 6   | Continue             | When LOW, indicates the message continues and the CM is 24 bits long.                                                                                                                            | 18  | Spare               |                                                                                                                                  |

|     |                      | If LOW in a read or write mode, an<br>error exists, causing the operation to<br>be terminated and generates a DM<br>error message.                                                               | 19  | Reset<br>Maint Mode | When LOW, the maintenance mode is reset.                                                                                         |

| 7   | Control              | When HIGH, indicates bits 8 through 24 are control bits. When LOW, the state of bit 8 determines the defini-                                                                                     | 20  | Set<br>Maint Mode   | When LOW, the maintenance mode is set.                                                                                           |

|     |                      | tion of bits 9 through 24.                                                                                                                                                                       | 21  | Spare               |                                                                                                                                  |

|     | ]                    | NOTE                                                                                                                                                                                             | 22  | Spare               |                                                                                                                                  |

|     |                      | IIGH, the following<br>ly to bits 8 through 24.                                                                                                                                                  | 23  | Parity              | Provides an even number of LOW states for bits 1 through 23.                                                                     |

| 8   | Offset On            | When LOW, indicates the head is to<br>be offset during a read mode. The<br>state of bit 9 will determine the direc-<br>tion of the offset.                                                       | 24  | End                 | End of message. It must be HIGH.<br>If LOW, the operations specified by<br>the previous bits will not start.                     |

| 9   | Offset In            | When LOW, indicates the offset is in toward the spindle. Action starts at bit 24.                                                                                                                |     | HIGH, the fo        | NOTE<br>LOW, and bit 8 is<br>llowing definitions<br>8 through 24.                                                                |

| 10  | Data Strobe<br>Early | When LOW, indicates read data is<br>detected using the early strobe. Used<br>to recover data errors. Action starts<br>at bit 24.                                                                 | 8   |                     | When HIGH, indicates that the cylinder address will follow.                                                                      |

| Bit   | Name                         | Function                                                     | Bit                                                                     | Name         | Function                                                 |  |  |

|-------|------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------|--------------|----------------------------------------------------------|--|--|

| 9-18  | Cylinder Address information |                                                              | NOTE                                                                    |              |                                                          |  |  |

| 19-22 | Spare                        |                                                              | When bit 7 and bit 8 are LOW, the following definitions apply to bits 8 |              |                                                          |  |  |

| 23    | Parity                       | Provides an even number of LOW states for bits 1 through 22. |                                                                         | through 24.  |                                                          |  |  |

| 24    | End                          | Same as above.                                               | 8                                                                       | Address Flag | When LOW, indicates head or spindle address will follow. |  |  |

|       |                              |                                                              | 9-13                                                                    | Address      | Head address, LSB to MSB.                                |  |  |

|       |                              |                                                              | 14-20                                                                   | Address      | Spindle address, LSB to MSB.                             |  |  |

|       |                              |                                                              | 21                                                                      | Write Status | When LOW, sets write enable.                             |  |  |

## Table 1-1. Controller Message Bits (Cont)

B 9499-3 Disk Pack Electronic Controller (Model 206), Vol. 3: Theory of Operation Basic Principles fore interface operative from other chart in DPEC

## Table 1-2. 206 DPEC Control Messages

| CM N-         | Nama                              | state                      | Outnut B   | 10                        |   |              | Innuto |    |               |

|---------------|-----------------------------------|----------------------------|------------|---------------------------|---|--------------|--------|----|---------------|

| CM No.        | Name <sub>I</sub> D <sup>je</sup> |                            | Output B   |                           |   |              | Inputs |    | <b>B</b> GINI |

|               |                                   | 0 1234 56<br>Mwra Pe       |            | 3456 7892 1234<br>PE      | М | RAE          | DIEL   | UD | RSIW          |

| СМ #1-0       | NO OFFSET/PLO                     |                            |            | LLLL LLLL LLHL            | 1 | XHH          | LLLL   | LL | LLLL          |

| CM #1-1       | OFFSET/PLO                        |                            |            | LLLL LLLL LL*L            | 1 | ХНН          | ****   | LL | LLLL          |

| CM #1-2       | POWER UP                          |                            |            | LLLL LLLL LLLL            | 1 | ХНН          | LLLL   | HL | LLLL          |

| СМ #1-3       | POWER DOWN                        |                            |            | HLLL LLLL LLLL            | 1 | хнн          | LLLL   | LH | LLLL          |

| СМ #1-4       | RESTORE-SEND STTS                 | L HHHH LH                  | ILL LLLL I | LHHL LLLL LLLL            | 1 | хнн          | LLLL   | LL | HHLL          |

| СМ #1-5       | SEND STATUS                       | L HHHH LH                  | ILL LLLL I | LHL LLLL LLLL             | 1 | ХНН          | LLLL   | LL | LHLL          |

| СМ #1-6       | FIND INDEX MARK                   | L HHHH LH                  | ILL LLLL I | LLLH LLLL LLLL            | 1 | ХНН          | LLLL   | LL | LLHL          |

| СМ #2-0       | WR EN HEAD SPNDL                  | L НННН LH                  | IHH        | HL*L                      | 2 | ХНН          | LLLL   | LL | LLLH          |

| СМ #2-1       | HEAD SPINDLE ONLY                 | L HHHH LH                  | IHH        | LL*L                      | 2 | ХНН          | LLLL   | LL | LLLL          |

| СМ #З         | CYLINDER                          | L НННН LH                  | IHL        | LL LL*L                   | 3 | ХНН          | LLLL   | LL | LLLL          |

| CM #4         | READ DATA                         | L HHLH HL                  |            |                           | 0 | ннн          | LLLL   | LL | LLLL          |

| СМ <b>#</b> 5 | WRITE DATA                        | L HLHH HL                  |            |                           | 0 | LHH          | LLLL   | LL | LLLL          |

| СМ #6         | READ ADDR MARK                    | L HHLL LL                  |            |                           | 0 | HLH          | LLLL   | LL | LLLL          |

| СМ #7         | WRITE ADDR MARK                   | L HLHL LL                  |            |                           | 0 | LLH          | LLLL   | LL | LLLL          |

| CM #8         | GO IDLE                           | L HHHH LL                  |            |                           | 0 | XHL          | LLLL   | LL | LLLL          |

| СМ #9         | SELECT DRIVE                      | HHHH HLLL LL               |            |                           |   | CM SE        | L =    | HI |               |

| СМ #10        | DE-SELECT DRIVE                   | L НННН НН                  |            |                           |   | CM SE        |        | LO |               |

|               |                                   |                            |            |                           |   |              |        |    |               |

|               | EGEND                             |                            |            |                           |   |              |        |    |               |

|               | INPUTS: M = MODE                  | 0 = SHORT C<br>2 = HEAD CM |            | CONTROL CM<br>CYLINDER CM |   | CMODE        |        |    |               |

|               |                                   | z - HEAD CM                | 4. 5 -     | CILINDER CM               |   | CMODE        | 52*1   |    |               |

|               | R = READ                          | (READ=H, WR                | RITE=L)    |                           |   | CM_R/V       | W/     |    |               |

|               | A = ADDRI                         | ESS MARK                   | – LO       | ACTIVE                    |   | CM_AD        | DD M/  |    |               |

|               | E = GO ID                         | LE CM                      | – LO       | ACTIVE                    |   | CMGO         | IDLE/  |    |               |

|               | O = OFFSE                         | T ON                       | – HI       | ACTIVE                    |   | OFFSE'       | TON    |    |               |

|               | I = OFFSE                         | T IN                       | ~ HI       | ACTIVE                    |   | <b>OFFSE</b> | TIN    |    |               |

|               | E = PLO E                         | ARLY                       | – HI       | ACTIVE                    |   | PLOEA        | RLY    |    |               |

|               | L = PLO LA                        | ATE                        | – HI       | ACTIVE                    |   | PLO_L        | ATE    |    |               |

|               | U = POWEF                         | R UP                       | – HI       | ACTIVE                    |   | POWER        | LUP    |    |               |

|               | D = POWER                         | R DOWN                     | – HI       | ACTIVE                    |   | POWER        | _DN    |    |               |

|               | R = RESTO                         | RE                         | – HI       | ACTIVE                    |   | RESTO        | RE     |    |               |

|               | S = SEND                          | STATUS                     | – HI       | ACTIVE                    |   | SEND         | STS    |    |               |

|               | I = FIND                          | INDEX MARK                 | – HI       | ACTIVE                    |   | INDXS        | RCH    |    |               |

| •             | W = REQUI                         | EST WRITE ENABI            | LE HI      | ACTIVE                    |   | ENABL        | WR     |    |               |

1-26

### DM MESSAGE

The drive communicates with the DPEC by sending a serial drive message (DM). The DM can be sent only while the DPEC has the drive selected (CM is HIGH). The drive status is stacked with an unselected drive and sent with a selected drive. The DM message can be 1 bit, 8 bits, or 32 bits in length. Each bit has a period of two clock pulses. Figure 1-25 illustrates the drive messages. (Refer to table 1-3 for bit functions.)

- a.1-bit DM. The 1-bit DM consists of only a mark bit. For each CM sent by the DPEC, the drive should respond with the 1-bit DM, if no errors exist.

- b.8-bit DM. If the drive is not selected, an 8-bit DM is stacked in the drive when the drive initially is placed on-line. When selected, the drive sends an 8-bit DM indicating on-line, ready, and previously unselected. If the CM is held LOW, the drive is deselected and the drive status is stacked. When again selected, the drive sends an 8-bit DM indicating on-line, ready, and previously unselected.

An 8-bit DM is also sent in response to a CM. When a CM commands a seek to a new cylinder, the drive responds immediately with an 8-bit DM, with ready inactive, and starts the seek. When the seek has been successfully completed, the drive responds with a 1-bit DM.

| Bit | Name                     | Function                                                                                                                                                                                                                  | Bit   | Name                  | Function                                                                                                                                                                                                                    |

|-----|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Mark                     | When LOW, indicates beginning of the message. A no error response to a CM consists of bit 1 LOW and bit 2 HIGH.                                                                                                           | 7     | CM Error              | When LOW, indicates an input error<br>(parity error or control bit conflicts)<br>other than the one specified by bit 6.<br>Presence of this bit will initiate the<br>generation of a drive message. When                    |

| 2   | Continue                 | When HIGH, indicates that the last<br>controller message was received<br>correctly, the drive is READY, and<br>there is no EXCEPTION.                                                                                     |       |                       | this bit is LOW, bits 9-32 of the DM<br>will contain the last CM sent to the<br>drive (preceded by zeros if less than<br>24-bit message).                                                                                   |

|     |                          | When LOW, indicates continuation of the message.                                                                                                                                                                          | 8     | Exception             | When LOW, indicates that a drive<br>exception condition exists or that<br>a read status command was sent to the                                                                                                             |

| 3   | AM/Index                 | When LOW, indicates an Address Mark<br>(AM) has been detected in response<br>to an AM search or that an Index Mark<br>has been detected in response to an<br>Index Mark search. A DM is generated<br>when bit 3 goes LOW. |       |                       | drive in the last CM. Presence of this<br>bit will initiate generation of a drive<br>message. When this bit is LOW and<br>bit 7 is HIGH, bits 9-32 of the DM<br>will contain status register information<br>from the drive. |

| 4   | OnLine                   | When HIGH, indicates the spindle is up to speed and ready for operation.                                                                                                                                                  | 9-32  | Status                | These bits will contain status informa-<br>tion if bit 8 is LOW and bit 7 is HIGH,                                                                                                                                          |

| 5   | Ready                    | When HIGH, indicates the spindle in ONLINE and the heads are not seeking                                                                                                                                                  |       |                       | or the previous controller message if bit 7 is LOW.                                                                                                                                                                         |

|     |                          | to a new cylinder. When a seek is completed, READY goes HIGH and a                                                                                                                                                        | 9     | Unit ID               | When LOW, indicates type 206 spindle.                                                                                                                                                                                       |

|     |                          | DM is generated.                                                                                                                                                                                                          | 10-12 | Spares                |                                                                                                                                                                                                                             |

| 6   | Previously<br>Unselected | When LOW, indicates bits 1 through 5 of the last CM were all LOW (bad parity). This could be the result of                                                                                                                | 13    | Maintenance<br>Mode   | When LOW, indicates maintenance mode.                                                                                                                                                                                       |

|     |                          | deselecting a drive (CM goes LOW).<br>When a drive is reselected (CM goes<br>HIGH), a DM is generated with bit 6<br>LOW.                                                                                                  | 14    | Write Data<br>Missing | When LOW, indicates no transitions<br>during a write mode. At the end of<br>the write mode, a DM is generated<br>with status bit 14 LOW.                                                                                    |

$\frac{1}{2}$

### Table 1-3. Drive Message Bits

## Table 1-3. Drive Message Bits (Cont)

| Bit | Name                              | Function                                                                                                                                                                                                                                          | Bit | Name                                    | Function                                                                                                                                                                                                            |

|-----|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15  | Write Protect<br>and Write Enable | When LOW, indicates WRITE<br>ENABLE bit (CM bit 21) was received<br>while WRITE ENABLE switch was<br>off. Bit 15 also goes LOW if WRITE<br>command (CM bit 2) is received while<br>WRITE ENABLE switch is off or<br>WRITE ENABLE bit is inactive. | 24  | Carriage Hit<br>Forward or<br>Rear Stop | When LOW, indicates heads have hit<br>forward or rear endstop and caused<br>an emergency head retract and power<br>off. To reset and power on, the drive<br>RUN/STOP switch must be turned off<br>and then back on. |

| 16  | Command When                      | When LOW, indicates cylinder address                                                                                                                                                                                                              | 25  | Spare                                   |                                                                                                                                                                                                                     |

|     | Not READY                         | CM was sent while drive was not READY.                                                                                                                                                                                                            | 26  | Write Current<br>and No<br>Write Gate   | When LOW, indicates write current sensed without a write command.                                                                                                                                                   |

| 17  | Illegal Head                      | When LOW, indicates head address is greater than 4.                                                                                                                                                                                               | 27  | Write Gate                              | When I OW indicator white command                                                                                                                                                                                   |

|     |                                   | C                                                                                                                                                                                                                                                 | 21  | and No Write                            | When LOW, indicates write command<br>and no write current sensed or write                                                                                                                                           |

| 18  | Illegal Cylinder                  | When LOW, indicates cylinder address is greater than 814.                                                                                                                                                                                         |     | Current                                 | command and no data transitions sensed to the write driver.                                                                                                                                                         |

| 19  | Spindle Address<br>Error          | When LOW, indicates drive spindle<br>address does not agree with CM<br>spindle address.                                                                                                                                                           | 28  | Head Select<br>Fault                    | When LOW, indicates no heads or<br>more than one head selected while<br>reading or writing.                                                                                                                         |

| 20  | Offset During<br>Write Enable     | When LOW, indicates an offset<br>command while in the WRITE<br>ENABLE state.                                                                                                                                                                      | 29  | DC Power<br>Fault                       | When LOW, indicates servo voltage or -12 Vdc low or missing.                                                                                                                                                        |

| 21  | Offset During<br>Seek             | When LOW, indicates OFFSET active when a cylinder address CM is received.                                                                                                                                                                         | 30  | Temperature<br>Warning                  | When LOW, indicates temperature has exceeded normal levels.                                                                                                                                                         |

| 22  | Seek Incomplete                   | When LOW, indicates the heads were not settled within 700 milliseconds                                                                                                                                                                            | 31  | Temperature<br>Critical                 | When LOW, indicates temperature has exceeded safe operating limits.                                                                                                                                                 |

|     |                                   | after seek started.                                                                                                                                                                                                                               | 32  | RPM Less Than 3420                      | When LOW, indicates the spindle speed is less than 3420 rpm.                                                                                                                                                        |

| 23  | Offtrack and<br>Write Enable      | When LOW, indicates the servo is<br>offtrack while the WRITE ENABLE<br>state is active.                                                                                                                                                           |     | 5120                                    |                                                                                                                                                                                                                     |

### DPEC-DPC CONTROL AND STATUS INTERFACE LINES

Term

### Description

In the read mode, the CLOCK levels

indicate that the INFOnn lines are

stable for at least 150 nanoseconds

and remain stable for the CLOCK

period.

The following are terms generated by the disk pack control (DPC) and sent to the DPEC, along with the terms generated by the DPEC in response to those terms.

BUSY status in table 1-4.

A TRUE indicates that the DPC is

ready to send data or receive data.

FALSE indicates that the DPC is

not ready to send or receive data.

For slip mode, the EXECUTE line

goes FALSE before word 91 of the

data field to indicate to the DPEC

that it is to go into a slip holding

mode during a multisector operation.

The width of the TRUE level is 300

The minimum period at transfer rate

nanoseconds at the transfer rate.

The clock level informs the DPC

that, in a write mode of operation,

the INFOnn lines information was

is 1.6 microseconds.

accepted by the DPEC.

| Term                         | Description                                                                                                                                                                                                                                 | PARITY (\$K)<br>(Bi-Directional)   | Parity is TRUE when the modulo 2 sum of the INFOnn lines is equal to                      |  |  |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-------------------------------------------------------------------------------------------|--|--|

| SELECT (#H)<br>(DPC to DPEC) | A TRUE level enables the initiate phase for the DPEC. The INFOnn                                                                                                                                                                            |                                    | 0; otherwise, parity is FALSE (odd parity).                                               |  |  |

|                              | lines must be stable at the time the SELECT level goes TRUE.                                                                                                                                                                                | READY STATUS<br>(#N) (DPEC to DPC) | When TRUE, indicates that the DPEC is powered on, in remote, and                          |  |  |

|                              | A SELECT FALSE before word 91                                                                                                                                                                                                               |                                    | ready to be selected.                                                                     |  |  |

|                              | indicates termination by the disk<br>pack control at completion of the<br>coincident sector.                                                                                                                                                |                                    | When FALSE, indicates that the power is off, or the DPEC is in a local mode of operation. |  |  |

|                              | A SELECT FALSE after word 92                                                                                                                                                                                                                | INFO 00 (\$W)                      | Least significant bit (LSB).                                                              |  |  |

|                              | indicates to continue the operation<br>for one more sector and then                                                                                                                                                                         | INFO 01 (\$N)                      |                                                                                           |  |  |

|                              | terminate the operation.                                                                                                                                                                                                                    | INFO 02 (\$T)                      |                                                                                           |  |  |

|                              | If the DPEC terminates the operation, the DPC will drop (SELECT FALSE) the select line within $1\pm0.5$ microsecond.                                                                                                                        | INFO 03 (#T)                       |                                                                                           |  |  |

|                              |                                                                                                                                                                                                                                             | INFO 04 (\$Q)                      |                                                                                           |  |  |

|                              |                                                                                                                                                                                                                                             | INFO 05 (#Q)                       | Sixteen-bit bidirectional information                                                     |  |  |

| READY (#R)<br>(DPEC to DPC)  | A TRUE level indicates that the<br>DPEC is ready to receive the second<br>initiate word.<br>READY goes TRUE 200±100<br>nanoseconds after the leading edge of<br>the first initiate clock sent to the<br>DPC.<br>Refer to SELECT, READY, and | INFO 06 (\$M)                      | lines between the DPC and the DPEC                                                        |  |  |

|                              |                                                                                                                                                                                                                                             | INFO 07 (#M)                       | These lines are HIGH for a "1" bit<br>and LOW for a "0" bit and are used                  |  |  |

|                              |                                                                                                                                                                                                                                             | INFO 08 (\$J)                      | to transfer initiate descriptors,                                                         |  |  |

|                              |                                                                                                                                                                                                                                             | INFO 09 (#J)                       | information, and result descriptors.                                                      |  |  |

|                              |                                                                                                                                                                                                                                             | INFO 10 (\$G)                      |                                                                                           |  |  |

|                              |                                                                                                                                                                                                                                             | INFO 11 (#G)                       |                                                                                           |  |  |

|                              | BUSY status in table 1-4.                                                                                                                                                                                                                   | INFO 12 (\$E)                      |                                                                                           |  |  |

| BUSY (\$R)                   | A TRUE level indicates that the                                                                                                                                                                                                             | INFO 13 (#E)                       |                                                                                           |  |  |

| (DPEC to DPC)                | DPEC has received the second<br>initiate word and is conditioned for                                                                                                                                                                        | INFO 14 (\$D)                      |                                                                                           |  |  |

|                              | normal operation.                                                                                                                                                                                                                           | INFO 15 (#D)                       | Most significant bit (MSB).                                                               |  |  |

|                              | BUSY goes TRUE 200±100                                                                                                                                                                                                                      | EX SEL (#K)                        | Not used.                                                                                 |  |  |

|                              | nanoseconds after the leading edge of the second initiate clock.                                                                                                                                                                            | EX BUSY (#U)                       | Not used.                                                                                 |  |  |

|                              | Refer to SELECT, READY, and                                                                                                                                                                                                                 |                                    |                                                                                           |  |  |

### **DPEC-DPC INTERFACE OPERATION**

The initiate operation begins with the interface in an idle state defined by the lines READY/\*BUSY/\*SE-LECT/ (refer to table 1-4). The DPC brings up the SEND line to begin the operation, simultaneously putting the first initiate word on the INFO (0-15) lines.

Within 166 to 500 nanoseconds after setting the SEND line, the DPC brings up the SELECT line. The interface lines are now SELECT\*BUSY/\*READY/. This state indicates to the DPEC that the first initiate word is on the INFO lines. When the DPEC has accepted the first initiate word, it puts out a clock pulse (300 nanoseconds minimum width). The leading edge of this pulse indicates to the DPC that the first word has been accepted by the DPEC and also causes the DPC to set the READY line.

EXECUTE (\$H)

(DPC to DPEC)

CLOCK (\$U)

| Level Status                  | State/Phase                  | Remarks                                                     |

|-------------------------------|------------------------------|-------------------------------------------------------------|

| SELECT/*BUSY/*READY/          | Idle                         |                                                             |

| SELECT * BUSY/*EXECUTE        | Initiate phase               | READY/ = DPEC<br>receiving the first<br>initiate word       |

|                               |                              | <b>READY</b> = <b>DPEC</b> receiving second initiate word   |

| SELECT*BUSY*READY*<br>EXECUTE | Data transfer<br>phase       | EXECUTE/ = Slip Mode<br>(see note section of this<br>table) |

| SELECT/*BUSY*READY/           | Result status phase          |                                                             |

| SELECT/*BUSY*READY            | Wait for result status phase | Operation terminated by<br>Disk Pack Control (DPC)          |

| SELECT/*BUSY/*READY           | Sequence error               | DPEC failure                                                |

| SELECT*BUSY*READY/            | Go to result<br>status phase | Operation terminated by the DPEC                            |

|                               | NOTE                         |                                                             |

### Table 1-4. SELECT, READY, and BUSY Status

NOIL

SELECT will stay up for the initiate and verify operations. SELECT/ will terminate the initiate and verify operation. For timing, see figure 1-26.

The DPC will drop the EXECUTE line if, during the data phase with more data to come, the DPC has full buffers during a read operation or empty buffers during a write operation. This will put the DPEC in the slip mode. When data or buffers become available, the DPC will raise the EXECUTE line and the operation will continue.