B9499-6 DISK DRIVE ELECTRONIC CONTROLLER (205, 206, 207)

TECHNICAL MANUAL VOLUME 3:

# THEORY OF OPERATION

BASIC PRINCIPLES

2 MODE FLOWS

3 RELATED CIRCUITS

4 DATA-RELATED CIRCUITS

RESET LOGIC

POWER SUPPLY

#

#### FIELD ENGINEERING PROPRIETARY DATA

The information contained in this document is proprietary to Burroughs Corporation. The information or this document is not to be reproduced, shown, or disclosed outside Burroughs Corporation without written permission of the Patent Division.

This material is furnished for Burroughs Field Engineering Personnel, and is not furnished to customers except under special License Agreement.

THIS DOCUMENT IS THE PROPERTY OF AND SHALL BE RETURNED TO BURROUGHS CORPORATION, BURROUGHS PLACE, DETROIT, MICHIGAN 48232.

Burroughs believes that information described in this manual is accurate and reliable, and much care has been taken in its preparation. However, no responsibility, financial or otherwise, is accepted for any consequences arising out of the use of this material. The information contained herein is subject to change. Revisions may be issued to advise of such changes and/or additions.

#### LIST OF EFFECTIVE PAGES

| Page          | Issue    |

|---------------|----------|

| Cover         | 6/78     |

| iii           | Original |

| v             | Original |

| vii           | Original |

| ix            | Original |

| 1-1 thru 1-25 | Original |

| 2-1 thru 2-29 | Original |

| 3-1 thru 3-11 | Original |

| 4-1 thru 4-23 | Original |

| 5-1 thru 5-21 | Original |

| 6-1 thru 6-3  | Original |

# **TABLE OF CONTENTS**

| Section | Title                                              | Page         |         | 206 READ and VERIFY                                    | 2-12<br>2-15 |

|---------|----------------------------------------------------|--------------|---------|--------------------------------------------------------|--------------|

|         | INTRODUCTION                                       | ix           |         | 206 Write Operation 206 End of Test Routine            | 2-13<br>2-15 |

| 1       | BASIC PRINCIPLES                                   | 1-1          |         | 207 Read or Verify Without Error                       | 2-15         |

|         | General Description                                | 1-1          |         | Correction                                             |              |

|         | Configuration                                      | 1-1          |         | 207 Write                                              | 2-16         |

|         | Disk Pack Drive Format                             | 1-1          |         | 207 Read or Verify With Error                          | 2-16         |

|         | 206 Platter Configuration                          | 1-1<br>1-1   |         | Correction 207 End Test Routine                        | 2-16         |

|         | Track Configuration (206)                          | 1-1          |         | Mode 7 Write Beginning-Of-Track                        | 2-10         |

|         | Error Protection Codes (206)                       | 1-3          |         | Mode 8 Initialize Sectors                              | 2-17         |

|         | 207                                                | 1-3          |         | 206 Operation                                          | 2-17         |

|         | Cylinder Configuration                             | 1-3          |         | 207 Operation                                          | 2-19         |

|         | Track Configuration                                | 1-4          |         | Mode 9 Disk Location Synchronize                       | 2-20         |

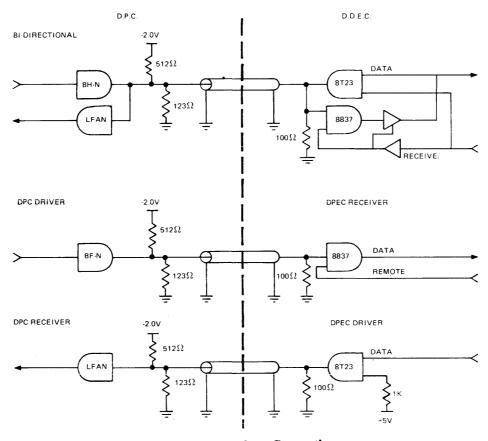

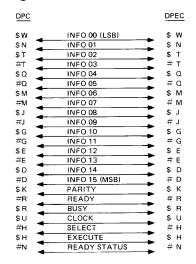

|         | Error Protection Codes (207) Interface DDEC to DPC | 1-4<br>1-5   |         | 206 Operation<br>207 Operation                         | 2-20<br>2-21 |

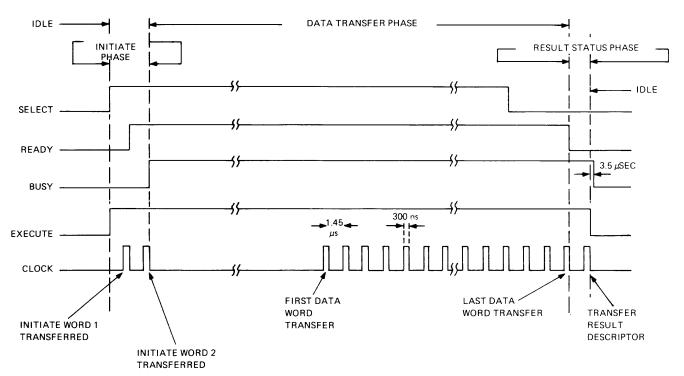

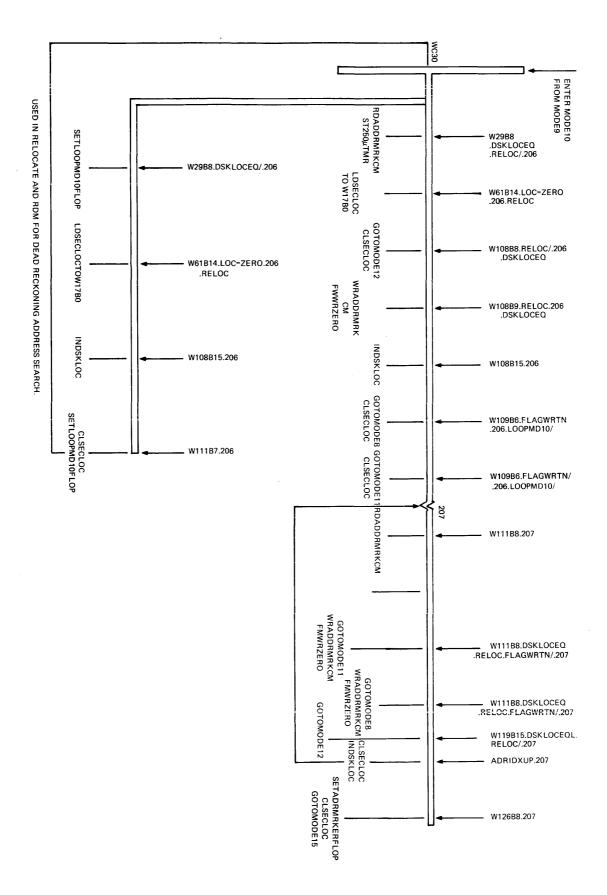

|         | General Description                                | 1-5          |         | Mode 10 Dead Reckoning Address                         | 2-21         |

|         | Initiate Phase                                     | 1-5          |         | Search                                                 |              |

|         | Data Transfer Phase                                | 1-5          |         | 206 Operation                                          | 2-21         |

|         | Result Status Phase                                | 1-5          |         | 207 Operation (dskloceql)                              | 2-24         |

|         | Electrical Characteristics                         | 1-7          |         | Mode 11 Overwriting A Bad Sector                       | 2-24         |

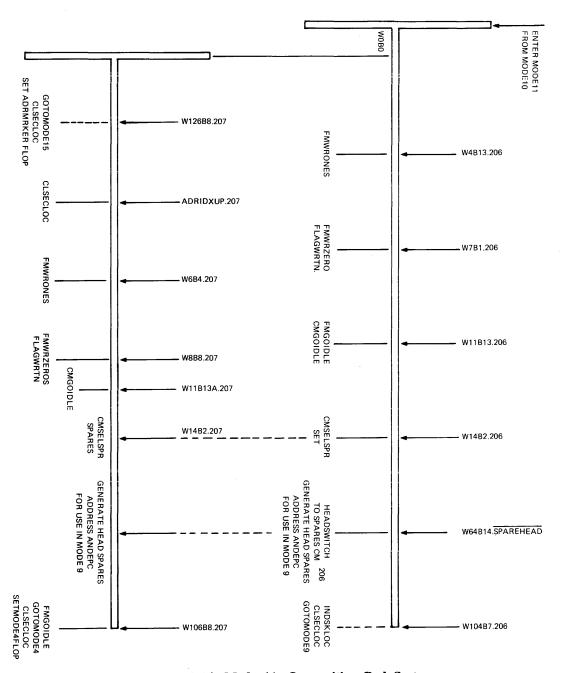

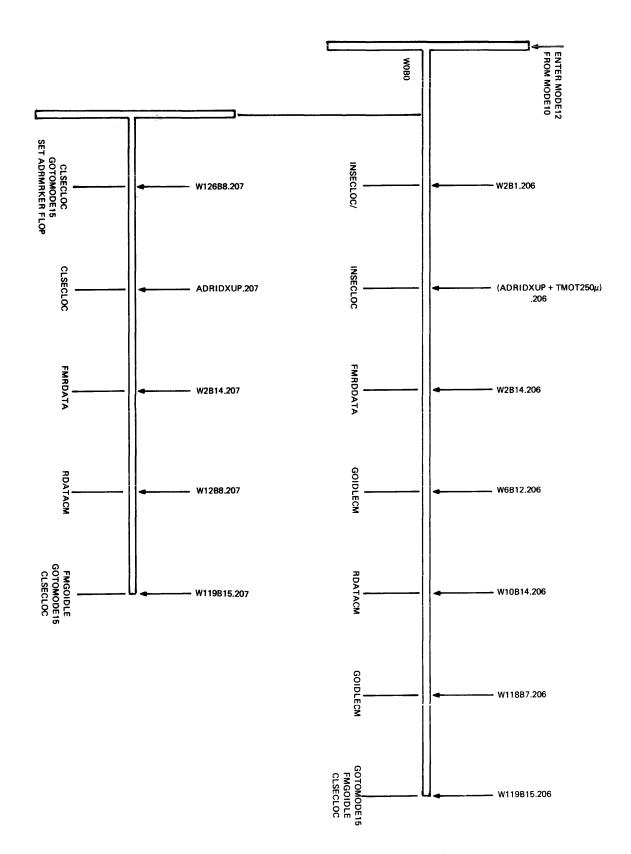

|         | Logical Levels Interface Lines and Timing          | 1-7<br>1-7   |         | 206 Operation<br>207 Operation                         | 2-24<br>2-24 |

|         | Result Descriptor Information                      | 1-8          |         | Mode 12 Read Maintenance Sector                        | 2-24         |

|         | Read Data Error                                    | 1-8          |         | Transfer                                               | 2-23         |

|         | Write Lockout                                      | 1-8          |         | 206 Operation                                          | 2-26         |

|         | Seek Status                                        | 1-8          |         | 207 Operation                                          | 2-26         |

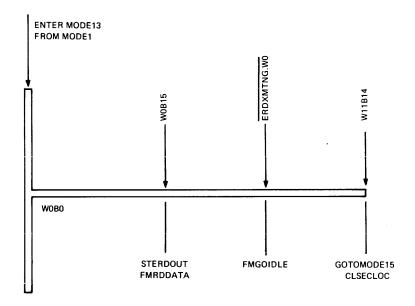

|         | Drive Not Ready                                    | .1-8         |         | Mode 13 Send Extended Result                           | 2-26         |

|         | Drive Off-Line Drive Unsafe                        | 1-8<br>1-8   |         | Descriptor                                             | 2-26         |

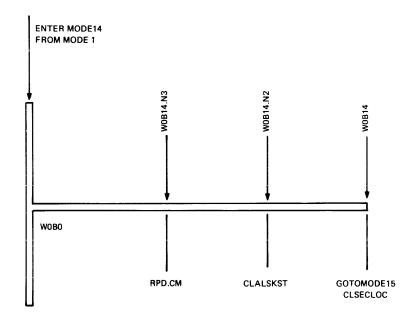

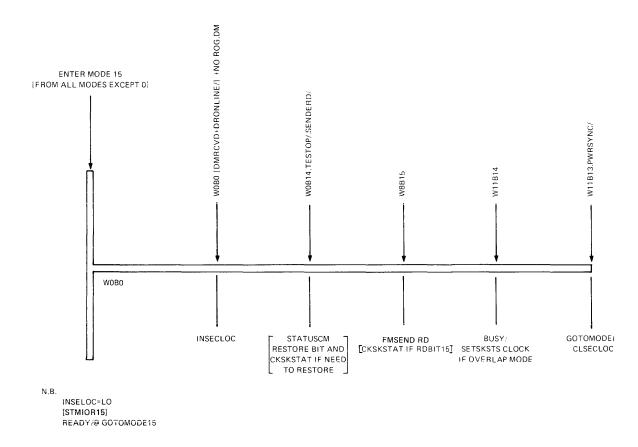

|         | Data Sync Error                                    | 1-8<br>1-9   |         | Mode 14 Test OP Mode 15 Terminate And Report           | 2-26         |

|         | Sector Address Error                               | 1-9          |         | Mode 15 Terminate And Report                           | 2-20         |

|         | Seek Timeout                                       | 1-9          | Section | Title                                                  | Page         |

|         | Drive Not Present                                  | 1-9          | 3 -     | ADDRESS RELATED CIRCUITS                               | 3-1          |

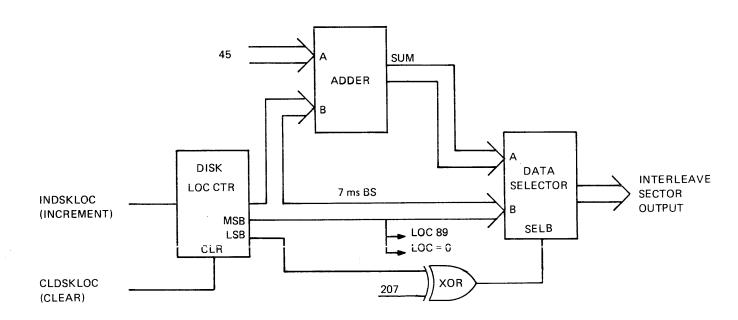

|         | Transmission Parity                                | 1-9          |         | Disk Location Counter And Interleave                   | 3-1          |

|         | Try Diagnostics Extended Result Descriptor         | 1-9<br>1-9   |         | Logic                                                  |              |

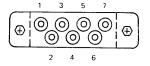

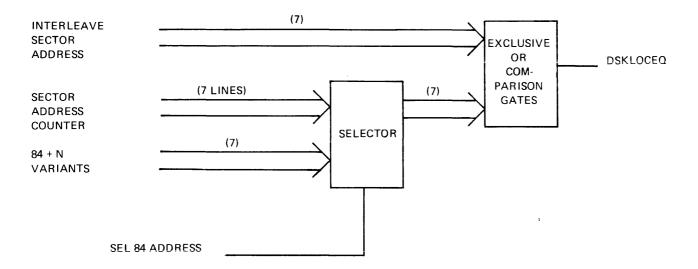

|         | Interface, DDEC to Drive                           | 1-11         |         | Disk Location Equal Logic Address Decode               | 3-2<br>3-3   |

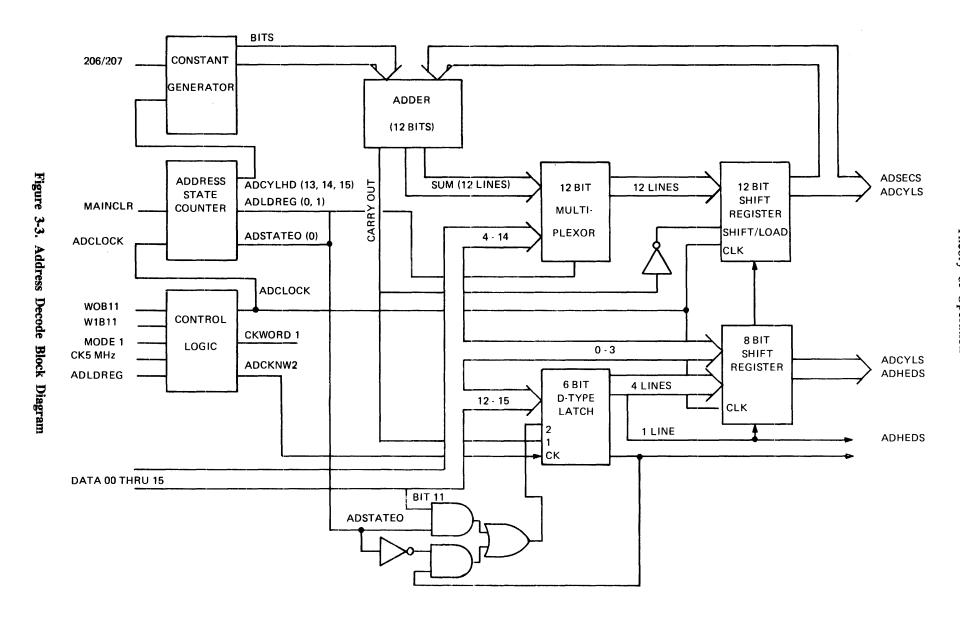

|         | Physical Characteristics                           | 1-11         |         | General Description                                    | 3-3          |

|         | Controller Message                                 | 1-11         |         | Address Constants                                      | 3-3          |

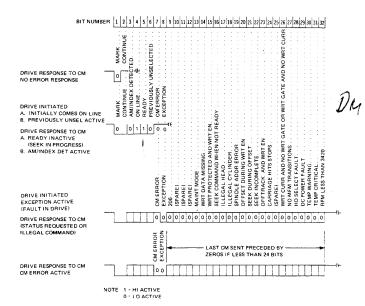

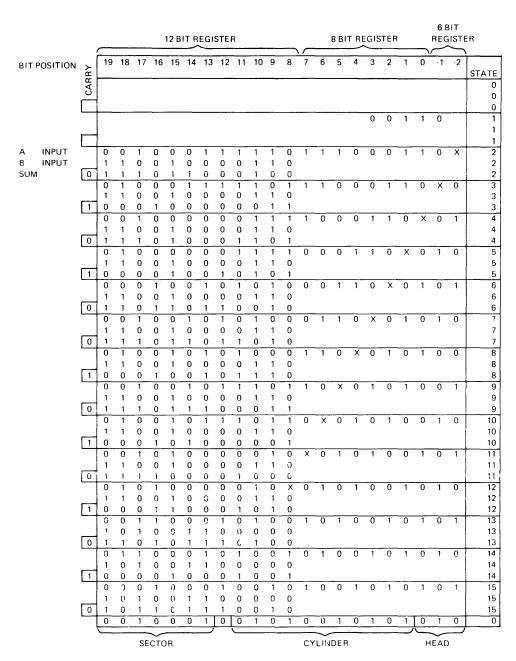

|         | Drive Message (dm)                                 | 1-14         |         | Binary Address Loading                                 | 3-3          |

|         | Clock                                              | 1-16         |         | Address Computation                                    | 3-5          |

|         | Data Electrical Characteristics                    | 1-16<br>1-16 |         | Address Counter                                        | 3-5          |

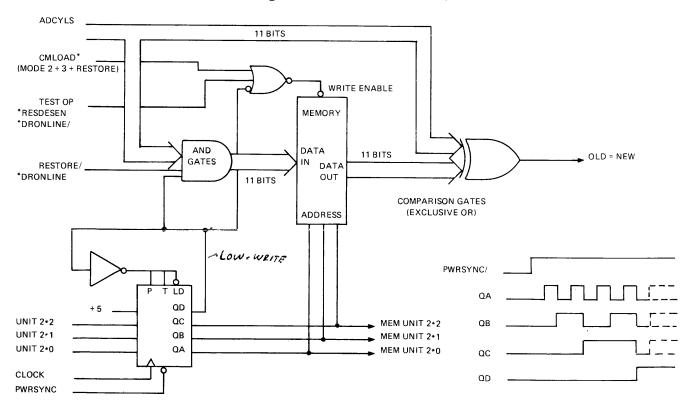

|         | Logical Levels                                     | 1-16         |         | OLD = NEW<br>Initial Clearing                          | 3-6<br>3-6   |

|         | Functions                                          | 1-17         |         | Memory Write                                           | 3-8          |

|         | General Description                                | 1-17         |         | Comparison                                             | 3-8          |

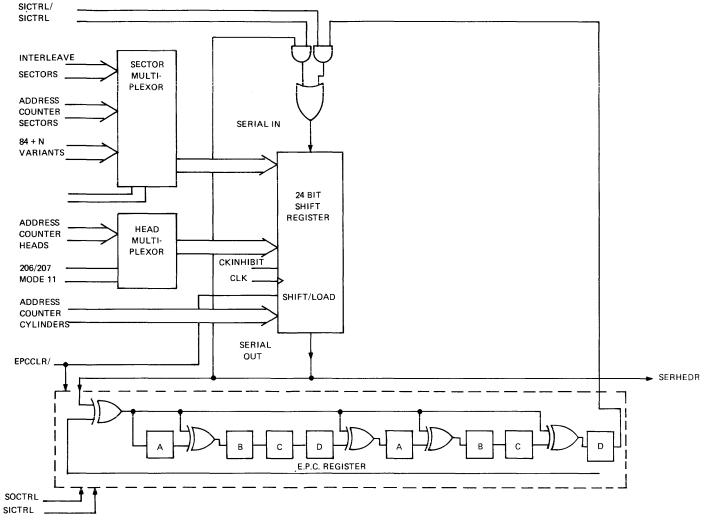

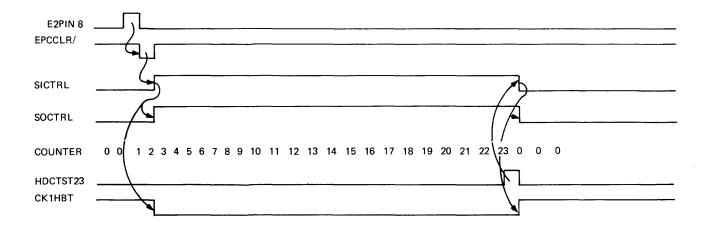

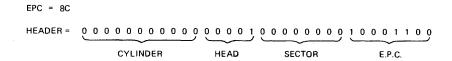

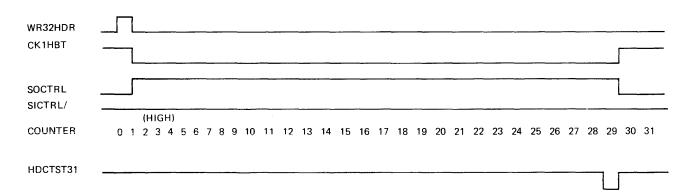

|         | Power Up (206 and 207)                             | 1-17         |         | Header Generation And EPC                              | 3-8          |

|         | Initial OP Processing                              | 1-17         |         | General Description                                    | 3-8          |

|         | Initialize (206)<br>Initialize (207)               | 1-19<br>1-19 |         | Header Generation                                      | 3-8<br>3-8   |

|         | READ, WRITE, and VERIFY (206)                      | 1-21         |         | Write Address Address Comparison                       | 3-10         |

|         | READ, WRITE, and VERIFY 207                        | 1-22         |         | Address Comparison                                     | 3-10         |

|         | RELOCATE                                           | 1-22         | Section | Title                                                  | Page         |

|         | Test OP                                            | 1-25         |         |                                                        |              |

|         | Read Extended Result Descriptor Read Maintenance   | 1-25<br>1-26 | 4       | DATA RELATED CIRCUITS                                  | 4-1          |

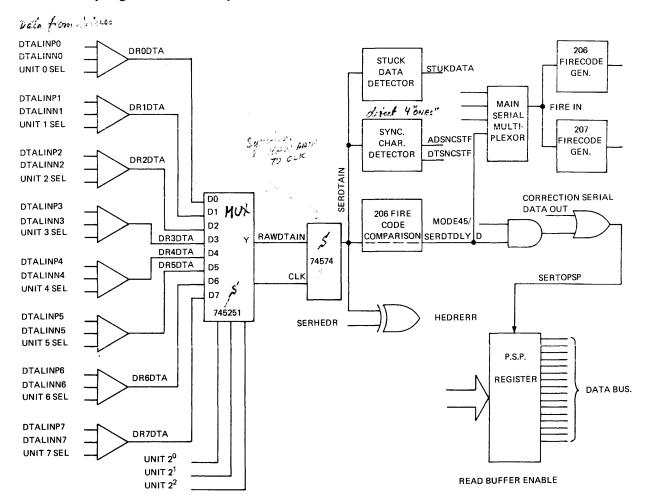

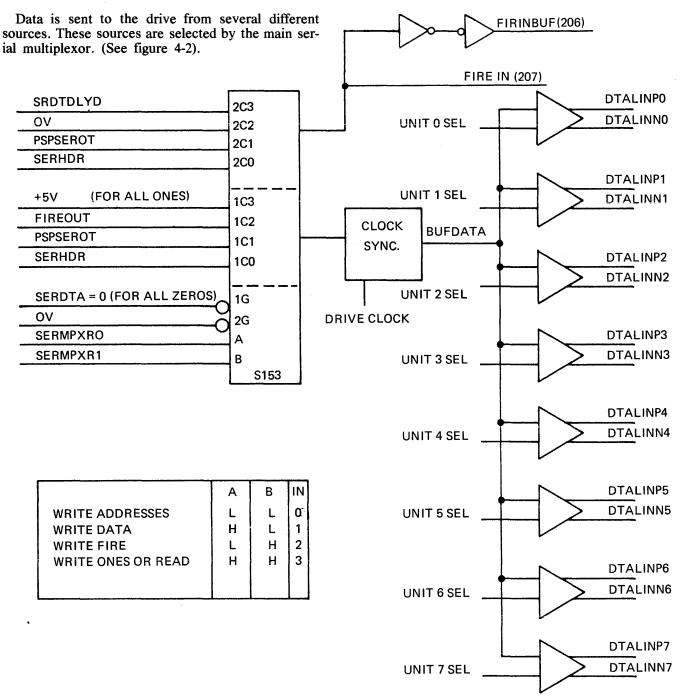

|         |                                                    |              |         | Data From The Drive Data Fo The Drive                  | 4-1<br>4-2   |

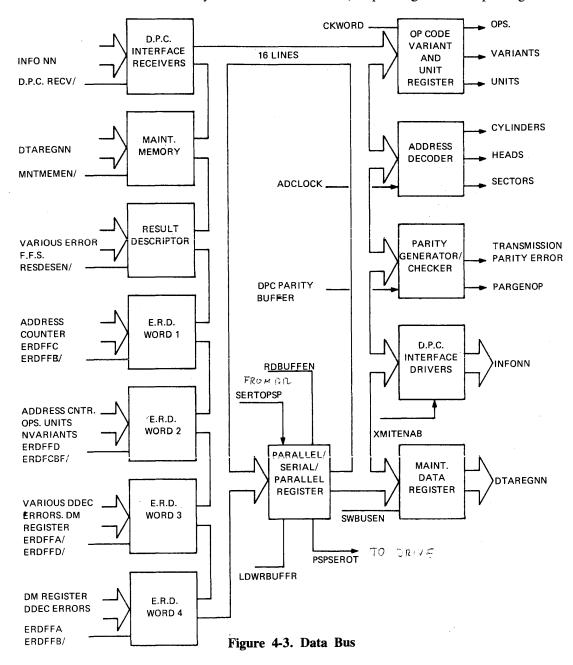

| Section | Title                                              | Page         |         | Data Bus                                               | 4-2          |

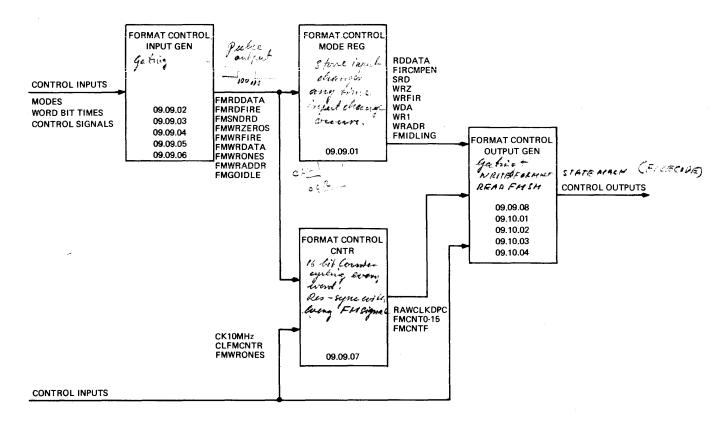

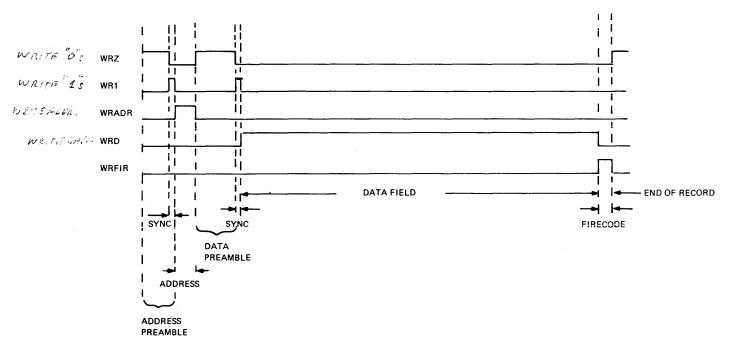

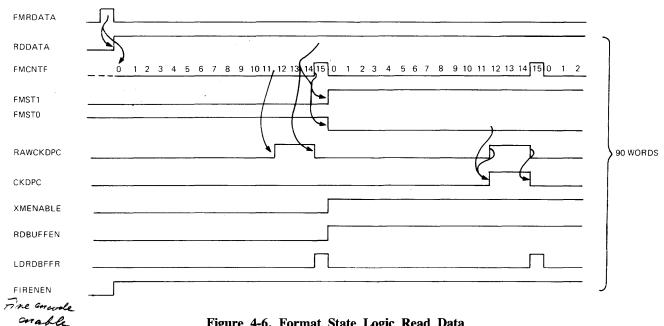

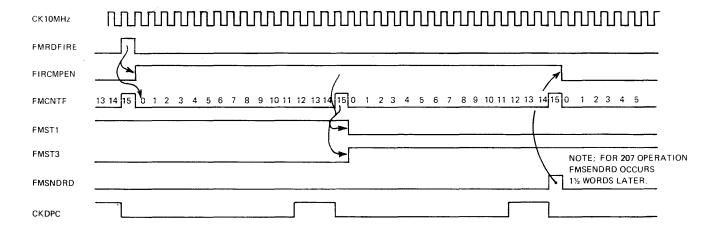

| 2       | MODE FLOWS                                         | 2-1          |         | Format Control Logic                                   | 4-4          |

|         | General Description                                | 2-1          |         | General Description                                    | 4-4          |

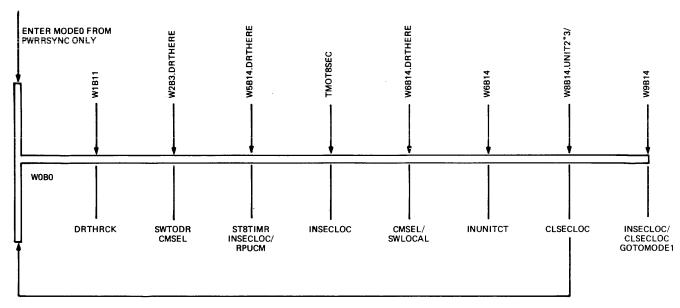

|         | Mode 0 Spindle Spinup                              | 2-1          |         | Block Diagram                                          | 4-4          |

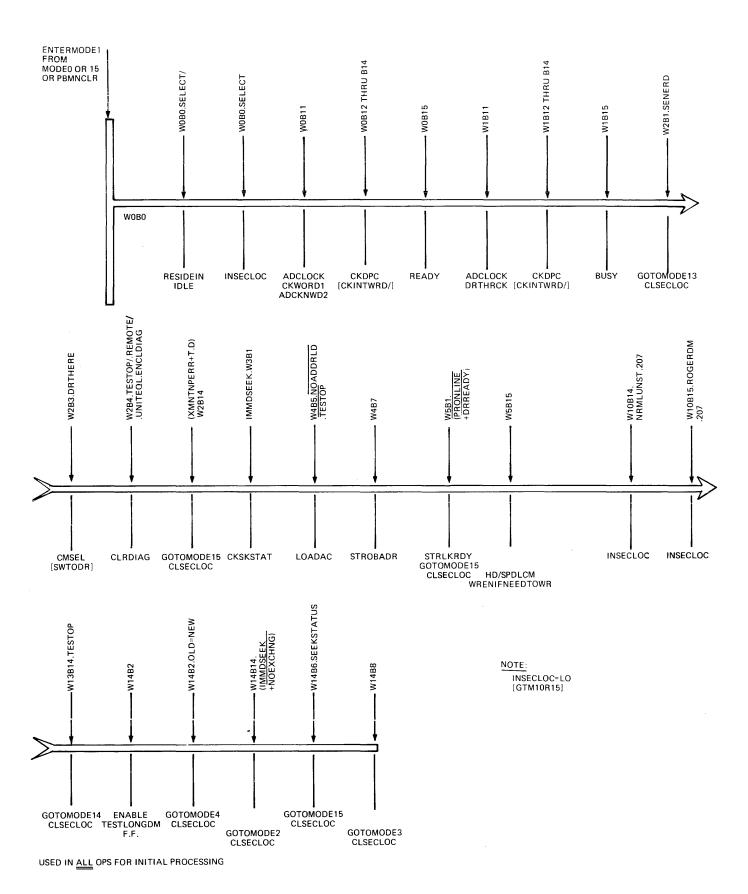

|         | Mode 1 Initial OP Processing                       | 2-3          |         | Format Control Input                                   | 4-4          |

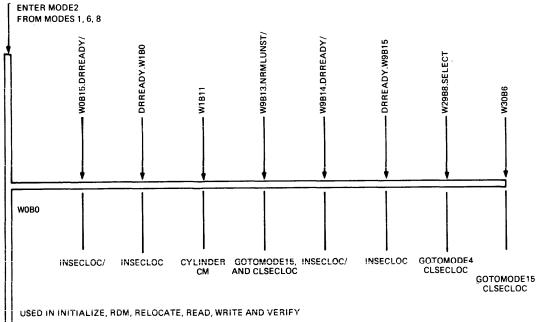

|         | Mode 2 Seek                                        | 2-6<br>2-7   |         | Format Control Register                                | 4-4<br>4-4   |

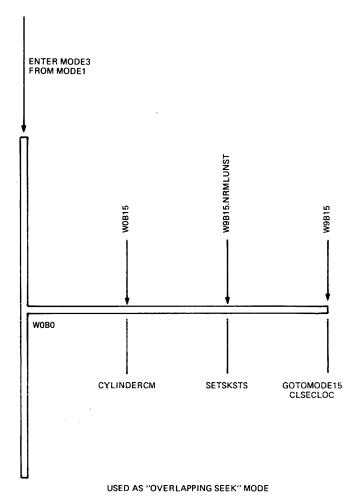

|         | Mode 3 Overlap Seeks Mode 4 Head Switch and Index  | 2-7<br>2-7   |         | Format Control Counter Format Control Output Generator | 4-4          |

|         | Search                                             | 2 /          |         | Format State Logic                                     | 4-6          |

|         | READ, WRITE, or VERIFY                             | 2-7          |         | Format State Logic (Read)                              | 4-6          |

|         | Read Maintenance, Initialize or                    |              |         | Format State Logic (Write Fire)                        | 4-6          |

|         | Relocate                                           | 2-9          |         | Format Control Functions                               | 4-6          |

|         | Mode 5 Address Search                              | 2-9          |         | FMRDDATA<br>EMBDEIRE                                   | 4-6<br>4-6   |

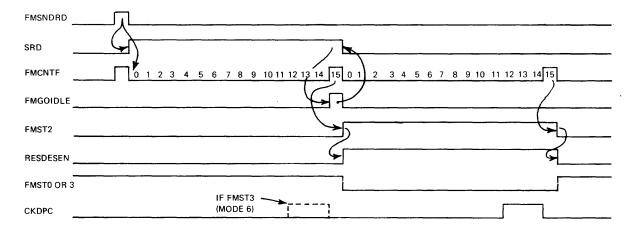

|         | 206 Operation                                      | 2-11         |         | FMRDFIRE<br>FMSENDRD                                   | 4-6<br>4-7   |

|         | 207 Operation<br>206 and 207 Operation             | 2-11<br>2-12 |         | FMWRZEROS                                              | 4-8          |

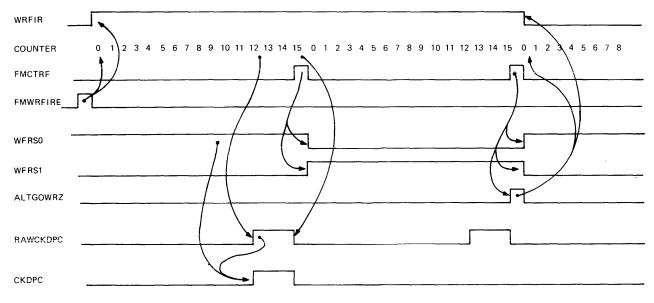

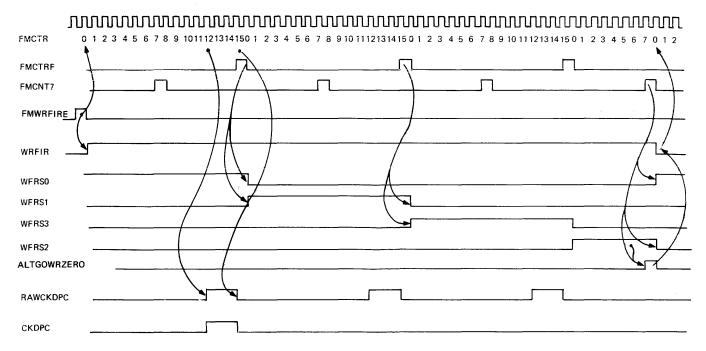

|         | Mode 6 Data Transfer                               | 2-12         |         | FMWRFIRE                                               | 4-8          |

|         |                                                    |              |         |                                                        |              |

1109550

# TABLE OF CONTENTS (Cont)

|         | FMWRDATA                                     | 4-9          |         | Temperature Warning                                  | 5-10         |

|---------|----------------------------------------------|--------------|---------|------------------------------------------------------|--------------|

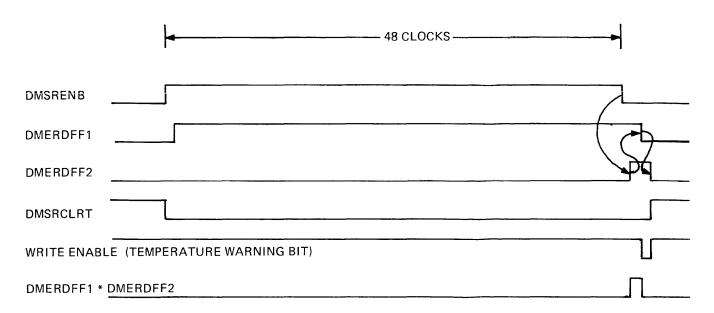

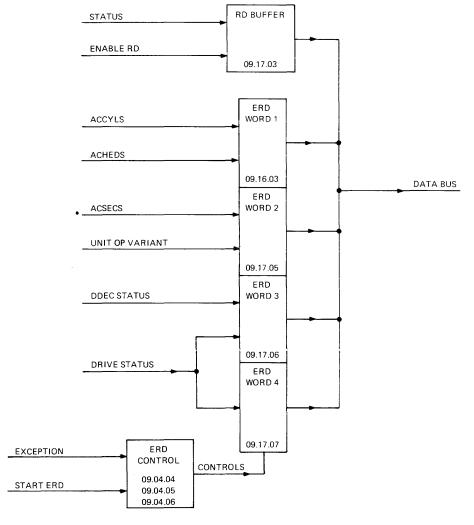

|         | FMWRONES                                     | 4-9          |         | Result Descriptor Logic                              | 5-10         |

|         | FMWRADDR (Write Address)                     | 4-10         |         | General Description Extended Result Descriptor Logic | 5-10<br>5-12 |

|         | Sync Character Detector Address Sync         | 4-10<br>4-10 |         | General Description                                  | 5-12<br>5-12 |

|         | Data Sync                                    | 4-10<br>4-10 |         | Loading the ERD Information                          | 5-12<br>5-12 |

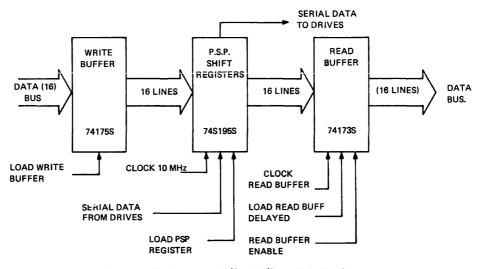

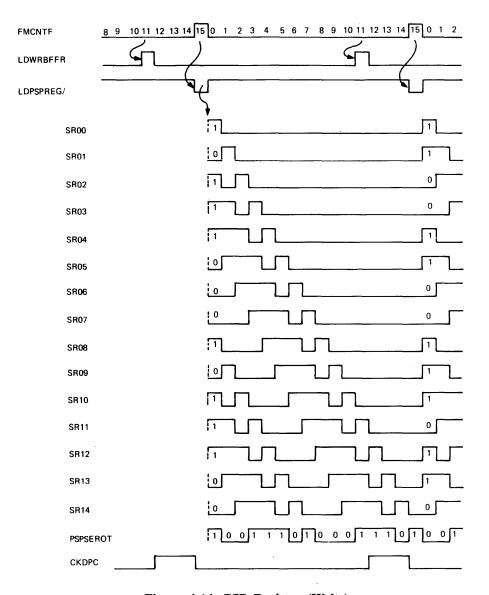

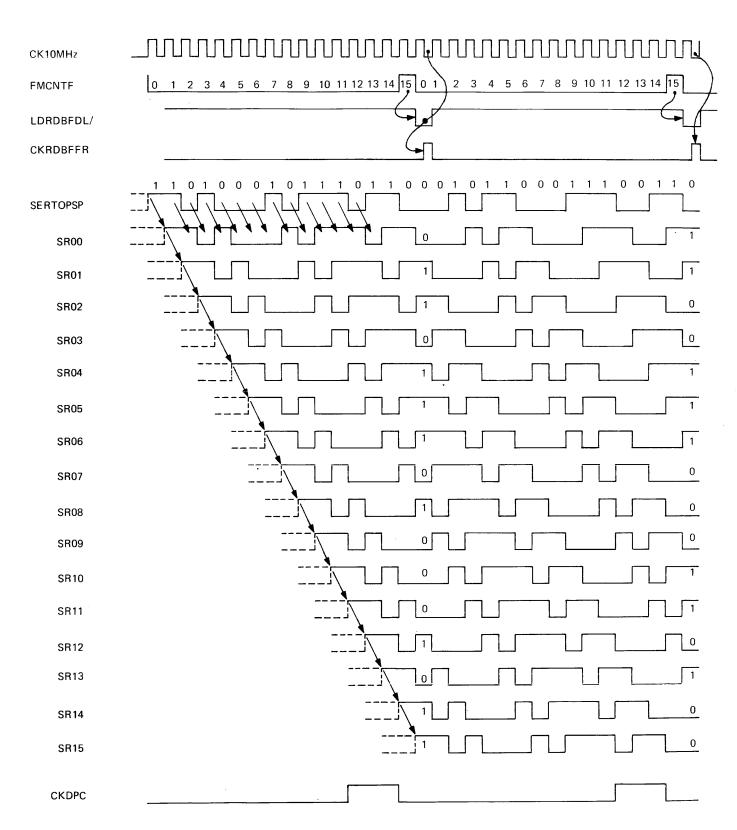

|         | Parallel/Serial/Parallel Register            | 4-10<br>4-10 |         | ERD Control Logic                                    | 5-12         |

|         | Write Buffer                                 | 4-10         |         | Maintenance Logic                                    | 5-12         |

|         | Shift Register                               | 4-10         |         | General Description                                  | 5-12         |

|         | Read Buffer                                  | 4-12         |         | 16-Word Read Write Memory                            | 5-12         |

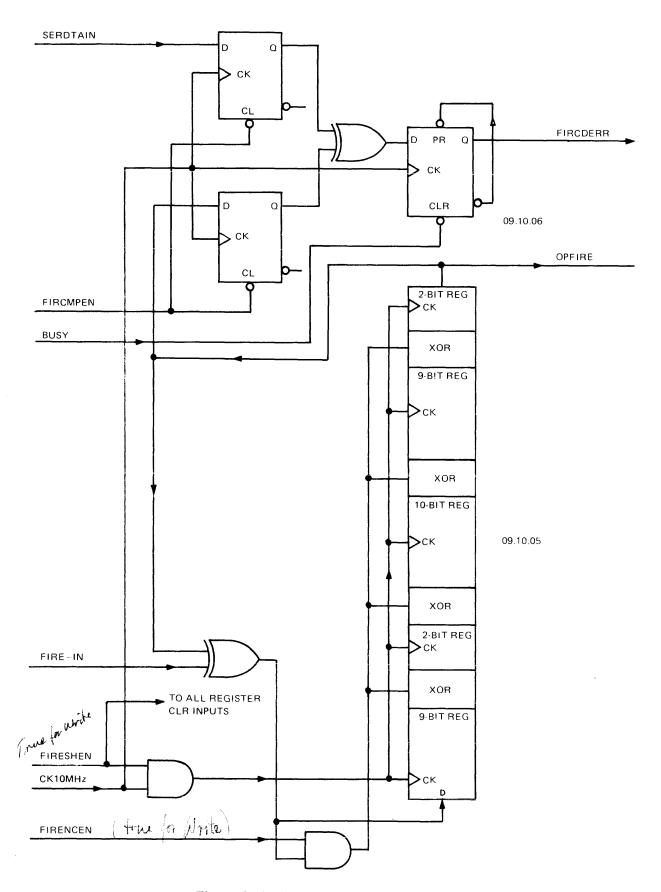

|         | 206 Firecode                                 | 4-12         |         | Data Input Keyboard                                  | 5-12         |

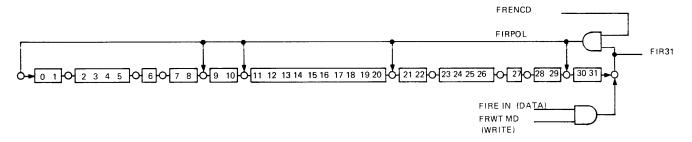

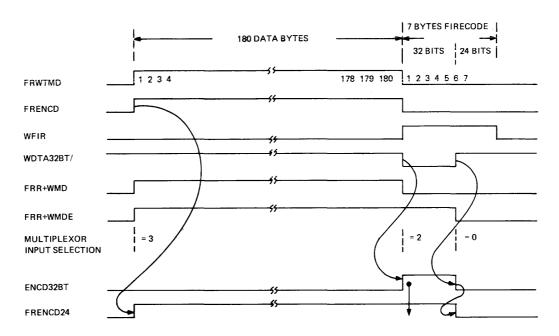

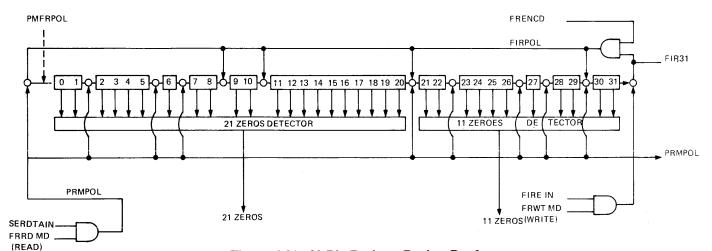

|         | Firecode Generation (206)                    | 4-12         |         | Switch Bus Register                                  | 5-13         |

|         | Write Firecode (206)                         | 4-15         |         | Switch Bus Display Drivers and LEDs                  | 5-13         |

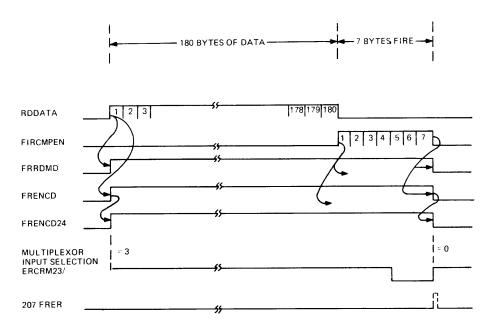

|         | Firecode Comparison (206)                    | 4-15         |         | Switch Bus Buffers                                   | 5-13         |

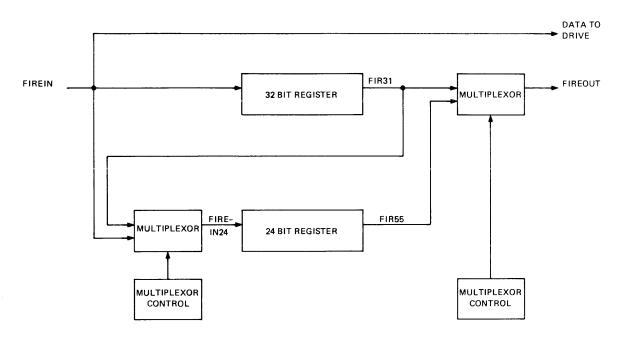

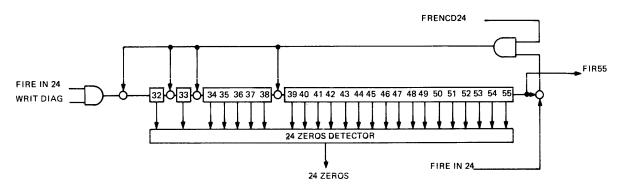

|         | 207 Firecode                                 | 4-15         |         | Memory Address Display                               | 5-13         |

|         | General Description                          | 4-15         |         | Control Keys And Switches                            | 5-13         |

|         | Firecode Generation During Write             | 4-15         |         | General Description                                  | 5-13         |

|         | Normal Write                                 | 4-15         |         | Single Sector/Run                                    | 5-17         |

|         | Diagnostic Write                             | 4-17         |         | Loop Head/Off/Loop Sector                            | 5-17         |

|         | Error Detection                              | 4-17         |         | Loop OP                                              | 5-17         |

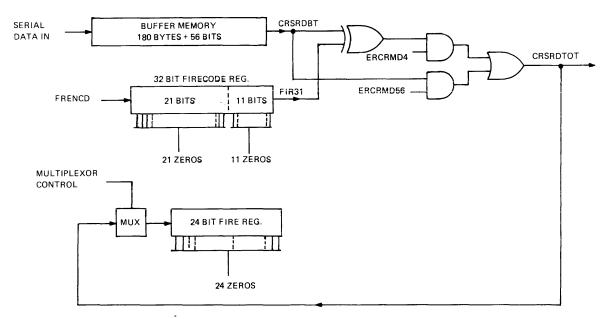

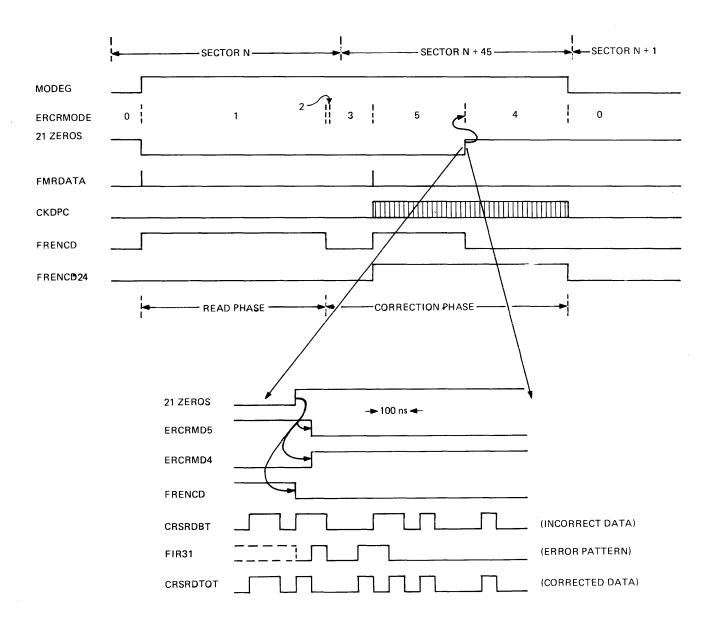

|         | Error Correction                             | 4-19         |         | Halt On Error/Off/No Halt                            | 5-17         |

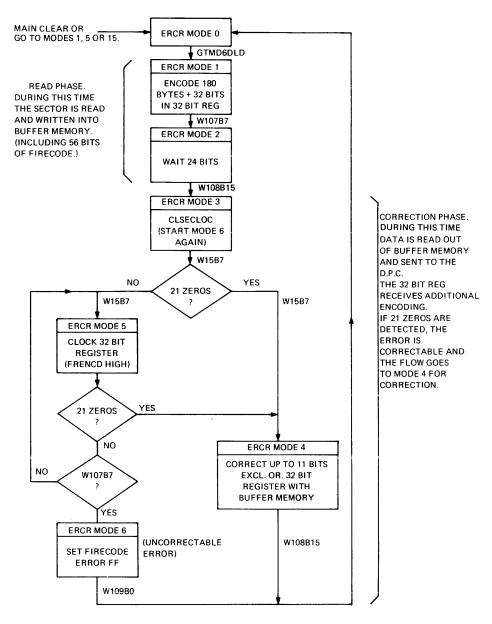

|         | Error Correction Modes                       | 4-19         |         | Alternate OPs                                        | 5-17         |

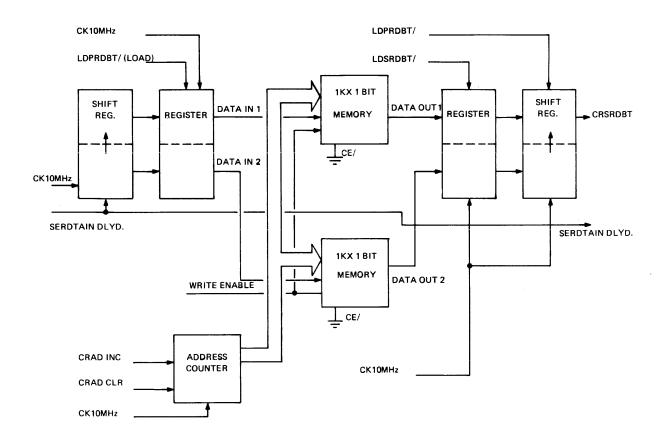

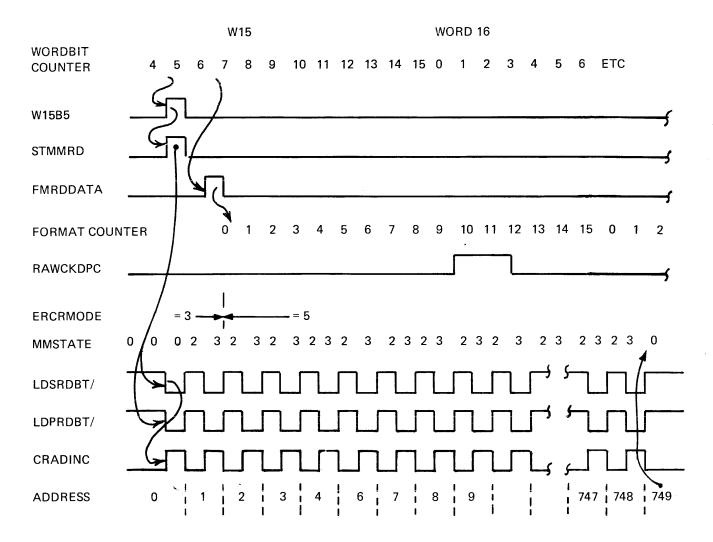

|         | Buffer Memory                                | 4-21         |         | No Address Load                                      | 5-17         |

| Section | Title                                        | Page         |         | Display Enable/Off                                   | 5-17<br>5-17 |

|         |                                              | · ·          |         | Slip<br>No Overlap/Off/Enab Stop                     | 5-17<br>5-17 |

| 5       | MISCELLANEOUS CIRCUITS                       | 5-1          |         | Master Clear                                         | 5-17<br>5-17 |

|         | Reset Logic                                  | 5-1          |         | Clear                                                | 5-17<br>5-17 |

|         | General Description                          | 5-1<br>5-1   |         | Step Mem                                             | 5-17         |

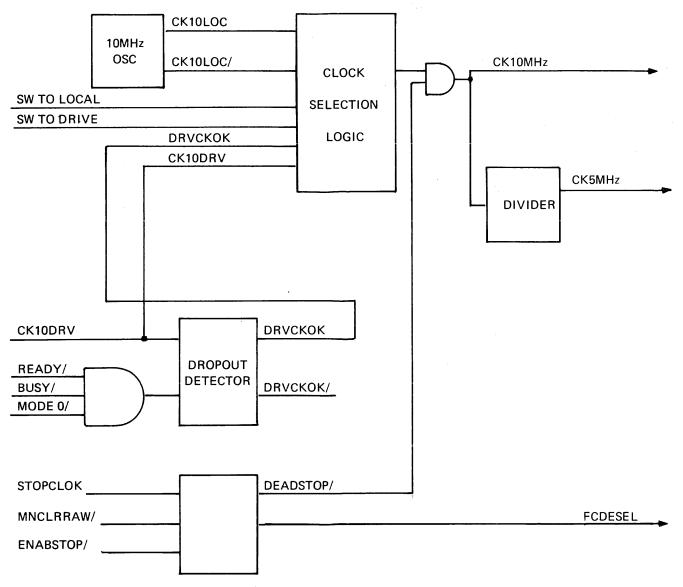

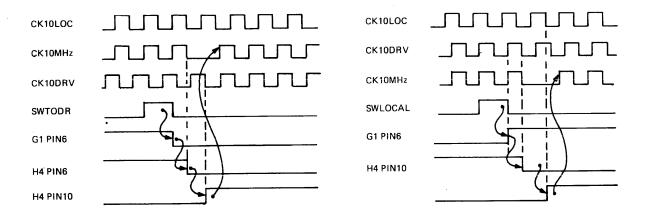

|         | Clock Logic General Description              | 5-1<br>5-1   |         | Load                                                 | 5-17         |

|         | Clock Stopper                                | 5-1<br>5-1   |         | Start                                                | 5-17         |

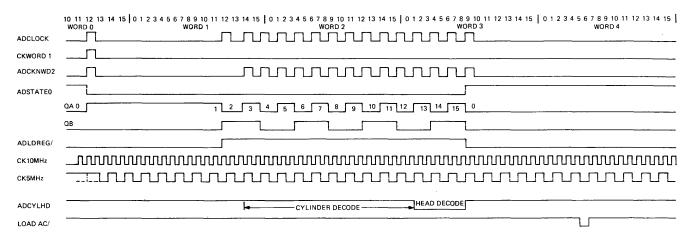

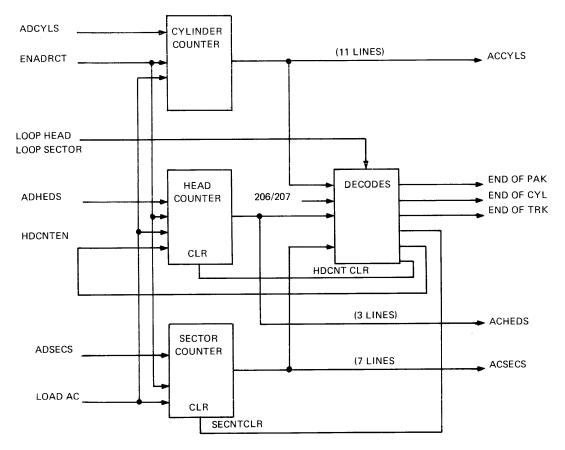

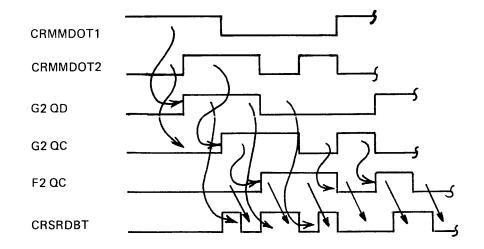

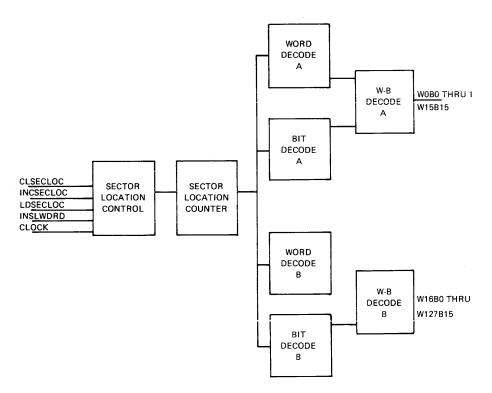

|         | Sector Location Counter                      | 5-3          |         | Stop                                                 | 5-17         |

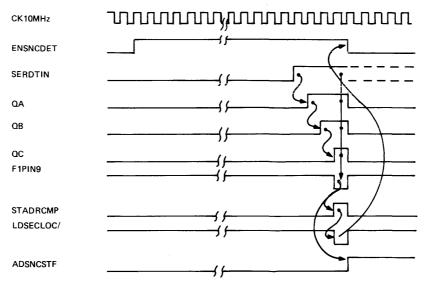

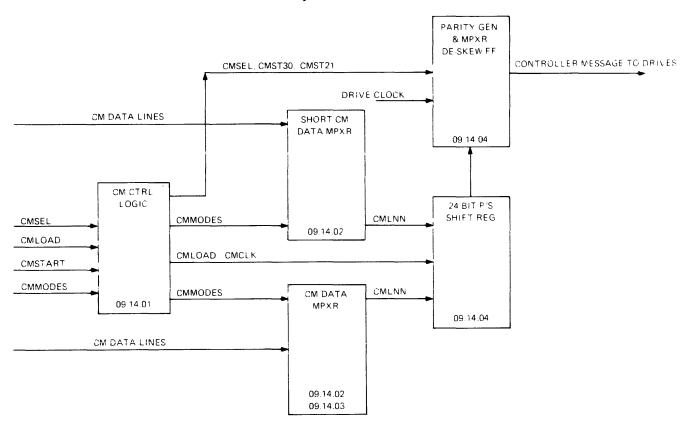

|         | Controller Message Logic                     | 5-3          |         | Loading Sequence                                     | 5-17         |

|         | General Description                          | 5-3          |         | Display Sequence                                     | 5-19         |

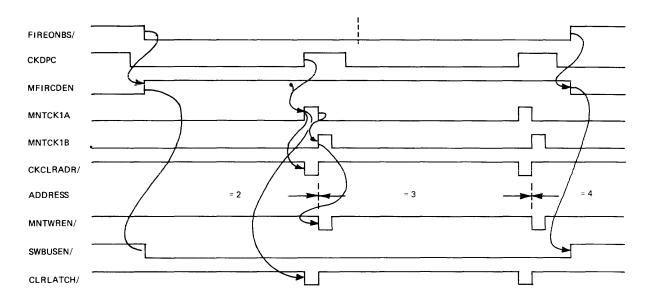

|         | Block Diagram                                | 5-4          |         | Start Sequence                                       | 5-19         |

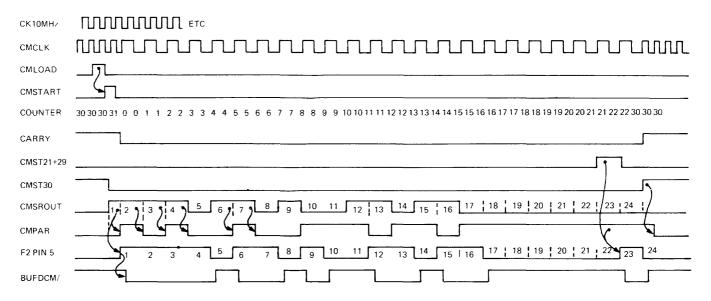

|         | CM Sequence                                  | 5-4          |         | Stop Sequence                                        | 5-19         |

|         | CM Modes                                     | 5-4          |         | Loop OP                                              | 5-20         |

|         | CM Load                                      | 5-5          |         | Result Descriptor Display                            | 5-20         |

|         | CM Start                                     | 5-5          |         | Alternate Operations                                 | 5-20         |

|         | Parity                                       | 5-5          |         | Firecode Storage                                     | 5-20         |

|         | Deskew Buffer                                | 5-6          |         | Send Extended Result Descriptor OP                   | 5-21         |

|         | Select                                       | 5-6          | Section | Title                                                | Page         |

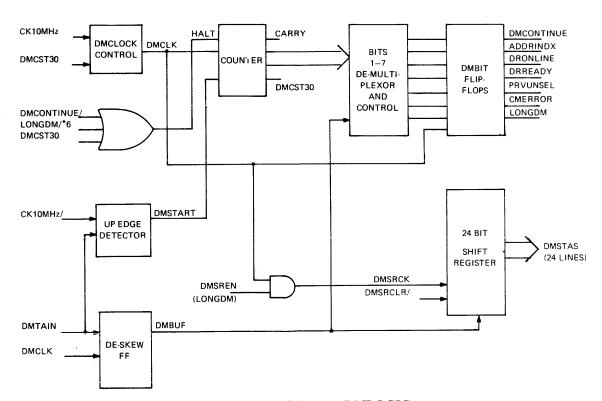

|         | Drive Message Logic                          | 5-6          |         |                                                      | -            |

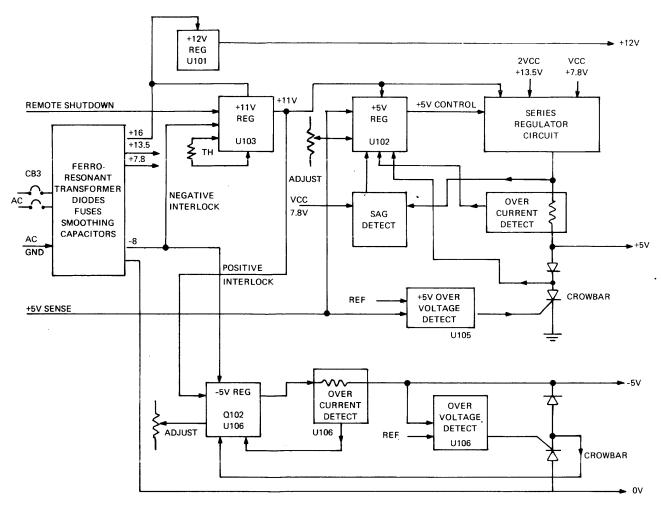

|         | General Description                          | 5-6          | 6       | POWER SUPPLY                                         | 6-1          |

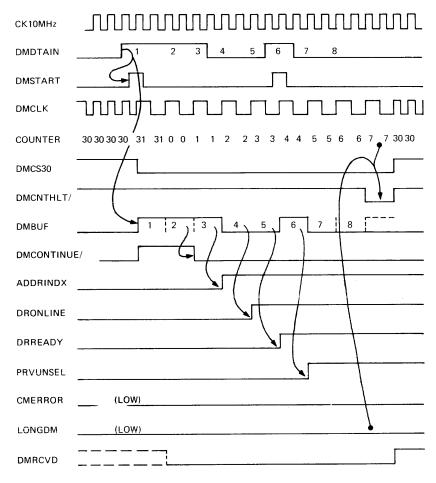

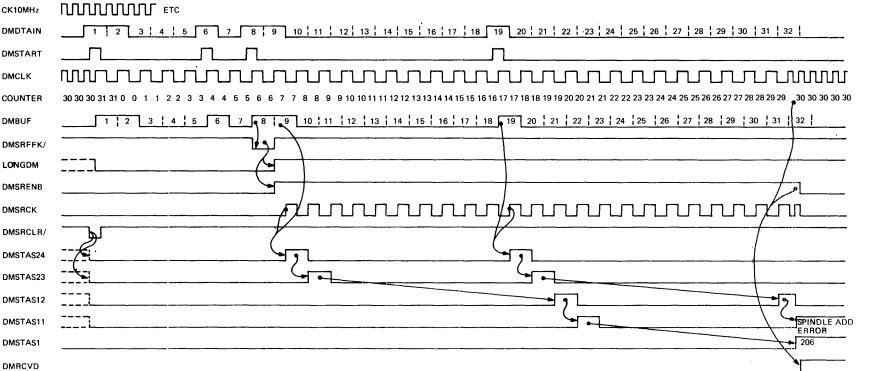

|         | Block Diagram                                | 5-6          |         | General Description                                  | 6-1          |

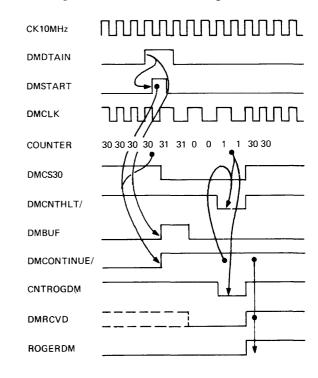

|         | Up-Edge Detector                             | 5-7<br>5-7   |         | Block Diagram                                        | 6-1          |

|         | Counter                                      | 5-7<br>5-7   |         | Primary Power Supply                                 | 6-1          |

|         | DM Clock Control                             | 5-7          |         | +12v Regulator                                       | 6-1          |

|         | Deskew Buffer                                | 5-7          |         | -5v Regulator                                        | 6-1          |

|         | Bits 1-7 De-Multiplexor<br>DM Bit Flip-Flops | 5-7<br>5-7   |         | -5v Overcurrent Detector                             | 6-1          |

|         |                                              | 5-7<br>5-7   |         | Positive Interlock  -5v Overvoltage Detection        | 6-2<br>6-2   |

|         | 24-Bit Shift Register                        | 5-7<br>5-7   |         | +11v Regulator                                       | 6-2          |

|         | DM Sequence<br>Roger DM                      | 5-7<br>5-7   |         | +5v Regulator                                        | 6-3          |

|         | Short DM                                     | 5-7<br>5-7   |         | Series Regulator Circuit                             | 6-3          |

|         | Long DM                                      | 5-8          |         | Current Sharing                                      | 6-3          |

|         | Drive Ready                                  | 5-8          |         | Regulation                                           | 6-3          |

|         | Error Logic                                  | 5-10         |         | +5v Overcurrent Detect                               | 6-3          |

|         | DPEC Exception                               | 5-10         |         | +5v Overvoltage Detect                               | 6-3          |

|         | DM Exception                                 | 5-10         |         | Sag Detect                                           | 6-3          |

|         | <b>r</b>                                     |              |         | -                                                    |              |

|         |                                              |              |         |                                                      |              |

# LIST OF ILLUSTRATIONS

| Figure                                                                                                                                                         | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Page                                                                                                                                                           | Figure                                                                                                                                      | Title                                                                                                                                                                                                                                                                                                                                                                                                                              | Page                                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-1                                                                                                                                                            | Maximum Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1-1                                                                                                                                                            | 4-18                                                                                                                                        | 32-Bit Firecode Register During Write                                                                                                                                                                                                                                                                                                                                                                                              | 4-16                                                                                                                                                  |

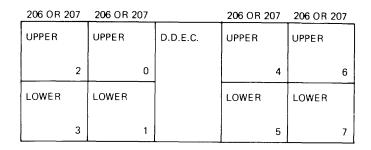

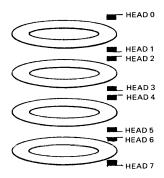

| 1-2                                                                                                                                                            | Pack Configuration (206)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1-1                                                                                                                                                            | 4-19                                                                                                                                        | 24-Bit Shift Register                                                                                                                                                                                                                                                                                                                                                                                                              | 4-16                                                                                                                                                  |

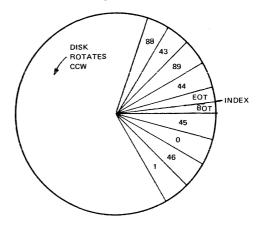

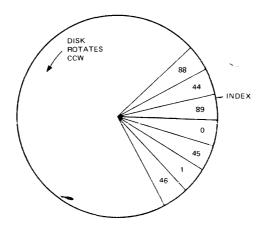

| 1-3                                                                                                                                                            | Interlaced Format (206)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1-2                                                                                                                                                            | 4-20                                                                                                                                        | Firecode Generation Control Signals                                                                                                                                                                                                                                                                                                                                                                                                | 4-17                                                                                                                                                  |

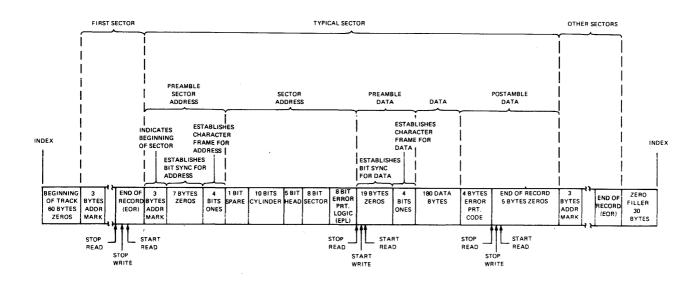

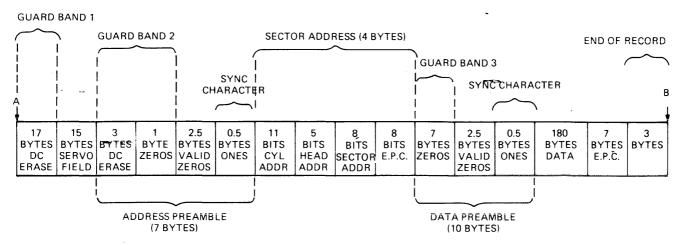

| 1-4                                                                                                                                                            | Track Format (206)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1-2                                                                                                                                                            | 4-21                                                                                                                                        | 32-Bit Register During Read                                                                                                                                                                                                                                                                                                                                                                                                        | 4-18                                                                                                                                                  |

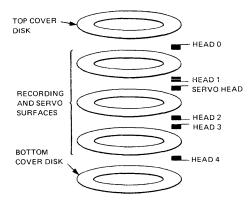

| 1-5                                                                                                                                                            | Platter Configuration (207)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1-3                                                                                                                                                            | 4-22<br>4-23                                                                                                                                | Error Detection Control Signals                                                                                                                                                                                                                                                                                                                                                                                                    | 4-18                                                                                                                                                  |

| 1-6                                                                                                                                                            | Interlaced Format (207)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1-4<br>1-4                                                                                                                                                     | 4-23<br>4-24                                                                                                                                | Block Diagram Error Correction<br>Error Correction Flow Chart                                                                                                                                                                                                                                                                                                                                                                      | 4-19<br>4-20                                                                                                                                          |

| 1-7<br>1-8                                                                                                                                                     | Track Format (207) Interface Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1-6                                                                                                                                                            | 4-2 <del>4</del><br>4-25                                                                                                                    | Error Correction Timing                                                                                                                                                                                                                                                                                                                                                                                                            | 4-20<br>4-21                                                                                                                                          |

| 1-0                                                                                                                                                            | Line Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1-7                                                                                                                                                            | 4-26                                                                                                                                        | Buffer Memory                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-22                                                                                                                                                  |

| 1-10                                                                                                                                                           | Typical Operation Terminated by DPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1-7                                                                                                                                                            | 4-27                                                                                                                                        | Buffer Memory WRITE                                                                                                                                                                                                                                                                                                                                                                                                                | 4-23                                                                                                                                                  |

| 1-11                                                                                                                                                           | Drive Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1-11                                                                                                                                                           | 4-28                                                                                                                                        | Buffer Memory READ                                                                                                                                                                                                                                                                                                                                                                                                                 | 4-23                                                                                                                                                  |

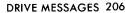

| 1-12                                                                                                                                                           | DM and CM Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1-11                                                                                                                                                           | 5-1                                                                                                                                         | Clock Logic                                                                                                                                                                                                                                                                                                                                                                                                                        | 5-2                                                                                                                                                   |

| 1-13                                                                                                                                                           | Drive Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1-17                                                                                                                                                           | 5-2                                                                                                                                         | Switch to Drive Clock                                                                                                                                                                                                                                                                                                                                                                                                              | 5-2                                                                                                                                                   |

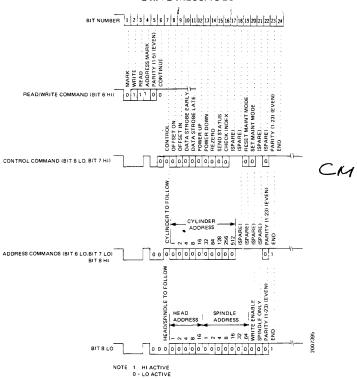

| 1-14                                                                                                                                                           | Spindle Spinup (206 and 207)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1-18                                                                                                                                                           | 5-3                                                                                                                                         | Switch to Local Clock                                                                                                                                                                                                                                                                                                                                                                                                              | 5-2                                                                                                                                                   |

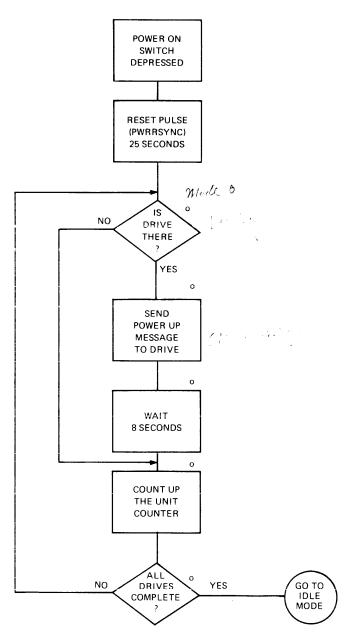

| 1-15                                                                                                                                                           | Initial OP Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1-19                                                                                                                                                           | 5-4                                                                                                                                         | Sector Location Counter                                                                                                                                                                                                                                                                                                                                                                                                            | 5-3                                                                                                                                                   |

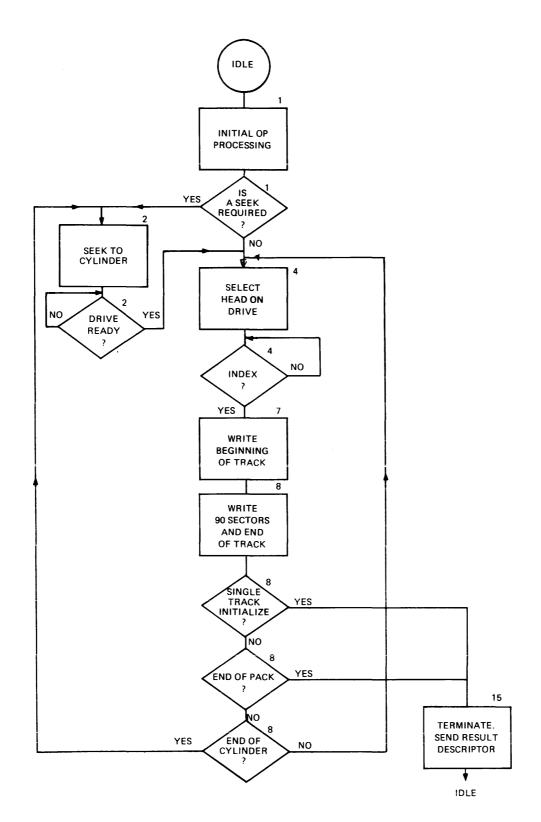

| 1-16                                                                                                                                                           | Initialize (206)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1-20                                                                                                                                                           | 5-5                                                                                                                                         | CM Logic                                                                                                                                                                                                                                                                                                                                                                                                                           | 5-4                                                                                                                                                   |

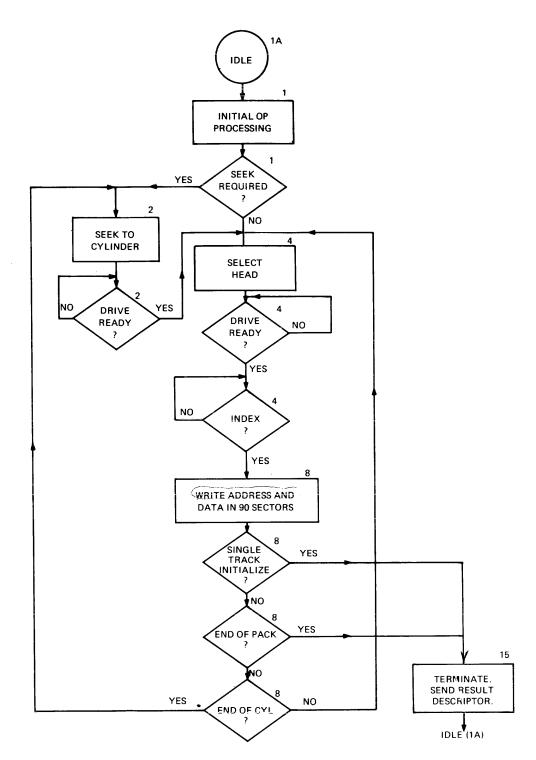

| 1-17                                                                                                                                                           | Initialize (207)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1-21                                                                                                                                                           | 5-6                                                                                                                                         | Long Controller Message                                                                                                                                                                                                                                                                                                                                                                                                            | 5-5                                                                                                                                                   |

| 1-18                                                                                                                                                           | READ, WRITE, or VERIFY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1-23                                                                                                                                                           | 5-7                                                                                                                                         | Block Diagram DMLOGIG                                                                                                                                                                                                                                                                                                                                                                                                              | 5-6                                                                                                                                                   |

| 1-19                                                                                                                                                           | RELOCATE OP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1-24                                                                                                                                                           | 5-8                                                                                                                                         | ROGER DM (1 Bit)                                                                                                                                                                                                                                                                                                                                                                                                                   | 5-7                                                                                                                                                   |

| 1-20                                                                                                                                                           | Test OP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1-25                                                                                                                                                           | 5-9<br>5-10                                                                                                                                 | Short DM (6 Bit)                                                                                                                                                                                                                                                                                                                                                                                                                   | 5-8                                                                                                                                                   |

| 1-21<br>1-22                                                                                                                                                   | Read ERD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1-26<br>1-26                                                                                                                                                   | 5-10                                                                                                                                        | Long DM (32 Bits)                                                                                                                                                                                                                                                                                                                                                                                                                  | 5-9<br>5-11                                                                                                                                           |

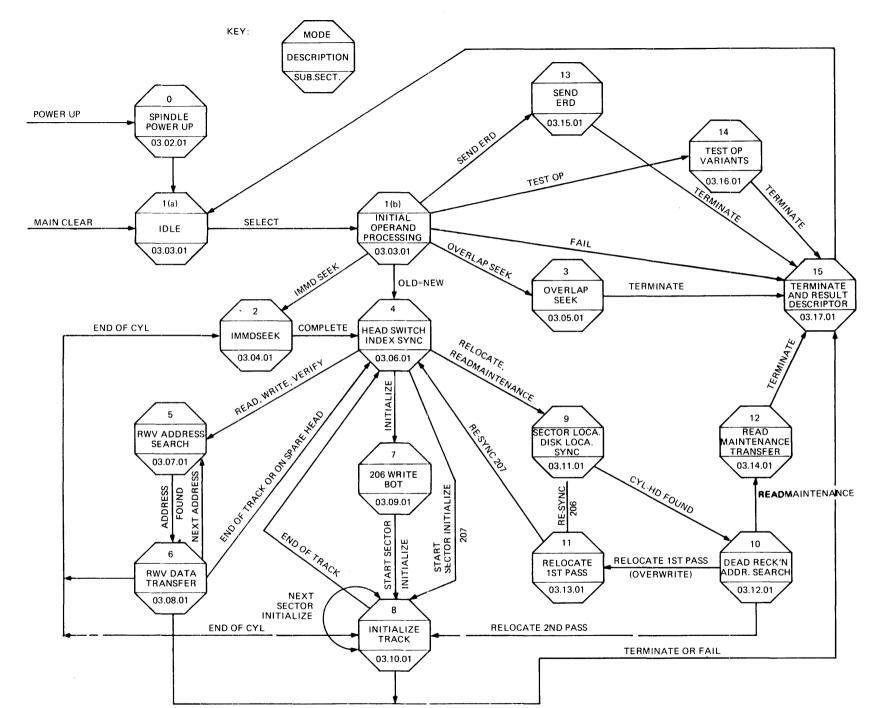

| 2-1                                                                                                                                                            | Read Maintenance Overall Operation Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-2                                                                                                                                                            | 5-11<br>5-12                                                                                                                                | DMERD Flip-Flops RD and ERD LOGIC                                                                                                                                                                                                                                                                                                                                                                                                  | 5-11<br>5-11                                                                                                                                          |

| 2-1                                                                                                                                                            | Mode 0, Spindle Spinup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-2<br>2-3                                                                                                                                                     | 5-12<br>5-13                                                                                                                                | ERD Control Counter                                                                                                                                                                                                                                                                                                                                                                                                                | 5-11                                                                                                                                                  |

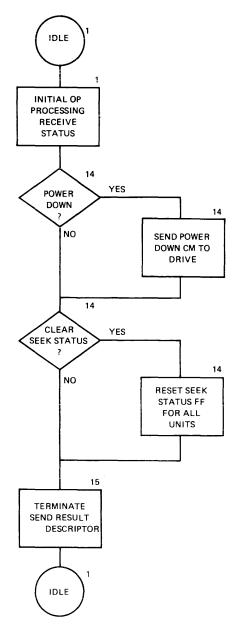

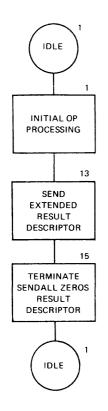

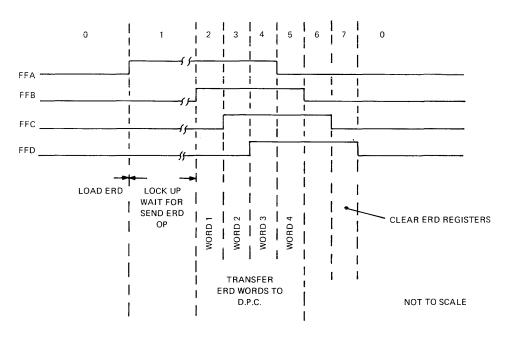

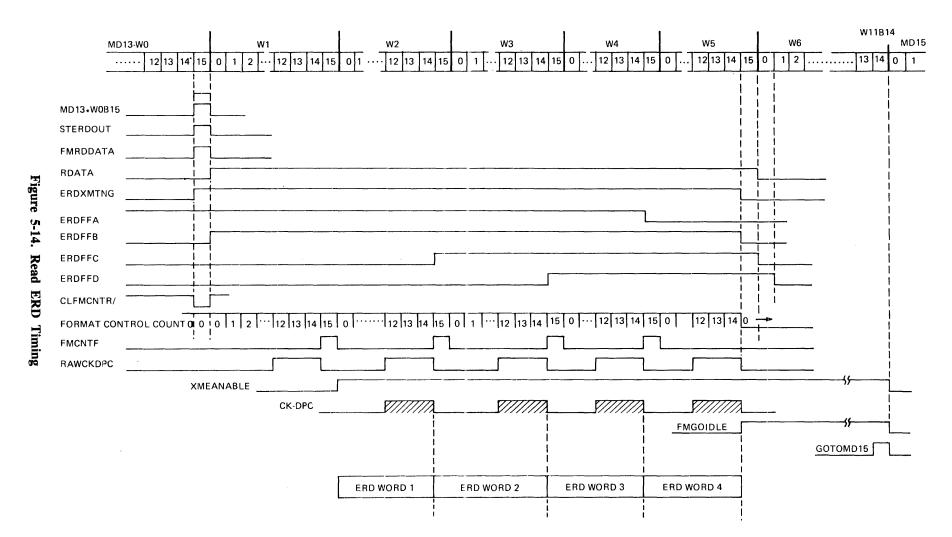

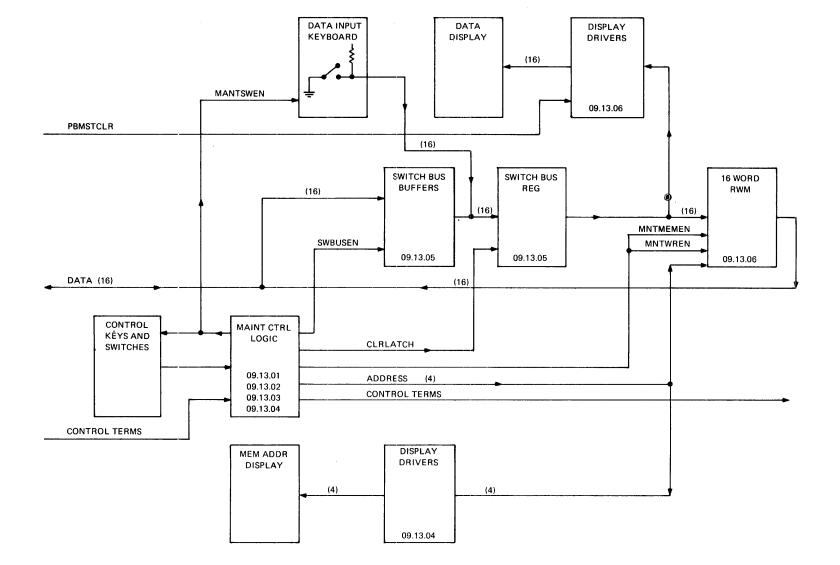

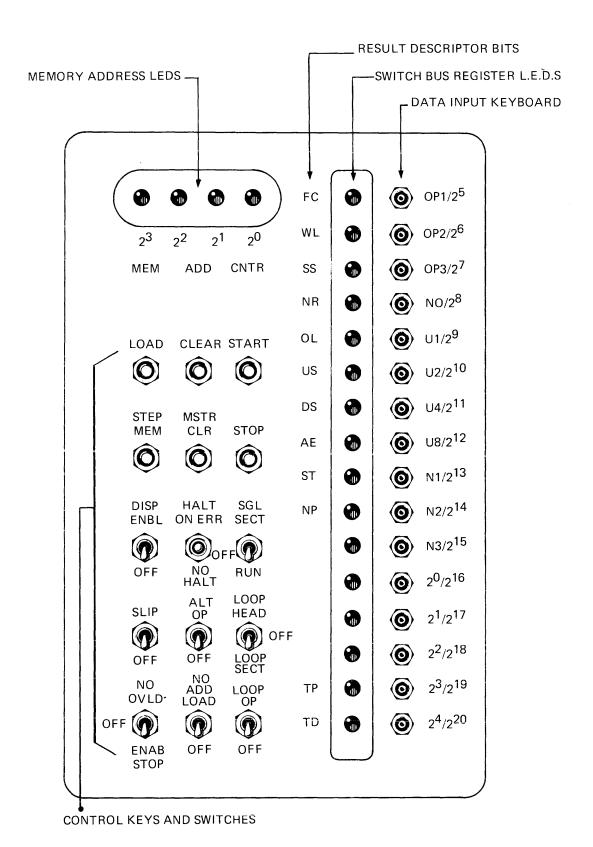

| 2-3                                                                                                                                                            | Mode 1, Initial OP Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-5                                                                                                                                                            | 5-13<br>5-14                                                                                                                                | Read ERD Timing                                                                                                                                                                                                                                                                                                                                                                                                                    | 5-14                                                                                                                                                  |

| 2-4                                                                                                                                                            | Mode 2, Seek Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-6                                                                                                                                                            | 5-15                                                                                                                                        | Maintenance Logic                                                                                                                                                                                                                                                                                                                                                                                                                  | 5-15                                                                                                                                                  |

| 2-5                                                                                                                                                            | Mode 3, Overlap Seeks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2-7                                                                                                                                                            | 5-16                                                                                                                                        | Maintenance Panel                                                                                                                                                                                                                                                                                                                                                                                                                  | 5-16                                                                                                                                                  |

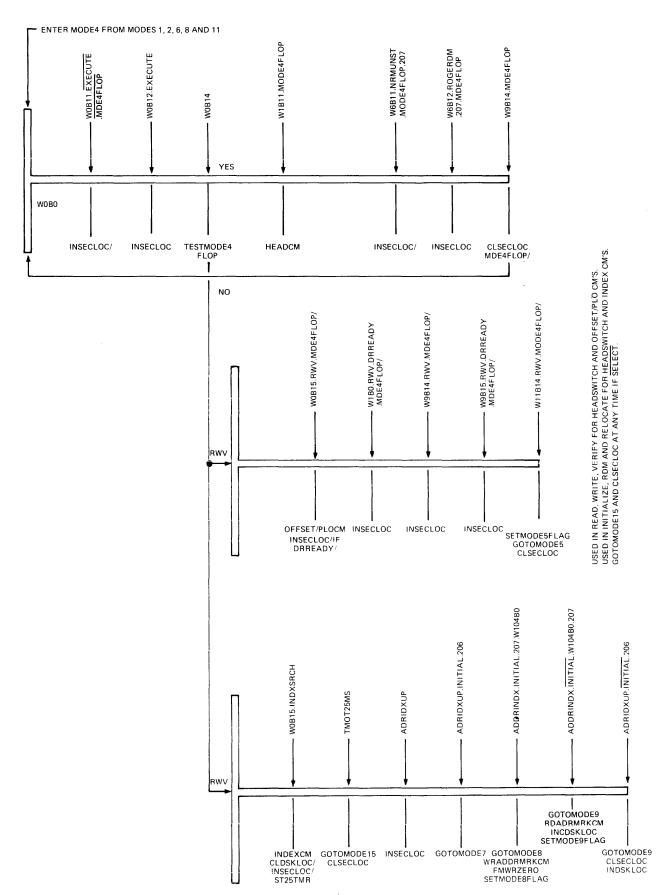

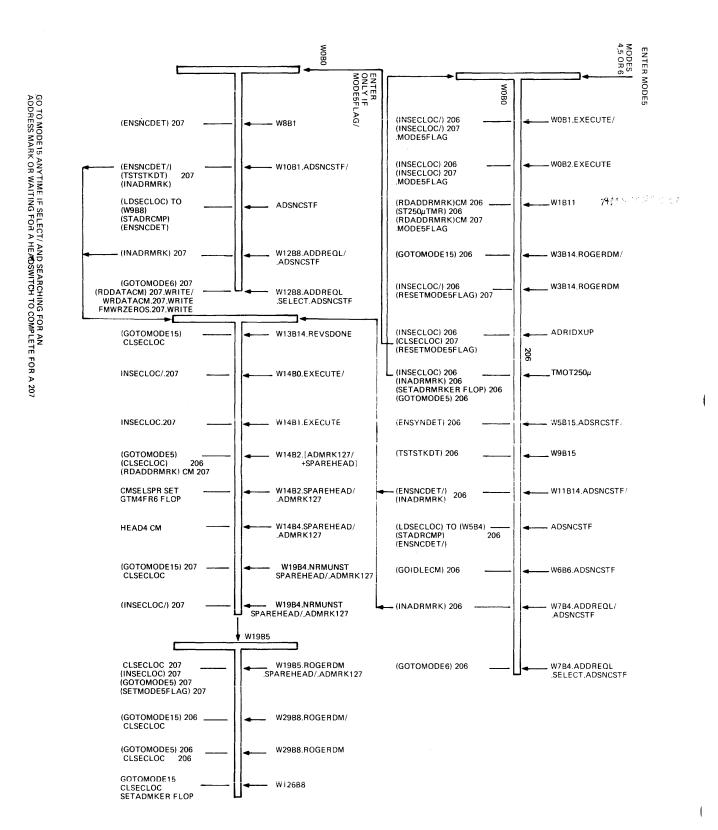

| 2-6                                                                                                                                                            | Mode 4, Headswitch/INDXSRCH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2-8                                                                                                                                                            | 5-17                                                                                                                                        | Load Maintenance Memory                                                                                                                                                                                                                                                                                                                                                                                                            | 5-18                                                                                                                                                  |

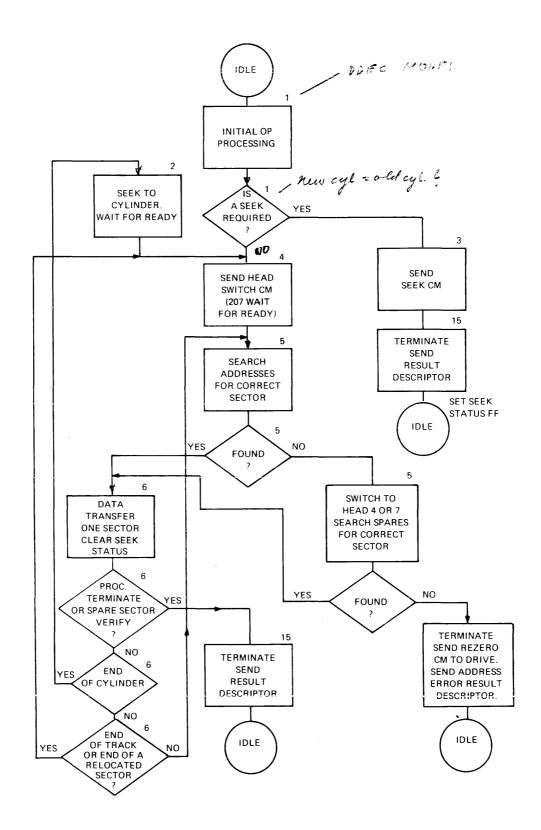

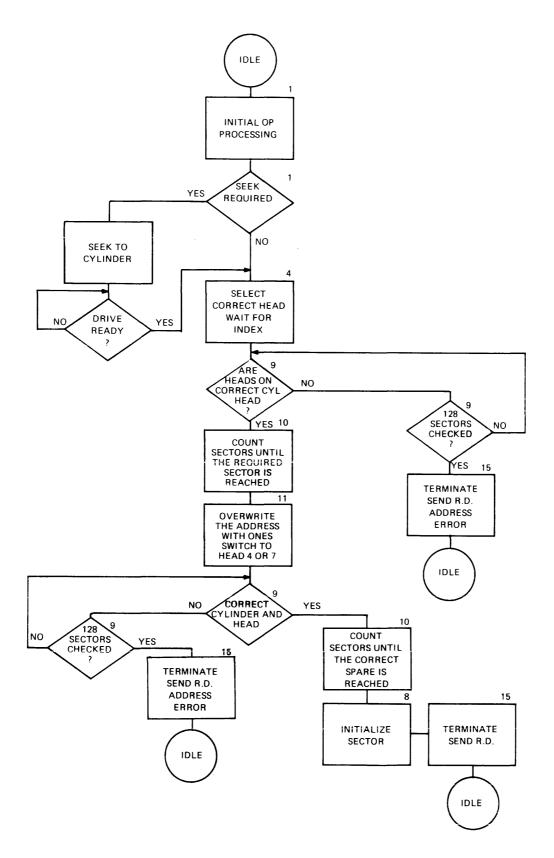

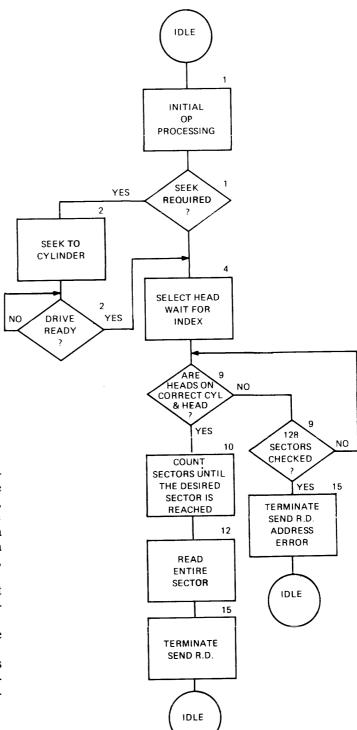

| 2-7                                                                                                                                                            | Mode 5, RWV Address Search                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-10                                                                                                                                                           | 5-18                                                                                                                                        | Display Sequence                                                                                                                                                                                                                                                                                                                                                                                                                   | 5-18                                                                                                                                                  |

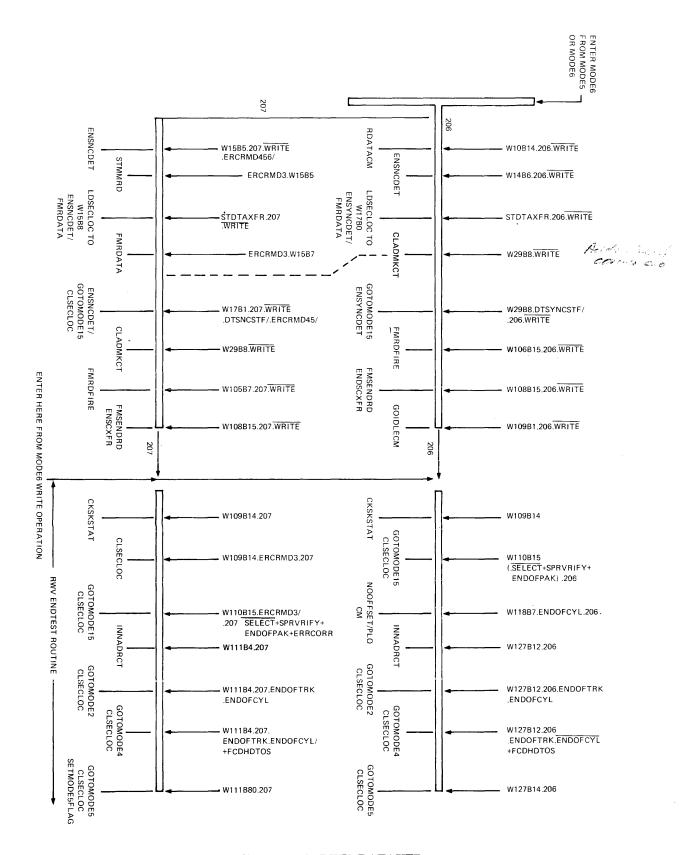

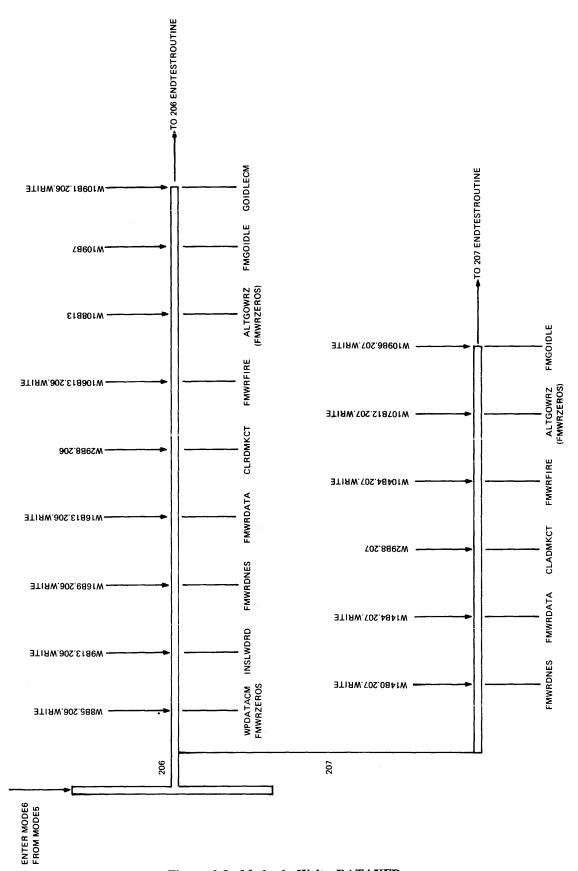

| 2-8                                                                                                                                                            | Mode 6, RWV DATAXFR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-13                                                                                                                                                           | 5-19                                                                                                                                        | Start Sequence                                                                                                                                                                                                                                                                                                                                                                                                                     | 5-19                                                                                                                                                  |

| 2-9                                                                                                                                                            | Mode 6, Write DATAXFR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2-14                                                                                                                                                           | 5-20                                                                                                                                        | Result Descriptor Display                                                                                                                                                                                                                                                                                                                                                                                                          | 5-20                                                                                                                                                  |

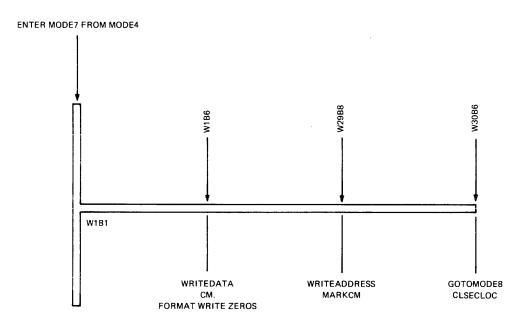

| 2-10                                                                                                                                                           | Mode 7, Write BOT OP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2-17                                                                                                                                                           | 5-21                                                                                                                                        | Firecode Storage                                                                                                                                                                                                                                                                                                                                                                                                                   | 5-21                                                                                                                                                  |

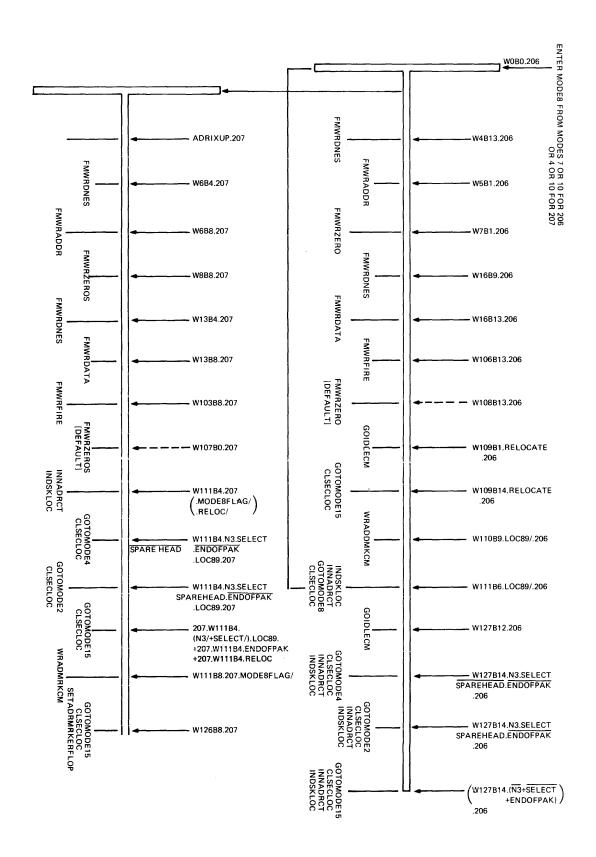

| 2-11                                                                                                                                                           | Mode 8, Track Format Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-18                                                                                                                                                           | 5-22                                                                                                                                        | ERD Write to Maintenance Memory                                                                                                                                                                                                                                                                                                                                                                                                    | 5-22                                                                                                                                                  |

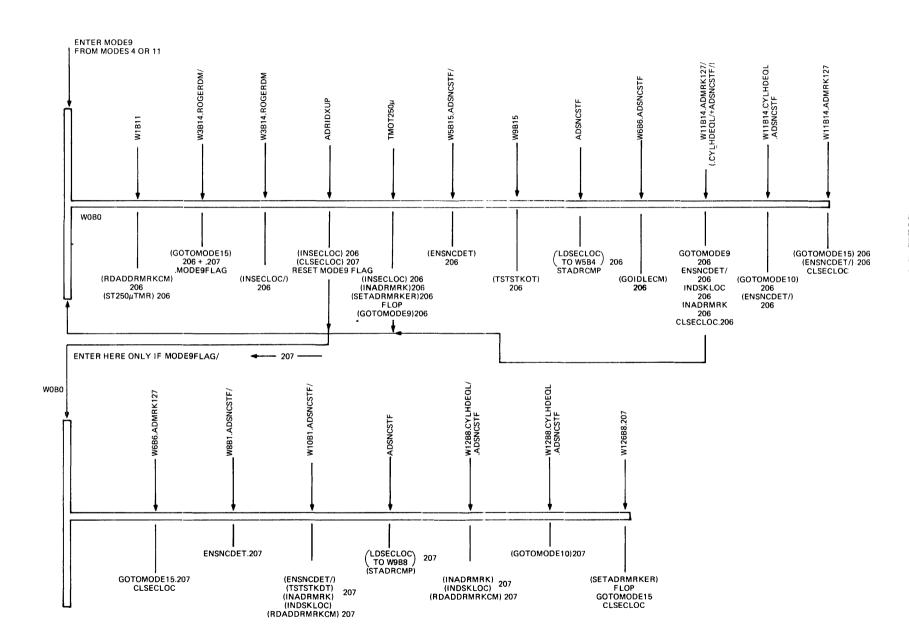

| 2-12                                                                                                                                                           | Mode 9, DSK LOC SYNC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2-22                                                                                                                                                           | 6-1                                                                                                                                         | Power Supply Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                         | 6-2                                                                                                                                                   |