# THE BURROUGHS D 825 MODULAR DATA PROCESSING SYSTEM

$\Box$

Π

D

0

Γ

E C

# **PROGRAMMING MANUAL**

31 JANUARY 1962

Contract No. Nonr 3521 (00) (x)

U.S. NAVAL RESEARCH LABORATORY WASHINGTON D.C.

SUBMITTED TO

-Burroughs Corporation -

# CONTENTS

| SECTION 1 - INTRODUCTION                      | • •   | •            | •            | •   | •                      | •         | •  | •  | •   | •  | 1 |

|-----------------------------------------------|-------|--------------|--------------|-----|------------------------|-----------|----|----|-----|----|---|

| SYSTEM ORGANIZATION                           | •     |              | •            | •   | •                      | •         |    | •  | •   | •  | 1 |

| SYSTEM OPERATION                              | •     |              | •            | •   |                        | •         |    | •  | •   |    | 1 |

| Parallel Operations .                         | •     |              | •            | •   | •                      |           |    |    |     |    | 1 |

| Operational Structure .                       | •     | •            | •            |     |                        | •         |    |    |     |    | 1 |

| Modes of Operation<br>Automatic Interrupt Cap | •     | •            | •            |     |                        | •         | •  | •  |     |    | 1 |

| Automatic Interrupt Cap                       | abili | ty           |              |     |                        |           |    | •  |     |    | 1 |

| COMPUTER MODULES D82                          | 25-1  | •            | •            | •   | •                      | •         | •  | •  | •   | •  | 1 |

| SECTION 2 - THE FEATURES (                    | OF D  | 825          | Ρ            | RO  | GR                     | AM        | MI | NG | •   | •  | 2 |

| VARIABLE LENGTH INSTE                         | RUCT  | וסוי         | NS           |     |                        |           | _  |    |     |    | 2 |

| OPERAND STACK                                 |       |              |              |     | •                      |           |    | •  | •   | •  | - |

| INDEXING                                      |       |              |              |     |                        |           |    |    |     |    |   |

| RELATIVE ADDRESSING A                         |       |              |              |     |                        |           |    |    | ING |    |   |

| FIELD DEFINED INSTRUC                         |       |              |              |     |                        |           |    |    |     |    |   |

|                                               |       |              |              | •   |                        |           |    |    |     |    | - |

| INTERRUPT SYSTEM                              | •     |              |              |     |                        |           |    |    |     |    | 2 |

| SECTION 3 - THE STRUCTURE                     | OF    | PR           | OG           | RA  | M                      | SYI       | LL | AB | LE  | s. | 3 |

| O-OPERATOR SYLLABLE.                          | •     |              |              | •   |                        |           | •  |    |     |    | ç |

| X-INDEX SYLLABLE                              |       |              |              |     |                        | •         | •  |    |     |    | 3 |

| M-MEMORY ADDRESS SYI                          | LAE   | BLE          | •            |     | •                      |           |    | •  |     |    |   |

| B-BRANCH ADDRESS SYL                          | LABI  | $\mathbf{E}$ | •            |     |                        |           |    |    |     |    |   |

| T-THIN FILM ADDRESS SY                        | LLA   | BL           | $\mathbf{E}$ |     |                        |           |    | •  |     |    |   |

| IV-INDEX INCREMENT VA                         | RIAN  | IT S         | SY I         | LL  | AB                     | LE        |    |    |     |    |   |

| Ia-INDEX INCREMENT AM                         | OUN   | тs           | YI           | LLA | BI                     | ${}_{-}E$ | •  | •  |     |    |   |

| S-SHIFT SYLLABLE                              | •     | •            | •            | •   |                        | •         | •  | •  |     |    | 3 |

| Vt-TRANSMIT VARIANT SY                        | YLLA  | ABI          | Æ            |     |                        | •         | •  |    |     |    |   |

| L-LOGICAL MACHINE CO                          | NDIT  | ION          | 1 S          | YL  | LA                     | BL        | E  |    |     |    | 3 |

| F-FIELD DEFINITION SYL                        |       |              |              |     |                        |           |    |    |     |    | 3 |

| C-CHARACTER SYLLABLE                          |       |              |              |     |                        |           |    |    |     |    | 3 |

| Ja-SUBROUTINE JUMP AD                         |       |              |              |     |                        |           |    |    |     |    | ļ |

| Ji-SUBROUTINE JUMP INC                        | CREN  | IEN          | <b>IT</b>    | SY  | $\mathbf{L}\mathbf{L}$ | AB        | LE | •  |     |    | 3 |

| Rc-REPEAT COUNT SYLL                          | ABL   | F.           |              |     |                        |           |    |    |     |    | 3 |

# CONTENTS (Cont'd)

| SECTION 3 - (continued)                    | Page  |

|--------------------------------------------|-------|

| RI-REPEAT INCREMENT SYLLABLE.              | 3-9   |

| IO-I/O SYLLABLE                            | 3-10  |

| Vs-SPECIAL REGISTER AND COMPUTER INTERRUPT |       |

| VARIANT SYLLABLE                           |       |

| SECTION 4 - D825 INSTRUCTIONS              | 4-1   |

| FIXED POINT ARITHMETIC INSTRUCTIONS        | 4-3   |

| FLOATING POINT ARITHMETIC INSTRUCTIONS     |       |

| DECISTED MANIDIL ATION AND DATA MONTHS     |       |

| INSTRUCTIONS                               | . 4-9 |

| UNPACKING AND PARTIAL WORD INSTRUCTIONS .  | 4-14  |

| PROGRAM CONTROL INSTRUCTIONS.              |       |

| INTERRUPT CONTROL INSTRUCTIONS             |       |

| SECTION 5 - INPUT/OUTPUT PROGRAMMING       | 5-1   |

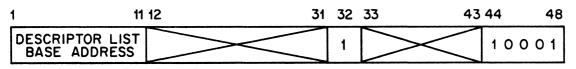

| DESCRIPTOR TYPES                           |       |

| DESCRIPTOR FUNCTIONS                       | 5-2   |

| SETUP DESCRIPTOR FORMAT                    |       |

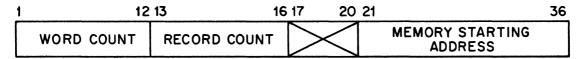

| COMMAND DESCRIPTOR FORMAT                  |       |

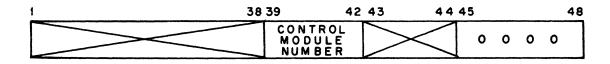

| IN-PROCESS DESCRIPTOR FORMAT               | 5-5   |

| RESULT DESCRIPTOR FORMAT.                  | 5-6   |

| RELEASE DESCRIPTOR FORMAT                  |       |

| SECTION 6 - THE D825 INTERRUPT SYSTEM      | 6-1   |

| PRIMARY POWER FAILURE                      | 6-3   |

| COUNT REAL TIME                            | 6-3   |

| RESTART AFTER PRIMARY POWER FAILURE        |       |

|                                            | 6-4   |

|                                            | 6-4   |

| INTERRUPT COMPUTER N                       | 6-4   |

| REAL-TIME CLOCK OVERFLOW                   | 6-4   |

| WRITE OUT OF BOUNDS                        | 6-4   |

| ILLEGAL INSTRUCTION                        |       |

# CONTENTS (Cont'd)

| SECTION 6 - (continued)                       |   |   | Page |

|-----------------------------------------------|---|---|------|

| PARITY ERROR                                  | • | • | 6-5  |

| ARITHMETIC OVERFLOW                           | • | • | 6-5  |

| HALT                                          | • | • | 6-6  |

| PROCESSING OF THE INTERRUPT CONDITIONS .      | • | • | 6-6  |

| APPENDIX A - D825 INSTRUCTION EXECUTION TIMES | • | • | A-1  |

| APPENDIX B - D825 TIMING ALGORITHMS           | • | • | B-1  |

| APPENDIX C - MAP OF THIN FILM REGISTERS       | • | • | C-1  |

| APPENDIX D - INDEX TO D825 INSTRUCTIONS       |   |   | D-1  |

.

#### SECTION 1

#### INTRODUCTION

This programming manual describes the machine language programming techniques used with the D825 Modular Data Processing System. This introduction includes system organization and operation to familiarize the programmer with the D825, and succeeding sections present the programming features of the D825, the structure of the instruction syllables, the operation codes, input/output programming, and the interrupt system. In addition, there are four appendices; Appendix A gives the D825 execution times, Appendix B gives the timing algorithms with an example, Appendix C gives the addressing structure for the thin film registers, and Appendix D is an index of operation codes.

#### SYSTEM ORGANIZATION

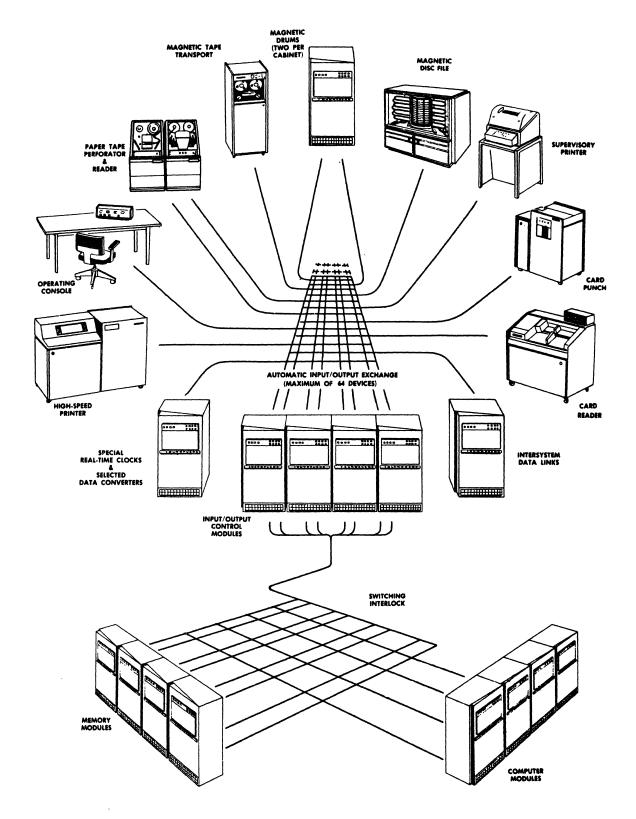

The Burroughs D825 Modular Processor is organized for a specific application in an appropriate complement of Computer Modules, Memory Modules, Input/Output (I/O) Control Modules, and a common exchange of I/O devices. Physically, a complete system, including power supplies, is housed in a number of standard cabinets, an operating console, various input/output equipments, and off-line test equipment. The general system organization is illustrated in figure 1-1.

The Computer Module arithmetic unit operates in parallel, but receives data from the switching interlock in serial-parallel form. A thin-film register storage and operand stack in each Computer Module operates at the 3 megacycle clock rate and greatly reduces the required accesses to Memory Modules. The command list of the computer includes binary fixed and floating point arithmetic instructions with the computer organization oriented toward efficient

Figure 1-1. D825 System Organization

floating-point computation. The addressing structure of the computer has been designed to incorporate all of the power of a threeaddress machine. (Less than the maximum of three addresses can be processed with each instruction, with commensurate savings in instruction time and program storage.)

The Memory Module is a linear-select (word-organized), randomaccess, ferrite-core memory which was once available only in computers designed for extreme environments. Each module contains 4096 words of 48 bits plus parity, and a fully expanded system of 16 modules provides 65,536 words of memory.

I/O Control Modules, consist essentially of control and data manipulation registers and associated decoding and timing circuits. Each is capable of controlling any device of the I/O complement, and there can be as many simultaneous I/O operations as there are I/O Control Modules. The I/O exchange automatically connects control modules with specified I/O devices on command from computer modules. The console, effectively an I/O device, displays system status to the operator and permits him to effect inquiries and manual interrupts.

#### SYSTEM OPERATION

The D825 adapts instantly to real-time influence, to new programs, to changes in program priorities, and to manual or automatic interrupt signals. Its operational structure permits broad programming flexibility and efficient operation and program storage. Man/machine communication is comprehensive.

#### Parallel Operations

Each D825 Computer Module has exclusive use of a data transfer bus by which it can communicate, via the switching interlock, with any memory module in the system. The I/O Control Modules of an I/O exchange share a single bus, and two exchanges, each on a separate bus, are available as an option.

Memory may be used concurrently by all computer and I/O exchange buses. If two or more buses simultaneously address the same Memory Module, the switching interlock automatically resolves the conflict according to priority and queues the lower priority items. One functional bus gains immediate access while the other is delayed only until completion of the first memory transfer.

#### **Operational Structure**

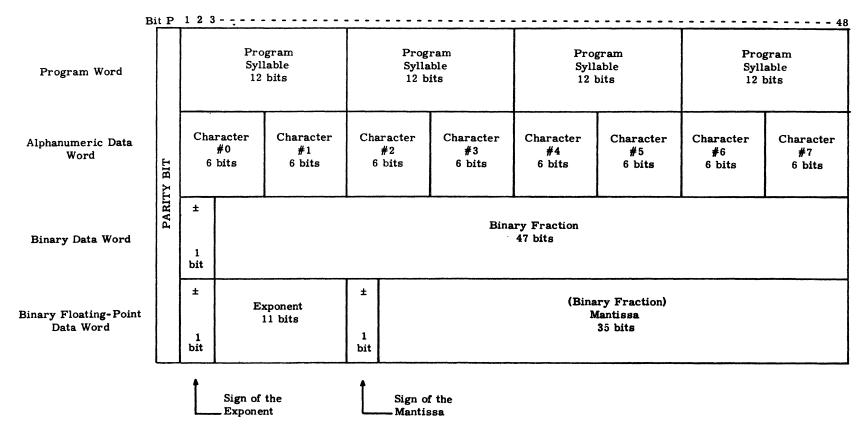

The D825 has been designed with a binary data word of sufficient length (49 bits including sign and parity) for almost all computing problems, and for really useful binary floating-point computation (36 bits of mantissa, including sign, and 12 bits of characteristic or exponent). This provides as much resolution for floating-point arithmetic as many large-scale computing systems offer in fixedpoint arithmetic. The D825 alphanumeric data word contains eight characters.

Operands may be called from memory or from a four-position stack of operand registers within the thin-film storage of the computer. The results of operations can be stored in memory or in the operand stack for subsequent processing at the will of the programmer.

The operand stack is a device, extremely useful in arithmetic and processing operations, which reduces the number of references to main memory by holding partial or intermediate results of computation. The stack operates in two modes: normal and hold. The hold mode is useful for list manipulation and for repeated use of a number.

The first syllable of an instruction supplies the operation code and three address indicators. The address indicator provides choice between fetching the operand from the stack or the memory, and indicates whether the stack mode is normal or "hold" and whether the memory address is to be indexed or not. Address syllables or syllable strings follow the operation syllable for each memory accesses called out. Each memory address syllable contains an eleven-bit literal address and an indirect address bit. The literal address is added to the 16-bit base address register in order to refer to an area of memory known as the direct-address area.

The contents of the direct-address area location may be either an operand or another memory address. Indirect addressing of any desired number of levels is available by this technique.

Any or all of the three operand addresses which can be developed for each instruction may be modified by three of fifteen thin-film index registers. This capability, combined with the powerful indirect addressing capability of this system, provides immensely flexible address control. A full discussion of D825 programming features is presented in Section 2.

#### Modes of Operation

The D825 Modular Data Processing System has two modes of operation, normal and control. The control mode has a slightly larger order code than the normal mode, in that several special control instructions are necessary in addition to the normal instructions. The interrupt system provides the means of transposing operation from the normal mode to the control mode, either by computer instruction or by the occurrence of an event internal or external to the computer. When a computer is in the control mode, it can adjust its mask register to accept or ignore certain of these events.

Object programs are performed in the normal mode, and control programs, such as an Automatic Operating and Scheduling Program, are performed wholly, or in part, in the control mode. Control mode is always used for transmitting I/O descriptors.

#### Automatic Interrupt Capability

The interrupt system provides the facility for interrupting the "normal" data processing mode of operation of the computer system. It recognizes programmed and hardware-generated interrupt conditions caused by situations arising in the execution of a program; recognizes manually-initiated requests and automated external requests for communication with the computer system; and also recognizes equipment faults such as parity errors, illegal operations, and primary power failures.

In general, an interrupt condition causes transfer of control of the interrupted computer from the object program to an Automatic Operating and Scheduling Program (AOSP). Interpreting the interrupt condition at hand, the AOSP transfers control to the appropriate routine for handling the condition. When the interrupt condition has been satisfied, control is returned to the object program.

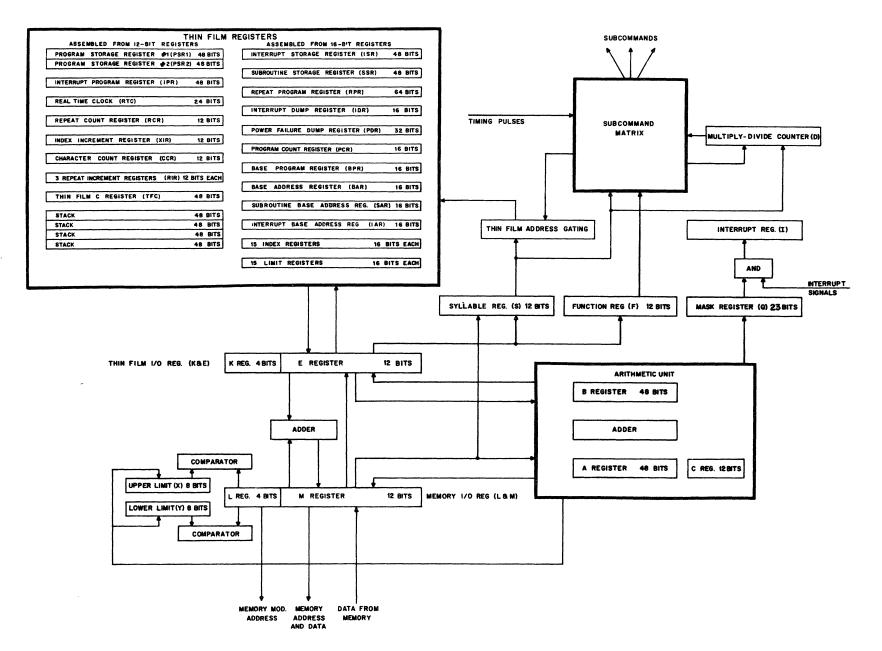

Figure 1-2. Computer Module Block Diagram

1-6

#### COMPUTER MODULES D825-1

The system can accommodate up to four Computer Modules. Each Computer Module consists of three functional areas. The first area, the arithmetic unit, is made up of three registers A, B, and C with associated controls. The second area is a set of 53 registers contained in a small thin-film magnetic storage. The third area is the control section which includes capability for indexing, address accumulation, indirect addressing, and the command and subcommand matrices. Figure 1-2 is a block diagram of the Computer Module showing all functional areas.

The memory I/O register (L and M) is a multipurpose register. To initiate a memory transfer, the memory address is transferred to the memory I/O register. The portion of this address that is the L register designates a specific Memory Module and is sent as dc levels to the switching interlock circuitry of the memory trunk. Address data for the Memory Module and information words entering the Computer Module from the memory module are transmitted through the M register 12 bits at a time.

The A register, B register and C register are the working arithmetic registers of the Computer Module. The A and B registers with associated adder circuitry perform the actual arithmetic operations. The A register is capable of shifting in optimum combinations of 12, 6, and 1 places to the right and iteratively 1 place to the left.

The function register (F) is a 12-bit register that holds the operator syllable being executed and provides the dc levels for driving the command and sub-command matrices.

The Multiply/Divide counter (D) controls the number of add or subtract cycles to be executed during multiply or divide operations. The counter also controls the number of shifts to be executed during an instruction.

The five operand registers include four operand stack registers which make up the thin-film operand stack, and the thin-film C (TFC) register which is used to store the least significant half of a doublelength product and the remainder for division. The two program-storage registers (PSR1 and PSR2) provide storage for eight instruction syllables and permit overlapped instruction fetch during long instructions.

The base address register (BAR) holds the base address of the data direct-address area. The base program register (BPR) holds the base address of the program address area. The program count register (PCR) holds the address of the last instruction (most recently fetched from memory) in the program-storage registers.

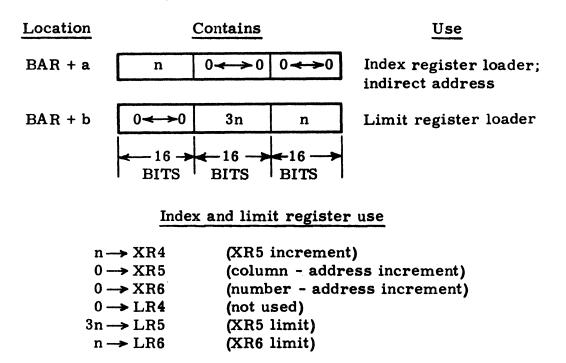

There are 15 index registers and 16 comparison limit registers. Any three of the index registers may be addressed by each index address syllable and used to modify each operand address. The index registers may be incremented, decremented, and compared in six different ways with the comparison limit registers. The index increment register (XIR) is used by the logic during the execution of the index increment instruction.

The contents of the real-time clock (RTC), a 24-bit register, is automatically read out and incremented once every 10 milliseconds. The real-time clock may be sampled and set by the program. An interrupt is initiated when the count overflows.

The character count register (CCR) is used by the character search instruction to indicate the character position last examined for the specified character.

When the repeat instruction is used, the repeat program register (RPR) provides storage for the four syllables of the program word being repeated; the repeat count register (RCR) contains the number of iterations yet to be performed; three repeat increment registers (RIR) contain the increments corresponding to the three addresses of the instruction being repeated.

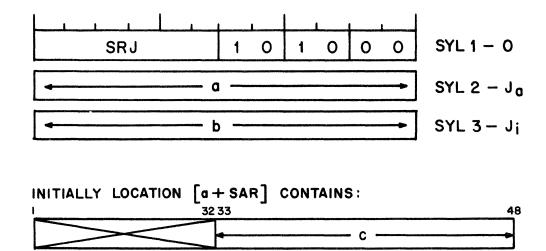

The subroutine base address register (SAR) contains the base address of a list of subroutine addresses. When a subroutine is executed, the subroutine storage register (SSR) holds subroutine return information, i. e., the former contents of the BAR, BPR, and PCR.

The interrupt system registers provide storage for data in the operational registers in the event of an interrupt. The interrupt base address register (IAR) contains the base address of the interrupt routines; the contents of this thin film register are protected during the normal operation mode. The interrupt storage register (ISR) holds interrupt return information, i.e., the former contents of the BAR, BPR, and PCR. The interrupt program register (IPR) provides storage for the contents of the presently addressed PSR, during interrupt. The interrupt dump register (IDR) holds the PSR and repeat controls for interrupt return. The power failure dump register (PDR) holds the contents of the control flip-flops and the flip-flop interrupt register in the event of a power failure.

There is an over-under voltage detector which will detect and signal excursions of primary power beyond fixed voltage limits. The out-oftolerance signal causes the computer module to store sufficient information to restart the program without loss of data. Provision is made for automatic program restart by automatically reloading stored data back into the flip-flop registers. The power supplies themselves have a sufficiently long time constant to protect the hardware, program, and data from all primary power transients and failures, and allows continuation of the program when stable primary power is restored.

The interrupt system handles interrupts arising from such conditions as arithmetic overflow, running down of the real-time clock, illegal orders, parity errors, external input-output requests, and I/O result situations, etc. Each Computer Module has an interrupt register which can be set through the interrupt mask register. When a particular condition has set a one at some bit position in the interrupt register, a program interrupt occurs. This interrupt stops the program being executed, stores sufficient registers to allow continuation of the interrupted program at a later time, and transfers control to a routine in an AOSP to service the interrupt.

、 、

#### **SECTION 2**

#### THE FEATURES OF D825 PROGRAMMING

The flexibility of D825 machine language programming is a result of the following programming features which are discussed in this section.

- Variable-Length Instructions

- A Four Level Operand Stack

- Single and Multiple Indexing

- Relative Addressing and Indirect Addressing

- Field-Defined Instructions

- Subrountine Control

- A Comprehensive Interrupt System

#### VARIABLE-LENGTH INSTRUCTIONS

The combination of two unique features - three address programming and variable length instructions - in the D825 yields new efficiency and versatility in programming. The three address capability takes advantage of the fact that many fundamental operations involve three factors, and therefore may need three storage locations: one each for the two operands and the result. The typical example is "add A and B; store the result in C". Single address programming, with each of the three factors using a separate storage location, requires three instructions to complete the operation: (1) clear and add A, (2) add B, and (3) store in C. There is a large group of such operations readily adaptable to three address programming; but there is an equally large group of operations that require fewer than three addresses. If all instructions were to be of exactly three addresses, the program would be wasteful, and nothing would be gained by three address programming over conventional single address programming. For this reason, variable length instructions are allowed.

The program in memory consists of blocks of 48-bit program words; program words, in turn, consist of four units of information each. These four 12-bit units are called "syllables". A syllable can be of a variety of different formats, and these special formats are determined by the information that a specific instruction needs, such as an address or an instruction variant. In fact, the operation code of the instruction itself occupies one of the syllables, known as the operator syllable. The formats and uses of the different syllables will be discussed in Section 3 in more detail.

The variability of the system comes from the fact that the instructions are considered as "strings of syllables", and these strings can vary in length from one to seven syllables per instruction. Also, an instruction can begin at any syllable location in the memory word, and end with this or any succeeding syllable of the memory word, or can continue on into as many as two succeeding memory words.

Although a particular instruction requires certain addresses, the top of the operand stack may be implied as one (or more) of the addresses and therefore needs no syllable(s) to identify it. On the other hand, certain addresses may be indexed and therefore need two syllables to identify the address. Whatever the case may be it is indicated by three address tags of two bits each which appear in the operator syllable, along with the operation code of the instruction.

There are two important things to remember about syllable strings. (1) The first syllable of an instruction is always an operator syllable, and will identify any syllables that may follow. (2) Individual syllables are not addressable, although program words are. For this reason a branch refers to the first syllable of a memory word, and will execute that particular syllable as an operator syllable (i.e., the beginning of a syllable string). Therefore when a branch is planned, the operator syllable of the instruction to be executed must be the first syllable of the memory word.

#### **OPERAND STACK**

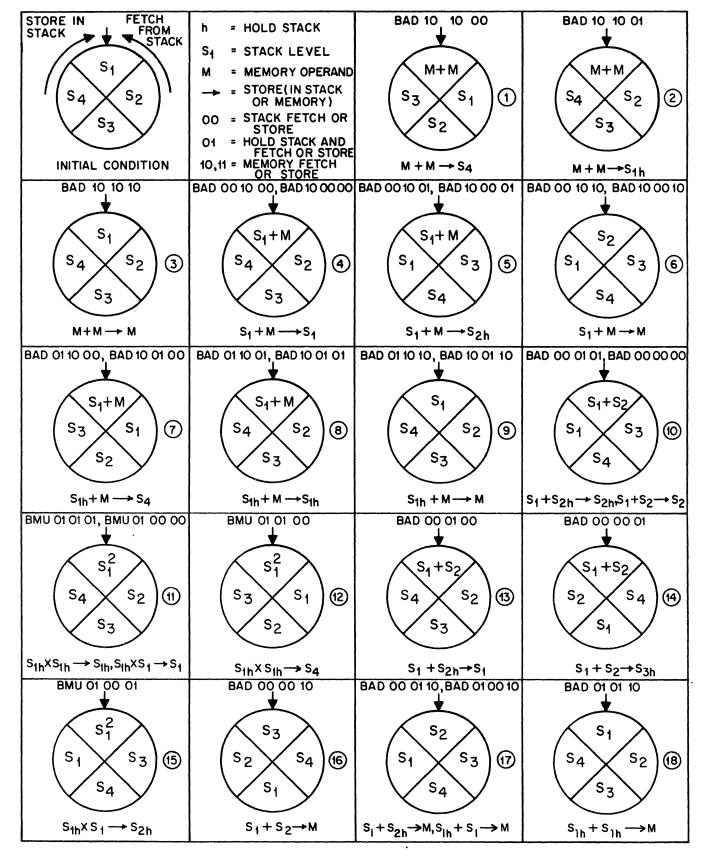

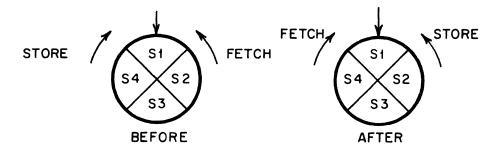

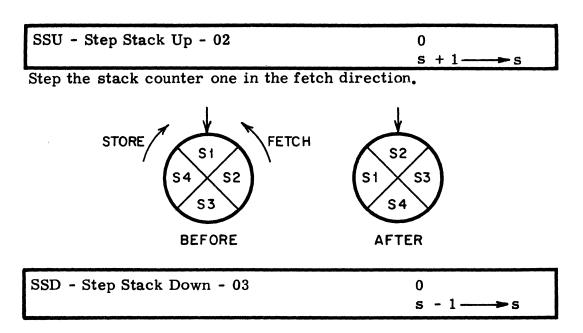

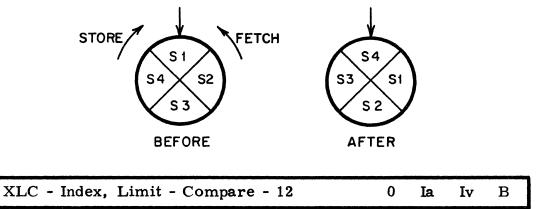

One of the features of the D825 is the fast access operand stack. Operands which are used again and again can be kept in the stack and addressed in a shorter time than would be required to get an operand out of memory. However, only the top of the stack is accessible at a given instant. The programmer must keep aware of what values are in each level of the stack and which level is currently accessible. The stack is effectively a four-word circular memory with an addressing counter. One of the four words is always being "pointed at" or is under the "read head". This circular concept and the pointer "read head" at the top of the stack are used in the examples shown in figure 2-1.

Whenever access is made to the stack, there is an option of either holding the stack or circulating the stack one step. Normal operation is to step the stack with each stack reference. The stepping operation follows all fetches from the stack and precedes a deposit made in the stack. As shown in figure 2-1 this stepping action is <u>counter-</u> clockwise following a fetch and <u>clockwise</u> preceding a deposit.

In the D825 operation syllable, address tag values 00 and 01 designate the stack as the intended operand source. Codes 10 and 11 refer to the memory. Code 00 designates normal stepping of the stack wheel and 01 designates that the stack be held (not stepped).

Figure 2-1 gives examples showing the resulting condition of the stack after all the possible combinations of stack operations. Examples 1 through 9 include one or more memory operands with the results stored in the stack or memory. In examples 10 through 15, both operands are from the stack and the results are stored in the stack. In examples 16, 17, and 18, both operands are taken from the stack but the results are stored in the memory. The initial condition for all the examples is shown in the upper left-hand corner.

#### INDEXING

D825 indexing implements two processes: (1) the modification of an address by adding the contents of one, two or three index registers to the address in order to obtain the effective address, and (2) the modification of the contents of an index register, comparing the

Figure 2-1. Operation of the D825 Operand Stack

modified contents of the index register with the contents of a specific limit register, and, depending on the results of the comparison, transferring program control to the appropriate location. The first process is performed automatically within an instruction, if desired, and can involve any or all of the three possible addresses of the instruction. The second process is performed by one specific instruction.

A special feature of the D825 is "multiple indexing", i.e., adding the contents of up to three index registers to the address. This is especially valuable in multicoordinate systems where it is necessary to maintain more than one separate index in computing the addresses of operands in an array.

Other features of the D825 indexing system are: (1) An ample quantity of index and limit registers (15 of each) is provided, and these are located in thin film, thus making them independent of program or data locations in memory. (2) The registers are 16 bits each, and therefore can contain an absolute memory address, i.e., not relative to any base address. (3) The contents of index and limit registers are unsigned quantities, but if a "negative address modifier" is desired, the two's-complement "positive address modifier" will serve the same purpose.

#### RELATIVE ADDRESSING AND INDIRECT ADDRESSING

The address syllable contains only 12 bits, in order that programs may be condensed. Sixteen bits, however, are required to specify an absolute machine address. Several techniques are available to the programmer to allow flexibility in addressing without the full sixteen bits.

Normally the program is contained in a block of contiguous memory locations, and programs for the D825 will in general be loaded this way. The beginning location of the block may be any location in memory. The address of this location is placed and retained in a thin film register called the BPR (Base Program Register). Any transfer of control in the program adds the literal specified in the branch syllable to the BPR and places this sum in the PCR (Program Count Register), another thin film register. In this way, transfers (branches) may be specified to locations relative to the beginning of the program block, and the program may be loaded and executed in any position in memory with no modifications of branch addresses and no wasted indexing.

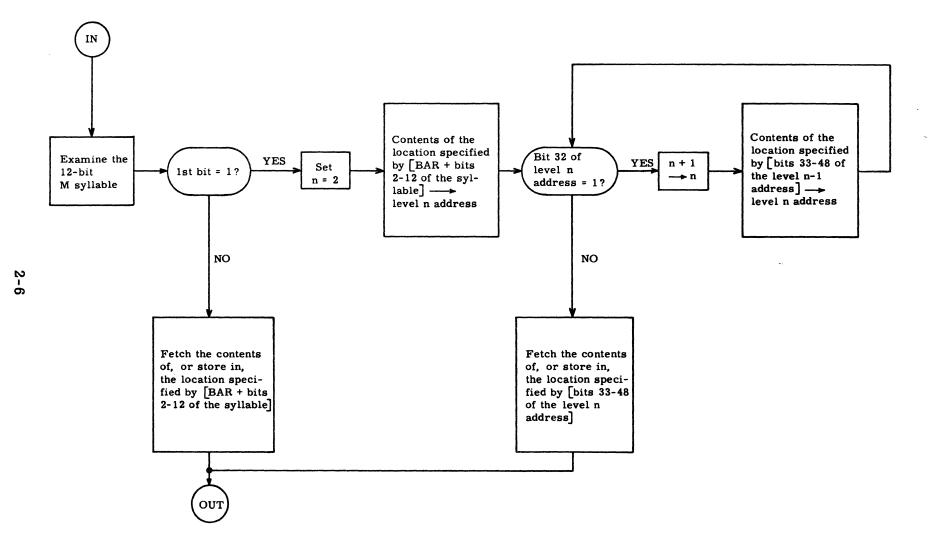

Figure 2-2. Flow Chart of Indirect Addressing

In the same way that instructions are contained in blocks, the constants and variable data may be placed together in a block of contiguous memory locations. This is a restriction of memory usage which is of considerable importance in being able to allocate any available space in memory to a program to be run. Eleven of the twelve memory syllable bits are used to specify the location of an operand relative to the beginning of the data block. The first location of the data block is placed in the thin film BAR (Base Address Register). When an operand memory reference is made, the eleven least significant bits of the memory syllable are added to the BAR to form the absolute address.

While only the first 2,048 words (direct address area) immediately following the location specified by the BAR are directly addressable, this restriction is trival due to the flexible indexing provided and the ability to indirect address beyond this area.

The most significant bit of the memory address syllable indicates, if it is a one, that the address is an indirect one. The 16 least significant bits of the location specified is then the absolute address of the operand or another indirect address. If the 17th-least significant bit of the location specified in the direct address area is a one, it indicates that the indirect address chain is to be continued; that is, the location specified in the direct address area is, in turn, an indirect address.

This indirect address chaining is provided for any number of levels. If indexing is specified for the operand in the instruction word, it is performed at the last level (i.e., at the completion of all indirect addressing). The flow chart (figure 2-2) describes the indirect addressing chain.

Indirect addressing can also be used to facilitate computer control of certain areas of the program by using a "snag bit." If the 18th-least significant bit of any level of addressing after the first is a "ONE"; an interrupt register bit will be set.

#### FIELD-DEFINED INSTRUCTIONS

A set of field-defined instructions is provided to facilitate code conversion and multiple use of a memory location. A field is defined to be a set of physically adjacent 6-bit characters in fixed locations in a word. The ability to perform simple arithmetic, manipulation, and comparison on such fields is available.

#### SUBROUTINE CONTROL

The ability to transfer control to a remote subroutine, and to return, is provided. This transfer of control enters a subroutine indirectly through a list of all subroutine addresses, and the location of this list is specified by the SAR (Subroutine Base Address Register). This feature eases the bookkeeping required to relocate a subroutine. An index register is set by the computer logic to allow the addressing of constants in the subroutine area. The ability to locate the workingstorage area of subroutines in the calling routine's direct address area is provided by the instruction logic. It is possible to have several computers independently and simultaneously execute a subroutine through the use of independent direct address areas. The facility of handling nested and recursive subroutines is considerable. The subroutine jump and return instructions are slightly more complex than those provided in other types of machines so that their use in a multiple computing system, with basic relative addressing, is enhanced.

#### INTERRUPT SYSTEM

A complex and comprehensive interrupt system is provided to facilitate the use of the computer in a control system. If an external request occurs, a computer will be interrupted at the completion of its current operation. The ability to automatically resume operation is provided. Computers may be interrupted by external requests, such as for I/O servicing, by internally generated signals such as the running-down of the clock, and by other computers. A computer which is interrupted is automatically placed in the control mode, in which it can execute a special class of instructions which are not available in the normal mode. The restrictions in the normal mode prevent changes to an AOSP by overwriting memory unexpectedly, modification of the interrupt controls, and initiating input/output for which the operating system would be unaware. These two modes of operation allow the operating system program, executed in the control mode to maintain its monitoring of all other programs.

A special type of interrupt occurs if power fails. All registers and controls are stored in non-volatile storage, and the system operation may resume when power is restored.

#### **SECTION 3**

#### THE STRUCTURE OF PROGRAM SYLLABLES

The structure of the 18 syllable types used in machine language programming of the D825 is presented in this section. The operator syllable, the index syllable and basic address syllables (memory and branch addresses) are given first, followed by the special-use syllables. The letter symbols preceding the syllable headings are used in Section 4, D825 Instructions, to represent the syllable structures given in Section 3. All syllables are 12 bits in length.

#### O-OPERATOR SYLLABLE

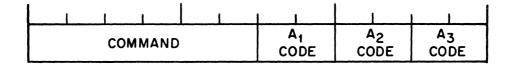

The operator syllable is the only one required for every instruction. It identifies any syllables that may follow and any stack usage for the instruction. This type of syllable is not indexable. The  $A_1$ ,  $A_2$ , and  $A_3$  codes identify the 3 possible "addresses" of the instruction as shown on the following page.

| Code | Definition                                                                                                |

|------|-----------------------------------------------------------------------------------------------------------|

| 00   | Stack (or no address)                                                                                     |

| 01   | Hold stack                                                                                                |

| 10   | An unindexed syllable follows                                                                             |

| 11   | An indexed syllable follows (index<br>syllable followed by any other<br>syllable, to which it is applied) |

|      | syllable, to which it is applied)                                                                         |

In the following example of the use of the operator syllable, the number contained in the top of the stack is squared, and the results are stored in the stack.

| BMU | 0 | 1 | 0 | 0 | 0 | 0 |

|-----|---|---|---|---|---|---|

#### X-INDEX SYLLABLE

| INDEX REGISTER | INDEX REGISTER | INDEX REGISTER |

|----------------|----------------|----------------|

| ADDRESS        | ADDRESS        | ADDRESS        |

The index syllable can be used with any other syllable except the index syllable itself, the operator syllable, or any syllable used in a repeated instruction (see RPT instruction). In all cases it is optional. The contents of up to 3 index registers can be applied to (added to the contents of) one syllable. If an index register contains the 2's complement of a number, use of this index register effectively subtracts the number from the contents of the syllable to which it is applied. When a syllable is indexed it is immediately preceded by its index syllable. An index register address equal to zero means no index. In indexed indirect-addressing, the contents of the index registers are applied to the last-level address only.

In the following example, the index syllable and memory address ayllable follow the operator syllable. If index register 15 (1111) contains b and index register 2 (0010) contains c, then the contents of the memory location specified by [a + b + c + BAR] is added to the top of the stack (floating-point in this case) and the results are stored in the stack.

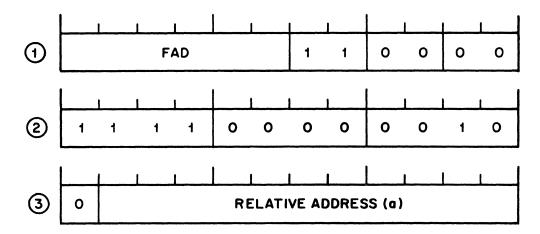

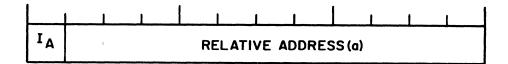

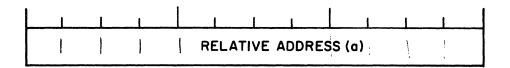

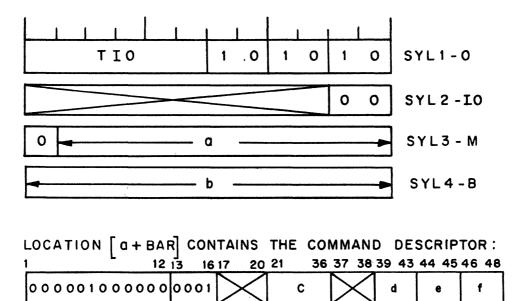

M-MEMORY ADDRESS SYLLABLE

The memory address syllable is used to address data words in memory. The relative address (a) is added to the contents of the base address register (BAR) to obtain the effective memory address. If  $I_A = 1$  this address is indirect, and the location specified by [a + BAR]then contains the next level address (the 16 least significant bits, with the 17th bit as an  $I_A$  bit). Note that each level of addressing, after the first, contains an absolute address, and therefore is not added to the BAR.

In this manual, an underlined memory symbol, <u>M</u>, represents the store address of the instruction, if any; memory symbols surrounded by parentheses, (M), represent optional syllables. If a memory syllable is omitted, the stack is the implied address; in any case, the  $A_1$ ,  $A_2$ , and  $A_3$  codes of the operator syllable define the address(es). For example, 0 (M) (M) (M) means operate on the contents of the locations specified by the first two addresses and store the result in the location specified by the third address. All three memory syllables are optional (i. e., can be replaced by stack references).

Since the first bit of the memory address syllable is a ONE in the example shown below, the memory address specified by [a + BAR] is indirect and contains the second level address. If a ZERO appears in the  $I_A$  bit of the second level address, the contents of the location specified by the second level address is added to the top of the stack and the results are stored in the stack. If the  $I_A$  bit is equal to ONE, this address also is indirect and contains the <u>next</u> level address; the indirect addressing chain will continue until an  $I_A$  bit is equal to ZERO.

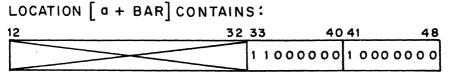

Second level (and subsequent level) absolute addresses are stored in bits 33 through 48 of the 48-bit memory word, and bit 32 is the  $I_A$  bit.

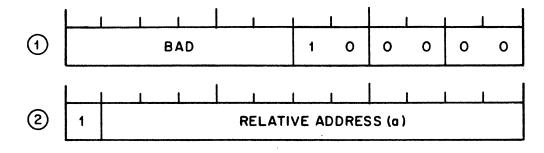

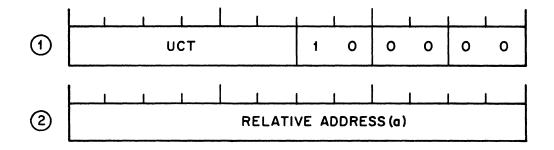

#### **B-BRANCH ADDRESS SYLLABLE**

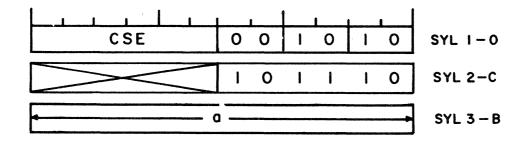

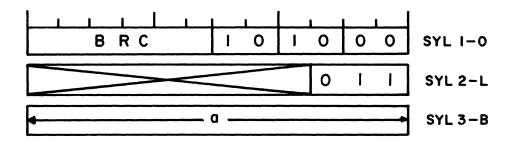

The branch address syllable is used to address program words in memory. The contents of the relative address (a) is added to the base program register (BPR) to obtain the effective branch address.

The following example is an unconditional transfer to the program word stored in the memory location specified by [a + BPR].

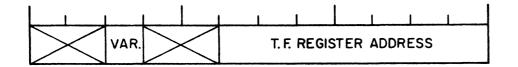

In all cases where a branch is used, the first syllable of the 48-bit memory location thus addressed <u>must</u> be the operator syllable of the next instruction to be performed. When a branch is made, the program count register (PCR) is automatically loaded with the address of the branch. **T-THIN FILM ADDRESS SYLLABLE**

The thin film address syllable is used for addressing all thin film registers, and applies only to the STF and LTF instructions described in Section 4.

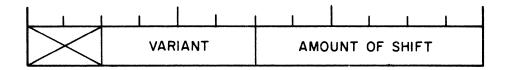

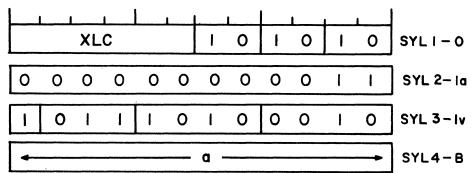

#### IV-INDEX INCREMENT VARIANT SYLLABLE

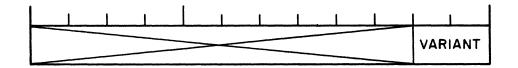

| VARIANT | INDEX REGISTER<br>ADDRESS | LIMIT REGISTER<br>ADDRESS |

|---------|---------------------------|---------------------------|

This syllable is used only with the XLC (index limit compare) instruction discussed in Section 4.

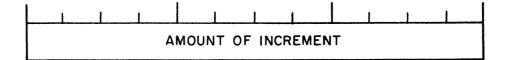

#### Ia-INDEX INCREMENT AMOUNT SYLLABLE

The index increment amount syllable is also used only with the XLC instruction and contains the amount to be added to, or subtracted from, the index register.

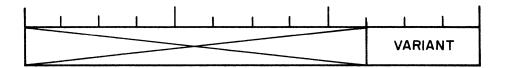

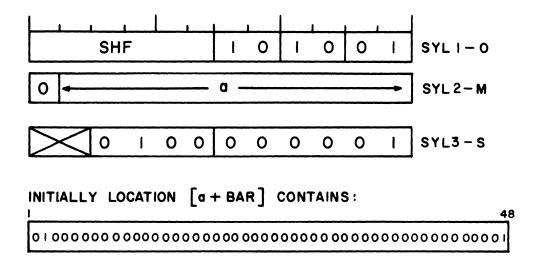

S-SHIFT SYLLABLE

The shift syllable gives the type of shift (variant) and the amount of shift, and is used only with the SHF instruction discussed in Section 4.

Vt-TRANSMIT VARIANT SYLLABLE

This syllable is used only with the TRM instruction for sign modification and rounding.

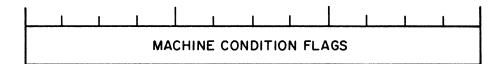

L-LOGICAL MACHINE CONDITION SYLLABLE

The logical machine condition syllable is used with the branch on condition (BRC) instruction to specify the conditions under which the branch is made.

## F-FIELD DEFINITION SYLLABLE

The field definition syllable is used with field-defined instructions as described in Section 4.

### C-CHARACTER SYLLABLE

The six-bit character of the character syllable is the actual character being searched for in the character search instruction, CSE.

#### Ja-SUBROUTINE JUMP ADDRESS SYLLABLE

The relative address contained in this syllable is added to the SAR to obtain the effective address of the start of the subroutine in the SRJ instruction.

Ji-SUBROUTINE JUMP INCREMENT SYLLABLE

This syllable is used with the SRJ instruction to increment the base address register (BAR) when a subroutine jump is made. Both the Ja and Ji syllables are required for each subroutine jump instruction.

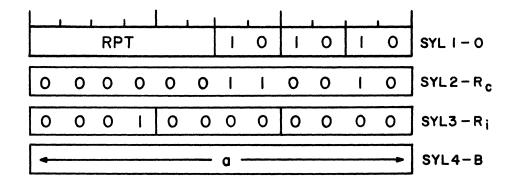

**Rc-REPEAT COUNT SYLLABLE**

The repeat count syllable contains the number of repetitions to be performed by the repeat instruction, RPT.

Ri-REPEAT INCREMENT SYLLABLE

| S <sub>2</sub> INCREMENT | S3 INCREMENT | S4 INCREMENT |

|--------------------------|--------------|--------------|

The repeat increment syllable is also used with the RPT instruction and gives the amounts by which the 2nd, 3rd, and 4th syllables are to be incremented with each repetition.

IO-I/O SYLLABLE

The IO syllable is used with the transmit input/output instruction, TIO, to select the I/O bus and to control I/O descriptors.

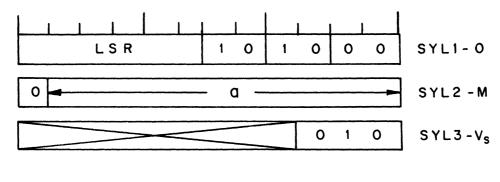

Vs-SPECIAL REGISTER AND COMPUTER INTERRUPT VARIANT SYLLABLE

This syllable is used only with the LSR instruction to designate the Computer Module to be interrupted, or for loading special registers.

#### SECTION 4

#### D825 INSTRUCTIONS

This section contains the D825 instructions and the rules for their use. They are arranged approximately in the order of importance and usage. Each instruction heading includes mnemonic code, instruction name, and octal code on the left, and the syllable layout on the right. Appendix D is an alphabetical index to the instructions in this section. D825 word structure is given in figure 4-1 and a glossary of symbols is given below.

Symbol Glossary

| A <sub>1</sub> , A <sub>2</sub> , A <sub>3</sub> | 1st, 2nd, and 3rd addresses                            |

|--------------------------------------------------|--------------------------------------------------------|

| (A <sub>N</sub> )                                | The contents of the address ${f A}_{f N}$              |

| >                                                | Store                                                  |

| , by A <sub>N</sub> ,                            | "as indicated by address $A_N^{\  \  "}$               |

| a:b                                              | If a is true then branch to b                          |

| S                                                | Stack Counter                                          |

|                                                  | Logical AND                                            |

| v                                                | Logical OR                                             |

| V                                                | Logical EXCLUSIVE OR                                   |

| (Ā <sub>N</sub> )                                | Logical (one's) COMPLEMENT the contents of address A N |

The conventions used in the above data words are:

"1" = minus "0" = plus

Numbers are represented in signed magnitude form.

Figure 4-1. D825 Word Structure

#### FIXED-POINT ARITHMETIC INSTRUCTIONS

| BAD - Binary Add - 65 | 0 | (M)                | (M)                | ( <u>M</u> )                 |

|-----------------------|---|--------------------|--------------------|------------------------------|

|                       |   | (A <sub>1</sub> )+ | (A <sub>2</sub> )- | $\rightarrow \overline{A}_3$ |

Algebraically add the contents of the location specified by  $A_1$  to the contents of the location specified by  $A_2$ ; store the result in the location specified by  $A_3$ .

NOTE 1: Overflow causes the program overflow flip-flop to be set, and in any event, the sum will be stored in the location specified by  $A_3$ . In the case of overflow the correct result (times  $2^{-1}$ ) can be obtained by program. Subtract out the end-around carry caused by over-flow, shift right 1, and add in the bit lost by overflow.

NOTE 2: If the result of an addition is zero, the sign is positive.

| $(M) (M) (M) (M) (A_1) - (A_2)$ | $(\underline{M})$<br>$\rightarrow A_3$ | (M)<br>(A <sub>2</sub> )- | I)<br>1)- | (M)<br>(A <sub>1</sub> | 0 | BSU - Binary Subtract - 64 |

|---------------------------------|----------------------------------------|---------------------------|-----------|------------------------|---|----------------------------|

|---------------------------------|----------------------------------------|---------------------------|-----------|------------------------|---|----------------------------|

Algebraically subtract the contents of the location specified by  $A_2$  from the contents of the location specified by  $A_1$ ; store the result in the location specified by  $A_3$ .

NOTE 1: Overflow causes the program overflow flip-flop to be set; in any event, the difference will be stored in the location specified by A<sub>3</sub>. In the case of overflow the correct result (times 2<sup>-1</sup>) can be obtained by program. Subtract out the end-around carry caused by over-flow, shift right 1, and add in the bit 1 lost by overflow.

NOTE 2: If the result of the subtraction is zero, the sign is positive.

|--|

Multiply the contents of the location specified by  $A_1$  by the contents of the location specified by  $A_2$ ; store the 47 high-order bits of the double-precision product, with sign, in the location specified by  $A_3$ , and leave the 47 low-order bits of the double-precision product, with sign, in the TFC register.

NOTE 1: If the result (the contents of the location specified by A<sub>3</sub>) of a multiplication is zero, the sign is positive. The TFC register, however, may contain a negative zero.

| BDV - Binary Divide - 60 | 0 | (M)               | (M)                 | ( <u>M</u> )    |

|--------------------------|---|-------------------|---------------------|-----------------|

|                          |   | (A <sub>1</sub> ) | ÷(A <sub>2</sub> )- | →A <sub>3</sub> |

Divide the contents of the location specified by  $A_1$  by the contents of the location specified by  $A_2$ ; store the 47-bit quotient with sign in the location specified by  $A_3$ , and store the 47-bit remainder with sign in the TFC register.

NOTE 1: The remainder takes the sign of the dividend.

- NOTE 2: At the end of the division process, if the absolute value of the divisor was not greater than the absolute value of the dividend, the program overflow flip-flop will be set, indicating quotient overflow.

- NOTE 3: If the quotient is zero, the sign is positive. The TFC register, however, may contain a negative zero.

FLOATING-POINT ARITHMETIC INSTRUCTIONS

Convert the contents of the location specified by  $A_1$  from binary to floating-point format, and store the result in the location specified by  $A_2$ .

- NOTE 1: If the contents of the location specified by  $A_1$  is zero, the operation is immediately terminated by inserting floating-point zero in the location specified by  $A_2$ . Floating-point zero is the smallest possible positive number,  $0 \ge 2^{-2047}$ , and appears as a negative exponent of all ones with a positive mantissa of all zeroes.

- NOTE 2: Otherwise, the contents of the location specified by A<sub>1</sub> is treated as a 48-bit signed fractional number with a zero exponent; the exponent is decreased as the number is normalized, and after normalization is complete, the 35bit mantissa is stored, together with the resulting exponent, in floating-point format. Floating-point format is defined, from left to right, as:

- sign of the exponent

- 11-bit exponent

- sign of the mantissa

- 35-bit mantissa

| FAD - Floating Add - 67 | 0         | (M)               | (M)                         | (M)             |

|-------------------------|-----------|-------------------|-----------------------------|-----------------|

|                         | Floating, | (A <sub>1</sub> ) | (M)<br>+ (A <sub>2</sub> )- | →Ā <sub>3</sub> |

Add the contents of the location specified by  $A_1$  to the contents of the location specified by  $A_2$ ; store the normalized floating-point sum in the location specified by  $A_3$ . Both operands are assumed to be in floating-point format.

- NOTE 1: After the addition is performed, mantissa overflow, if it occurs, is corrected, as is the exponent. If exponent overflow then occurs, the operation is terminated and the program overflow flip-flop is set. In this case the correct mantissa, with the overflow exponent (+.0----01), is inserted in the location specified by A<sub>3</sub>.

- NOTE 2: If the resulting mantissa (without sign) is zero, floatingpoint zero is inserted in the location specified by  $A_3$ , and the program under-flow flip-flop is set.

- NOTE 3: If the resulting mantissa is not equal to zero, normalization is performed until completed except that normalization is not performed in the case where the signs of the exponents of the two operands are different and the absolute value of the sum of the two exponents is greater than 2047. The exponent is then corrected; if exponent underflow should occur, the program underflow flip-flop is set and floating-point zero is inserted in the location specified by  $A_3$ .

- NOTE 4: Floating-point zero is the smallest possible positive number, or  $0 \ge 2^{-2047}$ , and appears as a negative exponent of all ones with a positive mantissa of all zeros.

| FSU - Floating Subtract - 66 | 0         | (M)               | (M)                   | ( <u>M</u> )    |

|------------------------------|-----------|-------------------|-----------------------|-----------------|

|                              | Floating, | (A <sub>1</sub> ) | - (A <sub>2</sub> ) - | ►Ā <sub>3</sub> |

Subtract the contents of the location specified by  $A_2$  from the contents of the location specified by  $A_1$ ; store the normalized floating-point difference in the location specified by  $A_3$ . Both operands are assumed to be in floating-point format.

- NOTE 1: After the subtraction is performed, mantissa overflow, if it occurs, is corrected, as is the exponent. If exponent overflow then occurs, the operation is terminated and the program overflow flip-flop is set. In this case the correct mantissa, with the overflow exponent (+.0----01), is inserted in the location specified by A<sub>3</sub>.

- NOTE 2: If the resulting mantissa (without sign) is zero, floatingpoint zero is inserted in the location specified by A<sub>3</sub>, and and the program underflow flip-flop is set.

- NOTE 3: If the resulting mantissa is not equal to zero, normalization is performed until completed except that normalization is not performed in the case where the signs of the exponents of the two operands are different and the absolute value of the sum of the two exponents is greater than 2047. The exponent is then corrected; if exponent underflow should occur, the program underflow flip-flop is set and floating-point zero is inserted in the location specified by  $A_3$ .

NOTE 4: Floating-point zero is the smallest possible positive number, or  $0 \ge 2^{-2047}$ , and appears as a negative exponent of all ones with a positive mantissa of all zeros.

| FMU - Floating Multiply - 63 | 0         | (M) | (M)                  | (M) |

|------------------------------|-----------|-----|----------------------|-----|

| · · ·                        | Floating, |     | × (A <sub>2</sub> )- |     |

Multiply the contents of the location specified by  $A_1$  by the contents of the location specified by  $A_2$ ; store the most significant portion of the floating-point double-precision product in the location specified by  $A_3$ , and store the least significant portion of the floating-point product in the TFC register (see Note 5). Both operands are assumed to be in floating-point format.

- NOTE 1: If the mantissa of either operand is not normalized, or if either one contains floating-point zero, the program nonnormalized flip-flop is set and the operation is performed.

- NOTE 2: When the exponents of the two operands are added, overflow or underflow can occur, in which case the FMU instruction is immediately terminated and the program overflow or underflow flip-flop is set. In the case of overflow, the absolute value of the mantissa portion of the location specified by  $A_1$ , together with the overflow exponent, is inserted in the location specified by  $A_3$ ; for underflow, floatingpoint zero is inserted in the location specified by  $A_3$ .

- NOTE 3: If the resulting mantissa (without sign) is zero, floatingpoint zero is inserted in the location specified by A<sub>3</sub>, and the program underflow flip-flop is set.

- NOTE 4: If the resulting mantissa is not equal to zero, it will be normalized one bit position, if necessary, and the exponent will be corrected. In correcting the exponent, underflow may occur, in which case floating-point zero is inserted in the location specified by A<sub>3</sub>, and the program underflow flip-flop is set.

- NOTE 5: The mantissa of the TFC register contains the thirty-five least significant bits of the product and the sign is the same as the sign of the mantissa of the result. The exponent of the TFC

register is the same as the exponent of the most significant portion of the product, except in the case where the result has been normalized one bit position. In this case, the exponent of the most significant portion will be one less than the exponent of the TFC register, and the least significant bit of the mantissa of the result will be the same as the most significant bit of the mantissa of the TFC register.

NOTE 6: Floating-point zero is the smallest possible positive number, or  $0 \ge 2^{-2047}$ , and appears as a negative exponent of all ones with a positive mantissa of all zeroes.

| FDV - Floating Divide - 62 | 0              | (M)                 | (M)                  | (M)             |

|----------------------------|----------------|---------------------|----------------------|-----------------|

|                            | 0<br>Floating, | (A <sub>1</sub> ) · | ÷ (A <sub>2</sub> )- | →Ā <sub>3</sub> |

Divide the contents of the location specified by  $A_1$  by the contents of the location specified by  $A_2$ ; store the floating-point quotient in the location specified by  $A_3$ , and store the floating-point remainder in the TFC register. Both operands are assumed to be in floating-point format.

- NOTE 1: If the mantissa of either operand is not normalized, or if either contains floating-point zero, the program non-normalized flip-flop is set and the operation is performed.

- NOTE 2: When the exponents of the two operands are subtracted, overflow or underflow can occur, in which case the FDV instruction is immediately terminated and the program overflow or underflow flip-flop is set. In the case of overflow, the absolute value of the mantissa portion of the location specified by  $A_1$ , together with the overflow exponent, is inserted in the location specified by  $A_3$ ; for underflow, floating-point zero is inserted in the location specified by  $A_3$ .

- NOTE 3: If the mantissa of the quotient (without sign) is zero, floatingpoint zero is inserted in the location specified by  $A_3$ .

- NOTE 4: Quotient overflow of 1 bit, if it occurs, is automatically corrected, as is the exponent. If exponent overflow then occurs, the operation is terminated and the program overflow flip-flop is set. In this case the correct mantissa,

with the overflow exponent (+, 0 - 01) is inserted in the location specified by A<sub>3</sub>. Quotient overflow resulting from non-normalized operands will cause the program overflow flip-flop to be set. Automatic mantissa and exponent overflow correction of 1 bit still occurs, but all other overflow bits are lost.

NOTE 5: The TFC contains the 35 bit remainder, right justified, with the sign of the dividend and a zero exponent.

This comparison test can be avoided by using the following equation: The correct remainder exponent = 2(dividend exponent) - (34 + divisor exponent + quotient exponent).

NOTE 6: Floating-point zero is the smallest possible positive number, or  $0 \ge 2^{-2047}$ , and appears as a negative exponent of all ones with a positive mantissa of all zeroes.

#### **REGISTER MANIPULATION AND DATA MOVING INSTRUCTIONS**

|--|

Transmit the contents of the location specified by  $A_1$  to the location specified by  $A_2$ .

| TRM - Transmit Modified - 34 | 0 | (M)<br>(A <sub>1</sub> ), | V <sub>t</sub><br>by A <sub>2</sub> | (M)<br>₂,→A <sub>3</sub> |

|------------------------------|---|---------------------------|-------------------------------------|--------------------------|

|------------------------------|---|---------------------------|-------------------------------------|--------------------------|

Transmit the contents of the location specified by  $A_1$ , modified as indicated by the contents of  $A_2$ , to the location specified by  $A_3$ .

NOTE 1: The transmit variant syllable  $(A_2)$ , numbering the bits from left to right, is coded as shown on the following page.

| Bit:    | 1 -  | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10 | 11 | 12 | Operation Indicated                                                                       |  |  |  |

|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|----|-------------------------------------------------------------------------------------------|--|--|--|

|         | Bla  | nk                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    | 0  | 1  | The operation is transmit, with the sign set to plus.                                     |  |  |  |

|         |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    | 1  | 0  | The operation is transmit, with the sign set to minus.                                    |  |  |  |

|         |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    | 1  | 1  | The operation is transmit, with the sign changed.                                         |  |  |  |

|         |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1  | -  | -  | The operation is transmit, with the number rounded, and can occur with sign modification. |  |  |  |

| NOTE 2: | E 2: | Rounding is accomplished by testing the most significant<br>data bit (bit 2) of the TFC register. If it is a one, one is<br>added to the least significant bit-position of the number con-<br>tained in the location specified by A <sub>1</sub> . If overflow occurs<br>during round, the program overflow flip-flop is set and the<br>overflow result is stored in the location specified by A <sub>3</sub> .<br>Rounding is for fixed-point numbers. |    |    |    |                                                                                           |  |  |  |

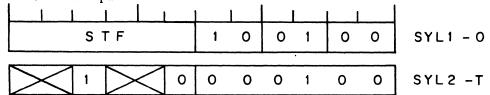

STF - Store Thin Film - 15  $0 T (\underline{M})$ Thin film,  $(\underline{A}_1) \rightarrow \underline{A}_2$

Store the contents of the thin film register (or group of registers) specified by  $A_1$  in the least significant end (or full word) of the location specified by  $A_2$ .

NOTE 1: The thin film syllable, numbering the bits from left to right, is coded thus:

Bits 1, 2, 4, and 5 are not used.

- Bit 3 if "one" indicates that more than one thin film register is addressed, and if "zero," indicates that one thin film register is addressed.

- Bit 6 if "one," indicates that 12-bit thin film registers are addressed, and if "zero," indicates that 16bit thin film registers are addressed.

#### Bits 6 through 12 are the thin film register address.

NOTE 2: If bit 3 of the thin film syllable is equal to 1, 48 bits, composed of four 12-bit or three 16-bit consecutive registers, are referenced. In this case, bits 11-12 of the thin film address are treated as zero. Although the operand stack registers are located in thin film, they are not normally addressed via the thin film instructions since they have special addressing controls associated with them. (See thin film map, Appendix C.)

NOTE 3: Example

Store the contents of index register number 4 in the 16 least significant bits of the top of the stack. Store the contents of index register number 5 in the next 16 bits of the top of the stack. Store the contents of index register number 6 in the 16 most significant bits of the top of the stack.

LTF - Load Thin Film - 30

$$(M)$$

T

$(A_1) \rightarrow A_2$ , thin film

Load the least significant end (or whole word) of the contents of the location specified by  $A_1$  into the thin film register (or group of registers) specified by  $A_2$ . (Seenotes 1 and 2 of STF for the thin film syllable description.)

NOTE 1: The IAR can only be loaded during control mode operation; all other thin film registers arê accessable in both modes.

| RVS - Reverse Stack - 06 | 0 |  |

|--------------------------|---|--|

|--------------------------|---|--|

Reverse the direction of the stack counter.

Step the stack counter one in the store direction.

Increase or decrease the contents of the index register specified by bits 5 thru 8 of  $A_2$ , by the amount specified in  $A_1$ . Then compare the contents of this index register with the contents of the limit register specified by bits 9 thru 12 of  $A_2$  for the condition(s) indicated by bits 2 thru 4 of  $A_2$ . If the condition(s) is (are) true, take the next instruction from the location specified by  $A_3$ ; otherwise, continue in sequence.

NOTE 1: The index variant syllable ( $A_2$ ), numbering the bits from left to right, is coded thus:

| Bit 1                                          | Bran<br>234                                                                                                                             | ich Condition                                                                                                                           | 5 - 8                                      | 9 - 12                                     |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--------------------------------------------|

| inc <b>rease</b> if 0<br>dec <b>rease</b> if 1 | $\begin{array}{ccccc} 0 & 0 & 0 \\ 0 & 0 & 1 \\ 0 & 1 & 0 \\ 0 & 1 & 1 \\ 1 & 0 & 0 \\ 1 & 0 & 1 \\ 1 & 1 & 0 \\ 1 & 1 & 1 \end{array}$ | none<br>equal<br>index > limit<br>index $\geq$ limit<br>index $\leq$ limit<br>index $\leq$ limit<br>index $\neq$ limit<br>unconditional | Index<br>register<br>number<br>(1 thru 15) | Limit<br>register<br>number<br>(0 thru 15) |

- NOTE 2: If limit register address zero is used, the contents of the specified index register is compared with the number "zero".

- NOTE 3: If an index register underflows when it is decreased or overflows when it is increased, the result is in the modulo 65, 536 form.

- NOTE 4: Example:

Decrease the contents of index register #10 by 3; compare the new contents of index register #10 with the contents of limit register #2, and if the contents of the index register are  $\geq$  to the contents of the limit register, take the next instruction from (unconditional transfer to) the location specified by [a + BPR]; otherwise, continue in sequence. SER - Store External Requests - 21

Store the external request lines in the least significant bits of the location specified by  $A_1$ . The external request lines are inputs to the D825 system whose 0 or 1 state serve to communicate a signal to a computer regarding external requests for input-output processing service.

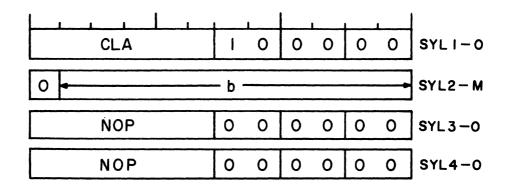

CLA - Clear - 20

$\begin{array}{c} 0 \quad (\underline{M}) \\ Zeroes \longrightarrow A_1 \end{array}$

0

(M)

Make the contents of the location specified by  $A_1$ , including the sign, equal to zero.

## UNPACKING AND PARTIAL WORD INSTRUCTIONS

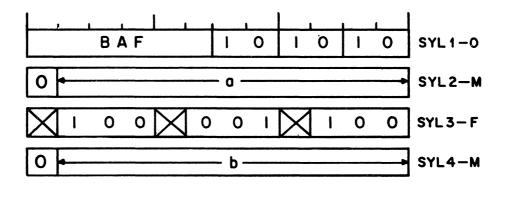

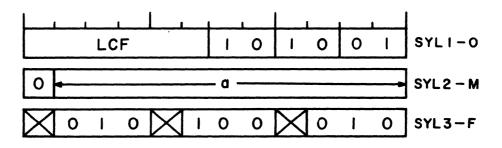

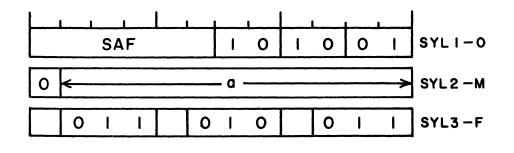

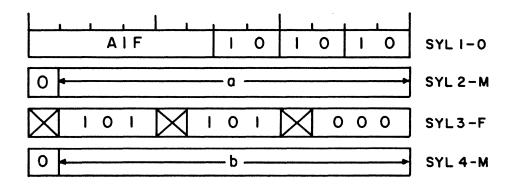

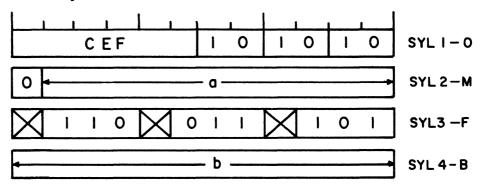

BAF - Binary Add, Field - 43

0 (M) F

(M)

Strip (extract) first the contents of the location specified by  $A_1$  and then the contents of the top of the stack, as indicated by the contents of A<sub>2</sub>. Perform a 48-bit unsigned addition on these two quantities and strip the result as indicated by the contents of A<sub>2</sub>. Clear a field of the contents of the location specified by A<sub>1</sub>, also defined by the contents of A<sub>2</sub>. Logically OR these two results, and adjust (shift) as indicated by the contents of A<sub>2</sub>; store this final result in the location specified by A<sub>3</sub>.

- NOTE 1: Note that the original contents of the top of the stack and of the location specified by  $A_1$  remain unchanged unless the contents of  $A_3$  specifies the same location as one of these.

- NOTE 2: The implied stack address mentioned above cannot be identified in the command syllable, since the instruction is essentially a 4-address instruction. The stack will be held, in order to make repeating of the instruction more useful. Note that this stack-read is included in the execution time of the instruction.

- NOTE 3: The special field syllable, numbering the bits from left to right, is defined thus:

- a. A field is composed of from 1 to 8 physically adjacent

6-bit characters; the character positions are numbers

0-7 from left to right.

- b. Bits 6-8 of the field syllable contain the length (number of characters) of the field which is to be stripped.

A length of zero means that the field to be stripped is a full 8-character word.

- c. Bits 10-12 of the field syllable contain the position number of the left-most character of the field to be stripped.

- d. Bits 2-4 of the field syllable contain the number of character positions through which the stripped field is to be shifted (adjusted). This shift is a single, right logical, end-around shift of 0-7 character positions.

- NOTE 4: The thin film C register is used to store the contents of A<sub>1</sub>.

INITIALLY LOCATION [ + BAR ] CONTAINS: 67 12 13 1819 24 25 30 31 36 37 42 43 48 U U U U W V W W 0 1 2 3 4 5 6 7

| 11                                     |                                                                                | Y THE TO                                              |                                                                                          |                                                                                          |                                                                                         |                                                                                    | 6374                                                                                  | 2 43 48                                                                                       |

|----------------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| Ĺ                                      | X                                                                              | 7 12<br>X                                             | X                                                                                        | 19 24<br>X                                                                               | 25 30<br>Y                                                                              | Z                                                                                  |                                                                                       | Z ]                                                                                           |

| L                                      | 0                                                                              |                                                       | 2                                                                                        | 3                                                                                        | 4                                                                                       | 5                                                                                  | 6                                                                                     | 7                                                                                             |

|                                        | conten<br>the top<br>Add th<br>the res<br>sition<br>corres<br>cified<br>end-ar | ese two<br>sult, aga<br>4, givin<br>sponding<br>by a+ | th the lo<br>stack (0<br>extract<br>ain extr<br>g 0000(<br>position<br>BAR ,<br>position | ocation<br>0000V00<br>ted port<br>ract a fi<br>V + Y)0<br>on of the<br>giving<br>as, and | specifie<br>0 and 00<br>ions, w<br>eld of le<br>00. Sto<br>conten<br>UUUUU(<br>store th | ed by<br>000Y00<br>ithout<br>ength 1<br>pre this<br>ts of th<br>V + Y)V<br>ae resu | a + BA<br>00, resp<br>sign, a<br>and st<br>s field i<br>ne locat<br>WWW,<br>ult in th | R and<br>pectively<br>nd from<br>arting po<br>in the<br>tion spe-<br>shift righ<br>e location |

| BSF - Bina                             | ary Sub                                                                        | otract, 1                                             | Field -                                                                                  | 42                                                                                       |                                                                                         | 0 (N                                                                               | <b>A)</b> F                                                                           | ( <u>M</u> )                                                                                  |

| The operation solute value cription an | ae of th                                                                       | e differ                                              | -                                                                                        |                                                                                          |                                                                                         |                                                                                    |                                                                                       |                                                                                               |

| LAF - Log                              | gical A                                                                        | ND, Fie                                               | ld - 47                                                                                  |                                                                                          |                                                                                         | 0 (M                                                                               | () F                                                                                  | ( <u>M</u> )                                                                                  |

| The operat                             | tion is                                                                        | logical .                                             | AND. S                                                                                   | See BAI                                                                                  | F for de                                                                                | sc <b>r</b> ipti                                                                   | ion <b>and</b>                                                                        | notes.                                                                                        |

| LOF - Log                              | gical O                                                                        | R, Field                                              | 1 - 44                                                                                   |                                                                                          |                                                                                         | 0 (1                                                                               | M) F                                                                                  | ( <u>M</u> )                                                                                  |